## Mobility degradation and series resistance in graphene field-effect transistors

Downloaded from: https://research.chalmers.se, 2021-08-31 12:25 UTC

Citation for the original published paper (version of record):

Jeppson, K., Asad, M., Stake, J. (2021) Mobility degradation and series resistance in graphene field-effect transistors IEEE Transactions on Electron Devices, 68(6): 3091-3095 http://dx.doi.org/10.1109/TED.2021.3074479

N.B. When citing this work, cite the original published paper.

©2021 IEEE. Personal use of this material is permitted.

However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

This document was downloaded from http://research.chalmers.se, where it is available in accordance with the IEEE PSPB Operations Manual, amended 19 Nov. 2010, Sec, 8.1.9. (http://www.ieee.org/documents/opsmanual.pdf).

# Mobility degradation and series resistance in graphene field-effect transistors

Kjell Jeppson, Life Member, IEEE, Muhammad Asad, and Jan Stake, Senior Member, IEEE

Abstract — Accurate device models and parameter extraction methods are of utmost importance for characterizing graphene field-effect transistors (GFETs) for predicting their performance in applications. For DC characterization, accurate extraction of mobility and series resistance is of particular concern. In this paper, we show how a first-order mobility degradation model can be used to separate information about mobility degradation and series resistance for a set of GFETs of different channel lengths. Data from a large set of top-gated GFETs based on chemical vapor deposited (CVD) graphene was analyzed to validate the proposed model and extraction procedures. For removing any uncertainties caused by observed device-to-device data variations due to the uneven quality of CVD graphene, the same methods were applied to a set of closely located bottom-gated GFETs found in literature. Those GFETs were designed for transfer length methods and fabricated on exfoliated graphene of homogenous quality. Similar mobility degradation behavior was observed for both sets of devices with the mobility being reduced to half for a voltage-induced charge carrier density of 1013 cm-2.

Index Terms— charge carrier mobility, graphene field-effect transistors, mobility degradation, series resistance.

#### I. INTRODUCTION

Graphene, a two-dimensional carbon material organized in a hexagonal pattern, holds a lot of promise for becoming the channel material of future field-effect transistors due to its high low-field mobility and extremely high charge-carrier saturation velocity [1]. For graphene field-effect transistors (GFETs) the low-field mobility is an important parameter for monitoring the quality of the channel material, and for predicting the GFET performance in circuit applications [2]. Accurate modeling of the current-voltage (I/V) characteristics is important for device design optimization, projection of performances, and exploration of analog/RF circuits providing new or improved functionalities [3].

The low-field mobility of a GFET is usually determined

This paragraph of the first footnote will contain the date on which you submitted your paper for review.

This work was supported in part by the European Union Graphene Flagship (Graphene Core2, grant 785219) and in part by Statens Tjänstepensionsverk (SPV).

The authors are with Chalmers University of Technology, Department of Microtechnology and Nanoscience, Terahertz and Millimetre wave Laboratory, 41296 Gothenburg, Sweden. (e-mail: kjell.jeppson@chalmers.se).

from drain current versus gate voltage measurements at low drain voltages, typically 10-100 mV, using a resistance model referred to as the Kim model [4]. This model, sometimes referred to as a "constant mobility model", assumes a constant mobility due to long-range impurity scattering, and a charge model including both impurity-induced residual carriers and gate voltage-induced carriers. However, it is generally expected that the mobility would decrease as the number of gate-induced carriers increases.

For MOSFETs, mobility degradation is a well-known phenomenon thoroughly investigated already in the mid-1960's. Of special relevance to this work is a remark made early on by Crawford who showed that mobility degradation had the same effect on the MOSFET I/V characteristics as the series resistance [5].

The analogy between GFETs and MOSFETs was discussed by Das Sarma et al. [6] who made comparisons between short-range scattering in GFETs and surface-roughness scattering in MOSFETs - two scattering mechanisms of increasing importance as the number of field-induced carriers increases.

For monolayer graphene, Zhu et al. found already in 2009, albeit in a low temperature context, that while mobility limited by Coulomb scattering was independent of carrier density, the mobility limited by short-range scattering was inversely proportional to carrier density [7].

By 2010 Dorgan et al. [8] had observed that for bottom-gated GFETs the charge carrier mobility was decreasing for carrier densities above  $2 \cdot 10^{12}$  cm<sup>-2</sup> also in the 300-500 K temperature range. Their observations of mobility degradation was later supported by observations made by Zhong et al. who found similar mobility degradation behavior both at 77 K and 300 K in their work on mobility extraction methods based on field-effect measurements [9, 10]. They also noted in passing that the fitting method developed by Kim et al. uses a higher contact resistance to compensate for the mobility degradation.

In this paper we will show how the series resistance extracted using the Kim model contains information about mobility degradation. Leaving further discussions of the scattering mechanisms in graphene to others, we propose a first-order mobility model based on two dominant scattering mechanisms similar to what has been used for MOSFET modeling for over fifty years. For this work we adopt an engineering approach; an approach from the parameter extraction and device modeling point of view that allows us to explain the experimental observation of why the series resistance, albeit designed to be constant from device-to-device, appears to depend on the gate length of the device. By showing how to separate information about mobility degradation from the series resistance, we hope to provide

new insights into GFET operation and modeling most helpful for device characterization engineers and circuit designers.

In the following sections we will discuss i) the proposed mobility model, ii) the two different sets of GFETs used to validate the model (one set being top-gated GFETs based on CVD graphene and the other set being bottom-gated GFETs on exfoliated graphene), iii) the parameter extraction methods used, iv) the experimental results found, and finally v) the validation of the mobility degradation model.

#### II. THEORY

Our intention with this section is to show that the Kim model [4] contains information about the mobility dependence on the charge carrier density. This information can be obtained by assuming the following first-order mobility model,

$$\mu = \frac{\mu_0}{1 + \theta \sqrt{V_0^2 + V_{GSO}^2}},\tag{1}$$

a model similar to the one successfully used for silicon MOSFETs for more than fifty years [6] [11] [12] [13]. The MOSFET model has been adapted for GFETs by using the transversal field model introduced by Kim et al. resulting in a carrier density

$$n = \frac{C_{ox}}{q} \sqrt{V_0^2 + V_{GSO}^2} \ . \tag{2}$$

In these equations,  $\mu_0$  is the long-range Coulomb scattering mobility,  $\theta$  the mobility degradation parameter,  $C_{ox}$  the gate oxide capacitance per unit area, q the electron charge, and  $V_0=qn_0/C_{ox}$  the residual voltage determined by the density of residual carriers  $n_0$  at the minimum conductivity Dirac point, [14]. Finally,  $V_{GSO}=V_{GS}-V_{Dirac}$  is the gate-to-source voltage overdrive of the Dirac voltage  $V_{Dirac}$ .

By inserting (2) into (1) we obtain

$$\mu = \frac{\mu_0}{1 + n/n_{ref}},\tag{3}$$

where  $n_{ref} = C_{ox}/(q\theta)$  is the carrier density for which the mobility is reduced to half. This mobility model is the result of two scattering rates being added using Mathiesen's rule, one being proportional to  $1/\mu_0$  and one being proportional to the carrier concentration, n.

Inserting the mobility degradation model into the linear region field-effect transistor equation upon which the Kim resistance model rests [15], yields

$$I_{D} = \frac{k\sqrt{V_{0}^{2} + V_{GSO}^{2}}}{1 + \theta\sqrt{V_{0}^{2} + V_{GSO}^{2}}} (V_{DS} - R_{C0} \times I_{D}), \qquad (4)$$

where the transconductance parameter  $k=(W/L)\mu_0C_{ox}$  is determined by the product of the geometry related width-to-length aspect ratio W/L of the channel, and the technology related parameter  $k'=\mu_0C_{ox}$ ,  $V_{DS}$  is the applied drain to source voltage, and  $R_{C0}=R_D+R_S$  is the sum of the drain and source series resistances to the external drain/source terminals including the resistances of the metal/graphene junctions and the access areas between the metal contacts and the channel.

Solving for  $I_D$  we obtain

$$I_{D} = \frac{kV_{DS}\sqrt{V_{0}^{2} + V_{GSO}^{2}}}{1 + (\underbrace{\theta + kR_{C0}}_{\theta_{eff}}) \times \sqrt{V_{0}^{2} + V_{GSO}^{2}}}.$$

(5)

This model equation has four model parameters, k,  $\theta_{eff}$ ,  $V_0$ , and  $V_{Dirac}$ , and is similar to the well-known models used for MOSFET parameter extraction [16, 17].

The modified Kim GFET resistance model now becomes

$$R_{DS} = \underbrace{\frac{1}{k\sqrt{V_0^2 + V_{GSO}^2}}}_{R_{chound}} + \underbrace{\frac{\theta}{k} + R_{C0}}_{R_C}. \tag{6}$$

This model equation shows that the parameter  $R_C$  in fact includes a combination of the real contact resistance  $R_{C0}$  and the mobility degradation effect  $(\theta/k)$ . For separating the two effects, measurement data is needed from devices of different gate lengths thereby taking advantage of the transconductance parameter k being geometry dependent while parameters  $\theta$  and  $R_{C0}$  are not. This will be explored in a following section based on measurement data from two sets of GFET devices, one set of bottom-gated GFETs on exfoliated graphene, and one set of top-gated GFETs on chemical vapor deposited (CVD) graphene.

#### III. DEVICE FABRICATION

For validating the proposed mobility model, data from experimental  $I_D$  vs  $V_{GS}$  GFET transfer curves were obtained from two sets of graphene field-effect transistors of different channel lengths. For this purpose, a test chip containing a large set of GFETs was fabricated using chemical vapor deposited (CVD) graphene transferred to the surface of a 1 µm SiO<sub>2</sub> layer grown by wet oxidation on a high-resistivity silicon substrate. Top-gated GFETs were fabricated using the same methods as described in detail in previous papers [2]. This includes the use of electron-beam lithography and reactive ion etching to shape the individual GFET active areas. Using an oxidized aluminum nucleation layer, a multi-stage atomic layer deposition process was used to form a 22 nm top-gate Al<sub>2</sub>O<sub>3</sub> dielectric (corresponding to  $C_{ox}$ =300 nF/cm<sup>2</sup>). Gate fingers 300 nm thick were formed by e-beam lithography using a 10 nm titanium adhesion layer. Finally, the source and drain microprobe pads were formed. All GFETs are 15 µm wide while gate lengths vary from 0.5 to 10 μm (0.5, 0.75, 1, 2, 4, 6, 8 and 10 µm). The use of e-beam lithography and reactive ion etching infers minimal deviations from the nominal gate dimensions. Transfer current/voltage (I/V) characteristics were obtained using Keithley 2612B dualchannel SourceMeter SMU and Cascade probe station using a drain voltage of 100 mV.

For comparison, data from a second set of GFETs was obtained from a paper by Zhong et al. [9, 10]. They used a compact test structure designed for the transfer length method (TLM) with back-gated GFETs of six different channel lengths ranging from 1 to 6 µm. As described in their paper, these GFETs were fabricated on mechanically exfoliated

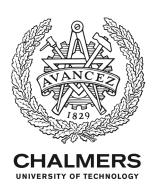

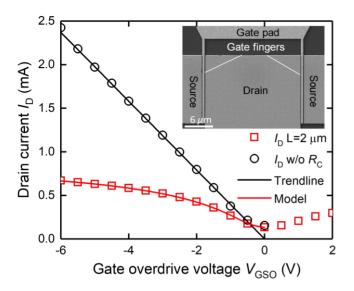

Fig. 1. The parameter extraction process includes finding and subtracting from the measured  $I_D$  vs.  $V_{GSO}$  data the series resistance  $R_C$  that gives the best straight line approximation for  $V_{GSO} >> V_0$ . Left-hand figure shows data for one example device from the set of top-gated GFETs from our laboratory, while the right-hand figure shows similar data for one of the TLM GFETs in [9]. Insets show SEM images of the GFETs - TLM structure inset courtesy of Zhiyong Zhang [9].

single-layer graphene placed on a heavily p-doped silicon substrate covered with 285 nm silicon oxide. The graphene sample was patterned into a 2.2  $\mu$ m wide strip using electron-beam lithography and reactive ion etching. Low resistance Pd/Au contacts were deposited by electron-beam evaporation and formed using lift-off technology.

#### IV. EXPERIMENTAL

Careful parameter extraction methods based on the Kim model were applied for extracting the transconductance parameter k and the series resistance  $R_C$  in regions where the influence of the residual carriers and the quantum capacitance was negligible, i.e. for  $V_{GSO} >> V_0$ . Figure 1 shows the transfer characteristics for one GFET of each set of devices. Also shown are the straight lines typical of field-effect transistors in their linear region obtained after subtraction of the contact resistance  $R_C$ . Based on an intelligent guess for the initial  $R_C$ value, the extraction process was fine-tuned to minimize the error yielding contact resistance values accurate within a few per cent. Inserted into the model, the extracted model parameters yielded excellent model fit to experimental data. We can also observe that while the narrow back-gated GFETs fabricated on high-quality graphene have well-defined Dirac points, the wide top-gated GFETs on CVD graphene seem to suffer from spatial variations of the Dirac point along the 15 μm width of the GFETs. However, the excellent linearity<sup>1</sup> of the I/V characteristics obtained after subtraction of the series resistance is a strong indication of the validity of the proposed mobility model.

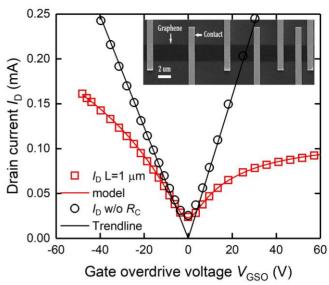

Figure 2 shows the results of the parameter extraction process for a set of twelve top-gated CVD GFETs and for the six bottom-gated GFETs of the TLM structure. The average mobility for the set of bottom-gated GFETs is 4990 cm<sup>2</sup>/Vs, while for the set of top-gated CVD GFETs it is 3300 cm<sup>2</sup>/Vs. The extracted resistance was found to increase with increasing gate length as shown in figure 2b. For the bottom-gated GFETs, the same excellent linear relationship of  $R_C$  vs. L from [10] could be repeated, while for the top-gated CVD GFETs variations in the graphene quality reflected in device-to-device variations of the contact resistance causes some uncertainties concerning the exact slope. Nevertheless, the extrapolated (L=0) contact resistance  $R_{C0}$  is well defined for both sets of devices. The extracted contact resistances are 190 and 400 Ωμm, respectively, for the bottom- and top-gated GFETs, where one reason for the difference could be due to the series resistance of the access areas of the top-gated GFETs.

Since the GFETs are designed for equal contact and access areas independent of channel length, we were rather confident at this point that mobility degradation was the reason for the series resistance varying with the gate length.

Figure 2c shows a plot of the extracted values for  $\theta_{\text{eff}}=kR_C$  vs. 1/L, where for comparison the values obtained for the bottom-gated GFETs have been rescaled to the same gate oxide thickness as that of the top-gated GFETs. A mobility roll-off parameter  $\theta$ =0.2 V<sup>-1</sup> was obtained, corresponding to a reference concentration  $n_{ref}$  of  $10^{13}$  cm<sup>-2</sup>, a value in excellent agreement with previous observations [8].

#### V. MODEL VALIDATION

Finally, it remains to validate the proposed model by comparing the results obtained with previously published observations. In their paper, Zhong et al. used their six GFET TLM structure for extracting the mobility as a function of the gate-overdrive voltage, or equivalently as a function of the

$<sup>^1</sup>$  Data points from the gate overdrive voltage range  $3V_{\rm o}{<}V_{\rm GSO}{<}14V_{\rm 0}$  with negligible influence of residual carriers were used to find the contact resistance  $R_{\rm C}.$  For almost all devices the linear fit resulted in R²>0.9985 - a strong indication of the validity of the proposed mobility model.

Fig. 2. Graphs showing the relationships between extracted model parameters and channel length for both sets of GFETs: a) mobility vs. L, b) resistance  $R_C$  vs. L, and c)  $\theta_{\text{eff}}$  vs. 1/L.

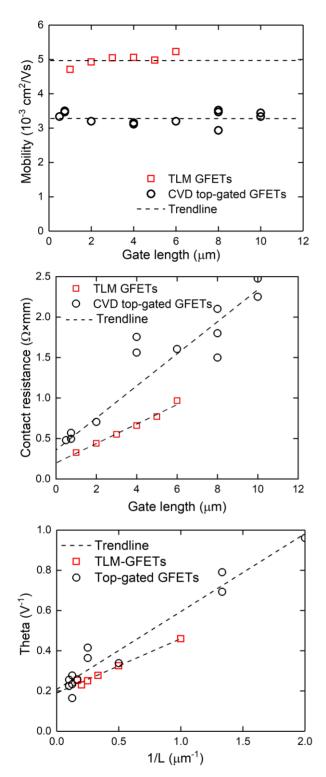

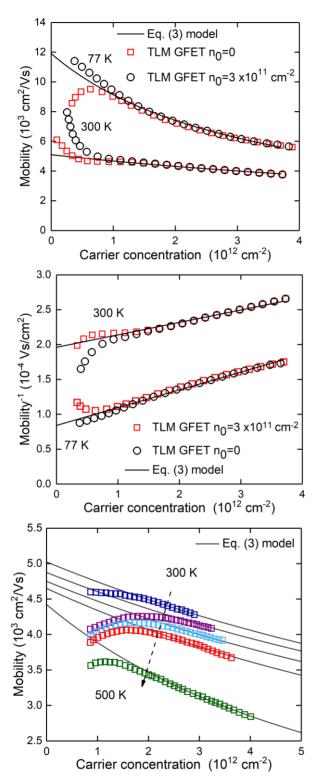

density of carriers, both at room temperature (300 K) and at 77 K. Figure 3a shows their extracted hole mobility together with our model from (3). Good agreement between their data and our model is shown for carrier densities much larger than the residual carrier density  $n_0$ , i.e. in the region used for extracting the mobility and contact resistance. However, as we approach

the Dirac point, the hole mobility extracted strongly depends on the density of residual carriers used in the charge model needed.

In further support of the mobility degradation model proposed in (3), figure 3b shows the inverse of the same hole mobilities versus carrier density. The excellent linearity shown strongly supports the proposed mobility model since the existence of other scattering mechanisms should have manifested themselves in the form of nonlinearities.

Figure 3c shows similar results published by Dorgan et al. showing the dependence of the mobility on the number of carriers using bottom-gated GFETs [8]. This graph shows our model fitted to their data at five different temperatures ranging from 300 to 500 K. Again, good agreement is shown for carrier densities in the region used for extracting the mobility and contact resistance. Whether the discrepancies close to the Dirac point between our model and their work solely depends on uncertainties in the charge model or on less efficient screening must be left for future investigations. Here, it is important to remember that Dorgan et al. noted that not all their samples displayed the dip in mobility at low charge density. In their attempt to study the transition from hole mobility to electron mobility at the Dirac point, they found uncertainties on the order of  $\pm 2000 \, \mathrm{cm^2/Vs}$ .

From the point-of-view of the circuit designer, we have to accept the fact that while the current at the Dirac point is given by the product of mobility and residual carrier density, it is difficult to separate the two. The use of a certain mobility model reduces the residual carrier density to the role of a fitting parameter compensating for possible errors.

### VI. CONCLUSIONS

In conclusion, we believe that the low-field mobility model proposed in this paper will pave way for a better understanding, and more accurate modeling, of graphene field-effect transistors. After having reviewed the relationship between mobility degradation and series resistance, we have shown how to separate the two effects yielding an average mobility degradation parameter and a correct series resistance for a set of GFETs of different channel lengths. Moreover, we hope this work will serve to remove the misconception of the Kim model being a "constant mobility model" only, since it actually contains first-order information about mobility degradation due to an increasing number of charge carriers induced by the transversal field.

#### VII. ACKNOWLEDGEMENT

The authors would like to thank professor Zhiyong Zhang of Peking University for supplying the figure 1b inset photo of the TLM structure. One of the authors (KJ) would also like to thank professor Seyoung Kim of POSTECH, Korea, for his efforts to quickly and most helpfully respond to email questions.

Fig. 3. Mobility vs. carrier density graphs. a) eq. (3) mobility model fitted to 300 K and 77 K data published by Zhong et al. [9] showing excellent model fit for carrier densities  $n>10^{12}$  cm<sup>-2</sup>, b) inverse of same mobility data plotted vs. carrier density showing excellent linearity for  $n>10^{12}$  cm<sup>-2</sup>, and c) eq. (3) mobility model fitted to data published by Dorgan et al. [8] at five different temperatures in the range from 300 K to 500 K in steps of 50 K.

#### **REFERENCES**

- F. Schwierz, "Graphene Transistors: Status, Prospects, and Problems," in Proceedings of the IEEE, vol. 101, no. 7, pp. 1567-1584, July 2013, doi: 10.1109/JPROC.2013.2257633.

- [2] M. Asad et al., "The Dependence of the High-Frequency Performance of Graphene Field-Effect Transistors on Channel Transport Properties," in *IEEE Journal of the Electron Devices* Society, vol. 8, pp. 457-464, 2020, doi: 10.1109/JEDS.2020.2988630.

- [3] D. Jimenez and O. Moldovan, "Explicit Drain-Current Model of Graphene Field-Effect Transistors Targeting Analog and Radio-Frequency Applications," in IEEE Transactions on Electron Devices, vol. 58, no. 11, pp. 4049-4052, Nov. 2011, doi: 10.1109/TED.2011.2163517.

- [4] S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, "Realization of a high mobility dual-gated graphene field-effect transistor with Al2O3 dielectric", Appl. Phys. Lett., 94, 062107, 2009, doi: 10.1063/1.3077021.

- [5] R.H. Crawford, MOSFET in Circuit Design, p. 68, McGraw-Hill Book Company (June 1967) ISBN-10: 0070134758.

- [6] S. Das Sarma, S. Adam, E.H. Hwang, E. Rossi, "Electronic transport in two-dimensional graphene", Rev. Mod. Phys., 83, pp. 407-470, 2011, doi: 10.1103/RevModPhys.83.407.

- [7] W. Zhu, V. Perebeinos, M. Freitag, and P. Avouris, "Carrier scattering, mobilities, and electrostatic potential in monolayer, bilayer, and trilayer graphene", Phys. Rev. B 80, 235402, 2009, doi: 10.1103/PhysRevB.80.235402.

- [8] V. E. Dorgan, M-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>", Appl. Phys. Lett. 97, 082112, 2010, doi: 10.1063/1.3483130.

- [9] H. Zhong, Z. Zhang, H. Xu, C. Qiu, and L-M Peng, "Comparison of mobility extraction methods based on field-effect measurements for graphene", AIP Advances 5, 057136 (2015), doi: 10.1063/1.4921400.

- [10] H. Zhong, Z. Zhang, B. Chen, H. Xu, D. Yu, L. Huang, and L. Peng, "Realization of low contact resistance close to theoretical limit in graphene transistors", Nano Research, 8(5), pp. 1669–1679 (2015) doi: 10.1007/s12274-014-0656-z

- [11] F. M. Klaassen, "A MOS Model for Computer-Aided Design", Philips Research Reports, 31, pp. 71-83, 1976.

- [12] N. D. Arora and G. Sh. Gildenblat, "A Semi-Empirical Model of the MOSFET Inversion Layer Mobility for Low-Temperature Operation", IEEE Trans. Electron Devices, 34, 1, pp. 89-93 (1987)

- [13] W. Liu, C. Hu, BSIM4 and MOSFET Modeling for IC Simulation, World Scientific Publishing, ISBN 10-981-256-863-8, 2011.

- [14] O. Habibpour, J. Vukusic and J. Stake, "A large-signal graphene FET model," in *IEEE Transactions on Electron Devices*, vol. 59, no. 4, pp. 968-975, April 2012, doi: 10.1109/TED.2012.2182675.

- [15] D. Schroder, "Series resistance, channel length and width, and threshold voltage" in *Semiconductor material and device* characterization, New York: Wiley, 1990, sec. 4.6, p. 208.

- [16] A. Ortiz-Conde, A. Sucre-González, F. Zarate-Rincón, R. Torres-Torres, R. S. Murphy-Arteaga, J. J. Liou, and F. J. García-Sánchez, "A review of DC extraction methods for MOSFET series resistance and mobility degradation model parameters", Microelectronics Reliability, 69, 2017, doi: 10.1016/j.microrel.2016.12.016.

- [17] P. R. Karlsson and K. O. Jeppson, "Extraction of series-resistance-independent MOS transistor model parameters," in IEEE Electron Device Letters, vol. 13, no. 11, pp. 581-583, Nov. 1992, doi: 10.1109/55.192846.