# MINING SECURE BEHAVIOR OF HARDWARE DESIGNS

Calvin Deutschbein

A dissertation submitted to the faculty at the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2021

Approved by: Cynthia Sturton Peng Huang Fabian Monrose Donald Porter Michael Reiter

© 2021 Calvin Deutschbein ALL RIGHTS RESERVED

# ABSTRACT

Calvin Deutschbein: Mining Secure Behavior of Hardware Designs (Under the direction of Cynthia Sturton)

Hardware presents an enticing target for attackers attempting to gain access to a secured computer system. Software-only exploits of hardware vulnerabilities may bypass software level security features. Hardware must be made secure. However, to understand whether a hardware design is secure, security specifications must be generated to define security on that design. Micro-architectural design elements, undocumented or under-documented features, debug interfaces, and information-flow side channels all may introduce new vulnerabilities. The secure behavior of each must be specified in order ensure the design meets its security requirements and contains no vulnerabilities. However, manual efforts can be overwhelmed by design complexity, and many hardware vulnerabilities, such as Memory Sinkhole, SYSRET privilege escalation, and most recently Spectre/Meltdown, persisted in product lines for decades despite extensive testing. An automated solution is needed to specify secure designs. Specification mining offers a solution by automating security specification for hardware. Specification miners use a form of machine learning to specify behaviors of a system by studying a system in execution. However, specification mining was first developed for use with software. Complex hardware designs offer unique challenges for this technique. Further, specification miners traditionally capture functional specifications without a notion of security, and may not use the specification logics necessary to describe some security requirements.

This work demonstrates specification mining for hardware security. On CISC architectures such as x86, I demonstrate that a miner partitioning the design state space along control signals discovers a specification that includes manually defined properties and, if followed, would secure CPU designs against Memory Sinkhole and SYSRET privilege escalation. For temporal prop-

erties, I demonstrate that a miner using security specific linear temporal logic (LTL) templates for specification detection may find properties that, if followed, would secure designs against historical documented security vulnerabilities and against potential future attacks targeting system initialization. For information–flow hyperproperties, I demonstrate that a miner may use Information Flow Tracking (IFT) to develop output properties containing designer specified information–flow security properties as well as properties that demonstrate a design does not contain certain Common Weakness Enumerations (CWEs).

# TABLE OF CONTENTS

| LIST OF TABLES x                              |                                               |                                      |      |  |

|-----------------------------------------------|-----------------------------------------------|--------------------------------------|------|--|

| LIST OF FIGURES xi                            |                                               |                                      |      |  |

| LIST O                                        | FABBR                                         | REVIATIONS                           | xiii |  |

| CHAPTER 1: INTRODUCTION 1                     |                                               |                                      |      |  |

| CHAPT                                         | ER 2:                                         | RELATED WORK                         | 8    |  |

| 2.1                                           | Autom                                         | atic Software Functional Correctness | 8    |  |

| 2.2                                           | Automatic Software Security   9               |                                      |      |  |

| 2.3                                           | 3 Automatic Hardware Functional Correctness 9 |                                      |      |  |

| 2.4                                           | 4 Manual Hardware Security 11                 |                                      |      |  |

| 2.5                                           | Automatic Hardware Security 1                 |                                      |      |  |

| 2.6                                           | Contextualizing this Thesis 1                 |                                      |      |  |

|                                               | 2.6.1                                         | Astarte                              | 12   |  |

|                                               | 2.6.2                                         | Undine                               | 13   |  |

|                                               | 2.6.3                                         | Isadora                              | 13   |  |

| CHAPTER 3: ASTARTE: MINING CISC ARCHITECTURES |                                               | 15                                   |      |  |

| 3.1                                           | Introdu                                       | action                               | 15   |  |

| 3.2 Properties                                |                                               | 17                                   |      |  |

|                                               | 3.2.1                                         | Example Properties                   | 17   |  |

|                                               | 3.2.2                                         | Control Signals for Preconditions    | 19   |  |

|                                               | 3.2.3                                         | Security Properties for Astarte      | 20   |  |

|                                               | 3.2.4                                         | Properties in Implementation         | 20   |  |

| 3.3 | Metho  | dology    |                                                           | 23 |

|-----|--------|-----------|-----------------------------------------------------------|----|

|     | 3.3.1  | Trace Ge  | eneration                                                 | 24 |

|     | 3.3.2  | Property  | Mining                                                    | 26 |

|     |        | 3.3.2.1   | Partitioning on Control Signals                           | 27 |

|     |        | 3.3.2.2   | Identifying Control Signals                               | 28 |

|     | 3.3.3  | Postproc  | essing                                                    | 29 |

|     |        | 3.3.3.1   | Intersection Across Trace Sets                            | 29 |

|     |        | 3.3.3.2   | Transitive Closure                                        | 30 |

|     |        | 3.3.3.3   | OS-Specific Values                                        | 31 |

|     |        | 3.3.3.4   | Identify Global Properties                                | 31 |

| 3.4 | Evalua | tion      |                                                           | 31 |

|     | 3.4.1  | Trace Da  | ıta                                                       | 32 |

|     | 3.4.2  | Control S | Signals                                                   | 33 |

|     | 3.4.3  | Achievin  | g Manageable Numbers of Properties through Postprocessing | 33 |

|     | 3.4.4  | Historica | ll Exploits                                               | 34 |

|     |        | 3.4.4.1   | Memory Sinkhole                                           | 35 |

|     |        | 3.4.4.2   | SYSRET Privilege Escalation                               | 35 |

|     | 3.4.5  | Manuall   | y Developed Properties                                    | 36 |

|     |        | 3.4.5.1   | Evaluating Astarte Coverage                               | 36 |

|     |        | 3.4.5.2   | Effectiveness of Control Signals                          | 36 |

|     |        | 3.4.5.3   | Implications of Postprocessing                            | 38 |

|     | 3.4.6  | Performa  | ance Expectations and Daikon                              | 39 |

|     | 3.4.7  | Operatin  | g System-Enforced Properties                              | 40 |

|     | 3.4.8  | Propertie | es in the Specification                                   | 42 |

| 3.5 | Limita | tions     |                                                           | 43 |

|     | 3.5.1  | Trace Re  | liance                                                    | 44 |

|     | 3.5.2  | Emulatio  | on Reliance                                               | 45 |

|       | 3.5.3  | Functional Properties                     | 45 |

|-------|--------|-------------------------------------------|----|

|       | 3.5.4  | Specification Logic and Abstraction Level | 46 |

| 3.6   | Concl  | usion                                     | 47 |

| СНАРТ | ER 4:  | UNDINE: MINING FOR TEMPORAL PROPERTIES    | 48 |

| 4.1   | Introd | uction                                    | 48 |

| 4.2   | Proper | rties                                     | 49 |

|       | 4.2.1  | Security Properties for Undine            | 50 |

|       | 4.2.2  | Evaluating Undine Properties              | 50 |

| 4.3   | Metho  | odology                                   | 51 |

|       | 4.3.1  | Trace Generation                          | 52 |

|       | 4.3.2  | Event Labels                              | 53 |

|       | 4.3.3  | Grammar of LTL Properties                 | 54 |

|       | 4.3.4  | Preprocessing                             | 55 |

|       | 4.3.5  | Property Mining                           | 56 |

|       | 4.3.6  | Postprocessing                            | 57 |

|       | 4.3.7  | Complexity                                | 57 |

| 4.4   | Evalua | ation                                     | 57 |

|       | 4.4.1  | Property Templates                        | 58 |

|       | 4.4.2  | Mining with Temporal Templates            | 58 |

|       | 4.4.3  | Labelling and Performance vs. Texada      | 59 |

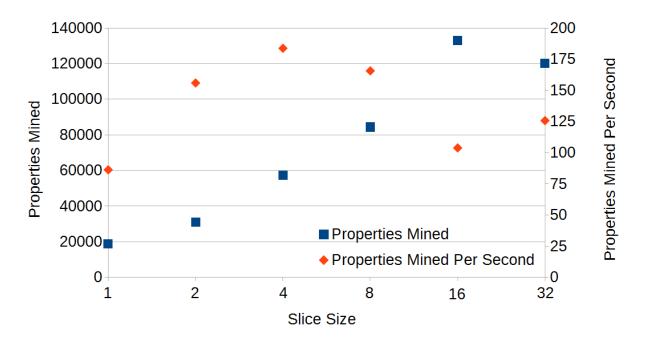

|       | 4.4.4  | Slicing and Performance                   | 61 |

|       | 4.4.5  | Example Exploit                           | 61 |

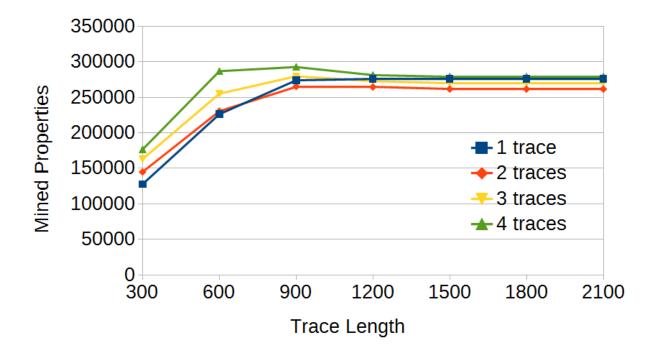

|       | 4.4.6  | Number of Properties                      | 63 |

| 4.5   | Limita | ations                                    | 65 |

|       | 4.5.1  | Trace Reliance                            | 65 |

|       | 4.5.2  | Uninteresting Properties                  | 66 |

|       | 4.5.3          | Library Limitations                              | 66 |

|-------|----------------|--------------------------------------------------|----|

|       | 4.5.4          | Labelling Limitations                            | 67 |

|       | 4.5.5          | Specification Logic                              | 67 |

| 4.6   | Conclu         | ision                                            | 67 |

| СНАРТ | 'ER 5:         | ISADORA: MINING FOR INFORMATION FLOW             | 68 |

| 5.1   | Introdu        | action                                           | 68 |

| 5.2   | 5.2 Properties |                                                  | 70 |

|       | 5.2.1          | Example Information Flow Properties              | 70 |

|       | 5.2.2          | Properties with Information Flow Tracking        | 72 |

|       | 5.2.3          | Expressing Conditions on Information Flow        | 73 |

|       | 5.2.4          | Properties and Common Weakness Enumerations      | 74 |

|       | 5.2.5          | Security Properties for Isadora                  | 76 |

|       | 5.2.6          | Properties in Implementation                     | 76 |

| 5.3   | Metho          | dology                                           | 78 |

|       | 5.3.1          | Generating Traces with Information Flow Tracking | 79 |

|       | 5.3.2          | Identifying All Flows                            | 80 |

|       | 5.3.3          | Mining for Flow Conditions                       | 81 |

|       | 5.3.4          | Postprocessing                                   | 82 |

| 5.4   | Impler         | nentation                                        | 83 |

|       | 5.4.1          | Generating Traces                                | 84 |

|       | 5.4.2          | Identifying Flows                                | 84 |

|       | 5.4.3          | Mining Flow Conditions                           | 84 |

|       | 5.4.4          | Postprocessing                                   | 85 |

| 5.5   | Evalua         | tion                                             | 85 |

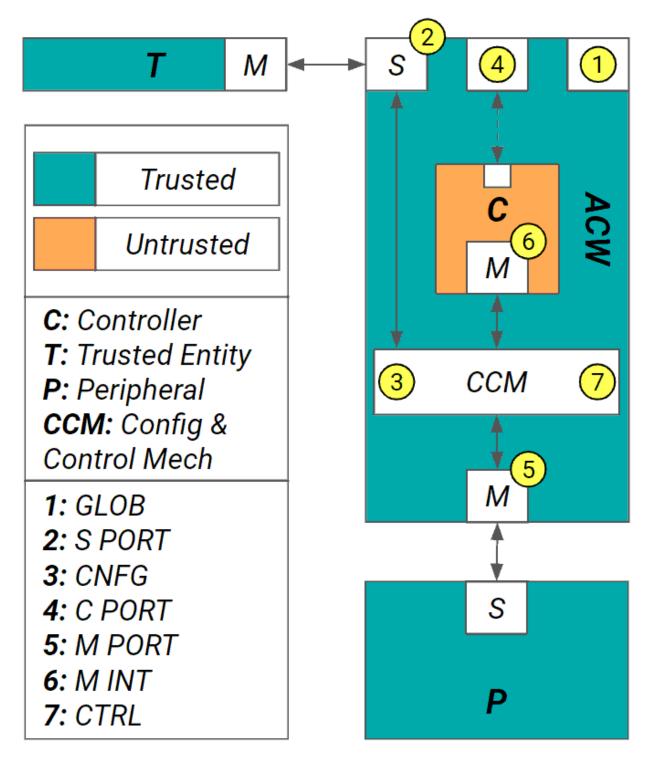

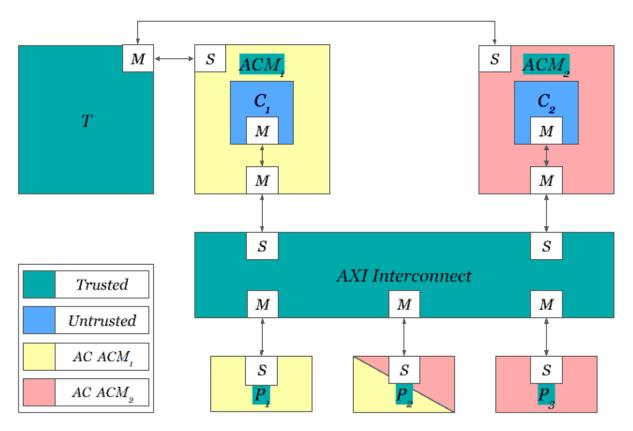

|       | 5.5.1          | Designs                                          | 86 |

|       | 5.5.2          | Time Cost                                        | 86 |

|        |        | 5.5.2.1   | Theoretical Gains to Parallelization  | 89  |

|--------|--------|-----------|---------------------------------------|-----|

|        | 5.5.3  | Designer  | Specified Security Properties         | 89  |

|        |        | 5.5.3.1   | Performance vs. Hyperminer            | 90  |

|        |        | 5.5.3.2   | Properties of SoCs                    | 91  |

|        | 5.5.4  | Automat   | ic Property Generation                | 92  |

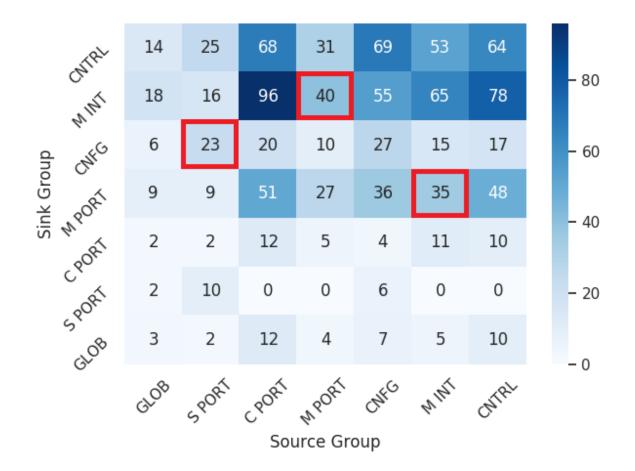

|        |        | 5.5.4.1   | ACM Conditional Information Flow      | 93  |

|        |        | 5.5.4.2   | PicoRV32 Conditional Information Flow | 94  |

| 5.6    | Limita | tions     |                                       | 98  |

|        | 5.6.1  | Trace Re  | liance                                | 99  |

|        | 5.6.2  | Function  | al Properties                         | 100 |

|        | 5.6.3  | Measurir  | ng Interference                       | 101 |

|        | 5.6.4  | Specifica | tion Logic                            | 101 |

| 5.7    | Conclu | sion      |                                       | 102 |

| CHAPT  | ER 6:  | CONCLU    | JSION                                 | 103 |

| REFERI | ENCES  |           |                                       | 104 |

# LIST OF TABLES

| Table 3.1 – Astarte partitions shown on the IOPL signal for instruction addl     | 28 |

|----------------------------------------------------------------------------------|----|

| Table 3.2 – Categorization of QEMU logged registers                              | 28 |

| Table 3.3 – QEMU unmodelled instructions by mnemonic                             | 32 |

| Table 3.4 – Control signals discovered by Astarte                                | 33 |

| Table 3.5 – Astarte properties' implied clauses per control signal.              | 34 |

| Table 3.6 – Astarte performance versus known historical bugs                     | 35 |

| Table 3.7 – Astarte performance versus manually specified properties.            | 37 |

| Table 4.1 – LTL templates over labelled events                                   | 59 |

| Table 4.2 – Properties mined using initialization template on Mor1kx.            | 60 |

| Table 4.3 – Time in seconds to mine the template library by miner implementation | 61 |

| Table 4.4 – Property numbers by postprocessing stage using Template 5            | 63 |

| Table 4.5 – Undine stage times in seconds per design                             | 64 |

| Table 5.1 – Various size measures of studied designs                             | 88 |

| Table 5.2 – Isadora performance versus manual specification, on the Single ACM   | 90 |

| Table 5.3 – The 14 CWEs considered for ACM                                       | 93 |

| Table 5.4 – Sampled Isadora properties on Single ACM                             | 95 |

| Table 5.5 – The 18 CWEs considered for PicoRV32                                  | 96 |

| Table 5.6 – Sampled Isadora properties on PicoRV32                               | 98 |

# LIST OF FIGURES

| Figure 3.1 – The grammar of Astarte properties                                               | 18 |

|----------------------------------------------------------------------------------------------|----|

| Figure 3.2 – Example properties                                                              | 19 |

| Figure 3.3 – All signals equal to zero or one during far jumps across code segments          | 21 |

| Figure 3.4 – All remaining signal equalities during far jumps across code segments           | 22 |

| Figure 3.5 – An overview of the Astarte workflow                                             | 24 |

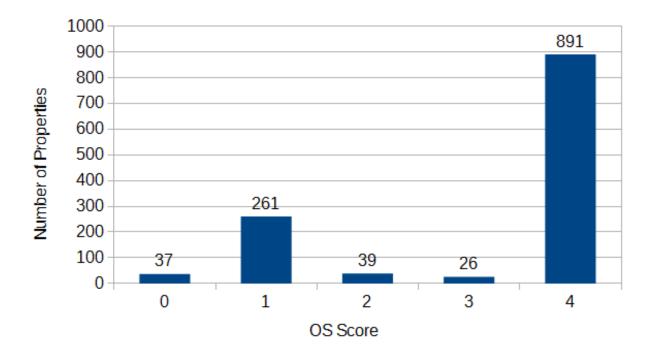

| Figure 3.6 – Distribution of properties by number of enforcing OSs                           | 40 |

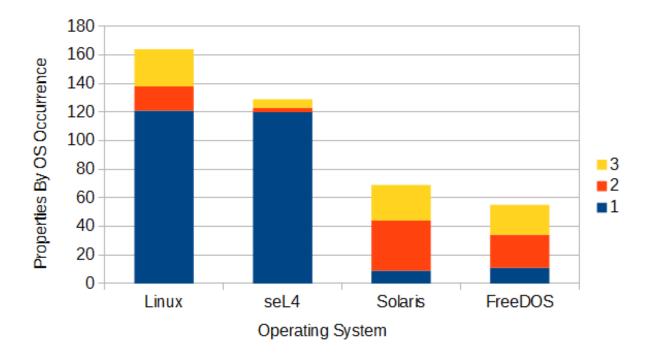

| Figure 3.7 – Distribution of partially OS enforced properties by enforcing OS                | 41 |

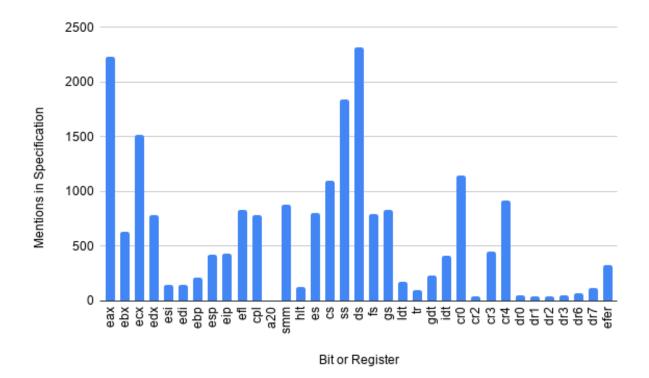

| Figure 3.8 – Signals by mentions in Intel documentation                                      | 42 |

| Figure 3.9 – Properties by relevant mentions in Intel documentation                          | 43 |

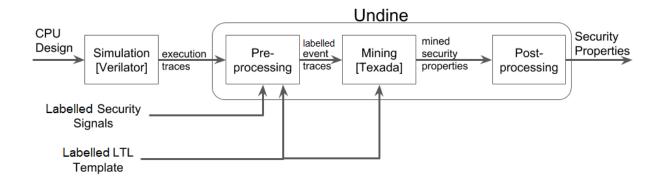

| Eisen 4.1 An energian of the He dia energial floor                                           | 50 |

| Figure 4.1 – An overview of the Undine workflow.                                             | 52 |

| Figure 4.2 – Commented excerpt of a trace of execution from the OR1200 processor             | 53 |

| Figure 4.3 – The grammar of labelled LTL properties                                          | 55 |

| Figure 4.4 – Sliced and labelled excerpt of a trace of execution from the OR1200 processor . | 56 |

| Figure 4.5 – Mining rate and quantity of output properties by slice size                     | 62 |

| Figure 4.6 – Steady state convergence of Undine output by trace data                         | 64 |

|                                                                                              |    |

| Figure 5.1 – A flow relation as formulated over IFT and original design signals              | 74 |

| Figure 5.2 – CWE 1272 expressed over generic signals                                         | 76 |

| Figure 5.3 – An example of an Isadora property, Case 154, over AKER                          | 77 |

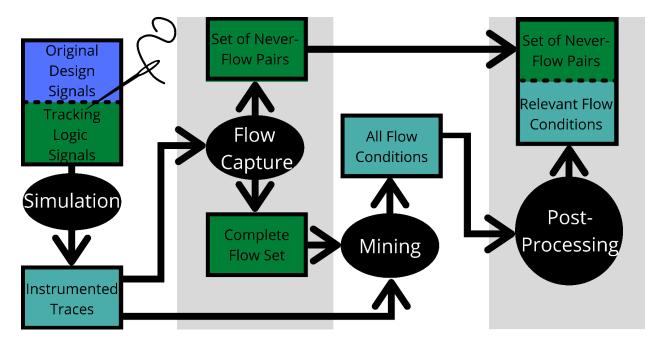

| Figure 5.4 – An overview of the Isadora workflow                                             | 79 |

| Figure 5.5 – Block diagram of the Single ACM, with the signal groups numbered                | 87 |

| Figure 5.6 – Block diagram of the Multi ACM                                                  | 88 |

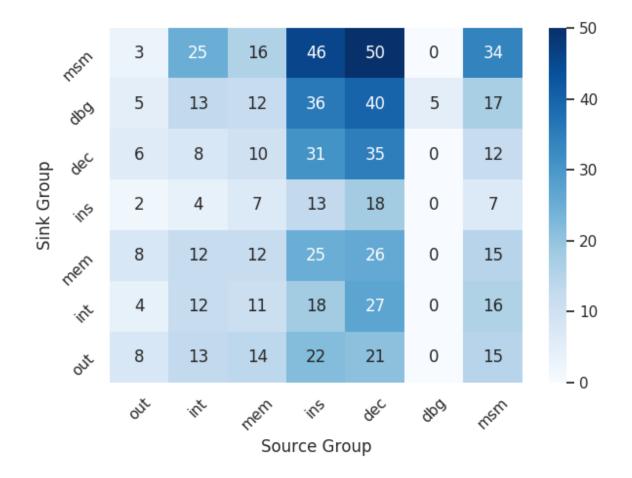

| Figure 5.7 – Group-to-group conditional flow heatmap for the Single ACM.                     | 95 |

| Figure 5.8 – | Group-to-group conditional flow heatmap for PicoRV32.     | 97  |

|--------------|-----------------------------------------------------------|-----|

| Figure 5.9 – | An example of an Isadora property, Case 144, over RISC-V. | 100 |

# LIST OF ABBREVIATIONS

| ACM  | Access Control Module            |

|------|----------------------------------|

| CISC | Complex Instruction Set Computer |

| CPU  | Central Processing Unit          |

| CWE  | Common Weakness Enumeration      |

| HDL  | Hardware Design Language         |

| IFT  | Information Flow Tracking        |

| ISA  | Instruction Set Architecture     |

| LTL  | Linear Temporal Logic            |

| OS   | Operating System                 |

| RISC | Reduced Instruction Set Computer |

| RTL  | Register Transfer Level          |

| SMM  | System Management Mode           |

| SoC  | System on a Chip                 |

| TLM  | Transcation Level Model          |

| VCD  | Value Change Dump                |

## **CHAPTER 1: INTRODUCTION**

Hardware presents an enticing target for attackers attempting to gain access to a secured computer system. Software-only exploits of hardware vulnerabilities may bypass software level security features. Hardware must be made secure. However, for designers to determine whether hardware is secure, security specifications must be generated for a given design. Micro-architectural design elements, undocumented or under-documented features, debug interfaces, and information-flow side channels all may introduce new vulnerabilities. The secure behavior of each must be specified in order to ensure the design meets its security requirements and contains no vulnerabilities. Yet manual efforts can be overwhelmed by design complexity. An automated solution is needed to specify secure designs. Mining secure behavior for hardware designs offers an automated approach to security specification, an important step toward achieving secure hardware design.

In hardware designs, weaknesses or vulnerabilities may be introduced, usually alongside new design features offering higher performance, that persist within product lines for years or decades. Consider the Memory Sinkhole vulnerability (Domas, 2015). Introduced to x86 designs in the mid-1990's with the new System Management Mode (SMM), it remained exploitable on x86 architectures until the Sandy Bridge-EP release in 2011. Despite affecting hardware for almost two decades, the vulnerability was first publicly demonstrated only in 2015. The vulnerable hardware was intended to be secure, and tested for security, but was not validated against a security specification that precisely disallowed the Memory Sinkhole's attack mechanisms. In Chapter 3, I show how mining can automatically generate such a security specification.

Mining can also promote best practice for the development of secure designs. For example, the Common Weaknesses Enumerations (CWEs) database describes high level design goals

for secure systems, often for software. Recently, as part of an industry-wide effort to secure hardware, CWEs describing many forms of secure design for hardware have been added to the database as well. CWEs may be specified over particular types of designs and represent best practices for generally secure design, such as debug and reset implementations. While assessing designs against CWEs relies on manual efforts, including reasoning about what security means for a given design, CWEs may offer an early line of defense against broad spectrums of attacks. Automated application of CWEs to designs could create designs secure against vulnerabilities to potential future attacks by eliminating common weaknesses. In Chapter 5, I show how mining can automatically generate a specification containing CWE–relevant properties for a given design.

Specification mining offers a powerful tool that designers may use as part of broader efforts to prevent future attacks. For the many designs for which there is no existing security specification, security specification mining can generate one. These generated specifications may then be used for validation efforts. Specification miners use a form of machine learning to specify behaviors of a system by studying the execution of said system, and these behaviors may include the secure operations of intentionally secure designs. In this work, I show how specification mining can address challenges of developing security specifications, including linear temporal logic (LTL) properties and hyperproperties. I design and implement a series of specification miners to create security specifications of hardware, and evaluate generated specifications against manually defined notions of security. Each miner uses unique methods developed for hardware security mining to define specific security goals.

Specification miners consider a design by taking as input traces of execution and producing as output lists of properties of the design. While traces may take different forms, they capture in some way the state of a design at different time points during a run of execution, such as in value change dumps (VCDs), which log every time the value held by a register or wire changes, or as in debug logs, which may log software-visible signals across clock cycles or control flow changes.

Specification miners may produce invariants, logical expressions that must hold over some design elements at all time points within a set of traces. Miners may also consider temporal properties, such as properties specified in Linear Temporal Logic (LTL), which define behavior across different time points. Miners may even consider hyperproperties, which require reasoning across multiple runs of execution of a design and therefore require reasoning about more than a single trace. Increasingly complex logics of specification allow defining security properties preempting correspondingly complex attack patterns. A temporal property may be used to secure a design against timing attacks, or a hyperproperty may be used to secure a design against information flow leakage.

Specification mining was pioneered for use on software, and state-of-the-art specification miners are often not intended for use on hardware designs. Early specification miners, such as DIDUCE (Hangal and Lam, 2002), which studied Java programs, or Perracota (Yang et al., 2006), which studied APIs, were specifically based around common errors in programs. Miners developed for hardware designs, which lack abstractions present in software such as types or functions, used different approaches to understand design behavior. Earlier hardware miners, such as IO-DINE (Hangal et al., 2005) and later on, GoldMine (Hertz et al., 2013), extracted only invariants, and often only specific kinds of invariants, such as one-hot encoding. These invariants were valuable for studying designs, but were not intended to capture all security agreements of the underlying hardware. Later hardware miners using more descriptive logics, such as SAM (Li et al., 2010) and A-TEAM (Danese et al., 2017) with temporal logics and Hyperminer (Rawat et al., 2020) with hyperproperties, generate valuable specifications more expressive than earlier tools. However, challenges remained to automatically generate properties such as temporal expressions over equalities between registers or information flows that may occur but only under certain conditions. And as expressiveness improves, mining hardware designs may produce far more properties than can be reasonably considered by human designers.

Mining for security introduces further challenges, as specification miners do not innately differentiate security and functional correctness. Especially when considering designs for which

no security specification exists, identifying which properties enact some implicit security agreement may require domain specific or even design specific solutions. Even when specifications cover some cases of insecure behavior identified on a given design, it is another matter entirely to compose these disparate examples into a notion of design–level security, much less a method for understanding secure design generally. Specification mining for security must engage with the question of what is, and is not, a security property.

Secure hardware behavior offers an ever-moving target for security researchers and hardware designers. This work must contend with what it means for a property to be a security property, or a specification to be a security specification. In the case of known attacks, such as Memory Sinkhole (Domas, 2015), security properties may be understood to be some specification mining output property that, if followed, would mean the attack could not be used against the design. Yet secure behavior with respect to known attacks does not necessarily mean a design is secure against all possible attacks. Vulnerabilities may only be classified as vulnerabilities after some attack is discovered, and many designs do not have complete functional specifications that are validated for correctness or complete enumerations of their security requirements in order to anticipate what forms an attack may take. Consequently, generated security specifications can, and in many cases should, contain properties for which there is no known attack or exploit. Further, secure behavior for hardware designs must also consider expectations of software, including operating systems, that run on the design. Hardware features, such as memory protections or privilege levels, may be implemented to service software-level requirements. When automatically generating specifications with the intent to support the security validation process, an automated process may target:

- Software expectations of hardware for security

- Historical examples of exploits

- Existing best practices

Each of these cases are considered in this thesis, often in conjunction.

While scaling to hardware and refining to security both represent challenges, specification mining remains well placed to specify hardware security. In fact, the additional complexities of hardware can in part be addressed by considering security cases specifically, and the comparative complexity itself makes use of automated tools more desirable. The usefulness of specification mining increases further when considering complex notions of security such as temporal properties or hyperproperties. This thesis demonstrates that specification mining can solve vital challenges for secure hardware designs by exploring three cases where security specifications would assist designers in securing hardware.

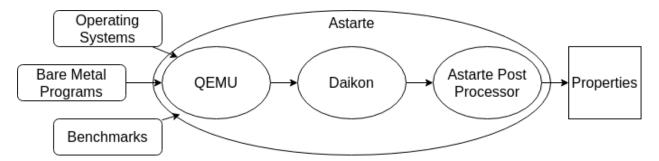

To demonstrate security specification mining on Complex Instruction Set Computer (CISC) architectures, I created Astarte, a specification miner that partitions the x86 design state space along control signals that govern secure behavior of the processor. Astarte works at the Instruction Set Architecture (ISA) level and may therefore be used for hardware designs that are closed source. By evaluating the output specification against security properties from a manual review of design documentation and additional properties capturing correct design behavior with respect to two historical attacks, Memory Sinkhole (Domas, 2015) and SYSRET privilege escalation (Dunlap, 2012), I show that the Astarte specifications contain properties that are security relevant in each of these cases. Astarte addresses software expectations of hardware for security by considering how operating systems interface with underlying hardware. Some hardware features, such as privilege levels and operating modes, are assumed to provide certain controls, and software may make assumptions of how underlying hardware manages internal state that introduce potential exploits. This was the case for SYSRET privilege escalation, where the SYSRET instruction had different specified behaviors on AMD and Intel designs. When software assumed the AMD behavior applied to Intel designs, the unanticipated hardware behavior allowed user-level attackers to elevate their privilege level. By applying Astarte to traces generated by different operating systems and comparing output properties across them, Astarte may provide insight into the security expectations software may have of hardware. In turn, hardware designers may implement or preempt design behavior related to these expectations to achieve the assumed notions of security.

Astarte is presented in Chapter 3 and is based on joint work with Cynthia Sturton (Deutschbein and Sturton, 2020).

To demonstrate security specification mining of temporal properties, I created Undine, a security specification miner that uses security specific LTL templates to mine security properties. Undine targets Reduced Instruction Set Computer (RISC) central processing unit (CPU) or System on a Chip (SoC) designs. As these designs are open source, Undine works at the Register Transfer Level (RTL). Undine is situated as an extension of the invariant detection methods of SCIFinder (Zhang et al., 2017) to temporal properties, and similarly is oriented toward describing secure design behavior against historical examples of exploits while also producing new properties. The output specification provides properties that, if followed, would prevent known and potential future attacks on hardware that can be defined before, after, and across system state transitions. I show an example exploit of privilege escalation that violates a generated temporal property specifying system behavior prior to reset in Section 4.4.5. Undine uses a labelling system of events to generate LTL properties over propositional variables including equalities between registers and over registers and values for RISC CPUs. Doing so results in output specifications with high coverage and density of historically established security properties. To produce these properties, Undine uses a library of labelled linear temporal logic templates useful across multiple designs, a valuable product of this line of research. Undine is presented in Chapter 4 and is based on joint work with Cynthia Sturton (Deutschbein and Sturton, 2018).

To demonstrate security specification mining of information flow properties, I created Isadora, a security specification miner that uses information flow tracking to mine information flow specifications. Like Undine, Isadora works at the Register Transfer Level (RTL) and is suitable for use on open source hardware designs including RISC CPUs and SoC designs. The output specification gives the information flow relations between all design elements, specifying whether flows may occur between two elements and, if so, specifying the design conditions under which information flow occurs. By evaluating the output specification against designer–provided sets of security properties and against high level Common Weakness Enumerations (CWEs), I show that

the Isadora miner finds security properties representing security efforts of individual designers for a specific design and security properties representing established best practices for security. The evaluation considers multiple designs, including an access control module, an SoC design, and a RISC-V CPU. This is presented in Chapter 5 and is based on joint work with Andres Meza, Francesco Restuccia, Ryan Kastner, and Cynthia Sturton (Deutschbein et al., 2021).

The thesis of this work is:

Specification mining can discover properties that can be used to verify the secure behavior of closed source CISC CPU designs, properties that can be used to verify the temporal correctness of CPU designs, and hyperproperties that can be used to verify that modules, SoCs, and CPUs have secure information flow.

The techniques developed and presented in this thesis can enable hardware designers to better specify their designs with respect to security, either fully automatically or alongside existing security efforts, and reduce the barriers to developing more secure hardware.

# **CHAPTER 2: RELATED WORK**

I organize work related to this thesis using three dichotomies:

- Manual versus Automatic

- Software versus Hardware

- Functional Correctness versus Security

# 2.1 Automatic Software Functional Correctness

Specification mining as a technique was introduced in Ammons et al. (2002) in which execution traces are examined to infer protocol specifications in the form of regular expressions. Weimer and Necula (2005) used both static and dynamic traces to filter out less useful candidate specifications. The Perracotta miner (Yang et al., 2006) tackled the challenges posed by having imperfect execution traces and by the complexity of the search space. DIDUCE (Hangal and Lam, 2002) studied software designs by instrumenting them to extract invariants online rather than offline. The Daikon Dynamic Invariant Detector (Ernst et al., 2007) learns properties that express desired semantics of a program running offline on execution traces.

While described as intended to discover program invariants, Daikon represents an ongoing and multi-decade research effort in dynamic invariant detection, and its underlying inference engine offers a powerful tool for exploration of hardware designs as well. For this reason, in this work Daikon is used within both the Astarte and Isadora framework. Astarte applies Daikon in multiple passes over trace sets to produce properties conditioned on extracted control signals. Isadora applies Daikon to trace slices identified by information flow tracking to define predicates that specify design conditions during information flows.

Specification mining has also been applied to temporal logics. The Javert miner (Gabel and Su, 2008a) finds temporal properties using small generic patterns that are composed soundly into larger specifications, and establishes this form of mining is NP-Complete. Reger et al. (2013) extends mining with patterns to parametric temporal specifications expressed as quantified event automata. The Texada General LTL Specifications Miner (Lemieux et al., 2015) accepts user-defined LTL templates and studies traces to produce instantiations of the LTL formula.

While first demonstrated for use in software engineering, the generality of Texada allows it to be easily extensible. Texada supports arbitrary templates and is helpfully maintained as an open source tool. For this reason, Texada is used within the Undine framework, where Texada's template enumerator is modified to incorporate a labelling system on trace events.

## 2.2 Automatic Software Security

In the software domain a number of technologies, including specification mining, have been applied to develop security specifications automatically.

AutoISES (Tan et al., 2008) uses security check rules and static analysis of source code to automatically generate security specifications of operating systems. Juxta (Min et al., 2015) also uses static analysis, in this case applied to the Linux file system and extensible to web browsers, network protocols, and other forms of software with multiple implementations. ClearView (Perkins et al., 2009) is a security autopatcher for Windows that works on binaries rather than source code with a specification mining component that studies normal behavior to devise error detectors. Yamaguchi et al. (2011) datamines API usage patterns which, when provided with a known vulnerability, enable automatic extrapolation of vulnerabilities over libraries.

# 2.3 Automatic Hardware Functional Correctness

Specification extraction has been applied to hardware, usually run in simulation, with different considerations made to handle hardware complexity. IODINE (Hangal et al., 2005) applied automatic specification generation to hardware by looking for instances of known patterns, such as one-hot encoded signals and req-ack. Reflecting the origins of the technique in the software domain, IODINE continues the research directions of both DIDUCE (Hangal and Lam, 2002) and Daikon (Ernst et al., 2007) from the software domain, applying optimizations from both online and offline software mining to generate results over hardware in an offline context.

Rather than rely on patterns, Chang and Wang (2010) use sequential data mining of simulation traces for automatic exploit detection specifically around potentially malicious inputs. Liu and Vasudevan (2013) perform mining at a higher abstraction level by studying Transaction Level Model (TLM) simulated traces.

El Mandouh and Wassal (2012) also use hardware specific patterns, but use static analysis to generate them before moving to a dynamic stage. GoldMine (Hertz et al., 2013) mines traces for specific patterns, and also includes manual efforts in a stage where designers rank assertions.

More recent work has focused on mining temporal properties from execution traces. Similar to techniques in software with temporal specification, Li et al. (2010) use predefined patterns and pattern chaining to mine temporal properties from traces. Liu et al. (2012) mine over traces specified at word level rather than bit level, and shows that experimentally this results in higher expressiveness, including on RISC CPU designs. Behavioral models (Danese et al., 2015) and power state machines of SoC designs (Danese et al., 2016) both may also provide useful abstractions to study hardware. The A–TEAM miner (Danese et al., 2017) is able to mine designs given LTL templates.

Most recently, Rawat et al. (2020) developed algorithms to mine hyperproperties expressed in HyperLTL using trace fuzzing. Their framework, Hyperminer, finds useful hyperproperties, including noninterference, an information flow property, over a small SoC design. In this respect, Hyperminer is similar to Isadora which produces information flow properties of small SoCs and other designs. By way of contrast, Isadora additionally describes flow conditions, or conditional interference patterns, which capture common security goals where design elements must interact but only with certain privileges, permissions, or under some other design condition.

#### 2.4 Manual Hardware Security

The first security properties developed for hardware designs were manually crafted. Security Checkers (Bilzor et al., 2011) uses manually defined hardware design language (HDL) assertions to generate hardware runtime monitors. SPECS (Hicks et al., 2015) also uses manual assertions but works on only security critical state at the ISA level to reduce overhead and run on a full RISC processor. Brown (2017) reviewed the Intel Software Developers Manuals (Intel, 2020) to manually define security critical properties at ISA level for x86. Recent case studies (Dessouky et al., 2019) have revealed the types of properties needed to find exploitable bugs in the design of a RISC-based system-on-chip.

### 2.5 Automatic Hardware Security

SCIFinder (Zhang et al., 2017) semi-automatically generates security critical properties by using machine learning to label generated invariants based on similarity to known bugs. Transys (Zhang and Sturton, 2020) is able to automatically generate security properties for a target design by translating known properties from some other design to analogous properties on the original design, but does require some initial set of known security properties.

#### 2.6 Contextualizing this Thesis

This thesis considers security specification mining with intent to support security validation of hardware designs. To do so, each miner takes lessons from across each dichotomy, and adapts them to work specifically on hardware security. For example, the Undine miner, which creates linear temporal logic (LTL) specifications, uses the Texada LTL Specifications Miner, and the Astarte miner, which discovers invariants using control signals, and the Isadora miner, which generates predicates that condition information flows, use the Daikon Dynamic Invariant Detector. However, Texada and Daikon are tools for automating software functional correctness. To use these tools for hardware security requires synthesizing insights from both applying specification mining to hardware, such as the patterns seen in IODINE and other miners, and from distinguishing security properties from functional properties, such as in SPECS and SCIFinder. In isolation, IODINE, A-TEAM, and other miners do not target security specifications, and SPECS and SCIFinder do not automatically generate information flow or LTL specifications or specifications for CISC designs. To automatically generate security specifications of hardware designs that cover known and potential future attacks, the work presented in thesis develops hardware security specification mining over different designs and logics of specification.

#### 2.6.1 Astarte

In the case of Astarte, which targets the Instruction Set Architecture level, existing tools including the Daikon Dynamic Invariant Detector readily produce trace invariants given some form of trace data. However, Daikon does not innately generate properties of the form  $A \implies B$ . Daikon allows users to specify possible predicates for the antecedent A, and will then generate implication properties which specify some consequent B. Many manual efforts to describe secure behavior of processor designs frequently contain implications (Bilzor et al., 2011; Hicks et al., 2015; Brown, 2017; Bilzor et al., 2012). One approach may be to specify every possible predicate A, but this approach is exceedingly costly over x86, the studied design, which contains too many possible antecedents to consider exhaustively. Further, this approach would produce many properties with no notion of their relevance to preventing future attacks.

The Astarte framework approaches the challenge of dynamic invariant detection over x86 using the notion of security critical control signals. Astarte iteratively performs invariant detection to restrict the space of candidate predicates and then uses these predicates to discover a property set expressive enough to contain manually developed security properties, including implications, yet excluding many redundant or uninteresting properties.

### 2.6.2 Undine

Undine approaches the challenge of generating LTL properties over up to three propositional variables to include register, subfield, bit, and delta values and equality between registers over gigabyte trace sets. Existing hardware miners could address subsets of these events or templates of up to two variables, and Texada could mine properties of this form generally but faced challenges with regard to complexity. Additionally, Undine targets output specifications that specifically prevent attacks. When approaching the trace sets needed to converge on a steady state of properties for open source RISC designs, Texada struggled to produce properties in under four hours due to the number of unique variables in RISC traces, which were approximately three times greater than the maximum of 1000 unique variables used to evaluate Texada by Lemieux et al. (2015). This is explored in depth in Section 4.4.3, where the Undine workflow is evaluated with unmodified and partially modified Texada instances to contextualize Undine with prior art on different templates.

Undine can also be considered in the context of temporal hardware miners. SAM (Li et al., 2010) extracts expressive properties using many scalability optimizations, including submodule and subtrace decomposition. SAM uses delta event traces which only capture register values, and extension to consider equality between registers would be nontrivial. A–TEAM extracts properties of the form  $G(\theta \implies \psi)$  by combining coverage analysis with data mining. By contrast, Undine is able to consider templates over three variables yet innately contains no coverage analysis. With respect to coverage for Undine, trace volume needed to converge to a steady set of properties was studied and is discussed in Section 4.4.6.

## 2.6.3 Isadora

In the case of Isadora, existing specification miners with the exception of Hyperminer were unable to produce information flow properties. Hyperminer produces noninterference properties over pairs of design elements using template enumeration (the technique used in Undine). An Isadora information flow specification contains two parts. The first part is the "Never-Flow Pairs" of Section 5.3.2 which are equivalently expressive to properties produced by Hyperminer using the noninterference template. The second part is the "Flow Conditions" which are equivalently expressive to declassification, a form of information flow property distinct from noninterference (and dynamic determinism, the other demonstrated Hyperminer template).

It is likely the case that Hyperminer template enumeration could be extended through further efforts to target declassification properties. This would be logically similar to property development in Isadora, which at a high level used IFT to determine interference patterns and from there composed declassification properties. This process and more comparisons to Hyperminer are discussed in Chapter 5.

# **CHAPTER 3: ASTARTE: MINING CISC ARCHITECTURES**

## 3.1 Introduction

Many existing property specification tools were developed for, and are applicable to, opensource programs with respect to functional correctness. Even when applied to hardware, tools often only work with open source designs, such as OR1200 or RISC-V. Considering the x86 instruction set architecture (ISA) introduces three main challenges. First, the size of the ISA makes even a semi-manual approach prohibitive; Second, x86 is closed-source and existing approaches to mining security specifications relied on access to both the source code and the developers' repositories, bugtracker databases, and email forums (Deutschbein and Sturton, 2018); Third, compared to today's RISC architectures, x86 offers a richer landscape of security features and privilege modes, increasing the number and complexity of the associated security properties.

To overcome these challenges, I developed Astarte, a fully automatic security specification miner for x86. On x86, the key challenge with mining security critical properties is automatically identifying those properties that are relevant for security, that if violated would leave the processor vulnerable to attack. In general, there is no fixed line separating functional properties from security properties. The environment in which a processor operates and the attacker's motivation and capabilities may move some properties across the security-critical boundary in either direction.

Prior work tackled this problem by analyzing existing design bugs and manually sorting them as exploitable or not exploitable (Zhang et al., 2017). However, this approach is labor intensive and does not easily scale to x86. Further, this approach requires knowledge of and access to the details of known design bugs culled from developers' archives, code repositories, and bugtacker databases, which are not available for the closed-source x86 designs.

Astarte uses a different approach. By mining properties that are conditioned on the state of the various control signals that govern security-critical behavior of the processor, Astarte need not rely on inaccessible documentation. The corresponding properties are by definition important for the correct and secure behavior of the processor, which in turn is important for the correct implementation of the security primitives that operating systems (OSs) and software rely on. In this respect, Astarte is inspired by prior, manual efforts (Bilzor et al., 2011; Hicks et al., 2015; Brown, 2017; Bilzor et al., 2012).

Astarte handles the complexity of the x86 ISA by independently considering the space of properties for each instruction preconditioned on the value of a single security-relevant control signal. In other words, the mining partitions the specification generation problem with respect to each control signal. It is perhaps counter-intuitive that this approach works; it would seem necessary to consider all possible combinations of all security-relevant signals for every instruction in order to produce meaningful security properties. Yet, compared to prior manual efforts and to known bugs in shipped x86 products, the specification output of Astarte independently produces valuable properties using this technique.

The Astarte framework relies on two existing tools, the QEMU emulator (Bellard, 2005), which creates traces over x86, and the Daikon Dynamic Invariant Detector (Ernst et al., 2007), a popular tool for mining specifications of programs. Using the QEMU debug interface, I generated ISA level traces of x86 running four distinct operating systems and bare metal programs. Astarte incorporates a custom front end for Daikon to interpret the QEMU debug logs as trace data and mine invariants over these emulated runs. Daikon, a major research and software engineering effort extending for decades, offers modular interfaces for this custom front end and a powerful internal inference engine. Together these provide a strong foundation for scalability to studying the x86 architecture.

When run on emulated traces, Astarte produces roughly 1300 properties. I evaluated these properties against 29 security properties manually discovered by Brown (2017). Of the 29 identified security properties, Astarte generates 23, and the remaining 6 require invariants over pro-

cessor state unimplemented in QEMU. Astarte also generates properties that, if followed, would prevent two bugs in x86 documented in public domain, Memory Sinkhole (Domas, 2015) and SYSRET privilege escalation (Dunlap, 2012).

By performing trace generation over multiple operating systems and bare metal execution, I show Astarte can also differentiate properties enforced by the processor from those that must be enforced by the operating system. This analysis also provides insight into properties that are not specified, but that operating systems have come to rely on.

This chapter presents a security specification miner for closed-source, x86 architectures and its evaluation for the Intel x86 (Ivy Bridge) processor. Astarte demonstrates:

- partitioning specification ming using security-relevant control signals;

- automatically identifying the control signals of interest;

- · differentiating processor-level properties and operating system-level properties; and

- identifying de facto security-critical properties upon which operating systems rely.

## 3.2 Properties

The Astarte framework generates properties written over instruction set architecture (ISA) level expressions conditioned on current instructions and automatically discovered control signals. This section discusses the structure of these properties and describes which properties are considered to be security properties for this framework.

# 3.2.1 Example Properties

Astarte properties describe the constraints and behavior of ISA level state. The grammar is described in Figure 3.1, where insn represents the predicate for some specific instruction and sig represents the valuation of a signal. Signals here can represent software visible registers

$$\begin{split} \phi &\doteq \mathtt{insn} \wedge e_1 \implies e_2 \mid e_1 \implies e_2 \mid \mathtt{insn} \implies e \\ e &\doteq \mathtt{sig}_1 = \mathtt{sig}_2 \mid \mathtt{sig} = n \mid \mathtt{sig} \in \{n_1, n_2, n_3\} \mid \mathtt{sig} = orig(\mathtt{sig}) \end{split}$$

Figure 3.1: The grammar of Astarte properties

or individual bits within some specific registers. The process of determining individual bits for consideration is detailed in Section 3.3.2.2.

Each property produced by Astarte describes the processor state as an implication. The antecedent may be a predicate specifying that the property describes processor state during the execution of a particular instruction, specifying that some expression over signals holds, or specifying both. For brevity, these antecedent predicates will be referred to as preconditions. The consequent specifies an expression over signals. Expressions over signals, in either antecedents or consequents, may be:

- equalities between the values of two signals,

- equalities between the value of a signal and a constant,

- a signal's value falling within a set of up to three constants, or

- equality between the current value of a signal and the previous value of the same signal, which is specified using *orig*().

For example, the property in Figure 3.2a states that when the in instruction executes, the I/O privilege level (IOPL, as given by bit 13 of the EFLAGS register) must be greater than or equal to the current privilege level (CPL, as given by bit 13 of the Code Segment Pointer). In this case, this is an property found in the context of a single instruction.

A property may refer to the value held by a bit or register both before and after the relevant instruction executes by using an *orig*() expression to describe the original value before execution. For example, the property in Figure 3.2b refers to the state of the Code Segment Pointer (CS)

before and after execution of the jmp\_far instruction. It states that if a new CS is loaded by a far jump, then the privilege levels of the other current segment pointers, the Stack Segment Pointer (SS) and Data Segment Pointer (DS), must be equal. Here DPL denotes 'descriptor privilege level' and is the privilege of a given segment pointer; the CPL is simply the DPL for the CS. In this case, this is a property found using a precondition that the CS value after instruction executes must differ from the CS prior to execution. Of note, while near and far jumps are not differentiated by name in emulation, the Astarte trace encoding stage inspects opcodes to differentiate near and far cases, and appends the \_far suffix at this time.

in → EFL[13] ≥ CS[13]

(a) After the in instruction executes IOPL must be greater than CPL

(jmp\_far ∧ CS ≠ orig(CS)) → DS.DPL = SS.DPL = CPL

(b) If a far jump loads a new code segment pointer, privilege levels of segment pointer must be equal.

Figure 3.2: Example properties

Given the constraints of generating traces over a closed source design, the example properties here describe values as reported through emulation debug interfaces. Astarte assumes the correctness of emulation. Prior work, such as Fast PokeEMU (Yan and McCamant, 2018), addresses directly the correctness of CPU emulation.

## **3.2.2** Control Signals for Preconditions

Key to the working definition of security property for Astarte is the notion of a control signal. Within Astarte, control signals are registers or bits which, when included in the trace generation stage within preconditions, produce output properties distinct from the set of output properties discovered when not using preconditions. The precise preconditions are described in detail in Section 3.3.2.1.

Should some signal, when used as a precondition for extracting properties, produce a distinct property set, the signal is then associated with some distinct behavior of the processor, such as that the signal's value may only be changed under certain conditions, that certain instructions may operate in a particular way while the signal is set, or that, when set, values of other design elements may or may not be updated. In brief, these signals control the allowable behavior of a design.

#### 3.2.3 Security Properties for Astarte

Astarte is intended to discover properties that describe the intended secure behavior of processor designs. Astarte should capture some notion of software's expectations of hardware, such as by enforcing control bits exercised by operating systems including the IOPL and CPL. Astarte should also provide coverage of some security properties discovered through manual review of documentation, and discover properties that, if followed, would prevent processors from being vulnerable to documented historical attacks. Ideally, Astarte would not be limited to just these cases and may additionally discover unanticipated properties that may aid hardware designers in ensuring secure behavior of the processor. Using control signals within property preconditions may address each of these goals.

For this reason, within the context of the Astarte framework, the working definition of a security property is a property over the design describing allowable designs states either when a control signal is fixed or when a control signal value is updated. Some of the limitations of this working definition are explored in the context of the results in Section 3.5.3.

#### **3.2.4** Properties in Implementation

To consider the output properties of Astarte, Figures 3.3 and 3.4 shows the invariant with the precondition of a far jumps that loads a new code segment pointer. This is the condition referenced by the example property in Figure 3.2b.

In these figures, the first line gives the preconditions, and each successive line (which may be wrapped) contains tuples of values or signals which are found to be equal within the trace set when this condition holds. The most frequent cases are comparisons to zero or one, which are broken out specifically in Figure 3.3. The size of this output is greatly inflated by considering

"..jmp\_far():::EXIT; condition="not(CS==orig(CS))"" ['1', 'A20', 'CR0\_0', 'CR0\_1', 'CR0\_18', 'CR0\_3', 'CR0\_5', 'CR4\_6', 'CR4\_9', 'D\_CPL', 'D\_CR0\_0', 'D\_CR0\_1', 'D\_CR0\_18', 'D CR0 2', 'D CR0 20', 'D CR0 3', 'D CR0 5', 'D CR0 7', 'D\_CR4\_11', 'D\_CR4\_12', 'D\_CR4\_6', 'D\_CR4\_8', 'D\_CR4\_9', 'D\_EFL\_1', 'D\_EFL\_11', 'D\_EFL\_13', 'D\_EFL\_2', 'D\_EFL\_4', 'D\_EFL\_6', 'D\_EFL\_8', 'D\_EFL\_9', 'D\_SMM', 'EFL\_1', 'EFL\_9', 'orig(A20)', 'orig(CR0\_0)', 'orig(CR0\_1)', 'orig(CR0\_18)', 'orig(CR0\_3)', 'orig(CR0\_5)', 'orig(CR4\_6)', 'orig(CR4\_9)', 'orig(D\_CR0\_0)', 'orig(D\_CR0\_1)', 'orig(D\_CR0\_18)', 'orig(D\_CR0\_2)', 'orig(D\_CR0\_20)', 'orig(D\_CR0\_3)', 'orig(D\_CR0\_5)', 'orig(D\_CR0\_7)', 'orig(D\_CR4\_11)', 'orig(D\_CR4\_12)', 'orig(D\_CR4\_6)', 'orig(D\_CR4\_8)', 'orig(D\_CR4\_9)', 'orig(D\_EFL\_1)', 'orig(D\_EFL\_11)', 'orig(D\_EFL\_13)', 'orig(D\_EFL\_2)', 'orig(D\_EFL\_4)', 'orig(D\_EFL\_6)', 'orig(D\_EFL\_8)', 'orig(D\_EFL\_9)', 'orig(D\_SMM)', 'orig(EFL\_1)', 'orig(EFL\_9)'] ['0', 'CR0\_2', 'CR0\_20', 'CR0\_7', 'CR4\_11', 'CR4\_12', 'CR4\_8', 'DR1', 'EFER', 'EFL\_11', 'EFL\_13', 'EFL\_4', 'EFL\_8', 'FS\_DPL', 'GS\_DPL', 'HLT', 'II', 'LDT\_DPL', 'SMM', 'orig(CR0\_2)', 'orig(CR0\_20)', 'orig(CR0\_7)', 'orig(CR4\_11)', 'orig(CR4\_12)', 'orig(CR4\_8)', 'orig(EFL\_11)', 'orig(EFL\_13)', 'orig(EFL\_4)', 'orig(EFL\_8)', 'orig(GS\_DPL)', 'orig(HLT)', 'orig(II)', 'orig(LDT\_DPL)', 'orig(SMM)']

Figure 3.3: All signals equal to zero or one during far jumps across code segments.

individual bit values and their delta values (with the 'D\_' prefix) within many registers and considering each of these both before and after the instruction executes. Delta values are not noted in the grammar and are not necessary to the Isadora workflow, but deriving these values offered niceties in implementation, and they are included here for completeness. The delta values for bits are incremented by one so that they do not take on a negative value which is used for error checking within the workflow, so 'orig(D\_CR0\_0) == 1' denotes that the 0th bit of the CR0 register was unchanged from the previous clock cycle before the far jump executes. This bit encodes whether the design is in protected mode, and means the trace set contains no case of a change to protected mode status immediately prior to a far jump that loads a new CS pointer.

```

".. jmp_far():::EXIT;condition="not(CS==orig(CS))""

...

['EFL_2', 'orig(EFL_2)']

['CPL', 'CS_DPL', 'DS_DPL', 'ES_DPL', 'SS_DPL']

['4294905840L', 'DR6', 'orig(DR6)']

['"0080c1100a800000207300008900"', 'TR', 'orig(TR)']

['1024', 'DR7', 'orig(DR7)']

['CR2', 'orig(CR2)']

['CR3', 'orig(CR2)']

['CR3', 'orig(CR3)']

['IDT', 'orig(IDT)']

['EFL_11', 'HLT', 'orig(EFL_11)', 'orig(II)']

['A20', 'D_EFL_11']

```

Figure 3.4: All remaining signal equalities during far jumps across code segments.

Beyond signals found to be equal to zero or one, the example property in Figure 3.2b appears within the output. The second line in Figure 3.4 shows that, over properly encoded traces and under the relevant preconditions, Astarte may detect an equality between the descriptor privilege levels (DPLs) of the code segment, stack segment, and data segment pointers after a far jump executes. Of note, CPL and CS\_DPL are both listed because both the emulator and Astarte derive the value independently. QEMU only derives the CPL and Astarte derives the DPL for all segment pointers; the two are always equal because they refer to the same bits in CS.

This output additionally specifies the values or equalities of other registers. The Extra Segment Pointer (ES) is also found to have a descriptor privilege level equal to that of the CS, SS, and DS. DR7, a debug register, is found to always hold the value 1024. DR7 is frequently set to 1024, and it fact is set to 1024 in all cases in operating system traces. CR3, the Page Fault Linear Address for recovery after page faults, is also held constant across code segment changes. CR3 is updated within the trace set but never during a far jump.

Astarte's output properties can appear large and complex due to the internal implementation details and scope of design state, but they conveniently define processor conditions within a single instruction and precondition and simply describe the software visible state as emulated and logged at these points.

## 3.3 Methodology

Astarte works in three phases: trace generation, property mining, and post-processing. Figure 3.5 provides an overview of the Astarte workflow. In the first phase I generate traces of execution of the processor. Without access to the source code of the processor design, I can not use a simulator to generate traces of processor execution as in prior work. Instead I use QEMU, an x86 emulator, to emulate processor execution. QEMU translates blocks of code at a time, and as such produces traces of basic blocks. The miner requires traces of individual instructions, so Astarte extends the generated traces so that each event in the trace represents a single instruction. This extension is sound with respect to the generated properties. In keeping with prior art, Astarte tracks processor state that is visible to software; the final security properties are written over this software-visible state. I emulate the processor loading and running four different operating systems as well as running software on the bare (emulated) metal.

In the second phase Astarte mines the traces of execution looking for security properties. I build the miner on top of the Daikon invariant generation tool (Ernst et al., 2007). The closed-source nature of x86 processors precludes using known, exploitable design bugs to differentiate security-critical properties from functional properties as was done by Zhang et al. (2017) when targeting RISC processors. Furthermore, the complexity of the many x86 protection modes and their associated control flags overwhelms the miner. In an initial experiment letting a naive miner run for 7 days, hundreds of millions of invariants were generated, with only a fraction representing useful security properties. To address this, Astarte partitions the state space of the processor on each of a small handful of security-critical control signals, and generates invariants within each partition. It is perhaps counter-intuitive that this approach works; it would seem necessary to consider all possible combinations of all security-relevant signals for every instruction in order to produce meaningful security properties. Yet, compared to prior manual efforts and to some known bugs in shipped x86 products, the specification output of Astarte independently produces valuable properties using this technique.

Figure 3.5: An overview of the Astarte workflow

In the third phase, post-processing, Astarte combines like invariants, integrates results across multiple runs of the miner (e.g., using traces generated from different operating systems), and simplifies expressions. The result is a manageable set of security properties.

# 3.3.1 Trace Generation

To generate traces of execution I use QEMU, a full system, open source machine emulator (Bellard, 2005). Running a processor in emulation allows us visibility into the processor's state. QEMU-emulated x86 CPUs can boot operating systems, run user-level applications, and output log data about the state of the CPU as software executes. The log data forms the basis of the execution traces over which security properties are mined.

QEMU dynamically translates machine instructions from the target architecture (in this case, x86) to the host architecture. To ease portability QEMU translates first to an intermediate language and then to the host instruction set. To improve performance QEMU translates a block of machine instructions at a time, rather than translating line by line. While this feature may be deactivated, doing so prevented emulation from being able to boot most modern OSs in under a day and greatly increases trace size.

A QEMU translation block (TB) is akin to a basic block (Aho et al., 2006). It is a sequence of instructions with a single entry point—the first instruction in the TB—and a single exit point—the last instruction in the TB. A TB ends at any instruction that modifies the program counter, such as syscall, sysenter, or jmp, or at a page boundary.

The translated TBs can be cached and reused, reducing translation time. However, translating a block of code at a time obscures CPU state at instruction boundaries. In other words, QEMU maintains consistent target CPU state at TB boundaries rather than at instruction boundaries.

From the QEMU execution logs, Astarte may extract *events* corresponding to the execution of a single TB. An event shows the sequence of instructions that make up the TB and the CPU state after the TB executes:

$$\langle \text{instruct}_1, \text{instruct}_2, \dots, \text{instruct}_n \rangle (r_0, r_1, \dots, r_m)$$

In the above,  $(r_0, \ldots, r_m)$  represents the state of the *m* ISA-level registers after the TB executes. A *trace* of events gives the CPU state at every TB boundary. The first event in a QEMU trace is always the single instruction ljmpw, which jumps to the code entry point. A trace of TBs might look like this:

$$\langle \texttt{ljmpw} \rangle (r_0^0, r_1^0, \dots, r_m^0)$$

$\langle \texttt{instruct}_1, \texttt{instruct}_2, \dots, \texttt{instruct}_n \rangle (r_0^n, r_1^n, \dots, r_m^n)$

$\dots$

$\langle \text{instruct}_1, \text{instruct}_2, \dots, \text{instruct}_j \rangle (r_0^*, r_1^*, \dots, r_m^*)$

The CPU state logged at the end of the first TB gives us the CPU state before the second TB executes. Consider this compared to a trace specifying each instruction. The single logged event  $\langle \text{instruct}_1, \text{instruct}_2, \dots, \text{instruct}_n \rangle (r_0^n, r_1^n, \dots, r_m^n)$ , would correspond to an extended trace of

events:

$$\langle \text{instruct}_1 \rangle (r_0^1, r_1^1, \dots, r_m^1) \tag{3.1}$$

$$\langle \text{instruct}_2 \rangle (r_0^2, r_1^2, \dots, r_m^2)$$

(3.2)

$$\langle \text{instruct}_{n} \rangle (r_{0}^{n}, r_{1}^{n}, \dots, r_{m}^{n})$$

(3.3)

Producing the extended trace of events would require the emulator translate code line-by-line. But, the emulator still needs to be fast enough to boot operating systems and run applicationlevel code. I take an intermediate approach for trace generation: I use QEMU translation blocks and build a lightweight extension to generate partial per-instruction events. For every TB in a trace, the event generator creates a new sequence of events, one event for each instruction in the TB. Each event lists the instruction executed and partial information about the CPU state. Any software-visible register that can be modified by the instruction is marked as invalid, and all other registers retain their value from the previous event. The generated event corresponding to the last instruction in the TB has the full CPU state as given by the original QEMU event. Continuing with the above extended trace of events, and considering the second event at line (3.2) in the trace,  $\forall i, 0 \le i \le m$  either  $r_i^2 = r_i^1$  or  $r_i^2 = invalid$ .

. . .

The event generator errs on the side of soundness: if it is possible for an instruction to change an aspect of CPU state, the generator assumes it does. I used the Intel 64 and IA-32 Architectures Software Developer Manuals (Intel, 2020) as reference when building the event generator.

# 3.3.2 Property Mining

Astarte uses Daikon (Ernst et al., 2007) as the base for property mining. I build a custom front-end that reads in the extended traces of events produced in the first phase, and outputs a trace of observations suitable for Daikon.

Daikon was developed for use with software programs: it looks for invariants over state variables for each point in a program. This front-end treats x86 instructions as program points; Daikon therefore will find invariants over ISA variables for each x86 instruction.

Daikon can handle individual program modules with relatively few program points and few program variables, it is not intended for analysis of entire programs. The amount of ISA state and the number of instructions in x86 is too large for Daikon to handle. The amount of trace data required to achieve coverage of a single instruction, and the size of the state over which to find invariant patterns for a single instruction overwhelm Daikon.

To mitigate the complexity, for each instruction Astarte partitions the space of properties on individual control signals.

# 3.3.2.1 Partitioning on Control Signals

For each instruction, Astarte separately considers the space of invariants over ISA state for that instruction, preconditioned on a single control bit. The key insight is that if Astarte chooses the control bits wisely, the partitioning not only mitigates performance and complexity issues with Daikon, it also produces sets of properties that are critical to security, and can then classify the properties by their precondition. The properties that make up each class provide some insight into the modes and behaviors of the processor governed by the preconditioning control signal.

For each control signal, how Astarte partitions the space of invariants for a single instruction depends on the control signal. For a one-bit signal Astarte creates four partitions, one for each combination of signal values before and after the instruction executes. For example, with the IOPL flag and addl instruction, Table 3.1 shows the four partitions of the space of invariants. Each row of the table represents one of the four possible antecedents of a property. The four antecedents represented in the table completely partition the space. For signals longer than one bit Astarte divides the space of invariants into two partitions for each instruction: instruct  $\land$  orig(reg) = reg and instruct  $\land$   $orig(reg) \neq reg$ .

| addl | $\wedge$ | orig(IOPL) = 0 | $\wedge$ | IOPL = 0 |

|------|----------|----------------|----------|----------|

| addl | $\wedge$ | orig(IOPL) = 0 | $\wedge$ | IOPL = 1 |

| addl | $\wedge$ | orig(IOPL) = 1 | $\wedge$ | IOPL = 0 |

| addl | $\wedge$ | orig(IOPL) = 1 | $\wedge$ | IOPL = 1 |

Table 3.1: Astarte partitions shown on the IOPL signal for instruction addl

| Category                        | Registers                     |  |

|---------------------------------|-------------------------------|--|

| General Purpose Registers       | EAX, EBX, ECX, EDX            |  |

| Interrupt Pointer               | EIP                           |  |

| Control Registers               | EFL, CR0, CR2, CR3, CR4, EFER |  |

| Individual Bitflags             | II, A20, SMM, HLT, CPL        |  |

| <b>Current Segment Pointers</b> | CS, SS, DS                    |  |

| Special Segments Pointers       | ES, FS, GS, LDT, TR           |  |

| Descriptor Tables               | GDT, IDT                      |  |

| Debug Registers                 | DR0, DR1, DR2, DR3, DR6, DR7  |  |

| Command Control                 | CCS, CCD, CC0                 |  |

Table 3.2: Categorization of QEMU logged registers

The set of properties produced for a particular preconditioning signal tell us something about the behavior governed by that signal. For example, providing  $CPL \neq orig(CPL)$  as a precondition will mine properties related to how the current privilege level (CPL) of the processor is elevated and lowered.

# 3.3.2.2 Identifying Control Signals

The first step is to choose which control signals to use as preconditions. I manually organized the x86 ISA state by category and then let Astarte find the meaningful signals within a category. The registers and their categories are given in Table 3.2.

Of these, Astarte focuses on the three control encoding categories: the Control Registers, the Individual Bitflags, and the Current Segment Pointers. These design elements either themselves control or contain fields that control security critical state, such as privilege levels and location of page tables. I chose these categories based on knowledge of the x86 ISA. Initially, Astarte used only the Control Registers and Bitflags, but initial evaluation led me to add the Current Segments. It is possible other categories may also yield interesting properties. Fortunately, each control signal is analyzed independently of the others, so additional categories of ISA state can be analyzed without incurring a combinational explosion in performance cost. (In Section 3.4.6 I discuss the cost.)

During the signal-finding phase Astarte unpacks registers to consider one- and two-bit fields separately. Mining can be used to reveal many fields that keep a constant value which are discarded as unused fields. To remove these from the considered fields, Astarte collapses all x86 instructions into a single pseudo-instruction and runs the property miner on this modified trace. Any found properties of the form reg = N are an indication that for all instructions reg has the constant value N and regis therefore unused. Astarte discards these flags from further consideration. At the end of this phase Astarte is left with 24 signals of interest that either single bits, two-bit fields, or registers.

### 3.3.3 Postprocessing

The Daikon miner produces tens of millions of properties. In post-processing Astarte removes invalid properties, removes redundant properties, and combines similar properties into a format that is easier to read.

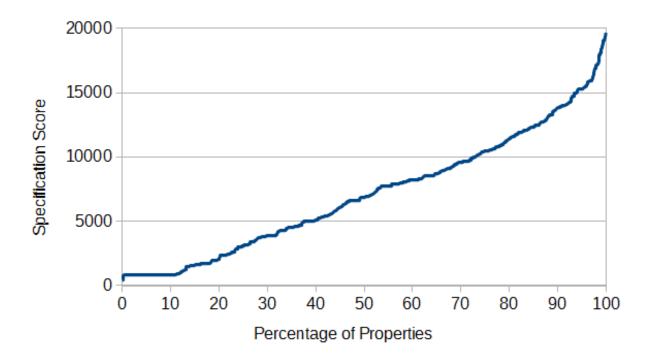

# 3.3.3.1 Intersection Across Trace Sets