## ENABLING REAL-TIME CERTIFICATION OF AUTONOMOUS DRIVING APPLICATIONS

Tanya Amert

A dissertation submitted to the faculty at the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2021

Approved by: James H. Anderson Marko Bertogna Parasara Sridhar Duggirala Glenn Elliott Jan-Michael Frahm F. Donelson Smith

©2021 Tanya Amert ALL RIGHTS RESERVED

## ABSTRACT

## Tanya Amert: Enabling Real-Time Certification of Autonomous Driving Applications (Under the direction of James H. Anderson)

The push towards fielding advanced driver-assist systems (ADASs) is happening at breakneck speed. Semi-autonomous features are becoming increasingly common, including adaptive cruise control and automatic lane keeping. Today, graphics processing units (GPUs) are seen as a key technology in this push towards greater autonomy. However, realizing full autonomy in mass-production vehicles will necessitate the use of stringent certification processes.

Unfortunately, currently available GPUs tend to be closed-source "black boxes" that have features that are not publicly disclosed; these features must be documented for certification to be tenable. Furthermore, existing real-time task models have not evolved to handle historical-result requirements common in computervision (CV) applications, which introduce cycles in processing graphs; existing models must be extended to account for such dependencies. Additionally, due to size, weight, power, and cost constraints, multiple CV applications may need to share a single hardware platform; if the platform contains accelerators such as non-preemptive GPUs, such sharing must be managed in a way that ensures applications are isolated from one another. For ADAS certification to be possible, these challenges must be addressed.

This dissertation addresses each of these three challenges. First, scheduling details of NVIDIA GPU are presented, as derived through extensive micro-benchmarking experiments. These details provide the foundation for identifying and automatically detecting key issues when using NVIDIA GPUs in real-time safety-critical applications. Second, a generalization of a real-time task model is introduced, enabling the computation of response-time bounds for processing graphs that contain cycles. This model exposes a trade-off between the age of historical data, the resulting response-time bounds, and the accuracy of the CV application; this trade-off is explored in detail. Finally, a time-partitioning framework for multicore+accelerator platforms is introduced. When applied alongside existing methods for alleviating spatial interference, this framework can help enable component-wise ADAS certification on multicore+accelerator platforms.

#### ACKNOWLEDGEMENTS

The completion of this dissertation would not have been possible without the help, guidance, and support of many, many people. First and foremost, I am thankful for my advisor, Jim Anderson, who took me on when I realized my path in graduate school was going in the wrong direction, and has always been there to push me towards becoming a better version of myself. Jim has shown a great balance of severity and kindness, from helping me to be a better writer and researcher to holding my fussy months-old child during a weekly research meeting. I am also grateful for my committee: Marko Bertogna, Sridhar Duggirala, Glenn Elliott, Jan-Michael Frahm, and Don Smith. Their guidance and feedback has been crucial to my success.

I am exceedingly grateful for the efforts of my collaborators: Joshua Bakita, Michael Balszun, Samarjit Chakraborty, Charlotte Dorn, Martin Geier, Manish Goyal, Abel Karimi, Saujas Nandi, Catherine Nemitz, Nathan Otterness, Stephen Tang, Peter Tong, Sergey Voronov, Thanh Vu, Kecheng Yang, and Ming Yang, as well as Ming Lin and Shan Yang. You all taught me so much. I have also enjoyed getting to know other current and former members of the Real-Time Systems group, including Shareef Ahmed, Lee Barnett, Shai Caspin, Micaiah Chisholm, Calvin Deutschbein, Zhishan Guo, Clara Hobbs, Namhoon Kim, Vance Miller, Sims Osborne, Sarah Rust, Abhishek Singh, Brittany Subialdea, Bryan Ward, and Tyler Yandrofski, as well as our newest members, Angelos Angelopoulos and Randal Tuggle. Thank you all for your discussions, and varying combinations of mentorship/menteeship.

My time at UNC would not have been so positive if not for the wonderful staff in the Computer Science Department. Thank you to Jodie Gregoritsch for being such a delight, and helping me when I felt lost. Thank you to Missy Wood for being the best stand-in for a favorite aunt that anyone could hope for so far from home; your fierce passion for UNC CS and its students really made the department feel welcoming. Thank you to the fabulous External Relations staff, including Brandi Day, Melissa Gunnell, Erin Lane, Brett Piper, Gina Rozier, Rosario Vila, and Hope Woodhouse, for their efforts to keep the department engaged in the community, and their endless patience and genuine interests in us as graduate students. I am grateful for so many more UNC CS staff, including Murray Anderegg, Robin Brennan, Bil Hays, Alicia Holtz, Denise Kenney, Beth Mayo, David Musick, and Mike Stone. Without you all, the CS department would not have

been such a welcoming place to spend so many years. I would also like to thank current and former UNC CS faculty, especially Sanjoy Baruah, Ming Lin, Dinesh Manocha, Don Porter, and Diane Pozefsky, as well as Gary Bishop and Stephen Pizer, who were pivotal in my teaching of COMP 550 at UNC.

My graduate school experience would not have been complete without the students I had the opportunities to teach at both UNC and Carleton. The terms I spent teaching were the perfect source of rejuvenation I needed, in particular for the final graduate-school push, and for that I am heavily indebted to the conversations and mentorship I received from Amy Csizmar Dalal, David Liben-Nowell, Dave Musicant, and Layla Oesper, as well as the support of the fantastic Paula Stowe and Mike Tie.

Getting through graduate school was made entirely possible by the friendships I formed and experiences those friends helped make happen. This includes students in the GAMMA group (especially Aniket Bera, Andrew Best, Nic Morales, Sahil Narang, Srihari Pratapa, Tanmay Randhavane, Atul Rungta, Auston Sterling, Justin Wilson, and Shan Yang), women from the Graduate Women in Computer Science (especially Catherine Nemitz, Marie Nesfield, and Sarah Rust, who helped keep it going in our early years), students in the board games group (Phil Ammirato and Marcy, Michael Deakin, Peter Lincoln, Nic Morales, True Price and Luci Pounders, Auston Sterling, Sergey Voronov, and Qiuyu Xiao), my wonderful Computer Science Student Associate co-officers (Marc Eder, Alan Kuntz, and Catherine Nemitz), members of our grading reading group (Shai Caspin, Calvin Deutschbein, Janine Hoelscher, Catherine Nemitz, Kaki Ryan, Aaron Smith, and Aaron Willcock), and all of the other wonderful friends I've made along the way, including Gio Acosta, Lisa Bauer, Kat Best, Alyssa Byrnes, Andrew Chi, Jeff Ichnowski and Chrissy Kistler, Bashima Islam, Kat Kirchoff, Kaci Kuntz (and Elias!), Xinran (Conny) Lu, Maja Najaran, and Natalie Stanley.

It is always a treasure when a friendship grows into something more like family, and I am so grateful to have met Catherine Nemitz so early in my time at UNC. We are so similar yet perfectly different, and that has made working on problem sets and paper deadlines, trips around the country and the world, and shared job searches all less lonely and more fun. You push me to be a kinder and stronger person, are the perfect extra aunt to Colin, and I cannot wait to continue to share in our personal and professional joys with each other.

I am endlessly grateful for the support of my family, especially my parents and my sisters, my in-laws, and my grandparents. You all mean so much to me, and have been so patient at the number of fishing trips that have turned into paper-deadline-induced couch-occupying work-cations.

All of the hard times over the past six years could only have been weathered with the neverending support of my wonderful husband, Chris. You have been my rock, and I could not have done it without you. I am so grateful for the love you have shown me and Colin, and look forward to our next set of adventures together. To my son, Colin, thank you for being such a joy in my life. To our pets, Lulu, Hobbes, Therese, and Sadie, thank you for your attention, comfort, and unconditional love.

The research in this dissertation was supported by NSF grants CPS 1239135, CNS 1409175, CPS 1446631, CNS 1563845, CNS 1717589, CPS 1837337, CPS 2038855, and CPS 2038960; AFOSR grant FA9550-14-1-0161, ARO grants W911NF-14-1-0499, W911NF-17-1-0294, and W911NF-20-1-0237; ONR grant N00014-20-1-2698; and a grant from General Motors.

# TABLE OF CONTENTS

| LIST OF | TABL     | ES                                                                   | xiii |

|---------|----------|----------------------------------------------------------------------|------|

| LIST OF | FIGU     | RES                                                                  | XV   |

| LIST OF | F ABBR   | EVIATIONSxv                                                          | viii |

| Chapter | 1: Intro | duction                                                              | 1    |

| 1.1     | Real-T   | ime Systems                                                          | 2    |

| 1.2     | Autono   | omous Driving Applications                                           | 3    |

| 1.3     | Graphi   | cs Processing Units                                                  | 4    |

| 1.4     | Thesis   | Statement                                                            | 5    |

| 1.5     | Contril  | putions                                                              | 6    |

|         | 1.5.1    | Generalized Task Model for Applications with Historical Dependencies | 6    |

|         | 1.5.2    | Evaluation of the History-vsResponse-Time-vsAccuracy Trade-Off       | 6    |

|         | 1.5.3    | Model of NVIDIA GPU Scheduling                                       | 7    |

|         | 1.5.4    | Guidance for Using NVIDIA GPUs in Real-Time Applications             | 7    |

|         | 1.5.5    | Enabling Isolation on Multicore+Accelerator Platforms                | 8    |

|         | 1.5.6    | Additional Evaluations                                               | 8    |

| 1.6     | Organi   | zation                                                               | 9    |

| Chapter | 2: Back  | ground                                                               | 10   |

| 2.1     | Autono   | omous-Driving Applications                                           | 10   |

|         | 2.1.1    | Path Planning                                                        | 10   |

|         | 2.1.2    | Perception                                                           | 13   |

|         | 2.1.3    | Control                                                              | 14   |

| 2.2     | Softwa   | re for Real-Time Autonomous-Driving Applications                     | 14   |

|         | 2.2.1    | Real-Time Software                                       | 15 |

|---------|----------|----------------------------------------------------------|----|

|         | 2.2.2    | CARLA: an Autonomous-Driving Simulator                   | 15 |

|         | 2.2.3    | CV and Other AI Frameworks                               | 15 |

| 2.3     | NVIDI    | A GPUs                                                   | 17 |

|         | 2.3.1    | NVIDIA GPU hardware                                      | 17 |

|         | 2.3.2    | CUDA Programming Fundamentals                            | 19 |

| 2.4     | Real-T   | ime Systems                                              | 21 |

|         | 2.4.1    | Real-Time Task Model                                     | 21 |

|         | 2.4.2    | Scheduling Algorithms                                    | 22 |

|         | 2.4.3    | Schedulability                                           | 23 |

|         | 2.4.4    | Graph-Based Tasks                                        | 25 |

|         |          | 2.4.4.1 OpenVX                                           | 25 |

|         |          | 2.4.4.2 Transforming OpenVX Graphs to Sporadic Task Sets | 26 |

| 2.5     | Chapte   | r Summary                                                | 31 |

| Chapter | 3: The H | History vs. Response Time vs. Accuracy Trade-Off         | 32 |

| 3.1     | Rp-Spc   | oradic Task Model                                        | 33 |

|         | 3.1.1    | Existing Task-Execution Models                           | 33 |

|         | 3.1.2    | Allowing Restricted Parallelism                          | 35 |

|         | 3.1.3    | The Rp-Sporadic Task Model                               | 36 |

| 3.2     | Trading  | g Off History and Response Time                          | 37 |

|         | 3.2.1    | Bounding Response Times for Rp-Sporadic Tasks            | 37 |

|         | 3.2.2    | Evaluating the History-versus-Response-Time Trade-Off    | 39 |

|         |          | 3.2.2.1 Experimental Setup                               | 40 |

|         |          | 3.2.2.2 Results                                          | 40 |

| 3.3     | Trading  | g Off History and Accuracy                               | 42 |

|         | 3.3.1    | Evaluation Metrics for MOT                               | 42 |

|         | 3.3.2    | Experimental Setup                                       | 44 |

|         |         | 3.3.2.1    | Driving Scenarios in CARLA                                         | 44 |

|---------|---------|------------|--------------------------------------------------------------------|----|

|         |         | 3.3.2.2    | Varying the Age of History                                         | 45 |

|         | 3.3.3   | Perfect S  | ensing                                                             | 47 |

|         | 3.3.4   | Camera-    | Based Sensing                                                      | 51 |

| 3.4     | Chapte  | er Summar  | y                                                                  | 53 |

| Chapter | 4: Usin | g NVIDIA   | GPUs in Real-Time Applications                                     | 55 |

| 4.1     | Docum   | nented Ord | lering and Execution of NVIDIA GPU Operations                      | 56 |

| 4.2     | Basic S | Scheduling | g Rules for NVIDIA GPUs                                            | 58 |

|         | 4.2.1   | Motivati   | ng Experiment                                                      | 58 |

|         | 4.2.2   | Scheduli   | ng Rules                                                           | 59 |

|         |         | 4.2.2.1    | General Scheduling Rules                                           | 61 |

|         |         | 4.2.2.2    | Non-Preemptive Execution                                           | 62 |

|         |         | 4.2.2.3    | Rules Governing Thread Resources                                   | 63 |

|         |         | 4.2.2.4    | Rules Governing Shared-Memory Resources                            | 63 |

|         |         | 4.2.2.5    | Register Resources                                                 | 64 |

|         |         | 4.2.2.6    | Copy Operations                                                    | 64 |

|         |         | 4.2.2.7    | Full Example                                                       | 65 |

|         | 4.2.3   | Open Qu    | estions, Answered                                                  | 65 |

| 4.3     | Extend  | led GPU S  | cheduling Rules                                                    | 66 |

|         | 4.3.1   | The NUI    | L Stream                                                           | 66 |

|         | 4.3.2   | Stream P   | riorities                                                          | 67 |

|         |         | 4.3.2.1    | Scheduling of Priority-Low Streams vs. Priority-High Streams       | 68 |

|         |         | 4.3.2.2    | Scheduling of Priority-None Streams vs. Prioritized Streams        | 68 |

|         |         | 4.3.2.3    | Scheduling of Prioritized Streams When Resource Blocking Can Occur | 69 |

|         |         | 4.3.2.4    | Additional Scheduling Rules                                        | 71 |

|         | 4.3.3   | Deviation  | ns From These Rules                                                | 72 |

|         |         | 4.3.3.1    | Concurrent Kernel Execution Limitations on the TX2                 | 72 |

|         |          | 4.3.3.2 Copy-Engine Count and Concurrent Copies                      | 74 |

|---------|----------|----------------------------------------------------------------------|----|

|         | 4.3.4    | Other Complications                                                  | 77 |

|         | 4.3.5    | Extensions to this Work                                              | 78 |

| 4.4     | Pitfalls | When Using NVIDIA GPUs in Real-Time Systems                          | 78 |

|         | 4.4.1    | Synchronization-Related Pitfalls                                     | 79 |

|         |          | 4.4.1.1 Explicit Synchronization                                     | 79 |

|         |          | 4.4.1.2 Implicit Synchronization                                     | 81 |

|         | 4.4.2    | Best-Practices-Related Pitfalls                                      | 84 |

|         | 4.4.3    | Additional Documentation-Related Pitfalls                            | 84 |

| 4.5     | CUPiD    | 0 <sup>RT</sup> Design                                               | 86 |

|         | 4.5.1    | Issues We Detect                                                     | 86 |

|         | 4.5.2    | Analyzing GPU-Using Programs                                         | 87 |

| 4.6     | CUPiD    | 9 <sup>RT</sup> Evaluation                                           | 88 |

|         | 4.6.1    | Experimental Setup                                                   | 88 |

|         | 4.6.2    | Evaluation of Issue Detection via CUPiD <sup>RT</sup>                | 88 |

|         |          | 4.6.2.1 Allocating and Freeing GPU Memory                            | 89 |

|         |          | 4.6.2.2 NULL-Stream GPU Operations                                   | 90 |

|         | 4.6.3    | Case Study: Impact of Issue Remediation                              | 90 |

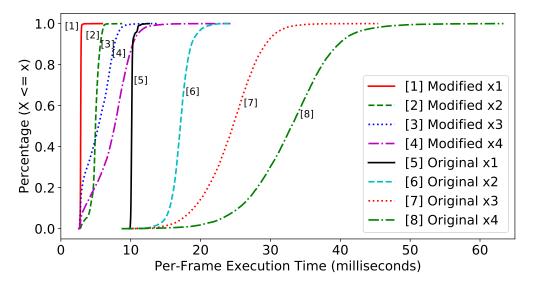

|         |          | 4.6.3.1 Impact on Execution Times                                    | 91 |

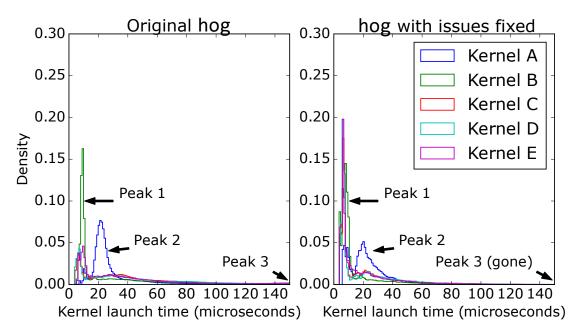

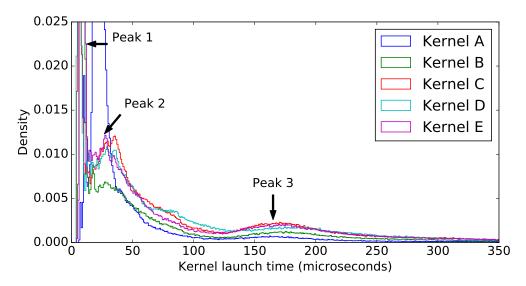

|         |          | 4.6.3.2 Impact on CPU Blocking                                       | 93 |

|         |          | 4.6.3.3 Case Study Summary                                           | 96 |

| 4.7     | Chapte   | er Summary                                                           | 97 |

| Chapter | 5: Enab  | ling Time Partitioning for Real-Time Multicore+Accelerator Platforms | 98 |

| 5.1     | System   | n Model                                                              | 99 |

|         | 5.1.1    | Component Model                                                      | 99 |

|         | 5.1.2    | Task Model                                                           | 99 |

|         | 5.1.3    | Request Model 10                                                     | 00 |

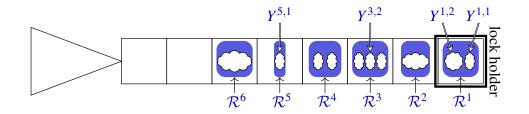

|         | 5.1.4   | Global C   | DMLP                                                  | )0 |

|---------|---------|------------|-------------------------------------------------------|----|

|         | 5.1.5   | Accelera   | tor Access Model                                      | )2 |

| 5.2     | TimeW   | all Desig  | n                                                     | )2 |

|         | 5.2.1   | Scheduli   | ng Hierarchy                                          | )3 |

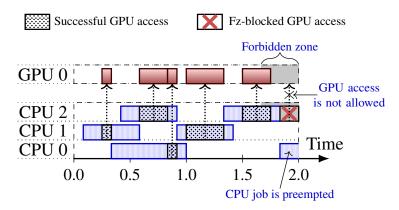

|         | 5.2.2   | Time Par   | titioning via Forbidden Zones10                       | )3 |

|         | 5.2.3   | Boundin    | g Fz-Blocking                                         | )5 |

|         | 5.2.4   | Performa   | ance Optimizations                                    | )6 |

| 5.3     | Theory  | Meets Pr   | actice                                                | )7 |

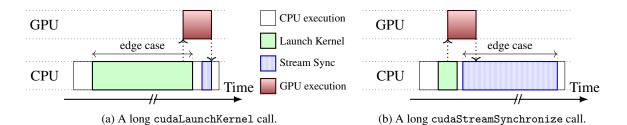

|         | 5.3.1   | Investiga  | ting Potential Culprits 10                            | )9 |

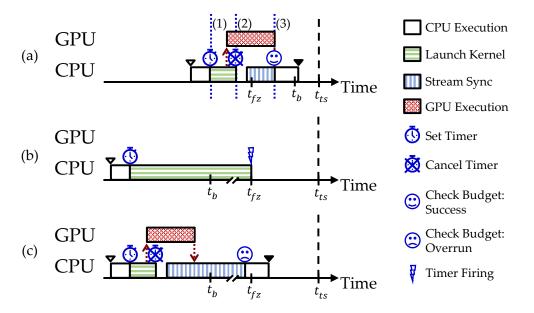

|         | 5.3.2   | Mitigatir  | ng Edge Cases through Budget Enforcement11            | 10 |

|         |         | 5.3.2.1    | Enforcing Forbidden Zones11                           | 11 |

|         |         | 5.3.2.2    | Handling Budget Overruns11                            | 12 |

| 5.4     | Experi  | mental Ev  | aluation11                                            | 13 |

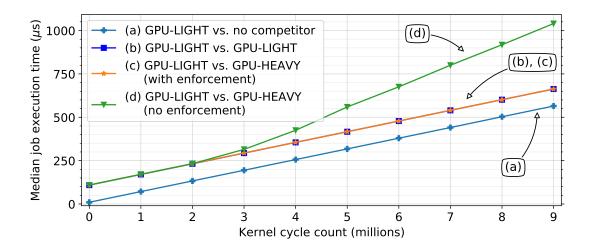

|         | 5.4.1   | Tempora    | l Isolation and the Cost of Enforcement11             | 13 |

|         |         | 5.4.1.1    | Verifying Temporal Isolation11                        | 13 |

|         |         | 5.4.1.2    | Overhead of Forbidden-Zone Enforcement                | 14 |

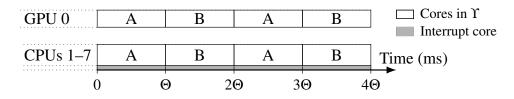

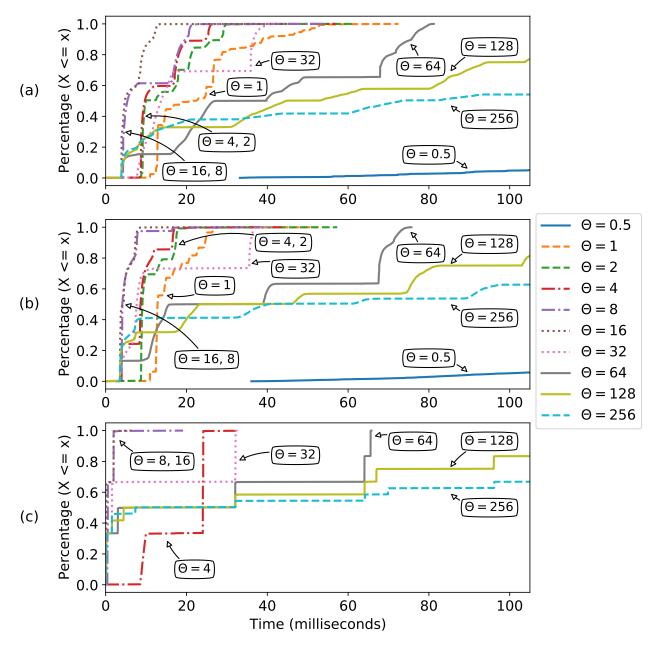

|         | 5.4.2   | Choosing   | g a Time-Slice Length11                               | 15 |

|         | 5.4.3   | Case-Stu   | dy Evaluation                                         | 8  |

|         |         | 5.4.3.1    | Choosing Time-Slice Lengths for hog 12                | 20 |

|         |         | 5.4.3.2    | Frame Dropping Due to GPU-Budget Enforcement          | 20 |

|         |         | 5.4.3.3    | The Cost of Enforcing Time Partitioning               | 22 |

|         |         | 5.4.3.4    | Putting It All Together 12                            | 24 |

| 5.5     | Chapte  | er Summai  | y12                                                   | 25 |

| Chapter | 6: Addi | tional Eva | luations                                              | 26 |

| 6.1     | Compe   | eting Auto | motive-Based Workloads                                | 26 |

| 6.2     | Case S  | tudy: The  | History-vsResponse-Time-vsAccuracy Trade-Off          | 27 |

| 6.3     | Case S  | tudy: Eva  | luating Time Partitioning for Automotive Applications | 31 |

| 6.4     | Chapte  | 135 r Summary                                |

|---------|---------|----------------------------------------------|

| Chapter | 7: Conc | lusion                                       |

| 7.1     | Summa   | ary of Results                               |

| 7.2     | Other l | Related Work                                 |

|         | 7.2.1   | Response-Time Bounds for GPU-Using Workloads |

|         | 7.2.2   | Real-Time Locking Protocols                  |

| 7.3     | Ackno   | wledgements                                  |

| 7.4     | Future  | Work                                         |

| BIBLIO  | GRAPH   | IY145                                        |

## LIST OF TABLES

| 2.1  | Details of NVIDIA GPUs we consider in this dissertation                                                                                                                              | 19  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

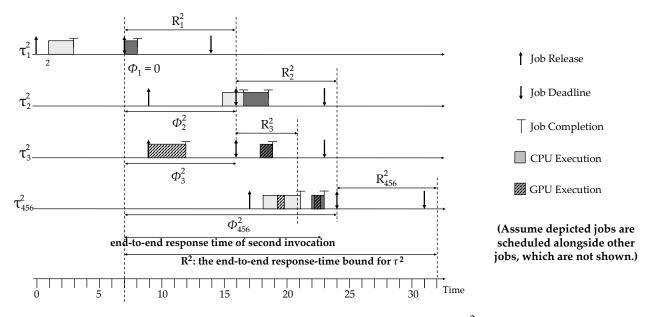

| 3.1  | Task parameters for the tasks in Figure 3.3, assuming a platform with $m = 3$ CPUs                                                                                                   | 38  |

| 3.2  | Probability mass functions (PMFs) corresponding to available history results.                                                                                                        | 47  |

| 3.3  | Results for vehicle tracking using ground-truth detections                                                                                                                           | 49  |

| 3.4  | Results for pedestrian tracking using ground-truth detections                                                                                                                        | 50  |

| 3.5  | Results for vehicle tracking using Faster R-CNN to detect vehicles                                                                                                                   | 52  |

| 3.6  | Results for pedestrian tracking using Faster R-CNN to detect pedestrians.                                                                                                            | 52  |

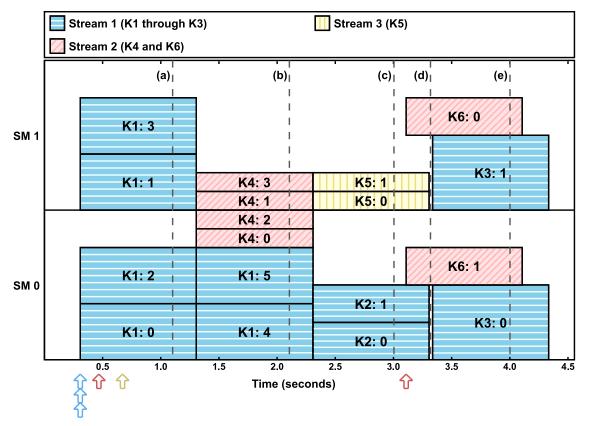

| 4.1  | Details of kernels used in the experiment in Figure 4.3                                                                                                                              | 59  |

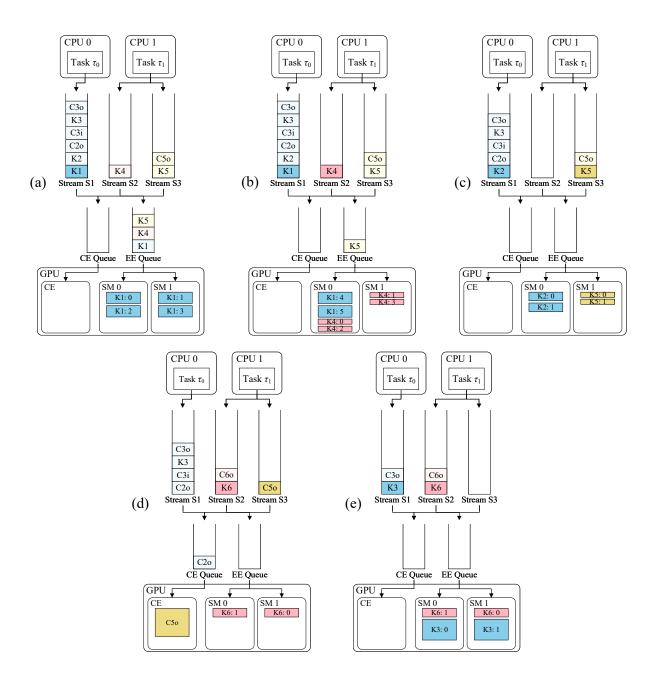

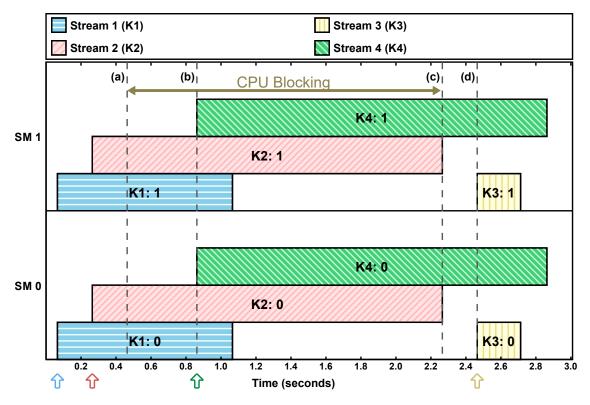

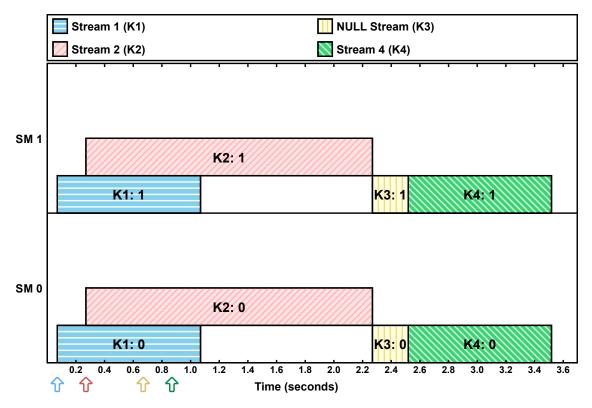

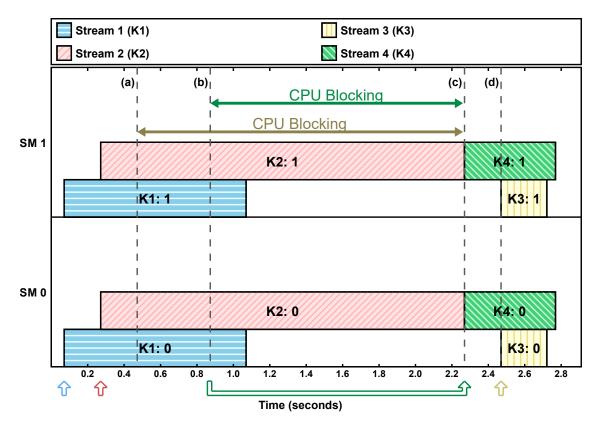

| 4.2  | Details of kernels used in the NULL-stream scheduling experiment in Figure 4.5                                                                                                       | 67  |

| 4.3  | Details of kernels used in the prioritized-stream scheduling experiment in Figure 4.6                                                                                                | 69  |

| 4.4  | Details of kernels used in the prioritized-stream scheduling experiment in Figure 4.7                                                                                                | 70  |

| 4.5  | Details of kernels used in the prioritized-stream scheduling experiment in Figure 4.8                                                                                                | 71  |

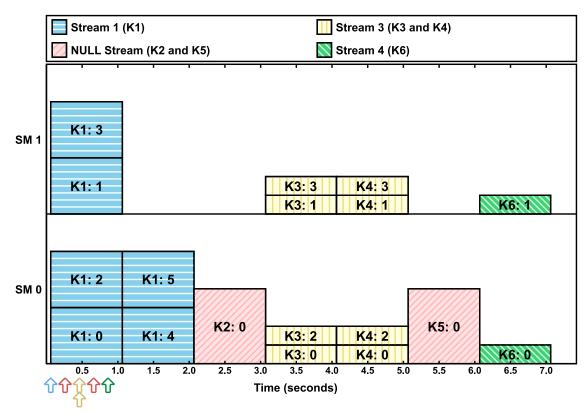

| 4.6  | Details of kernels used in the concurrent-kernel scheduling experiment in Fig-<br>ures 4.9 and 4.10.                                                                                 | 72  |

| 4.7  | Details of kernels used in the copy-engine experiment in Figures 4.11 and 4.12.                                                                                                      | 74  |

| 4.8  | Details of kernels used in the multiple-copy-engine experiment in Figure 4.13                                                                                                        | 76  |

| 4.9  | Observed vs. documented synchronization sources in CUDA.                                                                                                                             | 85  |

| 4.10 | Issue occurrences for ten GPU-using OpenCV sample applications                                                                                                                       | 89  |

| 4.11 | Per-frame execution times (in milliseconds) of hog with and without fixing issues                                                                                                    | 92  |

| 4.12 | Kernel launch times (in microseconds) of hog with and without fixing issues, with percentage improvements in bold.                                                                   | 93  |

| 5.1  | Statistics for durations of the two copies and five kernels comprising the hog case study in microseconds, as measured on the GPU using nvprof and on the CPU using clock_gettime(). | 108 |

| 5.2  | Observed response times across 75,000 frames for hog tasks in Component A without or with other tasks executing in Component B                                                       | 124 |

| 6.1 | Distributions of available history results, represented as tuples, for MOT tasks without and with competing workloads present                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2 | Results for vehicle and pedestrian tracking in Scenario 2 with MOT tasks in the presence of competing workloads, alongside selected results from Tables 3.5 and 3.6 129 |

| 6.3 | Observed response times (in seconds) of MOT tasks with varying intra-task parallelism 130                                                                               |

| 6.4 | GPU-access durations (in microseconds) as measured on the CPU for each of the three access-merging configurations we considered                                         |

| 6.5 | Observed response times across 10,000 frames for hog tasks in Component A with varying access-merging configurations and active components                              |

# LIST OF FIGURES

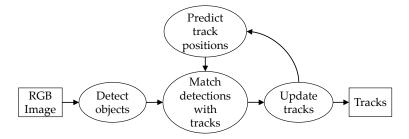

| 1.1  | The tracking-by-detection pipeline.                                                                                                                              | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The tracking-by-detection pipeline with a supernode in place of the cycle                                                                                        | 4  |

| 2.1  | A town from the autonomous-driving simulator CARLA (Dosovitskiy et al., 2017), overlaid with the graph corresponding to intersections and their connecting roads | 11 |

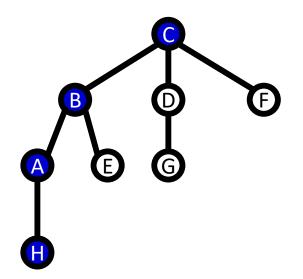

| 2.2  | The path from node C to node H resulting from breadth-first search.                                                                                              | 11 |

| 2.3  | The path from node C to node H resulting from breadth-first search.                                                                                              | 12 |

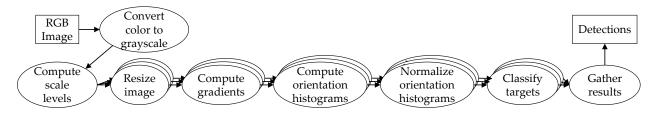

| 2.4  | Lane-detection pipeline using the Hough Transform.                                                                                                               | 13 |

| 2.5  | Pedestrian-detection pipeline using HOG features.                                                                                                                | 13 |

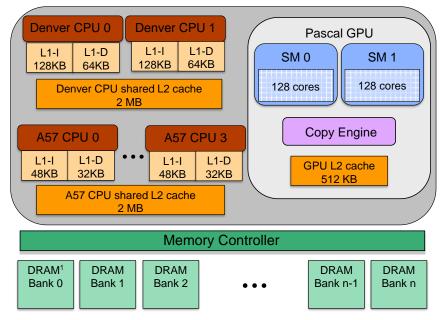

| 2.6  | Architecture of the Jetson TX2.                                                                                                                                  | 18 |

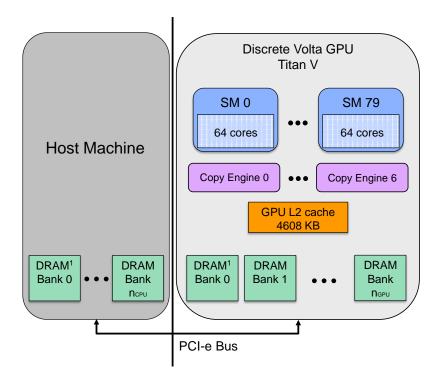

| 2.7  | Architecture of a platform equipped with a Titan V.                                                                                                              | 18 |

| 2.8  | Illustration of the real-time task model for a task $\tau_i = (2, 6, 2, 5)$                                                                                      | 22 |

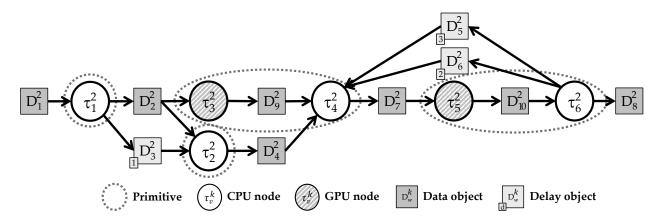

| 2.9  | An example OpenVX graph $\mathcal{G}^1$                                                                                                                          | 26 |

| 2.10 | The transformation process from an OpenVX graph to a set of sporadic tasks.                                                                                      | 27 |

| 2.11 | A fine-grained OpenVX graph $\mathcal{G}^2$ corresponding to the coarse-grained graph in Figure 2.9                                                              | 27 |

| 2.12 | A sporadic task graph $\Gamma^2$ derived from the fine-grained OpenVX graph $\mathcal{G}^2$ in Figure 2.11                                                       | 29 |

| 2.13 | A sporadic task DAG $\tau^2$ derived from the cyclic graph from Figure 2.12                                                                                      | 29 |

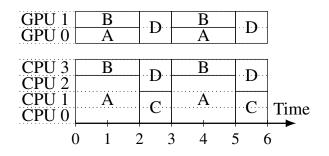

| 2.14 | A possible schedule of two sets of jobs of the sporadic tasks in $\tau^2$ in Figure 2.13.<br>The second job of each task is shaded darker than the first.        | 30 |

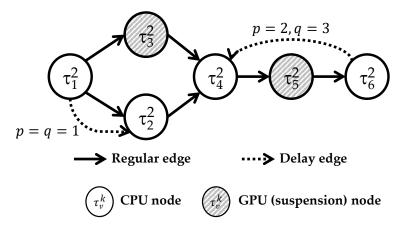

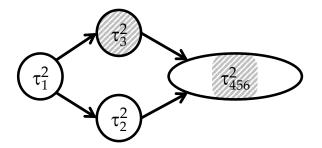

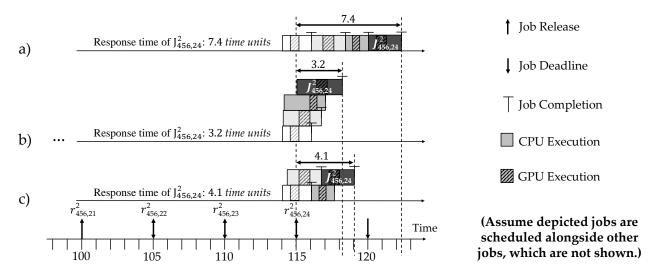

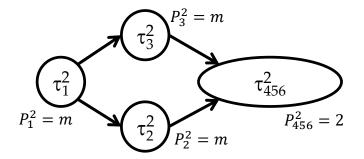

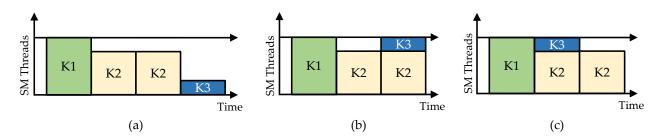

| 3.1  | Scheduling repercussions of the degree of intra-task parallelism, including a) sequential execution, b) fully parallel execution, and c) restricted parallelism. | 34 |

| 3.2  | Intra-task parallelism for nodes of $\tau^2$ from Figure 2.13                                                                                                    | 36 |

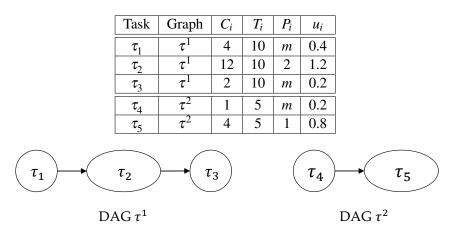

| 3.3  | An rp-sporadic task set derived from two DAGs, containing two supernodes, $\tau_2$ and $\tau_5$ , both with $p = 2$ .                                            | 38 |

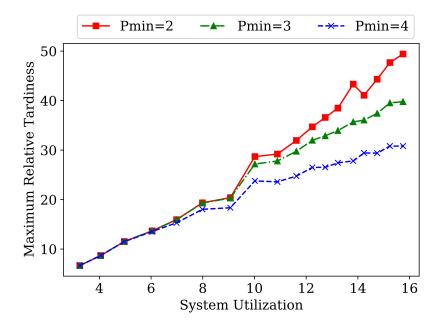

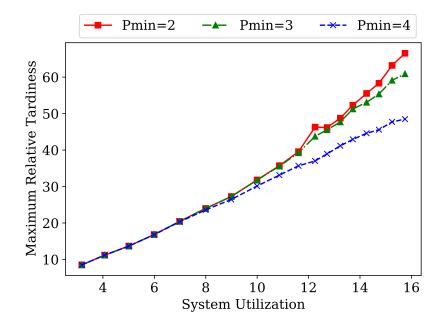

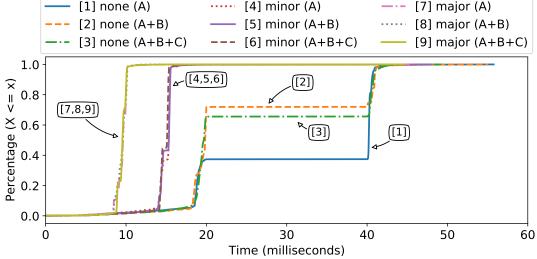

| 3.4  | Maximum relative tardiness results for uniform per-task utilizations                                                                                             | 41 |

| 3.5  | Maximum relative tardiness results for exponential per-task utilizations                                                                                         | 41 |

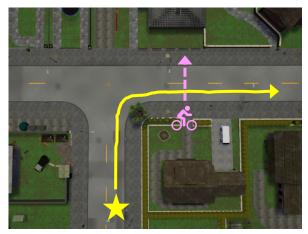

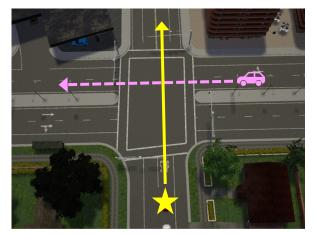

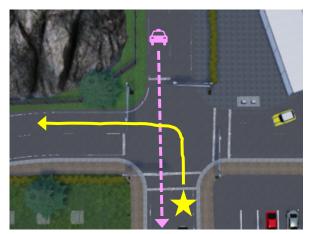

| 3.6  | The five scenarios we considered.                                                                                                                                | 46 |

| 3.7  | The tracking-by-detection pipeline.                                                                                                                              | 47 |

| 4.1  | The relation between CUDA programs, kernels, and thread blocks                                                                                                | 56  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2  | Potential GPU scheduling options.                                                                                                                             | 58  |

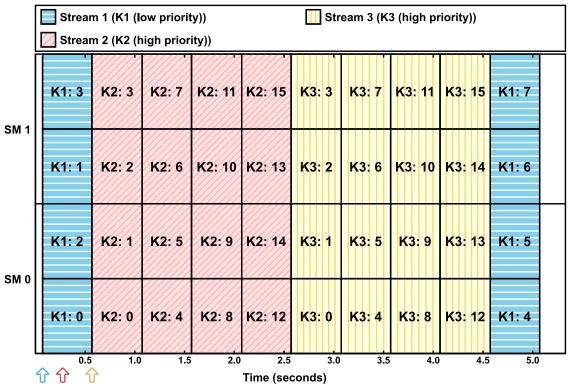

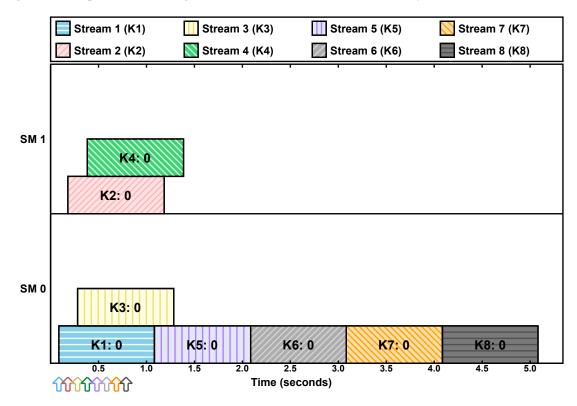

| 4.3  | Basic GPU scheduling experiment                                                                                                                               | 60  |

| 4.4  | Detailed state information at various time points in Figure 4.3                                                                                               | 61  |

| 4.5  | NULL stream scheduling experiment.                                                                                                                            | 67  |

| 4.6  | Experiment showing starvation of a priority-low stream.                                                                                                       | 69  |

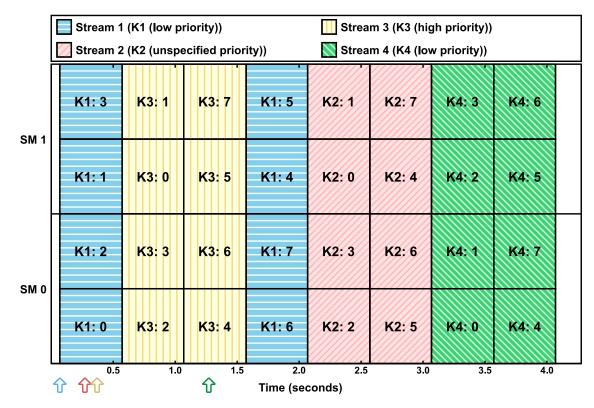

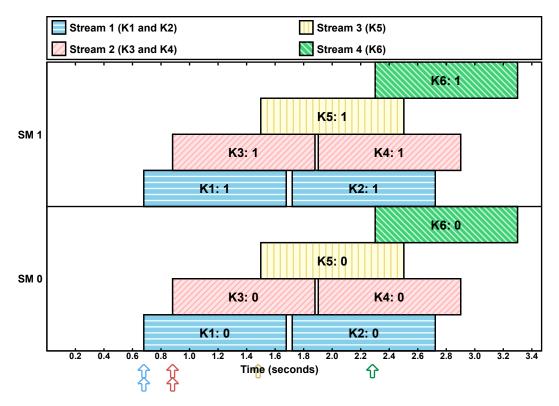

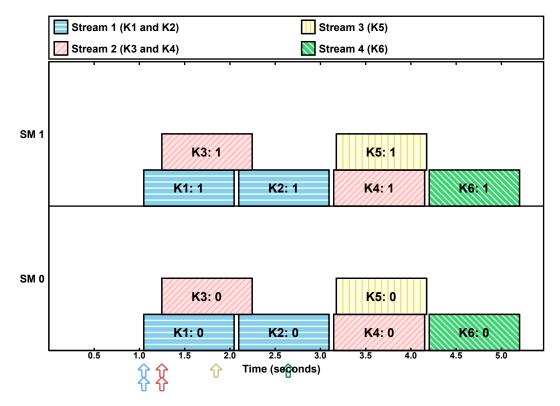

| 4.7  | Experiment demonstrating two actual stream priority levels                                                                                                    | 70  |

| 4.8  | Experiment with both stream priorities and resource blocking                                                                                                  | 71  |

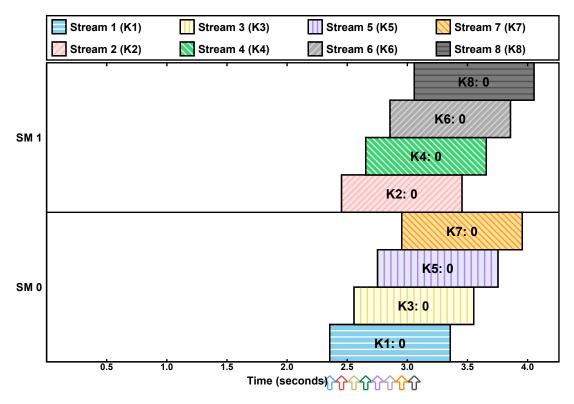

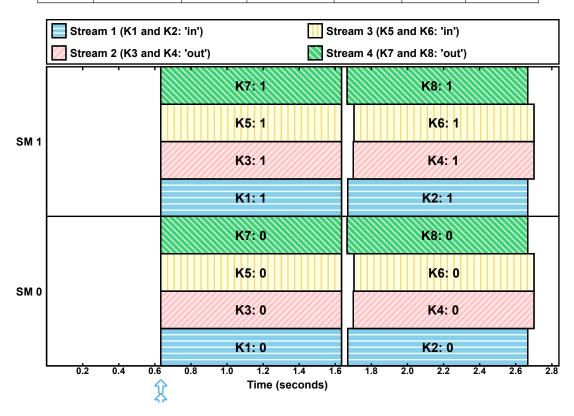

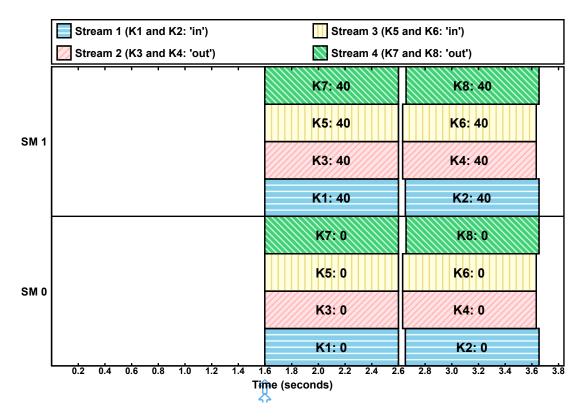

| 4.9  | Experiment with eight concurrent kernels on a Titan V (only two of 80 SMs are shown)                                                                          | 73  |

| 4.10 | Experiment with eight concurrent kernels on a TX2.                                                                                                            | 73  |

| 4.11 | Experiment with many copy operations on a 1070 (only two of 15 SMs are shown)                                                                                 | 75  |

| 4.12 | Experiment with many copy operations on a TX2.                                                                                                                | 75  |

| 4.13 | Experiment with different copy directions on a 1070 (only two of 15 SMs are shown)                                                                            | 76  |

| 4.14 | Experiment with different copy directions on a Titan V (only two of 80 SMs are shown). $\ldots$                                                               | 77  |

| 4.15 | Explicit synchronization due to cudaDeviceSynchronize                                                                                                         | 80  |

| 4.16 | Implicit synchronization caused by a NULL-stream kernel                                                                                                       | 82  |

| 4.17 | Implicit synchronization causing additional CPU blocking due to cudaFree                                                                                      | 83  |

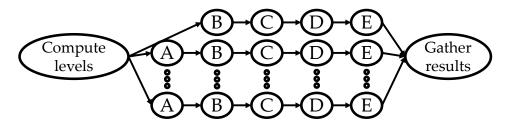

| 4.18 | Simplified structure of the hog application.                                                                                                                  | 91  |

| 4.19 | CDF of hog per-frame execution times with and without fixing issues.                                                                                          | 92  |

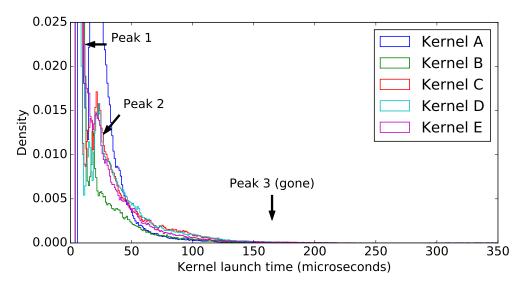

| 4.20 | Distribution of hog kernel launch times before and after fixing issues, with one, two, or four hog threads executing simultaneously                           | 94  |

| 4.21 | Zoomed-in distribution of the original hog kernel launch times                                                                                                | 95  |

| 4.22 | Zoomed-in distribution of hog kernel launch times after fixing issues                                                                                         | 95  |

| 5.1  | Five partitions on four cores. Partition 3 executes on two cores; other partitions each execute on one core. In-partition scheduling is shown for Partition 3 | 99  |

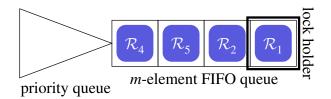

| 5.2  | The global OMLP structure for $m = 4$ CPUs                                                                                                                    | 101 |

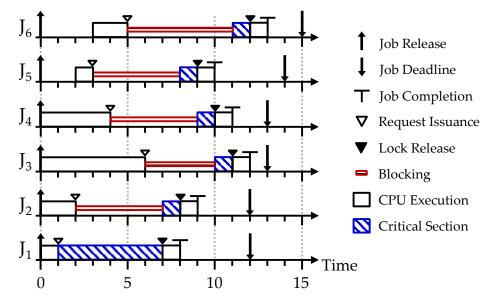

| 5.3  | Jobs issuing requests to the global OMLP with $m = 4$ CPUs                                                                                                    | 101 |

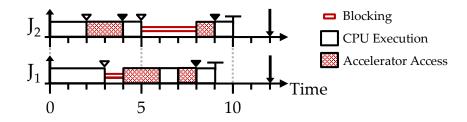

| 5.4  | Two jobs issuing requests to access the same accelerator.                                                                                                     | 102 |

|      |                                                                                                                                                               |     |

| 5.5  | A time-sliced schedule. Rectangles represent reservations                                                                                                                                                                                           |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.6  | Expanded view of the first time slice of Component A from Figure 5.5. Rectangles represent jobs of tasks in Component A                                                                                                                             |     |

| 5.7  | The global OMLP with support for forbidden zones. Request and access widths indicate worst-case critical-section and access durations, respectively                                                                                                 | 107 |

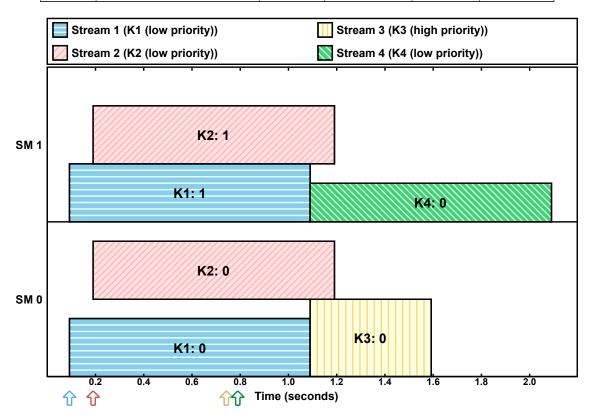

| 5.8  | Illustrations of two edge-case scenarios we observed using KUTrace and nvprof                                                                                                                                                                       |     |

| 5.9  | The budget-enforcement mechanisms used in TimeWall, for (a) a "well-behaved" GPU access, (b) a GPU access for which the watchdog timer fires, and (c) a GPU access that exceeds its budget.                                                         | 112 |

| 5.10 | Comparison of median GPU-LIGHT task execution times in the presence of alter-<br>nating component workloads (the middle $50^{th}$ -percentile percentile varied by less<br>than 3%). GPU-LIGHT tasks were not subject to forbidden-zone enforcement |     |

| 5.11 | Reservations for the two components in our time-slice experiments. We measured response times of tasks in Component A.                                                                                                                              |     |

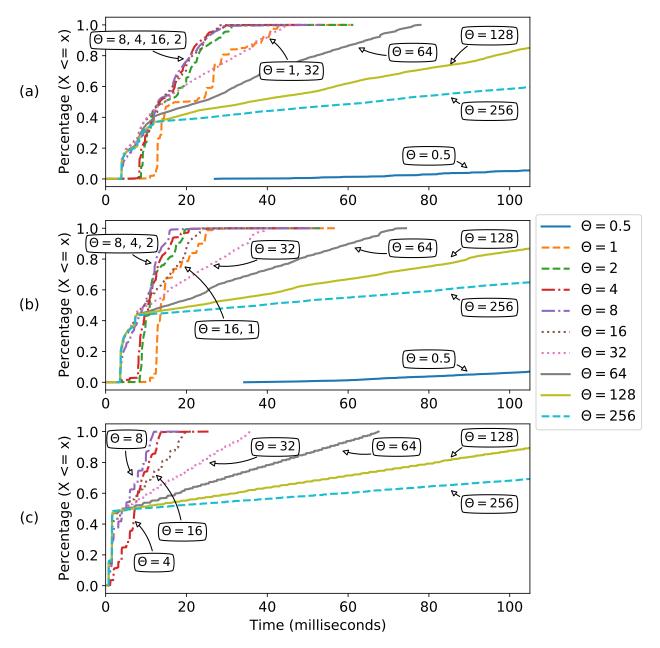

| 5.12 | Response times of jobs with releases aligned to time slices, for (a) short, (b) medium, and (c) long GPU accesses, with varying $\Theta$ (in milliseconds)                                                                                          |     |

| 5.13 | Response times of jobs with releases unaligned to time slices, for (a) short, (b) medium, and (c) long GPU accesses, with varying $\Theta$ (in milliseconds)                                                                                        |     |

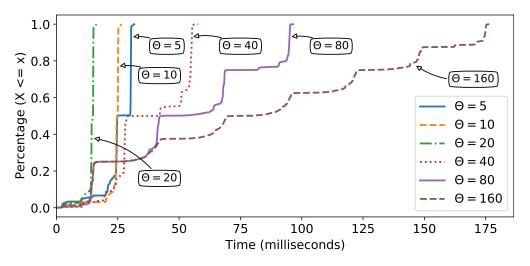

| 5.14 | CDFs of hog response times with varying $\Theta$ (in milliseconds)                                                                                                                                                                                  |     |

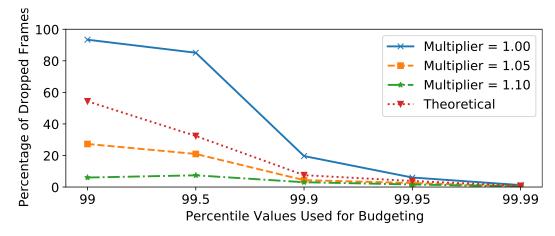

| 5.15 | Measured frame-drop rates for hog depending on multiplier used for provisioned GPU-access budgeting values, compared to the theoretical frame-drop rate                                                                                             | 121 |

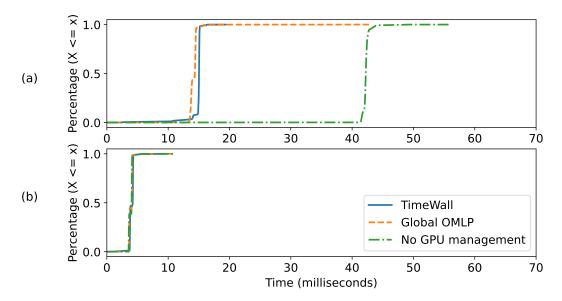

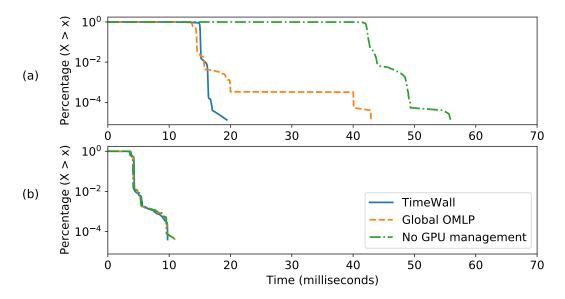

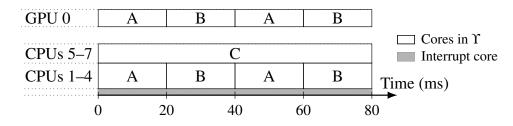

| 5.16 | CDFs of hog response times with different GPU-management approaches, with either (a) three or (b) one hog task(s) in Component A                                                                                                                    | 123 |

| 5.17 | CCDFs (tail distributions) of hog response times with different GPU-management approaches, with either (a) three or (b) one hog task(s) in Component A. Note that the y-axis uses a logarithmic scale.                                              |     |

| 5.18 | CDFs of observed response times for the hog tasks in Component A without and with a workload in Component B                                                                                                                                         |     |

| 6.1  | Reservations for the three components in our extended evaluation experiments                                                                                                                                                                        |     |

| 6.2  | CDFs of observed response times for the hog tasks in Component A with varying access-merging configurations and active components.                                                                                                                  |     |

# LIST OF ABBREVIATIONS

| ADAS                | Advanced Driver-Assist System                  |

|---------------------|------------------------------------------------|

| AI                  | Artificial Intelligence                        |

| A-MOTA              | Average Multiple Object Tracking Accuracy      |

| APF                 | Artificial Potential Field                     |

| API                 | Application Programming Interface              |

| CCDF                | Complementary Cumulative Distribution Function |

| CDF                 | Cumulative Distribution Function               |

| CE                  | Copy Engine                                    |

| CGLP                | Concurrency Group Locking Protocol             |

| CNN                 | Convolutional Neural Network                   |

| CPU                 | Central Processing Unit                        |

| CUDA                | Compute Unified Device Architecture            |

| CUPiD <sup>RT</sup> | CUDA Pitfall Detector for Real-Time Systems    |

| CV                  | Computer Vision                                |

| DAG                 | Directed Acyclic Graph                         |

| DM                  | Deadline-Monotonic                             |

| DNN                 | Deep Neural Network                            |

| DRAM                | Dynamic Random-Access Memory                   |

| DSP                 | Digital Signal Processor                       |

| EDF                 | Earliest-Deadline-First                        |

| EE                  | Execution Engine                               |

| FIFO                | First-In First-Out                             |

| FPGA                | Field Programmable Gate Array                  |

| FPS                 | Frames per Second                              |

| fz-blocking         | Forbidden-Zone-Induced Blocking                |

| G-EDF               | Global Earliest-Deadline-First                 |

| GEL                 | G-EDF-Like                                     |

| GPU                 | Graphics Processing Unit                       |

| HOG         | Histogram of Oriented Gradients                                  |

|-------------|------------------------------------------------------------------|

| IoU         | Intersection-over-Union                                          |

| JLFP        | Job-Level Fixed Priority                                         |

| L1          | Level 1 (Cache)                                                  |

| L2          | Level 2 (Cache)                                                  |

| L3          | Level 3 (Cache)                                                  |

| lidar       | Light Detection and Ranging                                      |

| LITMUSRT    | Linux Testbed for Multiprocessor Scheduling in Real-Time Systems |

| mAP         | Mean Average Precision                                           |

| MOT         | Multi-Object Tracking                                            |

| MOTA        | Multiple Object Tracking Accuracy                                |

| MOTP        | Multiple Object Tracking Precision                               |

| OMLP        | O(m) Locking Protocol                                            |

| OS          | Operating System                                                 |

| PA          | Partition Allocator                                              |

| PCI-e       | Peripheral Component Interconnect Express                        |

| PCR         | Periodic Component Reservation                                   |

| PDF         | Probability Density Function                                     |

| pi-blocking | Priority-inversion Blocking                                      |

| PID         | Proportional-Integral-Derivative                                 |

| PMF         | Probability Mass Function                                        |

| RM          | Rate-Monotonic                                                   |

| RRT         | Rapidly-exploring Random Tree                                    |

| RTOS        | Real-Time Operating System                                       |

| SM          | Streaming Multiprocessor                                         |

| SoC         | System-on-a-Chip                                                 |

| SVM         | Support Vector Machine                                           |

| SWaP-C      | Size, Weight, Power, and Cost                                    |

| TimeWall    | Time-Isolated Multicore Execution With Accelerator Locking       |

VCP Vertex Coloring Problem

WCET Worst-Case Execution Time

## **CHAPTER 1: INTRODUCTION**

Semi- and fully autonomous advanced driver-assist systems (ADASs) have become mainstream; systems such as Tesla Autopilot and Cadillac Super Cruise provide features like adaptive cruise control and automatic lane keeping. To produce fully autonomous vehicles at a mass scale, increasingly complex sensing and computer-vision (CV) algorithms will be necessary. However, there is a fundamental disconnect between the design of CV applications and the real-time guarantees necessary to certify their use in such safety-critical applications. CV applications are designed to be throughput-focused, *i.e.*, they seek to ensure *real-fast* execution. In contrast, *real-time* systems require predictable execution subject to timing constraints. If these timing constraints are violated, accidents and even fatalities can result.

Such timing constraints can be checked through extensive real-world testing. For example, Waymo, a leader in autonomous driving, has reported over 20 million miles driven by their autonomous vehicles (Waymo, 2021). However, it is prohibitive to drive million of miles to verify the predictable timing of any new features. Instead, timing guarantees can be provided by *real-time certification*. Such certification entails analyzing the computational workload and the hardware platform to provide bounds on the worst-case completion time, or *response time*, of any invoked task.

Response-time analysis of CV applications is complicated for several reasons; we focus on three specific challenges. First, many CV algorithms require results from prior execution instances, leading to potential delays in cases when those executions have not yet completed and made the results available. These CV algorithms are frequently structured as task graphs in which cycles represent dependencies on historical results. Unfortunately, existing analysis techniques prohibit cyclic dependencies or remove them in a way that results in overly conservative analysis. Second, the CV algorithms used in automotive applications typically make use of specialized hardware accelerators, such as graphics processing units (GPUs), to improve performance through parallelism. However, GPUs are designed for throughput rather than predictability, and therefore can have unexpected behavior (Otterness et al., 2016). Furthermore, autonomous vehicles are subject to size, weight, power, and cost (SWaP-C) constraints, so it is often necessary for multiple applications to execute on the same hardware. Thus, the scheduling policies of such hardware platforms

must be understood in order to ensure that timing constraints will be met. Finally, some existing certification specifications, such as ARINC 653 (Prisaznuk, 2008) for avionics platforms, require that temporal isolation be guaranteed when executing multiple applications on a single shared hardware platform. This is made significantly more challenging for CV applications, which may be developed and tested independently, possibly by different vendors, and which may utilize GPUs, which present a challenge for isolation due to non-preemptive GPU execution.

In this dissertation, we seek to address these challenges and bridge the divide between the design of CV algorithms and the requirements of the real-time systems of which they are a part. In the remainder of this chapter, we discuss the requirements of real-time systems. Next, we explore the sources of the disconnects between real-time systems and GPU-equipped CV applications. Then, we present the thesis of this dissertation and provide an overview of the contributions supporting that thesis. Finally, we outline the remaining chapters in this dissertation.

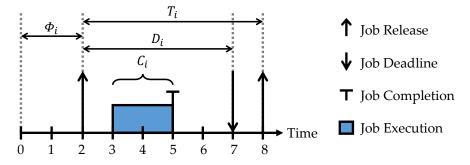

#### 1.1 Real-Time Systems

In real-time systems, the correctness of a system of applications depends not only upon the correctness of the output, but also upon the *timeliness* of the computations. Associated with each recurrent task in a real-time system are an invocation period, a relative deadline, and a worst-case execution time (WCET). To verify the correctness of a real-time task, one thus must prove that the response time of a task, *i.e.*, the time between its invocation and corresponding completion, will be bounded.

If the response time of a task must not exceed its relative deadline, then the deadline is considered to be *hard*; missing a hard deadline can have catastrophic consequences, such as a vehicle accident or occupant injury or fatality. Some deadlines, on the other hand, are classified as *soft*; it is sometimes acceptable for a soft deadline to be missed. Applications with soft deadlines are typically less safety critical. Multiple definitions exist for soft deadlines: for example, the *tardiness (i.e.,* the amount by which the deadline is missed) must be bounded, or at most a given number of deadline misses may occur. In this dissertation, we focus on soft deadlines for which the tardiness of each task must be bounded.

A hard-real-time task is *schedulable* if all of its deadlines are guaranteed to be met, whereas the soft-realtime tasks we consider are schedulable if every invocation of each task can be guaranteed to have bounded tardiness. Schedulability analysis is used to determine whether a set of tasks is schedulable, and takes into consideration the available processors on the platform, the parameters of each task, and the scheduling algorithm used to assign tasks to processors. Analysis has been developed for many different schedulers for uniprocessor platforms, and has been the subject of much research for multicore platforms in recent years. However, prior work has failed to adequately address systems that rely on multicore+accelerator platforms, or CV applications that may require cyclic data dependencies. In the next sections, we explore these challenges in more detail.

## 1.2 Autonomous Driving Applications

The input to an autonomous-driving system is a set of sensors, including cameras, lidar (light detection and ranging), and radar. Autonomous-driving applications use data from these sensors to determine the control values for the vehicle, typically specified as steering (direction), throttle (speed), and brake. There are two distinct approaches to autonomous-vehicle design. In the first approach, a system is composed of a large set of components, each developed to perform a specific task, *e.g.*, (Franke, 2017; Paden et al., 2016). Common components are those for sensor-based perception of the surrounding scene, path planning to navigate through the scene, and local control used to follow the desired path. The alternative approach takes a more end-to-end view: Deep Neural Networks (DNNs) are used to process all sensor input and directly select vehicle control values, *e.g.*, (Codevilla et al., 2018; Mnih et al., 2016). In this dissertation, we focus on the modular ADAS design approach. As many of these components involve scene perception via image-based sensors, much of our work has focused on CV algorithms used in ADAS applications.

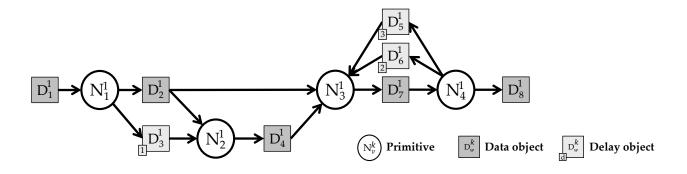

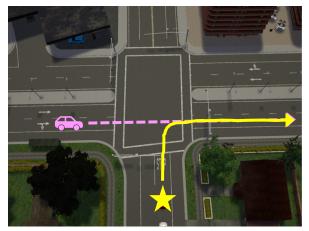

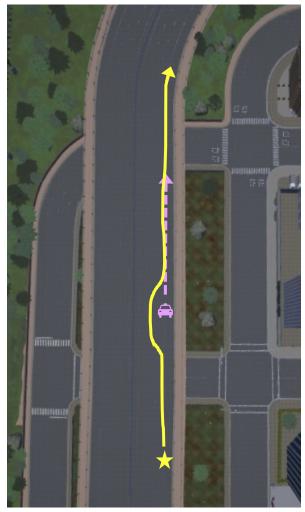

ADAS features like adaptive cruise control necessitate the anticipation of dangerous scenarios with enough time for driver or vehicle intervention. Predicting dangerous situations typically entails tracking dynamic objects, such as pedestrians and other vehicles, and using a motion model to extrapolate future positions. Such a tracking application can be expressed as a dataflow graph in which nodes represent computations or other high-level CV primitives and edges represent data dependencies. A graph for a tracking pipeline is depicted in Figure 1.1. In this example, the "Predict track positions" node uses the track produced by the "Update tracks" node during the prior time step to predict the location of an object in the current time step, introducing a *cyclical dependency* on prior results.

Recent work has applied real-time scheduling principles to produce response-time bounds for graphs (Elliott et al., 2015; Yang et al., 2015, 2016, 2018a). Unfortunately, most graph-based response-time analysis

Figure 1.1: The tracking-by-detection pipeline.

Figure 1.2: The tracking-by-detection pipeline with a supernode in place of the cycle.

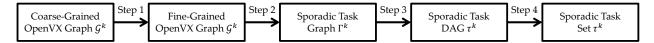

assumes that all graphs are directed acyclic graphs (DAGs), that is, that they do not contain any cycles. Thus, for prior analysis to apply, any cycles must be replaced with *supernodes*, as shown in Figure 1.2. To ensure the cyclic dependencies are respected, the supernodes are forced to execute *sequentially*, *i.e.*, a given invocation of a supernode must complete before the next can begin. However, if the utilization of the supernode is greater than 1.0 (*i.e.*, the sum of the WCETs of the nodes comprising the cycle is greater than the invocation period of the graph), then sequential execution may lead to unbounded response times. In order to be able to certify CV applications as used in ADASs, response-time analysis for cyclic graphs is needed. This requires a new task model that ensures data dependencies are respected while enabling the parallelism necessary to guarantee bounded task response times.

## **1.3 Graphics Processing Units**

GPUs were originally designed to work alongside Central Processing Units (CPUs) to accelerate computer-graphics applications. These applications require writing *shaders*, which process triangle-based matrix-multiply operations in parallel to render images. As a result, modern commercial GPUs have hundreds or thousands of parallel hardware cores to perform these computations.

The two primary GPU manufacturers are AMD and NVIDIA. AMD provides an open-source software stack for their GPUs, whereas the NVIDIA ecosystem is proprietary, including the drivers. However, in 2007, NVIDIA positioned itself as a market leader in GPU hardware with the introduction of the CUDA API (a C/C++ extension to enable general-purpose GPU computing). NVIDIA GPUs span the spectrum of

space and computing power: the Jetson series of system-on-a-chip (SoC) platforms, with low power and size profiles, are tailored for ADAS applications; the GeForce series of discrete GPUs, on the other hand, are heavier, larger, and require more power, but focus on providing high performance for personal computers.

Unfortunately, with this focus on performance, GPUs have traditionally been designed for throughput rather than predictability. For example, many details related to GPU scheduling policies are omitted from NVIDIA's documentation. This omission prevents users from developing programs that depend on CUDA features or hardware micro-architectures that may change. The cost to real-time system developers is the loss of information necessary for analysis of predictability. Furthermore, as NVIDIA drivers and CUDA source code are closed source, determining such scheduling details is a challenging task.

Additionally, the SWaP-C constraints that arise for ADAS systems necessitate sharing of hardware accelerators, such as GPUs, between multiple system components implementing the many ADAS functions. The question then arises: how can we ensure temporal isolation between multiple GPU-using components? Put another way, how can different components be given the illusion of full ownership of a GPU, such that each component may execute independently of the presence of others in the system? Once again, the closed-source nature of the NVIDIA software stack and a lack of clarity in CUDA documentation prevent simple solutions to these problems.

## 1.4 Thesis Statement

The disconnect between real-time requirements and CV-application design is a key hurdle that must be overcome to enable the certification of ADASs. In this dissertation, we assume a multicore+accelerator platform, with a focus on NVIDIA GPUs as hardware accelerators. With such a platform in mind, we address the design disconnect from three directions, as summarized in the following thesis statement:

Enabling the real-time certification of autonomous-driving applications relies on bridging the divide between real-time and computer-vision system design. This includes evaluating the trade-offs between history requirements, accuracy, and response-time bounds of computer-vision applications, utilizing knowledge of GPU scheduling policies and best practices for using GPUs in real-time applications, and enabling temporal isolation on multicore+accelerator platforms.

## 1.5 Contributions

We now briefly overview the contributions that support this thesis.

## 1.5.1 Generalized Task Model for Applications with Historical Dependencies

In Chapter 3, we introduce the rp-sporadic task model (restricted parallelism), which adds a per-task settable parameter, p, specifying the number of invocations of the same task that may execute concurrently. From a schedulability point of view, such parallelism for graph nodes in a cycle equates to setting of history age requirements for data produced by prior node execution instances. Therefore, instead of insisting on *sequential* cycle execution, which is the root cause of any over-utilization, we instead allow *parallel* execution by permitting the use of slightly older history, *i.e.*, p > 1. By allowing p > 1, the rp-sporadic task model thus enables response-time bounds to be computed for any graph containing a cycle, even if the cycle utilization exceeds 1.0.

## 1.5.2 Evaluation of the History-vs.-Response-Time-vs.-Accuracy Trade-Off

Allowing p > 1 is clearly not a solution that comes entirely "for free": as p increases, although response-time bounds may decrease, so too may CV accuracy due to using older history. This history-versusresponse-time-versus-accuracy trade-off is a key issue in the real-time certification of ADASs, of which both CV researchers and automotive designers should be aware, yet it has never been examined in depth.

In Chapter 3, we provide the first-ever detailed study of this trade-off. For the history-versus-responsetime trade-off, we explore the impact on analytical response-time bounds as p increases for a large set of synthetically generated cycle-containing graph-based task systems. To observe the impact of increasing p on the accuracy of a cyclic workload, we consider a CV application in which pedestrians and other vehicles are tracked via images recorded by a camera attached to a moving vehicle. We perform our evaluation using CARLA (Dosovitskiy et al., 2017), an open-source simulator designed for ADAS research. The use of CARLA allows us to generate a broad range of scenarios, to consider each sensing component independently, and to consider and evaluate potential modifications to the vehicle's behavior based on tracking results.

#### 1.5.3 Model of NVIDIA GPU Scheduling

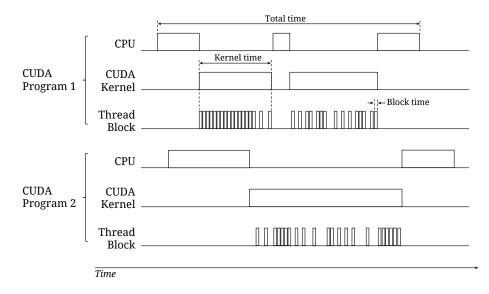

NVIDIA has marketed its Jetson line of embedded CPU+GPU platforms specifically targeting autonomous artificial-intelligence (AI) applications. In Chapter 4, we present a set of experimentally determined rules that define how the NVIDIA Jetson TX2's GPU schedules work submitted to it. These rules take into account the ordering within and among first-in-first-out (FIFO) *streams* of requests for GPU operations, the means by which various internal queues of requests are handled, the ability of the GPU to co-schedule operations so they execute concurrently, the selection mechanism used to determine the order in which requests are handled, and the resource limits that constrain the GPU's ability to handle new requests. Our rules indicate that the TX2's GPU employs a variant of hierarchical FIFO scheduling that is amenable to real-time schedulability analysis.

We then explore multiple optional GPU features that cause certain request streams to be treated specially, further complicating GPU scheduling. These features include the usage of a special stream called the *NULL stream* and the usage of *stream priorities*. The available documentation regarding both of these features lacks several details necessary for predicting specific runtime behavior. Through further experiments, we show how each of these features affects our derived scheduling rules. In addition, we discuss the differences between the rules we discerned for the TX2 and the scheduling behavior of several discrete NVIDIA GPUs.

## 1.5.4 Guidance for Using NVIDIA GPUs in Real-Time Applications

In Chapter 4, we detail several pitfalls that can arise when using NVIDIA's CUDA API to utilize NVIDIA GPUs in real-time systems, leading to unexpected delays not only on the GPU, but also on the host CPU. Such CPU blocking must factor into response-time analysis if it may occur in safety-critical applications, and thus can lead to system capacity loss.

To address the problem of detecting improper GPU use, we present CUPiD<sup>RT</sup> (<u>CUDA Pitfall D</u>etector for <u>R</u>eal-<u>T</u>ime Systems), a library we developed to monitor operations submitted to NVIDIA GPUs and report issues based on the most severe pitfalls we identified. CUPiD<sup>RT</sup> can be used with any applications that utilize NVIDIA GPUs, and although CUPiD<sup>RT</sup> was designed with real-time systems in mind, throughput-oriented applications can also benefit from detection and remediation of these issues.

To evaluate its usefulness, we detail the results produced by using CUPiD<sup>RT</sup> to analyze ten GPU-using sample applications from the popular CV library OpenCV (Bradski, 2000). Based on two of the most

problematic pitfalls we identified, we configured CUPiD<sup>RT</sup> to detect issues related to specific CUDA API commands. Of the ten sample applications we analyzed, we found that each was subject to at least one of the issues we sought to detect. We also performed a case study demonstrating the benefits of resolving the issues detected by CUPiD<sup>RT</sup>. To do so, we modified the source code of one of the ten applications, resolving all detected issues, and showed that such changes reduced execution times and improved predictability of computation-submission times.

## 1.5.5 Enabling Isolation on Multicore+Accelerator Platforms

In Chapter 5, we address the problem of ensuring temporal isolation between different components on a multicore+accelerator platform. We specifically focus on accelerators that require non-preemptive execution, and assume that each component in the system has been assigned to a given set of hardware resources that the component "owns" for given slices of time.

To ensure such isolation, we designed a hierarchical scheduler, which consists of three main parts: a tabledriven scheduler to allocate time slices and hardware resources to components, per-component schedulers that allocate processors to tasks, and a specialized locking protocol to orchestrate accelerator accesses while respecting time-slice boundaries. In addition, we provide blocking analysis for our locking protocol.

To evaluate our solution, we implemented the specialized locking protocol within the hierarchical scheduler as a scheduler plugin using LITMUS<sup>RT</sup> on a multicore+GPU platform. Enforcing temporal isolation between GPU accesses from different components revealed some unexpected edge cases, which we discuss in detail, as well as our resulting solution for budgeting GPU accesses.

## 1.5.6 Additional Evaluations

In Chapter 6, we consider a set of automotive applications, including the tracking application considered in Chapter 3, all running as real-time tasks within the LITMUS<sup>RT</sup> developmental real-time operating system (Brandenburg, 2011; Calandrino et al., 2006). We use this task set as a basis of further evaluation. First, we consider the full history-versus-response-time-versus-accuracy trade-off. Our experiments show that relaxing the history requirements (*i.e.*, allowing p > 1) can enable lower observed response times with only a minimal impact on application accuracy. Then, we provide a detailed evaluation of our time-partitioning solution from Chapter 5. We explore the appropriate choice of time-slice lengths and validate the isolation afforded by our approach.

## 1.6 Organization

The rest of this dissertation is organized as follows. In Chapter 2, we provide an overview of related background on real-time scheduling, CV applications used in ADASs, and the software and hardware used to enable such applications. We then dive into the trade-offs between historical data dependencies, algorithm accuracy, and application response times in Chapter 3. In Chapter 4, we detail the scheduling policies of NVIDIA GPUs, and address the pitfalls that can arise in their use in real-time applications and how to detect such issues. In Chapter 5, we introduce our framework to ensure temporal isolation on multicore+accelerator platforms between unrelated system components. Then, in Chapter 6, we discuss the results of our extended evaluations using a set of ADAS-related applications. Finally, we conclude in Chapter 7.

## **CHAPTER 2: BACKGROUND**

In this chapter, we provide an overview of background related to real-time autonomous-driving applications. We first discuss various applications necessary for ADASs (Section 2.1). Then, we list several software libraries and GPUs that can be used to realize such applications (Sections 2.2 and 2.3). Finally, we formally review existing real-time task models, including models for graph-based CV applications (Section 2.4). We conclude by discussing our contributions in the context of prior work (Section 2.5).

#### 2.1 Autonomous-Driving Applications

A common approach to autonomous-vehicle design is to separately develop several software components that facilitate path planning, perception, and control for a vehicle, *e.g.* (Franke, 2017; Paden et al., 2016). We now briefly survey different applications used to implement these components. We will see that a feature of these algorithms is that they are often graph based, *e.g.*, organized as a dataflow graph of processing steps.

## 2.1.1 Path Planning

Path planning can be done at two granularity levels: a global planner determines the high-level path from the start position to the goal position, and a local planner determines more fine-grained motion between waypoints on that path. For example, a global planner may determine which intersections and lanes a vehicle should traverse, whereas the local planner chooses the steering angles necessary to perform lane changes.

**Global planning.** Global planning algorithms typically act on graph-based discretizations of mapping data. As an example, consider the map depicted in Figure 2.1. This map has eight intersections, labeled A-H, which correspond to nodes in the map's graph-based representation. Roads connecting intersections correspond to edges in the graph. Global planning can thus be viewed as a shortest-path problem in a graph. For example, breadth-first search, depth-first search, or Dijkstra's algorithm may be used. A breadth-first path from intersection C to intersection H (assuming ties are broken alphabetically) is shown in Figure 2.2. The corresponding search graph is shown in Figure 2.3.

Figure 2.1: A town from the autonomous-driving simulator CARLA (Dosovitskiy et al., 2017), overlaid with the graph corresponding to intersections and their connecting roads.

Figure 2.2: The path from node C to node H resulting from breadth-first search.

Figure 2.3: The path from node C to node H resulting from breadth-first search.

Other shortest-path algorithms, such as  $A^*$ , can make use of heuristics to improve the shortest path found in global planning. Another approach, called Rapidly-exploring Random Trees (RRT) (LaValle and Kuffner Jr, 2001), randomly chooses a node in the graph to extend at each iteration.

**Local planning.** Local planners act on segments of the path produced by a global planner to determine more fine-grained actions. For example, given the path segment between intersections A and H in Figure 2.2, a local planner will navigate between waypoints along that segment, and utilize perception algorithms to ensure that the vehicle stays in the appropriate lane. Additionally, a global planner may not consider obstacles in the scene, but the local planner must ensure an obstacle-free path if possible.

One approach to local planning is the Pure Pursuit path-tracking algorithm (Coulter, 1992). This algorithm computes the curved trajectory necessary for a vehicle to travel from its current position to a goal point (*e.g.*, the next waypoint along the path computed by the global planner). If perception algorithms detect obstacles along the computed arc, an alternate steering direction can be chosen to avoid those obstacles.

Local planning can also be implemented using the Artificial Potential Field (APF) method (Khatib, 1986), which associates with each point in space (*e.g.* positions on the 2D road map) a potential value corresponding to whether the vehicle should occupy that point. Obstacles (or points not on the road) are assigned a high repulsive potential, and the center of the appropriate lane is given a high attractive potential. Additionally, vehicle-dynamics constraints can be included when determining potential values to rule out regions of space that the vehicle cannot reach, *e.g.*, based on its current orientation and turning radius (Song et al., 2020). The local planner then chooses a path that tends towards the attractive-potential points on the way to the goal.

Figure 2.4: Lane-detection pipeline using the Hough Transform.

Figure 2.5: Pedestrian-detection pipeline using HOG features.

## 2.1.2 Perception

The path-planning algorithms discussed in Section 2.1.1 rely on perception algorithms, *e.g.*, to determine lane boundaries and detect and track potential obstacles. We now discuss a few of these algorithms for CV applications that process streams of images from cameras.

Lane detection via the Hough Transform. Lane detection can be done using the Hough Transform, which detects features such as lines in an image. As shown in Figure 2.4, the image is first converted to grayscale and unnecessary regions (*e.g.*, the top half, which may correspond to the sky and is unlikely to contain lane lines) are masked out. Then, a threshold is applied, given the assumption that lane lines are bright and the road is dark. Finally, the Hough Transform can be used to detect lane lines in the thresholded image.

**Pedestrian detection via Histogram of Oriented Gradients (HOG).** The HOG-based pedestrian-detection algorithm (Dalal and Triggs, 2005; Prisacariu and Reid, 2009) computes gradients (the HOG features) within an image at a range of different scales, and classifies potential detections at each scale. The computational cost increases with the number of image scales, but each scale enables detection of a pedestrian at a different distance from the camera. The HOG features are provided to a classifier such as a Support Vector Machine (SVM), which determines whether a potential detection is a pedestrian. The output is a series of rectangular regions of the image ("bounding boxes") of varying sizes and positions, along with probability values that reflect the likelihood of a correct detection. This process is depicted in Figure 2.5 for three image scales; in the experiments in Chapters 4–6, we used 13 image scales.

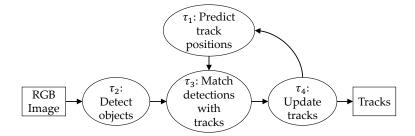

**Multi-Object Tracking (MOT).** MOT tracks an unknown number of objects, or *targets*, through a scene. A *track* is a sequence of estimated positions and sizes (as bounding boxes) of a target over time. A track is a model of a target's *trajectory*, *i.e.*, the sequence of its actual real-world positions through time. Time is measured by camera frames.

Tracking-by-detection is a common approach to MOT. This pipeline is illustrated in Figure 1.1. The output from frame t is the set of tracks after frame t. The input to frame t is an RGB image and the set of tracks from frame t - 1. A key challenge in tracking-by-detection is to match detected bounding boxes with predictions of new track positions. To do this, the percentage overlap is compared for all detection-prediction rectangle pairs. The Hungarian method (also known as Munkres' algorithm) can be used to quickly match detections to predictions (Milan et al., 2016; Stiefelhagen et al., 2006). The overlap of two rectangles is computed using the *Intersection-over-Union* measure (IoU) (Rezatofighi et al., 2019), also known as the Jaccard index. The IoU (a scalar) is the ratio of the size of the intersection to the size of the union of two rectangles within an image. The Hungarian algorithm chooses an assignment of detections to predictions that maximizes the IoU of the selected pairs.

## 2.1.3 Control

Using the results of perception algorithms, the local planner must output control values. For a vehicle, these are typically in the form of steering, throttle, and brake. However, the desired values may change greatly from one time step to the next. To generate a stable and smooth path, a controller, *e.g.*, a proportional-integral-derivative (PID) controller (Åström and Murray, 2021), uses a feedback loop to determine the control output for the current time step. For a PID controller, this output depends on the error (computed as the difference between the desired value and the observed value), as well as the integral and derivative of the error. The resulting control output can then be translated to motor revolution speed, wheel angles, *etc*.

## 2.2 Software for Real-Time Autonomous-Driving Applications

In this section, we provide a brief overview of several software libraries that enable real-time graph-based applications to be developed, autonomous vehicles to be simulated, and CV and other AI applications to be designed and built upon.

## 2.2.1 Real-Time Software

A real-time operating system (RTOS) provides support for predictable job execution based on real-time scheduling algorithms. One such RTOS is LITMUS<sup>RT</sup> (Brandenburg, 2011; Calandrino et al., 2006), which was designed for real-time researchers to prototype different schedulers and synchronization protocols. LITMUS<sup>RT</sup> is a modified Linux kernel that introduces a real-time scheduling class for which scheduling plugins can be written. LITMUS<sup>RT</sup> provides several existing plugins, and in Chapter 5 we discuss a new plugin that enables time partitioning between different system applications. As part of this plugin, we implemented a time-partitioning-aware locking protocol to arbitrate access to hardware accelerators.

To enable real-time scheduling of graph-based applications, Elliott *et al.* (2014) developed PGM<sup>RT</sup>. This library enables inter-process communication by operating-system threads representing different graph nodes; each invocation of a node in the graph must wait until all of its predecessors (corresponding to incoming graph edges) have produced data. We utilize PGM<sup>RT</sup> in our evaluation discussed in Chapter 6.

#### 2.2.2 CARLA: an Autonomous-Driving Simulator