Theses & Dissertations

Boston University Theses & Dissertations

2021

# True shared memory architecture for next-generation multi-GPU systems

https://hdl.handle.net/2144/42590 Boston University

# BOSTON UNIVERSITY COLLEGE OF ENGINEERING

#### Dissertation

# TRUE SHARED MEMORY ARCHITECTURE FOR NEXT-GENERATION MULTI-GPU SYSTEMS

by

#### MD SAIFUL AREFIN MOJUMDER

B.Sc., Bangladesh University of Engineering & Technology, 2013 M.Sc., Bangladesh University of Engineering & Technology, 2015

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

#### Approved by

First Reader

Ajay Joshi, Ph.D.

Associate Professor of Electrical and Computer Engineering

Second Reader

Martin Herbordt, Ph.D.

Professor of Electrical and Computer Engineering

Third Reader

Tali Moreshet, Ph.D.

Senior Lecturer and Research Assistant Professor of Electrical and Computer Engineering

Fourth Reader

David R. Kaeli, Ph.D.

Distinguished Professor of Electrical and Computer Engineering Northeastern University

#### Acknowledgments

First, I would like to express my sincere gratitude to my PhD adviser, Prof. Ajay Joshi, for his tireless support and encouragement throughout the course of the PhD program. During the ups and downs of the PhD life, Prof. Joshi was a constant source of guidance and assistance in enhancing my research endeavours and skills. Over the years, I have enjoyed working with and learning from him. Undoubtedly, this thesis would not have been complete without him.

I would like to thank my collaborators, Prof. David Kaeli, Prof. John Kim, Prof. José L. Abellán, Amir Kavyan Ziabari, Yifan Sun, and Trinayan Baruah for their sincere support, assistance and guidance throughout my PhD work. I learnt how to think about big picture and focus on solving problems from Prof. Kaeli. Prof. Kim provided the access to the multi-GPU system that we extensively used throughout this work. José's persistent scrutiny of my work always kept me on the right track and I learned the fact that "no detail is too small in research" from him. Amir helped me ramp up in research during the early stage of my PhD. I particularly enjoyed and learnt a lot working with Yifan Sun who was always there to help.

I want to thank the rest of my thesis committee memebers, Prof. Martin Herbordt and Prof. Tali Moreshet, for their precious time and insightful feedback. Additionally, I learnt the basics of computer architecture from the course taught by Prof. Moreshet, while the valuable lesson I learnt from the 'High Performance Programming with Multicore and GPUs' taught by Prof. Herbordt helped me design experiments for my research.

Many thanks to my labmates, Yenai Ma, Leila Delshadtehrani, Marcia Sahaya Luis and Furkan Eris at Boston University. I would also like to thank all the members of the ICSG research lab, the PEAC Lab research group, and the CAAD research group.

Finally, I want to express my gratitude to my parents for their endless love, unconditional support and incessant encouragement throughout my life. In particular, my mother

has been the constant source of inspiration for all the achievements in my life. I want to specially thank my wife, Tasmiah Nuzhath, who stood by me during this uncertain journey and was a persistent source of support and encouragement.

TRUE SHARED MEMORY ARCHITECTURE FOR

NEXT-GENERATION MULTI-GPU SYSTEMS

MD SAIFUL AREFIN MOJUMDER

Boston University, College of Engineering, 2021

Major Professor: Ajay Joshi, PhD

Associate Professor of Electrical and Computer

Engineering

**ABSTRACT**

Machine learning (ML) is now omnipresent in all spheres of life. The use of deep neu-

ral networks (DNNs) for ML has gained popularity over the past few years. This is because

DNNs are capable of efficiently solving complex problems such as image processing, ob-

ject detection, language processing, etc. To train these DNN workloads, graphics process-

ing units (GPUs) have become the most widely used platform. A GPU can support a large

number of parallel threads that execute simultaneously to achieve a very high throughput.

However, as the sizes of the DNN workloads grow, a single GPU is no longer adequate to

provide fast training, and developers resort to using multi-GPU (MGPU) systems that can

reduce the training time significantly. Consequently, to keep pace with the growth of DNN

applications, GPU vendors are actively developing novel and efficient MGPU systems.

To better understand the challenges associated with designing MGPU systems for

DNN workloads, in this thesis, we first present our efforts to understand the behavior of

the DNN workloads, in particular, the training of DNN workloads on MGPU systems.

Using the DNN workloads as benchmarks, we observe the evolution of MGPU system

architecture. Based on our profiling and characterization of DNN workloads on exist-

vi

ing high-performance MGPU systems, we identify the computation- and communication-intensiveness of the DNN workloads and the hardware- and software-level inefficiencies present in the existing MGPU systems. We find that the data movement across multiple GPUs and high remote data access cost leading to NUMA effects, data duplication, and inefficient use of GPU memory leading to memory capacity issues, and the complexity in programming MGPUs pose serious limitations in the execution of ever-scaling DNN workloads on MGPU systems.

To overcome the limitations of existing MGPU systems, we propose to unify the main memory of GPUs to design an MGPU system with true shared memory (MGPU-TSM). Our proposed MGPU-TSM system demonstrates a significant performance boost (3.8× for a 4 GPU system) over the best-performing existing MGPU system. This is because MGPU-TSM system eliminates the NUMA effects and the necessity for data duplication. To provide seamless data sharing across multiple GPUs and ease programming of MGPU-TSM, we propose a light-weight coherence protocol called MGCC. MGCC is a timestamp-based protocol that provides both intra- and inter-GPU coherence. We implement a number of hardware features including unified memory controller, request tracker and timestamp storage unit to support MGCC. Using both standard and synthetic stress benchmarks, we evaluate the MGPU-TSM system with MGCC leveraging sequential as well as relaxed consistency. Our evaluation of a 4-GPU system using MGPUSim simulator suggests that our proposed coherent MGPU system achieves up to 3.8× improved performance than current best-performing MGPU system while the stress tests performed using synthetic benchmarks suggests that MGCC leads to up to 46.1% performance overhead.

## **Contents**

| 1 | Intr | oductio | n                                                 | 1  |

|---|------|---------|---------------------------------------------------|----|

|   | 1.1  | A Brie  | ef History of GPUs                                | 1  |

|   | 1.2  | Backg   | round                                             | 3  |

|   |      | 1.2.1   | Deep Learning using MGPU Systems                  | 4  |

|   |      | 1.2.2   | MGPU System Architecture                          | 7  |

|   |      | 1.2.3   | Remote Memory Access Mechanisms in an MGPU System | 9  |

|   |      | 1.2.4   | Coherence and Consistency in GPU and MGPU Systems | 11 |

|   | 1.3  | Challe  | nges in Existing MGPU Systems                     | 14 |

|   |      | 1.3.1   | DNN Training on MGPU Systems                      | 14 |

|   |      | 1.3.2   | RDMA Access Cost                                  | 17 |

|   | 1.4  | Thesis  | Contributions                                     | 18 |

|   |      | 1.4.1   | DNN Workload Characterization on MGPU Systems     | 19 |

|   |      | 1.4.2   | MGPU Systems with True Shared Memory              | 21 |

|   |      | 1.4.3   | Coherence in MGPU-TSM                             | 21 |

|   | 1.5  | Relate  | d Work                                            | 23 |

|   |      | 1.5.1   | DNN Workload Characterization on MGPU Systems     | 23 |

|   |      | 1.5.2   | NUMA Effects in MGPU System                       | 24 |

|   |      | 1.5.3   | MGPU Memory System and Coherence                  | 25 |

|   | 1.6  | Organi  | ization                                           | 27 |

| 2 | DNI  | N Work  | load Characterization on Existing MGPU Systems    | 29 |

|   | 2.1  | Workle  | oad Characterization on Pre-Volta MGPU Systems    | 29 |

|   |      | 2.1.1  | DNNs                                             | 30 |

|---|------|--------|--------------------------------------------------|----|

|   |      | 2.1.2  | Evaluation Methodology                           | 36 |

|   |      | 2.1.3  | Evaluation Results                               | 38 |

|   |      | 2.1.4  | Summary                                          | 45 |

|   | 2.2  | Worklo | oad Characterization on DGX-1 Volta MGPU Systems | 46 |

|   |      | 2.2.1  | Evaluation Methodology                           | 47 |

|   |      | 2.2.2  | Evaluation Results                               | 50 |

|   |      | 2.2.3  | NCCL Overhead                                    | 55 |

|   |      | 2.2.4  | Training Time Breakdown                          | 57 |

|   |      | 2.2.5  | Memory Usage Analysis                            | 60 |

|   |      | 2.2.6  | Weak Scaling                                     | 63 |

|   |      | 2.2.7  | Accelerating Training of DNNs                    | 64 |

|   |      | 2.2.8  | Summary                                          | 65 |

|   | 2.3  | Evalua | tion of MGPU Systems Using Synthetic Workloads   | 66 |

|   |      | 2.3.1  | Synthetic Workloads                              | 67 |

|   |      | 2.3.2  | Evaluation Results Using Synthetic Workloads     | 70 |

| 3 | True | Shared | l Memory for MGPU System                         | 73 |

|   | 3.1  | MGPU   | T-TSM Architecture                               | 73 |

|   | 3.2  | Evalua | tion Methodology                                 | 76 |

|   |      | 3.2.1  | MGPU System Configurations                       | 76 |

|   |      | 3.2.2  | Simulation Platform                              | 77 |

|   |      | 3.2.3  | Standard Application Benchmarks                  | 77 |

|   | 3.3  | Evalua | tion Results                                     | 78 |

|   | 3.4  | Therm  | al Feasibility of MGPU-TSM                       | 80 |

|   | 3 5  | Summa  | arv                                              | 81 |

| 4  | Coh    | erence   | in MGPU-TSM                                    | 83    |

|----|--------|----------|------------------------------------------------|-------|

|    | 4.1    | Times    | tamp-Based Coherence in a Single GPU System    | . 83  |

|    |        | 4.1.1    | Applicability of G-TSC Protocol in MGPU System | . 85  |

|    | 4.2    | MGC      | C Protocol for Coherence in MGPU-TSM           | . 86  |

|    |        | 4.2.1    | Read Operations                                | . 86  |

|    |        | 4.2.2    | Write Operations                               | . 88  |

|    |        | 4.2.3    | Intra-GPU Coherence                            | . 90  |

|    |        | 4.2.4    | Inter-GPU Coherence                            | . 92  |

|    |        | 4.2.5    | Request Tracker Operation                      | . 93  |

|    |        | 4.2.6    | TSU Implementation                             | . 93  |

|    |        | 4.2.7    | Timestamp Design                               | . 95  |

|    | 4.3    | Evalua   | ation Methodology                              | . 96  |

|    |        | 4.3.1    | MGPU System Configurations                     | . 96  |

|    |        | 4.3.2    | Simulation Platform                            | . 97  |

|    |        | 4.3.3    | Synthetic Benchmarks                           | . 97  |

|    | 4.4    | Evalua   | ation                                          | . 100 |

|    |        | 4.4.1    | Standard Application Benchmarks                | . 100 |

|    |        | 4.4.2    | Xtreme Benchmarks                              | . 106 |

|    | 4.5    | Summ     | ary                                            | . 111 |

| 5  | Sum    | ımary a  | and Future Work                                | 112   |

|    | 5.1    | Summ     | ary of the thesis                              | . 112 |

|    | 5.2    | Future   | Directions                                     | . 114 |

|    |        | 5.2.1    | Workload Characterization and Benchmarking     | . 114 |

|    |        | 5.2.2    | MGPU System Design                             | . 115 |

| Re | eferen | ices     |                                                | 117   |

| C- | ıppian | ılıım Vi | taa                                            | 130   |

|    |        | 🗸 1      | IAE                                            | 1.7   |

## **List of Tables**

| 1.1 | .1 Comparison of different communication mechanisms in existing MGPU                                            |    |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------|----|--|--|--|

|     | systems. We compare the main memory usage and programmability of                                                |    |  |  |  |

|     | each mechanism w.r.t. P2P memcpy (baseline for comparison represented                                           |    |  |  |  |

|     | by '-'), and remote memory (RM) access latency and bandwidth w.r.t. local                                       |    |  |  |  |

|     | main memory access latency and bandwidth. ' $X$ ', ' $\checkmark$ ', and ' $\checkmark$ $\checkmark$ ' indicate |    |  |  |  |

|     | 'no', 'fair', and 'good', respectively                                                                          | 10 |  |  |  |

| 2.1 | Shape parameters of a CONV/FC layer                                                                             | 33 |  |  |  |

| 2.2 | MGPU Systems evaluated in this work                                                                             | 37 |  |  |  |

| 2.3 | Specifications of the CNN Networks used in this Work. More details about                                        |    |  |  |  |

|     | the CNN workloads can be found in Section 2.2.1                                                                 | 38 |  |  |  |

| 2.4 | Profiling results for different workloads on 1 and 2 GPUs in Kepler, Titan                                      |    |  |  |  |

|     | and DGX-1 MGPU systems                                                                                          | 42 |  |  |  |

| 2.5 | Evaluation results for different CNN workloads using 2 GPUs of the                                              |    |  |  |  |

|     | MGPU systems                                                                                                    | 43 |  |  |  |

| 2.6 | Scaling in DGX-1 MGPU system for different CNN workloads <sup>1</sup>                                           | 45 |  |  |  |

| 2.7 | Description of the networks. (Conv = Convolution, Incep = Inception, and                                        |    |  |  |  |

|     | FC = Fully Connected)                                                                                           | 49 |  |  |  |

| 2.8 | NCCL overhead compared to P2P for the workloads executed on a single                                            |    |  |  |  |

|     | GPU                                                                                                             | 56 |  |  |  |

| 2.9 | cudaStreamSynchronize API overhead for training LeNet with a batch                                              |    |  |  |  |

|     | size of 16, 32 and 64 using 1, 2, 4 and 8 GPUs                                                                  | 59 |  |  |  |

| 2.10 | Memory usage when using the NCCL-based communication method dur-         |    |

|------|--------------------------------------------------------------------------|----|

|      | ing the pre-training stage and the training stage of DNNs when using 4   |    |

|      | GPUs. The memory usage of all GPUs is the same for the pre-training      |    |

|      | stage. GPUz refers to the memory usage of a GPU during the pre-training, |    |

|      | where z can take any value from 0 to 3. GPU0 refers to the memory usage  |    |

|      | of the GPU0 during training while GPUx refers to memory usage of the     |    |

|      | remaining GPUs, where x can take any value from 1 to 3                   | 61 |

|      |                                                                          |    |

| 3.1  | GPU Architecture                                                         | 77 |

| 3.2  | Application benchmark suite used for evaluation. Memory represents the   |    |

|      | footprint of the GPU memory required by a benchmark                      | 78 |

| 3.3  | RDMA and DRAM transaction counts for MGPU-RDMA, per 100M instructions.   | 80 |

| 3.4  | MGPU-TSM components obtained from publicly available product speci-      |    |

|      | fications                                                                | 80 |

| 4.1  | Terminologies and definitions                                            | 84 |

# **List of Figures**

| 1.1 | The timeline of an epoch during MGPU DNN training using the data-          |    |

|-----|----------------------------------------------------------------------------|----|

|     | parallelism approach with synchronous SGD. FP, BP, AVG, and AG repre-      |    |

|     | sent forward propagation, backward propagation, averaging, and add gra-    |    |

|     | dients, respectively. (This figure is not drawn to scale.)                 | 6  |

| 1.2 | Conventional MGPU system. Switch (SW) handles the remote access re-        |    |

|     | quests from one GPU to another GPU. PCIe or NVLink is used as the          |    |

|     | off-chip link.                                                             | 8  |

| 1.3 | Runtime of SGEMM kernel from cuBLAS library for different matrix sizes.    |    |

|     | Each bar corresponds to a different distribution of local and remote mem-  |    |

|     | ory accesses                                                               | 18 |

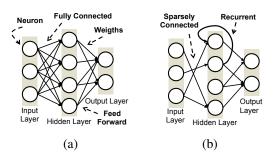

| 2.1 | Artificial Neural Networks commonly used in Deep Learning. (a) Multi       |    |

|     | Layer Perceptron (MLP). (b) Convolutional Neural Network (CNN):            |    |

|     | AlexNet (Krizhevsky et al., 2012). CONV = Convolutional layer, MP =        |    |

|     | Max-Pooling layer, and FC = Fully-Connected Layer. (c) Recurrent Neu-      |    |

|     | ral Network (RNN) with sparsely-connected neurons                          | 31 |

| 2.2 | Effect of changing batch size for MNIST dataset for training in a 3-layer- |    |

|     | MLP and LeNet network using 2 GPUs of the Kepler, Titan and DGX-1          |    |

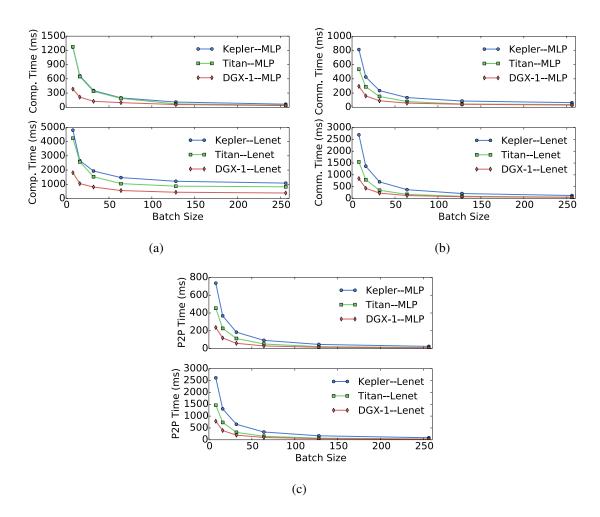

|     | system                                                                     | 40 |

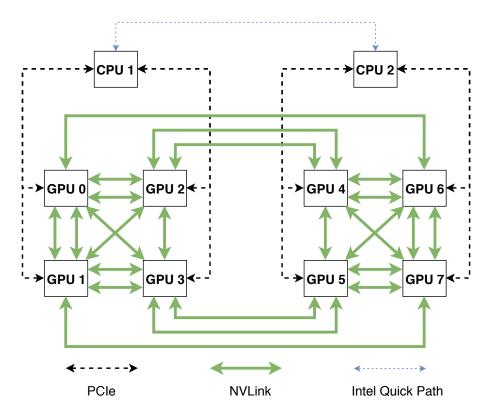

| 2.3 | Network Topology in a DGX-1 System.                                        | 48 |

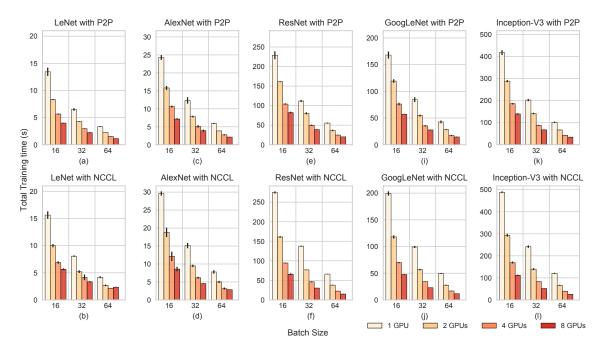

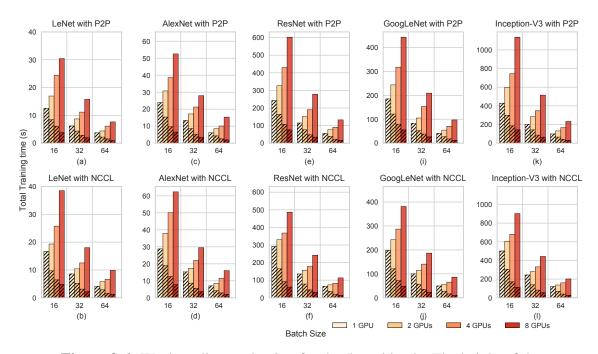

| 2.4        | Training time per epoch for 5 different workloads on the Volta-based DGX-    |     |

|------------|------------------------------------------------------------------------------|-----|

|            | 1 system using the P2P and the NCCL-based communication. Each bar            |     |

|            | represents the mean training time of 5 repetitions. The standard deviation   |     |

|            | is shown by the black line on top of each bar                                | 51  |

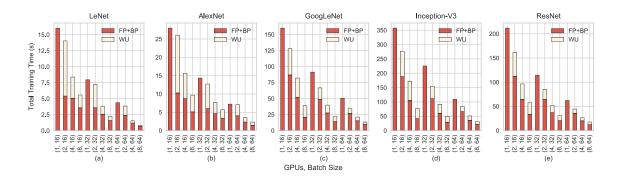

| 2.5        | Breakdown of training time into computation (FP stage and BP stage) time     |     |

|            | and communication (WU stage) time. The X-axis represents (GPU count,         |     |

|            | Batch Size)                                                                  | 57  |

| 2.6        | Weak scaling evaluation for the 5 workloads. The height of the 'entire bar'  |     |

|            | represents the total time per epoch for training with 256k, 512k, 1024k and, |     |

|            | 2048k images using 1, 2, 4 and, 8 GPUs, respectively. The height of the      |     |

|            | 'hatched bar' represents the average time to train with 256k images. This    |     |

|            | facilitates the comparison between the training time for weak scaling with   |     |

|            | that for strong scaling                                                      | 63  |

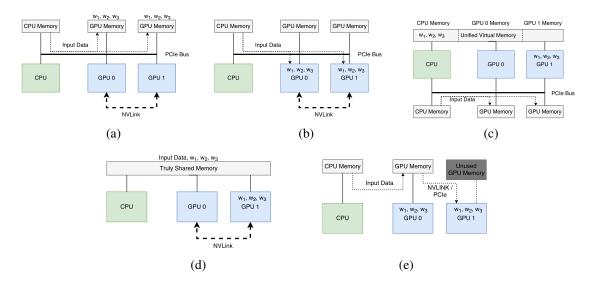

| 2.7        | Distribution of input data and weights for synthetic workload representing   |     |

|            | (a) baseline P2P memcpy, (b) zerocopy, (c) unified virtual memory for gra-   |     |

|            | dient synchronization, (d) our proposed true shared memory model and, (e)    |     |

|            | implementation of our true shared memory model to improve performance        |     |

|            | of DL workloads                                                              | 68  |

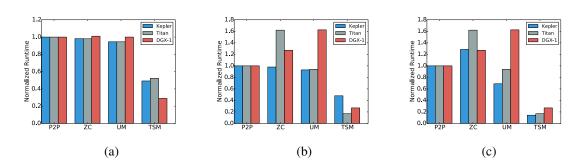

| 2.8        | Performance comparison of different data transfer mechanisms among the       |     |

|            | three MGPU systems (2 GPUs of each system) using synthetic workloads         |     |

|            | that mimic (a) MNIST dataset (b) Cifar10 dataset (c) ImageNet dataset with   |     |

|            | MLP network                                                                  | 70  |

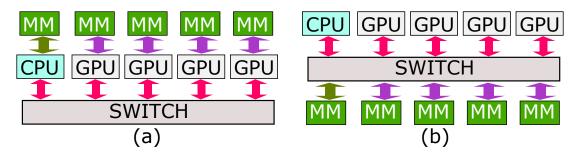

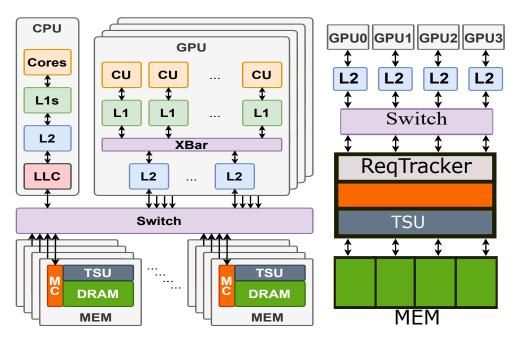

| 3.1        | (a) Conventional MGPU system vs. (b) MGPU-TSM                                | 74  |

| 3.2        | A high-level representation of our MGPU-TSM architecture (left). The         | , . |

| . <b>.</b> | description of the TSU is provided in Section 4.2.6                          | 75  |

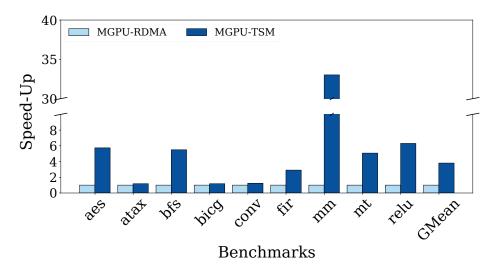

| 3.3        | Speedup of our MGPU-TSM system w.r.t. a MGPU-RDMA system                     | 79  |

| 55         | Special of our not of forth system with a more of indicate system.           | ,,  |

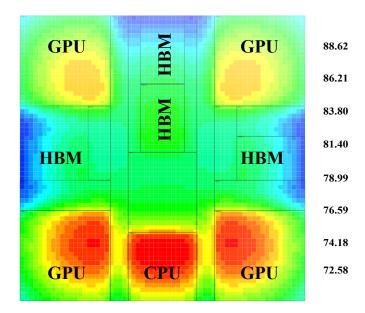

| 3.4 | Thermal map for an MGPU-TSM system with 4GPUs, 1 CPU and 4 HBM                  |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | stacks on an interposer (50mm $\times$ 50mm) using 2.5D integration technology. | 82  |

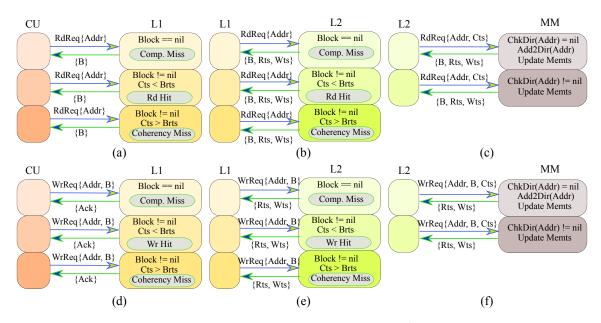

| 4.1 | Transactions between (a) a CU and an L1\$ for read operations, (b) an L1\$      |     |

|     | and an L2\$ for read operations, (c) an L2\$ and the MM for read operations,    |     |

|     | (d) a CU and an L1\$ for write operations, (e) an L1\$ and an L2\$ for write    |     |

|     | operations, and (f) an L2\$ and the MM for write operations                     | 87  |

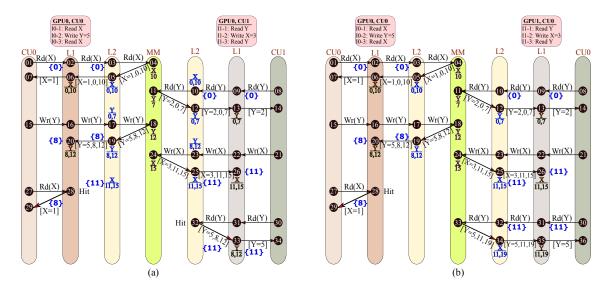

| 4.2 | The timeline for (a) the intra- and (b) inter-GPU coherence. [] represents      |     |

|     | response traffic in [Data, wts, rts] or [Data] format, {} represents the        |     |

|     | updated cts of a cache. In (a), the two L2\$ instances refer to the same        |     |

|     | physical L2\$                                                                   | 90  |

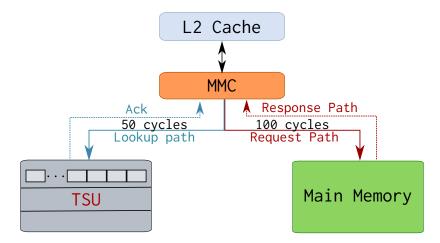

| 4.3 | Time Stamp Unit (TSU). The TSU operates independently and in parallel           |     |

|     | with the memory access                                                          | 94  |

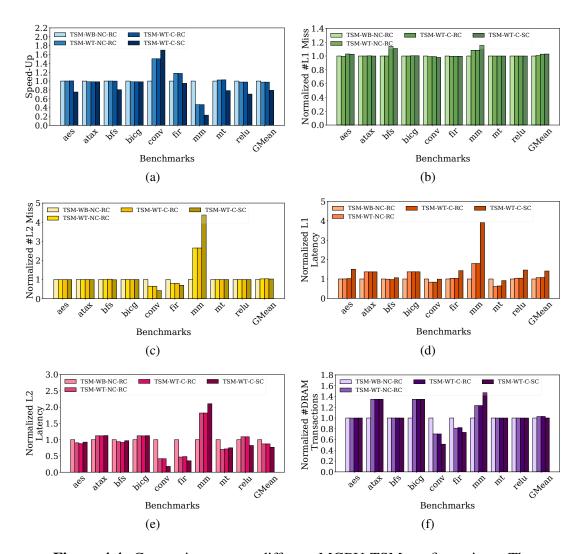

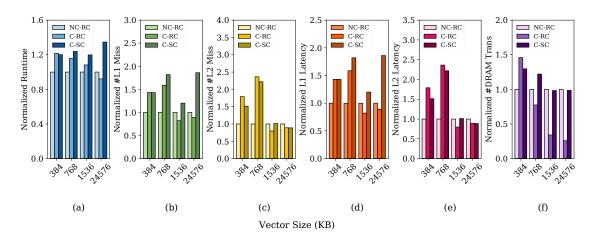

| 4.4 | Comparison across different MGPU-TSM configurations. The results are            |     |

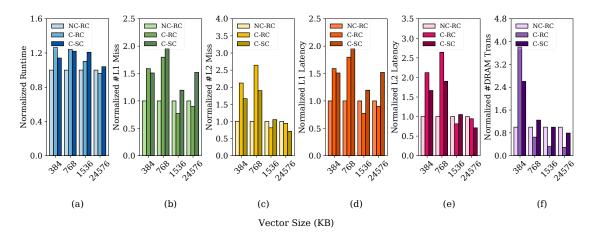

|     | normalized w.r.t. the TSM-WB-NC-RC                                              | 101 |

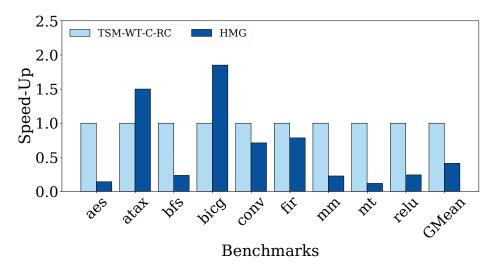

| 4.5 | Comparison of MGPU-TSM with MGCC to the state-of-the-art MGPU                   |     |

|     | with HMG. Figure shows the speedup of HMG w.r.t. TSM-WT-C-RC                    | 104 |

| 4.6 | Study of bandwidth sensitivity of MGPU-TSM with 4 GPUs for different            |     |

|     | system bandwidth ranging from 128GB/s to 4096GB/s in the case of RC             |     |

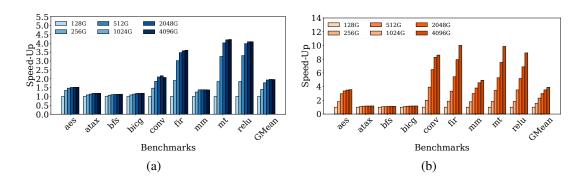

|     | (a) and SC (b)                                                                  | 104 |

| 4.7 | Scalability of coherent MGPU-TSM configurations. The results are nor-           |     |

|     | malized w.r.t. coherent MGPU-TSM with 4 GPUs                                    | 105 |

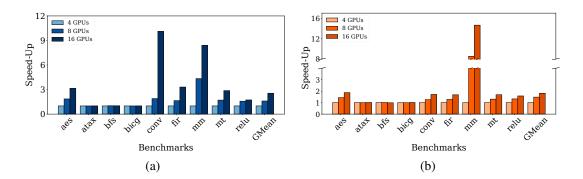

| 4.8 | Evaluation of MGPU-TSM configurations using <b>Xtreme1</b> benchmarks for       |     |

|     | different vector sizes per GPU                                                  | 108 |

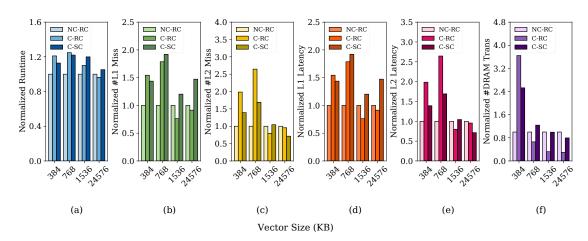

| 4.9 | Evaluation of MGPU-TSM configurations using <b>Xtreme2</b> benchmarks for       |     |

|     | different vector sizes per GPU.                                                 | 109 |

| 4.10 | Evaluation of MGPU-TSM configurations using <b>Xtreme3</b> benchmarks for |     |

|------|---------------------------------------------------------------------------|-----|

|      | different vector sizes per GPU                                            | 109 |

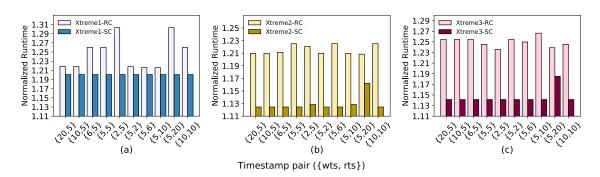

| 4.11 | Timestamp sensitivity for a vector size of 384KB. The runtime is normal-  |     |

|      | ized w.r.t. the TSM-WT-NC-C. {wts.rts} refers to {WrLease.RdLease}        | 110 |

## **List of Abbreviations**

| AWS         | <br>Amazon Web Services                |

|-------------|----------------------------------------|

| BP          | <br>Backward Propagation               |

| CPU         | <br>Central Processing Unit            |

| CU          | <br>Compute Unit                       |

| DL          | <br>Deep Learning                      |

| DNN         | <br>Deep Neural Network                |

| DtoH        | <br>Device-to-Host                     |

| FP          | <br>Forward Propagation                |

| GPU         | <br>Graphics Processing Unit           |

| HtoD        | <br>Host-to-Device                     |

| MC          | <br>Memory Controller                  |

| MCM         | <br>Multi-Chip Module                  |

| ME          | <br>Metric Evaluation                  |

| Memcpy      | <br>Memory copy                        |

| MGCC        | <br>Multi-GPU Cache Coherence          |

| MGPU        | <br>Multiple Graphics Processing Units |

| ML          | <br>Machine Learning                   |

| P2P         | <br>Peer-to-Peer                       |

| SGD         | <br>Stochastic Gradient Descent        |

| SM          | <br>Streaming Multiprocessor           |

| <b>SWMR</b> | <br>Single-Writer-Multiple-Reader      |

| TSM         | <br>True Shared Memory                 |

| TSU         | <br>Timestamp Storage Unit             |

| UM          | <br>Unified Memory                     |

| WU          | <br>Weight Update                      |

#### Chapter 1

#### Introduction

#### 1.1 A Brief History of GPUs

Graphics Processing Units (GPUs) have been used in computing systems for more than four decades. GPUs were first used in 1978 (Booth et al., 1985) to accelerate video processing. At the beginning, GPUs (although not officially called GPU) targeted the gaming applications. Among the early versions of GPU, the IBM Professional Graphics Controller (PGA) was launched in the market in 1984 and it took over the video processing tasks from the central processing unit (CPU) (James, 1987), (McClanahan, 2010). With the introduction of OpenGL in 1989, Silicon Graphics Inc. (SGI) pioneered the development of the graphics pipeline (Crow, 2004). The graphics cards released by SGI were mostly limited to the workstations, and graphics hardware vendors such as 3DFX, NVIDIA, ATI, and Matrox took the opportunity to market the consumer 3D graphics accelerators in the 1990s (Mc-Clanahan, 2010). The adoption of the GPU hardware started growing with the release of games such as Quake and Doom that relied on these graphics boards (McClanahan, 2010). The first true GPU was released by NVIDIA in 1999 (GeForce256) (Dietrich, 1999) and ATI released its first true GPU in 2000 (Radeon 7500) (Crayton et al., 2004). With the introduction of these two GPUs, the gaming industry started to surge. NVIDIA took the big step of making GPU pipeline programmable in 2001 (Crow, 2004). With the introduction of CUDA (Kirk et al., 2007) and OPENCL (Munshi, 2009), programming GPUs became easier.

Although initially GPUs were developed to accelerate 3D image processing for gaming

applications (Blythe, 2008), over time both academia and industry started using GPUs for general purpose computing (Booth et al., 1985), (Mišić et al., 2012). GPUs started to benefit a wide variety of applications, including image processing (Viola et al., 2003), (Strzodka et al., 2003), signal processing (Manocha, 2003), (Govindaraju et al., 2006), computer vision (Fung et al., 2002), (Woetzel and Koch, 2004), oil and gas exploration (Lin and Hall, 2007), (Deschizeaux and Blanc, 2007), linear algebra (Hoff III et al., 2001), (Bolz et al., 2003) physics (Zeller, 2005), (Hagen et al., 2006), chemistry (Harris et al., 2002), (Kim and Lin, 2003), databases and data mining (Govindaraju et al., 2005), (Govindaraju et al., 2005), biomedical applications (Tran et al., 2004), (Cates et al., 2004), and life sciences (Mosegaard and Sorensen, 2005), (Li et al., 2007). Nowadays, GPUs are ubiquitous and are extensively used in almost every computation domain, especially after the widespread adoption of machine learning (ML). Although ML applications leveraged GPUs in the late 1990s (Zheng and Pekhimenko, 1997), the introduction of high-level frameworks such as Caffe (Jia et al., 2014) and MXNet (Chen et al., 2015a) has enabled users from different application domains to use GPUs for training computation-intensive ML applications. To support the growth of ML applications, GPU vendors have introduced several innovations in the GPU architecture, designed powerful GPU systems such as NVIDIA DGX-1 (NVIDIA, 2016), NVIDIA DGX-2 (Choquette and Gandhi, 2020), AMD MI100 (AMD, 2020), etc. as well as developed highly optimized software libraries (NVIDIA, 2018; NVIDIA, 2008) and runtime support to ease programming the GPUs.

Both industry and academia commonly used single-GPU systems up until 2004. A typical single GPU has thousands of parallel threads that run concurrently to achieve very high throughput. However, die size restricts the number of parallel computing cores known as compute units (CUs)<sup>1</sup> or streaming multiprocessors (SMs) in a single GPU (Arunkumar et al., 2017). With the continued growth of applications that demand extremely high com-

<sup>&</sup>lt;sup>1</sup>Throughout this manuscript, we use CU to refer to compute cores

puting resources, the compute resources of a single GPU were no longer adequate. This led to the design and adoption of Multiple Graphics Processing Unit (MGPU) systems. Today, MGPU systems have become the platform of choice for accelerating a variety of applications, including ML (Chen et al., 2015b), (Al-Rfou et al., 2016), (Abadi et al., 2016), (Paszke et al., 2019), (Jia et al., 2014), (Tokui et al., 2015), graph applications (Che et al., 2013), (Xu et al., 2014), (Shi et al., 2019), (Wang et al., 2019), medical applications (Valero-Lara, 2014), (Saikia and Kanhirodan, 2014), (Zhu et al., 2019) and large-scale simulations (Zhu et al., 2018), (Yamazaki et al., 2014), (Zhang et al., 2018). Hence, MGPU systems have become an integral part of online services such as Amazon Web Services (AWS) (Amazon, 2015), Microsoft Azure (Copeland et al., 2015), and Google Cloud (Krishnan and Gonzalez, 2015).

In fact, MGPU systems have enabled researchers from different domains to solve complex, large and time-consuming problems that were previously impossible due to lack of computing resources. For instance, Goyal et al. (Goyal et al., 2017) trained ResNet-50 in 1 hour using 256 GPUs, which would have otherwise taken more than a week using a single GPU and months using high-end CPUs. As a result, there have been tremendous efforts from both industry and academia to improve the MGPU system design so that MGPU systems can continue to help solve the continually growing complex applications.

#### 1.2 Background

In this thesis, we present our work on the profiling of ML applications on MGPU systems, hardware and software design choices that limit the performance of MGPU systems while running the ML applications, and our novel memory system and associated coherence policies that improve the MGPU system design. To better understand our novel contributions to the field of MGPU systems, here we provide a background on running deep learning (DL) workloads on MGPU systems and MGPU system architecture.

#### 1.2.1 Deep Learning using MGPU Systems

DL is a branch of ML that has become increasingly popular for solving complex data-intensive problems. Deep Neural Network (DNN) model, a type of DL model, is commonly used today in a number of application domains. To maximize the potential of the DNN models, we need to train them carefully. Both single-GPU and MGPU systems are used for training DNNs (Jia et al., 2014). In this section, we provide an overview of DNNs, the process of training DNNs using MGPU systems and the associated challenges.

#### **DNN and its Training Process**

A DNN has multiple layers of neurons. Neurons in a layer are connected to the neighboring layers by weighted edges. Each layer applies a set of mathematical operations, such as dot-product, convolution, max-pooling or sigmoid to the layer's inputs. A DNN can be trained to classify input data samples with high accuracy. Training a DNN is an iterative process of updating the parameters (weights) of each layer. The iterative process consists of the following stages in each iteration:

- 1. Forward Propagation (FP)

- 2. Backward Propagation (BP)

- 3. Weight Update (WU)

- 4. Metric Evaluation (ME)

In FP, each layer performs a set of linear and non-linear operations using a set of weight parameters (randomly initialized in the beginning, but updated during each BP step in the training process) on the input data. The common type of layers in a model include: the convolution layers, the fully connected layers, and the activation layers. The observed output is then compared with the expected output. The difference between the two is then

fed back into the network, from the last layer back to the first layer. This is the BP stage. The outputs of the BP stage are the local gradients of the network parameters, suggesting how each parameter should change its value to reduce the difference between observed and expected output, i.e., improve neural network classification accuracy. After a complete backward pass, the gradients are used to update the weights during the WU stage. This process of updating weights using gradients is based on the Stochastic Gradient Descent (SGD) algorithm. During the ME stage, performance metrics such as training accuracy are calculated. This is performed for each batch of data. Since our evaluation only focuses on performance rather than algorithm efficiency and the ME stage only adds a fixed amount of execution time, we do not include the ME stage in our study.

The FP, BP, and WU stages are repeated multiple times until the output error rate is less than a desired value. For DNNs with large training datasets it is expensive to update the weights after performing FP and BP for each input-output pair of the whole training set. Hence, training data is randomly sampled into mini-batches. All inputs within a mini-batch go through the FP and BP stages. The gradients are accumulated for all input-output pairs within a mini-batch and WU is performed only once.

#### MGPU DNN Training

MGPU systems enable faster DNN training compared to single-GPU systems because the training is distributed and parallelized across multiple GPUs. In this work, we do not dive deep into how the DNN training algorithm works. We focus on how the training data is managed and moved in a typical DNN training process. Although the exact stages of the training process differ from framework to framework, the overall approach is the same. The timeline for training DNNs using the synchronous SGD algorithm with four GPUs is shown in Figure  $1\cdot1$ . When the algorithm starts, the CPU randomly generates the internal parameters of the network model (not shown in Figure  $1\cdot1$ , as this is a one time process). The network model is broadcasted to all the GPUs. The CPU also loads k mini-batches

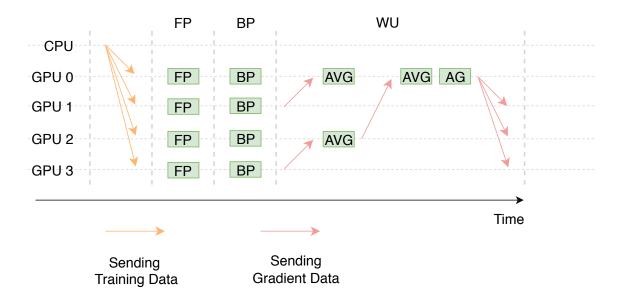

**Figure 1.1:** The timeline of an epoch during MGPU DNN training using the data-parallelism approach with synchronous SGD. FP, BP, AVG, and AG represent forward propagation, backward propagation, averaging, and add gradients, respectively. (This figure is not drawn to scale.)

of the training data, where k equals to the number of GPUs in the system, and sends one mini-batch to each GPU (see the left-most arrows in the figure). All the GPUs perform FP and BP to calculate the gradients. The size of the gradient data should be approximately equal to the size of data in the neural network model (Glorot and Bengio, 2010).

The gradients calculated by each GPU is not the same and we need to calculate the average gradient. The average is calculated with a *reduction* approach. For example, if four GPUs are used, the gradients calculated by GPU1 will be moved to GPU0 and GPU0 takes the average of the gradients from GPU0 and GPU1. Simultaneously, GPU2 collects the gradients from GPU3 and calculates the average. Finally, GPU0 collects the averaged result from GPU2 and then calculates the average. GPU0 updates the neural network data with averaged gradients and then, it broadcasts the updated network model to the remaining three GPUs. Once all the GPUs have the next mini-batch of the training set sent from the CPU, the next iteration will start. The process is repeated for a specific number of

epochs.<sup>2</sup> Here, the number of epochs depends on the desired accuracy of training and convergence of the training algorithm. Today, a large number of deep learning frameworks, including Caffe (Jia et al., 2014), CNTK (Yu et al., 2014), TensorFlow (Abadi et al., 2016), Torch (Collobert et al., 2011), MXNet (Chen et al., 2015a), Pytorch (Paszke et al., 2019), and Theano (Al-Rfou et al., 2016), use GPUs to reduce the training time of DNNs.

#### 1.2.2 MGPU System Architecture

Over the past few years, NVIDIA and AMD, the two major GPU vendors, have introduced a number of high performance MGPU systems such as NVIDIA Pascal-based DGX-1 (Foley and Danskin, 2017), NVIDIA Volta-based DGX-1 (NVIDIA, 2017), NVIDIA Volta-based DGX-2 (NVIDIA, 2018a), NVIDIA Ampere-based DGX-2 (Choquette and Gandhi, 2020), and AMD MI100 (AMD, 2020). These MGPU systems primarily target the ML domain. To support the ML workloads, GPU vendors have integrated a number novel hardware and software features in these MGPU systems. The noteworthy hardware features include NVLink interconnect (Foley and Danskin, 2017) and AMD Infinity Fabric Link (AMD, 2020) to accelerate data transfers across GPUs, and dedicated tensor cores (Markidis et al., 2018) and matrix cores (AMD, 2020) for fast and efficient matrix-related computations. On the software side, GPU vendors have introduced variety of software libraries including NCCL (NCCL, 2018), RCCL (AMD, 2021) cuDNN (NVIDIA, 2018), and cuBLAS (NVIDIA, 2008).

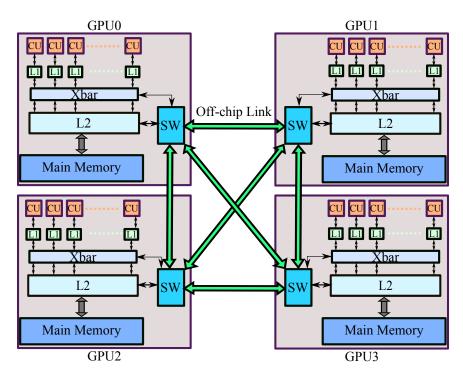

Figure 1·2 is representative of existing MGPU systems (Young et al., 2018; Milic et al., 2017). In this example MGPU system, there are 4 GPUs, where each GPU has 64 CUs in this example. Each CU has its own private L1\$. L2\$ is distributed and has multiple (8 in this example) banks. It is shared across all the CUs. The L1\$s and the L2\$ banks are connected via a network (a Xbar in this example). There is a memory controller connected

<sup>&</sup>lt;sup>2</sup>An epoch is a complete pass through all the data in the training dataset. Each epoch involves processing of multiple mini-batches of data.

**Figure 1.2:** Conventional MGPU system. Switch (SW) handles the remote access requests from one GPU to another GPU. PCIe or NVLink is used as the off-chip link.

with each L2\$ bank and the memory controller serves the requests it receives from L2\$ to read or write the data from main memory.

Thus, we have a total of 8 memory controllers in this example. Each GPU has its own native memory (8 GB for each GPU in this example). Hence, each memory controller controls 1 GB of main memory. The L2\$ banks and the main memory of a GPU are connected using high bandwidth and low-latency connections. Each GPU in the MGPU system can access the other GPUs' memory through low-bandwidth high-latency links (PCIe or NVLink) by means of Remote Direct Memory Access (RDMA). These off-chip links have 5× to 20× lower bandwidth (for transferring data between GPUs, and between CPU and GPU) than the bandwidth of the links used for accessing local main memory of a GPU (Young et al., 2018), (Buono et al., 2017). When the CU of a GPU requests data that resides on a remote GPU, the request goes to its remote direct memory access (RDMA)

engine via the L1\$ of the CU. This RDMA engine communicates with the RDMA engine residing on the remote GPU. The remote RDMA engine routes the request to the L2\$ and then to main memory (if data is not already in the L2\$) of the remote GPU. The response from the main memory of the remote GPU is cached in the L2\$ of the remote GPU, and then routed to the L1\$ of the local GPU via the two RDMA engines (remote and then local). Note that the CPU memory in a typical MGPU RDMA-based system is placed on the CPU side. Hence, off-chip links are used to transfer data between CPU and the GPUs.

#### 1.2.3 Remote Memory Access Mechanisms in an MGPU System

As mentioned before, GPUs in an MGPU system (as described in Section 1.2.2) need to communicate with each other due to the data sharing requirements of the applications. Hence, GPU vendors have introduced a number of mechanisms, summarized in Table 1.1, to enable data sharing across multiple GPUs. This section briefly describes different inter-GPU data transfer/access mechanisms and their pitfalls.

#### **P2P Memcpy**

Using the Peer-to-Peer (P2P) memcpy method, one GPU can directly copy data to/from another GPU's memory from/to its own memory. Hence, multiple copies of data exist in different GPUs' memory. The data is transferred using the RDMA engine using the off-chip links. In case of any modification of the copied data, the programmer has to manually update the data in all locations by copying back and forth to maintain coherence. Thus, this method leads to programming complexity.

#### **P2P Direct Access**

Using the P2P direct access method, one GPU can directly access the data that resides on remote GPU's memory without copying the data in its own memory. The details about P2P direct access using RDMA has been described in Section 1.2.2. As the same data may

**Table 1.1:** Comparison of different communication mechanisms in existing MGPU systems. We compare the main memory usage and programmability of each mechanism w.r.t. P2P memcpy (baseline for comparison represented by '-'), and remote memory (RM) access latency and bandwidth w.r.t. local main memory access latency and bandwidth. ' $\chi$ ', ' $\sqrt{\ '}$ , and ' $\sqrt{\ '}$  indicate 'no', 'fair', and 'good', respectively.

| Method         | RM Access<br>Latency | RM Access<br>Bandwidth | Data<br>Duplication | Improves<br>Programmability | Improves GPU<br>Mem. Usage |

|----------------|----------------------|------------------------|---------------------|-----------------------------|----------------------------|

| P2P Memcpy     | High                 | Low                    | Yes                 | _                           | _                          |

| P2P Direct     | High                 | Low                    | Partial             | <b>√</b>                    | $\checkmark$               |

| Zerocopy       | Extremely high       | Low                    | No                  | <b>√</b> √                  | X                          |

| Unified Memory | Extremely<br>High    | Low                    | No                  | <b>√</b> √                  | $\checkmark$               |

reside in local GPU's cache as well as remote GPU's cache and main memory, handling data races among multiple GPUs is programmer's responsibility as existing GPUs lack coherence support at hardware level. However, this method allows programmer to avoid multiple copies of data in GPUs' memory leading to relatively easier programming.

#### Zerocopy

Zerocopy method does not use GPU memory. Rather, all the GPUs in the system use the Host or CPU memory. This method addresses the memory capacity issue of GPUs. The memory is pinned to a particular GPU and that GPU can directly access the data using PCIe links. Caches are bypassed for this method. As a result, this method results in extremely slow data access and may introduce serialization delays if multiple GPUs need to access same address space.

#### **Unified Memory**

To ease the programming of MGPU systems, NVIDIA introduced unified memory which is a software abstraction of shared main memory. With unified memory, all the physically separate main memory of CPU and GPUs are presented as a single memory space to the programmer. Hence, the programmer can use a single pointer from any of the devices

(CPU or GPU) to access a desired memory location irrespective of its physical location. This method is facilitated by the recently introduced user transparent page fault support in GPUs (Chien et al., 2019). If a GPU wants to access a memory location that is outside its local memory region, a page fault occurs. The GPU runtime along with the CPU handles the page fault and provides the required page to the GPU. However, the unified memory is known to be inefficient in terms of performance even though it eases programmability (Baruah et al., 2020).

#### 1.2.4 Coherence and Consistency in GPU and MGPU Systems

Coherence is required to ensure that all the processors in a system see the same view of memory. In case of shared data, cache coherence ensures that all the components have the same view of shared data. On the other hand, memory consistency is a contract between the hardware and the software. A consistency model ensures that a hardware keeps its promises to maintain certain memory orderings that the software knows. As the CUs of a GPU share the L2 cache and copy data to their private L1\$, we need a coherence protocol to make sure all the CUs see the same view of the shared data. The GPU and MGPU consistency model dictates what a programmer should expect from the GPU or MGPU in terms of ordering of memory operations when writing programs. The programmer need to provide appropriate barriers/synchronizations accordingly to obtain the correct result from the hardware.

This section provides the overview on memory coherence and consistency, and discusses support for coherence and consistency on existing GPUs.

#### Coherence

Consider a system having multiple cores and the system is executing a multi-threaded application. In this multi-threaded application execution environment, coherence mechanism decides how updates to a single memory location are propagated. We use the single-writer–multiple-reader (SWMR) invariant to define coherence (Nagarajan et al., 2020).

SMWR invariant is defined as: at a given logical time, only one core can write to a given location and other cores can only read the same location (Nagarajan et al., 2020). The typical responsibilities (Nagarajan et al., 2020) of a cache coherence protocol involve:

- When a memory location is updated, the new value must be propagated to all-sharers.

This can be done in either of the two ways:

- (a) Update the private copies (known as write-update)

- (b) Invalidate the private copies (known as write-invalidate)

- 2. When a write operation is performed, the updated value must be globally visible i.e. visible to all threads and processors

- 3. A write operation must be logically seen by all thread at once (known as write-atomicity (Adve and Gharachorloo, 1996)). This can be achieved by invalidating or updating all private copies of data before completing a write operation.

#### Consistency

While memory coherence dictates how updates to a single memory location are propagated, the memory consistency model defines a set of allowed behaviors of multi-threaded programs to be correctly executed in a shared memory system (Nagarajan et al., 2020). A memory consistency model tells the programmer what to expect from a system with shared memory. In particular, a memory consistency model specifies the valid ordering of memory operations (i.e. read and write) to different memory locations. There are different memory consistency models such as sequential consistency (SC), relaxed consistency (RC), total store order (TSO) consistency, etc. According to Lamport (Lamport, 1979), a multiprocessor is sequentially consistent if "the result of any execution is the same as if the operations of all processors (cores) were executed in some sequential order, and the operations of each individual processor (core) appear in this sequence in the order specified by its program."

Sequential consistency represents the most strict form of memory consistency. Relaxed consistency models permit a multiprocessor to violate the program order of memory operations. The TSO consistency model is a form of relaxed consistency model that maintains the ordering of store operations but supports reordering of load operations. This model is a compromise between strict sequential consistency and an extremely relaxed consistency model that allows all types of memory reordering. In our work, we support sequential consistency model as well as the relaxed memory consistency model that allows re-ordering of memory operations (see Section 4.3)

#### Coherence and Consistency in GPUs and MGPUs

**Single GPU:** Existing GPUs support data-race-free (DRF) weak consistency (a form of relaxed consistency) without coherence (Alsop et al., 2016), (Singh et al., 2015). The programming model assumes that there is no inter-thread communication during kernel execution. Under the DRF consistency model in existing GPUs, a sequentially consistent execution is guaranteed only if program is data-race free. Hence, to make the program data race free the programmer must annotate all data races as synchronization operations by using fences or atomic operations (Singh et al., 2015). The programming model also completely relies on the programmer to take precautionary steps to manually support coherence if needed. There are several ways a programmer can achieve coherence manually. First, the programmer can disable private caching of data in the L1\$ and perform the coherence action in shared L2\$. Note that modern GPUs support some accesses as coherent accesses at the shared L2\$ (Tabbakh, 2018). Bypassing L1\$ and executing memory operation at shared L2\$ lead to additional traffic and performance degradation. Second, the programmer can perform kernel-stopping coarse-grained synchronization to maintain coherence. This results in poor performance as multiple kernels need to be launched. Third, the programmer can use atomic operation, but it does not support complex instructions.

However, all of the methods are inefficient and create additional burden on programmer

when programming a single GPU.

MGPU: The DRF consistency model along with lack of coherence support exacerbates the performance issues and programming complexities in an MGPU system. The programmer must manually address any consistency issues in a program. To maintain coherence across multiple GPUs, the programmer can again bypass the cache when accessing the remote data and directly access the data from a remote GPU's main memory. However, it leads to significant latency in memory access because of the involvement of high-latency low-bandwidth off-chip links. Another frequently used method is to manually copy data back and forth across multiple GPUs and use kernel-stopping synchronization to maintain coherence. This results in inefficient use of GPU memory because of the existence of multiple copies of the same data in different GPUs' memory.

#### 1.3 Challenges in Existing MGPU Systems

Data sharing across multiple GPUs during kernel execution leads to programming challenges as the programmer must choose between programmability and performance. In this section, we examine the challenges in existing MGPU systems using the DNN training process as an example. We highlight how different communication mechanisms trade-off programmability for performance. Finally, we show how remote memory accesses in an MGPU system is extremely expensive.

#### 1.3.1 DNN Training on MGPU Systems

Training a DNN on a MGPU system introduces various challenges:

• The programmer has to explicitly distribute the data (input data and network model data) among multiple GPUs. The programmer can either distribute the input data onto multiple GPUs while replicating the network model in each of the GPUs (Yadan

et al., 2013) (referred to as data parallelism), or assign different parts of the neural network model to distinct GPUs (referred to as model parallelism) (Yadan et al., 2013).

- Both approaches require data to be transferred and synchronized across GPUs. The

programmer needs to carefully handle data transfer and synchronization to ensure

correctness of computations.

- The input data is fed to the GPUs as mini-batches (also called batches). Each mini-batch consists of a certain number of unique inputs chosen by the programmer from the dataset. The choice of mini-batch size has implications on training time, GPU memory usage and training accuracy. Recent works (Goyal et al., 2017), (You et al., 2017), (Smith et al., 2017) have shown that batch size can be increased without losing accuracy.

- Although we can parallelize the computation required for training DNNs, the GPUs still need to communicate with each other during the different phases of training. High-end MGPU systems support different methods and libraries for communication. Depending on the size of neural networks, communication can pose significant bottlenecks. To minimize the communication time, both hardware-level (i.e. NVLinks) and software-level (i.e. NCCL library) solutions have been introduced. Nonetheless, the training algorithm requires more hardware-specific optimizations to achieve the peak performance from an MGPU system.

To understand the programming complexities and inefficiencies in an MGPU system, we use Algorithms 1, 2 and 3, where we consider three different ways a programmer can perform the WU stage.

#### **Algorithm 1:** Using Memcpy\*

```

Initialization: weights in CPU;

Copy weights from CPU to GPU0 \rightarrow wGPU0;

Copy weights from CPU to GPU1 \rightarrow wGPU1;

FP+BP on GPU0 using wGPU0 \rightarrow gGPU0;

FP+BP on GPU1 using wGPU1 \rightarrow gGPU1;

Copy gGPU1 from GPU1 to GPU0 \rightarrow gGPU0Copy;

WU on GPU0 using (gGPU0, gGPU0Copy) \rightarrow wGPU0;

Copy wGPU0 from GPU0 to GPU1 \rightarrow wGPU1;

```

#### **Algorithm 2:** Using P2P direct access\*

```

Initialization: weights in CPU; Copy weights from CPU to GPU0 \rightarrow wGPU; FP+BP on GPU0 using wGPU \rightarrow gGPU0; FP+BP on GPU1 using wGPU \rightarrow gGPU1; WU on GPU0 using (gGPU0, gGPU1) \rightarrow wGPU;

```

#### **Algorithm 3:** Using shared main memory\*

```

Initialization: weights in CPU; FP+BP \text{ on } GPU0 \text{ using weights} \rightarrow \texttt{g0} \text{ ;} \\ FP+BP \text{ on } GPU1 \text{ using weights} \rightarrow \texttt{g1} \text{ ;} \\ WU \text{ on } GPU0 \text{ using } (\texttt{g0, g1}) \rightarrow \texttt{weights} \text{ ;}

```

\*In the pseudocode, the right arrows point to destination variables of an operation.

We will assume a 2-GPU MGPU system here. Algorithm 1 shows that when using memcpy, the programmer must maintain coherence explicitly by periodically copying data to GPU1's memory. Thus, there is an additional copy of data i.e. SGD (gGPU1) in GPU0's memory, leading to additional memory usage. Nonetheless, this mechanism can be efficient in terms of kernel runtime because P2P memcpy can run asynchronously. Algorithm 2 shows how P2P direct access with RDMA can eliminate the data copy step, but at the expense of accessing data using off-chip links. Still, the programmer must transfer the data from the CPU to the GPUs. Algorithm 3 illustrates that a shared main memory could ease programmability and eliminate explicit GPU-to-GPU or CPU-to-GPU data transfers. Note that UM and Zerocopy solutions use Algorithm 3. UM, as proposed by NVIDIA,

eases programming with a software abstraction, but suffers from performance degradation due to inefficient page-fault support and expensive remote accesses (Baruah et al., 2020). A Zerocopy solution does not use GPU memory at all. The GPUs access *pinned* CPU memory using the off-chip (PCIe) links (Negrut et al., 2014). We argue that we need a solution which would not trade-off programmability to gain performance.

#### 1.3.2 RDMA Access Cost

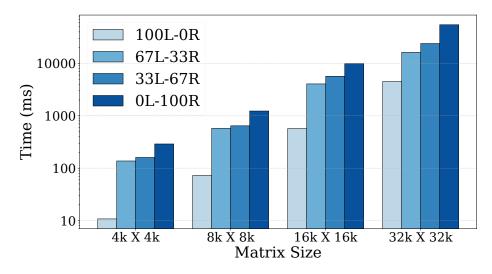

In this section, using the data access latency metric, we present the performance impact of remote data access in an MGPU system as the previous section demonstrates the necessity of communication across multiple GPUs in the exiting MGPU systems. Here, we run the commonly-used matrix multiplication kernel SGEMM (used in training DNNs), from NVIDIA's cuBLAS library (NVIDIA, 2008), on an MGPU system with V100 GPUs (compute capability of 7.0). We use two GPUs connected through NVLink 2.0 (total of 50 GB/s unidirectional bandwidth). The conclusions of our analysis are broadly applicable to systems with more than 2 GPUs that use GPU-GPU RDMA.

The computations in the SGEMM kernel consist of three matrices A, B, and C. In our experiment, we distribute the matrices in the memory of two GPUs (GPU0 and GPU1) and examine the performance degradation caused by different degrees of remote access (using P2P direct access as an example) when the SGEMM is executed on GPU0. We use the aL-bR format to represent a% local access and b% remote access for GPU0, where a and b are integers. We evaluate the following four matrix distributions across memory:

- 1. Matrices A, B and C are in GPU0's memory. This leads to 100% local access for GPU0 (100L-0R).

- 2. Matrices A and B are in GPU0's memory, and C is in GPU1's memory (67L-33R).

- 3. Matrix A is in GPU0's memory, and matrices B and C are in GPU1's memory (33L-67R).

4. Matrices A, B and C are in GPU1's memory. This leads to 100% remote access for GPU0 (0L-100R).

Figure 1.3 shows the runtime for the SGEMM kernel execution with different matrix sizes for the above four matrix distributions. For smaller matrix sizes, accessing remote memory is very expensive because of the fixed remote access overhead. The runtime of SGEMM for the 0L-100R distribution for a 4k×4k matrix is 27× longer than that of the 100L-0R distribution. On the other hand, the runtime of SGEMM for the 0L-100R distribution for the 32k×32k matrix is 12.2× longer than that of the 100L-0R distribution. Here, the fixed remote access overhead gets amortized. From these experiments, we can see the significant impact of remote accesses on performance, and in turn, argue that to improve the performance of applications, we need to avoid remote accesses as much as possible.

**Figure 1.3:** Runtime of SGEMM kernel from cuBLAS library for different matrix sizes. Each bar corresponds to a different distribution of local and remote memory accesses.

#### 1.4 Thesis Contributions

The first part of this thesis focuses on understanding the behaviour of DNN applications, the performance limiting factors for training DNN workloads in MGPU systems and prototyping a potential solution to eradicate the performance bottlenecks. Based on the insights gained from DNN workload characterization, we propose and evaluate a novel and efficient MGPU system with True Shared Memory (MGPU-TSM) in the second part of the thesis. Finally, the third part of the thesis concentrates on solving one of the major challenges, i.e. coherence, in the proposed MGPU system. The key contributions of the thesis are provided in the sections below.

## 1.4.1 DNN Workload Characterization on MGPU Systems

To understand the characteristics of emerging workloads and the performance limitations in existing MGPU systems, we perform workload characterization on different generations of MGPU system. We breakdown the characterization in two parts—the first part presents workload characterization on MGPU systems prior to the launch of NVIDIA Volta-based MGPU systems, and the second part of the workload characterization is performed on the NVIDIA Volta-based MGPU systems.

#### **Workload Characterization on Pre-Volta MGPU Systems**

The key contributions of our workload characterization on the Pre-Volta system are as follows:

- We evaluate three different MGPU systems (NVIDIA Kepler, Titan Z and DGX-1) using different DNN workloads, and observe that communication among GPUs, as well as between the CPU and GPUs, can consume up to 40.6% of the total execution time.

- We develop and use synthetic workloads to evaluate data transfer mechanisms between two NVIDIA GPUs, and between a CPU and a GPU. This evaluation is useful for DNN algorithm developers to find the best communication mechanism for training their algorithms in existing MGPU systems.

• By forcing the GPUs in the MGPU system to use data from a shared main memory space, we demonstrate that a prototype (real) MGPU system with shared main memory improves performance for synthetic MNIST, Cifar10 and Imagenet datasets on a MLP network by 3.7×, 3.2× and 3.5×, on average, (across all three MGPU systems when using 2 GPUs) as compared to their respective baseline that uses P2P memcopy for gradient synchronization.

## Workload Characterization on DGX-1 Volta MGPU Systems

For this characterization, we profile the three stages – Forward Propagation (FP), Backward Propagation (BP), and Weight Update (WU) of the DNN training process on a Volta-based NVIDIA DGX-1 system with 8 GPUs. The contributions of this work include:

- We compare the impact of P2P and NCCL based communication methods on the training time of DNN workloads (LeNet, AlexNet, GoogLeNet, ResNet and Inception-v3) on NVIDIA's Volta-based DGX-1 system. We profile these workloads to isolate and quantify the computation-intensive and the communication-intensive portion of the training process to identify the software and hardware-level bottlenecks.

- Our evaluation shows that MGPU communication latency cannot be hidden by simply increasing the computation-intensiveness of the workloads or compute capability of the GPUs. We also show that only increasing the bandwidth (BW) of the interconnect network in the MGPU system cannot completely eliminate the communication bottleneck.

We also need an efficient implementation by the developers/programmers of DNN workloads to take advantage of the high BW interconnect.

- We quantify the impact of growing network size and increasing batch size on memory usage, and identify memory capacity to be a key limiting factor that hinders the speedup of the training of DNNs on MGPU systems.

## 1.4.2 MGPU Systems with True Shared Memory

In this section, we highlight our proposal to eliminate the major performance bottlenecks that we observe from our DNN workload characterization efforts. To simplify programming, eliminate the costly remote data movement latency, increase the memory utilization efficiency, and avoid redundant data copies, our solution is to physically unify the main memory of the GPUs. We refer to this system as a *MGPU system with true shared memory (MGPU-TSM)*. Unlike existing MGPU systems that rely on RDMA to access non-local GPU memory, an MGPU-TSM system allows all GPUs to directly access the entire physical main memory of the system, thus eliminating non-uniform memory access (NUMA) effects observed in traditional MGPU systems. The major contributions of this work are as follows:

- We are the first to demonstrate the performance benefits of MGPU-TSM. Our MGPU-TSM system eliminates NUMA accesses to main memory as well as the need to transfer data back and forth between the CPU's or GPUs' main memory.

- We implement the MGPU-TSM system architecture with 4 GPUs in MGPUSim simulator (Sun et al., 2019) and compare the performance of MGPU-TSM with existing MGPU systems using standard benchmarks. We demonstrate that MGPU-TSM achieves 3.81× better performance on average versus an existing MGPU system that uses RDMA direct access.

#### 1.4.3 Coherence in MGPU-TSM

To provide efficient support for both intra-GPU and inter-GPU coherence, in this thesis, we propose MGCC- a new timestamp-based hardware-level cache coherence scheme for MGPU-TSM systems. MGCC uses hardware-level coherence support for inter-GPU and intra-GPU data sharing using a single-writer-multiple-reader (SWMR) invariant. The contributions of the work are as follows:

- We propose a novel timestamp-based hardware-level inter-GPU and intra-GPU coherence protocol named MGCC, a scheme that ensures seamless data sharing in an MGPU-TSM system. MGCC leverages the concept of a *logical timestamp* (Plakal et al., 1998)

- MGCC introduces a new cache-level logical time counter to reduce traffic in the memory hierarchy. MGCC can reduce request traffic by up to 41.7% and response traffic by up to 3.1%. MGCC includes a novel timestamp storage unit (TSU) to keep track of cache block timestamps. We strategically place the TSU outside the critical path of memory requests. The TSU is accessed in parallel with the MM, thereby avoiding any performance overhead.

- MGCC also provides support for tracking memory requests to avoid potential loadafter-store and store-after-load issues. Our implementation supports sequential and existing relaxed memory consistency models, but MGCC can also work as a building block for other memory consistency models, such as release consistency and total store ordering (TSO) consistency.

- We evaluate MGCC using both standard and synthetic benchmark suites with the MGPUSim simulator (Sun et al., 2019). Compared to an existing MGPU system supporting RDMA, for standard benchmarks, our MGPU-TSM system with MGCC delivers 3.7× and 3.0× better performance, on average, using RC and SC, respectively. Our MGCC protocol only introduces a 2% and 21% performance overhead, on average, for supporting RC and SC, respectively, when running standard benchmarks. Compared to MGPU systems utilizing the HMG coherence protocol (Ren et al., 2020), an MGPU-TSM system utilizing MGCC performs, on average, 2.4× better, when running standard benchmarks. Stress tests performed using our synthetic benchmark suite show that, compared to a non-coherent MGPU-TSM, a coher-

ent MGPU-TSM system with MGCC has 26.6% and 46.1% performance overhead for supporting RC and SC, respectively. However, this is a reasonable cost to pay for significantly lowering programmer burden.

## 1.5 Related Work

## 1.5.1 DNN Workload Characterization on MGPU Systems

As mentioned before, DNN has emerged as the most ubiquitous workload in the modern computing system. So, there are ongoing efforts to understand the behavior of DNN workloads on single GPU and MGPU systems, and to develop new software and hardware to achieve better performance.

Several prior works (Shi et al., 2016), (Bahrampour et al., 2015), (Kim et al., 2017), (Sze et al., 2017), (Li et al., 2016) have studied GPU-accelerated ML frameworks. Shi et. al. (Shi et al., 2016) benchmarked a selection of these frameworks including Caffe, CNTK, MXNet, TensorFlow, and Torch, using three popular types of deep neural networks (FCNs, CNNs, and RNNs) on two CPU platforms and three GPU platforms. The goal was to provide a guide for selecting appropriate combinations of the hardware platforms and software tools. Bahrampour et. al. (Bahrampour et al., 2015) present a comparative study of Caffe, Neon, TensorFlow, Theano, and Torch, from three different aspects, namely extensibility, hardware utilization, and performance. Kim et. al. (Kim et al., 2017) analyze the GPU performance characteristics of Caffe, CNTK, TensorFlow, Theano, and Torch from the perspective of a representative CNN model, focusing on the performance characteristics of these five frameworks on a single GPU system and a MGPU system. Unlike previous approaches, they measure layer-wise execution times, as well as the processing time, of an input batch. While these studies provide users some insight into the strengths and limitations of these deep learning frameworks, they do not introduce hardware or software modifications to improve the performance of these frameworks.

In comparison to the prior works, our DNN characterization work focuses on the both previous and current generations of MGPU systems to provide insight into the gradual evolution of MGPU architectures to support the emerging DNN workloads. Apart from that, unlike previous works, our characterization and profiling provide insight into communication—and computation—intensiveness of the DNN workloads.

## 1.5.2 NUMA Effects in MGPU System

MGPU system architecture is evolving over time along with the architecture improvement of individual GPUs. However, the works related to MGPU system architecture mostly focus on reducing the NUMA effects in existing MGPU systems. Hence, a number of recent works from both academia and industry have attempted to address the NUMA effects in existing MGPU systems, but they did not succeed in eliminating the NUMA effects completely. This is because eliminating NUMA effect requires drastic changes in the memory architecture and interconnect network architecture, and the previously proposed works mostly focus on achieving incremental improvements.

Milic et al. propose a NUMA-aware multi-socket GPU solution to resolve performance bottlenecks related to NUMA memory placement in multi-socket GPUs (Milic et al., 2017). The proposed system dynamically adapts inter-socket link bandwidth and caching policies to avoid NUMA effects. The proposed system exploits the changing application phase behavior in terms of inter-socket bandwidth demand and data locality in L1 and L2 caches by dynamically adapting the inter-socket link bandwidth and L1 and L2 caching policies, respectively. Our proposed MGPU-TSM system with MGCC completely eliminates the impact of NUMA on performance. Arunkumar et al. (Arunkumar et al., 2017) and Ren et al. (Ren et al., 2020) propose an MCM-GPU, where multiple GPU modules are integrated in a package to improve energy efficiency. As in MCM-GPU, our proposed MGPU-TSM can take advantage of novel integration technologies to improve energy efficiency and performance.

The recently introduced NVIDIA DGX-2 (NVIDIA, 2018a), (Choquette and Gandhi, 2020) system still suffers from NUMA effects as each GPU has its own local main memory and multiple GPUs still need to communicate via NVLinks. Although there has been improvement in the bandwidth of NVLink and the interconnect topology for connecting multiple GPUs to each other, the remote data access is still expensive as demonstrated in Section 1.3.2. Similarly, AMD introduced AMD Infinity Fabric Link (AMD, 2020) to improve the communication performance across MGPUs as well as between CPU and GPU. Kim et.al. (Kim et al., 2014) propose an MGPU system with unified memory network (UMN) that connects GPUs' main memory modules (knows as Hybrid Memory Cube or HMC (Pawlowski, 2011)) to provide faster connectivity across different GPUs and CPU. In particular, the authors propose a sliced flattened butterfly topology for the UMN by removing local HMC channels to ensure improved scalability. However, unlike our proposed MGPU-TSM system, the proposed UMN cannot provide GPUs with uniform memory access (UMA) to all the main memory modules. Arunkumar et al. (Arunkumar et al., 2019) also argue the need to improve inter-GPU communication. Our evaluation of MGPU-TSM also agrees with the argument.

In summary, our work on MGPU-TSM system is unique in the sense that no prior work comprehensively explored the impact of uniform memory access (UMA) to all the CPU and GPUs in the system.

#### 1.5.3 MGPU Memory System and Coherence

In recent years, coherence in MGPU systems have gained significant attention. To support coherence in MGPU systems, researchers have proposed architectural changes from both software—and hardware—perspective in the memory design. In this section, we first discuss prior works related to CPU and GPU coherence, and then we discuss the prior works related to coherence in the MGPU domain.

#### **CPU and GPU Coherence**

A number of works proposed directory-based cache coherence for APUs (Alsop et al., 2018), (Power et al., 2013), (Hechtman et al., 2014)<sup>3</sup>. In contrast, we are the first to propose an efficient timestamp-based cache coherence protocol for an MGPU. Kumar et al. (Kumar et al., 2015) and Boroumand et al. (Boroumand et al., 2019) propose protocols for coherence between a CPU and GPU. These works are complementary to our own and can be leveraged to address CPU-GPU coherence issues. Qian et al. (Qian et al., 2010) proposes ScalableBulk, a directory-based cache coherence protocol for multicore CPUs. Since GPUs have heavier traffic patterns than CPUs, invoking different directories in a GPU environment to maintain coherence would lead to severe performance degradation. Thus, we believe ScalableBulk is not suitable for GPUs.

## **MGPU Coherence**

NUMA-Aware multi-socket GPU (Milic et al., 2017) maintains inter-GPU coherence by extending SW-based coherence for L1\$s to the L2\$s. The resulting coherence traffic lowers application performance. Similarly, MCM-GPU (Arunkumar et al., 2017) leverages the software-based L1\$ coherence protocol for its L1.5\$. The flushing of the caches and coherence traffic hurt system scalability. Young et al. (Young et al., 2018) propose CARVE, a method where part of a GPU's memory is used as a cache for shared remote data and the GPU-VI protocol is used for coherence. This protocol does not scale well with an increase in the amount of read-write transactions and false sharing. Also, the CARVE method can cause performance degradation for workloads with large memory footprint as it reduces effective GPU memory space. HMG (Ren et al., 2020) is a recent hardware-managed cache coherence protocol for distributed L2\$s in GPUs using a scoped memory model consistency. HMG proposes to extend a simple VI-like protocol to track sharers in a hierarchical

<sup>&</sup>lt;sup>3</sup>An APU contains a CPU and a GPU in the same die

way, and achieves a cost-effective solution in terms of on-chip area overhead, inter-GPU coherence traffic reduction and high performance. This protocol, however, relies on errorprone scoped memory consistency model that increases programming complexity. Sinclair et al. (Sinclair et al., 2015) propose a memory consistency model for GPUs without using user-managed scopes of a variable in the memory hierarchy, while Alsop et al. (Kumar et al., 2015) propose a lazy release consistency model for GPUs. Both of these studies only consider single CPU and single GPU systems. Exploring efficient MGPU memory consistency models is an open challenge and results from these studies can be leveraged to address that challenge. We demonstrate the impact of RC and SC consistency in this work and our flexible MGCC protocol can be used as a building block for exploring other consistency models. To reduce coherence traffic, Singh et al. propose timestamp-based coherence (TC) protocol for intra-GPU coherence (Singh et al., 2013). As this protocol relies on a globally synchronized clock across all CUs, maintaining clock synchronization is a challenging task for large MGPU systems. To address this, Tabakh et al. (Tabbakh et al., 2018) propose a logical timestamp based coherence protocol (G-TSC). However, the G-TSC protocol is designed for single GPU systems and does not scale well for MGPU systems unlike our MGCC protocol.

All the prior MGPU coherence-related work focused on imposing a light-weight coherence protocol to improve NUMA effects. However, MGPU-TSM with MGCC provides the means to completely eradicate NUMA effects and impose a very light-weight low-overhead coherence protocol.

# 1.6 Organization

The rest of the thesis is organized as follows:

Chapter 2 discusses the workload characterization efforts on different generations of MGPU systems to quantitatively and qualitatively understand the inefficiencies in existing MGPU systems.

- Chapter 3 describes our proposed solution MGPU-TSM to overcome the inefficiencies in existing MGPU systems.

- Chapter 4 presents theory and evaluation of our proposed MGCC coherence protocol for MGPU-TSM.

- Chapter 5 discusses the future reserach direction and concludes the thesis.

# Chapter 2

# DNN Workload Characterization on Existing MGPU Systems