UNIVERSITÉ DE MONTRÉAL

# FLEXIBLE SCHEDULING OF TURBO DECODING ON A MULTIPROCESSOR PLATFORM

NEGIN SAHRAII DEPARTEMENT DE GENIE ÉLECTRIQUE ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (GÉNIE ÉLECTRIQUE) April 2009

© Negin Sahraii, 2009.

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-53925-5 Our file Notre référence ISBN: 978-0-494-53925-5

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manguant.

## <u>UNIVERSITÉ DE MONTRÉAL</u> <u>ÉCOLE POLYTECHNIQUE DE MONTRÉAL</u>

Ce mémoire intitulé:

## FLEXIBLE SCHEDULING OF TURBO DECODING ON A MULTIPROCESSOR PLATFORM

présenté par : SAHRAII Negin

en vue de l'obtention du diplôme de : <u>Maîtrise ès sciences appliquées</u> a été dûment accepté par le jury d'examen constitué de :

<u>M. DAVID Jean Pierre</u>, Ph. D., président

<u>M. SAVARIA Yvon</u>, Ph. D., membre et directeur de recherche

<u>M. THIBEAULT Claude</u>, Ph. D., membre et codirecteur

<u>M. LANGLOIS J.M. Pierre</u>, Ph. D., membre

## ACKNOWLEDMENTS

I would like to thank my supervisor, Professor Yvon Savaria and my co supervisor, Professor Claude Thibeault, for their precious time and effort, invaluable guidance and intellectual support during my graduate study. I have been extremely lucky to have supervisors who cared so much about my work and encouraged me to pursue my research objectives.

I must express also my gratitude to Hojat, my husband, for his continued support and encouragement. Also, completing this work would have been difficult were it not for the moral support provided by my mother, sister, and brother. Finally, I would like to thank my friends Parissa and Sandrine for their friendships and sharing their research experience.

## **RÉSUMÉ**

Ce projet présente un modèle de performance dynamique d'une application de communication à accès multiple et division de code à large bande (WCDMA – « wideband code division multiple access ») programmée sur un réseau sur puce à processeurs multiples (MPSoC – « multiple processor system on chip »). Nous développons une stratégie de modélisation dynamique pour évaluer le temps d'exécution des designs MPSoC basée sur des modèles à haut niveau des applications et de l'architecture. De tels modèles permettent de s'assurer que la plate-forme multi-noyaux est exploitée à son maximum et que les stratégies d'assignation et d'ordonnancement peuvent être validées.

Nous nous sommes concentrés sur le décodeur Turbo, qui est une partie de cette application comportant un nombre important des calculs et qui présente une variabilité de temps de traitement significative. Dans un système temps-réel, il est très important que les tâches respectent leurs délais limites. En raison de la variabilité du temps d'exécution des tâches, la plupart des algorithmes d'ordonnancement utilisés dans les systèmes temps-réel sont basés sur le pire cas du temps d'exécution de l'application choisie (WCET - « worst-case execution time »). Le problème d'une méthode de conception basée sur le WCET est le suivant : l'analyse d'ordonnancement basée sur les WCET mène à un faible taux d'utilisation des processeurs. Dans le cadre de ce projet, nous proposons quelques méthodes d'ordonnancement flexibles appliquées au décodage Turbo qui sont très avantageuses en comparaison de la méthode d'ordonnancement du WCET. Les méthodes proposées sont inspirées des méthodes d'ordonnancement qui traitent de calculs flexibles. Un modèle de performance de cette application nous a permis d'implémenter et valider quelques méthodes d'ordonnancement plus flexibles proposées pour l'exécution du décodage Turbo et qui sont adaptées à l'effort de traitement variable exigé par le décodeur.

Basée le modèle de performance proposé, l'efficacité des méthodes d'ordonnancement est démontrée. Elle justifie également l'utilisation de notre modèle d'évaluation de la performance. Les méthodes d'ordonnancement flexibles (FS – « flexible scheduling ») proposées améliorent substantiellement l'utilisation des ressources lorsque comparée à une méthode d'ordonnancement du temps d'exécution selon le pire cas (WCET). La méthode d'ordonnancement « priority-driven gradual », en comparaison de la méthode WCET, permet d'augmenter le nombre d'utilisateurs de 14 à 35, tout en maintenant une qualité de service acceptable, reflétée dans une dégradation très petite de 0.1 dB du gain de décodage.

## ABSTRACT

This project presents a dynamic performance model of a Wide band Code Division Multiple Access (WCDMA) application mapped on a homogeneous Multi Processor System-on-Chip (MPSoC). We develop a dynamic modeling strategy to evaluate the performance of MPSoC designs based on high level models of the applications and of the architecture. Such model permits ensuring that the multi-core platform is well exploited.

We focus on the Turbo decoder, which is a computationally intensive part of the application and which presents significant processing time variability. In a real-time system, it is very important that the tasks meet their deadlines. Due to the variability of tasks execution time, most scheduling algorithms used in real-time systems are based on the Worst Case Execution Time (WCET) of application tasks. The problem of such WCET based design is that, the scheduling analysis based on WCETs leads to low processor utilization. In this project, some flexible scheduling methods are proposed for Turbo decoding tasks which are highly advantageous comparing to the WCET scheduling method. The proposed methods are inspired from the scheduling methods which deal with flexible computations. A performance model of this application allows deriving and validating some proposed flexible scheduling methods for Turbo decoding tasks, which are adapted to the variable processing effort required by the decoder.

Using the proposed performance model, the efficiency of the scheduling methods is demonstrated. It also justifies the utilization of our performance evaluation model. The proposed flexible scheduling (FS) methods improve the resource utilization compared to a Worst Case Execution Time (WCET) scheduling method. In a specific benchmark reported in this thesis, the priority-driven gradual scheduling method, which most efficient FS method is the among the proposed FS methods, allows increasing the number of users from 14 to 35, while keeping an acceptable quality of service, as reflected in a very small degradation of 0.1 dB in the decoding gain.

# **CONDENSÉ EN FRANÇAIS**

#### 0.1. Introduction

Les plates-formes de réseau sur puces à processeurs multiples (MPSoC – « multiple processor system on chip ») peuvent fournir une puissance de traitement élevée par le partage de la charge sur un réseau des processeurs. De telles architectures sont des cibles appropriées pour l'exécution d'applications dynamiques qui nécessitent une quantité considérable de calculs. Les processeurs de traitement de signal numérique multi-cœur (DSPs – « Digital Signal Processors ») de haute performance sont de plus en plus employés dans les équipements de télécommunication qui traitent les signaux sonores, visuels et radio. Puisque ces DSP sont contrôlés par logiciel, lorsque suffisamment puissants, ils fournissent plus de flexibilité qu'un circuit intégré dédié (Application Specific Integrated Circuit – ASIC). Ces considérations ont mené au choix d'une plate-forme multi-DSP comme l'architecture cible dans ce projet. Celle-ci s'appelle Vocallo et elle a été conçue par la compagnie Octasic Semiconductor.

L'application cible de ce projet correspond au processus d'accès multiple à division de code à large bande (WCDMA – « wide-band code division multiple access ») d'une station de base de type « Universel Mobile Telecommunication Systems (UMTS) ». Le WCDMA rend possible le partage par différents utilisateurs d'une bande spectrale relativement large en l'étalement spectral par codage au lieu de tranches de temps exclusives. L'étalement de spectre (« spread spectrum ») est effectué en multipliant les flots (« stream ») de données de taux inférieur avec une séquence de taux plus élevé (connue sous le nom de « chip sequence ». Dans ce projet, nous avons l'intention de mettre en application le récepteur d'une station de base UMTS qui exploite le WCDMA sur une plate-forme multi-DSP.

Étant donné les caractéristiques temps réel et dynamiques de l'application cible et également la complexité de la conception de MPSoC, il est nécessaire d'avoir des

moyens de valider les capacités (par exemple, le trafic qu'elle peut servir) et la performance de la plate-forme avant l'implémentation, permettant ainsi de vérifier si une architecture MPSoC donnée convient à une application ou de déterminer le nombre de processeurs requis pour atteindre la performance désirée. Pour ces raisons, nous avons développé une stratégie de modélisation dynamique d'évaluation de la performance des MPSoC basée sur des modèles à niveau élevé des applications et de l'architecture. À ce niveau de modélisation, l'application est représentée comme un ensemble de tâches devant être exécutées, avec les ressources disponibles. L'architecture sur laquelle l'application s'exécutera est représentée simplement comme un ensemble de ressources de traitement reliées par un tissu de communication pour transférer des données entre elles. Un aspect exceptionnel de ce modèle est que la fonctionnalité est complètement absente du modèle, ce qui accélère la caractérisation et la conception du système. Une telle modélisation d'exécution permet une validation rapide de l'efficacité des stratégies d'assignation et d'ordonnancement d'une application complexe sur la plate-forme cible avant son exécution. La stratégie de modélisation développée est largement applicable et elle n'est pas limitée à l'application présentée dans ce projet.

Nous proposons ensuite une méthode pour l'assignation des différentes parties de l'application WCDMA sur la plate-forme. Ainsi, nous nous concentrons spécifiquement sur le processus de décodage Turbo qui est une partie de l'application WCDMA demandant une grande puissance de calcul. L'ordonnancement de ce genre de processus est étudié en détail. Le processus de décodage Turbo est caractérisé par une variabilité significative de l'effort de traitement qui rend l'ordonnancement d'un tel processus critique. Il est bien connu que les systèmes temps réel doivent fournir des réponses qui sont, non seulement logiquement correctes, mais également temporellement correctes. Dans un système temps réel, il est très important que les tâches respectent leurs limites de temps. Dans de tels systèmes, un des problèmes de conception le plus délicat est la variabilité des temps d'exécution des tâches. En raison de cette variabilité, la plupart des algorithmes d'ordonnancement utilisés dans les systèmes temps réel monoprocesseur ou multiprocesseur sont basés sur le temps d'exécution du pire cas (WCET – « Worst Case Execution Time ») des tâches. Le WCET des tâches est constant, par conséquent, les modèles de système en temps réel deviennent déterministes donc plus facile à comprendre et à mettre en application. Le problème de la conception basée sur le WCET est que, dans des applications temps réel avec une variabilité significative du temps d'exécution, l'analyse d'ordonnancement basée sur le temps d'exécution du pire cas mène à une faible utilisation des processeurs.

Dans ce projet, nous proposons quelques méthodes pour l'ordonnancement flexible des tâches du décodage Turbo qui sont très avantageuses en comparaison avec la méthode d'ordonnancement WCET. Les méthodes proposées sont inspirées des méthodes d'ordonnancement qui traitent des calculs flexibles. L'expression de calcul flexible se rapporte à une classe importante d'applications conçues et implémentés pour faire un compromis entre la qualité des résultats (services) qu'elles produisent et le temps et les ressources qu'elles emploient pour produire ces résultats. Plus spécifiquement, une application flexible peut réduire ses exigences de temps et de ressources aux dépens de la qualité de ses résultats tant que l'utilisateur trouve la qualité des résultats acceptable. Une application flexible peut dégrader graduellement sa qualité quand les ressources sont limitées et que les demandes en calculs sont élevées. Les méthodes d'ordonnancement proposées dans ce projet sont adaptées à la variabilité du processus de décodage Turbo et elles ajustent dynamiquement l'effort de traitement pendant l'exécution tout en gardant une qualité acceptable des résultats.

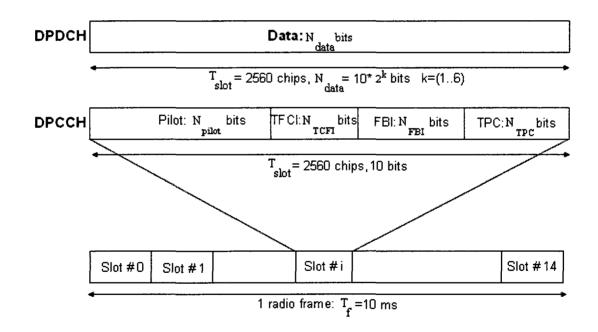

#### 0.2 Flot de traitement dans une station de base UMTS

Dans cette section, nous décrivons brièvement les flots de traitement dans une station de base WCDMA compris dans la liaison descendante (« downlink ») et ascendante (« uplink »), qui correspondent respectivement aux côtés émetteur et récepteur de la station de base [29]. Dans ce projet, le flux de traitement de la liaison montante qui correspond au côté récepteur de la station de base est considéré.

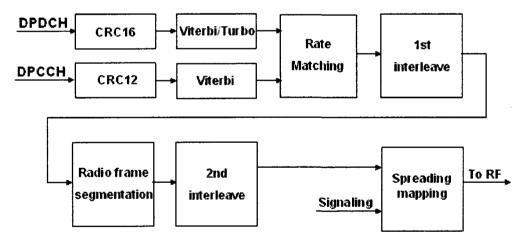

#### 0.2.1. Liaison descendante

Du côté de la liaison descendante, la station de base UMTS transmet un ensemble de canaux physiques communs aux utilisateurs dans la zone de portée de la station de base. La figure 2 (page 13) montre le flux de traitement de la station de base pour un utilisateur de la liaison descendante. Les données d'entrée venant de la couche du MAC (« Media Access Control ») se composent de différents flots (« streams ») de données. En premier lieu, le calcul de redondance cyclique (CRC – « Cyclic Redundancy Check ») et le codage de correction d'erreurs vers l'avant est ajouté aux flots. Ceux-ci sont alors envoyés par un ajusteur de taux (« rate matcher ») qui s'assure que le débit des trains est adapté à la couche physique. Les trains sont intercalés, segmentés dans des fenêtres et puis intercalées une autre fois. À la sortie, ils sont mappés, étalés au taux de chip (le chip est l'unité fondamentale de la transmission CDMA) et, finalement, envoyés à l'émetteur radio.

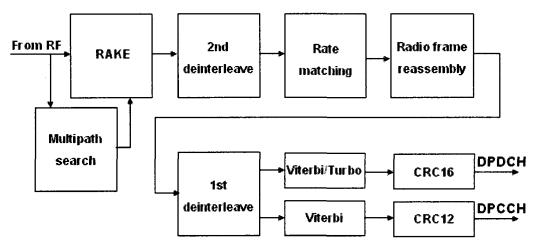

#### 0.2.2. Liaison montante

Le flux de traitement de la liaison montante est semblable au flux de la liaison descendante mais il inclut beaucoup plus de calculs. La figure 3 (page 14) montre le flux de données pour le traitement de la liaison montante. Une combinaison par trajets multiples est d'abord effectuée, basée sur un filtre de recherche de trajets multiples et un récepteur Rake. Le récepteur Rake additionne les trajets multiples et effectue l'étalement (« despreading ») du signal d'entrée. Ensuite, la trame est désentrelacée et on effectue l'ajustement inverse des taux (« reverse rate matching »). Ensuite, la reconstitution des trames radio (« radio frame reassembly ») est faite, suivi d'un désentrelaceur différent. Par la suite, un décodage pour correction d'erreurs est employé pour reconstituer les données reçues qui sont envoyées à la couche de MAC.

# 0.3. L'assignation d'application sur une plate-forme multiprocesseur

Comme mentionné auparavant, nous avons l'intention d'implémenter le traitement des signaux d'un récepteur de station de base UMTS sur une plate-forme multiprocesseur. Dans un récepteur de station de base UMTS, les trames radio arrivent à un taux définissant une période de traitement, où chaque trame radio reçue est une concaténation de blocs de transport, où chacun est associé à un utilisateur donné. L'application cible se compose d'un traitement de liaison montante montré dans la figure 3 (page 14) qui doit être appliqué aux blocs de données reçues correspondant aux utilisateurs de la station de base.

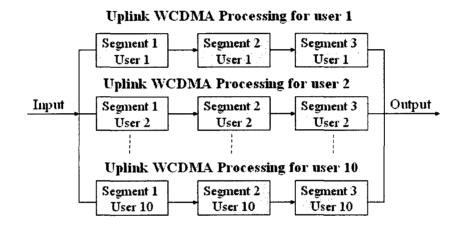

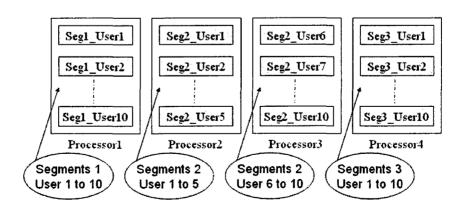

La figure 27 (page 67) montre un exemple d'application UMTS servant 10 utilisateurs. Afin de simplifier l'exemple, la liaison montante traitant chaque utilisateur est décrite comme comportant trois segments de traitement. Pour implémenter l'application sur une plate-forme multiprocesseur, les segments de traitement doivent être mappés sur les processeurs. Comme premier exemple de stratégie d'assignation, nous supposons que les segments de traitement de chaque utilisateur sont assignés à différents processeurs. Ainsi, les segments en chaîne de chaque utilisateur peuvent être exécutés en mode pipeline sur différents processeurs. Aussi, nous considérons que chaque processeur exécute seulement un type de traitement (à savoir un segment) pour les multiples utilisateurs. La stratégie d'assignation proposée est similaire à la méthode présentée dans [29]. Un exemple d'une telle stratégie d'assignation est illustré à la figure 28 (page 67), qui correspond au cas où l'application de la figure 27 (page 67) est implémentée sur quatre processeurs.

### 0.4. Modélisation de la performance

Comme mentionné précédemment, nous devons concevoir un modèle de performance pour estimer le temps d'exécution des applications sur la plate-forme avant leur exécution. Dans ce but, nous proposons une méthodologie de modélisation de la performance basée sur un modèle Matlab qui inclut les caractéristiques temporelles d'exécution de l'application et les primitives de la plate-forme à un niveau élevé. On suppose que les caractéristiques temporelles correspondant à l'exécution des différentes parties de l'application ont été extraites précédemment (à l'aide, par exemple, d'un simulateur de la plate-forme cible) et sont incluses dans le modèle de performance. Un tel modèle Matlab émule le temps d'exécution des différentes parties de l'application sans aucun test de fonctionnalité. De cette façon, le modèle fournit une évaluation rapide du temps d'exécution permettant également de valider les différentes stratégies pour l'assignation et l'ordonnancement de l'application sur la plate-forme. Le modèle permet également d'estimer la capacité de la plate-forme à soutenir les trafics demandés et il fournit une analyse statistique des services fournis par le système.

## 0.4.1. Étapes pour créer un modèle de performance

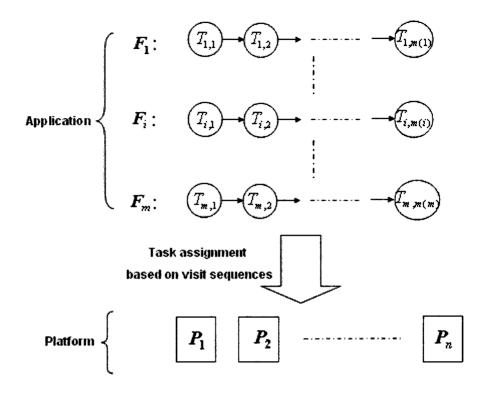

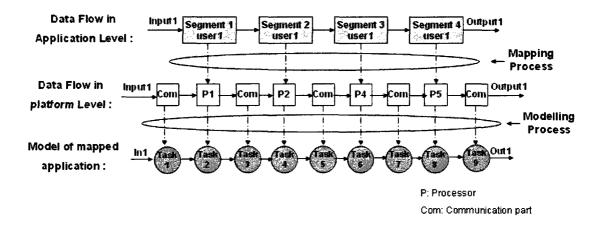

La méthodologie proposée pour la modélisation de performance inclut trois étapes. À la première étape, nous modélisons l'application qu'on désire mapper sur la plate-forme cible. Nous savons que l'application doit être divisée en plusieurs segments de traitement et que ces segments doivent être assignés aux différents processeurs de la plate-forme. À cette première étape, tous les segments de traitement sont présentés en tant que différentes tâches. Chacune de ces tâches inclut les paramètres temporels représentant l'exécution sur le processeur cible du segment de traitement correspondant. Également, les transmissions de données qui devront être affectées entre les processeurs sont modélisées par différentes tâches où sont inclus les paramètres temporels qui représentent les transmissions de données correspondantes. De cette façon, selon la stratégie d'assignation employée pour assigner les segments de traitement aux processeurs, nous créons un modèle de l'application mappée comprenant plusieurs tâches et l'information de dépendances entre ces tâches. La figure 9 (page 39) montre la première étape de notre stratégie de modélisation appliquée à un exemple simple.

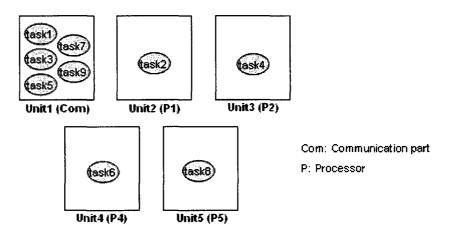

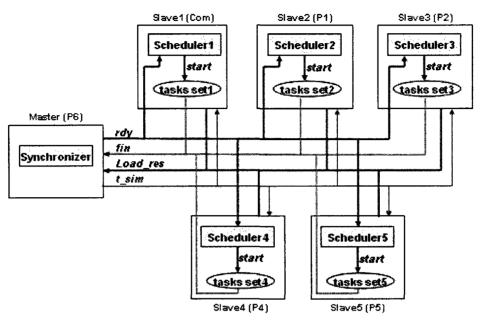

À la deuxième étape, nous modélisons l'architecture de la plate-forme cible comme un ensemble d'unités afin de représenter les différents processeurs ainsi que la partie communication de la plate-forme. Après, selon la stratégie d'assignation, les tâches créées à la première étape sont assignées aux unités créées lors de la première phase de la deuxième étape. Il est important de mentionner que les tâches qui représentent les transmissions de données entre les processeurs sont assignées à l'unité qui représente la partie communication de la plate-forme. À la fin de la deuxième étape, le modèle créé inclut plusieurs unités représentant l'architecture de la plate-forme où chaque unité inclut à son tour plusieurs tâches représentant les paramètres temporels de traitement ou des transmissions de données. La figure 11 (page 41) montre le modèle créé à la deuxième étape de la modélisation pour le même exemple que celui dans la figure 9 (page 39). Lors de la simulation du modèle, les tâches sur les différentes unités doivent être exécutées selon un ordre qui est imposé par les relations de précédence entre les segments de traitement modélisés. Une tâche est prête à être exécutée lorsque l'exécution des tâches précédentes, sur la chaîne de la tâche, est terminée.

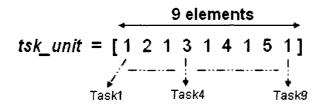

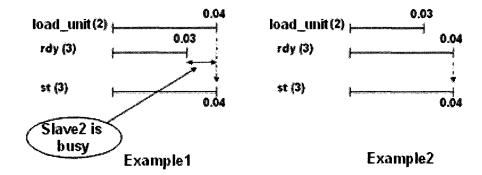

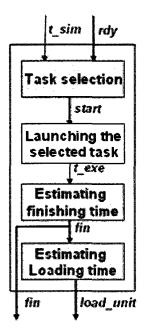

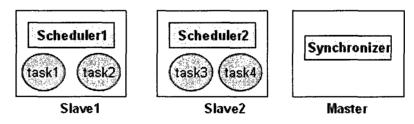

À la troisième étape de la modélisation, nous considérons une autre unité dans le modèle qui est responsable de contrôler l'exécution des tâches sur différentes unités. Cette unité supplémentaire s'appelle Maître (« Master ») et elle modélise un autre processeur de la plate-forme. Nous supposons que le Maître inclut un module appelé Synchroniseur (« Synchronizer ») pour définir les temps où les différentes tâches sont prêtes à être exécutées en vérifiant l'état d'exécution de toutes les tâches. Le Maître inclut également un module qui définit le temps de simulation. Le temps de simulation est utilisé pour calculer les paramètres temporels des tâches pendant la simulation. Les unités qui incluent les tâches s'appellent esclaves (« Slaves ») et elles sont responsables d'exécuter leurs tâches respectives. Nous supposons que chaque esclave inclut un module appelé Ordonnanceur (« Scheduler ») en plus de ses tâches. L'Ordonnanceur est responsable de choisir une tâche entre les tâches de l'esclave qui sont prêtes pour l'exécution basée sur sa stratégie d'ordonnancement. La tâche choisie par l'Ordonnanceur est exécutée par l'esclave. La figure 13 (page 43) démontre le modèle

de performance créé à l'étape finale de la modélisation pour le même exemple montré dans la figure 9 à la page 39.

De cette façon, nous créons un modèle de performance qui représente une description à niveau élevé de l'application ciblée et de l'architecture de la plate-forme. Pendant la simulation d'un tel modèle, toutes les unités mentionnées (Maître et esclaves) sont simulées. Nous considérons que la simulation est faite en plusieurs étapes. À chaque étape de la simulation, l'unité Maître est premièrement simulée alors que les Esclaves sont ensuite simulés les uns après les autres. La simulation de l'unité Maître produit les temps où les tâches sont prêtes à être exécutées. Aussi la Maître définit le temps de simulation à l'étape courante de la simulation. La simulation des unités esclaves peut mener à l'exécution de quelques tâches prêtes ainsi qu'une mise à jour de plusieurs des paramètres temporels concernant des tâches. La simulation d'un modèle de performance peut produire l'information temporelle de l'exécution des tâches et également de l'application entière.

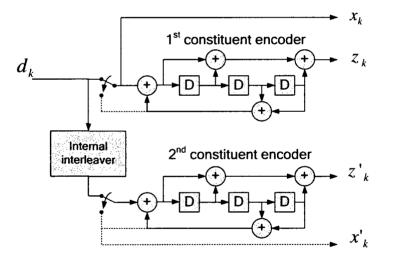

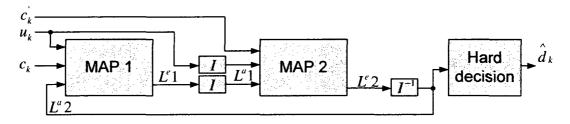

#### 0.5. Décodeur Turbo

Cette section se concentre sur un segment de traitement intensif de WCDMA appelé le décodeur Turbo qui est caractérisé par une variabilité substantielle du temps de traitement. Afin d'améliorer la robustesse de la transmission et de réduire au minimum le taux d'erreurs de bloc (BLER – « BLock Error Rate ») de l'application, la troisième génération de UMTS emploie la méthode de décodage Turbo. Les spécifications du procédé de décodage Turbo considéré dans ce projet sont comme suit. Le codeur convolutionnel de l'émetteur est basé sur un code convolutionnel parallèle concaténé (« Parallel Concatenated Convolutional Code – PCCC »), et inclut deux encodeurs convolutionnels récursifs systématiques identiques de 8 bits ainsi qu'un entrelaceur à taux de codage de 1/3 [28, 30]. Le décodeur Turbo a une structure itérative basée sur l'algorithme de « Maximum-A-Posteriori (MAP) » [30]. Le décodeur utilisé du côté de la réception inclut deux modules consécutifs de MAP qui constituent une des itérations exigées par le décodage. Puisqu'une itération simple implique beaucoup d'étapes de traitement, un critère automatique d'arrêt de décodage (ASDC – « Automatic Stop Decoding Criterion ») est employé pour terminer le processus de décodage dès qu'un niveau de fiabilité acceptable du décodage est atteint (selon un paramètre spécifique). Le nombre d'itérations est aussi limité entre 2 et 8. Dans la section suivante, la variabilité de traitement d'un processus de décodage Turbo est caractérisée et discutée. Puis, utilisant le modèle de performance, quelques algorithmes d'ordonnancement, à être utilisés par les processeurs qui sont consacrés à ce genre de traitement sont validés.

#### 0.5.1. Variabilité de traitement dans le décodeur Turbo

La variabilité du temps de traitement du décodage Turbo vient du nombre variable d'itérations de décodage exigées pour atteindre un niveau de correction d'erreur acceptable. Pour étudier la variabilité de traitement du décodage Turbo, nous avons utilisé un modèle complet de Simulink qui a été développé par notre équipe pour représenter exactement le processus entier de codage/décodage Turbo. Dans ce modèle, le canal de communication a été représenté par un bloc AWGN (« Additive White Gaussian Noise »), alors que le codeur et le décodeur ont été implémentés par plusieurs fonctions Matlab selon les caractéristiques précédemment mentionnées.

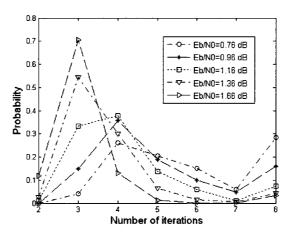

En simulant ce modèle Simulink, nous avons extrait le nombre d'itérations efficaces de décodage dans un décodeur Turbo qu'il faut exécuter selon les signaux reçus sous différents états du canal de communication. Étant donné la nature de l'algorithme et la manière dont il a été codé, le temps requis pour effectuer chaque itération de décodage par le processeur cible est constant pour une taille de trame donnée. Des résultats typiques pour le nombre d'itérations obtenues sous différents états du canal sont présentés dans la figure 29 (page 69). Les distributions de probabilité observées ressemblent à des distributions de Poisson. Notez que, étant donné que le nombre d'itérations est limité entre 2 et 8, la forme de la distribution est biaisée. Le

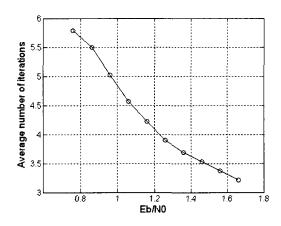

nombre moyen d'itérations a été également estimé selon différents états du canal tel que rapporté à la figure 30 (page 70). Cette figure montre une diminution du nombre moyen d'itérations de décodage lorsque l'état de canal s'améliore, autrement dit que Eb/N0 augmente.

#### 0.5.2. Ordonnancement du processus de décodage Turbo

Comme précédemment expliqué, dans ce projet, nous étudions l'implémentation d'un récepteur d'une station de base UMTS sur une plate-forme multiprocesseur. Le flot de traitement dans une transmission en liaison montante, qui correspond à notre récepteur de station de base UMTS, est présenté à la figure 3 (page 14). Basé sur la stratégie d'assignation expliquée à la section 0.3, nous avons supposé que chaque processeur de la plate-forme est consacré à l'exécution d'un seul type de segment de traitement tel que le « Rake », le « Rate matching » ou le décodage Turbo. Le traitement de ces segments s'effectue sur les blocs de données reçues de différents utilisateurs. Dans cette section, nous nous concentrons sur les processeurs consacrés à effectuer le processus de décodage Turbo des blocs reçus et nous discutons des concepts d'ordonnancement sur ces processeurs. Afin de simplifier le problème, nous considérons l'ordonnancement du décodage Turbo sur seulement un processeur.

Nous supposons que toutes les trames reçues par le récepteur de la station de base UMTS considéré ont le même taux d'arrivée définissant ainsi une période de traitement unique. Pour déterminer le nombre de blocs de données (nombre d'utilisateurs) qui peuvent être assignés à un processeur au cours de chaque période de traitement, nous devons estimer le temps d'exécution des processus correspondants de décodage Turbo sur le processeur cible. Nous supposons que le temps d'exécution total des processus de décodage Turbo assignés ne doit pas dépasser la période de traitement.

Vu la variabilité de traitement significative du décodage Turbo, nous supposons que l'estimation basée sur le pire cas du temps d'exécution serait fortement inefficace. Afin d'améliorer l'utilisation des ressources, nous considérons que le temps assigné à chaque processus de décodage Turbo est plus petit que celui du temps d'exécution du pire cas (WCET) et que nous pouvons par conséquent assigner un nombre plus élevé de blocs de données (nombre d'utilisateurs) à un processeur. Cependant, il est possible que, dans certains cas, les processus exigent plus que leurs fenêtres temporelles assignées nominalement, dues à une dégradation du canal qui peut mener à des problèmes d'ordonnancement. Pour résoudre ces problèmes, nous proposons quelques méthodes flexibles d'ordonnancement qui sont associées aux stratégies de contrôle qui peuvent limiter le traitement efficace afin de rencontrer les contraintes temporelles. La description des méthodes proposées est présentée dans les sections suivantes.

Pour étudier les méthodes d'ordonnancement, nous décrivons un modèle de performance comprenant une unité Maître et un esclave basés sur les concepts expliqués dans la section 0.4. Le Maître, comprenant le module de synchronisation, correspond à un processeur et l'esclave correspond à un autre processeur de la plate-forme. L'esclave est responsable des tâches représentant les processus de décodage Turbo sur les blocs de données de différents utilisateurs. La modélisation de performance du décodage Turbo n'est pas basée sur le décodage détaillé, mais plutôt sur les distributions de service précédemment rapportées (figure 29 à la page 69) qui ont été obtenues par le décodage détaillé. Chaque tâche représentant le décodage Turbo contient un générateur de nombres aléatoires qui modélise les distributions mentionnées. La simulation de chaque tâche de décodage Turbo fournit le nombre efficace d'itérations de décodage ( $it_eff$ ) et, par conséquent, le temps d'exécution du processus correspondant au décodage sur le processeur cible.

Mentionnons que, lorsqu'un bloc de données est reçu par le processeur pour être décodé, la tâche modélisant le processus est censée être activée. En d'autres termes, la tâche devient prête. Aussi, toutes les tâches assignées à l'esclave ont la même période d'activation qui est égale à la période de traitement. Nous supposons que toutes les tâches deviennent actives ou prêtes en même temps pour chacune des périodes de traitement.

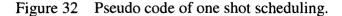

#### 0.5.2.1. Ordonnancement « one shot »

Premièrement, nous supposons qu'un certain nombre de tâches de décodage Turbo sont assignées à l'esclave. Ainsi, basées sur le nombre de tâches assignées à l'esclave et sur la période de traitement, les ressources consacrées pour exécuter le décodage par chaque tâche sont déterminées. Étant donné l'allocation des ressources pour chaque tâche de décodage Turbo, un budget d'itérations de décodage est garanti pour le décodage de chaque bloc. Ceci est déterminé par le système sous le nom de « Iteration Budget (*IB*) ». Au cours d'une période de traitement, l'Ordonnanceur placé sur l'esclave choisit une tâche à être simulée parmi toutes les tâches prêtes de l'esclave. Cette tâche est choisie à tour de rôle (« round robin »). Après la simulation de chaque tâche de décodage Turbo, si le nombre efficace d'itérations de décodage (*it\_eff*) est plus grand que son *IB*, le nombre d'itérations émulés de décodage pour le bloc correspondant est considéré égal à *IB*. Le bloc auquel l'Ordonnanceur n'a pu assigner son *it\_eff* avant la fin d'une période d'activation doit être considéré comme étant partiellement décodé.

Si le budget assigné est égal ou plus grand que  $it\_eff$ , le nombre d'itérations émulées est considéré égal au  $it\_eff$  correspondant. Un bloc qui peut atteindre son  $it\_eff$ est entièrement décodé. En effet, si  $it\_eff$  est inférieur au budget pour une tâche, la différence est distribuée entre les tâches non simulées dans la période de traitement courante et est ajoutée à leurs budgets assignés précédemment. Cette redistribution est faite aussi uniformément que possible. La figure 31 (page 75) démontre la méthode d'ordonnancement « one shot » sur un esclave comprenant quatre tâches de décodage Turbo au cours d'une période de traitement. Suivant les indications de cette figure, des blocs de données correspondants aux tâches 3 et 4 sont complètement traités, tandis que le décodage correspondant aux deux autres tâches est dégradé afin de respecter les budgets de ressource assignés.

#### 0.5.2.2. Ordonnancement progressif (« gradual »)

Comme expliqué pour la méthode d'ordonnancement « one shot », au cours de chaque période de traitement, la partie non utilisée du budget de chaque tâche simulée de décodage Turbo est distribuée et ajoutée aux budgets assignés des tâches non simulées. De cette façon, les *IB* (« Iteration Budget ») des tâches qui sont simulées plus tard ont une plus grande possibilité d'augmentation comparativement aux tâches simulées plus tôt. En raison de la qualité aléatoire du décodage des blocs, il est possible que les tâches simulées précédemment n'emploient pas totalement leur *IB* accru tandis que les tâches simulées précédemment auraient eu besoin de plus grands budgets.

Afin d'optimiser la répartition des ressources aux tâches, nous proposons une autre méthode appelée ordonnancement progressif. Dans cette méthode, un *IB* global est assigné à toutes les tâches qui est égal au nombre d'itérations de décodage qui pourraient être effectuées par le processeur cible au cours d'une période de traitement. Dans la méthode d'ordonnancement progressif, l'Ordonnanceur choisit à tour de rôle les tâches prêtes pour la simulation. Après l'émulation d'une itération de décodage pour chaque tâche choisie, la simulation de la tâche est suspendue (« preempted ») et, par conséquent, la prochaine tâche prête est choisie pour être simulée de la même manière.

La figure 33 (page 77) présente la méthode d'ordonnancement progressive sur un esclave comprenant quatre tâches de décodage Turbo au cours d'une période de traitement. Suivant les indications de la figure 33 (page 77), la valeur initiale de l'*IB* global dans l'exemple montré est égale à 17, ce qui est équivalent à la somme des *IB* initiaux des tâches dans l'exemple d'ordonnancement « one shot ». Après l'émulation d'une itération de décodage de chaque tâche, l'*IB* global est décrémenté par un. La simulation des tâches qui atteignent leur nombre efficace d'itérations de décodage est terminée. La simulation des tâches prêtes continue de la même manière jusqu'à ce que le budget global devienne zéro. Après l'arrêt dû à l'*IB* global, la simulation des tâches prêtes qui n'ont pas atteint à leur traitement efficace est arrêtée. Ceci mène à la

dégradation du traitement des blocs correspondants. Dans l'exemple montré dans la figure 33 (page 77), comme pour l'exemple « one shot », les décodages effectués pour la tâche 1 et la tâche 2 sont dégradées. Mais, dans cet exemple, une itération de plus est émulée pour les tâches mentionnées comparativement à l'exemple montré dans la figure 31 (page 75).

Dans la méthode d'ordonnancement progressif, le nombre d'itérations émulées pour chacune des tâches prêtes à chaque moment de la simulation est approximativement identique. Ainsi, les blocs correspondants aux tâches arrêtées, donc qui n'ont pas atteint leur nombre efficace d'itérations, ont presque le même niveau de traitement et par conséquent leurs traitements sont dégradés de manière presque identique.

#### 0.5.2.3. Ordonnancement « one shot » par priorité

Comme expliqué dans l'ordonnancement « one shot », les tâches simulées plus tôt ont la possibilité de recevoir de plus petits *IB*, ce qui cause des erreurs résiduelles plus prononcées en raison de la dégradation de traitement émulé, en comparaison aux tâches simulées postérieurement. Puisque les tâches prêtes sont choisies et simulées dans un ordre fixe pour toutes les périodes de traitement, les erreurs résiduelles associées aux tâches simulées plus tôt sont plus importantes que pour les tâches qui sont simulées plus tard.

De cette façon, les différences entre les qualités de service fournies pour les blocs (utilisateurs) correspondants augmentent en fonction du temps. Afin d'empêcher l'augmentation de la différence entre les qualités du service de l'utilisateur, nous faisons une modification dans la méthode d'ordonnancement « one shot ». Dans la méthode modifiée qui s'appelle ordonnancement « one shot » par priorité, nous assignons des priorités aux tâches prêtes pour déterminer leur ordre de simulation au cours de chaque période de traitement. Dans le modèle, nous avons considéré un paramètre appelé *sum\_add\_err*, qui est assigné à chaque tâche et qui représente les bits accumulés en

erreur additionnelle insérée dans le bloc correspondant, du commencement de la simulation jusqu'à la période de traitement courant.

Dans la méthode d'ordonnancement « one shot » par priorité, les budgets (*IBs*) sont assignés aux tâches de la même façon que dans la méthode « one shot ». La méthode pour la mise à jour du *IB* pour chaque tâche est également la même que pour l'ordonnancement « one shot » comme démontré dans la figure 31 (page 75). Avec cette méthode, l'ordre pour placer les tâches sur les colonnes montrées dans la figure 31 (page 75) est basé sur la priorité des tâches. À chaque période de traitement, les tâches prêtes ayant une valeur plus élevée de *sum\_add\_err* se voient assigner une priorité plus basse pour la simulation et sont placées sur les colonnes qui sont plus près de la dernière colonne. De cette façon, les tâches qui sont caractérisées par des taux d'erreurs accumulées plus élevés ont la possibilité de recevoir plus de ressource dans la période de traitement en cours. Ainsi, les qualités de service fournies pour différents utilisateurs deviennent plus uniformes comparativement à la méthode d'ordonnancement « one shot ».

#### 0.5.2.4. Ordonnancement progressif par priorité

Dans l'ordonnancement progressif, les tâches simulées postérieurement dans différents niveaux d'itération ont plus de possibilité de ne pas recevoir de ressource lorsque le *IB* global est terminé. Ainsi, plus d'erreurs additionnelles sont associées aux blocs décodés plus tard, en raison de la dégradation de traitement émulée, comparativement aux blocs décodés plus tôt. Puisque les tâches prêtes sont simulées dans un ordre fixe pour tous les niveaux d'itération et toutes les périodes de traitement, les erreurs additionnelles associées aux tâches simulées postérieurement à différents niveaux d'itération augmentent avec le temps beaucoup plus rapidement que les tâches qui sont simulées plus tôt. De cette façon, les différences entre les qualités de service fournies aux utilisateurs sont augmentées avec le temps.

Afin d'empêcher l'augmentation des différences entre les qualités de service pour chaque utilisateur, nous faisons une modification à la méthode d'ordonnancement progressif. Dans la nouvelle méthode d'ordonnancement modifiée, qui s'appelle ordonnancement progressif par priorité, comme pour l'ordonnancement progressif, les tâches sont simulées graduellement et un *IB* global est assigné pour limiter le traitement émulé des tâches comme démontré dans la figure 33 (page 77). En plus, comme pour la méthode « one shot » par priorité, le paramètre *sum\_add\_err*, est estimé et associé à chaque tâche totalement simulée dans chaque période de traitement qui définit la priorité de la tâche dans la période suivante.

Autrement dit, dans cette méthode, l'ordre de placement des tâches sur les colonnes montrées dans la figure 33 (page 77) est basé sur la priorité des tâches. À chaque période de traitement, les tâches prêtes avec une valeur plus élevée de *sum\_add\_err* ont une priorité plus élevée pour la simulation et sont placées sur les colonnes qui sont plus près de la première colonne. De cette façon, les tâches qui sont caractérisées par des taux des bits en erreur accumulés plus élevés ont la possibilité de recevoir plus de ressources dans la période de traitement courante. Ainsi, les qualités de service fournies aux différents utilisateurs deviennent plus uniformes comparativement à la méthode d'ordonnancement progressif.

#### 0.5.3. Résultats de simulation

Nous avons implémenté le modèle de performance expliqué dans la section 0.4 comprenant un Maître et une unité esclave. Les méthodes d'ordonnancement proposées dans la section précédente sont également incluses dans l'unité esclave en tant que différentes options pour ordonnancer les tâches de décodage Turbo. Le modèle a été simulé dans différents cas de figure afin de tester les méthodes d'ordonnancement proposées sous différents états de canal et charges pour des durées appropriées. La simulation du modèle a fourni le taux des bits en erreurs (BER) associés aux blocs décodés dans chacune des périodes de traitement. Afin de simplifier les résultats, nous

avons calculé le BER moyen de toutes les tâches correspondantes pendant la simulation selon différents cas de charges du système et d'états de canal. Les tâches spécifiques de décodage Turbo correspondent aux blocs de 656 bits de données (avant le codage donc (3\*656) +12 =1980 symboles après codage), et ces trames sont transmises à 64 k symboles/s pour des périodes de 40 ms.

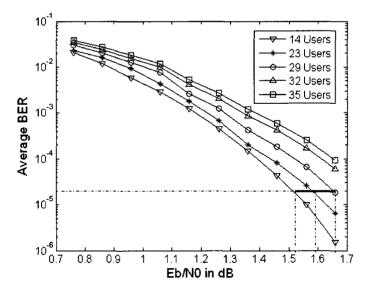

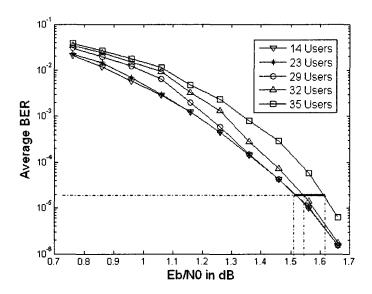

Étant donné la période des trames reçues et le pire temps de traitement du décodage Turbo sur le processeur cible qui comprend 8 itérations de décodage dans le cas de la conception WCET, les processus de décodage Turbo pour 14 utilisateurs peuvent être assignés au processeur. Autrement dit, dans notre modèle de performance, selon la méthode du WCET, nous pouvons assigner 14 tâches de décodage Turbo à l'esclave sans causer de dégradation de traitement. Le cas consistant à assigner 14 utilisateurs (méthode du WCET) est employé comme une référence pour toute comparaison avec les méthodes d'ordonnancement proposées où plus d'utilisateurs pourront être assignés.

#### 0.5.3.1. Ordonnancement « one shot »

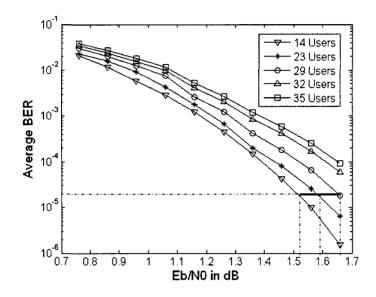

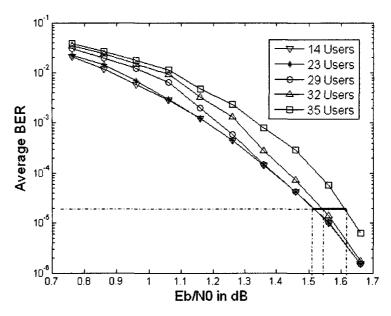

En simulant le modèle de performance mentionné suivant la méthode d'ordonnancement « one shot », le BER moyen de toutes les tâches (correspondant aux différents utilisateurs) est obtenu selon le nombre d'utilisateurs assignés et l'état du canal et est montré à la figure 35 (page 82). La distance horizontale entre les courbes du BER moyen et de la courbe de référence (cas de 14 utilisateurs) pour un BER précis, démontre la dégradation moyenne du gain de décodage. Basé sur la figure 35 (page 82), la dégradation moyenne du gain de décodage est obtenue pour 3 cas où diffèrent le nombre d'utilisateurs pour une valeur de BER de 2\*10<sup>-5</sup>. Ces résultats sont rapportés dans le tableau 4 qui démontre qu'avec 29 utilisateurs assignés à un processeur, la dégradation de gain de décodage est d'approximativement 0.15 dB. Une telle valeur de dégradation est négligeable et n'exerce aucun effet significatif sur la qualité du service.

#### 0.5.3.2. Ordonnancement progressif

En simulant le modèle de performance mentionné suivant l'algorithme d'ordonnancement progressif, le BER moyen des utilisateurs est obtenu pour un nombre variable d'utilisateurs assignés et pour différents états de canal et est montré à la figure 36 (page 84). Basé sur les figures 35 et 36 (pages 82 et 84), l'amélioration des BER moyen en utilisant la méthode d'ordonnancement progressif comparativement à la méthode d'ordonnancement « one shot » est remarquable. En examinant la figure 36 (page 84), la dégradation moyenne du gain de décodage dans 5 cas de figure avec un nombre d'utilisateurs différent et une valeur de BER de 2\*10<sup>-5</sup> est obtenue et présentée dans le tableau 5. Ce tableau montre que la dégradation moyenne du gain de décodage pour les cas de 23 et 29 utilisateurs est zéro tandis que nous avions une dégradation de gain pour le même nombre d'utilisateurs avec la méthode d'ordonnancement « one shot ». En se basant également sur le tableau 5, la dégradation moyenne du gain de décodeur pour plus d'utilisateurs, tels que 32 et 35, est négligeable.

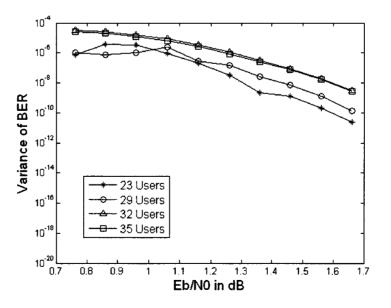

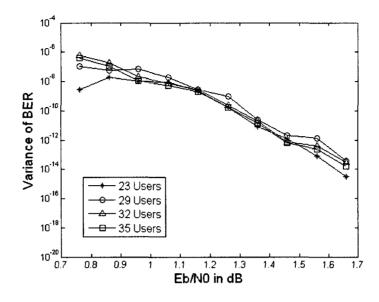

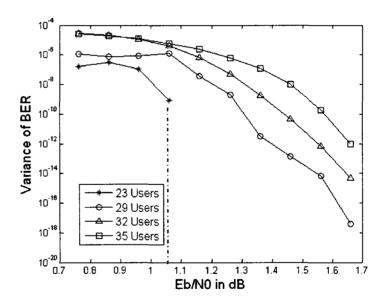

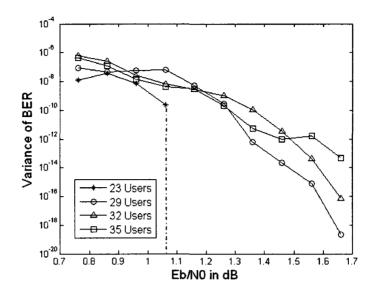

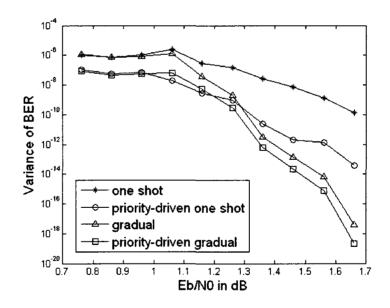

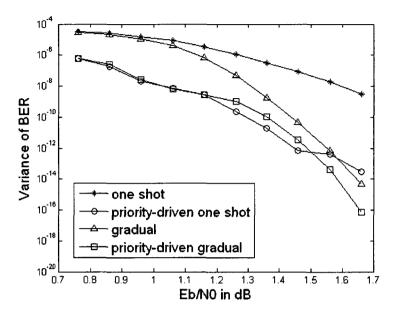

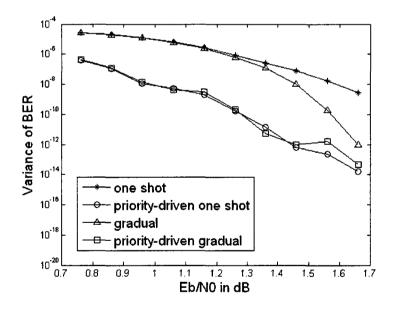

# 0.5.3.3. Ordonnancement « one shot » par priorité et progressif par priorité

En utilisant l'ordonnancement « one shot » par priorité et puis l'ordonnancement progressif par priorité dans notre modèle de performance et en simulant ces modèles correspondants, le BER moyen des utilisateurs selon le nombre d'utilisateurs assignés et l'état du canal sont obtenus. En observant les résultats, nous nous sommes rendu compte que les résultats moyens des BER obtenus en employant la méthode « one shot » par priorité sont identiques aux résultats correspondants dans le cas de méthode « one shot » montrée à la figure 35 (page 82). La méthode progressive par priorité fournit également les mêmes résultats de BER moyens que ceux produits par la méthode progressive et sont affichés à la figure 36 (page 84). Afin de démontrer l'avantage des méthodes par priorité à uniformiser les qualités de service des utilisateurs, nous avons également estimé la variance du BER des utilisateurs. La variance du BER des utilisateurs selon les différentes méthodes d'ordonnancement proposées sont présentés dans les figures 37, 38, 39 et 40 (pages 85,86 et 87). Ces courbes sont paramétrées en fonction du nombre d'utilisateurs. Dans les figures 39 et 40 (pages 86 et 87), les variances du BER pour les valeurs Eb/N0 qui sont supérieures aux valeurs montrées par les lignes pointillées sont égales à zéro. En observant les figures 37 et 38 (pages 85 et 86), nous nous rendons compte que la méthode « one shot » par priorité uniformise les performances des BER des utilisateurs en obtenant des variances plus petites comparativement à la méthode « one shot ». En comparant également les figures 39 et 40 (page 86 et 87), on peut prouver que la méthode d'ordonnancement progressif par priorité rend plus uniforme les performances des BER des utilisateurs en fournissant des variances plus petites comparativement à la

Étant donné les résultats affichés pour les BER moyen et la variance des BER, nous trouvons que l'ordonnancement progressif par priorité est la méthode la plus efficace entre les méthodes proposées puisqu'elle fournit la meilleure performance pour le BER et offre une uniformité de service pour plusieurs utilisateurs.

#### 0.6. Conclusion

méthode progressive.

Dans ce projet, un modèle dynamique a été présenté pour évaluer l'exécution d'une application WCDMA sur une plateforme MPSoC. Plus spécifiquement, nous nous sommes concentrés sur le décodeur Turbo, une partie de l'application demandant un grand effort de calcul et présentant une variabilité de traitement substantielle. Notre modèle nous a permis de dériver et valider quelques méthodes flexibles pour l'ordonnancement des tâches de décodage Turbo, qui sont adaptées à l'effort de traitement variable exigé pour le décodeur. En employant le modèle de performance présenté, l'efficacité de ces méthodes d'ordonnancement a été démontrée, ce qui a également justifié l'utilisation de notre modèle d'évaluation de performance.

Toutes les méthodes d'ordonnancement flexibles proposées, une fois comparées à la méthode d'ordonnancement du temps d'exécution du pire cas (WCET), améliorent l'utilisation des processeurs en employant une évaluation plus juste de l'effort de décodage et en causant une dégradation de traitement acceptable. La différence entre les méthodes d'ordonnancement flexible proposées était dans l'uniformité de la qualité de service fournit pour les utilisateurs. La dernière méthode d'ordonnancement flexible appelée ordonnancement progressif par priorité a fourni la qualité de service la plus uniforme pour les utilisateurs. Cette méthode, une fois comparée à une méthode d'ordonnancement du temps d'exécution du pire cas (WCET), a permis d'augmenter le nombre d'utilisateurs de 14 à 35, alors que la conservation d'une qualité du service acceptable se reflétait dans une dégradation très petite de moins de 0.1 dB de gain de décodage.

# TABLE OF CONTENTS

| ACKNOWLEDMENTS                                            | iv     |

|-----------------------------------------------------------|--------|

| RÉSUMÉ                                                    | v      |

| ABSTRACT                                                  | vii    |

| CONDENSÉ EN FRANÇAIS                                      | ix     |

| TABLE OF CONTENTS                                         | xxix   |

| LIST OF TABLES                                            | xxxiii |

| LIST OF FIGURES                                           | xxxiii |

| LIST OF SIGNS ANDABBREVIATIONS                            | xxxv   |

| CHAPTER 1 INTRODUCTION                                    | 1      |

| CHAPTER 2 BASIC CONCEPTS AND LITERATURE REVIEW            | 7      |

| 2.1. Universal Mobile Telecommunication System (UMTS)     | 7      |

| 2.1.1. WCDMA Physical layer                               | 8      |

| 2.1.2. Frame structure for uplink DPDCH/DPCCH             | 9      |

| 2.1.3. Processing in a WCDMA/FDD radio base station       | 10     |

| 2.1.3.1. Downlink processing flow                         | 11     |

| 2.1.3.2. Uplink processing flow                           | 11     |

| 2.1.4. Channel Coding                                     |        |

| 2.1.4.1. Turbo coder                                      | 13     |

| 2.1.4.2. Turbo decoder                                    | 15     |

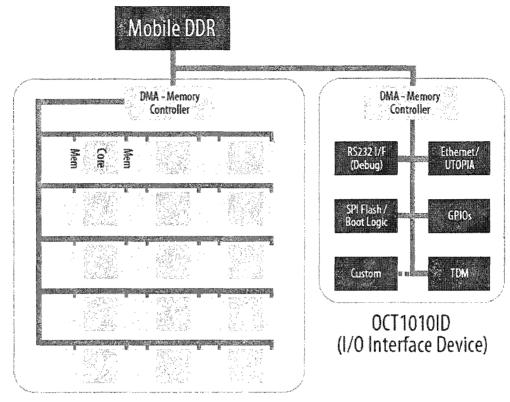

| 2.2. The Vocallo architecture                             | 16     |

| 2.2.1. Internal architecture                              |        |

| 2.2.2. External architecture                              | 19     |

| 2.2.3. Power and Performance Optimizations                | 19     |

| 2.3. Performance modeling                                 | 19     |

| 2.4. Mapping the system level models into MPSoC platforms |        |

| 2.5. Multiprocessor scheduling and synchronization        | 23     |

| 2.5.1. End-to-End system functions                        |        |

.

| 2.5.2. Elements of scheduling algorithms for end-to end periodic functions | 25    |

|----------------------------------------------------------------------------|-------|

| 2.5.3. Interprocessor synchronization protocols                            |       |

| 2.5.4. Scheduling the tasks on one processor                               |       |

| 2.6. Worst Case Execution Time (WCET) based design                         |       |

| 2.7. Scheduling flexible applications                                      |       |

| 2.8. Mapping and scheduling of Turbo decoding in MPSoC platforms           | 30    |

| 2.9. Conclusion                                                            | 31    |

| CHAPTER 3 PERFORMANCE MODELING                                             | 34    |

| 3.1. Steps to create a performance model                                   | 34    |

| 3.1.1. Modelling the Mapped Application on the Multi-Processor Pla         | tform |

| (Modelling Step 1)                                                         | 36    |

| 3.1.2. Structuring the model of mapped application (Modelling step 2)      | 38    |

| 3.1.3. Creating a Master/Slave Structure (Modelling Step 3)                | 40    |

| 3.2. Detailed description of the performance model                         | 46    |

| 3.2.1. Master                                                              | 46    |

| 3.2.2. Slave                                                               | 54    |

| 3.3. One performance model example                                         | 58    |

| 3.4. Conclusion                                                            | 60    |

| CHAPTER 4 SCHEDULING OF TURBO DECODING                                     | 62    |

| 4.1. Mapping the uplink WCDMA processing on an MPSoC platform              | 63    |

| 4.2. Processing variability of the studied Turbo decoder                   | 65    |

| 4.3. BER performance of the studied Turbo decoder                          | 67    |

| 4.4. Proposed methods for scheduling the Turbo decoding                    | 68    |

| 4.4.1. One shot scheduling                                                 | 70    |

| 4.4.2. Gradual scheduling                                                  | 73    |

| 4.4.3. Priority-driven one shot scheduling                                 | 75    |

| 4.4.4. Priority-driven gradual scheduling                                  | 76    |

| 4.5. Simulation results                                                    | 77    |

| 4.5.1. One shot scheduling                                                 |       |

|     | ٠ |

|-----|---|

| vvv |   |

| *** |   |

|     |   |

|     |   |

| 4.5.2. Gradual scheduling                                              | 80 |

|------------------------------------------------------------------------|----|

| 4.5.3. Priority-driven one shot and priority-driven gradual scheduling | 81 |

| 4.6. Validating investigation                                          | 85 |

| 4.7. Elapsed simulation time                                           | 88 |

| 4.8. Conclusion                                                        | 90 |

| CHAPTER 5 CONCLUSION                                                   | 92 |

| REFERENCES                                                             | 95 |

| APPENDIX 1                                                             | 98 |

#### xxxii

## LIST OF TABLES

| Table 1 | Task timing parameter definition                                             | 44 |

|---------|------------------------------------------------------------------------------|----|

| Table 2 | Possible cases of timing parameters for a task                               | 45 |

| Table 3 | Performance parameters of Turbo decoder                                      | 68 |

| Table 4 | Average decoding gain degradation at a BER of $2*10^{-5}$ for one shot       |    |

| sche    | duling                                                                       | 80 |

| Table 5 | Average decoding gain degradation at a BER of $2*10^{-5}$ in case of gradual |    |

| sche    | duling                                                                       | 80 |

| Table 6 | Elapsed simulation times.                                                    | 89 |

# **LIST OF FIGURES**

| Figure 1 Radio frame structure for uplink DPDCH/DPCCH [3                             | 1] 10                |

|--------------------------------------------------------------------------------------|----------------------|

| Figure 2 Downlink transmission flow [29]                                             |                      |

| Figure 3 Uplink transmission flow [29]                                               |                      |

| Figure 4 Turbo encoder structure [30]                                                |                      |

| Figure 5 Generic Turbo decoder architecture [4]                                      |                      |

| Figure 6 Block diagram of Vocallo architecture [21]                                  |                      |

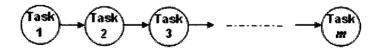

| Figure 7 Example of a system function                                                |                      |

| Figure 8 Example of a system including m functions and n pro                         | cessors 26           |

| Figure 9 Modelling a mapped application                                              |                      |

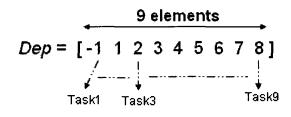

| Figure 10 Example of vector <i>Dep</i>                                               |                      |

| Figure 11 Example of the structured model of a mapped applic                         | ation 39             |

| Figure 12 Describing the structured model of mapped applicat                         | ion 39               |

| Figure 13 Performance model block diagram for an example c                           | ase 41               |

| Figure 14 Example for vectors <i>rdy</i> , <i>st</i> , <i>start</i> , and <i>fin</i> |                      |

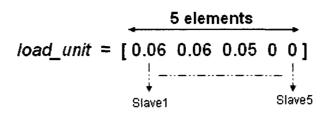

| Figure 15 Example of vector load_unit                                                |                      |

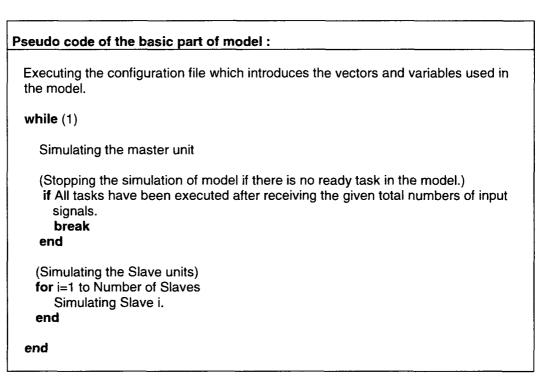

| Figure 16 Pseudo code of the basic part of model                                     |                      |

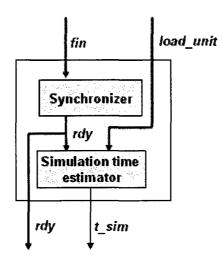

| Figure 17 Block diagram of the Master.                                               |                      |

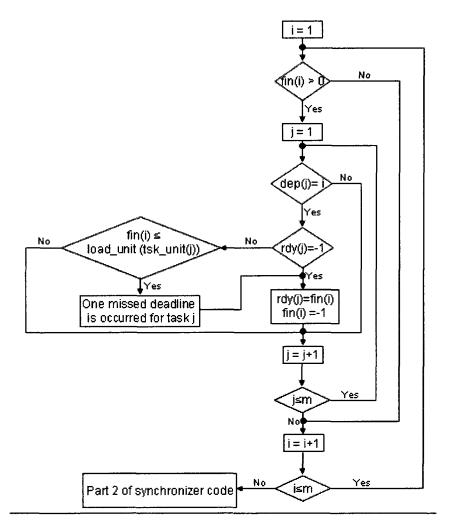

| Figure 18 Flow chart of the Synchronizer (Part 1)                                    |                      |

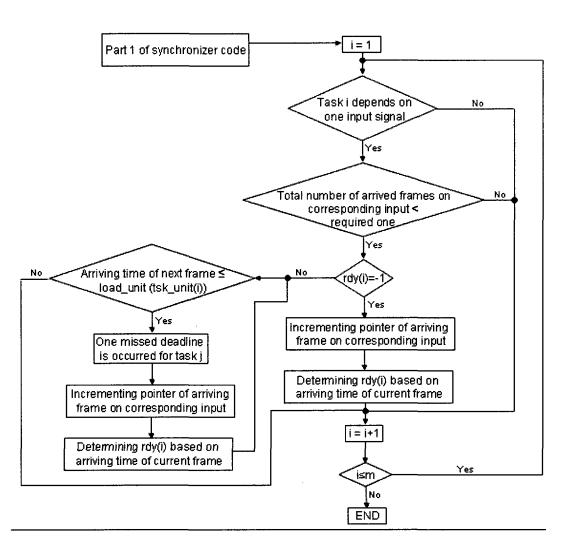

| Figure 19 Flow chart of the Synchronizer (Part 2).                                   |                      |

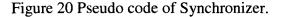

| Figure 20 Pseudo code of Synchronizer                                                |                      |

| Figure 21 Examples for estimating earliest start time                                |                      |

| Figure 22 Pseudo code of simulation Time Estimator                                   |                      |

| Figure 23 Block diagram of a Slave                                                   |                      |

| Figure 24 Pseudo code of a Slave unit                                                |                      |

| Figure 25 Block diagram of a performance model example                               |                      |

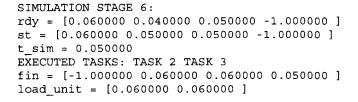

| Figure 26 Parameter values in a performance model during four                        | simulation stages 59 |

| Figure 27 Example of processing on an UMTS receiver base-s                           | tation64             |

#### xxxiv

| Figure 28 | Mapping Example                                                 | . 64 |

|-----------|-----------------------------------------------------------------|------|

| Figure 29 | Probability density of the number of iterations.                | . 66 |

| Figure 30 | Average number of decoding iterations                           | . 67 |

| Figure 31 | One shot scheduling example.                                    | . 72 |

| Figure 32 | Pseudo code of one shot scheduling                              | . 72 |

| Figure 33 | Gradual scheduling example                                      | . 74 |

| Figure 34 | Pseudo code of gradual scheduling                               | . 75 |

| Figure 35 | Average BER in case of one shot scheduling                      | . 79 |

| Figure 36 | Average BER in case of gradual scheduling.                      | . 81 |

| Figure 37 | BER variance in one shot scheduling.                            | . 82 |

| Figure 38 | BER variance in priority-driven one shot scheduling             | . 83 |

| Figure 39 | BER variance in gradual scheduling                              | . 83 |

| Figure 40 | BER variance in priority-driven gradual scheduling.             | . 84 |

| Figure 41 | BER variance in case of 29 users.                               | . 84 |

| Figure 42 | BER variance in case of 32users.                                | . 85 |

| Figure 43 | BER variance in case of 35 users.                               | . 85 |

| Figure 44 | Average BER in case of validation model and one shot scheduling | . 87 |

| Figure 45 | Average BER in case of validation model and gradual scheduling  | . 88 |

## LIST OF SIGNS AND ABBREVIATIONS

| ALU         | Arithmetic Logic Unit                              |

|-------------|----------------------------------------------------|

| ASIC        | Application Specific Integrated Circuit            |

| ATM         | Asynchronous Transfer Mode                         |

| ave_add_err | Average number of additional bits in error         |

| BER         | Bit Error Rate                                     |

| CDMA        | Code-Division Multiple-Access                      |

| CMOS        | Complementary Metal-Oxide-Semiconductor            |

| Com         | Communication part                                 |

| CPU         | Central Processing Unit                            |

| CRC         | Cyclic Redundancy Check                            |

| DDR         | Double Data Rate                                   |

| Dep         | Vector that describes dependencies between tasks   |

| DMA         | Direct Memory Access                               |

| DPCCH       | Dedicated Physical Control Channel                 |

| DPDCH       | Dedicated Physical Data Channel                    |

| DS-CDMA     | Direct-Sequence Code-Division Multiple-Access      |

| DSP         | Digital Signal Processor                           |

| DSSS        | Direct-Sequence Spread Spectrum                    |

| EDF         | Earliest-Deadline-First                            |

| F           | Function                                           |

| FBI         | Feedback Information                               |

| FDD         | Frequency Division Duplex                          |

| fin         | Vector that describes the completion time of tasks |

| FPGA        | Field-Programmable Gate Array                      |

| FS          | Flexible Scheduling                                |

| GMII        | Gigabit Media Independent Interface                |

| GPIO        | General Purpose Input/Output                       |

| HDLC        | High-Level Data Link Control                     |

|-------------|--------------------------------------------------|

| HW          | Hardware                                         |

| IB          | Iteration Budget                                 |

| IDE         | Integrated Development Environment               |

| it_eff      | Effective number of iterations                   |

| it_max_perm | Maximum permitted number of iterations           |

| LLR         | Log-Likelihood-Ratio                             |

| load_unit   | Vector that describes loading time of processors |

| MAC         | Medium Access Control                            |

| MAP         | Maximum-A-Posteriori algorithm                   |

| MII         | Media Independent Interface                      |

| MIPS        | Million Instructions Per Second                  |

| MPSoC       | Multi-Processor System-on-Chip                   |

| NoC         | Network-on-Chip                                  |

| OCT1010     | Octasic's platform including 15 Opus cores       |

| OPERA       | Octasic Polytechnique ETS Radio Application      |

| Р           | Processor                                        |

| PBMT        | Performance Based Modeling Tool                  |

| PCCC        | Parallel Concatenated Convolutional Code         |

| RACH        | Random Access Channel                            |

| rdy         | Vector that describes ready time of tasks        |

| RM          | Rate-Monotonic                                   |

| RMII        | Reduced Media Independent Interface              |

| PRACH       | Physical Random Access Channel                   |

| RRC         | Radio Resource Control                           |

| RSC         | Recursive Systematic Convolutional               |

| RS232       | Recommended Standard 232                         |

| RTL         | Register Transfer Level                          |

| SCH         | Synchronization Channel                          |

|             |                                                  |

| SF          | Spreading Factor                                             |

|-------------|--------------------------------------------------------------|

| SoC         | System-on-Chip                                               |

| SPI         | Serial Peripheral Interface Bus                              |

| SR          | Synchronous Reactive                                         |

| SR MoC      | Synchronous Reactive Model of Computation                    |

| st          | Vector that describes the earliest time for tasks' execution |

| start       | Vector that describes the execution starting time of tasks   |

| sum_add_err | Accumulated additional bits in error                         |

| SW          | Software                                                     |

| T           | Task                                                         |

| TDD         | Time Division Duplex                                         |

| TDM         | Time-Division Multiplexing                                   |

| t_exe       | Execution time of a task                                     |

| TFCI        | Transport Format Combination Identifier                      |

| TLM         | Transaction Level Modeling                                   |

| TPC         | Transmit Power Control                                       |

| tsk_unit    | Vector that describes assignment of tasks to processors      |

| t_sim       | Simulation time                                              |

| u           | Utilization of a task                                        |

| U           | Total utilization                                            |

| UMTS        | Universal Mobile Telecommunication System                    |

| Utopia      | An ATM protocol evolved into System Packet Interface         |

| V           | Vector                                                       |

| VPC         | Virtual Processing Components                                |

| VPU         | Virtual Processing Unit                                      |

| WCDMA       | Wide-band Code Division Multiple Access                      |

| WCET        | Worst Case Execution Time                                    |

| 3GPP        | 3 <sup>rd</sup> Generation Partnership Project               |

|             |                                                              |

xxxvii

## **CHAPTER 1**

## INTRODUCTION

Multi-Processor System-On-Chip (MPSoC) platforms can provide high computational performance along with load balancing on a network of processors. Such architectures are appropriate targets for the implementation of dynamic and computationally intensive applications. High-performance multi-core Digital Signal Processors (DSPs) are increasingly used for telecommunication equipments to process voice, video, and radio signals. Since DSPs are software-driven, when sufficiently powerful, they provide more flexibility than dedicated ASICs. Considering these explanations, a multi-DSP platform is chosen as the target architecture in this project.

The target application in this project is the WCDMA (Wide-band Code Division Multiple Access) process on the received data blocks corresponding to different users in a Universal Mobile Telecommunication Systems (UMTS) receiver base-station. The WCDMA makes possible that different users share a relatively wide spectral band using coding instead of time slots. The WCDMA modulator is based on the spread spectrum modulation technique which consists in multiplying the lower-rate data stream with a higher rate (known as the chip sequence). In this project, we intend to implement a UMTS receiver base-station including the corresponding WCDMA processes on a multi-DSP platform.

Considering the real-time and dynamic characteristics of the target application, and also the complexity of MPSoC design, it is necessary to have means of validating the capacity (e.g. the traffic it can serve) and performance of the platform before implementation, either to verify if a proposed MPSoC architecture is suitable for the application or to determine the number of processors required to fulfill the requirements. For these reasons, we have developed a dynamic modeling strategy for evaluating the performance of MPSoC designs based on high level models of the application and of the architecture. At this level of modeling, the application is represented as a set of tasks that are to be performed, their resource requirements, such as execution times, release time, etc., and the order in which the tasks are to be executed. Also, the architecture upon which the application will execute is represented simply as a set of computational resources and a communications fabric for transferring data between them. One outstanding aspect of this model is that the functionality is retrieved directly from the model, which speeds up characterization and system design. Such performance modeling allows quick validation of the efficiency of strategies for mapping and scheduling a complex application on the target platform before run time. The developed modeling strategy can be utilized for any MPSoC design and it is not limited to the target application of this project.

Afterward, we propose a method for mapping the different parts of the WCDMA application on the platform. We focus specifically on the Turbo decoding process which is a computationally intensive part of the WCDMA application and scheduling of this kind of process is investigated in details. The Turbo decoding process is characterized by a significant variability of the processing effort which makes the scheduling of such process more critical. It is well known that real-time systems must provide responses which are not only logically correct, but also temporally correct. In a real-time system, it is very important that the tasks meet their deadlines. In such systems, one of the most delicate design problems is the variability of tasks execution time. Due to such variability, most scheduling algorithms used in uniprocessor or multiprocessor real-time systems are based on the Worst Case Execution Time (WCET) of application tasks. The WCET of tasks are constant, consequently the real-time system models become deterministic, thus easier to understand and implement. The problem of such WCET based design is that, in real-time applications with a significant variability of the execution time, the scheduling analysis based on WCETs leads to low processor utilization. In this project, some flexible scheduling methods are proposed for Turbo decoding tasks which are highly advantageous comparing to the WCET scheduling method. The proposed methods are inspired from the scheduling methods that deal with

flexible computations. The term flexible computation (or application) refers to a wide class of applications that are designed and implemented to trade off, at run-time, the quality of the results (services) they produce with the amount of time and resources they use to produce the results. In particular, a flexible application can reduce its time and resources demands at the expense of the quality of its results. For as long as the user finds its quality result acceptable, a flexible application can degrade gracefully when resources are limited and the demands of competing workloads are high. The proposed scheduling methods in this project are adapted to the variability of the Turbo decoding process and they dynamically adjust the processing effort during the execution while keeping an acceptable quality of results.

There are several references on performance modeling methods in the literature such as [10, 13, 15 and 25]. In this project, similarly to the mentioned references, a performance model is structured, which is used to verify the execution time of applications on the platform before implementation. The mentioned model has been created using the Matlab/Simulink software and it is based on the structure of the target application and platform. Unlike the proposed tool in [15], in this project, we consider only the performance modeling methods presented in [10, 25] are SystemC-based where, in this project, the presented model is developed using the Matlab/Simulink software which is the same environment that is used in our project to model and characterize the target application.

Also, research has been published on the mapping and scheduling of Turbo decoding on an MPSoC platform such as [6, 8, 18, 19 and 20]. In this project, similarly to [6] and [18], scheduling of the Turbo decoding process for several encoded blocks on the dedicated processors is studied. However, our scheduling methods allow much more flexible degradation by considering dynamic iteration budgets, when compared to the decoding degradation presented in [18]. Such processing degradation concept is not considered in [6]. Unlike [8], [19] and [20], we consider that the Turbo decoder

algorithm consists of only one monolithic task and the Turbo decoding process on each coded block is performed solely on one processor. Thus, the Turbo decoding process on the individual processors is data independent, which reduces the data communications between the processors. By allocating different encoded blocks on the individual processors, we also exploit the platform parallelism.

This project is part of a project called OPERA which is a collaboration between Octasic semiconductor, École Polytechnique de Montréal and École de Technologie Supérieure de Montréal. The objective of the OPERA project is to develop a methodology for automatic mapping of a Simulink system-level model of the target application to the Vocallo multi-DSP platform (platform designed and fabricated by Octasic). Firstly, the target application must be modeled in the Simulink environment, using C/C++, Matlab scripts or Simulink library blocks. Thus, using several tools, we intend to effectively convert such a high-level Simulink model into low-level code executable by the Vocallo DSP cores. Moreover, we will perform resource requirement estimations which will let us determine an efficient strategy for mapping the obtained low-level code of the application on the platform processors. Besides the mentioned conversion process, the developed performance modeling methodology from my project allows rapid execution performance verification to validate several mapping and scheduling methods without any functional verification.

The rest of this thesis is organized as follows. Some basic concepts and a literature review regarding our project are presented in Chapter 2. We first describe the UMTS base-station and the WCDMA processing. Then, we describe the architecture of the Vocallo multi-DSP platform which is used as the target hardware in this project. Afterward, we present a literature review on performance modeling methods. Also, a literature review is presented on mapping system-level models into MPSoC platforms which describe the methods to combine system-level models and architecture-level descriptions for MPSoC designs. Then, we present some basic concepts on multiprocessor scheduling and synchronization. Also, we explain the WCET-based

design and the advantages and disadvantages of this method in a real-time system implementation. Afterwards, we present some methods for scheduling flexible applications which allow trading the quality of results for the amount of processing time and the required resources. At the end of Chapter 2, we introduce a literature review on the mapping and scheduling of Turbo decoding in an MPSoC platform.

In Chapter 3, the basic concepts of our proposed performance modelling methodology and several steps of providing a performance model are described. The proposed performance modelling methodology includes three steps of modelling to create a final performance model of a given application and platform. In the first step, we model the application which must be mapped to the target platform. The created model at this step includes a chain of tasks representing different processing and also the data transmissions in the platform. In the second step, we model the architecture of the target platform as a set of units to represent different processors and also the communication part of the platform. At the end of the second step, the created model includes several tasks that represent the architecture of the processing or data transmission. At the third modelling step, we consider another unit in the model which is responsible for managing or synchronizing the tasks execution on different units.