#### UNIVERSITÉ DE MONTRÉAL

# CHARACTERIZATION OF INTEGRATED MOS CIRCUITS UNDER VOLTAGE STRESS AND APPLICATION TO POWER CONVERSION CHAINS OF ELECTRONIC IMPLANTS

Seyed Saeid HASHEMI AGHCHEH BODY

DÉPARTEMENT DE GÉNIE ÉLECTRIQUE

ÉCOLE POLYTECHNIQUE DE MONTRÉAL

MÉMOIRE PRÉSENTÉ EN VUE DE L'OBTENTION DU

DIPLÔME DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (M.Sc.A)

(GÉNIE ÉLECTRIQUE)

Janvier 2004

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-90870-4 Our file Notre référence ISBN: 0-612-90870-4

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

exclusive permettant à la

Bibliothèque nationale du Canada de

reproduire, prêter, distribuer ou

vendre des copies de cette thèse sous

la forme de microfiche/film, de

reproduction sur papier ou sur format

électronique.

L'auteur a accordé une licence non

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manguant.

# Canadä

## UNIVERSITÉ DE MONTRÉAL

#### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Ce mémoire intitulé:

# CHARACTERIZATION OF INTEGRATED MOS CIRCUITS UNDER VOLTAGE STRESS AND APPLICATION TO POWER CONVERSION CHAINS OF ELECTRONIC IMPLANTS

présenté par: <u>HASHEMI AGHCHEH BODY Seyed Saeid</u>

en vue de l'obtention du diplôme de <u>Maîtrise ès sciences appliquées</u>

a été dûment accepté par le jury d'examen constitué de:

M. MARTEL Sylvain Ph.D., président

M. <u>SAWAN Mohamad</u> Ph.D., directeur de recherche

M. <u>SAVARIA Yvon</u> Ph.D., co-directeur de recherche

M. <u>DESJARDINS Patrick</u> Ph.D., membre

To whom we are waiting for,

To my father and mother,

To my wife and children,

### Acknowledgements

It has been my great pleasure to study in the Electrical Engineering Department at Ecole Polytechnique de Montreal working in GRM and PolyStim labs. This experience gave me a great chance for having wide and deep expertise in Microelectronic Engineering. My strong faith in God and in myself have remained constantly high enough to carry this work to the end.

First and foremost, I would like to express my gratitude to my supervisor, Professor Mohammad SAWAN, not only for his guidance, patience and for the freedoms he has granted me throughout my years of study.

I would also like to thank my co-supervisor, Professor Yvon SAVARIA. His many years of experience has allowed me to focus on the critical and interesting issues of all the problems encountered. The results of this research would not have been of the same quality without him pushing the design goals and test strategies always higher and higher.

I would like to thank the members of my thesis committee for their valuable feedback and contribution. I would like to acknowledge my family for their solid support of all my endeavors and their contribution in removing most of stresses from my student life.

I also wish to thank all fellow students, technicians and staff of PolyStim and GRM, in

particular Christian FAYOMI, Jonathan COULOMB, Yamu HU, Jean-Francois GERVAIS, Kamal EL-SANKARY, Jean-Luc TREPANIER, Moncef DJEBBI, Claudine OULETTE, Ghislaine ETHIER CARRIER, Rejan LEPAGE, Alex VESSY, Martin PARE for their help, support, encouragement and friendly discussions. I am very honored to be part of their family. Thanks to Robert CHEBLI, Abdallah KASSEM, Virginie SIMARD and specially, Annie TREPANIER for the French translation of the abstract and condensé en français.

Lastly, but not the least, I would like to thank the Canadian Microelectronic Corporation (CMC) for fabricating the test chip and NSERC for their financial support.

To all of you, thank you so much for all the support you have given to me during this research. Find through the above lines the expression of my heart and gratitude for all you have done for me.

#### Résumé

Les nouvelles technologies submicroniques améliorent la performance et l'efficacité des circuits intégrés. Cependant, ces technologies peuvent apporter quelques limitations pour certaines applications. Par exemple, ces technologies ont une tension nominale inférieure à la tension d'alimentation. D'autre part, les applications biomédicales spécifiques exigent des tensions plus élevée que celle de la nouvelle technologie submicronique. Utiliser les technologies pures CMOS qui supportent des tensions élevées ou employer des approches hybrides, où des technologies à haute et basse tension sont combinées, sont les solutions possibles. Le développement d'une chaîne de conversion de puissance ainsi qu'un circuit amplificateur de tension ont été étudiés dans ce mémoire. La fiabilité du dispositif dans des conditions de stress a été également couverte, constituant un élément important.

Il a été démontré que l'architecture d'un PCC est sujette à quelques contraintes et limitations qui influencent fortement son efficacité globale. Aussi, il est clair que l'intégration complète de l'implant pourrait améliorer sa performance d'une manière significative, mais elle impose également des issues de fiabilité. L'architecture de PCC conventionnelle a été caractérisée en termes d'efficacité de puissance. Deux nouvelles architectures ont été proposes, remplaçant les redresseurs de diode par des redresseurs synchrones intelligents, ce qui a presque doublé l'efficacité de la puissance relative et a aussi facilité l'intégration de EI.

De plus, les blocs fonctionnels de base et les caractéristiques d'un doubleur de tension ont été présentés. Il a été souligné que celui-ci souffre de la chute de tension d'une diode ou de la tension de seuil d'un commutateur MOS. Aussi, la structure d'une étape de multiplicateur de tension à rendement élevé a été introduit. Par après, la structure classique d'un multiplicateur à plusieurs étages de tension utilisant simplement des étages cascadés a été présentée. Il produit un facteur de multiplication proportionnel au nombre d'étage. En conclusion, une nouvelle structure améliorant le facteur de multiplication de façon exponentielle a été rapportée. Les résultats de simulation pour un multiplicateur simple et un multiplicateur de tension de plusieurs étages à rendement élevé ont été présentés et le résultat des paramètres de conception ont été caractérisés. Il a été prouvé que les soucis de fiabilité exigent l'utilisation de techniques de multiplication de tension d'efficacité inférieure.

Les résultats expérimentaux de la puce fabriquée ont été développés afin de caractériser les mécanismes de panne CMOS. Les résultats prouvent que le transistor MOS sera sujet à des problèmes de fiabilité lorsque des conditions de stress sont appliquées à ses bornes. Il est possible que les processus MOS ne puissent pas soutenir des tensions beaucoup plus hautes que la tension d'alimentation nominale. Lorsqu'on a besoin de telles tensions, des processus développés afin de les supporter devraient être utilisées.

#### **Abstract**

New sub-micron technologies improve the performance and efficiency of the integrated circuits. Taking advantages may bring some limitations in certain applications. For instance, these technologies have lower nominal power supply voltage. On the other hand, specific biomedical applications require voltages higher than the nominal power supply voltage of new sub-micron technologies. Using either pure CMOS technologies that support high voltages or using hybrid approaches, where low and high voltage technologies are combined are possible solutions. The development of power conversion chain and voltage boosting circuit were studied in this thesis. The device reliability under stress condition was also covered as a major concern.

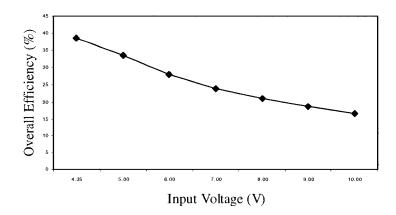

It was shown that the architecture of a PCC is subject to a few constraints and limitations that heavily impact its overall efficiency. It was also clarified that integrating the whole implant could improve its performance significantly, but it also imposes reliability issues. The conventional PCCs architecture was characterized in terms of power efficiency. Two new architectures were proposed that replace diode rectifiers with Smart Synchronous Rectifiers, and almost double the relative overall power efficiency and facilitate EI integration.

Moreover, the basic building blocks and characteristics of a voltage doubler were introduced. It was outlined that it suffers from forward voltage drop of a diode or

threshold voltage of a MOS switch. Then, the structure of a high efficiency voltage multiplier stage was introduced. Later, the classical structure of a multi-stage voltage multiplier using simply cascaded stages was presented. It provides a linear multiplication factor with the number of stages. Finally, a new structure that improves the multiplication factor exponentially was introduced. The result of simulation for a single and multiple stage high efficiency voltage multiplier were presented and the result of design parameter were characterized. It is shown that reliability concerns could result in using the voltage multiplication techniques of lower efficiency.

Experimental results from fabricated chips developed to characterized CMOS breakdown mechanisms. The results prove that the MOS transistor will be subjected to reliability problem when the stress conditions are applied to their terminals. MOS processes may not be able to support voltages much higher than the nominal supply voltage. When such voltages are needed, processes developed to support them should be used.

## Condensé en français

#### I. Introduction

Obtenir l'énergie nécessaire afin d'alimenter un implant électronique (EI) est un défi de mise en oeuvre significatif. Les systèmes de stimulation employant l'alimentation percutanée ou des batteries incorporées ne sont pas idéaux pour un fonctionnement sécuritaire à long terme. Pour les applications à long terme, les tendances récentes favorisent des liaisons RF inductives [10,64,159]. Cependant, des considérations biologiques imposent des limites sur la puissance maximale transférée à travers la peau [11].

#### II. Chaîne de conversion de puissance pour implants électroniques

La configuration d'une Chaîne de Conversion de puissance efficace (PCC) pour alimenter le EI est fortement désirable. De plus, les nouvelles technologies submicroniques sont très avantageuses pour l'intégration des implants électroniques.

# II.1 Contraintes et limitations des Simulateurs Electriques Fonctionnels (FES)à canaux multiples

Il y a plusieurs contraintes et limitations derrière les paramètres impliqués dans une application requérant un stimulateur à canaux multiples FES. Cette section énonce les

principales contraintes identifiées.

#### II.1.a Variation dans le courant de charge

La puissance consommée par un EI se répartit entre celle consommée par le coeur du EI et celle requise par le générateur de stimulus. Avec l'évolution de la technologie, la puissance requise pour faire fonctionner le coeur est faible et décroissante, tandis que la puissance nécessaire pour stimuler un secteur sensible est fixe, alors que le nombre de sites de stimulation a tendance à augmenter avec les besoins de l'application. La deuxième composante a donc tendance à dominer les exigences en puissance. De plus, la stimulation efficace exige une quantité de charge minimale pour être injectée dans le tissu. Cette quantité diffère pour les divers tissus et elle varie aussi d'un site de stimulation à un autre.

#### II.1.b Variation dans la tension de charge

L'aire de Contact d'Electrode-Tissu efficace (ETC) pour passer le courant de stimulation varie d'un site à un autre. Par conséquent l'impédance des canaux varie. Dans un tel cas, la production de courant de stimulation exige des tensions plus hautes que la tension d'alimentation nominale des nouvelles technologies.

#### II.1.c Variation de la tension d'entrée

Pour un EI donné (alimenté de façon transdermique), la valeur de la puissance reçue est affectée par la distance et l'orientation relative de l'émetteur et de l'EI. Ainsi, on s'attend à des variations considérables sur le signal d'entrée pour une certaine période de temps. Pour préserver une efficacité acceptable, il est essentiel d'ajuster la puissance transmise. Ceci impose l'emploi d'une rétroaction ou d'un redresseur intelligent pour réguler la puissance transmise.

#### II.1.d Défi associées à la conception du circuit

Comme les tensions d'alimentation sont réduites, l'efficacité des multiplieurs de tension se dégrade significativement. Donc, des techniques de conception de circuits complexes sont exigées pour surmonter ces problèmes [36,61,115,152,158,195,213]. L'intégration complète du EI pourrait améliorer considérablement ses performances, mais cela impose aussi quelques problèmes de fiabilité à long terme [99].

#### **II.2** Architecture de PCC conventionnelle

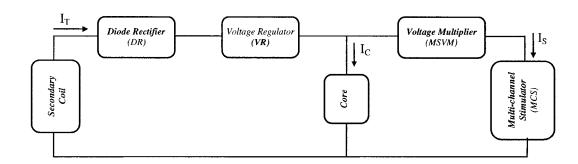

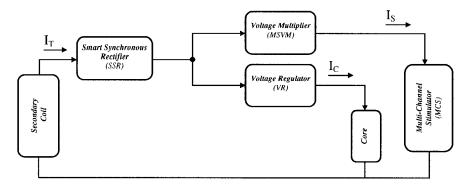

Une architecture conventionnelle de PCC se compose d'un redresseur à diode (DR) et d'un régulateur de tension (VR), en série avec la charge qui inclut un MCS aussi bien que le coeur de l'implant, comme illustré à la Figure 2.1. Un MSVM est inséré pour générer les hauts voltages demandés pour la stimulation. L'atténuation de tension inhérente à la polarisation directe de la diode (Vγ) résulte en une perte de puissance significative à

travers le (DR). Ceci affecte l'efficacité de la PCC et diminue la tension livrée aux modules suivants. Cet impact négatif devient de plus en plus significatif dans la conception des alimentations à basse tension. C'est notamment le cas pour les nouvelles technologies submicroniques. En plus, le DR est généralement mis en oeuvre en employant des diodes discrètes, ce qui va à l'encontre de l'objectif d'intégrer complètement l'EI.

### II.3 Redresseur Intelligent Synchrone (SSR)

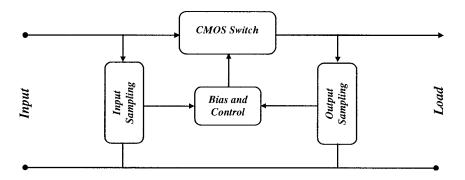

Dans la structure des redresseurs classiques, on ne peut rien faire pour éviter la chute de tension des diodes. Les diodes Schottky, qui ont des chutes plus faibles, ne sont pas disponibles sous la forme de composants discrets à basse tension. L'utilisation de SSR [135,144] ouvre de nouvelles possibilités, en ce qui concerne l'architecture des PCCs. Cela est possible parce que la perte de la puissance dans de tels composants est reliée à la chute ohmique dans les transistors MOS. Si les paramètres de conception sont attribués de telle sorte que l'atténuation à travers le SSR soit beaucoup plus basse que celle d'une diode, alors il en résulterait une amélioration significative de l'efficacité. Un autre avantage du SSR est d'éliminer des diodes externes, ce qui est un pas vers un EI entièrement intégré. Un diagramme bloc simplifié d'un tel dispositif est illustré à la Figure 2.3. Notons que la réalisation du comparateur approprié avec un taux adéquat de sur-échantillonnage peut être un défi.

#### II.4 Nouvelle Architecture PCC basée sur SSR

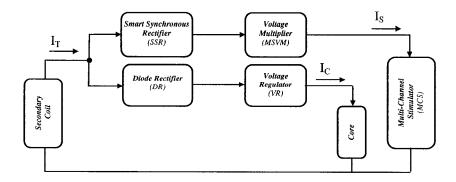

Une nouvelle architecture PCC est obtenue en insérant un SSR à l'étage d'entrée du MSVM, comme illustré à la Figure 2.4. Avec cette architecture, l'efficacité en puissance est améliorée et la prise de l'entrée du SSR directement au lieu de l'entrée du DR fournit une haute tension au MSVM. Ceci permet de réduire le nombre d'étages dans le convertisseur de tension et donc d'obtenir des modules de multiplication de tension plus efficaces.

La seconde architecture proposée combine les deux chemins de distribution de la puissance et les alimente avec un seul SSR, comme illustré à la Figure 2.5. L'avantage de cette architecture n'est pas tant l'amélioration de l'efficacité de la PCC, mais bien l'élimination du DR, qui est généralement réalisée par des diodes hors puce.

Les résultats de l'analyse mathématique sont récapitulés aux Tableaux 5.3 et 5.4. L'analyse de l'efficacité est effectuée en utilisant les suppositions et les paramètres de circuit fournis au Tableau 5.1, ainsi que le courant et les équations de puissance du Tableau 5.2. Donc, l'utilisation des architectures proposées réduit la puissance requise pour des implants électroniques et augmente significativement leur efficacité globale.

#### III. Multiplieur de tension à haute efficacité

Les tensions d'alimentation requises pour des circuits analogiques sont souvent dictées

par des sources de signal externes. De plus, la charge nécessite parfois des tensions plus grandes que la tension d'alimentation. Une alimentation à basse tension impose des contraintes sévères dans la conception de circuits. Compte tenu de la réduction des tensions nominales d'alimentation des technologies submicroniques, les facteurs de multiplication requis pour produire une tension donnée sont croissants.

Il existe deux circuits conventionnels, le régulateur à commutation et le convertisseur basé sur la pompe de charge. Ces circuits peuvent produire des tensions plus hautes que la tension d'alimentation. Les circuits à pompe de charge utilisent des capacités comme dispositifs d'emmagasinage d'énergie, tandis que les régulateurs à commutation utilisent des inductances ou des transformateurs comme dispositifs d'emmagasinage d'énergie.

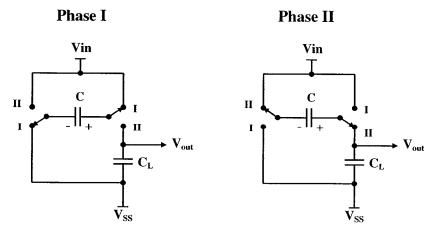

#### III.1 Pompe de charge

Les pompes de charge sont des circuits pouvant pomper la charge vers le haut pour produire des tensions supérieures à la tension d'alimentation régulière. Ils comportent des condensateurs, commutateurs et au moins une horloge à deux phases. Comme les pompes de charge n'utilisent aucun composant magnétique, il est plus facile de les implémenter dans une seule puce. Un circuit de pompe de charge typique est illustré à la Figure 3.1. Le circuit est organisé de façon à ce que dans une première phase, la capacité soit chargée à l'alimentation. Quand l'horloge est basculée, la capacité maintient la charge de la phase précédente et donc, la somme de l'alimentation et de l'amplitude d'horloge est induite sur

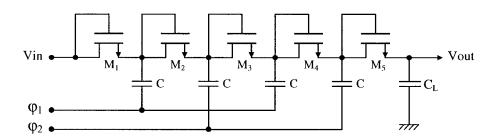

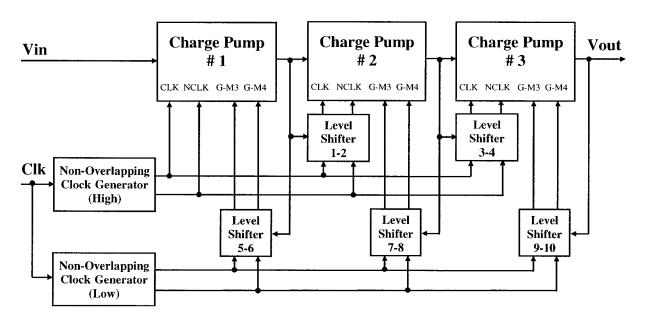

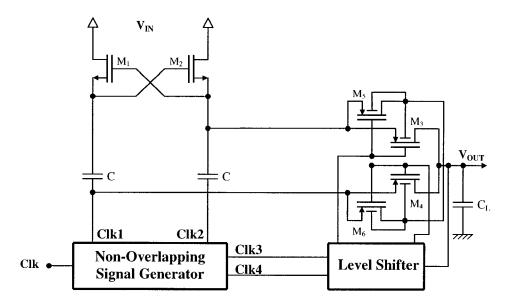

son autre borne. Une pompe de charge réalisée en technologie CMOS est présentée à la Figure 3.6.

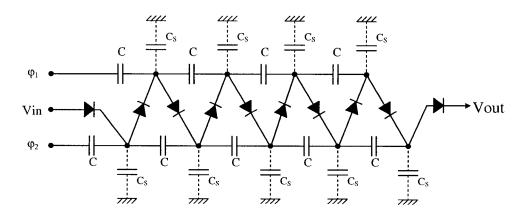

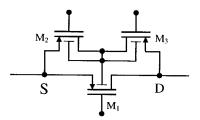

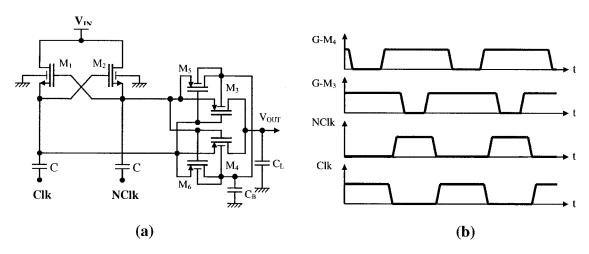

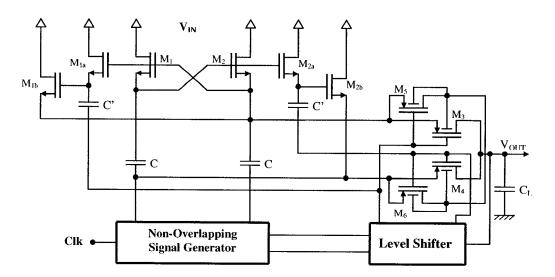

Une structure de pompe de charge a été proposée par Dickson (Figure 3.3) [48]. Ce circuit comporte deux transistors NMOS croisés, couplés avec des capacités de pompe de charge et deux horloges d'entrée ayant des phases inversées. Afin d'avoir un meilleur transfert de charge, un chemin unidirectionnel est établi au travers de commutateurs PMOS séries qui ne sont pas contraints par la tension de seuil. La conception a été améliorée récemment en utilisant des commutateurs de transfert de charge statiques et dynamiques (Figures 3.4 et 3.5) [213] et des techniques de commutation du puit (Figure 3.7) [138]. Une vue d'ensemble d'un étage de multiplication de tension est présentée à la Figure 3.8a.

#### III.2 Caractéristiques du Multiplicateur de tension

Les caractéristiques d'un multiplicateur de tension, incluant l'efficacité de la puissance, le courant de sortie, les ondulations de sortie et le gain de tension ont été étudiées. Dans cette étude, la résistance des commutateurs est ignorée. Le courant de sortie peut être exprimé par l'équation (3.3). En pratique, les tailles des condensateurs de la pompe de charge sont considérées comme étant les paramètres de conception dominants.

La pompe de charge produit de grandes oscillations en sortie. Dans la structure d'un étage d'une pompe de charge, la tension d'oscillation peut être exprimée par l'équation

(3.4). D'après (3.4), la tension d'oscillation peut être considérablement réduite en augmentant la fréquence des horloges, en changeant les paramètres des transistors ou en utilisant une grande capacité de sortie. Dans l'état stable, on s'attend à ce que la tension d'entrée soit augmentée par l'amplitude du signal d'horloge provenant des étages subséquents, comme exprimé dans l'équation (3.5). Cependant, considérant l'effet des capacités parasites dans le circuit, le gain de tension pourrait être exprimé par l'équation (3.8).

#### III.3 Amélioration de l'efficacité de puissance

Les capacités parasites, les horloges sans recouvrement, un court temps de charge et décharge, la résistance entre les bornes des capacités, les pertes statiques et dynamiques dans les commutateurs, l'injection de charge et les courants de fuite peuvent tous affecter l'efficacité de puissance des multiplicateurs de tension.

Pour obtenir une meilleure efficacité de puissance, il existe une valeur optimale pour la largeur des commutateurs MOS utilisés dans la pompe de charge. Cependant, en raison de l'impossibilité d'effectuer des changements dynamiques sur la largeur des transistors sur puce, un transistor assez large ayant une fréquence de commutation élevée doit être choisi afin de garantir les niveaux de tension de sortie pour une charge maximale.

Une pompe de charge efficace nécessite de grandes capacités. La valeur des capacités est cependant limitée par les contraintes d'intégration. Ainsi il est critique de minimiser le nombre et la valeur des condensateurs. De plus, le chevauchement des périodes des signaux d'horloge appliqués aux commutateurs de transfert de charge doit être évité. Ceci nécessite d'utiliser une horloge sans recouvrement (Figure 3.8b).

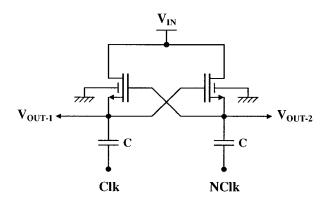

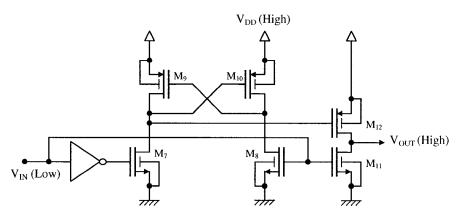

Une grande amélioration de la conductance des commutateurs de transfert de charge est obtenue si nous utilisons un décalage de niveau pour augmenter l'amplitude des signaux de grille, comme illustré dans la Figure 3.9. Cette solution pourrait aussi augmenter la dissipation de puissance. Pour les basses tensions d'entrée, une basse tension  $V_{\rm eff}$  peut dégrader l'efficacité en puissance et la fonctionnalité complète du VM. L'efficacité peut cependant être améliorée en utilisant une pompe de charge auxiliaire qui consiste en une pompe de charge supplémentaire tel qu'illustrée à la Figure 3.10 [61].

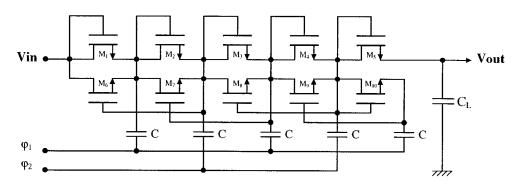

#### III.4 Multiplicateur de tension à plusieurs étages

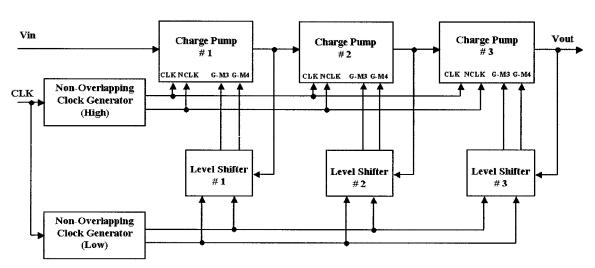

Le multiplicateur de tension classique à plusieurs étages utilise des étages de multiplication en cascade, comme illustré à la Figure 3.11. Un signal d'horloge commun alimente tous les modules de la chaîne. Ici, la tension de sortie est linéairement proportionnelle au signal d'horloge.

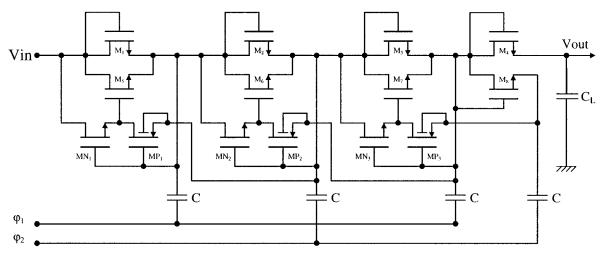

Une nouvelle architecture MSVM a l'avantage d'utiliser la sortie de chaque étage comme tension d'alimentation par l'étage suivant, comme illustré à la Figure 3.12. Pour un multiplicateur de tension de N étages, la tension de sortie peut alors augmenter exponentiellement comme le montre l'équation (3.14). Ce qui est remarquable avec cette

structure originale c'est que la croissance exponentielle est obtenue sans que le nombre de phases requises n'augmente avec le nombre d'étages.

#### IV Limites de tension des technologies submicroniques

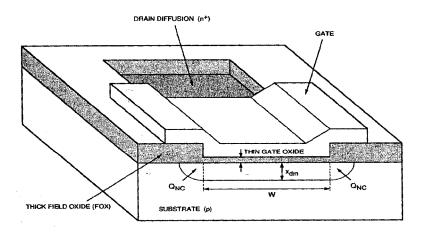

Comme les dimensions des dispositifs sont réduites, l'influence des régions périphériques du canal, c'est-à-dire la source, le drain et les structures d'isolation deviennent significatives. Les caractéristiques des dispositifs de petites dimensions ne sont donc qu'approximativement égales a celles des dispositifs de grandes dimension.

#### IV.1 Effet de canal court

L'annexe A présente une étude détaillée des effets de canal court et des manières de les gérer. Les effets d'une telle diminution de dimensions sont des changements de la tension de seuil, un manque de fiabilité des oxydes, des couches supplémentaires pour former les drain/source et puit, l'augmentation de résistance de sortie, la modulation de la longueur de canal, la dégradation de la mobilité des porteurs, la saturation de la vitesse des porteurs, la distribution aléatoire des dopants, ainsi que des délais d'intercommunication. De plus, la réduction de la longueur de canal mène à une augmentation indésirable de la résistance de la ligne de la grille.

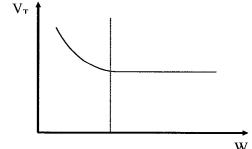

#### IV.2 Canal à effet étroit

La largeur du canal a aussi un impact significatif sur les caractéristiques des MOS à faible dimension. Pour des canaux étroits, la charge latérale devient comparable avec la charge directement au-dessous de la grille.

#### IV.3 Effets des porteurs

Lorsque les dimensions du dispositif et la tension d'alimentation ne sont pas ajustées proportionnellement, le résultat est un champ électrique latéral croissant près du drain. Ce grand champ électrique latéral pousse les porteurs à emmagasiner suffisamment d'énergie pour surmonter la barrière d'interface SiO<sub>2</sub>-Si, ce qui par la suite produit des pièges et peut injecter des électrons et des trous dans l'oxyde. Ceci endommage graduellement l'oxyde. Ces dommages peuvent aboutir à un changement des caractéristiques courant tension des MOS (Annexe B).

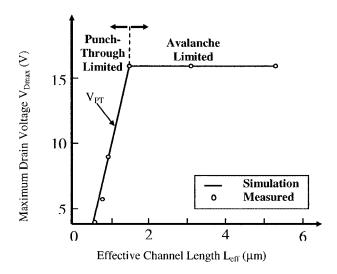

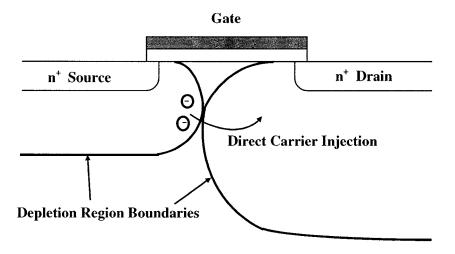

#### IV.4 Phénomène de Punch-through

Le punch-through est un mécanisme non destructif qui peut arriver quand l'épaisseur des couches de déplétion pour les jonctions de la source et du drain sont comparables avec la longueur du canal. Ainsi, quand la tension de drain augmente, les régions de déplétion des jonctions P-N de la source et du drain peuvent se toucher. En conséquence, un courant de fuite significatif peut circuler du drain vers la source à travers le substrat. Ce courant est alors mal contrôlé par la grille, parce qu'il n'est plus contraint au canal en

surface. La tension de punch-through inclut aussi la tension nécessaire pour surmonter la barrière Source-Substrat.

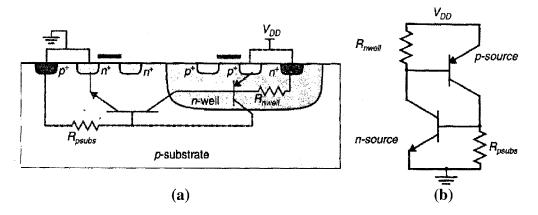

La polarisation du substrat a aussi tendance à supprimer le punch-through en augmentant la hauteur de la barrière initiale autour de la jonction de la source. La tension de punch-through pour une jonction brusque peut être exprimée selon l'équation (4.13). Notez que pour un procédé à puit n, le punch-through peut arriver pour des dispositifs parasites latéraux et verticaux.

#### IV.5 Tensions de claquage

Les dispositifs MOS soumis à un stress de tension sont sujets à différents mécanismes de claquage. Ces mécanismes peuvent impliquer le canal, la jonction et le claquage de l'oxyde. Ces phénomènes peuvent être destructifs ou non destructifs. Le claquage du canal par avalanche arrive quand le dispositif est actif et qu'un champ électrique excessif existe dans le canal. Cela produit des électrons non thermalités qui provoquent un processus d'ionisation menant à la multiplication par avalanche. Ainsi, une augmentation rapide du courant de drain, qui devient indépendant de la tension de la grille, sera observée.

Lorsqu'une jonction est polarisée en inverse, le potentiel à travers les semi-conducteurs augmente tout comme la largeur de la couche de déplétion. La tension maximale de polarisation inverse est limitée par la tension de claquage qui est caractérisée par

l'augmentation rapide du courant en polarisation inverse. Deux mécanismes peuvent causer le claquage, notamment la multiplication par avalanche et l'effet tunnel.

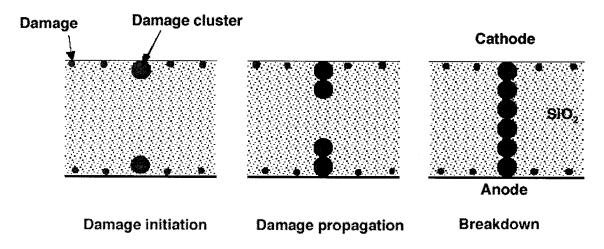

Le claquage de l'oxyde est une dégradation progressive et continue du volume et de l'interface de l'oxyde, suivie par la destruction finale du diélectrique. En conséquence, le claquage est un phénomène local avec un caractère statistique qui dépend de la densité des défauts déjà présents ou pouvant être produits lors du stress de l'oxyde. Sous un grand champ électrique, les dégâts s'introduisent à l'anode et la cathode et s'étendent finalement partout dans le corps du film d'oxyde selon un modèle non uniforme. Quand un nombre critique de défauts est atteint, un chemin conducteur est formé à travers l'oxyde et le claquage de l'oxyde est déclenché [175]. L'annexe C explique le mécanisme de claquage de l'oxyde et de la grille, ainsi que les modèles associés.

#### V Résultats expérimentaux

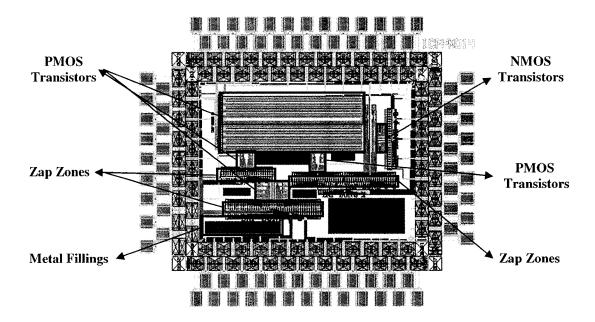

Une puce prototype a été conçue et fabriquée en utilisant la technologie CMOS 0.18 µm à puit n de la TSMC. Cette puce contient des transistors PMOS et NMOS de différentes tailles fabriqués en utilisant les diverses règles disponibles. Tous les transistors, même ceux de très grandes tailles, ont été faits comme des dispositifs monolithiques. Un zone de garde dans le puit n a été utilisé pour chaque transistor, servant comme anneau de garde. Un double anneau de plots a été utilisé afin d'économiser la superficie du dé, tout en ayant un accès individuel à autant de terminaux que possible. Le dessin des masques a

été fait manuellement sous l'outil Virtuoso de Cadence. Afin d'obtenir des résultats fiables en mesurant un nombre limité d'échantillons, un protocole systématique a été appliqué.

Nos mesures confirment que la distribution de porteurs dans le canal, dépendant des paramètres du procède et de la différence de potentiel entre la grille et le substrat, a un impact significatif sur les caractéristiques du dispositif. Nous avons découvert que la structure d'essai a un impact remarquable sur l'exactitude et la validité des résultats de mesure.

Pour quelques mesures, nous avons examiné quelques configurations possibles. Il a été trouvé que le claquage de l'oxyde de grille est indépendant de la géométrie du dispositif, tandis que le claquage entre les gilles est fortement dépendant de la surface du canal. Il a aussi été trouvé que le claquage de l'oxyde sur les côtés du drain et de la source survient à des tensions inférieures à celles mesurées à la surface du canal.

En raison des contraintes des puces multi projet, le nombre de dispositifs disponibles n'était pas suffisant pour conduire des essais de fiabilité. L'impact de facteurs comme le temps et la température sur la durée de vie des dispositifs, ainsi que l'usure, n'ont pas été examinés. Finalement, nos résultats montrent que par des techniques de conception circuit appropriées, des dispositifs MOS pourraient fonctionner à des niveaux de tension jusqu'à deux fois plus grands que la tension d'alimentation nominale du procédé.

# **List of Contents**

| Dedication      | iv                                              |

|-----------------|-------------------------------------------------|

| Acknowledgen    | nentsv                                          |

| Résumé          | vii                                             |

| Abstract        | ix                                              |

| Condensé en fi  | ançaisxi                                        |

| List of Figures | xxix                                            |

| List of Tables. | xxxii                                           |

| List of Abbrev  | iationsxxxiii                                   |

| List of Symbol  | s xxxv                                          |

| List of Append  | lixesxxxv                                       |

| List of Conten  | tsxxv                                           |

| Chapter 1       | Introduction 1                                  |

| 1.1             | Motivation                                      |

| 1.2             | Research goals                                  |

| 1.3             | Thesis outline                                  |

| Chapter 2       | Power conversion chain for electronic implant 6 |

| 2.1             | Implant power-up techniques                     |

| 2.2             | Constraints and limitations                     |

| 2.2.1           | Variation in load current                       |

| 2.2.2           | Variation in load voltage                       |

| 2.2.3           | Variation in input voltage                      |

| 2.2.4           | Circuit design concerns                         |

| 2.3             | Conventional PCC's architecture                 |

| 2.4             | Smart Synchronous Rectifier                     |

| 2.4.1           | Synchronous rectifiers                          |

| 2.4.2           | Smart synchronous rectifiers                    |

| 2.4.3           | MOS implementation for SSR                      |

| 2.4.4           | New implementation for SSR                      |

| 2.5       | Smart synchronous rectifier versus classical diode rectifier | 19 |

|-----------|--------------------------------------------------------------|----|

| 2.6       | New PCC architectures based on SSR                           | 20 |

| 2.6.1     | Distributed topology                                         | 21 |

| 2.6.2     | Monolithic topology                                          | 23 |

| 2.7       | Summary                                                      | 23 |

| Chapter 3 | High-efficiency voltage multiplier                           | 25 |

| 3.1       | Introduction                                                 | 25 |

| 3.2       | Charge pump                                                  | 26 |

| 3.2.1     | Concept and characteristics                                  | 27 |

| 3.2.2     | Charge pump types                                            | 29 |

| 3.3       | Single-stage voltage multiplier                              | 34 |

| 3.3.1     | MOS-based charge pump                                        | 34 |

| 3.3.2     | Charge transfer module                                       | 35 |

| 3.3.3     | Complete scheme                                              | 36 |

| 3.4       | Voltage multiplier characteristics                           | 37 |

| 3.4.1     | Output current                                               | 38 |

| 3.4.2     | Output ripples                                               | 39 |

| 3.4.3     | Voltage gain                                                 | 39 |

| 3.5       | Power efficiency improvement                                 | 40 |

| 3.5.1     | Switching frequency                                          | 41 |

| 3.5.2     | Integrated capacitor                                         | 41 |

| 3.5.3     | Non-overlapping clock                                        | 42 |

| 3.6       | Low-voltage application                                      | 45 |

| 3.7       | Multi-stage voltage multiplier                               | 46 |

| 3.7.1     | New architecture                                             | 48 |

| 3.8       | Summary                                                      | 49 |

| Chapter 4 | Reliability challenges of CMOS under sub-micron regime       | 51 |

| 4.1       | Short channel effects                                        | 51 |

| 4.2       | Narrow-channel effects                                       | 52 |

| 4.3       | Subthreshold and leakage currents                     | 54  |

|-----------|-------------------------------------------------------|-----|

| 4.3.1     | Subthreshold current                                  | 54  |

| 4.3.2     | Junction leakages                                     | 55  |

| 4.3.3     | Gate leakage current                                  | 56  |

| 4.3.4     | Latch-up                                              | 57  |

| 4.4       | Hot carriers effects                                  | 59  |

| 4.5       | Punch-through                                         | 60  |

| 4.5.1     | Punch-through voltage and current                     | 63  |

| 4.5.2     | Punch-through improvement techniques                  | 65  |

| 4.6       | Breakdown voltages                                    | 65  |

| 4.6.1     | Channel avalanche breakdown                           | 65  |

| 4.6.2     | Junction breakdown                                    | 66  |

| 4.6.3     | Dielectric breakdown                                  | 67  |

| 4.7       | Stress-induced measurement techniques                 | 73  |

| 4.8       | Summary                                               | 74  |

| Chapter 5 | Quantitative, simulation and measurement results      | 76  |

| 5.1       | Quantitative results for power conversion chains      | 76  |

| 5.2       | Simulation results for multi-stage voltage multiplier | 80  |

| 5.2.1     | Impact of charge pump capacitors                      | 81  |

| 5.2.2     | Impact of clock frequency                             | 82  |

| 5.2.3     | Impact of transistors dimensions                      | 84  |

| 5.2.4     | Impact of clock overlapping                           | 84  |

| 5.2.5     | Multi-stage voltage multiplier                        | 85  |

| 5.3       | Voltage limits; Experimental results                  | 86  |

| 5.3.1     | Test protocol                                         | 87  |

| 5.3.2     | Test structures                                       | 90  |

| 5.3.3     | Prototype chip                                        | 108 |

| 5.4       | Summary                                               | 111 |

| Chapter 6  | Conclusions                | 113 |

|------------|----------------------------|-----|

| 6.1        | Summary and discussion     | 113 |

| 6.2        | Directions for future work | 110 |

| References |                            | 119 |

# **List of Figures**

| Figure 2.1: Block diagram of a conventional PCC                               | 14 |

|-------------------------------------------------------------------------------|----|

| Figure 2.2: Smart Synchronous Rectifier (Half-Wave)                           |    |

| Figure 2.3: A simple block diagram for a SSR                                  |    |

| Figure 2.4: The scheme of a distributed PCC                                   |    |

| Figure 2.5: Block diagram of a monolithic PCC                                 |    |

| Figure 3.1: Charge Pump General Overview                                      | 27 |

| Figure 3.2: Cockcroft and Watson Charge Pump                                  | 29 |

| Figure 3.3 : Dickson Charge Pump                                              | 30 |

| Figure 3.4 : Charge pump using Static CTSs                                    | 32 |

| Figure 3.5 : Charge pump using Dynamic CTSs                                   | 33 |

| Figure 3.6 : MOS Implemented Charge Pump                                      | 34 |

| Figure 3.7: Dynamic Gate Biasing                                              | 30 |

| Figure 3.8: Classical Single Stage Charge Pump                                | 37 |

| Figure 3.9: Schematic of a level shifter                                      | 44 |

| Figure 3.10: High Efficiency Voltage Multiplier for Low Voltage Applications  | 45 |

| Figure 3.11 : Classical topology for a Multi-Stage Voltage Multiplier         | 40 |

| Figure 3.12: The scheme of an improved MSVM                                   | 48 |

| Figure 4.1: Narrow channel effect                                             | 52 |

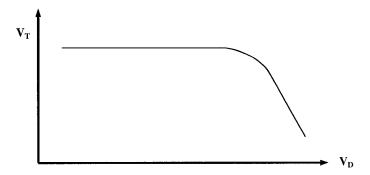

| Figure 4.2 : Threshold voltage variation versus channel width                 | 53 |

| Figure 4.3: CMOS device cross-section and parasitics responsible for latch-up | 58 |

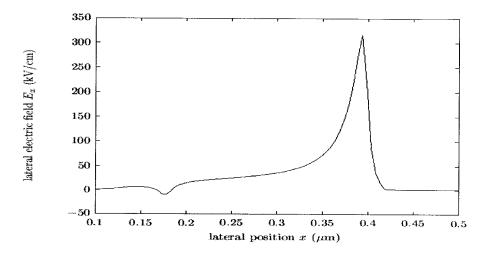

| Figure 4.4: Lateral electric field in saturation region                       | 59 |

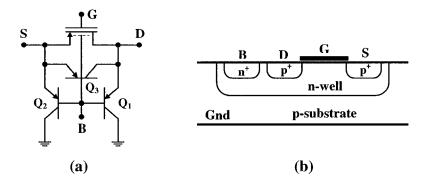

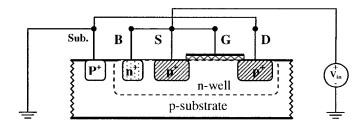

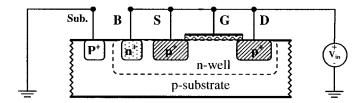

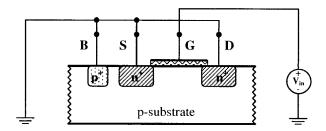

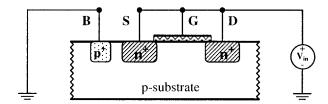

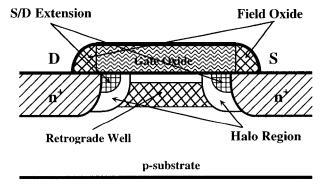

| Figure 4.5: PMOS transistor cross-section and parasitics                      | 60 |

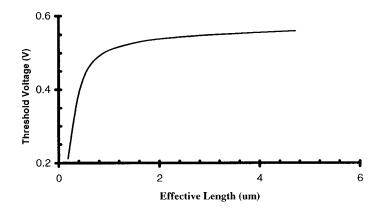

| Figure 4.6: Logarithmic plot of V <sub>Dmax</sub> versus L <sub>eff</sub>     | 61 |

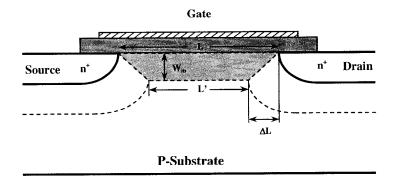

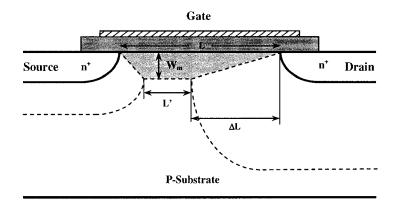

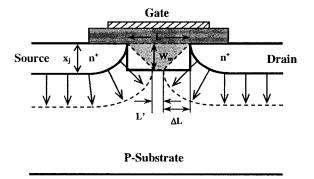

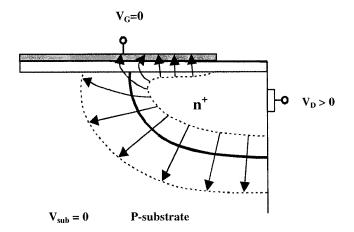

| Figure 4.7 : Illustration of Punch-through                                    | 62 |

| Figure 4.8 : Visualization of oxide breakdown failure                         | 69 |

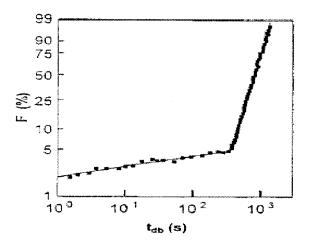

| Figure 4.9: Typical Weibull plot of the time to breakdown for MOS canacitors  | 70 |

| Figure 5.1: Power efficiency vs input voltage for the 2-stage conventional architecture. 79          |

|------------------------------------------------------------------------------------------------------|

| Figure 5.2: The schematic of a single stage voltage doubler                                          |

| Figure 5.3: Output voltage vs charge pump capacitor size                                             |

| Figure 5.4: Characteristics of the single stage charge pump vs clock frequency                       |

| Figure 5.5: Power efficiency versus the charge pump switch width                                     |

| Figure 5.6: 5-Stage Conventional Voltage Multiplier                                                  |

| Figure 5.7: The output voltage of 5-stage voltage multiplier                                         |

| Figure 5.8: Measurement procedure flow chart                                                         |

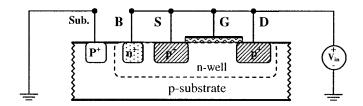

| Figure 5.9: Cross-section of PMOS transistor and relative parasitics                                 |

| Figure 5.10: The cross-section and schematic of ESDR protection                                      |

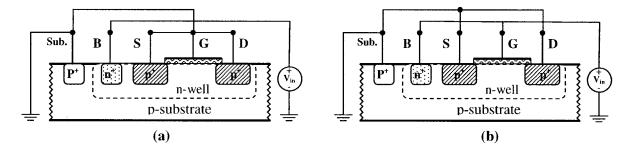

| Figure 5.11: Different setups for $P_{sub}$ - $N_{diff}$ junction reverse breakdown                  |

| Figure 5.12: Test setup for P <sub>sub</sub> -N <sub>well</sub> junction reverse breakdown voltage   |

| Figure 5.13: Test setup for $N_{\text{well}}$ - $P_{\text{diff}}$ junction reverse breakdown voltage |

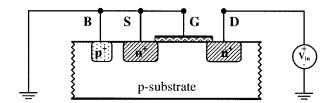

| Figure 5.14: Test setup for lateral punch-through voltage in NMOS                                    |

| Figure 5.15: Test setup for lateral punch-through voltage in PMOS                                    |

| Figure 5.16: Test setup for vertical punch-through voltage in PMOS 100                               |

| Figure 5.17: Test setup for gate oxide breakdown (edge) in NMOS                                      |

| Figure 5.18: Test setup for gate oxide breakdown (surface) in NMOS 104                               |

| Figure 5.19: Test setup for gate oxide breakdown (surface) in PMOS 100                               |

| Figure 5.20: The view of the prototype chip                                                          |

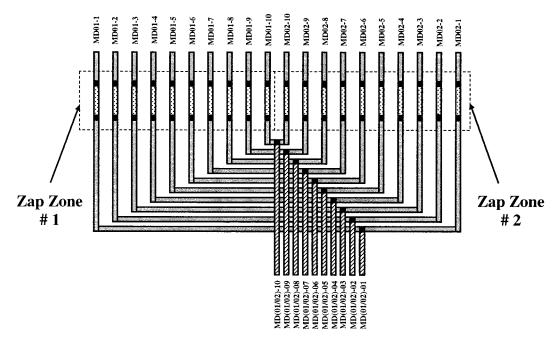

| Figure 5.21: The specimen schematic of the zap zones                                                 |

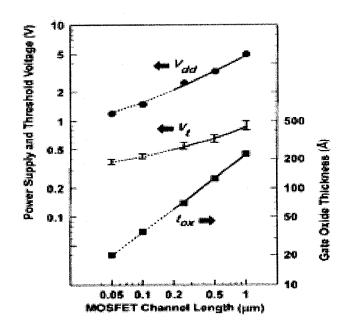

| Figure A- 1: Plot of $V_{DD}$ , $V_{T}$ and $t_{OX}$ trends versus L for MOS technologies            |

| Figure A-2: Charge-sharing effect for short-channel devices                                          |

| Figure A-3: Depletion layer with a large drain bias                                                  |

| Figure A-4: Drain currents for short- and long-channel devices                                       |

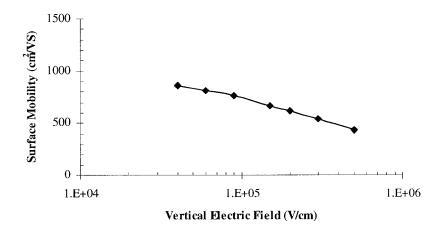

| Figure A-5: Surface mobility degradation versus electric field                                       |

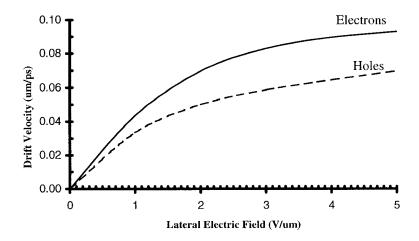

| Figure A-6: Drift Velocity versus Electric Field                                                     |

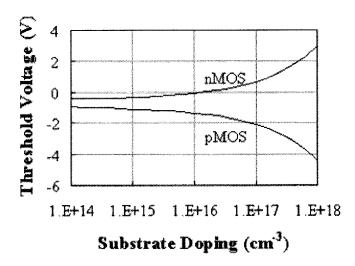

| Figure A-7: Threshold voltage versus substrate doping density                                        |

| Figure A-8: Threshold voltage-related short-channel effect                                           |

| Figure A-9: Threshold dependence on the channel length                     | 161 |

|----------------------------------------------------------------------------|-----|

| Figure A-10: Well Engineering representation                               | 162 |

| Figure A-11: Threshold dependence on drain voltage                         | 164 |

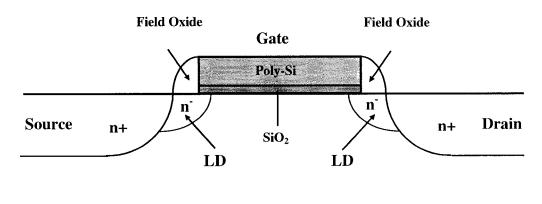

| Figure A-12: Cross-section of Lightly Doped Drain profile                  | 165 |

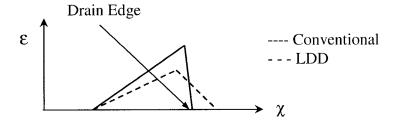

| Figure B-1: The electric field in vicinity of Drain                        | 170 |

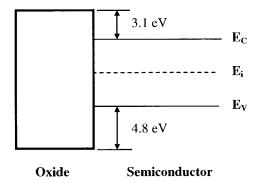

| Figure B-2: The energy Diagram showing barrier heights                     | 170 |

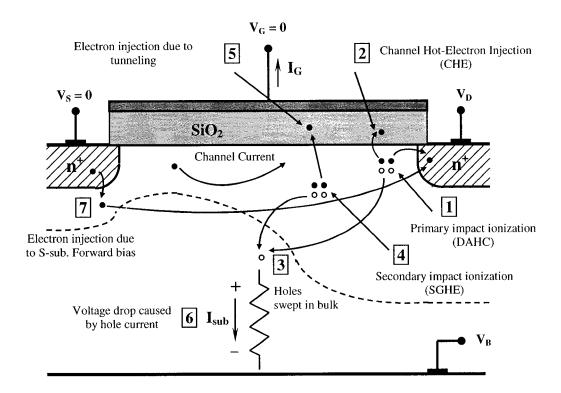

| Figure B-3: Visualization of carrier multiplication in NMOS                | 172 |

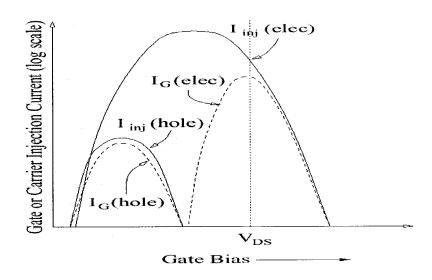

| Figure B-4: Quantitative comparison between HCI mechanisms in NMOS         | 173 |

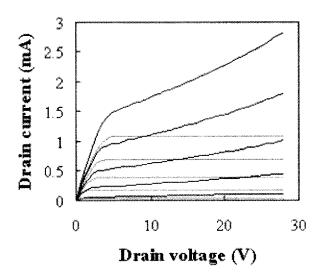

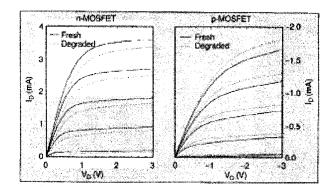

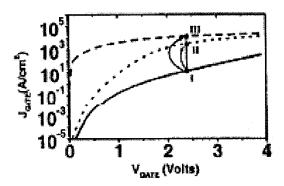

| Figure B-5: I-V characteristics for fresh and degraded MOS                 | 175 |

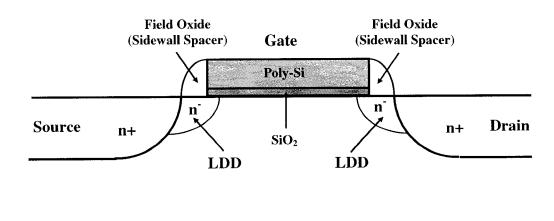

| Figure B-6: The LDD structure cross section                                | 179 |

| Figure B-7: Electric field distribution in conventional and LDD structures | 180 |

| Figure C-1: Plot of I-V characteristics for soft and hard breakdowns       | 184 |

# **List of Tables**

| Table 4.1: The specifications of electrical stress methods                                       |

|--------------------------------------------------------------------------------------------------|

| Table 5.1: The assumption and circuit parameters for analytical study                            |

| Table 5.2: Input current and power equations for various PCC architectures                       |

| Table 5.3: Required voltage and current for PCC architectures                                    |

| Table 5.4: Power and efficiency of various PCC architectures                                     |

| Table 5.5: ESDR Reverse Breakdown Voltage                                                        |

| Table 5.6: The $P_{sub}$ - $N_{diff}$ reverse breakdown vs channel length for different setups 9 |

| Table 5.7: The P <sub>sub</sub> -N <sub>well</sub> reverse breakdown voltage vs channel length   |

| Table 5.8: The N <sub>well</sub> -P <sub>diff</sub> reverse breakdown voltage vs channel length  |

| Table 5.9: Measured voltages in lateral punch-through setup for PMOS 10                          |

| Table 5.10: Oxide breakdown voltage for NMOS vs channel length                                   |

| Table 5.11: The test structures of oxide breakdown for PMOS                                      |

| Table 5.12: The gate oxide breakdown (surface) vs channel length for NMOS                        |

| Table 5.13: Oxide breakdown voltage (surface) for PMOSs                                          |

#### **List of Abbreviations**

AM Amplitude Modulation

ASK Amplitude Shift Keying

BD Breakdown

BJT Bipolar Junction Transistor

CDF Cumulative Distribution Function

CHE Channel Hot-Electron

CTS Charge Transfer Switch

DAHC Drain Avalanche Hot-Carrier

DC Direct Current

DIBL Drain-Induced Barrier Lowering

DR Diode Rectifier

EDT Edge Direct Tunneling

EI Electronic Implant

ESD Electro-Static Discharge

ESDR Electro-Static Discharge with Resistor

ETC Electrode-Tissue Contact

FES Functional Electrical Stimulation

HBD Hard Breakdown

HCI Hot-Carrier Induced

IC Integrated Circuit

LDD Lightly Doped Drain

MCS Multi-Channel Stimulator

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MSVM Multi-Stage Voltage Multiplier

NTS Neutral Trapping Site

NMOS N-channel Metal Oxide Semiconductor

PCC Power Conversion Chain

PPMOS P-channel Metal Oxide Semiconductor

RF Radio Frequency

SBD Soft Breakdown

SCR Silicon-Controlled Rectifier

SDE Source-Drain Extension

SGHE Secondary Generated Hot-Electron

SHE Substrate Hot-Electron

SOI Silicon On Insulator

SR Synchronous Rectifier

SSR Smart Synchronous Rectifier

TDDB Time Dependent Dielectric Breakdown

VLSI Very Large Scale Integration

VM Voltage Multiplier

VR Voltage Regulator

#### **List of Symbols**

\_\_\_\_\_\_

α Charge pump capacitance to stray capacitance ratio

β Shape parameter in Weibull distribution function

γ Body-effect constant of MOSFET

$\mu_{eff}$  Effective carrier mobility

μn Electron mobility

μs Carrier mobility at surface

$\mu_0$  Low-field carrier mobility

λ Channel length modulation parameter

η Scale parameter in Weibull distribution function

$\eta_{MSVM}$  Power efficiency of MSVM

$\eta_{Overall}$  Overall power efficiency of PCC

$\eta_{VR}$  Power efficiency of VR

$\varepsilon_{\rm S}$  Semiconductor permittivity

φ<sub>F</sub> Built-in Fermi potential

a impurity gradient

A<sub>i</sub> Junction area

C Charge pump capacitance

C' Auxiliary charge pump capacitance

C<sub>g</sub> Gate capacitance

C<sub>OUT</sub> Output capacitance

C<sub>OX</sub> Gate oxide capacitance per unit area

C<sub>S</sub> Stray capacitance

E<sub>bd</sub> Electric field to breakdown

E<sub>C</sub> Critical electrical field

E<sub>g</sub> Difference in energy between conduction and valance bands

E<sub>L</sub> Energy consumed by load

E<sub>m</sub> Peak lateral electric field

E<sub>OX</sub> Electrical field across gate oxide

E<sub>S</sub> Energy delivered by source

f Switching frequency

F(x) Cumulative failure rate function

F<sub>S</sub> Charge sharing factor

gds Source-drain small-signal Conductance of MOSFET

I<sub>FN</sub> Fowler-Nordheim tunneling current

I<sub>lk</sub> Leakage current

I<sub>OUT</sub> Output current

k Boltzmann's Constant

Effective lateral electric field length

L Channel length of MOSFET

L<sub>eff</sub> Effective channel length of MOSFET

n Junction shape factor

n<sub>i</sub> Intrinsic concentration of carriers in undoped silicon

N Number of cascaded stages of MSVM

N<sub>A</sub> Doping concentration in Channel

N<sub>B</sub> Background doping of lightly doped side of P-N junction

N<sub>C</sub> Density of states in conduction band

$N_{diff}$  N-type diffusion region

N<sub>OX</sub> Effective ion density of charge trapped in thin oxide

N<sub>V</sub> Density of sates in valance band

N<sub>well</sub> N-type well region

N<sub>Sub</sub> Substrate doping concentration of MOSFET

P<sub>Core</sub> Required power for Core

P-type diffusion region

P<sub>DRO</sub> Power loss of diode rectifier

P<sub>I</sub> Input power to PCC

P<sub>MCS</sub> Required power for MCS

P<sub>sub</sub> P-type substrate region

q Electron charge

Q<sub>bd</sub> Charge to breakdown

Q<sub>Ch</sub> Transferred charges by charge pump

r<sub>ds</sub> Output resistance of MOSFET

R<sub>L</sub> Load resistance

R<sub>ON</sub> Dynamic resistance of MOSFET

R<sub>S</sub> Source resistance

S Subthreshold slope

t<sub>bd</sub> Time to breakdown

t<sub>OX</sub> Gate oxide thickness

T Absolute temperature

v<sub>max</sub> Maximum drift velocity

$V_{\gamma}$  Diode forward-bias voltage drop

V<sub>bi</sub> Built-in voltage across junction

V<sub>eff</sub> Effective gate-to-source voltage of MOSFET

V<sub>BD</sub> Breakdown voltage

V<sub>Dmax</sub> Maximum drain voltage

V<sub>DD</sub> Positive power supply voltage

V<sub>DRO</sub> Output voltage of diode rectifier

V<sub>DS</sub> Drain-to-source voltage of MOSFET

V<sub>GS</sub> Gate-to-source voltage of MOSFET

V<sub>MSVMI</sub> Input voltage to MSVM

V<sub>MSVMO</sub> Output voltage of MSVM

V<sub>OX</sub> Voltage across the gate oxide

V<sub>PT</sub> Punch-through voltage of MOSFET

V<sub>R</sub> Ripple voltage

V<sub>SB</sub> Source-to-bulk voltage of MOSFET

V<sub>SS</sub> Negative power supply voltage

V<sub>SSRO</sub> Output voltage of SSR

V<sub>T</sub> Threshold voltage of MOSFET

V<sub>TO</sub> Threshold voltage shift

W Channel width of MOSFET

W<sub>m</sub> Depletion layer depth

X<sub>d</sub> Thickness of the depletion region

$X_{dm}$  Depletion depth in channel of MOSFET

$X_{j}$  Junction depth

# **List of Appendixes**

| Appendix A | 149 |

|------------|-----|

| Appendix B | 169 |

| Appendix C | 182 |

# Chapter 1

# Introduction

#### 1.1 Motivation

Since the first implantable pacemaker, exciting progress has been made in the development of a variety of implantable devices that address many different illnesses. For example, cardiac pacemakers, cochlear implants, bladder controllers, bone growth systems and nerve stimulators of various kinds have been demonstrated and have steadily improved over time. An entire industry has been created, providing meaningful employment to thousands of scientists, engineers, businessmen, and workers. Hundreds of thousands of lives have been saved by these devices, and the quality and duration of life has improved for many patients [69]. For instance, the first practical external pacemaker was invented in 1952 [218]. Such a device was approximately the size of a table radio of the time and was powered by electrical connection to 110 VAC line voltage. The treatment was painful and damaged the skin. Later, a hand-held external device was developed [106]. It was battery operated and used myocardial leads, eliminating the pain and burning associated to the ancient device.

With the advent of the transistor, the possibility of building a totally implantable device came true and the first experimental implantable pacemaker was placed in an animal [68]. This led to the first successful human implant [27]. The early units used discrete

components. They were powered by a battery and encapsulated in an epoxy compound. Many problems needed to be addressed in those early years. One area that required much research concerned the electrode materials and attaching them to the organ or nerve. The most serious remaining drawbacks and limitations to implant longevity and reliability was the power source. The first batteries were suffering from hydrogen gas generation, relatively quick self-discharge, low energy density and, failure due to the penetration of the separator by dendrites [69]. A rechargeable pacemaker was next developed using a transcutaneous recharging technology and two-way telemetry [62].

The past two decades saw further significant improvements in implant technology. The development of the printed circuit board, hybrid circuitry, and electronic microchips made possible the design of very small implants with an amazing array of features. Programmability, the ability to record various clinical parameters from inside human body and the use of telemetry to access the state of stimulation sites and broadcasting them back to the clinicians as well as multi-channel stimulation are some very common features of today implants. The future appears even more exciting, with the prospect of implantable devices and prostheses aiding in the recovery of body functions and the improvement in quality of life, as well as the saving of lives [69]. Although new submicron CMOS technologies provide higher performance in terms of higher speed, lower power consumption and reduced area, they also suffer from lower nominal supply voltage. For some applications, such as biomedical, the need for a given high supply voltage calls for techniques to boost supply voltage. This requirement sometimes crosses

the process reliability limits.

Hence, the solution might be using either hybrid processes, where combinations of different technologies are possible or, develop design methods such that the circuit functions within the limits of conventional CMOS technologies. The former calls for costly processes, while the latter necessitates circuit elements such as voltage boosters. The second option that produce circuits operating at voltage higher than nominal value raise questions with respect to reliability. The use of new technologies could also be beneficial if it allows producing fully integrated implants while having higher degree of power efficiency. It is worthy to notice that the increase in power efficiency is not only an issue at device level, but also an issue for further study at system and architecture level.

# 1.2 Research goals

The multiple goals of this work are related to the development of high efficiency multistage voltage multiplier capable of boosting an input voltage (from 1 V to 10 V) and of delivering it at the output terminal in an efficient manner. The design targets full integration and must provide a basis for reliable long term and safe application to implantable biostimulators.

#### 1.3 Thesis outline

The development of high efficiency power conversion chains for an electronic biomedical implant shall be the subject of this work. The said chain is using multi-stage voltage multiplier modules realized in CMOS technology. The presentation in this research will be organized according to three distinct levels of hierarchy. The first of the three shall be an investigation at the system level of power conversion chain architecture where a conventional structure is examined and new architectures will be proposed. The second shall be an investigation at a circuit level, where the design of a high efficiency multi-stage voltage multiplier and associated circuitries will be developed. The third shall be an investigation at a device level, where MOS transistors are characterized under stress condition.

Following this outline, Chapter 2 will describe the architecture of the power conversion chain for biomedical implants. The impact of architecture on the overall power efficiency will be examined and the theoretical background describing the efficiency for a conventional structure will be provided. New architectures based on synchronous rectifiers will also be developed. They can result in efficiency improvements and facilitate integration.

Chapter 3 will describe the structure and implementation of a single-stage voltage doubler realized in CMOS  $0.35~\mu m$  process. The impact of circuit parameters on the overall efficiency will be represented. The structure of a multi-stage voltage multiplier

will then be investigated and a new architecture will be introduced. It leads to a significant improvement in the overall voltage boosting factor.

Chapter 4 addresses the major mechanisms involved that influence MOS transistors characteristics under voltage stress. The fundamental electronic physics issues will be presented and the effect of hot carrier, short channel effects and breakdown phenomenon will be explained.

Chapter 5 presents the quantitative results of our study over different power conversion chain architectures, and simulations of multi-stage voltage multipliers. Finally, the strategies and the test structures used in order to characterize the MOS transistors from different type, size and terminal arrangements under voltage stress will be addressed, and some of the capabilities and limitations of these setups will be demonstrated. Device operation will be described, and a discussion of measured values and possible hypothesis with respect to breakdown nodes will be formulated and analyzed. The specifications of an implemented prototype chip will also be provided at the end of this chapter.

As a result of this work, the impact of architecture, circuit elements and design parameters will have been thoroughly investigated, and the characteristics of MOS technologies under voltage stress condition for new sub-micron processes will have been addressed. The final chapter shall provide conclusions that can be drawn from this work. We will also discuss some future directions for circuit design in CMOS technology.

# Chapter 2

# Power conversion chain for electronic implant

During the past two decades, sensors and stimulators operating inside the body have generated a lot of interest to monitor human organs behavior and/or to recuperate their functional activities. Advances in microelectronics have led to the development of powerful miniaturized devices, among them we find various implantable artificial organs, sensors, and Functional Electrical Stimulators (FES). These devices have recently been intensively used in many disease circumstances such as cardiac pacemakers, cochlear implants and bladder controllers. Despite the success in designing such devices, feeding them with a reliable and efficient power source remains one of the main issues that slows down progress towards building suitable miniaturized systems.

# 2.1 Implant power-up techniques

Procuring required energy to power up an Electronic Implant (EI) in an efficient way is a significant implementation challenge. Numerous alternatives are available for supplying power to EIs. In early implementations, power was delivered to the implants by wires passing through skin [106,218]. Hard-wired (percutaneous) stimulation systems are now considered obsolete, because they often cause infection at the points where wires break the skin, risking the safety of the patient. They also impose limitations to free movements, which increase the chance of lead wire failure [58,103,156]. In fact, these

factors remain the major drawbacks of this method, even after developing better understanding of basic electrochemistry of electrode/body interactions, further advances in electrode technology and development of alternate encapsulant materials, and refinements in electrode terminations in order to achieve better attachment of the electrode to the tissue [69].

A second approach to feed power to an EI is to include embedded batteries that are not ideal power sources for long-term use [27,62,91]. Indeed, their limited lifetime and stored energy requires frequent replacement or recharging, and their considerable size in comparison with active devices are main concerns limiting their use. Their chemical stability and probable current leakage also pose hazards for safety of live tissues and reliability of electronics. The remaining alternatives are based on wireless techniques that have none of the above listed limitations. They allow patient mobility and reduce risk of infection. Nowadays, most implant designs favor Radio-Frequency (RF) inductive links where an electromagnetic RF signal is used to transmit data and power to the implant [10,64,159]. The required energy is provided by an external and high efficiency source. The majority of available prosthetic power supplies are based on Amplitude Modulation (AM) transmission. The collected high-frequency signal (carrier) is rectified to power up the EI.

Using RF inductive link techniques, the EI lifetime is no longer limited by the stored energy, but rather by the implant electronics and body reaction. It also keeps the risk of

skin damage at a very low level and makes it possible to have bi-directional communication and energy transfer simultaneously. However, this technique lacks some characteristics such as high-energy-transfer efficiency and wide bandwidth. It also suffers from transversal, orthogonal, and other inductance alignments [57]. In fact, even though these modern power transmission techniques could provide fairly large power, biological considerations for long-term human safety impose a limit of 10 mW/cm<sup>2</sup> for the maximum power of transmitted RF signal through the skin [11].

In order to remove some of these restrictions, other transcutaneous power transmission techniques have been proposed. For instance, a transcutaneous optical power converter has been recently introduced. It consists of solar cells receiving light from an external light source [181]. The light source could be either a halogen-lamp- or a laser-diode-illustrating skin surface. This technique does not give the expected performances but is still employed in very restricted cases.

Therefore, configuring a high efficiency Power Conversion Chain (PCC) to feed EIs remains an area of interest. Also the need for integrating both power and stimulation circuitries on a single chip is increasingly desirable.

### 2.2 Constraints and limitations

Ideally, a PCC captures all the power received at its input terminals and delivers it to the load located at its output terminals. Its power efficiency is defined as the ratio of the

output to the input powers. Indeed, a part of the input power is dissipated in the circuit, because no existing circuit has ideal characteristics. This part deals with characterizing and optimizing that efficiency and therefore, accounts for the parameters which may affect it. There are several constraints and limitations behind the parameters involved in a multi-channel FES application that are described in the following sections.

#### 2.2.1 Variation in load current

The power consumed by an implant splits in two parts, the core and the load. The implant core includes all devices needed for biasing, control, generation of complex stimuli, and testing issues. A major load of an implant is its stimuli generator. With technology evolution, the power required to operate the core is small and decreasing, while the power to stimulate a sensitive area is fixed and the number of stimulation sites tends to grow with the sophistication of the implant. The second component tends to dominate power requirements.

FESs are generally Multi-Channel Stimulators (MCSs). For instance, a recently proposed cortical stimulator comprises a matrix of 4 modules stimulating 8 channels each, to stimulate 1024 possible sites [191]. That many channels are required for effective cortical stimulation. The maximum load current grows in proportion with the number of channels, and the average current grows with the number of stimulated sites.

Effective stimulation requires some minimal charge transfer (threshold charge per phase) to be injected in the tissue, which differs for various tissues and changes from a stimulation site to another. For instance, in the case of cortical stimulation, this threshold is reported to be 15 nC at a frequency of 250 Hz [86,148]. This charge is injected by the current flowing through the contacts during the stimulation phase and is proportional to the said current and the stimulation period. To perform a multi-channel stimulation at a sufficiently fast rate (>50 Hz), the commonly used stimulation current is as low as  $10 \,\mu\text{A}$  per channel [185].

In the case of cortical stimulation, the stimulation sites may present different interfacing conditions. Contacts are also known to age non-homogenously, as they gradually get surrounded by encapsulating tissues. Thus, in order to obtain the required stimulation efficiency, an increase of stimulation currents to values as high as  $100~\mu A$  may be required [185]. Therefore, the need for a wide range of stimulation currents is predictable. For instance, assuming a 25-channel stimulator, the current may vary from 0.25~mA to 2.5~mA.

#### 2.2.2 Variation in load voltage

The effective Electrode-Tissue Contact (ETC) area for passing the stimulation current varies from one site to another, which results in different effective impedances of the stimulation channels [86]. Contact aging makes this even worse. To our knowledge, the equivalent retina tissue impedance was found to be on the order of  $10 \text{ k}\Omega$  [86], while this

value is  $100 \text{ k}\Omega$  for cortex stimulations [148]. Therefore, to produce the specified range of stimulation currents, in the worst case, the required voltage is as high as 6 V for retina stimulation, and about 10 V for cortical stimulation. Always supplying stimulation current from a power supply set to the highest required voltage in worst case conditions can become very inefficient, since the voltage not needed by the load is simply dissipated in the transistor driving it. This leads to considering innovative solutions such as dynamic power supply adjustment and voltage multiplication discussed in chapter 3.

#### 2.2.3 Variation in input voltage

For a given power transmitted through skin, the value of the received power is affected by the distance and relative orientation of the remote transmitter and the implant. Moreover, taking advantage of modulation techniques such as ASK to transmit data and power simultaneously may cause significant variations in the magnitude of transmitted RF signals. Therefore, we can expect to have considerable input signal variations over time. Since the load part is independent from the feed part, the PCC must be configured to receive adequate power during its operation. To keep the overall PCC efficiency in a high enough range, it is essential to adjust the transmitted power, which imposes employing a feedback path. Therefore, in absence of highly effective feedback adjusting transmitted power, the power conversion chain can become fairly inefficient. Indeed, excess power will simply be dissipated in the implant. An analysis of this phenomenon is presented in the following.

### 2.2.4 Circuit design concerns

As supply voltages are scaled down, the efficiency of charge pumps – used in voltage multiplier modules - are severely degraded due to threshold voltage drop of pass transistors, and the voltage gain of pumping stages closer to the output is further degraded by the body-effect of MOS transistors. Therefore, complex circuit design techniques are required to overcome these problems. Several authors have investigated the design of body-effect-free, high performance, and low voltage charge pump based circuits [36,61,115,152,158,195,213].

Moreover, the required range of stimulation currents and observed load impedance per channel dictate adopting a highly flexible power conversion chain architecture. The stated requirements can be met by employing an adaptive Multi-Stage Voltage Multiplier (MSVM) module, composed of a few upward DC-DC voltage converters as its basic building block. The number of stages could be fixed, based on the specific input voltage, while the maximum output voltage is determined by the required maximum voltage across the various ETCs.

Finally, integrating the whole implant could improve its performance a great deal and may facilitate its connection to the tissue, but it also imposes some limitations and challenges. Among them, using voltages higher than the nominal values supported by the technology may greatly accelerate aging phenomena such as Hot Carrier Induced (HCI), which affect MOS characteristics and cause degradations in transconductance, a shift in

the threshold voltage, and a decrease in the drain current carrying capability and undesirable junction and oxide breakdowns. This leads to long term device reliability problems [99]. The significant challenges posed by higher than nominal supply voltages will be treated later on.

### 2.3 Conventional PCC's architecture

The architecture of the power conversion chain in an electronic implant has a strong impact on its performance, efficiency and reliability when designed to meet the safety limitations for human body. The proper architecture for an electronic implant must also be flexible enough to meet the design main goals. In order of importance, the main goals are: (1) To drive the high impedance of tissue stimulation and/or monitoring sites, (2) To provide biologically safe power transmission, (3) To handle simultaneous multi-channel stimulation, (4) To facilitate the stimulator integration on a single die and, (5) To provide high power efficiency. In the framework of deep sub-micron technologies, the nominal supply voltage is reducing to even less than 1 V, while FES applications still require higher voltages. Therefore, there is a demand for a voltage boosting module that can deliver high voltage to the MCS. Such a module should also be capable of adaptive output selection in order to provide adequate voltage in proportion with stimuli generator voltage requirements.

The conventional architecture of a PCC is shown in Figure 2.1. It consists of a diode rectifier (DR) and a voltage regulator (VR), in series with the load, which includes a

MCS as well as the core of the implant. Here, a Multi-Stage Voltage Multiplier (MSVM) module is inserted. The number of stages in a MSVM is adjusted so that it could generate the highest voltage required for stimulation [5, 84,168].

Figure 2.1: Block diagram of a conventional PCC

Considering the limited efficiency of the MSVM, VR and DR, a lot of power will be dissipated in the PCC. Recall that power consumption within the DR is proportional to the product of its inherent forward-bias voltage drop  $(V\gamma)$  and the forward current. The typical value for  $V\gamma$  of a silicon diode is about 700 mV. Assuming  $V_I$  and  $I_T$  as input voltage and current to the secondary coil, power loss  $(P_{DRO})$  and output voltage  $(V_{DRO})$  of the DR is calculated with equation (2.1).

$$P_{DRO} = V_{DRO} \times I_{T}$$

$$V_{DRO} = V_{I} - 0.7$$

(2.1)

Where

According to this equation, constant voltage drop across the DR results in a significant power loss. It affects the overall power efficiency of PCC and decreases the delivered voltage to the following modules. This equation also implicitly assumes the efficiency is controlled by the peak voltages seen before the rectifier.

In this topology, the current and required input power are determined by the following equations:

$$I_{T} = \left(\frac{I_{S}}{\eta_{MSVM}} \times \frac{V_{MSVMO}}{V_{MSVMI}}\right) + I_{C}$$

(2.2)

$$P_{I} = \left(\frac{P_{MCS}}{\eta_{MSVM} \times \eta_{VR}} + \frac{P_{Core}}{\eta_{VR}}\right) + V_{\gamma} \times I_{T}$$

(2.3)

Where  $\eta_{MSVM}$ ,  $\eta_{VR}$ ,  $P_{MCS}$ ,  $V_{MSVMO}$ ,  $V_{MSVMI}$  and  $P_{Core}$ , are the power efficiency of MSVM and VR, required power for MCS, output and input voltage of MSVM and required power for core, respectively.

New sub-micron integrated circuit technologies require low supply voltages, which are not much larger than the drop of a DR. Therefore, the voltage drop and power consumption related to a DR is a first order consideration. Besides, DR is commonly implemented by using discrete off-chip diodes, which goes against the objective of a fully integrated implant. Moreover, the significant constant voltage drop across DR requires multiple voltage multiplier stages in MSVM, which also results in lower overall power efficiency.

# 2.4 Smart Synchronous Rectifier

#### 2.4.1 Synchronous rectifiers

In low DC output voltage PCCs, it is quite difficult to achieve high power efficiencies

due to the power loss in the diode rectifiers. Thus, substituting those devices with other rectifiers that have lower voltage drop would be significant. Schottky diodes that exhibit lower drops are not available at low power as discrete components [18]. Currently, the most effective way to solve this problem is to use Synchronous Rectifiers (SR). Recent studies have confirmed that using SR is quite advantageous in comparison with Schottky diodes [19].

The concept of SR was introduced for amplitude detection applications [144], and was improved for high speed and high precision applications [135,164]. A synchronous rectifier is an active device that is driven ON when the applied voltage would normally cause diode conduction, and turned OFF when a reverse voltage is applied. However, SRs are not constrained by the diode constant voltage drop. Their use opens up new possibilities with respect to the architecture of PCCs. Power loss in SRs is composed of the switching and conduction losses of the active device. In case of MOSFET transistors, switching losses are proportional to gate parasitic capacitances, the square of gate voltage and switching frequency, while conduction loss is the product of the square of the instantaneous current by the R<sub>ON</sub>. Considering the application related low switching frequency, and parasitic capacitances for new sub-micron integrated circuit technologies, one can ignore switching loss in comparison with conduction loss. Technically, SRs were grouped into three categories, namely the self-driven SRs, the externally driven SRs and the smart SRs. Among them, the last one has the best performance on timing precision and system simplicity. In externally-driven versions, the gate-drive signals for SRs are

synchronized with the signals of the primary side. Self-driven SRs, unlike the latter, are driven by the voltage derived directly from the secondary winding. A smart SR is self-driven and behaves like a diode according to its external bias conditions [105,136].

### 2.4.2 Smart synchronous rectifiers

A Smart Synchronous Rectifier combines the behavior of a SR with the possibility of controlling the conduction angle of the said device. Recall that MOSFET transistors perform as voltage-controlled current sources. Thus, they can be used as rectifiers if suitable control voltage pulses are applied to their gate terminal.

### 2.4.3 MOS implementation for SSR

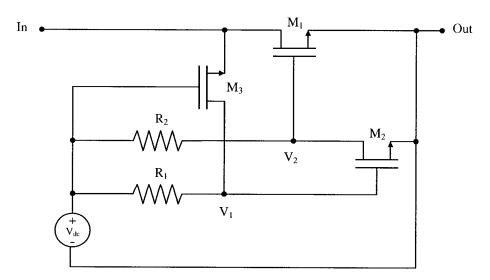

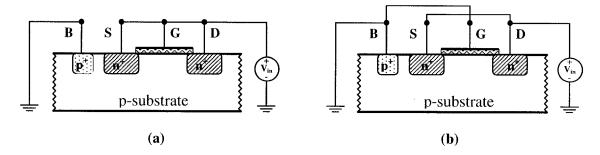

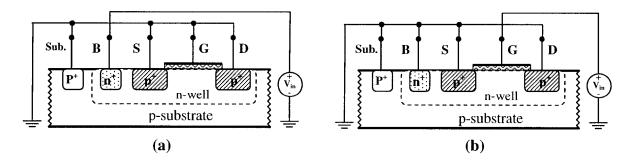

A MOS-based implementation for the SSR is presented in Figure 2.2, where all MOS transistors are N-channels [105,136].

**Figure 2.2:** Smart Synchronous Rectifier (Half-Wave)

The transistor  $M_1$  is the main transistor for current conduction towards the load, while  $M_2$  and  $M_3$  are parts of its control circuitry. The circuit functions as a half-wave rectifier and therefore has two modes of operation: blocking and conducting.

#### • Blocking mode $(V_{DS1} > 0)$ :

One can easily obtain equation (2.4) as the essential condition for  $M_3$  to conduct.

$$V_{GS3} = V_{dc} - V_{DS1} > V_{T3}$$

(2.4)

Therefore, if  $V_{dc}$  is set equal to  $V_{T3}$ , implies that any positive  $V_{DS1}$  will make  $M_3$  turned off. Node  $V_1$  will have a voltage close to  $V_{dc}$  ( $V_{dc} \ge V_{T2}$ ) and  $M_2$  is turned on. When this happens,  $M_1$  gate voltage will be pulled down to a very low level and,  $M_1$  is not turned on. In this case, the circuit is blocking the current path from input to output terminal.

#### • Conducting mode $(V_{DS1} < 0)$ :

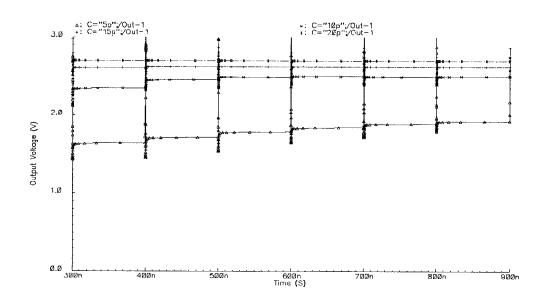

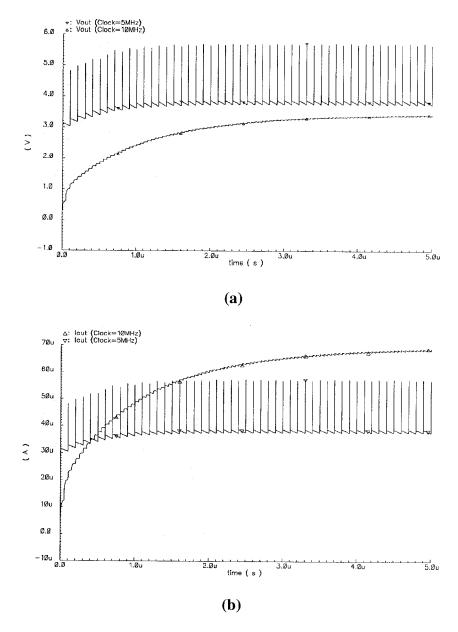

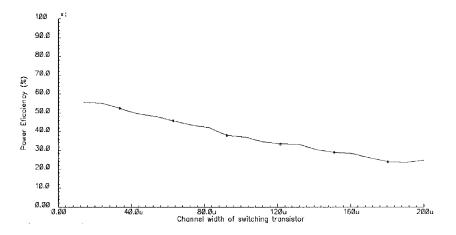

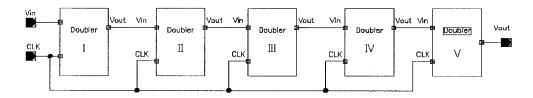

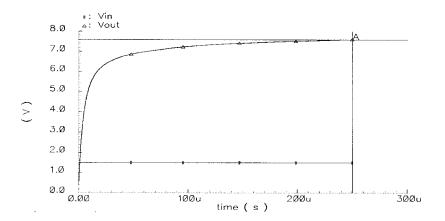

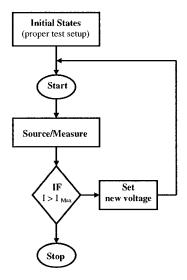

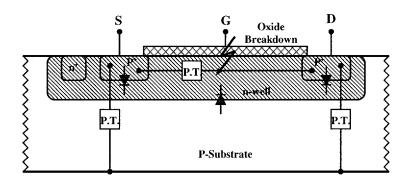

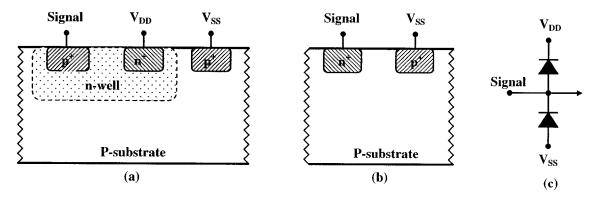

When  $V_{DS1}$  is negative, as per equation (2.4),  $M_3$  is turned on, which creates a conduction path from node  $V_1$  to the external terminal (In). Then, the voltage of node  $V_1$  drops. When  $V_1 < V_{T2}$ , transistor  $M_2$  turns off and the voltage at node  $V_2$  rises accordingly. This forces  $M_1$  to conduct.