# ON THE DESIGN OF ARCHITECTURE-AWARE ALGORITHMS FOR EMERGING APPLICATIONS

A Thesis Presented to The Academic Faculty

by

Seunghwa Kang

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2011

## ON THE DESIGN OF ARCHITECTURE-AWARE ALGORITHMS FOR EMERGING APPLICATIONS

#### Approved by:

Professor David A. Bader, Advisor School of Computational Science and Engineering/School of Electrical and Computer Engineering Georgia Institute of Technology

Professor D. Scott Wills School of Electrical and Computer Engineering Georgia Institute of Technology

Professor George F. Riley School of Electrical and Computer Engineering Georgia Institute of Technology Professor Bo Hong School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Richard W. Vuduc School of Computational Science and Engineering Georgia Institute of Technology

Date Approved: January 25th 2011

To my parents.

#### ACKNOWLEDGEMENTS

First of all, I want to thank my academic advisor, Prof. David A. Bader. As David holds his main affiliation in CSE and I joined Georgia Tech as an ECE student, I was extremely lucky to meet David. David has been an excellent advisor. I could work for the right project in the right timing under his guidance. He was also very supportive and understanding, and I could focus on research to finish my PhD. Thank you very much David!

I also want to thank Prof. Richard Vuduc. I could learn a lot during collaboration with him, and he also served as my committee member. I gratefully acknowledge Prof. D. Scott Wills, Prof. George F. Riley, and Prof. Bo Hong. Prof. Wills and Prof. Riley have served as my reading committee member from the dissertation proposal exam. Dr. Hong traveled from Savannah to serve as my dissertation defense committee member.

My colleagues in the HPC lab has been very helpful and I want to thank them as well. Thank you very much Kamesh Madduri, Virat Agarwal, Aparna Chandramowlishwaran, Vipin Sachdeva, Manisha Gajbe, Amrita Mathuriya, David Ediger, Karl Jiang, Xing Liu, Pushkar Pande, Sainath Mallidi, Robert McColl, Ivan Walker, Zhaoming Yin, Prashant Gaurav, Vyomkesh Tripathi, Jason Riedy, and Henning Meyerhenke. Logan Moon has provided great technical support during my doctoral research, and I also want to gratefully acknowledge his efforts.

Last but not least, I want to thank my parents and my brother, Seung Yub. I could not even start my PhD without them, and I definitely could not finish my PhD without their support and encouragement. Thank you very much Mom, Dad, and Seung Yub!

# TABLE OF CONTENTS

| DE            | DIC  | ATIO    | <b>N</b>                                                                            | iii  |

|---------------|------|---------|-------------------------------------------------------------------------------------|------|

| AC            | KNO  | OWLE    | DGEMENTS                                                                            | iv   |

| LIS           | вт о | F TAE   | BLES                                                                                | ix   |

| LIS           | вт о | F FIG   | URES                                                                                | x    |

| $\mathbf{SU}$ | MM   | ARY .   |                                                                                     | xiii |

| Ι             | IN   | TROD    | UCTION                                                                              | 1    |

|               | 1.1  | The C   | Organization of This Dissertation                                                   | 3    |

|               | 1.2  | Resear  | rch Contributions                                                                   | 6    |

| II            | RE   | NT MU   | STANDING THE DESIGN TRADE-OFFS AMONG CUF<br>ULTICORE SYSTEMS FOR NUMERICAL COMPUTA- | -    |

|               | 2.1  | Inter-a | architectural Design Trade-offs                                                     | 9    |

|               |      | 2.1.1   | Requirements for Parallelism                                                        | 10   |

|               |      | 2.1.2   | Computation Units                                                                   | 11   |

|               |      | 2.1.3   | Start-up Overhead                                                                   | 12   |

|               |      | 2.1.4   | Memory Latency Hiding                                                               | 13   |

|               |      | 2.1.5   | Control over On-chip Memory                                                         | 13   |

|               |      | 2.1.6   | Main Memory Access Mechanisms and Bandwidth Utilization                             | 13   |

|               |      | 2.1.7   | Ideal Software Implementations                                                      | 16   |

|               | 2.2  | Kerne   | l Descriptions and Qualitative Analysis                                             | 17   |

|               |      | 2.2.1   | Conventional Sequential Code                                                        | 17   |

|               |      | 2.2.2   | Basic Algorithmic Analysis                                                          | 18   |

|               | 2.3  | Baseli  | ne Architecture-specific Implementations                                            | 20   |

|               |      | 2.3.1   | Intel Harpertown (2P) and AMD Barcelona (4P) Multicore Implementations              | 20   |

|               |      | 2.3.2   | STI Cell/B.E. (2P) Implementation                                                   | 21   |

|               |      | 2.3.3   | NVIDIA Tesla C1060 Implementation                                                   | 22   |

|     |     | 2.3.4  | A Quantitative Comparison of Implementation Costs                              | 23        |

|-----|-----|--------|--------------------------------------------------------------------------------|-----------|

|     | 2.4 | Experi | mental Results                                                                 | 23        |

|     |     | 2.4.1  | Kernel1                                                                        | 25        |

|     |     | 2.4.2  | Kernel2                                                                        | 29        |

|     |     | 2.4.3  | Kernel3                                                                        | 30        |

|     | 2.5 | Summ   | ary                                                                            | 31        |

| III | FOI |        | CIENT TRANSACTIONAL MEMORY ALGORITHM IPUTING A MINIMUM SPANNING FOREST OF SPAN | RSE<br>33 |

|     | 3.1 | Transa | actional Memory and Algorithm Design                                           | 36        |

|     |     | 3.1.1  | Transactional Memory and Lockfree Algorithms                                   | 36        |

|     |     | 3.1.2  | Algorithmic Model for Transactional Memory System                              | 37        |

|     |     | 3.1.3  | Transactional Memory and Graph Algorithms                                      | 41        |

|     | 3.2 | Minim  | um Spanning Forest Algorithm for Sparse Graphs                                 | 42        |

|     |     | 3.2.1  | Sequential Minimum Spanning Forest Algorithm                                   | 42        |

|     |     | 3.2.2  | Parallel Minimum Spanning Forest Algorithm                                     | 43        |

|     | 3.3 |        | Spanning Forest of Sparse Graphs                                               | 45        |

|     |     | 3.3.1  | MST Data Merging and Composability                                             | 48        |

|     |     | 3.3.2  | Avoiding Excessively Large Transactions and Strong Atomicity                   | 50        |

|     |     | 3.3.3  | Color Filtering                                                                | 51        |

|     |     | 3.3.4  | Heap Pruning                                                                   | 52        |

|     | 3.4 | Experi | mental Results on STM                                                          | 53        |

|     |     | 3.4.1  | Test Graphs                                                                    | 53        |

|     |     | 3.4.2  | Experimental Setup                                                             | 54        |

|     |     | 3.4.3  | Experimental Results                                                           | 55        |

|     | 3.5 | Limita | tions of STM and Requirements for HTM                                          | 57        |

|     | 3.6 | Summ   | ary                                                                            | 59        |

| IV |     |        | ERATING JPEG2000 STILL IMAGE ENCODING US-<br>IBM CELL BROADBAND ENGINE | 61       |

|----|-----|--------|------------------------------------------------------------------------|----------|

|    | 4.1 | Data 1 | Decomposition Scheme                                                   | 63       |

|    | 4.2 | Parall | elization of JPEG2000                                                  | 65       |

|    |     | 4.2.1  | Parallelism in JPEG2000                                                | 65       |

|    |     | 4.2.2  | Parallelization Strategy                                               | 66       |

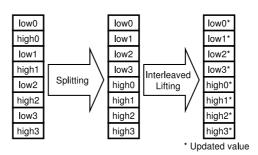

|    | 4.3 | Vector | rization of JPEG2000                                                   | 68       |

|    | 4.4 | Exper  | imental Results                                                        | 72       |

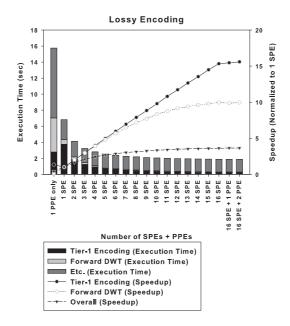

|    |     | 4.4.1  | Encoding Time and Scalability                                          | 72       |

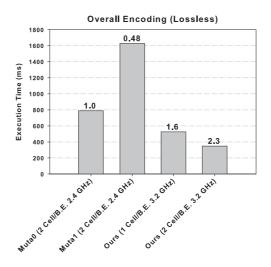

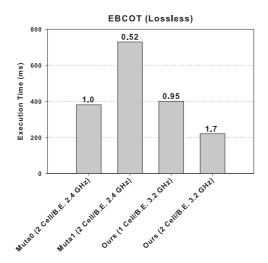

|    |     | 4.4.2  | A Comparison with the Previous Implementation                          | 74       |

|    |     | 4.4.3  | A Comparison with the Intel x86 Architecture                           | 76       |

|    | 4.5 | Summ   | nary                                                                   | 79       |

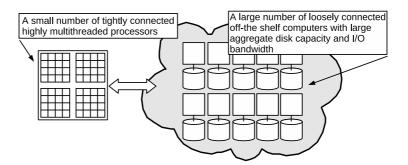

|    |     | HIGHL  | COMBINATION OF A MAPREDUCE CLUSTER AND Y MULTITHREADED SYSTEM          | 80<br>82 |

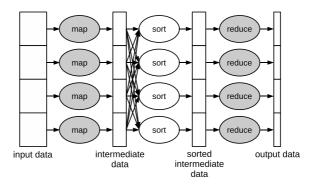

|    | 5.2 |        | deduce                                                                 | 84       |

|    |     | 5.2.1  | Algorithm Level Analysis                                               | 85       |

|    |     | 5.2.2  | System Level Analysis                                                  | 87       |

|    |     | 5.2.3  | Finding Shortest Paths in the Subgraph                                 | 88       |

|    | 5.3 | A Hig  | hly Multithreaded System                                               | 91       |

|    |     | 5.3.1  | Algorithm Level Analysis                                               | 91       |

|    |     | 5.3.2  | System Level Analysis                                                  | 92       |

|    |     | 5.3.3  | Finding Shortest Paths in the Subgraph                                 | 93       |

|    | 5.4 | The H  | Iybrid System                                                          | 94       |

|    |     | 5.4.1  | Algorithm Level Analysis                                               | 94       |

|    |     | 5.4.2  | System Level Analysis                                                  | 96       |

|    |     | 5.4.3  | Finding Shortest Paths in the Subgraph                                 | 96       |

|    | 5.5 | Exper  | imental Results                                                        | 97       |

|    | 5.6 | Summ   | nary.                                                                  | 100      |

| VI            | PHYLOGENETIC TREE RECONSTRUCTION USING GENE ORDER DATA AND PARALLELIZING THE COGNAC SOFT- |                                                                        |     |  |  |

|---------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|--|--|

|               | WA                                                                                        | RE PACKAGE                                                             | 101 |  |  |

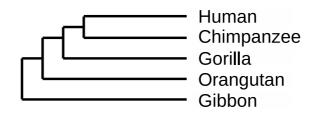

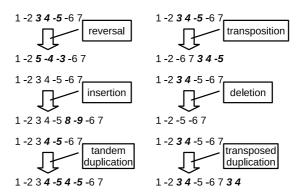

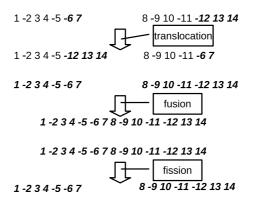

|               | 6.1                                                                                       | Phylogenetic Tree Reconstruction Using Gene Order Data                 | 102 |  |  |

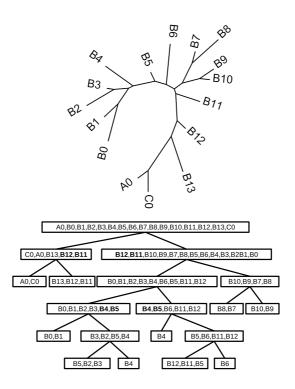

|               | 6.2                                                                                       | Disk-covering methods and GRAPPA                                       | 105 |  |  |

|               | 6.3                                                                                       | COGNAC                                                                 | 106 |  |  |

|               | 6.4                                                                                       | Nested Irregular Parallelism in COGNAC                                 | 108 |  |  |

|               | 6.5                                                                                       | Parallelizing COGNAC with Intel TBB                                    | 111 |  |  |

|               | 6.6                                                                                       | Experimental Results                                                   | 112 |  |  |

|               | 6.7                                                                                       | Summary                                                                | 114 |  |  |

| VII           | CC                                                                                        | ONCLUSIONS                                                             | 116 |  |  |

|               | 7.1                                                                                       | Major Challenges in software development for Modern Parallel Computers | 116 |  |  |

|               | 7.2                                                                                       | System Software Support for Nested Irregular Parallelism               | 121 |  |  |

|               | 7.3                                                                                       | Transactional Memory                                                   | 125 |  |  |

|               | 7.4                                                                                       | Hybrid Data Transfer Mechanism                                         | 126 |  |  |

|               | 7.5                                                                                       | Future Research Directions                                             | 127 |  |  |

|               | 7.6                                                                                       | Final Remarks                                                          | 128 |  |  |

| $\mathbf{RE}$ | FER                                                                                       | ENCES                                                                  | 130 |  |  |

# LIST OF TABLES

| 1  | Applications and architectures studied in this work                                             | 4   |

|----|-------------------------------------------------------------------------------------------------|-----|

| 2  | Summary of the test systems                                                                     | Ĉ   |

| 3  | A quantitative comparison of implementation costs in terms of code size and implementation time | 23  |

| 4  | Test graphs for MSF experiments                                                                 | 53  |

| 5  | A Performance comparison among different MSF implementations                                    | 53  |

| 6  | Latency for the SPE instructions                                                                | 69  |

| 7  | Technical specifications for the test platforms                                                 | 94  |

| 8  | Genetic data in different levels                                                                | 103 |

| 9  | A part of the parallelism in COGNAC                                                             | 109 |

| 10 | Performance statistics collected using Intel Vtune                                              | 113 |

# LIST OF FIGURES

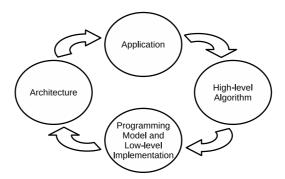

| 1  | The feedback loop from emerging applications to future architectures.                                                                                   | 3  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

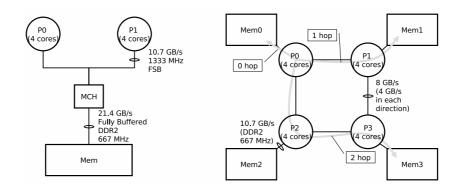

| 2  | The 2P Intel Harpertown system with the UMA architecture and the 4P AMD Barcelona system with the NUMA architecture                                     | 13 |

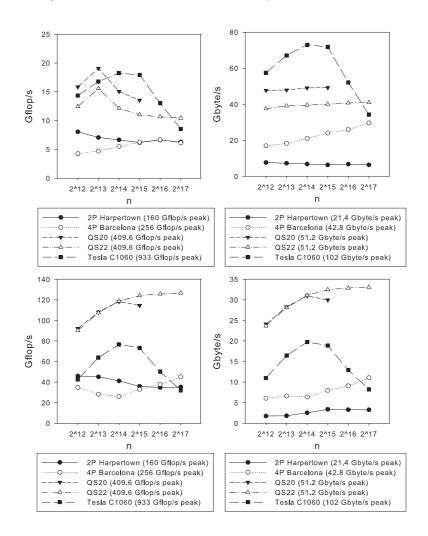

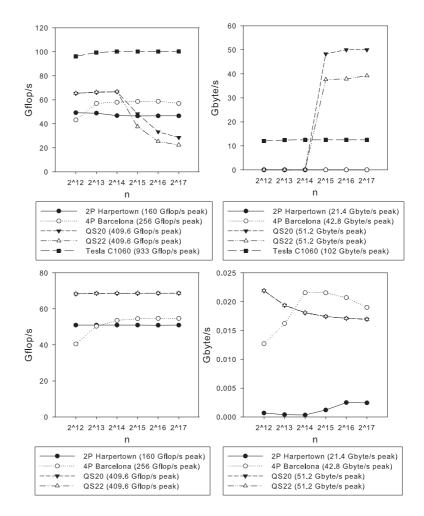

| 3  | Sustained Gflop/s and bandwidth utilization (GB/s) for the initial (top) and the blocking based (bottom) implementations of Kernel1 (single-precision)  | 24 |

| 4  | Sustained Gflop/s and bandwidth utilization (GB/s) (for the initial (top) and the blocking based (bottom) implementations of Kernel1 (double-precision) | 25 |

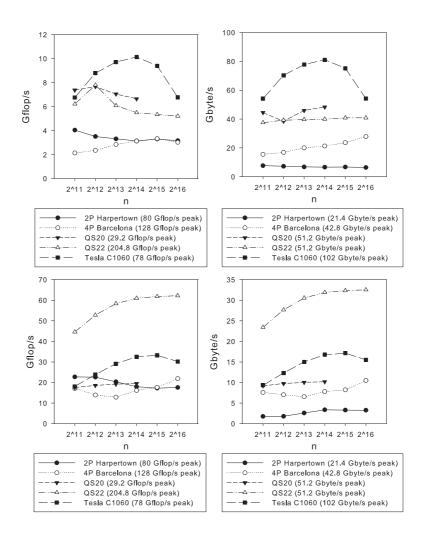

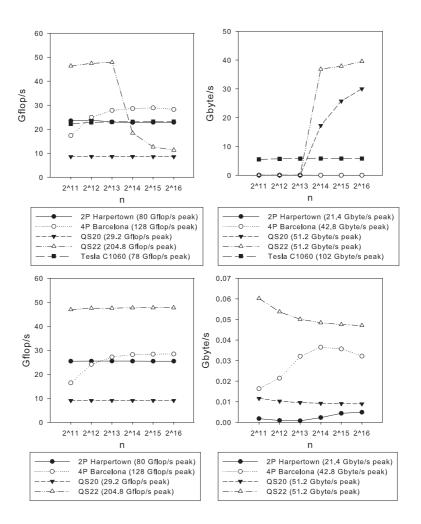

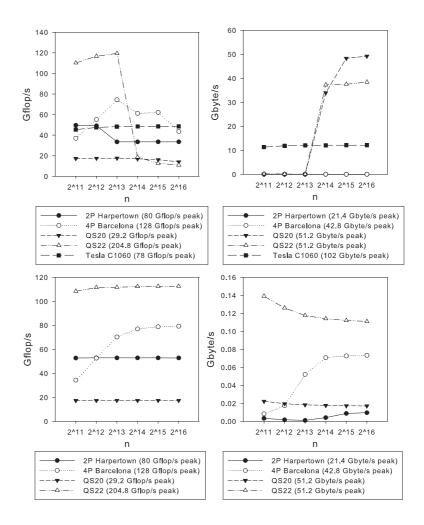

| 5  | Sustained Gflop/s and bandwidth utilization (GB/s) for the initial (top) and the blocking based (bottom) implementations of Kernel2 (single-precision)  | 28 |

| 6  | Sustained Gflop/s and bandwidth utilization (GB/s) for the initial (top) and the blocking based (bottom) implementations of Kernel2 (double-precision)  | 29 |

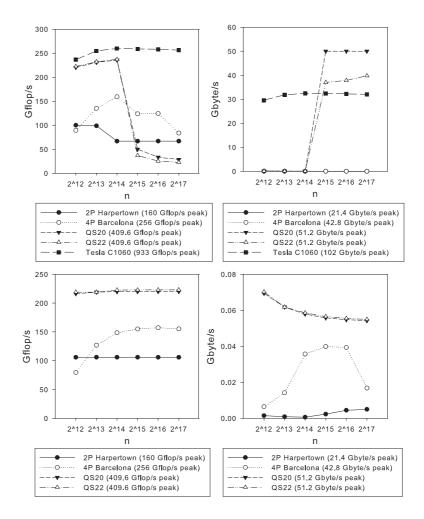

| 7  | Sustained Gflop/s and bandwidth utilization (GB/s) for the initial (top) and the blocking based (bottom) implementations of Kernel3 (single-precision)  | 31 |

| 8  | Sustained Gflop/s and bandwidth utilization (GB/s) for the initial (top) and the blocking based (bottom) implementations of Kernel3 (double-precision)  | 32 |

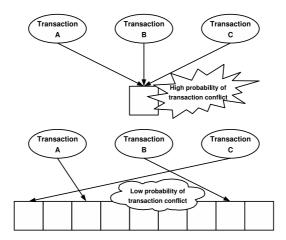

| 9  | Illustrations of high-contention and low-contention scenarios                                                                                           | 38 |

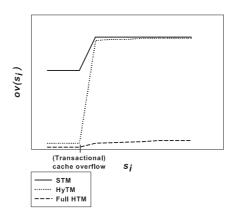

| 10 | Transactional overhead as a function of a transaction size                                                                                              | 39 |

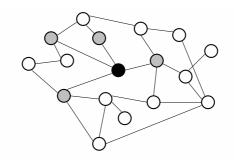

| 11 | A common graph operation                                                                                                                                | 41 |

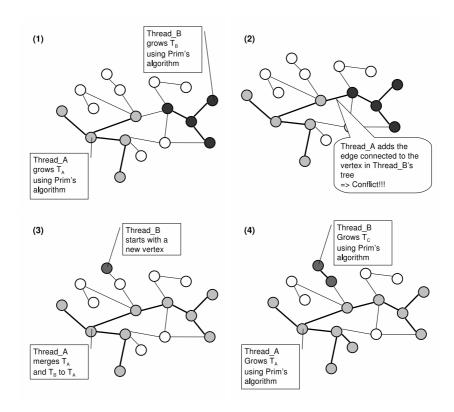

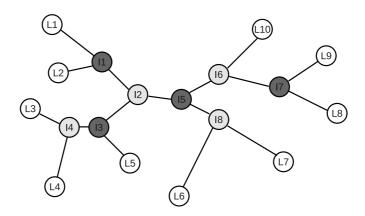

| 12 | A high level illustration of our MSF algorithm                                                                                                          | 45 |

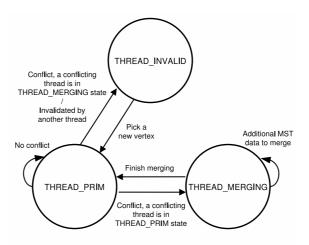

| 13 | A State transition diagram for our MSF algorithm                                                                                                        | 45 |

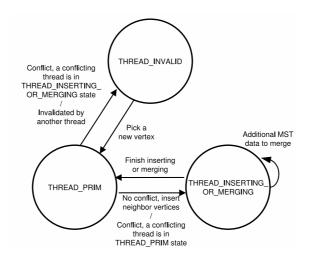

| 14 | A Modified state transition diagram for our algorithm                                                                                                   | 50 |

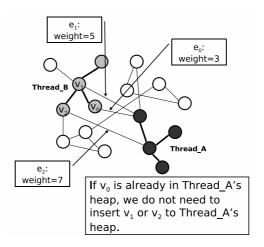

| 15 | Color filtering: filter out unnecessary inserts                                                                                                         | 51 |

| 16 | A pathological case for our algorithm                                                                                                                   | 54 |

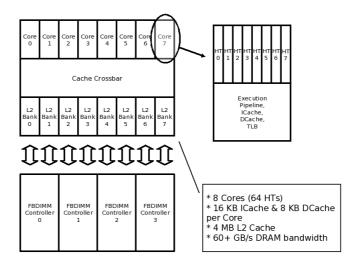

| 17 | Sun UltraSparc T2 (Niagara 2) processor                                                                                                                 | 54 |

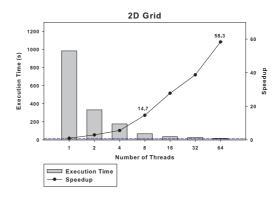

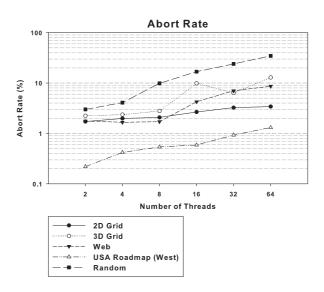

| 18 | Execution time and speedup for the 2-D grid graph (3.24M vertices, 6.48M edges)                                                                         | 55 |

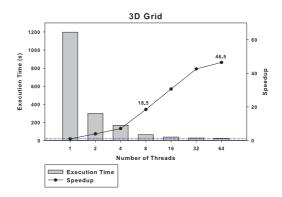

| 19 | Execution time and speedup for the 3-D grid graph (3.38M vertices, 10.1M edges)                                          | 56 |

|----|--------------------------------------------------------------------------------------------------------------------------|----|

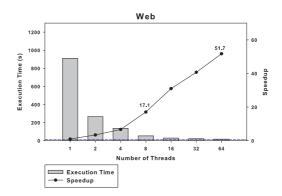

| 20 | Execution time and speedup for the web graph (3M vertices, 6M edges).                                                    | 56 |

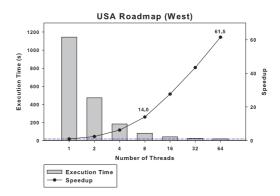

| 21 | Execution time and speedup for the USA West roadmap graph (6.26M vertices, 7.62M edges)                                  | 56 |

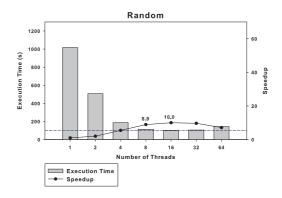

| 22 | Execution time and speedup for the random graph (3M vertices, 90M edges)                                                 | 57 |

| 23 | Abort rate for varying numbers of threads                                                                                | 58 |

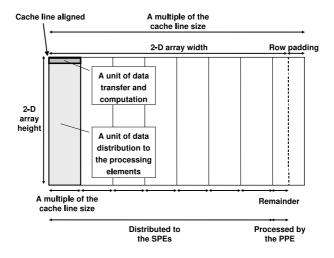

| 24 | Data decomposition scheme for two dimensional array                                                                      | 63 |

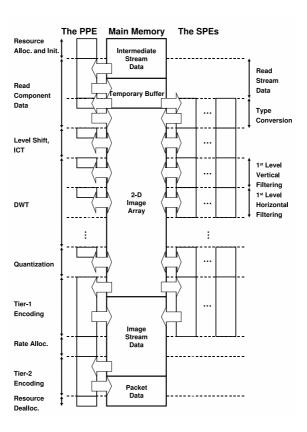

| 25 | Work partitioning among the PPE and the SPEs for JPEG<br>2000 encoding $$                                                | 66 |

| 26 | The splitting step and the interleaved lifting step for the vertical filtering                                           | 69 |

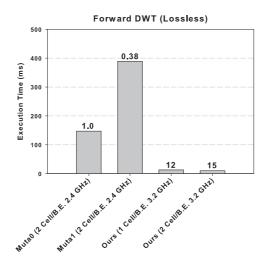

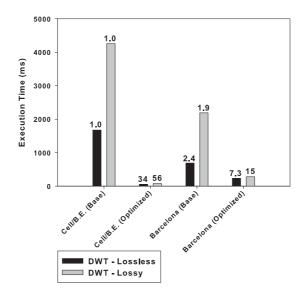

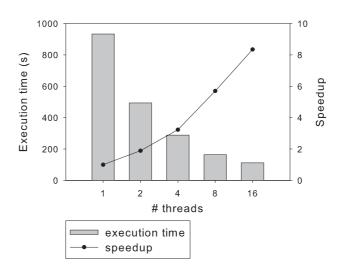

| 27 | Execution time and speedup for lossless encoding                                                                         | 73 |

| 28 | Execution time and speedup for lossy Encoding                                                                            | 73 |

| 29 | An overall performance comparison with the previous implementations for the Cell/B.E                                     | 74 |

| 30 | An EBCOT (Tier-1 + Tier2) encoding performance comparison with the previous implementations for the Cell/B.E             | 74 |

| 31 | A DWT performance comparison with the previous implementations for the Cell/B.E                                          | 75 |

| 32 | An encoding performance comparison of the Cell/B.E. to that of the Intel Pentium IV 3.2 GHz processor.                   | 77 |

| 33 | A DWT encoding performance comparison of the Cell/B.E. to that of the AMD Barcelona (Quad-core Opteron) processor        | 78 |

| 34 | The hybrid combination of a MapReduce cluster and a highly multi-<br>threaded system                                     | 81 |

| 35 | A MapReduce workflow                                                                                                     | 84 |

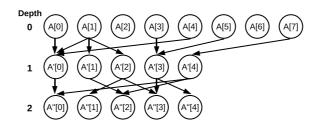

| 36 | A directed acyclic graph (DAG) for MapReduce computation                                                                 | 85 |

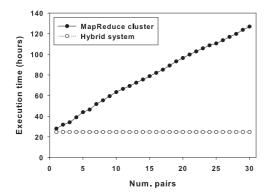

| 37 | Experimental results for extracting a subgraph with 10% of the vertices in the original graph and finding shortest paths | 97 |

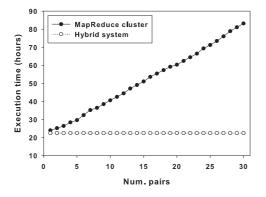

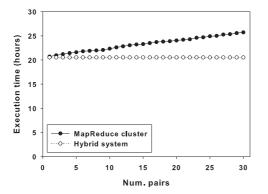

| 38 | Experimental results for extracting a subgraph with 5% of the vertices in the original graph and finding shortest paths  | 98 |

| 39 | Experimental results for extracting a subgraph with 2% of the vertices in the original graph and finding shortest paths  | 98 |

| 40 | An exemplar phylogenetic tree                                                                              | 102 |

|----|------------------------------------------------------------------------------------------------------------|-----|

| 41 | Intra-chromosomal genome rearrangement events                                                              | 104 |

| 42 | Inter-chromosomal genome rearrangement events                                                              | 105 |

| 43 | A model phylogenetic tree and a disk tree for the tree                                                     | 107 |

| 44 | An illustration of the data synchronization issue in scoring a single tree topology using multiple threads | 110 |

| 45 | Execution time and speedup on a 8-core 16-threads machine (two Nehalem-EP processors)                      | 113 |

#### **SUMMARY**

This dissertation maps various kernels and applications to a spectrum of programming models and architectures and also presents architecture-aware algorithms for different systems. Built on top of our experiences, we aim to provide feedback to system software researchers and computer architects.

The kernels and applications discussed in this dissertation have widely varying computational characteristics. For example, we consider both dense numerical computations—which are floating point intensive and have predictable data access patterns—and sparse graph algorithms—which are highly irregular and require intensive data synchronization. This dissertation also covers emerging applications from image processing, complex network analysis, and computational biology. JPEG2000 is the successor of JPEG and uses a mix of kernels with different computational requirements. To analyze large scale complex networks, we often need to process very large data to extract a network of interest. The structure of the extracted network often challenges modern hierarchical memory subsystems as well. We parallelize the COGNAC software package which reconstructs a phylogenetic tree using gene order data. The application has parallelism in multiple levels, and the degree of parallelism in each level varies widely.

We map these problems to diverse multicore processors (the Intel Harpertown and Nehalem architectures, the AMD Barcelona architecture, and the Sun UltraSparc architecture) and manycore accelerators (such as the IBM Cell Broadband Engine and NVIDIA GPUs). We also use new programming models—such as Transactional Memory, MapReduce, and Intel TBB—to address the performance and productivity

challenges in the problems.

Our experiences highlight the importance of mapping applications to appropriate programming models and architectures. We also find several limitations of current system software and architectures and directions to improve those. The discussion focuses on system software and architectural support for nested irregular parallelism, Transactional Memory, and hybrid data transfer mechanisms. We believe that the complexity of parallel programming can be significantly reduced via collaborative efforts among researchers and practitioners from different domains. This dissertation participates in the efforts by providing benchmarks and suggestions to improve system software and architectures.

## CHAPTER I

#### INTRODUCTION

Parallel algorithm design had been a topic of interest for only a portion of the programmers and researchers in the computing area. A group of researchers—often referred as theoreticians—have worked on extracting parallelism from seemingly sequential problems and designing parallel algorithms assuming a certain theoretical model; only a limited number of those algorithms have been implemented on real systems. Another group of researchers in the supercomputing area worked on solving large-scale science problems—mainly by manipulating extremely large matrices and vectors—using very expensive supercomputers. These problems often have obvious parallelism originated from the huge dimension of matrices and vectors, but scaling such computations to a large number of processors is far from trivial due to communication bandwidth and latency issues. Addressing such a challenge have been a task for a small number of highly-experienced top-notch programmers.

#### $Microprocessor \simeq Multicore$ (or Manycore) processor

As a consequence,

#### Computing $\simeq$ Parallel computing

Power wall, memory wall, and ILP wall [11] are forcing a paradigm shift to multicore and manycore architectures, and the landscape of computing is rapidly changing with the advent of multicore processors. Multicore—and even manycore—processors are replacing old single-core processors in nearly every area of computing. Most single-core processors will retire in the near future, and most computing systems will become parallel computing systems. Chip makers released and are developing microprocessors with varying architectures to balance power efficiency, programmability, and chip development cost for their target application areas. These changes impose several new research challenges.

Traditional algorithm works focus on designing new algorithms with low asymptotic complexity for a well defined theoretical model. Yet, transforming such algorithms to real implementations is not always straightforward. Due to the recent architectural changes in multicore processors and manycore accelerators, it becomes even more challenging or nearly impossible in many cases. Different architectures have widely varying execution units and memory subsystems, and this forces algorithm designers to consider such architectural design trade-offs from the very beginning.

Parallel computers are becoming ubiquitous, and this calls for new applications and more programmers to exploit those machines. New applications impose different computing challenges to traditional supercomputing applications. Finding new applications and identifying major computing issues in those applications are important research topics.

The computing industry cannot rely on a small number of highly-experienced programmers any more. However, new architectures often sacrifice programmability in favor of power efficiency, and this further increases the programming complexity to exploit parallel computers. System software researchers and computer architects are struggling to solve these problems, but their efforts will not come to fruition without help form researchers in application and algorithm domains. Designing future system software and architectures necessitates the solid understanding of future applications, key algorithms for those applications, and the role of software tools and hardware support in addressing the programming and performance challenges in those applications. This feedback loop (see Figure 1) is crucially important.

However, most system software researchers and computer architects do not understand applications and algorithms very well, and most researchers in the application

Figure 1: The feedback loop from emerging applications to future architectures.

and algorithm domains do not understand system software and computer architecture. System software researchers and computer architects design new tools and new microprocessors using old benchmarks. Researchers in the application and algorithm domains are significantly lagging behind the system- and architecture-level innovations. There have been several attempts to identify (e.g. [11, 19]) important kernels in current and future applications, but real applications require multiple kernels and mix those kernels in a complex way. Systems work well for individual kernels may not perform well for complete applications.

This dissertation presents parallel algorithms and performance tuning techniques for various applications and architectures (see Table 1). In presenting the algorithms and the techniques, we also discuss major computational challenges in those applications and the match between the algorithms for the applications and different programming models and architectures. Built on top of the lessons learned from the works, this dissertation provides feedback to system software researchers and computer architects.

# 1.1 The Organization of This Dissertation

The remainder of this dissertation is organized as the following. First, we discuss two classes of kernels with completely different computational characteristics in Chapters 2 and 3. Chapter 2 presents an inter-architectural comparison work for three

**Table 1:** Applications and architectures studied in this work.

| area                     | application/algorithm                      | architecture               |  |

|--------------------------|--------------------------------------------|----------------------------|--|

| computational statistics | Pearson's and Kendall's                    | Intel Harpertown, AMD      |  |

|                          | methods (covariance com-                   | Barcelona, IBM Cell Broad- |  |

|                          | putation) band Engine and                  |                            |  |

|                          |                                            | erXCell 8i, and NVIDIA     |  |

|                          |                                            | Tesla                      |  |

| graph algorithm          | minimum spanning forest                    | Sun Niagara with software  |  |

|                          | Transactional Memory                       |                            |  |

| image processing         | JPEG2000                                   | IBM Cell Broadband Engine  |  |

|                          | and AMD Barcelona                          |                            |  |

| complex network analysis | sub-graph extraction and Sun Niagara and a |                            |  |

|                          | analysis                                   | duce cluster with AMD      |  |

|                          |                                            | Opteron processors         |  |

| computational biology    | phylogenetic tree recon-                   | Intel Nehalem              |  |

|                          | struction using gene order                 |                            |  |

|                          | data                                       |                            |  |

kernels from computational statistics. These kernels are floating-point intensive and have a high degree of spatial locality and predictable data access patterns. The kernels also have large basic blocks (only a small number of branches) and do not require data synchronization. We study the impact of design trade-offs on the performance and programmability of the kernels for various multicore processors and accelerators—such as the Intel Harpertown and the AMD Barcelona architectures, the IBM Cell Broadband Engine and PowerXCell 8i architectures, and the NVIDIA Tesla architecture.

Chapter 3 maps irregular graph algorithms to Transactional Memory. Many graph algorithms are integer based and often have a very low degree of spatial and temporal locality. Data access patterns are highly irregular. Graph algorithms are often branchy and heavily involve data synchronization issues. We demonstrate that Transactional Memory can significantly reduce the programming and performance challenges in many graph problems in the chapter. We also present a new efficient Transactional Memory algorithm to compute a minimum spanning forest in irregular graphs. Our experimental results show the potential of Transactional Memory but

also reveal the limitation of software Transactional Memory. We discuss the necessity of hardware support.

Chapters 4, 5, and 6 present parallel algorithm design and performance tuning works for three different emerging applications: JPEG2000, complex network analysis, and gene order data based phylogenetic tree reconstruction. Chapter 4 studies parallelization and performance tuning of JPEG2000 for the Cell Broadband Engine. JPEG2000 is the successor of widely used JPEG still image coding standard and consists of multiple kernels with different computational characteristics such as Embedded Block Coding with Optimized Truncation (EBCOT) and Discrete Wavelet transform (DWT). The EBCOT algorithm is irregular and branchy but has a fixed memory footprint. The DWT is communication-intensive and requires both horizontal and vertical scanning of the input image; this challenges current cache based memory subsystems. The Cell Broadband Engine provides a DMA based block data transfer mechanism, and we present performance tuning strategies to exploit the block data transfer mechanism and the processors's vector units.

Chapter 5 presents a hybrid system of a highly multithreaded architecture and a MapReduce cluster as a solution to address the computational challenges in complex network analysis problems which are both data- and communication-intensive. Analyzing complex networks involves managing very large data and traversing irregular graphs. The hybrid system of the two widely different architectures efficiently addresses the computational challenges. The result shows the importance of using right programming models and architectures for applications of interest.

We present parallelization of our *COGNAC* software package in Chapter 6. *COGNAC* reconstructs a phylogenetic tree using gene order data. *COGNAC* enables accurate reconstruction of a phylogenetic tree but is also computationally expensive. *COGNAC* has parallelism in multiple levels, and the degree of parallelism in each parallelization point varies widely for different input data sets and throughout computing phases.

Managing nested irregular parallelism is key to address the computational challenges in *COGNAC* using parallel computers. We use the combination of Intel TBB and microprocessors with simultaneous multithreading support to address the challenges with the minimum increase in programming complexity. The chapter highlights the importance of system software and architectural support in solving the parallel programming crisis.

Based on our experiences with different kernels, applications, programming models, and architectures, we discuss the major challenges in parallel algorithm design and implementation for modern parallel computers and provide feedback to system software researchers and computer architects in Chapter 7. Especially, we discuss issues related to system software support for nested irregular parallelism, Transactional Memory, and a hybrid data transfer mechanism. This dissertation is based on our published papers—such as [66], [64], [12], [63], and [65].

#### 1.2 Research Contributions

The following summarizes the major contributions of this dissertation.

- 1. This dissertation discusses parallelization and performance tuning of kernels with widely varying computational characteristics and applications with a mix of kernels for a variety of architectures and programming models.

- 2. This dissertation presents mappings between classes of kernels and applications and different programming models and architectures.

- 3. This dissertation provides benchmarks for system software researchers and computer architects to test new programming models and architectural features.

- 4. This dissertation provides feedback to the system software and computer architecture communities from an application- and architecture-centric viewpoint.

#### CHAPTER II

# UNDERSTANDING THE DESIGN TRADE-OFFS AMONG CURRENT MULTICORE SYSTEMS FOR NUMERICAL COMPUTATIONS

This chapter discusses the impact of architectural design trade-offs among various multicore processors and accelerators for dense numerical computations and is based on the materials in Seunghwa Kang, David A. Bader, and Richard Vuduc, "Understanding the Design Trade-offs among Current Multicore Systems for Numerical Computing," The 23rd International Parallel and Distributed Processing Symposium (IPDPS), Rome, Italy, May 25th-29th, 2009.

Multicore processors and accelerator architectures are replacing single-core processors in nearly every computing area. These systems are attractive to application developers because of their impressive peak computational potential and (in several cases) their energy-efficient processing capabilities. However, the architectures themselves are diverse and reflect a wide variety of design trade-offs. Consequently, we might expect the performance of a given application to be an even more sensitive function of the architecture than in previous generation single-core general purpose processors, which in turn is expected to affect software development costs significantly.

The research literature on software optimization for these multicore systems is growing rapidly, particularly for platforms based on the Cell Broadband Engine (Cell-/B.E.) [25, 62, 110] and for GPUs [100, 124]. Ryoo, et al. [108, 109] have published extensively on generalizing optimization principles for the NVIDIA GPUs based on the CUDA framework [96]. In addition to the optimization research for a single platform, several inter-architecture comparisons have been published as well. Williams,

et al. [128] compared the performance of emerging multicore platforms, including the AMD dual-core Opteron processor, the Intel quad-core Harpertown processor, the Sun Niagara processor, and the Cell/B.E. processor for sparse matrix-vector multiplication. Also, there are several papers that compare the performance of CPUs, GPUs, FPGAs, the Cell/B.E. processor, and the Cray MTA-2 [82, 33, 25].

The focus of this chapter is on evaluating the impact of fundamental design tradeoffs on a particular class of widely-used but simple-to-analyze software kernels. We

study a range of systems with native double-precision support, described in detail

in Section 2.1, including a two processor (2P) system with Intel quad-core Harpertown 2.5 GHz E5420 processors, a four processor (4P) system with AMD quad-core

Barcelona 2.0 GHz 8350 processors, an IBM QS20 blade with two Cell/B.E. 3.2 GHz

processors, an IBM QS22 blade with two PowerXCell 8i 3.2 GHz processors, and a

desktop system equipped with one NVIDIA Tesla C1060 GPU. As the test systems

have varying numbers of chips, clock frequencies, prices, and power consumptions, we

focus on architectural design trade-offs and their impacts on different kernels rather

than identifying the best performing processor.

We evaluate these systems experimentally using three kernels from computational statistics with differing computational characteristics. First, we create two kernels by extracting the most computationally intensive part of the covariance/correlation computation from the R statistics package [3]. These kernels are based on Pearson's method and Kendall's method [68], which we hereafter refer to as Kernel1 and Kernel2, respectively. The third kernel (Kernel3) is created by modifying Kernel2 to highlight each system's capability in processing highly floating-point intensive computation. Section 2.2 describes these kernels in more detail.

We also discuss our implementation and software optimization process, to highlight the challenges and complexities of software development for each architecture (Section 2.3). However, we consider the main contribution of this chapter to be our inter-architectural analysis, not the optimization work. Our experimental results highlight the performance of each system in executing a different mix of instructions for compute-bound and communication-intensive cases (Section 2.4). We consider both single-precision and double-precision performance for floating-point operations and aim to characterize the resulting performance in terms of each system's design choices.

## 2.1 Inter-architectural Design Trade-offs

This section describes five multicore systems of interest in this study, which are summarized in Table 2. In particular, each subsection considers a particular design dimension, and qualitatively summarizes the differences among the architectures. For additional processor details, we refer interested readers elsewhere [48, 34, 75].

**Table 2:** Summary of the test systems.

| System         | 2P Harpertown<br>E5420           | 4P Barcelona<br>8350             | QS20-Cell/B.E.     | QS22-<br>PowerXCell<br>8i | Tesla C1060                 |

|----------------|----------------------------------|----------------------------------|--------------------|---------------------------|-----------------------------|

| Clock          | 2.5 GHz                          | 2.0 GHz                          | 3.2 GHz            | 3.2 GHz                   | 1.296 GHz                   |

| Num. chips     | 2                                | 4                                | 2                  | 2                         | 1.230 GHZ                   |

| Num. cores     | 4                                | 4                                | 1 PPE +            | 1 PPE +                   | $30 \text{ SMs} \times (8)$ |

| / chip         | 1                                | _                                | 8 SPEs             | 8 SPEs                    | single-precision            |

| / omp          |                                  |                                  | 0 01 20            | 0 01 20                   | SPs + 1 double-             |

|                |                                  |                                  |                    |                           | precision $SP + 2$          |

|                |                                  |                                  |                    |                           | SFUs)                       |

| DP Gflop/s     | 80                               | 128                              | 29.2               | 204.8                     | 78                          |

| SP Gflop/s     | 160                              | 256                              | 409.6              | 409.6                     | 933                         |

| On-chip        | 6 + 6 MB L2                      | 512 KB L2 cache                  | 256 KB local       | 256 KB local              | 16 KB shared                |

| memory         | cache per chip                   | per core and 2                   | store per SPE      | store per SPE             | memory per SM               |

|                |                                  | MB shared cache                  | _                  | _                         |                             |

|                |                                  | per chip                         |                    |                           |                             |

| DRAM type      | DDR2                             | DDR2                             | Rambus XDR         | DDR2                      | GDDR3                       |

| Shared DRAM    | UMA                              | NUMA                             | NUMA               | NUMA                      | N/A                         |

| access         |                                  |                                  |                    |                           |                             |

| Latency hiding | cache +                          | cache +                          | double (or triple) | double (or triple)        | hardware-                   |

|                | prefetching                      | prefetching                      | buffering          | buffering                 | multithreading              |

| Theoretical    | 21.4                             | 42.8                             | 51.2               | 51.2                      | 102                         |

| peak bandwidth |                                  |                                  |                    |                           |                             |

| (GB/s)         |                                  |                                  |                    |                           |                             |

| Power (W)      | $2 \times 80 \text{ (per chip)}$ | $4 \times 75 \text{ (per chip)}$ | 315 (per blade)    | 250 (per blade)           | 200 (max., per              |

|                |                                  |                                  |                    |                           | board)                      |

| Compiler       | Intel icc                        | Intel icc                        | IBM xlc (10.1)     | IBM xlc (10.1)            | NVIDIA nvcc                 |

|                | (10.1.018)                       | (10.1.015)                       |                    |                           | (release 2.0                |

|                |                                  |                                  |                    |                           | V0.2.1221)                  |

| Optimization   | -fast                            | -fast                            | -O5 -qarch=        | -O5 -qarch=edp            | -O3 -arch sm_13             |

| flag           |                                  |                                  | cellspu -qtune=    | -qtune=edp                |                             |

|                |                                  |                                  | cellspu            |                           |                             |

Among "conventional" general purpose multicore microprocessors, we consider the Intel quad-core E5420 Harpertown processor and AMD's quad-core 8350 Barcelona. The Intel Harpertown and AMD Barcelona processors share a similar micro-architecture, but take distinct approaches to cache hierarchy and memory subsystem design. The Intel Harpertown has 12 MB L2 cache memory, and two cores among four cores in a chip share 6 MB L2 cache. The AMD Barcelona has dedicated 512 KB L2 cache per core in addition to 2 MB L3 cache shared by all four cores in a chip. Also, the AMD Barcelona supports the NUMA (Non-Uniform Memory Access) architecture while the Intel Harpertown is based on the UMA (Uniform Memory Access) architecture.

Among the multicore accelerator systems, we consider two generations of the STI Cell/B.E. processor and the NVIDIA Tesla C1060 GPU. The Cell/B.E. processor is a heterogeneous multicore processor with one conventional PowerPC core ("PPE") and eight specialized single-instruction multiple-data (SIMD) accelerators ("SPEs"). The Tesla C1060 is a GPU from NVIDIA and delivers 933 Gflop/s in single-precision with native 78 Gflop/s double-precision support. The C1060, based on the Tesla architecture [75], has 30 SMs (Streaming Multiprocessors), and each SM has 8 SPs (Streaming Processors) for single-precision and one SP for double-precision support. Also, each SM has two SFUs (Special Function Units) for transcendental functions and attribute interpolation.

#### 2.1.1 Requirements for Parallelism

The Intel Harpertown, AMD Barcelona, and Cell/B.E. processors have four to nine cores, and each core supports SIMD instructions for acceleration. To exploit the parallelism in these processors, these chips require coarse-grain parallelism for their multiple cores in addition to SIMD parallelism.

In contrast, the Tesla C1060 has 240 SPs and 60 SFUs for single-precision. In

addition, to be detailed in Section 2.1.4, the Tesla architecture adopts massive hardware multithreading to hide DRAM access latency. The Tesla C1060 requires at least several thousand-way parallelism to exploit its architectural features. Also, the Tesla C1060 requires SIMT (Single Instruction Multiple Threads) parallelism, and every thread in a single warp (a group of 32 threads) needs to agree on the execution path to maximize chip utilization.

#### 2.1.2 Computation Units

Each core of the Intel Harpertown or AMD Barcelona processor can retire up to two SIMD floating-point instructions (one SIMD add and one SIMD multiply) [9, 58]; thus each core can deliver 4 double-precision floating-point operations per cycle. Also the Intel and AMD cores can execute integer instructions in parallel with floating-point instructions. Each SPE in the Cell/B.E. processor has two (even and odd) pipelines. The even pipeline can execute floating-point instructions, fixed point arithmetics, and logical and word-granularity shift and rotate instructions. The odd pipeline executes load/store instructions and fixed point byte-granularity shift, rotate mask, and shuffle instructions. Each SPE can retire one SIMD FMA (fused-multiply-and-add) instruction per cycle. Each SP in the Tesla C1060 executes one scalar instruction per cycle, including a single-precision FMA instruction. Each SFU can also execute four single-precision multiply instructions per cycle. One SP for double-precision support can retire one double-precision FMA instruction per cycle.

The sustainable flop-rate is highly affected by the mix of different instruction types in an execution stream and the structure of the computation unit. The Intel and AMD cores have separate multiply and add units instead of a FMA unit and also can run integer instructions in parallel; thus, they can more flexibly execute different combinations of integer and floating-point instructions. Still, to fully utilize both floating-point multiply unit and add unit, this chip requires a 1:1 ratio of multiply

and add instructions. One SPE of the Cell/B.E. can issue only one floating-point instruction in a single cycle (whether it is FMA or not), so if multiply cannot be fused with add, the achievable peak flop-rate becomes halved. Still, the Cell/B.E. can run several types of fixed point instructions in parallel with floating-point operations. Fully exploiting the SMs in the Tesla C1060 requires FMA instructions and additional multiply instructions for the SFUs. Also, one SP can execute only one instruction per cycle.

#### 2.1.3 Start-up Overhead

Kernel launching is faster on the Intel or AMD processors than on the Cell/B.E. or the Tesla C1060. Thus, for a small amount of computation, these general purpose processors outperform the accelerators while the accelerator architectures often exhibit impressive performance for larger data [82].

The test systems also incur different levels of data off-loading overhead. In the Harpertown, Barcelona, and Cell/B.E. processors, the off-loading overhead is largely determined by the off-chip memory bandwidth. In contrast, GPU systems incur additional host memory to on-board device memory data transfer via a slower PCI Express bus. While GPUs can partially hide the off-loading overhead with asynchronous data transfer (*i.e.*, double-buffering), this mechanism currently works only for page-locked memory and incurs additional programming overhead [98]. To amortize the off-loading overhead, GPUs require higher computational intensity than other processors [32, 114, 82]. However, the Tesla C1060's on-board memory is much larger (4 GB) than the Harpertown or Barcelona's cache memory (12 or 2 MB) or the Cell-/B.E.'s local store (256 KB per SPE × 8 SPEs). Accordingly, the Tesla C1060 can fit larger data into its on-board memory to minimize the data transfer over the PCI Express bus.

#### 2.1.4 Memory Latency Hiding

The Intel Harpertown and AMD Barcelona processors hide memory latency via cache memory and prefetching mechanisms. The Cell/B.E. overlaps computation with communication via double- or triple-buffering. Double buffering efficiently hides the latency but requires explicit software intervention. The Tesla C1060 tolerates several hundred cycle DRAM access latency via massive hardware multithreading. The Tesla GPU also has per SM shared memory (16 KB) in addition to constant cache and texture cache. Yet, as each SM can run hundreds of threads in parallel, these on-chip memories have little performance impact if there is only a low degree of data sharing among different threads.

#### 2.1.5 Control over On-chip Memory

For the cache-based multicore processors, cache memory is managed by hardware using the LRU (Least Recently Used) policy (or its variants), and programmers have essentially no control over cache partitioning. By contrast, programmers can explicitly manage on-chip ("local store") memory on the Cell/B.E. The Tesla C1060, along with the NVIDIA CUDA framework, also allows programmers to control the placement of data arrays to the chip's different types of memories.

#### 2.1.6 Main Memory Access Mechanisms and Bandwidth Utilization

**Figure 2:** The 2P Intel Harpertown system with the UMA architecture (left) and the 4P AMD Barcelona system with the NUMA architecture (right).

The AMD Barcelona and Cell/B.E. processors use the NUMA (Non-Uniform Memory Access) architecture, while the Intel Harpertown processor adopts the UMA (Uniform Memory Access) architecture. UMA is conceptually simpler but NUMA has scalability advantages if cores running on different chips access distinct data arrays. In particular, by locating data to the chip's local main memory, we can minimize the contention and interference in the main memory interface. For instance, if a computation accesses read-only data multiple times, we can replicate the data to each processor's local DRAM to maximize the bandwidth utilization for accessing the data. The Tesla C1060's device memory does not support shared memory access over two or more GPUs.

The systems also differ in their deliverable memory bandwidth [102]. In terms of peak aggregate bandwidth, the 2P Harpertown system can deliver 21.4 GB/s, the 4P Barcelona system supports 42.8 GB/s, and the QS20 and QS22 blades support 51.2 GB/s for main memory access. The Tesla C1060 supports 102 GB/s peak bandwidth to its 4 GB device memory. However, there is often a significant gap between the peak bandwidth and the sustainable bandwidth [59, 94]. The gap is even larger for multicore processors due to the interference among multiple threads performing data accesses [93, 103, 105].

The systems adopt different memory controller architectures. In general, most memory controllers are designed to deliver the highest data transfer rate when accessing a large contiguous chunk of data, in particular by exploiting the maximum locality of a row buffer and bank level parallelism. Switching between DRAM reads and writes should also be minimized to achieve the highest bandwidth utilization. However, even for simple computations in which each thread is reading a linear array with stride one, memory requests coming from multiple cores can be intermixed, thereby destroying the locality and parallelism of a DRAM chip. For the Intel Harpertown and AMD Barcelona processors, the granularity of memory access is the lowest

level cache line size (64 byte). For data-intensive applications, memory access requests from multiple cores with the size of 64 bytes can be heavily interleaved. The situation is even worse for the Intel Harpertown processor with its UMA configuration, as the memory controller hub must mix memory access requests coming out from two different chips. For NVIDIA GPUs, the access granularities are 32, 64, and 128 bytes [98].

By contrast, the Cell/B.E. adopts a different memory subsystem. First, each SPE generates DMA requests with significantly larger sizes—up to 16 KB. Even for communication-intensive applications, each SPE issues DMA requests in an intermittent fashion. This minimizes the inter-core interference in DRAM accesses. Therefore, programmers can maximize the bandwidth utilization by increasing the size of DMA accesses [62, 110]. Thus, the Cell/B.E. architecture fundamentally lends itself to higher bandwidth utilization than other systems, in spite of the significant effort toward increasing bandwidth utilization in general purpose multicore processors [93, 79, 59]. The AMD Barcelona processor adopts optimized scheduling algorithms especially for interleaved DRAM access streams as well [9]. Williams, et al., also demonstrated the first-generation Cell/B.E.'s high bandwidth utilization [128], though an open question is the impact of adopting different DRAM technologies (i.e., the first- and second-generation Cell/B.E. architectures adopt different DRAM technologies, namely, XDR and DDR2, respectively). Finally, the Cell/B.E. has an additional advantage in optimizing its memory controller, as this processor targets streaming applications that are highly latency tolerant. The Cell/B.E.'s memory controller can focus on bandwidth utilization, while general purpose multicore processors attempt to address the significantly more difficult problem of balancing bandwidth utilization with fairness and latency issues [94, 93, 103].

#### 2.1.7 Ideal Software Implementations

To optimize the code for the Intel Harpertown, AMD Barcelona, and Cell/B.E. processors, one first needs to identify coarse-grain parallelism and partition data to exploit all the cores. One then needs to consider data layout for higher data transfer and vectorization efficiency. The Harpertown and Barcelona processors are significantly less sensitive to data alignment than the Cell/B.E., since they support multiple additional instructions for unaligned data accesses; however, data layout still affects the performance in a non-negligible amount. At high level, optimizing for the Cell/B.E. does not differ much from the Harpertown and Barcelona processors, but the actual implementation is significantly more complex as programmers need to explicitly program for data transfer within the local store size limit of 256 KB. In addition, the gap between the performance of baseline and optimized code is significantly higher for the Cell/B.E., and this often mandates manual optimization.

The optimization process for the Tesla C1060 is largely different from the above three processors. For the Tesla C1060, easily identifiable coarse-grain parallelism does not suffice to fully exploit the chip. Thus, the optimization should focus on extracting additional parallelism. To benefit from the high bandwidth and low latency on-chip memories, programmers need to modify an algorithm to maximize data sharing among multiple threads. Data coalescing and broadcasting mechanisms are also crucial to achieve high performance, and this also needs to be considered in algorithm design. For the Tesla C1060 or other CUDA enabled GPUs, the key challenge arises from high level algorithm design, and the actual implementation is less complex in terms of code size.

For the NUMA-based systems, one can gain significant speedup for bandwidth-intensive algorithms by controlling thread binding and data allocation. The optimization result for the Cell/B.E. often is more predictable than the x86 based architectures or the Tesla C1060 owing to its simpler architecture. For the x86 based architectures,

the multi-level memory hierarchy with different latency, size, and associativity in each level and complex and adaptive prefetching mechanisms across the memory hierarchy significantly complicate performance analysis. The Tesla C1060 optimization is complicated by its large search space as well, which is non-linear in nature [109].

## 2.2 Kernel Descriptions and Qualitative Analysis

For our evaluation, we consider two versions of covariance computation based on Pearson's method and Kendall's method, as implemented in the open-source R statistics package [3]. We also create the third Kernel by modifying the second kernel based on Kendall's method. Given two test data sets, represented by an  $n_X \times n$  matrix X, an  $n_Y \times n$  matrix Y, and pre-computed mean vectors  $\bar{x}$  and  $\bar{y}$  of length  $n_X$  and  $n_Y$ , respectively, the basic covariance computation (based on Pearson's method) produces an  $n_X \times n_Y$  matrix C such that

$$C_{ij} \leftarrow \frac{1}{n-1} \sum_{k=1}^{n} (X_{ik} - \bar{x}_i) \cdot (Y_{jk} - \bar{y}_j)$$

In this section, we describe the three kernels, and explain their high-level characteristics.

#### 2.2.1 Conventional Sequential Code

Code 2.1 presents the C implementation of the basic covariance kernel based on Pearson's method. We refer to this code as "Kernel1." "Kernel2" computes covariance using Kendall's method, and we artificially create "Kernel3" by modifying Kernel2. Code 2.2 depicts Kernel2 and Kernel3. Kernel1 and Kernel2 are adopted from the R project source code [3].

In Kernell, we can first subtract the mean vector from each matrix operand to remove the redundant subtracts. Then, transposing matrix Y converts this algorithm to a dense matrix multiplication problem, which is extensively studied and also there

```

//p_x: a pointer for X

//p_y: a pointer for Y

//p_xm: a pointer for \bar{x}

//\mathrm{p\_ym}\colon a pointer for ar{y}

//p_ans: a pointer for C

for (i = 0 ; i < n_X ; i++) {

p_{-}xx = &p_{-}x[i * n];

xxm = p_xm[i];

for (j = 0 ; j < n_Y ; j++) {

p_{y} = & p_{y} [j * n];

yym = p_ym[j];

sum = 0.0;

for (k = 0 ; k < n ; k++) {

sum \; +\! = \; (\; p\_x \, x \, [\; k \;] \; - \; xxm) \; * \; (\; p\_y \, y \, [\; k \;] \; - \; yym \, ) \, ;

p_{ans}[i * n_Y + j] = sum / (n - 1);

}

```

Code 2.1: C code for Kernel1

is a highly optimized BLAS library for the problem. Kernel2 and Kernel3 have more complex data access patterns but still can be optimized based on the cache blocking approach. Initially, we intentionally ignore these particular optimization opportunities for the following two reasons. First, we wish to stress the memory systems experimentally, and secondly, we want to show the more typical and intuitive optimization process that is common in practice. Then, if memory bandwidth turns out to be a performance bottleneck, we implement the blocking approach. We focus on highlighting the impact of architectural design trade-offs on performance and programmability. In particular, we do not intend to conclude which system is the "best" for computing covariance, nor do we claim to have implemented the best possible covariance code.

#### 2.2.2 Basic Algorithmic Analysis

The memory footprint of all three kernels is  $O((n_X + n_Y) \times n)$  and the size of two input matrices are typically much larger than mean vectors or the output matrix. The computational complexity is  $O(n_X \times n_Y \times n)$  for Kernel1 and  $O(n_X \times n_Y \times n^2)$  for Kernel2 and Kernel3. While these kernels are compute-intensive in their asymptotic

```

//p_x: a pointer for X

//p_y: a pointer for Y

//p_ans: a pointer for C

for (i = 0 ; i < n_X ; i++) {

p_x x = & p_x [i * n];

for (j = 0 ; j < n_Y ; j++) {

p_{y} = &p_{y} [j * n];

sum = 0.0;

for (k = 0 ; k < n ; k++)

for (n1 = 0 ; n1 < n ; n1++) {

#if SIGN//Kernel2

sum += sign((p_xx[k] - p_xx[n1])

* (p_y[k] - p_y[n1]);

#else//Kernel3

sum += (p_xx[k] - p_xx[n1])

* (p_yy[k] - p_yy[n1]);

#endif

p_ans[i * n_Y + j] = sum;

```

Code 2.2: C code for Kernel2 and Kernel3

notations, if the entire memory footprint does not fit into the on-chip memory of the test systems, then these kernels can be bandwidth-bound. All three kernels have obvious  $n_X \times n_Y$  way parallelism as every pair of rows from matrix X and Y can be computed independently. Also, if we ignore the floating-point associativity issues, we can also trivially parallelize the innermost loop of Kernel1 and the second innermost loop of Kernel2 and Kernel3. For Kernel1, if we execute the code in a sequential way, there is higher temporal locality in the row data of matrix X than the row data of matrix Y. For Kernel2 and Kernel3, if we can place two rows from matrix X and Y on on-chip memory, we can perform  $O(n^2)$  computation over O(n) data without off-chip memory access. The total number of flops executed by Kernel1 is  $(n_X + n_Y) \times n + n_X \times n_Y \times n \times 2$ , and  $n_X \times n_Y \times n^2 \times 4$  for Kernel2 and Kernel3.

## 2.3 Baseline Architecture-specific Implementations

For subsequent evaluation, we create a basic parallel implementation for each architecture, described in this section. These implementations include "baseline" parallelization and tuning, meaning they include some degree of platform-specific tuning but are not extensively tuned. Again, as Section 2.2.1 states, our focus is on system evaluation and not on kernel optimization.

# 2.3.1 Intel Harpertown (2P) and AMD Barcelona (4P) Multicore Implementations

We can easily parallelize the outermost loop of all three kernels with OpenMP or pthreads for our 8 and 16 core systems, assuming sufficiently large  $n_X$  ( $n_Y$ ). For Kernel1, we apply auto-vectorization with two directives,  $\#pragma\ unroll(16)$  and  $\#pragma\ vector\ aligned$ , achieving comparable performance to an intrinsics-based vectorization approach.

For Kernel2, sign() function involves branches, lowering the performance significantly. We replace the branch with an SSE compare  $(e.g., \_mm\_cmpgt\_pd())$  and  $\_mm\_cmplt\_pd())$  and bitwise operations  $(e.g., \_mm\_and\_pd())$  and  $\_mm\_or\_pd())$ . The Intel icc compiler have failed to perform this replacement automatically, and so we hand-code this translation to use SIMD intrinsics. The Kernel3 code can be trivially vectorized in the same way.

For the 4P Barcelona system, which is NUMA-based, our code replicates the input matrices to all four chips' local DRAM, and pins the threads to each core. The replication cost can be amortized with multiple reads, and this optimization maximizes the available bandwidth while minimizing the interference.

Even though our test kernels are asymptotically compute-intensive, if the input matrices do not fit into the on-chip cache memory, these algorithms can be bandwidthbound. The blocking approach can reduce the amount of off-chip data transfer at the cost of increased implementation complexity. Also, for the Harpertown and Barcelona processors, selecting the optimal block size requires exhaustive search over parameter space as it is a complex function of the multiple levels of cache hierarchy and their size and associativity. This exhaustive search is beyond the scope of our work and we set the block size based on heuristics.

#### 2.3.2 STI Cell/B.E. (2P) Implementation

The Cell/B.E. implementation resembles the 4P AMD Barcelona implementation, though the Cell/B.E. provides an additional opportunity for fine-tuning owing to the higher level of control over on-chip memory supported by the architecture. In particular, observe that a row data of matrix X has, assuming the given loop order, higher temporal locality than a row data of matrix Y. Thus, we can assign a larger buffer for matrix X than Y. Furthermore, to reduce the bandwidth requirement even when a single row does not fit into the local store, our code allocates additional small buffers for streaming. In this case, our code reads data from the larger buffer for matrix X and Y for accessing the initial part of the row (which fits into the local store), and then our code switches to the streaming mode with the smaller buffers for the remaining.

However, fine-grained control over on-chip memory significantly increases the coding complexity, especially when the on-chip memory requirement varies as a function of the input data size. The blocking approach, even though it adds additional complexity in high level, fixes the on-chip memory requirement regardless of the input data size. Accordingly, the blocking approach can reduce the coding complexity for the Cell/B.E. in addition to the improved performance. For the Cell/B.E., the impact of different block size is easier to understand owing to its simple memory subsystem. Larger block height reduces the amount of traffic whereas larger block width increases the iteration count of the innermost loop to improve the compute efficiency. We can

also simply pick the largest block size that fits into the local store instead of considering different cache sizes in the memory hierarchy.

#### 2.3.3 NVIDIA Tesla C1060 Implementation

For the NVIDIA Tesla C1060, the  $n_X \times n_Y$ -way parallelism may not be sufficient for practical data set sizes. Even when  $n_X \times n_Y$  is very large, having every thread processes a distinct pair of rows can lead to poor bandwidth utilization (no coalescing in data transfer) or low on-chip cache utilization (no data sharing). For Kernell, we partition the innermost loop with chunks of size 16 elements (a half warp, as high memory bandwidth utilization is achieved when the memory accesses from a half warp can be coalesced [98]). Each thread in a half warp processes one element out of 16 elements in a chunk to maximize the coalescing. For Kernel2 and Kernel3, we partition the second innermost loop identical to the case of Kernel1. In this case, every thread in a half warp traverses same row data in a synchronized way (in the innermost loop of Code 2.2, array index k remains constant and only array index n1 changes. In our optimized code, every thread in a same half warp accesses  $p_-xx$  and  $p_-yy$  with same n1 but different k), and we can use the on-chip shared memory to exploit this fact. As every thread accesses a same data element, we can use the shared memory's broadcasting mechanism as well.

One critical issue is sign() function, which involves branch instructions. The NVIDIA CUDA compiler replaces branch instructions with predicates when the number of instructions controlled by the branch is equal to or less than the threshold value (4 or 7 instructions) [98]. Therefore, by using the CUDA framework, we do not need to manually optimize for sign() function, as we do on the Intel Harpertown, AMD Barcelona, and Cell/B.E. platforms. Optimization for the Tesla C1060 is more involved in high level, but simpler to program than the Cell/B.E. for these kernels.

Also, the proper use of on-chip cache memory significantly reduces the bandwidth

requirement, and Kernel2 and Kernel3 become compute-bound even without explicit blocking.

#### 2.3.4 A Quantitative Comparison of Implementation Costs

**Table 3:** Quantitative comparison of implementation costs in terms of code size and implementation time. This excludes the code for kernel invocation and the residual part computation.

|                                     | kernel code size (# of | approximate coding |

|-------------------------------------|------------------------|--------------------|

|                                     | lines)                 | time               |

| Harpertown and Barcelona - initial  | 335                    | 1 day              |

| Harpertown and Barcelona - blocking | 419                    | 2 days             |

| Cell/B.E initial                    | 1620                   | 7 days             |

| Cell/B.E blocking                   | 1004                   | 2 days             |

| Tesla C1060 - initial               | 52  (Kernel1) + 97     | 2 days             |

|                                     | (Kernel2/3)            |                    |

| Tesla C1060 - blocking              | 88 (Kernel1)           | 1 day              |

Table 3 summarizes the comparison. For the Cell/B.E., the blocking approach fixes the local store space requirement regardless of the input data size, and simplifies the coding in addition to the improved performance. We can also identify that the code size for the Tesla C1060 is significantly smaller than the other architectures. For the Tesla C1060, the challenge is in extracting additional parallelism and best exploiting the memory subsystem (based on the data access coalescing and broadcasting mechanisms and the efficient use of the shared memory).

# 2.4 Experimental Results

Recall the evaluation platforms from Table 2. To measure the sustained bandwidth of the 2P Harpertown system, we use PAPI [2] and count the number of memory bus transactions. For the 4P Barcelona system, we use AMD CodeAnalyst [1] and count the number of DRAM accesses. For the systems with the Cell/B.E. processors, we attach counter variables to every DMA memory requests and ignore the PPE initiated traffic. For the Tesla C1060, we estimate the total bandwidth requirement using the following equations:  $n_X \times n_Y \times n \times \text{sizeof(float or double)} \times 2 \text{ for Kernel1}$

and  $n_X \times n_Y \times n \times n \times \text{sizeof}$ (float or double)  $\times 2 \times \frac{1}{16}$  (a half warp width, owing to data sharing) for Kernel2 and Kernel3. For the NUMA-based AMD Barcelona and Cell/-B.E. architectures, our code replicates matrix X and Y, which are read multiple times, for higher bandwidth utilization. The reported numbers include this replication cost and the off-loading overhead to the device memory in the Tesla C1060.

**Figure 3:** Sustained Gflop/s (left) and bandwidth utilization (GB/s) (right) for the initial (top) and the blocking based (bottom) implementations of Kernel1 (single-precision). Missing points for the QS20 are due to memory allocation failure. Here,  $n_X = n_Y = 1024$ .

**Figure 4:** Sustained Gflop/s (left) and bandwidth utilization (GB/s) (right) for the initial (top) and the blocking based (bottom) implementations of Kernel1 (double-precision). Missing points for the QS20 are due to memory allocation failure. Here,  $n_X = n_Y = 1024$ .

#### 2.4.1 Kernel1

The top half of Figure 3 depicts the sustained Gflop/s and bandwidth utilization for Kernel1 in single-precision with the initial implementation. Although the algorithm is computationally intensive, the performance is bounded by memory bandwidth since the entire data do not fit into the on-chip memory. The Tesla C1060 benefits from its high bandwidth to on-board DRAM, but the sustained bandwidth is lower than the theoretical peak and varies significantly for different input matrix sizes. The

off-loading overhead accounts for 18% (for the smallest matrix) to 2.4% (for the largest matrix) of the total execution time. The QS20 and QS22 blades achieves the highest bandwidth utilization on average across the different values of n owing to their DMA based data transfer mechanism with a large chunk size. The QS20 blade (with Rambus XDR) achieves higher bandwidth utilization than the QS22 blade (with DDR2). The 4P Barcelona system achieves significantly higher sustained bandwidth and bandwidth utilization than the 2P Harpertown system. This exemplifies the scalability benefit of the NUMA architecture. The AMD Barcelona equips optimized memory access scheduling algorithms for interleaved streaming accesses, and this also contributes to higher bandwidth utilization. However, the 2P Harpertown system delivers higher flop rates per unit bandwidth consumption owing to the large shared cache memory.