Universidade do Minho Escola de Engenharia

João Pedro Antunes Gomes da Silva Reis

### **Cache-based Timing Side-channels** in Partitioning Hypervisors

Dezembro de 2019

Universidade do Minho Escola de Engenharia

João Pedro Antunes Gomes da Silva Reis

# Cache-based Timing Side-channels in Partitioning Hypervisors

Dissertação de Mestrado em Engenharia Eletrónica Industrial e Computadores

Trabalho efetuado sob a orientação do

**Professor Doutor Sandro Pinto**

Dezembro de 2019

#### DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada.

Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

Atribuição-NãoComercial-Compartilhalgual CC BY-NC-SA

https://creativecommons.org/licenses/by-nc-sa/4.0/

### **Agradecimentos**

As minhas primeiras palavras de apreço são dirigidas ao meu orientador Professor Doutor Sandro Pinto, pela partilha de conhecimento e sugestões ao longo da dissertação. De igual forma, agradeço ao Mestre José Martins pela prontidão e celeridade com que acorreu às minhas dúvidas. A disponibilidade que sempre demonstraram no decorrer da dissertação e o informalismo que demarcou a nossa relação, tornaram a realização da dissertação um projeto proveitoso e aprazível.

A todos os meus companheiros do laboratório *Embedded Systems Research Group* que me acompanharam durante a dissertação, agradeço os momentos importantes de companheirismo vividos durante o ano.

Em último, mas não menos importante, agradeço à minha família, especialmente aos meus pais e ao meu irmão, por me terem dado apoio incondicional e me terem alegrado nos momentos de maior angústia.

Um obrigado a todos!

#### STATEMENT OF INTEGRITY

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

### Abstract

#### **Cache-based Timing Side-channels in Partitioning Hypervisors**

In recent years, the automotive industry has seen a technology complexity increase to comply with computing innovations such as autonomous driving, connectivity and mobility. As such, the need to reduce this complexity without compromising the intended metrics is imperative.

The advent of hypervisors in the automotive domain presents a solution to reduce the complexity of the systems by enabling software portability and isolation between virtual machines (VMs).

Although virtualization creates the illusion of strict isolation and exclusive resource access, the convergence of critical and non-critical systems into shared chips presents a security problem. This shared hardware has microarchitectural features that can be exploited through their temporal behavior, creating sensitive data leakage channels between co-located VMs. In mixed-criticality systems, the exploitation of these channels can lead to safety issues on systems with real-time constraints compromising the whole system.

The implemented side-channel attacks demonstrated well-defined channels, across two real-time partitioning hypervisors in mixed-criticality systems, that enable the inference of a co-located VM's cache activity. Furthermore, these channels have proven to be mitigated using cache coloring as a countermeasure, thus increasing the determinism of the system in detriment of average performance.

From a safety perspective, this dissertation emphasizes the need to weigh the tradeoffs of the trending architectural features that target performance over predictability and determinism.

Keywords: Automotive Industry, Mixed-criticality Systems, Side-channel Attacks, Virtualization

### Resumo

#### **Cache-based Timing Side-channels in Partitioning Hypervisors**

Nos últimos anos, a indústria automotiva tem sido objeto de um crescendo na sua complexidade tecnológica de maneira a manter-se a par das mais recentes inovações de computação. Sendo assim, a necessidade de reduzir a complexidade sem comprometer as métricas pretendidas é imperativa.

O advento dos hipervisores na indústria automotiva apresenta uma solução para a redução da complexidade dos sistemas, possiblitando a portabilidade do software e o isolamento entre *virtual vachines* (VMs).

Embora a virtualização crie a ilusão de isolamento e acesso exclusivo a recursos, a convergência de sistemas críticos e não-críticos em *chips* partilhados representa um problema de segurança. O hardware partilhado tem características microarquiteturais que podem ser exploradas através do seu comportamento temporal, criando canais de fuga de informação crítica entre VMs adjacentes. Em sistemas de criticalidade mista, a exploração destes canais pode comprometer sistemas com limitações de tempo real.

Os ataques *side-channel* implementados revelam canais bem definidos que possibilitam a inferência da atividade de cache de VMs situadas no mesmo processador. Além disso, esses canais provaram serem passíveis de ser mitigados usando *cache coloring* como estratégia de mitigação, aumentando assim o determinismo do sistema em detrimento da sua performance.

De uma perspetiva da segurança, esta dissertação enfatiza a necessidade de pesar os *tradeoffs* das tendências arquiteturais que priorizam a performance e secundarizam o determinismo e previsibilidade do sistema.

**Palavras-chave:** Ataques *Side-channel*, Indústria Automotiva, Sistemas de Criticalidade Mista, Virtualização

## Contents

| Lis | List of Figures x |           |                       |     |      |  |

|-----|-------------------|-----------|-----------------------|-----|------|--|

| Lis | ist of Tables xiv |           |                       |     |      |  |

| Lis | t of L            | istings   |                       |     | xvi  |  |

| Glo | ossary            | /         |                       | )   | cvii |  |

| 1   | Intro             | duction   | I                     |     | 1    |  |

|     | 1.1               | Goals .   |                       | ••• | 2    |  |

| 2   | Back              | ground    |                       |     | 3    |  |

|     | 2.1               | State of  | Art                   |     | 3    |  |

|     | 2.2               | Virtualiz | ration                |     | 4    |  |

|     |                   | 2.2.1     | Definition            |     | 4    |  |

|     |                   | 2.2.2     | Advantages            |     | 5    |  |

|     |                   | 2.2.3     | Disadvantages         |     | 6    |  |

|     |                   | 2.2.4     | Hypervisors           |     | 7    |  |

|     | 2.3               | Jailhous  | se                    |     | 8    |  |

|     |                   | 2.3.1     | Terminology           |     | 10   |  |

|     |                   | 2.3.2     | Operation             |     | 10   |  |

|     | 2.4               | Bao .     |                       |     | 13   |  |

|     | 2.5               | Caches    |                       |     | 14   |  |

|     |                   | 2.5.1     | Definition            |     | 15   |  |

|     |                   | 2.5.2     | Cache Lines or Blocks |     | 15   |  |

|     |                   | 2.5.3     | Cache Associativity   |     | 16   |  |

|   |      | 2.5.4    | Cache Replacement Policies            | 17 |

|---|------|----------|---------------------------------------|----|

|   |      | 2.5.5    | Cache Inclusion Policies              | 18 |

|   |      | 2.5.6    | Cache Indexing                        | 19 |

|   |      | 2.5.7    | Cache Coherence                       | 20 |

|   | 2.6  | Side an  | d Covert Channels                     | 21 |

|   |      | 2.6.1    | Definition                            | 21 |

|   |      | 2.6.2    | Benchmarks                            | 21 |

|   |      | 2.6.3    | Attack Types                          | 23 |

|   |      | 2.6.4    | Countermeasures                       | 26 |

| 3 | Anal | ysis     |                                       | 29 |

|   | 3.1  | Attack S | Strategy                              | 29 |

|   |      | 3.1.1    | Experimental System Definition        | 29 |

|   |      | 3.1.2    | Resources Sharing Level Definition    | 30 |

|   |      | 3.1.3    | Temporal Concurrency Level Definition | 31 |

|   |      | 3.1.4    | Exploitation Technique Definition     | 32 |

|   | 3.2  | Attack ( | Challenges                            | 32 |

|   |      | 3.2.1    | Prime Step Challenges                 | 32 |

|   |      | 3.2.2    | Probe Step Challenges                 | 38 |

| 4 | Desi | gn       |                                       | 41 |

|   | 4.1  | Propose  | ed Channels                           | 41 |

|   |      | 4.1.1    | Simple Channel                        | 42 |

|   |      | 4.1.2    | Bits Transmission Channel             | 46 |

| 5 | Impl | ementa   | tion                                  | 52 |

|   | 5.1  | System   | Configuration                         | 52 |

|   |      | 5.1.1    | Jailhouse                             | 52 |

|   |      | 5.1.2    | Jailhouse with cache coloring         | 56 |

|   |      | 5.1.3    | Bao Hu                                | 60 |

|   |      | 5.1.4    | Bao Hu with cache coloring            | 62 |

|   | 5.2  | Eviction | n Strategy                            | 63 |

|   | 5.3  | Attack Challenges |                                |    |

|---|------|-------------------|--------------------------------|----|

|   |      | 5.3.1             | Prime Step                     | 65 |

|   |      | 5.3.2             | Probe Step                     | 68 |

|   | 5.4  | Propose           | ed Channels                    | 69 |

|   |      | 5.4.1             | Simple Channel                 | 70 |

|   |      | 5.4.2             | Bits Transmission Cannel       | 73 |

|   | 5.5  | Counter           | measures                       | 75 |

| 6 | Eval | uation            |                                | 78 |

|   | 6.1  | Experim           | nental Setup                   | 78 |

|   | 6.2  | Eviction          | Strategy                       | 79 |

|   |      | 6.2.1             | AutoLock's Eviction Strategy   | 79 |

|   |      | 6.2.2             | ARMageddon's Eviction Strategy | 80 |

|   | 6.3  | Propose           | ed Channels                    | 81 |

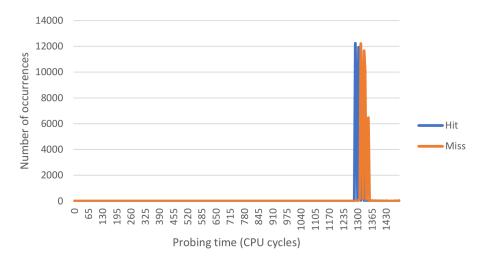

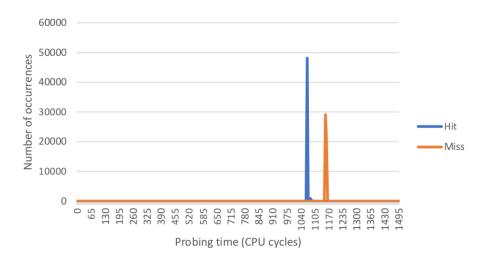

|   |      | 6.3.1             | Simple Channel                 | 81 |

|   |      | 6.3.2             | Bits Transmission Channel      | 83 |

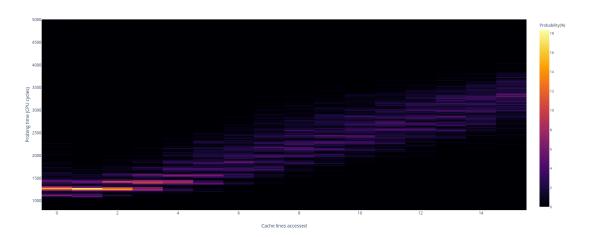

|   | 6.4  | Counter           | measures                       | 84 |

|   |      | 6.4.1             | First Channel                  | 84 |

| 7 | Cond | lusion            |                                | 88 |

|   | 7.1  | Future \          | Nork                           | 88 |

## **List of Figures**

| 2.1  | Illustration of a system virtualization stack with Type-1 hypervisor.                      | 8  |

|------|--------------------------------------------------------------------------------------------|----|

| 2.2  | Illustration of a system virtualization stack with Type-2 hypervisor.                      | 8  |

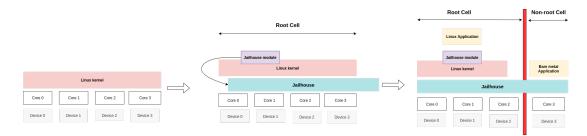

| 2.3  | Illustration of Jailhouse's partitioning scheme.                                           | 9  |

| 2.4  | Typical RAM layout in <i>ZCU104 Evaluation kit</i> .                                       | 12 |

| 2.5  | Example of the Jailhouse's activation procedure. After being initialized, Jailhouse        |    |

|      | reassigns hardware to Linux and a Bare metal application                                   | 13 |

| 2.6  | Illustration of the memory hierarchy with 2 cache levels. From the top to the bottom, the  |    |

|      | memory technology enlarges and gets slower.                                                | 15 |

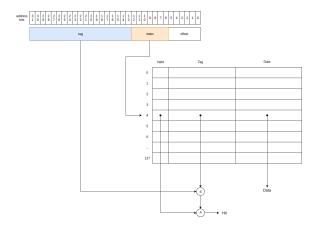

| 2.7  | Direct mapped cache                                                                        | 17 |

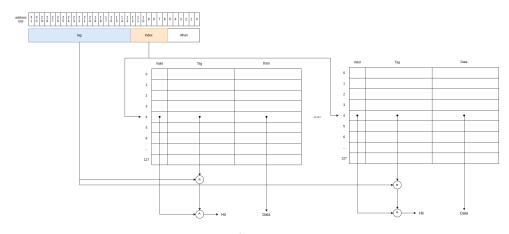

| 2.8  | Set associative cache                                                                      | 17 |

| 2.9  | Illustration of a cache coherence problem                                                  | 20 |

| 2.10 | Channel matrix for the unmitigated L1 I-cache channel on Sandy Bridge platform             | 23 |

| 2.11 | Channel matrix for the mitigated L1 I-cache channels on Hikey platform.                    | 23 |

| 2.12 | Illustration of the Prime+Probe attack by means of a 4-way (columns) cache with 8 sets     |    |

|      | (rows)                                                                                     | 24 |

| 2.13 | Illustration of the Flush+Reload attack by means of a 4-way (columns) cache with 8 sets    |    |

|      | (rows)                                                                                     | 25 |

| 2.14 | Disposition of colour bits in a 32-bits PA address from the point of view of an OS, L1 and |    |

|      | L2 (PIPT) caches                                                                           | 28 |

| 3.1  | Mixed-criticality system using Jailhouse as hypervisor. The first 3 cores are assigned to  |    |

|      | Linux, and the other core is within Erika RTOS's domain                                    | 30 |

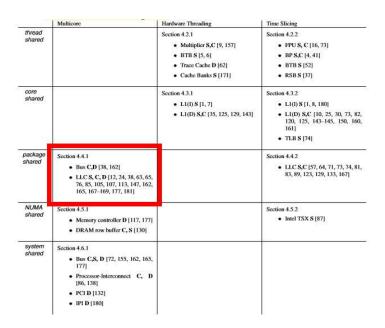

| 3.2  | Contended resources in a hierarchical multicore system with 3 cache levels [1]. Within             |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | the red rectangle, it is represented the resource sharing level intended to be studied and         |    |

|      | replicated.                                                                                        | 30 |

| 3.3  | Table with known microarchitectural timing attacks.                                                | 31 |

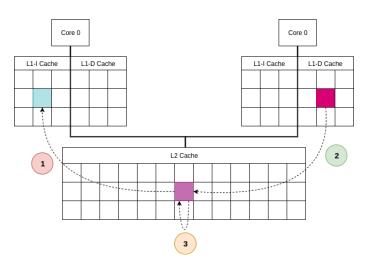

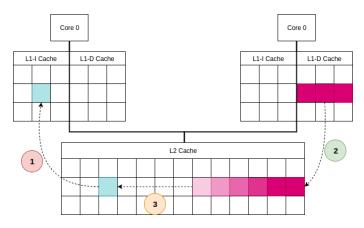

| 3.4  | Cross-core instruction cache eviction through data accesses on a instruction- inclusive,           |    |

|      | data-non-inclusive cache.                                                                          | 33 |

| 3.5  | Cross-core instruction cache eviction through data accesses on a instruction- inclusive,           |    |

|      | data-non-inclusive cache.                                                                          | 34 |

| 3.6  | Example of <i>/proc/self/maps</i> output when using a Linux application                            | 37 |

| 3.7  | Effect of 2MB-sized huge pages on <i>Cortex-A53 MPCore</i> 's caches address translation           | 38 |

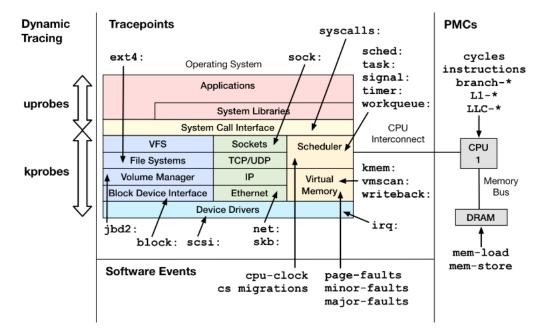

| 3.8  | Map of Linux event sources used by perf tool.                                                      | 39 |

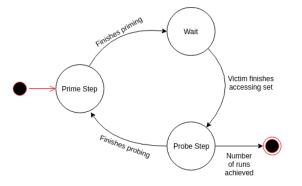

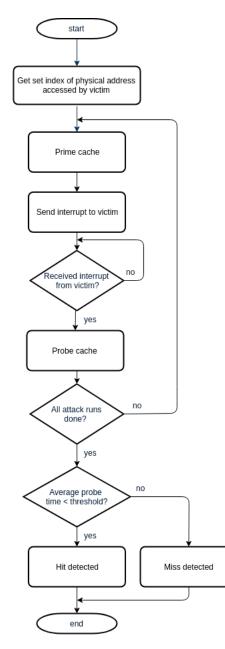

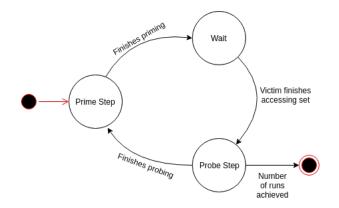

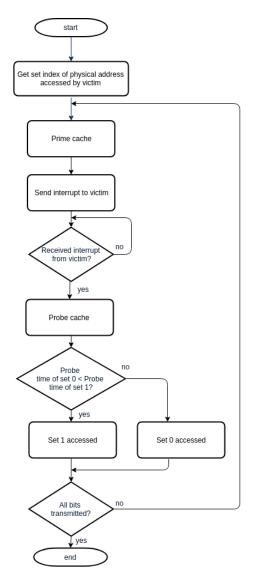

| 4.1  | Attacker state machine during the attack that allows observing the Simple Channel                  | 42 |

| 4.2  | Victim state machine during the attack that allows to observe the Simple Channel. $\ . \ .$        | 43 |

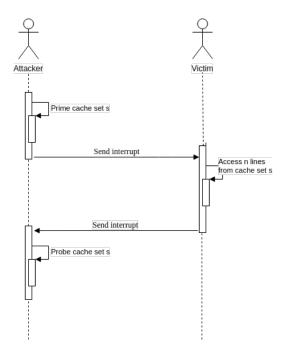

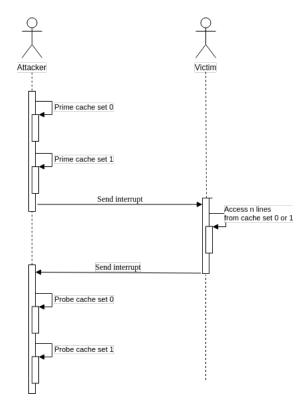

| 4.3  | Sequence diagram of the attack that allows to observe the Simple Channel                           | 43 |

| 4.4  | Attacker's flow chart during the attack that allows to observe the Simple Channel                  | 45 |

| 4.5  | Victim's flow chart during the attack that allows to observe the Simple Channel                    | 46 |

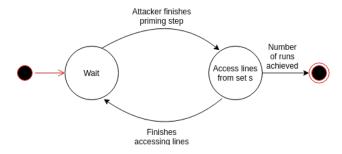

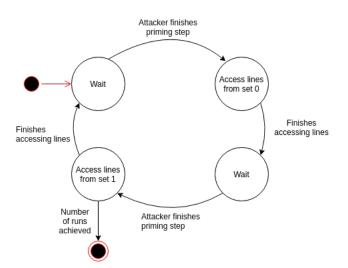

| 4.6  | Attacker state machine during the attack that allows observing the Bits Transmission               |    |

|      | Channel                                                                                            | 48 |

| 4.7  | Victim state machine during the attack that allows observing the Bits Transmission Channel.        | 48 |

| 4.8  | Sequence diagram of the attack that allows to observe the Bits Transmission Channel. $\ .$         | 49 |

| 4.9  | Attack's flow chart during the attack that allows to observe the Bits Transmission Channel.        | 50 |

| 4.10 | Victim's flow chart during the attack that allows to observe the Bits Transmission Channel.        | 51 |

| 5.1  | RAM's layout after configuring the system                                                          | 56 |

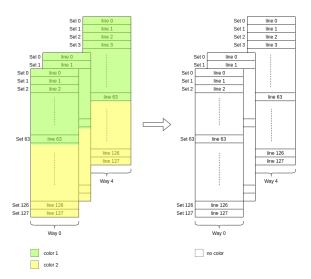

| 5.2  | L1-I cache with the highest index bit colored (left picture) and without coloring (right picture). | 75 |

| 5.3  | Coloring assignment with L1 cache coloring (above picture) and without L1 cache                    |    |

|      | coloring (below picture)                                                                           | 76 |

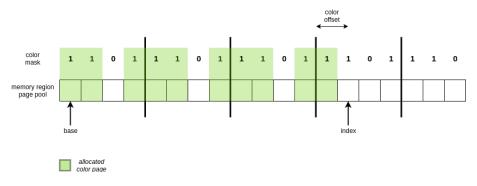

| 5.4  | Hypervisor's search mechanism for the next colored page                                            | 77 |

| 6.1  | Line graph for cache timing results on <i>ZCU104 Evaluation Kit</i> using N-A-D 23-2-5             | 80 |

| 6.2  | Line graph for cache timing results on <i>ZCU104 Evaluation Kit</i> using N-A-D 25-2-6             | 81 |

| 6.3 | Channel matrix for the unmitigated LLC channel on ZCU104 Evaluation Kit using a bare |    |  |

|-----|--------------------------------------------------------------------------------------|----|--|

|     | metal guest as the victim                                                            | 82 |  |

| 6.4 | Sample sequence of attacker's access time on <i>ZCU104 Evaluation Kit</i>            | 83 |  |

| 6.5 | Channel matrix for the mitigated LLC channel on ZCU104 Evaluation Kit using a bare   |    |  |

|     | metal guest as the victim                                                            | 85 |  |

| 6.6 | Memory latency of a partition on <i>ZCU104 Evaluation Kit</i>                        | 86 |  |

## **List of Tables**

| 3.1 | Different eviction strategies on <i>Cortex-A53</i>       | 36 |

|-----|----------------------------------------------------------|----|

| 6.1 | Hardware characteristics of <i>Cortex-A53</i> processor. | 79 |

## **List of Listings**

| 2.1  | Non-root cell code example                                                          |    |  |

|------|-------------------------------------------------------------------------------------|----|--|

| 5.1  | Memory reservation code. The mem= kernel boot parameter sets the available physical |    |  |

|      | memory and reserves the rest of the memory                                          | 52 |  |

| 5.2  | Root cell configuration code.                                                       | 53 |  |

| 5.3  | Non-root cell configuration code                                                    | 54 |  |

| 5.4  | Root cell configuration code.                                                       | 57 |  |

| 5.5  | Non-root cell configuration code                                                    | 58 |  |

| 5.6  | Non-root cell configuration code                                                    | 59 |  |

| 5.7  | Bao Hu guest images assignment                                                      | 61 |  |

| 5.8  | Bao Hu shared memory declarations                                                   | 61 |  |

| 5.9  | Bao Hu memory region assignment for Linux guest                                     | 61 |  |

| 5.10 | Bao Hu colored shared memory declarations.                                          | 62 |  |

| 5.11 | Bao Hu memory region assignment for colored Linux guest                             | 63 |  |

| 5.12 | Hit simulation function.                                                            | 64 |  |

| 5.13 | Miss simulation function.                                                           | 64 |  |

| 5.14 | Code to get physical address recurring to <i>/proc/self/pagemap</i>                 | 65 |  |

| 5.15 | Code to get physical address recurring to <i>/proc/self/pagemap</i>                 | 66 |  |

| 5.16 | Find congruent addresses used during Prime step code                                | 66 |  |

| 5.17 | Eviction strategy used during Prime step code                                       | 67 |  |

| 5.18 | Backwards access strategy used during Probe step code                               | 68 |  |

| 5.19 | perf syscall used during Probe step code                                            | 68 |  |

| 5.20 | perf syscall used during Probe step code                                            | 69 |  |

| 5.21 | First channel root cell code example.                                               | 70 |  |

| 5.22 | First channel root cell code example.                                               | 71 |  |

| 5.23 | First channel code example                          | 71 |

|------|-----------------------------------------------------|----|

| 5.24 | First channel root cell code example.               | 72 |

| 5.25 | First channel non-root cell code example.           | 73 |

| 5.26 | First channel code example                          | 73 |

| 5.27 | Second channel non-root cell code example           | 74 |

| 5.28 | Function that searches for the next available page. | 76 |

## Glossary

| ABI   | Application Binary Interface              |

|-------|-------------------------------------------|

| ACP   | Accelerator Coherency Port                |

| ACTLR | Auxiliary Control Register                |

| AMBA  | Advanced Microcontroller Bus Architecture |

| API   | Application Programming Interface         |

| APU   | Application Processor Unit                |

| ASIC  | Aplication Specific Integratedd Circuit   |

| AXI   | Advanced Extensible Interface             |

| CE    | Consumer Electronics                      |

| CPU   | Central Processing Unit                   |

| DCU   | Domain Control Unit                       |

| DMA   | Direct Memory Access                      |

| DMAC  | Direct Memory Access Controller           |

| DoS   | Denial-of-Service                         |

| DPR   | Dynamic Partial Reconfiguration           |

| DRAM  | Dynamic Random-Access Memory              |

| DSP   | Digital Signal Processing                 |

| E/E   | Electrical/Electronic                     |

| ECU   | Engine Control Unit                       |

| FIQ   | Fast Interrupt Request                    |

| FPGA  | Field Programmable Gate Array             |

| GIC   | Generic Interrupt Controller              |

| GPIO  | General-Purpose Input/Output              |

|       |                                           |

| GPOS      | General-Purpose Operating System          |

|-----------|-------------------------------------------|

| I/O       | Input/Output                              |

| laaS      | Infrastructure-as-a-Service               |

| IDE       | Integrated Development Environment        |

| ΙΟΜΜυ     | Input/Output Memory Management Unit       |

| ΙοΤ       | Internet of Things                        |

| IPC       | Inter-Partition Communication             |

| IPI       | Inter-Processor Interrupt                 |

| IRQ       | Interrupt Request                         |

| ISR       | Interruption Service Routines             |

| IVI       | In-Vehicle Infotainment                   |

| LLC       | Last-level Cache                          |

| LR        | Linker Register                           |

| LTZVisor  | Lightweight TrustZone-assisted Hypervisor |

| MMU       | Memory Management Unit                    |

| MPMU      | Message Passing Management Unit           |

| ОСМ       | On-Chip Memory                            |

| <b>0S</b> | Operating System                          |

| PA        | Physical Address                          |

| PFN       | Page Frame Number                         |

| PIPT      | Physically Indexed, Physically Tagged     |

| ΡΙΥΤ      | Physically Indexed, Virtually Tagged      |

| PL        | Programmable Logic                        |

| PS        | Processing System                         |

| RAM       | Random-Access Memory                      |

| ROM       | Read-Only Memory                          |

| RTOS      | Real-Time Operating System                |

| SCTLR     | System Control Register                   |

| SCU       | Snoop Control Unit                        |

| SLCR      | System-Level Control registers            |

| SMC       | Secure Monitor Call                       |

|           |                                           |

| SMT  | Simultaneous Multithreading          |

|------|--------------------------------------|

| SoC  | System on-Chip                       |

| SP   | Stack Pointer                        |

| SPSR | Saved Program Status Register        |

| SRAM | Static Random-Access Memory          |

| тсв  | Trusted Computing Base               |

| TZ   | TrustZone                            |

| VIPT | Virtually Indexed, Physically Tagged |

| νιντ | Virtually Indexed, Virtually Tagged  |

| VM   | Virtual Machine                      |

| VMCB | Virtual Machine Control Block        |

| VMM  | Virtual Machine Monitor              |

| XSDK | Xilinx Software Development Kit      |

## **1. Introduction**

The embedded systems used to be relatively simple, single-purpose devices with very specific functionalities focused on meeting hardware constraints and real-time requirements, thus exhibiting low to moderate software complexity. Over the years, while still being resource-constrained and keeping their real-time behavior, they started trending towards general-purpose systems with much more functionalities that impose a growth in software complexity [2], as it has been the automotive industry's case [3].

With the rising use of consumer electronics, comes a rising expectancy of infotainment-wise performance of modern vehicles. As such, the automotive industry must bridge the gap between consumers' expectations for infotainment features and the current performance of today's automotive systems. To address these problems, virtualization is emerging as a key solution.

Among the many benefits virtualization brings in the automotive domain, software portability and isolation between VMs stand as the most important features in virtualized automotive systems. With virtualization, the automotive systems can be separated into critical and non-critical partitions, allowing the integration of components with different criticality levels onto modern multi-core System on-Chips (SoCs) [4]. This feature makes it possible for the firmware of one partition (e.g., non-critical) to be updated without affecting the other, thus reducing the overall time-to-market and manufacturing costs [5] [6]. At the lower level, resides a hypervisor to enforce isolation - thus, reliability and safety - between the guest operating systems.

The automotive industry is also dependent on virtualization solutions due to the amount of needed Electronic Control Units (ECUs), which, prior to virtualization application, would require a set of dedicated microcontrollers, and which are currently being consolidated into fewer platforms, named Domain Control Units (DCUs).

While it is true that the isolation of VMs from each other was and is one of the goals of virtualization, it is inappropriate to consider the latter as a technique for bringing security into a system [7]. This results from the fact that using VMs may not be as secure as running OSes on dedicated physical hardware each.

Consequently, extreme precautions need to be taken in order to not introduce security risks and attack vectors with virtualization, otherwise, the safety of modern vehicles can be compromised.

The security and safety of a vehicle are tightly coupled, as one metric compromises the other. If a mixed-criticality system is vulnerable to attacks, the execution of critical tasks, such as airbag deployment, can be delayed by populating a cache that is shared by two critically-different VMs through a non-critical domain [5]. As the cache is shared, the non-critical domain can populate the shared cache, with the result that the content stored by the critical domain can be evicted, hence provoking cache misses at the next access. This phenomenon may generate large and unpredictable interference across domains, thus breaking isolation by introducing a strong coupling of their timing properties.

The shared hardware has microarchitectural features, such as control speculation [8], shared caches [9][10][1] or interruption service routines (ISRs) [11] that can be exploited through their temporal behavior, creating sensitive data leakage channels between co-located VMs. These channels can occur at any degree of hardware sharing and concurrency involved, as long as there are at least two VMs within the same chip [1].

This thesis focuses on the open problem of microarchitectural timing channels, which exploit timing variations to leak information between co-located VMs. They are harder to deal with, partially because of the breadth of exploitable mechanisms, being the usual defence to strive for deterministic execution time via constant-time algorithms [9] [12], which degrades substantially the system's performance.

#### 1.1 Goals

The goals to be achieved are summarized as follows:

- 1. Replicate the timing side-channel attacks which explore the microarchitecture of ARM-based platforms.

- Show the effectiveness of these attacks when the targeted system's security is not appropriately secured by an hypervisor which provides isolation across VMs, by benchmarking the replicated attacks.

- 3. Propose different mitigation strategies which prove to be relevant across similar ARM-based platforms, ultimately bringing security into the system.

### 2. Background

In this chapter, it is provided the required preliminaries and discussed related work in the context of cache attacks.

The themes addressed in this chapter range from the detection of exploitable modern caches' properties, to the dissection of known countermeasures against cache attacks. The concept of virtualization and its prominence in the embedded systems' world are briefly explained to introduce the software (i.e., Jailhouse, Bao) that is leveraged to find channels and upgraded to mitigate them.

#### 2.1 State of Art

Back in 1996, Kocher et al. [13] showed that it is possible to find factor RSA keys and break other cryptographic systems by measuring the execution time of private key operations. In 1999 Kocher et al. [14] introduced Simple Power Analysis (SPA) and Differential Power Analysis (DPA) where an attacker can extract cryptographic keys by studying the power consumption of a device.

Then, a different kind of side-channel focused on exploring the memory hierarchy, more specifically the caches, was introduced. Cache side-channel attacks exploit the different access times of memory addresses that are either held in the cache or the main memory. While the *Evict+Time* and *Prime+Probe* techniques by Osvik et al. [15] explicitly targeted cryptographic algorithms, Yarom et al. [16] introduced the *Flush+Reload* attack in 2014 that laid the foundation for new attack scenarios. The *Flush+Reload* attack allows an attacker to determine which specific parts of a shared library or a binary executable have been accessed by the victim with unprecedented high accuracy.

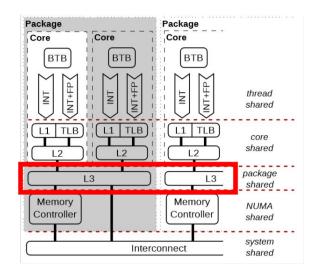

Although a major part of the known side-channel attacks targets the caches, they do not restrict to only one component of the microarchitecture. As Heiser et al. [1] demonstrated, these attacks occur across all hardware sharing levels (i.e., thread shared through system shared) and concurrency involved (i.e., full concurrency, time-sliced execution on a single core, or hardware threading). Heiser et al. [1] affirmed that

the attacks that occur closer to the core tend to achieve higher severity because they have more precise information available, while those at lower levels (e.g. the bus interconnect) could be mostly used to cause interference, thus jeopardizing the determinism of the co-located cores.

In 2015, Heiser et al. [17] have used cross-core cache attacks that relied on the inclusiveness of Lastlevel Caches (LLCs). The problem is that only the x86 architectures and the recent ARMv8 architectures used inclusive LLCs. To the other architectures that didn't use inclusive LLCs, Irazoqui et al. [18] exploited cache coherence protocols to mount cross-core cache attacks on SoCs with non-inclusive shared LLCs.

In 2016, Moritz et al. [19] attacked cryptographic implementations and utilized microarchitectural timing side-channel attacks to infer sensitive information (e.g., to differentiate between entered letters and special keys on the keyboard, or measure the length of swipe and touch gestures) of ARM-based smartphones. This disclosed the immense threat that those attacks represent, since they can be mounted on millions of stock Android devices without the requirement of any privileges or permissions.

In 2018, Heiser et al. [1] summarised all microarchitectural attacks known to date, alongside existing mitigation strategies, and developed a taxonomy based on both the degree of hardware sharing and concurrency involved.

#### 2.2 Virtualization

The increasing importance of isolation and security in modern systems (either for cloud servers which hold, more than ever, confidential and critical information, and more recently, embedded systems which are responsible for performing critical operations [20][21][22]), the underutilization of hardware, the increase in raw speed of processors over the decades (which makes the overhead of VMs more tolerable) and the preference of multicore processors over single-core processors [2] [7], paved the way to a natural adoption of the virtualization technology by the enterprise, cloud computing and embedded systems domains [23].

#### 2.2.1 Definition

Virtualization in general terms refers to the act of creating or using a virtual version of a resource (e.g., computer hardware platforms, operating systems, storage devices or network resources) rather than the physical one [24].

A virtual machine (VM) is commonly defined as a software program that emulates the behavior of a separate computer system, being capable of performing tasks such as running applications and programs

like a separate computer. The emulated system is called the *guest* system and the system on which it is being emulated is called the *host* system. The concept of emulation allows software or a peripheral designed for the guest system to be executed on the host system.

In virtualized systems, a single computer can run multiple VMs supporting a number of different operating systems (OSes) with all of them sharing the hardware resources. This contrasts with a conventional platform, where a single OS owns all hardware resources and no other OS can obtain them [25].

#### 2.2.2 Advantages

The relevance of virtualization in embedded systems stems from the ability to address some of the new challenges posed by them.

There are 3 main advantages regarding the use of virtualization on modern machines:

Improving protection, as it allows Infrastructure-as-a-Service (IaaS) companies (e.g., Amazon Web Services) to protect users from each other while sharing the same server [25], and general-purpose systems from jeopardizing systems with real-time constraints under the same hardware resources [2].

The protection is guaranteed as the access to memory between guests is not reachable by userland, because the accessed memory is perceived by the users as the physical one, instead of a virtual one which is then remapped to a physical address.

- 2. Managing software, which enables a developer to run multiple systems (some of them stable, and other, unstable releases) in one virtualized server without having a bunch of servers sitting around for the occasional use of tests [25], or providing architectural abstraction, as the same software architecture can be migrated essentially unchanged between a multicore and a (virtualized) single-core [2].

- 3. Managing hardware, by enabling the concurrent execution of an application OS (e.g., Linux) and a real-time OS (RTOS) on the same processor. This way, virtualization provides support for heterogeneous operating-system environments, as a way to address the conflicting requirements of high-level APIs for application programming, real-time performance, and legacy support [2].

Furthermore, the embedded systems can use the hardware management feature to meet their realtime constraints, which means: (i) managing the power consumption of a system by dynamically adding cores to an application domain which requires extra processor power, or (ii) removing processors and shutting down idle cores.

#### 2.2.3 Disadvantages

The costs of using virtualization in a business context depend on the requirements to run virtual machines. The embedded systems environment distinguishes from the server/desktop environment by its resource-constrained nature. The embedded systems are, by their nature, highly integrated and this characteristic conflicts with the isolation factor that virtualization brings onto them. Hence, there needs to be an effort made to not compromise the functional requirements of the embedded system without neglecting the isolation between the subsystems that compose a modern embedded system [21][? ][26].

The aforementioned advantages that made the virtualization a must on modern embedded systems, have some intrinsic mismatches with the embedded systems requirements that need to be addressed:

- Scheduling, as both co-located VMs are treated as black boxes with universal priorities, neglecting the fact that within the real-time VMs there are tasks that should interleave with tasks of the other general-purpose VMs [2].

- 2. Software complexity problem, that can lead, among other problems, to performance deterioration. Virtualization introduces a layer of memory abstraction that increases cache contention, mostly related to the frequent invocation of the hypervisor's enter-and-exit operations [27], and an increase in time taken to do memory operations, as every operation has to look up in page table, which means it needs to access the page table and then the memory address.

One can conclude that the process of virtualization can be used to provide platform independence and a secure environment for execution but this comes at a cost. Hence, one must ensure that embedded hypervisors are used only when needed and the overhead and performance dip is well compensated by the use of caching or multicore environments [24].

#### 2.2.4 Hypervisors

With the increasing importance of virtualization in embedded systems, comes the need to address the software layer that underlies the VMs. This section presents the definition and how hypervisors have evolved into different implementations that can be classified in many ways.

#### 2.2.4.1 Definition

The software that supports VMs is called a virtual machine monitor (VMM) or hypervisor, and presents a code size much smaller than a traditional OS. The underlying hardware platform is called the host, and its resources are shared among the guest VMs. The hypervisor determines how to map virtual resources to physical resources: a physical resource may be time-shared, partitioned, or even emulated in software [4] [21].

It presents a software interface to guest software, it must isolate the state of guests from each other, it must protect itself from guest software, and it must ensure that the guest system only interacts with virtual resources (i.e. a conventional guest OS runs as a user-mode program on top of the hypervisor) [4][25].

The qualitative requirements are:

- Guest software should behave on a VM exactly as if it were running on the native hardware (to improve emulation speed), except for performance-related behavior or limitations of fixed resources shared by multiple VMs [25]. This can be acquired by making the ISA of the VM the same as the host.

- 2. Guest software should not be able to change the allocation of real system resources directly [25].

To improve the performance of virtual machines, it is needed to:

- 1. Reduce the cost of processor virtualization [21].

- 2. Reduce interrupts overhead cost due to the virtualization [21].

- 3. Reduce interrupt cost by steering interrupts to the proper VM without invoking the hypervisor [21].

#### 2.2.4.2 Classification

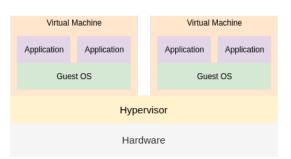

There are two types of hypervisors:

Type-1 - it runs directly on the hosting hardware to control it and to handle guest operating systems

[21] [26];

Figure 2.1: Illustration of a system virtualization stack with Type-1 hypervisor.

2. **Type-2** - hypervisor is provided as an extension to an operating system that is executed on the host while the guests run as tasks [21] [26].

Figure 2.2: Illustration of a system virtualization stack with Type-2 hypervisor.

Another element of distinction comes from the API exposed by the host to the generic guest OS:

- 1. **Full Virtualization** the guest executes transparently and without software modifications, while the hypervisor provides the API to emulate the underlying platform [26][28];

- Paravirtualization the guest is aware of the presence of virtualization. Thus it uses an API similar, but not identical, to that of the underlying hardware. This allows to create specific solutions and reduce the overhead [26][28].

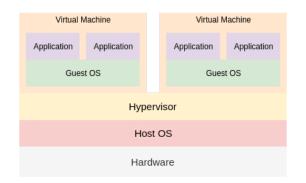

#### 2.3 Jailhouse

Jailhouse is a real-time, OS-agnostic partitioning hypervisor with a minimal code base that aims to minimize hypervisor activity and focus on isolation and resource partitioning. The system is divided into

isolated domains that directly access physical resources, instead of recurring to resource virtualization and scheduling (e.g., Xen hypervisor) [29].

This static approach derives from Jailhouse's target domain, which is safety-critical industrial applications [30], and allows to:

- Provide average latencies and jitters similar to bare metal solutions Jailhouse's only task is to use virtualization techniques to isolate guests, but doesn't emulate any devices for them. Besides that, it does one-to-one resource assignment to separate resources between partitions which means that, if one partition has access to some I/O port, PCI device or any other resource, the other partition hasn't. These properties make the performance of the Jailhouse to be very close as if tasks run on bare metal [31].

- 2. Ease potential certification processes Safety-critical industrial applications need to be certified according to numerous safety standards, and these standards give more strict requirements on systems with higher criticality. So, it is important to keep the complexity of the critically-high systems low, to ease the process of validation and certification, being this the main reason for the minimalistic code base of Jailhouse [30].

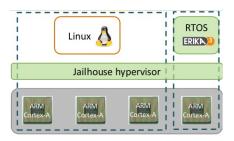

**Figure 2.3:** Illustration of Jailhouse's partitioning scheme. The root cell contains Linux, the Jailhouse module and two cores along with three devices. The first non-root cell (left) contains a bare-metal application and one core along with one device. The second non-root cell (right) contains Erika v3 and one core along with one device.

Regarding the classification of the hypervisor, it doesn't fit in the traditional classification (i.e., Type-1 or Type-2 hypervisor) because it runs on hardware like a bare-metal hypervisor, but needs to use Linux as bootloader to provide initialized hardware [29].

#### 2.3.1 Terminology

Each partition (i.e., allocated physical hardware) is called a *cell*, while the software, or VM, that can only reach that subset of physical hardware (i.e., *cells*) is called the *inmate*.

The partitions are divided in two categories: (i) the *root cell*, and (ii) the *non-root cells*. The partition with Linux that bootstraps Jailhouse and from where other cells could be managed is called *root cell*. The other partitions that are added afterward, which may contain RTOSes or GPOSes, are called *non-root cells*.

#### 2.3.2 Operation

This section describes the basic Jailhouse functionality, explains internal processes and also provides steps which should be done to enable and start the inmate in a cell.

#### 2.3.2.1 Cell Configuration

The first concept that the user must be aware of is the configuration of the cells (root or non-root). The configuration is done statically before Jailhouse starts running, and it determines which hardware resources can be accessed by each cell.

The configurations are done by using .c files where parameters have to be assigned as fields of special C structures (defined in *cell-config.h* file). For the non-root cell, this setup looks like in Listing 2.1.

| Listing 2.1: | Non-root cell | code examp | ble |

|--------------|---------------|------------|-----|

|--------------|---------------|------------|-----|

```

1 struct {

2

/*The size of arrays there must correspond with the amount of

fields of each type.*/

3

struct jailhouse_cell_desc cell;

4

5

__u64 cpus[1];

struct jailhouse_memory mem_regions[3];

6

7 } __attribute__((packed)) config = {

.cell = {

8

9

.signature = JAILHOUSE_CELL_DESC_SIGNATURE,

.revision = JAILHOUSE_CONFIG_REVISION,

10

.name = "gic-demo",

11

.flags = JAILHOUSE_CELL_PASSIVE_COMMREG,

12

.cpu_set_size = sizeof(config.cpus),

13

.num_memory_regions = ARRAY_SIZE(config.mem_regions),

14

.num_irqchips = 0,

15

.pio_bitmap_size = 0,

16

.num_pci_devices = 0,

17

```

18

```

19

.console = {

.address = 0xff010000,

20

.type = JAILHOUSE_CON_TYPE_XUARTPS,

21

.flags = JAILHOUSE_CON_ACCESS_MMIO |

22

JAILHOUSE_CON_REGDIST_4,

23

24

},

25

},

26

/*CPUs which are assigned to a cell.

27

<n> bit set = core <n> will be used.*/

.cpus = {

28

29

0x8, /* e.g., core 3 is assigned*/

30

},

31

/*Here is setup which mem regions this cell

32

could have access and with which rights (flags).*/

33

.mem regions = {

/* UART */ {

34

.phys_start = 0xff010000,

35

.virt start = 0xff010000,

36

.size = 0x1000,

37

.flags = JAILHOUSE_MEM_READ | JAILHOUSE_MEM_WRITE |

38

JAILHOUSE_MEM_IO | JAILHOUSE_MEM_ROOTSHARED,

39

},

40

/* RAM */ {

41

.phys_start = 0x800600000,

42

43

.virt_start = 0,

.size = 0x00010000,

44

.flags = JAILHOUSE_MEM_READ |

45

JAILHOUSE_MEM_WRITE ,

46

47

},

48

/* communication region */ {

.virt_start = 0x8000000,

49

.size = 0x00001000,

50

.flags = JAILHOUSE_MEM_READ |

51

52

JAILHOUSE_MEM_WRITE,

53

},

54

}

55 };

```

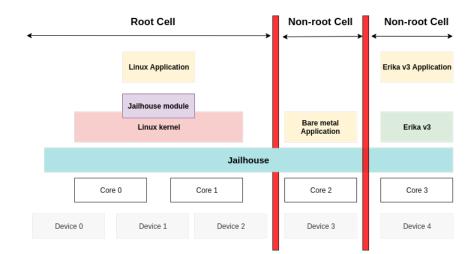

#### 2.3.2.2 Jailhouse Enabling

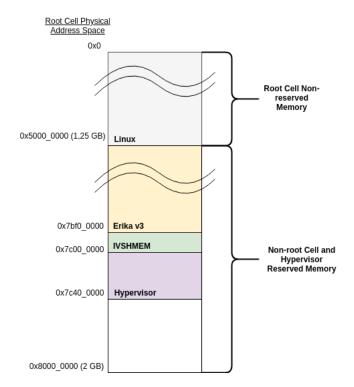

After configuring appropriately each cell, the user still needs to provide the reserved memory region to Jailhouse and non-root cells, appending *mem*= (which assigns the non-reserved memory space) kernel parameter on boot. The typical memory layout after reserving memory is depicted in Figure 2.4.

The values of *.phys\_start* and *.size* in the header of root cell configuration, and the physical address values of the defined memory regions on non-root cell configuration must be within the reserved memory.

**Figure 2.4:** Typical RAM layout in *ZCU104 Evaluation kit*. The first 1280 MB are available for the root cell, while the rest of the memory is reserved for the hypervisor and the non-root cells.

The first step to enable Jailhouse is to load the *jailhouse.ko* module into the kernel, which enables /*dev/jailhouse* in the system to enable the operation with Jailhouse user-space tools.

The second step is to execute jailhouse user-space program *jailhouse enable <path/to/cell/conf.cell>*. In this program, the driver remaps the reserved memory region to the kernel address space memory, so hypervisor could be accessed from the user-space. The driver also copies that binary at the start of this memory area and cell configuration right after it [30].

#### 2.3.2.3 Activation Procedure

Jailhouse can only be enabled after the full boot of Linux using a kernel module. After Linux inserts the module into the kernel, the hypervisor takes control over all hardware resources and, according to a partition configuration file (available for each cell), it reassigns the hardware to the cells, lifting Linux into the state of a VM [29].

The deferred activation procedure of Jailhouse has the considerable practical advantage that the majority of hardware initialization is fully offloaded to Linux, and Jailhouse can entirely concentrate on managing virtualization extensions [29].

Figure 2.5: Example of the Jailhouse's activation procedure. After being initialized, Jailhouse reassigns hardware to Linux and a Bare metal application.

Although it follows a hardware partitioning philosophy, Jailhouse allows the sharing of memory between cells in a region called *ivshmem*, enabling inter-cell communication and communication from the guests to the hypervisor. Such concurrent access is, however, not arbitrated by Jailhouse and needs to be addressed appropriately by the guests, in the correspondent configuration files [29].

Since Jailhouse only remaps and reassigns resources, the ideal design concept is that it does not need to be active after setting up and starting all guests. It only intercepts in case of access violations (e.g., illegal access across partitions), excepting some circumstances that still require intervention by the VMM, such as (i) interrupt reinjection [29], and (ii) interception of non-virtualizable hardware resources (e.g., parts of the GIC on ARM) [29].

#### 2.4 Bao

Bao is a real-time partitioning hypervisor that follows a similar approach to Jailhouse's approach concerning the preference of a minimal hypervisor activity that leverages hardware virtualization support to focus on isolation between guests and fault-containment over scheduling, as they target the same applications.

Bao was originally developed to serve as a base scaffold to research on, and deepen VM microarchitectural isolation. Nowadays, it supports Armv8-A and RISC-V architectures and is readily available through an open-source license.

Among the characteristics of it, Bao partitions and assigns resources at virtual machine (VM) instantiation time, and the virtual interrupts are directly mapped to physical ones, with one-to-one virtual-to-physical CPU mapping. Unlike other open-source hypervisors, Bao has no external dependencies, especially on privileged VMs running untrustable, large monoliths such as Linux, and as such, comprises a much smaller trusted computing base (TCB).

Regarding the classification of the hypervisor, it can be classified as a Type-1 hypervisor as it runs directly on top of the hosting hardware and, unlike Jailhouse, it loads firstly the hypervisor image which then allocates pages for the guests. This contrasts with the deferred activation procedure of Jailhouse, having the disadvantage of increasing the code size of the hypervisor since it needs to handle the hardware initialization. On the other hand, it is completely independent of Linux, which presents three main advantages: (i) as the hypervisor doesn't rely on Linux to boot, it has faster boot time than Jailhouse, (ii) it has a more universal behavior as it can host more operating systems aside Linux, and (iii) since the hypervisor is not controlled by a trusted partition (i.e., root cell), it has a much smaller trusted computing base (TCB), hampering the occurrence of attacks that could use Linux to jeopardize the hypervisor.

#### 2.5 Caches

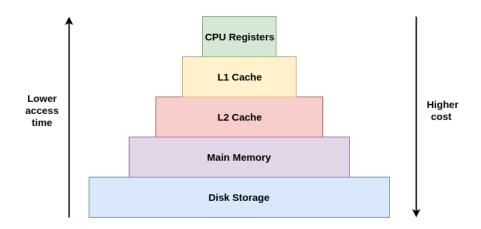

The steadfast development of the technology in the last decades has seen a divergence between the clock rate of processors and the latency of memory, creating a bottleneck between both memory and processor technologies that can be detrimental to the overall performance of a system [1]. Due to this divergence, the way that the memory is accessed needed to be changed for its latency to be reduced.

The memory hierarchy solution, sustained by a philosophy of using different memory technology layers that range from the fastest (but costliest) memory to the largest and cheapest memory, proved to be the solution that provides the best performance and narrows the bridge between memory and processor speed.

Figure 2.6: Illustration of the memory hierarchy with 2 cache levels. From the top to the bottom, the memory technology enlarges and gets slower.

#### 2.5.1 Definition

A part of the memory hierarchy are the caches, a small quantity of fast (but expensive) memory that hides the latency of large and slow (but cheap) main memory, by buffering frequently used data [19].

It lays in the lowest layer of the memory hierarchy, being the first memory to be accessed in all memory requests. Its effectiveness relies critically on the *hit rate* (i.e., the fraction of requests that are satisfied from the cache). Due to the large difference in latency, a small decrease in *hit rate* leads to a much larger decrease in performance [1].

#### 2.5.2 Cache Lines or Blocks

Caches are divided into lines. A cache line holds one aligned, power-of-two-sized block of adjacent bytes loaded from memory. If any byte needs to be replaced (i.e., evicted to make room for another), the entire line is reloaded. It is the minimum unit that may be cached [1].

On increasing the cache line size there is an increase in cache hits up to a certain extent. This results in performance enhancement based on the principle of locality <sup>1</sup>. However increasing block size beyond a certain point can also have a performance penalty because it will reduce the number of blocks which can fit in the cache, and whenever the block needs to be replaced, it will take much more time than a reduced block size. Not only this, each additional word will be less local and hence will be less used. Cumulatively, the probability of using newly fetched information will become less than the probability of reusing replaced.

<sup>&</sup>lt;sup>1</sup>Principle of locality: principle for which caches rule, that states that a computer program tends to access same set of memory locations for a particular period

#### 2.5.3 Cache Associativity

The associativity of the cache is another major property that must be taken into account when performing an attack as it can alter the way the address is divided (i.e., to appoint which address belongs to which line or set) or induct how many addresses must be accessed to completely evict a set. It refers to the way that each line can be replaced, if it is confined to a sole line (i.e., direct-mapped), if it can be replaced within a set (i.e., set-associative) or within any location (i.e., full associative). This choice of cache design can be seen as a tradeoff between complexity (and hence speed), and the rate of conflict misses [1].

#### 2.5.3.1 Fully Associative

Ideally, any memory location could be placed in any cache line, thus the cache would always be used to its full capacity (i.e., misses occur only when there is no free space in the cache). However, this cache architecture requires that all lines are matched in parallel to check for a hit, which increases complexity and energy consumption, limiting speed. Such designs are therefore limited to small and local caches, such as TLBs [1].

#### 2.5.3.2 Direct Mapped

The direct-mapped cache design is the opposite of the fully associative one. In this architecture, each memory location can be held by exactly one cache line, determined by the cache index function. If two memory locations that map to the same line are accessed, it will result in an eviction of the first one even though the cache may have unused lines, being the increase of miss rate the main disadvantage of this kind of design [1].

#### 2.5.3.3 Set Associative

In this design, the cache is divided into small sets (usually of between 2 and 24 lines), within which addresses are matched in parallel, as for a fully-associative cache. The calculation of a set that an address maps to is given by the function of its address (just like the index is given in a direct-mapped design).

A cache with *N*-line sets is called *N*-way associative. Using this terminology, we can refer to directmapped and fully-associative caches, as 1-way and *N*-way associativity, respectively (where *N* is the number of lines in the cache).

Figure 2.7: Direct mapped cache.

Figure 2.8: Set associative cache.

For both the direct-mapped and set-associative caches, the predictable map from address to line is exploited: (i) in attacks, to infer cache sets used by an algorithm under attack, and (ii) in cache coloring, to ensure that an attacker and its potential victim never share sets, and thus cannot conflict [1].

#### 2.5.4 Cache Replacement Policies

When the cache is full and a cache miss occurs, buffered code and data must be evicted from the cache to make room for new cache entries. The heuristic that is used to decide which entry to evict is called replacement policy. The replacement policy has to decide which existing cache entry is least likely to be used in the near future, being implemented in hardware and not controlled by software [28].

There are numerous ways of predicting future cache accesses to optimize the cache resource contention. The most known replacement policies are listed as follows:

1. Least Recently Used Replacement Policy - The least recently used cache entry will be replaced.

- Round Robin Replacement Policy The replacement occurs starting from the first cache entry until the last one, independent of the temporal locality of the cache entries.

- Pseudo-random Replacement Policy A random cache entry will be selected and evicted based on a pseudo-random number generator.

There is a wide consensus that deterministic replacement policies like LRU or FIFO are to be preferred in the context of real-time systems. Nonetheless, increasingly more vendors implement random replacement policies to favor applications targeting average performance [32].

# 2.5.5 Cache Inclusion Policies

The inclusiveness property of a cache determines if all cache lines from the lower-level cache are also stored in the higher-level cache [17].

The term is used to describe the higher-level cache with regard to the lower-level cache, and the higher-level cache can be classified as follows:

- 1. **Inclusive Cache** The higher-level cache contains all the data that is stored on the lower-level cache. This means a superset of the lower-level cache.

- Exclusive Cache The contents of the higher-level cache are not stored on the lower-level cache and vice versa. This architecture has the advantage of storing much more data in the cache subsystem than the inclusive one.

- 3. **Non-inclusive Cache** Both higher-level and lower-level cache can store at the same time the same content (just like an inclusive cache); however, the data can be evicted from the higher-level cache and still reside in the lower-level cache (like an exclusive cache). Hence, accesses to L1 cache cannot be detected by monitoring the LLC.

If a word is read from the cache, the data in the cache will be identical to the one in the main memory. However, when the core executes a store instruction, a cache lookup to the address that is written to is performed. If a cache hit occurs, there are two possible policies:

1. Write-back Policy - Writes are performed on the cache and not to the main memory, making the content of the cache lines diverge on both. To mark the cache lines with the most recent data, an

associated dirty bit is used. If the bit is set, it means that the write updated the cache and not the main memory. If the replacement policy evicts a cache line where the dirty bit is set, the cache line is written out to the main memory.

Write-through Policy - Writes are performed to both the cache and the main memory which means that they are kept coherent. Since there are more writes to the main memory, this policy is slower than the write-back policy.

# 2.5.6 Cache Indexing

The cache can derive the index of a certain memory from its virtual or physical address, making the cache virtually indexed or physically indexed, respectively.

The multiple cache indexing possibilities are listed as follows:

- Virtually Indexed, Virtually Tagged (VIVT) The virtual address is used for both, the index and the tag. This method is faster in general because the caches do not require virtual to physical address translation before the cache lookup [28][33][34]. However, this can lead to a problem of redundancy in the cache in which the same physical address, that has been accessed by different cores (each one with their virtual address that maps to same physical address), is cached in different cache lines, reducing the performance.

- Physically Indexed, Physically Tagged (PIPT) The physical address is used for both, the index and the tag. This method is slower since the virtual address has to be looked up in the TLB. However, shared memory is only held once in the cache[35].

- 3. Virtually Indexed, Physically Tagged (VIPT) The virtual address is used for the index, and the physical address is used for the tag. The advantage of this combination compared to PIPT is the lower latency since the index can be looked up in parallel to the TLB translation. However, the tag can not be compared until the physical address is available.

- 4. Physically Indexed, Virtually Tagged (PIVT) The physical address is used for the index, and the virtual address is used for the tag. This combination has no benefit since the address needs to be translated, the virtual tag is not unique and shared memory still can be held more than once in the cache.

# 2.5.7 Cache Coherence

In modern systems where each core has its local cache and shared memory is implemented, it is common for the applications to run simultaneously on different cores working on the same memory, urging the need to certify that multiple cached copies of data that reside in different cores are updated according to the main memory. This leads to the emergence of cache coherence protocols.

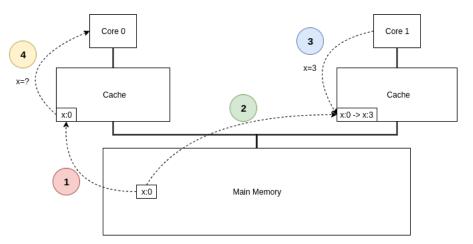

The coherency can be easily jeopardized in systems where the memory is shared, as it is illustrated in Figure 2.9. In the first step, the core 0 accesses data x. Afterward, in step 2, the core 1 accesses the same data x. In step 3, core 0 sets x to a new value, which is 3 in the illustrated example. Then, in step 4, core 0 re-accesses the value of x, reading an obsolete value concerning the other core. This problem is extendable to DMA devices for example. Therefore, it is needed a coherence mechanism which can act in these situations.

Figure 2.9: Illustration of a cache coherence problem.

There are three known mechanisms that tackle these coherency problems:

- Caching Disable An effective way of avoiding coherency problems is to disable the caching of memory. This is the costliest mechanism in terms of performance and power as all of the cache advantages are gone.

- Software-managed Coherency The software solution acts by cleaning dirty data and invalidating obsolete data to enable sharing with other processes each time a read or write of shared data is required.

- 3. **Hardware-managed Coherency** The hardware solution is the most effective, and universal, as it enables coherency to software applications transparently. The most known hardware

implementation of a coherency keeper is the *Bus Snooping*. In this mechanism, the cache controller snoops on the bus, thereby monitoring occurring transactions and taking action if such transaction pertains to it (e.g., a write to a memory block of which it has its copy in the cache). The coherence is managed at the granularity of a cache line and, thus, either an entire cache line is valid or invalid.

# 2.6 Side and Covert Channels

In this chapter, both side and covert channels are presented, along with their respective countermeasures. Moreover, the known benchmarks used to evaluate the attacks are listed.

# 2.6.1 Definition

Heiser et al. [1] differentiated side channels from covert channels by reporting that "side channels refer to the accidental leakage of sensitive data (e.g., an encryption key) by a trusted party, while covert channels are those exploited by a victim to deliberately leak information."

Hence, side and covert channel attacks exploit a device's hardware characteristics leakage (e.g., power dissipation, computation time or electromagnetic emission) to extract information about the processed data and, if used along statistical computations [36], use the data to deduce sensitive information (e.g., cryptographic keys, messages).

To observe both side or covert channels, not only a communication medium (i.e., shared hardware) is required but also an exploitation technique (e.g., *Prime+Probe*) to leverage the hardware's contention [9].

# 2.6.2 Benchmarks

To measure how much information each channel can leak, there have been some terms used to describe the amount of transmitted information through a channel. This section lists the most commonly used terms, and reflects on how the benchmarks can be affected by the cache's properties.

### 2.6.2.1 Channel Capacity or Bandwidth

The most known way of characterizing a channel is named capacity or bandwidth of a channel, and it represents, in bits per second, how much information can be transmitted through that channel. The more capacity a channel has, the more threatening it becomes to the targeted system [37].

Regarding the capacity of leaking information, it is known that collusion allows better utilization of the underlying hardware mechanism and hence covert channels tend to have much higher bandwidth than side channels based on the same mechanism (i.e., exploitation technique). The capacity of the covert channel is the upper bound of the corresponding side channel capacity [9].

A preponderant factor when obtaining the channel's capacity is the probing resolution of the LLC, which is not tied to the victim preemption, but is fundamentally limited only by the speed at which the attacker can perform the probe, in case of a *Prime+Probe* attack, referred in Section 2.6.3. This is much slower than for a local cache, for two reasons:

- 1. The LLC typically has higher associativity than the L1 cache (e.g., 12 to 24-way versus 4 to 8-way), hence more memory accesses are required to completely prime or probe a cache set [17].

- 2. The probe time increases due to the long access latency of the LLC (12 cycles more for *Cortex-A53* processor [38]). Even with all lines resident in the LLC, the attacker, when performing a probe of one LLC set, will still experience misses in the L1 and L2 caches, due to their lower associativity. Furthermore, a miss in the LLC will cause more than 150 cycles latency while a miss in the L1 or L2 cache has a latency of fewer than 40 cycles [17].

The slower the probing resolution, the less frequent will the cache's contents be observed, hence the channel capacity will decrease drastically.

## 2.6.2.2 Channel Matrix

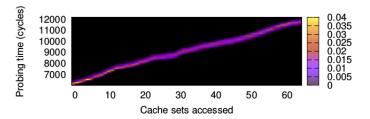

A more recent way of visualizing the channels was introduced by Heiser et al. [9], which specifies the conditional probability of an observed output symbol (e.g. spy, or attacker, probing time) given an input symbol (e.g. cache lines accessed), by the use of a heat map, or a graph when visualizing low-capacity channels.

An example of a heat map that demonstrates the existence of a well-defined channel (i.e., noticeable horizontal variation) is illustrated in Figure 2.10, which has been used to characterize a channel on the instruction side of an L1 cache.

Figure 2.10: Channel matrix for the unmitigated L1 I-cache channel on Sandy Bridge platform [10].

In the absence of a channel, outputs are independent of inputs and the graph will show no horizontal variation, as it is illustrated in Figure 2.11.

Figure 2.11: Channel matrix for the mitigated L1 I-cache channels on Hikey platform [10].

# 2.6.3 Attack Types

As mentioned in the definition of a side or covert channel, an attack needs a mechanism that explores a communication medium. The classification of the attacks is done taking into account which communication medium is leveraged: a) attacks that explore the cache, and b) attacks that explore real-time contention (e.g., buses or other resources present in the resource sharing hierarchy, described in Section 3.1.2).

#### 2.6.3.1 Cache Exploitation Techniques

### **Prime+Probe**

In the Prime+Probe technique, the attacker primes the cache by filling cache sets with its own data, then waits for the victim to replace some of the cache lines based on the input symbol it transmits. Lastly, the attacker probes the cache sets by measuring the access time to the previously cached data, thus measuring the victim's cache footprint. The output symbol is the total probing time of the attacker [10].

Although this technique doesn't rely on sharing memory, it can have some handicaps, such as lower resolution in comparison to other techniques because it can only target a cache set, and, due to the pseudo-random replacement policy, it might happen that the access to one congruent address evicts a

previously accessed address from the attacker and thus it is possible that during the probing phase false positives occur [28].

This technique is privileged in cases where there is a resource-sharing case but without memory sharing between victim and attacker.

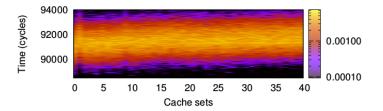

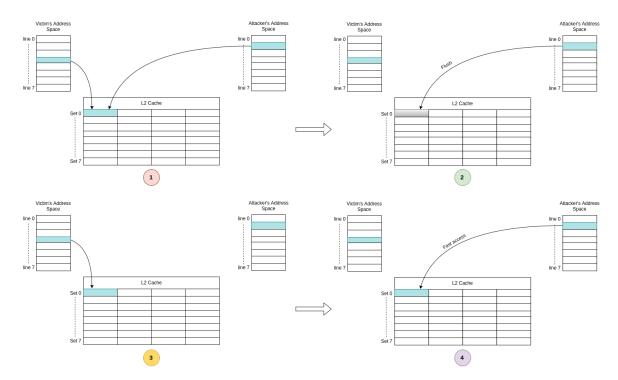

**Figure 2.12:** Illustration of the Prime+Probe attack by means of a 4-way (columns) cache with 8 sets (rows). In step 1, the attacker primes the cache filling all the ways from the same set. In step 2, the victim replaces some of the cache lines from the cache set. In step 3, the attacker probes the cache set accessing all cache lines. The cache lines changed by the victim have a slow access time, while the unchanged cache lines have a faster access time.

#### Flush+Reload

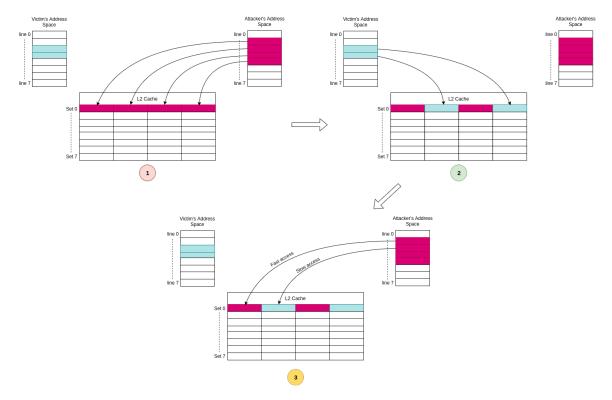

In Flush+Reload, the attacker first flushes a shared line of interest (by using dedicated instructions or by eviction through contention). Once the victim has executed, the attacker then reloads the evicted line by touching it, measuring the time taken. A fast reload indicates that the victim touched this line (reloading it), while a slow reload indicates that it didn't. The advantage of Flush+Reload over Prime+Probe is that the attacker can target a specific line, rather than just a cache set [1].

This technique relies on the existence of shared virtual memory (e.g., shared libraries or page deduplication), and the ability to flush by virtual address, bringing much more resolution (hence leakage capacity) to the attack as it can target cache lines instead of cache sets.

**Figure 2.13:** Illustration of the Flush+Reload attack by means of a 4-way (columns) cache with 8 sets (rows). In step 1, the attacker or the victim cache a shared line. In step 2, the attacker flushes the shared cache line. In step 3, the victim accesses the previously accessed cache line. In step 4, the attacker tries to reload the cache line. If the cache has been accessed by the victim, the attacker will experience a fast access time.

#### **Evict+Time**

This approach uses the targeted eviction of lines, together with overall execution time measurement. The attacker first causes the victim to run, preloading its working set, and establishing a baseline execution time. The attacker then evicts a line of interest and runs the victim again. A variation in execution time indicates that the line of interest was accessed [1].

#### Flush+Flush

The attack is basically the same as Flush+Reload. A binary or a shared object file is mapped into the address space of the attacker. An address is flushed from the cache, and the victim's program is scheduled. However, instead of the reloading step where the monitored address is accessed, it is flushed again causing no cache misses compared to Flush+Reload or Prime+Probe [28].

## 2.6.3.2 Exploiting real-time contention

These real-time attacks, also known as DoS attacks, target the systems by maliciously increasing the consumption of a shared resource. The attacks can occur wherever exists resource contention, including buses, by exhausting shared bus bandwidth with a large number of memory requests, as it was exemplified

by Woo et al. [39], who on a machine with a single frontside bus, generated a DoS attack with L2 cache misses in a simulated environment.

# 2.6.4 Countermeasures

All of the published countermeasures, listed by a survey made by Heiser et al. [1], are summarized in this section.

#### 2.6.4.1 Constant-time techniques

The most widely used countermeasure, primarily applied to microarchitectural attacks, is making the security operation time constant or random, regardless of the microarchitecture elements that are used. This approach comes with the disadvantage of deteriorating the performance of the system [36].

There are rudimentary techniques where the access to, presumed undetectable microarchitecture elements, depends on secret information. An example is the implementation of modular exponentiation in OpenSSL, which can access different memory addresses within a cache line, depending on the secret exponent. This countermeasure can be surpassed in processors that can leak information within a cache line (i.e., offset of a cache line), as it has been demonstrated by Bernstein et al. [40].

These techniques have been applied in debuggers and compilers. It is the case of *Valgrind* debugger, where Langley [41] modified it to trace the flow of secret information and warn if it is used in branches or as a memory index.

#### 2.6.4.2 Injecting noise

This countermeasure focuses on introducing noise to the attacker's measurements making them essentially useless [1]. As it occurs with the constant-time techniques, this technique has the disadvantage of deteriorating the performance of the system.

Zhang et al. [42] introduced a bystander VM for injecting noise on the cross-VM L2 covert channel with a configurable workload. They found that as long as the bystander VMs only adjust their CPU time consumption, working sets and memory access rates, they impact the cross-VM covert channel's bandwidth.

Although noise injection can difficult the leak of information, it is inefficient for obtaining high security, because the amount of actual required noise increases dramatically with decreasing channel capacity.

This significantly degrades system performance, and makes it infeasible to reduce channel bandwidth by more than about two orders of magnitude [43].

#### 2.6.4.3 Partitioning time

This countermeasure eliminates attacks which rely on either concurrent or consecutive access to shared hardware by either providing time-sliced exclusive access, or carefully managing the transition between time-slices (e.g., flushing the caches) [42]. Among the techniques that partition time to eliminate the attacks, the cache flushing and the kernel address space isolation techniques stand out.

#### **Cache flushing**

Zhang et al. [44] suggested flushing all local state, including BTB and TLB, and all levels of caches during VM switches in cloud computing when CPU switches security domains.

The lower and larger the cache level, the bigger the degradation of performance as the time to refill the caches is bigger, and the likelier a newly scheduled VM finds any data or instructions hot in the cache [45].

#### Kernel address space isolation

Gruss et al. [46] proposed isolating kernel form user address space by using separated page directories for each, so switching context between user and kernel spaces includes switching the page directory. This technique is designed to mitigate the timing attack on prefetch instructions.

#### 2.6.4.4 Partitioning hardware

The partitioning hardware mechanism is only used in truly concurrent attacks that can only be prevented by partitioning hardware resources among competing threads or cores [1].

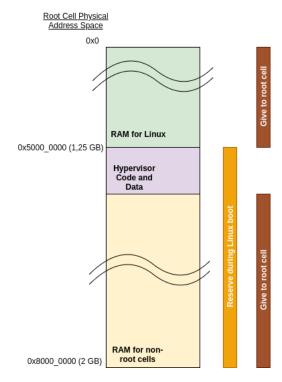

#### **Cache Coloring**

The cache coloring approach exploits set-associativity to partition caches in software. Besides improving determinism and predictability in detriment of average-case performance [32], it can be used to protect against cache timing channels.

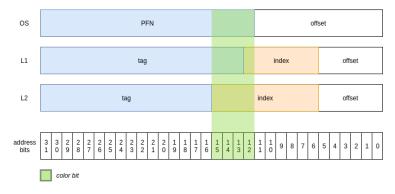

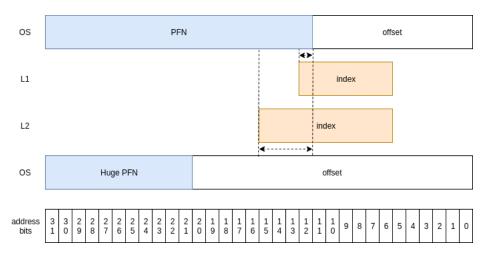

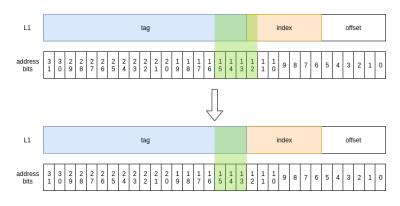

Cache coloring implementations divide memory into colored memory pools and allocate memory from different pools to isolated security domains. As an example, Figure 2.14 shows how the same physical address (PA) is interpreted from 4 different points of view. At the top, the bits of a PA are seen from the perspective of an OS/Hypervisor as divided into physical frame number (PFN) and page offset (PO) bits. At the lower layer, the structure of the same PA from the point of view of the L1 and L2 caches is

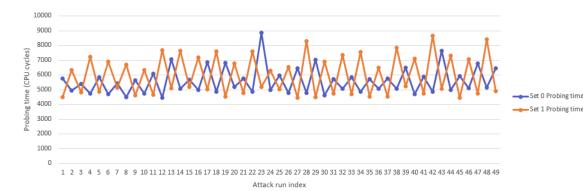

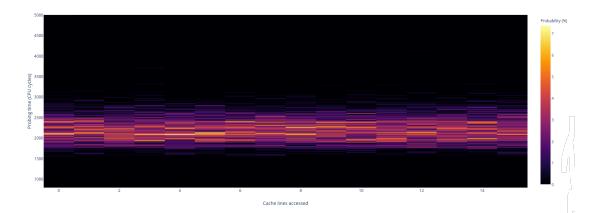

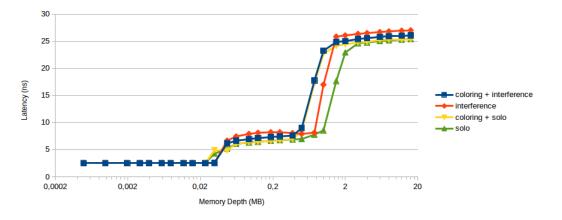

depicted, highlighting its color bits. Physical frames whose addresses diverge in any of these color bits are not mapped to the same cache set, and thus never conflict.