UNIVERSITY OF OKLAHOMA GRADUATE COLLEGE

# IMPLEMENTATION AND ANALYSIS OF ADAPTIVE SPECTRUM SENSING

A THESIS SUBMITTED TO THE GRADUATE FACULTY in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE

By

RYLEE MATTINGLY Norman, Oklahoma 2021

## IMPLEMENTATION AND ANALYSIS OF ADAPTIVE SPECTRUM SENSING

# A THESIS APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

BY THE COMMITTEE CONSISTING OF

Dr. Justin Metcalf, Chair

Dr. Nathan Goodman

Dr. Cliff Fitzmorris

© Copyright by RYLEE MATTINGLY 2021 All Rights Reserved.

# Acknowledgments

I want to thank Dr. Justin Metcalf and Dr. Jay McDaniel for giving me the opportunity to work at the ARRC and discovery the incredible world of radar systems and electromagnetics. Additionally, I want to thank Dr. Nathan Goodman and Dr. Cliff Fitzmorris for agreeing to be on my committee and taking the time to review my work.

I would also like to thank my sister, Cassi Marlow, and my parents, Ricky and Treva Mattingly. I am always grateful for their incredible support and encouragement to pursue my goals and persevere through great challenges.

Finally, I want like to thank all of my friends at the ARRC for helping provide support when encountering especially difficult challenges.

I thank the Defense Advanced Research Projects Agency (DARPA) for their support of this research under grant HR0011-20-1-0007.

# **Table of Contents**

| Acknowledgment |                   |         |             | iv                                  |      |

|----------------|-------------------|---------|-------------|-------------------------------------|------|

| Та             | Table of Contents |         |             |                                     | v    |

| Li             | List of Tables vi |         |             |                                     | viii |

| Li             | List of Figures i |         |             |                                     | ix   |

| Ał             | ostrac            | t       |             |                                     | xii  |

| 1              | Intr              | oductio | n           |                                     | 1    |

|                | 1.1               | Contri  | butions .   |                                     | 2    |

|                | 1.2               | Thesis  | Outline .   |                                     | 3    |

| 2              | Bacl              | kgroun  | d           |                                     | 5    |

|                | 2.1               | Cognit  | tive Sensor | rs and Greedy Fast Spectrum Sensing | 5    |

|                | 2.2               | Signal  | Detection   |                                     | 8    |

|                |                   | 2.2.1   | Cyclosta    | tionary Feature Detection           | 9    |

|                |                   | 2.2.2   | Energy I    | Detection                           | 14   |

|                |                   |         | 2.2.2.1     | Classic Energy Detection            | 14   |

|                |                   |         | 2.2.2.2     | Constant False Alarm Rate Detectors | 16   |

| 3              | Imp               | lementa | ation Plat  | form                                | 19   |

|                | 3.1               | Softwa  | are-Define  | d Radio                             | 19   |

|   | 3.2 | RF Network-on-Chip                                    | 22 |

|---|-----|-------------------------------------------------------|----|

|   | 3.3 | Block Interface                                       | 24 |

|   | 3.4 | Design and Control of a Block                         | 28 |

| 4 | Sim | ple FSS Architecture                                  | 41 |

|   | 4.1 | Changes to the Algorithm                              | 41 |

|   | 4.2 | Theory of Operation                                   | 42 |

|   | 4.3 | Implementation                                        | 43 |

|   |     | 4.3.1 Data and Registers                              | 44 |

|   |     | 4.3.2 FSS State Machine                               | 45 |

|   |     | 4.3.3 Send State Machine                              | 47 |

|   | 4.4 | Timing and Performance                                | 49 |

|   | 4.5 | Utilization                                           | 50 |

|   | 4.6 | Usage and Verification                                | 52 |

| 5 | Har | dware Optimized Cell Averaging Estimator              | 54 |

|   | 5.1 | Data Sets                                             | 54 |

|   |     | 5.1.1 Simulated Data                                  | 55 |

|   |     | 5.1.2 Real World Data                                 | 56 |

|   | 5.2 | CA-CFAR Performance                                   | 59 |

|   | 5.3 | OS-CFAR Performance                                   | 62 |

|   | 5.4 | Hardware Optimized Cell Averaging Estimation (HO-CAE) | 63 |

|   |     | 5.4.1 Simulation and Performance                      | 65 |

|   | 5.5 | Real-World Performance                                | 69 |

| 6 | НΟ- | -CAE Hardware Architecture                            | 74 |

|   | 6.1 | Theory of Operation                                   | 74 |

|   | 6.2 | Major Structures                                      | 76 |

|   |     | 6.2.1 The Buffer                                      | 76 |

|   |     | 6.2.2 The Accumulators                                | 77 |

| Re | References |         |                         |      |  |  |

|----|------------|---------|-------------------------|------|--|--|

| 7  | Con        | clusion | and Future Work         | 82   |  |  |

|    | 6.3        | Perform | mance                   | . 80 |  |  |

|    |            | 6.2.3   | Sorting Estimate Buffer | . 78 |  |  |

# List of Tables

| 3.1 | A description of the signal used in a simple AXI-Stream interface             | 25 |

|-----|-------------------------------------------------------------------------------|----|

| 3.2 | The relevant signals for the AXI-Stream Data user interface                   | 26 |

| 3.3 | The relevant files for the RFNoC block development cycle                      | 29 |

| 4.1 | Values used for an example run of the FSS state machine                       | 45 |

| 4.2 | Values used for an example run of the FSS state machine                       | 48 |

| 4.3 | Kintex®7-410T utilization of the FSS design shown in 3 stages:                |    |

|     | default image with FFT, default image with stream endpoints for               |    |

|     | FSS, and image with FSS block. This data was provided by the                  |    |

|     | Xilinx Vivado synthesis tools when the RFNoC images were built                | 51 |

| 5.1 | The resulting $P_{FA}$ from noise only simulation with $P_{FA}$ of $10^6$ and |    |

|     | window size of 64                                                             | 65 |

| 5.2 | The results of probability simulations for 5, 10 and 20 dB SNR                |    |

|     | signals. Probability data is given as wells as data compared to FSS           |    |

|     | with perfect knowledge.                                                       | 67 |

| 6.1 | A summary of operation carried out by each register in the sorted             |    |

|     | estimate buffer.                                                              | 79 |

# **List of Figures**

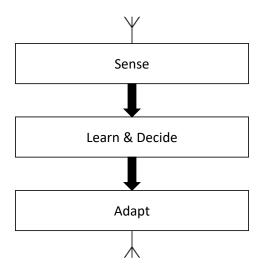

| 2.1 | Perception action cycle for a cognitive sensor streaming data from                        |   |

|-----|-------------------------------------------------------------------------------------------|---|

|     | an antenna into the sense stage. A transmission band is calculated                        |   |

|     | and the corresponding signal is generated by the adapt stage and                          |   |

|     | transmitted.                                                                              | 6 |

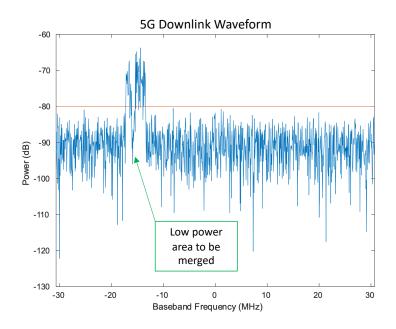

| 2.2 | A 5G downlink signal shown with a threshold used to sort bins into                        |   |

|     | high and low power groups. High power groupings with a small                              |   |

|     | number of low power bins are grouped as they are part of a signal                         | 7 |

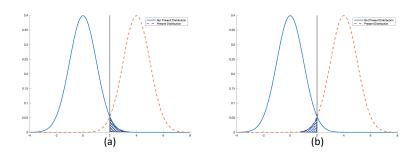

| 2.3 | Two Gaussian distributions. The not present distribution with a                           |   |

|     | mean of 0 and the present distribution with a mean of 4. (a) The                          |   |

|     | probability of false alarm shown as the highlighted area. (b) The                         |   |

|     | probability of missed detection is shown as the shaded area 10                            | 6 |

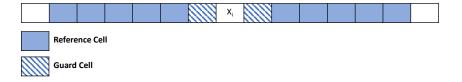

| 2.4 | The structure of CA-CFAR used when estimating the $\widehat{\sigma_w^2}$ for cell $x_i$ . |   |

|     | Reference cells are evenly split on either side of the cell under test                    |   |

|     | to provide a better estimate                                                              | 7 |

| 3.1 | X310 pictured with top cover removed to show daughter cards in-                           |   |

|     | stalled                                                                                   | 0 |

| 3.2 | GNURadio Companion software shown with a simple, two block                                |   |

|     | flowgraph that takes data streamed from the radio and process it                          |   |

|     | into a waterfall plot                                                                     | 1 |

| 3.3 | An example showing how the internal RFNoC structures may con-                             |   |

|     | nected for operation [1].                                                                 | 5 |

| 3.4 | The timing diagram for a the AXI-Stream Payload Context inter-           |    |

|-----|--------------------------------------------------------------------------|----|

|     | face. It shows a 4 word data packet with timestamp [1]                   | 27 |

| 3.5 | An example showing how the provided radio and DUC blocks can             |    |

|     | be used to replace the USRP Source block used previously [1]             | 40 |

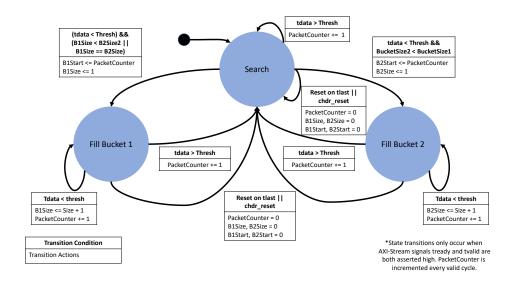

| 4.1 | The basic FSS state machine shown with transition conditions and         |    |

|     | transition actions.                                                      | 45 |

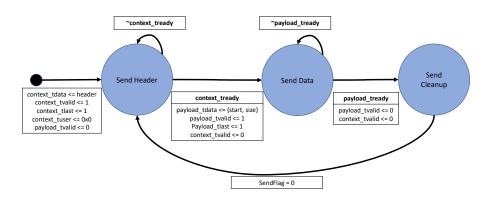

| 4.2 | The state machine used for transmitting the a packet of data out of      |    |

|     | an AXI-Stream port on an RFNoC block.                                    | 47 |

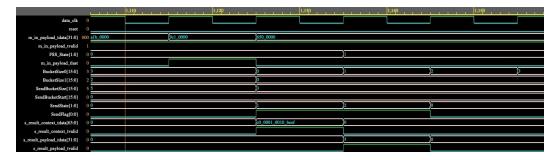

| 4.3 | The state machine used for transmitting the a packet of data out of      |    |

|     | an AXI-Stream port on an RFNoC block.                                    | 50 |

| 4.4 | GNURadio block for the RFNoC FSS block.                                  | 52 |

| 4.5 | The state machine used for transmitting the a packet of data out of      |    |

|     | an AXI-Stream port on an RFNoC block.                                    | 53 |

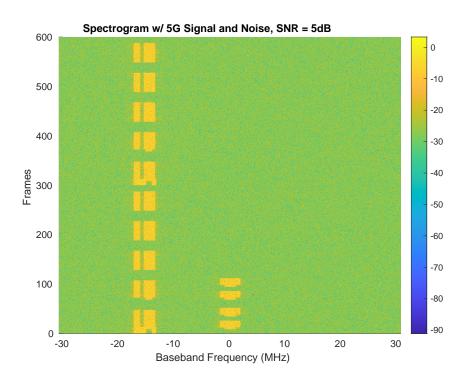

| 5.1 | Simulated 5G NR Downlink signal spectrogram with 5 dB SNR                | 55 |

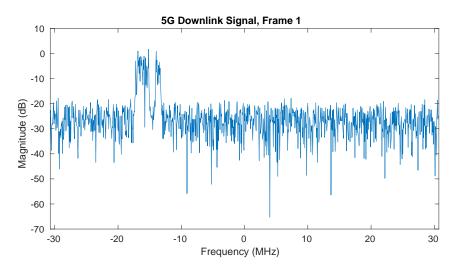

| 5.2 | Frame 1 of the of the 5G Downlink spectrogram with 5 dB SNR              | 56 |

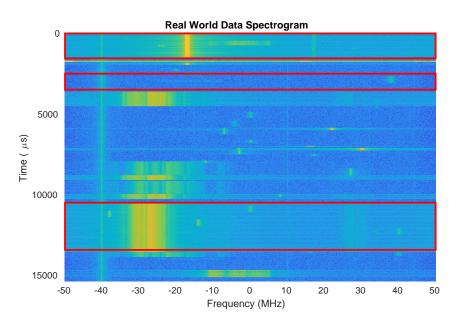

| 5.3 | Real world spectrogram with 100 MHz of bandwidth. Three dis-             |    |

|     | tinct regions of interest are highlighted to capture four different sig- |    |

|     | nals as well as a noise only case.                                       | 57 |

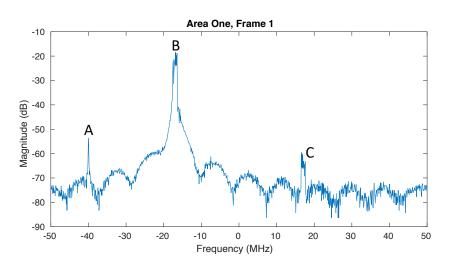

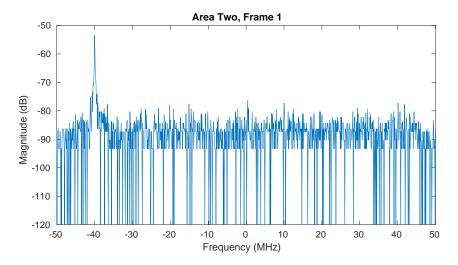

| 5.4 | Area of interest one with amplifier artifact and two distinct signals    | 57 |

| 5.5 | Area of interest two that contains only noise                            | 58 |

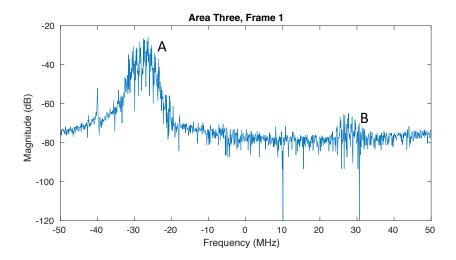

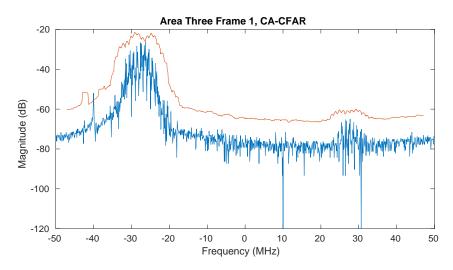

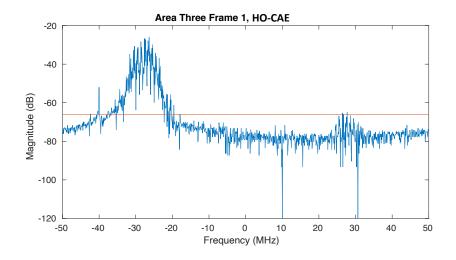

| 5.6 | Area of interest three containing a wide band high power signal          |    |

|     | with a low power signal.                                                 | 58 |

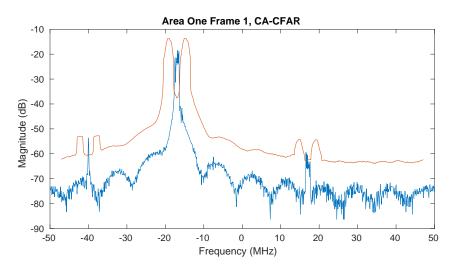

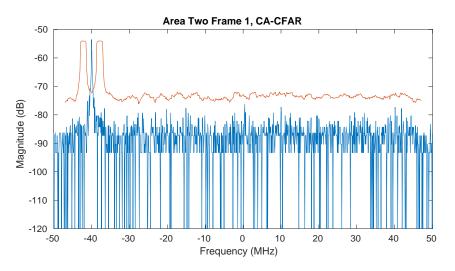

| 5.7 | CA-CFAR applied to the first area of interest. $N = 32, G = 28 \dots$    | 60 |

| 5.8 | CA-CFAR applied to the second area of interest of mostly noise. N        |    |

|     | = 32, G = 28                                                             | 60 |

| 5.9 | CA-CFAR applied to the first area of interest. $N = 32$ , $G = 28$       | 61 |

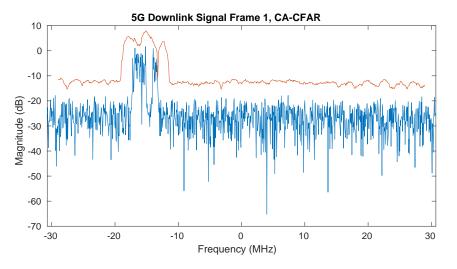

| 5.10  | CA-CFAR applied to the first frame of the simulated downlink sig-                       |    |

|-------|-----------------------------------------------------------------------------------------|----|

|       | nal. N = 32, G = 28                                                                     | 61 |

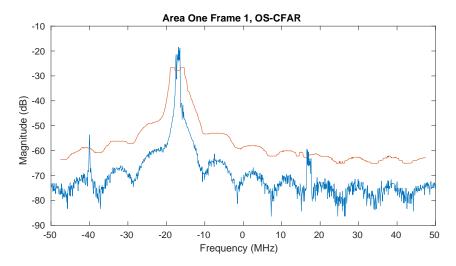

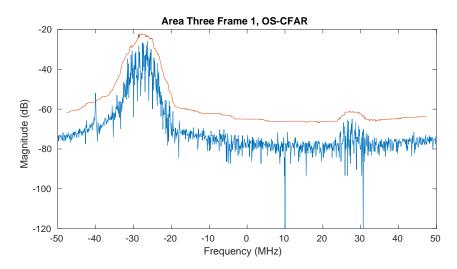

| 5.11  | OS-CFAR applied to the first area of interest with parameters $N =$                     |    |

|       | 54, K = 37                                                                              | 62 |

| 5.12  | OS-CFAR applied to the interest where the wideband signals are                          |    |

|       | missed. N = 54, K = 37                                                                  | 63 |

| 5.13  | The sliding averaging window used to generate the estimates of $\widehat{\sigma_W^2}$ . |    |

|       | Here a frame length of 20 is shown with a window length of 10. $\therefore$             | 64 |

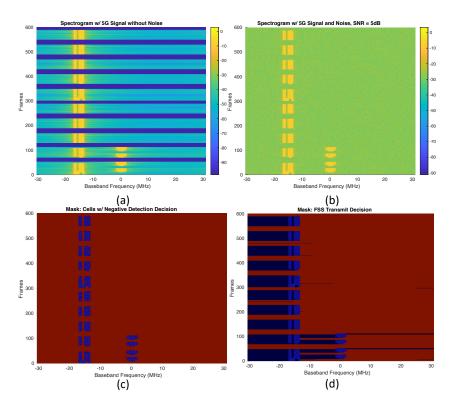

| 5.14  | Steps to generating and simulating a 5G Downlink waveform with                          |    |

|       | FSS. (a) The no noise signal after being partitioned into a block. (b)                  |    |

|       | Noise added to the signal. (c) A logical cube on top of a 5G mask.                      |    |

|       | (d) FSS decision based based on logical grid                                            | 67 |

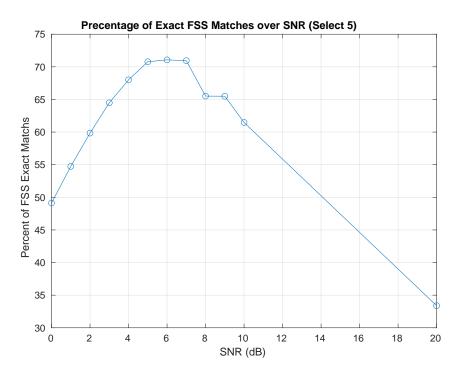

| 5.15  | The percentage of exact FSS matches between the perfect case and                        |    |

|       | HO-CAE over the simulated SNR values                                                    | 69 |

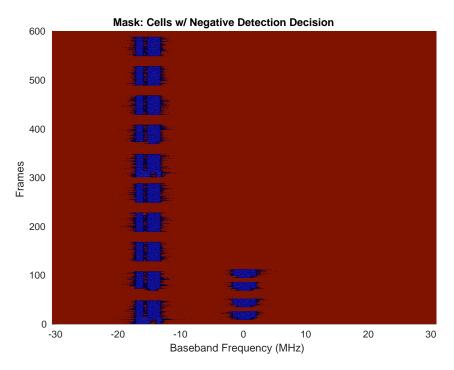

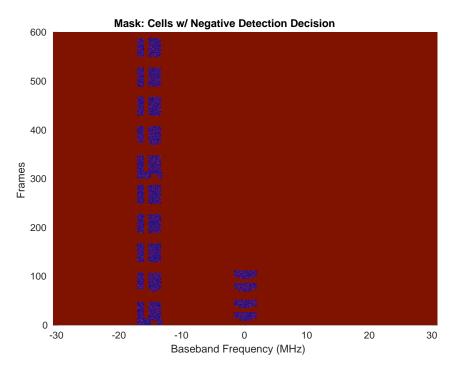

| 5.16  | The result of logical mask where non-detected bins are marked for                       |    |

|       | a 20dB SNR 5G downlink signal                                                           | 70 |

| 5.17  | The result of logical mask where non-detected bins are marked for                       |    |

|       | a 0 dB SNR 5G downlink signal                                                           | 71 |

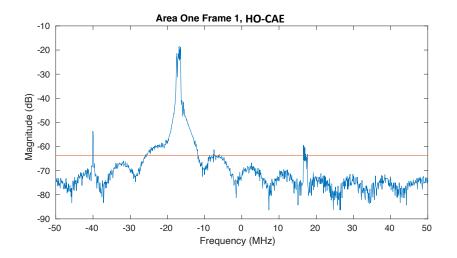

| 5.18  | The first frame of the first area of interest from the real-world data                  |    |

|       | with HO-CAE applied.                                                                    | 71 |

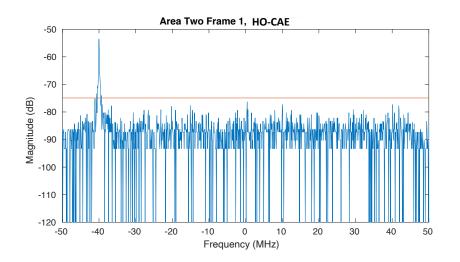

| 5.19  | The first frame of the second area of interest from the real-world                      |    |

|       | data with HO-CAE applied                                                                | 72 |

| 5.20  | The third frame of the second area of interest from the real-world                      |    |

|       | data with HO-CAE applied                                                                | 72 |

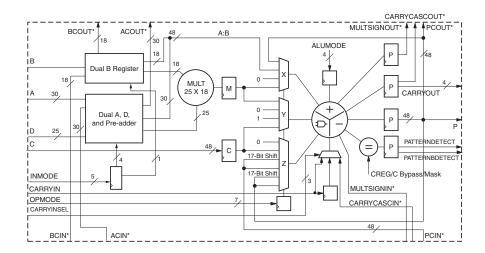

| 6.1   | The DSP48E1 Slice inside 7 Series Xilinx FPGAs                                          | 77 |

| ~ • • |                                                                                         |    |

#### Abstract

The electromagnetic spectrum is a finite resource that has become increasingly crowded as the day-to-day operation of the world has become increasingly reliant on wireless devices. With the growing deployment of the Internet-of-Things (IoT), 5G Networks, and broadband internet systems, the available spectrum for radar applications has been reduced and instances of interference across all device types have increased. To mitigate this problem going forward, devices need to be better able to intelligently access the spectrum based on the presence of other users.

A cognitive radio or radar system functions by using adaptive spectrum sensing to detect existing users in the frequency band and adapt to use 'open' spectrum bands. To ensure the predictable performance of the system and systems that it shares spectrum with, it must detect new users and adapt without interrupting its operation or interfering with the other users. Because modern communications networks can update their spectrum utilization on a sub-millisecond timescale, the critical detection and adaption phase must operate in real-time.

This work presents an implementation of a fast spectrum sensing (FSS) algorithm deployed on the field-programmable gate array (FPGA) of an Ettus USRP<sup>TM</sup> software-defined radio. This implementation allows for microsecond scale updates of the environment's spectrum availability. Unfortunately, this FSS algorithm is limited by its knowledge of the spectrum, which is ever-changing. To help improve the system's dynamic performance a new adaptive detection algorithm is proposed

to replace the static threshold of the first implementation. The new detection algorithm is a constant false alarm rate (CFAR) inspired detector which allows a cognitive sensor to work in a dynamic environment without a-priori information about the spectrum. Combining the FSS algorithm with dynamic signal detection allows the cognitive radio system to adapt to the ever-changing environment without requiring extensive 'listen before talk' periods before operation.

# **Chapter 1**

#### Introduction

Today, almost everyone takes advantage of technology or devices that use the electromagnetic spectrum for operation. With a projected 29.3 billion networked devices by 2023, 23.5 billion in IoT and mobile categories, a huge number of wire-less devices exist in the world [2]. Without deterministic access to this resource, many critical systems would fail or become unreliable. To mitigate interference, spectrum is licensed to primary users restricting the use of those frequencies to specific applications. While this licensing protects primary users of the band, the band utilization varies widely based on geographic location, leaving gigahertz of spectrum underutilized [3].

Recently, unlicensed bands have been approved for wireless communications use. These bands share spectrum using a listen-before-talk (LBT) technique [4] that requires an incoming unlicensed user to 'listen' for other users in the spectrum for some time before operating. Similarly, the unlicensed user must be prepared to immediately stop operating whenever a primary user is detected. While effective, operation time can be greatly impacted as new primary users enter and leave the environment, diminishing the performance for the secondary users.

LBT technique adoption and the availability of unlicensed bands shows a willingness on the part of regulators and the industry to try, at least on a limited basis, spectrum sharing to be used. The expansion to faster and more performant techniques of spectrum sensing and avoidance is necessary to spur further adoption and better spectrum management in the future.

This thesis analyzes existing fast spectrum sensing algorithms that allow a system to detect other users of the electromagnetic spectrum. By detecting a primary user, a secondary emitter to limit its interference to the primary users. Further, the implementation of these algorithms in an FPGA on commercial off-the-shelf (COTS) hardware is investigated, with a focus on real-time performance.

While the real-time knowledge of other emitters would be useful to all wireless users to improve performance and avoid interference, a special focus on radar systems is considered. Specifically, the pulsed radars allow spectrum estimates to be gathered while the radar is not transmitting, eliminating the need to censor the system's emissions when creating estimates. Additionally, the sensitivity of radar makes its interference avoidance that much more important.

The initial implementations of this system will use a static threshold, but because of the dynamic nature of the electromagnetic spectrum, a dynamic threshold estimation technique will also be analyzed. By estimating the noise of the spectrum, a better understanding of the environment over time can be used to set the spectrum threshold. This necessitates an investigation into estimation and signal detection techniques.

#### **1.1 Contributions**

This thesis makes the following contributions:

• Real-time FPGA implementation of static threshold, greedy fast spectrum sensing (FSS) algorithm. Developed novel rotating bucket architecture to

minimize latency and utilization resources.

- Demonstrates hardware acceleration on commercial off-the-shelf USRP radios. Leveraged open-source RF Network-on-Chip (RFNoC) framework to implement algorithms with real-time performance.

- Develops CFAR inspired noise estimation method designed with implementation on FPGA in mind. Proposed pipelined implementation to integrate threshold estimate and FSS into a single block.

## 1.2 Thesis Outline

This thesis is divided into the following chapters: In Chapter 2, a background on cognitive radios is given with a discussion on their functional cycle. The fast spectrum sensing algorithm is presented as the static threshold case. Next, is a discussion on dynamic signal detection techniques that are used as a primer for the dynamic threshold method implemented later. Included is a complexity analysis of the various types of signal detection methods.

Chapter 3 describes the implementation platform that was used for development. Details about the RF Network-on-Chip (RFNoC<sup>TM</sup>) FPGA framework are provided, including issues that were addressed and limitations that were discovered. This chapter also provides a high-level overview of the software used with the platform and how the Ettus X310 radio and host computer operate together.

In Chapter 4, the architecture for the static FSS algorithm is presented. The state machine is discussed with an overview of the data flow in and out of the algorithm block. An analysis of the clock level timing of the block is presented as a basis for the discussion on performance. Performance metrics will be derived that provide a

numeric performance figure so that the performance of the adaptive implementation can be compared later. Finally, FPGA resource utilization will be presented using the Vivado reports generated when the FPGA design was synthesized.

In Chapter 5, a detailed description of the proposed hardware optimized signal detection method is presented. Real-world data will be presented that provides a basis for the need for the new algorithm. Additionally, a 5G Downlink signal simulator that was used to benchmark this new process is presented. Performance analysis from the simulation across SNR is described with the probability of false alarm, probability of detection, and resulting FSS of particular interest. The chapter concludes with the new algorithm being applied to the same real-world data as was presented at the beginning of the chapter.

Chapter 6 proposes an FPGA architecture to implement the detection method described in Chapter 5. An analysis of the hardware structures necessary to the device's operation and the resources required will be given along with a discussion on operational performance. A special look at the latency of the FPGA block will be provided through a cycle-level timing analysis of the block and the previously derived performance metrics.

In Chapter 7, a conclusion to the work is provided with a discussion about opportunities for future work.

# **Chapter 2**

#### Background

Before discussing the implementation details of fast spectrum sensing or signal detection, the background for the algorithms and existing methods that served as the foundation of this work should be introduced. First, an introduction to the operation of a cognitive sensor is given with an introduction to the FSS algorithm. This chapter concludes with a discussion on detection methods. Specifically, energy detection and cyclostationary detection will be analyzed.

# 2.1 Cognitive Sensors and Greedy Fast Spectrum Sensing

The cognitive perception-action cycle (PAC) underlays the primary operation loop of a cognitive sensor. The cycle works in three stages: sense, decide, and adapt. Sensing should be occurring at all times on the sensor. Continuous sampling of the spectrum provides the system with a constant flow of data. The stream can be divided into 'frames' for which the fast Fourier transform (FFT) is applied.

These frames then act as spectral snapshots that can be sent to the second stage of the PAC. To generate the spectral frames the input stream is directly cut into frames of K samples with no sample overlapping across frames. K is an arbitrary value that can be set based on the desired frequency resolution given the bandwidth

of the system.

When the spectral frames arrive in the second stage, they are used to determine where signals may exist and the location of optimal band unoccupied spectrum for the system to operate in. The operation information is then sent into the third stage of the PAC: 'adapt'. Inside this third stage, a waveform selection system takes in the operation recommendation and adapts by transmitting the selected waveform in the appropriate spectrum. The PAC described above is shown as a streaming methodology in Figure 2.1.

The learning stage is where this work focuses and where the FSS algorithm lives. In this second stage, the system must 'learn' from the spectral frames and decide where other signals exist and what frequencies are available for its function. To determine where signals exist, we can analyze the magnitude output of the FFT to classify each frequency bin as either a high-power or low-power sub-band [5]. It

Figure 2.1: Perception action cycle for a cognitive sensor streaming data from an antenna into the sense stage. A transmission band is calculated and the corresponding signal is generated by the adapt stage and transmitted.

is assumed that all low-power sub-bands are unoccupied or noise only and therefore available for the system to occupy. After the initial classification of each bin, the bins must be examined again to group the bins. The grouping works to eliminate narrow, low-power frequency gaps that exist between high-power bands [6]. These gaps are closed and eliminated from operational consideration as they represent either a low-power component of the present signal or a gap between signals too narrow to be useful.

Figure 2.2 shows a threshold applied to a spectral frame with a 5G downlink signal present. The 5G waveform has variation within its signal structure. This variability causes a frequency bin, clearly within the 5G waveform's operational frequency, to fall below the threshold. The sub-band merging process would catch cases like this and prevent that single bin, or even an operator-defined number of

Figure 2.2: A 5G downlink signal shown with a threshold used to sort bins into high and low power groups. High power groupings with a small number of low power bins are grouped as they are part of a signal.

continuous bins, from being processed further for consideration. By merging these closely spaced bands, a better understanding of the location of the signal emerges.

For this work, a greedy algorithm is used to find the largest number of continuous open bins. This makes the merging of small bins seem redundant as those bins won't be selected anyway. It is still important to do the merging, however, so the bins don't have to be considered when looking at the continuous spaces. Merging is critically important for other types of uses of FSS that optimize for criteria other than the largest band. This could mean more complex computation may be carried out on the low power sub-bands than the greedy approach requires, which would be more costly.

FSS, in its original form, has a static threshold set manually by the operator from spectrum information gathered before the system is put into operation. This can cause the system to repeatedly fail or give a false positive over time. For this reason, signal detection techniques will now be introduced as a basis for the proposed dynamic threshold estimation discussed later.

#### 2.2 Signal Detection

Many methods of signal detection exist today. All attempt to provide the highest possible probability of detection while balancing a minimum number of false alarms . This work also considers mathematical complexity and data requirements as additional constraints. This section will discuss two detection methodologies: cyclostationary feature detection and energy detection. Three different implementations of energy detection will be shown: classic energy detection, cell averaging CFAR, and order statistic CFAR.

## 2.2.1 Cyclostationary Feature Detection

Human-generated signals have structures and "features" that are not found in natural noise which is usually modeled as a white Gaussian process [7]. If these features can be detected then signals should be detectable even in low signal-tonoise ratio (SNR) circumstances. Detection of signals in low power is one of the strengths of cyclostationary feature detection.

The autocorrelation function,  $R_{XX}(t_1, t_2)$ , provides the expected value of the product of the random process at time  $t_1$  and  $t_2$ . Further, the distance between  $t_1$  and  $t_2$  or lag time,  $\tau$  has its own properties for certain processes. One such case of interest is for wide sense stationary (WSS) signals.

WSS signals have an autocorrelation function that is strictly dependent on the lag time [8]. That is to say, for a WSS, if the lag between two points is the same, then the autocorrelation function is the same. This stationary autocorrelation function can be described by

$$R_{xx}(\tau) = E\{\mathbf{x}(t+\frac{\tau}{2})\mathbf{x}^{*}(t-\frac{\tau}{2})\}$$

(2.1)

where  $\tau = t_1 - t_2$ .

However, man-made signals are not strictly stationary and are instead called cyclostationary [9]. A cyclostationary signal's autocorrelation function is represented as a periodic or almost periodic function [10]. Unsurprisingly, the periodicity of the autocorrelation function of a cyclostationary process can be described as the Fourier coefficients.

$$R_{xx}(\tau) = \sum_{\alpha} R_x^{\alpha}(\tau) e^{j2\pi\alpha t}$$

(2.2)

where  $\alpha$  is the fundamental cyclic frequency.

For each value of  $\tau$ , the series in alpha describes the periodic nature of its autocorrelation. This function,  $R_x^{\alpha}(\tau)$ , is called the cyclic autocorrelation function (CAF) [10]. A frequency-domain dual of the CAF also exists and is named the spectral correlation function (SCF). Similar to the CAF, the SCF provides the cyclic frequency content of a process over its frequency.

The SCF function can be found by taking the Fourier transform of the CAF.

$$S_x^{\alpha}(f) = \int_{-\infty}^{\infty} R_x^{\alpha}(\tau) e^{j2\pi f\tau} d\tau$$

(2.3)

It is of note that the  $\alpha = 0$  value across frequencies is the power spectral density (PSD) of the signal. This is where this method excels, when the PSD is completely hidden within noise the other cyclic frequencies remain prominent. By remaining visible across other  $\alpha$  values, the signal is still detectable.

Unfortunately, it is not practical to directly calculate a set of SCFs for a given real-world signal. Therefore the SCF must be estimated as a cyclic periodogram, in this case using frequency smoothing [11],

$$S_x^{\alpha}(f) \stackrel{\Delta}{=} \frac{1}{\Delta f} \int_{f-\Delta/2}^{f+\Delta/2} \frac{1}{T} X_T(v+\alpha/2) X_T^*(v-\alpha/2) dv \tag{2.4}$$

Here  $X_T(v + \alpha/2)$  is the Fourier transform of x(t).

To carry out the frequency smoothing approach, a method called the FFT accumulation method (FAM) is used to demonstrate the computational complexity of the algorithm. The FAM method starts with several parameters: N, N', P and, L. N describes the number of samples in the signal observation. N' sets the frequency resolution as it is the length of the initial FFT operation. P sets the number of spectral frames of data that will be considered, while L is the overlap factor of the FFT. P and L are derived from N' and N and are given by the following:

$$L = N'/4 \tag{2.5}$$

$$P = N/L \tag{2.6}$$

Equation 2.5 shows a value of four selected to set the overlap. As the value increases and the overlap approaches N' so does the computational complexity of the algorithm. A divisor of four was shown to be a sufficient middle ground for computational complexity and preventing cycle leakage [12].

Before considering the FAM method the resulting domain should be formed. The desired output is a frequency-alpha matrix. If the sampling frequency is defined as  $f_s$ , the frequency dimension of the resulting field ranges from  $-f_s/2$  to  $f_s/2$ across 2N' bins. The  $\alpha$  dimension ranges from  $-f_s$  to  $f_s$  populating 2N bins. the resulting field is quite large even considering that only a diamond-shaped area of it will be used.

Starting the estimate, an  $N' \times P$  matrix is constructed such that a sliding FFT can be applied to the columns. The sliding factor of L is used to create a matrix from the signal, s, shown as:

$$\mathbf{Y} = \begin{bmatrix} s(1) & \dots & s((P-1)L+1) \\ s(2) & \dots & s((P-1)L+2) \\ \vdots & \ddots & \vdots \\ s(N') & \dots & s((P-1)L+N') \end{bmatrix}$$

(2.7)

A window is then applied down the columns before the FFT of each column is taken.

Each element of the matrix resulting from the previous step is multiplied by an exponential to smooth across frequency and compensate for any phase distortions introduced by the FFT. A complex conjugate matrix is generated, yielding the following 2 matricies:

$$\bar{\boldsymbol{Y}} = \begin{bmatrix} S(0, f_1) & \dots & S((P-1)L, f_1) \\ S(0, f_2) & \dots & S((P-1)L, f_2) \\ \vdots & \ddots & \vdots \\ S(0, f_{N'}) & \dots & S((P-1)L, f_{N'}) \end{bmatrix}$$

(2.8)

$$\bar{\boldsymbol{Y}}^* = \begin{bmatrix} S^*(0, f_1) & \dots & S^*((P-1)L, f_1) \\ S^*(0, f_2) & \dots & S^*((P-1)L, f_2) \\ \vdots & \ddots & \vdots \\ S^*(0, f_{N'}) & \dots & S^*((P-1)L, f_{N'}) \end{bmatrix}$$

(2.9)

An element multiply is carried out for each combination of rows in the matrix. The result of the operation is  $N^2 P$  length vectors, each at a new frequency and central alpha calculated using the following.

$$f_j = \frac{(f_k + f_l)}{2}$$

(2.10)

$$\alpha = f_k - f_l \tag{2.11}$$

Here  $f_j$  denotes the new frequency,  $f_k$  is the frequency from the row of the nonconjugate matrix and  $f_l$  is frequency from the row of the conjugate matrix. The new frequency is calculated for every combination The frequency value is used to index into the frequency-alpha matrix while the  $\alpha$  is the center of the alpha vector denoted by

$$\alpha + q\Delta\alpha \tag{2.12}$$

where  $\Delta \alpha$  is the resolution of the alpha component of the frequency-alpha matrix and q ranges from  $-\frac{P}{2}$  to  $\frac{P}{2}$  with a length of P.

A *P*-point FFT is taken across the rows after the multiplication. Unfortunately, only the central half of the elements of the resulting vectors are considered a good estimate of  $\alpha$ , which means calculated values were not all used [12]. Therefore, the central components of the estimate are inserted on the frequency-alpha matrix, across alpha, with an index of  $(f_j, \alpha_i)$  denoting the center point. This populates a diamond shape in the resulting matrix.

To determine the presence of a signal at any given frequency-cyclic frequency location, a simple hypothesis test can be employed. This is trivial as the threshold for this method can be pre-generated using the estimated SCF of a noise-only signal.

The parameters used to create the matrices that power this method can be used to describe the calculation complexities. There are a total of 2N'P multiplies required to taper the data, PN'N'-point FFTs must be carried out and 2N'P frequency shifts are carried out [12]. This is a massive amount of calculations, although most of the operations could be carried out in parallel, but instantiating many hundred or thousands of parallel FFT logic blocks would quickly devour the available floor space on the FPGA. A GPU could be used to accomplish this task but that would introduce latency as the data is transferred to the host PC.

Another big constraint that is connected to the complexity issue is observation length. To take advantage of the repeating structures of signals the observation of signal must be longer than a single spectrum estimate that may be used for simpler methods. The FAM method itself requires what are essentially spectral estimates to populate the columns of the first matrix. These constraints are the reasons that this thesis concentrates on energy detection methods. However, future work will examine efficient implementations of FAM or other cyclostaionary estimation methods to enable signal detection.

#### 2.2.2 Energy Detection

Energy detection describes an entire class of algorithms that are used for determining the presence of a signal based on power present in a sample of the electromagnetic spectrum. These methods work by estimating the noise floor of the environment and calculating a test statistic to apply to determine if a signal is present in a given frequency bin. Because this is only considering the power in a single snapshot the detection quality is based on the quality of the noise estimate. This section will discuss three specific methods: classic energy detection, cell averaging constant false alarm rate detection (CA-CFAR), and order statistic CFAR (OS-CFAR).

#### 2.2.2.1 Classic Energy Detection

Classic energy detection defines the two probability distributions as Gaussian for the noise-only case, and noncentral chi-squared for the signal present case [13]. For this method, the test statistic, V, is defined as the sum of the squared energy over a time T, defined by

$$V = \frac{1}{T} \int_{t-T}^{t} x^2(t) dt$$

(2.13)

For a signal of length T and bandwidth B to be captured effectively, 2TB samples must be taken or TB complex samples. This means that the test statistic becomes the sum of 2TB samples. 2TB, therefore, becomes the non-centrality parameter while the per-sample input signal to noise ratio (SNR) sets the mean of the noncentral chi-squared distribution. The signal-not-present distribution can therefore be defined as:

$$\boldsymbol{x_0} \sim \chi_{TB}^2 \tag{2.14}$$

The signal present distribution is defined as:

$$\boldsymbol{x_0} \sim \chi^2_{TB}(\mu) \tag{2.15}$$

with the  $\mu$  as the non-centrality parameter.

With the previous parameters set, the threshold,  $V'_T$ , for the test statistic can then be calculated using the following expression with the desired probability of false alarm [13].

$$P_{FA} = Prob\left[\boldsymbol{x_0} > V_T'\right] \tag{2.16}$$

Further, the probability of detection can be calculated using a similar probability expression or with the complementary error function  $erf(\bullet)$ .

$$P_D = Prob\left[\boldsymbol{x_p} > V_T'\right] = \frac{1}{2}\operatorname{erfc}\left[\frac{V_T' - 2TB - SNR}{2\sqrt{2}\sqrt{TB + SNR}}\right]$$

(2.17)

The SNR term is very limiting in this estimation approach. Signal SNR is one of the unknowns that signal detection and estimation are trying to solve. CFAR detectors mitigate this problem by employing a noise estimate that does not rely on SNR to create the threshold for their hypothesis tests.

Since both classic energy detection and CFAR use hypothesis testing, a brief discussion of the topic is presented here to give an intuition of what each probability value means. Figure 2.3 shows two Gaussian distributions with a vertical line denoting the threshold selected. These distributions were used for the sake of this

Figure 2.3: Two Gaussian distributions. The not present distribution with a mean of 0 and the present distribution with a mean of 4. (a) The probability of false alarm shown as the highlighted area. (b) The probability of missed detection is shown as the shaded area.

discussion and do not necessarily represent any detection method. The area in plot (a) shows the probability of false alarm. That is the area on the side of the threshold that registers a detection that is still under the not present curve. Similarly, the probability of a missed detection is the area to the left of the threshold that still lies below the present curve.

#### 2.2.2.2 Constant False Alarm Rate Detectors

CFAR detectors, as the name implies, adjust the threshold for each test, or each set of tests, to maintain a consistent number of false alarms coming through the system. Keeping this metric consistent helps to set the performance requirements for the systems that will be receiving the output of the detector. This is accomplished by observing the relationship between the threshold, T, and the probability of false alarm,  $P_{FA}$ , for a square law detector for a signal in complex Gaussian noise using the following expression [14].

$$T = -\sigma_w^2 ln(P_{FA}) \tag{2.18}$$

This relation relies strictly on the interference power,  $\sigma_w^2$ , which is not known. The interference power must, therefore, be estimated. Although there are numerous ways to accomplish this, only two will be discussed here.

It can be shown that the maximum likelihood estimate of  $\sigma_w^2$  is the average of the N available training samples [14]

$$\widehat{\sigma_w^2} = \frac{1}{N} \sum_{i=1}^N x_i \tag{2.19}$$

Cell averaging CFAR (CA-CFAR) takes advantage of this and takes the average of the 'cells' surrounding the cell under test. To prevent a signal that may be present in the cell under test from skewing the estimate, the cells around the cell under test are not included in the average. These excluded cells are called guard cells while the cells used are called reference cells. Figure 2.4 demonstrates this kind of structure.

Because an estimate for  $\sigma_w^2$  is now being used,  $ln(P_{FA})$  is no longer the correct scalar to be applied to find the threshold. This scalar is generalized as  $\alpha$  and must be determined for each type of CFAR detection. For CA-CFAR the relation between

Figure 2.4: The structure of CA-CFAR used when estimating the  $\widehat{\sigma_w^2}$  for cell  $x_i$ . Reference cells are evenly split on either side of the cell under test to provide a better estimate.

$\alpha_{CA}$  and  $P_{FA}$  are defined by

$$P_{FA} = \left(1 + \frac{\alpha_{CA}}{N}\right)^{-N} \tag{2.20}$$

From this equation, it follows that  $\alpha_{CA}$  is defined as

$$\alpha_{CA} = N \left( P_{FA}^{-1/N} - 1 \right) \tag{2.21}$$

Order Statistic CFAR (OS-CFAR) uses the same structure described in Figure 2.4, but instead of averaging the cells to create an estimate of  $\sigma$ , the cells in the reference are ordered and the  $k^{th}$  is selected as the estimate. Unsurprisingly, a new  $\alpha$  value is required for this method. However, no direct solution for  $\alpha$  exists. Therefore, it must be solved numerically using the following equation for  $P_{FA}$

$$P_{FA} = \frac{N! (\alpha_{OS} + N - k)!}{(N - k)! (\alpha_{OS} + N)!}$$

(2.22)

Notice, the calculation of  $\alpha$  in both CFAR cases only depend on  $P_{FA}$ . This means that the  $\alpha$  value can be precalculated and given to the system as a parameter. That makes these CFAR methods very computationally efficient. These algorithms can also operate with a small spectral snapshot.

The simplified operations of CFAR, and classic energy detection to a lesser extent, do come at the cost of reduced performance. Energy detection methods require a higher SNR for detection when compared to other, more complex methods. This degraded performance is one of the consequences of minimizing computation but also have limited knowledge of the signals to be detected [13].

## **Chapter 3**

# **Implementation Platform**

This chapter will discuss the implementation platform as a whole, before then driving down into the FPGA frameworks that enable the architecture discussed in Chapter 4. Software-defined radio will be discussed with the interaction between the radio hardware and the host PC described. An overview of the RFNoC<sup>TM</sup> framework is given in 3.2 with specific attention to the interconnects that allow data to move through the device. An analysis of the available interface options within the framework will be discussed with a justification for the interface that was selected for this work. The chapter concludes with a discussion on creating and modifying framework-generated files to make a custom RFNoC block.

#### 3.1 Software-Defined Radio

A software-defined radio (SDR), as the name suggests, allows the user to define the operation of the radio using only software without the need to change front-end hardware. Designed to be used for communications, SDRs have allowed for a shift away from application-specific hardware solutions to allow for more flexibility in application and use [15]. These systems use tunable oscillators and transceivers to allow for baseband data to be obtained from a wide range of operating frequencies. Similarly, these radios can take baseband data and mix it up to be transmitted at higher frequencies. Many radios allow for this to be done with minimal interruption to operation, only needing to wait long enough for an oscillator lock to be achieved.

An Ettus USRP X310 radio was used for this work and has a Xilinx Kintex®7-410T FPGA on the main motherboard to handle data movement through the various RF channels. with dual UBX-160 daughter cards, pictured in Figure 3.1. This hardware allows for dynamic transmit and receive from 10 MHz to 6 GHz with up to 160 MHz of instantaneous bandwidth [16]. The X310 provides options of dual 10-gigabit Ethernet and PCI express to enable control and data transfer to and from the host PC [17]. Dual 10 gigabit Ethernet connections were used to interface with the radio to ensure the highest data throughput.

Control of the hardware is accomplished using Ettus' software library, USRP Hardware Driver (UHD). This hardware driver communicates with the radio and

Figure 3.1: X310 pictured with top cover removed to show daughter cards installed.

allows for the transmission of data between the host computer and the radio [18]. UHD supports a C++ and Python API that can be used to create custom scripts. The open-source nature of UHD has seen it also be incorporated and extended into other software packages that can greatly simplify the use of the hardware.

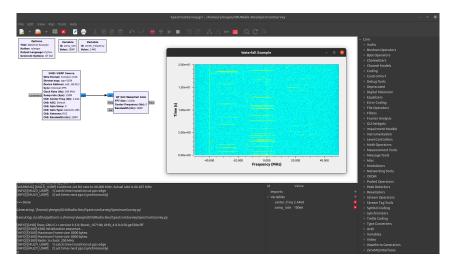

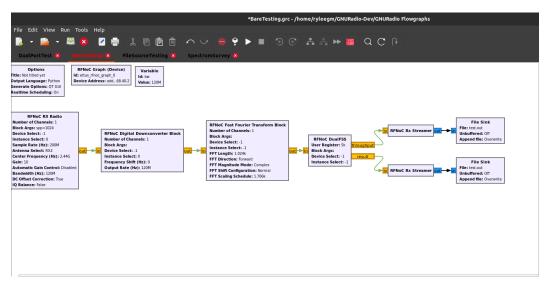

One such open-source project is GNURadio. GNURadio uses drag and drop blocks connected with virtual wires to build 'flowgraphs' that visually model the data processing flow of the program. Figure 3.2 shows a flow graph that streams data received by the radio to the host computer where the host computer then generates a waterfall plot showing the frequency content of the collected data. Although the flowgraph shown is very simple, GNURadio offers a large variety of radio blocks to enable many different types of complex behavior. All of the GNU-Radio blocks included with the software do the computation on the host PC and send data back and forth to the radio for transmit or receive as needed.

GNURadio is more flexible than just the included blocks, it is a platform that allows for the development of streaming algorithms that can be run on the host

Figure 3.2: GNURadio Companion software shown with a simple, two block flowgraph that takes data streamed from the radio and process it into a waterfall plot.

PC. To enable this development, GNURadio provides tools and tutorials that help streamline the use of the platform. Moreover, a strong user community exists with a large number of out-of-tree modules available to build on the already robust library of preinstalled apps. This helps to bridge the gap between the initial installation and developing the first block.

#### **3.2 RF Network-on-Chip**

Some of the Ettus radios, like the X310, have an FPGA inside with free space that can be utilized for hardware-accelerated processing [17]. Offloading computation from the host computer to application-specific FPGA designs not only provides a performance uplift but also removes the latency associated with the data transfer to the host PC. To allow for the development of additional capabilities utilizing the available FPGA space, a common framework is used to interconnect processing blocks and control data flow. RFNoC provides this function with a block-based architecture connected through two main operational planes, the control plane and the data plane [1]. The design steps needed to generate one of these NoC blocks will be presented in Section 3.4. This step-by-step discussion provides information that may not be otherwise available in a single place. The design flow also provides lessons learned to assist future users of the framework and reduce the learning curve for use.

Both planes use the same bus type called the Compressed Hierarchical Datagram for RFNoC (CHDR). This format is packetized with each packet containing a header, optional timestamp, a user-defined number of optional metadata words, and some number of payload words. The width of the busses is flexible at the design stage and can be changed for the entire architecture. This bus width is usually the width of each of the payload words, as the header has a set format width of 64 bits. One of the only constraints enforced with this bus is that at least one payload word must be in every packet.

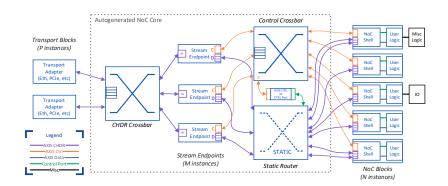

There are four main types of structures that make up the RFNoC framework: the RFNoC block, the streaming endpoint, the data plane and control plane routing crossbars, and the main CHDR crossbar. An RFNoC block is where the user develops and implements their algorithm. Data is fed into the block from the framework, some operation is carried out on the data, and then that data is transmitted out to the next block.

Each block or sequence of blocks sends and receives data and control packets from the block streaming endpoint. These streaming endpoints are responsible for routing the data to and from the block. Streaming endpoints are the origin of the data for user blocks and the destination point for the output data of the user blocks [1].

Between the RFNoC block and the streaming endpoint is the static data crossbar and the full mesh control crossbar. The control crossbar is mainly tasked with routing control packets from the origin stream endpoint to the appropriate consumer. Since this crossbar is full mesh, however, it also carries control packets from block to block without the need of routing to the stream endpoint.

Data is routed from the stream endpoint to block and back through the static router. Routes through this crossbar are fixed and require a new FPGA image to be synthesized to change. There is no rule about each RFNoC block requiring its own streaming endpoint, in fact, it is possible to link RFNoC blocks directly together across this crossbar.

Static routing is a critical design decision and the desired flexibility of a block connection must be considered when making routing determinations. Data flow between two blocks through static routing is preferred over that of the streaming endpoint as it reduces the FPGA resources and reduces the number of clock cycles between data leaving one block and arriving at another. So, while every block could have its own streaming endpoint for full flexibility, there is an incentive to limit block to block transmission to static connections when appropriate.

A great example of the use of the static crossbar is the radio block and the digital down-conversion block (DDC). These two blocks are always connected and therefore all of the default images have the Radio block and the DDC statically connected. Other blocks, like a hardware FFT, are not always going to be used in the data chain and therefore need to be connected to streaming endpoints. A single streaming endpoint connects to the input and output of its assigned RFNoC block and is connected to the main CHDR crossbar.

The main CHDR crossbar is where all of the dynamic connections take place. A connection between any two arbitrary ports connected to the crossbar can be established as it is a fully meshed structure. Additionally, this main crossbar is full bandwidth and can connect two stream endpoints dynamically without data loss. Importantly, the CHDR crossbar not only connects the stream endpoints but also provides the connections to the interfaces that connect to the host PC. Figure 3.3 shows how these structures are arranged for operation.

#### **3.3 Block Interface**

The CHDR bus itself is a lightweight implementation of the AXI bus interface introduced by Xilinx to standardize the connection between Xilinx-provided IP blocks. The RFNoC implementation of this interface utilizes only tdata, tvalid, tready, and tlast signal lines for each the input and the output [1]. This means

Figure 3.3: An example showing how the internal RFNoC structures may connected for operation [1].

that a framer/de-framer is needed to divide the data packets into their respective header, metadata, and data elements. Fortunately, Ettus provides two framer/deframer interfaces, AXI-Stream Payload Context and AXI-Stream Data, as part of their development tools.

Since both of these interfaces use the AXI-Stream interface to some extent, a brief overview should be provided before continuing. The AXI-Stream bus is a subset of a larger set of AXI bus protocols [19]. Table 3.1 describes the signals that are used in AXI. Notably, this interface provides a valid signal that is fed into

| Signal Name | Signal Description                                       |

|-------------|----------------------------------------------------------|

| tdata       | The payload word for the data stream.                    |

| tlast       | Asserted on the last payload word of the packet          |

| tvalid      | Asserted when the value on tdata is valid.               |

| tready      | Asserted when by the recipient to signal readiness.      |

| tuser       | Describes the word type for the current word on the bus. |

Table 3.1: A description of the signal used in a simple AXI-Stream interface.

the receiving block and a ready signal that comes from the receiving block to the sender. This allows for the blocks to agree on a successful transmission before the transaction is complete. This also makes the logic for advancing the stream incredibly simple. If the valid signal and ready signals are both asserted on a clock cycle then the stream can be advanced. The user signal is not strictly required for the AXI-Implementation but is used in the AXI-Stream Payload Context interface. This signal provides information about the currently presented word on the data line, which is useful if different types of data encodings are used in a single data stream.

The AXI-Data interface is the simpler of the two available interfaces. The interface provides a standard AXI-Stream interface for the payload data of the packet but removes user-facing complexity by presenting the header data as separate signals that are valid throughout the receipt of the data packet. Table 3.2 provides a list of signals that are provided to the block in addition to the previously described AXI-Stream signals that are used for the data stream. Although the AXI-Data inter-

| Signal Name | Signal Description                                |

|-------------|---------------------------------------------------|

| ttimestamp  | Timestamp associated with the packet.             |

| tlength     | Length of the packet in bytes.                    |

| teov        | Signals the end of a vector.                      |

| teob        | Signals the end of a burst of associated packets. |

Table 3.2: The relevant signals for the AXI-Stream Data user interface.

face does provide an easier interface to use, it does introduce some ambiguity into the timing of the packet transmission introduced by the need to generate its header data and reconstruct a new header if it is changed by the user block.

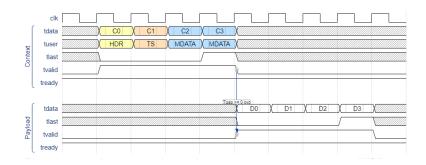

The other interface option is AXI-Stream Payload Context. This interface provides an AXI interface for data, like the previous option, but it also provides the header, timestamp, and metadata information in an additional AXI stream called the context stream. Because both of these streams are being put onto a single bus by the framer/de-framer logic it is important to serve the context data before the payload data. Both of the streams use the signals as they are described in Table 3.1 to provide the AXI-Streams, except that the user signal is only provided in the context stream as the data stream only has one encoding type. The timing diagram shown in Figure 3.4 shows how the context and payload streams are linked together and the structure that must be maintained when the packet is forwarded or a new packet is created. Although this interface requires more consideration for two separate data streams that are linked in time, it allows a consistent model to be applied to all data and allows metadata to be used if desired. It is for those reasons that the AXI-Stream Payload Context interface was chosen for this work.

The framer/de-framer for these interfaces is located in a module called the NoC shell and can be seen on the architecture graph inside the RFNoC blocks in Figure 3.3. The NoC shell is mostly a black box to the user, except for a first in first out (FIFO) buffer on each of the ports. This buffer allows the user block to stop accepting data, using the tready signal, without dropping packets or packet words. A backend interface is also implemented in the NoC shell as a 512-bit status interface and a separate control interface that is used by the larger framework and is not of use to the user [1].

Figure 3.4: The timing diagram for a the AXI-Stream Payload Context interface. It shows a 4 word data packet with timestamp [1].

# 3.4 Design and Control of a Block

RFNoC provides several tools to try to reduce the overhead required to build a custom FPGA block. One of the ways this reduction is accomplished is by managing abstraction and requiring the user to interact with and manage a bare minimum of files required to successfully implement a design. All development took place on a desktop machine with a Intel®Xeon®processor and 256 gigabytes of ram running Ubuntu 20.04. The process described in this section was tested using RFNoC 4.0 with no out-of-branch patches applied. Of course, the more complex a block is and the more the structure deviates from the default configuration, the more management must take place. This section seeks to describe the design flow of creating a block of similar complexity to those presented later in this work. Numerous topics will be covered in an order that mimics the actual order that a user may take to build a block. The topics discussed include: generating framework HDL using a configuration file, adding additional user registers to the block, changing the number of ports and their identifier, and making changes to the GNURadio block to reflect the new additions of the block.

The development journey begins with the rfnocmodtool, a command-line tool that is used to create RFNoC modules and blocks. Modules contain RFNoC blocks, this hierarchy allows users to group similar blocks together and help manage files when many blocks are in development [20]. A module can be created using the following command:

#### # rfnocmodtool newmod

The user will be prompted to enter information about the module that will be used to create a directory with the required folder structure. Navigating inside of the file directory that was created from the newmod command, a user can generate the files necessary to start work on the block.

# rfnocmodtool add

The add command above prompts the user for information about the block, of which only the name is a required field, the defaults for the remaining options are sufficient for a successful start to the process.

There are seven main files that the user needs to manipulate to make a fully flexible RFNoC block. Table 3.3 lists the files of interest and their location relative to the top level of the module. These files will be used throughout the development flow and their purpose will be discussed as they are used.

The Verilog files rfnoc\_block\_blockName.v and rfnoc\_shell\_blockName.v are both generated automatically. rfnoc\_block\_blockName.v is the file that describes the RFNoC block under development and this is where the HDL for the user's design will go. The rfnoc\_shell\_blockName.v is instantiated inside the main design and is responsible for the framer/de-framer of the selected interface as discussed in the previous section. The RFNoC shell also implements a backend interface that helps control RFNoC that is completely invisible to the user and should not be modified.

Before jumping into the Verilog files the user should first configure the block and generate new HDL files to meet their needs. Block configuration settings are the

| File Name                           | Location      |  |  |

|-------------------------------------|---------------|--|--|

| rfnoc_block_blockName.v             | /rfnoc/fpga   |  |  |

| noc_shell_blockName.v               | /rfnoc/fpga   |  |  |

| blockName_x310_rfnoc_image_core.yml | /rfnoc/icores |  |  |

| blockName_block_ctl_impl.cpp        | /lib          |  |  |

| blockName_impl.cc                   | /lib          |  |  |

| blockName.yml                       | /rfnoc/blocks |  |  |

| module_blockName.block.yml          | /grc          |  |  |

Table 3.3: The relevant files for the RFNoC block development cycle.

responsibility of the blockName.yml file. YAML Ain't Markup Language (YAML), is a human readable format that is used throughout RFNoC and GNURadio to define parameters and describe blocks and is denoted with the .yml file extension [21].

There are four main sections to the blockName.yml file: block information, clocks, control ports, and data ports. Block information should not be changed as it is mostly informative. The clocks section controls the clock frequencies of the various busses, there are two clocks that can be chosen from on the X310: 200 MHz and 184.32 MHz. It is critical to ensure that the CE clock is in the list and that 200 MHz is selected as its clock speed, enabling full speed operation. Setting the clock is as simple as

```

clocks:

- name: ce

freq: "[200 MHz]"

```

This work did not utilize the control port as a master port and therefore the default settings of this section were always used.

The final section defines the configuration of the data ports. Multiple named ports can be defined using the following parameters.

```

inputs:

input1:

item_width: 32

nipc: 1

info_fifo_depth: 32

context_fifo_depth: 32

payload_fifo_depth: 32

format: sc16

mdata_sig: ~

```

Buffer sizes are mostly up to the user to determine. These FIFOs sit at the port edges and help to prevent overflows if the user block very briefly stops accepting input. Ideally these FIFOs should be about one packet length as data beyond a full packet will be backed up to the streaming endpoints. The same settings apply to the output ports that have identical parameters under an outputs tag instead of an inputs tag.

Once the block YAML is configured to the users desired state, new Verilog files can be generated. Ettus provides a script called rfnoc\_create\_verilog.py that generates the framework for the configuration defined in blockName.yml. The script is a part of UHD and exits in the UHD install directory under /host/utils/rfnoc\_backtool directory. When the user is in the same directory as the script it can be executed from the command line using the following,

./rfnoc\_create\_verilog.py -c path/to/block/yaml

-d path/to/Verilog

Now that the two Verilog files have been updated, the user can begin to decide how many user registers they want. Register logic is generated inside of the rfnoc\_block\_blockName.yml file and a single register is defined by default, providing a template for the addition of more registers. Each register has an address parameter and a reset parameter, with the default address set to zero and a default value of 0. These two parameters should be copied and used for each new register, incrementing the address by four as the register words are passed in as 32-bit integers.

First, the user should instantiate a 32-bit Verilog register for each new RFNoC controlled register that is needed. The next part of the user logic is an *always* block synchronized with the control port clock. Inside this *always* block there are 3 *if* statements that control register functions. The first of these *if* blocks checks the reset line, here the user should add a simple register assignment resetting the Verilog register to the default value parameter

The other two *if* statements check for a register read or a register write. Both of these contain *case* statements using the address to multiplex between the registers. A copy of the default register logic with the appropriate changes to the parameters will successfully set up the hardware of the registers. The Verilog code in listing 3.2 provides this user logic as it can sometimes be absent from generated files in version RFNoC 4.0.

```

localparam REG_USER1_ADDR = 0; // Address for user register

localparam REG_USER1_DEFAULT = 0; // Defult value

reg [31:0] Reg One Value = REG USER DEFAULT;

always @(posedge ctrlport_clk) begin

if (ctrlport_rst) begin

Reg_One_Value = REG_USER_DEFAULT;

end else begin

// Default assignment

m_ctrlport_resp_ack <= 0;</pre>

// Read user register

if (m_ctrlport_req_rd) begin // Read request

case (m_ctrlport_req_addr)

REG_USER_ADDR: begin

m_ctrlport_resp_ack <= 1;</pre>

m_ctrlport_resp_data <= Req_One_Value;</pre>

end

endcase

end

// Write user register

if (m_ctrlport_req_wr) begin // Write requst

case (m_ctrlport_req_addr)

REG_USER_ADDR: begin

m_ctrlport_resp_ack <= 1;</pre>

Req_One_Value <= m_ctrlport_req_data[31:0];</pre>

end

endcase

end

end

```

Listing 3.1: The default register logic described above. Provided as it is not always correctly generated in version 4.0.

Immediately below the register logic, the port signals are set to default values. The user can replace these default connections and insert their well tested and simulated Verilog that they would like to operate on their data. User logic is the last part of the file and concludes the work that needs to be done in the Verilog files.

Next, the software interface must be informed of the changes to the port configuration and the additional user registers. blockName\_block\_ctl\_impl.cpp is where the the API goes to generate the control signals necessary to configure the block when the block constructor is called by the user script or GNURadio. First, the user needs to create new uint32\_t constants for the registers that were just created in the Verilog. A call to the register\_property function should be made inside of the private \_register\_props function with a closure to provide the functional information. After the property is registered, a custom property type needs to be instantiated at the bottom of the file, this is the property that is passed into the register\_property. The constant declaration, property call, and property type should look similar to:

```

const uint32_t Name_block_ctl::REG_USER1_ADDR = 0;

const uint32_t Name_block_ctl::REG_USER1_DEFAULT = 0;

void _register_props() {

register_property(&_user_reg, [this]() {

int user_reg = this->_user_reg.get()

this->regs().poke32(REG_USER_ADDR, user_reg);

});

...

});

...

}

property_t<int> _user_reg{"user_reg", REG_USER1_DEFAULT,

{res_source_info::USER}}

```

Similar to the process to create a register property, a block edge property is

end

required for each of the ports that are used on the block. Just like with the register, constants need to be defined for each of the ports, each property must be registered and a property type must be instantiated. Unlike the register, the constants should only be incremented by 1 and the input and output edges are indexed separately so there should be an output zero and an input zero. A further difference from the register is an additional property resolver that helps the software to understand what data types should be sent in and out of the block. This should match the value that was used in the port definition of the block YAML, but there is not a check to make sure that the values are consistent.

Below is a sample snapshot of code that helps define the necessary statements that are required to successfully set up the hardware:

```

constexpr uint32 t input1 port = 0;

constexpr uint32_t output1_port = 0;

void _register_props() {

. . .

register_property(&_type_in_input1);

register_property(&_type_out_output1)

. . .

add_property_resolver({&_type_in_input1},

{&_type_in_input1}, [this](){

_type_in_input1.set(IO_TYPE_SC16)

});

add_property_resolver({&_type_out_output1},

{&_type_out_output1}, [this](){

_type_out_output1.set(IO_TYPE_SC16)

});

. . .

}

. . .

property_t<std::string> _type_in_input1 =

property_t<std:string>{ PROP_KEY_TYPE,

IO_TYPE_SC16, {res_source_info::INPUT_EDGE,

input1_port } ;

property_t<std::string> _type_out_output1 =

property_t<std:string>{PROP_KEY_TYPE,

```

# IO\_TYPE\_SC16, {res\_source\_info::OUTPUT\_EDGE, output1\_port}};

If the user is planning on using the block with GNURadio then there is one more step before moving on to the final image synthesis tasks. The graphical representation of the block that is used for drag and drop connection of the block needs to know what the port configuration is and what each of the register values should be. All of this configuration is done in the module\_blockName.block.yml file, utilizing three main sections.

The first section is the template section, this provides the import argument and the constructor parameters so that GNURadio can correctly setup the auto generated script. Of these parameters only the callbacks need to be manipulated. These callbacks connect through to the previous properties that were instantiated to manage the control read and writes to the registers in the blocks. One call back is needed for each of the registers that are used and it is important that the first argument in the callback is the same as the one provided in the last property object in the implementation file.

The second section, parameters, is all of the fields within the GNURadio block. Register fields for the user to input values into the GUI block are created here. It is critical that the ID of this value is the same as the one given to the callback in the previous section of this file. The label and default value can be anything the user wants to have visible in the GUI. It is a good idea to have the block defaults in this file be the same as the default parameters previously set but, again, this is not a requirement.

The last section of this file is used to create the actual ports on the GUI block. Each port has three parameters: domain, label and dtype. For the purpose of this work the domain will always be rfnoc and the dtype will be sc16, the label can be whatever the user wants to display. The port assignment between these definitions and the properties defined in the previous file are based on the port number assigned previously, meaning that the first import port reference in the .block.yml file corresponds to the zeroth port in the property definition.

An example of each of the necessary fields are provided below for illustration.

```

callbacks:

- set_int_property('user_reg', $(user_reg))

. . .

parameters:

- id: user_reg

label: User Register Name

dtype: int

default: 0

. . .

inputs:

- domain: rfnoc

label: Input Port Name

dtype: 'sc16'

outputs:

- domain: rfnoc

label: Output Port Name

dtype: 'sc16'

```

With all of the initial block setup and design complete the user can define the blocks that are needed in the FPGA image and how they are connected through the various crossbars. Settings for the layout of the blocks are handled in the block-Name\_rfnoc\_image\_core.yml file. This file is structured into four section: streaming endpoint definitions, block definitions, block connections, and clock assignment.

First the streaming endpoints need to be defined, each have three block parameters: ctrl, data and buff\_size. The ctrl and data parameters determine whether or not traffic from that plane flows through the endpoint. buff\_size determines the size of the buffer that is used to prevent dropped packets if the recipient of the stream halts operation momentarily. The parameters are formated as follows

```

stream_endpoints:

ep0: #Label can be anything

ctrl: False

data: True

buff_size: 32768

```

Block definitions are next with each having a different set of parameters. The only common parameter is the block\_desc, this is the name of the blockName.yml file and should be formatted as seen below.

noc\_blocks: blockName0: #Label can be anything block\_desc: 'blockName.yml'

Since the block and module were created by the modtool then the software knows the directory structure and where to find these files.

Next, connections must be defined for each of the blocks. Decisions about the routing through an endpoint or through the static crossbar only are made at this point. Two different connection examples are given below. The first provides a connection from the ep0 as the source of the data to the input of duc0 (Digital Up Converter) block, then it is routed from the duc0 output to the input of the radio0 block. This is an example of a static connection between two block using only the static crossbar between the DUC and radio, this forms the transmit chain to the radio hardware.

The second example shows a block connected with the streaming endpoint on each end. It is important to note that each endpoint should only be used for a single pair of signals. If the user's block has an odd number of ports or multiple pairs of ports, multiple streaming endpoints are necessary.

#### connections:

```

- {srcblk: ep0, srcport: out0, dstblk: duc0, dstport:

in_0 }

- {srcblk: suc0, srcport: out_0 dstblk: radio0, dstport:

in_0 }

```

The final piece of this file defines the clock connections to the block. Clocking is a critical piece for ensuring that the operation of all of the blocks goes smoothly. For this work all of the clocks were defined using the compute engine (CE) clock except for radio blocks which are connected to the radio clock. An example of both types of clocking connections are shown as,

```

clk_domains:

- { srcblk: _device_, srcport: radio, dstblk: radio0,

dstport: radio }

- { srcblk: _device_, srcport: ce, dstblk: ddc0,

dstport: ce }

```

Finally, after all of these files have been updated to set up the configuration of the block, the module can be built and the FPGA image synthesized. To start the build and synthesis process the user needs to navigate, within the terminal, to the module build directory. Once in the directory, the make files for the install need to be created using

```

# sudo cmake -DUHD_FPGA_DIR=./path/to/uhd/fpga/dir

```

After this process completes the make files can be used to install the module into GNURadio with the command,

```

# sudo make install

```

At this point the block should be visible inside of GNURadio at the bottom of the module tree. The make files are now ready for synthesis to the FPGA. Synthesis requires that the Xilinx Vivado is already installed with version 2019.1 being the tested version. The Vivado build is initiated by executing, # make blockName\_rfnoc\_image\_core.yml

in the build directory.

The build process can take a significant amount of time, throughout this work 45 minutes was found to be very common but times of up to four or five hours were also encountered depending on the content of the user logic. Once the build is complete a .bit file is generated in the uhd/rfnoc/top/usrp3/x300/build directory. The .bit file is used to program the FPGA using the uhd image loader tool. The image loader was the most successful when using the following argument configurations:

####

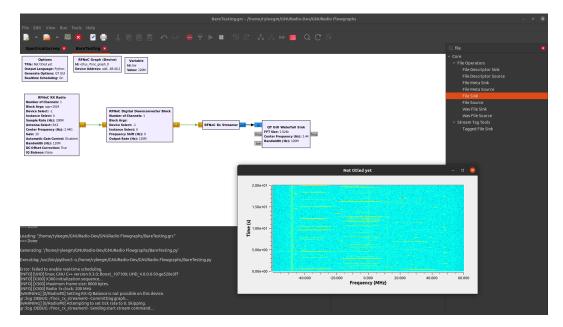

After the image loader has completed its operation, the user can power cycle the radio and test their new hardware block using the UHD API or GNURadio. Figure 3.5 shows the flowgraph enabling the waterfall display implemented with RFNoC blocks.

It is important to note that when using any RFNoC blocks the entire radio must be built using the RFNoC block variants. Using the RFNoC components means that instead of using the USRP source block that is packaged in GNURadio a user must instead use the RFNoC radio block. Because the RFNoC radio block is statically connected to the Digital Down Converter (DDC) it also must be inserted into the flowgraph. Having to model the receive chain using NoC blocks instead of the provided GNURadio source can present additional concerns. However, this is still simpler than the alternative of scripting from the UHD API directly, which has to instantiate the radio chain individually whether custom RFNoC blocks are used or not.

Figure 3.5: An example showing how the provided radio and DUC blocks can be used to replace the USRP Source block used previously [1].