## EFFICIENT DIGITAL BASEBAND PREDISTORTION FOR MODERN WIRELESS HANDSETS

A Thesis Presented to The Academic Faculty

by

Seydou Nourou Ba

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2009

## EFFICIENT DIGITAL BASEBAND PREDISTORTION FOR MODERN WIRELESS HANDSETS

Approved by:

Yucel Altunbasak, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

G. Tong Zhou, Co-advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Ghassan Al-Regib School of Electrical and Computer Engineering Georgia Institute of Technology Xiaoli Ma School of Electrical and Computer Engineering Georgia Institute of Technology

James Stevenson Kenney School of Electrical and Computer Engineering Georgia Institute of Technology

Ronghua Pan School of Mathematics Georgia Institute of Technology

Date Approved: October 30, 2009

For my family.

### ACKNOWLEDGEMENTS

As my PhD endeavor comes to an end, I would like to express my gratitude to the people who greatly contributed to its success.

First, I would like to thank my advisors, Dr. Yucel Altunbasak and Dr. G. Tong Zhou for their continuous support and guidance throughout my PhD studies. I have greatly benefited from their valuable advices and encouragements. I will certainly continue to benefit from my experience in the Center for Signal and Image Processing in my future career.

I would like to thank my thesis committee members: Dr. Xiaoli Ma, Dr. Ronghua Pan, Dr. James Stevenson Kenney, and Dr. Ghassan Al-Regib for accepting to serve on my committee and helping to greatly improve the quality of my dissertation with their thoughtful suggestions.

I would also like to thank Dr. Khurram Waheed, Dr. Fernando Mujica, Dr. Imtinan Elahi and Dr. Darnell Moore from Texas Instruments, whose fruitful collaboration has been essential to the successful completion of my thesis.

I also tremendously benefited from my teaching assistant experience under the supervision of Dr. James H. McClellan.

I would like to thank my fellow PhD students: Ibrahima Ndiour, Mamadou Diao, Arnaud Amadjikpe, Illenin Kondo, Salman Aslam, Bob Baxley, Rajbabu Velmurugan, Tariq Arici, Brett Matthews, Milind Borkar, and Ali C. Begen for their friendship and insightful discussions.

I would also like to thank the ECE graduate academic advisors. My special thanks go to Marilou Mycko and Dr. David Hertling for offering me my first teaching assistant position.

And last but not least, I thank my family for their unconditional support, their encouragements, and their prayers during difficult times. A lot of credit goes to my wife Oumou, who inspired me and helped me complete this thesis with her kindness and patience.

# TABLE OF CONTENTS

| DEI     | DICAT | ION                                                                         |

|---------|-------|-----------------------------------------------------------------------------|

| ACK     | NOV   | LEDGEMENTS iv                                                               |

| LIST    | OF    | rables vii                                                                  |

| LIST    | OF    | FIGURES                                                                     |

| SUMMARY |       |                                                                             |

| Ι       | INT   | RODUCTION                                                                   |

|         | 1.1   | Motivation                                                                  |

|         | 1.2   | Objectives                                                                  |

|         | 1.3   | Outline                                                                     |

| II      | BAG   | KGROUND                                                                     |

|         | 2.1   | Power Amplifier Nonlinearity                                                |

|         | 2.2   | Principles of Digital Predistortion 12                                      |

|         |       | 2.2.1 Cartesian Mapping Predistorter                                        |

|         |       | 2.2.2 Complex-Gain Predistorter                                             |

|         |       | 2.2.3 Polar Predistorter                                                    |

|         | 2.3   | Calibration and Adaptation                                                  |

|         |       | 2.3.1 Polynomial Predistorter                                               |

|         |       | 2.3.2 Lookup Table Predistorter                                             |

|         |       | 2.3.3 Predistorter with Memory 20                                           |

| III     | SPA   | CING OF A POLAR LUT PREDISTORTER                                            |

|         | 3.1   | Analysis of Linearly-Interpolated LUT                                       |

|         | 3.2   | Analysis of LUT Predistorter Spacing                                        |

|         |       | 3.2.1 Optimal Spacing of Nearest Neighbor LUT Predistorter                  |

|         |       | 3.2.2 Optimal Spacing of Linearly-Interpolated Polar LUT Predistorters 31   |

| IV      |       | IMAL SPACING OF INTERPOLATED COMPLEX-GAIN LUT PREDIS-         TERS       33 |

|         | 4.1   | Residual Distortion in LUT-Predistorted Transmitters                        |

|         | 4.2   | Optimal LUT Spacing                                                         |

|      |     | 4.2.1 Performance Evaluation with Optimal LUT Spacing    | 42 |

|------|-----|----------------------------------------------------------|----|

|      |     | 4.2.2 Interpolated vs. Non-Interpolated LUT Predistorter | 45 |

|      |     | 4.2.3 Effect of Operating Temperature                    | 47 |

|      | 4.3 | Complex Companding                                       | 48 |

|      | 4.4 | Physical Implementation of LUT Spacing                   | 50 |

|      | 4.5 | Conclusion                                               | 53 |

| V    | POV | WER CONTROL AND LUT SPACING                              | 54 |

|      | 5.1 | Constant-SNR Spacing                                     | 55 |

|      |     | 5.1.1 Constant-SNR Spacing in Polar Predistorters        | 55 |

|      |     | 5.1.2 Constant-SNR Spacing in Complex-Gain Predistorters | 56 |

|      | 5.2 | Low-Complexity LUT Spacing                               | 58 |

| VI   | AM  | PLITUDE APPROXIMATION FOR DIGITAL PREDISTORTERS          | 63 |

|      | 6.1 | A Low-Complexity Amplitude Approximation                 | 64 |

|      | 6.2 | Practical Implementation and Performance                 | 68 |

|      | 6.3 | Conclusion                                               | 71 |

| VII  | EFF | FICIENT LUT PREDISTORTER ADAPTATION                      | 72 |

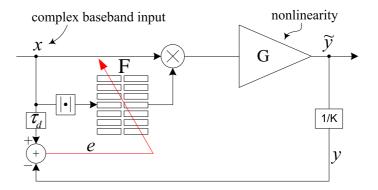

|      | 7.1 | Adaptation of Complex-Gain LUT Predistorters             | 72 |

|      | 7.2 | Updating a Linearly-Interpolated LUT                     | 77 |

|      | 7.3 | Limitations of Direct Learning                           | 79 |

|      | 7.4 | Conclusion                                               | 81 |

| VIII | PRI | EDISTORTION AND QUADRATURE IMBALANCES                    | 82 |

|      | 8.1 | Interactions Between IQ Imbalance and Nonlinearity       | 82 |

|      |     | 8.1.1 Effect of Nonlinearity on IQM Correction           | 85 |

|      |     | 8.1.2 The Mapping Predistorter                           | 87 |

|      |     | 8.1.3 Iterative IQMC Estimation                          | 88 |

|      | 8.2 | $2 \times 2$ Transform Predistorter                      | 89 |

|      | 8.3 | Conclusion                                               | 93 |

| IX   | EFF | FECT OF VSWR ON PREDISTORTER ADAPTATION                  | 94 |

|      | 9.1 | Effect of Varying Antenna Impedance                      | 94 |

|      | 9.2 | Adaptive Loop Gain Normalization                         | 96 |

| Х   | CONCLUSI     | ONS                              | 99  |

|-----|--------------|----------------------------------|-----|

|     | 10.1 Contril | butions                          | 99  |

|     | 10.2 Future  | Research                         | 100 |

| APP | ENDIX A      | LINEAR INTERPOLATION ERROR       | 101 |

| APP | ENDIX B      | VHDL CODE FOR HARDWARE SYNTHESIS | 103 |

| REF | ERENCES .    |                                  | 117 |

# LIST OF TABLES

| 4.1 | EDGE EVM for different compander LUT size $L$                               | 51 |

|-----|-----------------------------------------------------------------------------|----|

| 4.2 | Gate count resulting from hardware synthesis                                | 51 |

| 5.1 | Practical implementation of optimal spacing.                                | 60 |

| 5.2 | Practical implementation of optimal spacing.                                | 62 |

| 6.1 | WCDMA EVM and ACLR for amplitude and power indexing. $\ldots$               | 64 |

| 6.2 | Coefficients and error for an amplitude approximation with three intervals. | 68 |

| 6.3 | Performance of amplitude approximation: WCDMA EVM and ACLR                  | 69 |

| 8.1 | Effect of nonlinearity on IQM correction estimation                         | 87 |

| 8.2 | Iterative IQMC Estimation.                                                  | 89 |

## LIST OF FIGURES

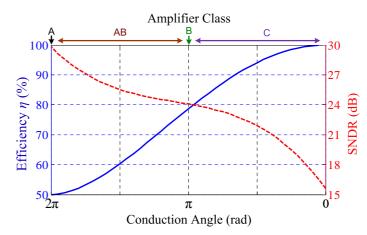

| 2.1  | Power efficiency and SNDR vs. conduction angle                                                                                                                                          | 7  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

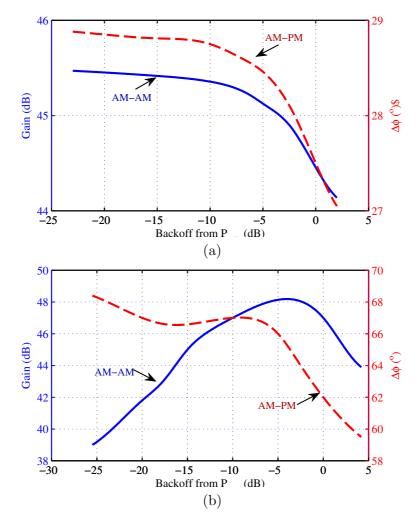

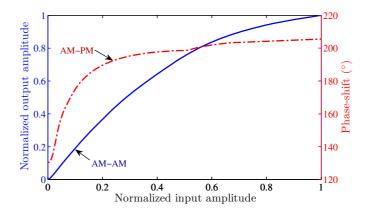

| 2.2  | AM-AM and AM-PM conversion functions. (a) Class-A amplifier. (b) Class-C amplifier                                                                                                      | 8  |

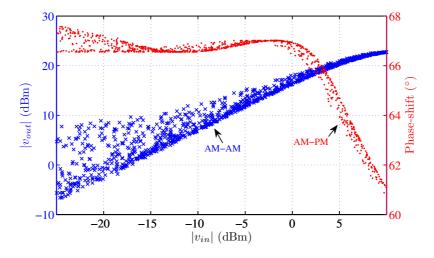

| 2.3  | Amplifier nonlinearity with memory effects.                                                                                                                                             | 9  |

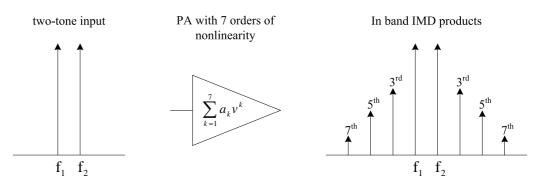

| 2.4  | In-band IMD products for an amplifier with up to seven orders of nonlinearity.                                                                                                          | 10 |

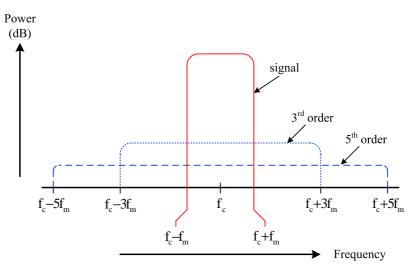

| 2.5  | Intermodulation spectrum of a typical digitally modulated signal [14, p. 185].                                                                                                          | 11 |

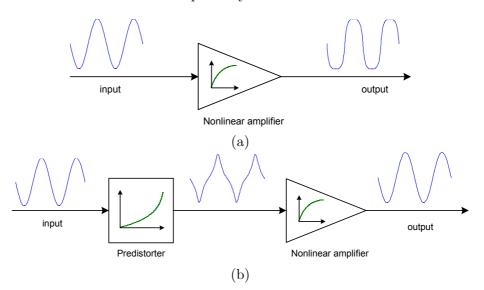

| 2.6  | Principle of predistortion. (a) Amplifier distortion. (b) Cascade of predistorter and amplifier                                                                                         | 12 |

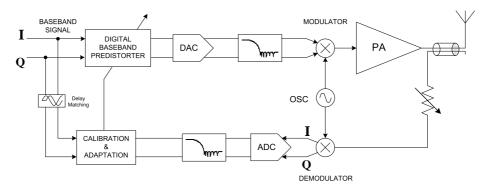

| 2.7  | Structure of an adaptive baseband predistorter                                                                                                                                          | 13 |

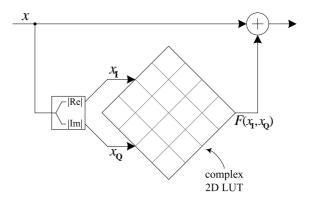

| 2.8  | Mapping predistorter.                                                                                                                                                                   | 14 |

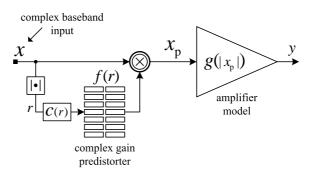

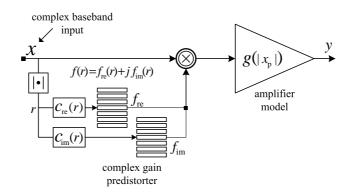

| 2.9  | complex-gain predistorter                                                                                                                                                               | 15 |

| 2.10 | Polar predistorter configuration. (a) Cascaded AM-AM and AM-PM corrections. (b) Parallel AM-AM and AM-PM corrections                                                                    | 16 |

| 2.11 | Indirect learning architecture                                                                                                                                                          | 17 |

| 2.12 | Hammerstein memory predistorter                                                                                                                                                         | 20 |

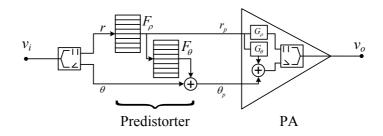

| 3.1  | Polar predistorter LUT arrangement (complex baseband model)                                                                                                                             | 23 |

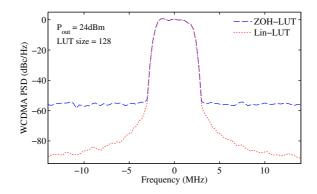

| 3.2  | PSD of a WCDMA signal using a LIN-LUT and a ZOH-LUT, with ${\cal N}=128$                                                                                                                | 26 |

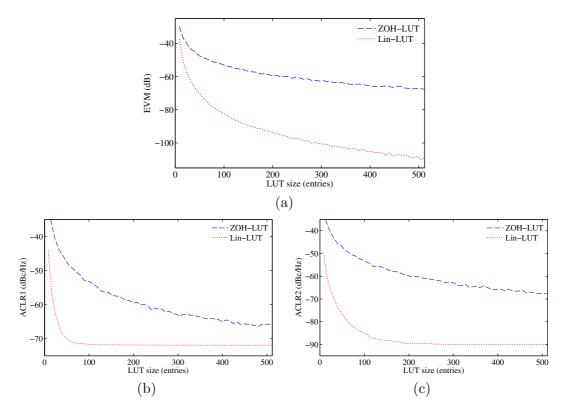

| 3.3  | WCDMA measurements for LIN-LUT and ZOH-LUT. (a) Error vector mag-<br>nitude. (b) Adjacent leakage ratio at 5 MHz offset (ACLR1). (c) Adjacent<br>leakage ratio at 10 MHz offset (ACLR2) | 26 |

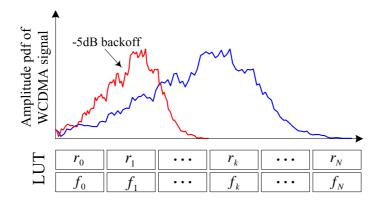

| 3.4  | Non uniform LUT spacing by companding                                                                                                                                                   | 28 |

| 3.5  | Class-E amplifier characteristics.                                                                                                                                                      | 30 |

| 3.6  | LUT distortion-to-signal power ratio vs. LUT size for ZOH-LUT                                                                                                                           | 31 |

| 3.7  | LUT distortion-to-signal-power ratio vs. LUT size for linearly-interpolated LUT                                                                                                         | 32 |

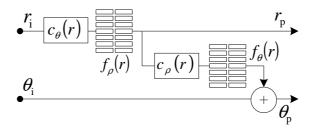

| 4.1  | Complex-gain LUT predistorter arrangement with unified compander. $\ . \ .$                                                                                                             | 35 |

| 4.2  | Linear interpolation of an arbitrary function. (a) Piece-wise linear interpola-<br>tion. (b) Comparison of the actual and approximated residual error functions.                        | 37 |

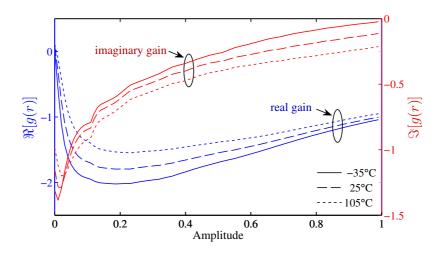

| 4.3  | Real and imaginary parts of a class-E amplifier nonlinearity expressed as a complex-gain, over different temperature settings                                                           | 39 |

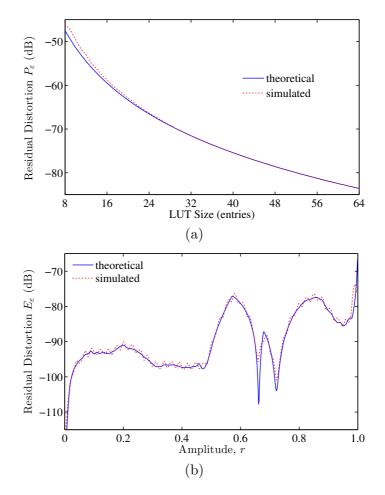

| 4.4  | Distortion characteristic of a class-E amplifier. (a) Residual distortion vs.<br>LUT size. (b) Distribution of residual distortion across normalized amplitude<br>for an LUT of size 64.       | 40 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

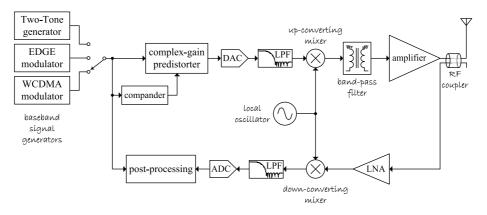

| 4.5  | Simulation setup for measuring the predistorter performance, with optimal LUT spacing                                                                                                          | 42 |

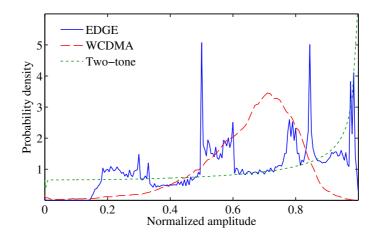

| 4.6  | Estimated envelope probability densities of test signals                                                                                                                                       | 42 |

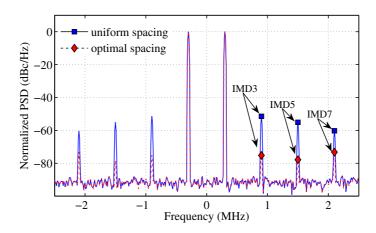

| 4.7  | Two-tone IMD products for uniform and optimal LUT spacing                                                                                                                                      | 43 |

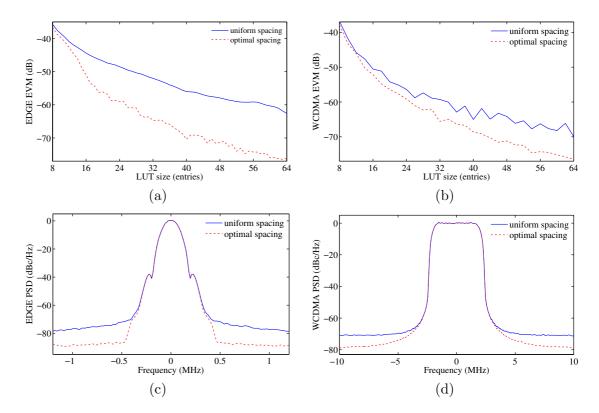

| 4.8  | EVM as a function of LUT size $N$ and PSD for $N = 40$ , using EDGE and WCDMA modulated signals with uniform and optimal LUT spacing. (a) EDGE EVM. (b) WCDMA EVM. (c) EDGE PSD. (d) WCDMA PSD | 44 |

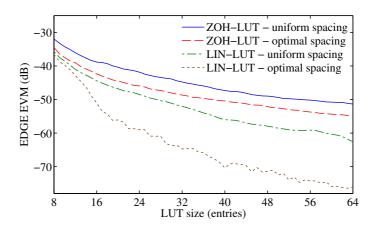

| 4.9  | Impact of optimal spacing on EDGE EVM using linearly-interpolated (Lin) and non-interpolated (ZOH) LUT predistorters.                                                                          | 46 |

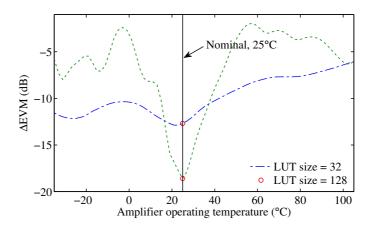

| 4.10 | Impact of temperature on $\operatorname{EVM}$ of fixed, nominally-derived optimal compander.                                                                                                   | 48 |

| 4.11 | Predistorter LUT implementation using a complex compander. $\ldots$ .                                                                                                                          | 49 |

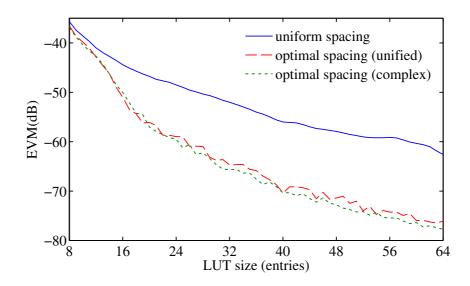

| 4.12 | Performance comparison of complex and unified companding schemes                                                                                                                               | 50 |

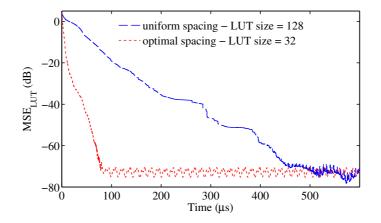

| 4.13 | Training convergence of uniformly and optimally spaced LUT predistorters.                                                                                                                      | 52 |

| 5.1  | Probability density function of the amplitude of a WCDMA backoff by 5dB.                                                                                                                       | 54 |

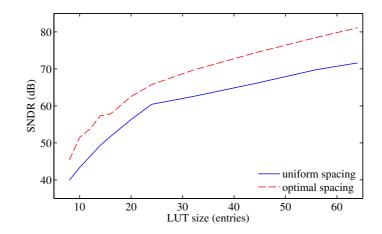

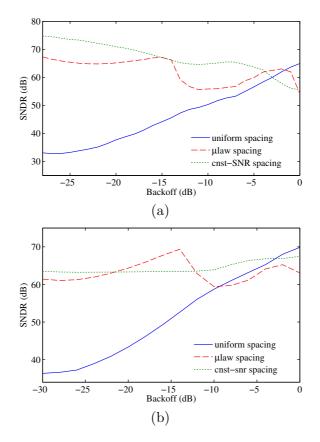

| 5.2  | Signal to noise and distortion ration (SNDR) vs. input power backoff for uniform, $\mu$ -law and constant-SNR spacings. (a) Polar predistorter. (b) Complex-<br>gain predistorter.             | 57 |

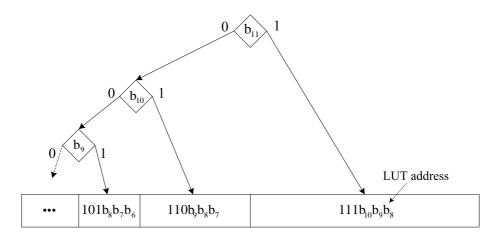

| 5.3  | Mapping of address bits in B2 spacing                                                                                                                                                          | 59 |

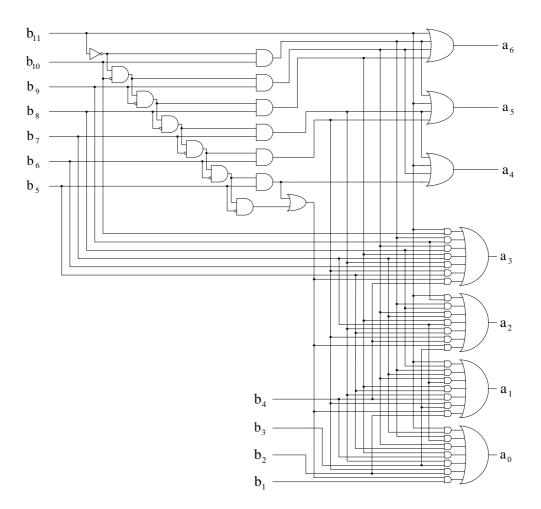

| 5.4  | B2 spacing address calculation circuit.                                                                                                                                                        | 61 |

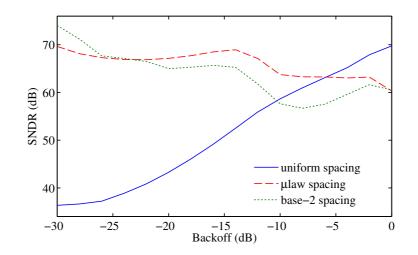

| 5.5  | Signal to noise and distortion ratio (SNDR) across different backoffs for uniform, $\mu$ -law, and B2 spacing.                                                                                 | 62 |

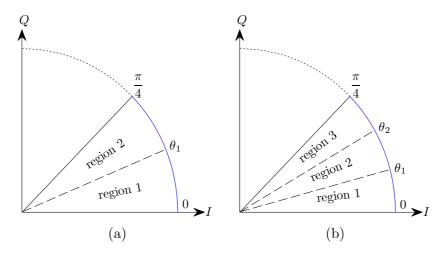

| 6.1  | Linear amplitude approximations. (a) Two angular intervals. (b) Three angular intervals                                                                                                        | 65 |

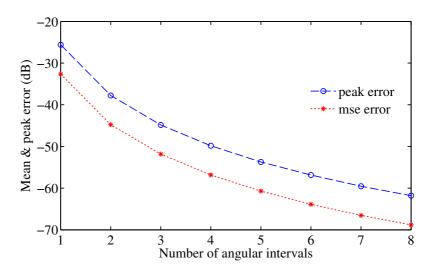

| 6.2  | Mean squared and peak errors as a function of the number of angular intervals.                                                                                                                 | 67 |

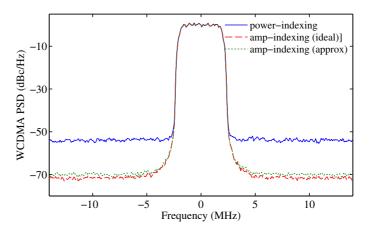

| 6.3  | Performance of amplitude approximation: WCDMA PSD                                                                                                                                              | 69 |

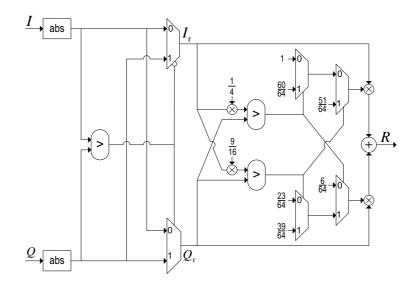

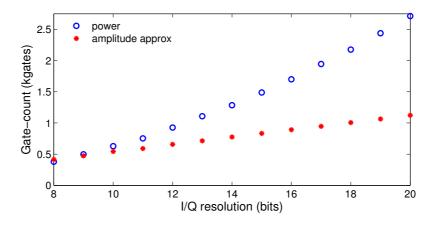

| 6.4  | Implementation of the amplitude approximation with three angular intervals.                                                                                                                    | 70 |

| 6.5  | Nand2-equivalent gate count for power index computation and amplitude approximation with three angular intervals.                                                                              | 71 |

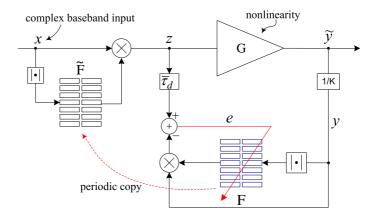

| 7.1  | Adaptation of complex-gain LUT predistorters using the indirect learning architecture.                                                                                                         | 73 |

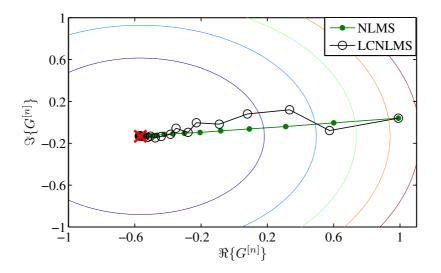

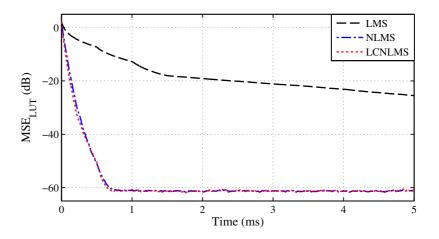

| 7.2  | Convergence paths of NLMS and LCNLMS                                                                                                                                                           | 75 |

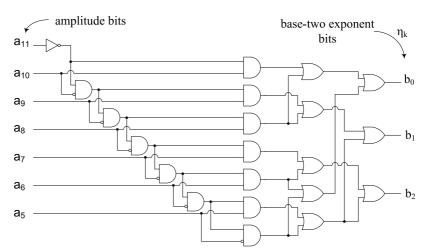

| 7.3  | Circuit that generates the base-two exponent $\eta_k$                                                                                                                                          | 76 |

| 7.4 | Convergence speed of LMS, NLMS, and LCNLMS                                                                                                                                                 | 77 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

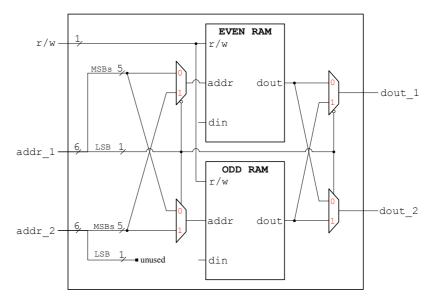

| 7.5 | Pseudo dual-port memory to implement a linearly-interpolated LUT                                                                                                                           | 78 |

| 7.6 | Direct learning architecture                                                                                                                                                               | 80 |

| 8.1 | Transmitter configuration with predistorter and IQM corrections                                                                                                                            | 83 |

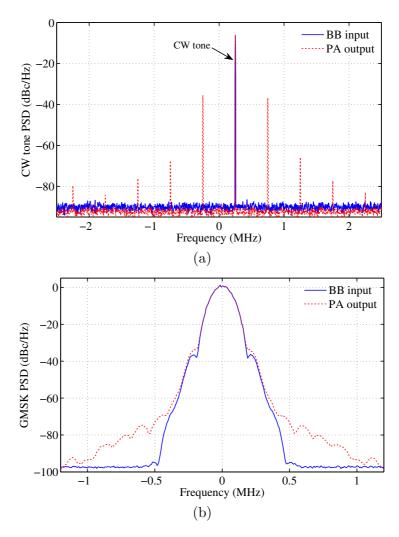

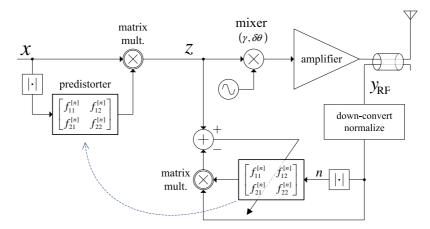

| 8.2 | PSD of PA output, when $\varepsilon = 5\%$ and $\delta\theta = 6^{\circ}$ . (a) CW tone input at 250 kHz offset. (b) GMSK input.                                                           | 85 |

| 8.3 | Mapping predistorter [39]                                                                                                                                                                  | 88 |

| 8.4 | Iterative IQM correction.                                                                                                                                                                  | 89 |

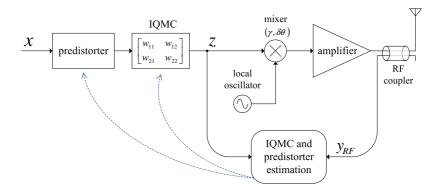

| 8.5 | Training of $2 \times 2$ transform predistorter                                                                                                                                            | 91 |

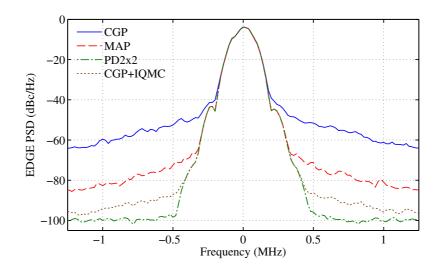

| 8.6 | EDGE PSD for a complex-gain (CGP), a mapping (MAP), 2×2 transform predistorters (PD2×2) and a combination complex-gain predistorter and the iteratively trained IQM correction (CGP+IQMC). | 92 |

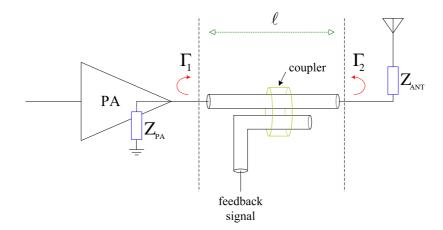

| 9.1 | Impedance mismatch and reflections at the antenna connection                                                                                                                               | 94 |

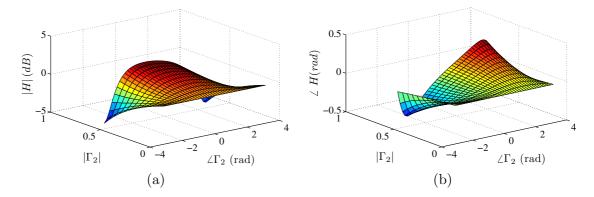

| 9.2 | Variations of the complex factor $H$ when the antenna matching conditions change. (a) Magnitude of $ H $ . (b) Angle of $ H $                                                              | 96 |

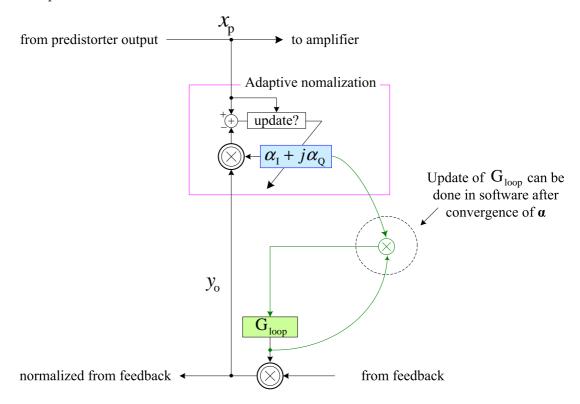

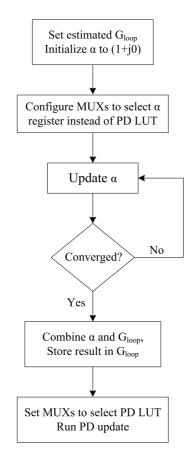

| 9.3 | Adaptive loop gain normalization.                                                                                                                                                          | 97 |

| 9.4 | Adaptive loop gain normalization and hardware sharing flow chart                                                                                                                           | 98 |

## SUMMARY

One of the major challenges in modern wireless transceiver design stems from the fundamental trade-off between the linearity and power efficiency of RF amplifiers. On one hand, the varying envelope of spectrally-efficient modulated signals such as wideband code division multiple access (WCDMA) and orthogonal frequency division multiplexing (OFDM) interacts with the amplifier nonlinearity, resulting in both in-band distortion and undesired out-of-band spectral regrowth. These distortions cause the violation of the strict standard requirements. On the other hand, improving the inherently low power efficiency of amplifiers generates significant savings in cooling and running costs at the base station infrastructure and enables an equally important increase in mobile handsets battery life.

Digital baseband predistortion is one of the most effective techniques used to reconcile the conflicting requirements of power efficiency and increased data throughput per unit bandwidth. The accuracy and flexibility of digital predistortion allows the use of a highly nonlinear amplifier to increase the overall power efficiency while meeting the strict performance requirements.

This dissertation studies the design of an efficient adaptive digital baseband predistorter for modern cellular handsets that combines low power consumption, low implementation complexity, and high performance. The proposed enhancements are optimized for hardware implementation.

We first present a thorough study of the optimal spacing of linearly-interpolated lookup tables supported by theoretical calculations as well as extensive simulation experiments. A constant-SNR compander that increases the LUT predistorter's supported input dynamic range is derived. A corresponding low-complexity approximation that lends itself to efficient hardware design is also implemented in VHDL and synthesized with the SYNOPSYS DESIGN COMPILER. This dissertation also proposes an LMS-based predistorter adaptation that is optimized for hardware implementation and compares the effectiveness of the direct and indirect learning architectures.

Analog RF imperfections such as quadrature imbalances and varying antenna impedance during the device operation severely reduce the effectiveness of adaptive predistorters. A novel predistorter design with quadrature imbalance correction capability is developed and a corresponding adaptation scheme is proposed. This robust predistorter configuration is designed by combining linearization and I/Q imbalance correction into a single function with the same computational complexity as the widespread complex-gain predistorter. An adaptive gain and phase normalization technique that reuses the predistorter update hardware is also proposed to mitigate the effects of varying antenna matching condition during predistorter adaptation.

## CHAPTER I

## INTRODUCTION

## 1.1 Motivation

In modern wireless communication systems, the power added efficiency (PAE) of the underlying power amplifier (PA) is of paramount importance. On the base station side, a slight improvement in power amplifier efficiency translates into considerable savings in cooling bills and running costs for the network operator. On the other side of the transmission link, increased battery life is the main driver for improving the efficiency of the power amplifier in the mobile station.

In the current state of the art amplifier design methodology, there is a fundamental tradeoff between power efficiency and device linearity. The power efficiency is improved at the cost of undesired envelope-dependent nonlinear distortions to the transmitted signal. For a long time, this has favored the design and extensive use of robust modulation techniques such as frequency shift keying (FSK) and Gaussian minimum shift keying (GMSK), which are immune to nonlinear amplifier distortions.

The strong demand in increased transmission rates has led to the development of modulation schemes with higher spectral efficiency such as orthogonal frequency division multiplexing (OFDM) and wideband code division multiple access (WCDMA). The resulting baseband signals have varying complex envelopes with high peak-to-average power ratios (PAPR), which further worsens the efficiency-linearity trade-off. The amplifier nonlinearity results in in-band distortion measured by the deterioration of the error vector magnitude (EVM) or the bit error rate (BER) and undesired out-of-band spectral regrowth [41, 52], which leads to the violation of the strict standard spectral requirements.

To reconcile the conflicting requirements of power efficiency and increased data throughput per unit bandwidth, it is necessary to linearize the radio frequency power amplifier. Numerous analog linearization techniques have been proposed and most of them were extensively used over the years. These analog techniques can generally be classified into one of three different categories:

- Indirect feedback

- Feedforward linearization

- Predistortion linearization

Two widely used indirect feedback techniques are the polar and Cartesian corrections. The complex input and output envelopes are compared to generate a correcting function, which is subsequently applied to the input signal envelope. These techniques typically achieve moderate performance improvement and are subject to bandwidth and stability issues.

The feedforward method is a powerful linearization technique that is immune to the bandwidth and stability issues of the above mentioned indirect feedback techniques. The feedforward correction is directly applied to the output RF signal. The high power consumption and overall cost of the feedforward technique constitute major limitations.

Simple analog predistortion techniques have been successfully used to provide moderate correction with little additional power consumption and at a very low cost. But their inability to track the drifts of amplifier characteristics and provide correction over a large dynamic range considerably limits their effectiveness.

The development of faster low-cost digital signal processors (DSP) has favored the emergence of adaptive digital predistortion linearization techniques. These techniques combine the computational power of DSP processors and advanced signal processing algorithms to provide accurate correction with the capability to precisely track both the short-term variations of the amplifier characteristics, which are caused by temperature fluctuations and the long-term drift effects resulting from the aging of analog devices.

Furthermore, the recent appearance of digital cellular transmitters with embedded processors has increased the appeal of digital baseband predistortion, which benefits from the low cost of implementation and high flexibility offered by digital circuit design. Consequently, digital predistortion is receiving increased attention and many digital baseband linearizers of varying complexity and performance have been proposed in the recent literature.

Even though the general principles of digital predistortion are the same across all applications, each design must be optimized with respect to the system under consideration. For example, a simple memoryless predistorter would be ineffective in the case of high power amplifiers (HPA) used in cellular base-stations (BS), which produce strong memory effects. A more complex predistorter structure with memory effect mitigation capability would be required. The Hammerstein and memory polynomial predistorters are two examples of such systems. On the other hand, memory effects are often negligible in low-power cellular handset amplifiers. For these resource-constrained devices, the focus is on minimizing the computational complexity of the predistorter hardware to produce low-cost handsets with increased battery life.

#### 1.2 Objectives

The objective of this dissertation is to develop an efficient digital baseband predistorter for modern cellular handsets that combines low power consumption, low implementation complexity, and high performance. The high peak-to-average power ratio and large signal bandwidth of modern modulation techniques (OFDM, WCDMA) represent significant challenges to the design of an effective digital predistorter for mobile devices with limited resources. Our research efforts focus on three main areas:

- Develop lookup table predistorter enhancement techniques

- Design an adaptive predistorter optimized for efficient hardware implementation

- Mitigate RF impairments affecting the effectiveness of an adaptive predistorter

Amplifiers used in cellular handsets are operated at a relatively low power (e.g. typical maximum of 1 W of power). At such a low output power and for the signal bandwidths considered, memory effects are negligible. Therefore, our research will focus on memoryless

predistorter design, even tough most of the proposed design optimizations can be extended to predistorters with memory correction capability. Additionally, as signal bandwidths continue to increase with 4G standards (e.g. up to 20 MHz for LTE), memory predistorters might be required even for low-power handsets in the near future.

## 1.3 Outline

This dissertation is organized as follows.

Chapter 2 reviews the principles of digital predistortion and presents different predistorter configurations. The characterization of nonlinear amplifier characteristics is illustrated with the AM-AM and AM-PM responses of different types of amplifiers. The main predistorter configurations proposed in the literature such as the Cartesian mapping predistorter [39], the complex-gain predistorter [8], and the polar predistorter [21] are presented. Predistorter training and adaptation techniques are also reviewed.

Chapter 3 and Chapter 4 present a study of optimal spacing of linearly-interpolated lookup tables (LUT) for the polar and complex-gain predistorters, respectively. Previous studies [11] have shown that optimal LUT spacing has little effect on non-interpolated LUTs. This chapter theoretically and experimentally demonstrates that the combination of linear interpolation with optimal spacing can greatly enhance the performance of LUT predistorters and decrease their cost of implementation by reducing the required memory space.

Chapter 5 presents a constant-SNR compander that increases the LUT predistorter's input dynamic range. A corresponding low-complexity approximation that lends itself to efficient hardware implementation is also presented. This approximation is implemented in VHDL and synthesized with the SYNOPSYS DESIGN COMPILER.

Chapter 6 analyzes the performance of power and amplitude LUT indexing when input signal backoff is supported. Traditionally, the use of power indexing has been favored in digital predistorter design because of the convenient computation of the instantaneous power  $(I^2 + Q^2)$  as opposed to using a suitably-accurate amplitude approximation. It is shown that the amplitude indexing results in better performance for highly nonlinear amplifiers. An efficient amplitude approximation is proposed and its hardware implementation is illustrated.

Chapter 7 proposes an LMS-based predistorter update that is optimized for hardware implementation. A comparison of the direct and indirect learning architectures is also presented.

Chapter 8 introduces a robust predistorter configuration that also mitigates quadrature gain and phase imbalances. The proposed predistorter has the same computational complexity as the complex-gain predistorter, but is more effective in the presence of analog impairments such as I/Q imbalances. A simple and efficient LMS-based adaptation is also proposed for this predistorter.

Chapter 9 studies the effects of varying impedance matching conditions on the predistorter adaptation during real-life device operation. An adaptive gain and phase normalization that reuses the predistorter update hardware is proposed to mitigate these effects.

Finally, Chapter 10 summarizes the contributions in this dissertation and suggests future research directions.

## CHAPTER II

#### BACKGROUND

In this chapter, an overview of the effects of amplifier nonlinearity is presented. The general concepts of predistortion linearization, the different prior-art predistorter configurations and their corresponding training algorithms are also reviewed.

#### 2.1 Power Amplifier Nonlinearity

Class-A power amplifiers represent the family of most linear and well-behaved power amplifiers. But they can only achieve a maximum theoretical power efficiency of 50%. The transfer characteristic of a class-A amplifier is linear at low amplitude levels and is compressed as the saturation level is approached. An important reference is the 1 dB compression point( $P_{1dB}$ ), which represents the output power level at which the PA gain is compressed by 1 dB. An amplitude modulated signal can be successfully transmitted through a suitably backed-off class-A power amplifier without suffering major distortions. The amount of backoff needed is proportional to the peak-to-average power ratio (PAPR) of the input signal. But in this configuration, the inherently low power efficiency of class-A amplifiers is further degraded by the input signal back-off. In the case of high spectral efficiency modulation techniques such as OFDM and WCDMA, which often have PAPRs of more than 10 dB, the resulting power efficiency may be well below 10%.

A sharp increase in efficiency can be achieved by lowering the quiescent bias level of the amplifier. This consequently results in a reduction of the conduction angle and the appearance of high-order harmonics, which can be filtered by a carefully designed matching network. The maximum efficiency of an amplifier is given as function of the conduction angle by [30]

$$\eta = \frac{2\gamma - \sin 2\gamma}{4(\sin \gamma - \gamma \cos \gamma)},\tag{2.1}$$

where  $\gamma$  is the conduction angle. This relationship between efficiency and conduction angle

is illustrated in Figure 2.1. A class-A amplifier has a conduction angle of  $\gamma = 2\pi$  and a maximum power efficiency of  $\eta = 50\%$ . Class-B operation corresponds to a conduction angle  $\gamma = \pi$  with a maximum efficiency of  $\eta = 78.5\%$ . When  $2\pi < \gamma < \pi$ , the amplifier is in class-AB operation. A conduction angle of  $\gamma < \pi$  corresponds to a class-C amplifier. The power efficiency increases dramatically when the conduction angle is biased towards class-C operation. But this huge gain in efficiency comes at the cost of severe degradation of the amplifier linearity, as illustrated by the decrease in signal to noise and distortion ratio (SNDR).

Figure 2.1: Power efficiency and SNDR vs. conduction angle.

Low-power amplifiers exhibit a *memoryless* type of nonlinearity. This type of nonlinearity causes a static, envelope-dependent amplitude distortion known as AM-AM conversion. A less intuitive but equally destructive type of distortion is the envelope-dependent phase distortion or AM-PM, which is observed in amplifiers with very short memory. The latter type of devices are also known as *quasi-memoryless* amplifiers. Let us consider an amplitude and phase modulated carrier:

$$S(t) = A(t)\cos[w_c t + \theta(t)], \qquad (2.2)$$

where A(t) represents the amplitude modulation and  $\theta(t)$  the phase modulation. The corresponding distorted output of a nonlinear amplifier is then given by

$$D(t) = f[A(t)] \cos\{w_c t + \theta(t) + g[A(t)]\}, \qquad (2.3)$$

where f(.) and g(.) respectively represent the AM-AM and AM-PM conversion functions. Figure 2.2 compares the AM-AM and AM-PM of typical class-A and class-C amplifiers.

**Figure 2.2:** AM-AM and AM-PM conversion functions. (a) Class-A amplifier. (b) Class-C amplifier.

The class-A amplifier has a maximum gain variation of 1.4 dB and a maximum phase variation of less than 2° across a 25 dB power range. The class-C characteristic is subject to significantly stronger distortions with a maximum gain variation of 9 dB and a maximum phase variation of 8° across the same power ranger. Unlike the relatively smooth compressed gain characteristic of the class-A amplifier, its class-C counterpart displays severe amplitude and phase distortions across all amplitude levels. Therefore, backing off a class-C amplifier will only reduce its effective power efficiency while doing little to reduce the effects of nonlinear distortions.

High-power amplifiers (HPA) such as those used in cellular base stations exhibit a nonlinear behavior that is coupled with strong memory effects [32, 48], especially in the case of wideband signals. This type of nonlinearity causes complex distortions that depend on the current as well as past amplitude levels. The memory effects can be observed on the input-output characteristics, as illustrated in Figure 2.3.

Figure 2.3: Amplifier nonlinearity with memory effects.

Two physical sources of PA memory effects are described in [48]. Electrical memory effects are due to the variations of complex envelope impedance across the signal's frequency band. The electro-thermal memory effects are caused by signal-dependent variations of the thermal impedance through the process of thermal power feedback (TPF). The transfer characteristics of amplifiers with memory effects can be accurately modeled with Volterra series [44]. The Wiener model [13], which is a special case of the Volterra system, consists of a linear time-invariant (LTI) system cascaded with a memoryless nonlinearity. Another special case of the Volterra series is the memory polynomial described in [31].

A widely adopted method of assessing an amplifier's linearity (or lack thereof) is the *two-tone* test. It consists of feeding the amplifier with a test signal that is constructed by summing two closely-spaced unmodulated RF carriers:

$$v_{in}(t) = A\cos(2\pi f_1 t) + A\cos(2\pi f_2 t).$$

(2.4)

This test signal is equivalent to an amplitude modulated carrier that is free of any distortion that would otherwise be caused by a non-ideal RF modulator. To illustrate this, equation (2.4) can be rewritten as follows:

$$v_{in}(t) = 2A\cos(2\pi f_m t) \times A\cos(2\pi f_c t), \qquad (2.5)$$

with  $f_m = \frac{f_2 - f_1}{2}$  and  $f_c = \frac{f_1 + f_2}{2}$ . Let us consider an amplifier with an amplitude conversion function (AM-AM) modeled by a polynomial function of arbitrary order N. The output is then given by

$$v_{out}(t) = a_1 v_{in}(t) + a_2 v_{in}(t)^2 + \dots + a_k v_{in}(t)^k + \dots + k_N v_{in}(t)^N.$$

(2.6)

When the two-tone signal is applied to the input of this amplifier, each order of nonlinearity k will generate additional frequency components or intermodulation products of the form

$$f_{im} = mf_1 + nf_2, (2.7)$$

where m and n are positive integers and m+n = k. The even orders of nonlinearity generate intermodulation (IMD) products that are located far away from the input frequencies. These IMD product terms are less important since they can be easily filtered. On the other hand, the odd-order terms generate IMD products that lie in the frequency band of interest. Figure 2.4 illustrates the in-band IMD products caused by the third, fifth, and seventh orders of nonlinearity. It is analytically shown in [14, p. 203] that the AM-PM effect results in the appearance of similar intermodulation products in the frequency band of interest.

Figure 2.4: In-band IMD products for an amplifier with up to seven orders of nonlinearity.

Over the years, the two-tone test has proven to be a powerful PA linearity assessment procedure that can be performed with a relatively simple experimental setup. However, modern modulated signals are far more complex than the simple two-tone test signals. It is therefore often necessary to perform a test with the modulated signal of interest. As a general rule of thumb, the *k*th order of PA nonlinearity causes the appearance of a parasitic component occupying *k* times the bandwidth of the input signal [14, p. 185]. The actual power level of this parasitic component depends on the strength of the nonlinear term in question. This is illustrated in Figure 2.5.

Figure 2.5: Intermodulation spectrum of a typical digitally modulated signal [14, p. 185].

It can be clearly seen in Figure 2.5 that the PA nonlinearity results in the appearance of parasitic components that span the adjacent channels, causing the effect known as spectral regrowth. It should also be noted that a portion of the unwanted distortion lies within the frequency band of the original signal, causing in-band distortions that degrade the BER performance. The amount of spectral spreading is measured by the adjacent channel power ratio (ACPR), which is defined as the ratio of the power contained in a given bandwidth at a defined frequency offset  $f_0$ , to the power in the channel bandwidth around the center frequency. The metric used for measuring the in-band distortion is the error vector magnitude (EVM). The EVM is defined as the ratio of RMS error vector power to the RMS power of the reference signal:

$$EVM_{RMS} = \sqrt{\frac{\sum_{k=1}^{N} |S_i[k] - S_m[k]|^2}{\sum_{k=1}^{N} |S_i[k]|^2}},$$

(2.8)

where  $S_i$  and  $S_m$  are respectively the ideally amplified and distorted complex signal samples. The EVM can be expressed in percentage (%) or decibels (dB):

$$EVM_{\%} = 100 \times EVM_{RMS}.$$

$$EVM_{dB} = 10 \log_{10} (EVM_{RMS}).$$

(2.9)

## 2.2 Principles of Digital Predistortion

The basic principle of predistortion is illustrated in Figure 2.6. It consists of inserting in the transmit path, prior to amplification, a nonlinear block with a transfer characteristic that is the inverse of the PA nonlinearity. The cascade of the two nonlinear elements will ideally result in a distortion-free and perfectly linear transmitter.

**Figure 2.6:** Principle of predistortion. (a) Amplifier distortion. (b) Cascade of predistorter and amplifier.

Predistortion can be applied at different points across the transmit chain. RF and IF signal predistorters are typically realized with relatively simple analog elements (such as diodes) that exhibit an expanding characteristic. The analog devices are calibrated to suppress the third order of amplitude nonlinearity, which is responsible for PA compression. These types of predistorters are capable of only moderate correction. But their simplicity, very low cost, and low power consumption make them particularly appealing for wireless handsets. Other major disadvantages of analog RF/IF predistorters include their lack of flexibility and their inability to precisely track the variations of nonlinear characteristics.

Another type of predistortion linearizer known as the data predistorter applies the correction to the complex symbols [28,43]. The data predistorter has a very low implementation complexity since only a few complex corrections values are needed. On the downside, this predistorter is modulation dependent and requires placing the Nyquist pulse-shaping filter at the output of the amplifier. This unattractive arrangement is difficult to realize.

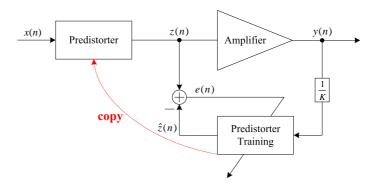

Predistortion can also be applied to the digital complex baseband signal after Nyquist filtering and prior to up-conversion. These digital baseband predistorters have been gaining increased popularity because of the flexibility and high accuracy provided by digital computations and their relatively low power consumption. Additionally, digital baseband predistorters further leverage the DSP processors that are embedded in modern wireless transmitters. They are also very well suited to adaptive algorithms, therefore allowing precise tracking of nonlinear characteristic variations resulting from temperature fluctuations and aging of analog devices. The basic structure of an adaptive baseband predistorter is illustrated in Figure 2.7.

Figure 2.7: Structure of an adaptive baseband predistorter.

The adaptation process in general requires an auxiliary receiver for the feedback path. This additional hardware component accounts for most of the cost of the adaptive predistorter. Several digital predistorters have been reported in the literature. The Cartesian mapping predistorter, the polar predistorter, and the complex-gain predistorter are three of the most popular configurations.

#### 2.2.1 Cartesian Mapping Predistorter

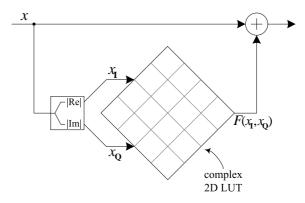

The Cartesian mapping predistorter was one of the early successful implementations of a digital baseband predistorter and was proposed by Nagata [39]. The structure of the mapping predistorter is illustrated in Figure 2.8.

Figure 2.8: Mapping predistorter.

This predistorter is implemented as a bi-dimensional lookup table (LUT) that is addressed by the quadrature input components (I/Q). It provides an incremental complex correction to the I/Q input, thereby mapping the complex plan to itself. This linearization method has minimal computational complexity but is plagued by high memory requirements. It requires an LUT size of 2000 entries for an input signal resolution of 10 bits. This requirement increases to 8000 entries with 11 bits of input resolution [8]. A direct consequence of the large LUT size is the very slow convergence (10 s for a sampling rate of 16 kHz).

#### 2.2.2 Complex-Gain Predistorter

The complex-gain predistorter was proposed by Cavers in [8]. The amplifier is modeled as a complex gain that is a function of the input power or amplitude. The complex envelopes of the amplifier's input  $v_p$  and its corresponding complex output  $v_o$  are then related by

$$v_o = v_p G\left(|v_p|^2\right).$$

(2.10)

The predistorter is similarly modeled and realized as a power-dependent complex gain. The predistorter's output is related to the input by

$$v_p = v_p F\left(|v_i|^2\right). \tag{2.11}$$

The transmitter is perfectly linear if the following condition is met:

$$F\left(|v_i|^2\right)G\left(\left|v_pF\left(|v_i|^2\right)\right|^2\right) = K,$$

(2.12)

where K is a constant representing the desired linear gain. An illustration of the complexgain predistorter is shown in Figure 2.9.

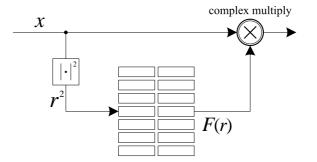

Figure 2.9: complex-gain predistorter.

In [8], the complex-gain predistorter is implemented as a lookup table that is indexed by the input power. This results in a non-uniformly spaced LUT in the amplitude domain, where entries are mostly concentrated near the saturation region. The predistorter F can also be implemented as a complex polynomial function [42]. The complex-gain predistorter's memory requirements and convergence time are four orders of magnitude lower than that of the Cartesian mapping predistorter. The cost of this improvement is the additional computations of the input power  $|v_i|^2$  and the complex multiplication.

#### 2.2.3 Polar Predistorter

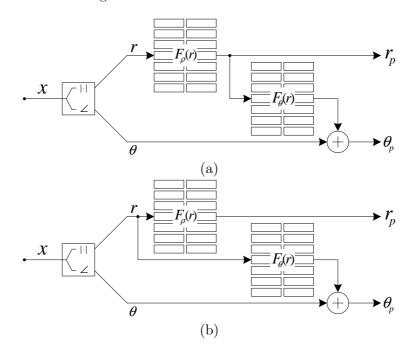

The polar predistorter proposed in [21] consists of an amplitude correction function  $F_{\rho}$  and a phase correction  $F_{\theta}$  that respectively compensate the power amplifier's AM-AM distortion  $G_{\rho}$  and AM-PM distortion  $G_{\theta}$ . The polar predistorter exploits the fact that the PA's distortion is only a function of the input amplitude (or power). Consequently,  $F_{\rho}$  and  $F_{\theta}$  are one-dimensional functions of the input amplitude. Two equivalent versions of the polar predistorter are shown in Figure 2.10.

**Figure 2.10:** Polar predistorter configuration. (a) Cascaded AM-AM and AM-PM corrections. (b) Parallel AM-AM and AM-PM corrections.

In both cases, the AM-AM distortion is perfectly compensated if the following relation holds:

$$G_{\rho}\left[F_{\rho}(r)\right] = Kr,\tag{2.13}$$

where r is the input amplitude and K is the desired linear gain. For the cascaded polar predistorter in Figure 2.10(a), the phase correction is given by solving

$$F_{\theta}(r) + G_{\theta}(r) = 0. \tag{2.14}$$

In the parallel configuration case of Figure 2.10(b), the phase correction is given by:

$$F_{\theta}(r) + G_{\theta}(F_{\rho}(r)) = 0.$$

(2.15)

The cascaded version of the polar predistorter is simpler and has a faster phase convergence. The parallel version has lower latency since the amplitude and phase corrections are done in parallel. The polar predistorter has low memory requirements and fast convergence speed, which are comparable to the complex-gain predistorter. The polar predistorter can be easily calculated from the amplifier's AM-AM and AM-PM characteristics. Unlike the complex-gain predistorter, the polar predistorter does not require a complex multiplier, but a rectangular to polar conversion is required if used in a Cartesian transmitter. This makes it more suitable for polar transmitter configurations since the baseband modulation signal is already available in polar form.

## 2.3 Calibration and Adaptation

Memoryless predistorters can be implemented as a set of lookup tables that model the inverse of the PA distortion. Alternatively, a functional approximation of the inverse distortion can be used as well. The most popular form of functional approximation is the polynomial predistorter, which has been extensively documented in the literature [4,5,25,26,45]. Its main advantage is the relatively low number of parameters that is needed to model the predistorter. A predistorter can be constructed by first identifying the amplifier's nonlinear transfer characteristic and then calculating its inverse. However, the inversion process of the nonlinear function is often a non-trivial task. The indirect learning architecture illustrated in Figure 2.11 avoids the inversion step by directly computing the inverse nonlinear function. The calibration process as well as the adaptation of the predistorter depend on the type of predistorter that is considered.

Figure 2.11: Indirect learning architecture.

#### 2.3.1 Polynomial Predistorter

Polynomial functions or power series models are widely used in predistorter design. The polynomial approximation is attractive for its simplicity and the relatively reduced number of parameters. This model has been used to provide a good predistorter model for amplifiers presenting relatively weak nonlinearity such as class-A and class-AB amplifiers. The simplicity of such a model lies mainly in the fact that the output is a linear function of the parameters (or coefficients) to be estimated. Once the output signal corresponding to a chosen training signal is recovered, the predistorter design boils down to solving a linear least-squares system.

Let  $z_k$  denote the amplifier's input envelope samples and  $v_k$  the corresponding output values normalized by the gain K. The vector of polynomial predistorter coefficients  $\mathbf{p}$  is obtained by solving the following equation:

$$\mathbf{z} = V\mathbf{p},\tag{2.16}$$

where  $\mathbf{z}$  and V are respectively given by

$$\mathbf{z} = \begin{bmatrix} z_1 \\ z_2 \\ \vdots \\ z_L \end{bmatrix} \quad \text{and} \quad V = \begin{bmatrix} v_1 & v_1^2 & \cdots & v_1^n \\ v_2 & v_2^2 & \cdots & v_2^n \\ \vdots & \vdots & \ddots & \vdots \\ v_L & v_L^2 & \cdots & v_L^n \end{bmatrix}.$$

To avoid numerical instabilities during the inversion of the matrix  $\mathbf{V}$ , the use of orthogonal polynomial basis is suggested in [42]. The high computational complexity associated with the least-squares identification method makes this solution quite unattractive for resource-constrained mobile devices. A significant amount of memory space is required to store the input and output samples  $z_k$  and  $v_k$ . Furthermore, this operation must be repeated periodically to track the nonlinear characteristic's drifts. A lower-complexity predistorter identification and adaptation method based on the adaptive least-mean-squares (LMS) algorithm is proposed in [4] and [45]. The algorithm in [4] was developed for the polar predistorter configuration discussed in Section 2.2.3. The amplitude and phase predistorters are modeled as polynomial functions of the input amplitude r.

$$F_{\rho}(r) = \alpha_1 r + \alpha_2 r^2 + \dots + \alpha_L r^L = \mathbf{a}^{\mathrm{T}} \mathbf{r}_{\rho}$$

$$F_{\theta}(r) = \beta_0 + \beta_1 r + \beta_2 r^2 + \dots + \beta_M r^M = \mathbf{b}^{\mathrm{T}} \mathbf{r}_{\theta}, \qquad (2.17)$$

with  $\mathbf{r}_{\rho} = [r, r^2, \cdots, r^L]^{\mathrm{T}}$ ,  $\mathbf{r}_{\theta} = [1, r, \cdots, r^M]^{\mathrm{T}}$ ,  $\mathbf{a} = [\alpha_1, \cdots, \alpha_L]^{\mathrm{T}}$ , and  $\mathbf{b} = [\beta_1, \cdots, \beta_M]^{\mathrm{T}}$ . The steepest descent algorithm is used to minimize the mean-squared amplitude and phase errors. The resulting LMS update algorithm is described by the following equations:

$$\mathbf{a}_{k+1} = \mathbf{a}_k + \mu_\rho \mathbf{r}_\rho^{[k]} e_\rho^{[k]} \tag{2.18}$$

$$\mathbf{b}_{k+1} = \mathbf{b}_k + \mu_{\theta} \mathbf{r}_{\theta}^{[k]} e_{\theta}^{[k]}, \qquad (2.19)$$

where  $e_{\rho}^{[k]}$  is the amplitude error between the *k*th input sample and the normalized output of the PA and  $e_{\theta}^{[k]}$  is the corresponding phase error.  $\mu_{\rho}$  and  $\mu_{\theta}$  are positive update coefficients that are carefully chosen to provide a suitable trade-off between the convergence speed and the steady-state error. This algorithm can be used for both the calibration and the adaptation of the predistorter. Its low complexity and minimal memory requirements make it particularly attractive. Even though the convergence speed is relatively slow, precise tracking of temperature and aging drifts is still achievable.

#### 2.3.2 Lookup Table Predistorter

Building a LUT predistorter from a set of stored input and output complex envelope samples is a trivial process. But just as for the least-squares polynomial identification, high storage requirements and periodic updates contribute to the high cost and complexity of the system identification process. Alternative LUT adaptation techniques with low complexity and low memory requirements have been proposed in the literature. The linear update algorithm [11, 21,39] consists of incremental small updates to LUT entries as they are accessed. When the *n*th entry of the LUT *F* is accessed and an error  $e_n[k]$  is produced at the output of the PA, the updated LUT is computed as follows:

$$F_n[k+1] = F_n[k] + \mu \times e_n[k], \qquad (2.20)$$

where  $\mu$  is a positive step size that must be smaller than two to guarantee the stability of the algorithm. A value of  $\mu$  less than one is required for better steady-state behavior, specially in the case of noisy output measurements. The linear update algorithm has a very low complexity but is plagued by slow convergence speed, which also depends on the signal envelope's statistics.

The secant update algorithm was proposed in [8] to provide faster convergence. With the secant method, the *n*th LUT entry is updated as follows:

$$F_n[k+1] = \frac{F_n[k-1]e_n[k] - F_n[k]e_n[k-1]}{e_n[k] - e_n[k-1]}$$

(2.21)

The secant update is reported as being twice as fast as the linear update algorithm. The cost of this improvement is the additional multiplications and the division required during the update step and to a lesser extent, the memory space needed to store the previous entries  $F_n[k-1]$  and the error samples  $e_n[k-1]$ .

## 2.3.3 Predistorter with Memory

Memoryless predistortion of a high power amplifier (HPA) that exhibits strong memory yields very marginal performance improvements [33]. The predistorter itself must be a system with memory in order to successfully mitigate the memory effects. A memory predistorter can be generally represented by a discrete Volterra system [19,34]:

$$y[n] = \sum_{q=0}^{Q} h_q^{(1)} x[n-q] + \sum_{q=0}^{Q} \sum_{q=0}^{Q} h_{q1,q2}^{(2)} x[n-q_1] x[n-q_2]$$

+

$$\sum_{q=0}^{Q} \sum_{q=0}^{Q} \sum_{q=0}^{Q} h_{q1,q2,q3}^{(3)} x[n-q_1] x[n-q_2] x[n-q_3] \cdots .$$

(2.22)

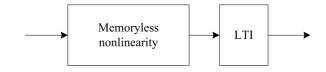

The Volterra system is not well suited to practical implementation because of the large number of parameters and the non-trivial estimation process involved. A special case of the Volterra system with a significantly lower number of parameters is the Hammerstein predistorter described in Figure 2.12.

Figure 2.12: Hammerstein memory predistorter

The Hammerstein predistorter is merely the cascade of a memoryless nonlinearity and a linear time invariant (LTI) system that emulates the desired memory effect. The Hammerstein system can be identified by using an iterative process such as Newton's or Narenda-Gallman (NG) algorithms [18]. The potential convergence issues of the latter iterative algorithms can be avoided by using the two-stage LS/SVD algorithm presented in [16]. Another special case of the Volterra system is the memory polynomial [17] described by the following equation:

$$z[n] = \sum_{k=1}^{K} \sum_{q=0}^{Q} h_{k,q} x[n-q] |x[n-q]|^{k-1}.$$

(2.23)

The parameters of the memory polynomial system can be identified by using the leastsquares approximation. Even though the memory polynomial predistorter requires a larger number of parameters than the Hammerstein system, it is more robust and the parameter identification process is much simpler.

## CHAPTER III

## SPACING OF A POLAR LUT PREDISTORTER

As previously discussed in Chapter 2, predistorters can implemented as lookup tables (LUT). Functional approximations such as fitted polynomials or power series approximations can be used as well. LUT predistorters have minimal computational complexity and can implement arbitrary nonlinear mappings. But they require significantly more memory space to store the model parameters than a polynomial approximation. A direct consequence of the larger number of parameters is a relatively slow convergence speed of iterative training algorithms. On the other hand, evaluating a polynomial function is more computationally complex than a simple memory lookup. Furthermore, compensating higher orders of nonlinearity requires a high-order polynomial predistorter evaluated at a sampling frequency a few orders of magnitude higher than the bandwidth of the input baseband signal. For modern high spectral efficiency modulation techniques such as WCDMA and OFDM, a predistorter bandwidth of several tens of MHz might be required. In this case, dedicated high-speed hardware is needed to implement a polynomial predistorter, therefore reducing its appeal in low-cost cellular handset applications. This chapter will focus on LUT enhancement techniques that combine the inherent low complexity of table lookup with reduced memory requirements achieved by using interpolation and efficient spacing of table entries.

## 3.1 Analysis of Linearly-Interpolated LUT

The use of linearly interpolated LUT predistorters has been reported in the literature [21] as an efficient way to reduce LUT approximation errors. A low-complexity and practical implementation of LUT interpolation is also discussed in [47]. In the present study, the problem is approached with a mathematical justification. The polar predistorter configuration [21] is considered here. The complex-gain configuration will be addressed in Chapter 4. A polar predistorter is illustrated in Figure 3.1.

Figure 3.1: Polar predistorter LUT arrangement (complex baseband model)

This setup uses the cascaded LUT arrangement discussed in Section 2.2.3. The amplifier's nonlinear AM-AM and AM-PM distortions are respectively designated by the amplitude-dependent functions  $g_{\rho}(r)$  and  $g_{\theta}(r)$ . To simplify the mathematical expressions, it is assumed that the gain of the amplifier is normalized to one (i.e., K = 1). The polar predistorter consists of two LUTs approximating the inverse function of the amplifier's amplitude distortion  $f_{\rho}(r) = g_{\rho}^{-1}(r)$  and the phase compensation function  $f_{\theta}(r) = -g_{\theta}(r)$ . The LUT approximation error of  $f_{\rho}(r)$  and  $f_{\theta}(r)$  respectively result in independently computable amplitude and phase errors at the output of the PA. The derivation for the two types of errors is similar. Therefore, the focus here will be on the amplitude table. Let us consider the kth bin of the amplitude LUT, which is delimited by the amplitude entries  $r_k$  and  $r_{k+1}$ and let  $d_k = r_{k+1} - r_k$  be the width of the kth interval. The amplitude predistorter  $f_{\rho}(r)$ will be precisely determined at the amplitudes  $r_k$  and  $r_{k+1}$ , where the approximation error is equal to zero. For an input amplitude  $r_i = r_k + \varepsilon_r$ , with  $0 < \varepsilon_r \leq d_k$ , the output of the LUT predistorter is  $f_{\rho}(r_i) + \varepsilon_{f_{\rho}}$ . Assuming that the predistorter  $f_{\rho}(r)$  is at least twice continuously differentiable and  $f_{\rho}''(r)$  varies little within the bin, it is shown in Appendix A that the linear interpolation results in an approximation error given by

$$\varepsilon_{f\rho} = f_{\rho}''(r) \, \frac{\varepsilon_r \, (\varepsilon_r - d_k)}{2}, \tag{3.1}$$

with  $f_{\rho}^{\prime\prime}$  being the second-order derivative of  $f_{\rho}$ . The amplitude at the output of the amplifier,

with normalized gain K = 1 is

$$r_{o} = g_{\rho} [f_{\rho}(r_{i}) + \varepsilon_{f_{\rho}}]$$

$$\approx g_{\rho} [f_{\rho}(r_{i})] + \varepsilon_{f_{\rho}} g_{\rho}' [f_{\rho}(r_{i})]$$

$$\approx r_{i} + \frac{f_{\rho}''(r_{i})}{f_{\rho}'(r_{i})} \frac{\varepsilon_{r} (\varepsilon_{r} - d_{k})}{2},$$

(3.2)

where (3.2) uses the relation between  $f_{\rho}$  and  $g_{\rho}$ , i.e.,  $f_{\rho} = g_{\rho}^{-1} \Rightarrow g'_{\rho} = 1/f'_{\rho}$ . It is also assumed that  $f'_{\rho}$  does not change appreciably within the bin (i.e, the number of LUT entries is large enough). The amplitude error measured at the amplifier's output can therefore be expressed as follows:

$$e_{\rho} = r_o - r_i$$

=  $\frac{f_{\rho}''(r_i)}{f_{\rho}'(r_i)} \frac{\varepsilon_r \left(\varepsilon_r - d_k\right)}{2}$  (3.3)

Calculating the phase error at the amplifier's output is a more straightforward process since the phase LUT approximation error is simply propagated to the output phase. Therefore, the output phase error is simply expressed as follows:

$$e_{\theta} = g_{\rho}^{\prime\prime}(r_i) \,\frac{\varepsilon_r \,(\varepsilon_r - d_k)}{2} \tag{3.4}$$

Assuming that the amplitude and phase errors are small enough, the complex baseband equivalent output of the amplifier can be written as

$$v_o = (r_i + e_r) e^{j(\theta_i + e_\theta)}$$

$$\approx (r_i + e_r) \left[ e^{j\theta_i} + e_\theta e^{j\left(\theta_i + \frac{\pi}{2}\right)} \right]$$

$$\approx v_i + e_r e^{j\theta_i} + e_\theta r_i e^{j\left(\theta_i + \frac{\pi}{2}\right)}.$$

(3.5)

The complex error at the output of the PA is thus given by

$$e_o = v_o - v_i$$

$$\approx e_r e^{j\theta_i} + e_\theta r_i e^{j\left(\theta_i + \frac{\pi}{2}\right)}.$$

(3.6)

The residual error at the output of the PA consists of two terms resulting from the approximation errors in the amplitude and phase LUTs. These two error terms can be considered independent of each other to simplify the remaining calculations. The total noise contribution of the kth bin to the output SNR can be computed using the usual quantizer assumption [24] that  $\varepsilon_r$  is a random variable uniformly distributed in  $[0, d_k]$ . The mean-squared error (MSE) contribution of the kth bin of the amplitude table is

$$E\left[|e_{\rho}|^{2}\right] = \frac{f_{\rho}''(r_{k})^{2}}{4 d_{k} f_{\rho}'(r_{k})^{2}} \int_{0}^{d_{k}} \varepsilon^{2} (\varepsilon - d_{k})^{2} d\varepsilon$$

$$= \frac{f_{\rho}''(r_{k})^{2}}{120 f_{\rho}'(r_{k})^{2}} d_{k}^{4}.$$

(3.7)

Similarly, the contribution of the kth of the phase LUT to the total residual error is

$$E\left[|e_{\theta}|^{2}\right] \approx \frac{f_{\theta}''(r_{k})^{2}}{120}r_{k}^{2}d_{k}^{4}.$$

(3.8)

For an arbitrary LUT spacing achieved using a compander [24] c(r), the bin width is related to the compander by

$$d_k \approx \frac{1}{Nc'(r_k)},\tag{3.9}$$

where N is the LUT size and V is the maximum amplitude addressable by the LUT. For the special case of uniform spacing c(r) = r and  $d_k = 1/N$  is constant. Assuming that the number of LUT bins is large enough, the total residual distortion power at the PA output can be approximated as follows:

$$P_{\rm dis} = P_{\rho} + P_{\theta} \tag{3.10}$$

with

$$P_{\rho} = \frac{1}{120 N^4} \int_0^1 \frac{f_{\rho}''(r)^2}{c'(r)^4 f_{\rho}'(r)^2} p(r) dr$$

(3.11)

$$P_{\theta} = \frac{1}{120 N^4} \int_0^{\tilde{A}} \frac{f_{\theta}''(r)^2}{c'(r)^4} r^2 \tilde{p}(r) dr$$

(3.12)

where p(r) is the probability density function (pdf) of the input amplitude and  $\tilde{p}(r)$  is the pdf of the predistorted amplitude of the input signal. Equations (3.11) and (3.12) show that the mean-squared amplitude and phase errors are inversely proportional to  $N^4$ , which is a much faster rate of decrease than for the ZOH LUT [11], which results in a MSE that is inversely proportional to  $N^2$ . The predistorted signal's SNR increases by 12 dB if the LUT size is doubled as opposed to just 6 dB for the ZOH LUT.

Figure 3.2: PSD of a WCDMA signal using a LIN-LUT and a ZOH-LUT, with N = 128

A comparison of the two approaches using a WCDMA input is summarized in Figure 3.2 and Figure 3.3. Figure 3.3(a) shows that linear interpolation improves the WCDMA error vector magnitude (EVM) by 25 dB. The adjacent channel leakage ratio at 5 MHz offset (ACLR1) and 10 MHz offset (ACLR2) are respectively improved by 0.5 dB and 17 dB.

**Figure 3.3:** WCDMA measurements for LIN-LUT and ZOH-LUT. (a) Error vector magnitude. (b) Adjacent leakage ratio at 5 MHz offset (ACLR1). (c) Adjacent leakage ratio at 10 MHz offset (ACLR2).

# 3.2 Analysis of LUT Predistorter Spacing

The early implementations of LUT predistorters were mainly based on uniform spacing in power to minimize the complexity of the LUT address calculation. To reduce LUT approximation errors, non-uniform spacing has been studied for nearest-neighbor or zero-order hold LUT (ZOH-LUT) predistorters. Several spacing schemes for the complex-gain predistorter configuration have been proposed in the literature. In [11], a closed-form optimal spacing expression that depends on the signal's probability distribution as well as the amplifier's characteristics has been derived. This result is modified in [6] to remove the dependency with respect to the input signal's statistics while maintaining a considerable performance advantage over uniform spacing.

Other LUT techniques have been presented in [29, 35, 36, 38]. These results mainly address the complex-gain predistorter configuration. In this work, the optimal spacing expression will be derived for the polar LUT predistorter configuration (Figure 2.10), in which the amplitude and phase predistorters reside in separate LUTs. It was shown in Section 3.1 that linear interpolation tremendously improves the performance of LUT predistortion with relatively little added complexity. It is therefore important to consider optimal spacing in the context of linearly-interpolated LUTs (LIN-LUT) as well.

#### 3.2.1 Optimal Spacing of Nearest Neighbor LUT Predistorter

The problem of optimal LUT spacing is quite similar to the design of an optimal quantizer. In the case of the polar LUT predistorter in Figure 3.1, both amplitude and phase predistorter LUTs must be optimally spaced to minimize the total transmitted residual distortion power resulting from LUT approximations. Optimal spacing can be achieved by applying a suitable compander c(r) to the amplitude signal prior to addressing the LUT. This is illustrated in Figure 3.4. The objective of this study is to find a set of companders  $c_{\rho}$  and  $c_{\theta}$  that minimize the total residual nonlinear distortion power at the output of the PA. To simplify the derived mathematical expressions, it is assumed that the input signal's amplitude and the amplifier's gain are normalized to unity. The generalization of the presented results is a matter of trivial extension.

Figure 3.4: Non uniform LUT spacing by companding

The amplitude and phase LUTs are assumed to be of the same size N. Let us first consider the amplitude LUT. The amplitude signal  $r_i$  is quantized to the nearest LUT entry  $r_k$ , therefore causing a quantization error  $\varepsilon_r = r_k - r_i$ . Assuming that  $r_k$  is located in the middle of kth LUT interval with width  $d_k$ , then  $\varepsilon_k$  is bounded by  $-d_k/2 < \varepsilon_r < d_k/2$ . The quantized predistorted amplitude is

$$r_{\rm p} = f_{\rho}(r_k)$$

=  $f_{\rho}(r_i + \varepsilon_r).$  (3.13)

Assuming a gain of unity and applying (2.13) with K = 1, the output amplitude is given by

$$r_o = g_\rho [f_\rho(r_i + \varepsilon_r)] = r_i + \varepsilon_r. \tag{3.14}$$

Similarly, the output phase is given by

$$\theta_o = \theta_i + f_\theta(r_p + \tilde{\varepsilon}_r) + g_\theta(r_p). \tag{3.15}$$

Using first-order approximation,

$$f_{\theta}(r_p + \tilde{\varepsilon}_r) \approx f_{\theta}(r_p) + \tilde{\varepsilon}_r f'_{\theta}(r_p).$$

The output phase can be simplified to

$$\theta_o \approx \theta_i + f_\theta(r_p) + \tilde{\varepsilon}_r f_\theta'(r_p) + g_\theta(r_p)$$

$$\approx \theta_i + \tilde{\varepsilon}_r f_\theta'(r_p). \tag{3.16}$$

Assuming that the amplitude and phase errors are small enough, the output of the amplifier

can be written as follows:

$$v_{o} = (r_{i} + \varepsilon_{r}) e^{j\left(\theta_{i} + \tilde{\varepsilon}_{r} f_{\theta}'(r_{p})\right)}$$

$$\approx (r_{i} + \varepsilon_{r}) \left[ e^{j\theta_{i}} + \tilde{\varepsilon}_{r} f_{\theta}'(r_{p}) e^{j\left(\theta_{i} + \frac{\pi}{2}\right)} \right]$$

$$\approx v_{i} + \varepsilon_{r} e^{j\theta_{i}} + \tilde{\varepsilon}_{r} r_{i} f_{\theta}'(r_{p}) e^{j\left(\theta_{i} + \frac{\pi}{2}\right)}, \qquad (3.17)$$

with

$$v_i = r_i e^{j\theta_i}$$

and  $v_o = r_o e^{j\theta_o}$ .

The distortion at the output of the PA is thus given by

$$e_o \approx \varepsilon_r e^{j\theta_i} + \tilde{\varepsilon}_r r_i f_{\theta}'(r_p) e^{j\left(\theta_i + \frac{\pi}{2}\right)}.$$

(3.18)

The result in equation (3.18) shows that the residual distortion error at the output of the PA consists of two terms resulting from the approximation errors in the amplitude and phase LUTs respectively. These two error terms can be reasonably considered independent of each other. For an LUT size N that is large enough, the errors  $\varepsilon_r$  and  $\tilde{\varepsilon}_r$  can be approximated by uniformly distributed zero-mean random variables over their respective interval  $\left[-\frac{d_k}{2}, \frac{d_k}{2}\right]$ . Using the approach described in [11], the total residual distortion power and the optimal companders can be estimated. The residual distortion power is given by

$$P_{\rm dis} = E\left[|e_o|^2\right] \\ = \frac{1}{12N^2} \left[ \int_0^1 \frac{w_\rho(r)}{c_\rho(r)} \, dr + \int_0^1 \frac{w_\theta(r)}{c_\theta(r)} \, dr \right],$$

(3.19)

where

$$w_{

ho}(r_i) = p(r)$$

and  $w_{ heta}(r) = \left|g_{

ho}(r)f'_{ heta}(r)\right|^2 \tilde{p}(r).$

p(r) and  $\tilde{p}(r)$  are the probability density functions of the input amplitude and predistorted amplitude, respectively. It is observed that similarly to the complex-gain predistorter configuration in [11], the total residual distortion power is inversely proportional to  $N^2$ . In other words, the residual distortion resulting from ZOH-LUT approximations decreases by 6 dB when the LUT size is doubled. The optimal companders for the non-interpolated polar predistorter LUTs are found by using an approach similar to the one described in [11]:

$$c_{\rho}(r) = \frac{w_{\rho}(r)^{1/3}}{\int_0^1 w_{\rho}(r)^{1/3} dr} \quad \text{and} \quad c_{\theta}(r) = \frac{w_{\theta}(r)^{1/3}}{\int_0^1 w_{\theta}(r)^{1/3} dr}.$$

(3.20)

It is interesting to note that the optimal amplitude LUT spacing only depends on the input probability density function. Experimental results have also shown that the dependence on the amplifier characteristics can be generally neglected for the phase LUT spacing. A residual distortion power difference of less than 0.1 dB is measured if  $w_{\theta} \approx \tilde{p}(r)$  is used in computing the phase LUT compander. This result corresponds to the traditional optimal quantizer in [24]. Therefore, the same LUT spacing can be used for both amplitude and phase LUTs if  $p(r) \approx \tilde{p}(r)$ . In this case, the spacing only depends on the input amplitude's statistics. Alternatively, instead of using an explicit compander, the LUT can be defined as optimally spaced pairs of input and output values  $[r_k, f(r_k)]$ , which are obtained by using the Lloyd-Max algorithm [24]. The theoretical results derived above have been validated through extensive simulations. The PA model is based on the measured characteristics extracted from a near class-E RF power amplifier. The AM-AM and AM-PM profiles are shown in Figure 3.5.

Figure 3.5: Class-E amplifier characteristics.

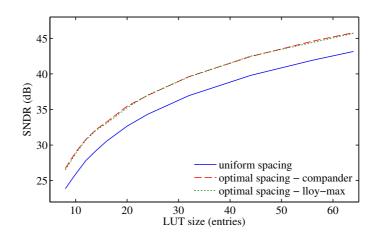

The signal to noise and distortion ratio (SNDR) has been measured from simulations for various LUT sizes, with both uniform and optimal spacing. The optimal spacing results in a 2.5 dB decrease of the residual distortion power when compared to uniform spacing. The experimental results in Figure 3.6 confirm the theoretical assertion that the residual distortion power decreases by 6 dB each time the LUT size is doubled. Moreover, the performance measured with the iterative Lloyd-Max algorithm spacing closely matches that of the optimal compander.

Figure 3.6: LUT distortion-to-signal power ratio vs. LUT size for ZOH-LUT.

## 3.2.2 Optimal Spacing of Linearly-Interpolated Polar LUT Predistorters

The use of linearly-interpolated LUT predistorters has been justified experimentally in the literature [21] as an efficient way to reduce the LUT approximation errors. A low-complexity and practical implementation of linear interpolation in LUT predistorters is also discussed in [47]. The problem has been approached with mathematical justification in Section 3.1 and the theoretical results validated with simulated experiments. As previously shown in Section 3.1, the residual distortion power resulting from linearly approximation errors can be written as follows:

$$P_{\rm dis} = \frac{1}{120N^4} \left[ \int_0^1 \frac{w_\rho(r_i)}{c'_\rho(r_i)^4} \, dr_i + \int_0^1 \frac{w_\theta(r_p)}{c'_\theta(r_p)^4} \, dr_p \right],\tag{3.21}$$

where

$$w_{\rho}(r_i) = \left| \frac{f_{\rho}''(r_i)}{f_{\rho}'(r_i)} \right|^2 p(r_i)$$

and  $w_{\theta}(r_p) = |g_{\rho}(r_p)f_{\theta}''(r_p)|^2 p(r_p)$

The set of companders that minimize the residual distortion power are found by using an approach similar to [11]:

$$c_{\rho}(r) = \frac{w_{\rho}(r)^{1/5}}{\int_0^1 w_{\rho}(r)^{1/5} dr} \quad \text{and} \quad c_{\theta}(r) = \frac{w_{\theta}(r)^{1/5}}{\int_0^1 w_{\theta}(r)^{1/5} dr}.$$

(3.22)

Equation (3.21) shows that the residual distortion power resulting from approximation errors in the linearly-interpolated predistorter is inversely proportional to  $N^4$ . The residual distortion power decreases by 12 dB when the LUT size is doubled as opposed to 6 dB for the nearest-neighbor LUT (ZOH-LUT). These results have been validated by simulations using the PA model previously shown in Figure 3.5. The simulated results are summarized in Figure 3.7.

Figure 3.7: LUT distortion-to-signal-power ratio vs. LUT size for linearly-interpolated LUT.

The plot in Figure 3.7 shows that when optimal spacing is used in a linearly-interpolated LUT predistorter with 64 entries, the residual distortion power is reduced by about 10 dB, as opposed to just 3 dB for the ZOH-LUT predistorter. Therefore, the important conclusion reached here is that optimal spacing is more beneficial and justifiable in the context of linearly-interpolated LUT predistorters.

## CHAPTER IV

# OPTIMAL SPACING OF INTERPOLATED COMPLEX-GAIN LUT PREDISTORTERS