# LHCb Trigger System : Technical Design Report

R. Antunes Nobrega, A. Franca Barbosa, I. Bediaga, G. Cernicchiaro, E. Correade Oliveira, J. Magnin, J. Marquesde Miranda, A. Massafferri, E. Polycarpo, A. Reis, et al.

# ► To cite this version:

R. Antunes Nobrega, A. Franca Barbosa, I. Bediaga, G. Cernicchiaro, E. Correade Oliveira, et al.. LHCb Trigger System : Technical Design Report. 2003, pp.xii-80. <in2p3-00025911>

# HAL Id: in2p3-00025911 http://hal.in2p3.fr/in2p3-00025911

Submitted on 7 Apr 2006  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

CERN LHCC 2003-031 LHCb TDR 10 9 September 2003

# LHCb

# **Trigger System Technical Design Report**

Printed at CERN Geneva, 2003 ISBN 92–9083–208–8 ii

# The LHCb Collaboration

# Brasilian Center for Research in Physics, CBPF, Rio de Janeiro, Brasil

R. Antunes Nobrega, A. Franca Barbosa<sup>1)</sup>, I. Bediaga, G. Cernicchiaro, E. Correa de Oliveira, J. Magnin, J. Marques de Miranda, A. Massafferri, E. Polycarpo, A. Reis

#### Federal University of Rio de Janeiro, UFRJ, Rio de Janeiro, Brasil

K. Akiba, S. Amato, T. da Silva, J.R.T. de Mello Neto, B. de Paula, L. de Paula, M. Gandelman, J.H. Lopes, B. Marechal, F. Marinho, D. Moraes<sup>2)</sup>, N. Pelloux<sup>1)</sup>, C. Perreira Nunes

#### LAPP Annecy, IN2P3-CNRS, Annecy-Le-Vieux, France

J. Ballansat, D. Boget, P. Delebecque, I. De Bonis, D. Decamp, C. Drancourt, N. Dumont Dayot, C. Girard, B. Lieunard, M.-N. Minard, B. Pietrzyk, H. Terrier

### LPC Clermont, IN2P3-CNRS and University Blaise Pascal, Clermont-Ferrand, France

Z. Ajaltouni, G. Bohner, C. Carloganu, R. Cornat, O. Deschamps, P. Henrard, J. Lecoq, R. Lefevre, S. Monteil,

P. Perret, C. Rimbault, A. Robert

#### CPPM Marseille, IN2P3-CNRS and University of Aix-Marseille II, Marseille, France

E. Aslanides, J.-P. Cachemiche, B. Dinkespiler, P.-Y. Duval, R. Le Gac, V. Garonne, O. Leroy, P.-L. Liotard, M. Menouni, A. Tsaregorodtsev, B. Viaud

#### LAL Orsay, IN2P3-CNRS and University of Paris-Sud, Orsay, France

G. Barrand, C. Beigbeder-Beau, R. Beneyton, D. Breton, O. Callot<sup>1)</sup>, D. Charlet, B. D'Almagne, B. Delcourt, O. Duarte, F. Fulda Quenzer, B. Jean-Marie, J. Lefrançois, F. Machefert, P. Robbe, M.-H. Schune, V. Tocut, K. Truong

## Technical University of Dresden, Dresden, Germany

R. Schwierz, B. Spaan

# Max-Planck-Institute for Nuclear Physics, Heidelberg, Germany

M. Agari, C. Bauer, D. Baumeister, J. Blouw, N. Bulian, H.P. Fuchs, W. Hofmann, K.T. Knöpfle, S. Löchner, A. Ludwig, M. Schmelling, B. Schwingenheuer

#### Physics Institute, University of Heidelberg, Heidelberg, Germany

S. Bachmann, P. Bock, H. Deppe, F. Eisele, S. Henneberger, P. Igo-Kemenes, R. Rusnyak, U. Stange, U. Trunk, M. Walter, D. Wiedner, U. Uwer

### Kirchhoff Institute for Physics, University of Heidelberg, Heidelberg, Germany

I. Kisel, V. Lindenstruth, M.W. Schulz<sup>2)</sup>

# Laboratori Nazionali dell' INFN, Frascati, Italy

G. Bencivenni, C. Bloise, F. Bossi, P. Campana, G. Capon, P. de Simone, C. Forti, G. Lanfranchi, F. Murtas, L. Passalacqua, V. Patera<sup>3)</sup>, M. Poli Lener, A. Sciubba<sup>3)</sup>

## University of Bologna and INFN, Bologna, Italy

G. Avoni, G. Balbi, M. Bargiotti, A. Bertin, M. Bruschi, A. Carbone, S. de Castro, P. Faccioli, L. Fabbri,

D. Galli, B. Giacobbe, F. Grimaldi, I. Lax, U. Marconi, I. Massa, M. Piccinini, N. Semprini-Cesari, R. Spighi,

V. Vagnoni, S. Vecchi, M. Villa, A. Vitale, A. Zoccoli

### University of Cagliari and INFN, Cagliari, Italy

W. Bonivento, S. Cadeddu, A. Cardini, V. de Leo, C. Deplano, A. Lai, D. Raspino, B. Saitta

## University of Ferrara and INFN, Ferrara, Italy

W. Baldini, V. Carassiti, A. Cotta Ramusino, P. Dalpiaz, S. Germani, A. Gianoli, M. Martini, F. Petrucci, M. Savrié

## University of Florence and INFN, Florence, Italy

A. Bizzeti, M. Lenti, M. Lenzi, G. Passaleva, P.G. Pelfer, M. Veltri

## University of Genoa and INFN, Genoa, Italy

S. Cuneo, F. Fontanelli, V. Gracco, G. Mini, P. Musico, A. Petrolini, M. Sannino

# University of Milano-Bicocca and INFN, Milano, Italy

T. Bellunato, M. Calvi, C. Matteuzzi, M. Musy, P. Negri, D. Perego, L. Trentadue<sup>4)</sup>

#### University of Rome, "La Sapienza" and INFN, Rome, Italy

G. Auriemma<sup>5)</sup>, V. Bocci, C. Bosio, E. Dane, D. Fidanza<sup>5)</sup>, A. Frenkel, G. Martellotti, G. Penso, S. Petrarca,

D. Pinci, G. Pirozzi, W. Rinaldi, R. Santacesaria, C. Satriano<sup>5)</sup>, A. Satta

## University of Rome, "Tor Vergata" and INFN, Rome, Italy

G. Carboni, S. de Capua, D. Domenici, R. Messi, G. Natali, L. Pacciani, E. Santovetti

## NIKHEF, The Netherlands

G. van Apeldoorn(i,iii), N. van Bakel(i,ii), T.S. Bauer(i), M. van Beuzekom(i), J.F.J. van den Brand(i,ii), H.J. Bulten(i,ii), M. Doets(i), R. Hierck(i), L. Hommels(i), J. van Hunen(i), E. Jans(i), T. Ketel(i,ii), S. Klous(i,ii), M.J. Kraan(i), M. Merk(i), F. Mul(ii), J. Nardulli(i), A. Pellegrino(i), G. Raven(i,ii), H. Schuijlenburg(i), T. Sluijk(i), P. Vankov(i), J. van Tilburg(i), H. de Vries(i), L. Wiggers(i), M. Zupan(i)

(i) Foundation of Fundamental Research of Matter in the Netherlands

(ii) Free University Amsterdam

(iii) University of Amsterdam

## Research Centre of High Energy Physics, Tsinghua University, Beijing, P.R.C.

M. Bisset, J.P. Cheng, Y.G. Cui, Y. Dai, Y. Gao, H.J. He, C. Huang, C. Jiang, Y.P. Kuang, Q.Li, Y.J. Li, Y. Liao, J.P. Ni, B.B. Shao, J.J. Su, Y.R. Tian, Q. Wang, Q.S. Yan

## Institute of Nuclear Physics and University of Mining and Metallurgy, Krakow, Poland

K. Ciba, K. Galuszka, L. Hajduk, P. Kapusta, J. Michalowski, B. Muryn, Z. Natkaniec, A. Oblakowska-Mucha, G. Polok, M. Stodulski, M. Witek<sup>1)</sup>, P. Zychowski

### Soltan Institute for Nuclear Studies, Warsaw, Poland

M. Adamus, A. Chlopik, Z. Guzik, A. Nawrot, K. Syryczynski, M. Szczekowski

# National Institute for Physics and Nuclear Engineering, IFIN-HH, Bucharest-Magurele, Romania

C. Coca, O. Dima, G. Giolu, C. Magureanu, M. Orlandea, S. Popescu<sup>1</sup>), A.M. Rosca<sup>6</sup>), P.D. Tarta

## Institute for Nuclear Research (INR), Moscow, Russia

S. Filippov, J. Gavrilov, E. Guschin, V. Kloubov, L. Kravchuk, S. Laptev, V. Laptev, V. Postoev, G. Rybkine, A. Sadovski, I. Semeniouk, V. Strigin

#### Institute of Theoretical and Experimental Physics (ITEP), Moscow, Russia

S. Barsuk<sup>1)</sup>, I. Belyaev<sup>1)</sup>, B. Bobchenko, V. Dolgoshein, A. Golutvin, O. Gouchtchine, V. Kiritchenko, V. Kochetkov, I. Korolko, G. Pakhlova, E. Melnikov<sup>1)</sup>, A. Morozov, P. Pakhlov, A. Petriaev, D. Roussinov, V. Rusinov, S. Semenov, S. Shuvalov, A. Soldatov, E. Tarkovski

## Budker Institute for Nuclear Physics (INP), Novosibirsk, Russia

K. Beloborodov, A. Berdiouguine, A. Bondar, A. Bozhenok, A. Buzulutskov, S. Eidelman, V. Golubev, P. Krokovnyi, S. Oreshkin, A. Poluektov, S. Serednyakov, L. Shekhtman, B. Shwartz, Z. Silagadze, A. Sokolov, A. Vasiljev

## Institute for High Energy Physics (IHEP-Serpukhov), Protvino, Russia

K. Beloous, V. Brekhovskikh, R.I. Dzhelyadin, Yu.P. Gouz, I. Katchaev, V. Khmelnikov, V. Kisselev, A. Kobelev, A.K. Konoplyannikov, A.K. Likhoded, V.D. Matveev, V. Novikov, V.F. Obraztsov, A.P. Ostankov, V.Romanovski, V.I. Rykalin, M.M. Shapkin, A. Sokolov, M.M. Soldatov, V.V. Talanov, O.P. Yushchenko

## Petersburg Nuclear Physics Institute, Gatchina, St. Petersburg, Russia

G. Alkhazov, V. Andreev, B. Botchine, V. Ganja, V. Goloubev, S. Guetz, A. Kashchuk, V. Lazarev, E. Maev, O. Maev, G. Petrov, N. Saguidova, G. Sementchouk, V. Souvorov<sup>1</sup>), E. Spiridenkov, A. Vorobyov, An. Vorobyov, N. Voropaev

### University of Barcelona, Barcelona, Spain

E. Aguilo, R. Ballabriga<sup>7)</sup>, M. Calvo, S. Ferragut, Ll. Garrido, D. Gascon, R. Graciani Diaz, E. Grauges Pous, S. Luengo<sup>7)</sup>, D. Peralta, M. Rosello<sup>7)</sup>, X. Vilasis<sup>7)</sup>

#### University of Santiago de Compostela, Santiago de Compostela, Spain

B. Adeva, P. Conde<sup>8)</sup>, C. Lois Gomez<sup>9)</sup>, A. Pazos, M. Plo, J.J. Saborido, M. Sanchez Garcia, P. Vazquez Regueiro

## University of Lausanne, Lausanne, Switzerland

A. Bay, B. Carron, O. Dormond, L. Fernandez, R. Frei, G. Haefeli, J.-P. Hertig, C. Jacoby, P. Jalocha, S. Jimenez-Otero, F. Legger, L. Locatelli, N. Neufeld<sup>1)</sup>, J.-P. Perroud, F. Ronga, T. Schietinger, O. Schneider, L. Studer, M.T. Tran, S. Villa, H. Voss

#### University of Zürich, Zürich, Switzerland

R. Bernet, R.P. Bernhard, Y. Ermoline, J. Gassner, St. Heule, F. Lehner, M. Needham, P. Sievers, St. Steiner, O. Steinkamp, U. Straumann, A. Vollhardt, D. Volyanskyy, M. Ziegler<sup>10</sup>

#### Institute of Physics and Technologies, Kharkiv, Ukraine

A. Dovbnya, Yu. Ranyuk, I. Shapoval

## Institute for Nuclear Research, National Academy of Sciences, Kiev, Ukraine

V. Aushev, V. Kiva, I. Kolomiets, Yu. Pavlenko, V. Pugatch, Yu. Vasiliev

## University of Bristol, Bristol, UK

N.H. Brook, R.D. Head, A. Muir, A. Phillips, A. Presland, F.F. Wilson

#### University of Cambridge, Cambridge, UK

A. Buckley, K. George, V. Gibson, K. Harrison, C.R. Jones, S.G. Katvars, J. Storey, C.P. Ward, S.A. Wotton

#### Rutherford Appleton Laboratory, Chilton, UK

C.J. Densham, S. Easo, B. Franek, J.G.V. Guy, R.N.J. Halsall, G. Kuznetsov, P. Loveridge, D. Morrow, J.V. Morris, A. Papanestis, G.N. Patrick, M.L. Woodward

# University of Edinburgh, Edinburgh, UK

R. Chamonal, S. Eisenhardt, A. Khan, J. Lawrence, F. Muheim, S. Playfer, A. Walker

A.G. Bates, A. MacGregor, V. O'Shea, C. Parkes, A. Pickford, M. Rahman, F.J.P. Soler<sup>11</sup>)

# University of Liverpool, Liverpool, UK

S. Biagi, T. Bowcock, G. Casse, R. Gamet, M. George, D. Hutchcroft, J. Palacios, G. Patel, I. Stavitskiy, M. Tobin, A. Washbrook

## Imperial College, London, UK

L. Allebone, G.J. Barber, W. Cameron, D. Clark, P. Dornan, A. Duane, U. Egede, A. Howard, S. Jolly, R. Plackett, D.R. Price, T. Savidge, D. Websdale, R. White

# University of Oxford, Oxford, UK

M. Adinolfi, J.H. Bibby, M.J. Charles<sup>12)</sup>, C. Cioffi, G. Damerell, N. Harnew, F. Harris, I.A. McArthur, C. Newby, J. Rademacker, L. Somerville, A. Soroko, N.J. Smale, S. Topp-Jorgensen, G. Wilkinson

# CERN, Geneva, Switzerland

G. Anelli, F. Anghinolfi, N. Arnaud, F. Bal, A. Barczyk, J.C. Batista Lopes, M. Benayoun<sup>13)</sup>, V. Bobillier, A. Braem, J. Buytaert, M. Campbell, M. Cattaneo, Ph. Charpentier, J. Christiansen, J. Closier, P. Collins, G. Corti, C. D'Ambrosio, H. Dijkstra, J.-P. Dufey, D. Eckstein, M. Ferro-Luzzi, W. Flegel, F. Formenti, R. Forty, M. Frank, C. Frei, C. Gaspar, P. Gavillet, A. Guirao Elias, T. Gys, F. Hahn, S. Haider, J. Harvey, J.A. Hernando Morata, E. van Herwijnen, H.J. Hilke, R. Jacobsson, P. Jarron, C. Joram, B. Jost, S. Koestner, D. Lacarrère, M. Letheren, C. Lippmann<sup>14)</sup>, R. Lindner, M. Losasso, P. Mato Vila, M. Moritz, H. Müller, T. Nakada<sup>15)</sup>, C. Padilla, U. Parzefall, W. Pokorski, S. Ponce, F. Ranjard, W. Riegler, G. Aglieri Rinella, E.M. Rodrigues<sup>16)</sup>, D. Rodriguez de Llera Gonzalez, S. Roiser, T. Ruf, H. Ruiz Perez, B. Schmidt, T. Schneider, A. Schopper, A. Smith, F. Teubert, N. Tuning, O. Ullaland, P. Vannerem, W. Witzeling, K. Wyllie, Y. Xie

- <sup>1)</sup> also at CERN, Geneva

- <sup>2)</sup> now at CERN, Geneva

- <sup>3)</sup> also at Dipartimento di Energetica, University of Rome, "La Sapienza"

- <sup>4)</sup> also at Universita degli Studi di Parma

- <sup>5)</sup> also at University of Basilicata, Potenza

- <sup>6)</sup> also at Humbolt University, Berlin

- <sup>7)</sup> also at departament d'Engineria Electronica La Salle, Universitat Ramon Llull, Barcelona

- <sup>8)</sup> now at DESY, Hamburg

- <sup>9)</sup> now at University of Zürich

- <sup>10)</sup> now at University of California, Santa Cruz

- <sup>11)</sup> also at Rutherford Appleton Laboratory, Chilton

- <sup>12)</sup> now at University of Iowa, Iowa City

- <sup>13)</sup> now at Universités de Paris VI et VII (LPNHE), Paris

- <sup>14)</sup> now at GSI, Darmstadt

- <sup>15)</sup> also at Lausanne, on leave from PSI, Villigen

- <sup>16)</sup> supported by a Marie Curie Fellowship under contract number HPMF-CT-2002-01708

## **Technical Associates Institutes**

Espoo-Vantaa Institute of Technology, Espoo, Finland Ecole d'ingénieurs, Geneva, Switzerland

# Acknowledgements

The LHCb Collaboration is greatly indebted to all the technical and administrative staff for their important contributions to the design, testing and prototype activities. We are grateful for their dedicated work and are aware that the successful construction and commissioning of the LHCb experiment will also in future depend on their skills and commitment.

"Trigger" on cover page: The compact edition of the Oxford English Dictionary Complete text reproduced micrographically 2 volumes Oxford University Press (23 edition, 1984) viii

# Contents

| 1        | $\mathbf{Intr}$ | oducti  | ion                                                                                                        | 1  |

|----------|-----------------|---------|------------------------------------------------------------------------------------------------------------|----|

|          | 1.1             | Physic  | cs requirements                                                                                            | 1  |

|          | 1.2             | Front-  | End Architecture Requirements                                                                              | 2  |

|          | 1.3             | Impler  | mentation Overview                                                                                         | 3  |

|          | 1.4             | Organ   | ization of this Document                                                                                   | 6  |

| <b>2</b> | Leve            | el-0 Ca | alorimeter Triggers                                                                                        | 9  |

|          | 2.1             | Conce   | pts of the L0 Calorimeter Trigger                                                                          | 9  |

|          | 2.2             |         | lorimeter Trigger performance                                                                              |    |

|          | 2.3             | ECAL    | and HCAL FE card $\ldots$ | 11 |

|          | 2.4             | PreSh   | ower FE card                                                                                               | 12 |

|          | 2.5             | Valida  | ation Card                                                                                                 | 13 |

|          |                 | 2.5.1   | ECAL candidates                                                                                            | 13 |

|          |                 | 2.5.2   | HCAL candidates                                                                                            | 14 |

|          | 2.6             | SPD N   | Multiplicity                                                                                               | 15 |

|          | 2.7             |         | plane and links                                                                                            | 15 |

|          | 2.8             | Selecti | ion Crate                                                                                                  | 15 |

|          |                 | 2.8.1   | Electromagnetic Candidates                                                                                 | 15 |

|          |                 | 2.8.2   | SPD multiplicity                                                                                           | 16 |

|          |                 | 2.8.3   | HCAL                                                                                                       | 16 |

|          |                 | 2.8.4   | Implementation                                                                                             | 16 |

|          | 2.9             | Latenc  | су                                                                                                         | 17 |

|          | 2.10            | Debug   | ging and Monitoring                                                                                        | 17 |

| 3        | Leve            | el-0 M  | luon Trigger                                                                                               | 19 |

|          | 3.1             | Overvi  | iew of the muon system                                                                                     | 19 |

|          | 3.2             | Trigge  | er implementation                                                                                          | 21 |

|          | 3.3             |         | er performance                                                                                             | 22 |

|          |                 | 3.3.1   | Low-energy background                                                                                      |    |

|          |                 | 3.3.2   | Beam halo muons                                                                                            | 24 |

|          |                 | 3.3.3   | Hardware parameters                                                                                        | 24 |

|          | 3.4             | Techni  | ical Design                                                                                                | 25 |

|          |                 | 3.4.1   | ODE Trigger interface                                                                                      | 25 |

|          |                 | 3.4.2   | Processing Board                                                                                           |    |

|          |                 | 3.4.3   | Muon selection board                                                                                       |    |

|          |                 | 3.4.4   | Controller board                                                                                           | 28 |

|          |                   | 3.4.5   | Backplane                                     | 29         |

|----------|-------------------|---------|-----------------------------------------------|------------|

|          |                   | 3.4.6   | Latency                                       | 29         |

|          |                   | 3.4.7   | DAQ Event size                                | <b>S</b> 0 |

|          |                   | 3.4.8   | Debugging and monitoring tools                | 80         |

| 4        | Lou               |         | le-Up System 3                                | 1          |

| 4        | <b>Lev</b><br>4.1 |         |                                               | 51         |

|          | 4.1<br>4.2        |         | •                                             | 32         |

|          | 4.2<br>4.3        |         |                                               | 92<br>33   |

|          | 4.5               | 4.3.1   | 0                                             |            |

|          |                   |         | 1                                             | 84<br>95   |

|          |                   | 4.3.2   | J 1                                           | 85<br>96   |

|          |                   | 4.3.3   | Trigger System Architecture                   | 6          |

| <b>5</b> | Lev               | el-0 D  | ecision Unit 3                                | 9          |

|          | 5.1               | LODU    | inputs                                        | <b>3</b> 9 |

|          | 5.2               | LODU    | overview                                      | 0          |

|          | 5.3               | LODU    | Prototype                                     | 1          |

|          | 5.4               | Studie  | s for the final implementation                | 1          |

|          | 5.5               |         | -                                             | 2          |

| c        | т                 | .l. 1   | d High Local Thingson                         | ი          |

| 6        | <b>Lev</b> 6.1    |         | 8 88 8                                        | <b>3</b>   |

|          | 0.1               | 6.1.1   | -                                             | 14<br>15   |

|          |                   | -       |                                               |            |

|          | C D               | 6.1.2   | 1                                             | 8          |

|          | 6.2               |         |                                               | 51         |

|          |                   | 6.2.1   |                                               | 52         |

|          |                   | 6.2.2   | 0                                             | 52         |

|          |                   | 6.2.3   |                                               | 53         |

|          |                   | 6.2.4   |                                               | 53         |

|          |                   | 6.2.5   | 3 0                                           | 53         |

|          |                   | 6.2.6   | VELO TT Matching and Momentum Determination 5 |            |

|          |                   | 6.2.7   | L1  timing                                    |            |

|          | 6.3               |         | LT Algorithm                                  |            |

|          |                   | 6.3.1   | 0                                             | 66         |

|          |                   | 6.3.2   | 0                                             | 66         |

|          |                   | 6.3.3   |                                               | 66         |

|          |                   | 6.3.4   | Tracking summary 5                            | 57         |

| 7        | Per               | formar  | ace Simulation 5                              | 9          |

|          | 7.1               |         |                                               | 59         |

|          |                   | 7.1.1   | Bandwidth Division                            | 50         |

|          | 7.2               | Perfor  |                                               | 52         |

|          |                   | 7.2.1   |                                               | 53         |

|          |                   | 7.2.2   |                                               | 33         |

|          |                   | 7.2.3   | 1 0                                           | 54         |

|          |                   | 7.2.4   |                                               | 54         |

|          | 7.3               | -       |                                               | 54         |

|          |                   | - 0.101 |                                               | -          |

|    |        | 7.3.1             | Level-1 Confirmation          | 66        |

|----|--------|-------------------|-------------------------------|-----------|

|    |        | 7.3.2             | Exclusive Selection           | 66        |

|    | 7.4    | Trigger           | Performance Robustness        | 67        |

|    |        | 7.4.1             | Resolutions                   | 68        |

|    |        | 7.4.2             | Execution Time and Event Size | 68        |

|    |        | 7.4.3             | Performance                   | 68        |

| 8  | •      | Cost a:<br>Schedu | ganization<br>nd Funding      |           |

| A  | Scal   | ability           | of Level-1                    | <b>75</b> |

| Re | eferei | nces              |                               | 78        |

# Chapter 1 Introduction

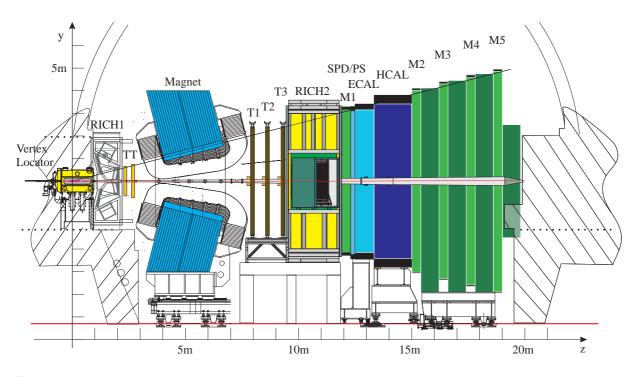

The LHCb experiment [1, 2] is designed to exploit the large number of bb-pairs produced in pp interactions at  $\sqrt{s}=14$  TeV at the LHC, in order to make precise studies of CP asymmetries and rare decays in bhadron systems. LHCb is a single arm spectrometer covering the range<sup>1</sup>  $1.9 < \eta < 4.9$ . The spectrometer is shown in Figure 1.1, and consists of the Vertex Locator (VELO), the Trigger Tracker (TT), the dipole magnet, two Ring Imaging Cherenkov detectors (RICH1&2), three tracking stations T1–T3, the Calorimeter system and the Muon system. LHCb uses a right handed coordinate system with the z-axis pointing from the interaction point towards the muon chambers along the beam-line, and the y-axis is pointing up-wards. All of the systems are described in detail in their respective Technical Design Reports [3-10], apart from TT and a new layout of RICH1 which are described in the LHCb Reoptimization TDR [2]. The LHCb experiment plans to operate at an average luminosity of  $2 \times 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup>, i.e. much lower than the maximum design luminosity of the LHC, which makes the radiation damage more manageable. A further advantage is that at this luminosity the number of interactions per crossing is dominated by single interactions, which facilitates the triggering and reconstruction by assuring low channel occupancy. Due to the LHC bunch structure and low luminosity the frequency of crossings with interactions visible<sup>2</sup> by the spectrometer is about 10 MHz, which has to be reduced by the trigger to a few hundred Hz, at which rate the events are written to storage for further offline analysis. This reduction is achieved in three trigger levels: Level-0 (L0), Level-1 (L1) and the High Level Trigger (HLT). Level-0 is implemented in custom electronics, while Level-1 and the HLT are executed on a farm of commodity processors.

In the remainder of this introduction the requirements from both the physics and the Front-End implementation will be given, followed by an overview of the whole trigger architecture.

# **1.1** Physics requirements

At a luminosity of  $2 \times 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup> the 10 MHz of crossings with visible pp interaction are expected to contain a rate of about 100 kHz of bb-pairs. However, in only about 15% of the events will at least one Bmeson have all its decay products contained in the acceptance of the spectrometer. Furthermore the branching ratios of B-mesons used to study CP violation are typically less than  $10^{-3}$ . The offline selections exploit the relatively large b mass and lifetime to select those b-hadrons, and stringent cuts have to be applied to enhance signal over background and thus increase the CP sensitivity of the analysis. Hence the requirement for the trigger is to achieve the highest efficiency for these offline selected events. The

<sup>&</sup>lt;sup>1</sup>The pseudo-rapidity  $\eta = -\ln(\tan(\theta/2))$  where  $\theta$  is the angle between a track and the beam-line.

$<sup>^{2}</sup>$ An interaction is defined to be visible if it produces at

least two charged particles with sufficient hits in the VELO and T1–T3 to allow them to be reconstructible.

Figure 1.1: The layout of the LHCb spectrometer showing the VELO, the two RICH detectors, the four tracking stations TT and T1–T3, the 4 Tm dipole magnet, the Scintillating Pad detector (SPD), Preshower (PS), Electromagnetic (ECAL) and Hadronic (HCAL) Calorimeters, and the five muon stations M1–M5.

trigger should be able to achieve high efficiency for a large variety of final states.

The trigger should allow overlapping and pre-scaled triggers. It should be possible to emulate the trigger from the data written to storage, which will give an additional handle on trigger efficiencies and possible systematics.

# 1.2 Front-End Architecture Requirements

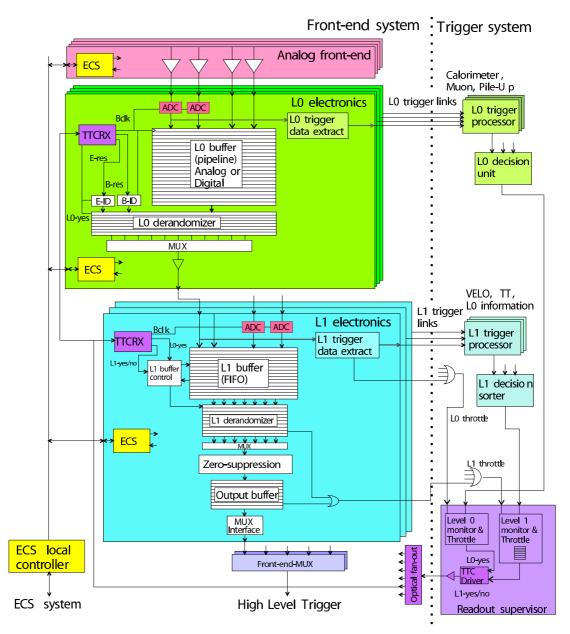

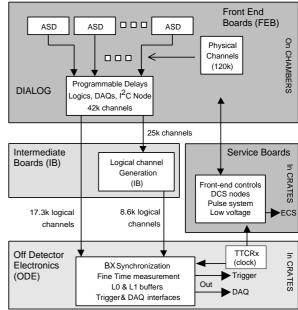

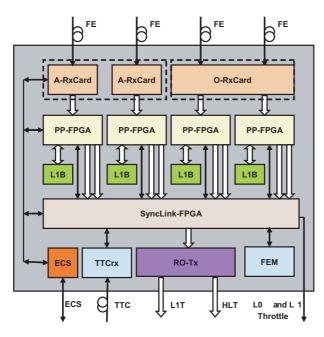

A detailed description of the requirements to the Front-End (FE) electronics can be found in [11]. A schematic overview of the FE system is given in Figure 1.2. Here we limit ourselves to those requirements which have a particular influence on the design of the Level-0 and Level-1 triggers. The Level-0 and Level-1 triggers. The Level-0 and Level-1 decisions are transmitted to the FE electronics by the TTC system [12].

The latency of Level-0, which is the time elapsed between a pp interaction and the arrival of the Level-0 trigger decision at the FE, is fixed to 4  $\mu$ s [13]. This time includes the time-of-flight, cable length and all delays in the FE, leaving 2  $\mu$ s for the actual processing of the data in the Level-0 trigger to derive a decision. The FE is required to be able to readout events in 900 ns, which combined with the 16-event-deep de-randomizer before the L1-buffer and a 1 MHz Level-0 accept rate gives less than 0.5% deadtime [14]. Level-0 will deliver its decision every 25 ns to the Readout Supervisor [15], which emulates the L0-buffer occupancy, and prevents buffer overflows by throttling the L0 accept rate.

The Level-1 trigger is a variable latency trigger and the data delivered to the trigger processors by the FE system must be delivered in chronological order and tagged with bunch and event identifiers. Despite the variable latency, Level-1 delivers a decision for each event in the same order to the Readout Supervisor. The maximum Level-1 output rate is fixed to 40 kHz, and overflow of the Level-1 de-randomizer buffers is prevented by a throttle system controlled by the Readout Supervisor. The

Figure 1.2: The FE architecture of LHCb.

depth of the L1-buffer<sup>3</sup>, combined with a 1 MHz Level-0 rate, and the requirement to deliver the decisions chronologically ordered allows a latency of up to 58 ms.

# **1.3** Implementation Overview

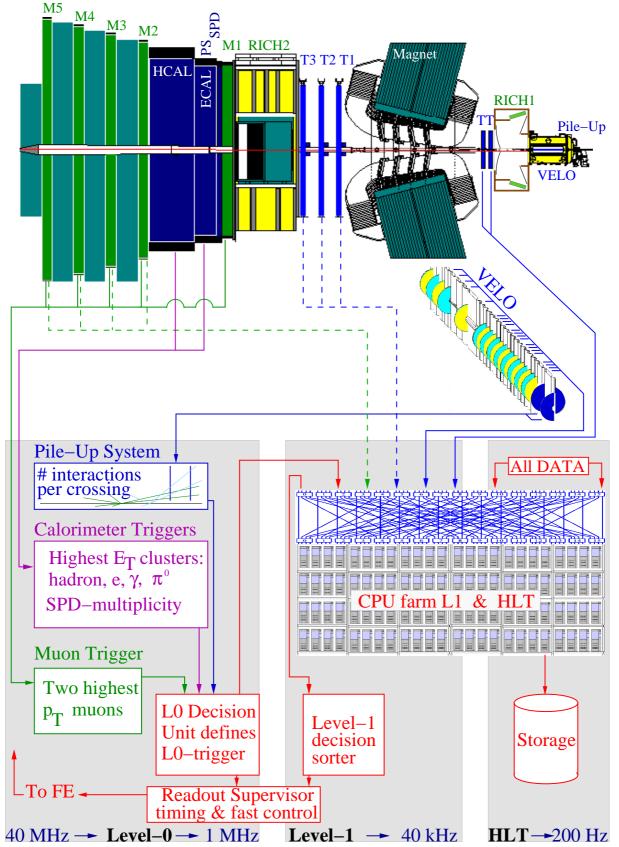

Given the physics requirement to achieve a maximum trigger efficiency for offline selected events, the main aim of the trigger implementation is to enable trigger algorithms to have access to the same data as the offline analysis, and anticipates the selection algorithms as closely as possible at the highest possible rate. Figure 1.3 shows an overview of the sub-detectors participating in the three trigger levels.

# Level-0

The purpose of Level-0 is to reduce the LHC beam crossing rate of 40 MHz, which contains about 10 MHz of crossing with visible pp-interactions, to the rate at which in

$<sup>^3{\</sup>rm The}$  size of the Level-1 buffer is 2 M words. With a 36-word-long event fragment, which contains 32 channels and up to four data tags, this allows up to 58254 events to be buffered.

Figure 1.3: Overview of the three trigger levels. Stations M1–M5 are used to reconstruct two muons per quadrant. The SPD, PS, ECAL and HCAL are used to reconstruct the hadron, e,  $\gamma$  and  $\pi^0$  with the largest transverse energy, the charged particle multiplicity, and the total energy. The Pile-Up detector is used to recognize multiple interactions per crossing. Level-1 uses the information from VELO, TT, and Level-0 to reduce the rate to 40 kHz. T1–T3 and M2–M4 could be included in Level-1. The HLT uses all data in the event apart from the RICH to reduce the rate to 200 Hz. Level-0 is executed in full custom electronics, while Level-1 and HLT are software triggers which share a commodity farm of 1800 CPUs.

principle all sub-systems could be used for deriving a trigger decision. Due to their large mass b-hadrons decay to give a large  $E_{\rm T}$  lepton, hadron or photon, hence Level-0 reconstructs:

- the highest  $E_{\rm T}$  hadron, electron and photon clusters in the Calorimeter,

- the two highest  $p_{\rm T}$  muons in the Muon Chambers,

which information is collected by the Level-0 Decision Unit to select events. Events can be rejected based on global event variables such as charged track multiplicities and the number of interactions, as reconstructed by the Pile-Up system, to assure that the selection is based on bsignatures rather than large combinatorics, and that these events will not occupy a disproportional fraction of the data-flow bandwidth or available processing power in subsequent trigger levels.

All Level-0 triggers are fully synchronous, i.e. their latency does not depend upon occupancy nor on history. All Level-0 electronics is implemented in full custom boards.

The implementation of the calorimeter trigger is based on forming clusters by adding the  $E_{\rm T}$  of 2×2 cells on the FEboards, and selecting the clusters with the largest  $E_{\rm T}$ . Clusters are identified as e,  $\gamma$  or hadron depending on the information from the Scintillating Pad Detector (SPD), Preshower (PS), Electromagnetic (ECAL) and Hadronic (HCAL) Calorimeter. The  $E_{\rm T}$  of all HCAL cells is summed to reject crossings without visible interactions. The total number of SPD cells with a hit are counted to provide a measure of the charged track multiplicity in the crossing.

The muon chambers allow stand-alone muon reconstruction with a  $p_{\rm T}$  resolution of 20%. Track finding is performed by processing units, which combine the strip and pad data from the five muon stations to form towers pointing towards the interaction re-

gion. One crate per quarter houses the trigger boards which reconstruct the two muons with the largest  $p_{\rm T}$ .

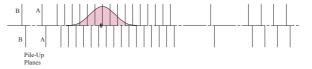

The Pile-Up system aims at distinguishing between crossings with single and multiple visible interactions. It uses four silicon sensors of the same type as those used in the VELO to measure the radial position of tracks, covering  $-4.2 < \eta < -2.9$ . The Pile-Up system provides the position of the primary vertex candidates along the beam-line and a measure of the total backward charged track multiplicity. The Pile-Up information allows a relative luminosity measurement which is not affected by system deadtime, and monitors the beam conditions.

The Level-0 Decision Unit (L0DU) collects all information from Level-0 components to form the Level-0 Trigger. The L0DU is able to perform simple arithmetic to combine all signatures into one decision per crossing. This decision is passed to the Readout Supervisor which transmits its Level-0 decision to the FE.

# Level-1

At the 1 MHz output rate of Level-0 the remaining analogue data is digitized and all data is stored for the time needed to process the Level-1 algorithm. All subsystems which deliver data to Level-1 make use of the same TELL1-board [16] to store the data in the L1-buffer, to perform zerosuppression and formatting, and to interface to Level-1. The Level-1 algorithm will be implemented on a commodity processors farm, which is shared between Level-1, HLT and offline reconstruction algorithms. The Level-1 algorithm uses the information from Level-0, the VELO and TT. The algorithm reconstructs tracks in the VELO, and matches these tracks to Level-0 muons or Calorimeter clusters to identify them and measure their momenta. The fringe field of the magnet between the VELO and TT is

used to determine the momenta of particles with a resolution of 20–40%. Events are selected based on tracks with a large  $p_{\rm T}$  and significant impact parameter to the primary vertex.

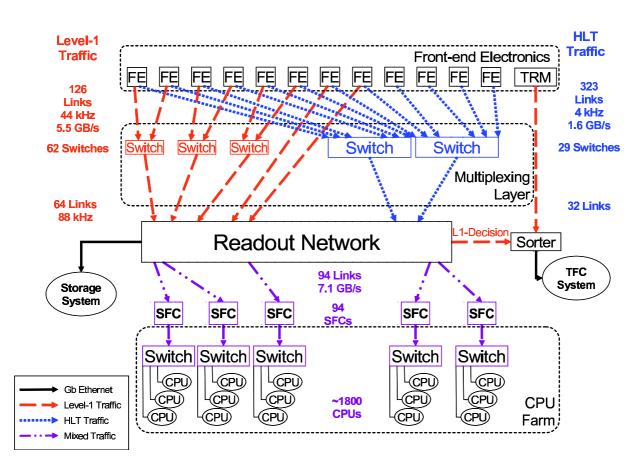

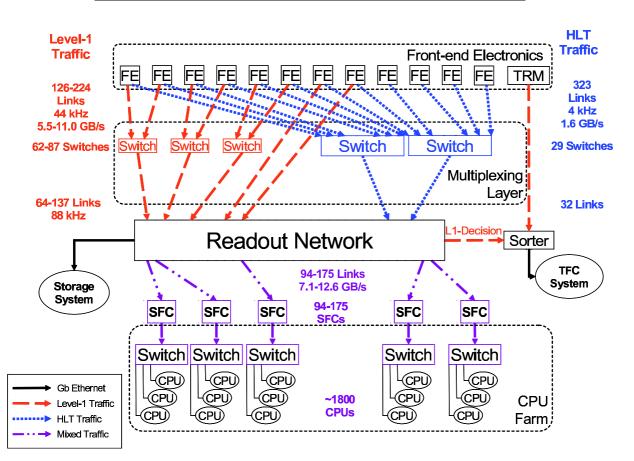

The event building architecture is inspired by the one described in the Online System TDR [9], but adapted to profit from new technologies due to the delayed startup of the LHC. The same event building network is used to collect the Level-1 decisions from all the processors, after which they are sorted according to their Level-0 event number and transmitted to the Readout Supervisor, which transmits its Level-1 decision to the FE. The maximum Level-1 output rate has been fixed to 40 kHz to allow the FE to execute more elaborate zerosuppression algorithms than the ones used to prepare the information for the Level-1 trigger. The implementation is easily scalable to allow the inclusion of stations T1– T3 and M2-M5. This will improve the Level-1 performance, and this implementation is described in Appendix A, but all performance figures given in this TDR will assume that the Level-1 algorithm will not use T1–T3 or M2–M5.

# High Level Trigger

The HLT will have access to all data. Since the design of the Online System [9] the LHCb spectrometer has been reoptimized [2], resulting in a considerably smaller data-size. Level-1 and HLT event building now share the same network, and this TDR supersedes the implementation as described in [9]. The HLT and Level-1 algorithms run concurrently on the same CPU nodes, with the Level-1 taking priority due to its limited latency budget. The HLT algorithm starts with reconstructing the VELO tracks and the primary vertex, rather than having this information transmitted from Level-1. A fast pattern recognition program links the VELO tracks to the tracking stations T1–T3. The final selection of interesting events is a combination of confirming the Level-1 decision with better resolution, and selection cuts dedicated to specific final states. While the maximum output rates of the first two trigger levels are dictated by the implementations of the FE hardware, the output rate of the HLT is kept more flexible. Considering the channels currently under study one could envisage output rates of a few Hz. However, the RICH information is not currently used by the HLT, and selection cuts have to be relaxed compared to the final selection to study the sensitivity of the selections and profit from refinements to the calibration constants. These considerations lead to an output rate of 200 Hz of events accepted by the HLT. The total CPU farm will contain about 1800 nodes. It is derived from the the expected CPU power in 2007, and performance studies discussed below, that the L1 and HLT algorithms will use about 55% and 25% of the available computing resources respectively. The remaining resources are used to fully reconstruct events accepted by the HLT, including the particle identification, before being written to storage.

# 1.4 Organization of this Document

While the trigger is logically divided into three trigger levels, its implementation is divided into five hardware sub-systems, four Level-0 sub-systems and one subsystem for Level-1 and HLT combined. The Level-0 sub-systems are the Calorimeter Triggers, the Muon Trigger, the Pile-Up Trigger and the Level-0 Decision Unit. Level-1 and the HLT form one sub-system from the technical design point of view, since they share the same event building network and processor farm. In the following chapters each of the five sub-system designs is described separately, including R&D and prototyping. Where applicable, the sensitivity of the performance of a subsystem to the LHC environment, so called robustness, will also be included, while the performance of the trigger as a whole will be described in Chapter 7. The last chapter deals with project organization.

# Chapter 2 Level-0 Calorimeter Triggers

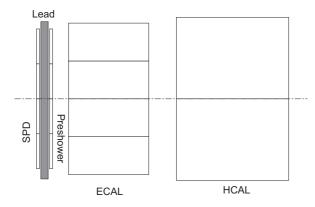

The purpose of the Calorimeter Triggers is to select and identify particles with high  $E_{\rm T}$  deposit in the calorimeters. A schematic view of the calorimeter is shown on Figure 2.1, showing the four detectors involved:

Figure 2.1: Schematic side view of the calorimeter system.

- The SPD (Scintillator Pad Detector) identifies charged particles, and allows electrons to be separated from photons.

- The PreShower detector, after 2.5 radiation length of lead, identifies electromagnetic particles.

- The electro-magnetic calorimeter ECAL, of the shashlik type, measures the energy of electromagnetic showers.

- The hadronic calorimeter HCAL, made of iron with scintillator tiles, measures the energy of the hadrons.

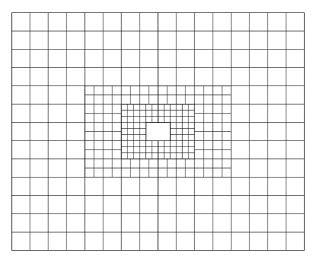

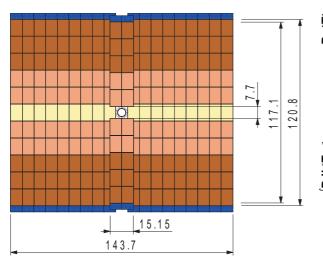

The first three detectors have the same cell geometry, displayed in Figure 2.2. The cells are about  $4 \times 4$  cm<sup>2</sup> in the central region,  $6 \times 6$  cm<sup>2</sup> in the middle region and

Figure 2.2: Layout of the SPD, Preshower and ECAL cells. Each square represents 16 cells.

$12 \times 12 \text{ cm}^2$  in the outer region. The exact size of the cells is proportional to their distance from the vertex in order to obtain a pointing geometry, and the total number of cells in each detector is 5984. The HCAL contains 1468 cells, with only two sizes,  $13 \times 13 \text{ cm}^2$  and  $26 \times 26 \text{ cm}^2$ , such that the HCAL cell boundaries project to ECAL cell boundaries. More details are given in the Calorimeter TDR [4].

# 2.1 Concepts of the L0 Calorimeter Trigger

The idea of the Calorimeter Triggers is to search for high  $E_{\rm T}$  particles: electrons, photons,  $\pi^0$  or hadrons. The way to identify each flavour is described in Section 2.5.

Showers are relatively narrow, with energy deposits in a small area. A zone of

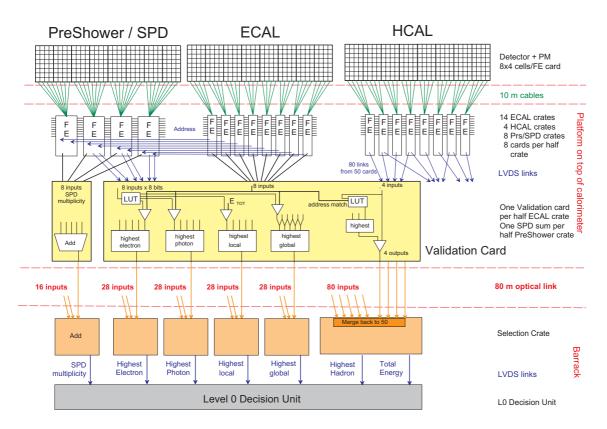

Figure 2.3: Overall view of the Calorimeter Triggers.

2 by 2 cells is used, large enough to contain most of the energy, and small enough to avoid overlap between various particles. Only the particle with the highest  $E_{\rm T}$  is looked at. Therefore at each stage only the highest  $E_{\rm T}$  candidate is kept, to minimize the number of candidates to process.

These candidates are provided by a three step selection system:

- A first selection of high  $E_{\rm T}$  deposits is performed on the Front-End (FE) card, which is the same for ECAL and HCAL. Each card handles 32 cells, and the highest  $E_{\rm T}$  sum over the 32 sums of 2 × 2 cells is selected. To compute these 32 sums, access to cells in other cards is an important issue.

- The Validation Card merges the ECAL with the PreShower and SPD information, prepared by the PreShower FE card, to identify the type of electromagnetic candidate,

electron, photon and  $\pi^0$ . Only one candidate per type is selected and sent to the next stage. The same card also adds the energy deposited in ECAL in front of the hadron candidates. A similar card computes the SPD multiplicity in the PreShower crates.

• The Selection Crate selects the candidate with the highest  $E_{\rm T}$  for each type, it also produces a measure of the Total  $E_{\rm T}$  in HCAL and the total SPD multiplicity.

An overall view of the Calorimeter Triggers is shown on Figure 2.3. Care has been taken to simplify the connections, and the system is fully synchronous, which will facilitate commissioning and debugging.

The first two steps are performed on the platform of the calorimeter, at a location with a radiation dose below 50 Gy during the whole lifetime of the experiment, and where Single Event Upsets (SEU) are expected to occur. Each component has been tested for radiation and SEU robustness [17, 18]. Anti-fuse PGAs are used, and "triple voting" techniques for all permanent memories. In this technique, each bit is stored in three copies, and a majority vote is taken before using it, so that one single bit flip does not affect the value.

# 2.2 L0 Calorimeter Trigger performance

The L0 Calorimeter Trigger provides 7 inputs to the Decision Unit, as shown on Figure 2.3. Frequently, the same energy deposit produces several candidates, as the electron, photon and  $\pi^0$  triggers are not exclusive. A hadron with a large deposit in ECAL may also produce electron, photon or  $\pi^0$  candidates. This overlap has advantages in terms of robustness of the system and allows cross-checks of the trigger behaviour, but makes difficult an analysis of the exclusive performance of each type of candidate. The overall performance in term of trigger efficiency is discussed in Chapter 7.

Figure 2.4: Performance of the Hadron Trigger.

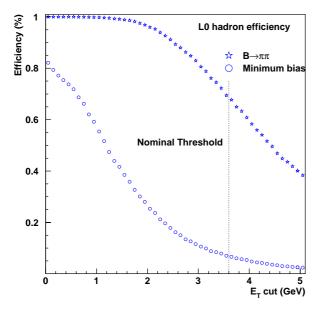

To illustrate how the signal events are different from the minimum-bias events, Figure 2.4 shows the fraction of events over a given hadron threshold, as function of this  $E_{\rm T}$  threshold, both for minimum-bias events and for offline selected  $B \rightarrow \pi \pi$ events. The nominal threshold is indicated, at which about 7% of the minimum-bias events are kept, with an efficiency around 70% on the signal.

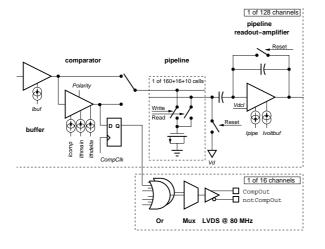

# 2.3 ECAL and HCAL FE card

The processing on the FE card is described in [19]. It is divided into several steps, performed synchronously in pipeline mode:

- Preparation of the data: the Calorimeter Trigger uses as input the 12 bit ADC value of each cell. This digitisation is already pedestal corrected [20], but has to be converted to 8-bit  $E_{\rm T}$ .

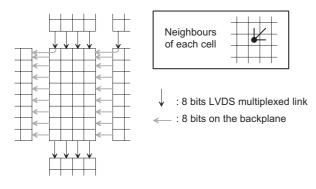

- Collection of the data: In order to compute all 32 sums over 2 × 2 cells, one has to access the neighbouring cells. A dedicated backplane connects neighbouring cards, while LVDS multiplexed links are used for the other connections.

- Computation of the 2 × 2 sums in parallel.

- Selection of the highest of the 32 sums, keeping track of its address.

- Computation of the total  $E_{\rm T}$  on the card.

- Sending the result of the processing to the next stage.

The conversion from ADC value to  $E_{\rm T}$  is performed by multiplying the ADC value by a 8 bit scale factor, and selecting the proper 8 bits. If the result would be larger than 8 bits, it is saturated to 255. This multiplication with saturation process is performed in one clock cycle [20]. The nominal scale factor is such that the value of  $E_{\rm T}$  covers the range 0 to 5.1 GeV. This choice is a compromise between the highest trigger threshold, around 4.5 GeV, and the loss of accuracy due to rounding effects. The gain is adjusted channel by channel to compensate for possible mis-calibration of the PM. The  $E_{\rm T}$  range can be varied, if needed, from about 3 GeV up to 10 GeV full scale.

The next step is to get the  $E_{\rm T}$  value for all the cells involved in the 32 sums. Each FE card covers an area of  $8 \times 4$  cells. In order to build the 32 sums, 8 right neighbours, 4 top neighbours, and one top-right neighbour are needed, as shown on Figure 2.5.

Figure 2.5: Connections to get the neighbouring cells.

Note that neighbouring cells of different size are not connected, as this would introduce unnecessary complications. The two halves of the detector are also not connected, as this would require to disconnect cables when opening the detector for maintenance. These two limitations introduce only a very small inefficiency, at the per mil level.

It is clear that local signals have to be delayed, to allow the remote information to arrive. The slowest signal is the corner one, which arrives in two steps. All other information is placed in pipe-lines, implemented using the internal memory of the PGA, with controllable length. The delay in these pipe-lines will be adjusted once the final layout is made, but it is estimated to be one clock cycle for every backplane link, and two clock cycles for an LVDS multiplexed link, since the cables will be around 2 m long. The corner signal waits 1 cycle, the LVDS signals wait 2 cycles, the backplane signals 3 cycles and the local signals 4 cycles. Note that these local signals are sent on 80 MHz multiplexed lines on the board, to reduce the number of I/O pins on the PGA. Details of this synchronisation, and of the backplane configuration, can be found in [19].

When the 45 signals are available, the 32 sums are computed in parallel. The sum is saturated when it overflows, around 5.1 GeV, which occurs for about one third of the  $B \to \pi \pi$  events as can be seen on Figure 2.4. Saturation has no effect on the performance, as the trigger relies only on the presence of a hight  $E_{\rm T}$  cluster. The highest of the 32 sum is then selected, in a series of binary comparisons: First 16 comparisons of two sums, then 8 comparisons of the 16 previous results, and so on. Five steps are needed to get the highest  $E_{\rm T}$  sum of the FE card, with its address on 5 bits. This is performed in pipeline mode, 3 cycles are needed for the sum and the comparisons.

The Total  $E_{\rm T}$  of the card is also produced, by summing the appropriate 8 sums of 4 cells. This result is also saturated. This total sum is the input for the local  $\pi^0$  trigger.

The card produces a 21 bit output on the backplane, for the Validation Card: 8bit highest  $E_{\rm T}$  sum, 5-bit address and 8bit total  $E_{\rm T}$ . It also sends on two multiplexed LVDS links, towards the PreShower FE card for ECAL and towards the Validation Card for HCAL, the 8-bit highest  $E_{\rm T}$ sum and its 5-bit address, together with 8bits Bunch Crossing IDentifier (BCID) for synchronisation.

# 2.4 PreShower FE card

The PreShower FE card digitizes the PreShower analog signals, corrects them for pedestal, gain and for the spill-over of earlier signals, and receives and synchronises the SPD information [21]. The PreShower trigger information is obtained by comparing the PreShower signal to a threshold, producing a Yes/No output. The SPD also provides binary information. The PreShower FE card handles 64 channels, and covers two ECAL cards. For each beam crossing, the PreShower FE card receives the address of two ECAL candidates, and for each candidate, sends to the corresponding Validation Card the 4 PreShower bits and the 4 SPD bits in front of the 4 cells of the candidate [21].

As for the Calorimeter card, access to the neighbouring information is needed. The same backplane is used, transporting this time only 2 bits per cell, but there are 8 vertical neighbours instead of 4, as the card covers  $8 \times 8$  cells. The core of the processing is a  $81 \times 2$  bit wide pipe-line (as the ECAL input arrives several clock cycles after the PreShower and SPD signals are ready) and the appropriate multiplexer to extract the  $4 \times 2$  bits of the wanted cells for the proper beam crossing. A prototype to test this processing has been built and is shown on Figure 2.6.

The input is the 5-bit address produced by the ECAL card, with 8 bits of BCID to select the proper event. The output is 8 bits of data, plus the BCID for cross-checking. This is sent to the ECAL Validation Card. As already mentioned, there are two independent inputs and two outputs, each corresponding to one half of the card.

The card computes also the SPD multiplicity, by counting how many of the 64 bits have fired. This multiplicity is coded on 7 bits and is sent to the SPD Multiplicity card using the backplane lines that are used in the ECAL crate to connect to the Validation Card.

As the PreShower crates will be in the same racks as the ECAL crates, the cable length between ECAL and PreShower cards will be around 2 m.

Figure 2.6: Photograph of the prototype of the trigger part of the Preshower FE card.

# 2.5 Validation Card

The Validation Card [22] has two largely disconnected functions. First it handles the candidates from the 8 ECAL cards in the half-crate, doing a "validation" with the PreShower and SPD information, in order to produce electron, photon and  $\pi^0$  candidates. From the 8 ECAL cards it is connected to, only one candidate of each type is selected, the one with the highest  $E_{\rm T}$ . The second part handles the HCAL candidates, it adds to its energy the energy released at the same location in ECAL. Up to 4 HCAL candidates are connected to the Validation Card, and there is one output, with updated energy, for each input.

# 2.5.1 ECAL candidates

The 8-bit PreShower information is converted to a photon flag (PreShower and not SPD) and an electron flag (PreShower and SPD). A Look Up Table (LUT) is used, with 3 bits output for each flag and triple voting, to be insensitive to SEU. Using a LUT allows the requirements to be modified, in particular the way the SPD is used, and a possible veto if too many of the 4 cells have fired. The ECAL inputs are delayed by about 5 cycles to wait for the PreShower information to arrive. Then the photons and the electrons candidates are sent to a selector 'highest in eight' similar to the one on the ECAL/HCAL FE board. The result is an 8-bit  $E_{\rm T}$  candidate with a 8-bit address, the 3 new address bits keep track of which input was selected.

The local  $\pi^0$  selection is quite similar, see [23]. For the so called "local  $\pi^0$ ", where the two photons are expected on the same FE card, one uses the Sum  $E_{\rm T}$  of the FE card as measure of the  $\pi^0 E_{\rm T}$ . The highest in eight is selected. A similar validation by the PreShower and the SPD is foreseen.

The "global  $\pi^{0}$ " candidate, when the two photons are on neighbouring cards, is obtained by adding the  $E_{\rm T}$  candidates of two neighbouring cards. This is a simple addand-saturate on 8-bit, followed by a selection "highest in eight". The address is somewhat arbitrary, it will be the address of the candidate of the first card.

These four outputs of the Validation Card are obviously quite similar. There is some flexibility in the validation by the PreShower and SPD, thanks to the use of a LUT to define which combinations are valid.

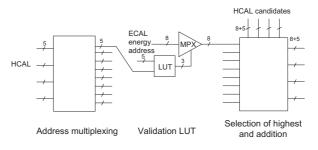

# 2.5.2 HCAL candidates

The motivation here is to add to the HCAL  $E_{\rm T}$  the ECAL  $E_{\rm T}$  in front, in order to improve the hadron energy estimate. Instead of bringing the ECAL information to the HCAL candidates, the HCAL candidates are sent to the ECAL crate. This reduces the number of connections between the two detectors by a factor 2.5, at the price of

some duplicate candidates [22]. As a side effect, the selection of the best version of the duplicated candidates has to be done in the Selection Crate.

The first processing is a time alignment, to handle the same event in ECAL and HCAL. Then the processing is in three steps:

- For each ECAL card, a single HCAL card can match. This is not the same pattern for each Validation Card, and is therefore performed by a programmable multiplexer.

- The ECAL and HCAL address are compared using a LUT, 5+5 bits input, 3 bits output for triple voting and SEU immunity. This indicates if the ECAL candidate is "in front" of the HCAL candidate. Eight such LUT are needed, one per ECAL card.

- As several ECAL candidates can be in front of an HCAL candidate, one selects for each HCAL card the matched ECAL candidate with the highest  $E_{\rm T}$ and then adds its  $E_{\rm T}$  to the HCAL  $E_{\rm T}$  to obtain an updated HCAL candidate, which is sent to the selection crate.

This section of the Validation Card is shown in Figure 2.7. The internal memory of the PGA is used as a LUT.

Figure 2.7: HCAL validation logic.

All outputs of the Validation Card are optical links (32 bits at 40 MHz) towards the Selection Crate. The information on each link is similar: 8-bit  $E_{\rm T}$  of the candidate, 8-bit address and 8-bits for BCID. In the remaining 8-bits we intend to send a "cable number" field, allowing cabling checks.

# 2.6 SPD Multiplicity

In the PreShower crates, a card is located in the same slot as the Validation Card in the ECAL crate. This card receives via the backplane 8 SPD multiplicity values computed by 8 PreShower FE cards. It adds these 8 numbers and outputs the sum on an optical fiber, in a similar format as the ECAL Validation Card, using the two 8-bits address and  $E_{\rm T}$  field described previously to transport the 10-bit multiplicity value. This will allow the computing the total SPD multiplicity in the Selection Crate.

# 2.7 Backplane and links

There is a large data flow between various boards, all at a frequency of 40 MHz. The problem has been simplified as much as possible by using a dedicated backplane [24] to implement most of the links. As shown in Figure 2.5, 9 of the 13 links between FE boards are via the backplane. The link between the FE board and the Validation Card is also via the backplane. They use multiplexed LVDS signals, where 4 pairs allow the transmission of 21 bits at 40 MHz. The same backplane is used for PreShower, ECAL and HCAL crates, the cost of any unused connection being overwhelmed by the simplification in debugging and maintenance.

The first part of the backplane, containing the power lines and the distribution of the timing and control signals, is shown on Figure 2.8.

Links between crates are implemented with multiplexed LVDS signals. Using Cat-5 cables, safe transmission is possible for lengths up to 20 m [24]. Most of the connections are between crates in

Figure 2.8: Photograph of the power backplane.

the same rack, either inside ECAL, inside PreShower or between ECAL and PreShower. Longer connections exist between HCAL and ECAL. The crates are on two platforms on top of the calorimeters, which move independently when the detector is opened. The cable length should allow for opening without decabling, 10 m should be enough, which is safe for the quality of the link.

# 2.8 Selection Crate

As can be seen in Figure 2.3, the Selection Crate [25] handles a lot of inputs, 4 times 28 optical links for electromagnetic candidates, and 80 links for HCAL. It is made in two parts. One handles the electromagnetic candidates, essentially selecting the one with the highest  $E_{\rm T}$  for each type, and the second part handles the HCAL candidates, in a slightly more complex way. One should note that the Selection Crate is in the barracks, and hence is not submitted to radiation or SEU problems, which allows the use of FPGAs.

# 2.8.1 Electromagnetic Candidates

Upon reception, the processing (after time alignment) is to select the highest  $E_{\rm T}$  of the 28 inputs, by successive binary comparison. The address of the final candidate, 8-bit received and 5-bits from this selection, is converted to the official calorimeter cell identifier on 14 bits, using a LUT. The resulting candidate, 8-bit  $E_{\rm T}$  and 14-bit address, plus 8-bit BCID and a 2-bit status, is

sent to the L0 Decision Unit (L0DU). The 4 types of candidates (electron, photon, local  $\pi^0$  and global  $\pi^0$ ) are handled exactly the same way.

# 2.8.2 SPD multiplicity

The functionality is similar: the 16 inputs are time aligned, then the 10-bit numbers are added without saturation, by a cascade of pair addition, and the result on 13 bits is sent to the L0 Decision Unit. The same hardware board can be used, with a different code for the processing FPGA. There is no address to send, and the 14-bit address field is used to send the result to the L0DU.

# 2.8.3 HCAL

The processing is similar, with two extra steps to eliminate duplicates and to obtain also the sum over the whole calorimeter. After time alignment, the duplicates are removed: 30 HCAL cards have their candidates sent to two Validation Cards, and thus to the Selection Crate. For each pair of inputs coming from the same HCAL card, only the one with the highest  $E_{\rm T}$  is kept. Then, the HCAL card with the highest  $E_{\rm T}$ is selected as in the ECAL case.

The sum of the 50 cards is performed, without saturating the result. This sum will be used to detect a minimal activity in the detector, with a threshold at a few GeV. It may also be used to detect dirty events, produced by piled-up interactions, and hence saturation at 5 GeV  $E_{\rm T}$  is not allowed.

As 80 optical links cannot be received on a single board, the HCAL processing is performed on 3 boards, receiving respectively 28, 28 and 24 links. A simple connection allows one of the boards to perform the final selection for the highest  $E_{\rm T}$  and total sum, based on the 3 intermediate results.

The output of the HCAL selection is then the highest  $E_{\rm T}$  HCAL candidate, with the same cell identifier processing and same final format as for the ECAL candidates, and the Total  $E_{\rm T}$  in HCAL. As there is no address in this case, the 14-bit address field is used to send the value, as for the SPD multiplicity.

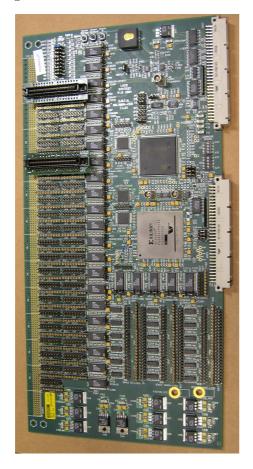

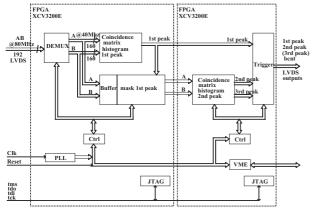

# 2.8.4 Implementation

Despite the diverse functionalities, the whole Selection Crate can be implemented with a single type of board, where some small part (inter-card connection, second output) is unused in the ECAL case. The boards will be equipped with three parallel 12-channel optical receivers connected to 28 low power consumption deserializers TLK2501 from Texas Instruments. After deserialization, the 28 16-bit words are demultiplexed 2:1 to 32 bits and synchronized to the TTC clock by 28 small FPGAs.

The synchronisation mechanism has been already successfully tested. It simply requires writing the data into a FIFO with the deserializer clock while reading it with the TTC clock.

The processing itself is reasonably simple, but requires a large number of connections. A single  $FPGA^1$  with 812 I/O pins can do the job.

The 28 inputs of each board are saved and transmitted to the DAQ after the Level-0 decision, to enable a detailed monitoring of the correct behaviour of the system. Like for most sub-systems in LHCb the TELL1-board [16] is used for this purpose. A simple zero suppression, removing candidates with exactly zero  $E_{\rm T}$ , gives an acceptable event size of around 500 bytes for final readout. The Selection Crate information is also made available to the Level-1 processors, as explained in Chapter 6, with a threshold at 1 GeV to reduce the average data size to 70 bytes.

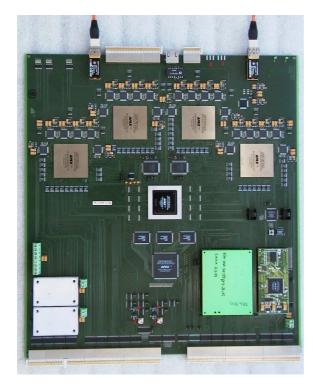

A prototype of the processing part has been built and tested in 2002, and is shown

<sup>&</sup>lt;sup>1</sup>For example the FPGA XILINX XC2VP50-5FF 1148C

in Figure 2.9.

Figure 2.9: Photograph of the prototype of the Selection Board.

# 2.9 Latency

The latency can be analysed in terms of internal processing time, transport time and delays for synchronisation of the inputs.

- FE boards: Seven cycles. On the ECAL and HCAL FE boards, the processing is 1 cycle for converting the ADC to  $E_{\rm T}$  and 3 cycles for the computation of the 2 × 2 sums and the selection of the highest. Time alignment of the inputs will require another 3 cycles.

- Validation Card: Eight cycles: The processing in the PreShower FE card adds to the latency: the ECAL candidate has to be received (2 cycles),

the answer extracted (1 cycle) and then transmitted (2 cycles) to the Validation Card. Five cycles are thus required for these operations. The ECAL input to the Validation Card have to wait during that time. Processing in the Validation Card is quite simple, and will take 3 cycles. The HCAL processing will take the same time, and the slower transmission (due to longer cables between HCAL and ECAL crates) is smaller than the latency due to the wait for the PreShower.

• Processing time in the Selection Crate takes 9 cycles for ECAL candidates, and 14 for HCAL candidates. Two cycles are requested to de-serialize and synchronize the data fluxes to the TTC clock. Data processing on the board takes 5 clock cycles. It takes two cycles to transfer data to the L0DU or to send them to the hadron master. Three more cycles have to be added to the previous 9 for the final hadron selection, and another two cycles to the hadron data transfer to the L0DU.

The total latency, not counting the optical transmission from the calorimeter platform to the barracks, is then below 30 cycles, or 750 ns, well within the budget, as discussed in Chapter 5.

# 2.10 Debugging and Monitoring

To monitor the correct behaviour of the system, the inputs are logged with the data: The 8-bits  $E_{\rm T}$  of each ECAL and HCAL cell, and the PreShower and SPD bits of each cell, are read out. As mentioned earlier, the inputs of the Selection Crate are also logged with the event, allowing checking that they correspond to what is expected from the individual cell inputs. The result of the Selection Crate is logged by the L0 Decision Unit, which permits to monitor the Selection Crate. Local tests of the FE cards and of the Validation Card are foreseen, with inputs from a memory writable by ECS and results logged in a FIFO readable by ECS. This will allow the debugging of the system and in-situ checks outside data taking periods.

# Chapter 3 Level-0 Muon Trigger

The muon system has been designed to look for muons with a high transverse momentum: a typical signature of a b-hadron decay.

An overview of the muon system is given first followed by the description of the L0 muon trigger implementation, its performance as a function of various running conditions and its technical design.

# 3.1 Overview of the muon system

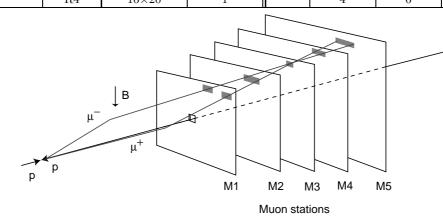

The muon detector [6] consists of five muon stations interleaved with muon filters (Figure 1.1). The filter is comprised of the electromagnetic and hadronic calorimeters and three iron absorbers. Stations M2-M3 are devoted to the muon track finding while stations M4-M5 confirm the muon identification. The first station M1 is placed in front of the calorimeter and plays an important role for the transverse-momentum measurement of the muon track. Station M1 improves the transverse momentum resolution by about 30%.

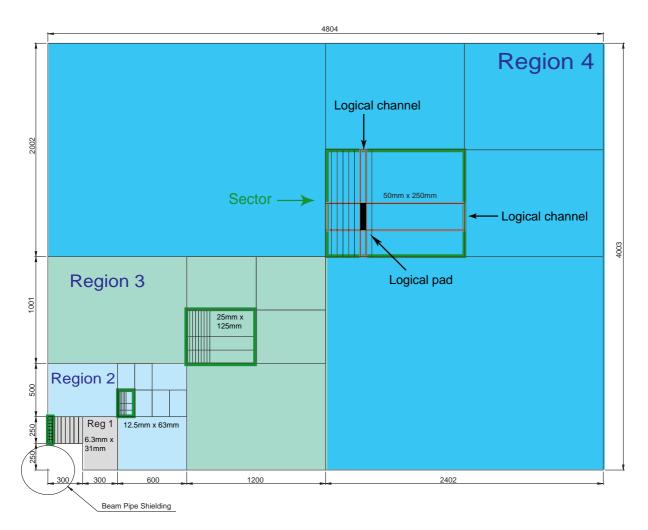

Each station has two detector layers with independent readout. A detector layer contains two gaps in station M2-M5. To achieve the high detection efficiency of 99% per station and to ensure redundancy, the signal of corresponding physical channels in the two gaps and two layers are logically OR-ed on the chamber to form a logical channel. The total number of physical channels in the system is about 120,000 while the number of logical channels is 25,920.

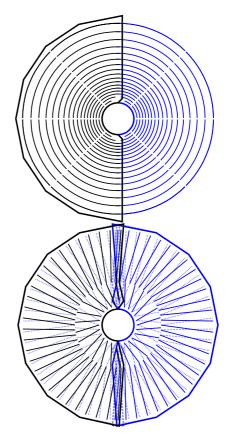

Each station is subdivided into four regions with different logical-pad dimensions, as shown in Figure 3.1. Region and pad sizes scale by a factor two from one region to the next. The logical layout in the five muon stations is projective in y to the interaction point. It is also projective in xwhen the bending in the horizontal plane introduced by the magnetic field is ignored.

The logical pad dimensions are summarized in Table 3.1. Compared to M1 the pad size along the x axis is twice smaller for M2-M3 and twice coarser for M4-M5.

Pads are obtained by the crossing of horizontal and vertical strips wherever possible. Strips are employed in stations M2– M5 while station M1 and region 1 (R1) of stations M4-M5 are equipped with pads.

Strips allow a reduction in the number of logical channels to be transferred to the muon trigger. The processor receives 25,920 bits every 25 ns forming 55,296 logical pads by crossing strips.

Each region is subdivided into *sectors* as shown in Figure 3.1. They are defined by the size of the horizontal and vertical strips and match the dimension of underlying chambers.

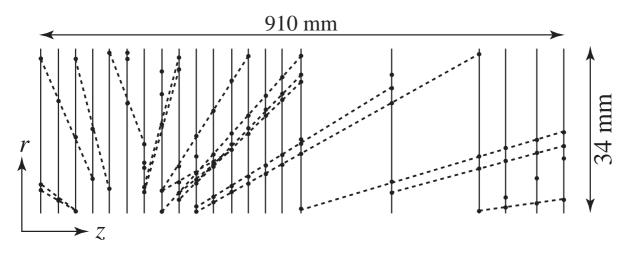

The L0 muon trigger looks for muon tracks with a large transverse momentum,  $p_{\rm T}$ . The track finding is performed on the logical pad layout. It searches for hits defining a straight line through the five muon stations and pointing towards the interaction point (Figure 3.2). The position of a track in the first two stations allows the determination of its  $p_{\rm T}$ .

Figure 3.1: Front view of one quadrant of muon station 2, showing the dimensions of the regions. Inside each region a sector is shown. It is defined by the size of the horizontal and vertical strips. The intersection of the horizontal and vertical strips, corresponding to the logical channels, are logical pads. The region and channel dimensions scale by a factor two from one region to the next.

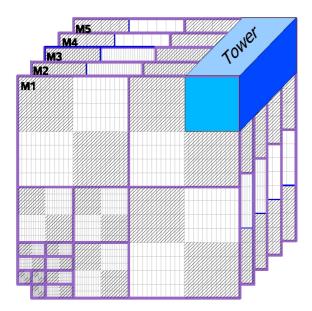

To simplify the processing and to hide the complex layout of stations, we subdivide the muon detector into 192 towers pointing to the interaction point as shown in Figure 3.3. A tower contains logical pads with the same layout: 48 pads from M1,  $2 \times 96$  pads from M2 and M3,  $2 \times 24$  pads from M4 and M5. Therefore the same algorithm can be executed in each tower, the key element of the trigger processor. Each tower is connected to a Processing Unit (PU).

All logical channels belonging to a tower are sent to a PU using six high speed optical links. The intersection between a tower and a station maps a sector. The corresponding logical channels are transported on a dedicated optical link to ease the connectivity between the muon detector and the trigger and the data distribution within a processor.

The data flow, however, is more complex for stations M2-M3 region R1 and R2. In region R1, a sector is shared by two towers while in region R2, a tower maps to two sectors (Figure 3.1 and Figure 3.3). The first case requires additional exchange of logical channels between PUs while the second one

| Station    | Region | Pad size         | links     | logical channels/link |          |          |       |

|------------|--------|------------------|-----------|-----------------------|----------|----------|-------|

|            |        | at M1 $[cm^2]$   | per tower | pads                  | H-strips | V-strips | Total |

| M1         | R1     | $1 \times 2.5$   | 2         | 24                    | _        | _        | 24    |

|            | R2     | $2 \times 5$     | 2         | 24                    | —        | —        | 24    |

|            | R3     | $4 \times 10$    | 2         | 24                    | —        | —        | 24    |

|            | R4     | $8 \times 20$    | 2         | 24                    | —        | —        | 24    |

| M2  or  M3 | R1     | $0.5 \times 2.5$ | 1         | -                     | 16       | 12       | 28    |

|            | R2     | $1 \times 5$     | 2         | -                     | 4        | 12       | 16    |

|            | R3     | $2 \times 10$    | 1         | -                     | 4        | 24       | 28    |

|            | R4     | $4 \times 20$    | 1         | -                     | 4        | 24       | 28    |

| M4  or  M5 | R1     | $2 \times 2.5$   | 1         | 24                    | _        | _        | 24    |

|            | R2     | $4 \times 5$     | 1         | -                     | 8        | 6        | 14    |

|            | R3     | $8 \times 10$    | 1         | -                     | 4        | 6        | 10    |

|            | R4     | $16 \times 20$   | 1         | _                     | 4        | 6        | 10    |

Table 3.1: The logical pad size in the four regions of each station projected to M1, and the number of optical links per tower and their content in term of logical channels.

Figure 3.2: Track finding by the muon trigger. For each logical-pad hit in M3, hits are sought in M2, M4 and M5, in a field of interest (highlighted) around a line projecting to the interaction region. When hits are found in the four stations, an extrapolation to M1 is made from the hits in M2 and M3, and the M1 hit closest the extrapolation point is selected. The track direction indicated by the hits in M1 and M2 is used in the  $p_{\rm T}$  measurement for the trigger, assuming a particle from the interaction point and a single kick from the magnet. In the example shown,  $\mu^+$  and  $\mu^-$  cross the same pad in M3.

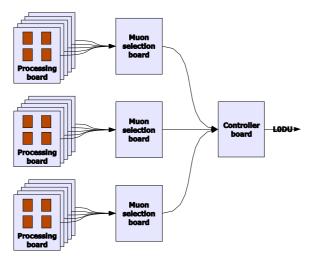

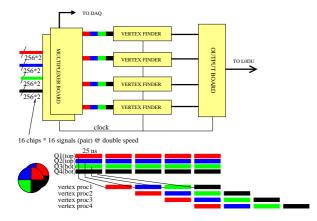

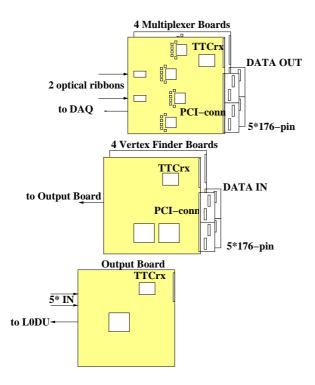

requires eight optical links instead of six, as shown in Table 3.1. A unique *processing board* containing four PUs deals with all cases by programming differently the FP-GAs and by grouping two interconnected PUs in region R2.

The L0 muon trigger is implemented with the four quadrants of the muon system treated independently.

# 3.2 Trigger implementation

The L0 muon trigger algorithm and its implementation are described in detail in LHCb notes [26, 27].

The logical channels are transported from the Front-End electronics to the muon trigger through a total of 148 high speed optical ribbons of 12 fibres each.

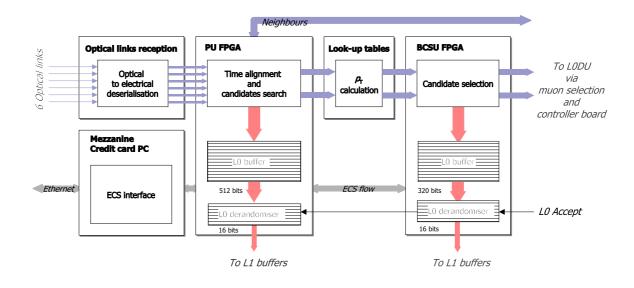

Track finding in each region of a quadrant is performed by 12 PUs, arranged on processing boards in groups of four for regions R1, R3 and R4, and in pairs for region R2.

A PU collects data from the five muon stations for pads and strips forming a tower, and also receives information from neigh-

Figure 3.3: A quadrant of the muon system showing the tower layout. Thick lines delimit the fraction of the system analyzed by a processing board. In this view the interaction point is shifted to  $\infty$ .

bouring towers, although they are in another region, to avoid inefficiency on boundaries. Logical channels are merged when they are transferred from region  $R_i$  to  $R_{i+1}$ . In the opposite direction, logical channels are transported as is and replicated in four channels to match the granularity of the receiving PU. Therefore all data collected in a tower have the same granularity.

Track finding in a PU starts from the 96 logical pads defined by the intersections of horizontal and vertical strips representing the unit's input from station M3. The track search is performed in parallel for all pads.

For each logical-pad hit in M3 (track seed), the straight line passing through the hit and the interaction point is extrapolated to M2, M4 and M5. Hits are looked for in these stations in search windows, termed Fields Of Interest (FOI), approximately centered on the straight-line extrapolation. FOIs are open along the x-axis for all stations and along the y-axis only for stations M4 and M5. The size of the FOI depends on the station considered, the level of background, and the minimum-bias retention required. When at least one hit is found inside the FOI for each of the stations M2, M4 and M5, a muon track is flagged and the pad hit in M2 closest to the extrapolation from M3 is selected for subsequent use.

The track position in station M1 is determined by making a straight-line extrapolation from M3 and M2, and identifying in the M1 FOI the pad hit closest to the extrapolation point.

Since the logical layout is projective, there is a one-to-one mapping from pads in M3 to pads in M2, M4 and M5. There is also a one-to-one mapping from pairs of pads in M2 and M3 to pads in M1. This allows the track-finding algorithm to be implemented using only logical operations.

Once track finding is completed, an evaluation of  $p_{\rm T}$  is performed for muon tracks. The  $p_{\rm T}$  is determined from the track hits in M1 and M2, using look-up tables. The number of muon tracks per PU is limited to two. When more candidates are found, they are discarded and the PU gives an overflow.

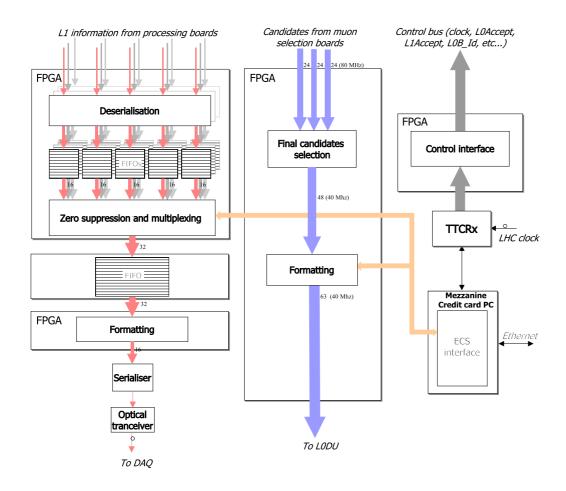

The two muon tracks of highest  $p_{\rm T}$  are selected first for each processor board, and then for each quadrant of the muon system. The information for up to eight selected tracks is transmitted to the L0 Decision Unit.

# **3.3** Trigger performance

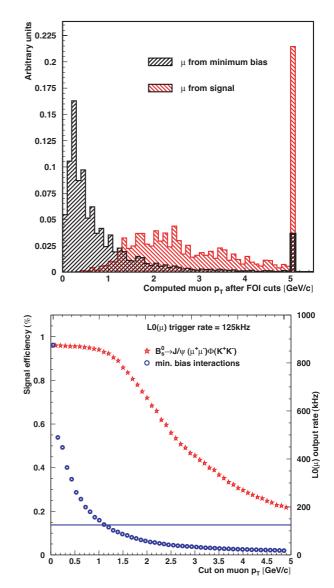

The L0 muon trigger is designed for a minimum-bias output rate of around 200 kHz<sup>1</sup>. This is obtained by optimizing the parameters of the algorithm given by the horizontal and vertical dimensions of the FOI and by the cut on  $p_{\rm T}$ . Decreasing the dimension of the FOI and increasing the cut on  $p_{\rm T}$  reduces the output rate. The size of the largest FOIs is an important

<sup>&</sup>lt;sup>1</sup>About 2/3 of the output rate is devoted to a single muon trigger and 1/3 to a di-muon trigger.

parameter for the processor since they define the number of data exchanged between PUs. This number determines the dimension of busses connecting PUs. The largest  $FOI^2$  are given in Table 3.2.

Table 3.2: The maximum size of the FOI along the x and y coordinates. It is expressed in terms of pads with respect to the pad lying on the straight line passing through the hit in M3 and the interaction point. A FOI of  $\pm 3$  corresponds to a total width of 7 pads.

|   | M1      | M2      | M4      | M5      |

|---|---------|---------|---------|---------|

| x | $\pm 3$ | $\pm 5$ | $\pm 3$ | $\pm 3$ |

| y | -       | -       | $\pm 1$ | $\pm 1$ |

Figure 3.4 shows the transverse momentum determined for L0 muon candidates found in minimum-bias and  $B_s^0 \rightarrow J/\psi\phi$ samples when the FOI are optimized for an output rate of 125 kHz (single muon trigger). The corresponding trigger efficiency is shown in the bottom plot as a function of a cut on  $p_T$ . The origin of the muon candidates in the accepted minimum-bias events is given in Table 3.3. They mainly come from pion and kaon decays in flight. The resolution on the transverse momentum was measured to be 20% for muons coming from a b-quark.

Table 3.3: Origin of candidate triggering minimumbias events when the rate for the single muon trigger is fixed to 125 kHz. The table includes hadron punchthrough.

|                                  | [%]  |

|----------------------------------|------|

| b-hadron                         | 2.2  |

| c-hadron                         | 3.3  |

| Pion                             | 63.2 |

| Kaon                             | 28.5 |

| Other particles (p, n, $\tau$ ,) | 1.1  |

| Ghost tracks                     | 1.7  |

<sup>&</sup>lt;sup>2</sup>They were obtained by optimizing the trigger efficiency while minimizing the size of the FOI. Studies were performed as a function of the output rate and running conditions [28, 29].

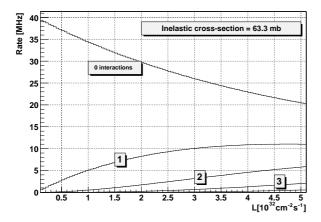

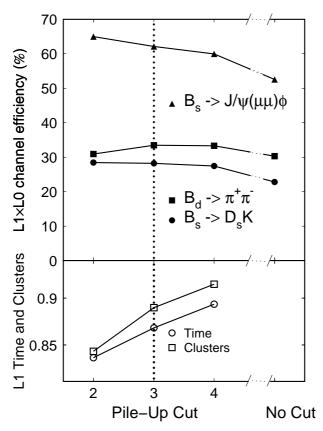

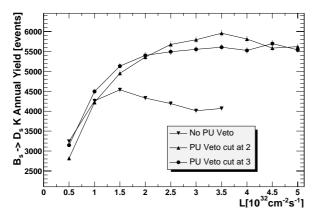

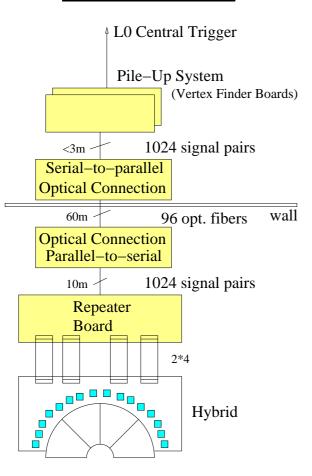

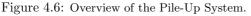

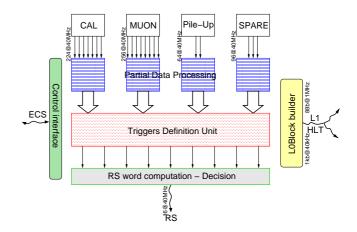

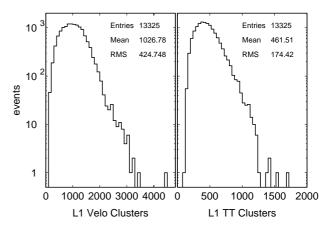

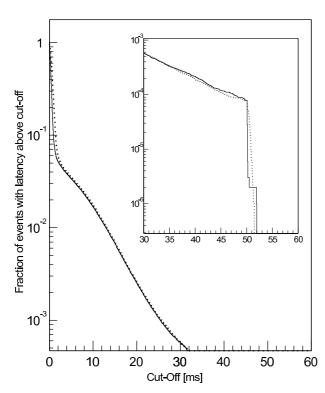

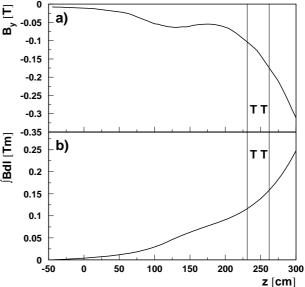

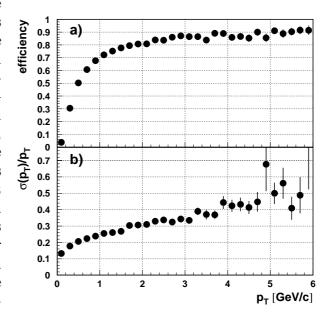

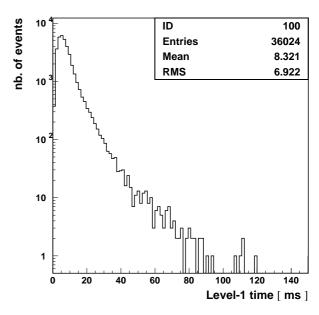

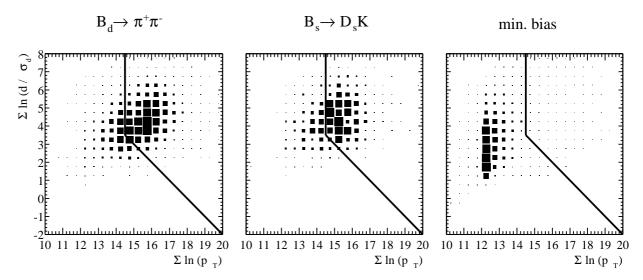

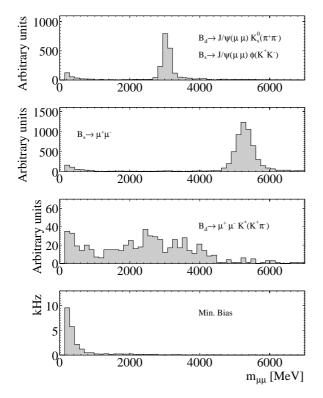

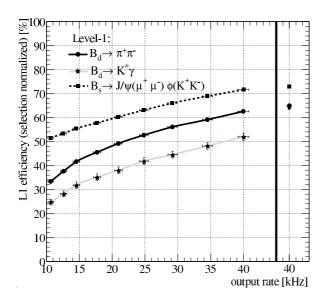

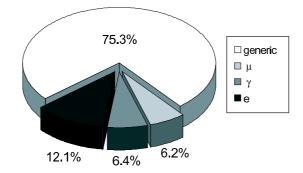

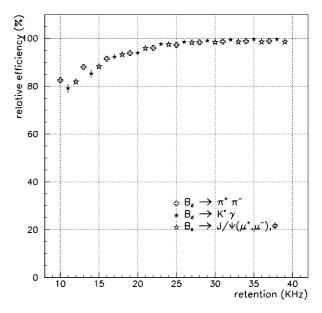

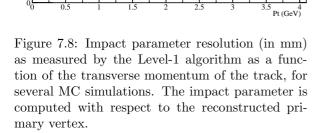

Figure 3.4: Top: reconstructed transverse momentum for minimum-bias and for  $B_s^0 \rightarrow J/\psi\phi$  events. It is encoded on 8 bits and saturated to 5 GeV/c. Both samples are normalized to unity. Bottom: the trigger efficiencies for minimum-bias and for  $B_s^0 \rightarrow J/\psi\phi$  events as a function of the cut on  $p_T$ . In both plots the dimensions of the FOI are optimized for an output rate of 125 kHz (single muon trigger). The  $B_s^0 \rightarrow J/\psi\phi$  events are selected by offline reconstruction.