# MICROARCHITECTURAL TECHNIQUES TO REDUCE ENERGY CONSUMPTION IN THE MEMORY HIERARCHY

A Dissertation Presented to The Academic Faculty

By

Mrinmoy Ghosh

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

in

Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology May 2009

# MICROARCHITECTURAL TECHNIQUES TO REDUCE ENERGY CONSUMPTION IN THE MEMORY HIERARCHY

#### Approved by:

Dr. Hsien-Hsin S. Lee, Advisor Associate Professor, School of ECE Georgia Institute of Technology

Dr. Sudhakar Yalamanchili Professor, School of ECE Georgia Institute of Technology

Dr. Saibal Mukhopadhyay Assistant Professor, School of ECE Georgia Institute of Technology Dr. Abhijit Chatterjee

Professor, School of ECE

Georgia Institute of Technology

Dr. Santosh Pande

Associate Professor, College of Computing

Georgia Institute of Technology

Date Approved: April 2, 2009

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without the help of many people over the past few years. First of all, I would like to thank my advisor, Dr. Hsien-Hsin S. Lee, for his motivation, excellent technical supervision, and support. I would also like to thank my committee members, Dr. Sudhakar Yalamanchili, Dr. Saibal Mukhopadhyay, Dr. Abhijit Chatterjee, and Dr. Santosh Pande, for their time and encouragement.

I would like to express gratitude for the valuable technical contributions and advice from the past and present student members of MARS: Dr. Weidong Shi, Dr. Taeweon Suh, Dr. Chinnakrishnan Ballapuram, Dr. Joshua Fryman, Fayez Mohamood, Dong Hyuk Woo, Dean Lewis, Richard Yoo, Ahmad Sharif, Eric Fontaine, Vikas Vasisht and Nak Hee Seong.

I am grateful to Emre Ozer, Stuart Biles and Simon Ford of ARM Inc. for providing assistance and guidance during the summer internship in 2005. A lot of credit goes to all my friends, Atri Dutta, Biswajit Mitra, Jacob Minz, Bevin G. Perumana, Prabir Saha, Saikat Sarkar, Payel Paul, Padmanava Sen, Arup Polley, Arindam Basu, Tapobrata Bandyopadhyay, Bhaskar Saha, Rahul Bhatia, Rishi Ranjan, Subrata Govil, Rajarshi and Rachana Mukhopadhyay, Nand and Neha Jha, Koushik and Priya Kundu, and many more for their invaluable assistance during the times of need and making my stay at Atlanta so memorable.

Finally, no person can be successful without the love and support of his family. My deepest gratitude is reserved for my parents, Shri Manik Chandra Ghosh and Smt. Bani Ghosh, who with their love, blessing, and sacrifices have made this possible.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS iv |                                                                       |     |  |

|--------------------|-----------------------------------------------------------------------|-----|--|

| LIST OF            | F TABLES viii                                                         |     |  |

| LIST OF            | F FIGURES ix                                                          |     |  |

| SUMMA              | ARY xii                                                               |     |  |

| CHAPTI             | ER 1 INTRODUCTION                                                     |     |  |

| 1.1                | Motivation                                                            |     |  |

| 1.2                | Thesis Statement and Contributions                                    |     |  |

| CHAPTI             | <b>ER 2 RELATED WORK</b>                                              |     |  |

| 2.1                | Methods of Reducing DRAM Power                                        |     |  |

| 2.2                | Techniques for Reducing Dynamic Power for Caches                      |     |  |

| 2.3                | Leakage Reduction Techniques for Caches                               |     |  |

| 2.4                | Microarchitectural Energy Reduction Techniques using Bloom filters 14 |     |  |

| 2.5                | Way Prediction and Estimation Techniques                              |     |  |

| СНАРТІ             | ER 3 REDUCING DRAM REFRESH POWER WITH SMART REFRESH                   | 17  |  |

| 3.1                | Redundancy in DRAM refresh                                            | 1 / |  |

| 3.1                | DRAM Refresh Techniques                                               |     |  |

| 3.3                | Smart Refresh                                                         |     |  |

| 3.3                | 3.3.1 Basic Operation                                                 |     |  |

|                    | 3.3.2 Staggered Countdown                                             |     |  |

|                    | 3.3.3 Smart Refresh Correctness                                       |     |  |

|                    | 3.3.4 Optimality of Smart Refresh                                     |     |  |

|                    | 3.3.5 Smart Refresh Technique for 3D DRAM                             |     |  |

|                    | 3.3.6 Smart Refresh for embedded DRAMs                                |     |  |

|                    | 3.3.7 Disabling Smart Refresh                                         |     |  |

|                    | 3.3.8 Area Overhead                                                   |     |  |

| 3.4                | Smart Refresh Implementation                                          |     |  |

| 3.5                | Evaluation Methodology                                                |     |  |

| 3.6                | Experimental Results                                                  |     |  |

| 5.0                | 3.6.1 Conventional DRAM                                               |     |  |

|                    | 3.6.2 3D Die-stacked DRAM                                             |     |  |

|                    | 3.6.3 Performance Implication                                         |     |  |

| 3.7                | Summary                                                               |     |  |

| 3.1                | Summary                                                               |     |  |

| CHAPTI             | CHAPTER 4 REDUCING LEAKAGE ENERGY IN CACHES FOR MULTI-                |     |  |

|                    | PROCESSOR SYSTEMS                                                     |     |  |

| 4.1                | Multi-Level Inclusion and Cache Coherence                             |     |  |

|                    | 4.1.1 Multi-Level Inclusion 47                                        |     |  |

|        | 4.1.2 Leakage Energy Reduction Schemes for Coherent Caches        | . 49  |

|--------|-------------------------------------------------------------------|-------|

| 4.2    | Applying Virtual-Exclusion                                        |       |

|        | 4.2.1 Generic Virtual-Exclusion Policy                            | . 50  |

|        | 4.2.2 Cache-Decay and Hybrid Virtual-Exclusion Policies           | . 55  |

|        | 4.2.3 Virtual-Exclusion in Multicore Processors                   |       |

| 4.3    | Simulation Framework for Virtual-Exclusion                        | . 59  |

| 4.4    | Energy Savings with Virtual-Exclusion                             | . 61  |

|        | 4.4.1 SMP Analysis                                                | . 62  |

|        | 4.4.2 Multicore Processors Analysis                               |       |

|        | 4.4.3 Performance Impact                                          |       |

| 4.5    | Summary                                                           | . 66  |

| CHAPTI |                                                                   |       |

|        | AND WAY ESTIMATION                                                |       |

| 5.1    | Energy Management for ever larger caches                          |       |

| 5.2    | Bloom Filters                                                     |       |

| 5.3    | Segmented Bloom Filter Design                                     |       |

| 5.4    | Processor Energy Management with Segmented Counting Bloom Filters |       |

| 5.5    | Way Guard Mechanism                                               |       |

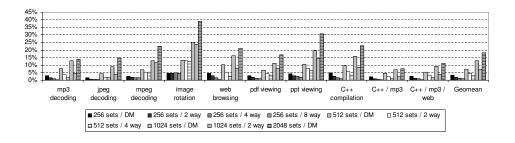

| 5.6    | Experimental Results                                              |       |

|        | 5.6.1 Experimental Framework and Benchmarks                       |       |

|        | 5.6.2 Energy Modeling                                             | . 83  |

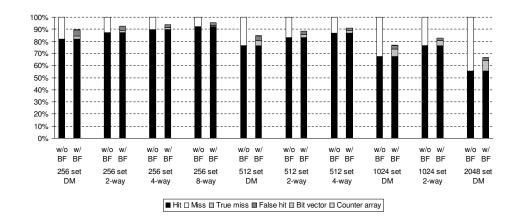

|        | 5.6.3 Cache and Bloom Filter Statistics                           |       |

|        | 5.6.4 Energy Consumption Results for Early Cache Miss Detection   |       |

|        | 5.6.5 Energy Savings for Way Guard                                |       |

| 5.7    | Summary                                                           | . 95  |

| CHAPTI |                                                                   |       |

|        | USING BLOOM FILTERS TO DETECT SYNONYMS                            |       |

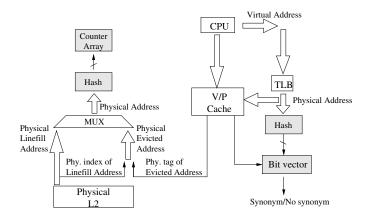

| 6.1    | Redundancy in Synonym Lookup in Virtual Caches                    |       |

|        | 6.1.1 Synonym Lookup and Tag Energy                               |       |

| 6.2    | Synergy: Early Synonym Detection with a Decoupled Bloom Filter    |       |

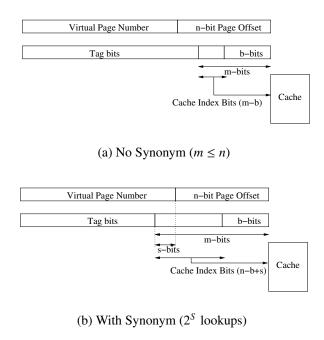

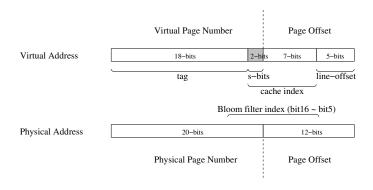

|        | 6.2.1 Virtually-indexed Physically-tagged Caches                  |       |

|        | 6.2.2 Virtually-indexed Virtually-tagged Caches                   |       |

| 6.3    | Counter Overflow Issues                                           |       |

|        | 6.3.1 Probability of Overflow                                     |       |

|        | 6.3.2 Simple Solutions to the Overflow Problem                    |       |

| 6.4    | Overflow-free Bloom Filter                                        |       |

| 6.5    | Experimental Results                                              |       |

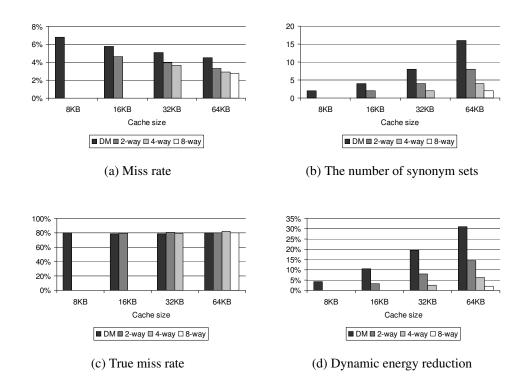

|        | 6.5.1 Simulation Environment                                      |       |

|        | 6.5.2 Results                                                     |       |

| 6.6    | Summary                                                           | . 125 |

| <b>CHAPTI</b> | ER 7 REDUCING DYNAMIC ENERGY CONSUMPTION OF CACHES              |

|---------------|-----------------------------------------------------------------|

|               | WITH COOLPRESSION                                               |

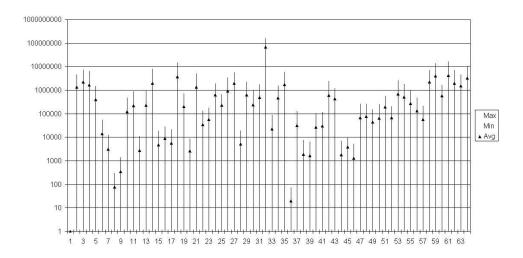

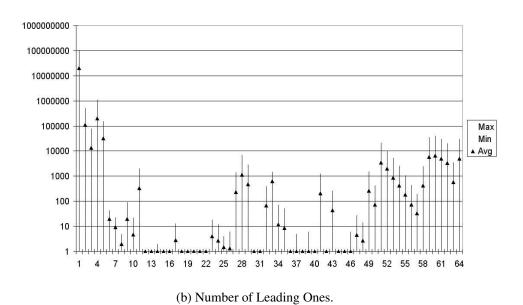

| 7.1           | Redundant Leading Zeroes and Ones                               |

| 7.2           | CoolPression Cache                                              |

|               | 7.2.1 Dynamic Zero Compression (DZC)                            |

|               | 7.2.2 CoolCount                                                 |

|               | 7.2.3 Hybrid Compression Scheme                                 |

| 7.3           | CoolPression Implementation                                     |

|               | 7.3.1 Overheads                                                 |

| 7.4           | Energy Savings and Performance Implications of Coolpression 135 |

| 7.5           | Summary                                                         |

| CHAPTI        | ER 8 CONCLUSIONS                                                |

| 8.1           | Summary of Contributions                                        |

| 8.2           | Future Work                                                     |

| REFERE        | ENCES                                                           |

# LIST OF TABLES

| Table 1  | DRAM Module and L2 Cache Configuration                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------|

| Table 2  | 3D DRAM Cache Configuration                                                                                                     |

| Table 3  | Parameter Values Used in Bus Energy Calculation                                                                                 |

| Table 4  | Architectural Parameters                                                                                                        |

| Table 5  | Spec2000 Benchmark used for simulations 61                                                                                      |

| Table 6  | Architectural assumption                                                                                                        |

| Table 7  | Architectural Configuration                                                                                                     |

| Table 8  | Abbreviations and their descriptions                                                                                            |

| Table 9  | Cache miss and miss filtering rates for configuration 1                                                                         |

| Table 10 | Cache miss and miss filtering rates for configuration 2                                                                         |

| Table 11 | L2 cache energy savings                                                                                                         |

| Table 12 | $P[Z_{n_c}^j > z] \dots $ |

| Table 13 | L1 data cache configuration                                                                                                     |

| Table 14 | 3-bit Counter vs. Overflow-free Counter                                                                                         |

# LIST OF FIGURES

| Figure 1  | Best Case for Smart Refresh                                                                 | 18 |

|-----------|---------------------------------------------------------------------------------------------|----|

| Figure 2  | Down-counting Timeout counters                                                              | 23 |

| Figure 3  | Countdown counters divided into logical segments and countdown is staggered                 | 24 |

| Figure 4  | Smart Refresh Correctness                                                                   | 26 |

| Figure 5  | Smart Refresh Control Schematic                                                             | 31 |

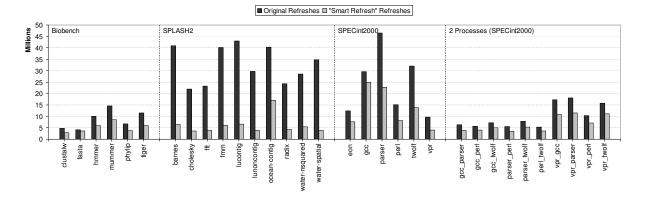

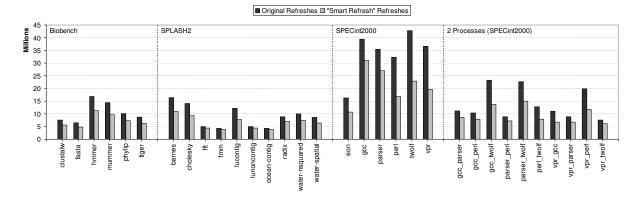

| Figure 6  | Comparison of Number of Refreshes per second for a 2GB DRAM                                 | 37 |

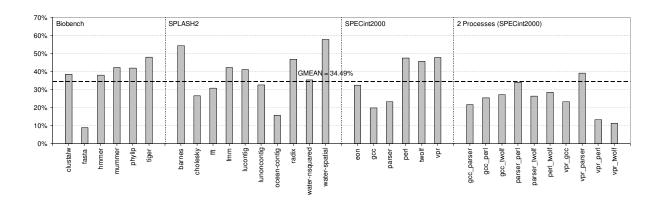

| Figure 7  | Relative Refresh Energy Savings for a 2GB DRAM                                              | 38 |

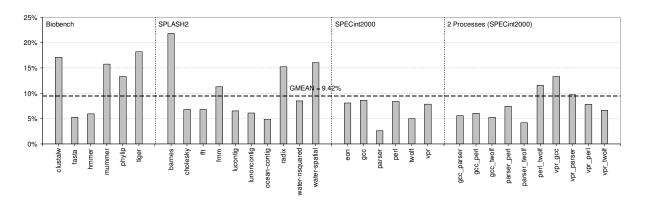

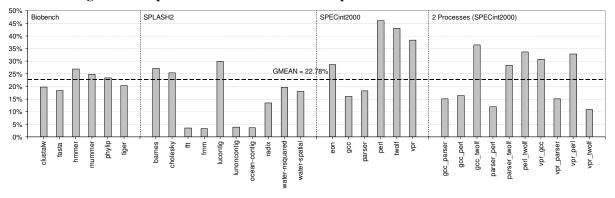

| Figure 8  | Relative Total Energy Savings for a 2GB DRAM                                                | 38 |

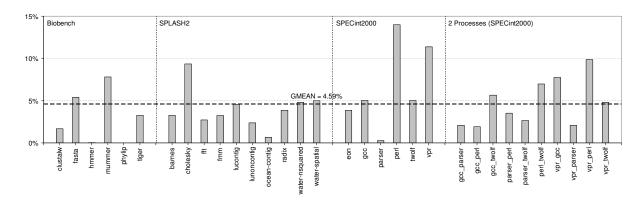

| Figure 9  | Comparison of Number of Refreshes per second for a 4GB DRAM                                 | 39 |

| Figure 10 | Relative Refresh Energy Savings for a 4GB DRAM                                              | 39 |

| Figure 11 | Relative Total Energy Savings for a 4GB DRAM                                                | 40 |

| Figure 12 | Comparison of Number of Refreshes for a 64MB 3D DRAM Cache with 64ms refresh rate           | 41 |

| Figure 13 | Relative Refresh Energy Savings for a 64MB 3D DRAM Cache with 64ms refresh rate             | 41 |

| Figure 14 | Relative Total Energy Savings for a 64MB 3D DRAM Cache with 64ms refresh rate               | 41 |

| Figure 15 | Comparison of Number of Refreshes for a 64MB 3D DRAM Cache with 32ms refresh rate           | 43 |

| Figure 16 | Relative Refresh Energy Savings for a 64MB 3D DRAM Cache with 32ms refresh rate             | 43 |

| Figure 17 | Relative Total Energy Savings for a 64MB 3D DRAM Cache with 32ms refresh rate               | 43 |

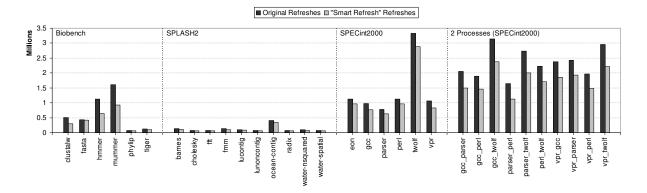

| Figure 18 | Performance improvement using Smart Refresh for a 64MB 3D DRAM Cache with 32ms refresh rate | 44 |

| Figure 19 | SRAM cell with both Gated-Vdd and DVS control                                               | 50 |

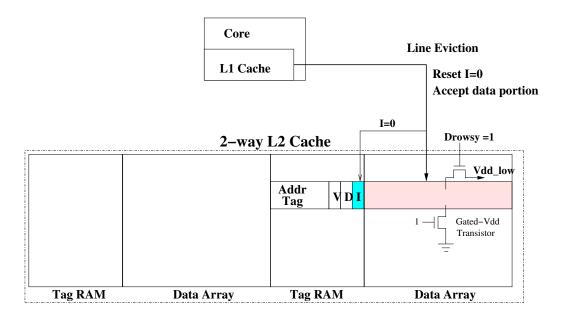

| Figure 20 | Cache Line Allocation for Virtual-Exclusion.                                                | 52 |

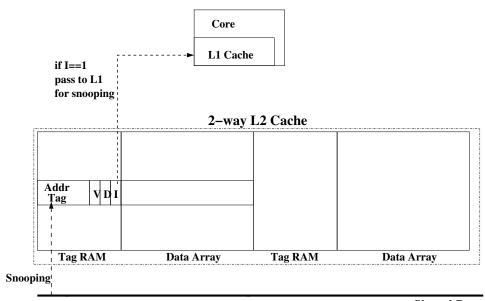

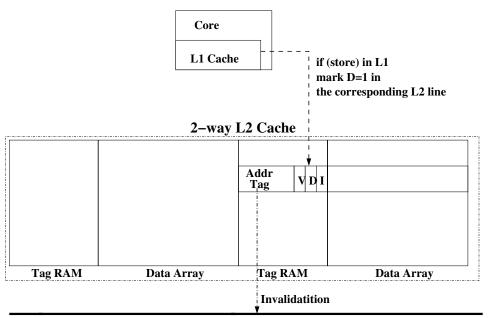

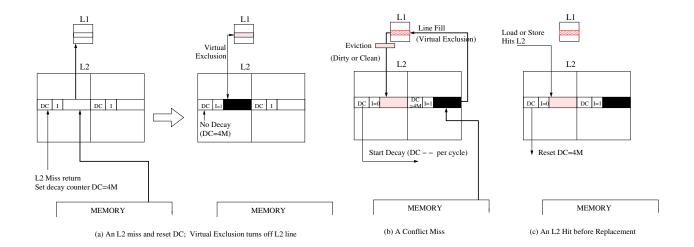

| Figure 21 | Protocol Changes for Virtual-Exclusion                                        | 54 |

|-----------|-------------------------------------------------------------------------------|----|

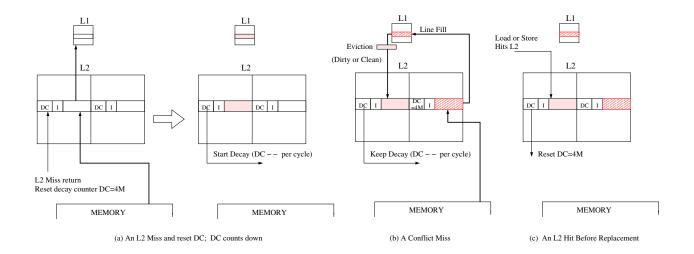

| Figure 22 | Cache-Decay Countdown Mechanism                                               | 56 |

| Figure 23 | Hybrid Virtual-Exclusion Countdown Mechanism                                  | 58 |

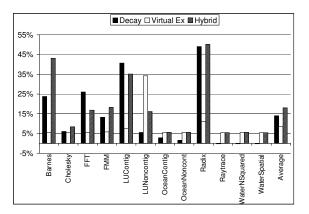

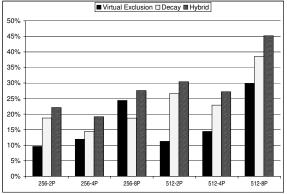

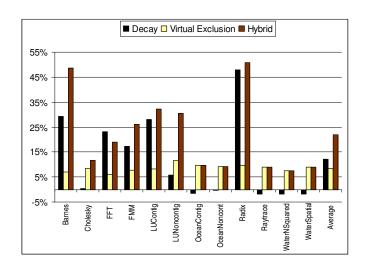

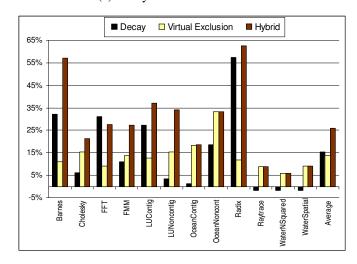

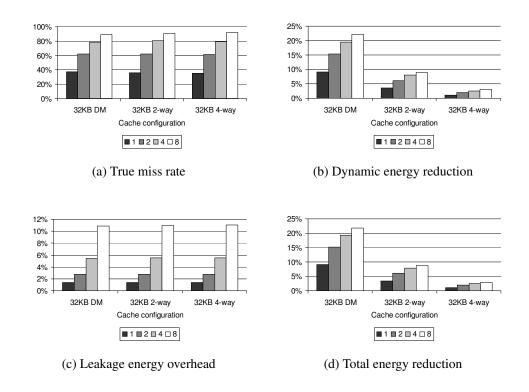

| Figure 24 | Leakage Energy Reduction for 2-way SMP (256KB L2)                             | 63 |

| Figure 25 | Average Leakage Energy Reduction for Different SMP Configurations             | 63 |

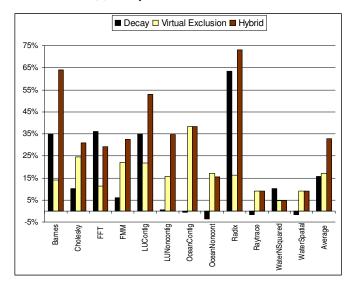

| Figure 26 | Leakage Energy Reduction for Multicore Processors (256KB L2)                  | 65 |

| Figure 27 | Leakage Energy Reduction for Multicore Systems (SPEC2000 Integer Benchmarks)  | 66 |

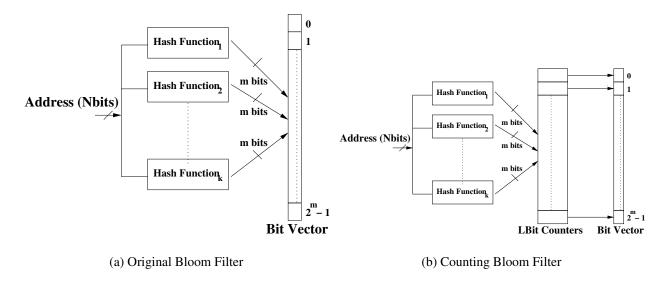

| Figure 28 | Bloom Filters                                                                 | 70 |

| Figure 29 | Segmented Bloom filter                                                        | 72 |

| Figure 30 | Bloom Filter Design with Inclusion Property                                   | 74 |

| Figure 31 | Way Guard Mechanism — Filtering Out Unnecessary Cache Way Lookup              | 77 |

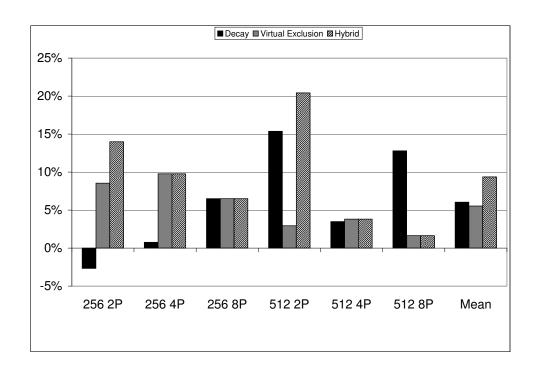

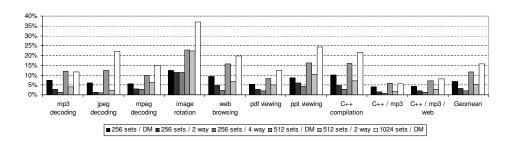

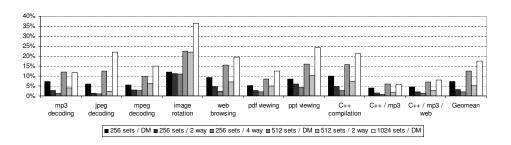

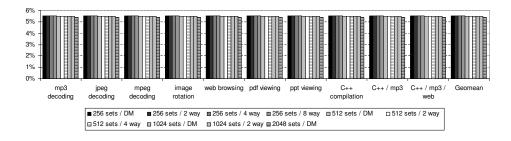

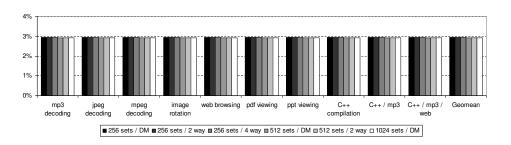

| Figure 32 | Static Energy results                                                         | 87 |

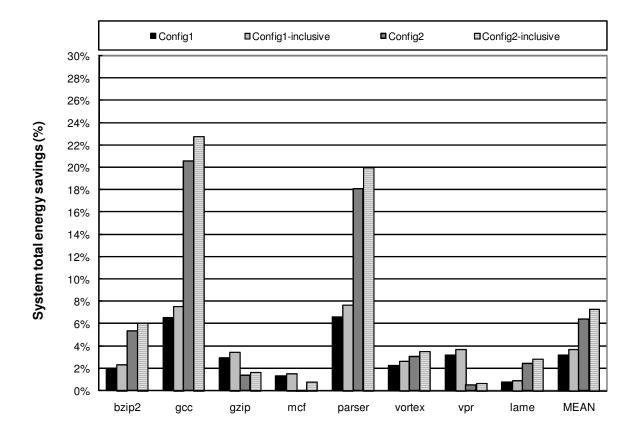

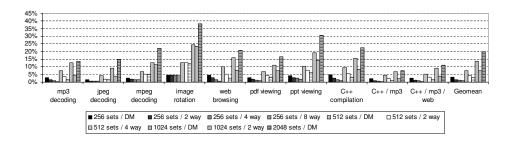

| Figure 33 | Total system energy results                                                   | 88 |

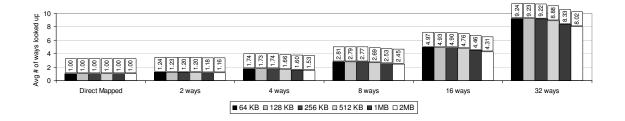

| Figure 34 | Average Number of Ways Looked Up for Hits in an L2 Cache                      | 89 |

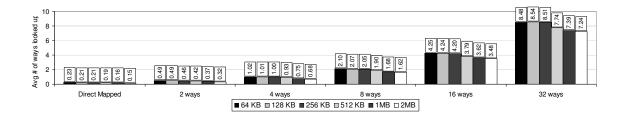

| Figure 35 | Average Number of Ways Looked Up for Misses in an L2 Cache                    | 90 |

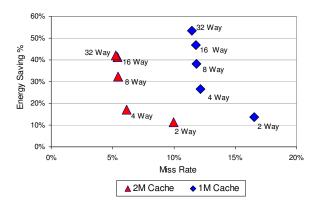

| Figure 36 | Energy Savings with respect to Miss Rate                                      | 90 |

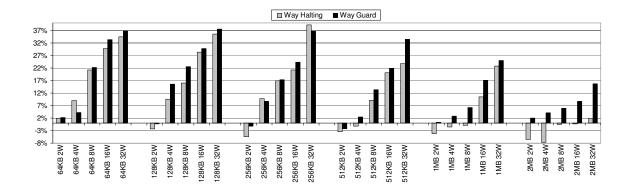

| Figure 37 | Comparing Way Halting and Way Guard Energy Savings in a Serial Lookup Cache   | 91 |

| Figure 38 | Comparing Way Halting and Way Guard Energy Savings in a Parallel Lookup Cache | 94 |

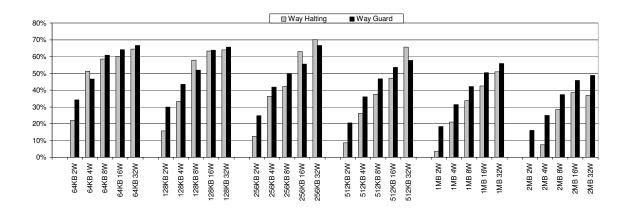

| Figure 39 | Average L1 I- and D-Cache Energy Savings                                      | 95 |

| Figure 40 | Virtual-to-Physical Addressing                                                | 02 |

| Figure 41 | Synonym problem and tag lookup energy                                         | 03 |

| Figure 42 | Early synonym detection in a V/P cache                                        | 05 |

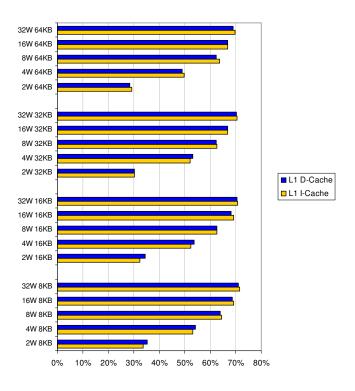

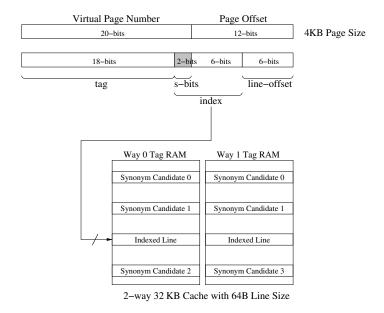

| Figure 43 | 2-way Set Associative 32KB Cache with 32B Line                                | 10 |

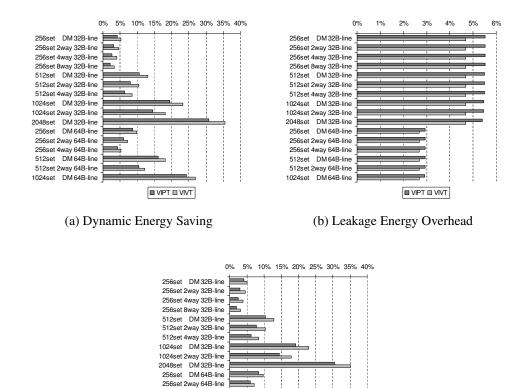

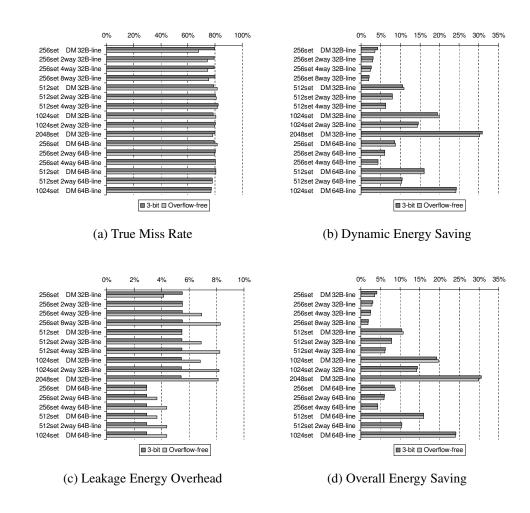

| Figure 44 | Dynamic Energy Savings (VIPT)                                                 | 15 |

| Figure 45 | Overall Energy Savings (VIPT)                                                 | 16 |

| Figure 46 | Leakage Energy Overhead (VIPT)                                                      |

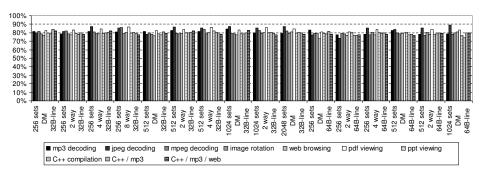

|-----------|-------------------------------------------------------------------------------------|

| Figure 47 | Relative Dynamic Energy Consumption of <i>PowerPoint</i> for 32B-Line Caches 118    |

| Figure 48 | Relative Number of L1 D-cache accesses of <i>PowerPoint</i> for 32B-Line Caches     |

| Figure 49 | Simulation Results of <i>PowerPoint</i> for 32B-Line Caches                         |

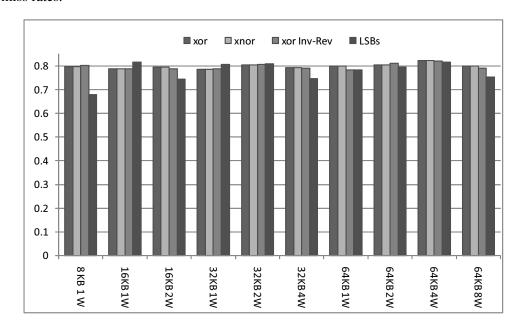

| Figure 50 | Sensitivity Study of the Bloom Filter Size with <i>PowerPoint</i> (32B-line Caches) |

| Figure 51 | Simulation Result with VIVT Caches using <i>PowerPoint</i>                          |

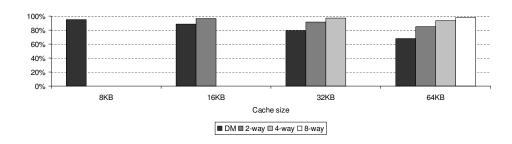

| Figure 52 | True Miss Rate Comparison                                                           |

| Figure 53 | Simulation Result of Overflow-free Synergy using <i>PowerPoint</i> 124              |

| Figure 54 | True Miss Rate using Different Hashing Functions                                    |

| Figure 55 | Leading 0's and 1's for SPECint2000                                                 |

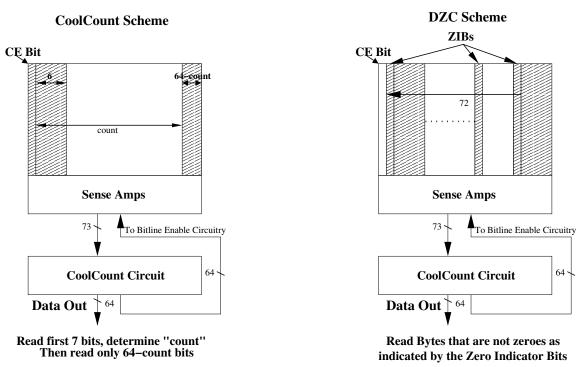

| Figure 56 | CoolPression Cache                                                                  |

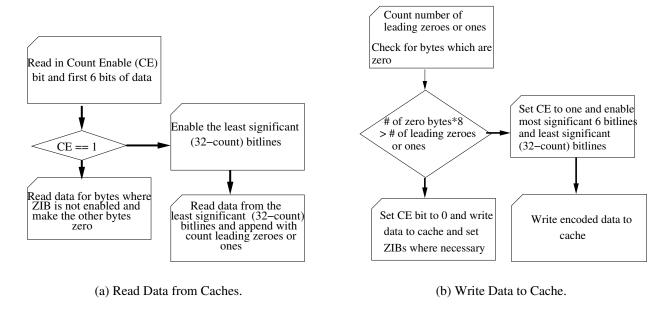

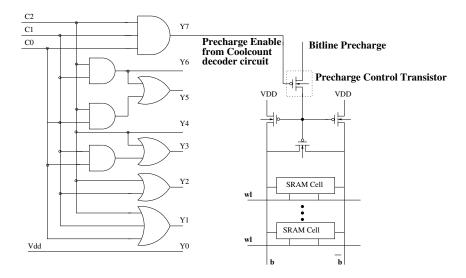

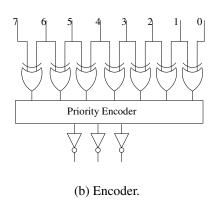

| Figure 57 | Flowchart for Reading and Writing Data to the CoolPression Cache 132                |

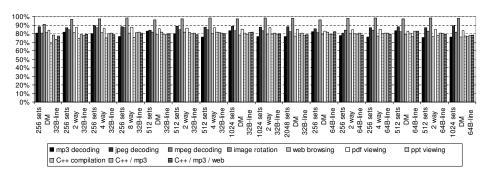

| Figure 58 | Decoding/Encoding Logic Circuits                                                    |

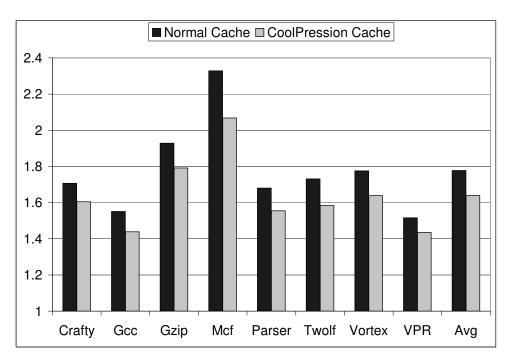

| Figure 59 | Impact on IPC                                                                       |

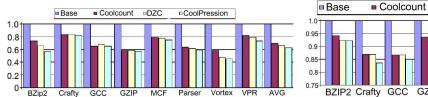

| Figure 60 | Norm. Energy in a 16KB L1 D- and I-Cache                                            |

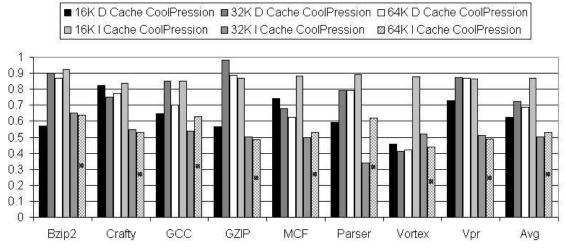

| Figure 61 | Norm. Energy in a 32k/64k L1 I/D-Cache                                              |

#### **SUMMARY**

This thesis states that dynamic profiling of the memory reference stream can improve energy and performance in the memory hierarchy. The research presented in this theses provides multiple instances of using lightweight hardware structures to profile the memory reference stream. The objective of this research is to develop microarchitectural techniques to reduce energy consumption at different levels of the memory hierarchy. Several simple and implementable techniques were developed as a part of this research. One of the techniques identifies and eliminates redundant refresh operations in DRAM and reduces DRAM refresh power. Another, reduces leakage energy in L2 and higher level caches for multiprocessor systems. The emphasis of this research has been to develop several techniques of obtaining energy savings in caches using a simple hardware structure called the counting Bloom filter (CBF). CBFs have been used to predict L2 cache misses and obtain energy savings by not accessing the L2 cache on a predicted miss. A simple extension of this technique allows CBFs to do way-estimation of set associative caches to reduce energy in cache lookups. Another technique using CBFs track addresses in a Virtual Cache and reduce false synonym lookups. Finally this thesis presents a technique to reduce dynamic power consumption in level one caches using significance compression. The significant energy and performance improvements demonstrated by the techniques presented in this thesis suggest that this work will be of great value for designing memory hierarchies of future computing platforms.

#### **CHAPTER 1**

#### INTRODUCTION

The increasing complexity and shrinking feature size of modern microprocessors has caused energy consumption to become a critical design constraint [87]. The demands of the working-set size from increasingly complex applications has led to ever-larger on-chip caches with a slew of read/write ports making it a major consumer of on-chip power. Apart from caches, other components of the memory hierarchy like DRAM also contribute significantly to the power consumption of the overall system. In this chapter, we start with discussing about energy consumption and redundancies in different parts of the memory hierarchy. Then, we explain how this research aims at addressing and eliminating the redundancies to reduce energy at different levels of the memory hierarchy.

#### 1.1 Motivation

In this section, we consider energy consumption problems at different levels of the memory hierarchy. We start with the level furthest from the processor, that is DRAMs, and continue to move towards the processor and discuss problems in Level 2 or higher level SRAM caches and finally talk about a couple of energy saving opportunities in the Level 1 cache.

First, we explain the energy consumption problems for DRAMs. DRAMs are used as the bulk of the main memory in computing systems for its high density, high capacity and low cost. Due to the dynamic, leaky nature of a DRAM cell, periodic refresh operations are required for retaining the data. Such regular refreshes account for a large energy consumption in DRAMs even in the *standby* mode [88]. When a DRAM is not being accessed, all the energy consumed in the DRAM is because of the refresh operations. During each refresh operation, the data of every DRAM bit cell is read out and then written back. Since DRAMs reads are destructive, an access to the DRAM does the same operations as a refresh for data retention purposes. Since the DRAM controller does not take into

account access patterns while refreshing DRAMs, a significant number of DRAM refresh operations are redundant. Elimination of these redundant refresh operations will lead to substantial savings in DRAM energy.

As processor designers moving toward the direction of integrating 3D die-stacked DRAM (or 3D DRAM) on a package to alleviate memory latency and bandwidth issues [14, 16, 95], the overhead of the refresh operations will increase. There are two reasons behind this increase. First, a 3D DRAM could be used either as a cache between the last level SRAM-based cache and the system memory or to replace the last level cache entirely. However, a tag array is still needed for such 3D DRAM caches for data lookup and storage. Thus, the refresh operation will become a significant overhead relatively.

Second, since the 3D DRAM is bonded directly on top of the processor using dieto-die vias, the heat dissipated from the processor will be conducted across the DRAM layers, leading to a much higher temperature operation environments for the DRAM. Annavaram *et al.* [27] showed that the operating temperature of a 64MB 3D DRAM will be 90.27°C. Furthermore, the leakage will also increase exponentially with an escalating operating temperature. According to the data-sheet of Micron DRAM [83], the refresh rate must be doubled if the operating temperature exceeds 85°C. Therefore, a 3D DRAM will require double (or more) refreshes, increasing the relative energy overhead substantially. Eliminating redundant refresh operations in 3D DRAMs will be very important for both energy and performance of such systems.

Apart from the DRAMs, the higher level caches(Level 2, Level 3) are also significant contributors to the energy consumption of a computing system. The primary reason for this is that with continuously shrinking CMOS technology, the capacity of single-chip processors has exceeded one billion transistors. To use such an immense amount of available transistors, processor architects tend to allocate more cache space and deepen the level of cache hierarchy. While these caches constitute a major portion of a processor's real estate, they are also the least active components and dominate the leakage power among all other

architectural modules. One redundancy in data content for such large cache hierarchies is the need to maintain multi level inclusion (MLI). MLI requires that if a cache line is present in a lower level cache (say L1), it must be present in all the higher level caches (L2 and beyond). Though MLI is important for efficient implementation of cache coherence, it leads to replication of data in the cache hierarchy. The elimination of this redundant replication without affecting performance can lead to significant leakage energy savings in the level 2 cache.

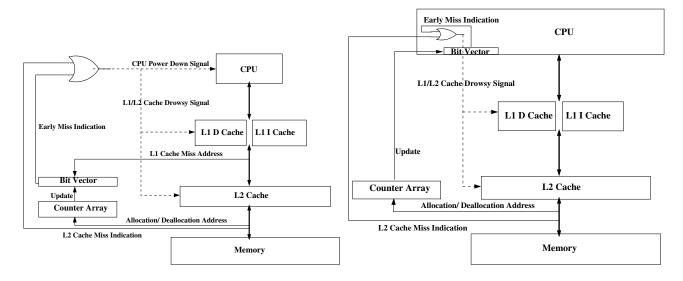

Another significant trend in the microprocessor industry is to shift towards scalable and simplistic multicore processors like the UltraSPARC T1 processor [110]. One side effect of moving towards simplistic cores is that severe stalls that may occur when a data access misses the last level cache and goes to DRAM memory. Such cache miss events can also be used as a trigger for several microarchitectural energy management processes in the processor. The energy management processes may include but are not limited to putting all caches in a state preserving low power drowsy mode and/or clock-gating or power-gating all or part of the processor core. Architectural techniques to efficiently utilize these energy management activities will lead to significant energy savings.

Along with modern processors having large caches, the caches have increasingly higher associativity [60]. Processors employing highly associative caches consume large amount of energy on every cache lookup. In the case of a cache hit, depending on the implementation, an N way set-associative cache does N tag comparisons, and optionally may read N data lines, and only use one of the cache data lines. For a miss, all tag comparisons and data reads are redundant. Thus most energy consumed in a set-associative cache is redundant and gives ample opportunity for saving dynamic energy.

From an energy consumption perspective, the L2 cache and other higher level caches are primary consumers of leakage power. But, a significant amount of the processor energy is the dynamic energy consumed by the level 1 caches. Virtual caches are employed in the first level memory hierarchy for both high performance and embedded processors to meet

their short latency requirement. However, they also introduce the synonym problem where the same physical cache line can be present at multiple locations in the cache due to their distinct virtual addresses from different processes, leading to potential data consistency issues. To guarantee correctness, common hardware solutions either perform serial lookups for all possible synonym locations in the L1 at the expense of additional energy. Since the occurrence of synonyms is relatively rare, the energy consumed in detecting synonyms is mostly redundant and presents significant opportunities for energy savings.

When considering the dynamic energy consumption of caches, a significant part is drawn by the bitline driver circuitry because the bitlines are densely loaded with a large number of storage cells thus increasing its effective switching capacitance. Also, it has been observed that a significant percentage of data getting stored in the caches have a large number of leading zeroes and ones. Therefore, there is a potential of significant dynamic energy savings if significance compression is performed on the data stored in the cache and the unused bitlines are gated-off.

In this section, we presented a number of facets of the energy consumption problem at all levels of the memory hierarchy. Section 1.2 gives an overview of the contributions of this thesis pertaining to each of the problems highlighted in this section. Section 1.2 constitutes a preview and framework for the rest of this thesis.

#### 1.2 Thesis Statement and Contributions

This thesis states that dynamic profiling of the memory reference stream can improve energy and performance in the memory hierarchy. The research presented in this theses provides multiple instances of using lightweight hardware structures to profile the memory reference stream. This profiled information has been used to identify and eliminate redundancies in memory operation primarily with the objective of saving energy consumption and in some cases improving performance. Several simple and implementable ideas to reduce dynamic power in caches, leakage power in higher-level caches, and refresh power

of DRAM were developed as a part of this research. Emphasis was given on several techniques of getting energy savings using a simple hardware structure called the Counting Bloom filter. A modified design of the Counting Bloom filter has also been used to improve performance in multicore systems. The rest of this section gives an overview of the key aspects of this research.

#### Smart Refresh: Using Decay Counters to Reduce Energy Consumption in DRAMs

One facet of this research has been to reduce energy consumption in DRAMs [50]. DRAMs require periodic refresh for preserving data stored in them. The refresh interval of DRAMs depend on the the vendor and the design technology they use. For each refresh in a DRAM row, the stored information in each cell is read out and then written back to itself, as each DRAM bit read is self-destructive. The refresh process often incurs large power and bandwidth overhead. However, it is inevitable for maintaining data correctness.

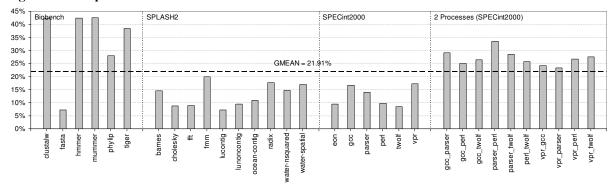

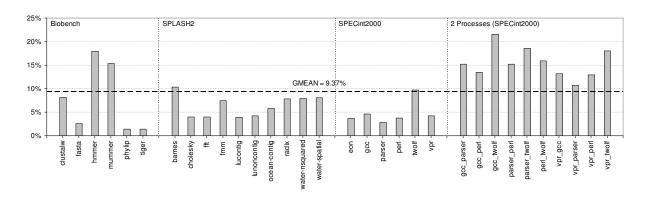

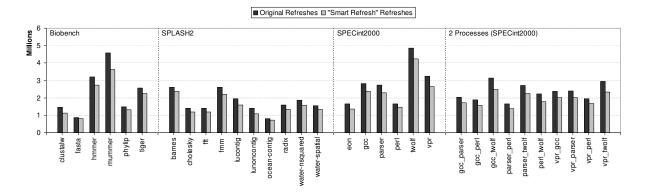

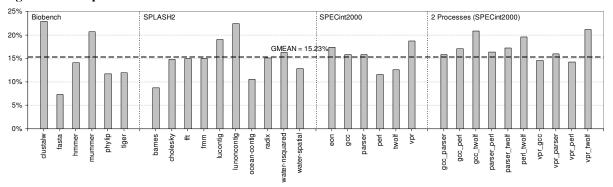

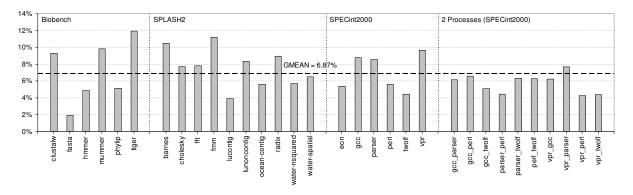

This research involved construction of an innovative scheme to reduce the refresh overhead in DRAMs. By using a countdown counter for each memory row of a DRAM memory module, all the unnecessary periodic refresh operations were eliminated. The basic concept behind this scheme is that a memory row that has been recently read or written to by the processor (or other devices that share the same DRAM), does not need to be refreshed again by the periodic DRAM refresh operation, thereby eliminating excessive refreshes and the energy dissipated. Based on this concept, we proposed Smart Refresh, a low-cost technique in the design of the memory controller for DRAM power reduction. The simulation results show that our technique can reduce 52% of all refresh operations. This saved 34.5% of the energy consumed for refresh operations. DRAM system energy savings of up to 22% and an average of 9.5% were obtained for SPECint2000, Biobench, and Splash-2 benchmark suites simulated with a 2GB DRAM. We used our Smart Refresh policy on the upcoming 3D die stacked DRAM technology and obtained energy savings up to 21% and 7.2% on an average when the refresh rate is 64 ms.

The rest of this research concentrates on reducing power consumption of SRAM caches.

We present three different techniques to reduce dynamic and leakage power in SRAM caches in the subsequent paragraphs.

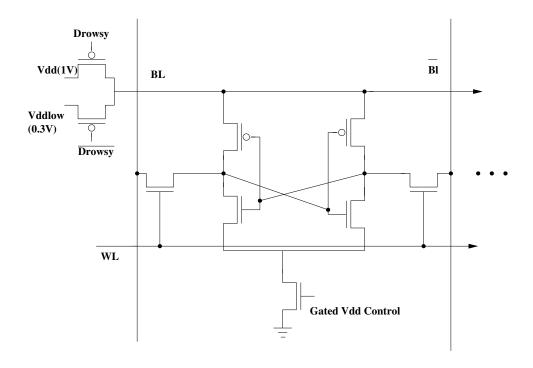

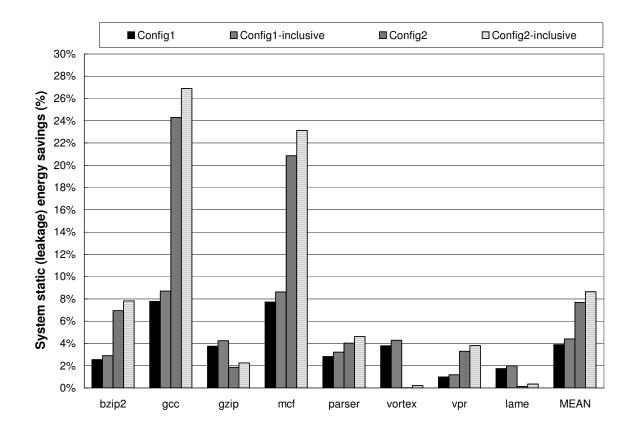

#### Using Virtual-Exclusion to reduce leakage power in Caches

Another aspect of our work was focused on architectural techniques to reduce leakage energy in the L2 caches for cache-coherent multiprocessor systems [51]. This research leverages two well-known circuit techniques, gated Vdd and drowsy cache, and proposes a low cost, easily implementable architecture scheme called Virtual-Exclusion. The Virtual-Exclusion scheme saves leakage energy by keeping the data portion of repetitive cache lines "off" in the large higher-level caches, while still manages to maintain Multi-Level Inclusion, an essential property for efficient implementation of conventional cache coherence protocols. By exploiting the existing state information in the snoop based cache coherence protocol, there is almost no extra hardware overhead associated with our scheme. The SPLASH-2 multiprocessor benchmark suite was found to execute correctly under our new Virtual-Exclusion policy. The benchmarks showed up to 72% savings of leakage energy (46% for SMP and 35% for multicore in L2 on average) over a baseline drowsy L2 cache.

#### Using Bloom filters to Improve Power and Performance of Caches and Memory.

The techniques explained above exploited different forms of redundancies in the memory hierarchy to reduce energy consumption. For DRAMs, redundant refresh operations were eliminated to reduce DRAM power. In higher level caches, redundancies were found in the Multi-Level Inclusion policy and the snooping protocol to reduce cache leakage power. The subsequent technique, in contrast, adds a new hardware structure called the "Counting Bloom filter" (CBF) to the memory hierarchy. The emphasis of the research being presented in this thesis are on several innovative uses of the CBF to reduce energy consumption in SRAM caches and sometimes improve performance.

A CBF is an efficient data structure that comprises of a signature of a large data set and indicates the absence of an element in that data set. Applying CBFs to cache lookups result in faster and more power-efficient cache queries. As part of the research on CBFs, we present four techniques of reducing cache energy using the structure.

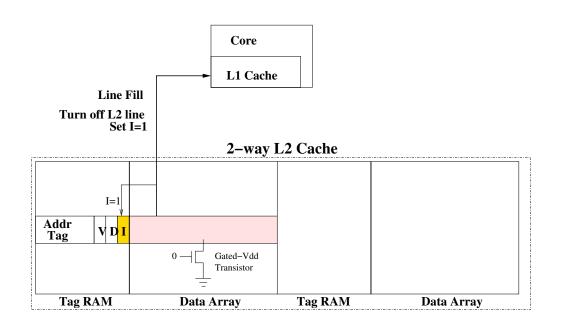

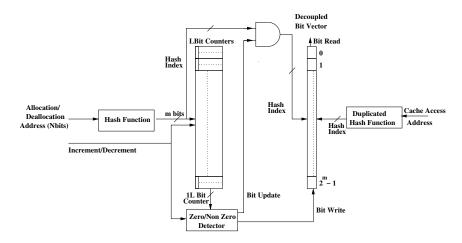

Firstly we use CBFs to predict cache misses by tracking addresses of cache lines brought in and evicted from the cache [52]. On every linefill, the block address is hashed to generate an index used to update a bitvector. Also the counter associated with that bit is incremented. During block eviction, the corresponding counter associated with the bit indexed by the hash of the evicted block's address is decremented. On a cache access, the CBF is accessed first, and a zero in the bitvector location obtained by hashing the block address, indicates a cache miss. This prevents access to the larger cache, thus saving power and latency. Our experiments based on SPECint2000 and embedded benchmarks showed that CBFs correctly predict 89% of all L2 Cache misses, and reduces overall energy consumption by 9%.

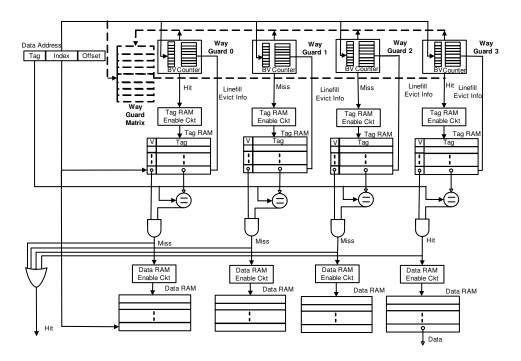

For the second technique, we present the Way Guard, an efficient hardware structure based on CBFs, for estimating ways in a set-associative cache. Way estimation saves significant amount of unnecessary energy dissipation by reducing lookups going into redundant ways when a set-associative cache is accessed. Our Way Estimation technique required caches to look up only an average of 25-30% of the ways and saved up to 65% of the L2 energy and up to 70% of the L1 cache energy.

Finally, we examine the energy issues due to synonyms in a Virtually Indexed Cache (V-Cache) [119]. V-Caches are used to isolate virtual to physical address translation from the cache access critical path. V-Caches may have the synonym problem, where the same physical cache line can be present at multiple locations in a cache. To maintain data consistency, V-Caches are designed to ensure only one exclusive copy exists in the cache. Towards this, many commercial processors perform serial lookups for all possible synonym locations upon every miss, leading to a large energy overhead. Using a CBF to track physical addresses of cache lines brought in and evicted from the cache, false synonym lookups in the L1 cache are aborted. Using Windows application workloads, the CBF demonstrated up to 27.6% savings in the total cache energy.

#### Cache Power Reduction via Hybrid Significance Compression

This technique tries to reduce dynamic power consumption in caches by identifying redundancies in the data-values stored in the cache [53]. The focus of this technique is to analyze and identify the characteristics of workload behavior, in particular, in the first-level instruction and data caches, for power saving opportunities. We performed data value profiling for a large number of workloads, such as, the SPECint2000 and Mediabench benchmarks and observed that the data values entering the cache consists of long sequence of leading zeros and leading ones in the significance bits, indicating redundancy in the information content.

We then conceived a new significance compression technique, as a part of this effort. The basic idea is that, instead of enabling all the bitlines, the homogeneous data are compressed to a more compact form and only the bitlines representing the compact data will be enabled during cache accesses. The technique called CoolPression, is a dynamic hybrid compression scheme that combines two significance compression methods — (1) CoolCount which involves counting the number of leading zeros or ones and keeping the count by reusing the leading significant bits, and (2) Dynamic Zero Compression (DZC), an existing technique that compresses data in one-byte granularity. CoolPression combines these two schemes and determines the lower power compression scheme on-the-fly. CoolPression reduced dynamic energy consumption by more than 35%, while improving the energy consumption of both the CoolCount and DZC scheme by 5-15%.

This thesis is organized as follows. Chapter 2 gives a detailed description of prior microarchitectural low power techniques for DRAMs and caches. Chapter 3 explains the Smart Refresh technique and its energy savings in the DRAM. Next, we discuss the leakage power reduction technique called Virtual-Exclusion in Chapter 4. Chapter 5 is composed of a description of CBFs and their role in reducing cache energy consumption and way estimation. Chapter 6 consists of the application of CBFs to reduce synonym lookups in virtual caches. This is followed by a presentation of the significance compression technique

called Coolpression in Chapter 7. Finally, Chapter 8 summarizes the contributions of this thesis, talks about potential impact of this work in future microprocessors and enumerates a few directions in which this work may be extended.

#### **CHAPTER 2**

#### **RELATED WORK**

As explained in Chapter 1, our research addresses different aspects of the energy consumption problem at different parts of the memory hierarchy. In this chapter we discuss prior research done on each of the problems considered by this research. Firstly, we discuss prior art in reducing refresh operations in DRAMs. Then we go on to discuss several techniques to reduce dynamic power in caches. Next, we do a survey of static and leakage power reduction techniques. This is followed by an overview of different microarchitectural techniques using Bloom filters. Finally, we discuss prior art on way prediction and estimation in set-associative caches.

### 2.1 Methods of Reducing DRAM Power

We discuss several methods of reducing DRAM energy in this section. Furthermore, we also elaborate a number of reducing redundant refresh operations.

Modern DRAM modules have several low power states for saving energy. For example, Micron DRAMs [7] have temperature controlled self refresh (TCSR), which dynamically changes the refresh interval of a DRAM module based on the ambient temperature of the DRAM component. This saves DRAM energy as the DRAM refresh interval does not need to be conservatively designed for correctness at its maximum operating temperature. Micron DRAMs also have a low power technique called partial array self refresh (PASR). This allows the DRAM module user to select a subset of banks of the DRAM module to be refreshed for data retention. If an application does not need the DRAM for extended periods of time, the DRAM module can be sent to a *deep power down* (DPD) mode, which does not retain data and turns off most of the array power generators. Similarly, RAMBUS DRAM [4] modules typically support three low power modes, namely, *idle*, when the clock distribution is paused, *power down*, when only the clock multiplier is on and a *deep power*

down mode that only consumes leakage power.

A number of compiler and microarchitectural techniques have been developed to efficiently use the low power modes supported by DRAM modules. We discuss a few of these techniques in this section. Delaluz *et al.* [41] discusses compiler techniques that performs clustering of data and mode control to detect modules that are not being acceessed. Furthermore, this paper discusses several heuristics implemented in hardware at the memory controller to predict idleness of modules and efficiently switch to a low energy state. The paper reports substantial energy savings of up to 89%.

In [18], the authors save energy in a broadcast based shared memory multiprocessor system by using a regional coherence array to keep track of data present in other processor's cache and reducing access to the DRAM. This reduces DRAM read traffic by 28-32% and reduces DRAM energy consumption by 16-21%.

Hur *et al.* [58] describe three different approaches of saving DRAM energy. The paper describes a simple power down policy to better exploit the low power states of modern DRAMs. It also describes an adaptive history based scheduler and a throttling scheme to save DRAM energy without affecting performance. The paper reports up to 46% DRAM energy efficiency improments using their techniques.

Zheng *et al.* [124] describe a technique that introduces a bridge chip to break a DRAM DIMM into mini DIMMs to reduce the number of devices involved in a single memory access. Experimental results show a 44% improvement in memory efficiency.

A number of DRAM circuit techniques have also been developed to reduce DRAM power. One such technique is explained in [89], in which the authors use ECC in Embedded DRAMs to introduce an Extended Data Retention Sleep mode that increases the data retention time in this mode by more that 8 times and reduces idle time refresh energy. Another circuit technique is explained in [62], where the authors implement a four rank 3D DRAM module using a master and three slave chips. Using a single master enables the authors to remove redundant circuitry like delay locked loops, input buffers and clock

circuitry from the slave chips. This helps this implementation of 3D DRAM to save power compared to conventional quad-die package structures that have 4 ranks per module.

One of the earliest techniques of using countdown timers for tracking DRAM refresh was proposed in a patent disclosure [43]. This patent describes a timer based circuitry to reduce the number of refresh operations in a DRAM based cache. The patent's objective was to invalidate lines (via decay) that have not been accessed for a given time interval in the context of DRAM Caches.

Another similar idea of using counters to reduce refreshes is described in [92]. However, as in the case of [43], the method described in the patent is far from optimal and does not have any technique to solve the burst refresh situation. The patent disclosed by Song *et al.* [108] also described a technique to selectively refresh DRAM rows based on their access pattern. However, the technique based on the limited explanation in the patent can lead to situations where the data of a row may be destroyed because it is not refreshed in time.

Venkatesan *et al.* in [113] introduced RAPID, a retention-aware placement algorithm. This work tries to reduce refresh operations to the DRAM by experimentally identifying that different rows require different refresh times. Kim *et al.* in [69] exploits multiple DRAM refresh times and ECC codes to reduce the number of refresh operations. Ohsawa *et al.* used several techniques in [91] to reduce refresh operations required. One of the techniques used by [91] is to statically declare a line to be dead. This may also be done with the help of the OS. The lines marked as dead in the DRAM are not refreshed. Another scheme is called VRA where counters are used to handle variable data refresh times.

# 2.2 Techniques for Reducing Dynamic Power for Caches

Although leakage power has become more important for higher level caches, dynamic power consumption still dominates the power consumption for L1 caches because of the high access rate. A significant part of the dynamic cache energy is drawn by the bitline

driver circuitry because the bitlines are densely loaded with a large number of storage cells, thus increasing its effective switching capacitance. To address this issue, many low-power cache techniques were proposed including sub-banking, segmented bit-lines [49, 109], and pulsed word-line drivers [22].

Another interesting approach to reduce dynamic power is to perform data compression which allows gating off unused bit-lines, while reading from and writing data to the cache. Kim *et al.* [70] describes a sign compression technique, where the most significant half word is compressed to a sign bit to reduce energy. Canal *et al.* in [32] also applies significance compression to reduce power consumption in all stages of the pipeline. Villa *et al.* [114] describe a Dynamic Zero Compression (DZC) scheme that compresses if an entire byte is zero.

#### 2.3 Leakage Reduction Techniques for Caches

There have been a large number of architectural and circuits techniques proposed to reduce leakage power in caches. Powell *et al.* [96, 121] shows that the leakage currents can be dramatically reduced by employing sleep transistors to gate off the supply voltage when the corresponding logic blocks are not in use. A microarchitectural technique called *Cache Decay* was proposed in [63] to exploit this circuit technique in the L1 cache. This technique saved energy by using simple counters to turn off cache lines if they are unlikely to be reaccessed. Although it did mention some implications of applying the decay scheme in large higher level caches, it provided no further in-depth evaluation, in particular, from the cache coherence standpoint, a correctness issue for implementing a multiprocessor (MP) system. One major drawback of the cache decay policy lies in the performance and power trade-offs of the extra misses induced due to the switch-off of decayed lines, which leads to additional accesses to the DRAM. This energy overhead often outweighs the leakage savings from the technique itself.

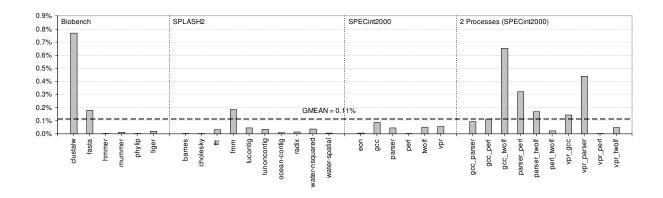

Another circuit technique for leakage reduction is using the ABC-MT-CMOS memory cell [90]. This circuit technique uses different supply and ground voltage levels to bias the transistors to increase their effective threshold voltage. It reduces leakage current dramatically while preserving transistor state in a lower supply-voltage, i.e., drowsy mode. Memory cells, however, have to incur a small performance penalty for waking up the drowsy cells. Flautner *et al.* [46] proposed an integrated architecture and circuit technique called Drowsy Cache, that implements a simple circuit to dynamically choose between two different supply voltage modes for leakage reduction. They analyzed different architectural policies for turning the L1 lines into drowsy mode. They also showed that they can achieve good leakage power reduction by simply keeping the data portion of all the L2 lines in drowsy mode. A specific data line is reinstated to a normal, high-power mode, only when it is re-accessed with some activation penalty. Since an L2 cache takes tens of cycles to access, adding an extra cycle or two for wake-up will be insignificant to the overall performance.

# 2.4 Microarchitectural Energy Reduction Techniques using Bloom filters

The initial purpose of Bloom filters was to build memory efficient database applications. Since then, Bloom filters have found numerous applications in networking and database areas [30, 99, 42, 72, 35, 39]. Bloom filters were also applied as microarchitectural blocks for tracking load/store addresses in load/store queues. For instance, Akkary *et al.* [19] uses one to detect the load-store conflicts in the store queue. Sethumadhvan *et al.* [103] improved the scalability for load store queues with a Bloom filter. More recently, Roth *et al.* [100] uses a Bloom filter to reduce the number of load re-executions for load/store queue optimizations. The use of Bloom filters as microarchitectural blocks for tracking load/store addresses for resolving load-store conflicts have been demonstrated in [20, 104].

The earliest example of tracking cache misses with a counting Bloom filter is given by

Moshovos *et al.* [86]. They proposed a hardware structure called *Jetty* to filter out cache snoops in SMP systems. Each processing node has a *Jetty* that tracks its own L2 cache accesses, and snoop requests are first checked in the *Jetty* before searching the cache. This is reported to reduce snoop energy consumption in SMP systems. A *Jetty*-like filter is also used by Peir *et al.* [94] for detecting load misses early in the pipeline so as to initiate speculative execution. Similarly, Mehta *et al.* [81] also uses a *Jetty*-like filter to detect L2 misses early so that they can stall the instruction fetch to save processor energy.

Memik *et al.* [82] proposed early cache miss detection hardware techniques encapsulated as *Mostly No Machine (MNM)*, to detect misses early in the multi-level caches below the L1 cache (i.e., L2, L3 etc). Their goal was to reduce dynamic cache energy and to improve performance by bypassing the caches that will miss. The MNM is a multi-ported hardware structure that collects block replacement and allocation addresses from these caches and can be accessed after the L1 access or in parallel with it.

# 2.5 Way Prediction and Estimation Techniques

The most common way prediction mechanism is to predict the MRU way as proposed in [31]. Similar way prediction techniques have been proposed in [59, 66]. Another way prediction scheme that uses the PC to predict ways is proposed in [25]. However, way prediction has the disadvantage of a large performance and energy loss if the prediction is wrong. One alternative to way prediction is way memoization proposed by Ma *et al* in [76]. Way memoization keeps way information in the instruction cache and also has a valid bit that ensures that the way information is correct. However, this technique can only be used in instruction caches. Way prediction has the disadvantage of a large performance and energy loss if the prediction is wrong. This disadvantage is mitigated by way estimation. Way estimation techniques do not predict one single way, but a set of ways where the data is guaranteed to be present for a cache hit. Therefore, way estimation techniques do not incur a large performance loss for a wrong estimation, because a wrong estimate

only results in a lookup in the cache, when it is missing the cache. One way estimation technique is the sentry tag technique proposed in [36]. This technique uses a buffer to hold one tag bit for each line of the cache. On a cache lookup, the last bit of the tag of the address is first compared to the corresponding set in the sentry buffer. On a mismatch for a particular way, the tag comparison for that way is halted, resulting in energy savings. The Way Halting technique [122] is an extension of the concept of sentry tags. This technique explained in Chapter 5.6.5 uses a buffer to hold multiple tag bits for each line of the cache. On a cache lookup, the least significant bits of the tag of the address is first compared to the corresponding set in the sentry buffer. On a mismatch for a particular way, the tag comparison for that way is halted, resulting in energy savings. Another way estimation technique is proposed in [64], in which the authors tried to predict lines that have decayed, because they have not been accessed for a fixed number of cycles. Since this technique incorporates cache decay, it is not suitable for use in the L1 caches as it may increase the miss rate considerably.

The following five chapters explain in detail the research done to exploit redundancies in the memory hierarchy to save power and improve performance. The following chapter explains a DRAM refresh power saving technique.

#### **CHAPTER 3**

#### REDUCING DRAM REFRESH POWER WITH SMART REFRESH

Dynamic Random Access Memory (DRAM) is used as the bulk of the main memory in computing systems for its high density, high capacity and low cost. Due to the dynamic, leaky nature of a DRAM cell, periodic refresh operations are required for retaining the data. Such regular refreshes account for a large energy consumption in DRAMs even in the *standby* mode. For instance, a detailed power analysis of the ITSY computer [88] shows that even in the lowest power mode, the refresh power needed accounts for about one third of the total DRAM power dissipated. The refresh rate for DRAMs depends on the memory vendor and the design technology they use. A typical refresh interval is 64ms [1, 2, 3]. The refresh intervals in embedded DRAMs are an order of magnitude shorter. A typical refresh interval for an NEC eDRAM is 4ms [8], and for an IBM eDRAM implementation is  $64\mu s$  [71]. During each refresh operation, the data of every DRAM bit cell is read out and then written back. This refresh can incur large power and bandwidth overhead, nonetheless, it is inevitable for the sake of data correctness.

As processor designers moving toward the direction of integrating 3D die-stacked DRAM (or 3D DRAM) on a package to alleviate memory latency and bandwidth issues [14, 16, 95], the overhead of the refresh operations will increase. There are two reasons behind this increase. First, a 3D DRAM could be used either as a cache between the last level SRAM-based cache and the system memory or to replace the last level cache entirely. A tag array is still needed for such 3D DRAM caches for data lookup and storage. For brevity, we simply call this 3D DRAM cache a 3D DRAM hereafter. Thus, the refresh operation will become a significant overhead relatively. Second, since the 3D DRAM is bonded directly on top of the processor using die-to-die vias, the heat dissipated from the processor will be conducted across the DRAM layers, leading to a much higher temperature operation environments for the DRAM. Annavaram *et al.* [27] showed that the operating temperature of a 64MB 3D

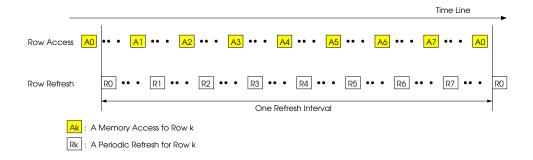

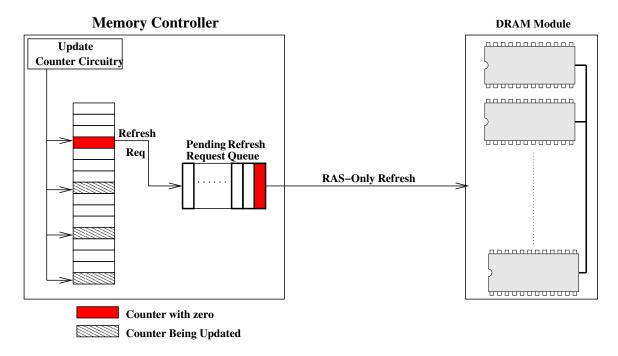

Figure 1. Best Case for Smart Refresh

DRAM will be 90.27°C. Furthermore, the leakage will also increase exponentially with an escalating operating temperature. According to the datasheet of Micron DRAM [83], the refresh rate must be doubled if the operating temperature exceeds 85°C. Therefore, a 3D DRAM will require double (or more) refreshes, increasing the relative energy overhead substantially.

To address these issues, in this chapter, we propose a novel technique called *Smart Refresh* to eliminate all the unnecessary DRAM refresh overheads. This technique uses a simple time-out counter for each row in a memory module, tracks the normal memory transactions, and eliminates the excessive refresh operations. The basic concept behind our scheme is that a memory row that has been recently read out or written to does not need to be refreshed again by the periodic refresh mechanism. By simply exploiting such property dynamically, the number of regular row-sweeping refresh operations in both conventional DRAMs and 3D DRAMs can be substantially reduced.

# 3.1 Redundancy in DRAM refresh

To motivate the case for our Smart Refresh technique, a conjured memory access pattern in Figure 1 is used to demonstrate the requirement for refresh operations. To simplify our illustration, we assume that there are only 8 rows in the DRAM.

In this example, we assume that the DRAM is accessed by the processor with a regular access pattern such that each memory row is accessed right before the row is to be refreshed.

For a normal, periodic refresh policy, all the memory rows will be, anyhow, refreshed by the memory controller without the knowledge of these recent accesses. Note that each access to a memory row initiated by the processor, in fact, performs an operation equivalent to a regular refresh from the standpoint of data preservation. In other words, if a row has been recently read or written to, there is no need to refresh the row immediately as shown in this figure. For the above example, in an ideal situation, there is no need to perform refresh at all since these regular memory accesses have already accomplished the same effect.

Our Smart Refresh technique exploits such energy savings opportunities by keeping a time-out counter for each row in the memory controller to minimize the required refresh cycles. Basically, the time-out counters of those rows being accessed will be reset to a default value (e.g. the refresh interval) and any following periodic refresh operation before the counter counts down to zero will be aborted. When applying such mechanism to the access pattern shown in Figure 1, the DRAM will not be refreshed at all by the default periodic refresh, without affecting the correctness. Thus we will be eliminating half of the refresh operations on the DRAM using this technique. So in theory, the best possible energy savings that can be achieved by using Smart Refresh is 50% of the entire DRAM, in which all the periodic refreshes are avoided.

# 3.2 DRAM Refresh Techniques

There are two common refresh modes in commodity DRAMs:

- Burst Refresh: In this scheme, the entire refresh operation of all the rows are done sequentially in a bursty fashion. The scheme is less desirable as it increases the peak power consumption of the DRAM. Moreover, during the time of the refresh operations, the DRAM module cannot handle normal access requests, causing potential performance degradation.

- Distributed Refresh: In distributed refresh, the memory controller spreads out the refresh cycles for different rows evenly across the refresh interval. This method is more

favorable as it refreshes each DRAM row in a timely manner, enables accesses to rows that are not being refreshed, and minimizes the delay of normal memory requests.

In addition, a DRAM refresh cycle can be implemented in two distinct ways [84]. Note that a refresh cycle can be executed in either the distributed mode or the burst mode explained above.

- RAS-only refresh: To perform a RAS-only refresh, a row address is put on the address lines and then the RAS (Row Address Strobe) signal is asserted LOW. When the RAS falls, that row will be refreshed as long as the CAS (Column Address Strobe) signal is held HIGH. It is the DRAM controller's function to provide the addresses to be refreshed and make sure that all rows are being refreshed at the appropriate times. It is important to note that for refresh operations the row order of refreshing does not matter; however, each row must be refreshed before the data stored by the cell is destroyed.

- CAS before RAS refresh: This is often referred to as CBR refresh, and is a frequently used method for refresh because it is easy to use and provides the advantage of lower power. A CBR refresh cycle is performed by setting the CAS signal to LOW (active) before the RAS signal is switched from HIGH to LOW. One refresh cycle will be performed each time the RAS signal falls. The Write Enable (WE) signal must be held HIGH during the period when the RAS signal is falling. The memory module contains an internal address counter which is initialized to a preset value when the device is powered up. Each time a CBR refresh is performed, the device refreshes a row based on the counter value, and then the counter is incremented. When CBR refresh is performed again, the next row indicated by the counter is refreshed followed by an increment in the counter. The counter is wrapped around automatically when it reaches the maximum allowable value equivalent to the number of rows. There is no way to reset the counter once set after initializing. Conventionally, CBR refresh is a more favorable refresh policy as it consumes lower power because the address does not have to be put on the bus. In this chapter we will show that our Smart Refresh technique

is suited to RAS-only Refresh, and despite the overhead over CBR, RAS-only refresh method with our Smart Refresh technique shows significant energy savings over a CBR refresh policy.

#### 3.3 Smart Refresh

#### 3.3.1 Basic Operation

Inspired by the Cache Decay work [63], our *Smart Refresh* technique applies the idea of using time-out counters in the context of the refresh operation of a DRAM to reduce dynamic energy consumption. Before we discuss Smart Refresh, we will discuss the basic operation of a DRAM access in more detail. Any DRAM read or write operation initiated by a bus agent (e.g., the processor) starts with the memory controller selecting a bank and asserting the RAS signal to LOW to be active. It simultaneously posts the row address on the address bus. This causes the corresponding memory module to activate the sense amplifiers for the entire row, and the data from the given row is brought into the sense amplifiers. Note that this read operation essentially destroys the data present in the DRAM cells. Subsequently, the CAS signal is set from HIGH to LOW (active) and the column address is placed on the address bus, which causes the column decoder to multiplex the data out for a read operation. In the case of a write operation, the data on the data bus is written to the correct set of the sense amplifiers. The data for the open row stays in the sense amplifiers until there is an access to another bank or a different row. In either case the data in the sense amps is written back to the original cells and the new row is pre-charged. We know that the refresh operation of a DRAM also involves reading from the cells and writing back to them. Thus we can see that a read or a write to a given row in the DRAM is actually the same as a refresh to that row for data retention purposes. To summarize, whenever a row is accessed, it does not need to be refreshed before another refresh interval is due. If the memory controller can keep track of the rows that have been accessed, then it can potentially delay the refresh of rows that have been recently accessed. This brings us to the concept of Smart Refresh.

The basic idea of our technique is to associate a time-out counter for each (bank, row) pair of a memory module. The proposed array of time-out counters is stored and updated in the memory controller. Each time-out counter is simply a 2-bit or 3-bit binary down counter. The time-out counters uniformly count down from its maximum value to zero within the refresh interval of the DRAM. If the value of a counter reaches zero, it indicates that the particular row must be refreshed. The counter is reset to its maximum value whenever the corresponding bank and row in memory is accessed and the row is opened. Since we assume an open page policy in this work, the counter corresponding to an open row is reset again when the page is closed with a precharge operation. This is because during the closing of a page, the values in the DRAM cells of the page are automatically refreshed. The memory controller does not refresh rows whose corresponding counters have a nonzero value. Hence that particular row for the accessed bank will not be refreshed during the regular refresh period. This means that whenever a row is accessed for a normal memory operation (e.g., one induced by a cache miss), the refresh operation for that row is delayed. In the best case, if every row happens to be accessed right before it needs to be refreshed, there will be no need for a separate, default refresh operation.

#### 3.3.2 Staggered Countdown

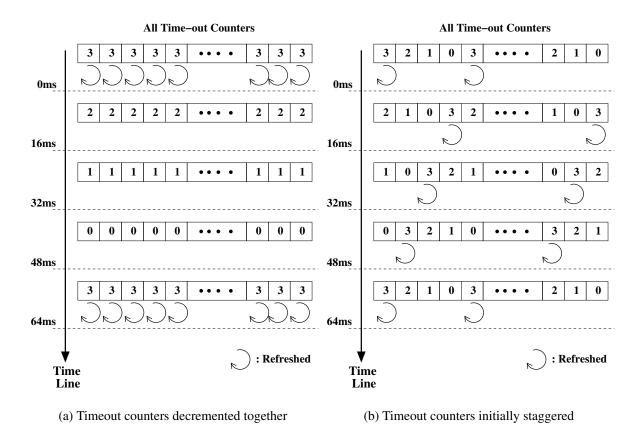

In this subsection we analyze the potential problems of accessing all time-out counters simultaneously. Let us consider a Smart Refresh memory controller that has a 2-bit time-out counter for each row of the DRAM. The array of counters is illustrated in Figure 2(a) horizontally. The refresh cycle in this example is assumed 64ms. For simplicity we assume that there is no access to the DRAM in these examples. The figure shows the counter value for each row of the DRAM as it is being updated by the memory controller. The time-line flows from top to bottom. The 2-bit counter is designed to down-count from 3 to 0 within 64 ms to ensure refresh to all rows are done timely to retain correct data values. If all counters are decremented simultaneously as shown in Figure 2(a), then they will be decremented at times 16ms, 32ms and 48ms respectively. At 48ms, all the counters reach 0 and when the

Figure 2. Down-counting Timeout counters

memory controller accesses them again at 64ms, all the rows must be refreshed at that time, similar to a burst refresh condition that adversely reduces memory system performance. We should note that even though all the rows need to be refreshed at the same time, they can only be refreshed in a sequential order.

One solution to partially take care of this unwanted burst refresh situation is shown in Figure 2(b). In this figure, the initialization of the time-out counters is staggered. In this case, one quarter of all the counters will decrement to zero at 16ms, another quarter become zero at 32ms, and so on. We have a situation similar to burst refresh where many memory rows need to be refreshed one after another. This staggering at the beginning also incurs some power overhead, because at the beginning even all rows have been refreshed, but 1/4 of the counters are initialized to 0. Therefore they are refreshed again within the first 64ms. This however does not solve our problem. When the rows are accessed during normal

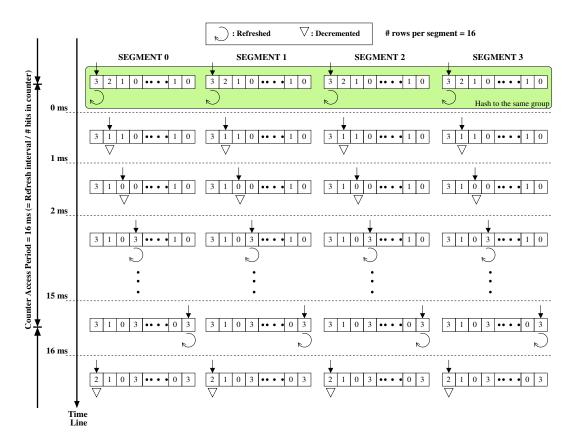

Figure 3. Countdown counters divided into logical segments and countdown is staggered

processor reads and writes, their corresponding counters are reset to its maximum value. This could lead to burst refresh like conditions as potentially a large number of counters may have the same value and since they are decremented together, they will all count down to zero at the same time. This problem can be solved only if the decrement to the counters is also staggered along with the initialization.

The solution used in our design is shown in Figure 3. In this scheme, the counters are evenly hashed into N logical segments where N=4 in this illustration. The selection of N segments is based on the size of the *pending refresh request queue* to be explained in Section 3.4. All simulations were done using 8 entry pending refresh queue and 8 segments. The major difference of this technique with previous techniques is that in this solution all the counters will not be accessed by the memory controller simultaneously.

In this new staggered scheme, refresh or counter decrement by the memory controller are only allowed for those four *indexed* counters (with arrows shown on top of the counter

in the figure) at a given time. As a result of the hashing function, only N counters (4 in this case) are active at the same time. The goal of this scheme is to index each counter exactly once within a so-called *counter access period* which is defined as the refresh interval (i.e., 64ms in our example) divided by the size of the counter (=  $2^{2bit}$  = 4). In Figure 3, the counter access period is 16ms. The index is advanced to the next counter by a clock period equal to the counter access period divided by the number of time-out counters (i.e., memory rows) within each segment. For example, if there are 16 memory rows for each segment and the refresh period is 16ms, then the counter index will advance by one every 1ms. The update of the counter is the same as previously described. When the value of the indexed counter is zero, at the next time it is indexed again, the counter will be reset back to the maximum value followed by a refresh request for the corresponding memory row; otherwise, the indexed counter value simply decrements by one. The refresh request is immediately sent to the pending refresh request queue for dispatching a refresh operation. Without any memory accesses issued by the memory controller, the refresh policy is similar to a distributed refresh policy, with each refresh operation performing a burst refresh for N memory rows, the same size of pending refresh request queue.

The above solution ensures that the number of counters accessed simultaneously is equal to the number of segments (N) chosen. This makes sure that we do not have more than N refreshes pending in the pending refresh queue simultaneously. In Section 3.4 we show that the for DRAMs with refresh time of 32ms, the time interval between accessing counters is enough for completing the refreshes in the pending refresh request queue. This proof for the 32ms case automatically proves the 64ms case. This staggering algorithm also ensures accesses to counters at regular intervals and thus the staggering will not reduce over time, avoiding any possible situation where burst refresh may occur.

Now let us assume there are normal accesses intersperse with refresh operations. Whenever a memory row is accessed by normal reads or writes, the counter corresponding to the row will be reset to the maximum value. Thus refresh operation to the counter will be

Figure 4. Smart Refresh Correctness

delayed until it counts down to zero. Our staggered countdown mechanism guarantees that another refresh only takes place 64ms after the row has been accessed instead of a regular refresh period. This delaying of refresh of memory rows that are being accessed enables Smart Refresh to save significant amount of refresh energy if enough rows are accessed.

The size of the counter is chosen to be 2 bits for our explanation for the technique. We actually used a 3-bit counter for our simulations. The size of the counter determines the granularity with which the refresh operations can be controlled. A larger sized counter will need more steps to count down and allow more finer grained control over how much time the refresh operation can be delayed once the corresponding row is accessed. This will lead to potentially greater power savings at the cost of maintaining and accessing a bigger counter array.

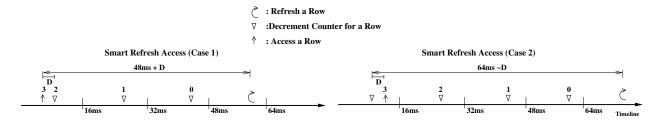

### 3.3.3 Smart Refresh Correctness

We prove that for an arbitrary access pattern the Smart Refresh scheme always refreshes the data within the refresh interval deadline. The proof for this is pictorially described in Figure 4. For the example shown in the figure the refresh interval chosen is 64 ms and the counter is 2 bits wide. The figure just shows the Smart Refresh technique is applied to one particular memory row and its associated counter. The inverted triangles show the times when the counter is decremented. The number above the triangle represent the counter value after it was decremented. As explained earlier, the counter is decremented exactly once within 16ms. We can have only two possible cases for an access to this row. The figure shows that in both cases the row will guarantee be refreshed within 64ms.

In the first case on the left-hand side, the row is accessed D ms before it is decremented. The access is denoted by an upward arrow. Note that D < 16ms. An access to the row resets the counter to its maximum value 3. After D ms the counter is indexed and decremented to 2. From the time-line progression the counter becomes  $\theta$  in D + 32 ms. Thus when the counter is accessed again at D + 48 ms, the memory controller sees a  $\theta$  and refreshes the row. Therefore, in this case the row is refreshed after D + 48 ms after it is accessed and meets the deadline of 64ms.

The second possible case is that the row is accessed *D* ms after the counter is decremented as shown in the right-hand side. The counter value becomes 3 on the access. It gets decremented to 2 at 16ms -D, and 0 at 48ms - D after its access. Finally, it is refreshed at 64ms -D after it was accessed. Since this is less than 64ms, the refresh is effective.

For a D greater than 16ms, the scenario can be reduced to either Case 1 or Case 2 by subtracting 16ms from D repeatedly until D is smaller than 16ms. Therefore, we show that in all possible access patterns, the row will always be refreshed before its data retention deadline.

# 3.3.4 Optimality of Smart Refresh

We define optimality for refresh as a metric of how close a DRAM row is refreshed to the data retention deadline. Thus an ideal scheme where each row is refreshed exactly after 64ms is said to be 100% optimal. In the Smart Refresh case, the optimality of the scheme depends on the number of bits we use for each counter. We can easily see from Section 3.3.3, if we use a two-bit counter for every row, the least optimal case will be when all the rows are refreshed at 48ms + D where D is close to zero. Thus the optimality of Smart Refresh for a 2 bit counter is 48/64 = 75%. Similarly for a 3 bit counter the worst case comes when each row is refreshed at 56ms. Thus the optimality of Smart Refresh for a 3 bit counter is 87.5%. The general optimality formula is a function of the counting

granularity and can be given by:

$$Optimality = \left[1 - \frac{1}{2^{N_{bits\_per\_counter}}}\right] * 100\%$$

### 3.3.5 Smart Refresh Technique for 3D DRAM

3D die stacking is an emerging technology that vertically integrates two or more die with inter-die vias [14, 16, 27, 28, 98]. These vias serve both as a fast communication interface and a stability providing mechanism to the stacked die structure. 3D die stacking reduces wire length and provides tight, high-speed coupling of die designed and manufactured with incompatible technologies. One immediate application is to integrate 3D diestacked DRAMs with processor cores to alleviate the memory latencies and global wire power consumption by replacing long on-board wires with short, fast inter-die vias [27].

The refresh operation will be a major overhead for 3D DRAMs. The operating temperature of the 3D DRAM will likely be much higher than their conventional DRAM counterpart. As shown in [27], a 64MB 3D DRAM will raise its operating temperature to 90.27°C. According to [83], the refresh rate must be doubled after the temperature exceeds 85°C in order to retain data. Therefore, 3D DRAMs will have a higher refresh rate than conventional DRAMs, increasing the power consumption and potentially the access latency. On the other hand, another design trend could increase the number of accesses to the 3D DRAM compared to a conventional DRAM. As multi-layer DRAM is made possible to be integrated on the same package, it reduces the requirement of having a large L2 on the processor core for area/cost efficiency. The constraints on the size of the 3D DRAM is mainly the number of DRAM cells that can be fitted into the available die layers and the number SRAM tags that can be fitted into the processor die for accessing the 3D DRAM.

Another interesting aspect of 3D DRAMs is that it will be more frequently accessed. Thus the refresh operation will also have a noticeable performance overhead. Our Smart Refresh technique, in fact, uses the more frequent accesses to its advantage to significantly reduce the amount of refreshes required for a 3D DRAM implementation. In Section 3.6.2

we will discuss in more detail the performance and energy benefits of using a 3D DRAM.

### 3.3.6 Smart Refresh for embedded DRAMs

Embedded DRAMs are increasingly being used in modern SOCs. The main reason for their use is compatibility with the logic CMOS process enables them to be integrated on a SOC at a relatively low cost. This allows eDRAMs to offer higher bandwidth with wider on-chip memory buses. However, the refresh intervals in embedded DRAMs are an order of magnitude shorter than conventional DRAM. A typical refresh interval for an NEC eDRAM is 4ms [8], and for an IBM eDRAM implementation is  $64\mu s$  [71]. Since the comventional DRAMs have refresh overhead of 64ms, embedded DRAMs need to be refreshed 16 times (for 4ms) or 1000 (for  $64\mu s$ ) times more frequently. This increases the overhead of refresh of an embedded DRAM by an order of magnitude compared to conventional DRAMs.

However, since embedded DRAMs are faster than their conventional counterparts, they will be typically accessed more often. This increasing access frequency significantly increases the opportunity of our Smart Refresh technique to save more energy. Furthermore, since in the embedded DRAM case the refresh operation is a major impediment to DRAM availability for normal accesses, the Smart Refresh technique will have a big impact in improving DRAM availability and hence system performance.

### 3.3.7 Disabling Smart Refresh