# IMPROVING PROCESSOR EFFICIENCY BY EXPLOITING COMMON-CASE BEHAVIORS OF MEMORY INSTRUCTIONS

A Thesis Presented to The Academic Faculty

by

Samantika Subramaniam

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology May 2009

# IMPROVING PROCESSOR EFFICIENCY BY EXPLOITING COMMON-CASE BEHAVIORS OF MEMORY INSTRUCTIONS

Approved by:

Professor Gabriel H. Loh, Advisor School of Computer Science Georgia Institute of Technology

Professor Milos Prvulovic School of Computer Science Georgia Institute of Technology

Professor Hyesoon Kim School of Computer Science Georgia Institute of Technology Professor Nathan Clark School of Computer Science Georgia Institute of Technology

Professor Hsien-Hsin S. Lee School of Electrical and Computer Engineering Georgia Institute of Technology

Aamer Jaleel, PhD Intel Corporation

Date Approved: 10 December 2008

To my family, for their unconditional love and support

# ACKNOWLEDGEMENTS

I take this opportunity to express my deepest gratitude to Professor Gabriel H. Loh, my thesis adviser for his unwavering support, immense patience and excellent guidance. Collaborating with him has been a tremendous learning experience and has been instrumental in shaping my future research career. I will especially remember him for his endless energy and superb guidance and thank him for continually bringing out the best in me. I thank Professor Milos Prvulovic for helping me throughout this journey, by being an excellent teacher and a helpful co-author as well as for providing me very useful feedback on my research ideas, presentations, thesis and general career decisions. I thank Professor Hsien-Hsien S. Lee for his excellent insights and tips throughout our research collaboration. He has always been a wealth of information to me and has helped me become a better researcher. I thank Professor Hyesoon Kim for her invaluable suggestions during my thesis proposal, dissertation writing and for always responding promptly to my requests. I thank Professor Nathan Clark for agreeing to serve on my thesis committee and for his feedback to help improve my work. I thank Aamer Jaleel from Intel Corporation for taking the time to be the external member on my thesis committee.

I would like to thank my friends, Kiran, Guru, Ioannis D, Rahul, Jon, Yuejien, Richard, Mrinmoy, Dong Hyuk, Dean, Gopi, Ioannis S, Carina and countless other friends and colleagues that I have met at Georgia Tech and who have supported me throughout. I thank Susie McClain, Deborah Mitchell, Becky Wilson and Alan Glass for their assistance in administrative matters and for providing me guidance throughout my time at Georgia Tech. I thank the various program committees and reviewers for their constructive feedback on my research papers. I thank Intel Corporation for research equipment, awarding me a fellowship to pursue my graduate studies and for hiring me as an intern with the MTL group in Santa Clara. This experience contributed greatly to my research career. I would also like to thank Georgia Tech and the College of Computing for giving me the opportunity and the infrastructure to pursue my graduate studies at this prestigious university.

I thank my parents, Mohana and Seetharam Subramaniam for being my pillars of strength throughout this journey. I thank my sister Menaka, my brother-in-law Vikram, my niece Kavya, my grandmother Visalakshi, my grandaunt Jayalakshmi, my mother-in-law Mangala and other family members for being tremendous sources of support and encouragement. I thank my late grandfather, Ramachandran, for his support and blessings all my life. Finally I would like to thank Sankar, my husband, for his endless love and support throughout my graduate career.

# TABLE OF CONTENTS

| DED  | ICAT | TION .   |                                                                                 | iii |

|------|------|----------|---------------------------------------------------------------------------------|-----|

| ACK  | NOW  | LEDG     | EMENTS                                                                          | iv  |

| LIST | OF 7 | TABLE    | NS                                                                              | xi  |

| LIST | OF   | FIGUR    | ES                                                                              | xii |

| SUM  | MAR  | Υ        |                                                                                 | xvi |

| Ι    | INT  | RODU     | CTION                                                                           | 1   |

|      | 1.1  |          | ation                                                                           | 1   |

|      | 1.2  | Efficier | ncy of Current Processors                                                       | 1   |

|      | 1.3  | Memor    | ry Instruction Processing                                                       | 2   |

|      |      | 1.3.1    | Conservativeness in Memory Instruction Processing                               | 2   |

|      |      | 1.3.2    | Scalability Concerns                                                            | 4   |

|      |      | 1.3.3    | Multi-threaded Microarchitectures                                               | 5   |

|      | 1.4  | Memor    | ry Instruction Behaviors                                                        | 6   |

|      |      | 1.4.1    | Predictability in Memory Dependencies                                           | 6   |

|      |      | 1.4.2    | Predictability in Data Forwarding                                               | 6   |

|      |      | 1.4.3    | Predictability in Instruction Criticality                                       | 7   |

|      |      | 1.4.4    | Conservative Allocation and Deallocation Policies                               | 8   |

|      | 1.5  | Scope    | and Overview of the Dissertation                                                | 8   |

|      |      | 1.5.1    | Scope                                                                           | 8   |

|      |      | 1.5.2    | Overview of Dissertation                                                        | 9   |

| II   | AN ( | OVERV    | VIEW OF MEMORY INSTRUCTION BEHAVIOR                                             | 11  |

|      | 2.1  | Specul   | ative Memory Disambiguation and Memory Dependencies $\ . \ . \ .$               | 11  |

|      | 2.2  | Load a   | and Store Queues and Data Forwarding Patterns                                   | 13  |

|      | 2.3  | Instruc  | ction Criticality and Criticality-Aware Load Execution                          | 15  |

|      | 2.4  | Alloca   | tion and Deallocation Constraints Imposed on Load and Store Queues              | 16  |

|      | 2.5  |          | ing Characteristics of Memory Behavioral Patterns to Improve Pro-<br>Efficiency | 18  |

| III |     |        | ECTORS: DESIGNING A SCALABLE, EFFICIENT, AND HIGH-<br>IANCE MEMORY DEPENDENCE PREDICTOR                               | 9 |

|-----|-----|--------|-----------------------------------------------------------------------------------------------------------------------|---|

|     | 3.1 | Introd | luction                                                                                                               | 9 |

|     | 3.2 | Backg  | round                                                                                                                 | 0 |

|     |     | 3.2.1  | Memory Dependence Predictors                                                                                          | D |

|     |     | 3.2.2  | Store Sets                                                                                                            | 2 |

|     |     | 3.2.3  | Scheduling Structures                                                                                                 | 6 |

|     | 3.3 | Store  | Vector Dependence Prediction                                                                                          | 7 |

|     |     | 3.3.1  | Step-by-Step Operation                                                                                                | 8 |

|     |     | 3.3.2  | Example                                                                                                               | D |

|     | 3.4 | Evalua | ation $\ldots \ldots 32$                        | 2 |

|     |     | 3.4.1  | Methodology                                                                                                           | 2 |

|     |     | 3.4.2  | Performance Results                                                                                                   | 3 |

|     | 3.5 | Optim  | nizations                                                                                                             | 0 |

|     |     | 3.5.1  | Sensitivity to Hardware Budget 40                                                                                     | D |

|     |     | 3.5.2  | Reduction of Store Vector Length                                                                                      | 1 |

|     |     | 3.5.3  | Most Recently Conflicting store                                                                                       | 3 |

|     |     | 3.5.4  | Store Window                                                                                                          | 4 |

|     |     | 3.5.5  | Tagged SVT                                                                                                            | 5 |

|     |     | 3.5.6  | Effect of Incorporating Control Flow Information                                                                      | б |

|     | 3.6 | Why I  | Do Store Vectors Work?                                                                                                | 7 |

|     | 3.7 | Imple  | mentation Complexity                                                                                                  | D |

|     | 3.8 | Concl  | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $52$                                                                       | 2 |

| IV  |     |        | PLYING PREDICTABILITY OF MEMORY DEPENDENCES IN SI-<br>COUS MULTI-THREADED PROCESSORS                                  | 4 |

|     | 4.1 | Introd | luction $\ldots \ldots 54$ | 4 |

|     | 4.2 | Backg  | round $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $56$                                                      | ô |

|     |     | 4.2.1  | SMT Fetch Policies and Resource Stalls                                                                                | ô |

|     |     | 4.2.2  | Memory Dependences and SMT                                                                                            | 3 |

|     | 4.3 | Adapt  | ing SMT Fetch Policies to Exploit Memory Dependences 60                                                               | 0 |

|     |     | 4.3.1  | Proactive Exclusion                                                                                                   | 1 |

|   |     | 4.3.2   | Leniency and Early Parole                                            | 63  |

|---|-----|---------|----------------------------------------------------------------------|-----|

|   | 4.4 | Evalua  | ation                                                                | 66  |

|   |     | 4.4.1   | Methodology                                                          | 66  |

|   |     | 4.4.2   | Proactive Exclusion Only                                             | 68  |

|   |     | 4.4.3   | Proactive Exclusion with Early Parole (PEEP)                         | 69  |

|   |     | 4.4.4   | Fairness Results                                                     | 72  |

|   | 4.5 | PEEP    | on an SMT Processor without Speculative Memory Disambiguation        | 74  |

|   | 4.6 | Sensit  | ivity Analysis                                                       | 76  |

|   |     | 4.6.1   | Sensitivity to Multithreading                                        | 76  |

|   |     | 4.6.2   | Scalability of PEEP                                                  | 78  |

|   |     | 4.6.3   | PEEP Combined with Other Fetch Policies                              | 78  |

|   |     | 4.6.4   | Delay Sensitivity                                                    | 79  |

|   | 4.7 | Evalua  | ating PEEP in an Industrial Simulator                                | 81  |

|   | 4.8 | Conclu  | usions                                                               | 84  |

| V |     |         | -FORGET: IMPLEMENTING SCALABLE STORE TO LOAD FOR-                    | 85  |

|   | 5.1 | Introd  | uction                                                               | 85  |

|   | 5.2 | Backg   | round                                                                | 86  |

|   |     | 5.2.1   | Conventional Load and Store Queues                                   | 86  |

|   |     | 5.2.2   | Load Re-Execution                                                    | 87  |

|   |     | 5.2.3   | Other Related Work                                                   | 91  |

|   | 5.3 | Fire-a  | nd-Forget Store-to-Load Forwarding                                   | 94  |

|   |     | 5.3.1   | Load Queue Index Prediction                                          | 94  |

|   |     | 5.3.2   | Complete Store Queue Elimination                                     | 97  |

|   |     | 5.3.3   | Speculative Memory Cloaking                                          | 99  |

|   |     | 5.3.4   | Corner Cases and Loose Ends                                          | 100 |

|   | 5.4 | Evalua  | ation                                                                | 100 |

|   |     | 5.4.1   | Methodology                                                          | 101 |

|   |     | 5.4.2   | Performance Results                                                  | 103 |

|   |     | 5.4.3   | Scalability of FnF: Performance analysis over a medium configuration | 104 |

|   | 5.5 | Specifi | ic Case Studies                                                      | 104 |

|    |      | 5.5.1  | A Good Example                                                          | 104 |

|----|------|--------|-------------------------------------------------------------------------|-----|

|    |      | 5.5.2  | A Neutral Example                                                       | 105 |

|    |      | 5.5.3  | An Extreme Example                                                      | 106 |

|    |      | 5.5.4  | A Misbehaving Example                                                   | 107 |

|    | 5.6  | Power, | Area and Latency considerations                                         | 107 |

|    | 5.7  | Specul | ative Stores to Improve FnF Efficiency                                  | 108 |

|    | 5.8  | FnF_R  | OB: Load/Store Scheduling without a Store Queue or a Load Queue         | 114 |

|    | 5.9  | NoSQ   |                                                                         | 117 |

|    | 5.10 | Conclu | sions                                                                   | 119 |

| VI |      |        | CRITICALITY PREDICTION FOR EFFICIENT LOAD INSTRUC                       | !_  |

|    | TIO  | N PRO  | CESSING                                                                 | 120 |

|    | 6.1  |        | uction                                                                  | 120 |

|    | 6.2  | Backgr | round                                                                   | 122 |

|    |      | 6.2.1  | Instruction (and Load) Criticality                                      | 122 |

|    |      | 6.2.2  | Predicting Instruction Criticality                                      | 123 |

|    | 6.3  | Our Lo | pad-Criticality Predictor                                               | 125 |

|    |      | 6.3.1  | Basic Operational Description                                           | 125 |

|    |      | 6.3.2  | Example                                                                 | 126 |

|    |      | 6.3.3  | Issue-Rate Filtering of the Predictor                                   | 128 |

|    |      | 6.3.4  | Intuition for Predictor Effectiveness                                   | 131 |

|    | 6.4  | Simula | tion Methodology                                                        | 132 |

|    | 6.5  | Optim  | ization Class 1: Faking the Performance of a Second Load Port $\ . \ .$ | 133 |

|    |      | 6.5.1  | Problem Description                                                     | 133 |

|    |      | 6.5.2  | Implementation Details                                                  | 134 |

|    |      | 6.5.3  | Performance Evaluation                                                  | 137 |

|    |      | 6.5.4  | Why Does FSLP Work?                                                     | 138 |

|    | 6.6  | Optimi | ization Class 2: Data Forwarding and Memory Disambiguation $\ . \ .$    | 140 |

|    |      | 6.6.1  | Data Forwarding                                                         | 140 |

|    |      | 6.6.2  | Memory Disambiguation and Memory Dependence Prediction                  | 141 |

|    | 6.7  | Optimi | ization Class 3: Data Cache                                             | 142 |

|    |      | 6.7.1  | Insertion Policy for Non-Critical Loads                                 | 142 |

|      |     | 6.7.2  | Cache Bypassing for Non-Critical Loads                                                                                               |

|------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------|

|      |     | 6.7.3  | Prefetching Policy for Non-Critical Loads                                                                                            |

|      |     | 6.7.4  | Performance Evaluation                                                                                                               |

|      | 6.8 | Comb   | ining Our Criticality-Based Load Optimizations                                                                                       |

|      | 6.9 | Concl  | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $148$                                                                                     |

| VII  |     |        | CLAYED ENTRY AND AGGRESSIVE DEALLOCATION OF CRIT-<br>OURCES                                                                          |

|      | 7.1 | Introd | luction $\ldots \ldots 150$ |

|      | 7.2 | Backg  | $round \dots \dots$            |

|      |     | 7.2.1  | Case Study: Stalls at Allocation                                                                                                     |

|      |     | 7.2.2  | Case Study: Unnecessary Delays for Deallocation                                                                                      |

|      |     | 7.2.3  | Related Work                                                                                                                         |

|      |     | 7.2.4  | Why Not Build Larger LQ/SQs?                                                                                                         |

|      | 7.3 | Out-o  | f-Order Allocation through Deferred Entry 158                                                                                        |

|      |     | 7.3.1  | Description of the Technique                                                                                                         |

|      |     | 7.3.2  | Step-by-Step Operation                                                                                                               |

|      |     | 7.3.3  | Bonus: Extending DE to the Reservation Stations                                                                                      |

|      | 7.4 | Out-o  | f-Order Resource Release through Aggressive Deallocation 163                                                                         |

|      | 7.5 | Evalua | ation Methodology                                                                                                                    |

|      | 7.6 |        | ating the Application of Deferred Entry (DE) and Aggressive Deal-<br>on (AD) in Critical Microarchitectural Resources                |

|      |     |        |                                                                                                                                      |

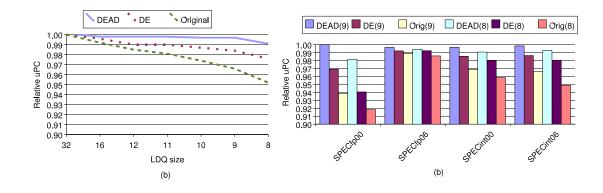

|      |     | 7.6.1  | Impact of DEAD on LQ 168                                                                                                             |

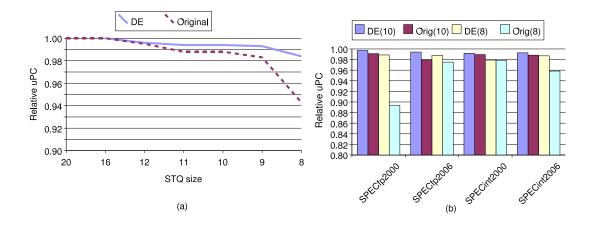

|      |     | 7.6.2  | Impact of DE on SQ $\dots$ 170                                                                                                       |

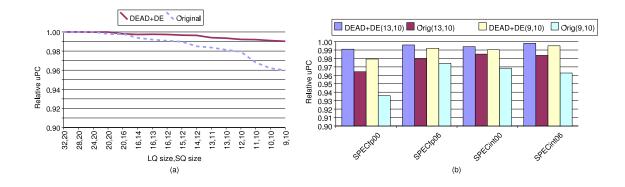

|      |     | 7.6.3  | Simultaneous Application of DEAD to LQ and SQ                                                                                        |

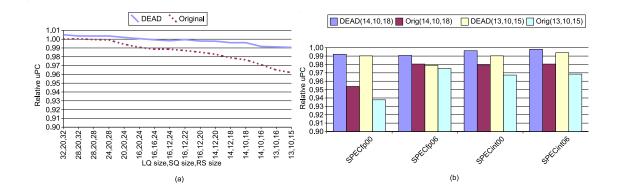

|      |     | 7.6.4  | Applying DEAD to LQ, SQ and RS                                                                                                       |

|      | 7.7 |        | arison with Scalable $LQ/SQs$                                                                                                        |

|      | 7.8 | Conclu | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $178$                                                                                     |

| VIII | SUN | IMARY  | Y AND CONCLUSION 180                                                                                                                 |

| IX   | APF | PENDE  | X                                                                                                                                    |

| REF  | ERE | NCES . |                                                                                                                                      |

# LIST OF TABLES

| 1  | Simulated processor configurations.                                                                                                                                                                                                                                                     | 33  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | The performance of the memory dependence predictors simulated<br>on the 'medium' configuration for the entire set of applications.<br>An 'x' signifies that the benchmark is dependency sensitive $(> 1\%$<br>performance change between blind prediction and perfect predic-<br>tion). | 36  |

| 3  | Continuation of the data from Table 2.                                                                                                                                                                                                                                                  | 37  |

| 4  | Simulated four-way SMT processor configuration.                                                                                                                                                                                                                                         | 67  |

| 5  | Multi-programmed application mixes used for the four-threaded experiments.                                                                                                                                                                                                              | 67  |

| 6  | Two-threaded workloads.                                                                                                                                                                                                                                                                 | 77  |

| 7  | Average ready-to-issue delay in cycles for critical (CL) and non-<br>critical loads (NCL).                                                                                                                                                                                              | 139 |

| 8  | Relative power contribution of different processor blocks. For the out-of-order and memory blocks, we include the individual power for some key units. The percentage contribution of these sub-units is already included in the macro-block's total.                                   | 167 |

| 9  | The performance of the memory dependence predictors simulated on the 'large' configuration for the entire set of applications. An 'x' signifies that the benchmark is dependency sensitive (> 1% performance change between blind prediction and perfect prediction).                   | 184 |

| 10 | Continuation of the data from Table 9                                                                                                                                                                                                                                                   | 185 |

| 11 | The performance of the memory dependence predictors simulated on the 'extra-large' configuration for the entire set of applications. An 'x' signifies that the benchmark is dependency sensitive (> 1% performance change between blind prediction and perfect prediction).             | 186 |

| 12 | Continuation of the data from Table 11.                                                                                                                                                                                                                                                 | 187 |

# LIST OF FIGURES

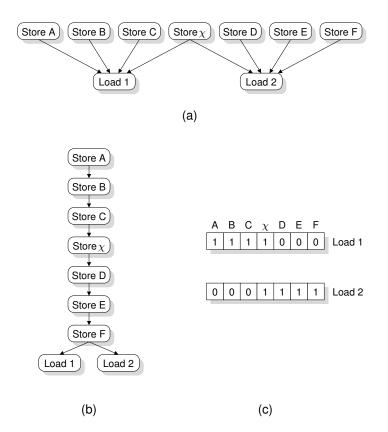

| 1  | Example showing the ambiguous dependence that can arise between memory instructions.                                                                                                                                                             | 12 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Dataflow graph that depicts how delaying the execution of some instructions increases the critical path.                                                                                                                                         | 15 |

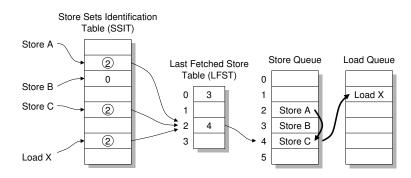

| 3  | Store sets data structures and their interactions                                                                                                                                                                                                | 23 |

| 4  | Store Sets implementation using a (a) CAM-based fully-associative organization and (b) a RAM-based direct-mapped organization.                                                                                                                   | 24 |

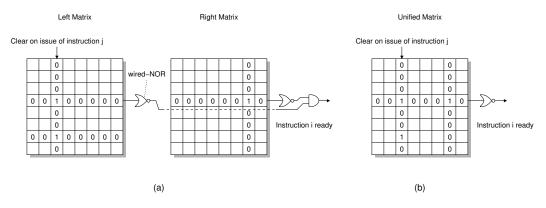

| 5  | (a) Two-matrix scheduler, (b) single-matrix unified scheduler                                                                                                                                                                                    | 26 |

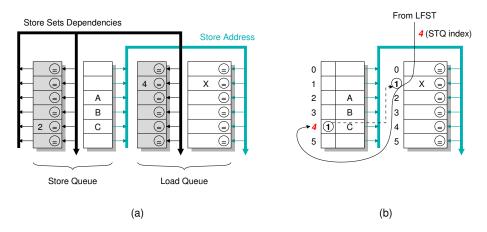

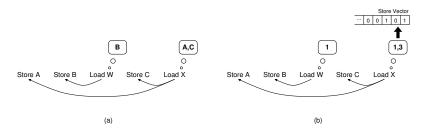

| 6  | (a) Store-address tracking of dependencies, and (b) store position or age tracking of dependencies.                                                                                                                                              | 27 |

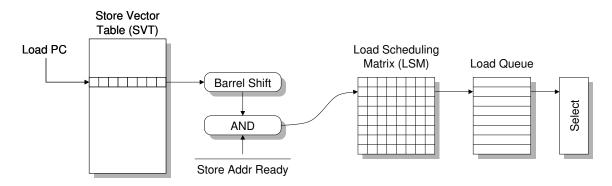

| 7  | Store vectors data structures and interaction with a conventional load queue.                                                                                                                                                                    | 28 |

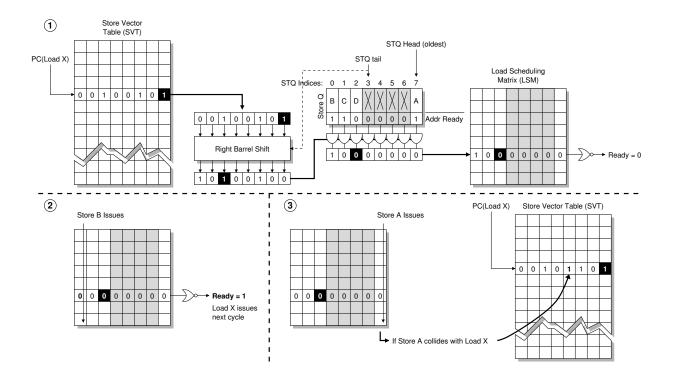

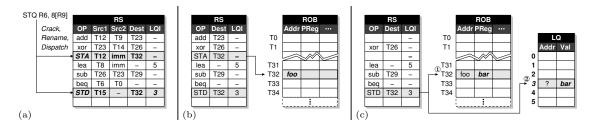

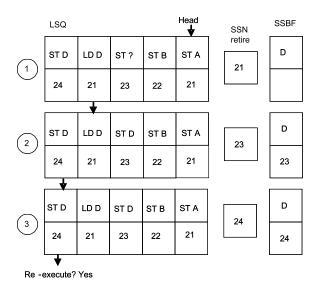

| 8  | Example Store Vector operation for the ① prediction phase, ② scheduling phase, and ③ update phase.                                                                                                                                               | 30 |

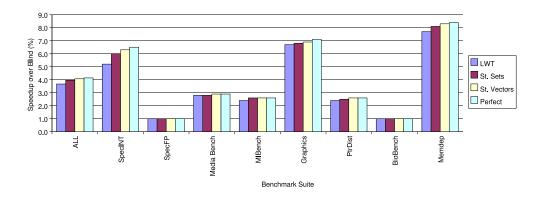

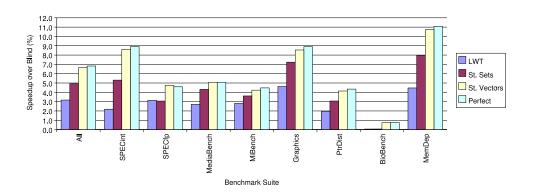

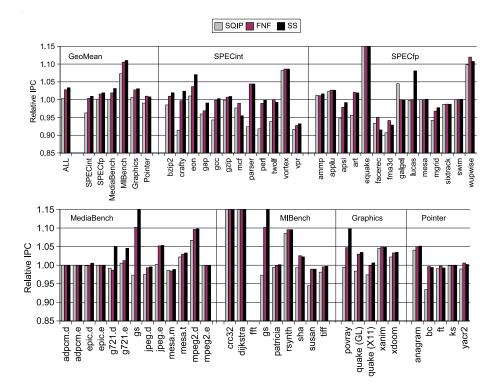

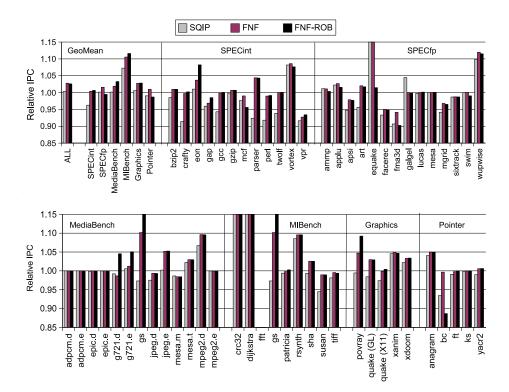

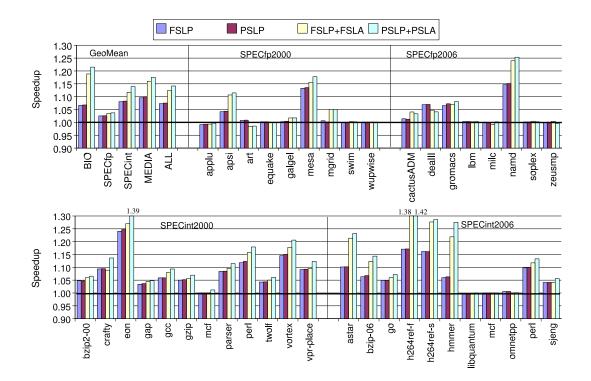

| 9  | Performance of the 'medium' sized configuration across all benchmark suites.<br>Memdep refers to those applications which were found to exhibit memory<br>dependence-sensitivity.                                                                | 34 |

| 10 | Performance of the 'large' sized configuration across all benchmark suites.<br>Memdep refers to those applications which were found to exhibit memory<br>dependence-sensitivity.                                                                 | 34 |

| 11 | Performance of the 'extra-large' sized configuration across all benchmark<br>suites. Memdep refers to those applications which were found to exhibit<br>memory dependence-sensitivity.                                                           | 34 |

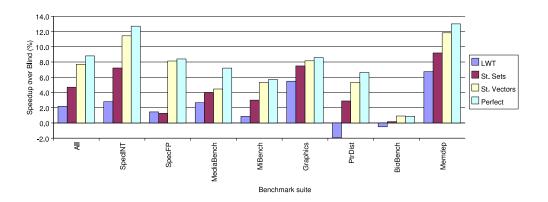

| 12 | S-curves illustrating the range of performance behavior of the simulated mem-<br>ory dependence predictors across all benchmarks for the extra-large configu-<br>ration.                                                                         | 39 |

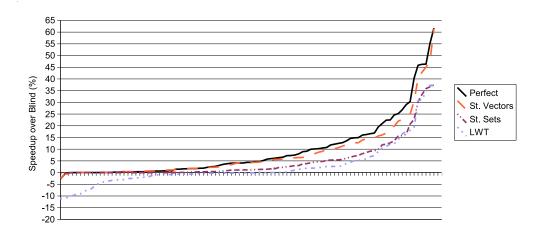

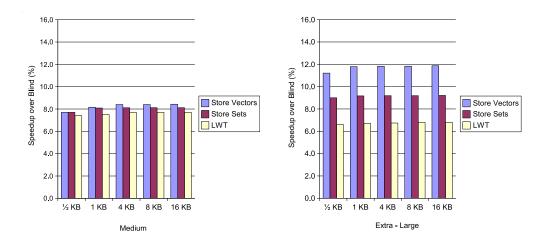

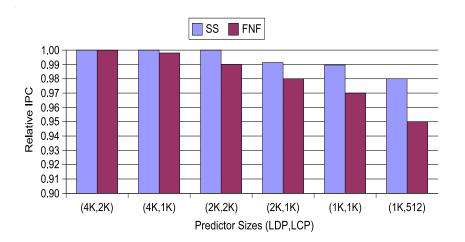

| 13 | Speedup over blind prediction for the memory dependence-sensitive bench-<br>marks of proposed memory dependence predictors across different hardware<br>budgets.                                                                                 | 41 |

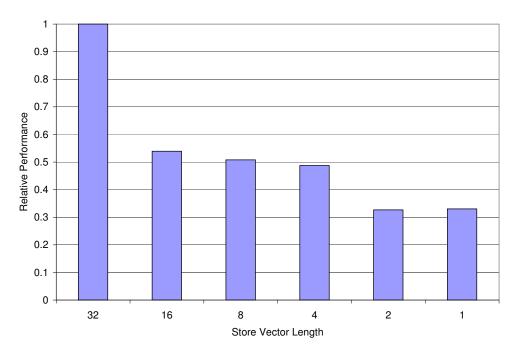

| 14 | The relative performance impact of reducing the length of the Store Vectors (dependence-sensitive applications only). Zero represents the performance with blind speculation, and 1.0 is the performance of the baseline Store Vector predictor. | 42 |

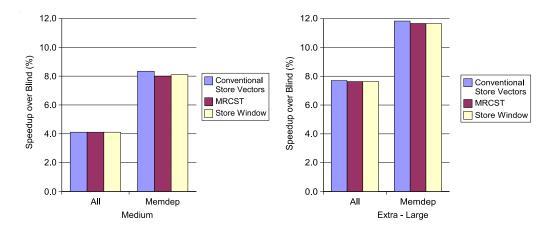

| 15 | Different Store Tracking Strategies. The second bar indicates the MRCST strategy and the third bar depicts the performance of the store window                                                                                                   |    |

|    | method.                                                                                                                                                                                                                                          | 43 |

| 16 | Performance of tagged SVT of different sizes compared with conventional untagged SVT. The first bar represents an 2KB untagged SVT. The second and third bars represent 0.625KB tagged SVT and 0.3125KB tagged SVT respectively while the fourth bar corresponds to a 0.1526KB tagged SVT storing only the MRCST.        | 45 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

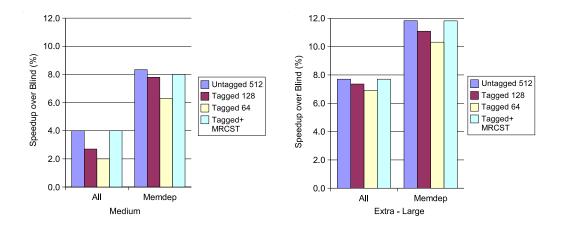

| 17 | (a) Ideal load synchronization against predicted store dependencies, and (b) actual serialization with Store Sets.                                                                                                                                                                                                       | 48 |

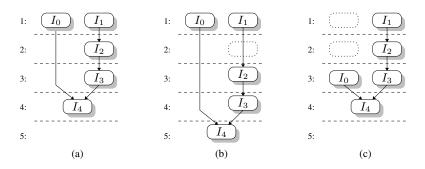

| 18 | (a) Ideal load synchronization for two loads against their predicted store dependencies, (b) actual serialization of merged Store Sets, and (c) the Store Vector values which avoid unnecessary serialization.                                                                                                           | 49 |

| 19 | Shared reservation station entries in an SMT processor can be completely occupied by a stalled thread when using simple fetch policies.                                                                                                                                                                                  | 57 |

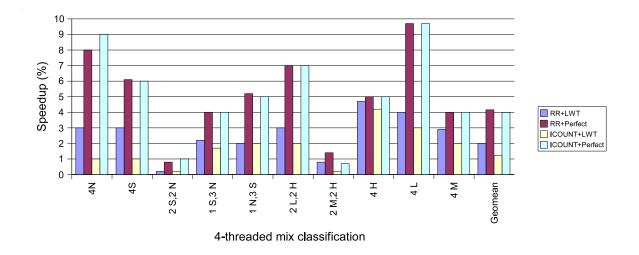

| 20 | Impact of speculative load disambiguation on an SMT machine. The speedups (throughput improvements) are relative to SMT machines running round-robin and ICOUNT policies with no speculative memory disambiguation. LWT is the load-wait table memory dependence predictor. Perfect prediction uses an oracle predictor. | 60 |

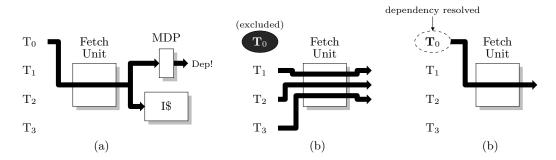

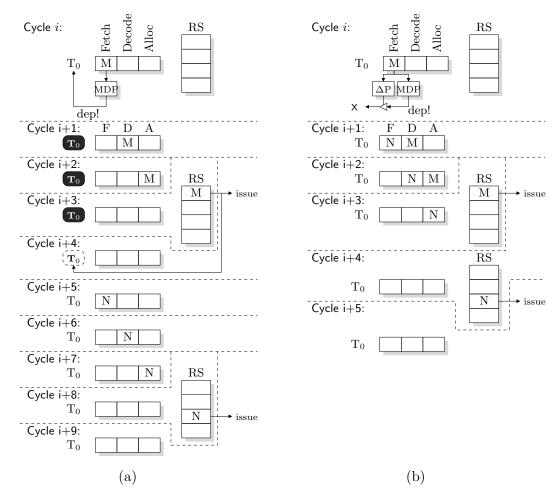

| 21 | Demonstration of Proactive Exclusion. (a) When fetching a load, a predicted memory dependence causes the thread $T_0$ (b) to be excluded from the list of fetch candidates. (c) Only when the dependence has been resolved does the thread's fetching resume.                                                            | 62 |

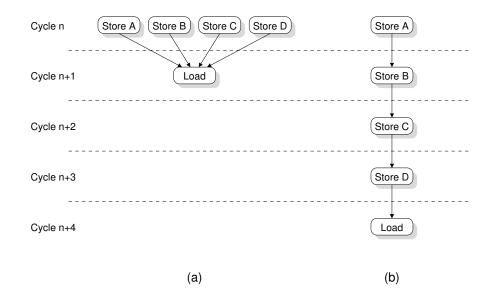

| 22 | Timing diagram illustrating additional delays induced by (a) excluding a thread when its resolution delay is very short, and (b) avoiding its exclusion.                                                                                                                                                                 | 64 |

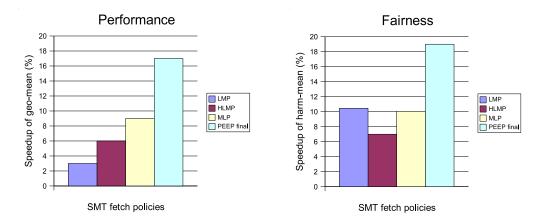

| 23 | Performance and fairness overview of the SMT fetch policies. PEEP <sub>final</sub> represents our proposed fetch policy after the previously described delay pre-<br>diction optimization                                                                                                                                | 66 |

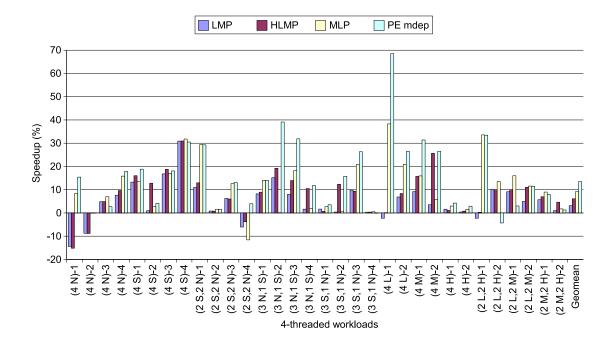

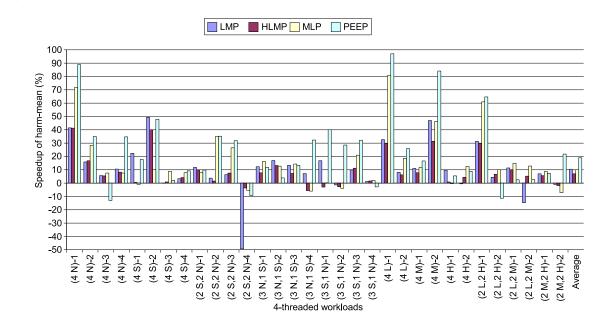

| 24 | Speedup over ICOUNT of the basic SMT fetch policies as well as the Proac-<br>tive Exclusion policy based on Memory Dependences without any delay pre-<br>diction.                                                                                                                                                        | 70 |

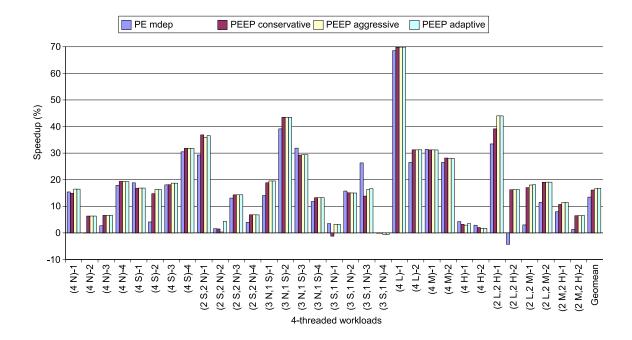

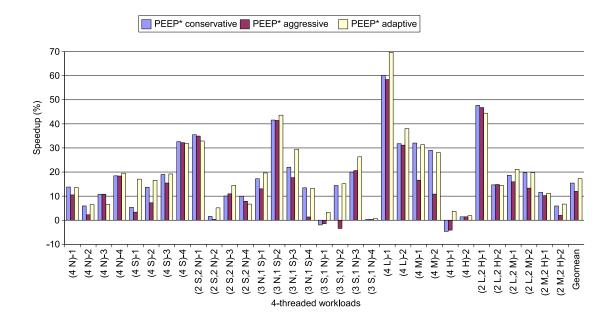

| 25 | Combining Proactive Exclusion and Early Parole with different delay predic-<br>tors                                                                                                                                                                                                                                      | 73 |

| 26 | Fairness as measured by the harmonic mean of weighted IPC                                                                                                                                                                                                                                                                | 75 |

| 27 | Benefit of memory dependence prediction without speculative load disambiguation.                                                                                                                                                                                                                                         | 76 |

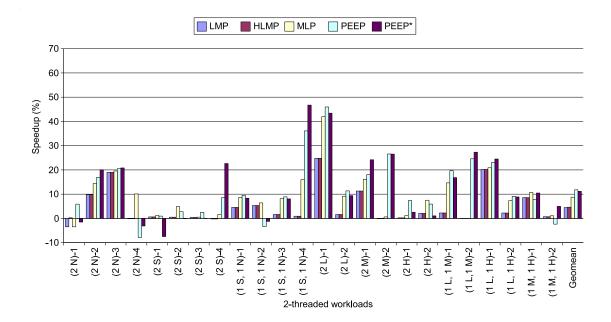

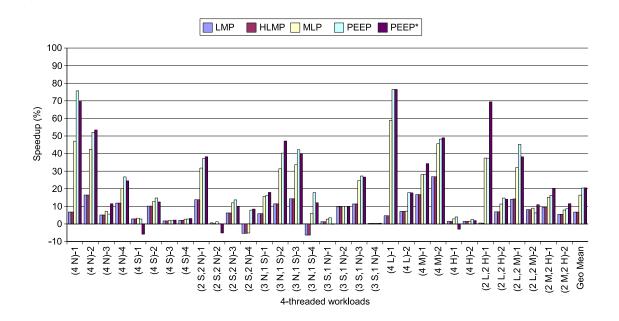

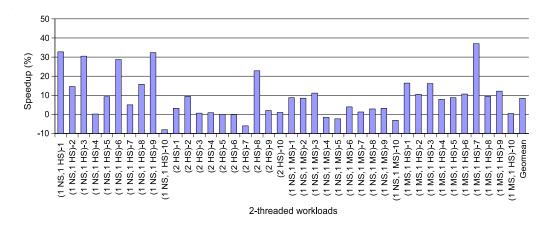

| 28 | Performance of the SMT fetch policies for two-threaded workloads                                                                                                                                                                                                                                                         | 77 |

| 29 | Performance of the SMT fetch policies on a large, aggressive processor con-<br>figuration                                                                                                                                                                                                                                | 79 |

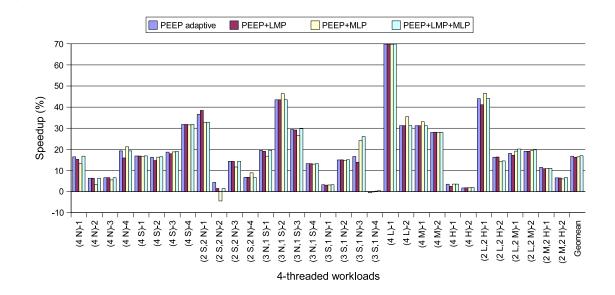

| 30 | Performance of PEEP combined with other fetch-gating policies                                                                                                                                                                                                                                                            | 80 |

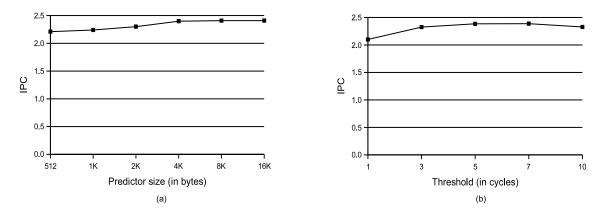

| 31 | Sensitivity of the policy to different predictor sizes and delay thresholds                                                                                                                                                                                                                                              | 80 |

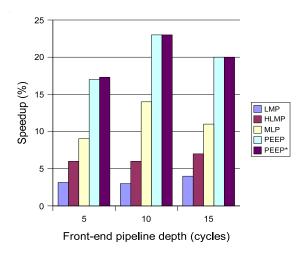

| 32 | Performance of the SMT fetch policies with larger front-end pipelines $\ldots$                                                                                                                                                                                                                                                                                           | 82  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

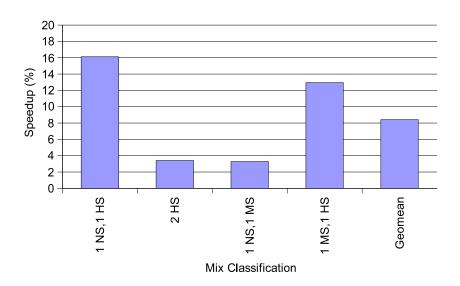

| 33 | Per-mix performance results as obtained in an IA32 simulator                                                                                                                                                                                                                                                                                                             | 83  |

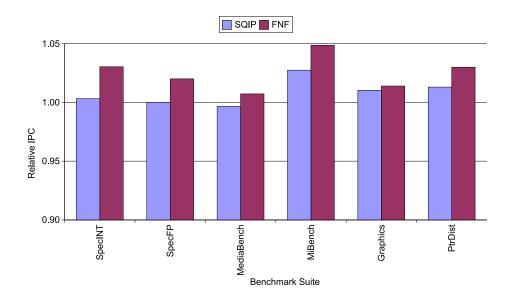

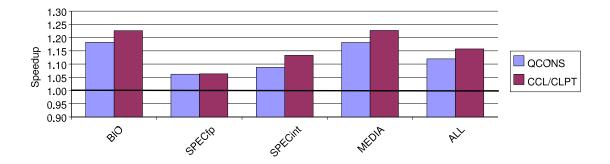

| 34 | Aggregate performance results per-mix type                                                                                                                                                                                                                                                                                                                               | 83  |

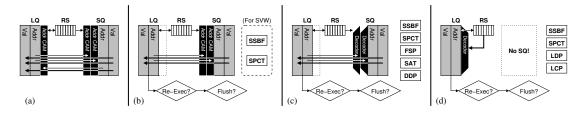

| 35 | Memory scheduler designs: (a) conventional fully-associative load and store queues, (b) non-associative load queue with optional SVW filtering, (c) Store Queue Index Prediction, and (d) Fire-and-Forget store forwarding                                                                                                                                               | 87  |

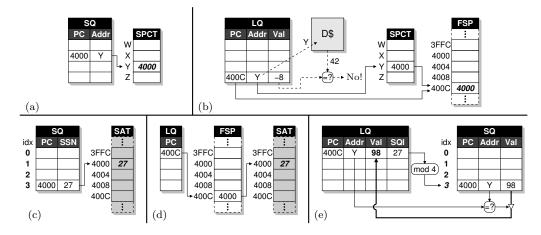

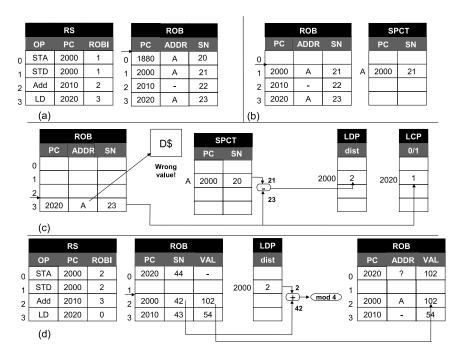

| 36 | Store Queue Index Prediction example illustrating (a) a store updating the SPCT, (b) a misforwarded load using the SPCT to update the FSP, (c) a later instance of the same store updating the SAT, (d), a later instance of the load using the FSP and SAT to compute a SQ index, and (e) the load using the predicted index to directly access the predicted SQ entry. | 92  |

| 37 | Fire-and-Forget example illustrating (a) a store tracking the LSN at dispatch,<br>(b) the store updating the SPCT at commit, (c) a misforwarded load tracking<br>its distance for future use by the store, (d) a later instance of the store<br>computing the index for the predicted LQ entry, and (e) forwarding a value<br>to the LQ entry.                           | 93  |

| 38 | An example of Fire-and-Forget without a store queue showing (a) cracking<br>and dispatch of a store, (b) store address tracking, and (c) store data tracking<br>and speculative forwarding                                                                                                                                                                               | 98  |

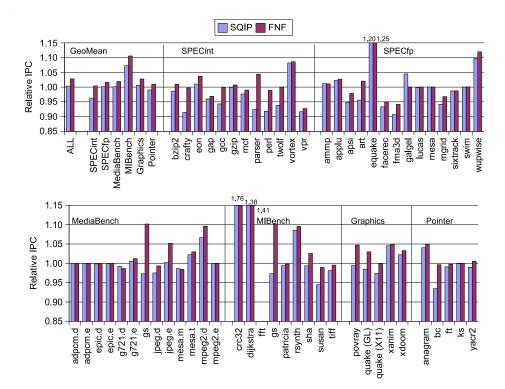

| 39 | Relative IPC performance over a fully-associative SQ                                                                                                                                                                                                                                                                                                                     | 102 |

| 40 | Relative performance of FnF and SQIP over the SVW mechanism for a medium sized machine                                                                                                                                                                                                                                                                                   | 105 |

| 41 | Working Example for Speculative Stores. (a) shows the working when simple SVW is applied and (b) shows the example when SVW is augmented with SS.                                                                                                                                                                                                                        | 109 |

| 42 | Store Re-execution in SS                                                                                                                                                                                                                                                                                                                                                 | 110 |

| 43 | Impact of Speculative Stores on FnF. The third bar shows the performance of the SS technique.                                                                                                                                                                                                                                                                            | 112 |

| 44 | Performance of SS and ${\rm FnF}({\rm base} {\rm ~algorithm})$ relative to baseline sizes $~$                                                                                                                                                                                                                                                                            | 112 |

| 45 | Implementing Fire-and-Forget with the ROB. Note that the SQ and the LQ have been eliminated.                                                                                                                                                                                                                                                                             | 113 |

| 46 | Implementing FnF without a LQ or a SQ. The third bar shows performance when FnF is implemented using only the ROB.                                                                                                                                                                                                                                                       | 116 |

| 47 | Example showing the collection of consumer counts and update to the pre-<br>diction table.                                                                                                                                                                                                                                                                               | 127 |

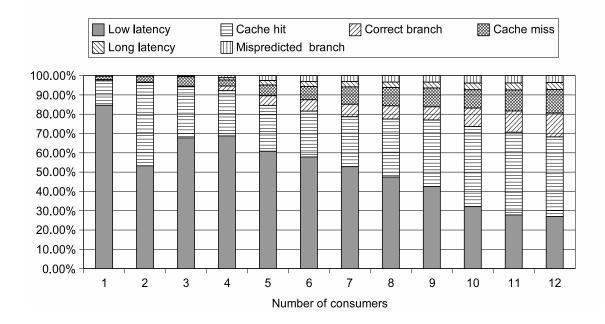

| 48 | Distribution of consumers (for different consumer count values) according to instruction type.                                                                                                                                                                                                                                                                           | 132 |

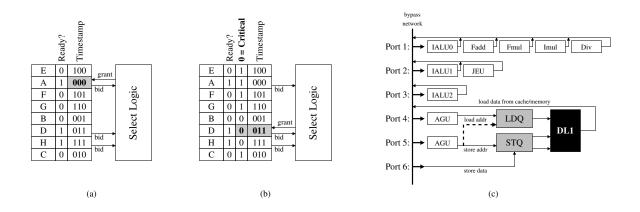

| 49 | (a) Conventional timestamp-based oldest-first select logic, (b) augmenting the select logic to support criticality-prioritized select, (c) issue port arrangement with modification to use the store address AGU for a second load. | 135 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 50 | Deferring non-critical loads to achieve the performance of a second load data port.                                                                                                                                                 | 136 |

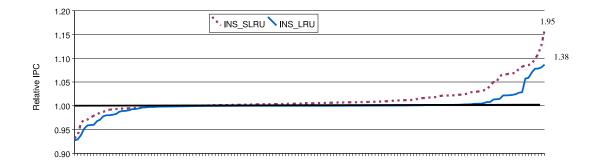

| 51 | Relative speedup across the applications when all data is brought into the LRU position (INS_LRU) and when only non-critical data is brought into the LRU position (INS_SLRU).                                                      | 142 |

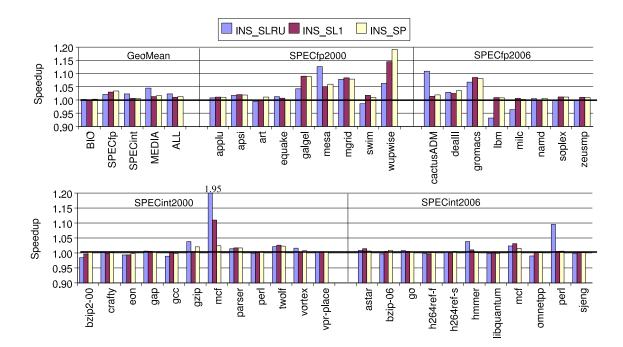

| 52 | Speedup when critical load prediction is employed to optimize the L1 data cache.                                                                                                                                                    | 145 |

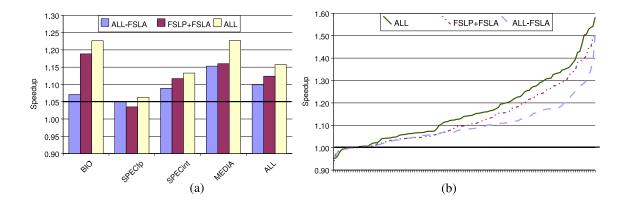

| 53 | Speedup when critical load prediction is applied to all optimizations together:<br>(a) per-suite averages and (b) S-curves for all benchmarks.                                                                                      | 147 |

| 54 | Speedup comparison of applying all proposed optimizations, but with differ-<br>ent underlying criticality predictors.                                                                                                               | 148 |

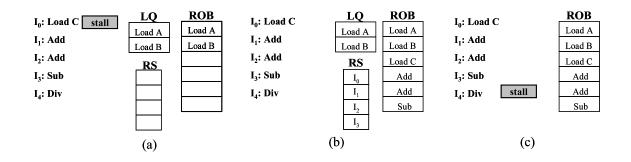

| 55 | Potential of OOO Alloc: (a)load allocation stalls due to full LQ, (b)allocation continues (c)allocation only stalls due to full ROB                                                                                                 | 152 |

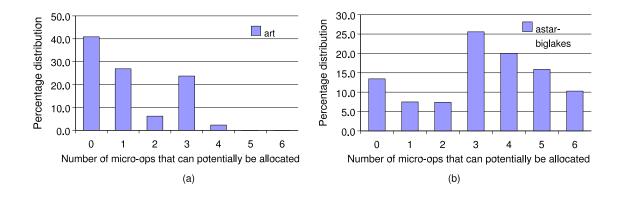

| 56 | Percentage distribution showing number of instructions that are ready to allocate when a (a) load is stalled due to full LQ (b) store is stalled due to full SQ                                                                     | 153 |

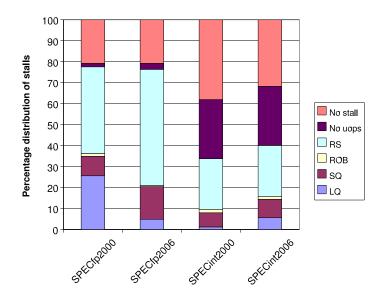

| 57 | Distribution of stall cycles at alloc for SPECcpu2000 and SPECcpu2006 applications                                                                                                                                                  | 154 |

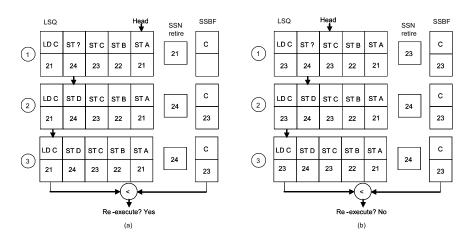

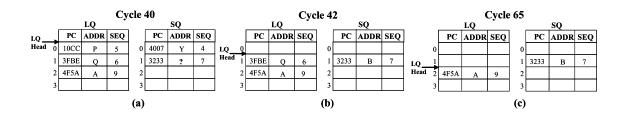

| 58 | Inefficiency of in-order deallocation:(a)load executes speculatively on cycle 40, (b)last store address resolves on cycle 42, (c)load is forced to wait until it is oldest load to deallocate on cycle 65                           | 155 |

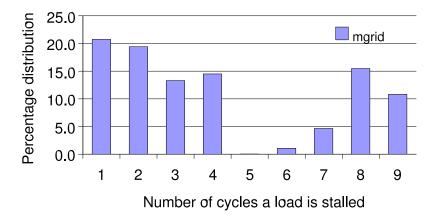

| 59 | Percentage distribution of stalls cycles when a load is forced to wait to deal-<br>locate                                                                                                                                           | 156 |

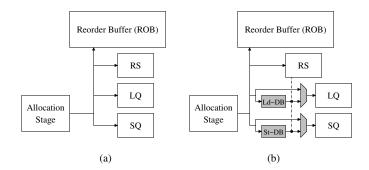

| 60 | (a) baseline processor and (b) changes for deferred entry. $\ldots$                                                                                                                                                                 | 159 |

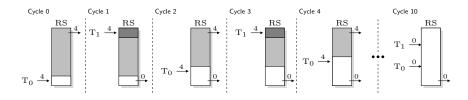

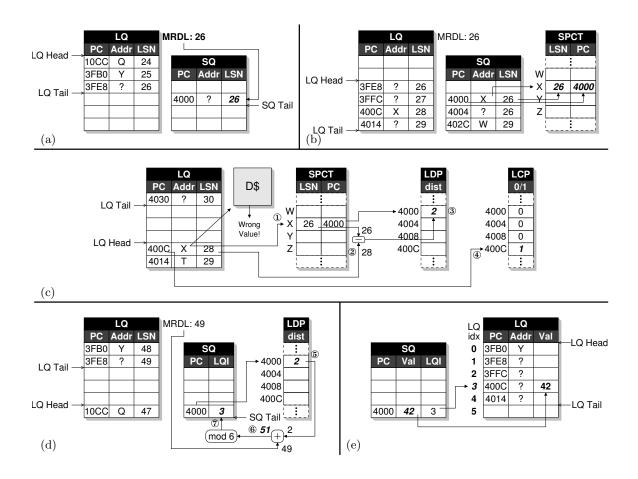

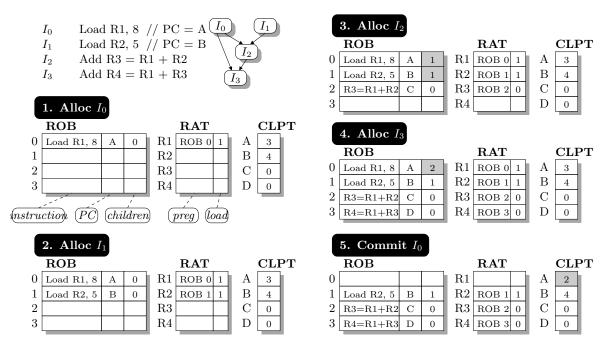

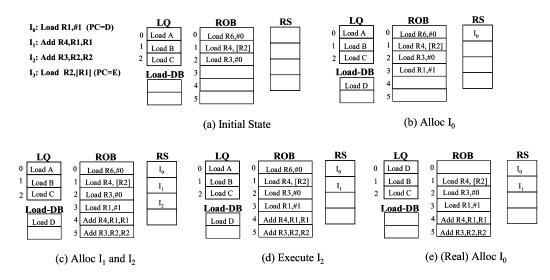

| 61 | Step-by-step example of Deferred Entry.                                                                                                                                                                                             | 161 |

| 62 | Performance impact of DEAD on LQ                                                                                                                                                                                                    | 168 |

| 63 | Performance impact of DE on SQ                                                                                                                                                                                                      | 170 |

| 64 | Performance impact of DEAD when simultaneously optimizing the LQ and SQ                                                                                                                                                             | 173 |

| 65 | Performance impact of DEAD when simultaneously optimizing the LQ, SQ and RS                                                                                                                                                         | 174 |

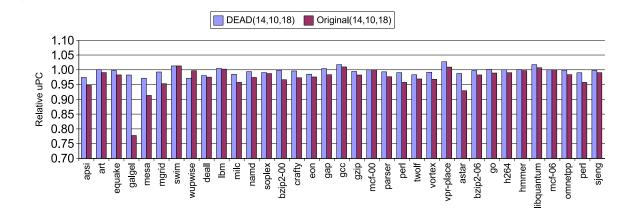

| 66 | Per-benchmark performance for final configuration.                                                                                                                                                                                  | 176 |

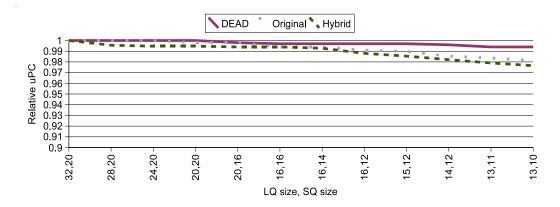

| 67 | Performance of the Hybrid Load and Store Queues, DEAD techniques for the<br>Load and Store Queues, and Original (Conventional) Load and Store Queues                                                                                | 179 |

|    |                                                                                                                                                                                                                                     |     |

### SUMMARY

Thesis statement: Processor efficiency can be improved by exploiting common-case and predictable behaviors of memory instructions.

The main contribution of this dissertation is exploring the impact of, and improving memory instruction processing to improve the efficiency of the processor. In particular, we propose and evaluate five techniques that tackle certain inefficiencies that exist in memory instruction processing units of conventional processors. Our proposals leverage certain commonly-occurring behavioral patterns in memory instructions which allow for relatively simple and scalable designs to improve processor efficiency.

One of the main aspects of this thesis is the study of memory dependence prediction. We explore the fundamental concepts in memory dependence prediction and propose, to the best of our knowledge, one of the most high-performing and power-efficient memory dependence predictors. Using the fundamental principles and benefits of memory dependence prediction, we then propose an application of it in simultaneous multi-threaded processors that reduces the resource contention in, and improves the performance of these processors.

In our third proposal, we focus on a useful corollary of the predictability in memory dependences, which is the predictability in memory data forwarding, to simplify, reduce and even eliminate some of the power-hungry and area-inefficient resources required by memory instructions in conventional processors. The designs proposed have low implementation complexity and high scalability.

We then focus our attention on another memory instruction behavioral pattern, that is predictability in instruction criticality and leverage this behavior to improve the performance of the processor as well as reduce its power consumption and area requirements. Finally we explore out-of-order allocation and deallocation of certain microarchitectural resources used by memory instructions in the processor which allows us to reduce the energy consumption and the area overhead of the processor.

Memory instructions constitute a significant portion of the instructions in traditional programs and as such their processing is very important to the performance, power, area, design complexity and scalability of modern processors. This research presented in this dissertation improves the processing of these instructions so that the above-stated parameters can be optimized and improved, which can lead to the design of highly efficient processors.

# CHAPTER I

# INTRODUCTION

### 1.1 Motivation

For some years now, processor designers have known that an increase in the number of available transistors due to technology scaling does not automatically translate into an increase in performance. Similarly, increasing the size or number of critical resources in the processor does not always translate into an equivalent increase in performance. Unfortunately, the power consumption of processors, however, increases exponentially with an increase in device count or structure size. These observations have led both designers and researchers to realize that it is not sufficient to design processors simply with a view to increasing performance, or reducing energy consumption or increasing scalability and so on. Instead, a more balanced or "holistic approach" to designing processors, which delves into and improves the core algorithms that utilize the processor structures, is necessary.

Keeping these observations in mind, we believe that improving processor efficiency works as an excellent goal in processor design. To improve efficiency, one needs to study the processor's critical structures and their associated control logic in order to decide how they can be improved. This process can further be streamlined by focusing on the frequentlyaccessed and contentious structures as well as the common instructions that access these structures. Memory instructions constitute nearly 40% of all instructions and are generally very important to performance, hence in our research we explore improving processor efficiency by focusing on memory instructions.

# 1.2 Efficiency of Current Processors

The efficiency of a system describes how well a system produces certain desired effects for a given set of inputs. For a processor, there are a number of desirable effects or metrics that can be used to describe its efficiency: performance, power, area, design complexity, scalability etcetera. Increasing processor efficiency may involve improving any one of these metrics or simultaneously optimizing more than one of them. For example, increasing the performance achieved or reducing the power consumed can help increase efficiency. On the other hand, reducing the power consumed while reducing design complexity and minimizing performance degradation may also be a desirable goal that improves the efficiency of a processor. Finally, some innovative approaches to improving the processor efficiency metrics may focus on one or two metrics and get improvement in another metric at a negligible cost. For example, reducing power consumed and design complexity may reduce access latency which could also improve the scalability of the processor. Thus, we can use a number of approaches to improve the efficiency of current processors. Any approach used, however, generally requires innovative microarchitectural proposals and designs that can optimize instruction processing and the associated control logic in the processor.

In this dissertation, we focus on optimizing the processing of memory instructions to improve one or more of the stated efficiency metrics which in turn improve the overall efficiency of the processor.

# 1.3 Memory Instruction Processing

Memory instructions are of two kinds: load instructions, which retrieve data from the memory into the processor, and store instructions, which write data from the registers in the processor to the memory. In this section we briefly describe the potential impact of memory instruction processing on processor efficiency. In particular, we explain certain inefficiencies, which exist in memory instruction processing, that we address in this dissertation.

#### 1.3.1 Conservativeness in Memory Instruction Processing

The first aspect of conservative memory instruction processing that we address in this dissertation is speculative memory execution.

Instruction level parallelism and speculative instruction execution are powerful tools to improve the performance of single-threaded microarchitectures. While branch prediction is a widely adopted and universally accepted technique to speculatively schedule branches as well as instructions following the unresolved branch, the use of instruction level speculation while processing memory instructions has only recently started appearing in mainstream

processor microarchitectures such as the Intel Core 2 Duo [19]. Store instructions write data to memory, hence allowing a store instruction to speculatively update data is not possible without special and non-trivial modifications to be able to undo updates to the data cache and memory. Since store instructions are not usually on the critical path of execution, however, conservative store processing does not significantly degrade performance. A load instruction, on the other hand, retrieves data from the cache which is generally used by subsequent instructions in the program. Being able to retrieve a load's data early can impact the scheduling of several instructions following the load and can thus provide a significant performance improvement. Unfortunately, executing a load before it is known to have resolved all of its dependencies can be dangerous, since the power cost of flushing and re-executing a wrongly-executed load and all of its subsequent instructions can be very expensive. Additionally the wrongly-executed instructions could have wasted critical resources that might have been used by other non-speculative instructions. Past proposals that have explored aggressive instruction level speculation in load instructions have either been limited in their performance benefit or have proposed sophisticated designs which are very complex and inefficient with respect to power and access latency [35, 17]. Due to these reasons most current processors use a conservative approach and only schedule loads when they have resolved all of their dependencies. This could limit the performance of the processor and ultimately impact its efficiency.

The second aspect of conservative memory instruction processing that we address in this dissertation is of instruction criticality, with specific emphasis on load criticality. Most load processing mechanisms treat all loads equally irrespective of how the load impacts subsequent instructions or overall processor performance. This may seem like a simple and reasonable strategy to handle loads, but consider a scenario where a critical shared resource is simultaneously budded on by many load instructions. Age-based priority can resolve the contention but the solution may be sub-optimal, since data fetched by the oldest load (or older loads) may not be needed by any subsequent instruction; i.e., the load's age does not necessarily imply its criticality. Furthermore, providing no criteria to classify loads, means that any load optimization, like speculative load execution described above, or data forwarding needs to be applied to all loads equally. Not only is this wasteful in terms of processor hardware but also power, since many load optimization implementations require fairly complex and power-hungry designs. This extra burden on the processor resources does not always translate into extra performance, since as explained earlier not all loads matter to processor performance.

Prioritizing loads based on their importance or criticality can streamline execution greatly and provide various performance and power benefits that can help improve processor efficiency. Unfortunately, previous proposals to determine load criticality have been fairly complex to implement and limited in their application viability. Hence, load prioritization has so far been an academic concept that has never really been implemented in hardware.

#### 1.3.2 Scalability Concerns

Load and store instructions are processed in microarchitectural queues known as the load queue and store queue, respectively. These buffers have a considerable amount of control logic associated with them that ensures the correct execution of memory instructions. Unfortunately, this complex control circuitry increases the power consumed and area occupied by the queues. These power-hungry structures are also at risk of becoming thermal hot-spots since they are accessed very frequently in the processor. Finally, since these structures are on the critical path of the processor, their size impacts their access latencies, which can slow down the entire program execution. As a result, it becomes difficult to increase the sizes of these structures beyond a limit without running into power, temperature and latency problems. With trends in the processor industry indicating a shift from high-frequency designs to microarchitectures that aggressively target ILP and require large buffers, as is evidenced by Intel's "Nehalem", scalability of the load queue and the store queue is likely to become a vital problem [33]. Even for current microarchitectures, the load and store queues are structures that cause considerable power concerns. Unless this scalability challenge is resolved, it could become difficult to improve or even maintain the efficiency of the processor.

As explained above, the LQ/SQ scaling problem is primarily due to the large buffer sizes that are required to expose ILP and improve performance. One of the reasons for needing large queues, however, is the inefficient processing of memory instructions in these queues. A classic example of this inefficiency is that a load instruction enters the LQ as soon as it is allocated and leaves only when it is committed; but the load instruction uses the LQ resources and control circuitry only when it executes and fetches its data. So, for a large portion of the load's lifetime, it is sitting in the large and power-hungry LQ not even utilizing it. Stores face a similar situation. Techniques that can reduce the amount of time that loads and stores spend in the LQ and SQ , respectively, without impacting performance, are useful to explore in this context. These techniques can reduce the hardware and power required by the LQ/SQ and utilize this in some other part of the processor thereby improving overall processor efficiency. There have been a few proposals that are geared toward building smaller load and store queues [75], but they have fairly high design complexity and hence the scalability of these queues still remains a challenge.

#### 1.3.3 Multi-threaded Microarchitectures

The problems described above have been explained in the context of single-threaded machines. With multi-threaded machines, the problems can be compounded. These machines generally have larger-sized resources and more complex circuitry that single-threaded outof-order machines, and so their power budgets are already constrained. Additionally, since many of the resources need to be fairly shared and managed across all threads, the performance per thread can sometimes be degraded. In such situations, a conservative approach to scheduling memory instructions can be quite undesirable. There is another challenge associated with multi-threaded architectures. While there are considerable resources available to the processor overall, the manner in which they are partitioned between the threads is not always optimal. Fairness is often a dominant parameter in deciding the allocation of resources, which does not always translate into efficient resource utilization. This could limit the throughput provided by the processor , which in turn could adversely impact the efficiency of the processor.

# 1.4 Memory Instruction Behaviors

The previous section described some of the inefficiencies in the processing of memory instructions that could limit the potential of current and future microarchitectures. While these challenges do pose serious design issues, there is scope and potential for improvement. In this section, we will briefly walk through some specific behavioral properties of memory instructions and their interactions and provide interesting insights into how their processing can be improved. A more detailed study of the following properties is presented in the next chapter.

#### 1.4.1 Predictability in Memory Dependencies

Memory disambiguation is a technique employed by high-performance, out-of-order processors that execute loads and stores out of program order. Speculative memory disambiguation allows the processor to disambiguate memory instructions even when there is the possibility of a dependence between the instructions. A memory dependence between a store and a following load occurs if the store instruction writes a data value to the same address that the load instruction reads from. Since address calculation is performed at execute, the address of an older store instruction may be unresolved at the time that a later load instruction is waiting to be scheduled. Conservative techniques employed in many processors do not use speculative memory disambiguation since the recovery for a misspeculated load involves a pipeline flush, which increases the power consumption and wastes useful processor resources thereby hurting processor performance. Analysis of memory address patterns show, however, that the instances of true dependencies follow a very predictable pattern. Thus **memory dependence prediction** can be employed to speculatively execute a load instruction and its dependent instructions while minimizing the need for recovery.

#### 1.4.2 Predictability in Data Forwarding

Most of the complex and power-hungry control logic associated with the load and store queues is used to support the memory disambiguation and data forwarding functions necessary for memory instruction processing. Data forwarding is a mechanism by which load instructions retrieve values that have not yet been written to the cache. Store instructions that have executed and have a value ready, need to forward this value to a younger load instruction reading from the same address, so that the load does not retrieve stale data from the memory. The alternative to data forwarding is to stall a load access until the matching older store does write to memory; this obviously increases the execution time which is very undesirable and thus data forwarding is employed in nearly all modern out-of-order processors. Determining when data need to be forwarded requires associative searches of the store queue. This leads to the increased power consumption of the load and store queue, which as explained earlier, poses a scalability challenge. Analysis of data forwarding patterns show, however, that the data forwarding pairs (store-load) are very predictable. This insight can be used to facilitate **data forwarding prediction** and completely eliminate the associative searches, simplifying the hardware considerably while not hurting the performance.

#### **1.4.3** Predictability in Instruction Criticality

The earlier observations dealt mainly with how memory instructions interact with one another. Even when considered independently, however, memory instructions have certain characteristic behaviors that can be used to improve their processing. Certain load instructions have a more pronounced effect on the performance of the processor than others. Being able to accurately identify these critical loads can open up various avenues of optimizations that are applied based on the priority of the load.

The main concern with load criticality is defining the set of heuristics or criteria that are used in classifying critical loads. Past proposals have been varied and diverse in their approach to defining and classifying critical load instructions. In our research we choose a heuristic that is an accurate indicator of load criticality and is also very predictable. This allows us to design and implement a simple **load criticality prediction** algorithm. The second important concern with load criticality is selecting optimizations that can benefit from it. Since loads have the potential to significantly impact many instructions following them, optimizations that prioritize some loads at the cost of others need to be carefully explored and evaluated. Mispredictions in load criticality can have severe effects since they are hard to track and correct unlike branch or memory dependence mispredictions. The next chapter describes in detail the properties of critical loads as well as the benefits of being able to accurately predict them. The next chapter also briefly outlines how we apply load criticality information to help improve processor efficiency.

#### 1.4.4 Conservative Allocation and Deallocation Policies

Another interesting observation regarding memory instructions (this can apply to other instructions, too) is that the utility of an instruction or the number of cycles when it is required to perform useful work in the processor (for example forwarding a value, helping to maintain in-order semantics), may be far less than the actual time that the instruction spends in the critical structures or the out-of-order core of the processor. As a result, memory instructions often sit idle occupying critical processor resources, which requires larger buffers to be built to avoid stalls. This contributes to wastage of critical resources as well as power since larger structures have longer wires and consume more power. Being able to determine the utility of an instruction can help streamline the utilization of processor resources and reduce the inefficiency in the design of the processor.

Specifically, the allocation and deallocation of LQ and SQ resources for memory instructions is done fairly conservatively in the pipeline in order to ensure correctness of the system. This approach leads to inefficient LQ and SQ designs which also contribute to the scalability challenge explained earlier. Fortunately, there are techniques that can allow **aggressive allocation and deallocation of resources** of memory instructions, while still maintaining correct in-order semantics. Exploiting these techniques can help reduce the amount of time loads and stores spend in the critical queues thereby allowing us to build smaller queues while maintaining processor performance.

# 1.5 Scope and Overview of the Dissertation

#### 1.5.1 Scope

The preceeding sections have helped to establish two facts. First, inefficiencies exist in current processors with respect to achieved performance and required power and area budgets. The manner in which memory instructions are processed contribute significantly to these inefficiencies. Second, there are certain properties of memory behavior that can intuitively be used to make the designs of the structures that support memory instruction processing more efficient. In this dissertation, we present designs that exploit these memory behavior patterns to improve the processing of memory instructions. Our techniques improve one or more of the stated efficiency metrics, which can improve the overall efficiency of the processor. We employ a two-pronged approach to achieve our goal.

1. We propose and evaluate optimizations that use predictable or common-case memory behavior to reduce the latency of memory instructions and improve overall resource utilization. These techniques are able to improve the performance of the processor.

2. We propose and evaluate optimizations that simplify, reduce and even eliminate specific hardware required for the processing of memory instructions. We get this hardware and consequent power reduction with negligible loss in performance.

Processor efficiency can also be improved by changing other design parameters such as the number of cores on a chip. A multi-core design can be used to significantly improve processor throughput as is evidenced by Intel's Core2 Duo [19]. For the design methodology used in our research work, we focus on single-core designs and propose optimizations that improve processor efficiency in a single-core environment. The number of cores, however, is orthogonal to the proposed designs that exploit memory instruction behaviors. Hence, our designs can be extended to improve efficiency even in a multi-core scenario. In Chapter 8, we briefly discuss how our techniques can be applied to multi-core processors.

#### 1.5.2 Overview of Dissertation

In this dissertation, we first give a detailed overview on the common-case behaviors that exist in memory instructions in Chapter 2. We focus on the following memory behavior patterns in this thesis: predictability of memory dependences, predictability of load instruction criticality and the conservativeness in allocation and deallocation of critical processor resources. We start with designing an efficient, scalable, and high-performance memory dependence predictor. Chapter 3 provides a detailed description and evaluation of our proposed memory dependence prediction mechanism. Our second optimization applies accurate memory dependence prediction to improve the efficiency of the fetch engine of a simultaneous multi-threaded processor, which in turn improves the overall throughput. This optimization is described in Chapter 4. We then use predictable memory dependence patterns to help identify predictable data forwarding patterns and use these to eliminate critical, power-hungry hardware in the processor with no loss in performance. Chapter 5 describes and evaluates this optimization. In Chapter 6, we describe load criticality and propose the design of an efficient criticality predictor. We also explore several applications that can exploit this criticality information to improve the overall efficiency of the processor. In Chapter 7, we present our design for aggressive allocation and deallocation for the LQ and the SQ and show how our techniques can be used to build much smaller queues with no loss in performance. Finally, in Chapter 8 we present our conclusions and discuss some extensions to our thesis that can help to further improve processor efficiency.

### CHAPTER II

# AN OVERVIEW OF MEMORY INSTRUCTION BEHAVIOR

### 2.1 Speculative Memory Disambiguation and Memory Dependencies

Out-of-order load execution can significantly improve performance by exposing more instruction level parallelism (ILP). Unfortunately, out-of-order load scheduling and execution is a non-trivial problem. Load instructions may have data dependencies through memory where an earlier store instruction writes to an address and the load instruction reads from the same memory location. The effective addresses of all load and store instructions may not be available because the corresponding address computations may not have executed. This leads to a dependence ambiguity: depending on the result of a store's address computation, a later load instruction may or may not actually be data dependent. If the load is actually independent, then it should be scheduled for execution to maximize performance. If the load is data-dependent, then it must wait for the store instruction.

Consider the code example as shown in Figure 1. Here, the store instruction writes to the memory location specified by the value in register R1, and the load instruction reads the memory location specified by the value in R2. A dependence checking scheme based purely on register dependencies would consider these instructions to be independent. Since both of the instructions access memory, however, the microprocessor cannot statically determine, prior to execution, if the memory locations specified by both instructions are different or are in fact the same. The apparent confusion or ambiguity is because the locations that the memory instructions read/write to depend on the values contained in registers R1 and R2. If the locations are different, the instructions are independent and can be successfully executed out of order. However, if the locations are the same (the address stored in R1 is equal to the address stored in R2), then the load instruction is dependent on the store to produce its value. Memory disambiguation is the technique used to resolve the dependencies between memory instructions in a processor.

| Store [R1], R5 |

|----------------|

| Load R6, [R2]  |

**Figure 1:** Example showing the ambiguous dependence that can arise between memory instructions.

Like many other properties in microprocessors, memory dependencies exhibit a form of temporal locality. Memory dependence prediction is a technique for speculatively disambiguating the relationships between loads and stores [50]. A load instruction that issues too early due to a dependence misspeculation, however, may retrieve a stale value from the data cache and propagate this incorrect value to its dependent instructions. Many cycles may pass between when the load instruction issues and when the processor finally detects the ordering violation. At this point, a large number of instructions from the load's forward slice [89] may have already executed. Tracking down and rescheduling all of these instructions is a difficult task, and so a memory dependence misspeculation is typically handled by flushing the pipeline. Overly aggressive load scheduling combined with the high cost of pipeline flushes can therefore result in a net performance decrease, power increase and overall reduced efficiency.

To avoid costly pipeline flushes and improve processor performance, load and store execution history can be incorporated in memory dependence prediction. Since memory dependences follow a predictable pattern, this approach improves the accuracy of the predictor. Most memory dependence predictors use history information to predict the *dependence status* of a load: whether a dependence currently exists or not, which determines if the load can issue. The Alpha 21264 employed such a dependence predictor called the *Load Wait Table* that tracks all loads that experience ordering violations [35]. When a store executes and exposes a load ordering violation, the load's PC indexes into the Load Wait Table and sets a bit. On subsequent instances of the load, the Load Wait Table will indicate that the load previously caused a memory ordering violation, and the scheduler will force the load to wait until all earlier store addresses have been resolved. The processor periodically clears the table to avoid permanently preventing loads from speculatively issuing and to allow the predictor to adapt to phasic application behavior in different parts of the program. The Intel Core 2 has a similar mechanism for tracking misspeculated loads that should be forced to wait for previous stores [19]. The memory dependence predictor used is comprised of a table of saturating counters which provides more accuracy than the 1-bit entry table used in the Alpha 21264.

Memory dependence prediction is useful for several reasons. As described above, it can help issue load instructions early which can potentially schedule instructions dependent on the load early as well. This can reduce the overall execution time thus improving efficiency. In our research work, we design an advanced and novel memory dependence predictor that improves processor performance while providing a simple and efficient hardware implementation. Our proposed design is called **Store Vectors** and is described in Chapter 3.