# SIGNAL AND POWER INTEGRITY CO-SIMULATION USING THE MULTI-LAYER FINITE DIFFERENCE METHOD

A Dissertation Presented to The Academic Faculty

By

Krishna Bharath

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

in

Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology May 2009

Copyright © 2009 by Krishna Bharath

# SIGNAL AND POWER INTEGRITY CO-SIMULATION USING THE MULTI-LAYER FINITE DIFFERENCE METHOD

#### Approved by:

Dr. Madhavan Swaminathan, Advisor Joseph M. Pettit Professor, School of ECE Georgia Institute of Technology

Dr. Andrew F. Peterson Professor, School of ECE Georgia Institute of Technology

Dr. David C. Keezer Professor, School of ECE Georgia Institute of Technology Dr. Saibal Mukhopadyay Assistant Professor, School of ECE Georgia Institute of Technology

Dr. Suresh Sitaraman Professor, School of ME Georgia Institute of Technology

Date Approved: March 2009

#### ACKNOWLEDGMENTS

It would be an understatement to say that I needed help with my Ph.D. This thesis required constant encouragement and much constructive criticism from some extraordinary individuals. They were always patient and indulged my rather intermittent work ethic. I thank them all.

My advisor, Prof. Swaminathan, has an extraordinary ability to spot and channel the talents of his students and to get them to work on some fascinating problems. I would like to to thank him for his support, trust, encouragement, and guidance over the last five years.

I would like to thank my committee members, Prof. Andrew F. Peterson, Prof. David C. Keezer, Prof. Saibal Mukhopadyay and Prof. Suresh Sitaraman for taking much of their valuable time to give me constructive advice and feedback.

If I could credit someone as my co-advisor, it would have to be Dr. Arif Ege Engin. His future students should consider themselves lucky.

One of the benefits of working in such a large research group that has multiple focus areas is that I got a big picture view that repeatedly reminded me of where my research fit in. I have been fortunate in having highly gifted colleagues at EP-SILON group. I benefited from the support and interaction with the following past members of EPSILON group: Souvik Mukherjee, Subramanian Lalgudi, Amit Bavisi, Bhyrav Mutnury, Tae Hong Kim, Rohan Mandrekar, Prathap Muthana, Wansuk Yun, Krishna Srinivasan, Jinwoo Choi, Janani Chandrashekar, Abdemanaf Tambawala, Ranjeeth Doppalapudi, and Vishal Laddha. I offer the following students and future PhD's my gratitude: Kijin Han, Nevin Altunyurt, Bernie Yang, Abhilash Goyal, Eddy Hwang, Myunghyun Ha, Suzanne Huh, Narayanan Terizhandur, Nithya Sankaran, Mohit Pathak, Tapo Bandhopadyay, Sukruth Pattanagiri, Aswani Kurra, Rishiraj Bheda, Jae Young Choi and Jianyong Xie.

I've had many valuable discussions with research faculty and visiting scholars. Thanks to Dr. Daehyung Chung, Dr. Yoshitaka Toyota, Dr. Sunghwan Min, Dr. Andy Seo, Dr. H. Rao, Dr. Arijit Majumder and Mr. Kazuhide Uriu.

Murali, Lal, Souvik & Moumita, Amit & Atura, Vishwa, Nevin, Raj, Ganesh & Vidhya, Abdemanaf, Janani, Sourabh, Ashwini, Pradeep, Marie-so, Jayaram, Shyam, Narayanan, Jae and Sehun: thank you for your friendship.

It is hard to express in words my gratitude to my sister and brother-in-law, Deepa and Maneesh. Thanks for your unwavering support and belief.

Finally, I'd like to thank my parents, Lakshmi and Bharath Srinivasan. I have a small measure of my mother's love of books, and my father's drive to solve engineering problems. They gave me the freedom to think freely, and this is the greatest gift of all.

# TABLE OF CONTENTS

| ACKN   | OWLEDGMENTS                                                     | iv       |

|--------|-----------------------------------------------------------------|----------|

| LIST O | F TABLES                                                        | x        |

| LIST O | F FIGURES                                                       | xi       |

| SUMM   | ARY                                                             | xviii    |

| CHAP   | TER 1 THEORETICAL BACKGROUND AND SUMMARY                        |          |

|        | OF CONTRIBUTIONS                                                | 1        |

| 1.1    | Electrical Bottlenecks in Microelectronic Packaging             | 1        |

| 1.2    | Motivation: Increasing Efficiency of the Design Flow            | 4        |

| 1.3    | Simultaneous Switching Noise                                    | 5        |

|        | 1.3.1 SSN and Signal Integrity                                  | 7        |

|        | 1.3.2 Coupling in Package Structures                            | 8        |

|        | 1.3.3 Target Impedance                                          | 9        |

| 1.4    | Electrical Simulation of the Package                            | 11       |

|        | 1.4.1 Circuit-based Methods                                     | 11       |

|        | 1.4.2 EM-based Methods                                          | 14       |

| 4 F    | 1.4.3 Hybrid Methods                                            | 14       |

| 1.5    | Overview of the Proposed Hybrid Method                          | 18       |

| 1.6    | Nodal Admittance Matrices and Shifting of Reference Nodes       | 21       |

| 1.7    | Modeling the Interaction between Signal Lines and the Non-Ideal | 0.4      |

| 1 0    | Power/Ground Planes                                             | 24       |

| 1.8    | Contributions and Dissertation Outline                          | 28       |

|        | 1.8.1 Summary of Contributions                                  | 31       |

|        | 1.8.2 Dissertation Outline                                      | 32       |

| CHAP   |                                                                 |          |

| 0.1    | LAYER FINITE DIFFERENCE METHOD                                  | 34       |

| 2.1    | Introduction                                                    | 34       |

|        | 2.1.1 Single Plane-Pair                                         | 34       |

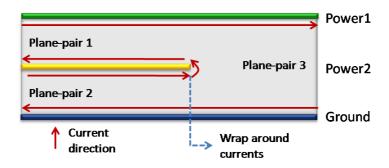

| 2.2    | 2.1.2 Multiple Plane-Pair                                       | 35       |

| 2.2    | Formulation for Single Plane-Pair Geometries                    | 36       |

|        | 2.2.1 Governing Equation                                        | 36       |

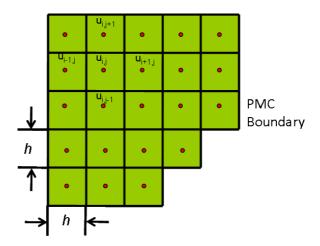

|        | 2.2.2 Application of the Finite Difference Method               | 37       |

|        | 2.2.3 5- and 9- Point Approximations                            | 38       |

|        | 1                                                               | 40       |

|        |                                                                 | 42       |

| 2.3    | 2.2.6 Results                                                   | 42<br>46 |

| ∠.3    | 2.3.1 Aperture Coupling                                         | 46       |

|      | 2.3.2  | Formulation                                                     | 46       |

|------|--------|-----------------------------------------------------------------|----------|

|      | 2.3.3  | Equivalent Circuit and Matrix Equation                          | 51       |

|      | 2.3.4  | Model to Hardware Correlation for Structures with Apertures     | 54       |

|      | 2.3.5  | Results Demonstrating Scalability                               | 58       |

| 2.4  | Conclu |                                                                 | 60       |

| CHAP | ΓER 3  | MODELING OF FRINGING FIELDS IN M-FDM FOR MULTI-LAYERED PACKAGES | <b>₹</b> |

| 3.1  | Introd | luction                                                         | 63       |

|      | 3.1.1  | Significance of the Fringing Fields                             | 63       |

|      | 3.1.2  | Prior Work in Modeling Fringing Fields                          | 65       |

| 3.2  | Additi | ion of Fringe Elements to M-FDM                                 | 66       |

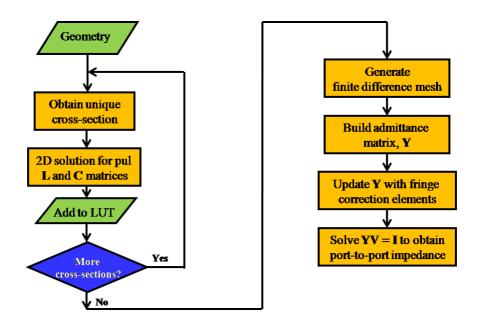

|      | 3.2.1  | Simulation Flow                                                 | 66       |

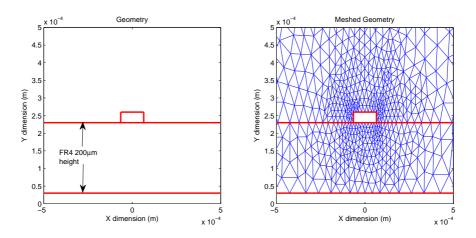

|      | 3.2.2  | 2D Electrostatic Solver                                         | 67       |

|      | 3.2.3  | Formulation                                                     | 69       |

|      | 3.2.4  | Matrix Equation for Single Plane-Pair Geometries                | 71       |

|      | 3.2.5  | Equivalent Circuit for a Single Plane-Pair                      | 74       |

|      | 3.2.6  | Matrix Equation for Multiple Plane-Pair Geometries              | 74       |

|      | 3.2.7  | Equivalent Circuit for Multiple Plane-Pairs                     | 77       |

|      | 3.2.8  | Computational Complexity                                        | 79       |

| 3.3  | Result |                                                                 | 79       |

|      | 3.3.1  | Microstrip Meander                                              | 79       |

|      | 3.3.2  | Three Layer Problem                                             | 80       |

|      | 3.3.3  | Model to Hardware Correlation                                   | 84       |

| 3.4  | Conclu | usions                                                          | 86       |

| CHAP | ΓER 4  |                                                                 |          |

|      |        | LAYERED PACKAGES                                                | 88       |

| 4.1  | Introd | luction                                                         | 88       |

|      | 4.1.1  | Significance of Gap Effect                                      | 89       |

| 4.2  |        | ion of the Gap Effect using the Plane-Gap Augmentation Method   |          |

|      |        | Simulation Flow                                                 | 91       |

|      | 4.2.2  | Formulation for Single Plane-Pair Structures                    | 93       |

|      | 4.2.3  | Matrix Equation for a Single Plane-Pair                         | 96       |

|      | 4.2.4  | Formulation for Multiple Plane-Pairs                            | 98       |

|      | 4.2.5  | Computational Complexity                                        | 99       |

| 4.3  |        |                                                                 | 100      |

|      | 4.3.1  |                                                                 | 100      |

|      | 4.3.2  | V 1 1                                                           | 100      |

|      | 4.3.3  | 9                                                               | 102      |

|      | 4.3.4  | v 1                                                             | 105      |

|      | 4.3.5  | 1                                                               | 109      |

| 1.1  | Conclu | usions                                                          | 100      |

| CHAPT  | $\Gamma ER 5$ | MODELING TRANSMISSION LINES V                 | VITH NON- | -            |

|--------|---------------|-----------------------------------------------|-----------|--------------|

|        |               | IDEAL POWER/GROUND PLANES US                  | ING M-FDN | <b>A</b> 112 |

| 5.1    | Introd        | luction                                       |           | 112          |

|        | 5.1.1         | Non-ideality of Return Paths                  |           | 112          |

|        | 5.1.2         | Prior Work with Transmission Line Referencing |           | 114          |

| 5.2    | Simula        | ation Flow                                    |           | 117          |

| 5.3    | Modal         | Decomposition                                 |           | 119          |

|        | 5.3.1         | Microstrip                                    |           | 121          |

|        | 5.3.2         | Stripline                                     |           | 122          |

|        | 5.3.3         | Conductor Backed Co-planar Waveguide          |           | 123          |

|        | 5.3.4         | Summary of Modal Decoposition Techniques      |           | 124          |

| 5.4    | Port F        | Reduction                                     |           | 127          |

| 5.5    | Implei        | mentation Using M-FDM                         |           | 127          |

| 5.6    | Test C        | Cases and Results                             |           | 129          |

|        | 5.6.1         | Mixed Signal Board                            |           | 129          |

|        | 5.6.2         | Microstrip Line Traversing a Slot             |           | 131          |

|        | 5.6.3         | Microprocessor Package                        |           | 133          |

|        | 5.6.4         | Microstrip Via Transition                     |           | 134          |

|        | 5.6.5         | Stripline                                     |           | 135          |

|        | 5.6.6         | CPW line                                      |           | 138          |

| 5.7    | Concl         | usion                                         |           | 140          |

|        |               |                                               |           |              |

| CHAPT  | $\Gamma$ ER 6 | GENETIC ALGORITHM BASED OPTI                  |           |              |

|        |               | OF DECOUPLING CAPACITOR PLACE                 |           | 142          |

| 6.1    |               | luction                                       |           | 142          |

|        | 6.1.1         | Role of Decoupling Capacitors                 |           | 142          |

|        | 6.1.2         | Target Impedance                              |           | 143          |

|        | 6.1.3         | Placement of Decoupling Capacitors            |           | 144          |

| 6.2    |               | ion of Decoupling Capacitors in M-FDM         |           | 145          |

| 6.3    |               | nization using the Genetic Algorithm          |           | 146          |

|        |               | Formulation                                   |           | 146          |

|        |               | Convergence                                   |           | 148          |

|        | 6.3.3         | Decoupling Capacitor Library                  |           | 151          |

| 6.4    |               | Cases and Results                             |           | 151          |

|        | 6.4.1         | Test Case 1                                   |           | 151          |

|        | 6.4.2         | Test Case 2                                   |           | 154          |

|        | 6.4.3         | Test Case 3                                   |           | 156          |

|        | 6.4.4         | Summary of Results for Test Cases 1 and 2     |           | 158          |

| 6.5    | Concl         | usions                                        |           | 158          |

| CILADO |               | EUTHDE WODE, THE MILET LAXED                  |           |              |

| CHAPT  | LEKT          | FUTURE WORK: THE MULTI-LAYER                  |           |              |

| 7 1    | Int           | EMENT METHOD (M-FEM)                          |           | 160          |

| 7.1    |               | luction                                       |           | 160          |

| 7.0    | 7.1.1         | Limitations of M-FDM                          |           | 160<br>162   |

| 1.2    | - POLIDII     | nation for ourse clause-call Geomethes        |           | 102          |

|       | 7.2.1  | Basis Function                   | 162 |

|-------|--------|----------------------------------|-----|

|       | 7.2.2  | Equivalent Circuit               | 165 |

|       | 7.2.3  | Results                          | 167 |

| 7.3   | Formu  | llation for Multiple Plane-Pairs | 168 |

|       | 7.3.1  | Meshing                          | 168 |

|       | 7.3.2  | Solid Planes without Apertures   | 169 |

|       | 7.3.3  | Inclusion of Apertures           | 172 |

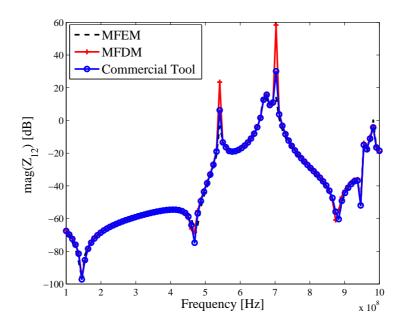

|       | 7.3.4  | Results                          | 173 |

| 7.4   | Summ   | ary                              | 175 |

| CHAPT | ER 8   | CONCLUSIONS                      | 177 |

| 8.1   | Papers | s Published                      | 180 |

|       | 8.1.1  | Journal Publications             | 180 |

|       | 8.1.2  | Conference Publications          | 180 |

| 8.2   | Award  | 1                                | 182 |

| 8.3   | Invent | ion Disclosure                   | 182 |

| APPEN | IDIX A | A NETWORK DATA CONVERSIONS       | 183 |

| BEFER | ENCE   | NG.                              | 18/ |

# LIST OF TABLES

| Table 1 | Theoretical and calculated resonance frequencies          | 45  |

|---------|-----------------------------------------------------------|-----|

| Table 2 | Simulation results for realistic package                  | 58  |

| Table 3 | Target impedance through technology nodes                 | 143 |

| Table 4 | Library of decoupling capacitors (Courtesy [1])           | 152 |

| Table 5 | Summary of results for automatic decap placement using GA | 158 |

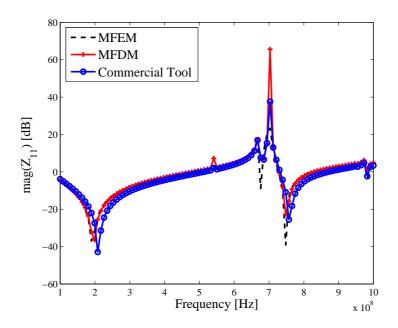

| Table 6 | Summary of results for structure in Figure 134            | 168 |

| Table 7 | Summary of results for structure in Figure 135            | 174 |

# LIST OF FIGURES

| Figure 1  | A System on Package Module (courtesy [2])                                                               | xix |

|-----------|---------------------------------------------------------------------------------------------------------|-----|

| Figure 2  | Package hierarchy.                                                                                      | 2   |

| Figure 3  | Schematic of a system on package (courtesy [2])                                                         | 3   |

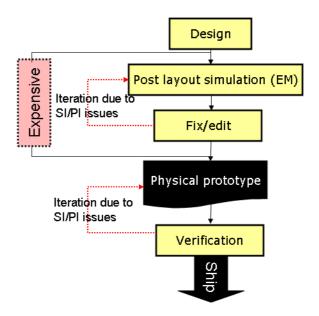

| Figure 4  | Current design flow                                                                                     | 5   |

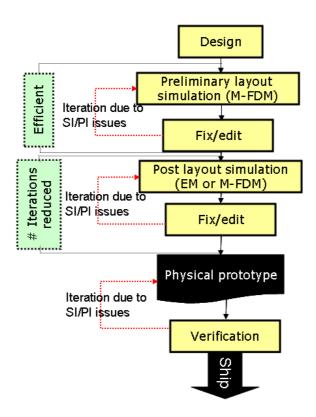

| Figure 5  | Efficient design flow                                                                                   | 6   |

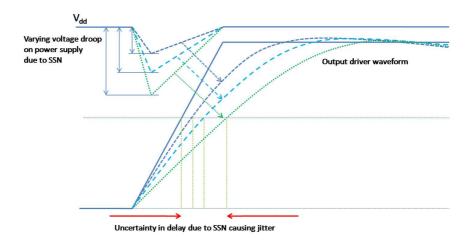

| Figure 6  | SSN induced jitter (courtesy [1])                                                                       | 8   |

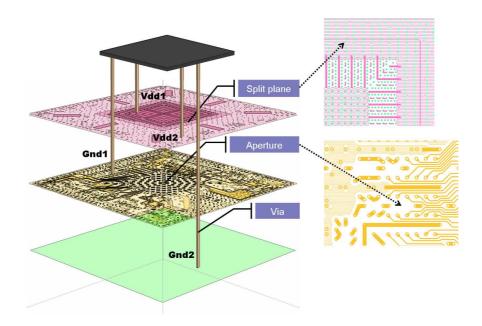

| Figure 7  | SSN coupling mechanisms in a realistic package                                                          | 9   |

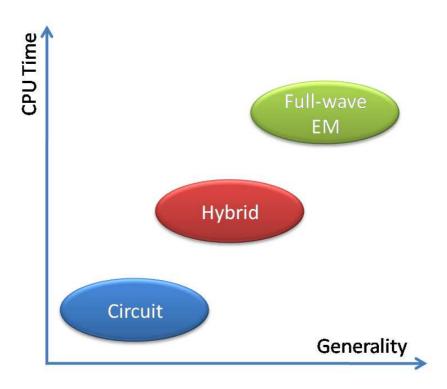

| Figure 8  | Trade-off between generality and CPU time for package simulation methods                                | 12  |

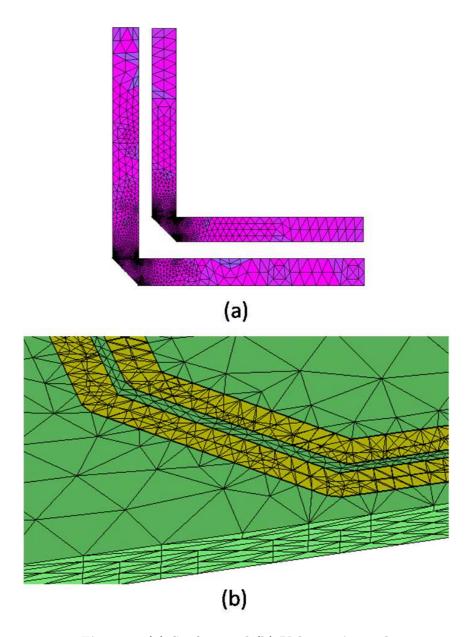

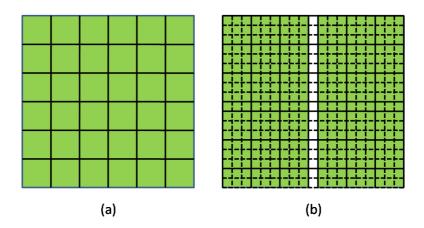

| Figure 9  | (a) Surface and (b) Volumetric mesh                                                                     | 13  |

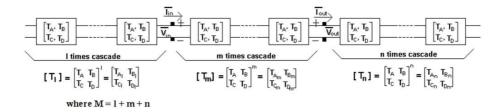

| Figure 10 | Cascade connection in TMM                                                                               | 15  |

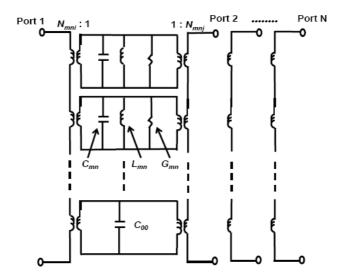

| Figure 11 | Equivalent circuit for a plane-pair                                                                     | 17  |

| Figure 12 | Segmentation of an L-shaped plane-pair                                                                  | 18  |

| Figure 13 | Overview of proposed hybrid method                                                                      | 19  |

| Figure 14 | Simple circuit containing conductances                                                                  | 22  |

| Figure 15 | (a) Two-port networks with separate references (b) Combined four-<br>port network with common reference | 23  |

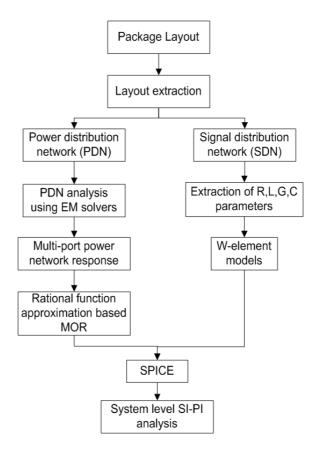

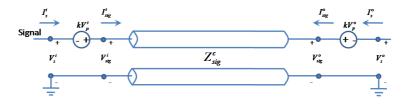

| Figure 16 | Flowchart for system level SI-PI analysis                                                               | 25  |

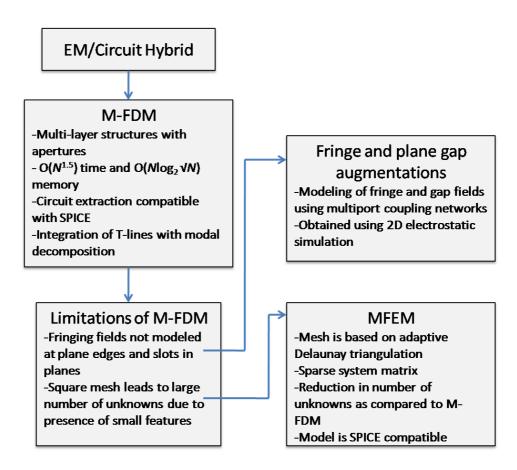

| Figure 17 | Contributions of this research                                                                          | 29  |

| Figure 18 | Single Plane-Pair Problem                                                                               | 35  |

| Figure 19 | Multiple Plane-Pair Problem                                                                             | 35  |

| Figure 20 | Discretization of the Laplace operator                                                                  | 37  |

| Figure 21 | Unit-cell model using 5-Point Approximation (T-Unit cell)                                               | 38  |

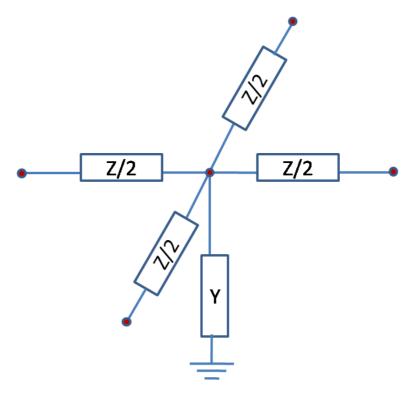

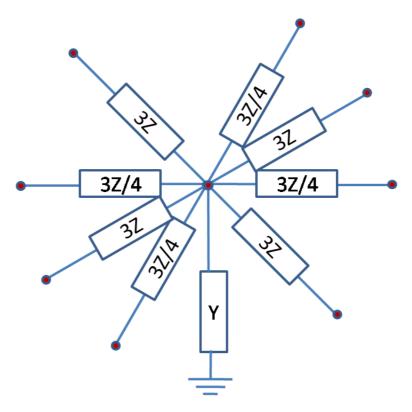

| Figure 22 | Unit-cell model using 9-Point Approximation (X-Unit cell)                                               | 40  |

| Figure 23 | Electrical model for a plane-pair                                                                       | 41  |

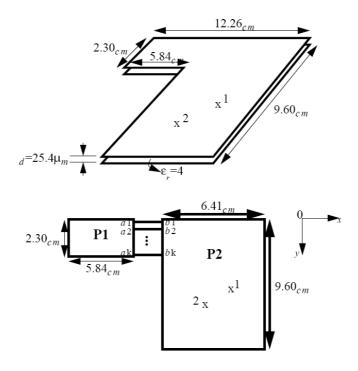

| Figure 24 | Geometry of test case                                                                                                                                                                                                                  | 43 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

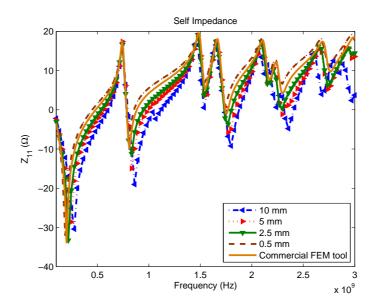

| Figure 25 | Self impedance, $Z_{11}$ , with increasing mesh refinement                                                                                                                                                                             | 44 |

| Figure 26 | Transfer impedance, $Z_{21}$ , with increasing mesh refinement                                                                                                                                                                         | 44 |

| Figure 27 | Equivalent network model of geometry in Figure 19                                                                                                                                                                                      | 46 |

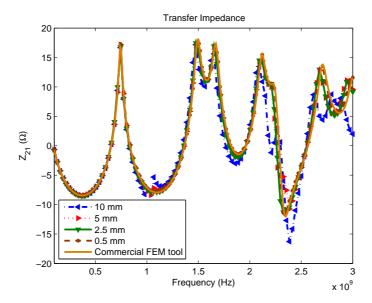

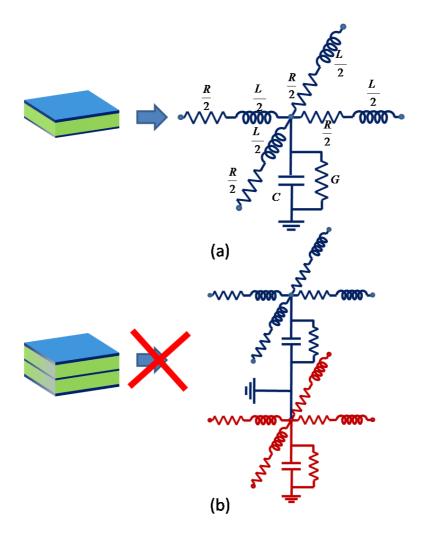

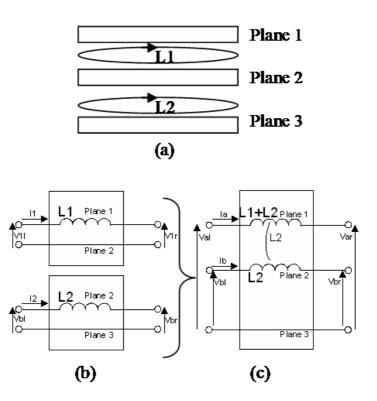

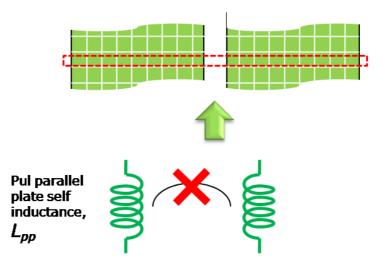

| Figure 28 | (a) T-unit cell for single plane-pair (b) Incorrect model for multiple plane-pairs based on stacking of individual T-unit cells                                                                                                        | 47 |

| Figure 29 | (a) Side view of a unit cell for a 3 plane structure showing the current loops associated with the p.u.c. inductances. (b) P.u.c. inductance of each plane pair. (c) Combining the p.u.c. inductances by changing the reference planes | 48 |

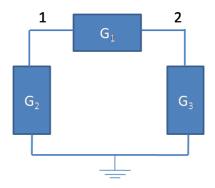

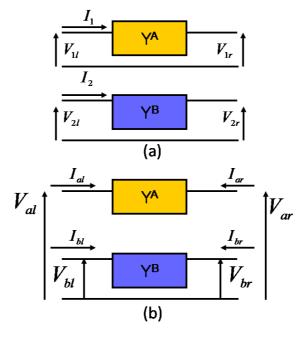

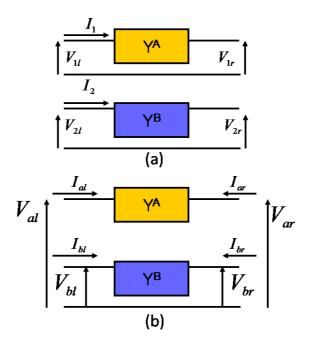

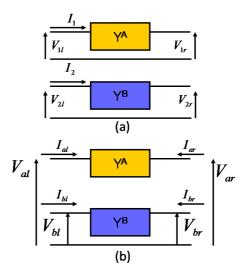

| Figure 30 | (a) Two-port networks with separate references (b) Combined fourport network with common reference.                                                                                                                                    | 50 |

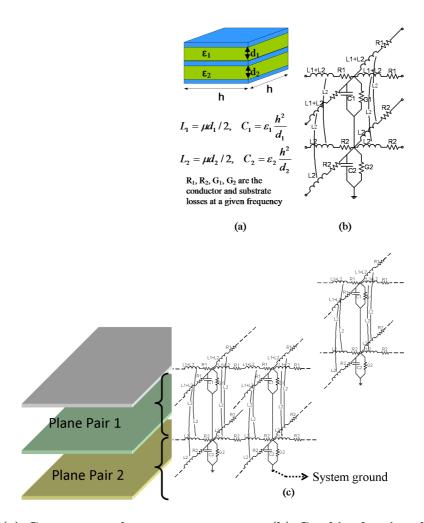

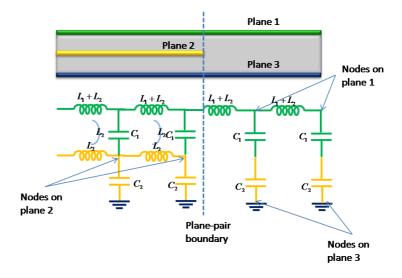

| Figure 31 | (a) Geometry and p.u.c. parameters. (b) Combined unit cell model for three planes. (c) Plane model consisting of multilayer unit cells.                                                                                                | 52 |

| Figure 32 | (a) Multiple plane-pair problem containing apertures. (b) 1D Equivalent Circuit                                                                                                                                                        | 52 |

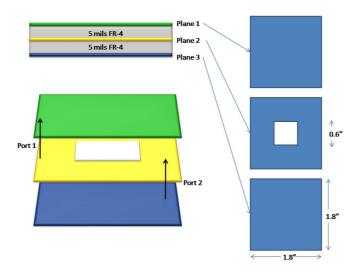

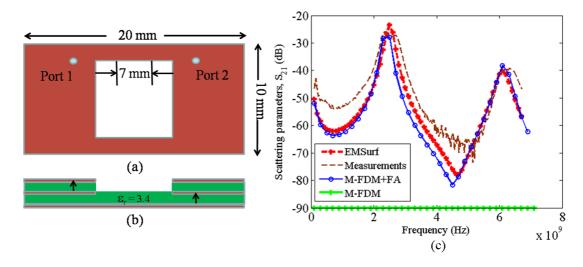

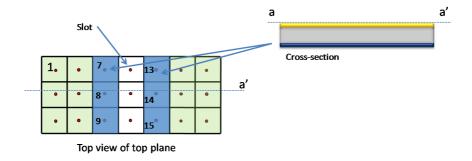

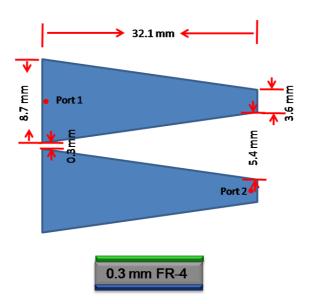

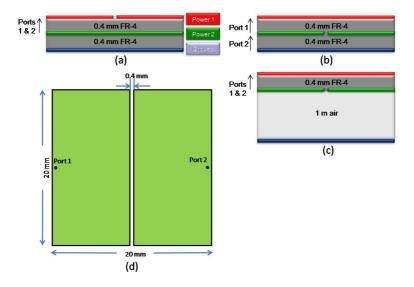

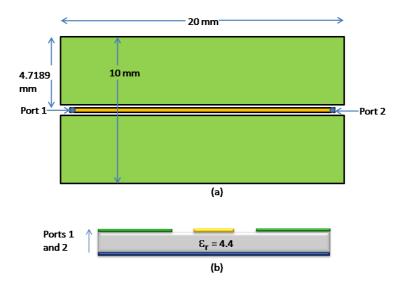

| Figure 33 | Test vehicle 1 (a) Geometry (b) Stack cross-section                                                                                                                                                                                    | 55 |

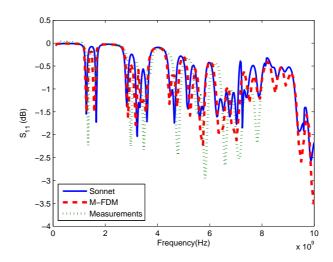

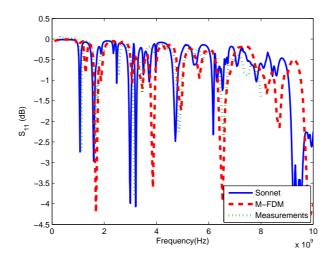

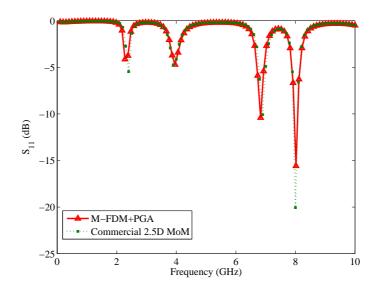

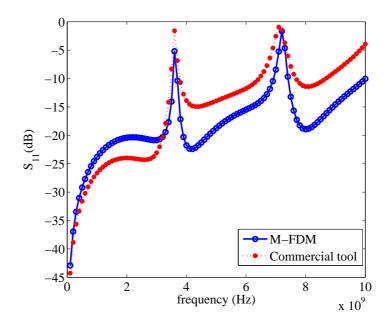

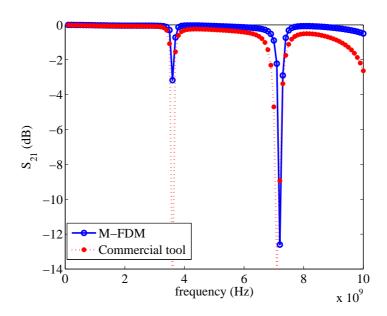

| Figure 34 | $S_{11}$ (dB) (return loss) for test vehicle 1 (Fig 33)                                                                                                                                                                                | 56 |

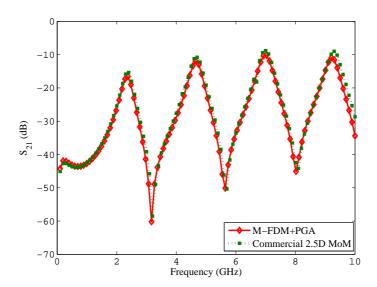

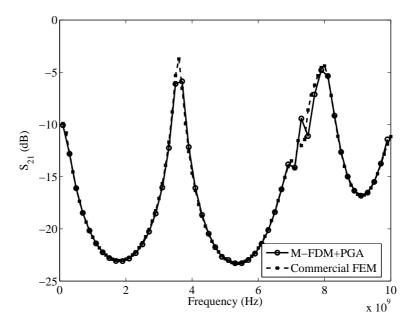

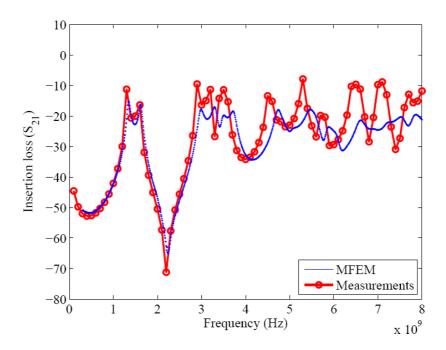

| Figure 35 | $S_{21}$ (dB) (insertion loss) for test vehicle 1 (Fig 33)                                                                                                                                                                             | 56 |

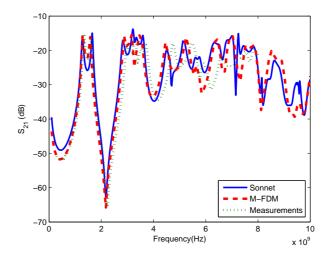

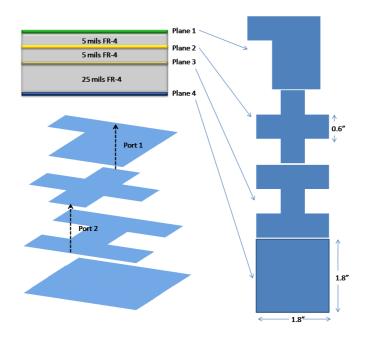

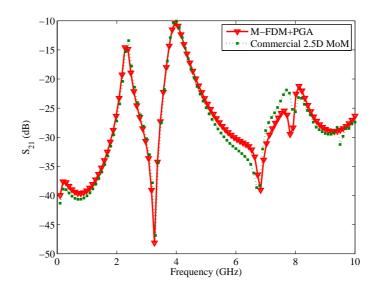

| Figure 36 | Test vehicle 2 (a) Geometry (b) Stack cross-section                                                                                                                                                                                    | 57 |

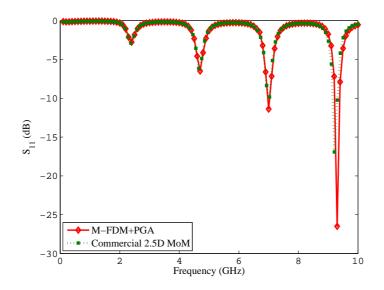

| Figure 37 | $S_{11}$ (dB) (return loss) for test vehicle 2 (Fig 36)                                                                                                                                                                                | 57 |

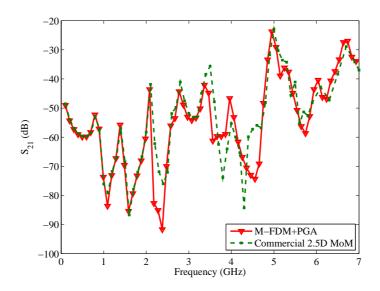

| Figure 38 | $S_{21}$ (dB) (insertion loss) for test vehicle 2 (Fig 36)                                                                                                                                                                             | 58 |

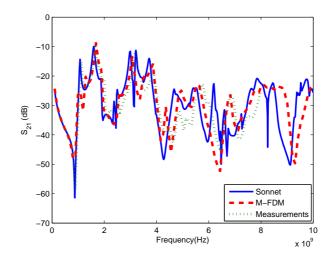

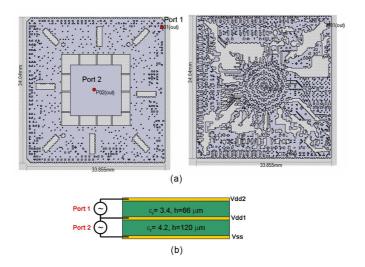

| Figure 39 | (a) Layouts for two package layers. Dimension is $34\text{mm} \times 34\text{mm}$ . (b) Cross-section for the three layer example                                                                                                      | 59 |

| Figure 40 | Insertion loss (dB)                                                                                                                                                                                                                    | 59 |

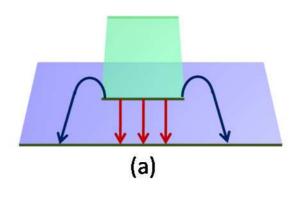

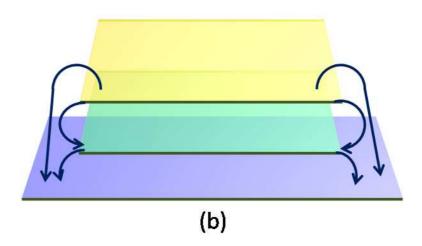

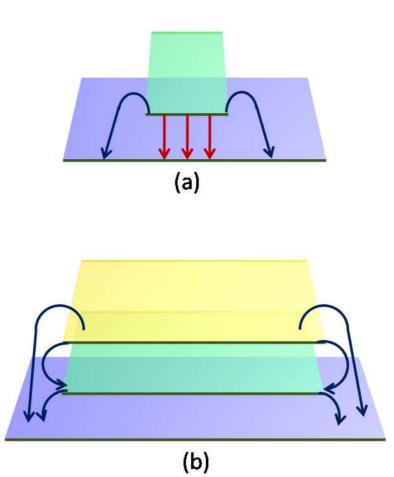

| Figure 41 | (a) Fringing fields due to narrowing of PDN (b)Fringing fields at edges in multi-layer geoemtries                                                                                                                                      | 61 |

| Figure 42 | Gap coupling across slots in planes                                                                                                                                                                                                    | 62 |

| Figure 43 | (a) Fringing fields due to narrowing of PDN (b)Fringing fields at edges in multi-layer geoemtries                                                                                                                                      | 64 |

| Figure 44 | Relative percentage error in first resonance frequency (Return Loss, $S_{11}$ .)                                                                                                                   | 64 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

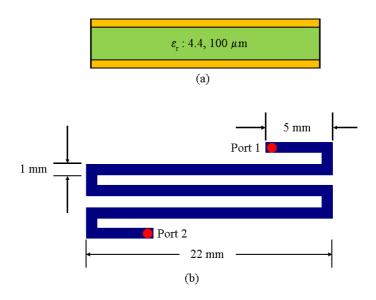

| Figure 45 | A microstrip meander line, (a) cross section (b) top view                                                                                                                                          | 65 |

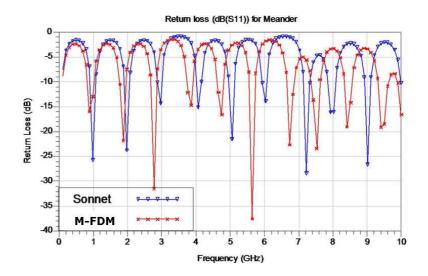

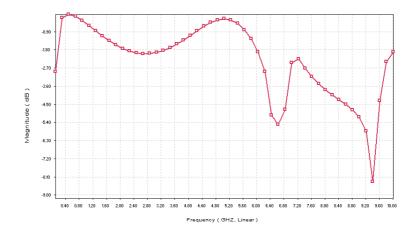

| Figure 46 | Return Loss (dB) of structure in Figure 45                                                                                                                                                         | 66 |

| Figure 47 | Flowchart for the addition of fringe augmentation elements                                                                                                                                         | 67 |

| Figure 48 | A microstrip line                                                                                                                                                                                  | 69 |

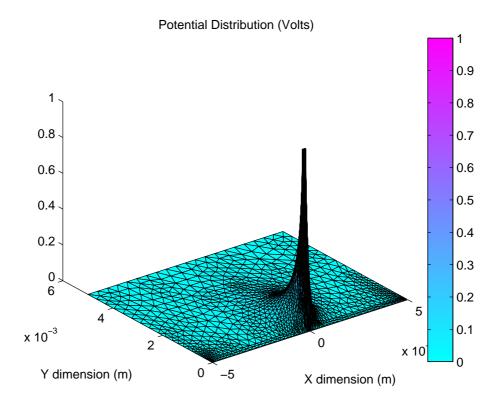

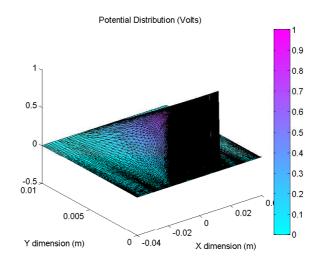

| Figure 49 | Potential distribution of microstrip in Figure 48                                                                                                                                                  | 70 |

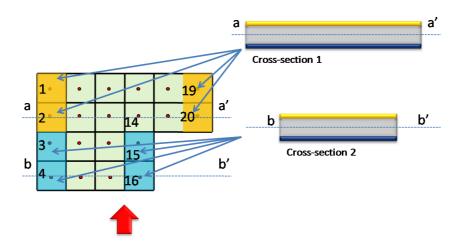

| Figure 50 | Two plane structure with two unique cross-sections                                                                                                                                                 | 71 |

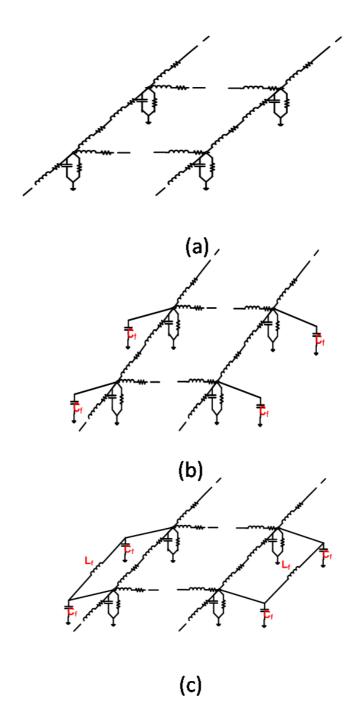

| Figure 51 | Addition of Fringe elements for single plane-pair structures. Equivalent circuit (a) from uncorrected M-FDM (b) upon addition of fringe capacitance (c) upon further addition of fringe inductance | 73 |

| Figure 52 | Three layer structure showing location of fringe nodes                                                                                                                                             | 74 |

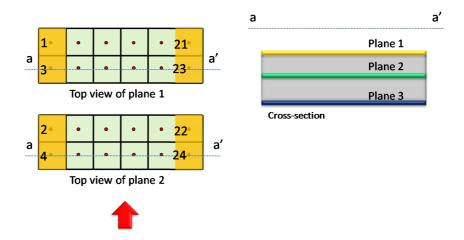

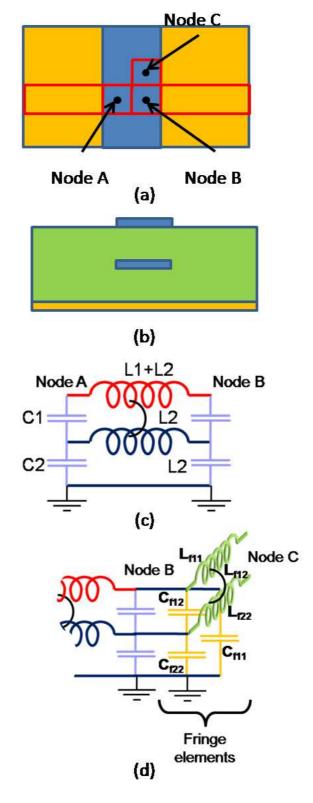

| Figure 53 | Addition of Fringe elements. (a) Top view of top and middle layers (b) Cross section (c) M-FDM circuit model between Nodes A and B (d) Circuit model as a result of fringe augmentation (FA)       | 78 |

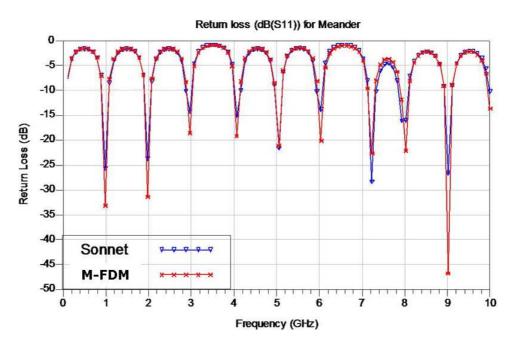

| Figure 54 | Return loss (dB) for structure in Figure 45 with fringe models. $$ .                                                                                                                               | 81 |

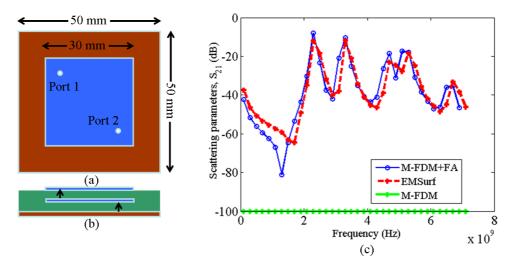

| Figure 55 | Geometry of multilayer test structure I. (a) Top view of top and middle layers (b) Cross section (c) Insertion Loss                                                                                | 81 |

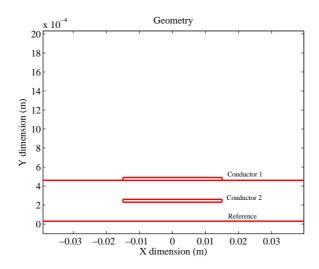

| Figure 56 | Geometry of electrostatic problem with cross-section from Figure 55(b)                                                                                                                             | 82 |

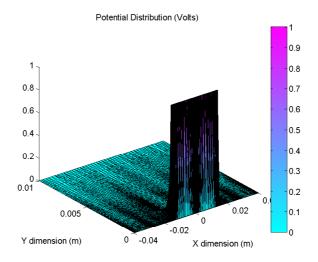

| Figure 57 | Potential distribution due to 1V excitation on top conductor                                                                                                                                       | 83 |

| Figure 58 | Potential distribution due to 1V excitation on middle conductor                                                                                                                                    | 83 |

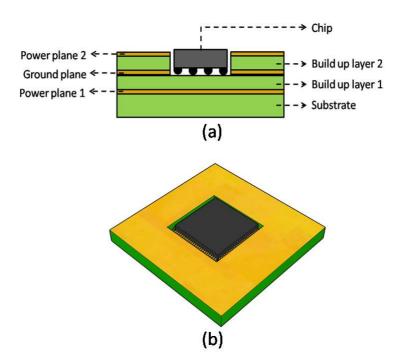

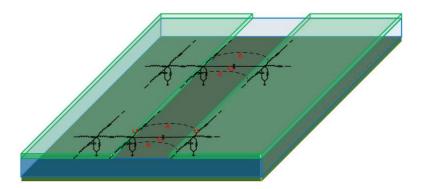

| Figure 59 | Model of package with embedded die in cavity (a)Stack-up (b)3D View                                                                                                                                | 85 |

| Figure 60 | Geometry of multilayer test structure II. (a) Top view of top and middle layers (b) Cross section (c) Insertion Loss                                                                               | 86 |

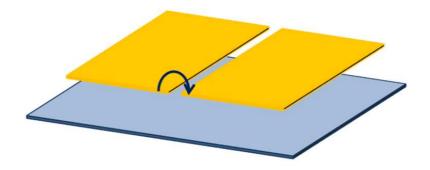

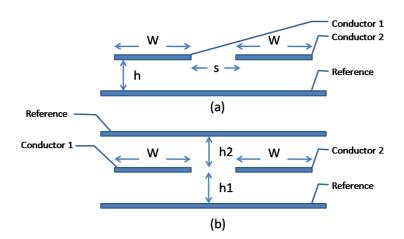

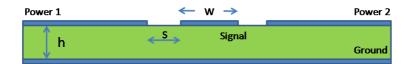

| Figure 61 | Gaps in Power Planes (a)Microstrip type gap (b)Stripline type gap.                                                                                                                                 | 88 |

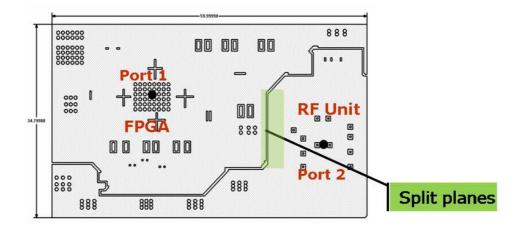

| Figure 62 | Mixed signal board                                                                                                                                                                                 | 90 |

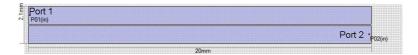

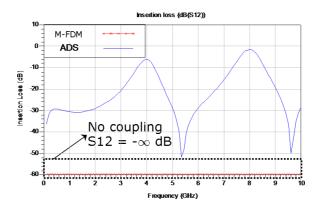

| Figure 63 | Top view of a power bus (20mm×1mm) with 100 $\mu$ m separation                                                                                                                                     | 90 |

| Figure 64 | Insertion loss results for structure shown in Figure 63                                                                                                                                            | 91 |

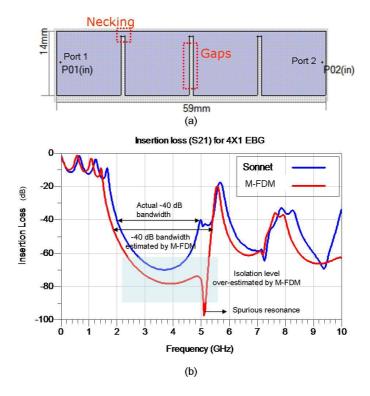

| Figure 65 | (a) Top view of the AI-EBG (b) Insertion loss of the AI-EBG                                    | 92       |

|-----------|------------------------------------------------------------------------------------------------|----------|

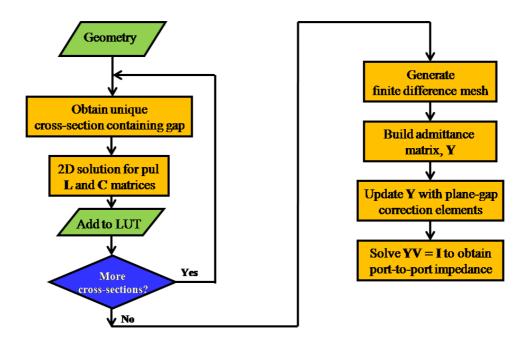

| Figure 66 | Flowchart for the addition of plane-gap augmentation elements                                  | 92       |

| Figure 67 | FDM mesh for the microstrip type slot shown in Figure 61(a)                                    | 94       |

| Figure 68 | Equivalent circuit - M-FDM with PGA models for a microstrip case.                              | 95       |

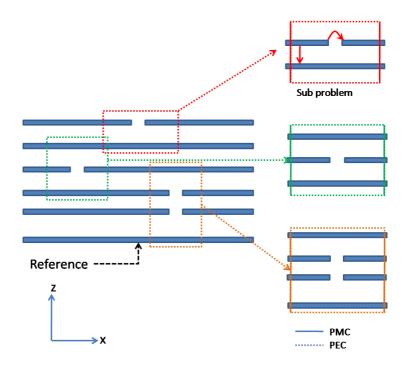

| Figure 69 | Two plane structure with a slot                                                                | 96       |

| Figure 70 | Multilayer geometry with multiple slots                                                        | 98       |

| Figure 71 | Insertion loss (dB) for structure in Figure 65(a) with fringe and gap models                   | 101      |

| Figure 72 | Geometry of coupled lines with a bend                                                          | 101      |

| Figure 73 | Return loss of structure in Figure 72                                                          | 102      |

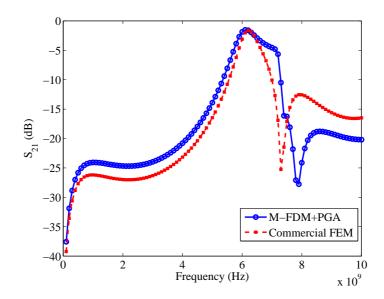

| Figure 74 | Insertion loss of structure in Figure 72                                                       | 103      |

| Figure 75 | Geometry of coupled tapered lines                                                              | 103      |

| Figure 76 | Return loss of structure in Figure 75                                                          | 104      |

| Figure 77 | Insertion loss of structure in Figure 75                                                       | 104      |

| Figure 78 | Insertion loss of structure in Figure 62                                                       | 105      |

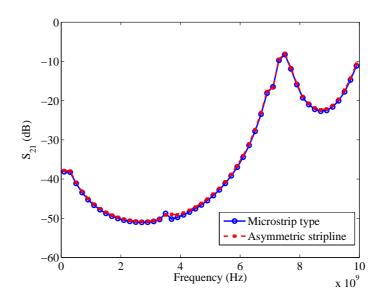

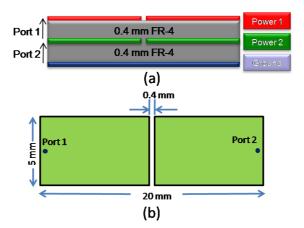

| Figure 79 | Cross-section (a)Microstrip type (b)Symmetric stripline (c)Asymmetric stripline, and (d)Layout | с<br>106 |

| Figure 80 | Insertion loss of structure in Figure 79(a)                                                    | 107      |

| Figure 81 | Insertion loss of structure in Figure 79(b)                                                    | 107      |

| Figure 82 | Insertion loss of structure in Figure 79(c)                                                    | 108      |

| Figure 83 | Test case containing overlapping slots (a) Cross-section (b)Layout.                            | 108      |

| Figure 84 | Insertion loss of structure in Figure 83                                                       | 109      |

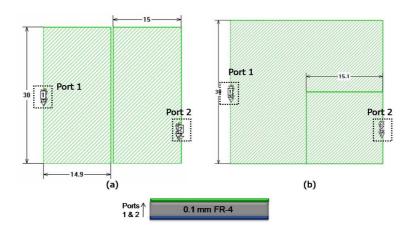

| Figure 85 | Manufactured test vehicles with variable slot widths (a)Type 1 and (b)Type 2                   | 110      |

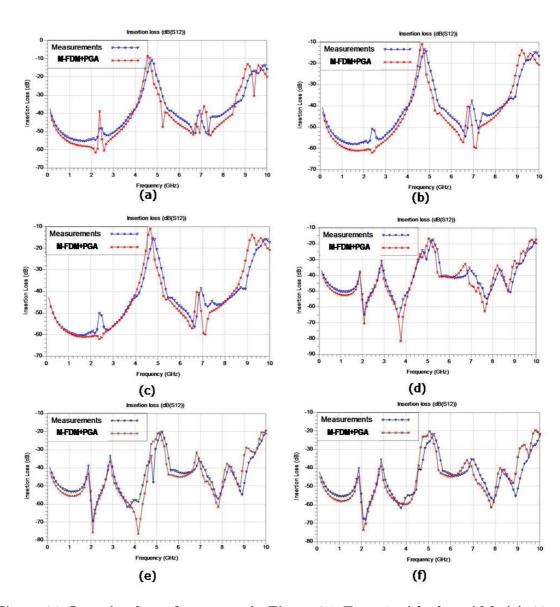

| Figure 86 | Insertion loss of structure in Figure 85                                                       | 111      |

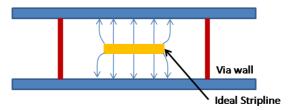

| Figure 87 | Ideal stripline mode                                                                           | 112      |

| Figure 88 | Parallel plate mode of propagation in stripline with non-ideal references.                     | 113      |

| Figure 89  | Four port transmission line model                                                                                                                                                                            | 114    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

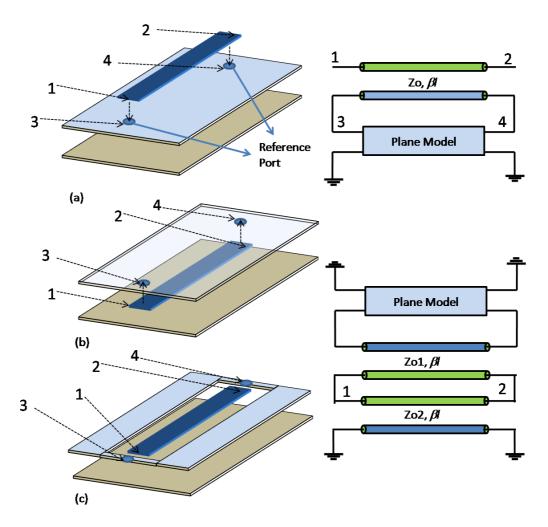

| Figure 90  | Transmission line models for (a) Microstrip (b) Stripline (c) Conductor-backed CPW with shorted side-grounds                                                                                                 | 115    |

| Figure 91  | Transmission line models conductor backed CPW-line with shorted side grounds                                                                                                                                 | 116    |

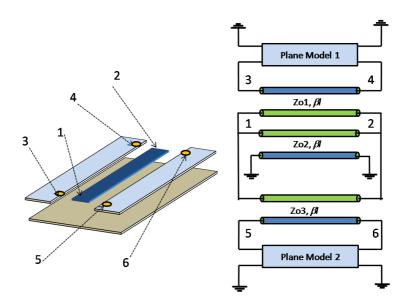

| Figure 92  | Proposed methodology for system level SI-PI analysis                                                                                                                                                         | 118    |

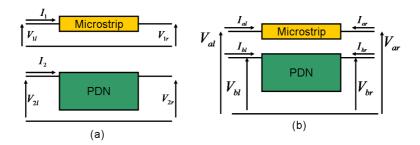

| Figure 93  | 4-port electrical model of signal line                                                                                                                                                                       | 121    |

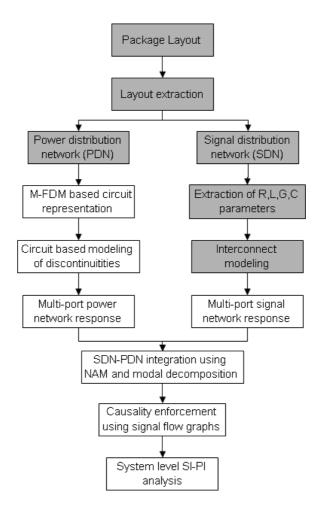

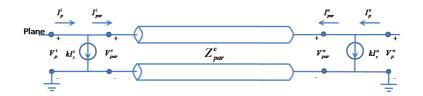

| Figure 94  | (a) Two-port model of microstrip over PDN (b) Equivalent four-port model with common ground reference                                                                                                        | 122    |

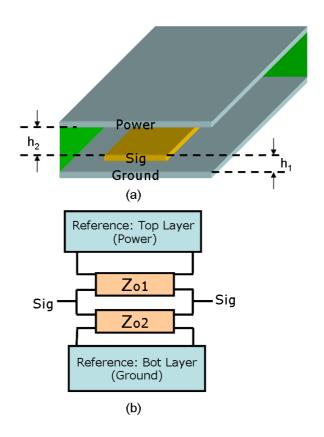

| Figure 95  | (a) 3D schematic of a stripline (b) Equivalent model                                                                                                                                                         | 123    |

| Figure 96  | Conductor backed co-planar waveguide cross section                                                                                                                                                           | 123    |

| Figure 97  | Four port equivalent circuit model for CPW line with shorted coplanar references                                                                                                                             | 124    |

| Figure 98  | Six port equivalent circuit model for CPW line                                                                                                                                                               | 125    |

| Figure 99  | Summary of modal decomposition methods applied to different transmiline configurations                                                                                                                       | ssion- |

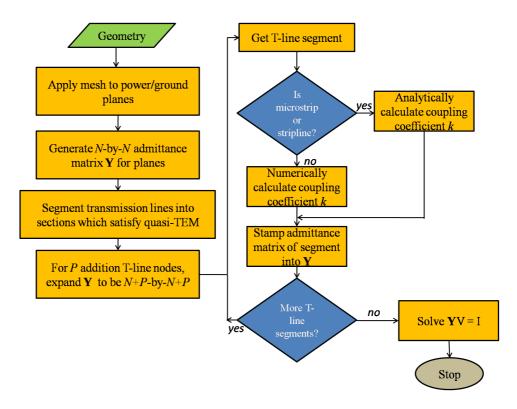

| Figure 100 | Flowchart for integrating transmission lines with M-FDM                                                                                                                                                      | 128    |

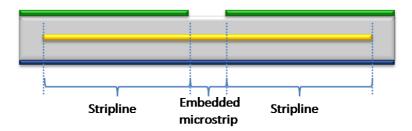

| Figure 101 | Stripline to embedded microstrip transition                                                                                                                                                                  | 128    |

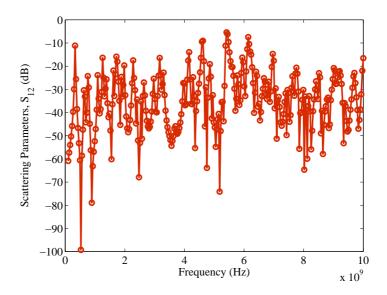

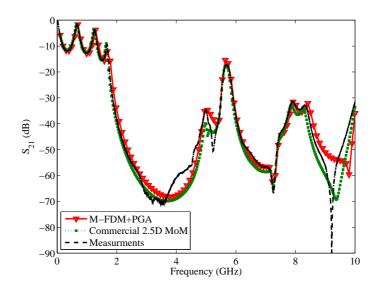

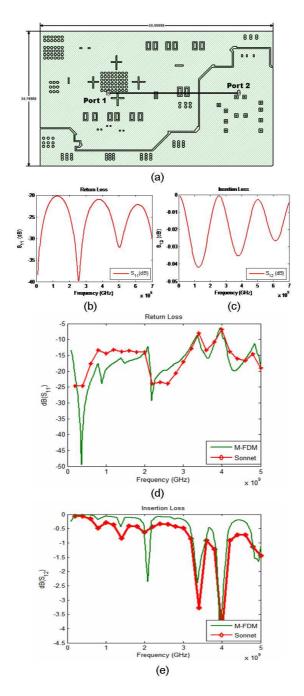

| Figure 102 | 2(a) Mixed signal board with transmission line traversing a slot (b) Return loss results - Ideal Microstrip (c) Insertion loss results - Ideal Microstrip (d) Return loss results (e) Insertion loss results | 130    |

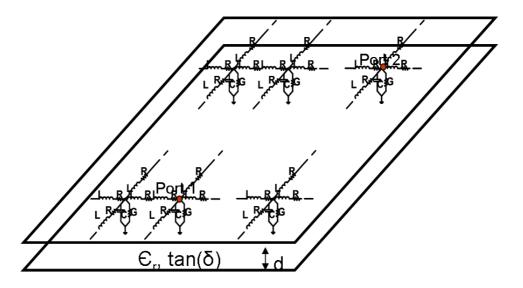

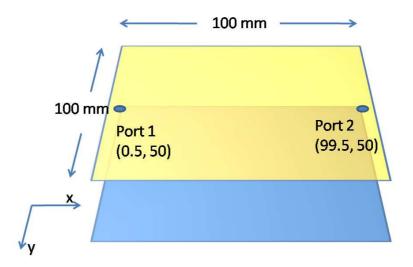

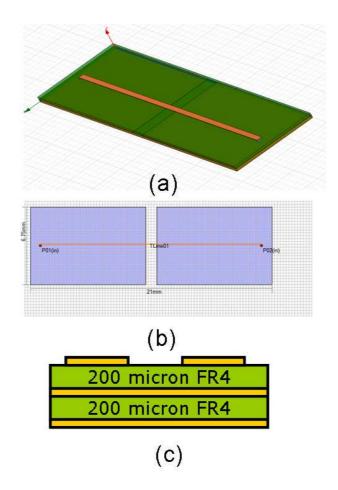

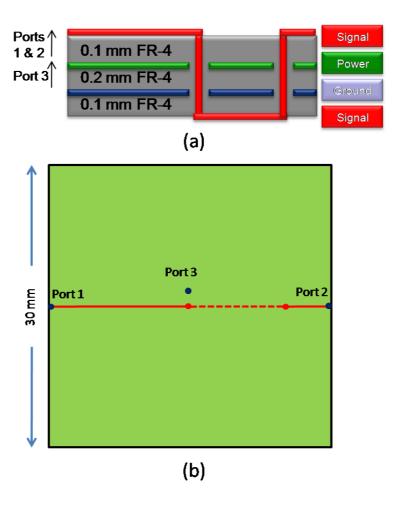

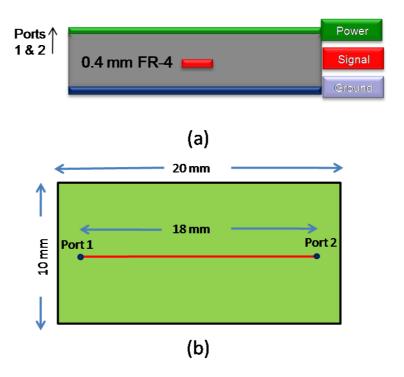

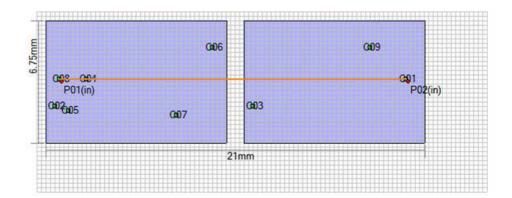

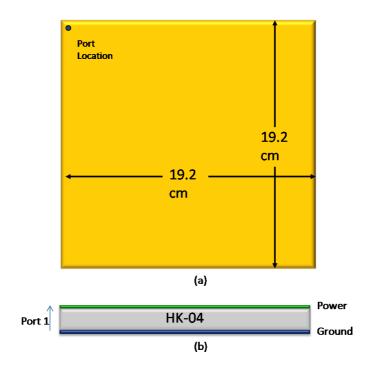

| Figure 103 | Top view of test case. Microstrip interconnects ports 1 and 2                                                                                                                                                | 132    |

| Figure 104 | Insertion loss results for structure in Figure 103                                                                                                                                                           | 133    |

| Figure 105 | (a) Top view of example showing locations of ports (b) Cross section.                                                                                                                                        | 134    |

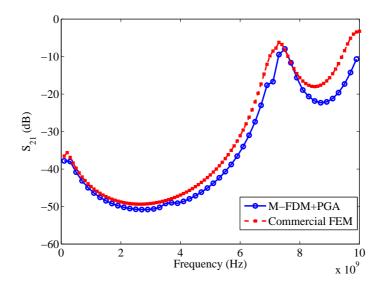

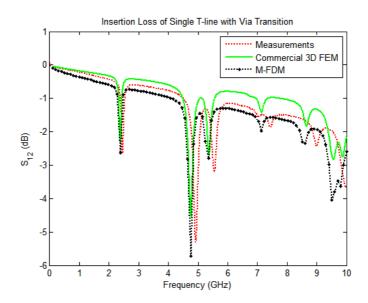

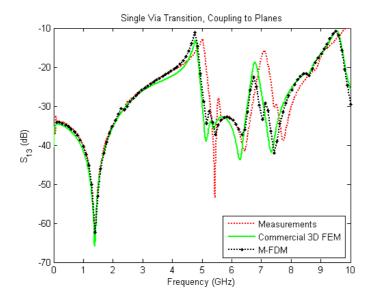

| Figure 106 | SInsertion loss (dB)                                                                                                                                                                                         | 135    |

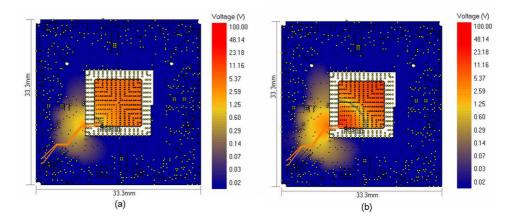

| Figure 107 | <sup>7</sup> 2D voltage distribution plots. (a) 2.4 GHz (b) 5 GHz                                                                                                                                            | 135    |

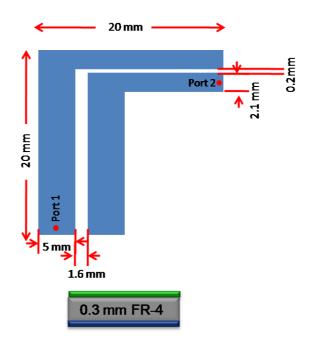

| Figure 108 | B(a) Cross-section and (b) layout of microstrip transition                                                                                                                                                   | 136    |

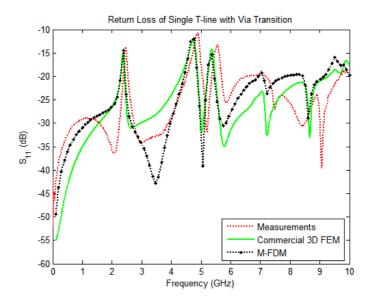

| Figure 109 | Return loss of microstrip transition shown in Figure 108                                                                                                                                                     | 136    |

| Figure 110 | Insertion loss of microstrip transition shown in Figure 108                                                                                                                                                  | 137    |

| Figure 111 Coupling to PDN for microstrip transition shown in Figure 108                                                                | . 137  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 112(a) Cross-section and (b) layout of stripline                                                                                 | . 138  |

| Figure 113 Return loss, $S_{11}$                                                                                                        | . 139  |

| Figure 114(a) Layout and (b)Cross-section of CPW line                                                                                   | . 139  |

| Figure 115 Return loss of structure in Figure 114                                                                                       | . 140  |

| Figure 116 Return loss of structure in Figure 114                                                                                       | . 141  |

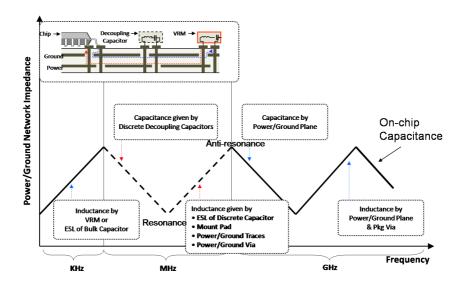

| Figure 117 Typical PDN impedance profile due to interaction between various components of PDN (Courtesy [1])                            |        |

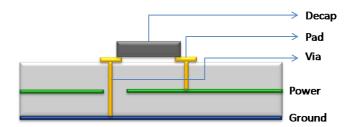

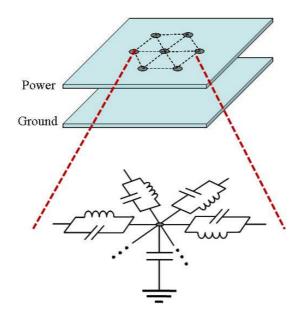

| Figure 118 Surface mount decoupling capacitor mounted on power/ground pair                                                              | r. 146 |

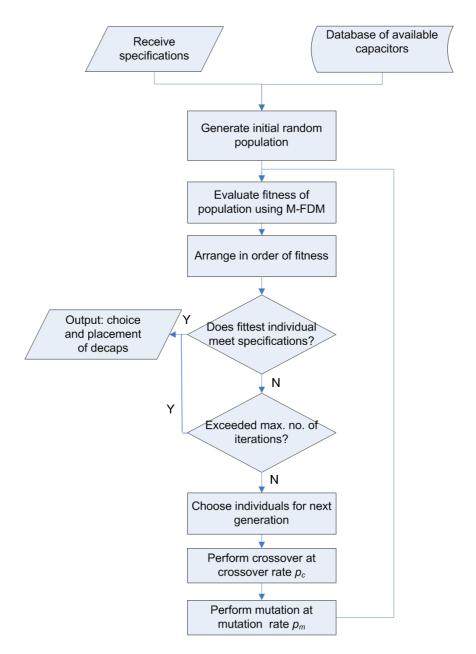

| Figure 119 The flow of the GA based optimizer                                                                                           | . 149  |

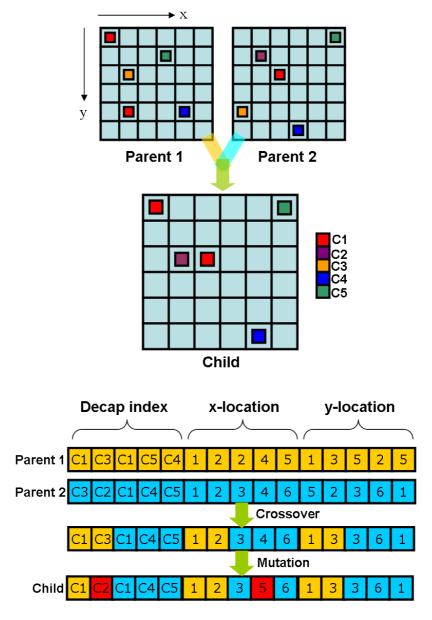

| Figure 120 Schematic Illustration of Crossover and Mutation                                                                             | . 150  |

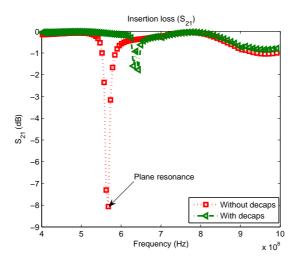

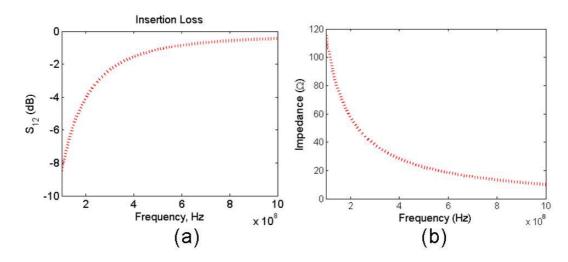

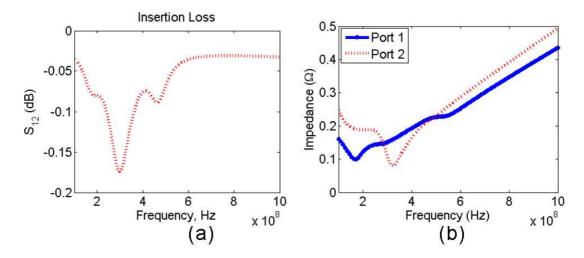

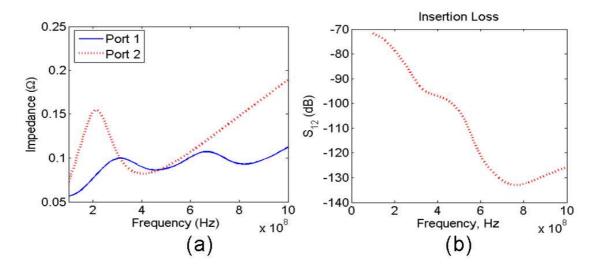

| Figure 121 (a) Insertion loss of transmission line, and (b) Impedance looking into PDN at port locations in Figure 103                  | -      |

| Figure 122 Top View of Optimized Capacitor Placement                                                                                    | . 153  |

| Figure 123 (a) Insertion loss of transmission line, and (b) Impedance looking into PDN at port locations in Figure 122                  | -      |

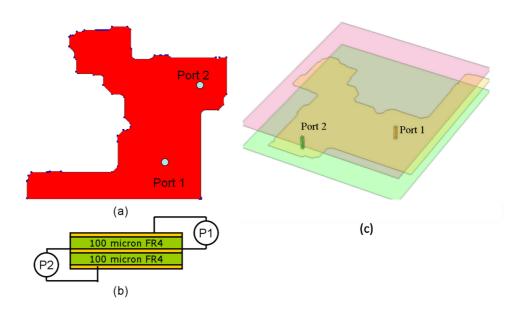

| Figure 124(a) Geometry of middle layer (b) Cross section (c) 3D view                                                                    | . 155  |

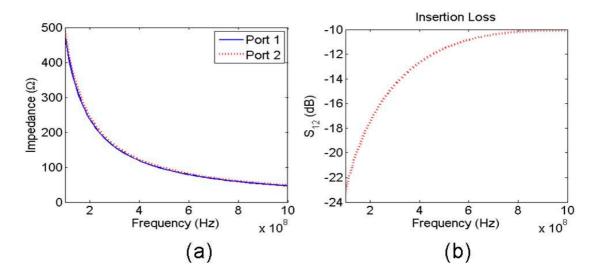

| Figure 125 (a) Impedance looking into PDN at port locations and, (b) Insertion loss between ports $(S_{12})$ of structure in Figure 124 |        |

| Figure 126 (a) Optimized impedance looking into PDN at port locations and (b) Optimized insertion loss between ports $(S_{12})$         | •      |

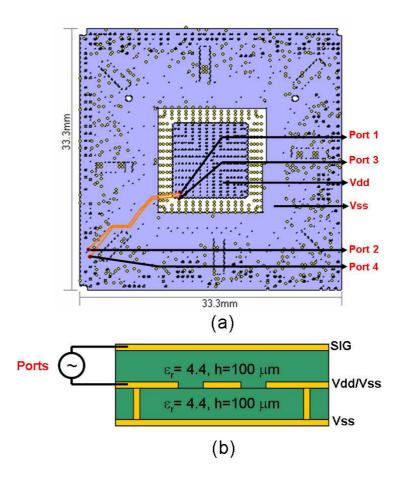

| Figure 127 Structure of test case 3 (a) Top-view (b) Cross-section                                                                      | . 157  |

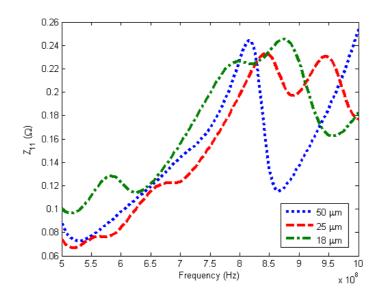

| Figure 128 Self impedance at Port 1 after optimization                                                                                  | . 157  |

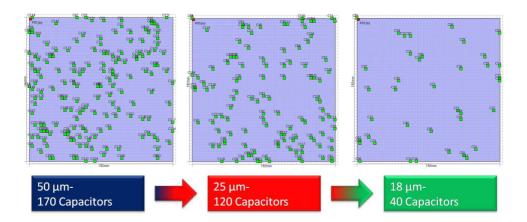

| Figure 129 Locations of Decoupling Capacitors                                                                                           | . 158  |

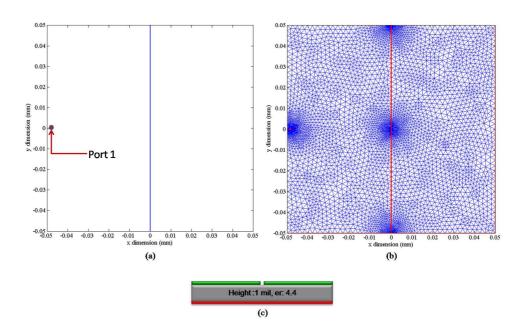

| Figure 130 (a) Mesh generated based on maximum frequency (b) Mesh generated due to geometry                                             |        |

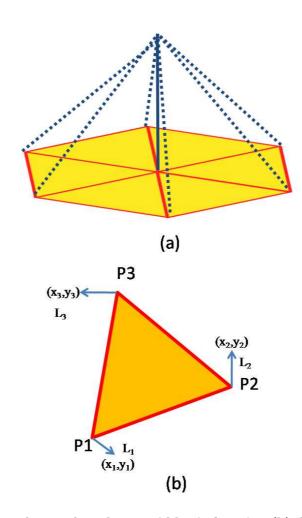

| Figure 131 (a) Triangular mesh and pyramid basis function (b) Cartesian and Simplex coordinates.                                        |        |

| Figure 132 Topology of equivalent circuit for single plane-pair structures                                                              | . 166  |

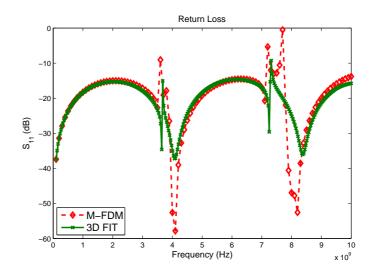

| Figure 133 (a) Geometry of split-plane structure (b) Mesh (c) Cross-section.                                   |   | 167 |

|----------------------------------------------------------------------------------------------------------------|---|-----|

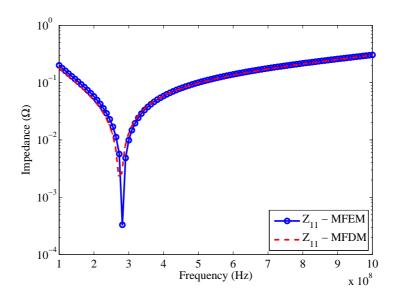

| Figure 134 Self Impedance $Z_{11}$                                                                             |   | 168 |

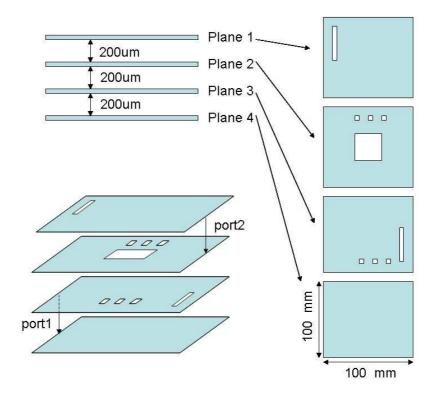

| Figure 135 Four-plane test structure: cross section, location of ports, and t view of each plane               | - | 169 |

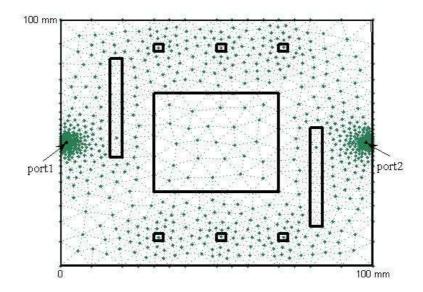

| Figure 136 Top view of the meshed planes                                                                       |   | 170 |

| Figure 137 (a) Two-port networks with separate references (b) Combined for port network with common reference. |   | 171 |

| Figure 138 Insertion loss for structure in Figure 33                                                           |   | 173 |

| Figure 139 Magnitude of Self Impedance $(Z_{11})$                                                              |   | 174 |

| Figure 140 Magnitude of the transfer impedance $(Z_{12})$                                                      |   | 175 |

#### **SUMMARY**

Mixed signal system-on-package (SoP) technology is a key enabler for increasing functional integration, especially in mobile and wireless systems. SoP allows the integration of high speed digital, RF and passive components at a package level, thereby preserving performance at a lower cost compared to system-on-chip based solutions. Due to the presence of multiple dissimilar modules, each having unique power supply requirements, the design of the power distribution network (PDN) becomes critical.

Typically, this PDN is designed as alternating layers of power and ground planes with signal interconnects routed in between or on top of the planes. This arrangement serves two purposes - firstly, it allows a reduction in the package inductance, and secondly, signal lines on separate layers are isolated from each other due to the shielding effect of the planes.

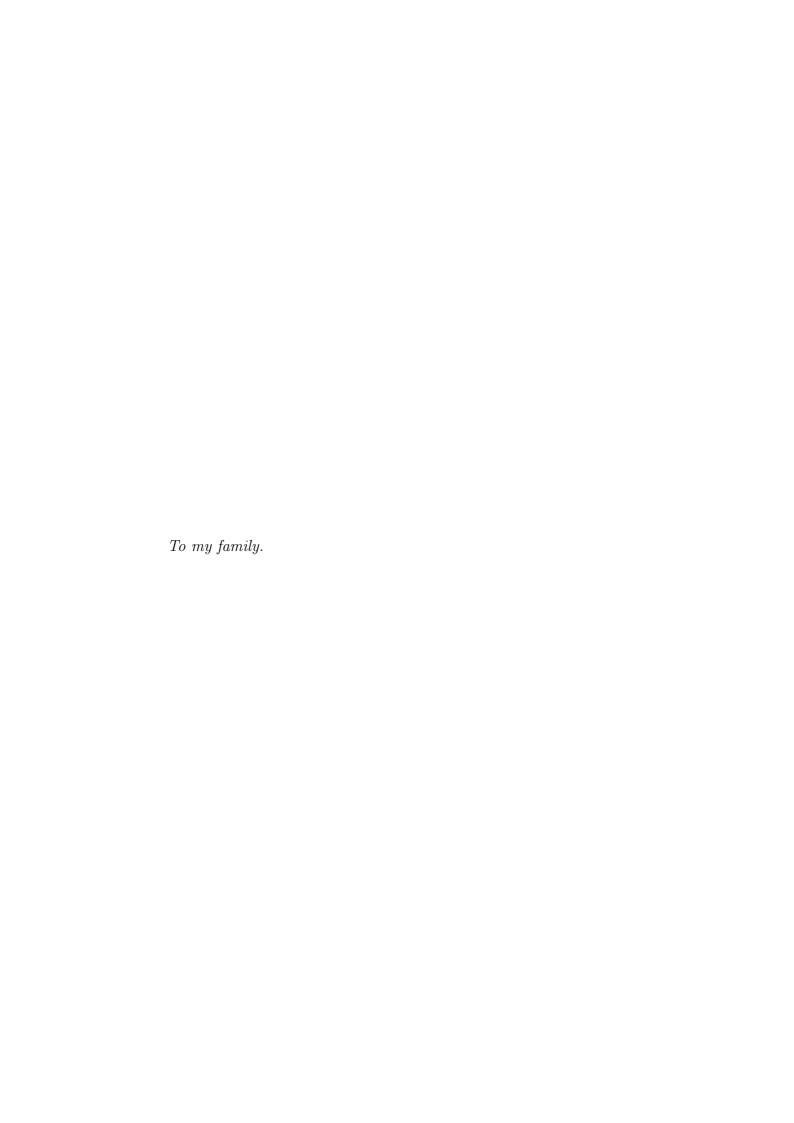

In the case of a SoP module, to provide DC isolation between power supplies, the power and ground planes may be segmented into islands. In this case, electromagnetic (EM) coupling becomes a critical factor. Consider the SoP containing four modules shown in Figure 1. The digital module is the source of the simultaneous switching noise (SSN) containing harmonics at multiples of the clock frequency. For the case of a cell phone receiver, even relatively low levels of insertion loss between the digital and RF modules can significantly degrade the performance of the front-end low-noise amplifier. Also, decreasing supply voltages coupled with increasing power requirements tends to place stringent requirements on the target impedance [3] of the digital IC. Time-efficient and accurate signal and power integrity (SI/PI) simulation is therefore a critical component of the SoP design flow.

The goal for the simulation of multi-layer power/ground planes, is the following: Given a stack-up and other geometrical information, it is required to find the network parameters (S/Y/Z) between port locations. For simple structures, it is possible to

Figure 1. A System on Package Module (courtesy [2]).

use existing commercially available methods (full-wave EM solvers) to obtain the response of the PDN. However, commercial packages have extremely complicated stack-ups, and the trend to increasing integration at the package level only points to increasing complexity. It is computationally intractable to solve these problems using these existing methods.

The approach proposed in this thesis for obtaining the response of the PDN is the multi-layer finite difference method (M-FDM). A surface mesh / finite difference based approach is developed, which leads to a system matrix that is sparse and banded, and can be solved efficiently. The approach relies on approximating the electric field distribution in power/ground planes. Certain geometrical features may invalidate these approximations, which may lead to significant inaccuracy in simulation results. Thus, methods to update the system matrix to restore accuracy to M-FDM, while not adding significant computational overhead, have been considered. These methods are called the fringe augmentation (FA) and plane gap augmentation (PGA) methods.

While discussing the simulation of multi-layer packages, it is not possible to isolate the PDN from the signal traces routed between them. With increasing frequency, these signal traces behave as transmission lines, and hence, their distributed properties such as delay and phase become important. Also, signal traces use the PDN as their reference planes, and hence their characteristics cannot be decoupled from the PDN. Discontinuities in the PDN can manifest as signal integrity problems such as reduction in eye height or increased jitter.

Finally, an application of M-FDM for the optimization of a PDN design using Genetic Algorithms (GA) is considered. From a design perspective, the requirement on the PDN is that it should represent a low impedance at all frequencies at which current transients exist. Traditionally, the solution to providing a low impedance power supply as seen by the device has been to place decoupling capacitors (decaps) across the power supply pins [4].

The impedance profile of the PDN can be optimized by carefully choosing the values and placement locations of the decaps. This is critical since the anti-resonances (or parallel-resonances) that occur between decaps and between the decap and the PDN can lead to an impedance maximum. If this impedance maximum occurs at a frequency at which current transients exist, the severity of the SSN can be exacerbated. This choice and placement of decoupling capacitors can be accomplished using an optimization engine based on a genetic algorithm (GA).

To summarize, the contributions of this research are the following:

- The development of a PDN modeler for multi-layer packages and boards called the the multi-layer finite difference method.

- 2. The enhancement of M-FDM using multi-port connection networks to include the effect of fringe fields and gap coupling.

- 3. An adaptive triangular mesh based scheme called the multi-layer finite element method (MFEM) to address the limitations of M-FDM

- 4. The use of modal decomposition for the co-simulation of signal nets with the PDN.

- 5. The use of a robust GA-based optimizer for the selection and placement of decoupling capacitors in multi-layer geometries.

6. The implementation of these methods in a tool called MSDT 1.

#### CHAPTER 1

# THEORETICAL BACKGROUND AND SUMMARY OF CONTRIBUTIONS

#### 1.1 Electrical Bottlenecks in Microelectronic Packaging

An electronic package or board module is an electromechanical platform which has traditionally provided the following functions for an integrated circuit (IC)[5]:

- 1. Mechanical support and protection

- 2. Thermal dissipation

- 3. Geometric translations

- 4. Interfaces to the next level package

- 5. Electrical connectivity

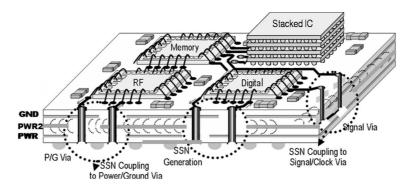

However, modern packages are moving beyond these traditional roles. In a complex multi-functional device, system level integration occurs in stages, where the I/O pads of ICs are connected to individual packages or to multi-chip modules (MCM). This is the first level package, a few of which are integrated together onto daughter cards or printed wiring boards (PWB). These daughter cards may then be connected to backplanes, as shown in Figure 2.

While the reduction of size and corresponding increases in power and operating frequency have been key drivers for ICs, a corresponding scaling on package has not occurred, leading to the package being a significant electrical bottleneck in terms of supporting high frequency signalling. The solution to this problem has been to progressively integrate more functionality at lower levels of packaging. This has resulted in system integration strategies such as the system on package (SoP) approach, where multiple dissimilar components are integrated together.

Figure 2. Package hierarchy.

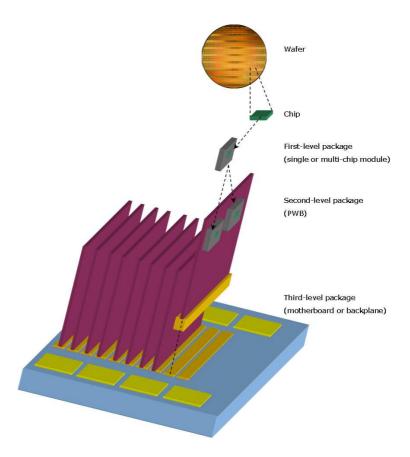

Mixed signal SoP technology is a key enabler for increasing functional integration, especially in mobile and wireless systems. SoP allows the integration of high speed digital, RF and passive components in the first-level package, thereby preserving performance at a lower cost compared to system-on-chip based solutions. A conceptual SoP test bed is shown in Figure 3[2]. This illustration depicts the integration of different kinds of circuits on package. These circuits include embedded RF thin-film components such as resistors, inductors and antennas. To support high performance digital components, SoP also supports digital thin-film components such as embedded capacitors. Also, shown are optical waveguides with laser diodes for signaling, other packaged and bare modules, and a MEMS device.

While conceptually this integration scheme shows incredible promise in revolutionizing the electronics industry, there are still several challenges to be faced. One

Figure 3. Schematic of a system on package (courtesy [2]).

of the key reasons for the success of past efforts in system integration (for example, the system-on-chip), is because of key advances in design automation technology [6]. Novel technology advances require support for the designer, and in this regard, Computer-aided-design (CAD) for SoP is still emerging.

The contributions of this work are aimed primarily at improving the state-of-theart in design tools for conventional packages and boards, while also addressing some of the new challenges posed by SoP. The problem being considered is the design of the power distribution network (PDN). The challenge posed by SoP is primarily due to the integration of multiple dissimilar modules, each having unique power supply requirements. In traditional packaging, each of these dissimilar modules have power supplies that are relatively isolated from each other. This isolation is essential, because some modules are *noisy* (such as high-speed digital), while others are extremely sensitive to noise (such as RF-circuits). In this context, the noise is because of simultaneous switching of multiple circuits, a characteristic of synchronous digital circuits. The magnitude and impact of this noise is dependant on the design of the power supply, which in turn depends on accurate and efficient design tools capable of analyzing the complex and large problems posed by next generation package PDNs.

Typically, this PDN is designed as alternating layers of power and ground planes with signal interconnects routed in between or on top of the planes. This arrangement serves two purposes - firstly, it allows a reduction in the package inductance,

and secondly, signal lines on separate layers are isolated from each other due to the shielding effect of the planes. The former, i.e., reduction in package inductance, is one of the design guidelines for the reduction of simultaneous switch noise (SSN).

#### 1.2 Motivation: Increasing Efficiency of the Design Flow

A typical approach that is used in the industry for the design of printed circuit boards (PCBs) and packages is shown in Figure 4. This approach is called the partialsimulation approach to PCB/package design and involves making modifications to an original design layout based on rigorous simulations and analysis. In this approach a design engineer develops an initial layout of a system based on the design specifications of the product and the design rules of the fabrication process. The signal distribution network (SDN) and the PDN, which are a part of this layout are then analyzed using rigorous post-layout simulations. The simulation and analysis of the SDN, termed as signal integrity (SI), is typically carried out in the time domain and involves analyzing voltage drops on interconnects, conductor and substrate losses, reflections on electrically long interconnects, impedance mismatches, and transmission line discontinuities like vias and bends. On the other hand, the simulation and analysis of the PDN, termed as power integrity (PI), is performed in the frequency domain and primarily involves analyzing power/ground planes, decoupling capacitors, and simultaneous switching noise (SSN). The original layout is modified based on these SI and PI analyses to account for any design flaws. This process is often iterated through multiple times until the SI and PI analysis are satisfactory. The layout is then sent for fabrication. The physical prototype obtained from fabrication is measured and analyzed in a laboratory. Design flaws arising due to parasitic effects that could not be captured in the simulation phase are accounted for here by performing the necessary layout modifications. This modified layout is then re-fabricated and re-measured till a working prototype of the required system is obtained.

Figure 4. Current design flow.

The bottleneck of the above flow is the need to iteratively perform time expensive EM simulations for post-layout verification. Major design flaws, when detected post-layout, are costly and can cause significant delays.

The simulation method proposed in this research is called the multi-layer finite difference method (M-FDM).

The proposed design flow (Figure 5) adds an additional step, based on the computational efficiency of M-FDM. Since simulations with M-FDM, as will be shown, are relatively inexpensive, an iterated verification and re-design can be performed at the pre-layout stage. Catching major design flaws at this step can significantly reduce budget overruns. These simulations are used to guide the final layout process, which as before is validated using full-wave EM simulations, or M-FDM. This process leads to minimizing the number of EM iterations, reducing cost and time to market.

### 1.3 Simultaneous Switching Noise

The elaborate design of the PDN is required to provide a clean and stable power supply to the switching elements on-chip. These switching elements are primarily

Figure 5. Efficient design flow.

CMOS drivers and other logic gates. Typical digital computers are synchronous circuits, with their various components synchronized by a clock. At each clock cycle, depending on the process being carried out, a significant portion of the circuits on-chip can switch, leading to simultaneous switching noise (SSN).

SSN is created as a consequence of Faraday's law, which can be stated as:

$$e = -L\frac{\mathrm{d}I}{\mathrm{d}t} \tag{1}$$

where e is the electromotive force, or the potential drop across an inductor, L, subjected to a time-varying current. In digital systems, this inductance is the effective inductance between the device ground (or power supply) and the system ground (or power supply). The direction of this induced electromotive force is determined by Lenz's law. The system ground is usually located on a voltage regulator module (VRM), off-chip, and the switching current required by the switching transistors on-chip follows a loop through the board and the package, which essentially constitutes

this inductance.

In a digital device, there are usually two kinds of circuits that need to be powered, the core and the I/O circuits. The core circuits are entirely contained on an IC, while the I/O circuits allow communication between multiple ICs (for example, memory and CPU), which requires that the signal traces exit the chip, and traverse the package and board.

For a single core circuit, the maximum voltage dropped across the inductor can be shown[1] to be

$$\Delta v \approx \frac{L_c \times V_{dd}}{Rt_r} \tag{2}$$

where  $t_r$  is the rise time of the switching signal, and R is the interconnection resistance, and  $L_c$  is the loop inductance associated with the core I/O circuits.

Since I/O circuits drive off-chip interconnections, which are typically much longer, these behave as transmission lines. Hence, the expression for the maximum voltage dropped across a I/O circuit is[1]:

$$\Delta v \approx \frac{L_{I/O} \times V_{dd}}{Z_0 t_r} \tag{3}$$

where  $Z_0$  is the characteristic impedance of the transmission line and  $L_{I/O}$  is the loop inductance of the I/O circuits.

#### 1.3.1 SSN and Signal Integrity

Simultaneous switching noise causes transients on the DC power supply, as seen by the drivers. To see the effect of these transients on signaling, consider the voltage at the input end of a transmission line for a pulse with a rise time  $t_r$ , given by

$$v(t) = \begin{cases} \frac{Z_o V_{dd}}{L t_r} \left( \frac{L^2}{Z_0^2} \left[ e^{\frac{-t}{(L/Z_0)}} - 1 \right] + \frac{L}{Z_0} t \right) & \text{for } t \le t_r \\ A + B \left( 1 - e^{\frac{-t}{L/Z_0}} \right) & \text{for } t > t_r \end{cases}$$

$$(4)$$

where

$$A = V_{dd} - [V_{dd} - v(t_r)] e^{\frac{t_r}{L/Z_0}} B = [V_{dd} - v(t_r)] e^{\frac{t_r}{L/Z_0}}$$

(5)

Figure 6. SSN induced jitter (courtesy [1]).

Clearly, transients on the power supply rail can lead to uncertainty in the rise time of the input pulse, causing jitter.

Figure 6, reproduced with modifications from [1], illustrates the impact of SSN on signal jitter. An increase in voltage droop on the power supply strongly correlates with increasing rise times. For pseudo-random bit sequences, SSN (and hence voltage droop) is random, and hence there is uncertainty in the rise time of the signal. This uncertainty is the jitter caused due to SSN. Thus SSN can lead to delay and false switching.

#### 1.3.2 Coupling in Package Structures

In the case of a SoP module, to provide DC isolation between power supplies, the power and ground planes may be segmented into islands. In this case, EM coupling becomes a critical factor. Consider an SoP containing four modules shown in Figure 1. The digital module is the source of the simultaneous switching noise (SSN) containing harmonics at multiples of the clock frequency. For the case of a cell phone receiver, a -60dB insertion loss between the digital and RF modules can significantly degrade the performance of the front-end low-noise amplifier.

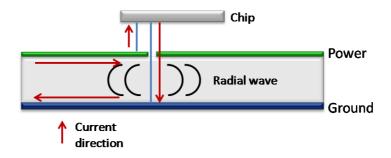

Figure 7 shows a three layer package PDN supplying power to a mixed-signal IC. Multiple power supplies are typically required in modern SoPs due to the various

Figure 7. SSN coupling mechanisms in a realistic package.

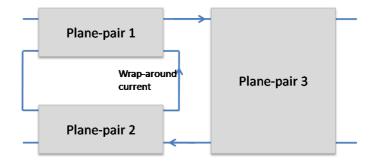

integrated components. Split planes are required to provide DC isolation to the different supply voltages. Also, holes are created in the solid power/ground planes in order to route signals or to provide via anti-pads. The switching activity of digital circuitry causes a time varying current to be drawn from its power supply terminals, Vdd1-Gnd1. Due to the associated inductance of the loop, SSN is generated. SSN can couple horizontally across a plane pair and across power islands. Also, SSN couples vertically through vias, and through apertures. This can be regarded as a coupling by means of a wrap-around current on the edges of the planes. Through these mechanisms, ground bounce can occur across the Vdd2-Gnd2 planes in Figure 7. Thus, it becomes critical to model split planes and apertures.

#### 1.3.3 Target Impedance

Digital components are broadband circuits whose switching circuits typically have energy concentrated in multiple discrete frequencies, which tend to be harmonics of the various clock frequencies that are employed. On the other hand, the transient behavior of the system depends on a large number of variables, including some high level considerations such as the program being executed.

The PDN has a capacitive behavior at low frequencies and shows inductive behavior as we move towards the higher frequency range. However, this inductive trend is punctuated with a number of discrete resonances and anti-resonances. As far as a driver on-chip is concerned, the PDN must appear to be an ideal AC ground between its power and ground terminals. Therefore, the inductance of the PDN must be reduced to enable easy flow of charge to the required active circuits to mitigate the noise. The target impedance of the PDN is decided based on the core voltage and average current drawn by the processor. Based on the equations for voltage droop across the power supply impedance, it is possible to define a maximum allowed ripple. In practice, the maximum allowed ripple is assumed be 5% of the power supply voltage (Vdd)[3].

$$Z_{tar} = \frac{Vdd \times 5\%}{Id \times 50\%} \tag{6}$$

The current term in the denominator is  $\frac{1}{2}$  the switching current in a clock cycle, which is assumed to be the current in each clock edge.

Decreasing supply voltages coupled with increasing power requirements tends to place stringent requirements on the target impedance [3] of the digital part. Clearly, time-efficient and accurate signal and power integrity (SI/PI) simulation will be a critical component of the SoP design flow.

#### 1.4 Electrical Simulation of the Package

To meet the demands of high-performance packages, a simulation tool will have to capture the effects of the following geometrical features of the package:

- 1. Multiple power supply and signal layers

- 2. Apertures in power/ground planes

- 3. Slots in power/ground planes

- 4. Multiple signal line configurations (microstrip, stripline, CPW; single ended, differential)

- 5. Power/ground planes with necking (i.e. narrow strips)

- 6. Signal and power supply vias

- 7. Decoupling capacitors

The simulation methods for packages may be classified based on their formulation as circuit-based or EM-based, as well as a a third category which borrows conceptually from the two, and is labeled hybrid. These methods face a trade-off between their generality and CPU Time, as illustrated in Figure 8. Here, generality is meant to emphasize the class of problems for which a particular method can provide reasonably accurate results.

#### 1.4.1 Circuit-based Methods

The simplest PDN model for packages is an equivalent inductance to model each ground pin. This has been used for quad flat packages (QFP) [7] and other lead-frame packages. However, for high speed micro-processors and ASICs, power/ground planes are routinely used to distribute power. These power/ground planes are electrically large and can support steady state cavity resonances. These resonance occur

Figure 8. Trade-off between generality and CPU time for package simulation methods.

because the excitation port, for example, the I/O pin of a microprocessor can create noise which propagates in the lateral directions as a radial wave. This radial wave impinges upon what is effectively an open-circuit boundary at the edges of the package which causes reflections. Hence, circuit-based methods using partial inductance are applicable for low-frequency applications where the distributed effects of the PDN geometry can be neglected.

A circuit-based method which can be applied to package geometries is based on the transmission-line method (TLM). In this method, the power-plane is modeled as a 2D-grid of transmission line segments [8]. This method is applicable only for twolayer geometries, and is the basis for the transmission matrix method (to be discussed in Section 1.4.3.1).

Figure 9. (a) Surface and (b) Volumetric mesh.

#### 1.4.2 EM-based Methods

Of the full-wave EM methods available to simulate a package, the techniques resorted to are conventionally frequency domain methods. Packages are highly resonant low-loss structures. To completely characterize a package (in the time domain) requires simulating it for an impractically long period of time.

Full-wave frequency domain simulation methods can be broadly classified under the integral equation based method-of-moments (MoM) or differential equation based finite element method (FEM). These methods are accurate for the broadest class of problems. For package geometries, MoM methods are available [9][10] that use multi-layer Green's functions which enable it to use a surface mesh (Figure 9(a)). However, the resulting system matrix is dense. Hence, the computational complexity for such methods can be large, and the goal of full-package simulation is intractable. FEM-based techniques, on the other hand, lead to volumetric meshes (Figure 9(b)). Although the resultant system matrix is sparse, the use of a volumetric mesh results in rapid growth of the number of unknowns as problem size grows. Since packages are electrically large structures, only small subdomains of the package geometry can be simulated using FEM.

#### 1.4.3 Hybrid Methods

A package can be described as a planar circuit. The concept of planar circuits was introduced in [11]. A planar circuit is a microwave structure in which one of the three dimensions, say z, is much smaller than the wavelength. Under this condition, it can be assumed that the field is invariant along the z-direction. Hence,  $\frac{\partial}{\partial z} = 0$  and the Helmholtz wave equation can be reduced to 2 dimensions as follows:

$$\left(\nabla_t^2 + k^2\right) \mathbf{u} = j\omega\mu dJ \tag{7}$$

Figure 10. Cascade connection in TMM.

where

$$\nabla_t^2 = \left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2}\right)$$

$$k = j\omega\sqrt{\mu\varepsilon}$$

The open circuit at the boundary can be represented by a magnetic wall or Neumann boundary condition, which completes the problem formulation.

The two most prominent solutions in literature are the transmission matrix method (TMM)[12] and the Green's function based segmentation technique.

#### 1.4.3.1 The Transmission Matrix Method

TMM is a technique used to solve the equivalent circuit representation that results under the finite difference solution of the wave equation. The equivalent circuit described in [8] can conventionally be solved using SPICE. However, the same equivalent circuit can also be reduced in terms of cascaded transmission matrices, as shown in Figure 10. Each of the cascaded T-matrices represents one column of cells in the discretized geometry. Thus, port to port ABCD parameters can be calculated which can in turn be used to calculate S-, Y-, or Z-parameters.

The advantage of this approach is that the overall system to be solved for a problem containing N cells is only of order  $\sqrt{N}$ , and with the ability to incorporate decoupling capacitors, this technique does have considerable advantages for single plane-pair geometries.

Using Gauss elimination, the equivalent circuit solved directly (resulting in a system containing N equations) will have a computational complexity of  $O(N^3)$ , while

by employing TMM, the complexity reduces to  $O(N^{1.5})$ . Memory reduces from  $O(N^2)$  to O(N).

However, it must be noted that while the equivalent circuit when solved directly leads to a much larger matrix, this matrix is also sparse. Thus, by employing reordering techniques such as nested dissection [13], and by using an optimized sparse-solver, the computational complexity of direct solution can be reduced to  $O(N^{1.5})$  and memory to  $O(N \log N)$ .

Thus, in terms of computational effort, TMM has a slight if not overwhelming advantage. This advantage needs to be reconciled with the limitations of the technique, which are:

- 1. TMM relies on identical columns of cells. The matrix-power operations that have to be performed while cascading the T-matrices requires a similarity transformation for each non-identical column. Thus, this technique works well for rectangular geometries, but is not as efficient for irregular geometries.

- 2. The matrix power operations lead to an ill-conditioned system.

- 3. The modeling of gap-coupling may require placing elements between columns of cells which are not neighbors. This cannot be done under TMM, as the cascading property is lost.

- 4. TMM cannot be applied for multiple plane-pair geometries with apertures, as this would require placing coupling elements between non adjacent layers.

### 1.4.3.2 The Segmentation Technique

The impedance matrix of a rectangular plane-pair of dimensions  $a \times b$ , with plane separation d and dielectric constant  $\varepsilon$ , with aribitrary port locations  $(x_i, y_i)$  and  $(x_j, y_j)$ , can be derived as [11]:

$$Z_{ij}(\omega) = j\omega\mu d \sum_{n=0}^{\infty} \sum_{m=0}^{\infty} \frac{\varepsilon_n^2 \varepsilon_m^2}{(k_{mn}^2 - k^2) ab} f(x_i, y_i, x_j, y_j)$$

(8)

Figure 11. Equivalent circuit for a plane-pair.

where

$$f(x_i, y_i, x_j, y_j) = \left(\cos \frac{m\pi x_i}{a} \sin c \frac{m\pi t_{xi}}{2a}\right) \left(\cos \frac{n\pi y_i}{b} \sin c \frac{n\pi t_{yi}}{2b}\right)$$

$$\left(\cos \frac{m\pi x_j}{a} \sin c \frac{m\pi t_{xj}}{2a}\right) \left(\cos \frac{n\pi y_j}{b} \sin c \frac{n\pi t_{yj}}{2b}\right)$$

(9)

Here  $t_{x(i/j)}, t_{y(i/j)}$  is the size of the port,  $k_{mn}^2 = \left(\frac{m\pi}{a}\right)^2 + \left(\frac{n\pi}{b}\right)^2$  and k is the complex wavenumber. Further details can be found in [14][15][16].

While (9) provides a numerical technique for calculating the response of a rectangular plane-pair, this response cannot be directly used in a system-level simulation, containing other circuit elements such as non-linear circuitry and terminations. An intermediate step is required whereby the frequency response is used to synthesize a SPICE netlist. This macro-modeling step is not desirable because the synthesized equivalent circuit may not preserve passivity. Thus, to eliminate this step, (9) can be used to directly synthesize an equivalent circuit. This process is described in [17], and the equivalent circuit for a plane-pair is shown in Fig 11.

When irregular geometries are encountered, the structure is segmented into sections which are rectangular. The rectangular sections are then simulated separately and the boundaries between segments are stitched together using many "virtual

Figure 12. Segmentation of an L-shaped plane-pair.

ports". An example of this segmentation process is shown in Figure 12.

The limitations of this technique are:

- 1. Equation (9) requires a double infinite sum for all the modes that may exist in the structure. The convergence of the sum may be slow. However, an acceleration technique has been proposed in [18], which compromises on accuracy.

- 2. The technique is cumbersome for extremely irregular geometries, which requires several virtual ports between segments. Also, for multi-layered structures with apertures, the segmentation must be performed both horizontally and vertically.

## 1.5 Overview of the Proposed Hybrid Method

The methods developed in this thesis are based on a combination of insights from circuit theory and EM-field solvers, specifically tuned to modeling electrically large, multi-layer planar package geometries. The flow for the proposed method is shown in Figure 13.

Figure 13. Overview of proposed hybrid method.

Modern packages consist of the PDN and the SDN. As can be expected, the response of the SDN is highly dependent on the design of the PDN. This is because the interconnects that form the SDN use the power/ground planes of the PDN as their reference planes. In this thesis, the complexity of the problem is reduced by decoupling the SDN and PDN problems. Thus the PDN and the SDN can be simulated in isolation, and the obtained response can finally be integrated together.

### 1. Simulation of the PDN in isolation:

The PDN problem involves obtaining the frequency response of an irregular, electrically large, multi-layer power/ground planes containing apertures, vias and decoupling capacitors. This thesis focuses on the development of two methods, the second of which is an evolutionary development of the first. These methods are the multi-layer finite difference method (M-FDM) and the multi-layer finite element method (M-FEM). Both methods are based on the extraction of

an equivalent circuit model for a two-layer geometry, which is then extended to multiple layers based on transformations of the admittance matrix (to be described in Section 1.6.

### 2. Simulation of the SDN in isolation

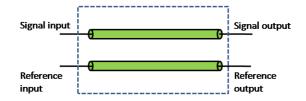

The difficulty in using a full-wave method for co-simulating the SDN and the PDN is primarily because the interconnection width is much smaller than the lateral dimensions of the PDN. This leads to a dense mesh and a computationally intractable problem size. However, the interconnections can be divided into segments which can be considered to support a quasi transverse electromagnetic (TEM) mode. These segments can be analyzed as multi-conductor transmission lines (MTL). In this thesis, an electrostatic 2D solver is used to obtain the multi-conductor per unit length inductance and capacitance matrices, that characterize the interconnects.

### 3. Integration of the PDN and SDN responses to obtain the system response

One of the solution techniques for the simulation of multi-conductor transmission structures is the theory of modal decomposition, to be described in Section 1.7. Modal decomposition enables the decoupling of the multi-conductor transmission line (MTL) equations, such that a system of n-conductors (including the reference conductor) can be represented in terms of a circuit containing n-1 transmission-lines referenced to the system ground, and coupling networks containing controlled sources. This model can be shown to provide an exact solution to the MTL equations. Thus modal decomposition can be used to integrate the responses of the PDN and the SDN, that have been obtained in isolation.

### 1.6 Nodal Admittance Matrices and Shifting of Reference Nodes

The Helmholtz wave equation (7) is the governing equation for power/ground plane problems. The solution of this equation using finite methods leads to system of equations that can be expressed in terms of an equivalent circuit containing only passive elements and independent current sources. These equations hence are expressions of Kirchoff's current law (KCL).

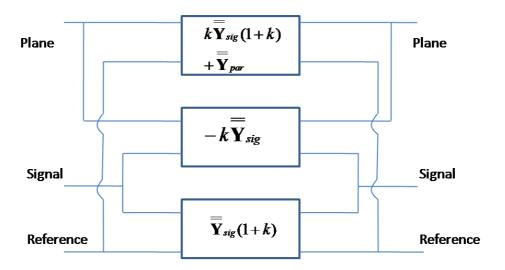

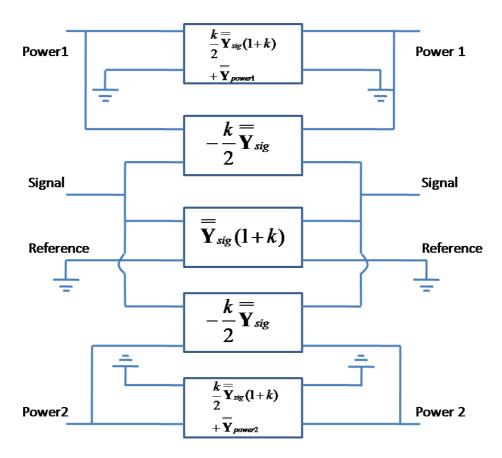

Thus, the theory of indefinite admittance matrices can be applied to the solution of power/ground problems. Although the application of finite methods such as finite differences to (7) directly provides the admittance matrix for a simple two-layer problem, an understanding of the properties of admittance matrices is required to extend the method to multi-layer geometries, as well as for addition of components to the PDN. These components include decoupling capacitors, transmission lines referenced to power planes, as well as circuit models to capture second order effects, such as fringing fields.