# ADVANCES IN ELECTRONIC PACKAGING TECHNOLOGIES BY ULTRA-SMALL MICROVIAS, SUPER-FINE INTERCONNECTIONS AND LOW LOSS POLYMER DIELECTRICS

A Thesis

Presented to

The Academic Faculty

by

Venkatesh Sundaram

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Materials Science and Engineering

Georgia Institute of Technology

May 2009

COPYRIGHT 2009 by Venkatesh Sundaram

# ADVANCES IN ELECTRONIC PACKAGING TECHNOLOGIES BY ULTRA-SMALL MICROVIAS, SUPER-FINE INTERCONNECTIONS AND LOW LOSS POLYMER DIELECTRICS

Approved by:

Dr. Rao R. Tummala, Advisor School of Materials Science & Engg. *Georgia Institute of Technology*

Dr. C. P. Wong School of Materials Science & Engg. *Georgia Institute of Technology*

Dr. Ashok Saxena School of Materials Science & Engg. *Georgia Institute of Technology*  Dr. Madhavan Swaminathan School of Electrical & Computer Engg. *Georgia Institute of Technology*

Dr. Mahadevan K. Iyer Director of Worldwide Packaging *Texas Instruments*

Date Approved: December 9 2008

#### ACKNOWLEDGEMENTS

This thesis research has been a long road and there are many people to whom I owe my gratitude for helping me along the way. I would like to first thank my thesis advisor, Prof. Rao Tummala, who has been a major influence in my professional life, introducing me to packaging technology and teaching me to think at multiple levels to solve complex problems, and also to always look well ahead of the state-of-the-art. I want to thank my committee members, Prof. C. P. Wong, Prof. Ashok Saxena, Prof. Madhavan Swaminathan, and Dr. Mahadevan Iver, for their patience and constant support and encouragement. I would like to extend a special thanks to two research collaborators who played a major role in guiding me with this research work; Dr. George White, who has been a mentor and friend during all these years, and Dr. Fuhan Liu, who has worked with me on all aspects of the substrate technology presented here. The LCP research and electrical characterization work was supported in a significant way by Dr. Sid Dalmia and Dr. Vinu Govind, during their stay at Georgia Tech and at Jacket Micro Devices. Dean Sutter has been a constant source of positive motivation ever since I started working with him at the Packaging Research Center in the late 1990s.

This dissertation research was done as a part-time student while working at the Georgia Tech PRC and I would like to thank my working family over the years for their friendship and support, both administrative staff – Traci Walden, Patricia Allen, Christine Baker, Reed Crouch, Lauren Hall, Carl Rust, Leyla Conrad, Barbara Park, Jennifer Belford, and research staff, Boyd Wiedenman, Dr. Raj, Hunter Chan, Dr. Baik Woo Lee, Dr. Ritwik Chatterjee, Dr. Pradeep Dixit, Nitesh Kumbhat, Dr. Goud, Dr. Lixi Wan, Dr. Ege Engin, Dr. Robin Abothu, Dr. Swapan Bhattacharya, Dr. Lilly Tsai, Dr. Chong

Yoon. Several students at Georgia Tech helped me with improving the quality of the research, including Prof. Tummala's current and former students – Ankur Agarwal, Dev Balaraman, Shubhra Bansal, Nitesh Kumbhat, Piyush Gupta, Ganesh Krishnan, Nithya Sankaran among others, undergraduate research assistants and visiting interns from TU Dresden, and Prof. Swaminathan's Epsilon group students in the electrical design area. I would like to especially thank Susan Bowman and Prof. Tom Sanders from the School of Materials Science & Engineering for patiently guiding me through the Ph.D. requirements during this long journey.

The support and partnership from my industry collaborators from the US, Europe, Japan and Asia has been instrumental in the successful completion of this thesis and I would like to extend my gratitude especially to from Scott Kennedy, Dirk Baars, John Dobrick , Al Horn (Rogers Corporation) for LCP and RXP4 materials and discussion, Hugh Roberts, Sven Lamprecht, Patrick Brooks (Atotech) for plating and metallization process discussion, Guillermo Borges (Starfire Systems) for SiC composite materials, Karl Dietz, Dave McGregor (DuPont) for lithography discussion, photoresist materials, Voya Markovich, John Lauffer, Frank Egitto, Francesco Marconi (Endicott Interconnect) for laser ablation discussion and support, Dow Chemical (for providing BCB) and all my friends at Jacket Micro Devices.

This thesis would not be a reality without the unconditional support of my wife Aarti over the course of a decade, and my son Aneesh for the joy and motivation to get to the finish line. I would also like to thank my parents without whom I would not be here. I want to thank my brother in Boston and my sisters in India and their families, and my inlaws for their patience.

### **TABLE OF CONTENTS**

|                                                                      | Page |

|----------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                     | iii  |

| LIST OF TABLES                                                       | ix   |

| LIST OF FIGURES                                                      | Х    |

| LIST OF SYMBOLS AND ABBREVIATIONS                                    | XX   |

| SUMMARY                                                              |      |

| <u>CHAPTER</u>                                                       |      |

| 1. Introduction And Objectives                                       | 1    |

| 1.1. Thesis Motivation: Bridge The Widening Interconnect Gap Between | 1    |

| IC and Package Substrate                                             |      |

| 1.2. Research Objectives Driven by Wiring Gap                        | 6    |

| 1.3. Historical Development & Current State of the Art Ultra High    | 7    |

| Density Wiring Substrates                                            |      |

| 1.3.1. Thin Film on Ceramic                                          | 10   |

| 1.3.2. Thin Film on Silicon                                          | 11   |

| 1.3.3. Sequential Build-Up Organic Substrates                        | 14   |

| 1.4. Technical Barriers to Address the Wiring Gap                    | 16   |

| 1.5. Research Outline to Address Barriers and Gaps                   | 17   |

| 2. Low CTE Core Substrates                                           | 21   |

| 2.1. Property Requirements and Selection of Core Substrates          | 21   |

| 2.2. Core Substrate Materials Studied in this Research               | 24   |

|    | 2.3. Results and Discussion - Source of Surface Defects and Roughness In      | 25 |

|----|-------------------------------------------------------------------------------|----|

|    | C-SiC Substrates                                                              |    |

|    | 2.4. Results And Discussion - Surface Planarization For Ultra-Fine Line       | 27 |

|    | Conductors                                                                    |    |

| 3. | Polymer Dielectrics Basics & Advanced Deposition Processes                    | 32 |

|    | 3.1. Historical Trends In Polymer Dielectrics                                 | 32 |

|    | 3.2. Epoxy Dielectric: Chemistry, Processing-Structure-Property Relationship  | 34 |

|    | 3.3. Emerging Needs For Next Generation Of Polymer Dielectrics                | 37 |

|    | 3.4. Low Loss Polymer Dielectrics & Processes Explored In This Research       | 38 |

|    | 3.4.1. Benzocyclobutene (BCB) Dielectric Polymer Microstructure And           | 39 |

|    | Properties                                                                    |    |

|    | 3.4.2. Liquid Crystal Polymer (LCP) Structure And Properties                  | 41 |

|    | 3.4.3. Low Loss Polymer Structure-Property Relationship And Processing        | 43 |

|    | Challenges                                                                    |    |

|    | 3.5. Ultra-Thin Polymer Dielectric Film Deposition Process-Structure-Property | 46 |

|    | Relationship                                                                  |    |

| 4. | Advanced, Ultra-Small Microvia Formation Processes                            | 60 |

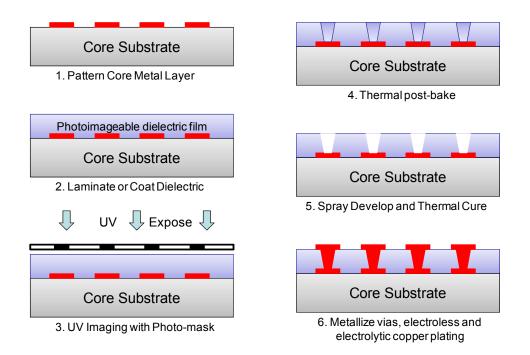

|    | 4.1. Photovia Process To Achieve 25µm Via Diameter In Epoxy Dielectric        | 61 |

|    | 4.2. Excimer And UV Laser Ablation Of Small Microvias – Photo Ablation By     | 68 |

|    | Nanosecond Excimer Laser And Downscaling Of Via Diameter (10-30 $\mu$ m) I    | n  |

|    | Ultra-Thin (10-25µm Thickness) Low Loss Polymer Dielectrics                   |    |

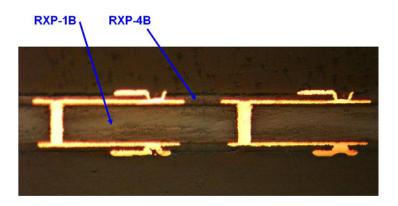

|    | 4.3. Nd-YAG Laser Ablation Of 30-40µm Diameter Microvias In RXP-4             | 73 |

|    | 4.4. Excin | ner Laser Ablation System And Process Fundamentals                | 77  |

|----|------------|-------------------------------------------------------------------|-----|

|    | 4.5. Chem  | istry And Physics Of Polymer Ablation By Nanosecond Pulsed 308nm  | 83  |

|    | Excin      | ner Lasers                                                        |     |

|    | 4.6. Excin | ner Laser Ablation Of 25-50µm Diameter Microvias In LCP           | 85  |

|    | 4.6.1.     | Excimer Laser (308nm) Ablation Of 25µm Thick LCP Film             | 88  |

|    | 4.6.2.     | Discussion Of 25-50µm Microvia Ablation In 25µm Thick LCP Film    | 91  |

|    | 4.6.3.     | Effect Of Via Size And Fluence On Carbon Re-Deposition, Debris    | 95  |

|    |            | Removal And Cone Formation                                        |     |

|    | 4.7. Excin | ner Laser Ablation Of 10-40µm Diameter Microvias In BCB           | 100 |

|    | 4.8. Chapt | er Summary                                                        | 110 |

| 5. | Advanced   | l Conductor Metallization And Plasma Surface Modification         | 111 |

|    | Processes  |                                                                   |     |

|    | 5.1. Major | Challenges For Ultra-Fine Line Conductors                         | 112 |

|    | 5.2. Diele | ctric-Copper Interface Control For Low Conductor Loss In The      | 114 |

|    | Multi      | ple Ghz Frequency Range                                           |     |

|    | 5.2.1.     | Processing Techniques For Polymer Dielectric Surface Treatment    | 116 |

|    | 5.2.2.     | Chemical & RF Plasma Roughening Of Low Loss Polymers              | 121 |

|    | 5.2.3.     | Impact Of Dielectric Surface Roughness On Sub-10µm Copper         | 128 |

|    |            | Lines                                                             |     |

|    | 5.3. Advar | nced Processes For <10µm Lines/Spaces And Extreme-Fine Line       | 130 |

|    | Coppe      | er Conductor Formation Using Low Cost Package Substrate Materials |     |

|    | 5.3.1.     | Ultra-Fine Line Test Vehicle Design And Layout                    | 130 |

|    |            |                                                                   |     |

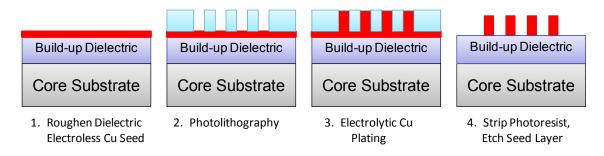

|    | 5.3.3. Semi-Additive Plating (SAP) Process                             | 132 |

|----|------------------------------------------------------------------------|-----|

|    | 5.3.4. Low Stress Electroless Plating                                  | 134 |

|    | 5.3.5. Low Cost And Ultra-Fine Line Photolithography                   | 136 |

|    | 5.3.5.1.UV Lithography Methods                                         | 137 |

|    | 5.3.5.2. Principles For Resolution Of Proximity Photolithography       | 137 |

|    | 5.3.5.3.Experiments On Gap Effect                                      | 138 |

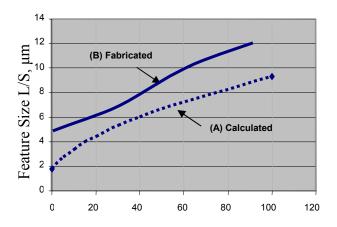

|    | 5.3.5.4.Calculations On Gap Effect                                     | 141 |

|    | 5.3.5.5. Photo Resist And Fine Line Formation Challenges               | 142 |

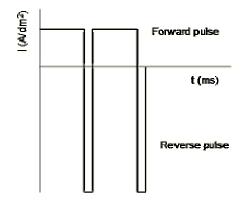

|    | 5.3.5.6.Electrolytic Plating Process And Sub-10µm Line/Space Results   | 143 |

|    | 5.3.5.7. Surface Irregularity Challenges For Sub-10µm Lines And Spaces | 147 |

|    | 5.4. New Sub-10µm Copper Conductor Surface Treatment Process           | 153 |

|    | 5.4.1. Advanced Copper Surface Treatment Process Description           | 153 |

|    | 5.4.2. Copper Adhesion Process Testing Results                         | 157 |

|    | 5.4.3. Advanced Silane Treatment Process For Sub-10µm Lines/Spaces     | 159 |

|    | 5.5. Chapter Summary                                                   | 161 |

| 6. | Next Generation Advanced Organic Substrate Integration Research        | 162 |

| 7. | Summary and Conclusions, Future Work                                   | 168 |

| 8. | Scientific And Technical Contributions                                 | 173 |

| RF | EFERENCES                                                              | 177 |

### LIST OF TABLES

|           |                                                                                | Page |

|-----------|--------------------------------------------------------------------------------|------|

| Table 1.1 | Microprocessor Performance Parameters for 2004 and 2010 from ITRS              | 04   |

|           | Roadmap                                                                        |      |

| Table 1.2 | Comparison of State-of-the-art and Proposed Research Parameters                | 20   |

| Table 2.1 | Comparison of Electrical and Mechanical Properties of SiC Composite            | 25   |

|           | Substrates with Carbon, Alumina and Glass Fiber Reinforcement                  |      |

| Table 3.1 | Molar Polarization Comparison of Various Polymer Functional Groups             | 44   |

| Table 3.2 | Summary of Electrical and Thermo-mechanical Properties of Build-up             | 45   |

|           | Dielectrics                                                                    |      |

| Table 4.1 | Calculated Values of Y Scan Feed Rate (vs) for Various Repetition              | 90   |

|           | Rates (R in Hz) for a Dose (NAbl) of 500 pulses @ 200mJ/cm <sup>2</sup> /pulse |      |

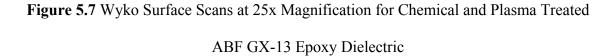

| Table 5.1 | Summary of Wyko Surface Analysis of Chemical and Plasma Treated                | 122  |

|           | ABF GX-13 Epoxy Dielectric (all units in µm)                                   |      |

| Table 5.2 | Fabricated and calculated Lmin/Smin on 8µm thick photo resist in               | 142  |

|           | proximity mode lithography                                                     |      |

| Table 5.3 | Secure <sup>TM</sup> HFz Process                                               | 155  |

| Table 5.4 | AFM Surface Analysis Before and After Copper Surface Treatment                 | 158  |

| Table 5.5 | Line Width and Space Measurements of Untreated and Silane Treated              | 160  |

|           | Copper Fine Lines and Comparison to Bond Film etch based adhesion              |      |

|           | Treatment                                                                      |      |

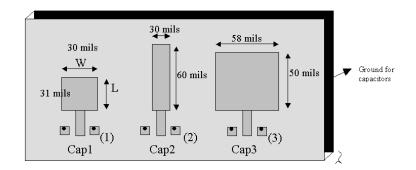

| Table 6.1 | High Frequency Measurement Results for Embedded RF Capacitors in               | 164  |

|           | 50µm thick LCP                                                                 |      |

### LIST OF FIGURES

|            |                                                                      | Page |

|------------|----------------------------------------------------------------------|------|

| Figure 1.1 | Bridging the Widening Interconnect Gap Through Ultra-High Density    | 03   |

|            | Substrate Wiring Research                                            |      |

| Figure 1.2 | Component Integration Trends and Package Substrate Wiring Density    | 08   |

|            | Increase                                                             |      |

| Figure 1.3 | Key Milestones in the Evolution of High Density Substrates           | 09   |

| Figure 1.4 | Dual Level Metal (DLM) Stacked Via Process for Cu-Polyimide on       | 10   |

|            | Ceramic Substrate by IBM                                             |      |

| Figure 1.5 | Cross-section schematic of thin film on silicon (TFOS) substrate     | 12   |

|            | technology by AT&T Bell Labs                                         |      |

| Figure 1.6 | Top View and Cross-Section of Fully Packaged Multi Chip Module       | 12   |

|            | using Cu-Polyimide TFOS Substrate                                    |      |

| Figure 1.7 | GE Chips-First HDI Substrate Technology with Cu-polyimide thin film  | 13   |

|            | multilayer wiring                                                    |      |

| Figure 1.8 | Thick and Thin Film Organic Substrate Microvia Technologies          | 15   |

|            | Worldwide                                                            |      |

| Figure 1.9 | Eight Major Research Elements in the Proposed SOP Substrate Research | n 18 |

| Figure 2.1 | Correlation of Substrate Warpage and Via-Pad Misalignment            | 22   |

| Figure 2.2 | Thermo-mechanical Modeling of Substrate Warpage Based on Modulus     | 23   |

|            | & Thin Film Build-up Process                                         |      |

| Figure 2.3 | Thermo-mechanical Properties of Core Substrates Explored in this     | 24   |

|            | Research                                                             |      |

| Figure 2.4 | Fabrication Process for Carbon Fiber Reinforced SiC Composite        | 26   |

Substrate

| Figure 2.5  | Schematic of the surface roughness. Typically, pores of three size         | 27 |

|-------------|----------------------------------------------------------------------------|----|

|             | ranges can be seen (around 3-5 microns, 5-15 microns and 20-60 microns)    | )  |

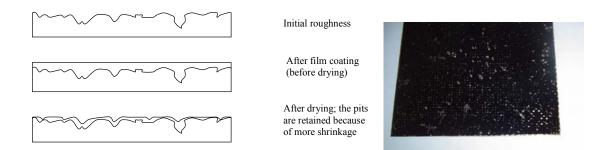

| Figure 2.6  | Effect of liquid coating process on the planarization of the C-SiC         | 28 |

|             | substrate (left) and photograph of coated and cured substrate showing      |    |

|             | surface defects (right)                                                    |    |

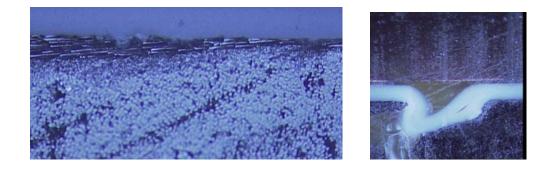

| Figure 2.7  | Tenting of poyimide film over large pits on the surface of C-SiC substrate | 29 |

| Figure 2.8  | (a) Complete flow and fill planarization of Carbon fiber bundles on the    | 30 |

|             | surface of C-SiC substrates by Speedboard lamination                       |    |

|             | (b) Incomplete planarization of large pits due to insufficient resin       | 30 |

| Figure 2.9  | Profiles of C-SiC Substrate "Before" and "After" Planarization             | 31 |

| Figure 2.10 | Cross-section of C-SiC Substrate Planarized with Speedboard C prepreg      | 31 |

| Figure 3.1  | Historical evolution of dielectric materials                               | 33 |

| Figure 3.2  | Structure of the Main Constituents of Epoxy Resins, (a) Bisphenol A,       | 34 |

|             | (b) Epichlorhydrin, and (c) Bromine functional side groups                 |    |

| Figure 3.3  | Chemical Reaction in Polymerization of Epoxy Dielectric                    | 34 |

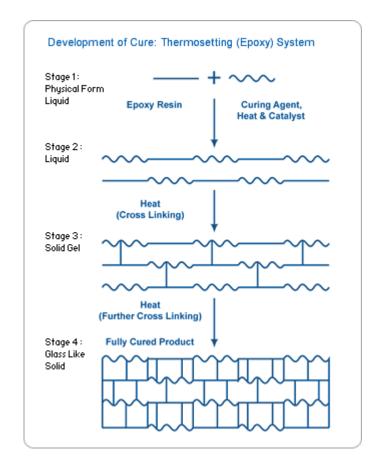

| Figure 3.4  | Various Stages in the Cross-linking & Curing of Epoxy Dielectrics          | 35 |

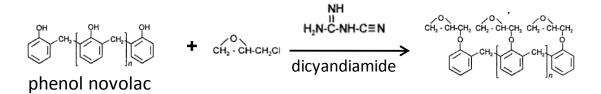

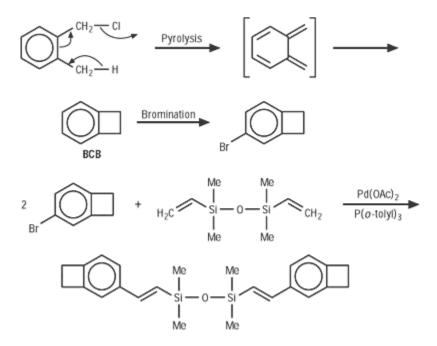

| Figure 3.5  | Process for the Synthesis of BCB                                           | 40 |

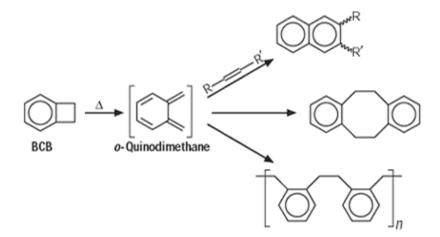

| Figure 3.6  | Diels-Alder Reaction for Polymerization and Curing of BCB                  | 41 |

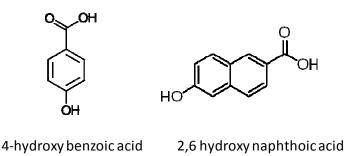

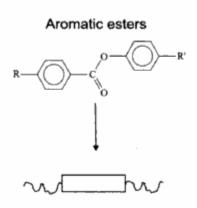

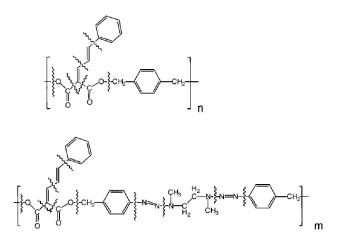

| Figure 3.7  | Structure of Monomers used for the Synthesis of VectraTM LCP               | 42 |

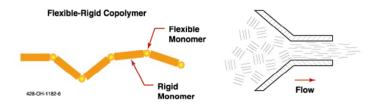

| Figure 3.8  | Structure of Aromatic Ester typical of Liquid Crystal Polymers             | 43 |

| Figure 3.9  | Dielectric Deposition Challenge for the Current Research Compared          | 47 |

|             | to State-of-the-Art                                                        |    |

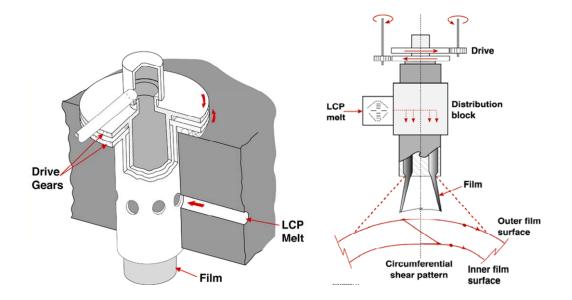

| Figure 3.10 | Conventional Melt Flow Extrusion Process for LCP results in Electrical     | 47 |

|             |                                                                            |    |

and Mechanical Property Anisotropy

| Figure 3.11 | Counter-Rotating Die Concept for Producing LCP Dielectric Films with  | 48 |

|-------------|-----------------------------------------------------------------------|----|

|             | Biaxial In-Plane Property Isotropy                                    |    |

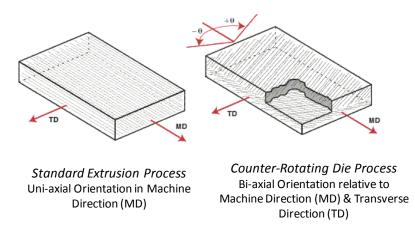

| Figure 3.12 | Uniaxial and Biaxial Orientation of LCP Films                         | 49 |

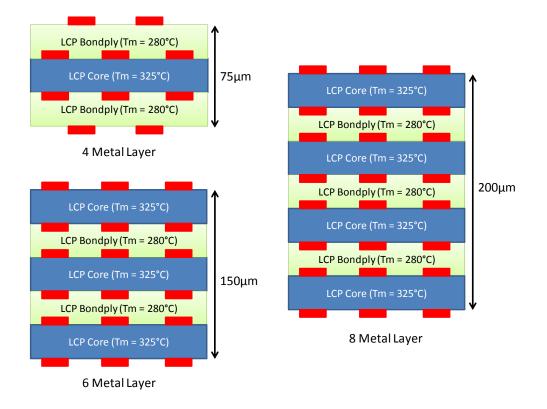

| Figure 3.13 | Four, Six and Eight Metal Layer Thin All-LCP Substrate Cross-section  | 50 |

|             | Schematic                                                             |    |

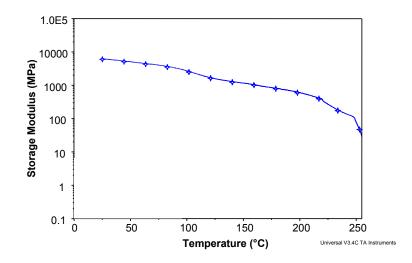

| Figure 3.14 | Drop in Modulus of LCP with Temperature as measured by DMA            | 51 |

|             | analysis                                                              |    |

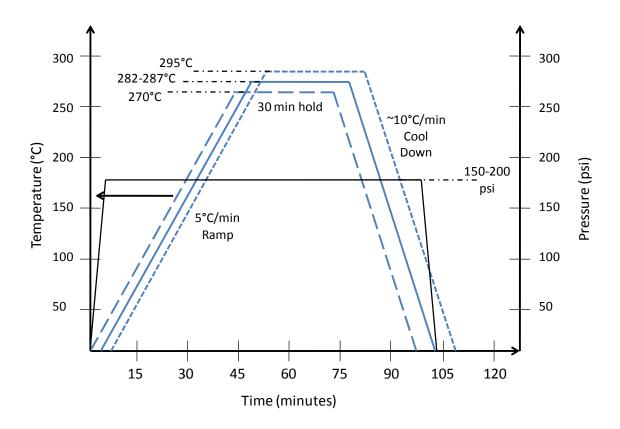

| Figure 3.15 | Lamination profiles optimized for multilayer LCP substrate shown in   | 52 |

|             | Figure 3.14                                                           |    |

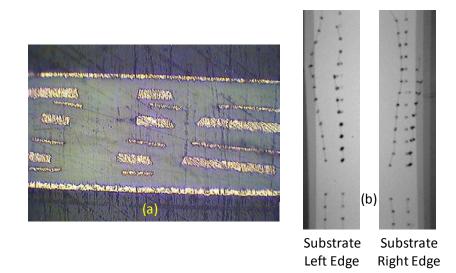

| Figure 3.16 | Distortion in Metal Traces during LCP Lamination at Temperature Much  | 53 |

|             | Above the Melting Point (280°C) as seen in (a) Microsection, and      |    |

|             | (b) X-Ray imaging                                                     |    |

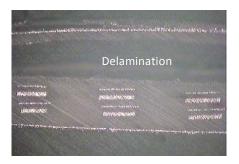

| Figure 3.17 | Delamination due to Insufficient Melting and Bonding of LCP at 260-   | 54 |

|             | 270°C                                                                 |    |

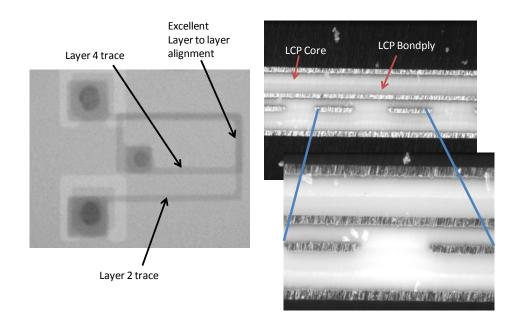

| Figure 3.18 | Results from Optimized Lamination of LCP Core and LCP Bondply         | 54 |

|             | showing excellent layer to layer alignment, no distortion and good    |    |

|             | bonding as seen in X-ray image (left) and microsections (right)       |    |

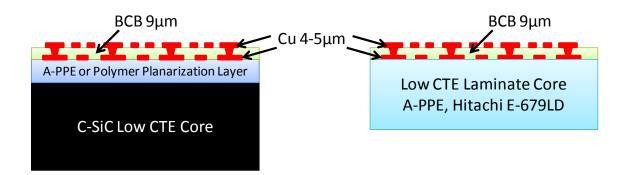

| Figure 3.19 | Target Structure for BCB deposition on C-SiC (left) and low CTE       | 56 |

|             | laminate (right) core substrates                                      |    |

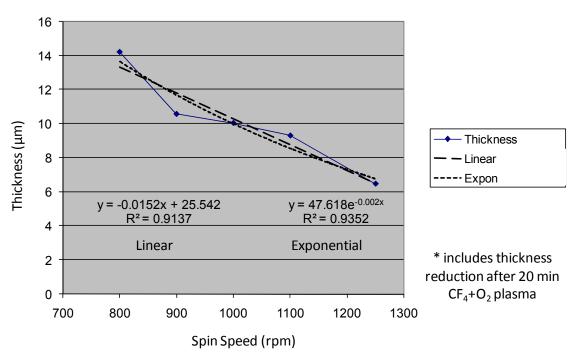

| Figure 3.20 | BCB Film Thickness after Curing and Plasma Surface Treatment plotted  | 57 |

|             | against Spin Speed                                                    |    |

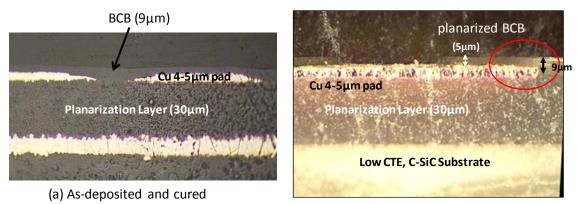

| Figure 3.21 | Planarization of BCB Thin Film after (a) spin coating and curing, and | 58 |

|             | (b) using an intermediate planarization step before curing            |    |

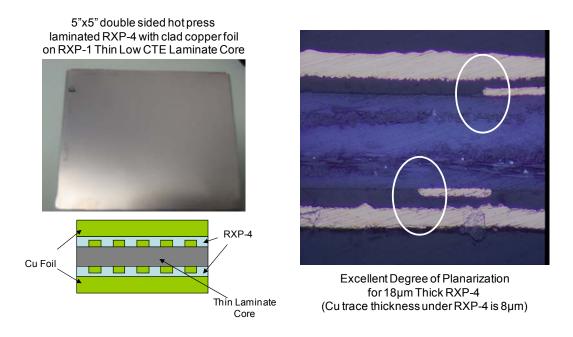

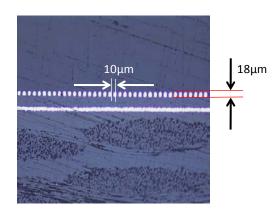

| Figure 3.22 | Lamination Schematic for Thin Low Loss RXP-4 Thermoset Dielectric     | 59 |

|             | Film (left bottom) and excellent planarity achieved after optimized   |    |

xii

lamination of 18um thick RXP-4 dielectric (right)

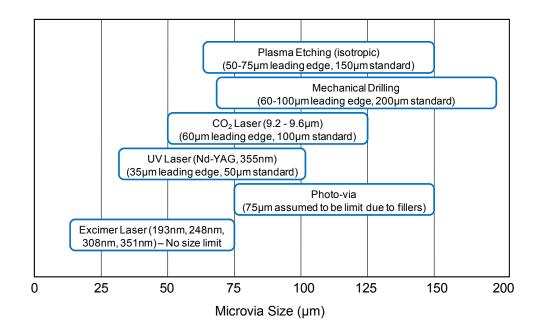

| Figure 4.1  | Microvia Fabrication Technologies for Package Substrates                    | 60 |

|-------------|-----------------------------------------------------------------------------|----|

| Figure 4.2  | Process Sequence for Photo-Via Fabrication                                  | 62 |

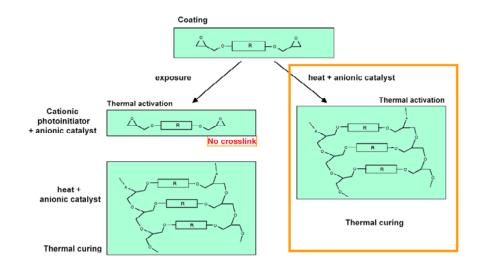

| Figure 4.3  | Fundamental Polymer Reactions during Photo-Epoxy Via Processing             | 63 |

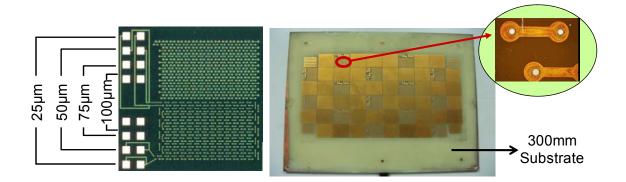

| Figure 4.4  | Microvia Daisy Chain Test Structures (Left), and Fabricated Substrate       | 65 |

|             | with Photo Microvias (Right)                                                |    |

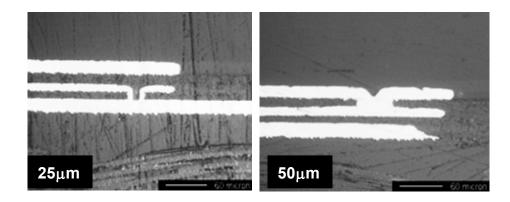

| Figure 4.5  | Micro-sections of $25\mu m$ and $50\mu m$ Diameter Microvias in Photo-Epoxy | 66 |

|             | that Survived after 2000 Thermal Shock Cycles                               |    |

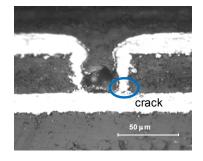

| Figure 4.6  | Micro-section of 50µm Diameter Microvia in Photo-Epoxy that Failed          | 67 |

|             | during Thermal Shock Testing                                                |    |

| Figure 4.7  | Photograph of Nd-YAG laser during ablation                                  | 68 |

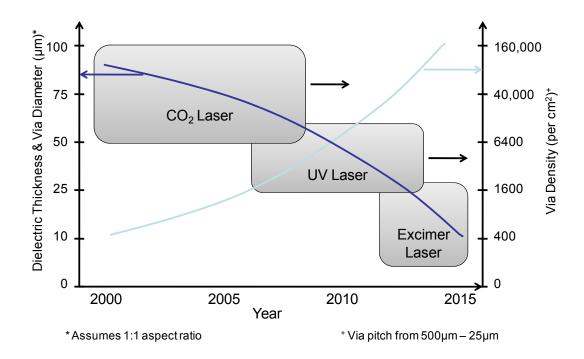

| Figure 4.8  | Trends in Down Scaling of Microvias and Three Major Laser                   | 70 |

|             | Technologies                                                                |    |

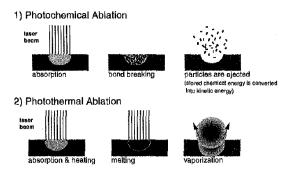

| Figure 4.9  | Mechanism of Ablation                                                       | 71 |

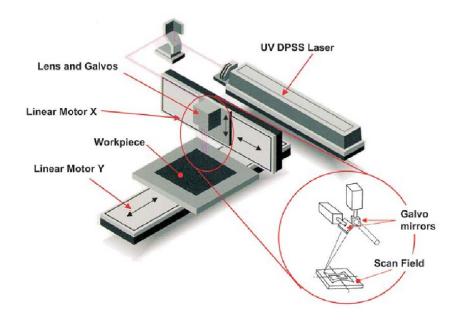

| Figure 4.10 | Typical Configuration of a Nd-YAG UV Laser for Point to Point Ablation      | 73 |

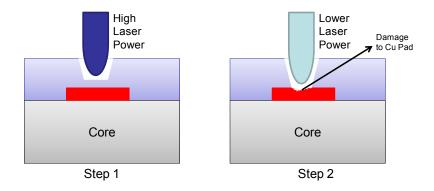

| Figure 4.11 | Two Step UV Laser Ablation Process to Improve Throughput for                | 74 |

|             | Dielectric Ablation and Precise Stopping on Copper Landing Pad              |    |

| Figure 4.12 | Damage to $8\mu m$ thick copper landing pad with 1W power setting for       | 75 |

|             | UV laser ablation of $18\mu m$ thick RXP-4 low loss dielectric ( $10\mu m$  |    |

|             | dielectric via depth)                                                       |    |

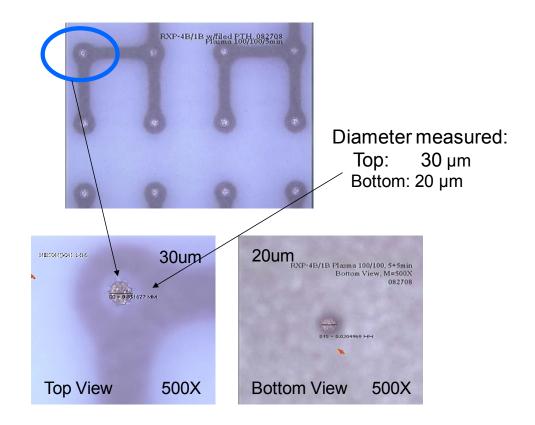

| Figure 4.13 | Optimized $30\mu m$ Top Diameter Microvias in RXP-4 by UV Laser             | 76 |

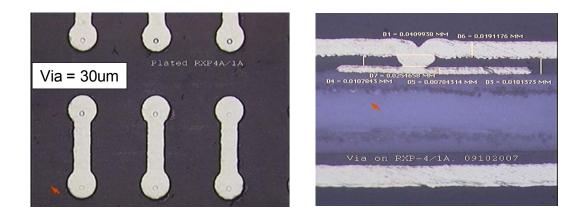

|             | Ablation at low power (<0.5W)                                               |    |

| Figure 4.14 | Top View of a $30\mu m$ Microvias in RXP-4 after Metallization (left) and   | 77 |

|             | Microsection Picture of Plated Microvia with Top Diameter of $40 \mu m$     |    |

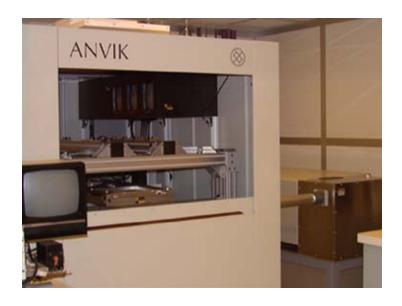

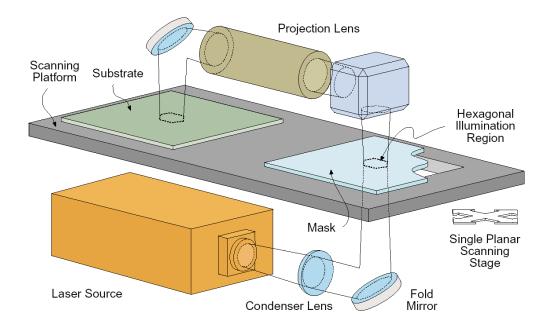

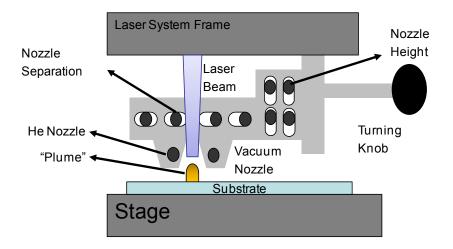

| Figure 4.15 | Scanning projection lithography/ablation system with a 308nm excimer        | 78 |

laser

| Figure 4.16 | Schematic of the various components of the Anvik 2150 SXE Excimer | 80 |

|-------------|-------------------------------------------------------------------|----|

|             | Laser Lithography/Ablation System at Georgia Tech PRC             |    |

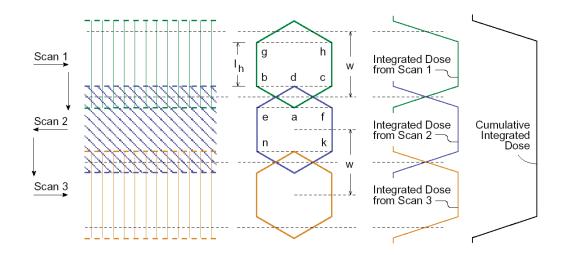

- Figure 4.17 Illustration of the seamless scanning technique used in the Anvik 2150 82 SXE Excimer laser system

- Figure 4.18 Debris Removal System (DRS) using He & Vac to Remove Ablation 83 Debris

- Figure 4.19 Potential Bond Breaking Sites for Typical Polymers During 308nm Laser 84 "Photo-chemical" Ablation

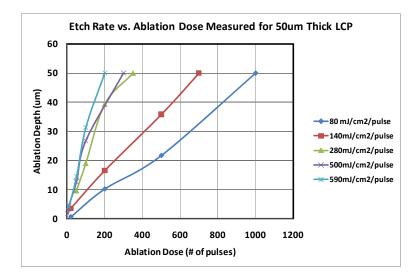

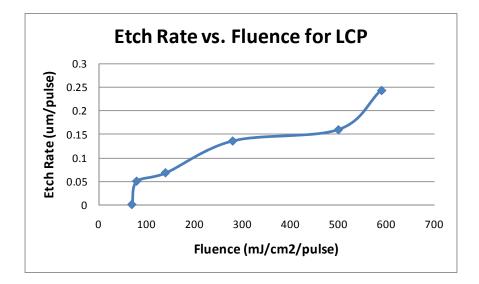

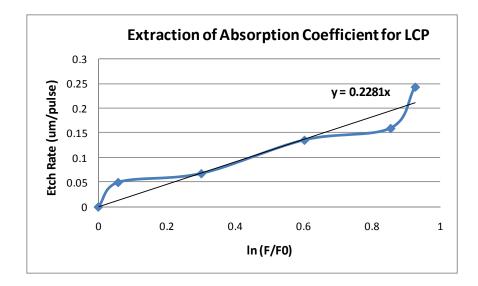

- Figure 4.20 Ablation Depth vs. Dose for Various Fluences for LCP 85

- Figure 4.21 Etch Rate vs. Fluence for LCP (threshold around 70 mJ/cm<sup>2</sup>) 86

- Figure 4.22 Extraction of Linear Absorption Coefficient from Etch Rates for LCP 87

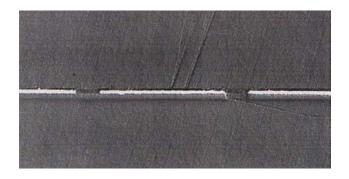

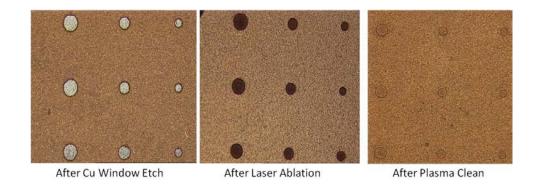

- Figure 4.23 Copper Window Etched in Foil on LCP (left) and Via after Ablation 89 through 62.5µm diameter copper window (right) in 25µm LCP film

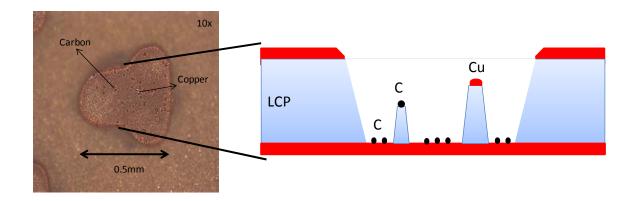

- Figure 4.24 Top View of Ablated Feature (left) and Cross-section Schematic 91 Illustrating Stalagmitic Cone Structures on the Floor of the Via Due to C and Cu Re-deposition

- Figure 4.25 View of the etched copper window at the Cu-LCP interface92Figure 4.26 Top View of the Ablated Alignment Feature after Smoothing of the93

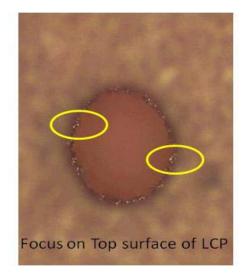

- Figure 4.26 Top View of the Ablated Alignment Feature after Smoothing of the Copper Windows, Carbon re-deposition and cone formation can still be observed

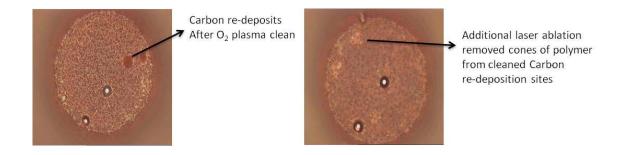

- Figure 4.27 Carbon re-deposits removed by O<sub>2</sub> plasma clean (left) and after 94 subsequent ablation (right)

- Figure 4.28 Cross-section of "Cone" structure formed during laser ablation after 95 electroless and electrolytic copper plating

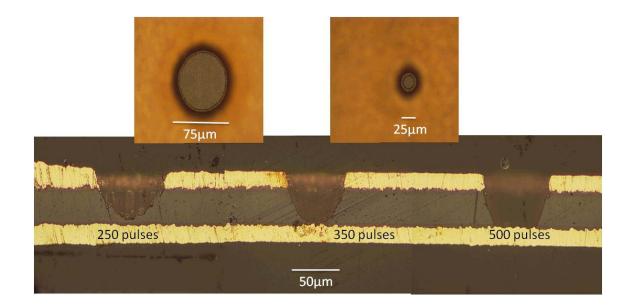

| Figure 4.29 Three Different Via Sizes Ablated at Identical Conditions showing               | 96    |

|---------------------------------------------------------------------------------------------|-------|

| correlation between via size and amount of cones formed                                     |       |

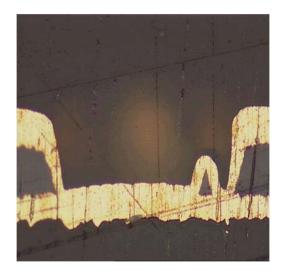

| Figure 4.30 Evolution of Excimer Laser Ablation of LCP; top views after 250 pulse           | s 97  |

| (top), and microsections (bottom)                                                           |       |

| Figure 4.31 Vias of 50, 37.5 and $25\mu m$ diameter after major steps in the via            | 98    |

| formation process                                                                           |       |

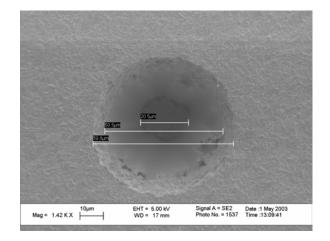

| Figure 4.32 Scanning electron micrograph top view of a $50\mu m$ microvia in LCP            | 99    |

| Figure 4.33 Demonstrated 25µm, 37.5µm, and 50µm Excimer Laser Ablated                       | 100   |

| Microvias after Electroless and Electroplating of LCP                                       |       |

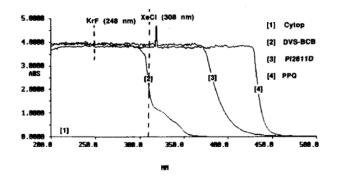

| Figure 4.34 UV-vis absorption spectra for DVS-BCB compared to other common                  | 102   |

| polymers used in microelectronics applications                                              |       |

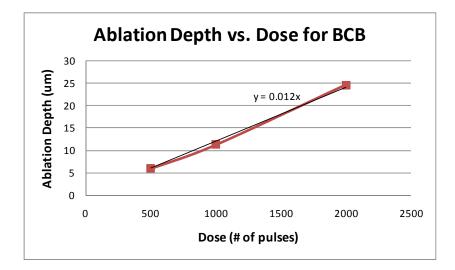

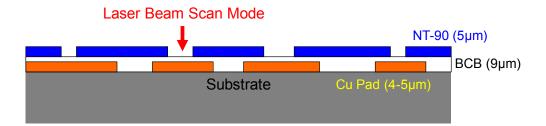

| Figure 4.35 Ablation Depth vs. Dose for BCB (Cyclotene 3022) at 200mJ/cm <sup>2</sup> /puls | e 103 |

| Figure 4.36 Cross-section schematic of new conformal mask method using high                 | 104   |

| resolution photoresist for BCB excimer laser ablation                                       |       |

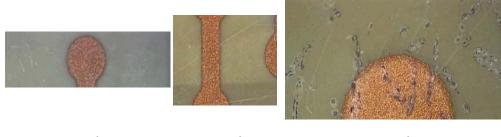

| Figure 4.37 Micrographs of Top Surface of Eagle NT-90 photoresist coated on BCI             | 3 105 |

| (underlying Cu pattens) at various ablation doses at 200mJ/cm <sup>2</sup> /pulse           |       |

| and 200Hz                                                                                   |       |

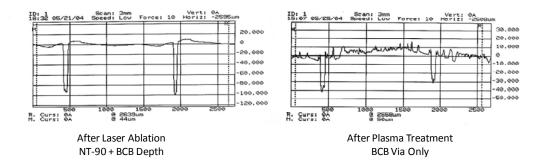

| Figure 4.38 Surface profilometry scans of the NT-90/BCB/Cu structure before and             | 106   |

| after 308nm excimer laser ablation                                                          |       |

| Figure 4.39 Profilometry scans of BCB Microvia after laser ablation (left) and after        | · 107 |

| plasma treatment (right) showing removal of $5\mu m$ NT-90 and                              |       |

| roughening of BCB                                                                           |       |

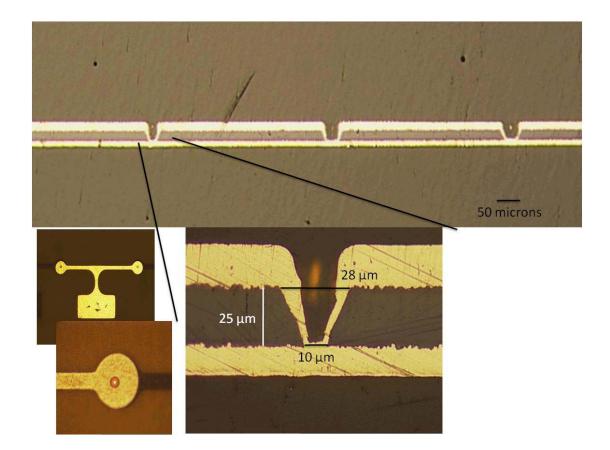

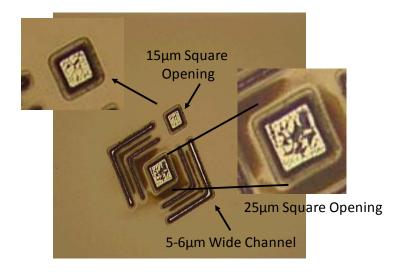

| Figure 4.40 Demonstration of $15-25\mu m$ Vias in BCB by 308nm Excimer Laser                | 108   |

| Ablation. 5-6 $\mu$ m wide ablated channels can also be seen in the picture                 |       |

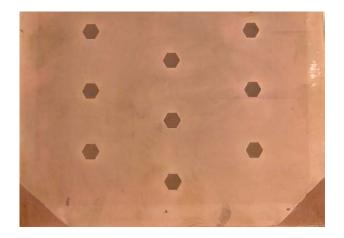

| Figure 4.41 Electroless Cu plated and annealed hexagonal laser ablated areas in BC          | B 109 |

XV

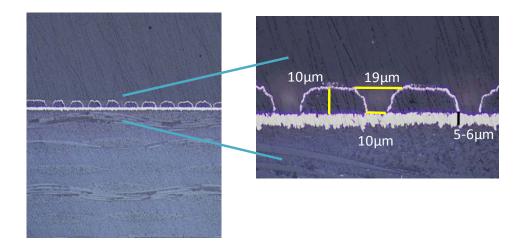

| Figure 4.42 | Microsections of $20\mu m$ Diameter Microvias in BCB after Electroless    | 110 |

|-------------|---------------------------------------------------------------------------|-----|

|             | Cu seed layer deposition                                                  |     |

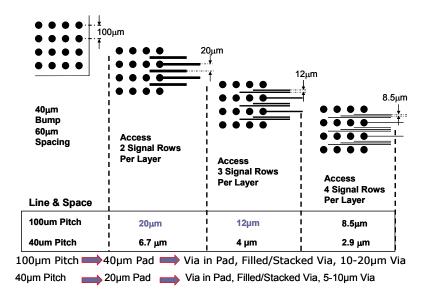

| Figure 5.1  | Wiring Density in terms of Lines/Spaces and Via/Pad Dimensions            | 112 |

|             | Required for 20-100µm pitch area array flip-chip package substrates       |     |

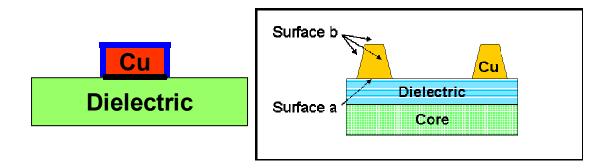

| Figure 5.2  | Illustration of Critical Interfaces for ultra-fine line multilayer copper | 113 |

|             | wiring: Cu-to-polymer (a) and polymer-to-Cu (b)                           |     |

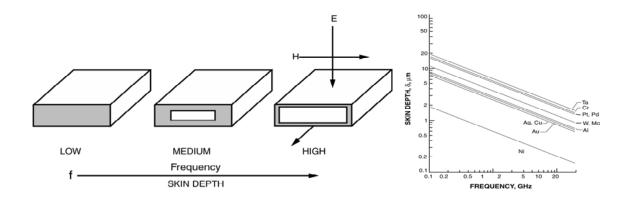

| Figure 5.3  | Skin depth at various frequencies (schematic – left) for common metals    | 115 |

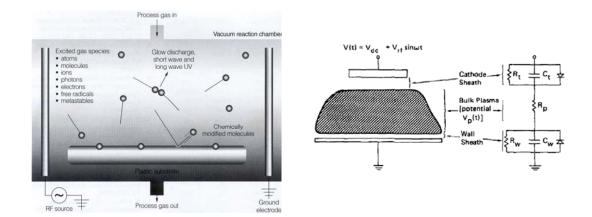

| Figure 5.4  | Plasma Etching System (Plasma Etch BT-1) for 300mm x 300mm                | 117 |

|             | substrates                                                                |     |

| Figure 5.5  | Plasma Etching Fundamentals (left) and Schematic and Equivalent           | 118 |

|             | Circuit for Capacitively Coupled RF Plasma                                |     |

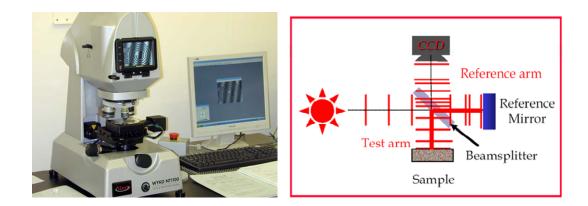

| Figure 5.6  | Wyko NT1100 Optical Interferometer and Operating Principle                | 121 |

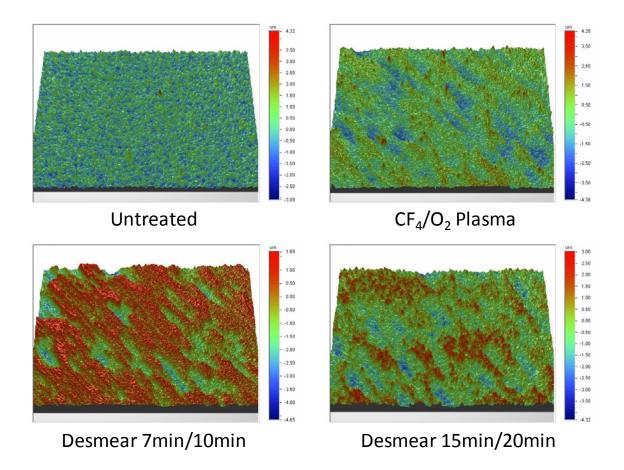

| Figure 5.7  | Wyko Surface Scans at 25x Magnification for Chemical and Plasma           | 123 |

|             | Treated ABF GX-13 Epoxy Dielectric                                        |     |

| Figure 5.8  | Summary of Optical Interferometry Analysis of Surface Roughness for       | 125 |

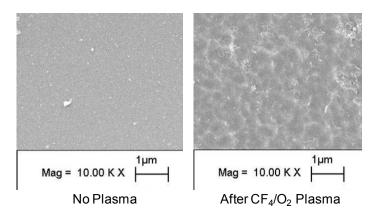

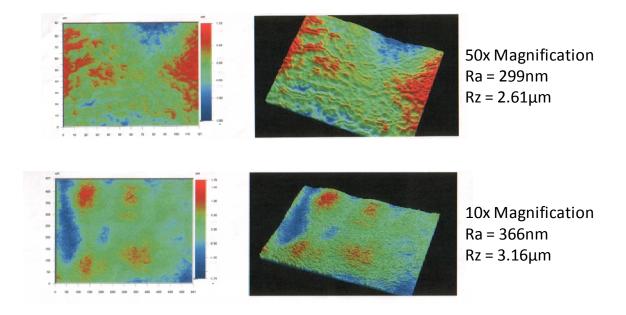

|             | BCB                                                                       |     |

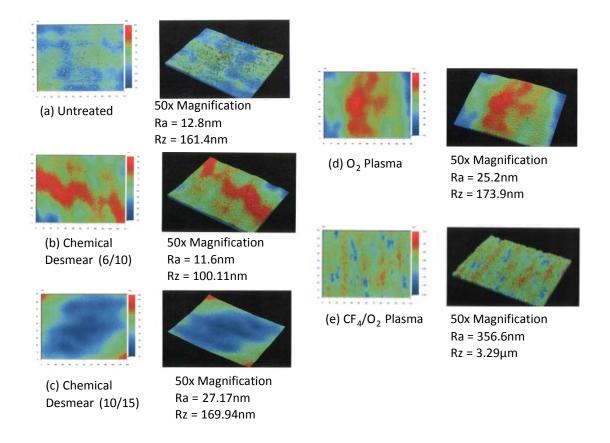

| Figure 5.9  | Surface Profile (Å) of BCB after CF4/O2 Plasma Treatment for 12           | 126 |

|             | minutes                                                                   |     |

| Figure 5.10 | FESEM Images of BCB Surface Before and After CF4/O2 Plasma                | 126 |

| Figure 5.11 | Summary of Optical Interferometry Analysis of Surface Roughness           | 128 |

|             | for LCP                                                                   |     |

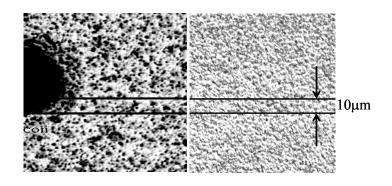

| Figure 5.12 | High Magnification Optical Micrographs of Surface of Build-up             | 129 |

|             | Dielectric after (a) permanganate desmear, and (b) plasma desmear         |     |

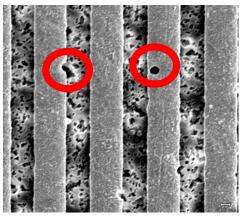

|             | showing overlay of 10µm line                                              |     |

| Figure 5.13 | SEM micrograph of defects in 10µm lines due to deep pits from             | 129 |

chemical desmear

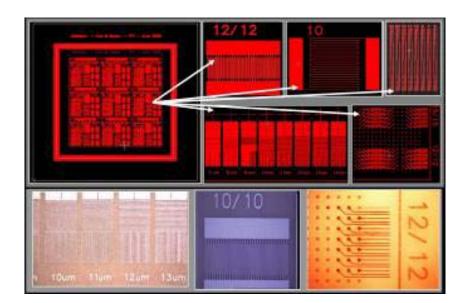

- Figure 5.14 Process test vehicle (TV) as designed (above images), and as fabricated 130 (below) containing various test structures for fine line and space process Development

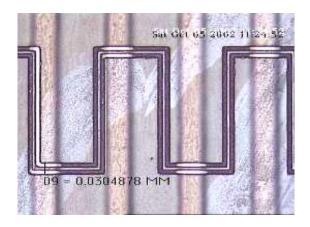

- Figure 5.15 Fine Pitch Traces (20μm Line Width, 20μm Spacing) by Copper 132

Etching (Top view and Micro-section) with Copper Thickness of 12μm (aspect ratio 1.6:1)

- Figure 5.16 Process Flow for Semi-Additive Process (SAP) 132

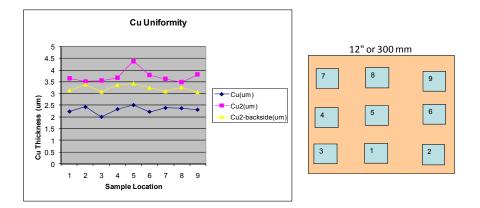

- Figure 5.17 Advanced Electroless Copper Plating System with Pd Activation 135

- Figure 5.18 Electroless Plated Cu Uniformity Measurement by XRF for 1hr 135 (front only) and 2hr plating time (front and back side) of 300mm x 300mm substrate

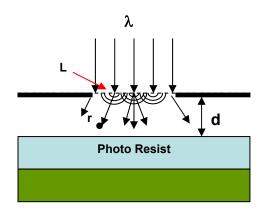

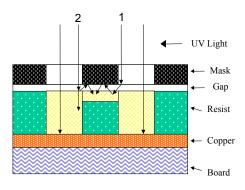

- Figure 5.19 Principle of photolithography with UV light. Light diffraction becomes 138 problematic when transparent area becomes smaller

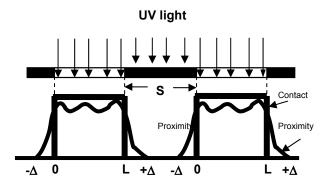

- Figure 5.20 UV Beam Intensity on the surface of photoresist. When  $\Delta$  reaches L/2, 138 the comb structure having equal line and space will not be resolved

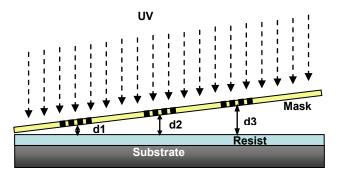

- Figure 5.21 Experimental Setup for UV exposure at different gap distances for 140 studying the gap effect on the resolution of proximity mode photolithography

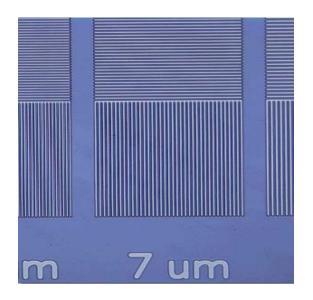

- Figure 5.22 Optical micrograph of test comb structure with equal line width and

space. 7μm line and space resolved on 8μm thick photo resist at a gap

of 30μm by using i-line UV lithography

- Figure 5.23 Calculated (lower) and fabricated minimum (upper) line and space with 142 various gap distances between photo-mask and an 8µm thick photo resist

- Figure 5.24 Feature Width Deviation from Designed Values for Dry Film Photoresist 144

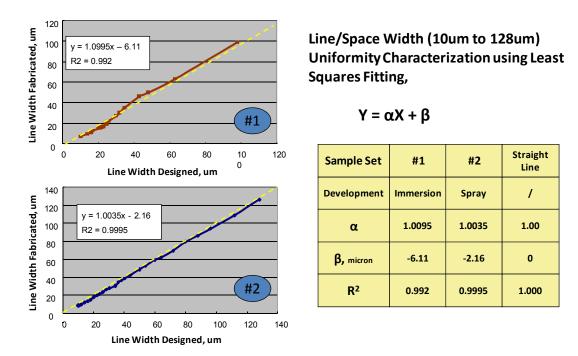

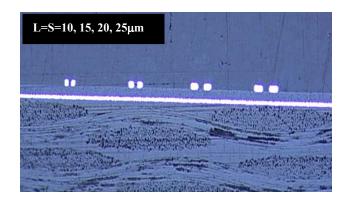

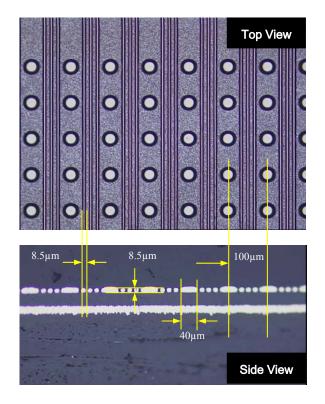

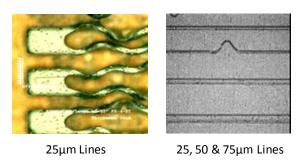

Figure 5.26 Plated copper traces with line widths and space widths of 10/15/20/

25μm on ABF/BT by using dry film photo resist provided by DuPont.

The copper thickness measured is 18μm.

145

- Figure 5.27 Ultra-fine line routing on ABF for 100μm pitch flip chip with 40μm

pads. Line and space shown at 8.6μm for 3 lines/channel routing & Cu

thickness of 8.5μm

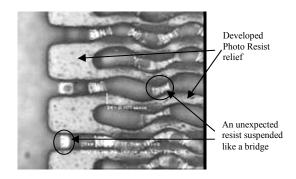

- Figure 5.28 Non-planar surface, due to thick copper trace under the dielectric layer, 149 resulting in photolithography non-uniformity for 10µm lines/spaces in 15µm thick photoresist

- Figure 5.29 "Bridge" effect showing very thin photoresist film remaining in the 150 opening

- Figure 5.30 Explanation for bridge effect in narrow photoresist spaces by UV light 151 scattering between mask and resist under the opaque areas of the mask

- Figure 5.31 (a) & (b) Fine line photoresist lifting caused by insufficient adhesion 151

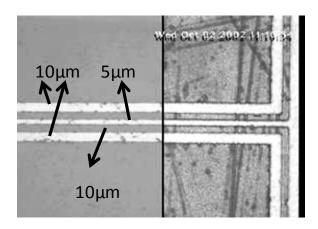

- Figure 5.32 Comparison of glass mask (left) and plated copper (right) for a structure 152 with 5µm and 10µm lines/spaces on a epoxy build-up layer on FR-4

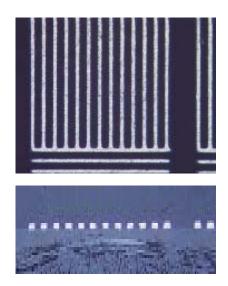

- Figure 5.33 Microsection of high aspect ratio plated copper fine lines with 10μm 152 line/space and 18μm copper thickness

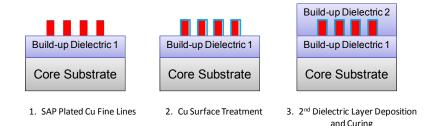

- Figure 5.34 Process Sequence from SAP to Subsequent Build-up Layer Fabrication 153

- Figure 5.35 SEM micrograph of a 12µm wide copper conductor chemically treated 154 with a conventional micro-roughening process for adhesion

- Figure 5.36 12µm conductor before adhesion promotion treatment 157

- Figure 5.37 SEM micrograph of 12µm line after treatment with silane filming 158 process

| Figure 5.38 | SEM micrographs of 5-12µm lines/spaces after Sn-silane treatment              | 160 |

|-------------|-------------------------------------------------------------------------------|-----|

| Figure 5.39 | Conductor cross-section (left) and summary (right) of interface               | 161 |

|             | roughness measured for various materials and processes                        |     |

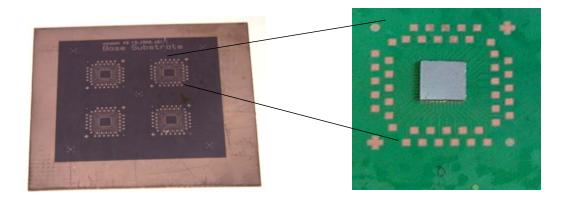

| Figure 6.1  | Two Metal Layer High Density LCP Substrate with Embedded RF                   | 163 |

|             | Passives                                                                      |     |

| Figure 6.2  | Capacitor Structures in Two Metal Layer LCP Substrate with                    | 163 |

|             | Microvias                                                                     |     |

| Figure 6.3  | Low CTE Composite Substrate with Cu-Invar-Cu Core and LCP                     | 165 |

|             | Dielectric (left) and after assembly of $200\mu m$ pitch flip chip IC (right) |     |

| Figure 6.4  | All-LCP Substrate Panel (12"x18") with Six Metal Layer Test                   | 165 |

|             | Structures                                                                    |     |

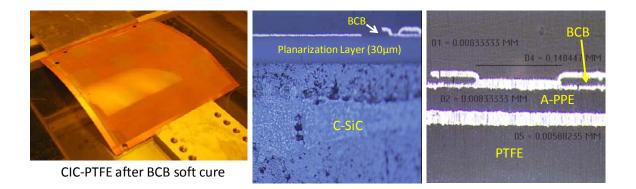

| Figure 6.5  | Top view of BCB coated on CIC-PTFE Core (left), and microsections             | 166 |

|             | of completed BCB build-up substrate on C-SiC (middle) and CIC-PTFE            |     |

|             | (right)                                                                       |     |

| Figure 6.6  | Ultra-Thin Four Metal Layer High Density and Low Loss RXP based               | 167 |

|             |                                                                               |     |

Organic Substrate

### LIST OF SYMBOLS AND ABBREVIATIONS

| SOP        | System on a Package                                 |  |

|------------|-----------------------------------------------------|--|

| SOC        | System on a Chip                                    |  |

| SiP        | System in Package                                   |  |

| SiP        | System in Package                                   |  |

| MCM        | Multi Chip Module                                   |  |

| MEMS       | Micro Electro Mechanical Systems                    |  |

| RF         | Radio Frequency                                     |  |

| MCM        | Multi Chip Module                                   |  |

| CTE or TCE | Coefficient of Thermal Expansion                    |  |

| 3-D        | Three Dimensional Package or Chip Stacking          |  |

| ITRS       | International Technology Roadmap for Semiconductors |  |

| NEMI       | National Electronics Manufacturing Initiative       |  |

| Gbps       | Giga bits per second                                |  |

#### SUMMARY

The fundamental motivation for this dissertation is to address the widening interconnect gap between integrated circuit (IC) demands and package substrates specifically for high frequency digital-RF systems applications. Moore's law for CMOS ICs predicts that transistor density on ICs will double approximately every 18 months. Packaging of ICs at the 32nm and 22nm nodes in the next few years will require 20µm (peripheral) and 80µm (area array) I/O pad pitch on the IC, which must be matched by flip-chip interconnection and substrate wiring pad pitch of the same 20-80µm dimension. System on a Package (SOP) technology pioneered by Georgia Tech PRC enables future "mega-function" electronic and bio-electronic systems through ultra-thin film component integration from the current 50/cm<sup>2</sup> to over 10000/cm<sup>2</sup>. This puts added wiring density and performance demands on the substrate. The other driving force in this thesis research is the increasing adoption of high frequency wireless and wired communication pushing the need for package substrate materials that are stable into multiple GHz frequencies.

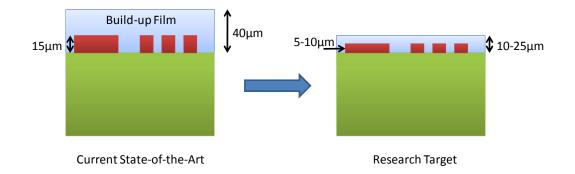

The current state-of-the-art in IC package substrates is at 20 $\mu$ m lines/spaces and 50-60 $\mu$ m microvia diameter using epoxy dielectrics with loss tangent above 0.01. The research targets are to overcome the barriers of current technologies and demonstrate a set of advanced materials and process technologies capable of 5-10 $\mu$ m lines and spaces, and 10-30 $\mu$ m diameter microvias in a multilayer 3-D wiring substrate using 10-25 $\mu$ m thin film dielectrics with loss tangent in the <0.005. The research elements are organized as follows with a clear focus on understanding and characterization of fundamental materials structure-processing-property relationships and interfaces to achieve the next generation targets.

- 1. <u>Low CTE Core Substrate:</u> Advanced low CTE and high modulus core substrates, consisting of composite materials, and processing challenges and solutions.

- 2. Low Loss Dielectrics with 25µm and smaller microvias: Advanced low loss, thin film polymers liquid crystal polymer (LCP) and benzocyclobutene (BCB) and comparison to epoxies, with emphasis on polymer chemistry, effect of chemical processing on microstructure and properties, and exploration and demonstration of advanced processes for planarization, photolithographic via formation, and excimer/UV laser via ablation. Fundamental understanding of the laser-polymer interactions will be used to explain the experimental results from excimer laser photo-chemical ablation processes.

- 4. <u>Sub-10µm Width Cu Conductors:</u> Chemical and plasma surface modification to achieve sub-µm polymer-to-Cu interfaces and correlation of surface characteristics to ultra-fine (<10µm) copper conductor formation processes, photolithography and semi-additive plating process demonstration of sub-10µm lines and spaces. Novel non-etch silane based surface treatment processes for Cu traces to enhance the bond strength of polymer to Cu interfaces.</p>

The dissertation will conclude with research on integration of the various dielectric and conductor processes to demonstrate the 20-80µm pitch wiring in a low-cost, large area substrate platform.

#### **CHAPTER 1**

#### **INTRODUCTION AND OBJECTIVES**

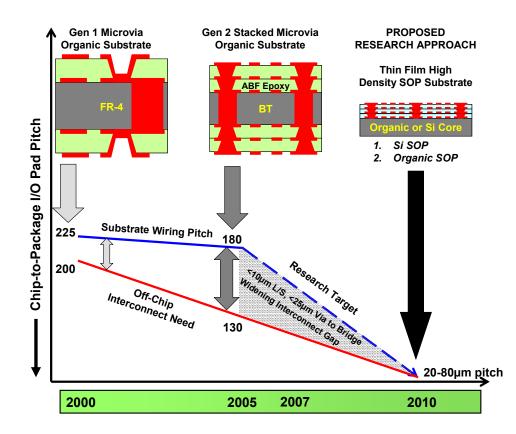

## 1.1 Thesis Motivation: Bridge The Widening Interconnect Gap Between IC And Package Substrate

The fundamental motivation for this dissertation is to address the widening interconnect gap between integrated circuit (IC) demands and package substrate solutions while maintaining high performance. Moore's law for CMOS ICs predicts that transistor density on ICs will double approximately every 18 months. Based on this miniaturization curve, the International Technology Roadmap for Semiconductors (ITRS)<sup>1</sup> predicted the need for interconnecting ICs to systems at an I/O interconnect pitch of 200um in the year 2000 (for 250nm node) and 130um in 2005 (for 130nm node). However, due to limitations in package substrate wiring density, state-of-the-art solutions could only meet 225um I/O pitch flip-chip interconnects in 2000. By 2005, this gap of 25um between IC pad pitch and substrate pad pitch had increased to 50um based on leading edge substrate pad pitch capability of 180um. As shown in Figure 1-1, this IC-to-package interconnect gap is expected to increase further since ICs are following Moore's law and 45nm gate technology will migrate to 32nm and 22nm by 2010. Such transistor nodes will require 20-50 um I/O pad pitch on the IC, which must be matched by flip-chip interconnection and substrate wiring pad pitch of the same 20-50µm dimension. The wiring pitch on the substrate is determined by three important parameters, (i) line width and space, (ii) microvia diameter, and (iii) microvia capture and landing pad diameter. Substrate wiring pitch of 20-50um requires multiple layers of materials and high precision processes for

sub-10um lines/spaces and sub-25um diameter microvias. The National Electronics Manufacturing Initiative (iNEMI) roadmap also defines the need for 4-8 layers of 5-10µm wiring for future system boards<sup>2</sup>. However, current state-of-the-art microvia substrates are at 20um lines/spaces and 60-75um microvias. Higher levels of on-chip integration continue to increase the IC size and large System on Chip (SoC) ICs can be up to 20mm x 20mm with more than 5,000 I/Os at 50µm pitch. This imposes stringent specifications on the flatness of the substrate (5-10µm per inch) for flip chip assembly and reliability. Ultra fine pitch interconnects result in very low stand-off heights between the IC and substrate and poses severe challenges for underfill processing. Current package substrates fabricated using bis-maleamine triazide (BT) laminates with thermal coefficient of expansion (CTE) of 16-18ppm/°C and low modulus (15-20 GPa) need to be replaced by a new generation of low CTE and high modulus core substrates. High stiffness and low CTE lead to improved dimensional stability and less warpage, resulting in tighter layer to layer registration, important for smaller via pad diameters. Low CTE cores are needed for fine pitch flip chip interconnect reliability to reduce the expansion mismatch between IC and substrate. High modulus in the core substrate is especially critical in light of the drive towards thinner core substrates to reduce overall package height for mobile products.

Figure 1.1 Bridging the Widening Interconnect Gap Through Ultra-High Density Substrate Wiring Research

Electrical Drivers for High Density Substrates: As on-chip clock speeds continue to increase, interconnect signal speed between the transistors need to keep up with the switching speed of transistors. On the contrary, it is widely recognized that interconnects have in fact become the bottleneck to semiconductor and system performance rather than the switching speed limitation of transistors. The ITRS roadmap translates IC performance to signal transmission speed required through the package substrate. Signal data rates of 5-10Gbps in the substrate drives the need for dielectric materials with loss tangent ~0.001. Signal delay in global interconnects on ICs will dominate gate delay, and 5-10µm line/space in the substrate provides opportunity to off-load the longest global

wires from IC to substrate. Multi-core processor architectures, driven by the need to reduce power levels, increase the demand for signal I/O density and data bandwidth.

ITRS 2003: 2004 2010 90nm Technology generation 45nm Chip Frequency (local clock) 4GHz 15GHz Number of package pins 500-1,600 780-2,782 2.5Gb/s Chip-Board I/O (narrow) 9.5Gb/s Chip size at production 140mm2 140mm2 Power (cost-performance) 84W 120W Vdd(high) 1.2V 1.0V

Table 1.1 Microprocessor Performance Parameters for 2004 and 2010 from ITRS

Roadmap

Table 1.1 lists some of the attributes of microprocessors in 2004 and 2010 according to the ITRS roadmap. The signal data rate in the package substrate is expected to increase from 1-2 Gbps to about 10 Gbps per channel. At the same time, the voltage level is expected to decrease to 1V. These electrical needs translate to dielectric materials with low dielectric constant (<3.0) for higher signal speed in the substrate, and low loss tangent (<0.001) to minimize signal loss and maintain high signal-to-noise ratio at lower Vdd levels. Current state-of-the-art package substrates cannot match the performance of ICs primarily due to lossy epoxy based dielectrics that have been predominantly used for package substrates. The wiring gap described above must be bridged without any degradation in substrate electrical performance.

Added Wiring Demand from System on a Package (SOP) Technology: The research in this dissertation is a part of System-on-a-Package (SOP)<sup>3</sup> technology that targets full system integration by embedded thin film components in a single multi-function, microminiaturized package or module. In the SOP concept, the "package is the system" and not the bulky board. While systems of the past consisted of bulky boxes housing hundreds of components that perform one task such as computing or communications, the SOP concept consists of system functions to include computing, communication, consumer and other functions — all of these functions in a small system package no greater than the size of a Pentium processor package (35 mm in size). The SOP concept makes this possible by ultra-thin film integration of components in the substrate. A typical SOP package has a size of approximately 35 x 35 mm, with about four ICs for analog, digital and optical functions. Similar to a wafer-to-IC concept, the SOP packages will be fabricated on 600 x 600mm panels using low-cost processes used in high-density organic packages, and then diced — leading to tremendous size and cost reduction, functionality, performance and reliability.

The integration of multiple organic and inorganic materials for multiple functions into a high density substrate forms the core of SOP miniaturization. Embedding thin film passive and active components in the SOP substrate drives additional demand for substrate wiring density and performance as explained below.

- Embedded passive and active components in the substrate that used to compete for real estate on the package surface now compete for space with wiring inside the substrate.

- Interconnection of the embedded passive and active components buried inside the substrate requires additional wiring.

• Embedding and miniaturization of passives and actives brings them in close proximity, sometimes on the same substrate layer, and improved isolation between components by use of ultra-low loss dielectrics.

This research addresses to close the above wiring gap by:

- Low CTE Core Substrate for Minimizing Warpage During High Density Wiring Build-up and Flip Chip Reliability

- Low loss dielectric materials for high speed signal performance

- Thin Dielectric (10-25um thick) materials and microvia processes for 10-20um diameter

- Ultra-fine line and space conductor processes (5-10µm line/space) and multilayer high wiring density structures

As seen in Figure 1.1, these high density multilayer wiring structures can be integrated on dimensionally stable, flat and smooth organic or silicon based SOP substrates.

#### 1.2 Research Objectives Driven By Wiring Gap

The primary objective of this research is to close the wiring gap through innovative new materials, processes and microstructures for ultra-fine line conductors and stacked ultra-small microvia interconnects. The specific objectives include:

- 1. Selection and exploration of new substrate core and dielectric materials consistent with the thermo-mechanical and electrical property requirements.

- 2. Fundamental understanding of materials, processes, interfaces and microstructures for future ultra-high density package substrates.

- Research new low cost processes beyond current state-of-the-art to achieve 5-10μm conductor geometries and 10-20μm microvias.

- Exploration of new process integration methods to demonstrate wiring pitch of 20-80µm in a large area organic substrate platform

The focus of this thesis research is to address each of the technical barriers related to new materials, substrate processes and structures by developing a fundamental understanding of the materials interactions including interface mechanical and chemical bonding, and novel process methods to achieve the target signal data rate and wiring density in the substrate.

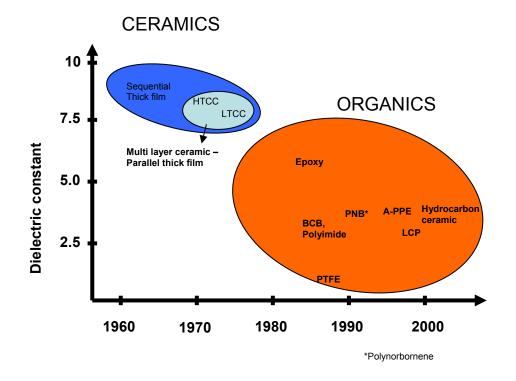

## 1.3 Historical Development & Current State Of The Art Ultra High Density Wiring Substrates

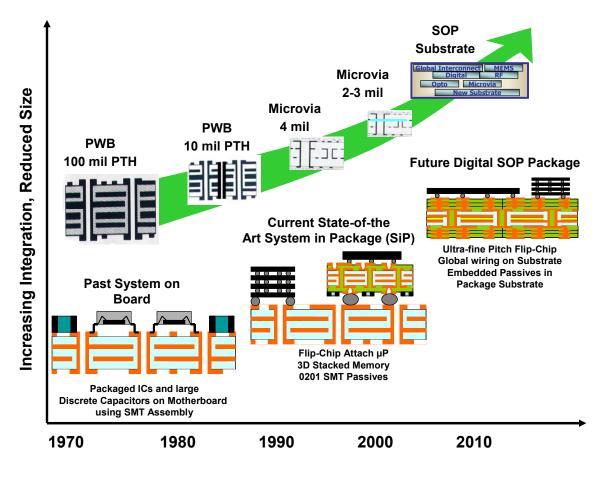

The historical evolution of package substrates, as shown in Figure 1.2, started with big and bulky, low density boards with discrete passive components and packaged ICs in the 1970s and 1980s. The introduction of microvia build-up substrates in the early 1990s led to the concept of high density interposer package substrates to bridge the gap between sub-micron IC interconnects and milli-scale PWB interconnects. System in Package (SiP) technologies developed in the late 1990s further miniaturized IC packages through integration of small discrete passives (0201 and 01005) along with 3D stacked ICs into small form factor package substrates and package on package (POP) stacking. However, to fully leverage the scaling, integration and miniaturization advances of semiconductor technology, significant challenges remain in interconnect and wiring density enhancement and integration of passive and active components at the package substrate level. System-On-Package (SOP) technology pioneered by GT-PRC in the early

1990s aims to achieve miniaturization with ultra-high functional density by concentrating on the package as a whole rather than aim for miniaturization at the IC level alone.

Figure 1.2 Component Integration Trends and Package Substrate Wiring Density Increase

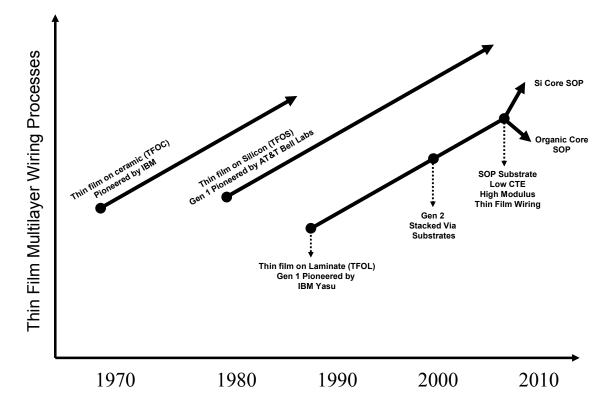

Ultra-thin film wiring technology have been developed around the world on three primary platforms, namely, (i) thin film on ceramic substrates; (ii) sequential build-up organic substrates; and (ii) silicon redistribution and wafer level package processes. This section provides a summary of historical developments and current state-of-the-art technology for ultra-thin film multilayer wiring for SOP substrates. Figure 1.3 illustrates key historical milestones in these three platform technologies.

Figure 1.3 Key Milestones in the Evolution of High Density Substrates

The advent of thin film high density wiring, driven by the wiring demands of multi-chip modules (MCM), started in the 1970s with Cu-polyimide multilayer processing on low temperature co-fired ceramic (LTCC) substrates by IBM (MCM-C)<sup>4</sup>. A similar approach using spin-on polyimide dielectric was developed by Bell Labs on Silicon carrier substrates a few years later (MCM-D)<sup>5</sup>. Both of these substrate technologies were derived from semiconductor processing and utilized high cost processes such as chemical mechanical polishing (CMP) and sputter deposited metal seed layers. In the early 1990s, IBM Yasu in Japan adopted thin film build-up wiring on low cost FR-4 organic substrate cores using low cost epoxy dielectric materials and large area processes like electroless copper plated seed layers and photo-defined microvias (MCM-L). This technology, Surface Laminar Circuitry (SLC)<sup>6</sup> is widely considered as the

pioneering high density build-up organic substrate solution that enabled the widespread use of flip-chip for mainstream IC packaging. In the late 90s and early 2000s, the density of microvia organic substrates was further enhanced by advancements in fine line conductor processes and filled/stacked microvias developed by many groups worldwide.

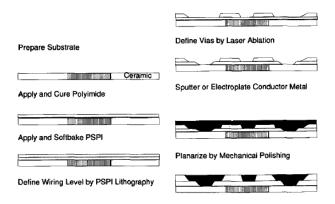

#### 1.3.1 Thin Film on Ceramic (TFOC) Technology

Multilayer thin film wiring using polyimide-Cu was developed extensively by IBM in the 1970s and 80s on a variety of ceramic substrates for use in multi-chip module (MCM) packaging for high performance computing systems. The thin redistribution layers were developed on top of ceramic substrates including alumina, low temperature co-fired alumina (LTCC) and high temperature co-fired glass-ceramic (HTCC) materials in panel sizes from 125mm up to 150mm. Both conformal via and stacked via structures (process flow shown in Figure 1.4) were fabricated using spin-on liquid polyimide dielectric films from 5-12µm thickness per layer.

Figure 1.4 Dual Level Metal (DLM) Stacked Via Process for Cu-Polyimide on Ceramic

Substrate by IBM<sup>4</sup>

One to four metal layers have been demonstrated in high volume production processes with minimum line widths of  $10-25\mu m$  and line pitch of  $>50\mu m$ . Photosensitive polyimide and laser ablation processes were used to define 1:1 aspect ratio vias to interconnect the metal levels. Cr-Cu seed layers were deposited on the cured polyimide using sputter deposition and additive electroplating or subtractive etching was used to pattern the metal circuits.

The primary limitations of thin film on ceramic substrate technology are the expensive processes and small panel sizes used, leading to high cost of the individual packages. For example, only two to four individual packages could be laid out on one ceramic panel of 50mm or 125mm, compared to the SOP targets of hundreds if not thousands of package substrates on one large manufacturing panel of 450mm or 600mm size. Also, the thin metal traces (1-3µm thick) resulted in high conductor loss affecting high frequency performance for longer wires, which had to be routed through low density layers in the co-fired ceramic substrate core. Additional concerns are the high cure temperature of polyimide (350°C) and high diffusion rate of Cu into polyimide requiring barrier metal layers.

#### 1.3.2 Thin Film on Silicon (TFOS) Technology

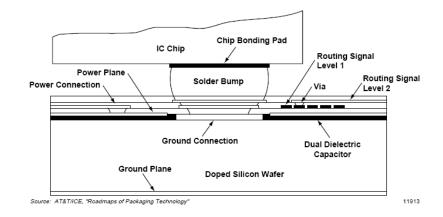

Thin film multilayer wiring on silicon wafers was first developed by AT&T Bell Labs in the 1980s with polyimide dielectric and thin film copper metallization, a process known as Polymer Hybrid Integrated Circuit (PolyHIC)<sup>7</sup>. This process initially used thin copper metallization on triazide polymer dielectrics on alumina substrates, and was later adapted to Cu-polyimide layers on Silicon wafers. Power and ground plane wiring levels

were integrated with higher density signal routing layers and dry etching processes defined the microvia interconnects (Figure 1.5)

Figure 1.5 Cross-section schematic of thin film on silicon (TFOS) substrate technology

#### by AT&T Bell Labs

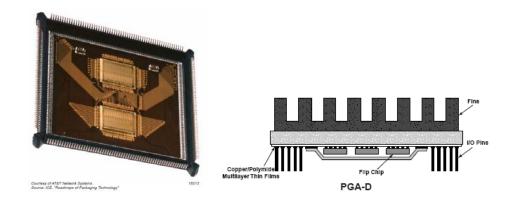

The silicon substrates with thin film wiring was used to attach multiple ICs using eutectic solder bumps and external I/O connections were made using pin grid arrays. Figure 1.6 illustrates the top view and cross-section of the completely packaged MCM-D module with TFOS substrate.

Figure 1.6. Top View and Cross-Section of Fully Packaged Multi Chip Module using Cu-Polyimide TFOS Substrate

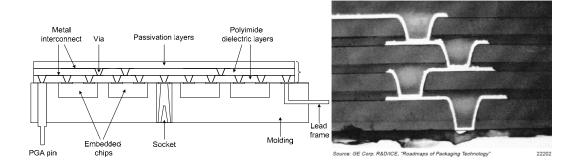

Cu-polyimide thin film wiring was then applied to embedded chip in substrate technology pioneered by GE in the late 1980s and early 1990s as HDI or Chips-First build-up substrates. This concept is shown in Figure 1.7, and since then, several groups around the world have developed high density wiring technology on silicon substrates, by utilizing spin-on thin film polyimide or BCB dielectrics and back end of the line (BEOL) processes commonly used in wafer foundries<sup>8</sup>. Via interconnections were formed by photolithography or reactive ion etching (RIE) processes and sputter deposited metallization schemes were implemented in combination with lift-off processing or chemical mechanical polishing (CMP).

Figure 1.7 GE Chips-First HDI Substrate Technology with Cu-polyimide thin film multilayer wiring

Recent examples of silicon carrier for build-up wiring layers include PASSI technology by Philips/NXP, Redistributed Chip Package (RCP) by Freescale Semiconductor, and bumpless build-up layer (BBUL) by Intel. Similar high density package wiring have also been implemented on glass substrates, so called thin film on glass (TFOG), by ST Microelectronics. BCB-Cu multilayer wiring has also been fabricated on GaAs semiconductor wafers for high performance routing and embedded passives. The common elements to the above silicon/glass based substrates are semiconductor-like processes such as Deep Reactive Ion Etching (DRIE) for dielectric patterning, chemical mechanical polishing (CMP) for planarization and vacuum metallization for conductors. These substrate techniques are limited by their high cost process methods, thin metallization layers (1-3µm) affecting signal loss and lossy substrates in case of Si and other semiconducting materials that contribute to further signal degradation, especially when through vias in the core substrate are needed.

#### 1.3.3 Sequential Build-up (SBU) Organic Substrates

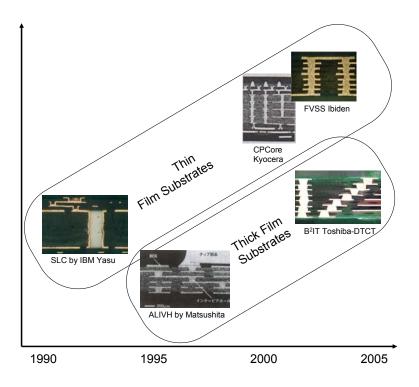

The historical evolution of microvia technology on organic substrates is shown in Figure 1.8<sup>9</sup>. Microvia technologies, also called build-up substrates or boards were pioneered at IBM Japan in 1987 to replace ceramic substrates for area array flip-chip assembly of ICs. There are two main classes of organic microvia technologies, thin film and thick film. The first group is based on thin film technology combined with conventional PWB–cores with through hole plating such as SLC by Japan IBM<sup>6</sup>, IBSS/AAP10 by Ibiden<sup>10</sup>, DYCOstrate by Dyconex<sup>11</sup>, VIL by Japan Victor<sup>12</sup>, CLLAVIS by CMK<sup>13</sup> and others. These technologies are further classified by microvia formation processes as follows. SLC and IBSS/AAP10 are photo-via processes. DYCOstrate is by plasma via process and VIL and CLLAVIS are laser via processes. The second group is based on thick film technology combined with conventional through hole plating. These are ALIVH by Matsushita<sup>14</sup> and B<sup>2</sup>IT<sup>TM</sup> by Toshiba/DTCT/DNP<sup>15</sup>. The ALIVH microvias are formed by laser drilling and subsequent filling with Cu thick film paste and the B<sup>2</sup>IT<sup>TM</sup> is formed by piercing prepreg by Ag filled thick film paste.

Figure 1.8 Thick and Thin Film Organic Substrate Microvia Technologies Worldwide

In order to meet lower cost and shorter-turn around time requirements, colamination technologies such as SSP-Multi and Full Via Stacked Structure (FVSS) by Ibiden<sup>16</sup>, Parallel Lay-up (PALAP) by Denso<sup>17</sup>, CPCore by Kyocera<sup>18</sup> and Core Printing Method of B<sup>2</sup>IT<sup>TM</sup> by DTCT<sup>15</sup> have been developed since 1999. These technologies are called parallel build-up technologies because each layer is separately built and then laminated in one vacuum co-lamination press process using advanced manufacturing processes. To further extend the wiring density of these parallel build-up substrates, ultra high density multi-layer wiring using ultra small microvias has been developed using thin film technologies. Therefore, second generation build-up substrates are based on a combination of thin and thick film technologies, and are being developed by DNP/DTCT, Shinko and Kyocera in Japan and AMITEC<sup>19</sup> in Israel. The progress in wiring density enhancement in organic substrates has not kept pace with the wiring demand of ICs driven by Moore's law. The state of the art organic substrates have 20-30µm lines/spaces and 50-75µm microvia diameters. Additionally, the high expansion coefficient and low stiffness of BT and FR-4 laminates limits the size reduction of microvia pads due to poor layer to layer registration, and fine pitch flip-chip reliability concerns persist. Leading edge epoxy build-up dielectrics with film thickness of 35-40µm and high moisture absorption are not conducive for high wiring density and high electrical performance. The latest organic substrates have wiring pitch of 150-180µm compared to the IC pad pitch of 80-100µm today reducing to 20-50µm in the next five years.

#### 1.4 Technical Barriers To Address The Wiring Gap

The objectives listed above and state-of-the-art review bring about a set of unique technical barriers and gaps in technology that must be overcome to meet the needs for SOP packages in the next 3-10 years. From a materials and process perspective, the critical barriers and technology gaps based on current state-of-the-art are as follows:

- FR-4, BT and other laminate core substrates used in current package substrates limit flip chip interconnect down scaling due to their high CTE mismatch with silicon (18ppm/°C vs. 3ppm/°C) and low elastic modulus (15-20GPa) resulting in excess warpage.

- Current lossy (0.01-0.03) epoxies are limited in performance to 1-3 GHz and high cost thin film processes are a major barrier for available ultra-low loss (0.001) dielectrics.

- Current dry film dielectrics limited to 30-50µm thickness and a new set of dielectric materials and process integration is needed to achieve 10-25µm thickness target.

- Semi-additive and subtractive etch processes used today are limited to 20-50μm lines/spaces. New processes for 5-10μm lines and spaces are in all major roadmaps but no solutions exist or have been identified.

- Current CO<sub>2</sub> and UV laser processes are limited to 25-100µm via diameters and these "sequential" drilling processes not suited for very high via density (>10000 / cm<sup>2</sup>) and 10-20µm microvia diameters.

- Chemical surface treatment processes used for today's epoxy dielectrics depend on mechanical locking and surface roughness of 1-3μm for metal-polymer adhesion. Rough interfaces lead to high signal loss.

- 7. Chemical etching processes used for bond enhancement of copper conductors are not compatible with sub-10µm lines due to excess copper etching resulting in damage to fine lines. A new set of non-etch processes are needed to treat ultrafine copper conductors for multilayer adhesion and reliability.

### **1.5 Research Outline To Address Barriers**

This research focuses on the fundamental microstructures and properties, novel process innovations and mutilayer substrate integration necessary to address the barriers detailed above for three major materials — (i) low CTE and high modulus core substrate, (ii) ultra-low loss and low-stress thin film dielectrics, and (iii) ultra-fine line conductors; both for high speed, high density and high reliability wiring. These innovations are also

integrated into multilayer thin film build-up wiring with minimum via capture pads, on top of core substrates with ultra-high modulus and close to silicon CTE for improved solder joint reliability.

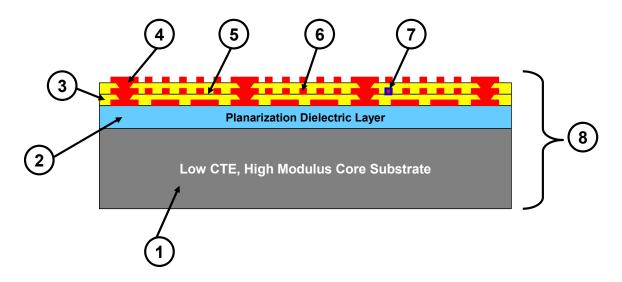

The key elements of the research are illustrated in Figure 1.9 in a cross-section schematic of the proposed ultra high density SOP substrate.

Figure 1.9 Eight Major Research Elements in the Proposed SOP Substrate

## Research

Referring to Figure 1.9, the research elements are organized in the following chapters as follows. Chapter 2 presents materials, microstructure, processing and properties of core substrate. Low CTE and high modulus core substrates to replace FR-4 and BT. Metal (Cu-Invar-Cu), composite (SiC matrix) and new laminate (aramid reinforced) core materials and their processing are described.

Chapter 3 presents a background on current lossy and new low loss polymer dielectrics, including low loss and thin film polymer dielectric chemistry, and the effect

of chemical processing on microstructure and properties of epoxy, liquid crystal polymer (LCP) and benzocyclobutene (BCB) including thin film planarization processes.

Chapter 4 focuses on photovia, UV and excimer laser via ablation processes in BCB and LCP dielectrics for 10-30µm diameter vias and fundamental analysis to overcome ablation process challenges. Via metallization results are also presented and discussed.

Chapter 5 presents the research addressing sub-10 $\mu$ m conductor lines. It begins with surface treatment of dielectrics through plasma and chemical treatment processes to achieve sub- $\mu$ m roughness including effect of polymer chemistry and surface analysis results. Following this are results and discussion of photolithography and semi-additive plating processes including effect of dielectric surface microstructures for copper conductor fine lines. The chapter ends with novel non-etch surface treatment processes for Cu traces to enhance the bond strength of polymer – to – Cu interfaces.

Chapter 6 presents the research into integration of the various dielectric and conductor processes to demonstrate high density SOP substrates to bridge the wiring gap and achieve 20-80µm pitch wiring in a low-cost, large area substrate platform.

Table 1.2 shows the current state-of-the-art parameters and advanced research focus in this thesis.

| Parameter                      | Current State-of-the-art<br>Package Substrate            | Proposed Research         |  |

|--------------------------------|----------------------------------------------------------|---------------------------|--|

| Core Substrate with low        | CTE: 16-18ppm/°C                                         | CTE: 3-10ppm/°C           |  |

| CTE and high modulus           | Modulus: 20-30 GPa                                       | Modulus: 100-200 GPa      |  |

|                                | Ероху                                                    | BCB or other thin film    |  |

| Low Loss and Thin Film         | Loss tangent: 0.01-0.02                                  | Loss tangent: 0.001-0.005 |  |

| Dielectric                     | Film Thickness per layer: 30-                            | Film Thickness per layer: |  |

|                                | 50µm                                                     | 10-25µm                   |  |

| IC & Substrate Wiring<br>Pitch | 150-180µm                                                | 20-80µm                   |  |

| Fine Lines and Spaces          | 20µm (Subtractive Etching)                               | 5-10µm (Additive Plating) |  |

| Microvia Diameter              | 35-50μm (UV laser), 50-<br>100μm (CO <sub>2</sub> laser) | 10-30μm (Excimer Laser)   |  |

| Copper-Dielectric              | Chemical Treatment                                       | Plasma Surface            |  |

|                                | (1-3µm Ra)                                               | Modification (< 1µm Ra)   |  |

| Interfaces                     | Microetch for Cu Roughening                              | Non-Etch Cu Treatment     |  |

Table 1.2 Comparison of State-of-the-art and Proposed Research Parameters

#### **CHAPTER 2**

## LOW CTE CORE SUBSTRATES

High density substrates require a stable and high modulus core substrate on which to build multiple layers of thin film dielectric and conductor wiring. The core must have dimensional stability of <10 microns per inch in order to achieve the required layer to layer alignment of build-up dielectric layers. The build-up dielectric films must also have low thermal coefficient of expansion (CTE) in order to match the low CTE core substrate and prevent additional warpage and dimensional change during multilayer processing. Thin polymer films with low processing temperature are important for ultra-small microvias and low process cost. Low loss tangent and low dielectric constant are also critical for the dielectric material for signal integrity. This chapter is organized into two major sections, (a) new low CTE, high modulus core substrate materials and processes, and (b) results and analysis from processes and microstructures for low loss thin film polymer dielectrics.

## 2.1. Property Requirements and Selection of Core Substrates

The main properties considered during the selection of core materials for ultrahigh density SOP substrates include:

- Low to medium coefficient of thermal expansion (CTE) in the range of 3-10 ppm/°C matching Silicon CTE of 3ppm/°C for improved IC-to-substrate flipchip interconnect reliability

- High elastic modulus (100-400 GPa) for minimum warpage during thin film build-up processing and flat substrates for ultra-fine pitch (20-80µm) flip-chip assembly

- Excellent dimensional stability with less than 10µm/inch change in dimension across the 300mm panel during thermal excursions from room temperature to dielectric cure temperature (180-250°C) and back.

- High temperature stability to withstand dielectric processing and interconnect assembly processes up to 260°C

- Large area (300-600mm) and low-cost processing capabilities to allow for inexpensive and easy machinability for singulation into individual packages

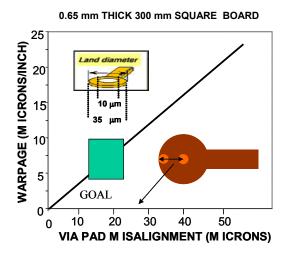

The stringent need to process 10 or more layers of thin films, with via sizes of 10  $\mu$ m and capture pads less than 50  $\mu$ m, requires substrate materials with warpage in the few microns over 300-mm in size. As shown in Figure 2.1, via-to-pad misalignment of less than 10  $\mu$ m requires warpage control to 5 to 10  $\mu$ m/inch over 300 mm for 0.65-mm-thick substrates.

Figure 2.1. Correlation of Substrate Warpage and Via-Pad Misalignment

The warpage for a two layered structure consisting of a core and build-up film as given by Stoney's equation is:

$$\rho \prec E_s \Rightarrow Warpage \prec \frac{1}{E_s}$$

where

$\rho$  is the radius of curvature of the substrate

$E_s$  is the elastic modulus of the substrate

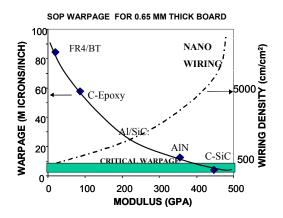

It can be seen that a higher modulus results in a higher radius of curvature (and consequently lesser warpage). Figure 2.2 shows the relationship between substrate modulus and process-induced warpage for sequential buildup of 10 layers of 5 $\mu$ m line/space wiring with 35 $\mu$ m via pads. Based on thermomechanical modeling, the modulus required for the substrate is in excess of 400 GPa, represented by the acceptable warpage<sup>20</sup>.

Figure 2.2. Thermo-mechanical Modeling of Substrate Warpage Based on Modulus & Thin Film Build-up Process

Current flip chip package solutions for 200-µm pitch area array use BT resin and high glass transition temperature (Tg) FR-4 laminates with a CTE of 18 ppm/°C. A silicon die has an approximate CTE of 2 to 3 ppm/°C, and thermomechanical stresses are induced in the package from the CTE mismatch between the die, the substrate and the buildup materials. These thermomechanical stresses result in solder joint failure, die

cracking, delamination of the solder bumps and cracking of the build-up layers - leading to failure of the assemblies<sup>21,22</sup>.

## 2.2. Core Substrate Materials Studied in this Research

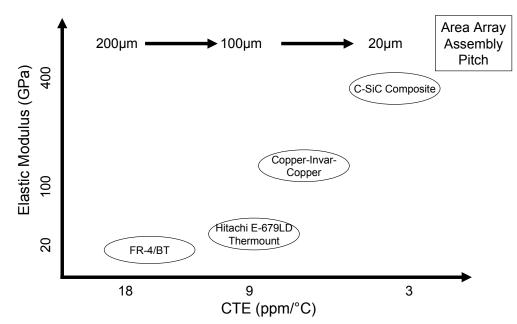

Based on the property requirements for the core substrate, several new materials were explored during this research and they are shown in chronological order in Figure 2.3.

Figure 2.3 Thermo-mechanical Properties of Core Substrates Explored in this Research

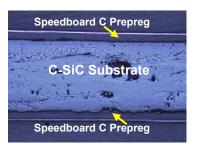

Epoxy-based low CTE laminates from Hitachi Chemical have CTE of around 8-11 ppm/°C and modulus of 30 GPa<sup>23</sup>. Laminates using thin Cu-invar-Cu cores (50-200µm thickness) and multilayer PTFE dielectric resulted in composite CTE of 6-8ppm/°C although they had low modulus (1-5 GPa)<sup>24</sup>. The main focus of this research was on a novel Carbon fiber reinforced SiC composite substrate.

A manufacturing process (patented by Starfire Systems Inc., NY) has been demonstrated to yield large area, thin, carbon-silicon-carbide-based composite boards with the required stiffness and Si-matched CTE<sup>25</sup>. Composite C-SiC cores with 2.5-

$3ppm/^{\circ}C$  CTE and 150-300GPa modulus was selected for further process development and integration. The C-SiC cores (Starboard<sup>TM</sup> C) have a CTE of 2.5ppm/°C to improve flip-chip reliability at 20-100µm pitch and modulus in excess of 200GPa to minimize warpage during single sided build-up processing. Alternate reinforcements in the SiC matrix have also been developed to tailor the substrate properties, such as low loss tangent using alumina (Starboard<sup>TM</sup> A - composite loss tangent of 0.03) and glass fibers (Starboard<sup>TM</sup> G - composite loss tangent <0.01). The key properties of the three SiC matrix composite substrates are shown in Table 2.1

Table 2.1 Comparison of Electrical and Mechanical Properties of SiC Composite

Substrates with Carbon, Alumina and Glass Fiber Reinforcement

| Substrate Properties          |        | Material System |         |        |         |

|-------------------------------|--------|-----------------|---------|--------|---------|

| Property                      | Level  | Units           | С       | Α      | G       |

| Glass Transition Temp.        | DMA    | °C              | 850     | 850    | 650     |

| Flex Modulus                  | 20 °C  | GPa             | 300     | 115    | 35 - 55 |

|                               | 200 °C | GPa             | 300     | 115    | 35 - 55 |

| СТЕ                           | 20 °C  | ppm/°C          | 2.5-3.5 | 4 - 5  | 3 - 4** |

|                               | 240 °C | ppm/°C          | 2.5-3.5 | 4 - 5  | 3 - 4** |

| Relative Hardness             | 20 °C  |                 | 300     | 200    | 150     |

|                               | 200 °C |                 | 300     | 200    | 150     |

| Dielectric Constant           | 1.2GHz |                 | -       | 7.55   | 3.9     |

| Dissipation Factor            | 1.2GHz |                 | -       | .030   | .001    |

| Volume/surface<br>resistivity |        | Ωcm             | -       | >10 14 | ~10 15  |

# 2.3. Results and Discussion - Source of Surface Defects and Roughness in C-SiC

## Substrates

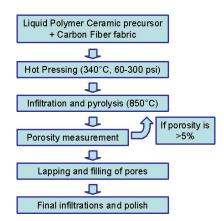

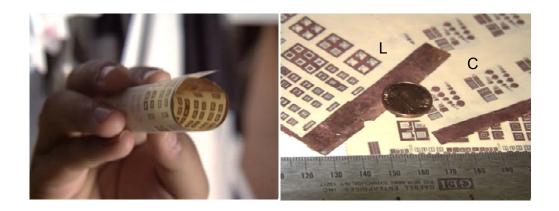

The unique chemical process used for fabricating the SiC matrix – Carbon fiber composite substrate is shown in Figure 2.4. This process has been used to demonstrate large area panels up to 300mm size, with scalability to 600mm square panels due to the molding process used for the fabrication.

Figure 2.4 Fabrication Process for Carbon Fiber Reinforced SiC Composite Substrate

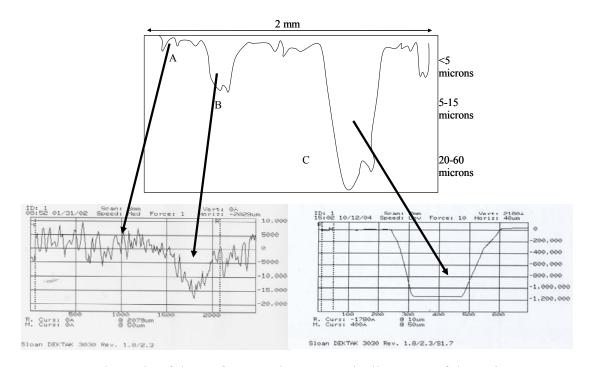

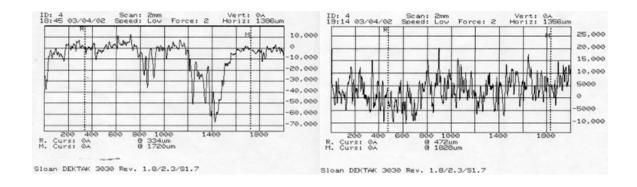

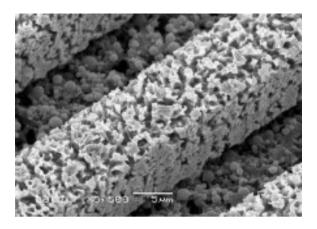

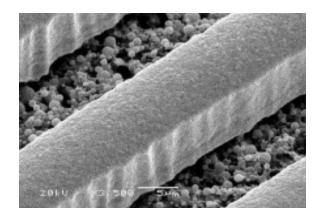

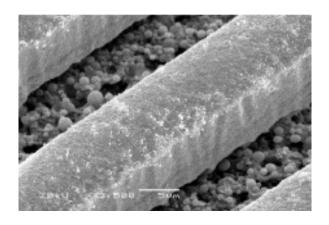

A schematic of the topography of C-SiC composite substrates is shown in Figure 2.5, which illustrates surface roughness, planarity and small and large porosity based surface defects that were encountered during processing. Contact profilometry (Veeco Dektak 30 profilometer) was used to characterize the surface topology and roughness of the C-SiC substrates. The pore dimensions were measured over a span of 10 mm. For simplicity, the roughness can be categorized into three ranges, (a) roughness of under  $5\mu$ m R<sub>z</sub>, these are mainly from the roughness of the molding plate surface used and from carbon fiber bundles appearing close to the surface during grinding and polishing processes to achieve flat substrates; (b) small pits caused by surface and sub-surface porosity in the range of 5-15 $\mu$ m depth; and (c) large pits in the 20-30 $\mu$ m range with some as large as 60 $\mu$ m depth caused by the exposure of internal porosity related to knots in the carbon fiber fabric reinforcement.

Figure 2.5: Schematic of the surface roughness. Typically, pores of three size ranges can be seen (around 3-5 microns, 5-15 microns and 20-60 microns).

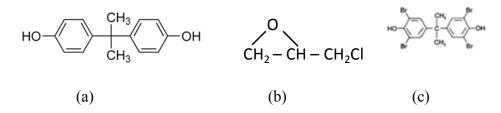

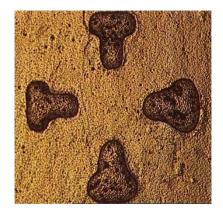

Initially, 1mm and 2.5mm thick C-SiC substrates were obtained with minimum amount of the large pits. As the thickness of the substrate was reduced to 0.5mm, the incidence of large pits increased, and it was found to be related to the increasing volume percentage of carbon fiber reinforcement and knots in the carbon fiber fabric.