#### - INSTITUTO SUPERIOR DE ENGENHARIA DE LISBOA

Área Departamental de Engenharia de Eletrónica e Telecomunicações e de Computadores

# Coluna de som utilizando array de Transdutores de Ultrasons

Paulo Jaime Estrela Janganga (Grau académico)

Trabalho Final de Mestrado para Obtenção do Grau de Mestre em Engenharia de Electrónica e Telecomunicações

Orientador:

Doutor Joel Vera Cruz Preto Paulo

Júri:

Presidente:

Doutora Maria Manuela Almeida Carvalho Vieira

Vogais:

Doutor Mário Pereira Véstias Doutor Joel Vera Cruz Preto Paulo

Dezembro de 2015

#### Resumo

Este relatório documenta a Tese de Mestrado com o tema *Audio Spotlight* - Coluna de Som utilizando Arrays de Transdutores de Ultrassons realizado por Paulo Jaime Estrela Janganga.

Este trabalho assenta na implementação de um sistema de áudio direcional *Audio Spotlight*. Atualmente começam-se a dar os primeiros passos ao nível da comercialização de produtos com este tipo de tecnologia. No entanto, existem ainda aspetos técnicos que necessitam de ser resolvidos antes da sua aplicação no nosso dia-a-dia.

O problema principal é a distorção que um sistema deste tipo gera ao utilizar interações nãolineares de ondas de alta frequência (ultrassons) para gerar ondas de baixa frequência dentro da gama audível pelos seres humanos. Depois de resolvido este e outros problemas adjacentes ao sistema, o seu potencial é promissor, sendo a lista de aplicações práticas e comerciais muito abrangente. Alguns exemplos são:

- Num automóvel, em que cada um dos ocupantes poderá ouvir a sua própria música, sem perturbar os companheiros de viagem;

- Numa conferência, onde cada membro da audiência poderá ouvir o áudio no seu idioma, sem recorrer à utilização de headphones;

- Em sistemas de anúncios sonoros nas ruas e praças, que poderão ser substituídos por mensagens áudio direcionadas a cada um dos transeuntes, eliminando a poluição sonora.

Esta tese está organizada em três partes:

- 1. Teoria e Evolução de sistemas de Audio Spotligh;

- 2. Implementação do Sistema de Audio Spotlight na FPGA Spartan 3E;

- 3. Implementação do Sistema de Audio Spotlight no DSP TMS320C6713;

- 4. Resultados experimentais.

A primeira parte introduz todos os aspetos teóricos referentes à tecnologia, para que seja possível compreender os fenómenos físicos e a matemática associada a um sistema deste tipo. Na segunda parte é explicada a forma como o sistema foi implementado na FPGA Spartan 3E, com a explicação de todos os módulos constituintes da aplicação. A terceira parte é idêntica à segunda, mas desta vez a implementação é realizada no DSP TMS320C6713. Na última parte é feita a demonstração experimental dos conceitos aplicados nesta tese recorrendo à captura de sinal com osciloscópio.

#### Abstract

This report documentary Master's Thesis with the theme Audio Spotlight - Sound Column using Ultrasound Transducers Arrays conducted by Paul Jaime Estrela Janganga.

This work will be based on the implementation of an Audio Spotlight system, which is a way audio technology. These days, begin to take the first steps in terms of marketing of such products, but there are still some issues that need to be resolved before the technology really come on a day-to-day of all of us. The main problem is the distortion that generates such a system by using nonlinear interaction of high frequency waves (ultrasound) to generate low frequency waves audible to humans.

After solved the problems surrounding the system, the benefits are huge with a list of practical applications and virtually endless commercials:

- In a car each occupant can listen to your own music, without disturbing fellow travelers;

- At a conference, each audience can receive the sound in your language, without the use of headphones in the ears;

- Ad systems on the streets and squares may be replaced by targeted messages to each of the passers-by, eliminating noise pollution.

This document is divided into three distinct parts:

- 1. Theory and Evolution of Audio Spotlight systems.

- 2. Implementation of the Audio Spotlight system in Spartan 3E FPGA.

- 3. Implementation of the Audio Spotlight system in the TMS320C6713 DSP.

The first part will introduce all the theoretical aspects related to technology, so you can understand the physical phenomena and the mathematics associated with such a system.

In the second part it is explained how the system was implemented in FPGA Spartan 3E, with the explanation of all the constituent modules of the application.

The third part is identical to the second, but this time the implementation is done in DSP TMS320C6713.

At the end of the last two parts there is an area reserved for testing in order to view the results, especially through oscilloscope captures.

#### **Acrónimos**

SSB Single Sideband

LSB Lower Sidebands

USB Upper Sideband

SC Supress Carrier

**SSB-WC** single-sideband with carrier

DSB double side band

THC Total Harmonic Current

SPL Sound Pressure Level

ADC Analog to digital converter

DAC Digital to analog converter

AM Amplitude modulation

**SFDR** Spurious Free Dynamic Range

**VHDI** VHSIC Hardware Description Language

DSP Digital Signal Processor

DA Distributed Arithmetic

IP Intellectual Property

RMS Root mean square

RAM Random access memory

MAC Multiplication and accumulate

**FFT** Fast Fourier transform

# Índice

| Lista de Figuras                                                                                | III    |

|-------------------------------------------------------------------------------------------------|--------|

| Capítulo 1: Introdução                                                                          | 1 -    |

| 1.1 - Histórico                                                                                 | 2 -    |

| 1.2 - Cronologia de desenvolvimento                                                             | 3 -    |

| Capítulo 2: Revisão de Literatura                                                               | 5 -    |

| 2.1 - Base teórica da acústica não linear de ultrassons                                         | 5 -    |

| 2.2 - Base matemática                                                                           | 6 -    |

| 2.2.1- Equação padrão                                                                           | 6 -    |

| 2.2.2-Equação de Continuidade                                                                   | 8 -    |

| 2.2.3 - Equação de Euler                                                                        | 8 -    |

| 2.2.4-Combinando as equações                                                                    | 9 -    |

| 2.3 - Modulação e desmodulação de feixes de ultrassons direcionáveis para renderização de áudio |        |

| 2.4 - Distorção em sistemas de ultrassons                                                       | 12 -   |

| 2.5 - Metodologia de redução da distorção do trabalho prático                                   | 14 -   |

| Capítulo 3: Metodologia e Dados                                                                 | 15 -   |

| 3.1 - Metodologia processual                                                                    | 15 -   |

| 3.2 - Planeamento conceptual                                                                    | 16 -   |

| 3.3 - Implementação do sistema de ultrassons em Matlab                                          | 17 -   |

| 3.4.1 - Arquitetura 1 – SSB – WC (Filtro passa-banda)                                           | 17 -   |

| 3.4.2 - Arquitetura 2 – SSB – WC (Filtragem de Hilbert)                                         | 19 -   |

| Capítulo 4 – Implementação do sistema na FPGA                                                   | 21 -   |

| 4.1 - Acondicionamento de sinal                                                                 | 23 -   |

| 4.2 - PCB                                                                                       | 25 -   |

| 4.3 - Módulo de controlo do ADC-DAC                                                             | 26 -   |

| 4.4 - IP CORES                                                                                  | 27 -   |

| 4.4.1 - DDS                                                                                     | 27 -   |

| 4.4.2 - Multiplier                                                                              | 28 -   |

| 4.4.3-CORDIC                                                                                    | 29 -   |

| 4.5-Componentes                                                                                 | 29 -   |

| 4.5.1-Máquina de estados                                                                        | 34 -   |

| 4.6- Simulações – MATLAB (Sysgen)                                                               | 36 -   |

| 4.7-Problemas na implementação                                                                  | 38 -   |

| MAP REPORT                                                                                      | - 39 - |

| 4.8-Resolução dos problemas na implementação                           | - 39 - |

|------------------------------------------------------------------------|--------|

| 4.9-Testes à implementação do sistema na FPGA SPARTAN 3E               | - 40 - |

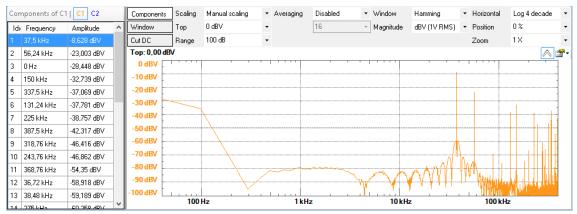

| 4.9.1-Frequência de Amostragem                                         | - 40 - |

| 4.9.2-Portadora                                                        | - 41 - |

| 4.9.3-Sinal capturado pelo ADC                                         | - 42 - |

| 4.9.4-Sinal Modelado                                                   | - 43 - |

| 4.10-Filtragem                                                         | - 44 - |

| 4.10.1-Filtro Passa-Banda 20 - 40Khz                                   | - 47 - |

| 4.10.2-Filtro Passa-Banda 40 - 60Khz                                   | - 48 - |

| 4.10.3-Filtragem de Hilbert                                            | - 50 - |

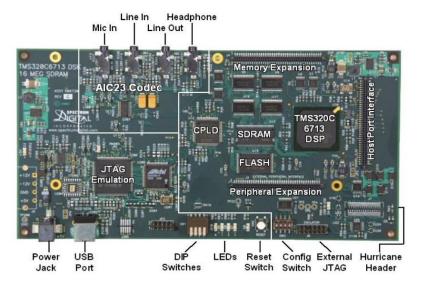

| Capítulo 5 – Implementação no DSP TMS320C6713s                         | - 51 - |

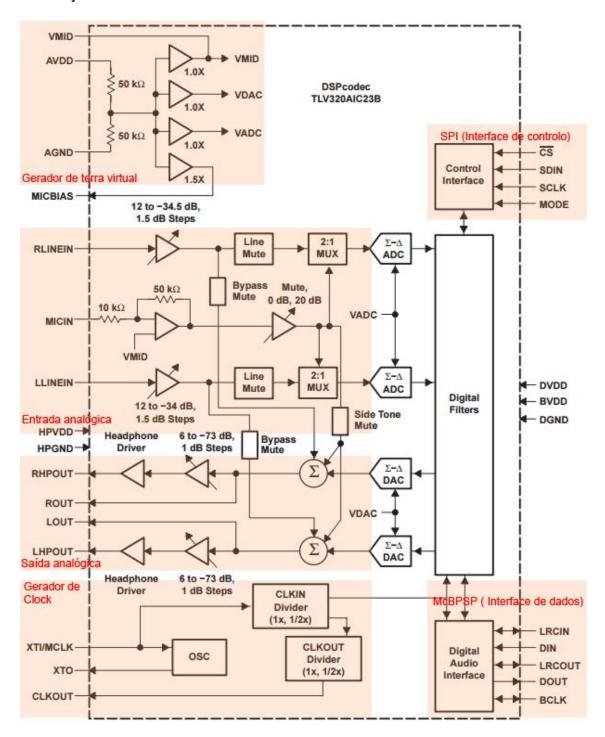

| 5.1- Codec AIC23                                                       | - 52 - |

| 5.1.1-Registos e respetivas funcional idades do Codec AIC23            | - 52 - |

| 5.1.2-Interface do codec AIC23                                         | - 53 - |

| 5.2- Implementação do código                                           | - 54 - |

| 5.2.1-Inicialização do DSP TMS320C6713                                 | - 55 - |

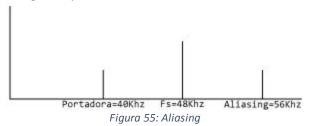

| 5.2.2-Portadora                                                        | - 56 - |

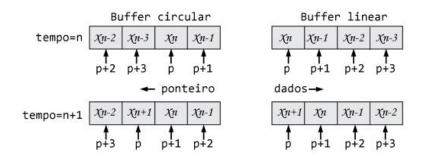

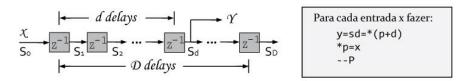

| 5.2.3-Atraso                                                           | - 57 - |

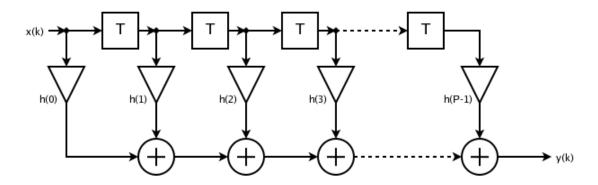

| 5.2.4-Filtragens                                                       | - 59 - |

| 5.3 - Análise dos resultados dos módulos programados                   | - 60 - |

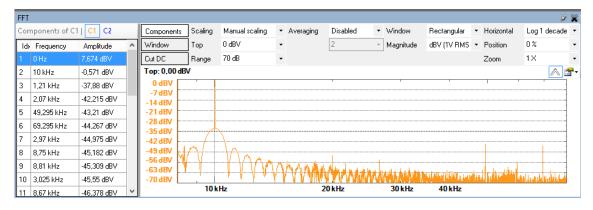

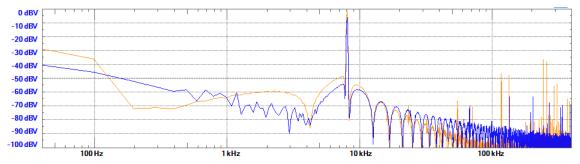

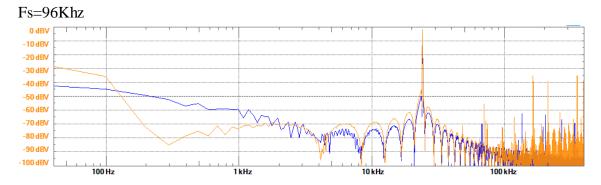

| 5.3.1-Frequência de amostragem                                         | - 61 - |

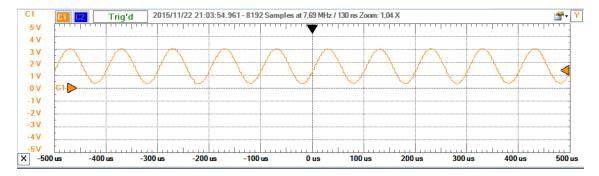

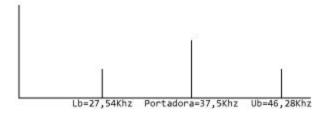

| 5.3.2-Portadoras de ultrassons                                         | - 62 - |

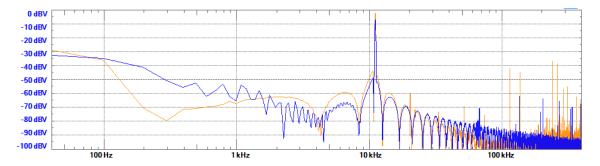

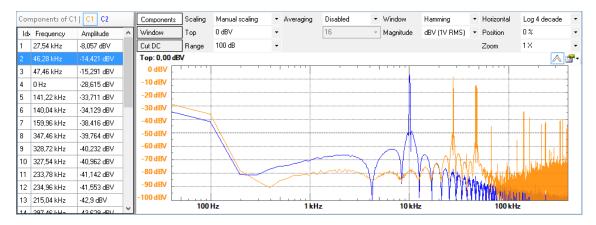

| 5.3.3-Sinal modelado                                                   | - 64 - |

| 5.3.4-Filtro passa-baixo                                               | - 66 - |

| 5.3.5-Filtros passa-banda                                              | - 68 - |

| Número de coeficientes=15 Fc1=25Khz Fc2=40Khz                          | - 69 - |

| 5.4-Sistema de ultrassons                                              | - 70 - |

| 5.5-Processos de redução da distorção                                  | - 71 - |

| Capítulo 6: Comparação de resultados, Limitações e Investigação Futura | - 73 - |

| 6.1-Comparação de resultados                                           | - 73 - |

| 6.2-Limitações                                                         | - 74 - |

| 6.3-Investigação futura                                                | - 74 - |

| Capítulo 7 – Conclusão                                                 | - 75 - |

| Bibliografia                                                           | - 77 - |

# Lista de Figuras

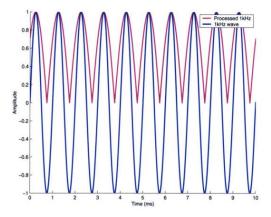

| Figura 1: A Azul temos o sinal antes de ser processado e a lilás o sinal pós processado | - 13 - |

|-----------------------------------------------------------------------------------------|--------|

| Figura 2: Azul - Sinal de entrada Lilás - Sinal processado                              | - 13 - |

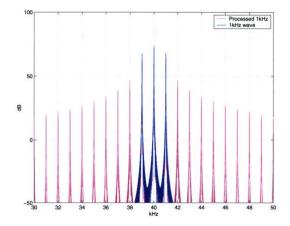

| Figura 3:Atenuação do sinal ultrassónico                                                | - 14 - |

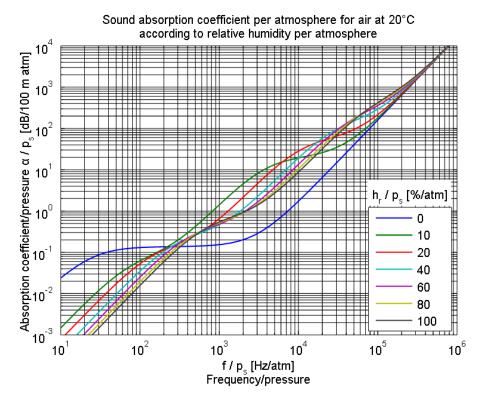

| Figura 4: Processo de desenvolvimentos dos sistemas.                                    | - 15 - |

| Figura 5: Primeira arquitetura - Sistema DSB-WC                                         | - 16 - |

| Figura 6: Segunda arquitetura SSB                                                       | - 17 - |

| Figura 7: Captura da aplicação de ultrassons gerada em Matlab                           | - 18 - |

| Figura 8:Block set DSP do Sysgen                                                        | - 21 - |

| Figura 9: Configuração inicial no Sysgen                                                | - 21 - |

| Figura 10:Token System Generator                                                        | - 22 - |

| Figura 11: Sistema de captura analógica                                                 | - 23 - |

| Figura 12: Circuito de acondicionamento de sinal                                        | - 24 - |

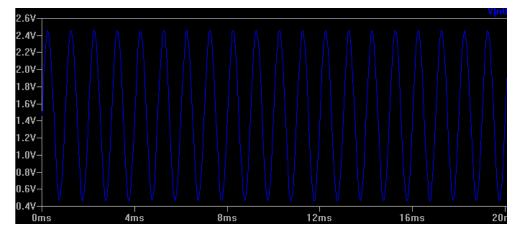

| Figura 13: Sinal de entrada                                                             | - 24 - |

| Figura 14: Sinal de saída                                                               | - 24 - |

| Figura 15: Sinal de entrada, saída e referência                                         | - 25 - |

| Figura 16: Controlo_tensao.SchDoc                                                       | - 25 - |

| Figura 17: controlo_tensao_PcbDoc                                                       | - 26 - |

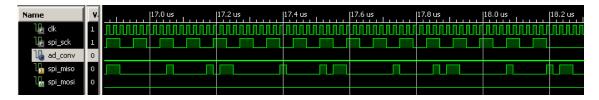

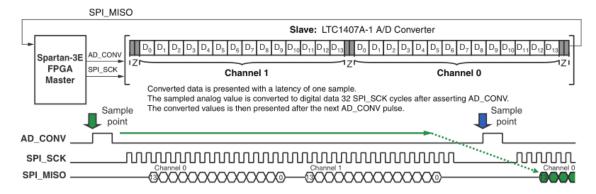

| Figura 18:Captura no ISIM do sistema de controlo do ADC/DAC                             | - 26 - |

| Figura 19: Trama do ADC                                                                 |        |

| Figura 20: Máquina de estados do componente ADC                                         | - 34 - |

| Figura 21: Máquina de estados do DAC                                                    | - 35 - |

| Figura 22:Máquina de estado dos do componente Top_Module                                | - 36 - |

| Figura 23: Sinal modulado                                                               | - 37 - |

| Figura 24: Sinal filtrado                                                               | - 38 - |

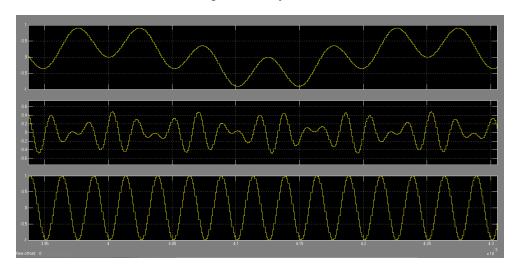

| Figura 25: [1]Sinal modulado - [2]Sinal filtrado - [3]Portadora                         | - 38 - |

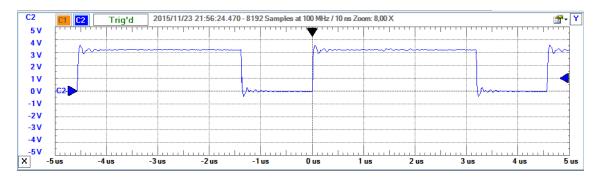

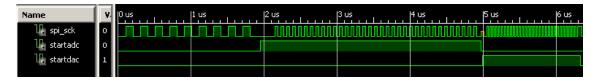

| Figura 26: Sinal STAR_ADC (Tempo em que a operação realizada pelo ADC está ativa)       | - 40 - |

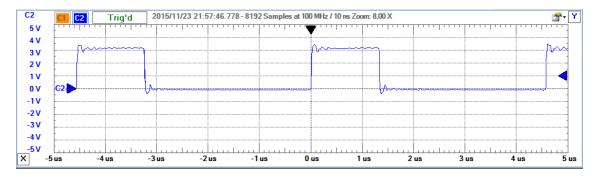

| Figura 27: Sinal START_DAC (Tempo em que a operação realizada pelo DAC está ativa)      | - 41 - |

| Figura 28:Portadora [Sinusoide a 40Khz]                                                 | - 41 - |

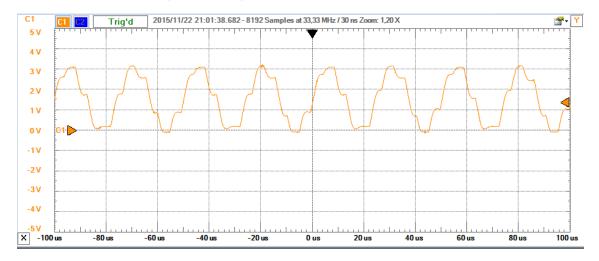

| Figura 29: Portadora no domínio do tempo                                                | - 42 - |

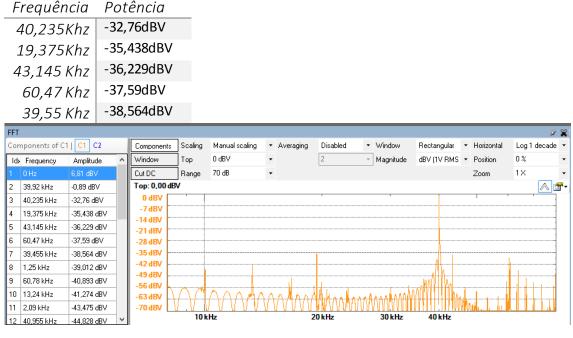

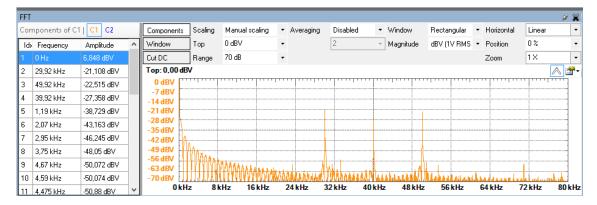

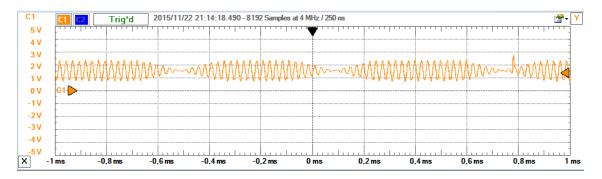

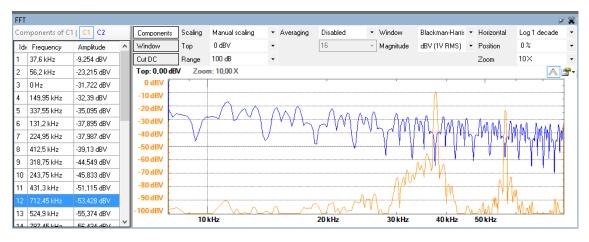

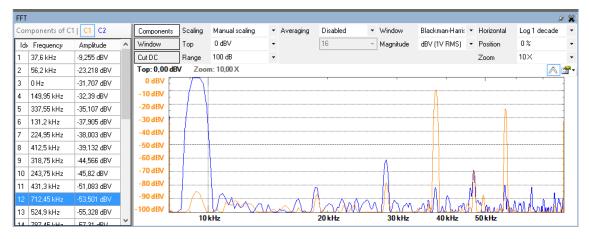

| Figura 30: FFT do sinal capturado pelo ADC e amostrado pelo DAC                         | - 42 - |

| Figura 31:Sinal capturado pelo ADC e amostrado pelo DAC no domínio do tempo             |        |

| Figura 32: Sinal modulado no domínio da frequência                                      | - 43 - |

| Figura 33:SInal modulado no domínio do tempo.                                           | - 44 - |

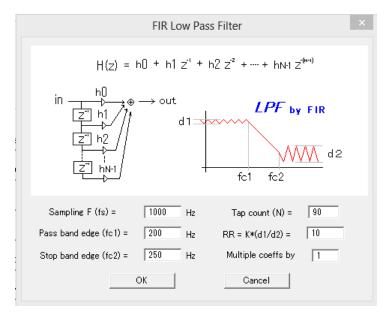

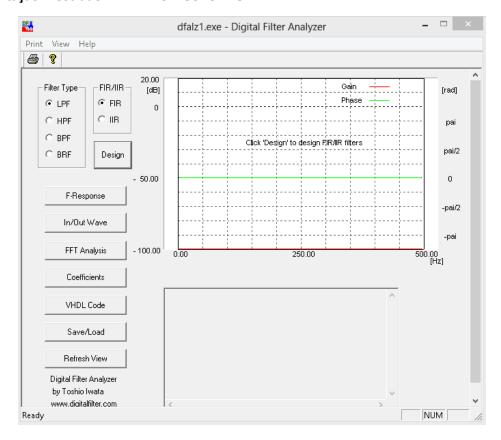

| Figura 34:Opções de configuração                                                        | - 46 - |

| Figura 35: Programa dfalz1                                                              | - 47 - |

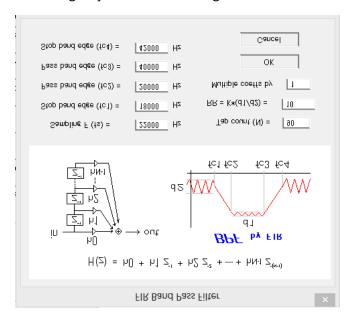

| Figura 36: Configuração do Filtro Passa-Banda 20 - 40Khz                                |        |

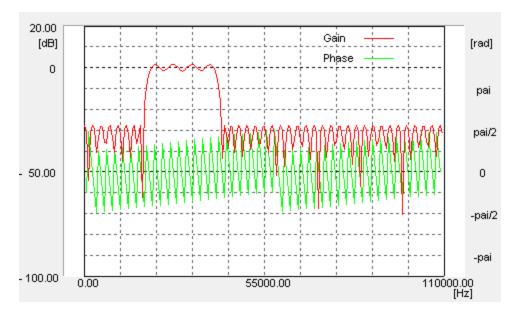

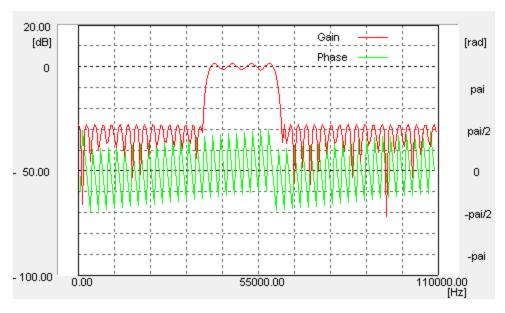

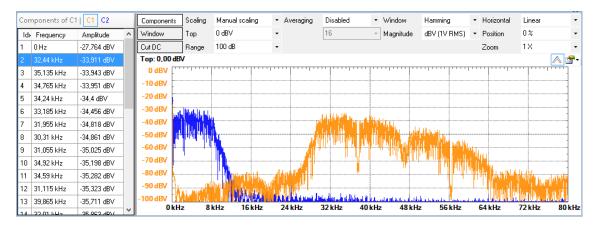

| Figura 37: Banda passante do Filtro Passa-Banda 20 - 40Khz                              | - 48 - |

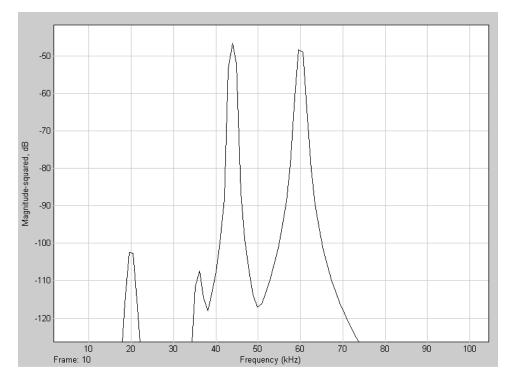

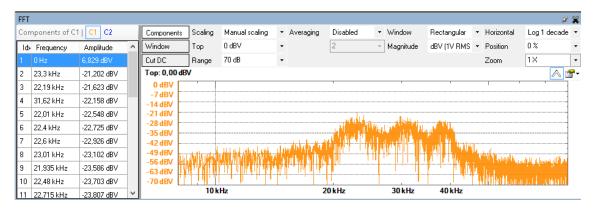

| Figura 38: Captura do Filtro Passa-Banda 20 - 40Khz ao injetar um sinal de ruído branco | - 48 - |

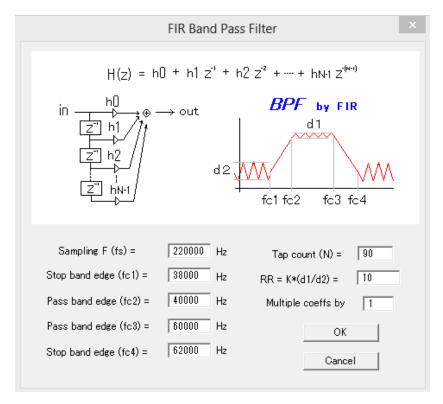

| Figura 39: Configuração do Filtro Passa-Banda 40 - 60Khz                                | - 49 - |

| Figura 40:Banda passante do Filtro Passa-Banda 40 - 60 Khz                              | - 49 - |

| Figura 41: Captura do Filtro Passa-Banda 40 - 60Khz ao injetar um sinal de ruído branco | - 50 - |

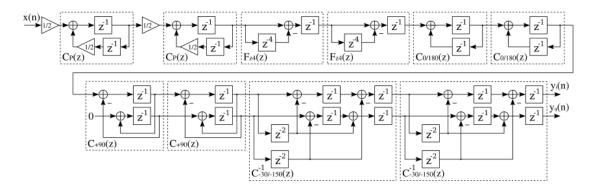

| Figura 42: Diagrama de blocos do filtro de Hilbert                                      | - 50 - |

| Figura 43: DSP TMS320C6713 DSK                                                          | - 51 - |

| Figura 44: Valores possíveis do registo 8                                               | - 52 - |

| Figura 45: Blocos constituintes e implementação interna do codec AIC23                  | - 54 - |

| Figura 46: Arquiteturas dos buffers linear e circular                                   | - 58 - |

| Figura 47: Diagrama de blocos e pseudo-código de processamento de amostras         | 59 -     |

|------------------------------------------------------------------------------------|----------|

| Figura 48: Estrutura interna do filtro FIR                                         | 60 -     |

| Figura 49: Código - Fs = 8Khz                                                      | 61 -     |

| Figura 50: Código - Fs = 32Khz                                                     | 61 -     |

| Figura 51: Código - Fs = 44,1Khz                                                   | 62 -     |

| Figura 52: Código - Fs = 48Khz                                                     | 62 -     |

| Figura 53: Código - Fs = 96Khz                                                     | 62 -     |

| Figura 54: Geração da portadora a 40Khz                                            | 63 -     |

| Figura 55: Aliasing                                                                | 63 -     |

| Figura 56: Captura do sinal modelado em DSB                                        | 64 -     |

| Figura 57: Modulação DSB                                                           | 65 -     |

| Figura 58: Sinal de teste de ruído branco gerado no Adobe Audition                 | 65 -     |

| Figura 59: Modulação DSB com ruído branco com Fc1=300Hz e Fc2=8Khz como sinal      | de teste |

| 65 -                                                                               |          |

| Figura 60: Modulação com um sinal de 5Khz conjuntamente com a adição da portado    | ora 66 - |

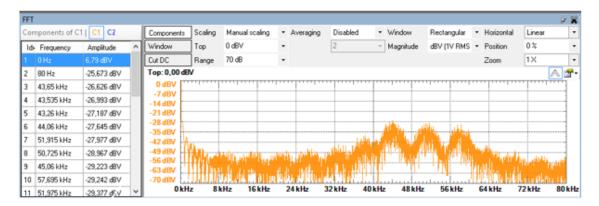

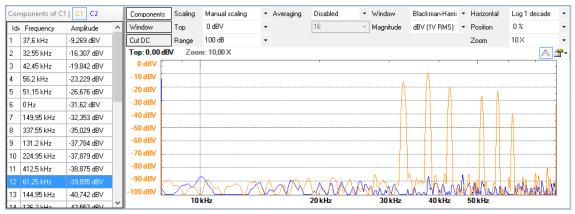

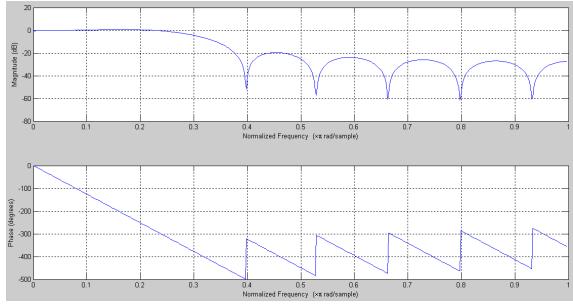

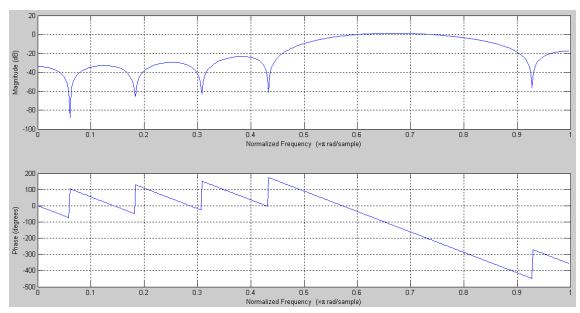

| Figura 61: Fase e magnitude do filtro passa-baixo de 15 coeficientes               | 67 -     |

| Figura 62: Captura do filtro passa-baixo de 15 coeficientes                        | 68 -     |

| Figura 63: Fase e magnitude do filtro passa-banda com Fc1=25Khz Fc2=40Khz de 15    |          |

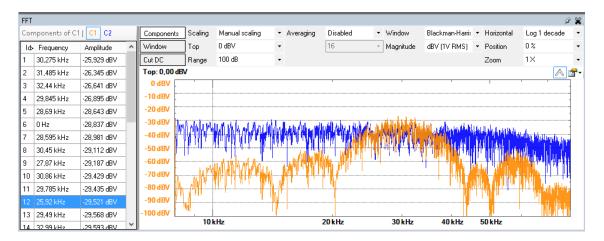

| coeficientes                                                                       | 69 -     |

| Figura 64: Captura do filtro passa-banda com Fc1=25Khz Fc2=40Khz de 15 coeficiente | es 70 -  |

| Figura 65: Arquitetura SRAM                                                        | 71 -     |

| Figura 66: Aplicação do algoritmo SRAM com ruído branco                            | 72 -     |

| Figura 67: Aplicação do algoritmo SRAM com uma sinusóide de 10Khz                  | 72 -     |

| Figura 68: Relógio SPI                                                             | 74 -     |

# Capítulo 1: Introdução

Este trabalho efetua um estudo sobre o método predominante de se alcançar um feixe de som direcional. A primeira parte tem como objetivo introduzir a tecnologia, apesentando os conceitos basilares adjacentes a qualquer sistema que tenha como premissa atingir um elevado grau de direccionalidade. Para além disso também é apresentada a evolução que os diversos conceitos abordados foram sofrendo ao longo dos tempos. O segundo capítulo do trabalho vai incidir essencialmente no estado de arte dos diferentes módulos do sistema de áudio spotlight, com principal enfoque nos trabalhos desenvolvidos por Bertkay e Pompei, pois estes foram os investigadores que mais contribuíram para o estado atual da tecnologia, sendo então estudada a forma como estes dois investigadores fizeram a abordagem teórica e matemática ao problema, tendo especial foco na questão das não-linearidades.

No terceiro capítulo são abordadas as metodologias a seguir para desenvolver o sistema, e paralelamente inicializa-se a abordagem prática ao se descrever a implementação de simulações em Matlab de forma a se perceber o funcionamento e resposta do sistema às diferentes arquiteturas, assim como para se antever a melhor forma de se implementar o sistema na FPGA e no DSP. O quarto capítulo incide na abordagem prática, com descrição pormenorizada das tecnologias utilizadas (FPGA Spartan 3E e DSP TMS320C6713 DSK), assim como das arquiteturas desenvolvidas para realizar os sistemas de Áudio Spotlight, acompanhadas pelos resultados obtidos. Por último entra-se no quinto capítulo que aborda as limitações encontradas no sistema, as futuras investigações e por fim a conclusão.

A dissertação de mestrado pretende abordar a diretividade sonora em várias vertentes testando várias arquiteturas de modulação, e valendo-se ora da banda lateral superior ou da inferior resultante da modulação DSB-WC de forma a comparar a performance do sistema em diferentes casos, também para depurar os problemas inerentes aos sistemas desenvolvidos de forma a encontrar a solução mais viável para os resolver.

Basicamente a diretividade de uma fonte sonora está relacionada com a relação existente entre o comprimento de onda a reproduzir e as dimensões da fonte sonora. Para fontes sonoras mais pequenas, ou do tamanho do comprimento de onda a reproduzir, vamos obter um modo de propagação omnidirecional; contrariamente, para fontes sonoras com um tamanho bastante maior que os comprimentos de onda transmitidos por esta, vamos ter o som a propagar-se com um elevado grau de direccionalidade. As ondas sonoras estão compreendidas entre os 20Hz e os 20Khz e têm comprimentos de onda que vão desde os 17,2 milímetros até aos 17,2 metros assumindo a velocidade de propagação igual a 344 metros por segundo e tendo em conta a seguinte formula:

$$\lambda = \frac{c}{f}$$

$\lambda$  = Comprimento de onda da onda sonora.

c = velocidade de propagação das ondas sonoras no ar.

f = frequência da onda sonora.

Tendo em conta estes pressupostos, as fontes sonoras que se encontrem dentro destas dimensões vão ter um comportamento omnidirecional. A ideia adjacente ao som direcional é ao invés de transmitir o som na faixa audível, passar a transmitir a informação sonora em ultrassons, com comprimentos de onda centrado nos milímetros de forma a obter comprimentos de onda bastante mais pequenos que as fontes sonoras para que se consigam criar feixes de som estreitos o suficiente para alcançar o pressuposto referido anteriormente de ter a fonte sonora com uma dimensão superior aos comprimentos de onda emitidos de forma a se alcançar um feixe de som direcional.

Os ultrassons são completamente inaudíveis ao ouvido humano, mas as tecnologias de som direcional baseiam-se nas não-linearidades presentes no meio de propagação para que se consiga converter os ultrassons em som audível. No ar as não-linearidades estão presentes na forma de uma perturbação da velocidade do som em função da pressão e densidade do ar.

As não-linearidades podem ser expressas na forma de séries de Taylor[4], pelo que se pode considerar o primeiro termo não linear como a relação com a função quadrática:

$$y = (\sum_{i=0}^{\infty} a_i \sin \omega_i)$$

(1)

Partindo do pressuposto que uma coleção de ondas sinusoidais é elevada ao quadrado, demonstra-se que através das não linearidades é criada uma onda constituída pelas soma e diferença das frequências originais.

$$y = \sum b_{i,j} \left( \sin(\omega_i + \omega_j) + \sin(\omega_i - \omega_j) \right)$$

(2)

Caso as frequências  $\omega_i \ e \ \omega_j$  estejam presentes na zona dos ultrassons, os termos  $\omega_i + \omega_j$  podem ser ignorados, pois resultam em frequências ultrassónicas adicionais.

Já os termos  $\omega_i - \omega_j$ , caso tenham sido escolhidos corretamente vão cair dentro da gama audível. As não-linearidade causam uma transferência de energia das frequências ultrassónicas para as frequências audíveis. O comprimento do feixe de som é limitado pela absorção dos ultrassons pelo ar, podendo atingir vários metros de comprimentos. Regra geral alcança uma distância bem maior do que os feixes produzidos pelos sistemas de som normais, que reproduzem frequências na gama do som audível.

#### 1.1 - Histórico

A história do som direcionado inicializa-se a meio do século 19 quando Helmholtz introduz o conceito de geração de tons adicionais através da combinação de dois ou mais tons. Este trabalho foi desenvolvido recorrendo ao uso de tons gerados em violinos. O estudo na altura teve um grande impacto no campo da acústica, e deu iniciou a novas áreas de investigação, mas carecia ainda de algum formalismo físico e matemático de forma a dar suporte a um campo com tanta especificidade como as não-linearidades.

Foi então em meados do século vinte que se deu uma nova reviravolta neste campo científico, pois apareceram novas investigações, especialmente ao nível do desenvolvimento de sonares que vieram impulsionar a área. Posteriormente à paragem que se seguiu aos estudos de Helmholtz's, a tecnologia não-linear começou novamente a ser abordada a partir de meados de 1960. Inicialmente começou por ser estudada pela Marinha dos Estados Unidos e da União Soviética de forma a aperfeiçoar o alcance e a precisão dos sonares. É sabido que grande parte das tecnologias conhecidas pelo mundo atual tiveram os seus primeiros passos na investigação dentro do mundo militar. Já por volta de 1980 foram os japoneses que trouxeram alguns avanços no desenvolvimento do sistema não-linear, mas este apresentava na altura algumas limitações, especialmente referentes à qualidade do som, associada a um nível de distorção bastante elevado, e para além disso o sistema apresentava um elevado custo de desenvolvimento, fabrico e manutenção. Estes problemas ficaram por resolver até 1988, ano em que o Dr. F. Joseph Pompei do MIT lançou uma publicação que descrevia pormenorizadamente uma forma eficaz de reduzir a distorção, fazendo com que o sistema se tornasse bastante mais atrativo. A metodologia desenvolvida por Pompei perdura até hoje como o método predominante para se desenvolver sistemas sonoros diretivos.

# 1.2 - Cronologia de desenvolvimento

#### 1850

Os princípios básicos das operações não lineares começaram a ser delineados no século 19, data em que Helmholtz's lançou uma publicação de nome "Combination tones in violins" [23], onde realizou experimentos com a combinação de tons. Este cientista introduziu ao mundo a teoria descrevendo a geração de não linearidades através da combinação de tons, mostrando que um par de tons gerados por uma fonte comum podem gerar um par extra de tons no ar, com frequências correspondentes à soma e à diferença das frequências dos tons i niciais. Porém, apesar das experiências de Helmholtz's provarem a presença de tons adicionais no ar correspondentes à subtração e adição de um tom sobre o outro, a sua teoria não era sustentável a nível científico, e foram necessários muitos anos até começarem a ser encontradas soluções viáveis que introduzissem o mundo das não linearidades à comunidade científica.

#### Dezembro de 1962

O Professor de física Peter Westervelt da Universidade de Brown publicou uma investigação de nome "Parametric Acoustic Array"[21], onde o professor considerava a interação de ondas sinusoidais num determinado volume, calculando a pressão devido às não-linearidades dentro de uma pequena porção do volume. No estudo é referido a geração de um tom adicional ao longo do feixe constituído por um sinal de dois tons.

Foram tidos em conta vários pressupostos de forma a simplificar o trabalho, tais como:

- 1. O Tom gerado vai ter exatamente a mesma amplitude dos dois tons iniciais.

- 2. Um feixe colimado primário perfeito.

- 3. As duas sinusoides atenuam de forma idêntica ao mesmo sample rate.

- 4. Etc.

Este trabalho não apresentava a complexidade dos últimos desenvolvimentos, mas já apresentava um elevado nível de precisão, o que proporcionou de facto uma framework de desenvolvimento para os próximos investigadores refinarem o seu trabalho.

#### Outubro de 1965

H.O. Berktay publica um estudo de nome "Possible Exploitation of Non-Linear Acoustics in Underwater Transmitting Applications", que permite ter uma visão teórica bastante mais assertiva e conclusiva em relação aos arrays paramétricos acústicos.

Este trabalho foi de facto mais geral e completo pois explora vários casos em que por exemplo os sinais primários são cilíndricos ou esféricos. Para além disso abordou os planos das ondas colimadas em observação. Bertkay também não se limitou somente aos estudos de casos envolvendo sinais de dois tons, pois introduziu o conceito de envolvente, que permitiu que o estudo fosse aproximado da realidade, pois os altifalantes paramétricos não estão limitados a gerar somente um ou dois tons de cada vez.

## Capítulo 2: Revisão de Literatura

Este capítulo foi elaborado de forma a se compreender o estudo teórico por trás dos sistemas de Áudio Spotlight. Nele são abordados de forma mais aprofundada, os estudos de Bertkay e Pompei [4], que presentemente ilustram o estado de arte da tecnologia.

#### 2.1 - Base teórica da acústica não linear de ultrassons

As equações matemáticas que caracterizam a acústica não linear são por si só bastante complexas, e infelizmente não existe uma solução analítica geral. Normalmente recorre-se a uma simulação em computador para se tentar aproximar de situações realistas. No entanto, em 1965 Bertkay realizou uma análise que permitiu simplificar algumas das premissas tendo como resultado uma solução que tornou possível expressar o nível de pressão sonora (SPL) do sinal desmodulado em termos da pressão sonora da portadora ultrassónica modulada em amplitude [5]. De notar que o processo de desmodulação é extremamente danoso em termos de perdas, sendo que o mínimo previsto é de 60 dBs ao se passar do SPL ultrassónico para o SPL da onda acústica audível. O grande avanço de Berktay foi o facto deste conseguir antecipar um esquema de pré-compensação derivado da sua expressão, ao efetuar a raiz quadrada da envolvente do sinal em banda base (E) e seguidamente ao integrar o resultado duas vezes, de forma inverter o efeito da segunda derivada de tempo parcial[11]. Para conseguir atingir este resultado era usado um circuito analógico equivalente, em que um ampop com feedback realizava a operação de raiz quadrada, enquanto um equalizador era o circuito análogo a uma operação de integração. De seguida temos a expressão de Berktay's:

$$P_2(\mathbf{x}, \mathbf{t}) = \mathbf{K} \cdot P_c^2 \cdot \frac{\partial^2}{\partial t^2} E^2(\mathbf{x}, t)$$

(3)

Onde

$P_2(x,t) = Pressão sonora da onda secundária audivel$

$K = Variável \ que \ comporta \ vários \ aspectos \ fisicos \ do \ sistema$

$P_c = SPL da portadora ultrasónica$

E(x,t) = Função Envolvente (DSB - AM)

A equação diz-nos que a pressão sonora da onda ultrassónica desmodulada audível, ou seja, o sinal audível à saída é proporcional à raiz quadrada da segunda derivada da função da envolvente, ou seja, do sinal de entrada. O sistema de pré-compensação consiste em antecipar as operações do sinal de entrada, e aplicar as operações inversas ao mesmo, assumindo que o sinal de saída vai ser parecido com o sinal de entrada depois de aplicadas as operações inversas. Em meados de 1990 a tecnologia de áudio spotlight já conseguia operar, mas ainda com um elevado nível de distorção. Por esta altura os esquemas de pré-compensação fizeram com que se procurasse otimizar a resposta em frequência dos transdutores ultrassónicos [4]. A pesar a este facto os transdutores também precisaram de ter uma resposta de frequência mais ampla de forma a acompanhar os processos de pré-compensação digitais. Assim, em 1998 foi efetuado um estudo em simulação de computador de forma a quantificar a ineficiência da resposta em frequência dos transdutores usando o esquema de pré-compensação da expressão de Berktay's.

Em 1990 um artigo escrito por Pompei descreveu um novo protótipo de transdutor capaz de atender às crescentes exigências de transdutores com uma resposta em frequência mais ampla e dinâmica, uma vez mais baseado na expressão de Bertkay's. Finalmente a tecnologia que originalmente tinha sido desenhada para operar como sonar debaixo de água tinha alcançado um patamar de qualidade praticamente idêntico ao dos sistemas de som normais, graças ao sistema desenvolvido por Pompei.

#### 2.2 - Base matemática

Comparativamente, pode afirmar-se com toda a certeza que existe muito menos estudos científicos realizados para as matrizes paramétricas ao ar livre, do que para as mesmas em ambiente subaquático. Também se pode afirmar que as aplicações em meio subaquático são bastante diferentes das aplicações ao ar livre, mas estas proporcionam uma framework teórica bastante sólida, a partir da qual se pode desenvolver um trabalho conciso e objetivo para a propagação não linear em espaço aberto. As equações que exprimem a propagação não linear de ondas acústicas são bastante similares com a equação geral da propagação de ondas, excetuando do facto de nestes casos não se descartar os termos não-lineares.

#### 2.2.1- Equação padrão

Nesta equação é estabelecida a relação entre a pressão P, a densidade ( $\rho$ ) e a entropia (s). Para um fluido em geral, a pressão em função da densidade e entropia é não linear, pelo que pode ser definida numa série de Taylor num ambiente isotrópico de pressão ambiente (P0).

$$P = P(\rho, s) \tag{4}$$

$$P = P_0 + \left(\frac{\partial P}{\partial \rho}\right)_{s,0} (\rho - \rho_0) + \frac{1}{2!} \left(\frac{\partial^2 P}{\partial \rho^2}\right)_{s,0} (\rho - \rho_0)^2 + \cdots$$

(5)

A pressão e a densidade caracterizam-se por:

$$p = P - P_0 \tag{6}$$

$$\rho' = \rho - \rho_0 \tag{7}$$

Fazendo a substituição:

$$p = A\left(\frac{\rho'}{\rho_0}\right) + \frac{B}{2!} \left(\frac{\rho'}{\rho_0}\right)^2 + \frac{C}{3!} \left(\frac{\rho'}{\rho_0}\right)^3 + \cdots, \tag{8}$$

Onde:

$$A = \left(\frac{\partial P}{\partial \rho}\right)_{s,0} \tag{9}$$

$$B = \partial_0^2 \left( \frac{\partial^2 P}{\partial \rho^2} \right)_{s,0} \tag{10}$$

$$C = \partial_0^3 \left( \frac{\partial^3 P}{\partial \rho^3} \right)_{s,0} \tag{11}$$

A velocidade do som num fluido isotrópico é definida da seguinte forma:

$$c^{2} \left(\frac{\partial P}{\partial \rho}\right)_{s} = \left(\frac{\partial P}{\partial \rho}\right)_{s,0} + \left(\frac{\partial^{2} P}{\partial \rho^{2}}\right)_{s,0} (\rho - \rho_{0}) + \frac{1}{2!} \left(\frac{\partial^{3} P}{\partial \rho^{3}}\right)_{s,0} (\rho - \rho_{0})^{2} + \cdots$$

$$= c_{0}^{2} + B \frac{\rho'}{\rho_{0}^{2}} + \frac{C}{2} \frac{{\rho'}^{2}}{\rho_{0}^{3}}$$

(12)

Depois de efetuar a raiz quadrada, a expansão binominal permite achar uma solução para c:

$$\frac{c}{c_0} = 1 + \frac{B}{2} \left( \frac{\rho'}{\rho_0} \right) + \frac{1}{4} \left[ \frac{C}{A} - \frac{1}{2} \left( \frac{B}{A} \right)^2 \right] \left( \frac{\rho'}{\rho_0} \right)^2 + \cdots$$

(13)

Onde  $c_0$  é a velocidade de uma onda no ambiente, e é igual a  $\sqrt{A/

ho_0}$

Caso a densidade seja assumida como pequena perante a densidade do ar, os termos contendo os termos quadráticos superiores a  $\left(\frac{\rho'}{\rho_0}\right)$  podem ser omitidos. Para uma onda plana esta aproximação permite afirmar que  $u\ll c_0$ , em que u é a velocidade da partícula, ou equivalentemente  $p\ll \rho_0 c_0^2\approx 197dB~SPL$ . Pelo que para um gás diatómico isotrópico como o ar a equação de estado pode ser escrita diretamente como:

$$p = P_0 \left(\frac{\rho}{\rho_0}\right)^{\gamma} \tag{14}$$

Em que  $\gamma = \frac{c_p}{c_v}$  é a razão de diferentes temperaturas. No ar  $\gamma = 1,4$ , logo

$$\frac{c}{c_0} = 1 + \frac{\gamma - 1}{2} \left( \frac{\rho'}{\rho_0} \right) \tag{15}$$

#### 2.2.2-Equação de Continuidade

Para um cubo de ar estacionário de volume dV, área de face dA e comprimento de aresta dx, a taxa de massa de ar que flui para dentro do cubo ao longo do eixo x, menos a taxa de massa de ar que flui para fora é igual à taxa de aumento da massa de ar dentro do volume:

$$dV \frac{\partial \rho}{\partial t} = \rho u dA - \rho u|_{x+dx} dA$$

$$= \left[ \rho u - \rho u - \frac{\partial (\rho u)}{\partial x} dx \right] dA$$

$$= \frac{\partial (\rho u)}{\partial x} dV$$

(16)

Combinando as três dimensões espaciais e cancelando dV têm-se o seguinte resultado:

$$\frac{\partial \rho}{\partial t} + \nabla \cdot (\rho \vec{u}) = 0 \tag{17}$$

#### 2.2.3 - Equação de Euler

Considerando o volume do ar dV, de massa dm, é sabido a partir da segunda equação de Newton F=ma

Após alguma manipulação matemática obtém-se:

$$d\vec{f} = \vec{a}dm = dPd\vec{A}$$

- A pressão no lado esquerdo do volume é de P.

- A pressão no lado direito do volume é de  $P + \frac{\partial \rho}{\partial x} dx$

Fazendo com que a força resultante seja caracterizada pela seguinte expressão:

$$d\vec{f} = -\frac{\partial \rho}{\partial x}dV \tag{18}$$

A expressão a três dimensões toma a seguinte forma:

$$d\vec{f} = -\nabla P dV \tag{19}$$

Já a aceleração do volume de ar pode ser escrita da seguinte forma:

$$\vec{a} = \frac{d\vec{u}}{dt} = \lim_{dt \to 0} \frac{\vec{u}_1 - \vec{u}_0}{dt} \tag{20}$$

Onde:

$$\vec{u}_1 = \vec{u}_0 + \frac{\partial \vec{u}}{\partial x} u_x dt + \frac{\partial \vec{u}}{\partial y} u_y dt + \frac{\partial \vec{u}}{\partial z} u_z dt + \frac{\partial \vec{u}}{\partial t} dt$$

(21)

Em que:

$$\frac{\partial \vec{u}}{\partial x} u_x dt + \frac{\partial \vec{u}}{\partial y} u_y dt + \frac{\partial \vec{u}}{\partial z} u_z dt = (\vec{u}.\nabla) \vec{u} dt$$

(22)

Pelo que a aceleração da massa de ar corresponde a:

$$\vec{a} = \frac{\partial \vec{u}}{\partial x} + (\vec{u}.\nabla)\vec{u}$$

Que substituindo pela equação de força dá:

$$d\vec{f} = \vec{a}dm = \vec{a}\rho dV$$

E a equação de Euler transforma-se em:

$$-\nabla \mathbf{p} = \rho \left[ \frac{\partial \vec{u}}{\partial x} + (\vec{u}.\nabla)\vec{u} \right]$$

(23)

#### 2.2.4-Combinando as equações

A este ponto da derivação da equação linear de onda os termos não lineares como  $(\vec{u}.\nabla)\vec{u}$  são também eles linearizados e a equação final é simplificada para:

$$\nabla^2 p = \frac{1}{c_0^2} \frac{\partial^2 \mathbf{p}}{\partial t^2} \tag{24}$$

Como os termos não lineares são necessários, e a não linearidade é fraca, é necessário um método perturbativo de forma a nos aproximarmos de uma solução realista. Caso as perturbações no som tenha um µ pequeno,

$$\frac{\rho'}{\rho_0} \sim \frac{p'}{p_0} \sim \frac{u}{c_0} \sim \mu \tag{25}$$

Ao serem consideradas as ondas ao longo do eixo dos x's, pode ser escrita uma função de propagação arbitrária F em termos de  $t-\frac{x}{c_0}$

$$\rho', u_x, p = F\left(t - \frac{x}{c_0}\right) \tag{26}$$

A forma da onda é alterada pelas não linearidades enquanto percorre o meio ambiente, em ambas as direções, transversal e axial. Existe uma relação direta da alteração da forma de onda com a difração e as não linearidades:

- Transformações axiais: Não linearidades.

- Transformações transversais: Difração.

Caso seja assumido que as alterações transversais são mais acentuadas que as axiais a solução da equação de onda assume a seguinte forma:

$$\rho', u_{x}, p' = \varphi\left(t - \frac{x}{c_0}, \mu x, \sqrt{\mu y}\right)$$

(27)

Os argumentos podem ser definidos da seguinte forma:

$$\tau = t - \frac{x}{c_0}, \mathbf{x}' = u\mathbf{x}, \mathbf{y}' = \sqrt{\mu \mathbf{y}}$$

(28)

Ao se efetuar as definições acima indicadas as derivadas parciais são automaticamente simplificadas para:

$$\frac{\partial \rho'}{\partial x'} \sim \frac{\partial u_x}{\partial x'} \sim \frac{\partial p'}{\partial x'} \sim \mu^2, \frac{\partial \rho'}{\partial y'} \sim \frac{\partial u_y}{\partial y'} \sim \frac{\partial p'}{\partial y'} \sim \mu^{3/2}, \mu^y \sim \frac{\partial u_x}{\partial y} \sim \mu^{3/2}$$

Quando as últimas equações são combinadas, os elementos de menor ordem  $O(\sqrt{\mu}), O(\mu), O(\mu^2)$

Podem ser combinados, e os de ordem mais elevada podem ser descartados. Depois de muita manipulação nas equações chega-se a uma equação final, de nome KZK (Khokhlov, Zabolotskaya, e Kuznetsov)[18].

$$\frac{\partial^2 p}{\partial z \partial \tau} = \frac{c_0}{2} \nabla_r^2 p + \frac{\delta}{2c_0^3} \frac{\partial^3 p}{\partial \tau^3} + \frac{\beta}{2\rho_0 c_0^3} \frac{\partial^2 p^2}{\partial \tau^2}$$

(29)

Esta equação é uma boa aproximação para feixes de som direcionais ao longo do eixo.

# 2.3 - Modulação e desmodulação de feixes de ultrassons direcionáveis para a transmissão e renderização de áudio

A modulação em amplitude teve sempre um papel vital no estudo dos parametric arrays. Dentro dos esquemas de modulação em amplitude, o DSB [3] é um dos mais simples de perceber e implementar.

Este tipo de modulação é alcançando multiplicando uma portadora sinusoidal pelo sinal que contém a informação, que no nosso caso é um sinal áudio. O seu espectro é composto por duas bandas laterais, simétricas em relação à frequência da portadora. A envolvente da modulação AM é o sinal de áudio propriamente dito, sendo que o recetor do sinal modelado em AM é simplesmente um detetor de envolvente. Neste ponto podem-se inferir dois pontos:

Primeiro que tudo é aceitável usar o trabalho de Berktay's baseado na envolvente do sinal de forma a ter um modelo básico para calcular a pressão, pois no AMa envolvente é a diferença de pressão.

Em segundo lugar, e mais importante é o facto das interações não lineares acontecerem entre ambos os componentes de frequências do esquema de modulação AM causando distorção.

Neste tipo de modulação estão presentes dois tipos de distorção.

Distorção intra-sideband causada pelos efeitos da subtração dos diferentes componentes em frequência.

Distorção inter-sideband causada pela interação entre as componentes presentes em ambas as bandas laterais.

Neste último caso as duas bandas laterais interagem uma com a outra causando os efeitos indesejáveis da distorção. Este tipo de distorção pode ser reduzida si gnificativamente. Kite et al propôs um algoritmo de pré-processamento que reduz de forma viável a distorção intersideband, e é o que é usado na maioria das aplicações em uso hoje em dia. Este algoritmo é baseado no trabalho de Bertkay's, sendo que o que faz é aplicar a operação oposta presente no modelo de Bertkay's.

De acordo com o modelo, uma onda colimada é consistida pela seguinte pressão de uma onda modelada em amplitude:

$$p_1(t) = P_1 E(t) \sin(\omega_c) \tag{30}$$

Em que:

$P_1$ : Amplitude da portadora

E(t): A envolvente modulante

$\omega_c$ : A frequência angular da portadora

Consequentemente o sinal depois de desmodulado através do fenómeno da não linearidade vai ser transformado num som audível com a seguinte expressão:

$$p_d(t) = \frac{\beta P_1^2 A}{16\pi \rho_0 c_0^4 z \alpha} \frac{\partial^2}{\partial t^2} E^2(\tau)$$

(31)

Em que:

$\beta = (\gamma + 1)$ : Coeficiente de não linearidade  $\beta_{ar}$ =1,2

γ: Razão de temperaturas

A : Área de radiação do transdutor

$\rho_0$ : Densidade do ar

$c_0$ : Velocidade do sinal a transmitir

z : Distância axial

lpha: Coeficiente de absorção do ar para a portadora

A expressão mostra a dependência da pressão do sinal de áudio desmodulado com a envolvente do sinal modelado em amplitude. A envolvente é por definição um sinal em banda de base. Esta expressão apresentada por Pompei é uma adaptação do modelo para colunas em parametric arrays de Berktay's, onde o sinal modelado é um sinal de áudio. Mais uma vez é referido o trabalho de Pompei, pois este foi um dos poucos e primeiros produtos comerciais a ser

desenvolvido. O modelo baseia-se no estudo de Bertkay's, na modulação AM e no algoritmo de Kite's. O algoritmo de pré-processamento de Kite's aplica um integral duplo de forma a compensar a derivada de segundo grau e uma raiz quadrada para compensar as não linearidades quadráticas no modelo de Bertkay's. A portadora é multiplicada pelo sinal de áudio pré-processado. Ao serem aplicados sequencialmente, o algoritmo de Kite's e a solução de Bertkay's permite que na saída esteja presente uma boa atenuação na banda lateral inferior do espectro AM devido à dupla derivação e dupla integração. Pelo que o pré-processamento de Kite's reduz significativamente a distorção inter-sideband.

Pensando neste modelo salta á vista que a melhor solução a adotar de forma a reduzir a distorção inter-sideband é aplicar o esquema de modulação single side band (SSB), que tem como característica principal o facto de o seu espectro apresentar somente uma banda lateral. Aqui pode ser escolhida tanto a Lower Sideband (LSB) como a Upper Sideband (USB). O padrão do SSB usado em telecomunicações é supress carrier (SC), mas no caso das aplicações por parametric array é necessário usar a portadora para que seja possível gerar as diferenças nas frequências no sinal de áudio. Este tipo de modulação é designada por sinal SSB-WC (singlesideband with carrier) que significa que é adicionada a portadora por via acústica ou elétrica, depois de ser efetuada a modulação SSB padrão. Ao se ter somente uma banda lateral, não é necessário ter em conta a distorção inter-baseband, pelo que doravante não é necessário recorrer ao pré-processamento de Kite's. Somando ao facto que este modelo de modulação AM permite uma maior versatilidade dado ao facto que se pode escolher uma das duas bandas laterais atendendo às características do equipamento, e á resposta em frequência do transdutor, assim como à absorção do canal de transmissão. Uma vantagem visível deste modelo é também o facto de este usar de forma mais eficiente a largura de banda disponível dado somente usar-se uma banda lateral.

#### 2.4 - Distorção em sistemas de ultrassons

Como já foi mencionado anteriormente, a distorção é uma variável muito presente nos sistemas de ultrassons. No capítulo anterior, que aborda os processos de modulação e desmodulação, foi referido o facto das interações não lineares acontecerem entre ambos os componentes de frequências do esquema de modulação AM causando dois tipos de distorção.

Distorção intra-sideband causada pelos efeitos da subtração dos diferentes componentes em frequência.

Distorção inter-sideband causada pela interação entre as componentes presentes em ambas as bandas laterais.

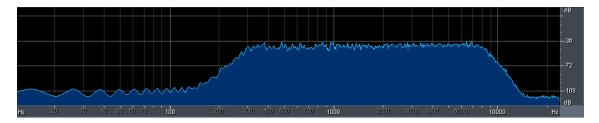

Para além da distorção causada pela modulação, um dos desafios mais preeminentes das operações envolvendo operações quadráticas é o facto que estas introduzem harmónicos no sinal, aumentando a largura de banda exponencialmente como nos mostra a figura que se segue. Quando o sinal é modelado com ultrassons o sistema de reprodução tem de reproduzir de forma fiável a largura de banda de todo o sinal da forma mais precisa possível, pelo que limitações na largura de banda, ou mesmo não uniformidades na resposta em frequência ultrassónica vão levar a um aumento na distorção.

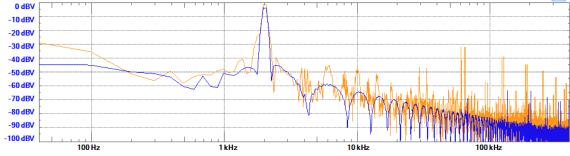

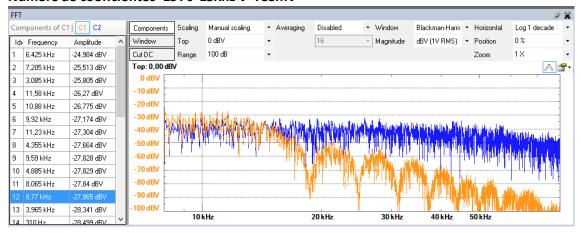

Figura 1: A Azul temos o sinal antes de ser processado e a lilás o sinal pós processado.

Figura 2: Azul - Sinal de entrada Lilás - Sinal processado

Para além dos fatores geradores de ruído, mencionados anteriormente, há que ter em conta a atenuação associada a frequências elevadas e as características do ambiente que contribuem significativamente para a redução da potência efetiva da propagação e reprodução do sinal.

O figura que se segue ilustra a relação existente entre a frequência do som e a atenuação num ambiente a 20 graus Celsius. Como se pode verificar, quanto mais elevada a frequência, maior a atenuação, o que faz com que se tenha de ter este parâmetro em conta. Para além disso a humidade também vai influenciar a propagação do som, como se pode verificar. Em termos práticos, verifica-se que para uma frequência de 50Khz, e com uma humidade relativa de 40%, a 1 atmosfera de pressão, temos uma atenuação de 1dB a cada metro, o que por si só já é um valor bastante significativo, tendo em conta que o gráfico não conta com a atenuação provocada pela desmodulação do sinal de ultrassons para som audivel.

Figura 3:Atenuação do sinal ultrassónico

#### 2.5 - Metodologia de redução da distorção do trabalho prático

Assumindo o campo distante, foi mostrado que:

$$p_{2(x,0,\tau)} = \propto \frac{d^2}{d\tau^2} E^2(\tau)$$

(32)

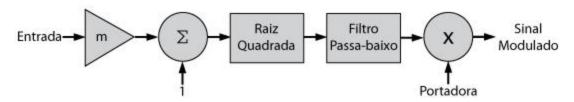

Assim sendo, para reproduzir um sinal de áudio g(t), a solução mais simples é apenas efetuar o integral duplo e a raiz quadrada[11] antes de modular:

$$E(t) = \left(1 + m \iint g(t)dt^2\right)^{\frac{1}{2}} \tag{33}$$

O fator m corresponde à modulação. Caso o sinal modulado  $E(t)sinw_ct$  seja transmitido precisamente, o sinal desmodulado vai ser um sinal áudio livre de distorção, mas de facto, transmitir um sinal áudio modelado com ultrassons não é uma tarefa simples para sistemas tradicionais, em particular dado ao facto da largura de banda disponibilizada pelos transdutores ser limitada, o que pode levar a níveis de distorção extremamente elevados.

## Capítulo 3: Metodologia e Dados

Neste capítulo vão ser abordados os métodos e processos de trabalho usados na parte prática da dissertação.

#### 3.1 - Metodologia processual

O processo de desenvolvimento que foi seguido está descrito no modelo que se segue.

Figura 4: Processo de desenvolvimentos dos sistemas.

O planeamento conceptual vai consistir na definição das arquiteturas a ser implementadas. Este ponto vai ser decisivo na escolha das parametrizações a seguir. Eventualmente e dada a forma como os problemas técnicos foram surgindo, foram havendo ligeiras alterações na forma como as arquiteturas foram sendo seguidas. Um exemplo é que inicialmente na implementação no DSP tanto na primeira como na segunda arquitetura eram para ser realizados testes sobre a banda lateral inferior e superior, mas dado ao facto da banda lateral superior ter mais ruído e a banda reduzida (8kHz), somente foram avaliadas as bandas inferiores. Seguidamente passa-se à simulação dos modelos em Matlab. A partir deste ponto o modelo vai ser repetido por duas vezes; uma para o DSP e outra para a FPGA como demonstra o diagrama de blocos. Os dois passos seguintes na prática acabam por ser um só, pois à medida que se foi desenvolvendo o código, este foi sempre testado em modo de debug, de forma a estudar a forma mais eficiente de organizar sua a estrutura.

Por fim foram realizados testes de forma a inferir conclusões acerca das opções tomadas. Os sinais de teste usados consistiram em sinusoides, sinais swept sine e ruído branco filtrado passabaixo com uma frequência de corte de 8Khz e sem filtragem.

#### 3.2 - Planeamento conceptual

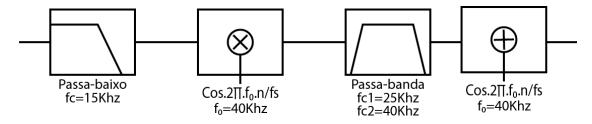

A primeira arquitetura a ser implementada consiste num filtro passa-baixo de 8Khz de forma a somente passarem a frequências correspondentes à fala. Seguidamente o sinal é modelado por uma portadora de 40Khz de forma a 'puxar' o sinal para a gama de ultrassons. Após a modulação o sinal sofre novamente uma filtragem, mas desta vez passa-banda com frequências de corte iguais a:

Fc1: 32KhzFc2: 40Khz

Com esta segunda filtragem fica-se somente com a banda lateral inferior da modulação DSB (double-side-band). Depois deste passo, e dado ao facto que este sistema implementa uma modulação DSB-WC (double-side-band with carrier) falta somente adicionar a portadora ao sinal filtrado. A portadora deve, por norma, ter mais 10dB de potência que o sinal filtrado. A próxima imagem ilustra o diagrama de blocos deste sistema.

Figura 5: Primeira arquitetura - Sistema DSB-WC

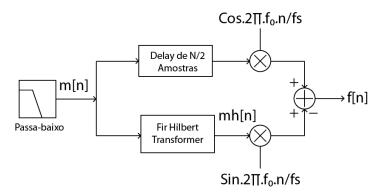

A segunda arquitetura do sistema vai consistir em um filtro passa-baixo que vai ter como frequência de corte 8Khz de forma a só passarem as frequências correspondentes à fala, depois o sinal vai tomar dois caminhos distintos, em que num deles vai passar pelo filtro de Hilbert, e no outro vai ser atrasado N vezes correspondentes a metade do número de coeficientes do filtro de Hilbert de forma a sincronizar as amostras. Seguidamente o sinal no troço onde sofre o atraso é multiplicado por uma portadora com um cosseno a 40Khz, enquanto no troço onde sofre a transformação de Hilbert, o sinal é multiplicado por uma portadora com um seno também ele a 40Khz. Depois de ter ambos os troços concluídos, ambos podem sofrer uma, das duas operações:

- Soma: Caso se queira ter a banda superior.

- Subtração: Caso se queira ter a banda inferior.

Finalmente, o sinal já somado, ou subtraído vai sofrer uma filtragem passa-banda, em que vão ser retiradas as frequências compreendidas entre os 40Khz e os 48Khz.

A imagem que se segue ilustra a arquitetura do sistema num diagrama de blocos de forma a simplificar a compreensão do sistema.

Figura 6: Segunda arquitetura SSB.

#### 3.3 - Implementação do sistema de ultrassons em Matlab

A partir deste momento começa a descrição da execução técnica do trabalho. O primeiro ponto é implementar as várias arquiteturas em Matlab, de forma a se visualizar a resposta do sistema. Na implementação do scripts de simulação do sistema de áudio spotligth da segunda arquitetura, que envolve a filtragem de Hilbert, foi evitado o uso de objetos disponibilizados no Matlab (do tipo filter por exemplo), dado ao facto de se querer aproximar o código do script o máximo possível com o código a implementar nos sistemas em ambas as plataformas, especialmente no DSP.

#### 3.4.1 - Arquitetura 1 – SSB – WC (Filtro passa-banda)

De forma a testar o sistema de áudio spotlight, inicialmente foram criados dois scripts em Matlab para decidir de forma antecipada quais os melhores caminhos a seguir para as duas arquiteturas. Primeiro foi implementada a arquitetura DSB-WC e por fim a arquitetura SSB-WC. Esta foi também uma forma de ter um primeiro contacto com os arrays parametric. O código da aplicação foi o seguinte:

```

format long;

clear all;

close all;

A1 = 2; f1 = 2000; p1 = 0;

% Amplitude, Frequência e fase do sinal

modulante

A2 = 4; f2 = 40000; p2 = 0;

% Amplitude, Frequência e fase da

Portadora

% Frequência de amostragem

Fs = 128000;

t = 0: 1/250000 : 1;

% Janela temporal.

sinalAudio = A1*sin(2*pi*f1*t + p1); % Sinal modulante

portadora = A2*sin(2*pi*f2*t + p2); % Portadora

sinalModelado = sinalAudio.*portadora;

% DSB-SC

sinalModeladoPortadora = sinalModelado + portadora;

% DSB-WC

order=63;

% Ordem

Fn=Fs/2;

% Frequência de Nyquist

w1=32000/Fn;

% Frequência de corte inferior normalizada

wu=40000/Fn;

% Frequência de corte Superior normalizada

wc=[wl,wu];

% Vetor das frequências de corte

b=fir1(order,wc);

% coeficientes do filtro

```

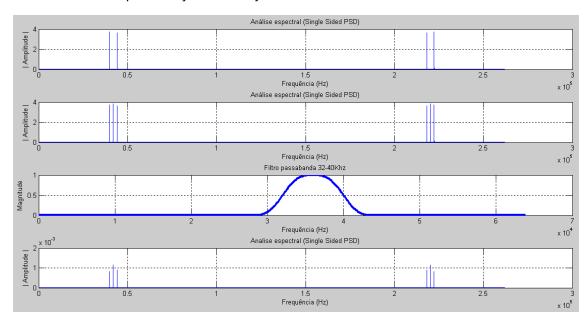

O resultado da implementação foi a imagem que se segue. A captura foi dividida e quatro frames distintas de forma a compreender os processos envolvidos na simulação. Na primeira imagem temos a modulação DSB-SC, na segunda imagem foi adicionada a portadora de forma a obter a modulação SSB-WC, necessária para a implementação deste sistema.

A imagem seguinte ilustra o filtro passa-banda realizado, de forma a visualizar as suas frequências de corte. Nesta primeira simulação as frequências de corte usadas foram as correspondentes à banda lateral inferior compreendidas entre:

Fc1: 32KhzFc2:40Khz

Por fim temos a representação do sinal já filtrado.

Figura 7: Captura da aplicação de ultrassons gerada em Matlab.

O excerto de código de Matlab não contém a programação para gerar as visualizações de forma a deixar somente o código que à posteriori vai ser implementado no DSP e também para tornar a percepção do código mais intuitiva. O som gerado correspondeu às expectativas, apresentando um elevado grau de directividade, e um nível de potência sonora bastante razoável, com um nível de distorção praticamente omisso.

#### 3.4.2 - Arquitetura 2 - SSB - WC (Filtragem de Hilbert)

```

N = 100000;

fs = 192000;

%Frequência de amostragem

t = (0:N-1)/fs;

fm1 = 5000; Em1 = 2; m1 = Em1*cos(2*pi*fm1*t); % Componente 1 da

fm2 = 10000; Em2 = 2; m2 = Em2*cos(2*pi*fm2*t); % Componente 2 da

mensagem

m = m1 + m2;

% Mensagem

fc = 40000; portadora = 5*cos(2*pi*fc*t); %Frequência da portadora

d = fdesign.hilbert(50,0.1);

hd = design(d,'firls');

coef = hd.Numerator;

j=1;

xv = zeros(size(m));

xz = zeros(size(m));

NZEROS = length(coef);

tempo = 1;

hilbertDelay = zeros(size(m));

while(tempo <= N)</pre>

for ii = 1 : NZEROS

xv(ii) = xv(ii+1);

xv(NZEROS) = m(tempo);

sum = 0.0;

for k = 1: NZEROS

sum = sum + (coef(k) * xv(k));

end;

mh (tempo) = sum;

for ii = 1 : N-1

hilbertDelay(ii) = hilbertDelay(ii+1);

end;

hilbertDelay(NZEROS) = m(tempo);

filterDelay = round(NZEROS/2);

x1(tempo) = hilbertDelay( filterDelay ).*2.*cos(2*pi*fc*t(tempo));

x2 \text{ (tempo)} = mh \text{ (tempo)} .*2.*sin (2*pi*fc*t (tempo));

sbl(tempo) = x1(tempo) - x2(tempo);

sbu(tempo) = x1(tempo) + x2(tempo);

sinalModeladoPortadora(tempo)=sbu(tempo)+portadora(tempo); %DSB-WC

tempo = tempo + 1;

order=63; % Ordem

Fn=fs/2; % Frequé

Fn=fs/2; % Frequência de Nyquist

wl=40000/Fn; % Frequência de corte inferior normalizada

wu=60000/Fn; % Frequência de corte Superior normalizada

wc=[wl,wu]; % Vetor das frequências de corte

b=fir1(order,wc); % Coeficientes do filtro

sinalModeladoPortadoraFiltrado = filter(b,1,sinalModeladoPortadora);

%-----

ultrassons = audioplayer(sinalModeladoPortadoraFiltrado,fs);

play(ultrassons)

```

# Capítulo 4 - Implementação do sistema na FPGA

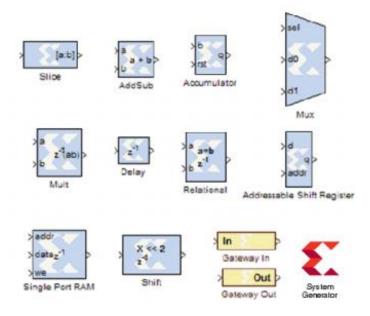

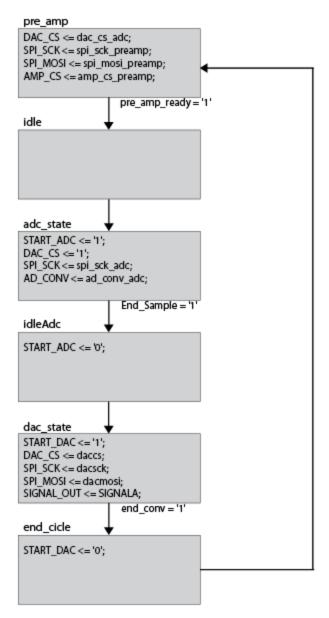

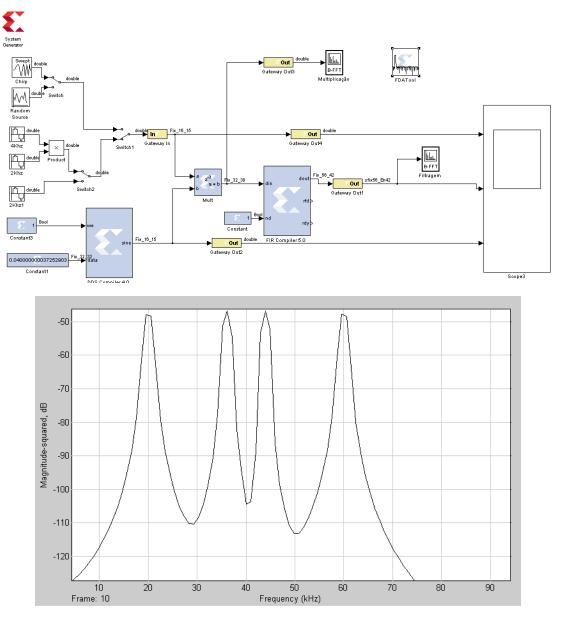

Como foi referido anteriormente, o sistema de som direcionado foi inicialmente implementado na FPGA Spartan 3E. Para tal foram usadas as ferramentas da XILINX, especialmente o ISE, e complementarmente também foi usada a ferramenta de simulação Sysgen, disponibilizada pelo MATLAB, que contém componentes nas suas livrarias que virtualizam vários módulos de hardware para serem implementados na FPGA. Dentro deste rol de componentes temos a livraria DSP, que disponibiliza cerca de 90 blocos de hardware virtualizados que podem ser adicionados ao Simulink. A imagem que se segue ilustra alguns dos componentes disponibilizados pela livraria DSP da ferramenta Sysgen.

Figura 8:Block set DSP do Sysgen

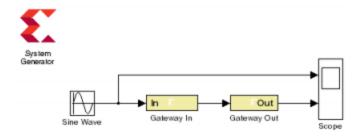

A ferramenta, para além de poder simular o sistema a implementar na FPGA, com componentes que posteriormente são exportados para a FPGA, tem a capacidade de criar simulações aceleradas através da co-simulação com o hardware. Este processo de simulação é possível dado ao facto da ferramenta Sysgen, através do System Generator, conseguir criar uma simulação captada no Simulink com o Xilinx DSP blockset que vai correr na plataforma de Hardware suportada, que no nosso caso é a Spartan 3E. Este tipo de sistema contém quatro componentes fundamentais para ser implementado

Figura 9: Configuração inicial no Sysgen

Token System Generator: Este componente é um membro constituinte da livraria de módulos disponibilizado para o Simulink, e tem de estar presente em todos os modelos desenhados de forma a ser possível simular e traduzir essa mesma simulação para Hardware. No caso do sistema gerado para a simulação do sistema de ultrassons, foi somente usado um token, e todos os módulos de hardware presentes na simulação estão ligados a este componente, pois é aqui que é configurado o Simulink System Period, assim como o tipo de FPGA, e a linguagem de descrição do hardware (VHDL ou Verilog)

Figura 10:Token System Generator

Gateway In: A ligação entre os componentes Xilinx e os restantes componentes presentes no Simulink é feita através dos componentes de gateway. O Gateway In converte os sinais double para sinais Xilinx. Dentro deste bloco pode ser configurado o número de bits envolvidos na conversão. No caso da simulação de ultrassons, e devido ao número de bits prese ntes no ADC e no DAC da FPGA, foram configurados 12 BITS.

Gateway Out: Este componente converte o sinal Xilinx novamente num sinal double, de forma ao sinal poder operar no ambiente Simulink.

JTAG Co-Sim: Este é o bloco responsável pela co simulação de hardware. O componente interage com a FPGA, automatizando tarefas, como por exemplo, a configuração da FPGA, a transferência de dados, a sincronização, clock, etc.

#### 4.1 - Acondicionamento de sinal

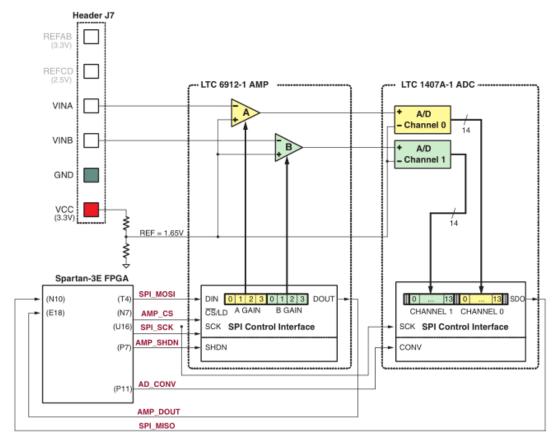

O sinal a transmitir vai ser capturado pelo ADC da FPGA de forma a ser modulado e transmitido em ultrassons. A imagem que se segue mostra o sistema de captura analógica da FPGA.

Figura 11: Sistema de captura analógica.

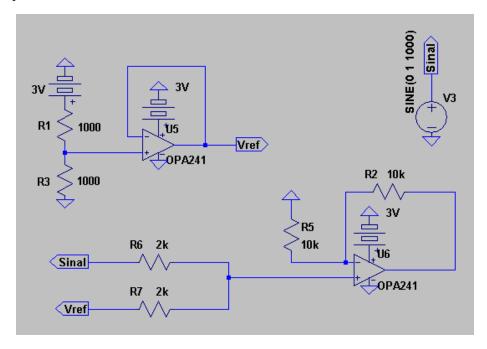

Como se pode verificar o kit da FPGA inclui dois pinos analógicos VINA e VINB que servem de interface com o exterior. Estes canais de captura analógica consistem num pré-amplificador programável (Linear *Technology* LTC6912-1) que amplifica o sinal analógico proveniente das entradas VINA e VINB presentes no conjunto de pinos J7. A saída do pré-amplificador é ligada ao acima referido ADC (Linear Technology LTC1407A-1ADC). Tanto o ganho do pré-amplificador como os sinais de controlo do ADC são definidos digitalmente pela FPGA, utilizando o protoloco de SPI. O ganho do pré-amplificador escolhido para esta aplicação é o (-1), que proporciona uma excursão dos 0,4V até aos 2,9V, ideal para o objetivo final da aplicação. A tensão de referência no ADC é de 1,65V pelo que este valor é subtraído à tensão de entrada em VINA e VINB, tendo em atenção que a excursão máxima de tensão da aplicação do ADC é de ± 1,25V centrados na tensão de referência. De forma a maximizar a performance do ADC é necessário que o sinal de entrada esteja centrado na tensão de referência, e com uma amplitude que vai dos 0,4V até aos 2,9V. Para desenvolver um circuito que permita alcançar estes valores foi realizada uma simulação no LTSPICE. De seguida temos os resultados alcançados.

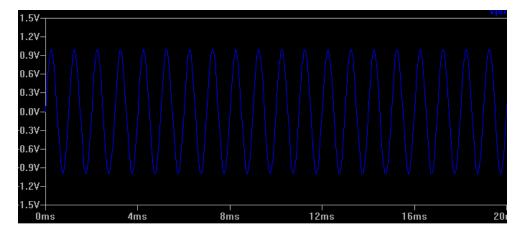

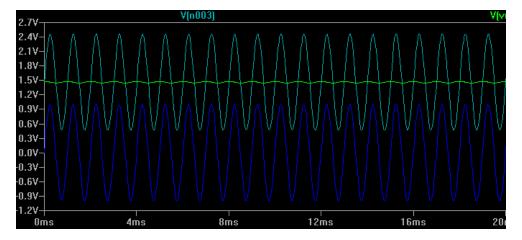

Figura 12: Circuito de acondicionamento de sinal.

Figura 13: Sinal de entrada

Figura 14: Sinal de saída

Figura 15: Sinal de entrada, saída e referência.

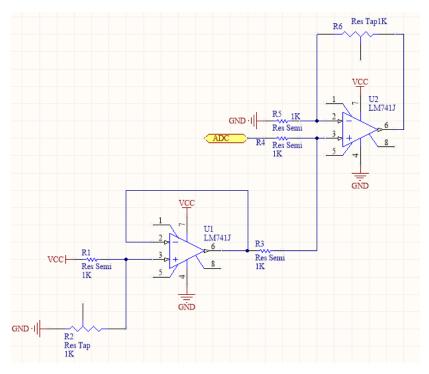

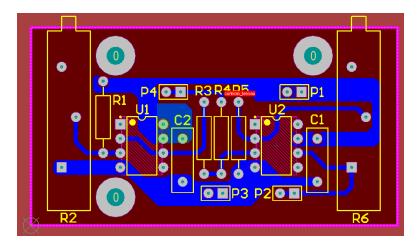

### 4.2 - PCB

Para realizar o acondicionamento de sinal foi criada uma placa PCB no programa Altium de forma a maximizar o sinal com o menor nível de ruido possível.

O programa consiste essencialmente em dois ficheiros:

- O Esquemático Controlo\_tensao.SchDoc

- Ficheiro PCB Controlo\_tensao\_PcbDoc

De seguida temos as imagens dos dois ficheiros:

Figura 16: Controlo\_tensao.SchDoc

Figura 17: controlo\_tensao\_PcbDoc

### 4.3 - Módulo de controlo do ADC-DAC

O módulo de controlo do ADC e do DAC tem por finalidade controlar o sistema de comunicação com o exterior, assente num ADC e num DAC. A comunicação entre a FPGA e o ADC e o DAC fazse através do protocolo SPI (Serial Peripheral Interface) como foi referido anteriormente.

A imagem que se segue ilustra a forma como o módulo atua para controlar o sinal de entrada e o sinal de saída.

Figura 18:Captura no ISIM do sistema de controlo do ADC/DAC

Como se pode verificar pela imagem, os sinais que formam o módulo de controlo do ADC-DAC são os seguintes:

- CLK: Sinal de relógio

- SPI\_SCK: Sinal de relógio do protoloco SPI.

- AD\_CONV: Sinal que controla a captura de amostras analógicas.

- SPI\_MISO: Master Input, Slave Output

- SPI\_MOSI: Master Output, Slave Input

Estes quatro sinais controlam o ciclo de entrada e saída das amostras da FPGA atendendo ao ciclo do ADC e do DAC, enquanto os sinais STARTADC e STARTDAC controlam o processo que está a decorrer no momento, ou seja:

- STARTADC a 1: Indica à máquina de estados que o ADC está a processar uma captura.

- STARTDAC a 1: Indica à máquina de estado que o DAC está a processar uma amostra.

O ADC processa duas amostras de cada vez, uma proveniente do porto VINA e outra proveniente do porto VINB. Cada uma das amostras contém 14 bits no formato complemento para dois. A

trama que contém ambas as amostras é de 34 bits pois no início, meio e fim da trama o canal é colocado em alta impedância durante dois bits de forma a sinalizar o início e fim da trama, ou a entrada de uma amostra do outro porto. A imagem que se segue ilustra a trama do ADC.

Figura 19: Trama do ADC

#### 4.4 - IP CORES

Para desenvolver a aplicação também se recorreu ao uso de IP Cores disponibilizados pela Xilinx. Um IP (Intellectual Property) Core é uma aplicação disponibilizada que realiza uma determinada operação. Também podem ser disponibilizados agregados de IP Cores desenhados com uma determinada especificidade, mas neste trabalho somente vão ser usados IP Cores isolados. Esta livrarias são de extrema importância pois garantem ao utilizador máxima performance do seu hardware, pois são desenhados tendo em conta a FPGA a usar, e permitem diminuir o tempo de execução do projeto.

Os IP Cores usados são os seguintes:

- DDS Compiler

- Multiplier

- CORDIC

#### 4.4.1 - DDS

Um dos componentes críticos dos sistemas DSP é o gerador sinusoidal. A maior parte das vezes recorre-se a uma Look Tablet de forma a colmatar o problema, mas na maior parte das vezes, caso se queira recorrer a uma sinusoide de elevada performance, esta solução mostra-se ineficaz, tornando-se um componente gerador de ruído adicional.

Um dos problemas mais recorrentes, é o facto de ser muito difícil manter baixo o nível de memória consumida num sistema que exija um nível elevado de SFDR (Spurious Free Dynamic Range) que consiste na relação entre a amplitude RMS da frequência portadora e o valor RMS da componente de ruído mais próxima ou do componente de distorção harmônica, assim como também é muito difícil implementar um gerador de sinusoide que tenha um comportamento linear ao nível da geração do ruído a velocidade muito elevadas de relógio.

No caso desta aplicação, é necessário gerar um seno e um cosseno, de elevada performance, de forma a se proceder à modulação AM DSB e SSB. Para tal viu-se que aqui era necessário recorrer

a um IP Core, de forma a se poder alcançar a performance desejada, e adicionalmente se poder alterar os parâmetros de forma simples e igualmente eficaz.

- Este IP Core contém um gerador de fase e uma Lookup Table para Seno e Cosseno.

- O gerador e a Lookup Table pode ser usados individualmente ou em conjunto, tendo opcionalmente recurso a um sistema de dither.

- A Lookup Table pode ser armazenada em RAM distribuída ou RAM em bloco.

- Sistema de dithering de fase, de forma a espalhar a energia linha espectral para um Spurious Free Range Dinâmico (SFDR) mais elevado.

- Opções de correção de ruído usando o mínimo de recursos de FPGA (Phase Dithering ou Taylor series correction).

- Suporte de SFDR desde 18 dB até 150 dB

- 16 Canais independentes multiplexados no tempo.

- Saída em complemento de 2 com sinais de 3 a 26 bits.

### 4.4.2 - Multiplier

A operação multiplicação é usada abundantemente em aplicações DSP, sendo necessário alcançar a máxima eficiência na implementação, de forma a obter os melhores resultados a velocidades de relógio elevadas.

O Multiplicador LogiCORE ™ simplifica este desafio abstraindo as especificidades da FPGA ao mesmo tempo que mantém o desempenho e a eficiência de recursos no máximo exigido. O multiplicador é capaz de gerar multiplicadores paralelos, e os multiplicadores de coeficientes constantes. Este IP Core disponibiliza um sistema de estimativa de recursos instantâneos, pelo que o utilizador pode selecionar rapidamente a solução ótima para o seu sistema.

Este IP fornece um bom controlo sobre a latência (pipelining) dos multiplicadores (puramente combinatória para fully pipeline) e symmetric rounding na slice DSP48. A implementação em fully pipeline permitem um desempenho de frequência de clock máximo

- Multiplicador fixed-point de complemento de 2 signed/unsigned

- Multiplicação paralela ou de coeficiente constante

- Suporta entradas que variam de 1 a 64 bits de largura e saídas que variam de 1 a 128 bits de largura com qualquer parte do produto completo selecionável.

- Suporta arredondamento simétrico ao infinito quando se utiliza o DSP Slice

- Instantânea Estimativa de Recursos

- Relógio opcional Ativar e Synchronous Limpar

- Modelos comportamentais VHDL

- Estimativa de Recursos Instantânea

- Para uso com Catalog Vivado® IP e Xilinx Sistema Gerador para DSP

#### 4.4.3-CORDIC

O CORDIC (coordinate rotational digital computer) é um IP LogiCORE da Xilinx que implementa um algoritmo rotacional de coordenadas generalizado, inicialmente desenvolvido para resolver equações trigonométricas iterativamente, e mais tarde o algoritmo foi generalizado de forma a resolver uma gama mais ampla de equações, incluindo a hiperbólica e equações de raiz quadrada. O IP CORE CORDIC implementa os seguintes tipos de equações:

- Conversão Rectangular <-> Polar

- trigonométrico

- Hiperbólico

- Raiz quadrada

## 4.5-Componentes

A implementação do trabalho assentou na premissa de se tentar tornar o sistema o mais modular possível, de forma a isolar cada uma das ações em módulos diferentes, para que seja mais fácil desenhar e interpretar o sistema, mas também para ser mais intuitivo fazer debug ao sistema.

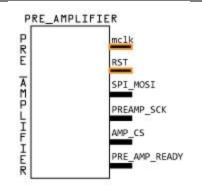

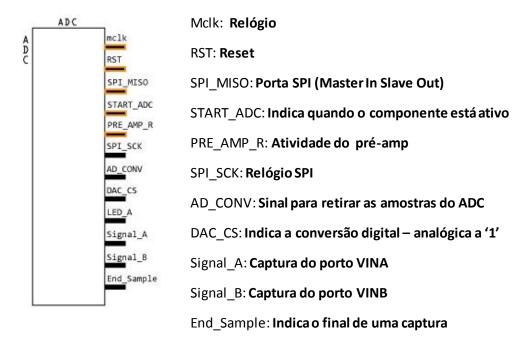

Neste capítulo são enumerados os diferentes componentes que constituem a implementação do sistema de Audio Spotlight. As portas de entrada são referenciadas a amarelo e as saída são referenciadas a preto.

O Componente que se segue tem por final idade amplificar o sinal, antes de este dar entrada no ADC. A arquitetura deste amplificador é Inversor, e o ganho determinado foi de 1. Este componente partilha o meio SPI com o ADC e com o DAC, pelo que a arquitetura teve de ter este ponto em conta, de forma a sincronizar as portas dos respetivos componentes. A sincronização foi realizada através de uma máquina de estados como foi referido anteriormente.

Mclk: Relógio RST: Reset

**SPI\_MOSI:** Porta SPI(Master out Slave In)

PREAMP\_SCK: Relógio SPI

AMP\_CS: A '0' indica que o pre-amplifier está ativo

PRE\_AMP\_READY: Indica quando o componente está ativo

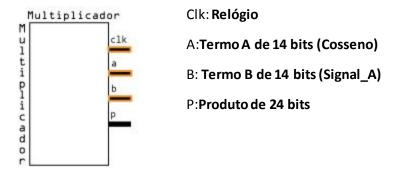

O multiplicador á imagem do componente anterior também é um IP Core. Havia a hipótese de implementar este Core através de LUTS, mas visto que todos os filtros são implementados através da arquitetura Distributed Arithmetic, no final, sobraram alguns multiplicadores, e dado

ao facto que estes têm um tempo de execução mais rápido, optou-se por usar multiplicadores nesta operação.

O próximo componente é o responsável pela comunicação com o exterior. Como foi referido anteriormente, as amostras são capturadas a uma frequência de 222Khz. Atendendo a que a portadora do sistema é de 40Khz, esta frequência de amostragem é suficiente para ter um sistema robusto, com uma boa pureza espectral. Este componente partilha o meio SPI com o Pré-amplificador e com o DAC, como já foi referenciado anteriormente. Este componente está a funcionar com um relógio SPI de 12,5Mhz. A partir desse valor, as amostras começam a ter resultados insatisfatórios.

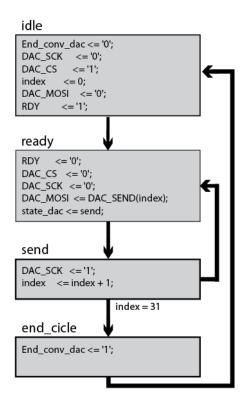

O DAC é o componente responsável por colocar o resultado da operação de modulação e filtragem no exterior. Foi possível colocar este componente a funcionar com um relógio SPI de 25Mhz, que é um valor bastante significativo para um componente desta natureza.

DAC

CLK

RST

DAC\_DATA

START\_DAC

DAC\_MOSI

DAC\_SCK

DAC\_CS

RDY

End\_conv\_dac

CLK: Relógio

RST: Reset

DAC DATA: Dados a ser amostrados

SPI\_MISO: Porta SPI (Master In Slave Out)

START\_DAC: Indica quando o componente está ativo

DAC\_MOSI: Porta SPI (Master Out Slave In)

DAC\_SCK: Relógio SPI

DAC\_CS: Indica a conversão digital – analógica a '1'

RDY: Indica que o DAC pode receber uma amostra

End\_Conv\_dac: indica o final de uma amostragem

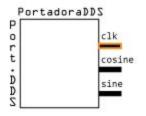

Como foi referido anteriormente, o componente gerador da portadora de 40Khz é um IP Core fornecido pela XIlinx, de nome DDS Compiler 4.0. A opção de usar um core, foi de otimizar o resultado final, e de encurtar significativamente o tempo de implementação do sistema na sua globalidade.

Clk: Relógio

Cosine: Cosseno de 14 bits

Sine: Seno de 14 Bits

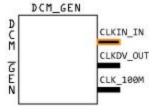

O último IP Core usado na implementação deste sistema foi do gerador de relógio que temos a seguir. A geração deste módulo foi de bastante importância, especialmente porque a única forma de obter um relógio de 100Mhz era através deste componente, é essa frequência é bastante importante, pois os filtros exigem que se use uma frequência de execução 384 vezes superior à frequência de amostragem. Como a frequência de amostragem é de 222Khz, a frequência de execução dos filtros terá de ser superior a 85,248Mhz.

CLK\_IN: Relógio (50Mhz)

CLKDV\_OUT: Sinal de relógio (25 Mhz)

CLK 100M: Sinal de relógio (100 Mhz)

O módulo que se segue tem por finalidade gerar uma frequência de relógio de 220Khz de forma a termos as operações a decorrerem com uma velocidade semelhante em todos os módulos. A ter em conta que a frequência de amostragem é de 222Khz, mas não existe problema, pois o valor das amostras é guardada num registo, e a operação de modulação vai buscar o valor a esse registo a uma frequência de 220Khz.

CLK\_DIVIDER

CLK\_in

reset

Clk\_out

divide\_value

E

Clk\_in: Relógio

reset: Reset

clk\_out: Sinal de relógio

divide\_value: Inteiro que indica metade do período em

ciclos de relógio.

O Componente que se segue é responsável por realizar a filtragem de Hilbert, de forma a se poder realizar a modulação SSB. Como se pode verificar o módulo tem duas saídas a I e a Q, e para obter a modulação SSB multiplica-se a saída I por uma portadora em forma de seno a 40Khz e a saída Q por uma portadora cosseno também ela a 40Khz. Depois de realizar essa operação basta somar ambos componentes para se obter a zona espetral superior ou subtrair ambas as componentes para obter a zona espetral inferior da modulação.

Clk i: Relógio

Rst i: Reset

Data i: Entrada de dados de 14 bits

Data\_str\_i: Entrada de dados de 14 bits

Data i o: Saída de dados filtrados em fase

Data\_i\_q: Saída de dados filtrados em quadratura

Data\_str\_o: Entrada de dados de 14 bits

O proximo componente é o filtro passa-banda. Vão haver duas aplicações distintas, em que o fator de distinção é exatamente este filtro, pois um vai filtrar a banda lateral inferior da modelação DSB e a outra aplicação vai filtrar a banda lateral superior de forma a alcançar a modelação SSB ao se ficar somente com uma banda lateral.

RST: Reset

FSCLK: Relogio (Frequência de amostragem)

D IN: Entrada de dados de 14 bits

MCLK: Relogio Minimo de 384 a Frequência de amostragem

D OUT: Saída de dados filtrados em fase

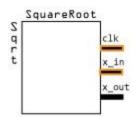

Os componentes que se seguem realizam as operações necessárias para o tratamento de ruido da aplicação. O componente que se segue recorre também a um IP Core, o CORDIC, que Realiza várias operações através de um rotor algébrico. Entre essas operações está a raiz quadrada, necessária para a redução de distorção nos sistemas de Audio Spotlight.

Clk: Relógio

X\_in:Entrada de dados

X\_out: saída de dados

O componente que se segue realiza a operação de integração. Para tal, este módulo assenta numa arquitetura de moving Integrator, que calcula a área subjacente à onda do sinal.

Clk: Relógio

Clr: Clear

X: Entrada de dado(14 bits)

Y: Saída de dados (14 bits)

O componente que se segue realiza a transformação do sinal de complemento de dois para inteiro.

Clk: Relógio

Reset: Reset

Entrada: Entrada de dados em complemento de dois

Saída: Saída de dados em Unsigned

O componente que se segue realiza a transformação do sinal de inteiro para complemento de dois.

Clk: Relógio

Reset: Reset

Entrada: Entrada de dados em Unsigned

Saída: Saída de dados em complemento de dois

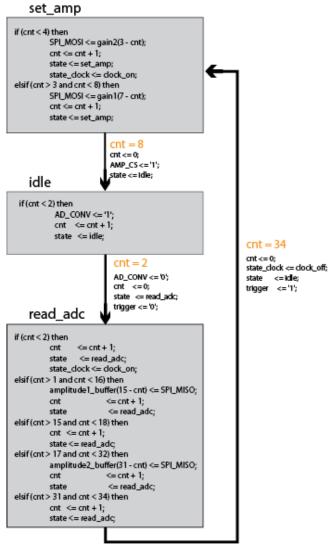

### 4.5.1-Máquina de estados

Na aplicação foram implementadas três máquinas de estados para os seguintes componentes:

ADC, DAC e Top\_Module

A máquina de estados que se segue é referente ao componente ADC. O primeiro estado corresponde à configuração do pré-amplificador. Como se pode verificar são enviados oito bits para a porta SPI\_MOSI que controlam o ganho de cada uma das portas. No segundo estado o sinal AD\_CONV é colocado a '1' de forma a ser retirada uma amostra de cada porta (VINA e VINB). O último estado tem a missão de enviar a tensão já digitalizada (em palavras de 14 bits) de cada uma das portas para o porto SPI\_MISO. Inicialmente enquanto o contador é menor que dois não é enviado bit nenhum, pois a saída é colocada em alta impedância, depois é enviada a tensão da porta VINA, depois a saída é novamente colocada em alta impedância, para de seguida

enviar a tensão da porta VINB.

Figura 20: Máquina de estados do componente ADC.