# COPPER TO COPPER BONDING BY NANO INTERFACES FOR FINE PITCH INTERCONNECTIONS AND THERMAL APPLICATIONS

### A Thesis

Presented to

The Academic faculty

## By

#### **GOPAL CHANDRA JHA**

In Partial Fulfillment

Of the Requirements for the Degree

Master of Science in Materials Science and Engineering

Georgia Institute of Technology

15<sup>th</sup> February 2008

# COPPER TO COPPER BONDING BY NANO INTERFACES FOR FINE PITCH INTERCONNECTIONS AND THERMAL APPLICATIONS

# Approved by:

Prof. Rao R. Tummala, Advisor School of Materials Science and Engineering Georgia Institute of Technology

Prof. C. P. Wong School of Materials Science and Engineering Georgia Institute of Technology

Dr. P. M. Raj School of Mechanical Engineering Georgia Institute of Technology

Date Approved: February 15, 2008

#### **ACKNOWLEDGEMENT**

I wish to record my deep sense of gratitude to all those who have helped me in the successful completion of this project. Firstly, I acknowledge my thesis advisor, Dr. Rao R. Tummala for the problem formulation and objective definition. His guidance and encouragements throughout the research work was a prime motivation for the current work. I also wish to express my gratitude to Dr. C. P. Wong and Dr. P. M. Raj for serving on my reading committee and helping me with valuable suggestions.

Special thanks are due to Dr. P. M. Raj for his continuous support throughout this work. I sincerely acknowledge his valuable suggestions and discussions on the experimental design and results. His incessant encouragement always motivated me to work. My sincere thanks are also due to Dr. J. Gaud, who helped me in synthesizing gold nanoparticles, and without whose support it would have been difficult to finish my work. I also wish to acknowledge Dr. I. Robin for his invaluable help in nanoparticle synthesis. I am also thankful to Dr. Swapan Bhattacharya for his help in getting me started with my research work at Georgia Tech.

I would also like to express my gratitude to several administrators and staffs in the School of Materials Science and Engineering and Microsystems Packaging Research Center. Heartiest thanks to Dr. M. Iyer, Mr. Vanky Sundaram, Dr. Jin Hwang, Dr. Baik-Woo Lee, Dr. Lisa Rosenstein for their input, Mr. Dean Sutter, Ms. Tracy Walden, Ms Patricia Allen, Ms. Tina Turner, Ms. Susan Bowman for their administrative support.

Many thanks are due to all my colleagues including Ganesh, Manish, Gaurav, Aditya, Tapo and Dhanya for making my stay at Georgia Tech a pleasant one. Finally, I am eternally indebted to my family and all my friends without whose love, support, encouragement and well wishes, I could never have accomplished my goal.

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENT                                                           | 3  |

|---------------------------------------------------------------------------|----|

| LIST OF TABLES                                                            | 7  |

| LIST OF FIGURES                                                           | 8  |

| SUMMARY                                                                   | 10 |

| 1. INTRODUCTION                                                           | 1  |

| 1.1 Thermal Challenges in SOP Based Systems                               | 2  |

| 1.1.1 Thermal structures and interface challenges                         | 7  |

| 1.2 Fine Pitch Interconnection Trends and Challenges                      | 9  |

| 1.2.1 Limitations of current chip-to-package interconnection technologies | 11 |

| 1.3 Objective of The Current Research                                     | 13 |

| 1.4 Proposed Approaches                                                   | 14 |

| 1.5 Thesis Outline                                                        | 15 |

| 2. LITERATURE REVIEW                                                      | 17 |

| 2.1 Process Parameters for Thermo-Compression Bonding                     | 26 |

| 2.1.1 Bonding Temperature:                                                | 26 |

| 2.1.2 Post bonding annealing                                              | 27 |

| 2.1.3 Bonding and annealing duration                                      | 27 |

| 2.1.4 Bonding pressure                                                    | 27 |

| 2.1.5 Bonding Environment                                                 | 27 |

| 2.1.6 Surface conditions                                                  | 28 |

| 2.1.7 Bond quality assessment                                             | 28 |

| 2.2 Bonding Mechanisms                                                    | 30 |

| 3. EXPERIMENTS                                                            | 32 |

| 3 1 Nanostructured Spherical Copper Particles                             | 32 |

| 3.1.1 Maskless patterning of copper nanoparticles precursor | 33 |

|-------------------------------------------------------------|----|

| 3.2 Solution Reduction Derived Nanostructured Silver        | 35 |

| 3.3 Wet chemical synthesis of nanostructured Gold           | 37 |

| 3.3.1 Patterning of Gold nanoparticles                      | 38 |

| 3.4 Test Vehicle Fabrication                                | 39 |

| 3.5 Copper to Copper Bonding                                | 40 |

| 3.5.1 Copper bonding using copper precursor solution        | 40 |

| 3.5.2 Copper to copper bonding using silver nanoparticles   | 41 |

| 3.5.3 Copper bonding using gold nanoparticles               | 42 |

| 3.6 Bonding Characterization                                | 42 |

| 3.6.1 X-ray diffraction analysis                            | 42 |

| 3.6.2 Field emission scanning electron microscope           | 43 |

| 3.6.3 Destructive die shear test                            | 43 |

| 4. RESULTS AND DISCUSSIONS                                  | 44 |

| 4.1 Sol-gel Derived Nanostructured Copper                   | 44 |

| 4.2 Silver Nanoparticles Using Solution Reduction           | 53 |

| 4.3 Thin Interface Bonding Using Gold Nanoparticles         | 60 |

| 4.3.1 Patterning of gold nanoparticles                      | 63 |

| 5. CONCLUSIONS                                              | 71 |

| 6. FUTURE RECOMMENDATIONS                                   | 73 |

| 6.1 Void Characterization                                   | 73 |

| 6.2 Electrical characterization                             | 73 |

| 6.3 Thermal characterization                                | 74 |

| REFERENCES                                                  | 75 |

# LIST OF TABLES

| TABLE 1.1 TRANSISTOR AND INTERCONNECT DELAY AT DIFFERENT TECHNOLOGY NODES [9]                           | 10 |

|---------------------------------------------------------------------------------------------------------|----|

| TABLE 2.1 CHRONOLOGICAL LISTING OF IMPORTANT LITERATURES ON COPPER-TO-COPPER BO VARIOUS RESEARCH GROUPS |    |

| TABLE 4.1 BOND STRENGTHS OF COPPER TO COPPER BONDING USING COPPER NANOPARTICLE INTERLAYER               | 52 |

| TABLE 4.2 SHEAR STRENGTH OF COPPER-TO-COPPER BOND USING SILVER NANOPARTICLE INTE                        |    |

| TABLE 4.3 COPPER TO COPPER BOND STRENGTH WITH GOLD NANOPARTICLES INTERLAYER                             | 68 |

# LIST OF FIGURES

|               | POWER SUPPLY VOLTAGE AND MAXIMUM POWER CONSUMPTION IN HIGH-PERFORM PROCESSORS                                                | _  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.2 C  | COMPARISON OF HEAT FLUXES IN VARIOUS PHENOMENA AND SYSTEMS                                                                   | 5  |

| FIGURE 1.3 In | MPACT OF SOP ON THERMAL CHALLENGES                                                                                           | 6  |

| FIGURE 1.4 M  | MAXIMUM ALLOWABLE JUNCTION AND AMBIENT TEMPERATURE AS A FUNCTION OF                                                          |    |

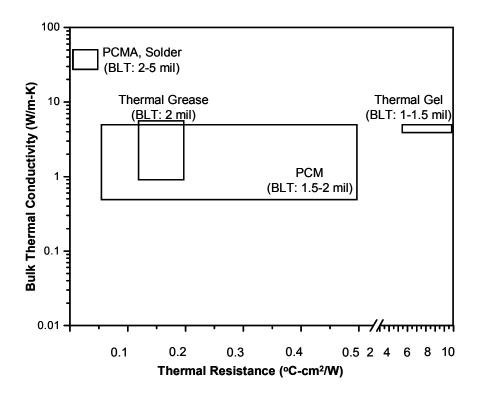

| FIGURE 1.5 T  | RENDS IN THERMAL INTERFACE MATERIALS                                                                                         | 8  |

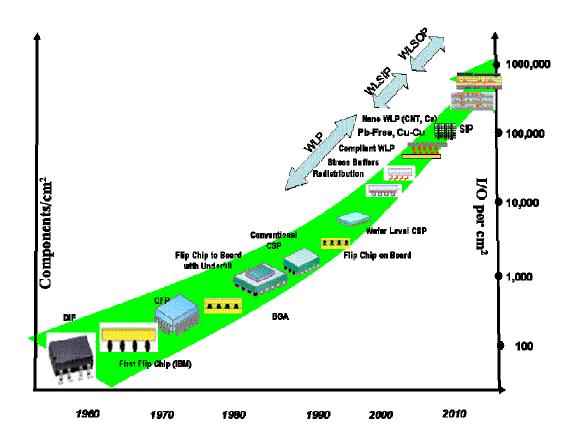

| FIGURE 1.6 C  | CHRONOLOGICAL ADVANCEMENT IN IC PACKAGING                                                                                    | 10 |

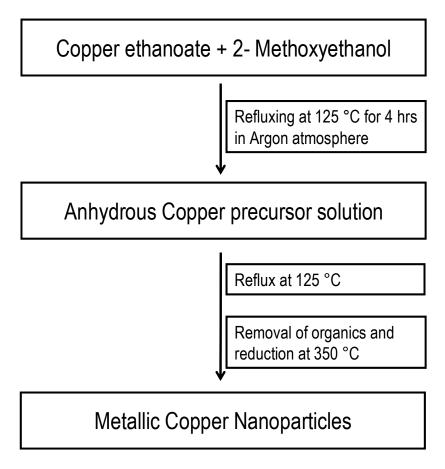

| FIGURE 3.1 S  | SYNTHESIS SCHEME OF SOL GEL DERIVED COPPER NANOPARTICLES                                                                     | 35 |

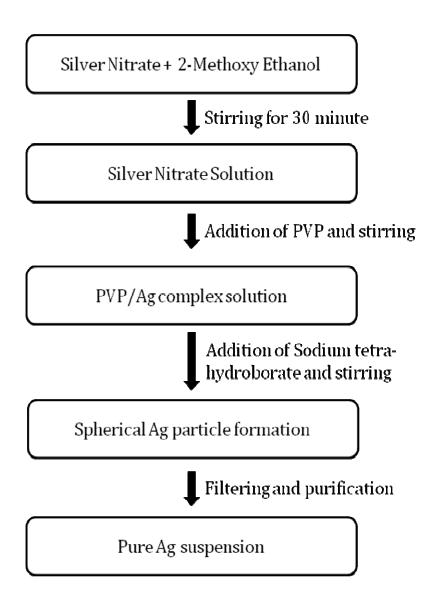

| FIGURE 3.2 P  | PROCESS FLOW OF SOLUTION REDUCTION SYNTHESIS OF NANOSTRUCTURED SILVER                                                        | 37 |

| FIGURE 3.3 A  | A GENERIC PROCESS FLOW OF GOLD NANOPARTICLE SYNTHESIS                                                                        | 38 |

| FIGURE 3.4 G  | GENERIC PROCESS FLOW OF ETCH PROCESS FOR DIE FABRICATION                                                                     | 40 |

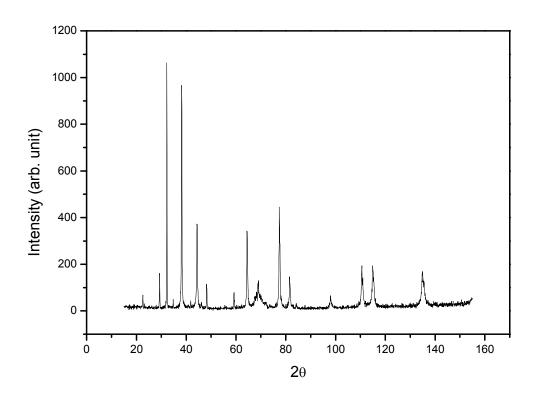

|               | K-RAY DIFFRACTION PROFILE OF SOL-GEL DERIVED COPPER AFTER REDUCTION IN R  THERMAL PROCESSING TOOL IN FORMING GAS ENVIRONMENT |    |

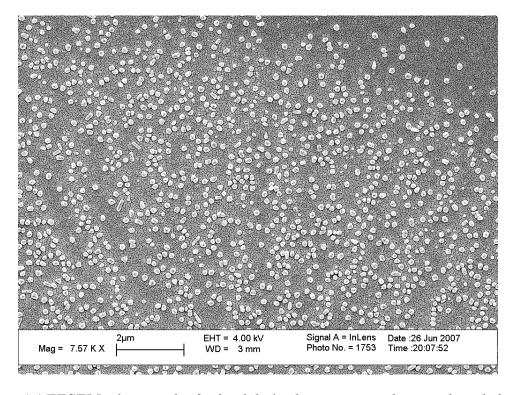

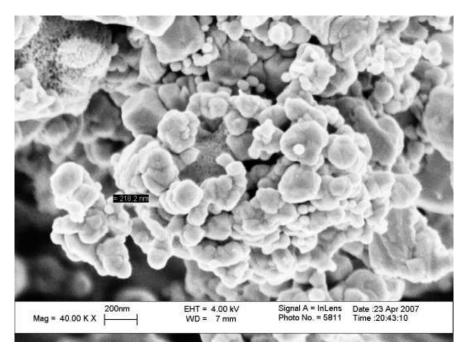

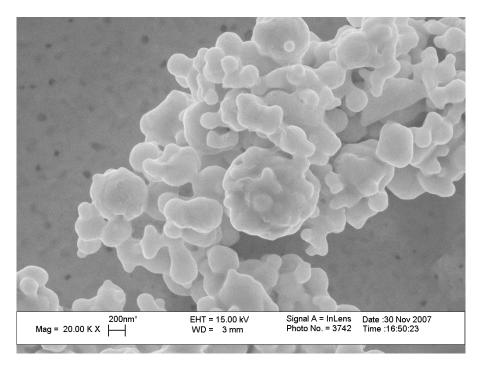

| FIGURE 4.2 F  | FESEM MICROGRAPH OF SOL-GEL DERIVED COPPER NANOPARTICLES                                                                     | 46 |

| FIGURE 4.3 C  | OPTICAL MICROGRAPH OF SELECTIVE WETTING OF COPPER GEL ON COPPER                                                              | 48 |

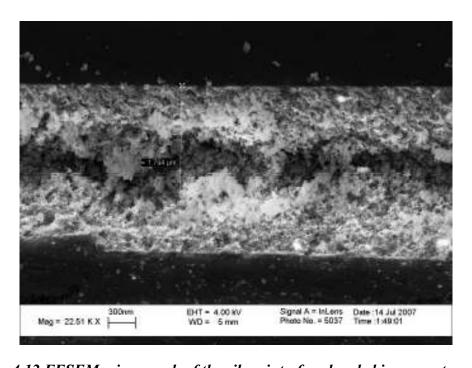

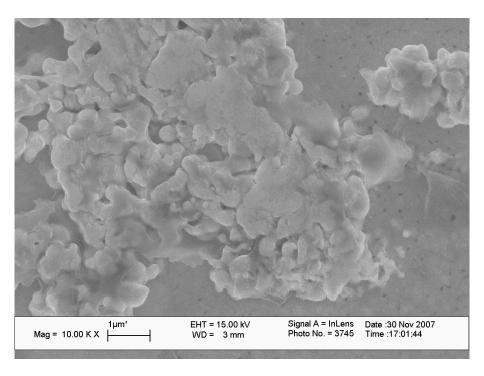

|               | FESEM MICROGRAPH OF SOL-GEL DERIVED NAOSTRUCTURED COPPER LOOSELY HE                                                          |    |

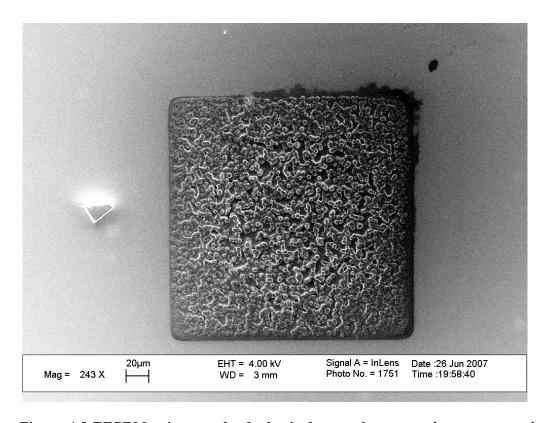

| FIGURE 4.5 F  | FESEM MICROGRAPH OF SELECTIVELY WETTED COPPER GEL ON COPPER PAD                                                              | 49 |

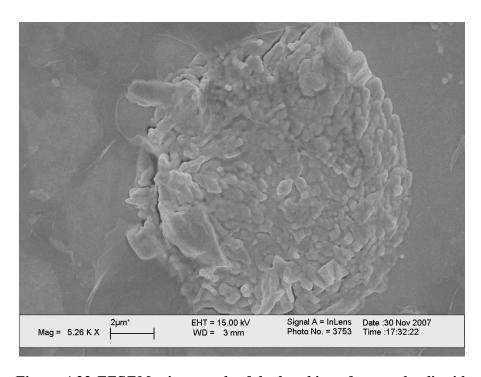

| FIGURE 4.6 F  | TESEM MICROGRAPH OF COPPER NANOPARTICLES ON DIE PADS AFTER SHEERING                                                          | 52 |

| FIGURE 4.7 X  | X-RAY DIFFRACTION PROFILES OF SILVER NANOPARTICLES                                                                           | 55 |

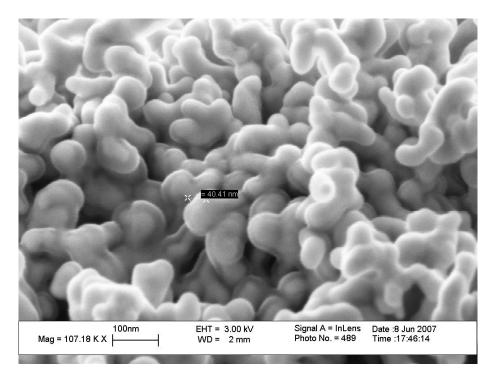

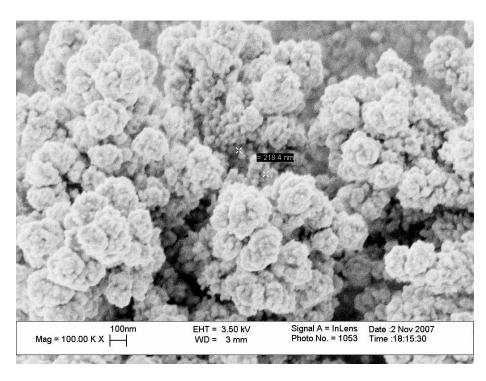

| FIGURE 4.8 F  | TESEM MICROGRAPH OF SILVER NANOPARTICLES AS SYNTHESIZED                                                                      | 55 |

| SINTERED AT 60 C                                                                           |     |

|--------------------------------------------------------------------------------------------|-----|

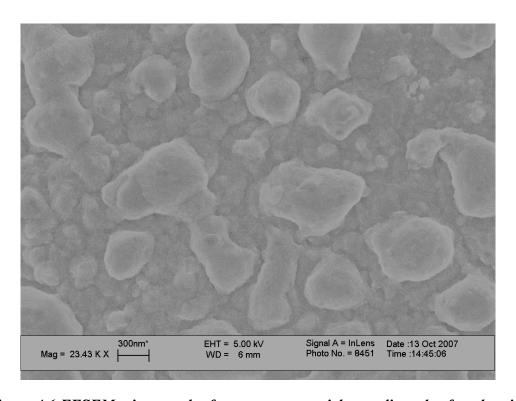

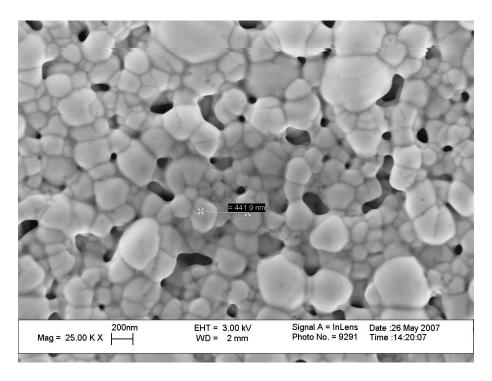

| FIGURE 4.10 FESEM MICROGRAPH OF THE SILVER NANOPARTICLES SINTERED AT 250 C                 | 56  |

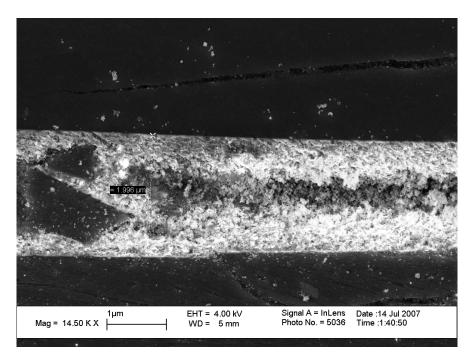

| FIGURE 4.11 FESEM MICROGRAPH OF THE SILVER INTERFACE IN N <sub>2</sub> ATMOSPHERE          | 59  |

| FIGURE 4.12 FESEM MICROGRAPH OF THE SILVER INTERFACE BONDED IN OPEN ATMOSPHERE             | E59 |

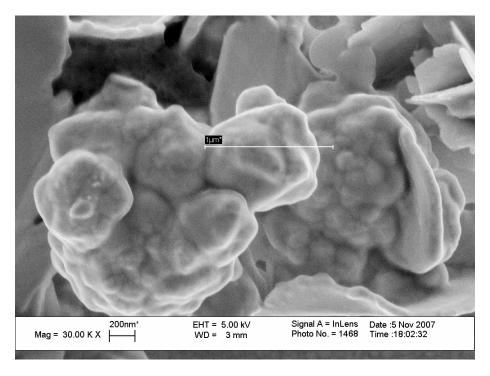

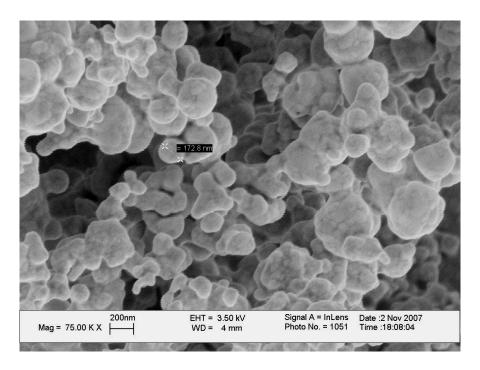

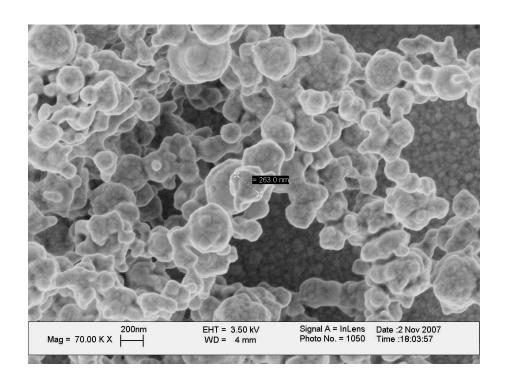

| FIGURE 4.13 FESEM MICROGRAPH OF GOLD NANOPARTICLES                                         | 62  |

| FIGURE 4.14 FESEM MICROGRAPH OF ENCAPSULATED GOLD NANOPARTICLES                            | 62  |

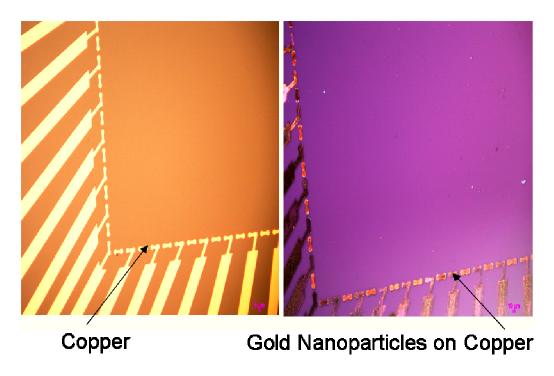

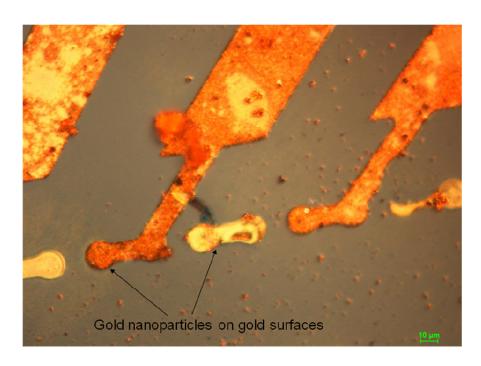

| FIGURE 4.15 OPTICAL MICROGRAPH SHOWING SELECTIVE WETTING OF GOLD NANOPARTICLES PAD         |     |

| FIGURE 4.16 OPTICAL MICROGRAPH SHOWING SELECTIVE WETTING OF GOLD NANOPARTICLES PAD         |     |

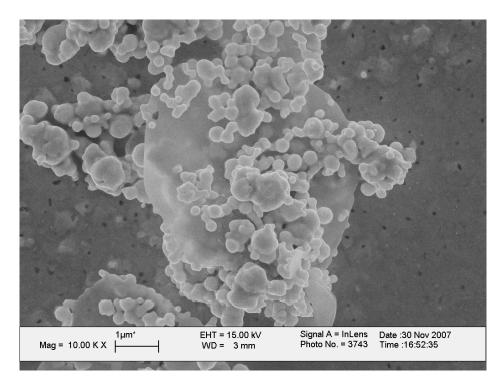

| FIGURE 4.17 FESEM MICROGRAPH OF SELECTIVELY DEPOSITION GOLD NANOPARTICLES ON C             |     |

| FIGURE 4.18 FESEM MICROGRAPH OF SELECTIVELY DEPOSITED GOLD NANOPARTICLES ON GOLD SUBSTRATE |     |

| FIGURE 4.19 FESEM MICROGRAPH OF GOLD NANOPARTICLES ON COPPER SURFACE AFTER SII 350 C       |     |

| FIGURE 4.20 FESEM MICROGRAPH OF GOLD NANOPARTICLES ON GOLD SURFACE AFTER SINT 350 C        |     |

| FIGURE 4.21 FESEM MICROGRAPH OF THE BOND INTERFACE ON THE SUBSTRATE SIDE                   | 70  |

| FIGURE 4.22 FESEM MICROGRAPH OF THE BOND INTERFACE ON THE DIE SIDE                         | 70  |

#### **SUMMARY**

Ever growing demands for portability and functionality have always governed the electronic technology innovations. IC downscaling with Moore's law at IC level and system miniaturization with System-On-Package (SOP) paradigm at system level, have resulted and will continue to result in ultraminiaturized systems with unprecedented functionality at reduced cost. However, system miniaturization poses several electrical and thermal challenges that demand innovative solutions including advanced materials, bonding and assembly techniques. Heterogeneous material and device integration for thermal structures and IC assembly are limited by the bonding technology and the electrical and thermal impedance of the bonding interfaces. Solder - based bonding technology that is prevalent today is a major limitation to future systems.

The trend towards miniaturized systems is expected to drive downscaling of IC I/O pad pitches from 40µm to 1-5µm in future. Solder technology imposes several pitch, processability and cost restrictions at such fine pitches. Furthermore, according to International Technology Roadmap for Semiconductors (ITRS-2006), the supply current in high performance microprocessors is expected to increase to 220 A by 2012. At such supply current, the current density will exceed the maximum allowable current density of solders. The intrinsic delay and electromigration in solders are other daunting issues that become critical at nanometer sized technology nodes. In addition, formation of intermetallics is also a bottleneck that poses significant mechanical issues. Similarly, thermal power dissipation is growing to unprecedented

high with a projected power of 198 W by 2008 (ITRS 2006). Present thermal interfaces are not adequate for such high heat dissipation.

Recently, copper based thin film bonding has become a promising approach to address the abovementioned challenges. However, copper-copper direct bonding without using solders has not been studied thoroughly. Typically, bonding is carried out at 400°C for 30 min followed by annealing for 30 min. High thermal budget in such process makes it less attractive for integrated systems because of the associated process incompatibilities. Hence, there is a need to develop a novel low temperature copper to copper bonding process. In the present study, nanomaterials based copper-to-copper bonding is explored and developed as an alternative to solder-based bonding. To demonstrate fine pitch bonding, the patterning of these nanoparticles is crucial. Therefore, two novel self-patterning techniques based on: 1.) Selective wetting and 2.) Selective nanoparticle deposition, are developed to address this challenge. Nanoparticle active layer facilitates diffusion and, thus, a reliable bond can be achieved using less thermal budget. Quantitative characterization of the bonding revealed good metallurgical bonding with very high bond strength. This has been confirmed by several morphological and structural characterizations. A 30-micron pitch IC assembly test vehicle is used to demonstrate fine pitch patternability and bonding. In conclusion, novel nanoparticle synthesis and patterning techniques were developed and demonstrated for low-impedance and low-cost electrical and thermal interfaces.

# 1. INTRODUCTION

This chapter deals with the electrical and thermal challenges in highly miniaturized and multifunctional System-On-Package (SOP) based systems. The electrical, thermophysical, and mechanical limitations of present interconnection and thermal structure technologies are discussed in order to define the need for innovative solutions. Finally, the present research objectives and thesis outline are presented.

Ever-growing demands for portability and functionality have always governed electronic technology innovations. Gordon E. Moore foresaw the market demand and set forth the empirical Moore's law [1], or the so-called first law of electronics, which predicts the increment in the number of transistors on a chip as a function of time. This coupled with shrinking die size contributed to several electrical and thermal challenges.

In the past, driven by Moore's law, the integration efforts were focused predominantly on silicon using CMOS technology. The System-on-Chip (SoC) approach of integrating functionalities on a single chip is beset with several fundamental and practical barriers like high cost, several photolithography steps, low yield and licensing and Intellectual Property (IP) issues. Currently, System-in-Package (SIP) approach of vertical stacking of bare and packaged ICs is pursued by several packaging companies for integration of functions at module and subsystem levels. SIP extends silicon integration in 3D but is still limited by CMOS capabilities.

To overcome the limitations of SoC approach, the System-On-Package (SOP) approach was proposed by Prof. Rao Tummala at the Packaging Research Center in 1994 [2]. The SOP enables highly miniaturized heterogeneous integration of RF/digital/opto/sensing functions by system-centric IC-package codesign and functional optimization with 3D integration of thin film components between the ICs and package. The focus of SOP is thus on miniaturization of system components, including not only actives, but also passives, power sources, I/Os, thermal structures, and system I/Os. With this fundamentally new paradigm, the SOP methodology overcomes the barriers of SoC leading to cheaper and faster-to-market convergent Microsystems. SOP is expected to enable the electronic devices to achieve unprecedented functionality and miniaturization at reduced cost.

# 1.1 Thermal Challenges in SOP Based Systems

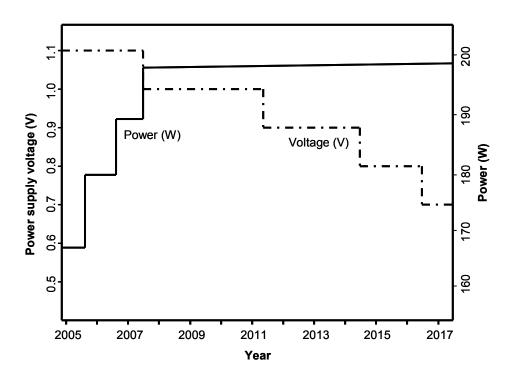

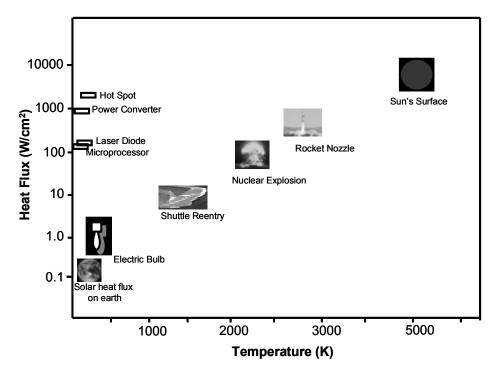

The chip power consumption has been increasing despite reductions in the power supply voltage and an increase in the efficiency of devices. According to the International Technology Roadmap for Semiconductors (ITRS-2006), high-performance microprocessors may dissipate 198 W by 2008 as seen in Figure 1.1 [3]. This situation can be worse in radiofrequency (RF) and power electronic components. The resulting thermal management challenges can be appreciated by comparing heat fluxes in various electronic components with those in some well-known heat generating systems (see Figure 1.2) [4].

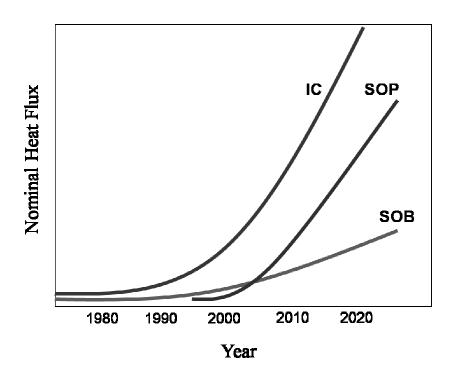

The thermal implications of SOP are enormous. Since SOP has two major components—device components and system components, it is convenient to understand the thermal

implications in these two parts of SOP technology separately. The thermal aspects of devices in the SOP concept remain the same whether the system is based on SOP or SOB (system-on-board). However, the system miniaturization of SOP has a huge impact because of the exponential decrease in the available volumetric system space. An illustration of such an impact is shown in Figure 1.3 [5].

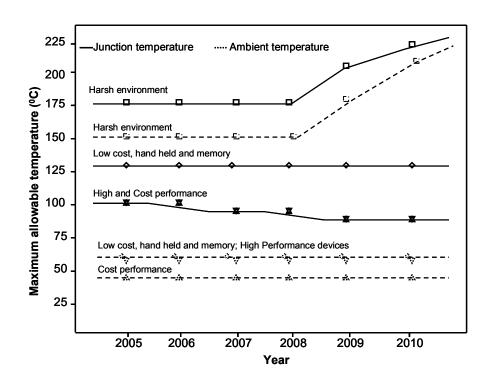

The cooling requirements of SOP systems are dictated by performance and reliability needs. Operating temperatures outside a range can cause deteriorated performance of active semiconductors—the leakage current may increase in DRAM, clock frequency may reduce, and wavelength drift and power drop may occur in optoelectronic modules. The mismatch in the coefficient of thermal expansion (CTE) between ICs and organic substrates (2.8 ppm/°C for Si, ~6 ppm/°C for GaAs, ~25 ppm/°C for eutectic Sn<sub>63</sub>Pb<sub>37</sub> solder, and 14 to 20 ppm/°C for organic epoxy fiberglass FR4) generates thermal stress at the solder joints. Repeated thermal cycling due to switching thus can lead to thermal fatigue and ultimate failure. Both operational reliability and functional performance are thermally influenced. An approach often taken by designers of multifunctional microsystems is to limit the maximum "junction temperature," an average measure of the chip temperature during operation. This limit is usually different for commercial and military equipment, as each sees different ranges of ambient temperatures in operation. For handheld and portable devices, the market sometimes demands an even more stringent limit to ensure a greater degree of customer satisfaction. The International Technology Roadmap for Semiconductors (ITRS) provides a projected value of allowable junction and operating temperatures in various microsystems [3]. This is illustrated in Figure 1.4 [3]. As evident from the figure, the junction temperature for single chip-packaged devices can't be allowed to rise above 125°C in low-cost, handheld, and memory devices; above 175°C in devices working in

harsh environment; and above 100°C in high-performance and cost-effective devices. SOP modules and systems, thus, may fail due to a variety of causes unless they are designed with the right set of materials and appropriate thermal management solutions.

Figure 1.1 Power supply voltage and maximum power consumption in high-performance processors [3, 5]

Figure 1.2 Comparison of heat fluxes in various phenomena and systems [4, 5]

Figure 1.3 Impact of SOP on thermal challenges [5]

Figure 1.4 Maximum allowable junction and ambient temperature as a function of time [3, 5]

#### 1.1.1 Thermal structures and interface challenges

The heat transfer path from the source, such as an IC, to the eventual heat sink consists of various interfaces. Microscale surface roughness at these interfaces results in regions of contacts and air gaps, and thus effective heat conduction may severely reduce due to increased interfacial resistance. Howeverm this resistance can be decreased using compliant and gap filling interface materials, known as thermal interface materials (TIM). TIM can be fabricated to minimize voids by providing a conformal and planar surface, thereby reducing the interfacial thermal resistance. Thermal resistance of TIM is governed by both the bulk, as well as the contact resistance [6, 7], as given by

$$R_{TIM} = \frac{BLT}{A \times K_{TIM}} + R_{C1} + R_{C2}$$

1.1

where BLT is the bond line thickness, A is the contact area,  $K_{\text{TIM}}$  is the bulk thermal conductivity of TIM, and  $R_{C1}$  and  $R_{C2}$  are the contact resistances. From Equation 1.1 it is apparent that the TIM should be as thin as possible, while still filling all the voids between the two higher conducting parts. BLT, however, can't be reduced below a limiting thickness due to reliability concerns. An increase in thermal conductivity and reduction of contact resistance are other ways to reduce the effective thermal resistance. Contact resistance is dependent on the surface roughness, contact pressure, and compressive modulus [7]. Various limiting factors can affect the selection of TIM including thermal conductivity, thermal resistance, operating temperature range, electrical conductivity, phase change temperature, pressure, viscosity, outgassing, surface finish, mechanical stability, reliability, and cost [7].

The present thermal interface solutions are not adequate for the next generation SOP based systems. They have high BLT, low thermal conductivity, low diffusivity and very high thermal impedance as shown in Figure 1.5 [5].

Figure 1.5 Trends in thermal interface materials [5]

Similar limitations are seen in thermal structures. Therefore, there is a need to develop new materials based interfaces that can alleviate thermal challenges by providing improved thermomechanical properties. One of the most attractive materials is copper that presents excellent thermal, electrical and mechanical properties suitable for abovementioned applications.

## 1.2 Fine Pitch Interconnection Trends and Challenges

Miniaturization at system and component level is plagued with myriads of electrical challenges in addition to the aforementioned thermal challenges. Integration of over a billion transistors on high end microprocessors witnesses interconnection scaling challenges that include issues related to degradation of resistivity, material integration, planarity control, high aspect ratio via and wire coverage, and reliability problems due to electrical, thermal and mechanical stresses in a multilevel wire stack [3].

According to the International Technology Roadmap for Semiconductors (ITRS 2006), the transition in electronic industry will cause nanochips with less than 32 nm nodes, in excess of 10000 I/Os and pitch down to 20 µm [3, 8]. A chronological trend in transition in electronic technology is shown in Figure 1.6. With such downscaling of the feature size signal integrity, interconnection delay, parasitics, mechanical stability of the interconnections and electromigration become utmost important.

Table 1.1 compares intrinsic interconnection delay with transistor switching delay at different technology nodes [9]. As the nodes become smaller, evidently interconnection delay becomes more prominent. At 35 nm node, the intrinsic delay surprisingly becomes two order magnitudes higher than the transistor delay. SIP technology has shown potential to address abovementioned issues by enabling vertical integration of devices and allowing significant reduction in interconnect length and thus high packing density [10, 11]. Heterogeneous device integration (e.g., logic, memory, analog, sensors, microfluidics, and power sources) at wafer-scale will push the interconnection pitch to 2-10 microns and terabit bandwidth.

Figure 1.6 Chronological advancement in IC packaging [8]

Table 1.1 Transistor and interconnect delay at different technology nodes [9]

| Technology Node                | MOSFET<br>Switching delay<br>(ps) | Intrinsic delay of<br>minimum scaled<br>1mm interconnect<br>(ps) | Intrinsic delay of<br>reverse scaled 1mm<br>interconnect (ps) |

|--------------------------------|-----------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|

| 1.0 μm (Al, SiO <sub>2</sub> ) | 20                                | 5                                                                | 5                                                             |

| 0.1 μm (Al, SiO <sub>2</sub> ) | 5                                 | 30                                                               | 5                                                             |

| 35 nm (Cu, low K)              | 2.5                               | 250                                                              | 5                                                             |

#### 1.2.1 Limitations of current chip-to-package interconnection technologies

Current solder-based interconnection technologies are becoming inadequate to address the emerging needs for pitch, electrical and reliability performance. Fine pitch solder plating inevitably leads to processing issues associated with controlled plating chemistry and solder bridging. Solders require a complex stack of UBM, barriers and surface finish making them less attractive for size miniaturization. Formation of intermetallics is another big concern in solder based technologies. In addition, underfill is required to compensate for the thermomechanical stress in solder based interconnections, which raises significant concern in fine pitch technologies where dispensing of underfill becomes a daunting challenge. According to ITRS-2006, the supply current in high performance microprocessors is expected to increase to 220 A by 2012 [3]. At such supply current, the current density will exceed the maximum allowable current density of solders [12]. Moreover, solder performance at gigahertz frequency is modest and electro-migration becomes a critical issue.

Polymer based adhesives, including nano anisotropic conductive film (ACF), and nonconductive film (NCF) are some of the recent alternatives. However, materials reliability at fine pitch and issues with copper interfaces are still a major concern and have not yet been addressed. Moreover, these alternatives have modest electrical and mechanical properties, making them less attractive for nanometer node technologies.

All-Copper interconnections is identified as one of the key enabling technology to address many of the abovementioned challenges. Thin film die to wafer and wafer-to-wafer bonding with copper-based interconnections have several benefits in terms of low cost, process compatibility with semiconductor infrastructure, and the shortest interconnection with the best electrical performance. Copper is electrically and thermally more conductive, and thus will be able to reduce the interconnect delay to a significant extant. In addition, copper interconnections will provide an efficient thermal path. Copper to copper bonding will also avoid formation of intermetallics and thus is mechanically more reliable. Electro-migration problem can also be reduced to a significant extent. Furthermore, the copper interconnection can be designed to achieve high mechanical compliance and thus the underfill can be eliminated. This will further enhance the electrical reliability by lowering the permittivity and loss and also will be instrumental in lowering cost [12]. Such direct wafer bonding using copper-copper bonding is also attractive for Microelectromechanical systems (MEMS) for device applications [13] such as sensors and actuators [14] and SOI [15].

Copper to copper bonding has been investigated by several research groups that include Reif et al [16, 17] and Chen et al [13, 18-27] using thermocompression bonding; Tadepalli et al [11] using ultrahigh vacuum technology; Kohl et al [12] using electroless copper bonding technology. However, the bonding is accomplished in ultrahigh vacuum and cleanroom environments with careful copper oxide cleaning procedures at around 400°C, with pressures exceeding 30 N/cm², which may not be compatible with thinned dies. The bonding is carried out by exposing the device at high bonding and annealing temperature for about an hour that limits the throughput. The process windows are relatively narrow with several temperature compatibility issues. Lowering the thermal budget is a critical issue especially in SOP systems as they integrate several thermally sensitive elements including sensors, optoelectronic devices and polymer thin films [10, 11]. Therefore, there is a need to develop a novel process that can address the issue of lowering the thermal budget in the copper to copper bonding process.

# 1.3 Objective of The Current Research

The present research attempts to address two fundamental issues associated with system miniaturization--- the thermal and interconnection issues

- 1) Copper to copper thin metallurgical bonding using high thermal conductivity metallic nanoparticles: This is done to achieve low thermal impedance interface. Nanoparticle approach helps reduce the thermal budget during thermocompression bonding. In addition, it helps decreasing the bond line thickness and thus reduces the thermal path and hence the overall thermal resistance.

- 2). High electrically conductive metallic nanoparticles based copper to copper thin film bonding: This is done to achieve fine pitch interconnections with low electrical impedance, low electromigration, high current carrying capability and good mechanical reliability.

- 3) Novel patterning technique for patterning of nanoparticles: Patterning of nanoparticle is done to assist the fine pitch copper-to-copper bonding. The patterning techniques studied in this work are based on selective wetting of copper solution and selective deposition of gold nanoparticles.

# 1.4 Proposed Approaches

Metallic nanoparticles of copper, silver and gold are explored and evaluated for the nanostructured bonding layers between the copper surfaces. High surface energy of the nanoparticle lowers the melting temperature of the material [28]. Notably, kinetics of interdiffusion of copper is dependent on the homologous temperature. Therefore, diffusion rate is enhanced by lowering the melting temperature. In addition, high surface energy and high grain boundary to volume ratio endows the particles with elaborate mobility making the diffusion kinetic even faster.

However, nanoparticle approach has several issues including particle aggregation, particle oxidation during processing and particle coarsening (Oswald ripening). In-situ nanoparticles formation and bonding can overcome many of these disadvantages. In addition, patterning of these nanoparticles is crucial for fine pitch interconnection. In the present research, therefore novel methods to accomplish fine pitch patterning of copper (and gold) nanoparticles are also discussed.

Previous studies mostly deal with qualitative analysis of bond reliability such as dicing and razor test. In the present study, emphasis has been give to quantify the bond strength using die shear test. This gives a unique opportunity to study the bond characteristics in more comprehensive manner. In order to demonstrate the feasibility of this technology, the nanoparticle self-patterning was demonstrated on a 30 micron pitch silicon carrier substrate, followed by bonding with 30 micron pitch thin film copper pads.

In summary, a novel approach has been studied to achieve maskless patterning of metal nanoparticles that has been used to carry out copper to copper bonding at low temperature and reduced bonding time. The bond strength has been quantified to get better understanding of the bonding mechanisms.

#### 1.5 Thesis Outline

This thesis deals with copper-to-copper thin film bonding based on metallic nanoparticles. Novel approaches for nanoparticle patterning, based on selective wetting or selective catalytic deposition approach are also studied. Various metallic nanoparticles including solgel derived copper, solution reduced silver and catalytically deposited gold, are studied for the purpose of fine pitch interconnection and thermal structure applications in 3D SOP systems.

Chapter 2 deals with the chronological advancement in copper-to-copper direct bonding technology. In addition, a brief review of alternate bonding technologies is presented. The process parameters affecting the bonding characteristics are reviewed. Lastly, various mechanisms affecting diffusion controlled copper to copper direct bonding are discussed.

Chapter 3 covers the experimental approach of the present work. This includes synthesis of different nanoparticles using sol-gel technique followed by gas reduction, and wet-chemical synthesis. Experimental details of nanoparticle patterning approach are also presented. Lastly, the details of thermocompression bonding and methods of structural, mechanical and morphological characterization are presented in the chapter.

Chapter 4 describes the nanomaterial synthesis results, thermocompression copper to copper bonding, bonding characterization and fine pitch process demonstration.

Chapter 5 presents the key conclusions from this research work. Chapter 6 recommends some future works that can be done to further consolidate the results, and to provide greater understanding and industrial viability of nanoparticle based copper-to-copper bonding.

### 2. LITERATURE REVIEW

High speed and multi functionality in digital and mixed signal devices demand short and reliable interconnections, fine pitch, higher I/O density and 3D packaging [29]. Thinner modules with embedded actives are beginning to drive the need for less than 20 micron pitch interconnections [29]. Multicore microprocessors to achieve high signal speed and data rates at low power constitute another application that is being witnessed by present generation computer and communications technology [30]. These multi-core architectures are pushing the I/O density to more than 10.000/cm<sup>2</sup> and pitch to less than 50 microns [30, 31]. Downscaling solder plating inevitable leads to barriers from solder plating process control and solder bridging at fine pitch. Solder reliability requires a complex stack of UBM, barriers and surface finish making them less attractive for size miniaturization and low cost. Dominating role of intermetallics at fine pitch and the associated thermomechanical failures is another big concern with solder based technologies. In addition, underfill is required to compensate for the thermomechanical stress in solder based interconnections, which raises significant concern in fine pitch technologies where dispensing of underfill becomes a daunting challenge. According to International Technology Roadmap for Semiconductors (ITRS-2006), the supply current in high performance microprocessors is expected to increase to 220 A by 2012 [3]. At such supply current, the current density will exceed the maximum allowable current density of solders [12]. In addition, traditional solder based interconnection technology has high resistivity, mechanically reliability issues due to formation of intermetallics at the bond interface and high electromigration at high frequency. Microelectromechanical systems (MEMS) based sensors and actuators are other

applications that would require alternate interconnection approach beyond solder [14]. Therefore, there is a need for an innovative bonding and assembly approach that can address the aforementioned issues.

Various research groups have reported alternate technologies to address these issues. Yeoh et al [32] have studied on copper pillar technology coupled with solder technology to achieve electrically and mechanically more reliable bonding. It has been reported to be beneficial for low k interlayer dielectrics integration into back end interconnect architecture. Such approach can partially or fully reduce the low k dielectric failure. Moreover, copper die bumps as used in the process has added advantages that includes lowering of critical dimension floor, simple underbump metallization scheme that can improve electromigration resistance and higher I/O density than seen in earlier technologies. In addition, they are very compatible to high volume manufacturing as observed in Intel's 65 nm technology, which employs eutectic lead-tin solders to mate copper die bumps [32]. Similar approach has been reported by Wang et al [33]. The novel characteristic of their study is the use of non-reflowable pillar like copper base and reflowable eutectic lead tin (Sn63Pb37) solder cap processed using electroplating for 200 micron pitch for silicon on insulator substrate. They reported no shear strength deterioration after 1000 hr thermal cycling. In addition, it has been claimed that the maximum shear stress for 200 micron pitch lies below the shear strength of copper, and thus a notably reliable interconnect can be expected. Such composite technology based on Copper bumping reportedly enables easier processing, minimizes the thermomechanical concerns, distribute the current density uniformly over the interconnection, and lowers the bump temperature to mitigate several reliability issues. Nevertheless, solders based bonding approach involves several interconnection processing steps, barrier layers to prevent diffusion and still impose bottlenecks associated with intermetallics and electromigration. Traditional solder interconnections may not be adequate to meet the fine pitch process constraints, thermo-mechanical and electrical reliability requirements in the emerging packaging applications [3, 34].

Another emerging technology is gold stud bumping [35-48]. Gold bumping can be grouped into two categories - thermocompression gold to gold bonding without any adhesive layer and thermocompression bonding using adhesive layer such as Anisotropic Conductive Fillers (ACF) and Nonconductive Filler (NCF). Details of gold stud bumping technology can be found out in the research paper of Miessner et al [38]. Gold stud bumping, typically, involves bonding of gold wire to the substrate, which is induced by thermal and ultrasonic energy coupled with pressure, followed by shearing off the wire from the formed ball to leave a stud bump [35]. Direct gold to gold bonding using thermocompression technique can be useful to lower the bonding temperature and achieve high bond reliability. However, planarity and the bump shape are important issues that are deterrent to the effectiveness of such process. Majeed et al has studied the reliability issues in gold bump technology for flip chip applications [35]. Some of the reliability concerns can be addressed using conductive film adhesives. Oh et al has reported a thermoplastic conducting polymer bumping approach that uses thick film photoresist to achieve high planarity bumps [49]. Such process can decrease the bonding temperature and eliminate the need of adhesive. A notably low contact resistance and high degree of planarity have been reported. However, this technology involves added process steps and low pitch resolution. Similar approach by Johanson et al uses an epoxy perform and aligns it on the die which is then aligned to the substrate and bonded by simultaneous application of pressure and temperature [50]. This approach needs very high degree of alignment resolution. Gold stud bumping and bonding using Anisotropic Conductive Film (ACF), Isotropic Conductive Film (ICF) and

Nonconductive Film (NCF) have been understood to be more attractive [35, 51]. This polymeric adhesive can eliminate some of the problems associated with the earlier bonding approaches. Low temperature bonding, simple processing steps, fine pitch capability and high reliability make these attractive candidates for next generation packaging applications [35, 52]. However, these polymeric adhesives have modest electrical performance than the metal interconnects such as copper. Therefore, there is a need to develop an all copper based interconnect approach that can enhance the electrical performance and enable high signal speed.

Recently, there has been several reported works that discuss approaches to carry out copper to copper direct bonding. Table 2.1 lists important works in chronological order. Copper to copper direct bonding using thermo-compression method is most attractive in this regards. The bonding is carried out by thermally induced diffusion. Several research group including Veer, Kolster et al. [53], Ward and Carroll [54], and Iijima, Wakabayashi et al. [55] have studied the diffusion characteristics of copper in copper silicon systems that includes the inter diffusion coefficient and vacancy assisted self diffusion coefficient. Though the reported values of temperatures are higher than the bonding temperature of interest, the above mentioned works give the basic understanding of the diffusional process that is crucial for thermo-compression bonding. The pioneering work on actual demonstration of copper to copper direct bonding has been done by Fan et al [17] and Chen et al [13, 18-27]. Fan et al demonstrated copper to copper face to face bonding at 450 C for 30 min. followed by 30 min nitrogen annealing at same temperature range. The thickness of evaporated copper, which was used in the process, was 300 nm. They reported good quality bonding with their processes. However, in absence of quantitative bond strength measurement bonding at different process parameters could not be comprehensively compared. In addition, it was found that the presence of diffusion layer (Ta) did

not affect the bonding at the bonding temperature of interest. From this finding it can be safely concluded that the bonding doesn't involve copper –silicon diffusion that is only interlayer copper self diffusion across the bonding interface is only important. This is an important understanding because the diffusional work done in copper silicon systems reveals very fast diffusion kinetics of copper in silicon [53-55]. Since copper is a deep-level trap for carriers, a diffusion barrier is indispensable [17].

Further work by Chen et al developed methods to carry out bonding at 400 C at 4000 mbar pressure. Also, studies on microstructural evolution at the interface and other bonding locations during the bonding process suggest several phenomena including copper self diffusion, recrystallization and grain growth acting together to form a strong metallurgical bond some time free of any identifiable interfacial region. However, the bonding interfaces may take several forms including indistinguishable interface, zigzag interface and distinct interface.

Table 2.1 Chronological listing of important literatures on copper-to-copper bonding by various research groups

| Research<br>Group                | Experimental Variables                                                                                                                                                                                                                                                  | Salient features                                                                                                                           | Reference |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Iijima,<br>Wakabayashi<br>et al. | <ul> <li>Copper-silicon (up to 8%) system</li> <li>Temperatures ranging from 900-1150 K</li> </ul>                                                                                                                                                                      | <ul> <li>Inter-diffusion of copper in copper in copper rich silicon system</li> <li>Intrinsic diffusion of copper</li> </ul>               | [55]      |

| Fan, Rahman et al.               | <ul> <li>Silicon wafers with evaporated copper (150-300 nm)</li> <li>Bonding temperature – 450 C for 30 min</li> <li>Bonding pressure- 4000 mbar</li> <li>Annealing temperature – 450 to 600C for 30 min</li> <li>Qualitative Razor test for bond assessment</li> </ul> | <ul> <li>Ta diffusion barrier has no effect on bonding</li> <li>Post bonding annealing improves the bonding quality.</li> </ul>            | [17]      |

| Chen, Fan et al.                 | <ul> <li>Silicon wafer with 300 nm evaporated copper</li> <li>Bonding temperature – 400 C for 30 min</li> <li>Bonding pressure – 4000 mbar</li> </ul>                                                                                                                   | <ul> <li>Good morphological understanding</li> <li>Homogeneously distributed oxides and defects</li> <li>Basic understanding of</li> </ul> | [21, 25]  |

|              | • Annealing – 400 C for  | underlying mechanisms         |      |

|--------------|--------------------------|-------------------------------|------|

|              | 30 min                   |                               |      |

|              |                          |                               |      |

| Chen, Fan et | Process parameters same  | • Roughness is found to be    | [13] |

| al.          | as [17]                  | very critical                 |      |

|              |                          | • Indication of               |      |

|              |                          | recrystalization and grain    |      |

|              |                          | growth                        |      |

|              |                          | • Various possible            |      |

|              |                          | mechanisms are proposed       |      |

|              |                          | meenamsins are proposed       |      |

|              |                          |                               |      |

| Chen, Fan et | • Bonding -300-400 C for | • Effect of bonding           | [24] |

| al.          | 30 min                   | temperature and time is       |      |

|              | • Nitrogen annealing at  | established                   |      |

|              | 300-400 C for 30 min     | • Good bonding at high        |      |

|              |                          | bonding temperature           |      |

|              |                          | coupled with less             |      |

|              |                          | annealing time as well as     |      |

|              |                          | at low bonding                |      |

|              |                          | temperature and more          |      |

|              |                          | annealing time suggesting     |      |

|              |                          | diffusion to be very critical |      |

|              |                          | for bonding                   |      |

|              |                          | Bonding temperature can       |      |

|              |                          | be thus reduced to 350 C at   |      |

|              |                          | the expense of overall        |      |

|              |                          | bonding time (1.5 hr)         |      |

|              |                          |                               |      |

|              |                          |                               |      |

|              |                          |                               |      |

| Chen, Fan et al.   | 400 C for 30 min  • Nitrogen annealing at 400 C for 30-60 min                                                   | <ul> <li>Demonstration of copper to copper bonding technology for 3D integration</li> <li>Contact resistance is appreciably low especially for longer annealing time suggesting that the contact resistance is directly related to the post-bonding annealing</li> </ul> | [23] |

|--------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Chen, Chang et al. | • 4 layers stacking of silicon wafers                                                                           | <ul> <li>Demonstration of multistacking using copper to copper bonding</li> <li>High residual stress to cause bowing in large wafers</li> <li>A homogenous bonding with nonidentifiable interface</li> </ul>                                                             | [27] |

| Chen, Tan et al.   | <ul> <li>Face to face bonding with various surface roughness</li> <li>Bonding parameter same as [24]</li> </ul> | Better understanding of<br>the effect of surface<br>roughness on the bond<br>strength and quality                                                                                                                                                                        | [18] |

| Chen, Fan et al.   | • Bonding parameter similar to [24]                                                                             | • Review of various bonding parameters that affect the bonding quality and electrical performance                                                                                                                                                                        | [22] |

| Chen, Chang et al.        | • Bonding parameter similar to [24]                                                                                                                                                                                     | <ul> <li>Thermal annealing is effective at high bonding temperature only</li> <li>Investigation of bond quality using various qualitative as well as quantitative methods (Die shear and wire pull test</li> </ul> | [26] |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Ate, Osborn et al.        | <ul> <li>Silicon wafer with high aspect ratio electroplated copper</li> <li>Bonding at room temperature followed by annealing at 250 C</li> <li>Mechanical shear force measurement for bond characterization</li> </ul> | <ul> <li>Room temperature bonding using electroless copper deposition</li> <li>Electroless copper makes up for nonplanarity and misalignment</li> </ul>                                                            | [12] |

| Tadepalli and<br>Thompson | <ul> <li>Silicon all copper to copper bonding</li> <li>Ultrahigh vacuum (2 X 10<sup>-10</sup> torr)</li> <li>Bond strength analysis using AFM surface energy analysis at high vacuum (10<sup>-10</sup> torr)</li> </ul> | <ul> <li>Room temperature bonding in ultrahigh vacuum environment</li> <li>In presence of oxide layer needed bonding temperature is 300 C or above</li> <li>Good bonding</li> </ul>                                | [11] |

## 2.1 Process Parameters for Thermo-Compression Bonding

Copper to copper direct bonding using thermocompression is a diffusion driven process and thus the quality of the bond depends on several diffusion thermodynamic and kinetic phenomena. Therefore, several critical process parameters that can affect the bonding behavior include bonding temperature, pressure and time, annealing temperature and time, bonding environment, cleanliness, intimate contact and roughness of the matting surfaces. The effect of various bonding parameters on the bond characteristics is reviewed by Chen, Fan et al. [22]. A short overview of that is as following.

## **2.1.1 Bonding Temperature:**

For diffusion-driven process, temperature becomes very important parameter. Temperature provides copper atoms with required kinetic energy to diffuse across the interface. In addition, the grain growth is higher at high temperature. Therefore, the bond quality can be enhanced by adopting high bonding temperature. Nevertheless, material considerations require low thermal budget to prevent degradation. Typically, bonding is done at 400°C for 30 minute followed by annealing for 30 min. This has been reported to provide a reliable bonding with a distinguishable bond interface. However, bonding at 300° C for 30 min and longer annealing time can also help achieving reliable bonding; however a longer total bonding time can make the bonding interface indistinguishable.

## 2.1.2 Post bonding annealing

Post bonding annealing has been found to be very important in enhancing the quality of the bonding by providing more opportunity for diffusion processes. The annealing temperature is usually kept same as the bonding temperature. As discussed earlier, longer post bonding annealing can render indistinguishable bond interfaces.

#### 2.1.3 Bonding and annealing duration

Since diffusion is a kinetic phenomenon, the bonding and annealing durations therefore are important key parameters. Bonding time becomes even more crucial for low temperature bonding. 30 min bonding and 30-60 min post bonding annealing has been reported to be optimal for reliable bonding at 300-400 bonding temperature.

## 2.1.4 Bonding pressure

Inter diffusion is enhanced by making the matting surfaces as close as possible. Therefore, sufficient pressure is needed to achieve a reliable bonding. Typical, bonding pressure applied by various researchers is around 4000 mbar.

# 2.1.5 Bonding Environment

Bonding environment should be chosen with care to facilitate a good quality bond. As copper is very reactive, presence of oxygen can form oxide layer on copper surface and thus can deteriorate the bonding quality. Thus, a vacuum or inert environment is better suited for copper-copper direct bonding. Vacuum has an added advantage in that it can ensure a clean atmosphere by effectively ensuring less number of particles present in the bonding atmosphere. Typical,

bonding is done in a vacuum atmosphere (10<sup>-3</sup> torr). Oxygen is removed by nitrogen purging prior to bonding.

#### 2.1.6 Surface conditions

For good bonding, it is imperative to have a clean bonding surface free of deleterious particulates, which can appear as barriers to the bonding process. Surface roughness is also very important. A good bonding requires surface roughness as low as possible. The recommended surface roughness is around 5 nm. Surface roughness increases when the copper oxide layer is removed from the copper surface using HCL as cleaning reagent. Hence, prevention of copper oxide formation is necessary. Bonding is better if the bonding follows immediately after copper evaporation or electrodeposition. Some research groups have carried out bonding without removal of copper oxide. A good bonding can still be achieved using higher temperature and bonding duration, thus making this less attractive.

#### 2.1.7 Bond quality assessment

Bond quality analysis using bond strength measurement helps understand the underlying bonding mechanism including the chemical reactions that takes place during bonding and annealing [56]. Vallin, Jonsson et al. have done a thorough review on various methods for bond quality assessment [56]. A brief description of some of the available methods is presented in this section. There are several qualitative and quantitative methods for bond quality assessment. However, the attractiveness of a method is quantized in terms of cost and time involved in a measurement. In addition, nondestructive testing is more attractive in such a way that the bond strength can be measured without breaking the bond interface.

Qualitative approaches give fair idea regarding the bond quality. However, they are not suited for good comparison of the bonding strengths. A small change in the bonding strength is not detected through qualitative approach. There are several qualitative approaches including dicing and razor test. The bond quality assessment using these methods are based on the percentage of successful dicing or cutting..

Quantitative bond strength assessment approaches, however, provides quantified measurements to compare and contrast between the bonding of interest. There are several techniques for quantification of the bond strength including Double Cantilever Beam (DCB) test, Tensile test, Chevron test and Die Shear test. In DCB method the bonded interface is sheared apart using thin blade and bond strength is measured in terms of the length of the crack. This is a difficult process especially for brittle materials, such as Silicon, since insertion of blade might break Silicon. In addition, it is most suited for week bonds as it is very difficult to insert blade inside strong bonds. Tensile test is also not very suitable for brittle silicon as the test involves pulling test samples by a tensile test machine. Chevron test is similar to tensile test. This is done using test structures with chevron shaped notch. This test is particularly useful for brittle materials. Die shear test involves shearing of the bond using shear force parallel to the bonding interface. The shear force per unit contact area that is required to break bonding gives the shear strength.

## 2.2 Bonding Mechanisms

Chan, Fan et al have proposed several mechanisms of copper to copper direct bonding [13]. Their work reveals that the bonding is a strong function of the surface roughness, and bonding is associated with recrystallization and grain growth during bonding and annealing processes. Copper to copper bonding occurs due to interdiffusion of copper between two contact surfaces due to temperature and pressure. Three possible mechanisms based on contact between two matting surfaces include peak to peak contact between two surfaces having comparable roughness, peak to valley contact of two surfaces with comparable roughness, and contact between two surfaces with different scale roughness [13]. The abovementioned mechanisms have been reported to explain various kinds of interfaces including indistinguishable interface, distinguishable interface and zigzag interface.

Despite of the several developments, copper to copper direct bonding is still in the embryonic stage. The bonding needs high temperature that might not be attractive to next generation SOP based technologies, which integrate several temperature sensitive elements. The situation is excruciated by the longer bonding and annealing time duration to which the system has to be exposed. In most of the cases, the total bonding time is approximately 1 hour. Moreover, to avoid thermal stress induced cracking special care is taken to cool the bonded system, which sometime requires prolonged cooling duration as high as 2 hours. Moreover, emerging trend in semiconductor industries to add low k polymeric materials to reduce RC delay also demands alternate bonding approaches to reduce the thermal budget. Very few alternate technologies have been reported to avoid the high thermal budget induced challenges. Tadepalli and Thompson discussed a low temperature pressure bonding method to join copper films [11].

However, this method requires ultrahigh vacuum of the order of  $10^{-10}$  torr. Similar approach was reported by Kim et al., which was based on surface activated bonding approach [57]. They claimed void or defect free bonding with a bonding strength of 6.47 MPa. However, this method requires extremely clean and planarized surface, activated using Argon ions bombardment in ultrahigh vacuum. Another method was reported by Ate, Osbom et al., which was based on electroless copper deposition [12]. High aspect ratio copper pillars are first fabricated using thick polymer layer on both substrate and die side, and then bonding is carried out using electroless copper deposition. Electroless copper is claimed to compensate for the misalignment and coplanarity issues. However, this method is too process intensive. Therefore, still there is a need to devise novel technologies that can some of the aforementioned concern.

To overcome the abovementioned disadvantages, metallic nanoparticle based thin film copper bonding has been investigated. Next chapter discusses the details of the experimental procedures.

## 3. EXPERIMENTS

This chapter deals with the experimental details used in the synthesis of nanostructured metallic particles that include Copper, Silver and Gold. The shape of the nanomaterials significantly depends on the process variables such as choice of precursors, concentration, stirring conditions and reaction temperature. However, an optimal synthesis scheme is chosen to ensure spherical nanostructural metallic particles, as suited for thin film bonding purpose. Various techniques used for copper to copper bonding with different interface layers are also described in later subsections. Lastly, different characterization schemes including structural, morphological and bond strength characterization, as utilized in the study, are presented.

# 3.1 Nanostructured Spherical Copper Particles

An increase in the surface area to volume ratio increases the surface energy of the copper nanoparticles, hence nanoparticles are very prone to oxidation and grain coarsening even at room temperature. This is more predominant with base metals such as copper. To avoid these, an insitu synthesis and bonding approach using gel-derived nanocopper is pursued. A low cost, low temperature sol-gel technique was employed to prepare copper ethoxide gel by dissolving copper precursor in a carrier solvent. The so synthesized copper ethoxide gel upon subsequent reduction in a reducing atmosphere produces nanostructured copper thin films for in-situ bonding.

A generic process flow of copper nanoparticles synthesis using such scheme has been shown in the Figure 3.1. A 0.05 Molar Copper (II) ethoxide Cu(OC<sub>2</sub>H<sub>5</sub>)<sub>2</sub> (Alfa Aesar) was dissolved in 50 ml of 2-methoxyethanol (2-MOE) as the carrier solvent in a flask and refluxed at 125°C for 4 hours in nitrogen atmosphere. The solution was then cooled to room temperature under same environment. The anhydrous copper precursor solution so formed was again refluxed at 125°C for 1 hour. The resulting precursor solution was then spin coated at 2000 RPM for 30 seconds on silicon wafer coated with titanium/copper thin layer to form a thin and uniform organometallic film. The thickness and uniformity of the film are function of the spinning variables such as speed and time of spinning. Therefore, optimization of process variables is needed to ensure uniform thin layer of copper gel. The film thickness affects the reduction ease and hence, a thin film (approximately 1-5 micron thick) was deposited to facilitate reduction. The spin coated wafers were then reduced in forming gas (5-10% H<sub>2</sub> and N<sub>2</sub>) atmosphere at 200-400°C in a tube furnace and Rapid Thermal Processing (RTP) chamber. The RTP chamber is an enclosed chamber, which due to high temperature ramping rate is useful to decrease the reduction time. As compared to RTP chamber, reduction in tube furnace calls for extra precautionary measures to prevent gas leakage and unwarranted oxidizing atmosphere due to bad sealing of the tube. Therefore, reduction in the tube furnace warrants purging for several times with forming gas before increasing the furnace temperature.

#### 3.1.1 Maskless patterning of copper nanoparticles precursor

Metal based bumping is easily done with electroless or electrochemical plating. However, nanoparticle and nanopaste patterning technologies at fine pitch of less than 100 microns are not widely developed. Selective patterning of copper precursor gels on bond pads was investigated to

avoid complex photopatterning and inkjet printing processes. Such maskless patterning process reduces number of process steps associated in patterning of bonding layer. A suitable polymer surfaces is selected to enable selective wetting on the metal pads.

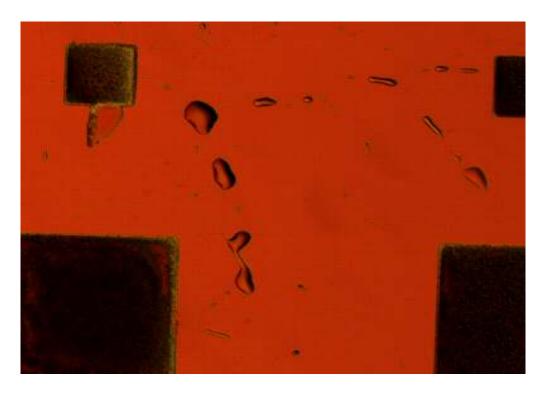

Solution carrier chosen for the copper precursor induces selective wetting on preferred surfaces and does not wet unwanted surface, and thus ensure maskless patterning of the copper gel. The wetting behavior of the copper precursor was qualitatively studied by spin coating of the solution over various surfaces including copper, gold, silicon dioxide and polyimide. Process variables of spin coating were optimized to get an optimal wetting on copper surface and insignificant or no wetting on polymer and silicon dioxide surface. The spin coating resulted in formation of thin film on the copper pads, and some loosely bonded droplets of copper precursor on polymer and silicon dioxide surface, which was then, removed using acetone or isopropanol solvent.

Figure 3.1 Synthesis scheme of sol gel derived copper nanoparticles

## 3.2 Solution Reduction Derived Nanostructured Silver

The nanogranular silver used in the process was synthesized using solution reduction technique. The process detail has been shown in Figure 3.2. A 0.04 molar Silver Nitrate (Sigma Aldrich) was dissolved in 50 ml of 2-methoxyethanol (2-MOE) that acts as an organic solvent. The solution was thoroughly mixed using magnetic stirrer for 30 min. Polyvinyl Pyrrolidone (PVP, Sigma Aldrich) was then added to solution and thoroughly mixed by stirring for several minutes. The molar ratio of PVP to Silver Nitrate is an important parameter that dictates the silver particle size and distribution after reduction by a reducing agent. Therefore, an optimum

amount of PVP was chosen to control the silver size in the range below 200 nm. Furthermore, addition of PVP in the Silver Nitrate solution results in formation of Ag-PVP complex due to PVP lone pair electron donated to Ag s-orbital. This complex is easier to be reduced by a mild reducing agent at low temperature. Sodium Tetrahydridoborate (NaBH<sub>4</sub>, Sigma Aldrich), a reducing agent, was then added to the solution and stirred for several hours. The resulting solution was kept for 6-7 hours, and then filtered to get fine granular silver particles. The silver particles thus formed were then dissolved in low molecular weight organic solvent.

Figure 3.2 Process flow of solution reduction synthesis of nanostructured Silver

# 3.3 Wet chemical synthesis of nanostructured Gold

The Gold particles were prepared at room temperature using wet chemical process by catalytic reduction of Gold (III) Chloride. A generic process flow of gold particle synthesis has been shown in the Figure 3.3. The aqueous solutions of analytical grade Gold (III) Chloride (HAuCl<sub>4</sub>, 99.999%, Sigma Aldrich) was added to dilute nonionic surfactant t-

Octylphenoxypolyethoxyethanol solution (Triton X-100 solution, Sigma Aldrich), followed by addition of Hydroxylamine (NH<sub>2</sub>OH, 99.999%, Sigma Aldrich) under sonication for rapid mixing. The resulting reaction mixture was purified by washing several times with de-ionized water (ddH<sub>2</sub>O). The particles were stored in ddH2O until use.

Figure 3.3 A generic process flow of gold nanoparticle synthesis

#### 3.3.1 Patterning of Gold nanoparticles

Preferential patterning of gold nanoparticles on copper and gold pads was done by taking advantage of catalytic effect of copper on the reduction reaction on the desired locations. The die with copper interconnection patterns was immersed into a beaker containing the aqueous solution of gold (III) chloride, the nonionic surfactant Triton X-100 solution and hydroxylamine. The gold particles are instantly preferential nucleated on the copper surfaces. The reaction was stopped by immersing and rinsing the die with ddH<sub>2</sub>O.

#### 3.4 Test Vehicle Fabrication

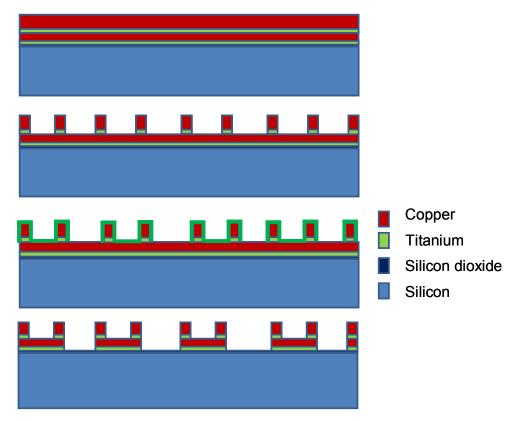

A simple die-substrate assembly was fabricated to demonstrate copper-to-copper bonding. The die, consisting of peripheral array of interconnects at a pitch of 30 and 200 µm was fabricated onto a 4" silicon wafer using etch back process. The fabrication was assisted by two glass masks, containing a thick (800 Å) chromium layer that acted as an absorber pattern metal. These transparent glass masks (to UV light) were placed in direct contact with the photo resist coated wafer surface in subsequent process steps and exposed to UV light. The first glass mask defined the copper pad and the second defined the daisy chain structures on the die. A generic process flow of die fabrication method is illustrated in Figure 3.4. The process consisted dc sputtering deposition of Ti/Cu/Ti/Cu layer on a silicon wafer with a thin layer of silicon dioxide deposited by plasma enhanced chemical vapor deposition. Titanium layer works as the adhesion layer as well as etch protection layer. Shipley 1827 photoresist was spin coated on the wafer at 3000 rpm spinning rate and a ramping rate of 500 for 30 seconds. This was then exposed and patterned. Top copper and titanium layer was then etched out to make copper pad on the wafer. After striping the first photoresist layer, a thick Shipley 1827 photoresist was spin coated on the wafer at 1000 rpm spinning rate and 500 ramping rate for 30 seconds. This photoresist was patterned using daisy chain mask and similar procedure was repeated.

Similarly the substrate was fabricated on silicon wafer using etch back process. Ti/Cu was sputtered on Si/SiO<sub>2</sub> using DC sputterer. Copper interconnection were made on the substrate using substrate mask. A similar process flow as die fabrication was adopted to fabricate substrate.

Figure 3.4 Generic process flow of etch process for die fabrication

# 3.5 Copper to Copper Bonding

Copper to copper bonding process involved synthesis and subsequent or simultaneous patterning of nanoparticles followed by thermocompression bonding. Thermocompression bonding was done in various environments at different process parameters to optimize the bonding process.

## 3.5.1 Copper bonding using copper precursor solution

Copper precursor solution was preferentially coated on the substrate copper pads using spin coating at 2000 rpm and 500 ramping rate for 40 seconds. The die and the substrate was

then aligned, and pressed using a normal compressive force. The assembly was then heated at a temperature of 350°C under an applied pressure of 500 kPa under a reducing dry forming gas (5-10% N<sub>2</sub>/H<sub>2</sub>) environment. The copper bump stand-off height allowed reducing atmosphere under the whole die area. For simplicity, sometime substrate with copper interconnections was replaced by copper blanket (sputter deposited wafer). A novel rapid thermal processing (RTP) tool with infrared lamps was utilized to lower the process time to less than 10 minutes. In this way, a high throughput can be accomplished compared to traditional Cu-Cu bonding that takes 1 hour.

#### 3.5.2 Copper to copper bonding using silver nanoparticles

The solution containing silver suspension was first spin coated on a silicon wafer coated with copper thin layer using 3000 RPM for 30 min. High spinning speed ensured a thin and uniform layer of silver solution over the copper surface. This spin-coated wafer was then placed onto a silicon substrate with copper finishing. The bonding was done using simultaneous application of temperature and pressure. The bonding was performed under various atmospheric conditions –

a. FINETECH Flip Chip Bonder (FINEPLACER) was used to bond copper to copper in ambient atmospheric conditions. After placement of the chip on the substrate, the chip and substrate are heated to a specified temperature. The chip-contact heating module and heating plate ensure controlled temperature on die and the substrate heating. The chip contact module heats the die by direct contact thermal transfer. The heating plate is attached with an internal gas cooling system that helps to achieve very high ramping rate. Simultaneous force is applied using bonding force module. The bonding force is applied

by lever-shaft force transmission using a separate force arm. The FINEPLACER can apply as high as 20 N bonding force and has a resolution of 0.1 N. For thin film bonding using silver nanoparticles a thermal load of 370 degrees for 5 minutes on the substrate side and same temperature for 10 minutes on the die side were applied. The normal compression force was maintained at 20 N.

b. A nitrogen gas furnace was utilized to perform bonding under an inert atmosphere. The bonding temperature and pressure were same as above. The bonding time varied from 5-30 minutes.

## 3.5.3 Copper bonding using gold nanoparticles

Die and substrate were prepared as discussed in earlier section and gold nanoparticles were preferentially deposited on substrate copper pads using catalytic gold deposition as described in section 3.3.1. The substrate and the die were then aligned in FINEPLACER flip chip bonder. A detailed description of the procedure has been given in section 3.5.2. The bonding temperature was 370°C and the compressive bonding pressure of 500 MPa was used for 5 min.

# 3.6 Bonding Characterization

## 3.6.1 X-ray diffraction analysis

X-ray diffraction study of the nanostructured copper was done using PANalytical X'pert PRO Alpha. The diffraction profile was measured using Cu-K $\alpha$  (1.54 A) radiation. A divergence slit of ½ degree and an Xcelerator detector was used. To minimize the diffraction from the

substrate an offset of  $1^{\circ}\omega$  was used. Measurements were taken from  $20\text{-}100^{\circ}$  at a scan rate of 0.002 counts per second.

## 3.6.2 Field emission scanning electron microscope

The morphological study of the copper nanoparticles and the bonding interface was done using Thermally Assisted Field Emission Scanning Electron Microscope (FESEM LEO 1530). This has a capability of 3 nm resolution at low voltage (1kV).

#### 3.6.3 Destructive die shear test

The bond strength was measured using DAGE 4000 (Dage Precision Industries) die shear testing tool. Compressed air (4 bar minimum) is utilized to operate the shear cartridge, which can apply a shear load of as high as 100 Kg. A frictionless load cartridge system and air bearing technology ensures maximum accuracy and thus is useful to measure very small load with high precision.

## 4. RESULTS AND DISCUSSIONS

This chapter describes the key process results from this research and discusses the key findings. This includes results involved in the synthesis of sol-gel derived nanostructured Copper by gas phase reduction, nanostructured silver by solution reduction technique, and wet-chemical synthesis of nanostructured gold, and subsequent processing techniques. Structural and morphological characterizations are done using X-ray diffraction and thermally assisted field emission scanning electron microscope (FESEM). The results associated with thin film copper to copper bonding using aforementioned nanostructured metallic interfaces and subsequent bond strength characterization are also presented in this chapter.

## 4.1 Sol-gel Derived Nanostructured Copper

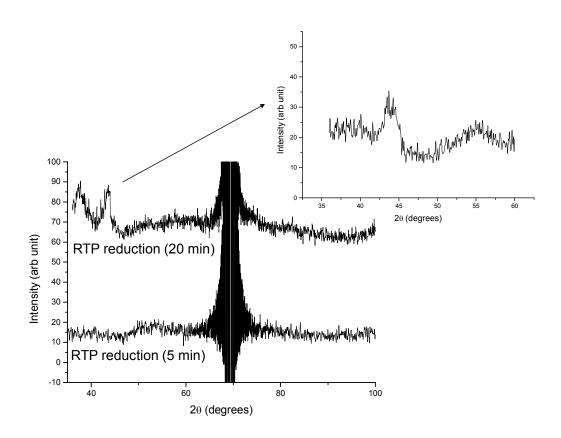

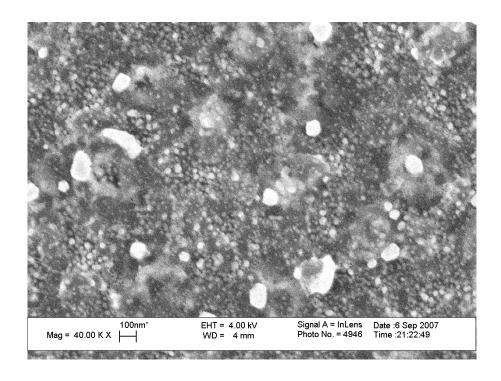

As described in the previous chapter, the nanostructured copper was synthesized by gas phase reduction of sol-gel derived copper precursor solution in forming gas atmosphere. The Cu  $K_{\alpha}$  X-ray diffraction profile, as shown in Figure 4.1 shows the copper diffraction peaks for the nanocopper reduced in RTP for 5 min and 20 minutes time at 350°C. Notably a reduction for 5 min can result in partial reduction of copper precursor to copper particle. However, an increase in the reduction time up to 20 min completely can drive complete reduction of copper precursor. Ankur et al. has shown that such solution sol-gel derived copper precursor can be reduced at a

temperature less than 300°C [58]. However, the time for reduction is higher (approximately 40 min) for low reducing temperature.

Figure 4.1 X-ray diffraction profile of sol-gel derived copper after reduction in rapid thermal processing tool in forming gas environment