University of Warwick institutional repository: http://go.warwick.ac.uk/wrap

### A Thesis Submitted for the Degree of PhD at the University of Warwick

http://go.warwick.ac.uk/wrap/2561

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

## Investigation of the Electrical Properties of $Si_{1-x}Ge_x$ Channel pMOSFETs with High- $\kappa$ Dielectrics

by

**Andrew Dobbie**

Thesis

Submitted to the University of Warwick

for the degree of

**Doctor of Philosophy**

### **Department of Physics**

September 2007

# Contents

| List of | Tables vii                    |  |  |  |  |

|---------|-------------------------------|--|--|--|--|

| List of | Figures viii                  |  |  |  |  |

| Acknow  | ledgments xvi                 |  |  |  |  |

| Declara | tions xvii                    |  |  |  |  |

| Publica | tions xviii                   |  |  |  |  |

| Abstrac | Abstract xix                  |  |  |  |  |

| Abbrevi | Abbreviations xx              |  |  |  |  |

| Chapte  | Chapter 1 Introduction 1      |  |  |  |  |

| 1.1     | The Semiconductor Industry    |  |  |  |  |

| 1.2     | High- $\kappa$ Dielectrics    |  |  |  |  |

| 1.3     | Germanium                     |  |  |  |  |

| 1.4     | Current Work                  |  |  |  |  |

| Chapte  | r 2 Theoretical Background 10 |  |  |  |  |

| 2.1     | Introduction                  |  |  |  |  |

| 2.2     | Basic MOSFET Operation        |  |  |  |  |

| 2.3           | Carrier                                                                           | Mobility and Scattering Mechanisms                                      | 15                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|               | 2.3.1                                                                             | Ionised Impurity Scattering                                             | 16                                                                                                                     |

|               | 2.3.2                                                                             | Phonon Scattering                                                       | 17                                                                                                                     |

|               | 2.3.3                                                                             | Surface Roughness Scattering                                            | 19                                                                                                                     |

|               | 2.3.4                                                                             | Alloy Scattering                                                        | 19                                                                                                                     |

| 2.4           | Band S                                                                            | Structure                                                               | 19                                                                                                                     |

| 2.5           | Short                                                                             | Channel Effects                                                         | 25                                                                                                                     |

|               | 2.5.1                                                                             | Threshold Voltage Roll-off                                              | 26                                                                                                                     |

|               | 2.5.2                                                                             | Channel Length Modulation                                               | 27                                                                                                                     |

|               | 2.5.3                                                                             | Drain-Induced Barrier Lowering and Punchthrough                         | 28                                                                                                                     |

|               | 2.5.4                                                                             | Velocity Overshoot                                                      | 30                                                                                                                     |

|               | 2.5.5                                                                             | Further High Field Effects                                              | 31                                                                                                                     |

| 2.6           | Proces                                                                            | is Considerations for High- $\kappa$ Gate Dielectric Ge Channel MOSFETs | 32                                                                                                                     |

|               |                                                                                   |                                                                         |                                                                                                                        |

| Chapte        | r3 Ex                                                                             | perimental Techniques                                                   | 37                                                                                                                     |

| Chapte<br>3.1 |                                                                                   | xperimental Techniques                                                  | <b>37</b><br>37                                                                                                        |

|               | Introd                                                                            |                                                                         |                                                                                                                        |

| 3.1           | Introd                                                                            | uction                                                                  | 37                                                                                                                     |

| 3.1           | Introdi<br>Electri                                                                | uction                                                                  | 37<br>37                                                                                                               |

| 3.1           | Introdu<br>Electri<br>3.2.1                                                       | uction                                                                  | 37<br>37<br>37                                                                                                         |

| 3.1           | Introdu<br>Electri<br>3.2.1<br>3.2.2                                              | uction                                                                  | 37<br>37<br>37<br>39                                                                                                   |

| 3.1           | Introdu<br>Electri<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                            | uction                                                                  | 37<br>37<br>37<br>39<br>40                                                                                             |

| 3.1<br>3.2    | Introdu<br>Electri<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                            | uction                                                                  | 37<br>37<br>37<br>39<br>40<br>42                                                                                       |

| 3.1<br>3.2    | Introdu<br>Electri<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>MOS <i>J</i>            | uction                                                                  | <ol> <li>37</li> <li>37</li> <li>37</li> <li>39</li> <li>40</li> <li>42</li> <li>43</li> </ol>                         |

| 3.1<br>3.2    | Introdu<br>Electri<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>MOS /<br>3.3.1          | uction                                                                  | <ul> <li>37</li> <li>37</li> <li>37</li> <li>39</li> <li>40</li> <li>42</li> <li>43</li> <li>43</li> </ul>             |

| 3.1<br>3.2    | Introdu<br>Electri<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>MOS 2<br>3.3.1<br>3.3.2 | uction                                                                  | <ul> <li>37</li> <li>37</li> <li>37</li> <li>39</li> <li>40</li> <li>42</li> <li>43</li> <li>43</li> <li>45</li> </ul> |

|        | 3.3.6   | Split C-V                                                                                | 59  |

|--------|---------|------------------------------------------------------------------------------------------|-----|

|        | 3.3.7   | Mobility                                                                                 | 61  |

|        | 3.3.8   | Carrier Velocity                                                                         | 63  |

| Chapte | r4De    | evelopment of $Si_{1-x}Ge_x$ Capacitors with High- $\kappa$ Dielectric and               |     |

| Met    | al Gate |                                                                                          | 65  |

| 4.1    | Introdu | uction                                                                                   | 65  |

| 4.2    | Proces  | s Outline and Specification                                                              | 66  |

| 4.3    | Electri | cal Characterisation Results                                                             | 70  |

|        | 4.3.1   | Gate Leakage                                                                             | 70  |

|        | 4.3.2   | Capacitance-Voltage Characteristics                                                      | 76  |

|        | 4.3.3   | Oxide Capacitance and Thickness                                                          | 82  |

|        | 4.3.4   | Doping Profile and Interface Trap Density                                                | 84  |

|        | 4.3.5   | Flatband Voltage                                                                         | 86  |

|        | 4.3.6   | Hysteresis                                                                               | 87  |

| 4.4    | Conclu  | sion                                                                                     | 90  |

| Chapte | r5 Ele  | ectrical Characterisation Results of $Si_{1-x}Ge_x$ Channel pMOS-                        |     |

| FET    | s with  | High- $\kappa$ Dielectric and Metal Gate                                                 | 92  |

| 5.1    | Introdu | uction                                                                                   | 92  |

| 5.2    | Device  | Specification and Processing                                                             | 93  |

| 5.3    | Electri | cal Characterisation of ${\sf Si}_{1-x}{\sf Ge}_x$ Channel pMOSFETs $\ldots\ldots\ldots$ | 95  |

|        | 5.3.1   | Uniformity                                                                               | 95  |

|        | 5.3.2   | Effective Mobility and Split C-V                                                         | 96  |

|        | 5.3.3   | Transconductance, Threshold Voltage and Subthreshold Slope .                             | 101 |

|        | 5.3.4   | Saturation Drain Current and Off-Current                                                 | 106 |

| 5.4    | Conclu  | sion                                                                                     | 108 |

| Chapt |         | Certical Characterisation Results and Discussion on Certification      | ••         |

|-------|---------|------------------------------------------------------------------------|------------|

| Ch    | annel p | MOSFETs                                                                | 110        |

| 6.1   | Introd  | luction                                                                | 110        |

| 6.2   | Device  | e Specification and Processing Details                                 | 111        |

| 6.3   | Device  | e Characteristics                                                      | 113        |

|       | 6.3.1   | I-V Characteristics                                                    | 113        |

|       | 6.3.2   | Threshold Voltage                                                      | 123        |

|       | 6.3.3   | Subthreshold Slope, DIBL and Transconductance                          | 124        |

|       | 6.3.4   | Gate Leakage                                                           | 131        |

|       | 6.3.5   | Split C-V Characteristics                                              | 133        |

|       | 6.3.6   | Effective Mobility                                                     | 136        |

|       | 6.3.7   | Off-State Leakage                                                      | 140        |

| 6.4   | Concl   | usion                                                                  | 147        |

| Chapt | er7H    | igh-Field Transport Effects in Buried Si $_{1-x}$ Ge $_x$ Channel pMOS | <b>j</b> - |

| FE    | Ts      |                                                                        | 149        |

| 7.1   | Introd  | luction                                                                | 149        |

| 7.2   | Invest  | igation of Hole Carrier Velocity in $Si_{1-x}Ge_x$ Channel pMOSFETs    | 152        |

|       | 7.2.1   | Device Specification and Processing Details                            | 152        |

|       | 7.2.2   | Mobility and Long-Channel Behaviour                                    | 152        |

|       | 7.2.3   | Short Channel Behaviour and Carrier Velocity                           | 159        |

| 7.3   | Impac   | t Ionisation Investigation                                             | 174        |

|       | 7.3.1   | Device Specification and Processing                                    | 174        |

|       | 7.3.2   | Impact Ionisation                                                      | 174        |

| 7.4   | Concl   | usion                                                                  | 179        |

| Chapt | er8C    | onclusion                                                              | 181        |

| . 8.1 |         | nary                                                                   | 181        |

| -     |         |                                                                        |            |

### Chapter 6 Electrical Characterisation Results and Discussion on Germanium

| Bibliog |                                             | 186     |

|---------|---------------------------------------------|---------|

| 8.2     | Discussion and Suggestions for Further Work | <br>183 |

# **List of Tables**

| 1.1 | Important properties of silicon and germanium relevant for CMOS device                               |

|-----|------------------------------------------------------------------------------------------------------|

|     | processing (after Sze [1981])                                                                        |

| 4.1 | Capacitor specification for $Si_{1-x}Ge_x/HfO_2/Thick TiN capacitors 69$                             |

| 4.2 | Capacitor specification for $Si_{1-x}Ge_x/HfO_2/Thin TiN$ capacitors 69                              |

| 4.3 | Capacitor specification for $Si_{1-x}Ge_x/HfO_2/W$ capacitors                                        |

| 4.4 | Magnitude of oxide charges responsible for hysteresis behaviour in $Si_{1-x}Ge_x/HfO_2/W$            |

|     | gate capacitors                                                                                      |

| 5.1 | Growth specification for $Si_{1-x}Ge_x/HfO_2/W$ gate pMOSFETs 93                                     |

| 5.2 | Capacitive equivalent thickness (CET) values for ${\sf Si}_{1-x}{\sf Ge}_x/{\sf HfO}_2/{\sf W}$ gate |

|     | pMOSFETs 100                                                                                         |

| 6.1 | Summary of the activation energy values for the off-state leakage in                                 |

|     | germanium pMOSFETs                                                                                   |

| 7.1 | Summary of series resistance and effective channel length for silicon and                            |

|     | SiGe pMOSFETs at room temperature and 77 K                                                           |

| 7.2 | Growth specification of ${\rm Si}_{0.64}{\rm Ge}_{0.36}$ wafers to investigate impact ionisa-        |

|     | tion. After Palmer [2001]                                                                            |

# **List of Figures**

| 1.1 | Schematic of direct tunnelling current, $J_{DT}$ , through an oxide of thick-           |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | ness, $t_{ox}$ , with a barrier height, $arPsi_B$                                       | 3  |

| 1.2 | Gate leakage current and oxide thickness for silicon oxynitride as specified            |    |

|     | by the ITRS. The simulated gate leakage for a given oxide thickness is                  |    |

|     | also shown. After ITRS [2006 Update]                                                    | 4  |

| 2.1 | Schematic of a simple pMOSFET.                                                          | 11 |

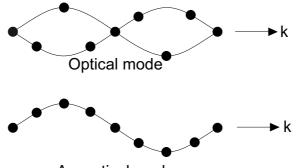

| 2.2 | Simple schematic showing the difference between transverse optical and                  |    |

|     | transverse phonon modes. After Kittel [1996]                                            | 18 |

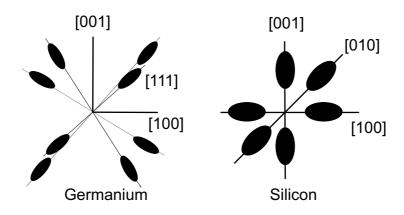

| 2.3 | Schematic of the conduction band minima for bulk germanium and bulk                     |    |

|     | silicon. After Paul [2004]                                                              | 20 |

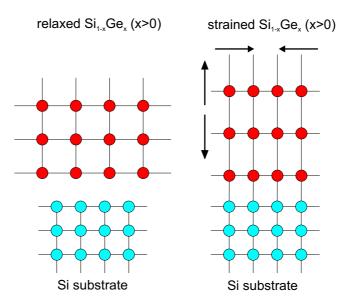

| 2.4 | Schematic showing the pseudomorphic strained ${\sf Si}_{1-x}{\sf Ge}_x$ layer (below    |    |

|     | the critical thickness) on a silicon substrate                                          | 22 |

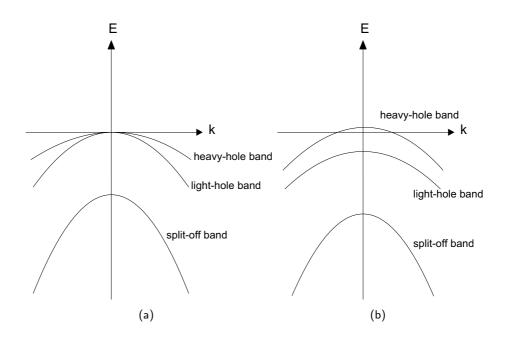

| 2.5 | Schematic of the (a) unstrained and (b) biaxial compressively strained                  |    |

|     | $Si_{1-x}Ge_x$ valence band showing the band splitting and change of effective          |    |

|     | mass                                                                                    | 23 |

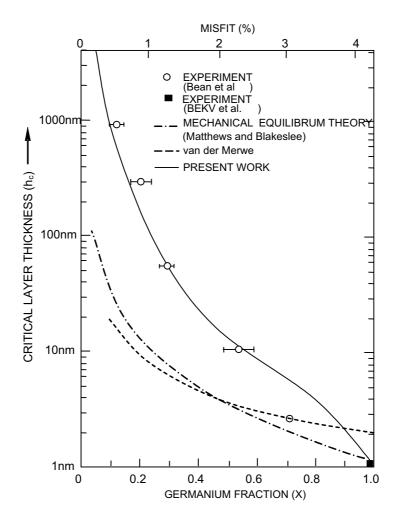

| 2.6 | Critical thickness of ${\sf Si}_{1-x}{\sf Ge}_x$ layers grown on silicon substrate as a |    |

|     | function of germanium composition. After People and Bean [1985]                         | 24 |

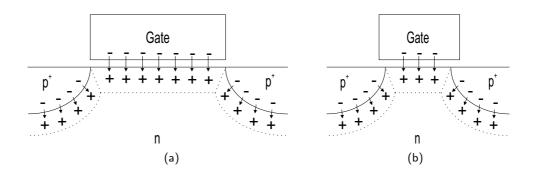

| 2.7 | Schematic to show the charge sharing of the depletion region for (a) long               |    |

|     | and (b) short-channel pMOSFET.                                                          | 26 |

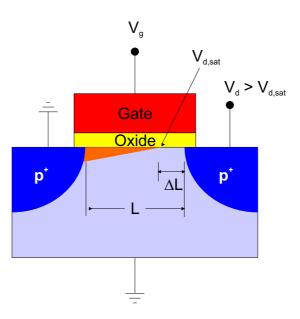

| 2.8 | Channel length modulation in a MOSFET for a drain bias higher than         |    |

|-----|----------------------------------------------------------------------------|----|

|     | the saturation drain voltage                                               | 28 |

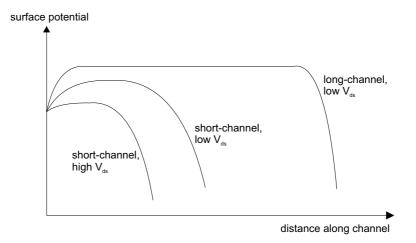

| 2.9 | Schematic of the surface potential versus distance along a MOSFET          |    |

|     | channel showing how the drain bias in long and short-channel devices       |    |

|     | influences the barrier height at the source. After Taur and Ning [1998].   | 29 |

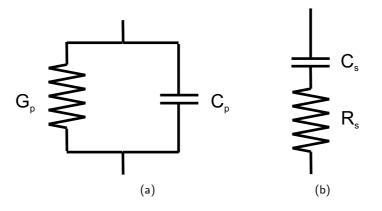

| 3.1 | Simplified equivalent MOS circuits measured in (a) parallel and (b) series |    |

|     | mode                                                                       | 41 |

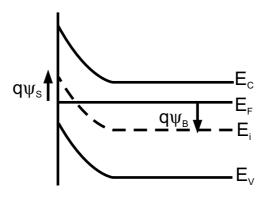

| 3.2 | Definition of threshold voltage for a pMOSFET. The condition for thresh-   |    |

|     | old is when $q\psi_B = q\psi_S$                                            | 43 |

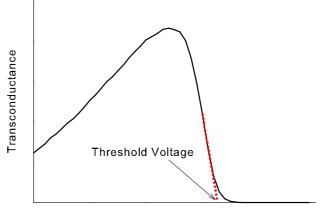

| 3.3 | Extraction of threshold voltage by linear extrapolation of the transcon-   |    |

|     | ductance                                                                   | 44 |

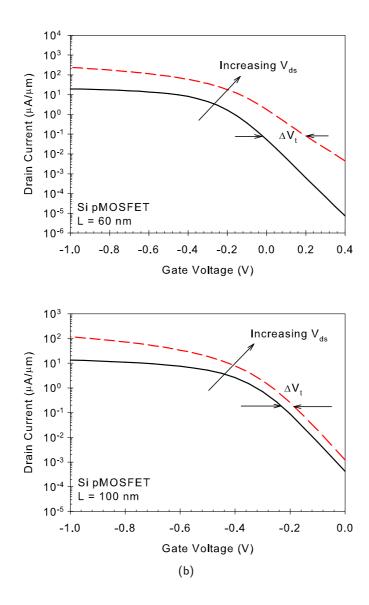

| 3.4 | Example of DIBL extraction for a Si pMOSFET (a) with and (b) without       |    |

|     | the effects of punchthrough.                                               | 47 |

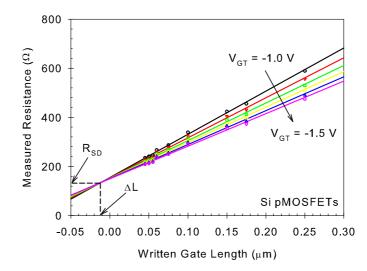

| 3.5 | Example of series resistance and effective length extraction using the 1st |    |

|     | regression method for bulk silicon MOSFETs                                 | 50 |

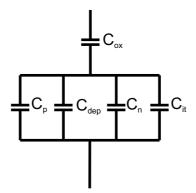

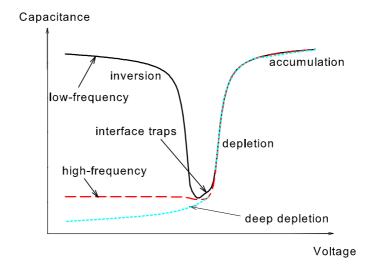

| 3.6 | Equivalent circuit model showing the capacitances in the MOS capacitor.    | 52 |

| 3.7 | Example of low and high frequency C-V characteristics of an n-type MOS     |    |

|     | capacitor.                                                                 | 53 |

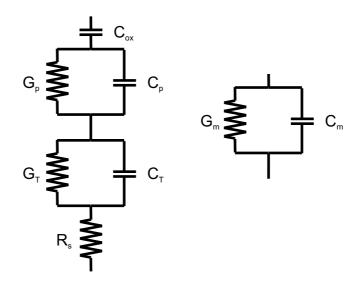

| 3.8 | (a) Equivalent MOS circuit model to account for an interfacial dielectric  |    |

|     | layer and (b) the equivalent circuit measured by the LCR meter             | 58 |

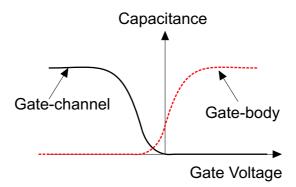

| 3.9 | Typical split C-V characteristics for a silicon pMOSFET.                   | 60 |

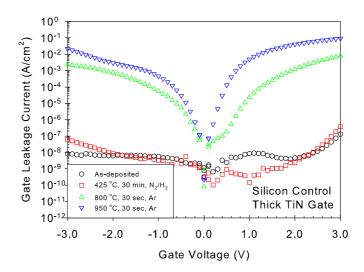

| 4.1 | Gate leakage characteristics for Silicon control capacitors with thick TiN |    |

|     | gate with different anneal conditions                                      | 70 |

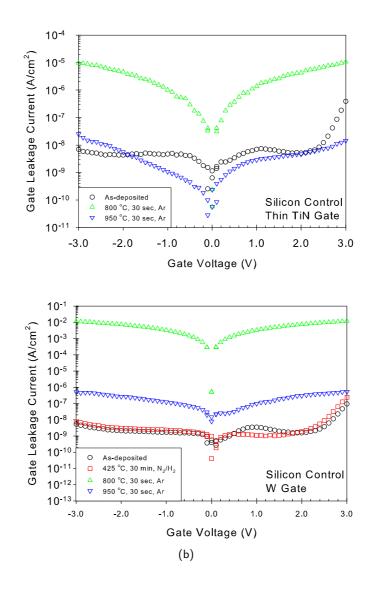

| 4.2 | Gate leakage charactereristics of silicon capacitors with (a) thin TiN and |    |

|     | (b) W metal gates following different anneal conditions                    | 72 |

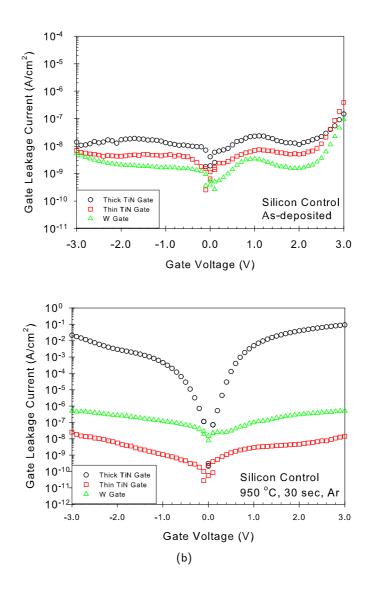

| 4.3  | Gate leakage charactereristics for silicon capacitors with different metal                     |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | gates that are (a) as-deposited and (b) following RTA anneal at 950 $^\circ\text{C}$           |    |

|      | for 30 seconds in Ar.                                                                          | 74 |

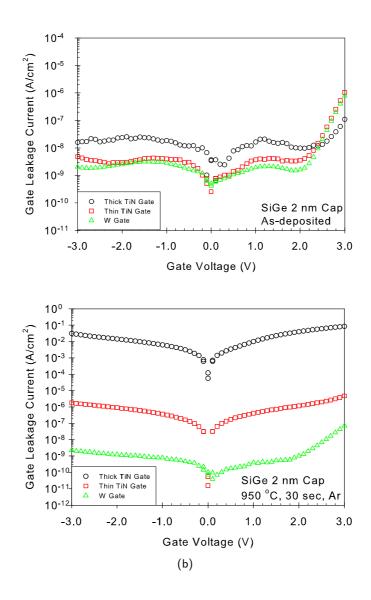

| 4.4  | Gate leakage charactereristics for SiGe capacitors with 2 nm Si cap and                        |    |

|      | different metal gates that are (a) as-deposited and (b) following RTA                          |    |

|      | anneal at 950 $^\circ\text{C}$ for 30 seconds in Ar                                            | 75 |

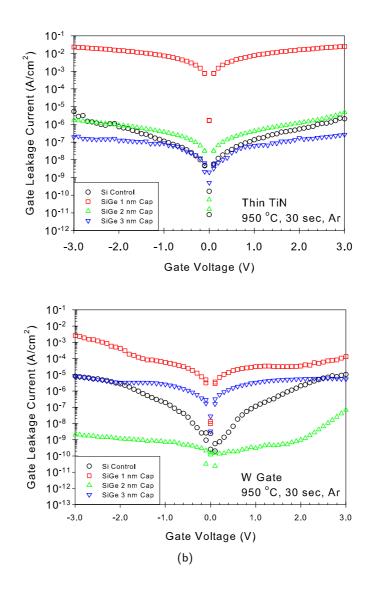

| 4.5  | Gate leakage charactereristics for SiGe capacitors showing the effects of                      |    |

|      | the silicon cap for (a) thin TiN and (b) W metal gates after RTA2. $\ .$ .                     | 77 |

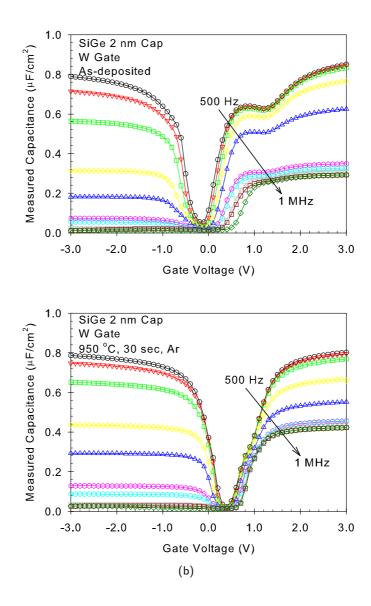

| 4.6  | Measured C-V characteristics for (a) as-deposited and (b) 950 $^\circ\text{C}$ an-             |    |

|      | nealed SiGe capacitors with 2 nm cap and W gate                                                | 78 |

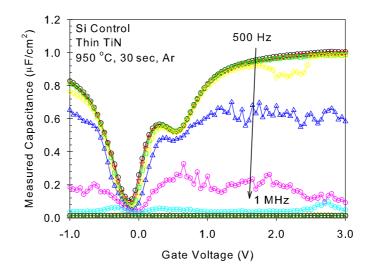

| 4.7  | Capacitance-voltage characteristics for Si control capacitors with thin                        |    |

|      | TiN gate following RTA2                                                                        | 79 |

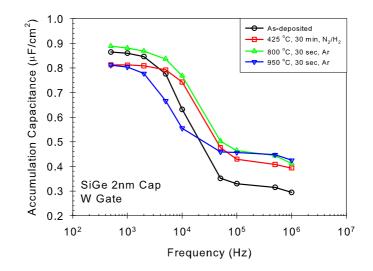

| 4.8  | Accumulation capacitance for SiGe capacitors with 2 nm cap and W gate                          |    |

|      | as a function of measurement frequency and anneal condition                                    | 80 |

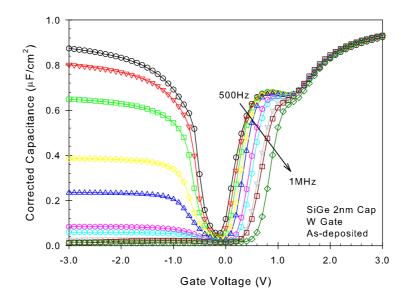

| 4.9  | Corrected C-V characteristics for as-deposited SiGe capacitors with 2 nm                       |    |

|      | cap and W gate                                                                                 | 81 |

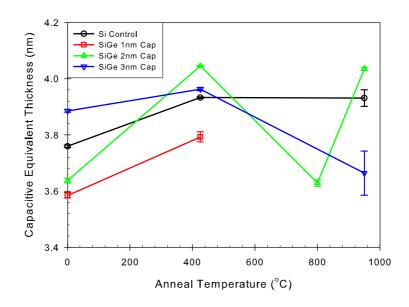

| 4.10 | Capacitive equivalent thickness (CET) for ${\sf Si}_{1-x}{\sf Ge}_x$ capacitors as a func-     |    |

|      | tion of anneal temperature                                                                     | 82 |

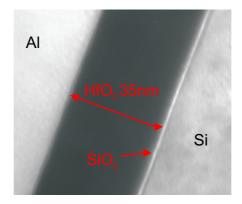

| 4.11 | TEM image of sputtered $HfO_2$ gate dielectric on silicon with Al gate                         |    |

|      | showing the presence of an $\ensuremath{\text{SiO}}_2$ interfacial layer. Reproduced with per- |    |

|      | mission from Raeissi [2007]                                                                    | 83 |

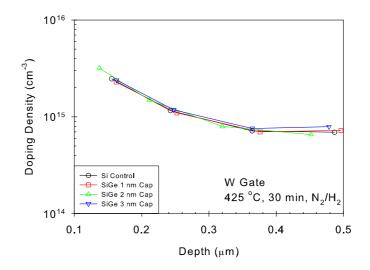

| 4.12 | Typical doping density profiles for both silicon and SiGe capacitors fol-                      |    |

|      | lowing PMA anneal                                                                              | 84 |

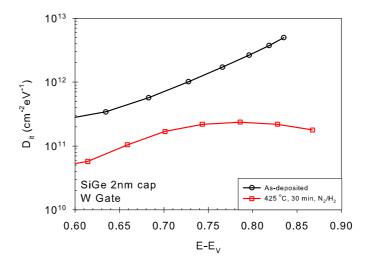

| 4.13 | Interface trap density distribution for SiGe capacitors with 2 nm Si cap.                      | 85 |

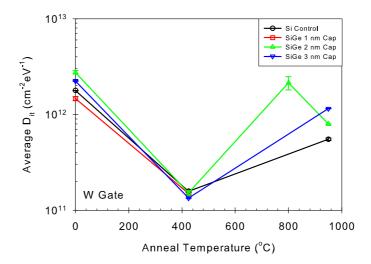

| 4.14 | Average interface trap densities for $Si_{1-x}Ge_x$ capacitors as a function of                |    |

|      | anneal temperature                                                                             | 86 |

|      | x                                                                                              |    |

|      |                                                                                                |    |

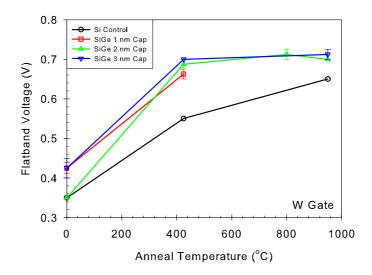

| 4.15 | Flatband voltage for silicon and SiGe capacitors as a function of cap                                               |     |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

|      | thickness and anneal condition                                                                                      | 87  |

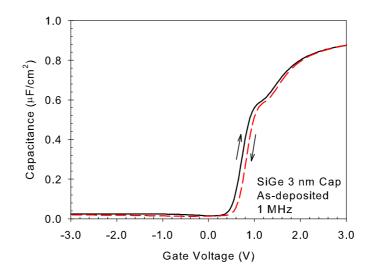

| 4.16 | High frequency C-V characteristics showing the clockwise hysteresis be-                                             |     |

|      | haviour for as-deposited SiGe capacitors with 3 nm Si cap                                                           | 88  |

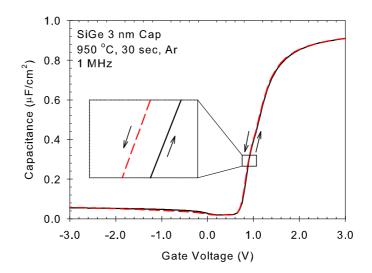

| 4.17 | High frequency C-V characteristics showing the clockwise hysteresis be-                                             |     |

|      | haviour for SiGe capacitors with 3 nm Si cap following RTA2                                                         | 89  |

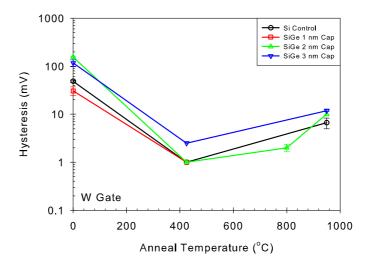

| 4.18 | Magnitude of hysteresis for ${\sf Si}_{1-x}{\sf Ge}_x$ capacitors with W gate as a func-                            |     |

|      | tion of anneal temperature                                                                                          | 90  |

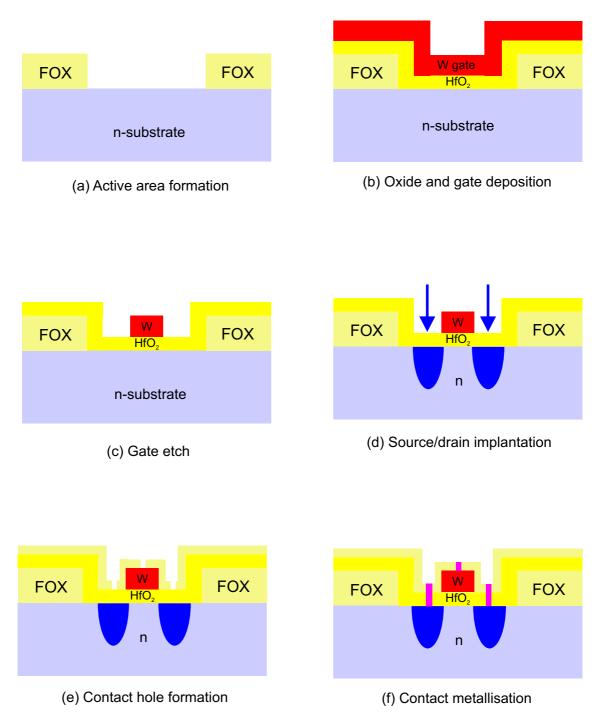

| 5.1  | Schematic of the process flow for ${\rm Si}_{1-x}{\rm Ge}_x/{\rm HfO}_2/{\rm W}$ transistors                        | 94  |

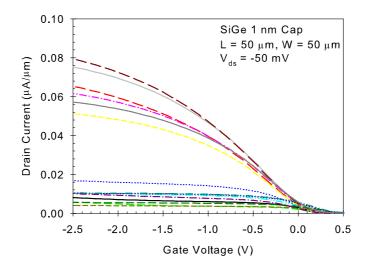

| 5.2  | Linear transfer characteristics for 50 $\mu{\rm m}$ x 50 $\mu{\rm m}$ SiGe transistors with                         |     |

|      | 1 nm Si cap highlighting the significant spread in device characteristics                                           |     |

|      | across a wafer                                                                                                      | 96  |

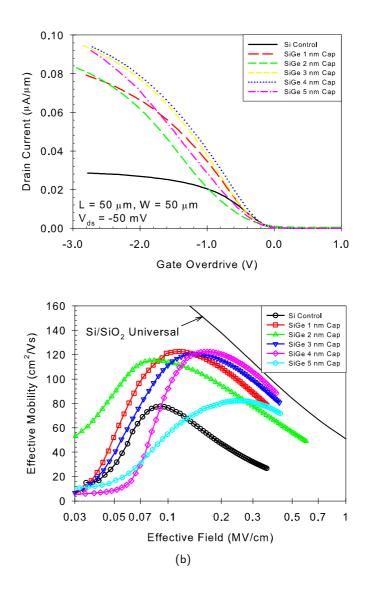

| 5.3  | (a) Linear drain current and (b) effective hole mobility as a function of                                           |     |

|      | effective field for the best-performing 50 $\mu{\rm m}$ x 50 $\mu{\rm m}$ Si $_{1-x}{\rm Ge}_x/{\rm HfO}_2/{\rm W}$ |     |

|      | gate pMOSFETs.                                                                                                      | 97  |

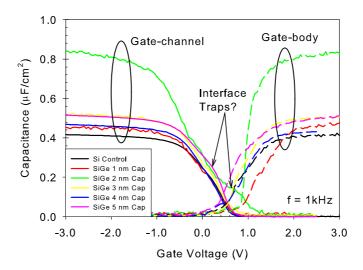

| 5.4  | Typical split C-V characteristics for ${\sf Si}_{1-x}{\sf Ge}_x/{\sf HfO}_2/{\sf W}$ gate pMOSFETs                  |     |

|      | taken at 1 kHz                                                                                                      | 99  |

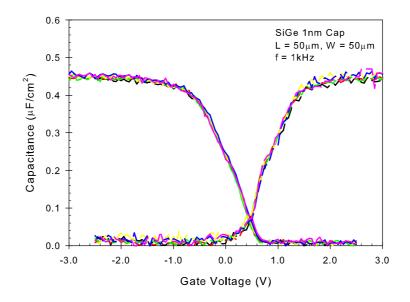

| 5.5  | Split C-V characteristics measured at 1 kHz for several 50 $\mu{\rm m}$ x 50 $\mu{\rm m}$                           |     |

|      | SiGe pMOSFETs with 1 nm Si cap.                                                                                     | 101 |

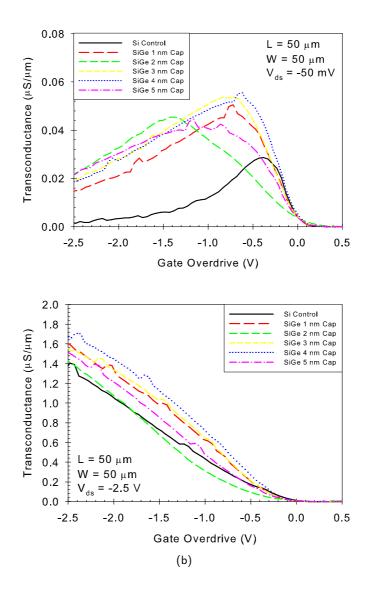

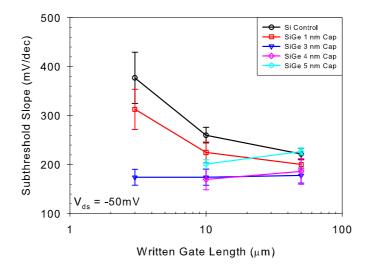

| 5.6  | (a) Linear and (b) saturation transconductance for ${\rm Si}_{1-x}{\rm Ge}_x/{\rm HfO}_2/{\rm W}$                   |     |

|      | gate transistors.                                                                                                   | 102 |

| 5.7  | Average field effect mobility for ${\rm Si}_{1-x}{\rm Ge}_x/{ m HfO}_2/{ m W}$ gate transistors as a                |     |

|      | function of written gate length                                                                                     | 103 |

| 5.8  | Average values for the subthreshold slope measured in the linear regime                                             |     |

|      | for $Si_{1-x}Ge_x/HfO_2/W$ gate transistors as a function of written gate length.                                   | 104 |

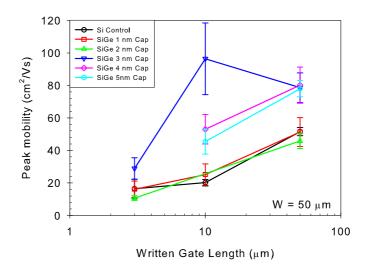

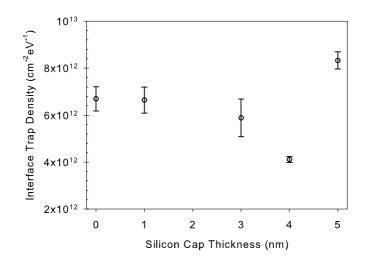

| 5.9  | Interface trap density measured from the subthreshold slope on ${\sf Si}_{1-x}{\sf Ge}_x/{\sf H}$  | $IfO_2/W$ |

|------|----------------------------------------------------------------------------------------------------|-----------|

|      | pMOSFETs as a function of Si cap thickness, where a cap thickness of                               |           |

|      | '0' has been used to represent the Si control. $\ldots$ $\ldots$ $\ldots$ $\ldots$                 | 105       |

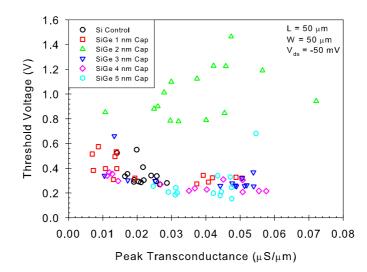

| 5.10 | Scatter plot of threshold voltage vs peak linear transconductance for                              |           |

|      | 50 $\mu$ m x 50 $\mu$ m transistors                                                                | 106       |

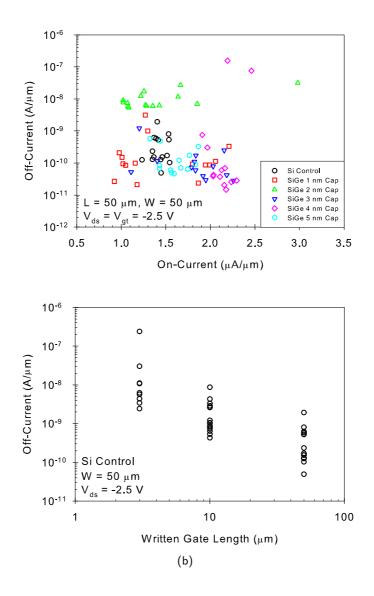

| 5.11 | (a) Saturation drain current versus off-current for ${\rm Si}_{1-x}{\rm Ge}_x/{\rm HfO}_2/{\rm W}$ |           |

|      | gate transistors and (b) off-current versus gate length for silicon control                        |           |

|      | devices.                                                                                           | 107       |

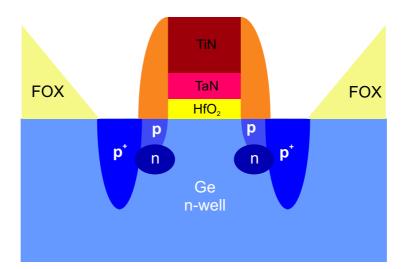

| 6.1  | Schematic of a Ge/HfO $_2$ /TaN/TiN pMOSFET                                                        | 112       |

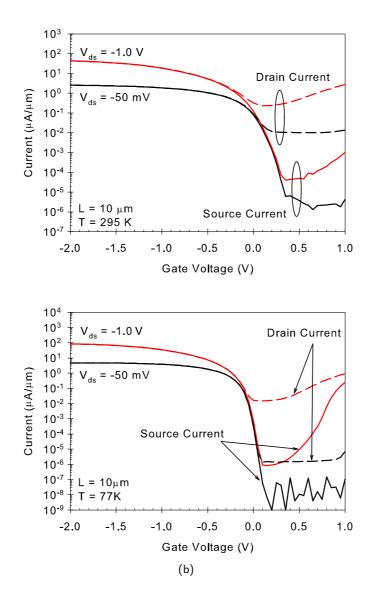

| 6.2  | Transfer characteristics for L = 10 $\mu m$ Ge pMOSFET measured at (a)                             |           |

|      | room temperature and (b) 77 K                                                                      | 114       |

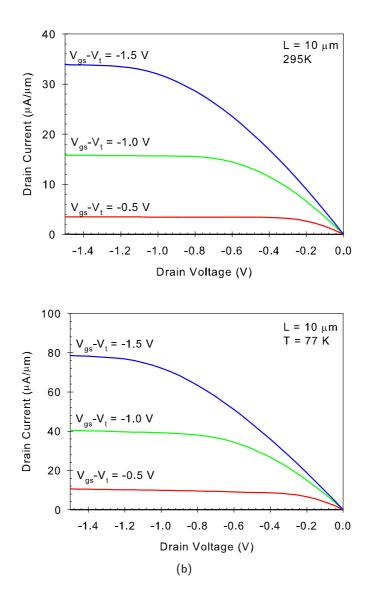

| 6.3  | Output characteristics of L $=$ 10 $\mu\text{m}$ Ge pMOSFET measured at (a)                        |           |

|      | room temperature and (b) 77 K                                                                      | 116       |

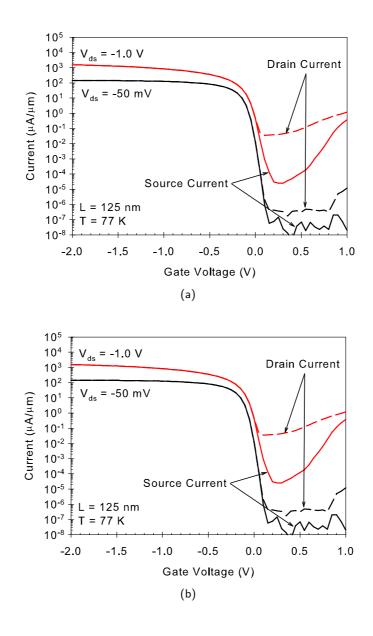

| 6.4  | Transfer characteristics of L = 125 nm Ge pMOSFET measured at (a)                                  |           |

|      | room temperature and (b) 77 K                                                                      | 117       |

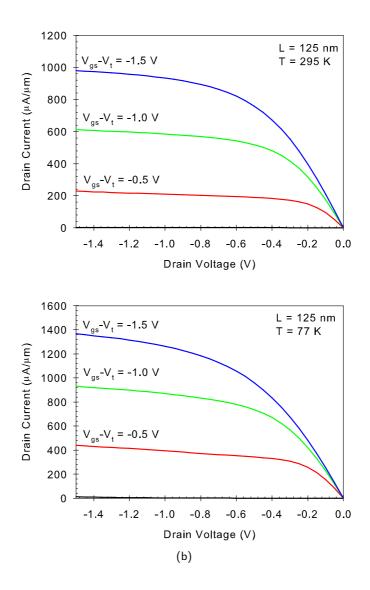

| 6.5  | Output characteristics of L $=$ 125 nm Ge pMOSFET measured at (a)                                  |           |

|      | room temperature and (b) 77 K                                                                      | 118       |

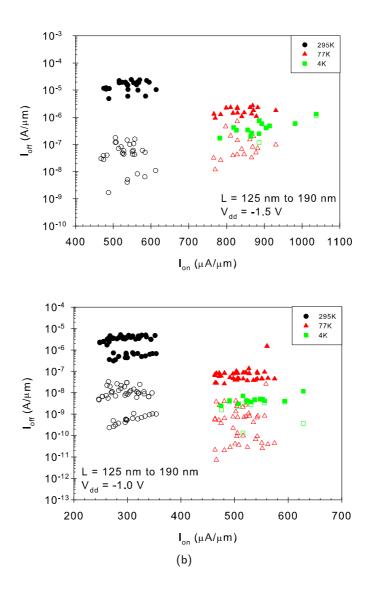

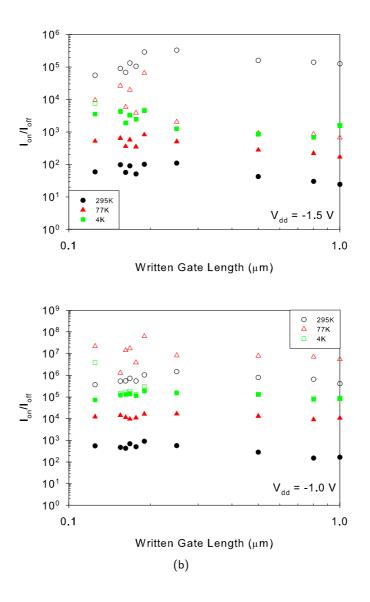

| 6.6  | $I_{off}$ versus $I_{on}$ for Ge pMOSFETs measured at both the source and the                      |           |

|      | drain at room temperature, 77 K and 4 K for power supply voltages                                  |           |

|      | of (a) -1.5 V and (b) -1.0 V. The open symbols represent the current                               |           |

|      | measured at the source; the closed symbols the current at the drain                                | 120       |

| 6.7  | $I_{\it on}/I_{\it off}$ ratio versus gate length for Ge pMOSFETs measured at both                 |           |

|      | the source and the drain at room temperature, 77 K and 4 K for power                               |           |

|      | supply voltages of (a) -1.5 V and (b) -1.0 V. The open symbols represent                           |           |

|      | the current measured at the source; the closed symbols the current at                              |           |

|      | the drain                                                                                          | 122       |

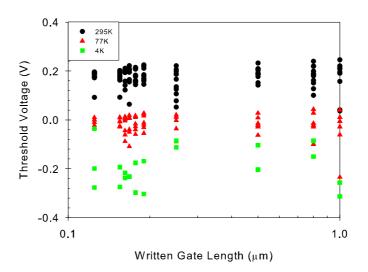

| 6.8  | Threshold voltage values for germanium $pMOSFETs$ as a function of                                    |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | gate length measured at room temperature, 77 K and 4 K                                                | 123 |

| 6.9  | Threshold voltage vs temperature for L = 10 $\mu m$ and L = 125 nm Ge                                 |     |

|      | devices                                                                                               | 124 |

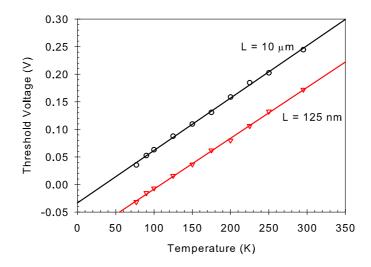

| 6.10 | Subthreshold slope versus gate length for devices measured at room tem-                               |     |

|      | perature and 77 K, with V $_{ds}$ $=$ (a) -50 mV and (b) -1.0 V                                       | 126 |

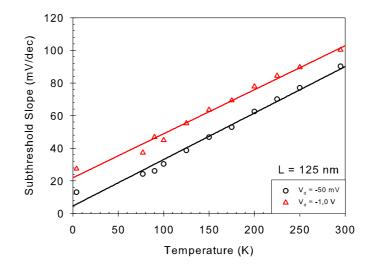

| 6.11 | Subthreshold slope versus temperature for a device with a gate length of                              |     |

|      | 125 nm with V $_{ds}=$ -50 mV and -1.0 V. $\hdots$                                                    | 127 |

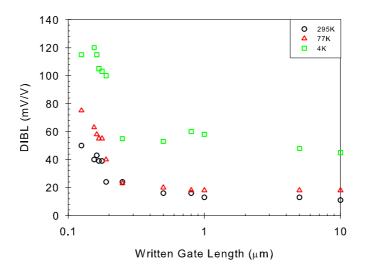

| 6.12 | DIBL as a function of gate length measured at room temperature, 77 K $$                               |     |

|      | and 4 K                                                                                               | 128 |

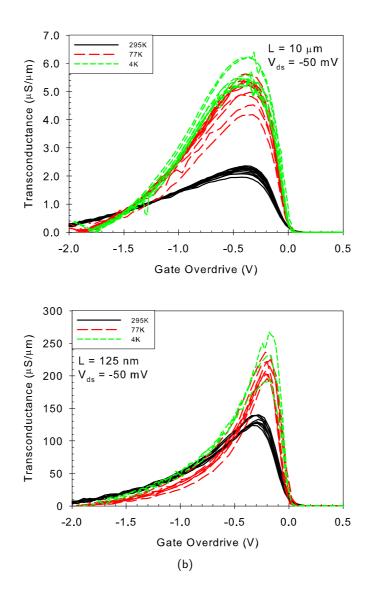

| 6.13 | Linear transconductance for a selection of devices with gate lengths of                               |     |

|      | (a) L = 10 $\mu m$ and (b) 125 nm at room temperature, 77 K and 4 K. $$ .                             | 129 |

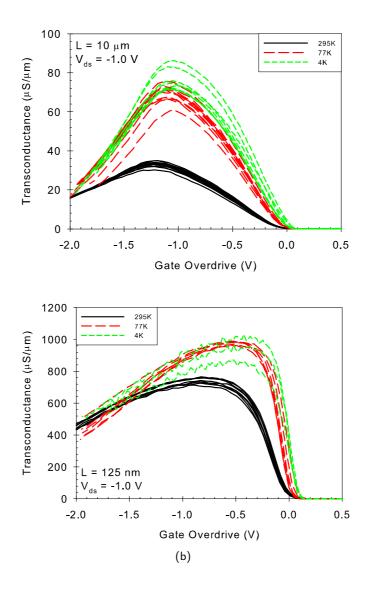

| 6.14 | Saturation transconductance for a selection of devices with gate lengths                              |     |

|      | of (a) L = 10 $\mu$ m and (b) 125 nm at room temperature, 77 K and 4 K.                               | 130 |

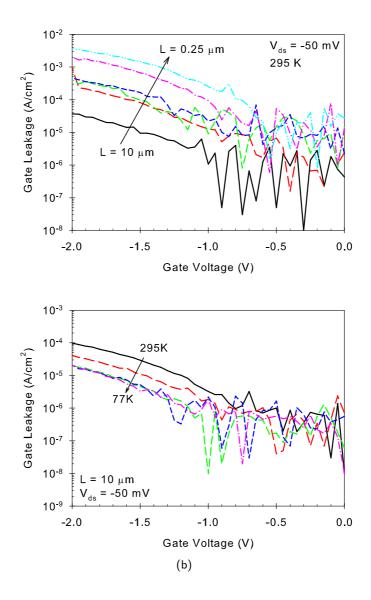

| 6.15 | (a) Gate leakage at room temperature as a function of gate length (b)                                 |     |

|      | as a function of temperature for an L = 10 $\mu m$ device                                             | 132 |

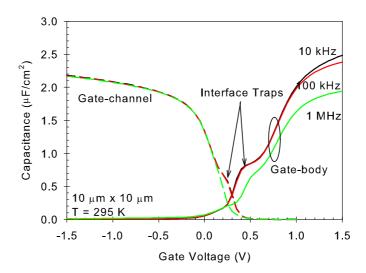

| 6.16 | Split C-V characteristics of a 10 $\mu{\rm m}$ x 10 $\mu{\rm m}$ device as a function of              |     |

|      | frequency at room temperature.                                                                        | 134 |

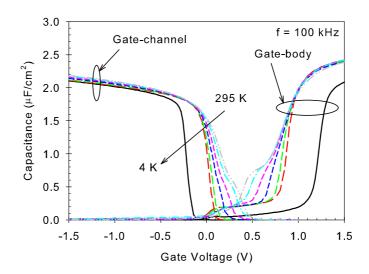

| 6.17 | Split C-V characteristics of a 10 $\mu{\rm m}$ x 10 $\mu{\rm m}$ device as a function of              |     |

|      | temperature                                                                                           | 135 |

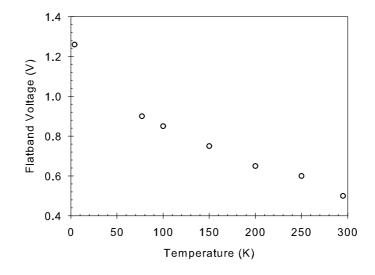

| 6.18 | Flatband voltage as a function of temperature for a 10 $\mu{\rm m}$ x 10 $\mu{\rm m}.$                | 135 |

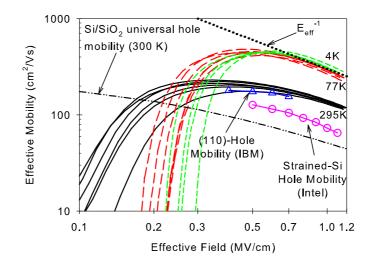

| 6.19 | Effective hole mobility at room temperature, 77 K and 4 K for 10 $\mu{\rm m}{\rm x}{\rm 10}\mu{\rm }$ | m   |

|      | germanium pMOSFETs. Data also includes hole mobility values for                                       |     |

|      | (100)-silicon [Yang et al., 2003] and for uniaxial strained silicon with                              |     |

|      | SiGe source/drain regions ([Ghani et al., 2003])                                                      | 137 |

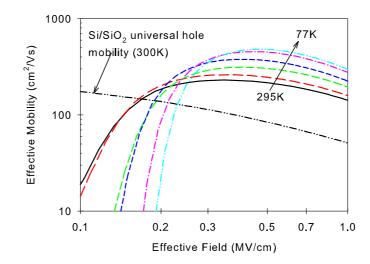

| 6.20 | Effective hole mobility vs effective field for a 10 $\mu{\rm m}$ x 10 $\mu{\rm m}$ germanium          |     |

|      | pMOSFET as a function of temperature                                                                  | 139 |

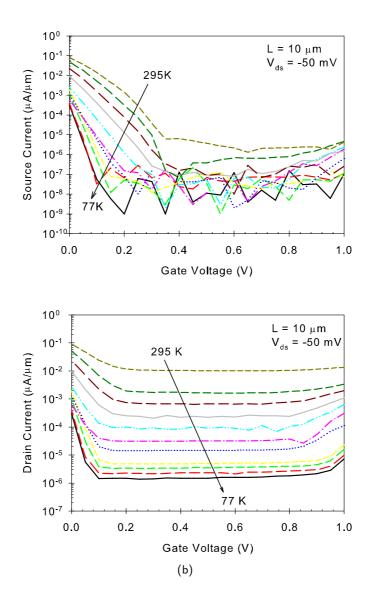

| 6.21 Leakage current measured from (a) the                                  | source current and (b) the drain            |

|-----------------------------------------------------------------------------|---------------------------------------------|

| current on 10 $\mu$ m x 10 $\mu$ m devices at a                             | low drain bias of $V_{ds} = -50 \text{ mV}$ |

| as a function of temperature                                                |                                             |

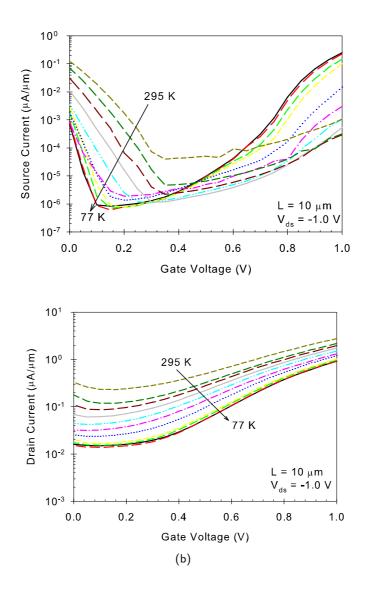

| 6.22 Leakage current measured from (a) the                                  | source current and (b) the drain            |

| current on 10 $\mu$ m x 10 $\mu$ m devices at a                             | high drain bias of $V_{ds}=$ -1.0 V         |

| as a function of temperature                                                |                                             |

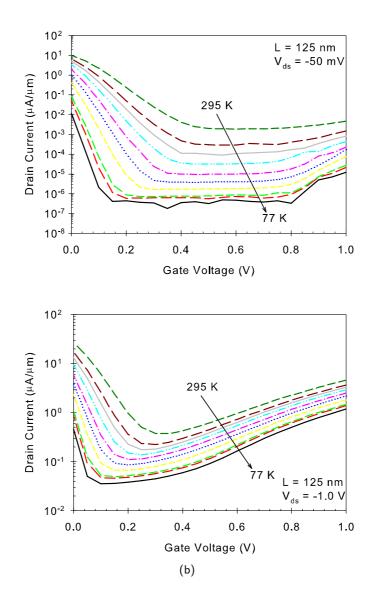

| 6.23 Leakage current measured on 125 nm x                                   | 10 $\mu$ m devices with (a) V $_{ds}$ = -   |

| 50 mV and (b) ${ m V}_{ds}=$ -1.0 V, as a func                              | tion of temperature                         |

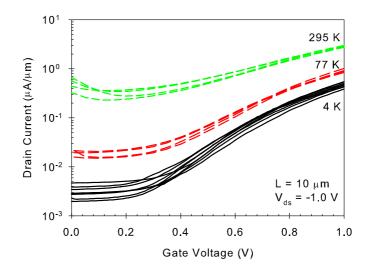

| 6.24 Leakage current measured on a selection                                | n of 10 $\mu$ m x 10 $\mu$ m devices with   |

| $V_{ds}=$ -1.0 V, at room temperature, 77                                   | K and 4 K                                   |

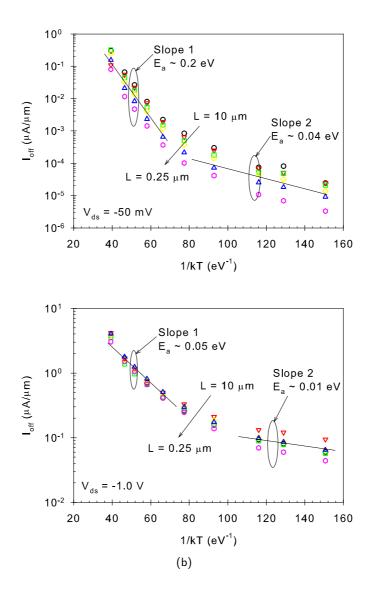

| 6.25 Arrhenius plots of $I_{off}$ vs $1/k_BT$ for                           | devices with gate lengths from              |

| 10 $\mu$ m to 0.25 $\mu$ m for (a) V $_{ds}$ = -50 m                        | V and (b) $V_{ds} = -1.0$ V 146             |

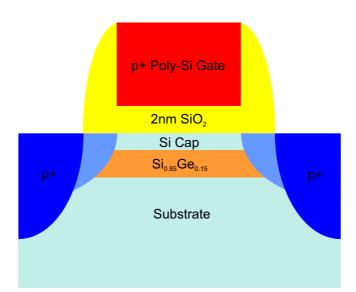

| 7.1 Device schematic of $Si_{0.85}Ge_{0.15}$ MOS                            | EET used to study help corrier              |

| 7.1 Device schematic of Si <sub>0.85</sub> Ge <sub>0.15</sub> MOS velocity. |                                             |

| -                                                                           |                                             |

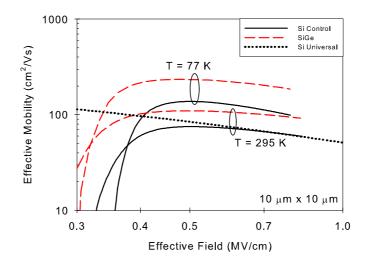

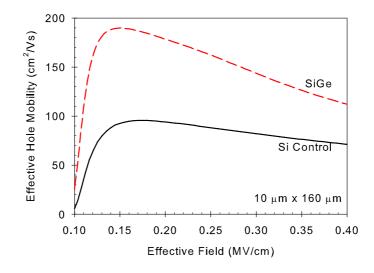

| 7.2 Comparison of hole effective mobility f                                 |                                             |

| control pMOSFETs at room temperatur                                         |                                             |

|                                                                             |                                             |

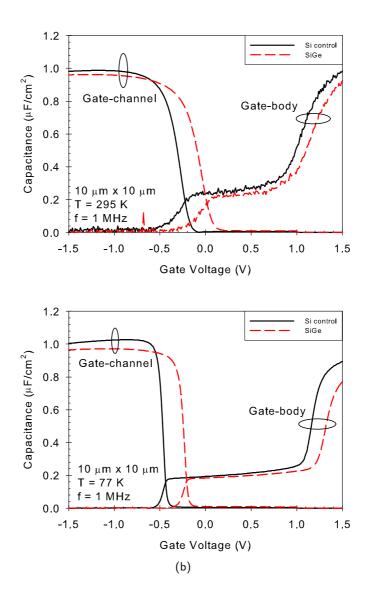

| 7.3 Split CV characteristics of 10 $\mu$ m x 1                              |                                             |

| measured at (a) room temperature and                                        |                                             |

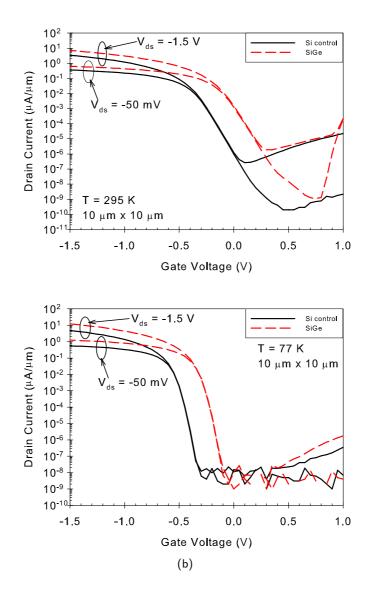

| 7.4 Transfer characteristics for 10 $\mu$ m x 1                             |                                             |

| measured at (a) room temperature and                                        | (b) 77 K 157                                |

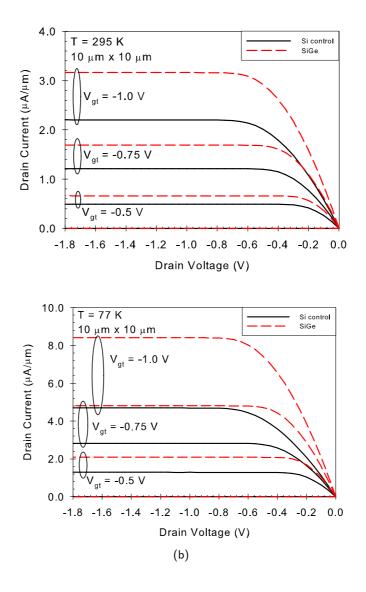

| 7.5 Output characteristics for 10 $\mu$ m x 10 $\mu$                        |                                             |

| sured at (a) room temperature and (b) 7                                     | 7 K as a function of gate overdrive.158     |

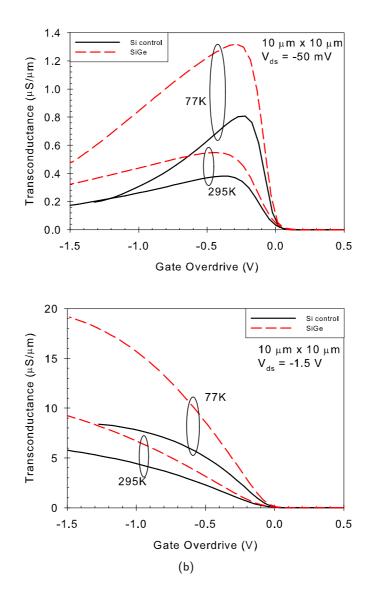

| 7.6 (a) Linear and (b) saturation transcond                                 |                                             |

| and Si pMOSFETs at room temperatur                                          | e and 77 K 160                              |

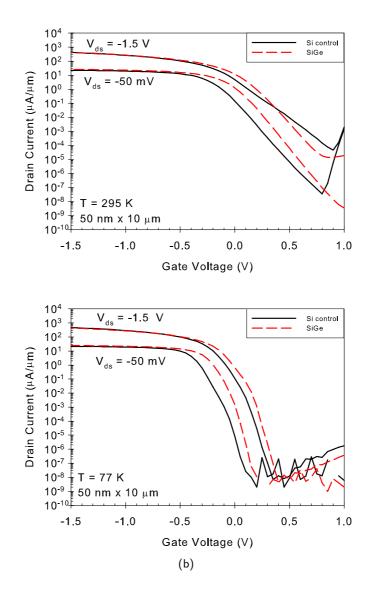

| 7.7  | Transfer characteristics for 50 nm x 10 $\mu\text{m}$ SiGe and Si pMOSFETs          |      |

|------|-------------------------------------------------------------------------------------|------|

|      | measured at (a) room temperature and (b) 77 K                                       | 161  |

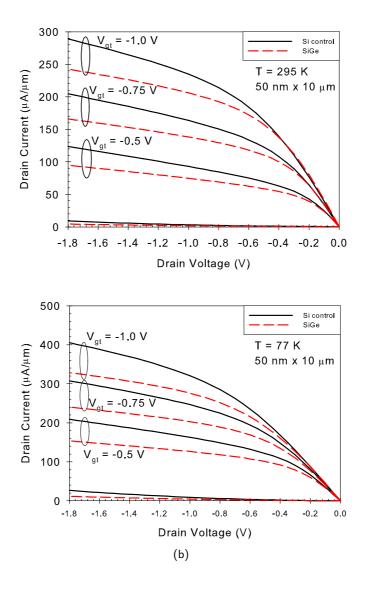

| 7.8  | Output characteristics for 50 nm x 10 $\mu {\rm m}$ SiGe and Si pMOSFETs mea-       |      |

|      | sured at (a) room temperature and (b) 77 K                                          | 163  |

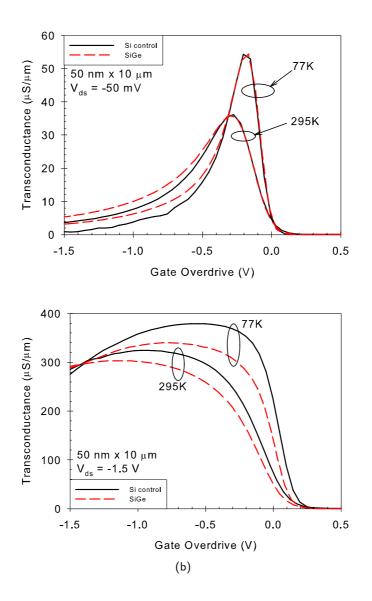

| 7.9  | (a) Linear and (b) saturation transconductance for 50 nm $\times$ 10 $\mu m$ SiGe   |      |

|      | and Si pMOSFETs measured at room temperature and 77 K                               | 164  |

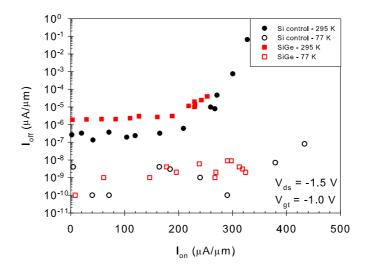

| 7.10 | $I_{on}$ versus $I_{off}$ for Si and SiGe pMOSFETs at room temperature and 77 K     | .165 |

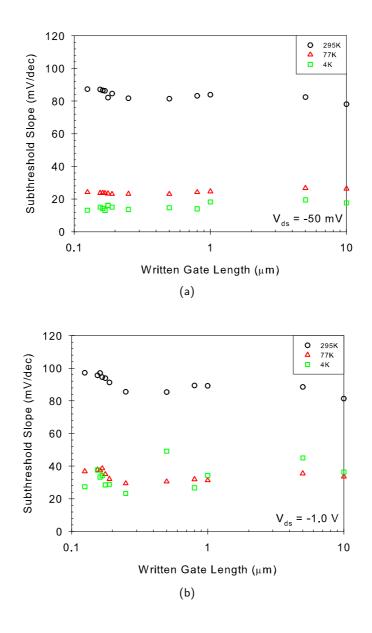

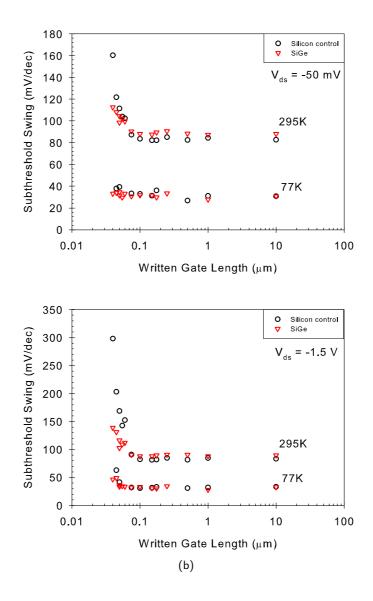

| 7.11 | Subthreshold slope measured in the (a) linear and (b) saturation regime             |      |

|      | for SiGe and Si control pMOSFETs as a function of written gate length               |      |

|      | at room temperature and 77 K                                                        | 166  |

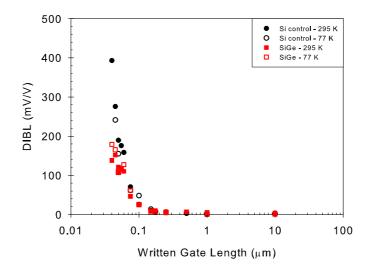

| 7.12 | DIBL for SiGe and Si pMOSFETs at room temperature and 77 K as a                     |      |

|      | function of written gate length                                                     | 167  |

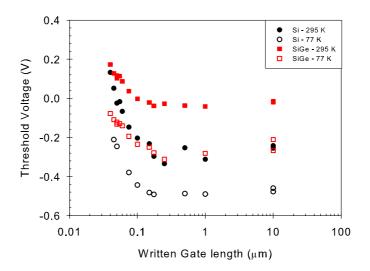

| 7.13 | Threshold voltage for SiGe and Si pMOSFETs at room temperature and                  |      |

|      | 77 K as a function of written gate length                                           | 168  |

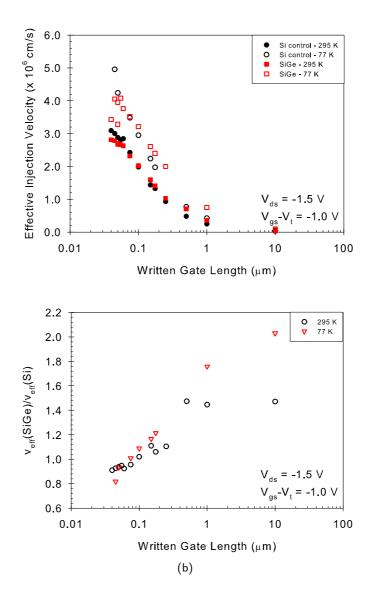

| 7.14 | (a) Hole carrier velocity (after Lochtefeld et al. [2002]) and (b) ratio of         |      |

|      | the hole carrier velocity for SiGe and silicon control pMOSFETs measured            |      |

|      | at room temperature and 77 K                                                        | 171  |

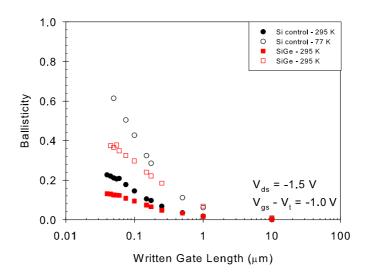

| 7.15 | Ballisticity as a function of written gate length for SiGe and Si pMOS-             |      |

|      | FETs at room temperature and 77 K                                                   | 173  |

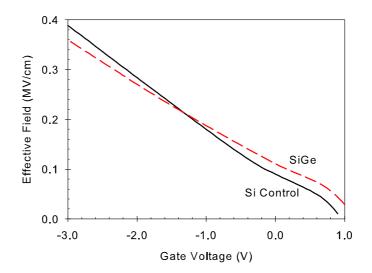

| 7.16 | Vertical effective field extracted from split C-V measurements against              |      |

|      | gate voltage for Si control and strained SiGe pMOSFETs                              | 175  |

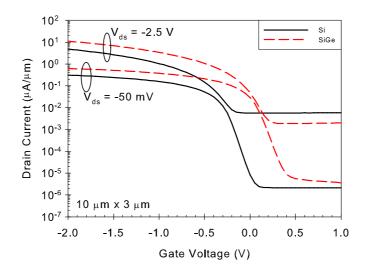

| 7.17 | Comparison of the linear and saturation transfer characteristics of 10 $\mu{\rm m}$ |      |

|      | x 3 $\mu$ m Si and SiGe pMOSFETs                                                    | 176  |

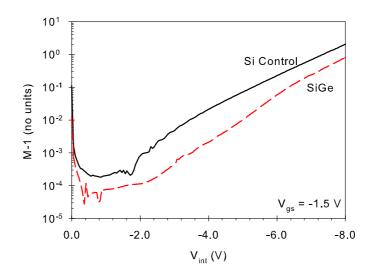

| 7.18 | Impact ionisation multiplication coefficient against intrinsic voltage for          |      |

|      | Si control and strained SiGe pMOSFETs.                                              | 177  |

| 7.19 | Low field hole mobility against effective vertical field for Si and strained        |      |

|      | SiGe pMOSFETs.                                                                      | 177  |

## Acknowledgments

Firstly, I would like to thank Dr. David Leadley, Prof. Evan Parker and Prof. Terry Whall for their support during this work. Terry deserves special praise for the number of hours spent proof-reading this thesis despite "retiring" a year ago! Secondly, I have to thank both past and present members of the Nano-Silicon Group for providing what was, on the whole, an enjoyable place to work for the last few years. In particular, Dr. Gareth Nicholas for help with both the Ge and high-field work, Chris Beer for his efforts in helping to set up the low temperature probe station, and Steve Thomas for additional electrical characterisation work deserve special mention. This work would not have been possible without the collaboratory efforts involving several institutions across Europe, and naturally I thank my working colleagues at IMEC, KTH, Chalmers University, AMO and LETI-CEA for providing the samples necessary for the work in this thesis. Finally, I wish to thank my friends and family who are too numerous to mention individually for all their support during the last few years. Finally, I thank my dad, Jim, and my mum, Yvonne for all their love and support! Thank-you!

# Declarations

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has not been submitted for a degree at any other University. Except where specifically stated, all of the work described in this thesis was carried out by the author or under his direction in the Department of Physics at the University of Warwick from September 2003 until September 2007.

# **Publications**

The following publications and presentations contain material included in this thesis:

A. Dobbie, S. M. Thomas, D. J. Fulgoni, B. Raeissi, O. Engstrom, M. Schmidt, M. C. Lemme, P.-E. Hellstrom, E. H. C. Parker, D. R. Leadley and T. E. Whall, 'Electrical Characterisation of  $Si_{1-x}Ge_x$  pMOSFETs using Sputtered HfO<sub>2</sub> Dielectric and W Metal Gate,' to be submitted.

A. Dobbie, G. Nicholas, M. Meuris, E. H. C. Parker, D. R. Leadley and T. E. Whall, 'Low Temperature Electrical Characterisation and Analysis on the Performance of Deep Submicron Germanium pMOSFETs,' to be submitted.

A. Dobbie, G. Nicholas, M. Meuris, E. H. C. Parker, and T. E. Whall, 'Low Temperature Performance of Deep Submicron Germanium pMOSFETs,' Proceedings of 2007 International Workshop on Electron Devices and Semiconductor Technology, Beijing, China, June 2007.

G. Nicholas, A. Dobbie, T. J. Grasby, T. E. Whall and E. H. C. Parker, 'Impact Ionisation in Strained SiGe pMOSFETs,' Electronics Lett., 41(16), pp925-927, 2005

## Abstract

It is now apparent that the continued performance enhancements of silicon metaloxide-semiconductor field effect transistors (MOSFETs) can no longer be met by scaling alone. High-mobility channel materials such as strained  $Si_{1-x}Ge_x$  and Ge are now being seriously considered to maintain the performance requirements specified by the semiconductor industry. In addition, alternative gate dielectric, or high- $\kappa$  dielectrics, will also be required to meet gate leakage requirements.

This work investigates the properties of using strained  $Si_{1-x}Ge_x$  or Ge as alternative channel materials for pMOSFETs incorporating hafnium oxide (HfO<sub>2</sub>) high- $\kappa$  gate dielectric. Whilst the SiGe pMOSFETs (x = 0.25) exhibited an enhancement in hole mobility (300 K) over comparable silicon control pMOSFETs with sputtered HfO<sub>2</sub> dielectric, high Coulomb scattering and surface roughness scattering relating to the dielectric deposition process meant that the effective hole mobilities were degraded with respect to the silicon universal curve.

Germanium channel pMOSFETs with halo-doping and HfO<sub>2</sub> gate dielectric deposited by atomic layer deposition showed high hole mobilities of 230 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 480 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature and 77 K, respectively. Analysis of the off-state current for the Ge pMOSFETs over a range of temperatures indicated that band-to-band tunnelling, gate-induced drain leakage and other defect-assisted leakage mechanisms could all be important.

Hole carrier velocity and impact ionisation were also studied in two batches of buried channel SiGe pMOSFETs with x = 0.15 and x = 0.36, respectively. SiGe channel pMOSFETs were found to exhibit reduced impact ionisation compared to silicon control devices, which has been attributed to a strain-induced reduction of the density of states in the SiGe conduction and valence bands. Analysis of the hole carrier velocity indicated that pseudomorphic SiGe offered no performance enhancements over Si below 100 nm, possibly due to higher ion implantation damage and strain relaxation of the strained SiGe channel. The results indicate that velocity overshoot effects might not provide the performance improvements at short channel lengths that was previously hoped for.

# Abbreviations

#### A Area

- ALD Atomic layer deposition

- BTBT Band-to-band-tunnelling

- C Capacitance

- $C_{dep}$  Depletion capacitance

- $C_{qb}$  Gate-body capacitance

- $C_{gc}$  Gate-channel capacitance

- $C_{hf}$  High-frequency capacitance

- $C_{it}$  Interface trap capacitance

- $C_{lf}$  Low-frequency capacitance

- $C_m$  Measured capacitance

- $C_{ox}$  Oxide capacitance

- ${\it C}_p\,$  Parallel equivalent circuit capacitance

- $C_s$  Series equivalent circuit capacitance

- CET Capacitive equivalent thickness

- CMOS Complimentary metal-oxide-semiconductor

- CVD Chemical vapour deposition

- $D_p$  Einstein diffusion coefficient for holes

- DIBL Drain-induced barrier lowering

- $D_{it}$  Interface trap density

- DUT Device under test

- E Energy

- $E_a$  Activation energy

- $E_c$  Conduction band edge energy

- $E_F$  Fermi level

- $E_i$  Intrinsic Fermi level

- $E_v$  Valence band edge energy

- EOT Equivalent oxide thickness

- $\epsilon_0$  Permittivity of free space (= 8.85 x 10<sup>-14</sup> F/cm)

- $\varepsilon\,$  Electric field

- $\varepsilon_{eff}$  Effective vertical field

- f Frequency

- FOX Field oxide

- $\phi_B$  Barrier height

- $\phi_{ms}$  Metal-semiconductor work function difference

- $g_m$  Transconductance

- $g_{mi}$  Intrinsic transconductance

- G Conductance

- $G_m$  Measured conductance

- $G_p$  Parallel equivalent circuit conductance

- GIDL Gate-induced drain leakage

- HBT Heterojunction bipolar transistor

- HRTEM High-resolution transmission electron microscopy

- h Planck's constant (=  $6.63 \times 10^{-34}$  Js)

- I Current

- $I_b$  Body current

- $I_{ds}$  Drain current

- Ids,sat Saturation drain current

- I<sub>off</sub> Off-state current

- Ion On-state current

- $I_s$  Source current

ITRS International Technology Roadmap for Semiconductors

- ${\cal J}\,$  Current density

- $J_{DT}$  Current density due to direct tunnelling

- k Wave vector

$k_B$  Boltzmann's constant (=1.38 x 10<sup>-23</sup>)

- $\kappa\,$  Relative dielectric constant

- L Gate length

- $L_D$  Debye length

- $L_{eff}$  Effective channel length

LPCVD Low pressure chemical vapour deposition

$m_0$  Free electron mass (= 9.1 x 10<sup>-31</sup> kg)

- $m^*$  Effective mass

- $m_{ij}^*$  Effective mass in tensor form

M Avalanche multiplication factor

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field-effect-transistor

- $\mu$  Mobility

- $\mu_{\it eff}\,$  Effective mobility

- n Electron density

- $N_D$  Doping density

- $N_{hys}$  Hysteresis charge density

- $N_s$  Inversion sheet density

- PDA Post-oxide deposition anneal

- PMA Post-metallisation anneal

- q Electron charge (=  $1.6 \times 10^{-19}$  C)

- $Q_{dep}$  Depletion charge density

- $Q_{inv}$  Inversion charge density

- $Q_{ox}$  Oxide charge density

- p Hole density

- $r_c$  Backscattering coefficient

- R Resistance

- $R_{channel}$  Channel resistance

- $R_d$  Drain series resistance

- $R_m$  Measured resistance

- $R_s$  Source series resistance

- $R_{sd}$  Source-drain series resistance

- RTA Rapid thermal anneal

- ${\cal S}~$  Subthreshold slope

- SCEs Short channel effects

- T Temperature

- $t_{ox}$  Oxide thickness

- $\tau\,$  Relaxation time

- v Carrier velocity

- $v_{eff}$  Effective carrier velocity

- $v_T$  Thermal velocity

- V Voltage

- $V_c(x)$  Channel potential at a distance x from the source

- $V_{dd}$  Power-supply voltage

- $V_{ds}$  Drain-source voltage

- $V'_{ds}$  Intrinsic drain voltage

- $V_{ds,sat}$  Saturation drain voltage

- $V_{fb}$  Flatband voltage

- $V_{gs}$  Gate-source voltage

- $V'_{qs}$  Intrinsic gate voltage

- V<sub>int</sub> Intrinsic voltage

- $V_t$  Threshold voltage

- VLSI Very large scale integration

- VTA Threshold voltage adjustment implant

- W Channel width

- $\omega$  Angular frequency

- XPS X-ray photoelectron spectroscopy

- Y Admittance

- $Y_p\,$  Parallel equivalent circuit admittance

- $\psi_B~~{\rm Bulk}$  potential

- $\psi_S~{\rm Surface}~{\rm potential}$

- Z Impedance

- $\mathbb{Z}_p$  Parallel equivalent circuit impedance

## Chapter 1

## Introduction

#### 1.1 The Semiconductor Industry

The semiconductor industry the largest industry in the world with global sales totalling \$213 billion in 2004 [SIA-Online, 2005]. At the core of this technology lies the metal-oxide-semiconductor field effect transistor (MOSFET) - effectively nothing more than a simple switch, but perhaps the most numerous man-made structure ever produced. The current generation of Intel Core 2 Duo microprocessors, fabricated at the 65nm technology node, contain a staggering 291 million transistors in an area of just 118 mm<sup>2</sup> [Intel, 2005].

For the last 30 years, silicon (Si) based technologies have dominated the industry, accounting for more than 97% of all microelectronic devices [Paul, 2004]. The dominance of silicon is due to a combination of both its physical properties and its high natural abundance and is therefore inexpensive. The oxide of silicon, SiO<sub>2</sub>, forms an excellent insulator between the gate electrode and the channel in a MOSFET with a low defect density at the Si/SiO<sub>2</sub> interface, which is typically  $\sim 10^{10}$  cm<sup>-2</sup> [Nicollian and Brews, 1982]. In addition, its excellent insulating properties can also be exploited as a mask during device fabrication [Sze, 1983]. The growth of the semiconductor industry is based upon an observation by Gordon Moore, who in 1965, noted that the number of transistors on an integrated circuit doubles approximately every two years - an observation that has since become known as *Moore's Law* [Moore, 1965]. This remarkable feat has been achieved through a phenomenon known as *scaling* - a systematic reduction of the MOSFET dimensions. In the main this has been achieved by advancements in device fabrication techniques and in particular, advancements in lithographic techniques that allow ever-decreasing dimensions to be defined.

However, despite the historical success of scaling, it is now very clear that the continued performance enhancements in complimentary metal-oxide-semiconductor (CMOS) circuits that the industry has become accustomed to, cannot be achieved by scaling alone. Indeed, a major concern is the cost of new fabrication plants, predicted to exceed \$10 billion by 2010 [Paul, 1999]. However, of even greater importance could be that MOSFET dimensions are rapidly approaching a regime where the key device features consist of just a few hundred atoms, such that quantum effects such as tunnelling become increasingly problematic, resulting in higher leakage currents and power consumption. Transistors with written gate lengths of 35 nm and 1.2 nm silicon oxynitride gate dielectric are already in high-volume production [Tyagi et al., 2005]. In addition, other effects such as random dopant fluctuations are likely to become critical in achieving uniform characteristics across a wafer [Asenov et al., 2003].

However, despite the industry pushing the boundaries closer and closer to its fundamental limit, there still remains great optimism that continued performance enhancements can be maintained using silicon-based technologies in the next few years. There are many materials with intrinsically superior electrical properties compared to silicon, which have found roles in niche market applications such as optical devices and the high frequency components of mobile communication devices. One of the most promising materials is *germanium* (Ge).

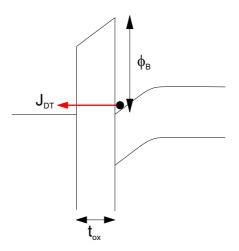

Figure 1.1: Schematic of direct tunnelling current,  $J_{DT}$ , through an oxide of thickness,  $t_{ox}$ , with a barrier height,  $\Phi_B$ .

### **1.2** High- $\kappa$ Dielectrics

The quality of the Si/SiO<sub>2</sub> interface is arguably the single-most important reason for the dominance of silicon in the microelectronics industry despite there being several known materials with superior electronic properties. However, the current scaling trends for CMOS devices, as specified by the International Technology Roadmap for Semiconductors (ITRS), dictates that the thickness of the gate dielectric should be reduced to below 1 nm by the end of the roadmap [ITRS, 2006 Update]. However, this results in a large increase in the gate leakage current due to quantum mechanical tunnelling, increasing exponentially with decreasing oxide thickness [Plummer and Griffin, 2001]. The gate leakage current due to direct tunnelling is given by:

$$J_{DT} = \frac{A}{t_{ox}^2} exp\left(-2t_{ox}\sqrt{\frac{2m^*q\phi_B}{\hbar^2}}\right)$$

(1.1)

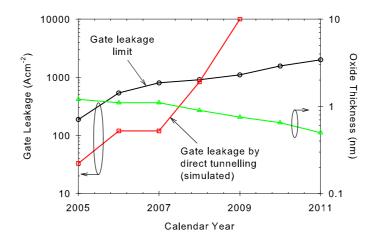

where A is a constant,  $t_{ox}$  is the oxide thickness,  $m^*$  is the carrier effective mass and  $\phi_B$  is the barrier height. The direct tunnelling gate leakage exhibits an exponential dependence on both the physical oxide thickness and the barrier height (Figure 1.1). Figure 1.2 shows the gate leakage limit and oxide thickness, as specified

Figure 1.2: Gate leakage current and oxide thickness for silicon oxynitride as specified by the ITRS. The simulated gate leakage for a given oxide thickness is also shown. After ITRS [2006 Update].

by the ITRS [2006 Update], for high-performance devices in the forthcoming years. Also shown, are simulated results for the gate leakage due to *direct tunnelling* for bulk, planar silicon MOSFETs with a silicon oxynitride gate dielectric. The simulated results show that there exists a 'crossover point' such that beyond 2008, the gate leakage limit cannot be met using silicon dioxide (or oxynitride) because of direct tunnelling. This means that silicon dioxide has to be replaced as gate dielectric by a material with higher permittivity than SiO<sub>2</sub>, a so-called *high-\kappa dielectric* in order to achieve the same capacitive coupling between the gate and the channel but for a thicker physical thickness to suppress tunnelling.

The gate capacitance, C, of a MOSFET can be considered as a parallel plate according to:

$$C = \frac{\kappa \epsilon_0 A}{t_{ox}} \tag{1.2}$$

where A is the area of the capacitor,  $\kappa$  is the dielectric constant,  $\epsilon_0$  is the permittivity of free space (8.85 × 10<sup>14</sup> F/cm) and  $t_{ox}$  is the thickness of the gate oxide. For high- $\kappa$  dielectrics, it is convenient to define an *equivalent oxide thickness* (EOT) as being the theoretical physical thickness of SiO<sub>2</sub> required to achieve the same capacitance as that provided by an alternative dielectric, with a dielectric constant greater than that of SiO<sub>2</sub>. Thus, the equivalent oxide thickness can be expressed in terms of an alternative dielectric with a dielectric constant,  $\kappa_{high-\kappa}$ , and physical thickness,  $t_{high-\kappa}$ , according to [Wilk et al., 2001]:

$$EOT = \frac{\kappa_{SiO_2}}{\kappa_{high-\kappa}} t_{high-\kappa} = \frac{3.9}{\kappa_{high-\kappa}} t_{high-\kappa}$$

(1.3)

This means, for example, that an alternative dielectric with a dielectric constant of 20 and a physical thickness of 5 nm could be used to replace  $SiO_2$  to achieve an EOT of 1 nm, providing a physically thicker barrier to suppress the gate leakage due to direct tunnelling.

In selecting an alternative high- $\kappa$  dielectric to replace silicon dioxide, there are several properties other than the dielectric constant itself, which must be given due consideration. Barrier height, thermodynamic stability, interface quality, film morphology, gate compatibility, process compatibility and reliability have all been shown to be important [Wallace and Wilk, 2005]. At the time of writing, the most promising candidates appear to be hafnium oxide (HfO<sub>2</sub>) and zirconium oxide (ZrO<sub>2</sub>).

Intel have recently announced that production of transistors at the 45 nm technology node will commence later this year and that these transistors will include high- $\kappa$  gate dielectrics [Intel, 2007].

### 1.3 Germanium

Germanium channel transistors have long been an attractive alternative to silicon for CMOS circuits, mainly due to electron and hole bulk mobility values being two and four times that of silicon, respectively (Table 1.1). In addition, the electron and hole mobility values are closer than those of silicon, which would enable a more symmetrical

| Property                             | Silicon             | Germanium           |

|--------------------------------------|---------------------|---------------------|

| Electron bulk mobility (cm $^2$ /Vs) | 1450                | 3900                |

| Hole bulk mobility ( $cm^2/Vs$ )     | 450                 | 1900                |

| Electron effective mass, $m^*/m_0$   | $m_l^* = 0.98$      | $m_l^* = 1.64$      |

|                                      | $m_t^*=0.19$        | $m_t^* = 0.082$     |

| Hole effective mass, $m^*/m_0$       | $m_{lh}^{*} = 0.16$ | $m_{lh}^* = 0.044$  |

|                                      | $m_{hh}^* = 0.49$   | $m_{hh}^{*} = 0.28$ |

| Melting point (°C)                   | 1415                | 937                 |

| Band gap (eV)                        | 1.12                | 0.66                |

Table 1.1: Important properties of silicon and germanium relevant for CMOS device processing (after Sze [1981]).

CMOS. Finally, the lower melting point of germanium compared to silicon, and the lower dopant activation energies in germanium, would allow the thermal budget of CMOS processing to be substantially reduced.

In fact, the first demonstration of the transistor, the bipolar transistor, back in 1948, used germanium as the active material [Bardeen and Brattain, 1948]. However, the absence of good quality native oxide has, to date, led to germanium only playing a bit-part role in the microelectronics industry. But with the inevitable replacement of  $SiO_2$  as gate dielectric with an alternative high- $\kappa$  dielectric, silicon's dominance in the microelectronics industry could be compromised. There have already been numerous publications on germanium pMOSFETs with hole mobilities exceeding those in silicon [Shang et al., 2003, Ritenour et al., 2006]. However, even at this early stage, results for germanium nMOSFETs appear less promising (see Chapter 2.6), and further research is still required in this area [Martens et al., 2006]. It might be such that in future generations, germanium is used in CMOS circuits for the p-channel devices, and a different high-mobility material such as gallium arsenide (GaAs) is used for n-channel devices. Ultimately, if germanium channel transistors are to become prevalent in CMOS circuits, the low natural abundance and high cost of germanium will mean that it will have to be incorporated in thin layers in an *on-insulator* technology [Feng et al., 2006,

Nakaharai et al., 2003].

Germanium can also be combined with silicon to form a random silicon-germanium (SiGe) alloy. In particular, this allows for the incorporation of *strain* into CMOS devices and higher carrier mobility (see Chapter 2). There are several ways in which strain can be introduced into CMOS devices, which can be divided into either *global* or *process-induced* (also, referred to as *local*) straining techniques.

Perhaps the easiest way to introduce global strain, is to grow a thin SiGe layer pseudomorphically on a silicon substrate, such that it assumes the lattice constant of the underlying silicon. Since the lattice constant of Ge is 4.2% bigger than silicon, the SiGe layer will be under biaxial compressive strain. Such structures are usually grown with a thin silicon cap on top of the SiGe layer for the purposes of cleaning and oxidation, which makes them unlikely to ever enter mainstream production due to the inherent problems of operating buried channel devices, although the use of a high- $\kappa$  dielectric might overcome this problem.

An alternative global straining technique uses a SiGe *virtual substrate*. In such structures a thin strained silicon layer is grown on a relaxed SiGe buffer layer such that it is under biaxial tensile strain. Whilst this architecture permits surface channel devices, the high density of threading dislocations associated with the relaxation of the SiGe virtual substrate can lead to high leakage currents. Furthermore, the low thermal conductivity of the SiGe virtual substrate results in self-heating becoming an important issue [Nicholas et al., 2005a]. Whilst these problems mean that chips incorporating strained silicon on a virtual substrate are unlikely to enter commercial production, it is feasible that the virtual substrate platforms could be used to provide high-quality strained silicon layers for an on-insulator technology through layer transfer techniques [Langdo et al., 2004].

There are several methods by which process-induced straining techniques can be exploited for CMOS devices. For example, whilst germanium has yet to enter mainstream production as a channel material for CMOS devices, Intel have recently shown that it can be incorporated into the source and drain regions of a silicon pMOSFET, resulting in a uniaxial compressively strained silicon channel, and these devices are now in highvolume production [Tyagi et al., 2005]. It is also possible to incorporate carbon into the source and drain regions to create a uniaxial tensile strained silicon channel to enhance electron mobility for nMOSFETs [Chui et al., 2007]. However, this work is still very much in development. Instead, state-of-the-art nMOSFETs use a silicon nitride thin film around the nMOSFET to induce a uniaxial tensile strain in the channel of the underlying MOSFET, to achieve higher electron mobilities [Tyagi et al., 2005].

As a final point, it should be mentioned that the narrow band gap of SiGe can be used in the base of a heterojunction bipolar transistor (HBT) to reduce the barrier to electron transport between the n-type emitter and collector contacts, to increase the current gain of the device. SiGe HBTs are already in commercial production.

### 1.4 Current Work

This thesis examines some of the important issues when either SiGe or Ge are used as conducting channel materials in pMOSFETs, in combination with high- $\kappa$  dielectrics. This research has been conducted within several ongoing research development projects, including the Ge MOSFET Programme at IMEC (Belgium) and the New Channel Materials Work Package within the SINANO Network of Excellence.

Whilst there have been numerous publications regarding the performance of both SiGe and Ge channel MOSFETs with high- $\kappa$  dielectrics, many aspects of carrier transport are not well understood. For example, the impact of the high- $\kappa$  dielectric on the effective mobility of inversion layer carriers remains an important issue. Furthermore, it is still unknown as to whether band-to-band tunnelling will prove to be a fundamental problem in Ge channel MOSFETs due to the smaller Ge band gap.

Chapters 2 and 3 serve to provide the necessary background details required to understand the current investigation. Chapters 4 and 5 investigate the properties of SiGe channel capacitors and MOSFETs with high- $\kappa$  dielectric and metal gate. Chapter 6 concerns work on the behaviour of long and short channel Ge pMOSFETs, with a particular emphasis on understanding the effective hole mobility and also the role of band-to-band tunnelling through measurements at cryogenic temperatures. Finally, with carriers experiencing very high lateral fields in modern state-of-the-art devices, the roles of both impact ionisation and velocity overshoot are discussed in Chapter 7 for two batches of SiGe channel pMOSFETs, one of which was processed by CEA-LETI (France) and the other as part of the UK-based HMOS project.

## Chapter 2

# **Theoretical Background**

#### 2.1 Introduction

This chapter serves as an introduction to the field of  $Si_{1-x}Ge_x(0 \le x \le 1)$ channel MOSFETs, including the integration of high- $\kappa$  dielectrics and metal gates, which form the subject of this thesis. The chapter divides into four main parts.

In the first part, the basic operation of the simple bulk long-channel MOSFET is reviewed. The second part introduces the carrier mobility and the scattering mechanisms encountered by carriers in a MOSFET. This also includes a brief discussion on the role of the valence band structure, and in particular, how *strain* can be used to modify the valence band structure and the ensuing results. The third part provides a summary of *short-channel effects* (SCEs), now important in state-of-the-art CMOS devices that have resulted directly from the aggressive down-scaling of the MOSFET channel length. Finally, the chapter concludes with a section on process considerations specific to the fabrication of bulk Ge MOSFETs incorporating high- $\kappa$  dielectrics and metal gates.

Whilst every effort has been made to include all of the important aspects relating to  $Si_{1-x}Ge_x$  channel MOSFETs, this chapter merely serves as an introduction to the field, providing the salient points relevant to the current work. There are several

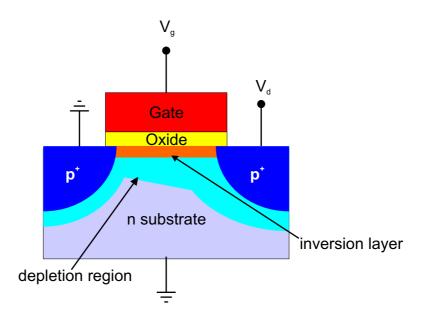

Figure 2.1: Schematic of a simple pMOSFET.

excellent books, to which the reader is referred for a more comprehensive discussion. For example, Taur and Ning [1998], Tsividis [1999], Sze [1981] and Shur [1990] provide an excellent foundation for device physics; Lundstrom [2000] is an excellent introduction to scattering; band structure of the silicon-germanium materials system is reviewed by Schäeffler, F. [1997]; and Huff and Gilmer [2005] provides one of the most thorough reviews of high- $\kappa$  dielectrics available at the present time.

### 2.2 Basic MOSFET Operation

Figure 2.1 shows a schematic of a bulk silicon pMOSFET. The simple MOSFET is a four-terminal device, with a source, a drain, a gate and a substrate or body contact, each of which can be biased independently. For a pMOSFET, the source and drain are  $p^+$  doped and the substrate is n doped. Traditionally,  $p^+$  poly-silicon is used as gate electrode, although as will be seen in Section 2.6, a metal with suitable workfunction can be employed instead. The gate electrode is insulated from the bulk silicon substrate by a thin oxide, typically SiO<sub>2</sub>, such that the gate and silicon substrate form a parallel

plate capacitor with the oxide layer serving as the dielectric. When the voltage applied to the gate is zero, majority carriers (electrons) in the n-substrate are accumulated under the gate, thus isolating the source and drain regions. This prevents current flow along the channel and the MOSFET is in the off-state. As the gate voltage is increased (i.e. made more negative for a pMOSFET), the electrons in the bulk silicon substrate are repelled away from the Si/SiO<sub>2</sub> interface, forming a depletion region under the gate, devoid of free carriers. If the gate voltage is increased further, it becomes energetically favourable for holes in the p<sup>+</sup> source and drain regions to populate the area under the gate forming an *inversion layer*, which serves as a conducting channel connecting the source and the drain, and the MOSFET is in the on-state. Since the drain is negatively biased with respect to the source, holes are able to flow along the channel from the source to the drain. Increasing the gate voltage even further increases the concentration of holes under the gate and also the drain current. Hence, the gate modulates the current flowing from the source to the drain. It is this drain current modulation that gives rise to the switching operation in fully integrated CMOS circuits.

Despite the simplicity of its operation, some of the effects observed in MOS-FETs, and in particular short-channel MOSFETs, can be quite complicated. In order to explore some of these effects, a quantitative discussion of the operation of a longchannel MOSFET now follows, which will serve as the basis for the short-channel effects, introduced in Section 2.5.

The behaviour of the long-channel MOSFET can be described under the gradual channel approximation, in which it is assumed that the electric field along the channel is much smaller than the electric field perpendicular to it [Shur, 1990]. Furthermore, the analysis is further simplified under the charge sheet approximation, which assumes that the minority carriers that form the inversion layer are located in a sheet at the semiconductor surface [Taur and Ning, 1998]. This implies that no voltage is dropped across the inversion layer and Poisson's equation can be reduced to one-dimension.

The inversion charge density,  $Q_{inv}$ , at a point x along the channel can be expressed as:

$$Q_{inv} = C_{ox} \left( V_{qs} - V_t - V_c(x) \right)$$

(2.1)

where  $C_{ox}$  is the oxide capacitance,  $V_{gs}$  is the gate voltage with respect to the source,  $V_t$  is the threshold voltage of the device, which is assumed to be constant, and  $V_c(x)$  is the potential at a distance x along the channel with respect to the source.

The carrier velocity at a position x in the channel, v(x), is related to the longitudinal electric field,  $\varepsilon(x)$ , by the carrier mobility,  $\mu$ , according to:

$$v(x) = \mu \varepsilon(x) = \mu \frac{dV_c(x)}{dx}$$

(2.2)

where it is assumed that the carrier mobility is constant along the channel. The current flowing from the source to drain,  $I_{ds}$ , is given by the product of the inversion charge, the carrier velocity and the device width:

$$I_{ds}(x) = WQ_{inv}(x)v(x)$$

(2.3)

Substituting Equations 2.1 and 2.2 into Equation 2.3, the drain current for the MOSFET can be written as:

$$I_{ds} = C_{ox}W\mu \left(V_{gs} - V_t - V_c(x)\right) \frac{dV_c x}{dx}$$

(2.4)

where it has been assumed that the drain current,  $I_{ds}$ , is constant along the channel.

Equation 2.4 can be integrated, with the appropriate boundary conditions such that  $V_c(\theta) = 0$  and  $V_c(L) = V_{ds}$ , to obtain the expression for the drain current:

$$I_{ds} = C_{ox} \frac{W}{L} \mu \left[ (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2} \right]$$

(2.5)

The drain current has a maximum value when  $V_{ds} = V_{gs} - V_t$ . This point corresponds to the MOSFET entering the *saturation regime*, and the *saturation current* can be expressed as:

$$I_{ds,sat} = C_{ox} \frac{W}{2L} \mu \left( V_{gs} - V_t \right)^2 \tag{2.6}$$

The onset of the saturation regime in a MOSFET can be understood as follows. As the drain voltage of the MOSFET increases, the drain current increases according to Equation 2.5. However, the inversion charge at the drain,  $Q_{inv}(L)$ , decreases according to Equation 2.1, such that as  $V_{ds}$  approaches  $V_{gs} - V_t$ , the inversion charge density approaches zero. This point is referred to as *pinch-off*, and results in a highly resistive region forming at the drain, since the inversion charge vanishes. Any further increase in  $V_{ds}$  will be result in the pinch-off point being moved towards the source, with the extra potential being dropped across this high resistive region near the drain. Hence, the drain current behaves as if  $V_{ds} = V_{gs} - V_t$ , and saturates. At the saturation point, the gradual channel approximation breaks down, with carriers no longer being confined to the surface channel. Consequently, carriers are injecting from the pinch-off point into the drain depletion region and drift to the drain.

Whilst the assumptions made in the gradual channel approximation and charge sheet approximation are valid for describing the behaviour of long-channel MOSFETs, this simple model *cannot* be used to describe the behaviour of short channel MOSFETs, in which, short channel effects such as punchthrough, drain-induced barrier lowering (DIBL), velocity overshoot and quantum mechanical tunnelling must also be considered [Tsividis, 1999]. Hot carrier effects also become increasingly important due to the higher longitudinal field experienced by carriers along the channel, resulting directly from scaling. A summary of these effects is presented later in Section 2.5.

When considering the operation of a MOSFET, it is also important to consider

the effects of parasitic elements that effect its behaviour. One of the most important parasitic elements is the finite resistance of the source and drain regions,  $R_s$  and  $R_d$ , respectively [Schroder, 2006]. In a conventional planar MOSFET, the source and drain regions are formed by ion implantation of dopants, which are activated by a high temperature anneal. The voltages specified so far, refer to those voltages applied at the drain and gate electrodes, thus neglecting any voltage dropped across the source and drain regions. In order to account for these effects, it is necessary to replace the voltages,  $V_{ds}$  and  $V_{gs}$ , with their intrinsic equivalents,  $V'_{ds}$  and  $V'_{gs}$ :

$$V_{ds} \rightarrow V'_{ds} = V_{ds} - I_{ds}R_s - I_{ds}R_d \tag{2.7}$$

$$V_{gs} \to V'_{qs} = V_{gs} - I_{ds} R_s \tag{2.8}$$

## 2.3 Carrier Mobility and Scattering Mechanisms

The carrier mobility is perhaps the single-most important parameter with regards to MOSFET performance, particularly when trying to demonstrate the improved performance of alternative channel materials over silicon. Since the drain current of a MOSFET is proportional to the mobility, increasing the mobility should, in theory, improve the drive current and hence the CMOS circuit performance. Indeed, it is the higher electron and hole bulk mobility values in germanium [Sze, 1981] that provides the motivation for the incorporation of germanium into the channel region of a MOSFET.