# Florida International University FIU Digital Commons

FIU Electronic Theses and Dissertations

University Graduate School

3-24-2011

# The Development of Hardware Multi-core Testbed on Field Programmable Gate Array

Mohan Shivashanker Florida International University, mohan.uvce@gmail.com

Follow this and additional works at: http://digitalcommons.fiu.edu/etd

#### **Recommended** Citation

Shivashanker, Mohan, "The Development of Hardware Multi-core Test-bed on Field Programmable Gate Array" (2011). *FIU Electronic Theses and Dissertations*. Paper 395. http://digitalcommons.fiu.edu/etd/395

This work is brought to you for free and open access by the University Graduate School at FIU Digital Commons. It has been accepted for inclusion in FIU Electronic Theses and Dissertations by an authorized administrator of FIU Digital Commons. For more information, please contact dcc@fu.edu.

## FLORIDA INTERNATIONAL UNIVERSITY

# Miami, Florida

# THE DEVELOPMENT OF HARDWARE MULTI-CORE TEST-BED ON FIELD PROGRAMMABLE GATE ARRAY

A thesis submitted in partial fulfillment of the

requirements for the degree of

MASTER OF SCIENCE

in

# ELECTRICAL ENGINEERING

by

Mohan Shivashanker

2011

To: Dean Amir Mirmiran College of Engineering and Computing

This thesis, written by Mohan Shivashanker and entitled The Development of Hardware Multi-core Test-bed on Field Programmable Gate Array, having been approved in respect to style and intellectual content, is referred to you for judgment.

We have read this thesis and recommend that it be approved.

Chen Liu

Jean Andrian

Gang Quan, Major Professor

Date of Defense: March 24, 2011

The thesis of Mohan Shivashanker is approved.

Dean Amir Mirmiran College of Engineering and Computing

> Interim Dean Kevin O'Shea University Graduate School

Florida International University, 2011

# DEDICATION

I dedicate this thesis to my parents. Without their patience, understanding, support, and most of all love, the completion of this work would not have been possible.

#### ACKNOWLEDGMENT

I feel pleasure and privilege to express my deep sense of gratitude, indebtedness and thankfulness towards my advisor, Dr. Gang Quan, for his guidance, constant supervision and continuous inspiration and support throughout the course of work. His valuable suggestion and critical evaluation have greatly helped me in successful completion of the work. I would like to thank the members of my committee Dr. Chen Liu and Dr. Jean Andrian, for their support and patience. Their gentle but firm direction has been most appreciated. I am also thankful to all those who helped me directly or indirectly in completion of this work.

This thesis is supported in part by NSF under projects CNS-0969013, CNS-0917021 and CNS-1018108.

# THE DEVELOPMENT OF HARDWARE MULTI-CORE TEST-BED ON FIELD PROGRAMMABLE GATE ARRAY

**ABSTRACT OF THE THESIS**

by

Mohan Shivashanker

Florida International University, 2011

Miami, Florida

Professor Gang Quan, Major Professor

The goal of this project is to develop a flexible multi-core hardware test-bed on field programmable gate array (FPGA) that can be used to effectively validate the theoretical research on multi-core computing, especially for the power/thermal aware computing. Based on a commercial FPGA test platform, i.e. Xilinx Virtex5 XUPV5 LX110T, we develop a homogeneous multi-core test-bed with four software cores, each of which can dynamically adjust its performance using software. We also enhance the operating system support for this test platform with the development of hardware and software primitives that are useful in dealing with inter-process communication, synchronization, and scheduling for processes on multiple cores. An application based on matrix addition and multiplication on multi-core is implemented to validate the applicability of the test bed.

# TABLE OF CONTENTS

| CH | HAPTER                                                                     | PAGE |

|----|----------------------------------------------------------------------------|------|

| 1. | INTRODUCTION                                                               | 1    |

| 2. | GENERAL FRAMEWORK                                                          | 8    |

|    | 2.1 The Hardware Architecture.                                             | 8    |

|    | 2.2 The System Software Setup                                              | 12   |

|    | 2.3 Hardware/Software Test Platform                                        |      |

| 3. | HARDWARE ARCHITECTURE DESIGN                                               | 18   |

|    | 3.1 The Design of DFS                                                      | 19   |

|    | 3.2 The Design of Sharing Memory                                           | 34   |

|    | 3.3 The Design of Inter-processor Communication                            |      |

| 4. | OPERATING SYSTEM SUPPORT AND SOFTWARE PLATFORM                             |      |

|    | SETTINGS                                                                   | 45   |

|    | 4.1 Standalone Board Support Package                                       | 45   |

|    | 4.2 Building of Xilkernel Real-time Operating System                       | 46   |

|    | 4.3 Scheduling                                                             | 47   |

| 5. | EXPERIMENTS AND RESULT                                                     | 50   |

|    | 5.1 Varying the Working Frequency                                          | 50   |

|    | 5.2 Debugging                                                              |      |

|    | 5.3 Four Microblazes System Using Single PLB Bus                           | 53   |

|    | 5.4 Four Microblazes System Using Different PLB Buses and a Shared Console |      |

| 6. | CONCLUSIONS AND FUTURE WORK                                                | 59   |

|    | LIST OF REFERENCES                                                         | 60   |

|    | GLOSSARY                                                                   | 64   |

# LIST OF FIGURES

| FIC | GURE                                                                               | PAGE |

|-----|------------------------------------------------------------------------------------|------|

| 1.  | Exponential Increase in Power Consumption                                          | 2    |

| 2.  | The Hardware Architecture                                                          | 9    |

| 3.  | Microblaze Core Block Diagram                                                      | 10   |

| 4.  | Clock Control Unit                                                                 | 11   |

| 5.  | Software Design Flow                                                               | 13   |

| 6.  | Front view of Xilinx virtex-5 LX110T FPGA board                                    | 15   |

| 7.  | Back view of Xilinx virtex-5 LX110T FPGA board                                     | 16   |

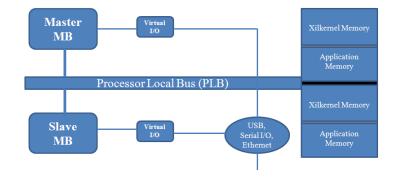

| 8.  | Dual Microblaze Processor System                                                   | 19   |

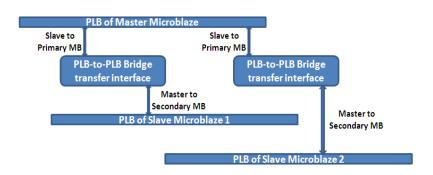

| 9.  | Schematic diagram of PLB-to-PLB Bridge                                             | 20   |

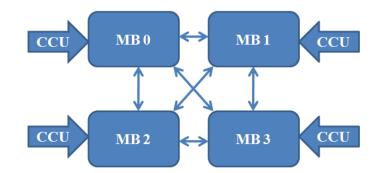

| 10. | . Homogeneous multi-core architecture with variable working frequency              | 21   |

| 11. | . Microblaze Cache Setup                                                           | 22   |

| 12. | . MPMC base Configuration                                                          | 23   |

| 13. | . Address Port configure for MPMC                                                  | 24   |

| 14. | . MPMC Port and Pipeline configuration                                             | 24   |

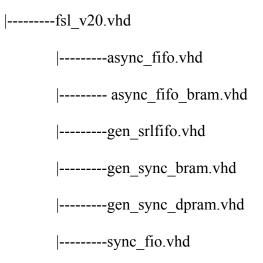

| 15. | . CacheLink.vhd instantiate two FSL unit                                           | 26   |

| 16. | . Cache Link signal declaration in mpmc_xcl_if.v                                   | 27   |

| 17. | . Cache link signal assignment and instance in mpmc_xcl_if.v                       |      |

| 18. | . Cache link signal and clock replacement of read data interface in mpmc_xcl_if.v  | 29   |

| 19. | . Cache link signal and clock replacement of write data interface in mpmc_xcl_if.v |      |

| 20. Sample of FSL signal assignment                         |    |

|-------------------------------------------------------------|----|

| 21. Port signal declaration                                 |    |

| 22. Clock Control Unit declaration in file user_logic.vhd   |    |

| 23. File Structure of Clock Control unit                    |    |

| 24. Clock assignment in top.vhd                             |    |

| 25. Port declaration in Configuration Unit                  |    |

| 26. Logic in Configuration Unit                             |    |

| 27. Implicit Multiprocessing                                |    |

| 28. Explicit Multiprocessing                                |    |

| 29. Schematic Representation of XPS Mutex connection        |    |

| 30. Schematic Representation of Matrix Addition             |    |

| 31. Loading more than one image into FLASH PROM             |    |

| 32. Define starting address of image in FLASH PROM          | 40 |

| 33. Reset other processor before image loading              | 40 |

| 34. How to enter main program after loading                 | 40 |

| 35. Boot Program Sample                                     | 41 |

| 36. Programming FLASH memory                                |    |

| 37. Setting RS232 serial port terminal for output           |    |

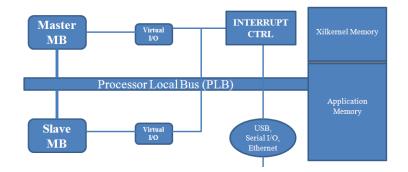

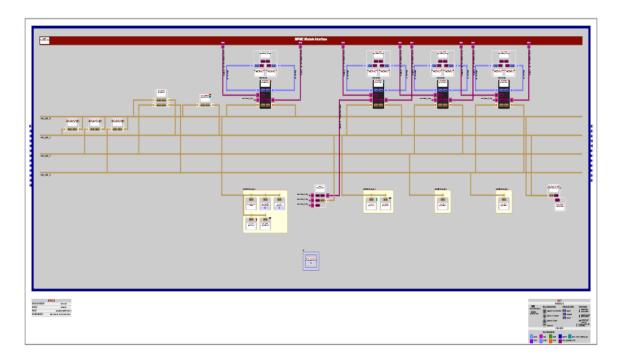

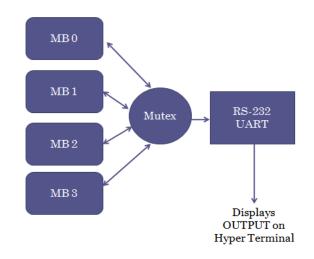

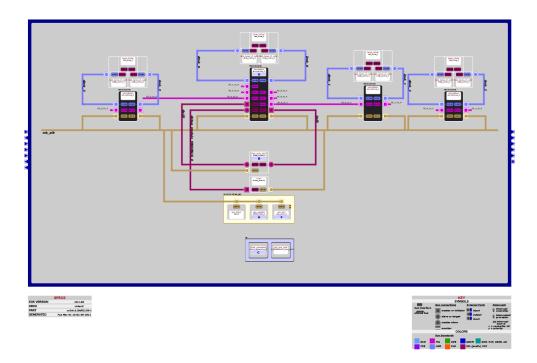

| 38. Overall System View                                     |    |

| 39. Software Platform Settings                              | 45 |

| 40. Setting Compiler Options                                |    |

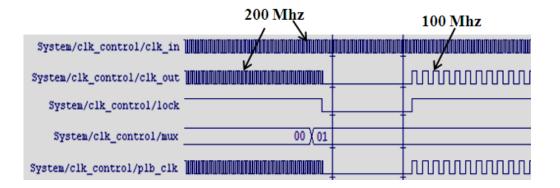

| 41. The Timing Overhead for Varying the Working Frequencies | 51 |

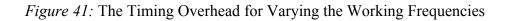

| 42. Block Diagram of Microblaze Debug Module (MDM)          | 53 |

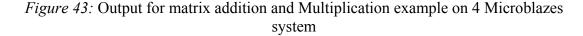

| 43. | Output for matrix addition and multiplication example on 4 Microblazes system                                             | 55 |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 44. | For 4 Microblaze system using different PLB buses and a shared console                                                    | 57 |

| 45. | System architecture view for 4 Microblaze system with single PLB bus                                                      | 58 |

|     | System architecture view for 4 Microblaze system with individual PLB buses connected with PLB-to-PLB Bridge and XPS Mutex | 58 |

#### CHAPTER 1

#### INTRODUCTION

The computer industry is switching from the single core based platform to the multi-core. Die yield, limits in instruction level parallelism (ILP) and memory/processor performance gap, coupled with the exponentially increased power consumption and heat dissipation have forced this switching. Increasing the working frequency and building a more complicated single processor is no longer an effective way to improve the computing performance. Multi-core platforms, which facilitate the process or thread level parallelism and can thus work at lower clock rates, can potentially deliver high computing performance without consuming excessive power and producing prohibit heat. As a result, multi-core processor systems have been one of the most popular methods to overcome the complexities for many applications within the corporate, medical, military and other commercial markets requiring high performance and real-time processing power. For example, Cisco today embeds in its routers a network processor with 188 cores implemented in 130 nm technology, which dissipates 35W at a 250MHz clock rate, and produces an aggregate 50 billion instructions per second [1].

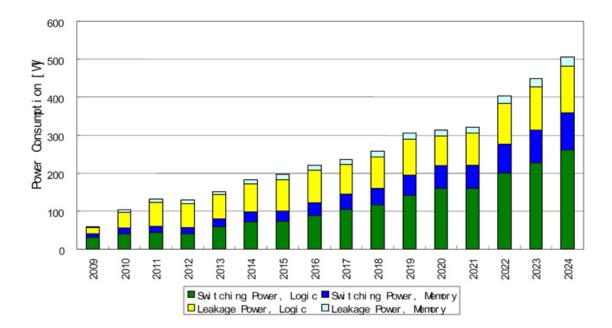

Power consumption and thermal management have been two of the most critical issues in developing all but the most trivial computing systems. With the demand for increased performance and decrease in size from mobile electronics to high performing game consoles, there has been an exponential increase in power density and chip temperature, according to SOC consumer stationary power consumption trends shown in Figure 1.

Figure 1: Exponential Increase in Power Consumption

The power consumption has been one of the most critical constraints for multi-core computing. The power consumption in modern processors consists of (i) the dynamic power and (ii) the leakage power. The dynamic power is due to the transistor switching activities during runtime, and used to be the dominant between the two. The dynamic power is given by,

$$P_{dyn} = \alpha C V^2 f$$

where,  $P_{dyn}$  is the dynamic power consumed,  $\alpha$  is the activity factor, C is the load capacitance, V is the supply voltage and *f* is the working frequency.

Leakage power is due to the leakage current flowing through the transistor and is given by,

$$P_{leak} = VI_{leak}$$

where,  $P_{leak}$  is the leakage power, V is the supply voltage and  $I_{leak}$  is the leakage current through the transistor. As shown above, the dynamic power consumption is quadratically dependent on supply voltage. Thus, reducing the supply voltage can dramatically reduce the power consumption for the processor. As a result, many processors are designed to have the Dynamic Voltage and Frequency Scaling (DVFS) capability, i.e. being able to dynamically vary the supply voltage and/or frequency of a microprocessor. DVFS has proven to be one of the most effective ways to reduce the power consumption and also to manage the thermal condition of the processor while meeting the required performance [3, 10].

Besides power consumption, the rapidly elevated temperature in the computing system also raises serious concerns for computing system designers. The rise in chip temperature has significant impact on power consumption, reliability, cooling and packaging costs. In fact, the rapid increase in cooling and packaging costs has the potential to greatly affect the computer industry capability to deploy new systems. There have been extensive theoretical researches conducted on power and thermal aware computing for a multi-core platform [26, 27]. Dynamic power management techniques have already been developed to cover a wide spectrum of system characteristics [8]. It has been shown that, proactive use of software on top of the hardware can balance the overall thermal profile with minimal overhead using the operating system support. There also exists a hardware DVFS technique [7, 9] where they have proposed a novel method of producing high speed variable fractional clock rates. Y Liu et. al. [27], have presented a design time optimization technique for real-time embedded systems that make use of DVFS to minimize peak temperature. In [26], DVFS technique is used to reduce the overall energy consumption by exploiting both static and dynamic slack times where, voltage and frequency is decreased below the operating level.

While a variety of power/thermal aware techniques have been proposed for a hardware multi-core platform, most of the existing works are validated through software simulations with simplified and idealized theoretical models. The change in computer architecture to multi-core has complicated the use of software simulators as they are difficult to parallelize well with greater number of processors [13]. Even though the SPEC2k benchmark suite and Virtutech's Simics [15] are more robust, they provide limited application programming interface (APIs) and become extremely time consuming as greater number of cores are added to the system. Furthermore, while the software simulators help to simplify the problem, results may also lead to conclusions deviated from what they really are in the practical scenarios, since the practical computing systems need to deal with more complicated scenarios that cannot be accurately modeled in the software simulation. Thus, it becomes necessary to test or verify the theoretical results in a more practical environment.

While a number of commercial platforms based on multi-core architecture are reported in the literature, such as IBM's Cell processor [1], they are not readily available at a reasonable price. Researchers also use current multi-core desktops for the validation purpose [9]. However, such a "test-bed" can only be used to test theoretical research based on a fixed architecture. In addition, these test beds are also limited by their software supports and cannot be easily updated.

To design a versatile, flexible, and reusable multi-core test bed, we seek to develop such a test bed using the FPGA technology [4]. FPGA is an integrated circuit that can be reconfigured according to the required application by the designer. The configurable logic cell blocks are the basic logic unit in an FPGA even though the features and number of logic cells used vary from device to device. Today's FPGAs are highly scalable, field debuggable, re-configurable, have a lower cost and readily available in the market. They can be re-programmed using the powerful and versatile developing tools commercially available today. It has a much shorter design cycle and requires much less engineering equipment costs compared with those for the design of Application Specific Integrated Circuits (ASIC). The FPGA has thus been widely used in both academy and industry to build test platforms to test design alternatives and validate theoretical research results. For example, recent works on FPGA like Fort et al. [33] employed multi-threading to improve utilization of soft-core processors with little dimensional costs. The FPGA based complete system called Protoflex [15] was designed to provide similar functionality of Simics [14] is the motivation research for us to choose FPGA as our test bed.

#### Project goals and objectives

The goal of our project is to develop a multi-core hardware test bed on Field Programmable Gate Array (FPGA). Specifically, we want to develop a test platform that can be used effectively to validate the theoretical researches on power/thermal aware computing. We envisioned our test platform to have the following capabilities: (1) Consisting of 4 or more homogeneous soft-core processors such as Microblaze system [12]; (2) The performance enhancement, i.e., working frequency, of each core can be dynamically varied and evaluated; (3) The multi-core platform can be supported with a real-time operating system for ease of development and testing.

#### **Our Contributions**

From our work, we have successfully developed a hardware multi-core test-bed with a real-time operating system booted on each core. The test platform consists of four homogeneous soft-core processors (i.e., Microblazes system [12]). By using a customized clock control unit in the design, we were able to dynamically vary the working frequency i.e., improve performance of each core. As discussed before, it is desirable that both the supply voltage and working frequency of a processor core can be dynamically varied. However, it would be extremely expensive if not totally impossible to change the supply voltage for a soft core on the FPGA chip. Therefore, we change the performance of the processor only by changing its working frequency. We also considered inter-processor communication between the processors to perform synchronization when accessing the shared resource. Finally, an application example of matrix addition is implemented to validate the applicability of the test-bed.

#### Thesis Organization:

The rest of the thesis is organized as follows. We first present the general framework of our design. In Chapter 3, we discuss the hardware aspect in our development and present our work on the design and implementation of a multi-core system with dynamically variable frequency based on Virtex5 using FPGA development tools. Chapter 4 presents the operating system boot up and software platform settings. The experiments conducted and results are discussed in Chapter 5. We conclude the thesis in Chapter 6.

#### CHAPTER 2

#### GENERAL FRAMEWORK

The goal of this project is to develop a multi-core hardware test-bed on FPGA that can be used effectively to validate the theoretical research on power-aware computing embedded system design. The system is supposed to be flexible and support different applications. The number of processing element can be configured according to our computational needs and the chip capacity. The flexibility of FPGA has helped us in customizing necessary peripheral components.

#### 2.1 The Hardware Architecture

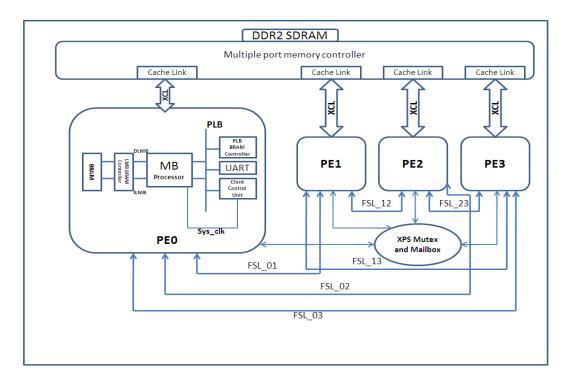

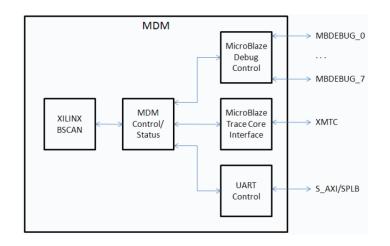

Figure 2 shows the overall hardware architecture of our system. The systems consists of four homogeneous processing core. To support different clock speeds on each of the processing element units during runtime, a configurable clock control unit is developed that can be accessed through software. All four cores are connected using so called the Fast Simplex Link (FSL) [16]. Note that since each processing core can potentially work at different working frequencies, connecting all processing core using bus is not an option in our case. FSL allows asynchronous communication mechanism and is therefore selected to connect the multiple processor cores. In addition, multiple port memory controller (DDR\_SDRAM) and inter-processor communication-XPS Mutex hardware IP [17] are also incorporated into our test bed to facilitate the memory sharing and inter processor synchronization and communication. Each processing element consists a Microblaze soft-core processor, a small scratch-pad memory, Local Memory Bus (LMB),

Processor Local Bus (PLB), a customized clock control IP and some specific peripheral components.

Figure 2: The Hardware Architecture

# Microblaze

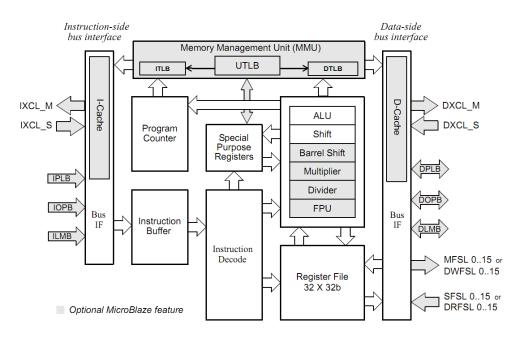

In our project, a Microblaze core is used as the processor core. The Microblaze soft-core processor is a 32-bit Reduced Instruction Set Computer (RISC) architecture optimized for embedded applications. Microblaze can be user configured like pipeline depth, cache size, embedded peripherals, and bus-interfaces. The Microblaze core block diagram is shown in Figure 3.

Figure 3: Microblaze Core Block Diagram [12].

The fixed feature set of the processor includes:

- Thirty-two 32-bit general purpose registers

- 32-bit instruction word with three operands and two addressing modes

- 32-bit address bus

- Single issue pipeline

In addition to these fixed features, the Microblaze processor is parameterized to allow selective enabling of additional functionalities like floating point arithmetic, multiplication and division.

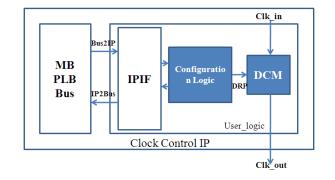

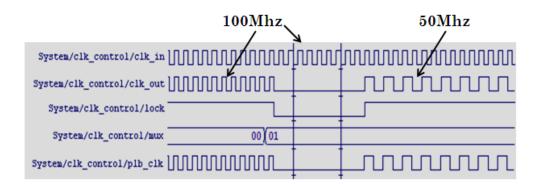

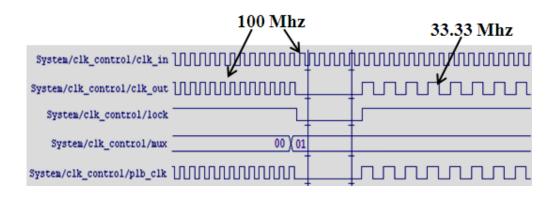

### Customized Clock Control Unit

To dynamically vary the frequency of the processors, we built a customized IP (as shown in Figure 4) that can control the clock for each processor core at run-time. Each customized clock control IP consists of a digital clock management (DCM) unit [18] and a configuration logic unit. The Xilinx's DCM is a multi-function clock management unit which supports dynamic configuration of clock frequencies ranging from 33MHz-210MHz. For the Virtex5, the DCM unit includes a Dynamic Reconfigurable Port (DRP), which can be used by FPGA fabric to access the configuration memory within DCM.

*Figure 4:* Clock Control Unit

The configuration logic translates the control signal from bus into control data for DCM, which makes the run-time programmable clock possible. In our design, four different clock frequencies, i.e. 40MHz, 50MHz, 66.7MHz and 100MHz, are provided and we use the two least significant bits of the bus to select the desired frequency. The customized clock control IP is connected with the PLB bus via the standard PLB-IPIF interface.

#### **Bus Interfaces**

There are a number of choices for Microblaze soft-core processor interconnections. It follows the Harvard architecture with separate paths for data and instruction accesses. Processor Local Bus (PLB) is a fully synchronous bus that provides connection to both on-chip and off-chip peripherals and memory. The Local Memory Bus (LMB) provides single-cycle access to on-chip dual-port Block RAM. The Xilinx Cache Link (XCL)

interface is intended for use with specialized external memory controllers. Memory located outside the cache area is accessed through PLB or LMB. The debug interface is used with the Microblaze Debug Module (MDM) and is controlled through JTAG port by the Xilinx Microprocessor Debugger (XMD).

For our design, even though the traditional bus connection is possible, it is less attractive due to scalability concern. An alternative is to use the logic source in FPGA to create the Network-On-Chip (NOC) infrastructure. For example, Schelle and Grunwald [19] implemented a switching network as interconnection for general purpose processor in a Virtex II-pro device. One major disadvantage of this solution is the large amount of resources it requires. Henceforth, we made use of a convenient point-to-point connection mechanism, i.e., the Fast Simplex Link (FSL) bus, provided by Xilinx. FSL is a FIFO-based connection and can be synchronous or asynchronous. An asynchronized communication scheme is particularly useful in our design with different processors running at different speeds. Each core from Xilinx supports multiple FSL buses. For example, a Microblaze has up to sixteen FSL ports with one master and one slave interface to connect up to sixteen different components for duplex communication, which makes it reasonably easy and effective to build popular multi-core topologies, such as the tree, mesh, or torus structure.

#### 2.2 The System Software Setup

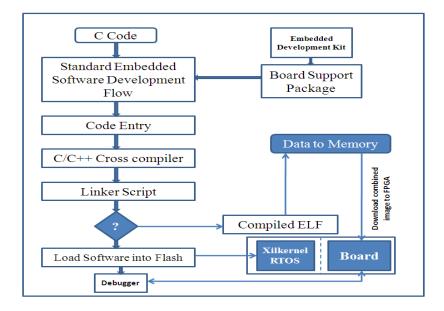

In our project, we made use of software platform settings under XPS GUI to boot the Xilkernel RTOS into the board and configured the operating system and library files according to our requirements. C code was implemented and compiled through RTOS, as shown in Figure 5 below.

Figure 5: Software Design Flow

### 2.3 The Hardware/Software Test Platform

In order to develop the embedded system design on the chip, Xilinx has provided the Embedded Development Kit (EDK) suite. We used EDK design suite 10.1.03 version. Using this suite of tools we can incorporate a wide range of Hard and soft-IP cores, such as microprocessors, interconnects, memories, and an assortment of peripherals. The main advantage of EDK suite is that on a single environment we can perform design, simulation, synthesis, and compilation.

In EDK embedded system design, we have two separate steps, hardware and the software design which interact each other. Firstly, we have to develop and design the hardware part where a custom circuitry IP core is developed using a hardware description language

(HDL) like verilog or VHDL. Synthesis tool translates this hardware description language into the low level gate logic. Then, all available IP cores are combined into a single design using the Xilinx platform studio tool. The microprocessor is connected to all the IP cores using the bus architecture, thus allowing the entire design to be controlled using software programs. Secondly, in order to control the microprocessor and all connected peripheral, application software is developed where a system programmer should correctly implement the low level details of interacting with any given peripheral. We can install the embedded operating system on the chip design, which helps in the development of our design.

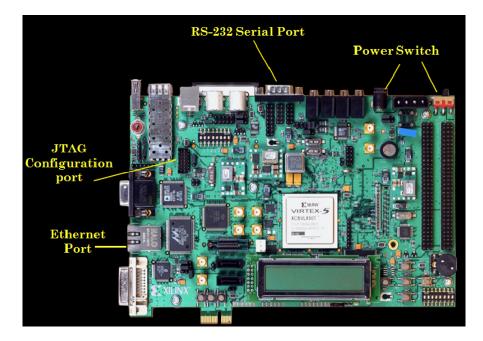

Xilinx Embedded Development Kit (EDK) is the package for building Microblaze in Xilinx FPGAs. It consists of two separate environments: Xilinx Platform Studio (XPS) and Software Development Kit (SDK). As said earlier, we have used Xilinx viretx-5 LX110T FPGA board for our project. Below are the figures (Figure 6 and 7) showing the front and back view of virtex-5 LX110T FPGA.

Figure 6: Front view of Xilinx virtex-5 LX110T FPGA board

The main features of this board are:

- Xilinx XCF32P Platform Flash PROMs (32 MB each) for storing large device configurations

- Xilinx System ACE Compact Flash configuration controller

- 64-bit wide 256Mbyte DDR2 small outline DIMM (SODIMM) module compatible with EDK supported IP and software drivers

- On-board 32-bit ZBT synchronous SRAM and Intel P30 Strata Flash

- 10/100/1000 tri-speed Ethernet PHY supporting MII, GMII, RGMII, and SGMII interfaces

- USB host and peripheral controllers

- Programmable system clock generator

- Stereo AC97 codec with line in, line out, headphone, microphone, and SPDIF digital audio jacks

• RS-232 port, 16x2 character LCD, and many other I/O devices and ports.

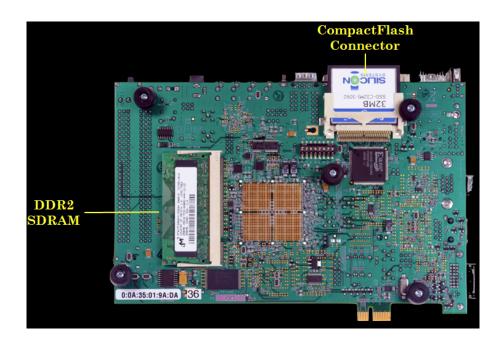

Figure 7: Back view of Xilinx virtex-5 LX110T FPGA board

Once we have completed the embedded design, it is translated into an implementation suitable to the board. Here we have two phases for the implementation process: (a) Synthesis phase and (b) Compilation phase. Under the synthesis phase, a Xilinx synthesis tool will translate the hardware description language into a gate level description. EDK provides Xilinx Synthesis Technology (XST) the following, which happens in the synthesis phase: (1) System-on-Chip elaboration: It translates the HDL into a computer readable format. (2) Soft-IP core synthesis: Converts soft-IP core into a Net list which is a logical circuit description. (3) Physical Mapping: Maps the low-level Net list into a physical description circuit. (4) Net list placement and routing: Physical Net lists are placed into the FPGA and channel is established between the different components for

communication. (5) Bit-stream generation: Physical design is converted into a bit-level description i.e., bit-stream files which can be downloaded into the board for execution. In the compilation phase, the software program design is compiled from the C source and converted into the binary format used by the microprocessor. After the software has been compiled into a binary executable file, the hardware and software are combined into one overall bit-stream. This bit-stream is used to initialize the SRAM with the hardware design, and the chip memories with the software program. Thus, when the system-on-chip is boot-strapped, any microprocessors in the system will execute the software associated with them.

#### **CHAPTER 3**

#### HARDWARE ARCHITECTURE DESIGN

As explained in the previous chapter, we have used FPGA board from Xilinx. The board is Xilinx Virtex5 XUPV5-LX110T evaluation platform [20]. The chip is xc5vlx110t, grade ff1136, speed -1. In order to develop the embedded system design on the chip, Xilinx has provided the Embedded Development Kit (EDK) [21] and an Integrated synthesis environment (ISE) software design suite [23]. Using this suite of tools, we can incorporate a wide range of hard and a soft-IP core, such as microprocessors, interconnects, memories, and an assortment of peripherals. The main advantage of this design suite is that on a single environment, we can perform design, simulation, synthesis, place and routing and finally, download and debug the system.

Xilinx Intellectual Property (IP) is the building block of several Xilinx design platforms. Various IP cores are available to address requirements of FPGA designers in Digital Signal Processing (DSP), embedded and other connectivity application designs. The entire used IPs version is specified in the following sections. Xilinx keep updating IPs regularly and are available on their website but, these new IP versions have no guarantee to work in this project.

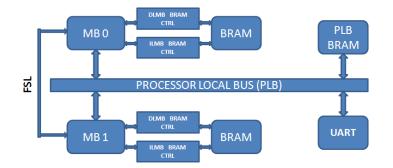

We started with a single Microblaze processor design. The local BRAM is connected and used to instantiate the processor with an instruction and data BRAM controllers. The Microblaze is sitting on the PLB. The next processor was added to the system from the IP catalog and provided with connections of different BRAM and BRAM controllers similar to the first processor. A block diagram of the dual processor system is shown in Figure 8.

Figure 8: Dual Microblaze Processor System

The PLB BRAM acts as a shared memory for the two processors. Any address on the PLB is accessible by both the Microblazes. Since Microblaze uses memory mapped I/O, both of them can access any resource on the PLB bus. The XPS Mutex can also be used in place of FSL for inter-processor communication between the processors.

After the hardware platform design is complete, FPGA configuration bitstream is generated. Xilinx Platform Studio (XPS) is used to build the net list and bitstream file. Then, the software component is set with a downloadable Executable Linked Format (ELF) file and merged with the hardware bitsream to dynamically download onto the board via JTAG cable connected to the FPGA.

#### 3.1 The Design of DFS

To accommodate more numbers of Microblaze processors and to improve the system performance, we made use of PLB bus for each individual processor and connected them using PLB-to-PLB Bridge. The Xilinx PLB-to-PLB Bridge design allows the user to tailor the bridge according to a specific application by setting certain parameters to enable/disable features. The PLB-to-PLB Bridge is a slave on the primary and master on the secondary PLB. We can isolate some of the slow PLB peripheral from the primary PLB and improve the system performance. The bridge allows the Microblazes to access the external DDR2SDRAM memory and other peripherals on different buses by mapping to their address space.

Figure 9: Schematic diagram of PLB-to-PLB Bridge

Further, a hardware test-bed with four Microblaze homogeneous soft-cores on a same chip of FPGA and point-to-point network topology was built (as shown in Figure 10). Each core was made to dynamically change its working frequency using the clock control unit (CCU) based on Xilinx's Digital Clock Manager (DCM) [18]. A clock generator module is used to initiate the DCM, where the clock control unit translates the control into the DCM and generates the desired clock. The configuration and customized units for the experiment to test the multi-core test bed is explained below.

*Figure 10:* Homogeneous multi-core architecture with variable working frequency

#### Configuration and Customized Units

Xilinx provides two types of processor units, hard-core PowerPC and soft-core Microblaze. The so-called hard-core unit is basically a silicon unit integrated into FPGA. The advantage of hard-core is the speed, but it lacks the flexibility of a soft-core unit. The soft-core is an integrated logic design based on FPGA fabric, which make Microblaze much more flexible. The Virtex5 board supports only microblaze processor with speed of 125MHz. With soft-core, you can add an arbitrary number of processors, as long as the FPGA chip has enough capacity. Besides, each processing unit could be tailored according to need. For Microblaze, you can specify the number of the pipeline stages, add or delete the float point unit, change the bus interface, make tradeoff between space and throughput, and so on.

The detailed configuration for Microblaze (7.10.d) is explained as follows:

*Bus Interface:* Setting from BUS Interface Tab. It can also be seen and changed from MHS file. Remember to name the 3 FSL master and slave channels.

*Port Interface:* Change the clock to the one you are going to drive the processor. By default, it is all sys\_clk\_s.

*Instruction Tab-Optimization (Select implementation to optimize area):* This option could make tradeoff between area and processor throughput. Enable this option when you need to reduce the logic used by Microblaze.

*Exception:* Enable both data and instruction side PLB exceptions, enable illegal instruction exception and enable unaligned data exception

*Cache:* Due to the current bus connection, you must enable cache to use XCL interface. Enable both Instruction and Data caches. Also enable the option "Use cache links for all D/I cache memory access". Because we are going to modify the XCL interface in MPMC in order to support different clocks. All the memory access must go through this XCL interface, otherwise system fails. The cache tab configuration is listed as below.

| Instructions | Exceptions      | Cache | MMU | Debug | Interrupt and Reset | PVR     | Buses | :                                               | HDL Toggle | 💯 Datasheet | P     |

|--------------|-----------------|-------|-----|-------|---------------------|---------|-------|-------------------------------------------------|------------|-------------|-------|

| Enable Inst  | uction Cache    |       |     |       |                     |         |       |                                                 |            |             |       |

| Instruction  | Cache Feature   |       |     |       |                     |         |       |                                                 |            |             |       |

| Size of th   | e I-Cache in By | tes   |     |       |                     |         |       |                                                 |            | 2kB         | •     |

| I-Cache B    | ase Address     |       |     |       | 03                  | K900000 | 00    | I-Cache High Address                            |            | 0x9FFI      | FFFFF |

| Enable I-I   | Cache Writes    |       |     |       |                     |         |       | Use Cache Links for All I-Cache Memory Accesses |            |             |       |

| Instructio   | n Cache Line L  | ength |     |       | 4                   |         | *     | Number of I-Cache Address Tag Bits              |            | 0           | 1     |

| Enable Dati  | a Cache         |       |     |       |                     |         |       |                                                 |            |             |       |

| Data Cach    | e Feature       |       |     |       |                     |         |       |                                                 |            |             |       |

| Size of D    | Cache in Bytes  |       |     |       |                     |         |       |                                                 |            | 2kB         | •     |

| D-Cache      | Base Address    |       |     |       | 02                  | x900000 | 00    | D-Cache High Address                            |            | 0x9FFI      | FFFFF |

| Enable D     | Cache Writes    |       |     |       |                     |         |       | Use Cache Links for All D-Cache Memory Accesses |            |             |       |

| Data Cac     | he Line Length  |       |     |       | 4                   |         | ~     | Number of D-Cache Address Tag Bits              |            | 0           | 1     |

Figure 11: Microblaze Cache Setup

Buses: Choose the appropriate number of FSL for the example project.

#### Multiple-port Memory Controller (MPMC) 4.03.a version: DDR2\_SDRAM

Memory control unit manages the DDR2\_SDRAM memory and provides multiple ports access for processors. The basic configuration of MPMC is as follows:

*Bus interface:* Rename the XCL interface so that each one connected to a Microblaze XCL bus.

*Port interface:* The basic ports configuration is based on the board setting. Their corresponding user constraints are defined in the system.ucf file. The memory unit needs a 200MHz clock to enable the DDR2. This unit also requires a 100MHz clock with a 90 degree shift, which can be generated by module Clock Generator.

Base Configuration: Set the all the ports interface to be XCL.

Figure 12: MPMC base Configuration

Memory Interface Tab: Choose the right part number: MT4HTF3264H-53E

*Port Configuration Tab:* XCL port is left default. Choose common Port Address for easy access.

| B | ase Configuration  | Memo     | ry Interface | Port Configu  | Iration | Advanced  |        |      |

|---|--------------------|----------|--------------|---------------|---------|-----------|--------|------|

| [ | Addresses Configur | ation    | Data Path C  | Configuration | Arbitra | ation ECC | PM/PHY | Misc |

|   | Use Commo          | n Port A | uddresses —  |               |         |           |        |      |

|   | Base Addr          |          |              |               |         |           | 0x9000 | 0000 |

Figure 13: Address Port configure for MPMC

Advanced Tab: Set BRAM as the FIFO configuration for each Port.

| se Configuration Mem      | ory Interface | Port Configuration    | Advanced      |            |                   |        | HDL Toggle  🌹 | Datasheet |

|---------------------------|---------------|-----------------------|---------------|------------|-------------------|--------|---------------|-----------|

| Addresses Configuration   | Data Path Cor | nfiguration Arbitrati | on ECC/PM/PHY | Misc       |                   |        |               |           |

| -General Pipeline Setting | J\$\$         |                       |               |            |                   |        |               |           |

| Write TML Pipeline        |               |                       |               | 🗹 🛛 Read P | peline Max Fanout |        |               | 0         |

| Port Specific Settings-   |               |                       |               |            |                   |        |               |           |

| Port                      | Port 0        | Port 1                | Port 2        | Port 3     | Port 4            | Port 5 | Port 6        | Port 7    |

| Read FIFO Config B        | RAM 😽         | BRAM 🗸                | BRAM 🖌        | BRAM 😽     | BRAM 😽            | BRAM 🖌 | BRAM 🖌        | BRAM      |

| Write FIFO Config B       | RAM 🔽         | BRAM 💌                | BRAM 💌        | BRAM 🗸     | BRAM 💙            | BRAM 🔽 | BRAM 💌        | BRAM      |

| Read Memory Pipeline      |               |                       | <b>V</b>      |            | <b>V</b>          |        |               |           |

| Read Port Pipeline        |               |                       | <b>V</b>      |            | <b>V</b>          |        |               |           |

| Write Memory Pipeline     |               |                       |               |            |                   |        |               |           |

| Write Port Pipeline       |               |                       |               |            |                   |        |               |           |

| Address Ack Pipeline      |               |                       |               |            |                   |        |               |           |

Figure 14: MPMC Port and Pipeline configuration

In vhdl, we need to add source files from FSL. The added source files and structure are listed as below:

cachelink.vhd

As you can see, cachelink.vhd is the top file of the added sources. You can view the source by opening file cachelink.vhd. It can be treated as a wrapper. It did not add any logic into the system. The only function it performs is creating two instance of FSL unit. Because FSL is unidirectional, you need one pair of FSL to communicate in duplex mode.

```

239

fsl 0 : fsl v20

240

generic map(

C_EXT_RESET HIGH

241

=> 1,--Active HIGH

242

C ASYNC CLKS

=> 1,--Async

243

C IMPL STYLE

=> 0,--Using LUT RAM

C USE CONTROL

=> 1,--Enable control bit

244

=> 32,

245

C_FSL_DWIDTH

C_FSL_DEPTH

246

=> 16,

247

C READ CLOCK PERIOD

=> 10 )

248

port map (

249

-- Clock and reset signals

250

FSL Clk => FSL A clk,

SYS_Rst => SYS_A_clk,

251

FSL Rst => FSL O Rst,

252

253

254

-- FSL master signals

FSL_M_Clk => FSL_A_M_CLK,

255

256

FSL_M_Data => FSL_A_M_DATA,

257

FSL M Control => FSL A M Control,

FSL_M_Write => FSL_A_M_Write,

258

FSL_M_Full => FSL_A_M_Full,

259

260

261

-- FSL slave signals

FSL_S_Clk => FSL_B_S_Clk,

FSL_S_Data => FSL_B_S_Data,

2.62

263

264

FSL S Control => FSL B S Control,

FSL_S_Read => FSL_B_S_Read,

265

266

FSL_S_Exists => FSL_B_S_Exists,

267

268

-- FIFO status signals

FSL_Full => FSL_0_Full,

FSL_Has_Data => FSL_0_Has_Data,

269

270

271

FSL Control IRQ => FSL 0 Control IRQ );

272

273

274

fsl 1 : fsl v20

275

276

generic map(

C_EXT_RESET HIGH

277

=> 1,--Active HIGH

278

C ASYNC CLKS

=> 1,--Async

C IMPL STYLE

279

=> 0,--Using LUT RAM

C_USE_CONTROL

=> 1,--Enable control bit

280

C_FSL_DWIDTH

=> 32,

281

282

C FSL DEPTH

=> 16,

C READ CLOCK PERIOD

=> 10 )

283

284

port map (

285

-- Clock and reset signals

FSL_Clk => FSL_B_clk,

286

287

SYS_Rst => SYS_B_clk,

FSL Rst => FSL 1 Rst,

288

```

Figure 15: CacheLink.vhd instantiate two FSL unit

Fsl\_v20 and others file are copied from Xilinx's fsl\_v2.11.a. The entire source files can be found from Xilinx ISE's IP library. For the verilog, all you need to take care is the file mpmc\_xcl\_if.v (If you want to create your own mpmc\_xcl\_if.v, be sure to change the file property to write/read from read only). This file provides the XCL interface to the external memory access. The original interface conforms to Xilinx's FSL bus interface. The inserted cachelink.vhd unit also conforms to FSL bus interface. The only difference lies in the clock because; each side is synchronized to different clock. In simple way, you can deem the cache link as an asynchronous FIFO with XCL interface.

At first, you need to introduce some intermediate signal between the inserted unit and the original FSL interface as shown below.

| 270        |                                         |                                   |                                         |

|------------|-----------------------------------------|-----------------------------------|-----------------------------------------|

| 270        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|            |                                         | chelink intermediate w            |                                         |

| 272        |                                         |                                   | /////////////////////////////////////// |

| 273        |                                         |                                   |                                         |

| 275        | //Signal for                            | FSL bus internal inte             | rface                                   |

| 276        | wire                                    |                                   | //                                      |

| 270        | wire [0:31]                             | `                                 |                                         |

| 278        | wire [0.31]                             | FSL A S Control;                  |                                         |

| 270        | wire                                    |                                   |                                         |

| 2 79       | wire                                    |                                   |                                         |

| 280        |                                         | FSL_A_S_EXISCS;<br>FSL A M Clk;   |                                         |

| 282        |                                         | FSL_A_M_CIK;<br>FSL A M Data;     |                                         |

| 283        | wire [0:31]                             | FSL_A_M_Data;<br>FSL A M Control; |                                         |

|            |                                         |                                   |                                         |

| 284<br>285 |                                         | FSL_A_M_Write;                    | 11                                      |

| 285        | wire                                    |                                   | //                                      |

|            | //Interal FSI                           | -                                 |                                         |

| 287        |                                         | FSL_int_S_Clk;                    |                                         |

| 288        |                                         | FSL_int_S_Data;                   | // (0-31)                               |

| 289        | wire                                    | FSL_int_S_Control;                |                                         |

| 290        | wire                                    | FSL_int_S_Read;                   |                                         |

| 291        | wire                                    |                                   |                                         |

| 292        | wire                                    | FSL_int_M_Clk;                    | 11                                      |

| 293        | wire [0:31]                             |                                   |                                         |

| 294        | wire                                    | FSL_int_M_Control;                |                                         |

| 295        | wire                                    | FSL_int_M_Write;                  |                                         |

| 296        | wire                                    | FSL_int_M_Full;                   | 11                                      |

| 297        |                                         |                                   |                                         |

Figure 16: Cache Link signal declaration in mpmc\_xcl\_if.v

Second, assign intermediate signals and instantiate the cache link unit.

```

301

302

assign FSL_A_M_Data = FSL_int_S_Data;

assign FSL_A_M_Control = FSL_int_S_Control;

303

assign FSL_int_M_Data = FSL_A_S_Data;

304

305

assign FSL_int_M_Control = FSL_A_S_Control;

306

307

assign FSL_int_M_Write = FSL_A_S_Exists && (!FSL_int_M_Full);

assign FSL_A_S_Read = FSL_A_S_Exists 66 (!FSL_int_M_Full);

308

309

310

assign FSL_A_M_Write = (! FSL_A_M_Full) && FSL_int_S_Exists ;

assign FSL_int_S_Read = (! FSL_A_M_Full) && FSL_int_S_Exists ;

311

312

313

// assign FSL & S Clk =Clk;

// assign FSL_A_M_Clk =Clk;

314

//Change Clk to Clk_MPMC

315

316

assign FSL & S_Clk =Clk MPMC;

assign FSL_A_M_C1k =C1k_MPMC;

317

318

319

cachelink #(

320

.C_BASEADDR(C_BASEADDR),

.C_HIGHADDR(C_HIGHADDR)

321

322

323

xcl_cachelink(

324

//.FSL & Clk(Clk),

//I

//Change Clk to Clk MPMC

325

.FSL_A_C1k(C1k_MPHC),

//1

326

327

.FSL_A_Rst(Rst),

//I

//.FSL_A_S_CIk(Cik),

328

//I

//Change Clk to Clk_MPMC

329

.FSL & S Clk(Clk MPMC),

330

//1

331

.FSL_A_S_Data(FSL_A_S_Data),

//0 (0-31)

.FSL_A_S_Control(FSL_A_S_Control),

.FSL_A_S_Read(FSL_A_S_Read),

332

110

//1

333

334

.FSL_A_S_Exists(FSL_A_S_Exists),

//0

.FSL_A_M_C1k(FSL_A_S_C1k),

335

//I

.FSL_A_M_Data(FSL_A_M_Data),

336

//I (0-31)

.FSL_A_M_Control(FSL_A_M_Control),

//I

337

338

.FSL_A_M_Write(FSL_A_M_Write),

//I

.FSL_A_M_Full(FSL A M Full),

339

110

340

341

.FSL_B_Clk(Read_Data_FSL_S_Clk),

//I

342

.FSL_B_Rst(Rst),

//I

.FSL_B_S_Clk(Read_Data_FSL_S_Clk),

//I

343

.FSL_B_S_Data(Read_Data_FSL_S_Data),

//0 (0-31)

344

345

.FSL_B_S_Control(Read_Data_FSL_S_Control),

//0

//I

346

.FSL B S Read (Read Data FSL S Read),

.FSL B S Exists (Read Data FSL S Exists) .

110

347

```

*Figure 17:* Cache link signal assignment and instance in mpmc xcl if.v

Third, modify the original read interface. Replace old signals with the new one from cache link. In addition, modify the original write interface. Note the clock signal need to be replaced carefully. Assigning a wrong clock signals will make the system very difficult to debug.

| 360   | ///////////////////////////////////////                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| 361   | // Handle Read Data Path Signals                                                                                      |

| 362   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                               |

| 3 6 3 | xcl read data #(                                                                                                      |

| 364   | .C PI DATA WIDTH (C PI DATA WIDTH),                                                                                   |

| 365   | .C PI RDWDADDR WIDTH (C PI RDWDADDR WIDTH),                                                                           |

| 366   | .C PI RDDATA DELAY (C PI RDDATA DELAY),                                                                               |

| 367   | .CLINESIZE (CLINESIZE),                                                                                               |

| 368   | .C_MEM_SDR_DATA_WIDTH (C_MEM_SDR_DATA_WIDTH),                                                                         |

| 369   | .C READ FIFO PIFE (P READ FIFO PIFE),                                                                                 |

| 370   | .C_RDFIFO_EMPTY_PIPE (P_RDFIFO_EMPTY_PIPE)                                                                            |

| 371   | )                                                                                                                     |

| 372   | xcl read data O (                                                                                                     |

| 373   | //.Clk (Clk), // I                                                                                                    |

| 374   | //Change Clk to Clk MPMC                                                                                              |

| 375   | .Clk(Clk_MPMC), //I                                                                                                   |

| 376   | .Clk_MPMC (Clk_MPMC), // I                                                                                            |

| 377   | .Rst (Rst), // I                                                                                                      |

| 378   | .Clk_PI_Enable (clk_pi_enable), // I                                                                                  |

| 379   | .PI_RdFIFO_Data (PI_RdFIFO_Data), // I [C_PI_DATA_WIDTH-1:0]                                                          |

| 380   | .PI_RdFIFO_Pop (PI_RdFIFO_Pop), // O                                                                                  |

| 381   | .PI_RdFIFO_RdWdAddr (PI_RdFIFO_RdWdAddr), // I [C_PI_RDWDADDR_WIDTH-1:0]                                              |

| 382   | .PI_RdFIFO_Empty (PI_RdFIFO_Empty), // I                                                                              |

| 383   | .PI_RdFIFO_Flush (PI_RdFIFO_Flush), // O                                                                              |

| 384   | .Target_Word (access_data[26:29]), // I                                                                               |

| 385   | // Comment the old port mapping                                                                                       |

| 386   | <pre>// .Read_Data_Exists (Read_Data_FSL_S_Exists), // 0 // .Read_Data_Control (Read_Data_FSL_S_Control), // 0 </pre> |

| 387   | // .Read_Data_Control (Read_Data_FSL_S_Control), // O                                                                 |

| 388   | // .Read_Data (Read_Data_FSL_S_Data), // O                                                                            |

| 389   |                                                                                                                       |

| 390   | // Start of new mapping                                                                                               |

| 391   | .Read_Data_Exists(FSL_int_S_Exists), // O                                                                             |

| 392   | .Read_Data_Control(FSL_int_S_Control), // O                                                                           |

| 393   | .Read_Data(FSL_int_S_Data), // O                                                                                      |

| 394   | .Read_Data_Read(FSL_int_S_Read), // I                                                                                 |

| 395   | .Read_Start (read_start), // I                                                                                        |

| 396   | .Read_Done (read_done) // O                                                                                           |

| 397   | );                                                                                                                    |

| 308   |                                                                                                                       |

*Figure 18:* Cache link signal and clock replacement of read data interface in mpmc\_xcl\_if.v

```

400

// Instantiate FSL FIFOs

401

402

403

// Access FSL FIFO

404

SRL16E access fifo[0:32] (

405

//.CLK(C1k),

//Change Clk to Clk_MPMC

406

407

.CLK(C1k MPMC),

//I

408

11

.CE(Access_FSL_M_Write),

409

11

.D({Access FSL M Control, Access FSL M Data}),

410

//Start of change

.CE(FSL_int_M_Write),

411

.D({FSL int M Control, FSL int M Data}),

412

413

//end of change

414

.AO(access raddr[0]),

415

.A1(access_raddr[1]),

416

.A2(access_raddr[2]),

417

.A3(access raddr[3]),

418

.Q({access_control_i, access_data_i})

419

);

420

421

// Access FSL read counter

422

mpmc rdcntr access raddr cntr (

423

//.rclk(Clk),

//Change Clk to Clk MPMC

424

425

.rclk(Clk_MPMC),

//I

426

.rst(Rst),

427

.ren(access ren i),

428

11

.wen(Access FSL M Write),

429

//Change

430

.wen(FSL_int_M_Write),

431

.raddr(access_raddr),

.full(Access FSL M Full),

432

17

433

//Change

434

.full(FSL int M Full),

435

.exists(access exists i)

436

1:

437

```

*Figure 19:* Cache link signal and clock replacement of write data interface in mpmc\_xcl\_if.v

If all these source files are changed for particular experiment, we need to add these source file in the pao files. (The .pao file is introduced in <u>Platform Specification Format</u> <u>Reference Manual</u>, which can be found at <u>http://www.xilinx.com/support/documentation/sw\_manuals/edk63i\_psf\_rm.pdf</u>. Besides, Xilinx's XAPP 967 gives the detail to create an IP, which is available at <u>http://www.xilinx.com/support/documentation/application\_notes/xapp967.pdf</u>). The declaration in pao file will help the parser recognize these files and compile them before use.

#### *Fast Simplex Link (FSL)*

As explained in the previous chapter, FSL is a fast connection between 2 processors. It is a uni-direction channel, so you should use a pair for duplex communication. It supports asynchronous communication between two clock domains. The base version is 2.10.a. The lasts version 2.11.a would cause some implementation error, so we stick to the older version. Any later version should be tested before you integrated it into the system.

*Base configuration:* Set this unit run in asynchronous mode. The depth of FIFO can also be configured from 1 to 32. You can tailor the depth according to communication need.

*Port Configuration:* In each FSL channel, you should assign a master clock, FSL\_M\_CLK, to transmitter end and a slave clock, FSL\_S\_CLK, to the receiver. There is another clock FSL\_CLK, which only used in synchronous communication. You can ignore it in this project. There are some other handshake signals in the port section. For their usage, you can refer to FSL datasheet. Here is an example:

| 🖃 🗢 fsl01 |            |               |   |   |

|-----------|------------|---------------|---|---|

| FSL_Co    | ontrol_IRQ | No Connection | ~ | 0 |

| FSL_Ha    | as_Data    | No Connection | ~ | 0 |

| FSL_Fu    | II         | No Connection | ~ | 0 |

| FSL_S_    | Clk        | sys_clk1_s    | ~ | 1 |

| FSL_M     | _Clk       | sys_clk_s     | ~ | 1 |

| SYS_R     | st         | sys_rst_s     | ~ | 1 |

| -FSL_CI   | <          | sys_clk_s     | ~ | 1 |

Figure 20: Sample of FSL signal assignment

#### Clock Control Unit

The clock unit is based on Xilinx's dynamic programmable Digital Clock Manager (DCM). The detail of the clock generation can be found in the DCM datasheet and manual. The data interface is PLB. Clock control unit has a PLB slave interface. The processor can program this unit via PLB bus. The function of this unit is to translate the

control word, and write the control into DCM unit, and generate the desired clock. There is no need to configure this unit. The customization work is given in the following.

There are two version of clk\_control. In /ProjectName/pcore, clk\_control\_v2\_01\_a and clk\_control\_v3\_01\_a. The former one is obsolete unit. We only used the latter unit. The user ports are declared in mpd file, which can be found in /ProjectName/pcore/ clk control v3 01 a/data.

| 37 | ## Ports                            |

|----|-------------------------------------|

| 38 | PORT clk_in = "", DIR = I           |

| 39 | PORT clk0 = "", DIR = O             |

| 40 | PORT clk90 = "", DIR = O            |

| 41 | Port clk2x = "", DIR = O            |

| 42 | PORT clk_out = "", DIR = O          |

| 43 | PORT lock = "", DIR = O             |

| 44 | PORT mux = "", DIR = 0, VEC = [1:0] |

Figure 21: Port signal declaration

In file user\_logic.vhd, the design unit is declared like this.

| USER signal declarati | ions added here, as needed for user logic |

|-----------------------|-------------------------------------------|

| signal mux_i          | : std_logic_vector(13 downto 0);          |

| component top is      |                                           |

| Port ( clk in : in    | n STD LOGIC;                              |

| comment clk           | sam                                       |

| clk sam :             | out std logic;                            |

| c1k0 : ou             | it std logic;                             |

| c1k90 : ou            | it std logic;                             |

| clk2x : ou            | it std logic;                             |

| clk out : ou          | it std logic;                             |

| rst : ir              | n STD_LOGIC;                              |

| mux : ir              | n std logic vector(13 downto 0);          |

| lock : ou             | at STD LOGIC);                            |

| end component;        | -                                         |

Figure 22: Clock Control Unit declaration in file user\_logic.vhd

For the design source file, you can see files like this. The clk\_control.vhd and user\_logic.vhd are generated by system template. The design top unit, top.vhd is instantiated in user\_logic.vhd. The top.vhd calls drp\_control.vhd for logic control, dcm1.vhd for clock generation. The sample.vhd is for debug purpose.

| Look in:                          | 🗁 vhdi                                                                                                                        |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| My Recent<br>Documents<br>Desktop | जिम्म clk_control.vhd<br>जिम्म dcm1.vhd<br>जिम्म drp_control.vhd<br>जिम्म sample.vhd<br>जिम्म top.vhd<br>जिम्म user_logic.vhd |

Figure 23: File Structure of Clock Control unit

The decode logic is included in top.vhd and the following code specify the desired clock. You can change it to other clock frequency or you can modify them to support more clock choices.

| 219 | process(clkin)                                                             |

|-----|----------------------------------------------------------------------------|

| 220 | begin                                                                      |

| 221 | if(clkin'event and clkin ='1') then                                        |

| 222 | if mux_reg /=mux then                                                      |

| 223 | start <= '1';                                                              |

| 224 | case mux is                                                                |

| 225 | <pre>when "01" =&gt; multiply&lt;="00001"; divide&lt;="00100";40M</pre>    |

| 226 | <pre>when "10" =&gt; multiply&lt;="00001"; divide&lt;="00011";50M</pre>    |

| 227 | <pre>when "11" =&gt; multiply&lt;="00001"; divide&lt;="00010";66.7M</pre>  |

| 228 | when "00" => multiply<="00001"; divide<="00101";33.3M                      |

| 229 | <pre>when others =&gt; multiply&lt;="00001"; divide&lt;="00001";100M</pre> |

| 230 | end case;                                                                  |

| 231 | else                                                                       |

| 232 | start <= '0';                                                              |

| 233 | end if;                                                                    |

| 234 | end if;                                                                    |

| 235 | end process;                                                               |

| 226 |                                                                            |

Figure 24: Clock assignment in top.vhd

# Configuration Unit

This is also a simple customized unit to facilitate the multiple processor programs loading. The purpose is to enable the main processor (program loading processor) to reset the other processor when the program loading from flash to DDR2 is done. The added ports are declared at the beginning of user\_logic.vhd.

| 2.1 | poro                                                           |

|-----|----------------------------------------------------------------|

| 98  |                                                                |

| 99  | ADD USER PORTS BELOW THIS LINE                                 |

| 100 | USER ports added here                                          |

| 101 | ADD USER PORTS ABOVE THIS LINE                                 |

| 102 | mb_reset : in std_logic;input MicroBlaze reset                 |

| 103 | mbctrl_rst : out std_logic; output controlled MicroBlaze reset |

| 104 | DO NOT FDIT BELOW THIS LINE                                    |

Figure 25: Port declaration in Configuration Unit

The basic logic is shown in the following figure. The mbctrl\_rst is the output reset signal. This unit controls the reset signal by the data (Bus2IP\_Data) from main processor. In this way, the main Microblaze can reset the other processors and release them after program loading.

```

143 begin

144

145

--USER logic implementation added here

146

process(Bus2IP_Clk) is

147

148

begin

149

150

151

152

else

153

if Bus2IP_WrCE(0) = '1' then

ctrl <= Bus2IP_Data(0);

else</pre>

154

155

156

ctrl <= ctrl;

157

end if;

158

end if:

159

end if:

160

end process;

161

162

process(Bus2IP_Clk) is

163

begin

if Bus2IP_Clk'event and Bus2IP_Clk ='1' then

if ctrl = '1' then

164

165

166

mbctrl_rst <= '1';</pre>

167

else

168

mbctrl_rst <= mb_reset;</pre>

169

end if;

170

end if;

171

end process;

172

173

```

Figure 26: Logic in Configuration Unit

# 3.2 The Design of Sharing Memory

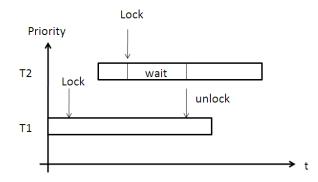

#### A. Implicit Multiprocessing

In this method, a single copy of operating system runs and controls any number of processors in the system (as shown in Figure 27). Parallelism between the processers is

hidden by an operating system and hardware. The Microblaze processor does not support cache coherency and hence the implementation of cache coherency in software application has a very large impact.

Figure 27: Implicit Multiprocessing

# B. Explicit Multiprocessing

Another method of achieving multi-processor systems is to run every Microblaze with its own copy of RTOS. The Microblazes will have their private own address zones within the shared memory and the shared memory region with protocols. Since a different RTOS sits on each of the processor it leads to lot of memory space.

Figure 28: Explicit Multiprocessing

However, for more number of processors using shared BRAM is not supported, so we make use external memory controller MPMC. To enable large test programs and data sizes, we divide the external memory (DDR2\_SDRAM) into several memory sections and one shared section. Each private memory section is associated with one processor and can only be accessed by that processor. The shared memory section, on the other hand, can be accessed by all processor cores.

#### 3.3 The Design of Inter-processor Communication

## A. XPS Mutex

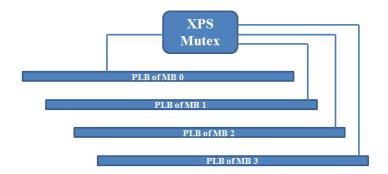

In multiple processors XPS Mutex helps in synchronization when accessing shared resources. The mutex core has a configurable number of mutexes and writes to lock scheme. The mutex provides a mechanism for mutual exclusion to enable one processor to gain access to the shared resource. The shared resource in our project is the on board RS 232 UART interface where all the processors redirect their STDOUT to this shared console. Without synchronization, the console output would become useless. Hence, each processor locks XPS Mutex core before doing any output and then unlocks when done. The XPS Mutex IP currently available can support up to 8 processors. The connection of XPS Mutex to the PLB of individual processors is shown in figure below. The current XPS Mutex IP supports up to 8 PLB or FSL interfaces.

Figure 29: Schematic Representation of XPS Mutex Connection

#### B. XPS Mailbox

In a multi-processors environment, Processors need to communicate the data among them. The mailbox IP helps passing these simple messages (< a few 100 bytes) from one processor to another in a FIFO fashion. These mailboxes have a bi-directional communication channel and can be connected through PLB or FSL interface (similar to Figure 29). Apart from sending the data between processors, the mailbox can also be used to generate interrupts between the processors. The XPS Mailbox has two interfaces that are used to connect to the rest of the system. Both of these interfaces can be independently configured to use PLB or FSL bus.

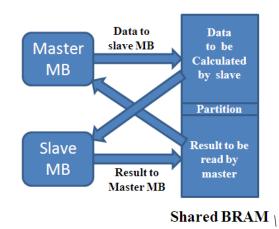

#### The Matrix Addition Example on the system

Initially, the dual Microblaze processor system was tested with matrix addition example with booted real-time operating system, xilkernel. Using inter-processor communication technique, a system with two processes that uses a shared BRAM and an external memory DDR2SDRAM to accommodate the OS xilkernel, is built. The master

Microblaze has the data on which matrix addition is to be performed. It writes the data to the shared BRAM. The slave Microblaze waits and keeps on checking whether a particular bit is set or not flagging that data has been written completely. Then the slave Microblaze starts reading the data. Once completed it calculates and writes the result to a different location on the shared BRAM memory. The master Microblaze then calculates the final result and displays the result on the hyper terminal window (RS232 UART).

Figure 30: Schematic Representation of Matrix Addition

# Output Display RS232UART

The serial output is supposed to print out computation result. The baud rate can be configured in this IP. Due to the limit of computer serial output, the highest baud rate can be set to 112k. In addition, the parity and bit number should be set the same as with the computer serial terminal.

## Boot loader

The scratch pad memory within a PE unit is limited. The Xilinx's EDK boots only one processor at a time. To boot all four Microblazes, we need to customize the bootloader and configure other programs like link script. Also, the flash programmer is supposed to program the main program into the flash. Boot loader is the program in charge of program loading from flash memory into DDR2\_SDRAM. As we have multiple programs to load, we also need to customize the default bootloader, so that they can load all the images into DDR\_SDRAM. After the program loading, it needs to notify the other processor, so that they can jump into the memory. The default boot loader only loads one image. The following code reloads multiple copies of program images from flash:

```

120

//Load the image for MB3

121

print(" Start of Image 3\r\n"):

flbuf = (uint8 t*)FLASH IMAGE BASEADDR3;

122

123

ret3 = load exec ();

124

print(" End of Image 3\r\n");

125

//Notify the MB3_Boot to jump into the program address

126

127

//putfsl(1,2);

128

129

//Load the image for MB2

print(" Start of Image 2\r\n");

130

131

flbuf = (uint8_t*)FLASH_IMAGE_BASEADDR2;

ret2 = load_exec ();

132

133

print(" End of Image 2\r\n");

134

//Notify the MB2 Boot to jump into the program address

135

//putfsl(1,1);

136

137

//Load the image for MB1

138

print(" Start of Image 1\r\n");

flbuf = (uint8_t*)FLASH_IMAGE_BASEADDR1;

139

140

ret1 = load_exec ();

print(" End of Image 1\r\n");

141

//Notify the MB1 Boot to jump into the program address

142

//putfs1(1,0);

143

144

145

//Load the image for MBO

146

//Make sure the last image is for MBO

print(" Start of Image O(r n");

147

flbuf = (uint8_t*)FLASH_IMAGE_BASEADDR;

148

149

ret = load exec();

print(" End of Image 0\r\n");

150

151

//laddr = (uint8_t *)XPAR_DDR_SDRAM_MPMC_BASEADDR ;

1.52

//(*laddr)(); //start the program

153

```

*Figure31*: Loading more than one image into FLASH PROM

The starting address of each image can be found in header file blconfig.h.

1

#define FLASH\_IMAGE\_BASEADDR

( XPAR\_FLASH\_MEMO\_BASEADDR+ 0x90000000)//Program for MB0

2

#define FLASH\_IMAGE\_BASEADDR1

( XPAR\_FLASH\_MEMO\_BASEADDR+ 0x91000000)//Program for MB1

3

#define FLASH\_IMAGE\_BASEADDR2

( XPAR\_FLASH\_MEMO\_BASEADDR+ 0x91000000)//Program for MB1

4

#define FLASH\_IMAGE\_BASEADDR3

( XPAR\_FLASH\_MEMO\_BASEADDR + 0x92000000)//Program for MB2

5

5

Figure 32: Define starting address of image in FLASH PROM

Before the program loading, reset all other processor via Configuration control unit.

```

109 -

110

110

111 //reset other MicroBlazes

112 val = 1;

113 shift = val<<31;

114 CONFIG_CTRL_mWriteReg(XPAR_CONFIG_CTRL_0_BASEADDR,0,shift);

115</pre>

```

Figure 33: Reset other processor before image loading

After the program loading, reset other processors, and jump into starting address of new

program. The jump start address is predefined.

| 154 |                                                             |

|-----|-------------------------------------------------------------|

| 155 |                                                             |

| 156 | //Release other MicroBlazes                                 |

| 157 | val = 0 ;                                                   |

| 158 | <pre>shift = val&lt;&lt;31;</pre>                           |

| 159 | CONFIG_CTRL_mWriteReg(XPAR_CONFIG_CTRL_0_BASEADDR,0,shift); |

| 160 |                                                             |

| 161 | //Jump to the starting address of MBO                       |

| 162 | <pre>func_ptr = PROG_START_ADDR;</pre>                      |

| 163 | func_ptr();                                                 |

| 164 |                                                             |

| 165 | <pre>/* If we reach here, we are in error */</pre>          |

| 166 |                                                             |

|     |                                                             |