# Aging-Aware Design Methods for Reliable Analog Integrated Circuits using Operating Point-Dependent Degradation

Dem Fachbereich Physik, Elektrotechnik und Informationstechnik der Universität Bremen

zur Erlangung des akademischen Grades eines DOKTOR-INGENIEUR (Dr.-Ing.) genehmigte Dissertation

von

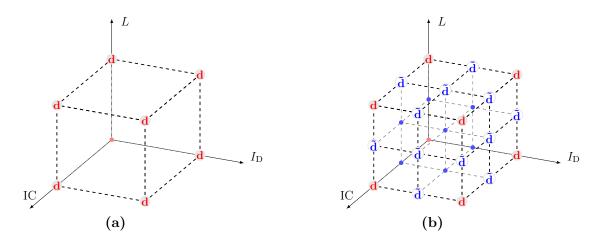

Dipl.-Ing. Nico Hellwege aus Bremerhaven

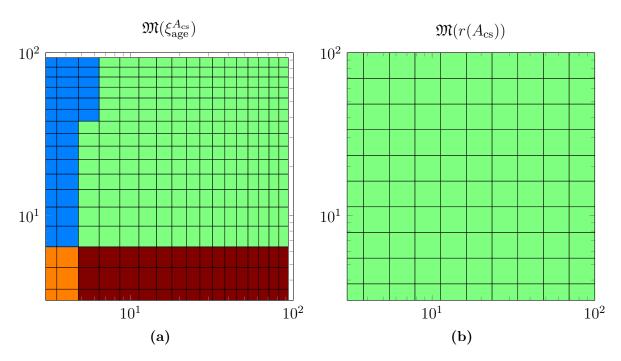

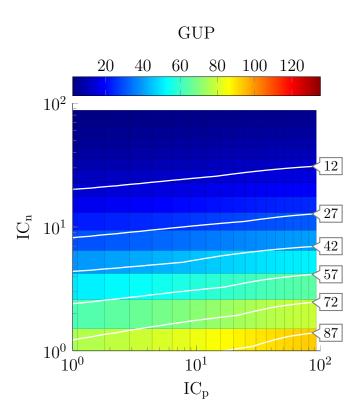

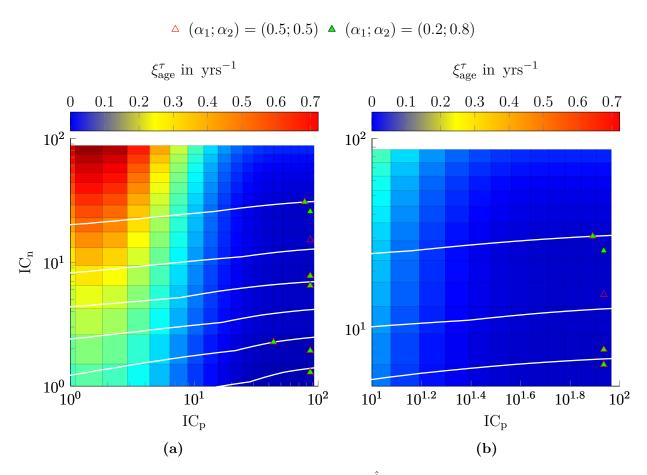

Referent: Professor Dr.-Ing. St. Paul Korreferent: Professor Dr.-Ing. W. Nebel

Eingereicht am: 29.09.2015 Tag des Promotionskolloquiums: 11.12.2015

# Abstract

Reliability of integrated circuits fabricated using deep-submicrometer technology nodes is significantly affected by variations in process parameters, supply voltage and ambient temperature (PVT). More recently, also time-dependent degradation modes in complementary metal oxide semiconductors (CMOS) have risen as a key aspect in a reliability-driven analog integrated circuit design, as aging mechanisms additionally threaten a reliable operation over lifetime. These so called PVTA variations need to be considered during circuit design, in order to satisfy given specification limits and reliability constraints. Whereas in the digital domain methods handling these shifts have already been established over the past decades, the analog domain is still in need of aging-aware design methods, which help to solve the challenges caused by degrading circuit characteristics.

In practice, most analog designs start with hand calculated estimates of circuit characteristics, which need to be proven and refined by SPICE equivalent circuit simulations. However, the impact of degradation modes on circuit characteristics is first investigated after all design targets have been set. Special reliability simulators use complex models of degradation effects in order to compute expected deviations in circuit behavior based on a series of different SPICE simulations. This scheme results in long iterative simulation runs and leaves no insight to the designer on how to optimize towards higher reliability.

The focus of this thesis is on the development and implementation of aging-aware design methods, which are suitable to satisfy current needs of analog circuit design. Based on the well known  $g_{\rm m}/I_{\rm D}$  sizing methodology, an innovative tool-assisted aging-aware design approach is proposed, which is able to estimate shifts in circuit characteristics using mostly hand calculation schemes. The developed concept of an operating point-dependent degradation leads to the definition of an aging-aware sensitivity, which is compared to currently available degradation simulation flows and proves to be efficient in the estimation of circuit degradation. Using the aging-aware sensitivity, several analog circuits are investigated and optimized towards higher reliability. Finally, results are presented for numerous target specifications.

# Kurzfassung

Die Zuverlässigkeit von integrierten Schaltkreisen, die unter Verwendung von Technologieknoten im Submikrometerbereich hergestellt werden, unterliegen signifikanten Variationen der Prozessparameter, Versorgungsspannung und Temperatur (PVT). Unlängst erhalten auch zeitabhängige Degradierungsmoden eine Schlüsselrolle im zuverlässigkeitsorientierten Entwurf analoger integrierter Schaltungen, da diese Alterung zusätzlich den Betrieb über die Lebenszeit beeinflusst. Diese sogenannten PVTA Variationen müssen im Entwurf berücksichtigt werden, um gegebene Spezifikationen der Zuverlässigkeit einzuhalten. Während in der digitalen Domäne bereits seit Jahrzehnten Verfahren zur Einhaltung von Spezifikationen unter Berücksichtigung von PVTA Variationen existieren, werden diese Methoden in der analogen Domäne noch vermisst.

Im Allgemeinen beginnt der Entwurf von analogen Komponenten durch Berechnung von einfachen Gleichungen ohne Rechnerunterstützung. Die abgeschätzten Charakteristiken werden basierend auf einer Netzliste durch eine SPICE äquivalente Simulation gestützt und verfeinert. Die Auswirkung der Degradationsmoden auf Schaltungseigenschaften wird erst nach der Festlegung aller Entwurfsziele betrachtet. Spezielle Zuverlässigkeitssimulatoren verwenden komplexe Alterungsmodelle zur Berechnung der erwarteten Abweichung in den Schaltungseigenschaften, aufbauend auf einer Reihe unterschiedlicher SPICE Simulationen. Hierdurch entstehen lange Simulationszeiten und es ergeben sich keine Einblicke für den Entwurf der Schaltung, durch welche Änderungen eine Erhöhung der Zuverlässigkeit erzielt werden kann.

Der Schwerpunkt dieser Arbeit ist die Entwicklung und Implementierung einer Entwurfsmethode für analoge Schaltungen, die die Berücksichtigung von Alterungsmechanismen bereits im Handentwurf ermöglicht. Basierend auf der bekannten  $g_{\rm m}/I_{\rm D}$  Dimensionierungsmethode wird ein programmgestützter Entwurfsansatz vorgestellt, der auf Basis von Handberechnungen die alterungsabhängige Verschiebung von Schaltungseigenschaften bestimmen kann. Das entwickelte Konzept der arbeitspunktabhängigen Degradierung führt zur Definition von alterungsabhängigen Sensitivitätsfeldern, die mit bestehenden Simulationsabläufen verglichen werden und sich als effiziente Methode zur Approximation von Alterungseinflüssen herausstellt. Mit Hilfe dieser Methodik werden verschiedene Schaltungen untersucht und auf höhere Zuverlässigkeit hin optimiert. Abschließend werden Ergebnisse für unterschiedliche Schaltungseigenschaften präsentiert.

# Foreword

This work originated as part of my research activities as a doctoral student and research assistant at the Institute of Electrodynamics and Microelectronics (ITEM) at the university of Bremen at the department of mobile communication. I would like to thank Prof. Steffen Paul for the supervision of this work and also for the comments, hints and methodical advices I was given over the years. Also I have to thank Prof. Wolfgang Nebel of the university of Oldenburg for being the second reviewer of this thesis. I thank Prof. Walter Lang and Prof. Alberto Garcia for the examination at the colloquium. I have to thank all of my colleagues, which I have had the pleasure working with over the past years. With some of them I had worked very closely and had numerous discussions and debates, which enriched this thesis as well as my personal development. Specifically, I want to thank Nils Heidmann, for sharing his scientific abilities with his officemate and also for his ongoing encouragement during our stay at the ITEM. Secondly, I have to thank Jonas Pistor for his ideas, advices and inspiring talks. I want to thank Dagmar Peters-Drolshagen for her support and encouraging advices and also Valerie Gerdes, for being her my omniscient language consultant and for always helping me out. Great thanks also to the Michael Peeper and the technical staff, which I have worked very closely with.

All of this would not have been possible, without the continuous support from my family, especially my parents Monika and Jürgen, and also from my partner Sandra, who had always taken care of me with her love, strength and understanding.

| T | Int | coduction                                        |

|---|-----|--------------------------------------------------|

|   | 1.1 | Contributions by the Author                      |

|   | 1.2 | Structure of this Work                           |

| 2 | Rel | iability in CMOS Circuits                        |

|   | 2.1 | Fundamentals                                     |

|   |     | 2.1.1 Yield and Reliability                      |

|   |     | 2.1.2 Reliability Function and Failure Rate      |

|   | 2.2 | Classification of Reliability Issues             |

|   |     | 2.2.1 Variability                                |

|   |     | 2.2.2 Systematic Inter-device Effects            |

|   |     | 2.2.3 Random Intra-device Effects                |

|   |     | 2.2.4 Transient Degradation Effects              |

|   |     | 2.2.5 Other Variability Sources                  |

|   | 2.3 | Aging                                            |

|   |     | 2.3.1 Physical Origin of Aging Mechanisms        |

|   |     | 2.3.2 Hot Carrier Degradation (HCD)              |

|   |     | 2.3.3 Bias Temperature Instability (BTI)         |

|   |     | 2.3.4 Time Dependent Dielectric Breakdown (TDDB) |

|   |     | 2.3.5 Electromigration (EM)                      |

|   | 2.4 | Aging and Reliability Simulation                 |

|   |     | 2.4.1 Mentor Graphics ELDO                       |

|   |     | 2.4.2 Synopsys MOSRA                             |

|   |     | 2.4.3 Cadence RelXpert                           |

|   |     | 2.4.4 RelXpert Simulation Flow                   |

|   | 2.5 | Compact Modeling of Aging Mechanisms             |

|   |     | 2.5.1 Reaction-Diffusion Model for NBTI          |

|   |     | 2.5.2 Lucky Electron Model for HCD               |

|   |     | 2.5.3 Circuit Lifetime Model                     |

|   | 2.6 | Summary 30                                       |

viii Contents

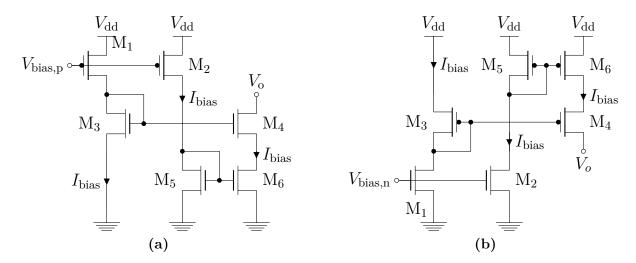

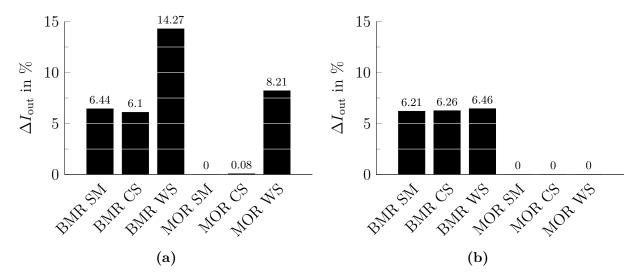

| 3 | Deg | gradation-Oriented Analog Circuit Design                         |

|---|-----|------------------------------------------------------------------|

|   | 3.1 | Single Transistor Degradation Behavior                           |

|   | 3.2 | Current Mirrors                                                  |

|   | 3.3 | Bias Circuits                                                    |

|   |     | 3.3.1 Mos Only Reference (MOR)                                   |

|   |     | 3.3.2 Beta Matching Reference (BMR)                              |

|   | 3.4 | Mirror Circuits                                                  |

|   |     | 3.4.1 Cascode Mirror Structure                                   |

|   |     | 3.4.2 Wide Swing Mirror Structure                                |

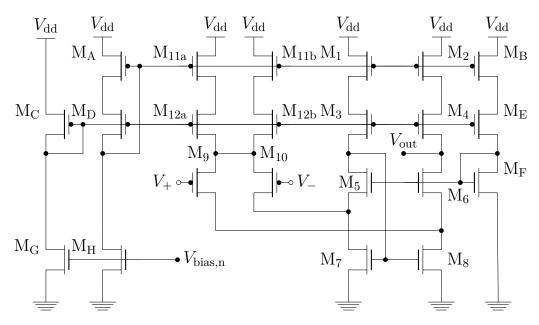

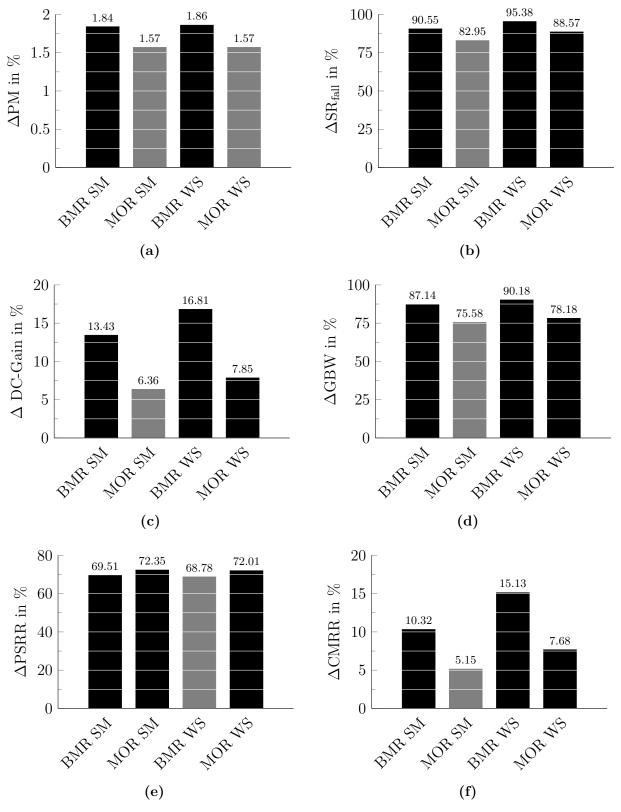

|   | 3.5 | Structural Degradation-Oriented Circuit Design                   |

|   |     | 3.5.1 Degradation in Bias and Mirror Circuits                    |

|   |     | 3.5.2 Degradation in a Folded Cascode Amplifier                  |

|   | 3.6 | Generation of Reliability Figures                                |

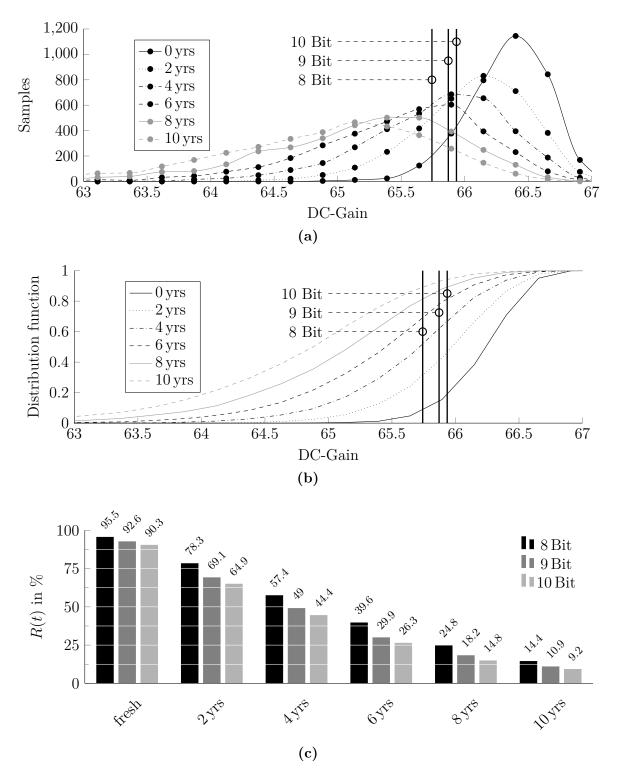

|   |     | 3.6.1 Stochastic Circuit Simulation                              |

|   |     | 3.6.2 Variability-Aware Gradual Aging                            |

|   | 3.7 | Reliability Analysis for a Neural Measurement System             |

|   |     | 3.7.1 Neural Measurement System                                  |

|   |     | 3.7.2 Reliability Figures for Neural LNA                         |

|   | 3.8 | Summary                                                          |

| 4 | Op  | erating Point Dependent-Degradation                              |

|   | 4.1 | MOS Models                                                       |

|   | 4.2 | Description of Operating Points                                  |

|   | 4.3 | $g_{\rm m}/I_{\rm D}$ Sizing Method                              |

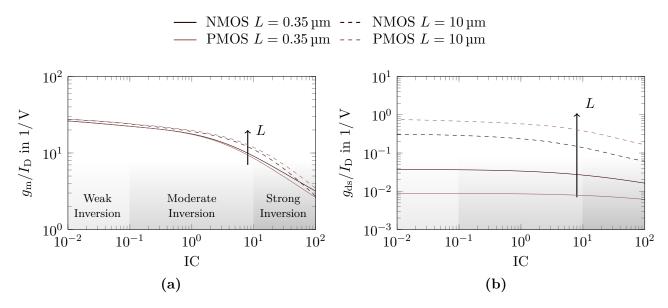

|   |     | 4.3.1 Transconductance Efficiency                                |

|   |     | 4.3.2 Inversion Coefficient                                      |

|   |     | 4.3.3 Levels of Inversion and IC                                 |

|   |     | 4.3.4 Simulation Setup                                           |

|   |     | 4.3.5 Sizing Rules within the $g_{\rm m}/I_{\rm D}$ Scheme       |

|   | 4.4 | Operating Point and Degradation                                  |

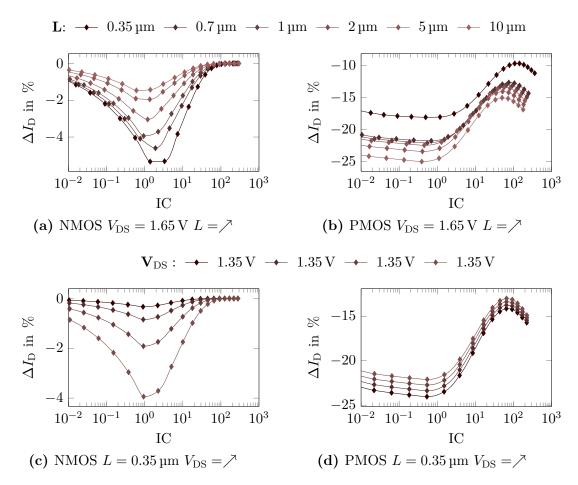

|   |     | 4.4.1 Drain Current $I_D$                                        |

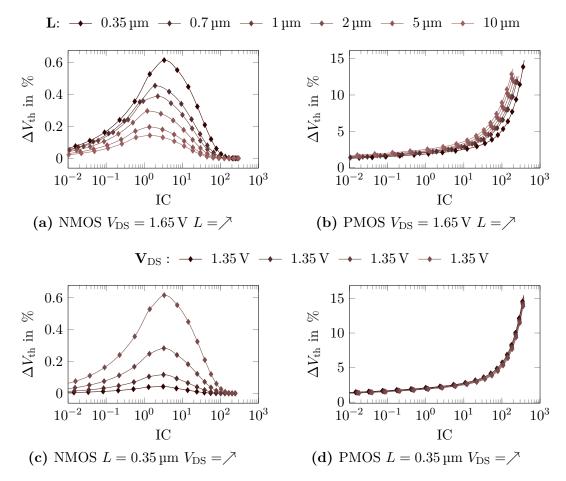

|   |     | 4.4.2 Threshold Voltage $V_{\rm th}$                             |

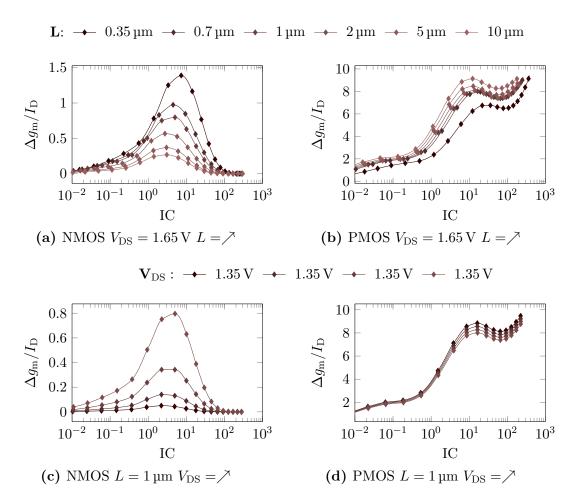

|   |     | 4.4.3 Transconductance Efficiency $g_{\rm m}/I_{\rm D}$          |

|   |     | 4.4.4 Output Conductance Efficiency $g_{ds}/I_D$                 |

|   | 4.5 | Aged Performance Characteristics of a Common Source Amplifier 70 |

|   | 4.6 | Tool-Assisted Design within the $g_{\rm m}/I_{\rm D}$ Scheme     |

|   |     | 4.6.1 The GMID-Tool                                              |

|   |     | 4.6.2 Aging-Aware Design Flow                                    |

|   | 4.7 | Aging-Aware Design of a Miller Amplifier                         |

|   | 4.8 | Summary                                                          |

<u>Contents</u> ix

| 5            | Agi   | ng-Aware Sensitivity for Analog Circuit Design 8              |

|--------------|-------|---------------------------------------------------------------|

|              | 5.1   | Sensitivity in Circuit Design                                 |

|              | 5.2   | Aging-Aware Sensitivity (AAS)                                 |

|              |       | 5.2.1 Definition of AAS                                       |

|              |       | 5.2.2 AAS of Composed Performance Values                      |

|              | 5.3   | AAS for a Common Source Amplifier                             |

|              |       | 5.3.1 DC-Gain                                                 |

|              |       | 5.3.2 Unity-Gain-Frequency                                    |

|              |       | 5.3.3 Comparison of Designs                                   |

|              | 5.4   | Validity of Aging-Aware Sensitivity Maps                      |

|              | 5.5   | Optimum Aging-Aware Operating Point                           |

|              | 5.6   | Summary                                                       |

| 6            | Cor   | nclusion and Outlook                                          |

|              | 6.1   | Conclusion                                                    |

|              | 6.2   | Outlook                                                       |

| $\mathbf{A}$ | Apj   | pendix 10                                                     |

|              | A.1   | Transistor Dimensions for Structural Degradation Analysis 10- |

|              | A.2   | Results for the Structural Degradation Analysis               |

|              | A.3   | Results of the Miller-Opamp Design                            |

|              | A.4   | Degraded System Characteristics (VAGA)                        |

|              |       | Dimensions for Miller Amplifier                               |

|              | A.6   | Optimum Operating Points from AAS Analysis                    |

| Li           | st of | <b>Abbreviations</b>                                          |

| Li           | st of | Symbols                                                       |

| Bi           | blio  | graphy                                                        |

# 1 Introduction

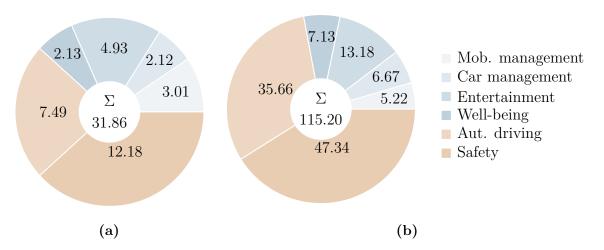

Design and development of electronic components with reliable operational lifetimes of several years or even decades has become a key challenge in several fields of safety-critical applications, such as automotive, avionic or medical. The need for reliable electronics is seen for all three of these fields. In the case of automotive applications, two fields are emerging at a rapid development pace: safety systems and components for autonomous driving. A recent study [117] shows a huge increase in the potential market share for automotive electronics from 2015 to 2020, which is almost entirely driven by an increase for safety systems and components for autonomous driving, as seen in Fig. 1.1. The total market share increases from 31.86 billion Euro to 115.20 billion Euro, where the difference of 83.34 billion Euro is almost completely build on the increase in those to sectors (63.33 billion Euro). Avionic manual systems have been replaced by electronics over the past decades, e.g. in fly-by-wire systems [37]. Obviously, those systems need to be highly reliable during flight operation. This not only includes the algorithmic core, but also sensors and measurement systems, which are distributed throughout the aircraft. Most of these exterior components are composed of mixed-signal circuits with a high percentage of analog circuitry. A main relief on the constraints of reliability for automotive and avionic electronic systems is the ability to replace parts as needed (or demanded by service intervals). In medical applications, such as a pacemaker or an intracortical neural measurement system, a change of components is not easily performed, as this mostly involves medical surgeries. These surgeries put patience in danger, which should be avoided under any circumstances. All of the above fields of electronic applications build upon reliable systems and circuits, which need to satisfy high standards.

The design of integrated circuits usually incorporates the use of transistor models, which describe the behavior of a device directly after fabrication. However, there exist several physical degradation mechanisms, which alter transistor parameters over time, leading to degraded circuit characteristics. One of the most discussed modes are negative bias temperature instability (NBTI) and hot carrier degradation (HCD), which both lead to a shift of the threshold voltage of a transistor. These physical degradation modes are a major source of reliable issues, which need to be addressed, in order to assure a proper operation of the system.

2 1 Introduction

Figure 1.1: Developement of potential market share considering the automotive sector in billion Euro. Estimates for (a) 2015 and (b) 2020 [117].

When these reliability issues first occurred, the design flow for developing analog integrated circuits had not been adopted to the upcoming challenges. In the digital domain an impact of degradation is mostly seen as a shift in a gate delay, which could already be analyzed with existing yield and timing analysis tools. The analog domain is based on a completely different development flow and the impact on circuit level is seen in many different performance characteristics. However, decades ago the measured influence on analog circuits seemed little, so not attempt was made to account for degradation in the design flow. As smaller technology nodes evolved, the impact of degradation effects on analog circuits increased. Since the design flow has not changed, an estimation of reliability (or lifetime) has only been performed at the very end and has more been considered as a post-schematic analysis. This is mostly due to the complicated nature of the degradation modes, for which specific simulators are needed to calculate the estimated deviations in behavior. Typically, a simulation addressing transistor reliability effects is at least two to three time slower, than a regular circuit simulation. Both of these factors, the need of additional simulators and the enormous increase in the computational runtime of the simulators, has led to the situation that even today, no effort is made to put these steps to earlier design phases.

However, as degradation and reliability become more and more a key aspect in circuit design, these issues should be dealt with as early as possible in the design flow, as major decisions are made in the very beginning of the design flow: the hand calculation phase. Although modern research approaches try to cover the aspect of aging circuits in early design phases, all of them basically still rely on complete circuits, which again puts the investigation of degradation to end of the design flow. An approach, where the estimation of reliability effects is brought to the hand calculation phase, has not been thoroughly investigated so far.

# 1.1 Contributions by the Author

The core contribution of this work is an aging-aware design methodology for analog integrated circuits, which provides methods and tools allowing a consideration of degradation-induced deviations of circuit characteristics at the very beginning of the design flow. This is achieved by using normalized small signal parameters, which degrade in dependence on the operating point of the device [51]. The notion of an operating point-dependent degradation leads to the definition of a so called aging-aware sensitivity (AAS) [54] [48], enabling designers to take degradation into account as an analytical parameter.

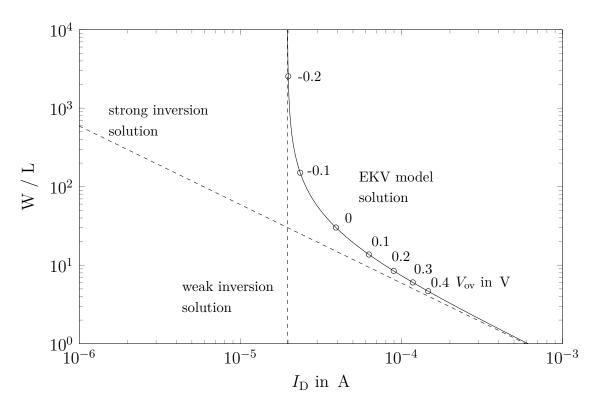

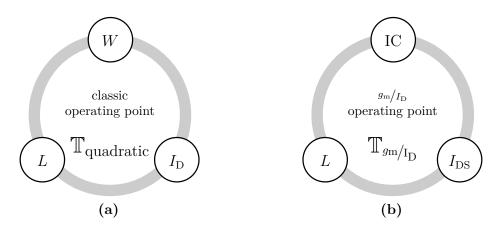

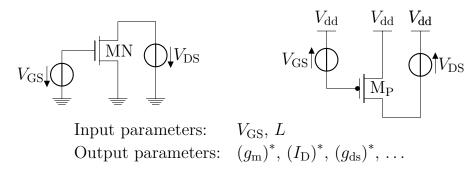

In order to allow an investigation on reliability effects at an early design phase, a proper design method needs to be chosen and evaluated first. In general, there exist several different design methods, which account for simple hand calculations results. The majority of these methods are based on Shockley's quadratic MOS equations, which have been used for years. However, modern technology nodes do not follow these models anymore, which is why innovative charge-based MOS models, such as the EKV MOS model, have led to a different approach: the  $g_{\rm m}/I_{\rm D}$  sizing methodology. Within this work the  $g_{\rm m}/I_{\rm D}$  methodology is chosen as the basis for a degradation analysis on transistors. The normalized small signal parameters, which are taken from the  $g_{\rm m}/I_{\rm D}$ method, are expanded to account for a transistor degradation, which is dependent on the operating point of the device. This phenomenon leads to the definition of a new operating tuple, which accounts for the aging behavior and still is fully compatible with the already known sizing methodology. The methods developed around the operating point-dependent degradation have been implemented into a math-assisted tool, which provides easy access to all transistor parameters within the  $g_{\rm m}/I_{\rm D}$  regime at a fresh and also at a degraded state. This GMID-Tool is also able to calculate an estimated degradation of circuit characteristics by using analytic performance expressions [55]. The results of the operating-point degradation analysis are used to estimate deviations in circuit characteristics over time, by solely relying on hand calculation approximations. Several circuit characteristics are investigated on different analog circuits. Further, a complete analysis method is developed, which is able to predict the degradation for any analytical performance expression, as it is usually provided in analog circuit design [54] [48]. The definition of the aging-aware sensitivity is directly built upon the concept of the operating point-dependent degradation.

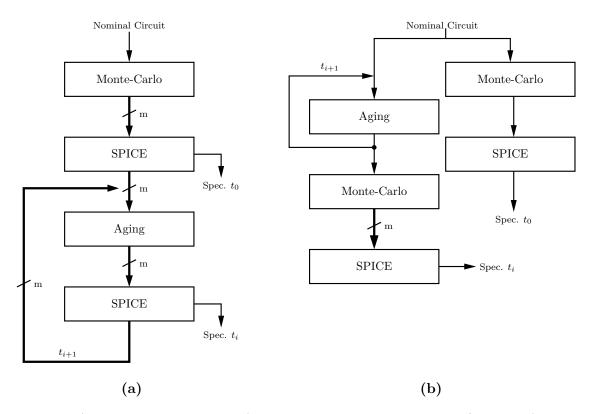

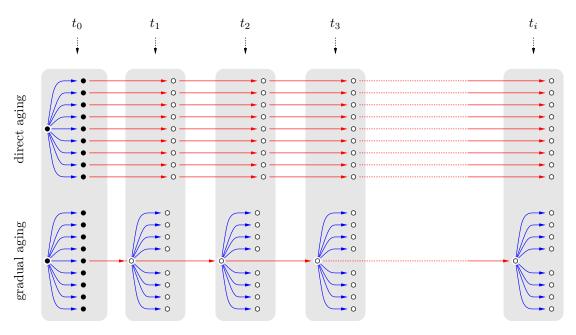

Also other aging-aware design methods for analog circuits have been explored. A topology driven design method for increasing the reliability of amplifiers has been proposed in [50]. In this study, different bias circuits and current mirror topologies are compared in regards of their response to certain degradation modes. The results are used in a folded cascode amplifier design and lead to a considerable increase in reliability. In order compute reliability figures out of a statistically generated batch of samples, an efficient simulation flow has been developed, which accounts for process variability and

4 1 Introduction

degradation mechanisms simultaneously. The variability-aware gradual aging (VAGA) approach [52] reduces the overall simulation effort compared to a standard Monte Carlo flow.

# 1.2 Structure of this Work

In chapter 2 the fundamental terms yield and reliability are introduced. Also, a nomenclature is presented, which is used throughout this work. After that, different aging mechanisms and the according modeling approaches are described, introducing hot carried degradation as well as bias temperature instability. At last, a brief overview of current aging simulation tools is given.

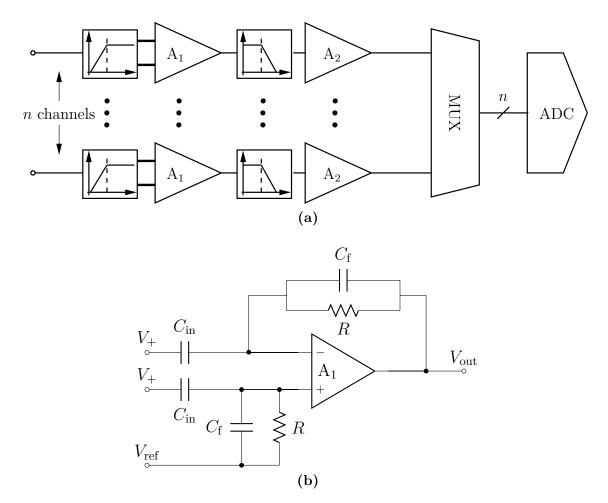

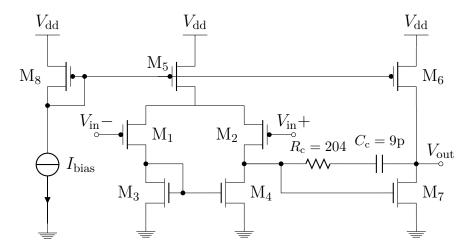

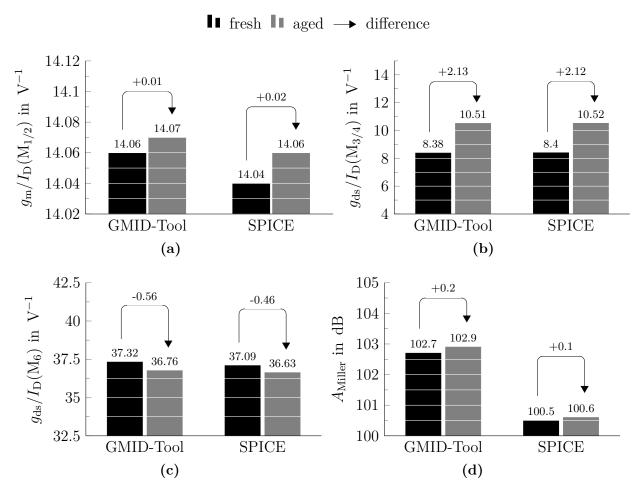

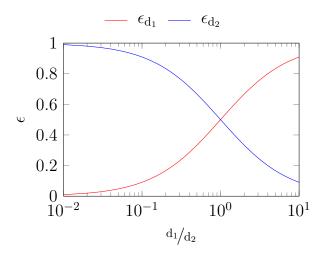

Chapter 3 begins with a study on different current mirror and bias circuit topologies. Multiple combinations are investigated in regards of their response to degradation modes. After that, an innovative variability-aware gradual aging simulation flow is presented, which generates reliability figures from a set of distributed samples. The result of the structural bias circuit and current mirror study are used to increase the aging behavior of folded cascode amplifier, as used in a neural measurement system. In chapter 4 the concept of operating point-dependent degradation and the underlying  $g_{\rm m}/I_{\rm D}$  sizing methodology is introduced. These are used to investigate aged performance characteristics of a common source amplifier. After that, the GMID-Tool is presented and used to demonstrate an aging-aware design of a Miller amplifier.

Chapter 5 presents the aging-aware sensitivity (AAS) method for analog circuit design. An analysis on a common source amplifier demonstrates the AAS method by generating so called AAS-maps. A validity analysis is shown to explore the extend of the AAS and its boundaries. At last, optimum aging-aware operating points are found through the use of the AAS method.

In the last chapter a summarized conclusion of each of the main contributions of this work is given. Also, an outlook to the development of the AAS method is presented and discussed.

# Reliability in CMOS Circuits

A system based on integrated circuits is designed to perform a specific function. The range, in which the system operates, is limited by specifications and only if these are met, the system properly fulfills its task. A designer is responsible for the design of the system and its ability to operate within these limits. These designs are based on models and assumptions, which describe the behavior of the circuit and its inherent transistors in a most ideal way. However, imperfections within the CMOS process scheme cause deviations from the model, leading to small changes in geometries or other process related metrics. The influence of these imperfections act spatially as well as temporally, some are systematic and others random, but all of them limit the functionality of the design and may even cause failures, which make a system unreliable.

The analysis of these failures on circuit or system level demands a fairly deep understanding of the underlying unreliability issues on transistor and process level. Not all of these unreliability effects apply to all levels of design, e.g. some effects need to be addressed at layout level, others at schematic level, and the impact even differs in dependence on the technology node. It is therefore important to understand the extend and applicability of each effect and how these alter characteristics of an integrated circuit design.

This chapter first introduces a terminology around the notion of reliability. After that, the most common degradation modes are compared using a spatial basis, which nicely describes the extend of each effect from atomic to die level. Each of these effects is then described in subsequent sections. A brief introduction to common reliability simulators is given. At last compact models for the most important aging mechanisms are described.

# 2.1 Fundamentals

The analysis of unreliability issues in CMOS environments is mathematically described through stochastic definitions and expressions. The formalism, which is described in this section, derives a basic understanding of the terms yield and reliability and how these relate to metrics found in the area of integrated circuits. Both terms are linked to the reliability function and failure rate, which is discussed afterwards.

## 2.1.1 Yield and Reliability

Yield and reliability are strongly connected and, as it will be shown, may be used interchangeably, within a certain extend. Whereas reliability is a function of time, the term yield is usually not connected to a transient behavior. The definition of yield is used in the semiconductor processing in order to provide a metric on how many samples of a circuit passed the post-fabrication test successfully. Optimizing the yield of a batch involves many different aspects, but the following two major sources can be regarded as the most important ones: a well defined and calibrated technology node, which provides accurate MOS models for the designer, and also circuit designs, which are able to withstand variabilities, which occur during the fabrication process. Calibration and modeling of the CMOS process is usually provided by the processing semiconductor foundry and is of no concern for the designer. In this work, the focus is given from the designer's view, leaving processing aspects aside.

In order to distinctively define the term yield, a special nomenclature is used, which will be introduced in the following. Let a specific design of a circuit be defined as  $\tau$ , which is, e.g., a schematic. A **sample** c is a specific incarnation of  $\tau$ , where process related variations are taken into account. The vector containing m samples of a topology  $\tau$  shall be defined as

$$\mathbf{c}_{\tau}^{\top} = [c_1 \ c_2 \ \cdots \ c_m]. \tag{2.1}$$

A topology consists of multiple transistors, each defined by various parameters ( $V_{\text{th}}$ ,  $g_{\text{m}}$ ,  $g_{\text{ds}}$ ,  $i_{\text{ds}}$ , etc), which are dependent on the operating point tuple  $\mathbb{T}_{\text{OP}}$ . Note that the placement of a transistor in a schematic, is bound to the topology  $\tau$ , whereas the transistor parameter are dependent on the actual process corner and therefore bound to a sample. The vector containing all **transistor parameters** of a specific transistor k is defined as

$$\mathbf{d}_{\mathbb{T}_{\mathrm{OP}}}^{k}^{\top} = [d_0 \ d_1 \ \cdots \ d_w]. \tag{2.2}$$

Each circuit holds specific characteristics such as gain or bandwidth. A **performance** value is a scalar value, which represents a specific characteristic of a sample of a circuit. Ultimately, the characteristic of each sample is given by the transistor parameters  $\mathbf{d}_{\mathbb{T}_{OP}}^k$ . The vector of n performance values is defined as

$$\mathbf{p}(c_j)^{\top} = [p_1(c_j) \ p_2(c_j) \ \cdots \ p_n(c_n)]$$

(2.3)

with

$$c_j = c_j \left( \mathbf{d}_{\mathbb{T}_{OP}}^k \right)$$

. (2.4)

2.1 Fundamentals 7

A **specification** sets limits, which a performance value needs to achieve. The set of n specification limits is defined as

$$\mathbf{s}_{\mathbf{p}}^{\top} = [s_{p1} \ s_{p2} \ \cdots \ s_{pn}]. \tag{2.5}$$

An evaluation function  $f_{s_j}(c_i)$  probes whether the j-th performance value of sample  $c_i$  fulfills its specification limit  $s_j$ . It is defined as

$$f_{s_j}(c_i) = \begin{cases} 1, & \text{if } p_j(c_i) \text{ fulfills } s_{p_j} \\ 0, & \text{else.} \end{cases}$$

(2.6)

A specific sample  $c_i$  is considered to be a **good sample**, if all performance values fulfill their specification limits, such that

$$f_{s_i}(c_i) = 1 \ \forall \ j = \{1, 2, \dots, n\}$$

(2.7)

or in equivalence, a good sample fulfills

$$\prod_{j=1}^{n} f_{s_j}(c_i) = 1. (2.8)$$

The quotient of good samples to all samples is considered to be the yield of the circuit (topology), which shall be denoted as  $Y_{\tau}$ :

$$Y_{\tau} = \frac{\sum_{i=1}^{m} \prod_{j=1}^{n} f_{s_{j}}(c_{i})}{m}.$$

(2.9)

The definition from Eq. (2.9) describes how many samples have been processed, which are unable to fulfill certain specification limits. The reason of failure is a design, which is unable to compensate for variability. Once a sample is processed and operates, time-dependent issues arise, which change the behavior of the sample over time and failures or dysfunctions will occur eventually. These in-field failures are not taken into account by the definition of yield in Eq. (2.9). Therefore, a new metric needs to be introduced.

The probability, that a given sample fulfills all its specifications for a certain operating time t is defined as reliability [36]. The definition of reliability can directly be determined from (2.9), if  $c_i$  (and therefore  $f_{s_j}(c_i)$ ) is considered to be time-dependent. Since the performance value of a sample is dependent on the transistor parameters, these need to be dependent on the operating time

$$p_i(c_j(t)) = f(\mathbf{d}_{\mathbb{T}_{OP}}^k, t). \tag{2.10}$$

From this, the reliability  $R_{\tau}$  is defined as

$$R_{\tau}(t) = \frac{\sum_{i=0}^{m} \prod_{j=0}^{n} f_{s_j}(c_i(t))}{m}.$$

(2.11)

The expressions in Eq. (2.9) and (2.11) show, that reliability may be interpreted as a time-dependent yield and correspondingly, yield as the reliability at time t = 0:

$$R_{\tau}(t) = Y_{\tau}(t) \tag{2.12}$$

$$Y_{\tau} = R_{\tau}(0) \tag{2.13}$$

As the difference for yield and reliability is its dependence on time, both are often referred to as fresh and aged yield respectively [79].

## 2.1.2 Reliability Function and Failure Rate

The definition from (2.11) links the term reliability to a time-dependent yield, which is useful for determining the fresh and aged yield of a specific design, e.g. through simulation and evaluation. In addition to this definition, there exist fundamental principles when modeling reliability. Aside from reliability, failure rate is an important indicator for time-dependent device properties.

In order link both terms, a different approach on defining reliability than the one in (2.11) has to be used. Let  $X_{\text{life}}$  be a random variable, which denotes the lifetime of a device and F(t) shall correspond to its cumulative distribution function, which returns the probability of a device not exceeding a specific operating time t,

$$F(t) = \operatorname{prob}(X_{\text{life}} \le t), \tag{2.14}$$

then the reliability R(t) may be written as

$$R(t) = \operatorname{prob}(X_{\text{life}} > t) \tag{2.15}$$

$$= 1 - F(t). (2.16)$$

The term R(t) is referred to as the reliability function and F(t) is the lifetime distribution function [75] [126]. The failure rate (or hazard function) h(t) may be interpreted as the frequency at which a device fails (e.g. once per decade). If the failure of the device is non-recoverable, then h(t) is an indicator for how fast the device approaches its end of lifetime. The definition can be derived through the use of R(t):

$$h(t) = -\frac{\dot{R}(t)}{R(t)} = \frac{f(t)}{R(t)},\tag{2.17}$$

2.1 Fundamentals 9

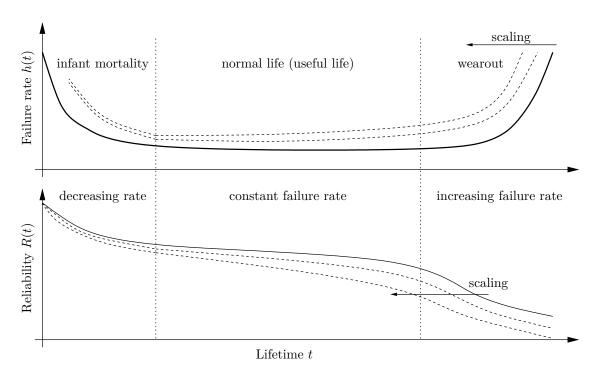

Figure 2.1: Failure rate (or hazard) function h(t) and the corresponding reliability function R(t) given for the lifetime of a device. Plot is divided into three regions: infant mortality, normal life and wearout, each with its corresponding failure rate behavior.

where f(t) is the lifetime probability density function, which is defined as

$$f(t) = \frac{\mathrm{d}F(t)}{\mathrm{d}t} = \dot{F}(t). \tag{2.18}$$

The most common type of the failure rate function is the *bathtub curve* [70] [1]. The name is given by the shape of h(t), which is depicted Fig. 2.1 (top). The corresponding reliability R(t) function is shown underneath h(t). Three distinct regions can be identified:

#### Infant mortality

Within this period the device fails due to initial defects or imperfections. The failure rate decreases until a steady state is reached. Each failing sample also decreases the reliability, consequently also R(t) decreases.

#### Useful life

This is the normal mode of operation and the failure rate is approximately constant. The region is also known as intrinsic failure period. In general the value of h(t) is very low in this period. As only a small amount of samples fails, the reliability function only decreases little.

#### Wearout

This last period is dominated by a steep increase in the failure rate. The raise in

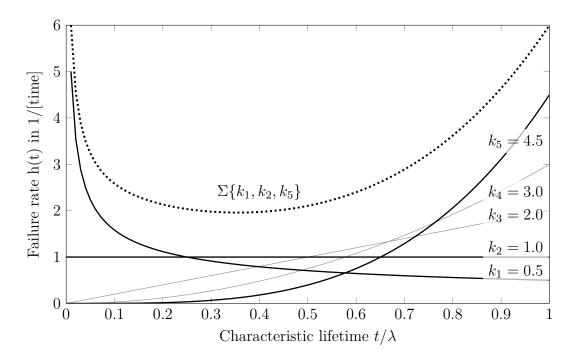

Figure 2.2: Weibull failure rate function h(t) for different shape factors k over the characteristic lifetime  $t/\lambda$ . The dotted line is the sum of three Weibull functions generated by  $k_1 = 0.5$ ,  $k_2 = 1.0$  and  $k_5 = 4.5$  and is also known as the bathtub curve. Weibull functions generated from  $k_3 = 2.0$  and  $k_4 = 3.0$  show how the shape factor influences the shape of the Weibull curve.

failure rate forces reliability to steadily decrease until the last sample failed (approaching  $R(t) \to 0$ ). The main cause of failures are time-dependent unreliability issues.

There exist different methods to model the failure rate. One of the most common models is the use of an exponential failure distribution

$$F(t) = \int_0^t \lambda e^{-\lambda \tau} d\tau = 1 - e^{-\lambda t},$$

(2.19)

which according to (2.17) and (2.16) results in a reliability and failure rate function of

$$R(t) = e^{-\lambda t} (2.20)$$

$$h(t) = \lambda. (2.21)$$

In order to describe the lifetime and reliability of electronic components, the Weibull distribution is used throughout literature. The distribution is given as

$$F(t) = 1 - \exp\left[-(\lambda t)^k\right],\tag{2.22}$$

where  $\lambda$  is the scale parameter and k is the shape parameter. The hazard function of a Weibull distribution results to

$$h(t) = \lambda k(\lambda t)^{k-1}. (2.23)$$

The bathtub curve from 2.1 can be modeled using a superposition of several Weibull failure functions [126], which is illustrated in Fig. 2.2. Here, the sum of three failure functions results in a representation of the bathtub curve, where k < 1 is used to model infant mortality,  $k \approx 1$  models the constant failure rate and k > 1 mimics the wearout. The time line can be adjusted to fit any lifetime using the scaling factor  $\lambda$ .

As seen in Fig. 2.1, scaling has a huge impact on device reliability. This phenomenon consists of several individual mechanisms. Scaling reduces the minimum channel length of transistors and therefore leads to steadily decreasing geometries. During the process of CMOS circuits, defect particles cause errors in the lithography, which highly depend on the size of the defect particle. The impact of a defect particle of a specific size increases, as scaling reduces the size of the transistors. This mainly results in an increase of infant mortality.

Secondly, wearout mechanisms also increase, as scaling not only decreases device dimensions, but also the thickness of the gate dielectric. A thin dielectric is more likely to conduct a higher leakage current, than a thick equivalently stressed one under the same voltage conditions. This increase in leakage induces effects like time-dependent dielectric breakdown (TDDB) and ultimately bias temperature instability (BTI). Due to scaling, these time-dependent wearout modes cause a device to fail earlier for each new technology node [121].

Both scaling induced mechanisms, an increase of infant mortality and the impact of wearout modes, worsen the reliability of upcoming technology nodes. As safety-critical applications cannot tolerate high failure rates, these applications are covered by established nodes. However, even if the device is fabricated using a rather large CMOS process, there still exist unreliability issues, which need to be addressed. The most common are discussed in the following.

# 2.2 Classification of Reliability Issues

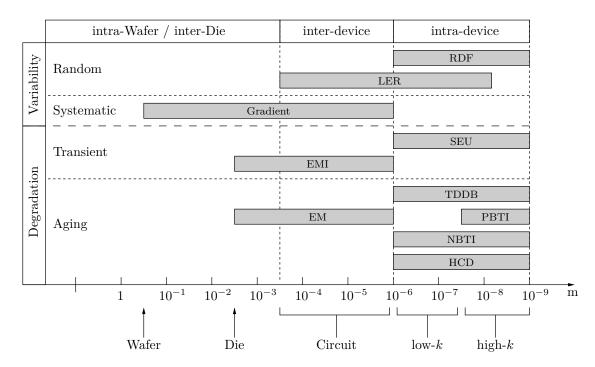

A summary of physical degradation and unreliability modes is illustrated in Fig. 2.3. In contrast to other illustrations [27] [17] [79], the modes are ordered by their spatial influence, which can be thought of as a spatial wavelength or characteristic length, ranging from the largest to the smallest. The classification in order of spatial influence is chosen in accordance to Pelgrom's mismatch law [87], which is further discussed in section 2.2.3. The largest spatial influence indicates an effect which acts on wafer level, whereas the smallest represents an influence on atomic scale. The center of action is virtually placed inside the channel of a transistor, such that effects with a spatial range

Figure 2.3: Spatial view on CMOS variability and reliability effects.

less than a channel length are considered to act inside the channel area. This scheme helps to understand which mode has to be regarded at what scale, e.g. the separation of inter- and intra-device modes. Depending on the used technology nodes, the spatial classification depicted in Fig. 2.3 may change due to different wafer or device sizes. The illustration is chosen to follow an artificial technology node with a channel length of around 1 µm and a wafer diameter of about 8 inch.

As shown in the last section, yield and reliability are strongly linked, since since  $Y_{\tau}(t)$  is just a time dependent yield, which is exactly the definition of  $R_{\tau}(t)$ . In equivalence, the terms variability and degradation are linked in the same way. Variability describes effects, which are responsible for a statistical spread of process and transistor parameters after fabrication. Degradation shall be defined as all effects, which act during the lifetime of a circuit.

Variability effects occur immediately after production and do not depend on the operating time. This mode consists of random components (e.g. random dopant fluctuations (RDF) and line edge roughness (LER)) and systematic components (e.g. process gradient effects). These effects highly depend on the actual layout geometry and are mostly due to a non-idealistic lithography. Minor differences in the projection from the mask result in small deviations of transistor and circuit characteristics and thus determines the fresh yield of a circuit. Degradation effects are time-dependent and further separated into transient modes (e.g. electromagnetic interference (EMI), single event upsets (SEU)) and aging modes (electromigration (EM), bias temperature instability (BTI), etc.). Transient modes occur once in time and lead to a sudden deviation or failure and usually do not leave a permanent change in the circuit. Aging modes are

operating-time-dependent and may result in a permanent shift of circuit characteristics. The random and systematic part is equivalent to the separation of degradation into transient and aging effects, as these either occur randomly or systematically in time. Note that the classification borders given in Fig. 2.3 are not considered to be sharp, since relative dimensions of a wafer or die change over different technology nodes. In the following sections, variability and degradation effects are described. Aging effects are discussed in a separate section, as the remaining chapters of this work highly focus on these degradation modes.

## 2.2.1 Variability

Process variability (or static reliability) becomes worse for decreasing geometries in newer technology nodes. As complexity in lithography increases, e.g. through the use of double pattering [85] or stepper motion [127], it is more and more difficult to ensure proper development of CMOS layers. Variability is usually distinguished in local (or intra-die) variations and global (or inter-die) variations. Intra-die variability causes mismatch in transistors or circuits, which originally were designed to be identical. The spatial impact only affects neighboring devices or short distanced circuits. Inter-die variability addresses effects, which act from die to die, even across a whole wafer. This occurs, if dies or wafers are processed at a different time or in a different manufacturing chain. Intra-die variation changes the mean value of process related metrics (e.g. dopant concentration or threshold voltage). Most issues in unreliability originate from local variations [7], which will be further discussed in the following.

Local variability is further differentiated into random and systematic effects. As shown in Fig. 2.3, these effects act on different spatial ranges. From a variability perspective, both may be seen as the same statistical process variable at different spatial frequencies. This idea has first been formulated in [87], but outside the context of degradation. The illustration in Fig. 2.3 expands this view by the addition of time-dependent degradation effects. In the following the most important variability sources are discussed.

# 2.2.2 Systematic Inter-device Effects

Most of these effects are more general and are described as offsets of gradients. A gradient describes the change of process parameters in dependence on the area coordinate across a wafer, which affects e.g. the oxide thickness or dopant concentration. These effects can be seen as the systematic time-independent part of each individual unreliability effect. As channel lengths decrease in modern technology nodes, these effects will become more apparent and a major limitation to circuit characteristics [2]. Systematic effects like gradients in layout are addressed by symmetric transistor positioning, e.g. a common centroid layout for transistors [46].

#### 2.2.3 Random Intra-device Effects

Random variability has a short spatial characteristics length and therefore acts on an inter-device level. Most described phenomena are random dopant effects, line edge and width roughness, trapped charges at the gate-channel interface and also variations in oxide thickness resulting from interface roughness [79] [2]. Intra-device effects add mismatch to circuit elements, which are designed to be identical and are positioned closely in the layout. As the spatial range is limited to the boundaries of the device, these effects are statistically independent from one device to another. A general formalism describing how area-dependent variability influences the mismatch of transistors is given by Pelgrom [87].

Let P(x, y) be an arbitrary process parameter, which is dependent on the die coordinates x and y, then the mismatch  $\Delta P$  of two identical parameters located at different coordinates defined by  $(x_1, y_1)$  and  $(x_2, y_2)$  is given by [87]

$$\Delta P(x_{12}, y_{12}) = \frac{1}{A} \left( \iint_{A(x_1, y_1)} \rho(x', y') \, dx \, dy - \iint_{A(x_2, y_2)} \rho(x', y') \, dx \, dy \right). \tag{2.24}$$

Using a two-dimensional Fourier transformation, it is possible to separate the geometry-dependent part and the mismatch source<sup>1</sup>:

$$\Delta \mathcal{P}(\omega_x, \omega_y) = \mathcal{G}(\omega_x, \omega_y) \mathcal{P}(\omega_x, \omega_y)$$

(2.25)

According to [87], these parts can be regarded as a mismatch source  $\mathcal{P}(\omega_x, \omega_y)$ , which generates spatial frequencies, and a geometry dependent filter function given by  $\mathcal{G}(\omega_x, \omega_y)$ . The concept of spatial frequencies is the basis for the diagram in Fig. 2.3, where each unreliability effect is treated as a mismatch source with different spatial bandwidths, ordered by the spatial wavelength.

The description in (2.25) can be used to determine the variance of  $\Delta P$ . The solution leads to Pelgrom's model:

$$\sigma^{2}(\Delta P) = \frac{A_{P}^{2}}{WL} + S_{P}^{2}D_{x}^{2} \tag{2.26}$$

where  $A_P$  is a technology dependent area proportionality constant for P and  $S_P$  is the variation of parameter P with respect to the spacing  $D_x$ , WL is the are of the device. Unreliability modes, which only act within a device, are mostly uncorrelated to the distance and therefore can be described by a first order approach [79]:

$$\sigma^2(\Delta P) \approx \frac{A_P^2}{WL} \tag{2.27}$$

<sup>&</sup>lt;sup>1</sup>The integral in (2.25) may be interpreted as the convolution of double box functions formed by the integral boundaries [87].

At device level, most variations are seen in the gate length L, the threshold voltage  $V_{\rm th}$  and the current factor  $\beta$  [129], which is modeled using (2.27)

$$\sigma(\Delta V_{\rm th}) = \frac{A_{V_{\rm th}}}{\sqrt{WL}}.$$

(2.28)

The mismatch constant  $A_{V_{\text{th}}}$  scales down with each new technology node, but is mostly limited by the accuracy of the lithography and also other factors. There exist two major effects, which need to be discussed: random dopant fluctuation and line edge (and width) roughness.

#### **Random Dopant Fluctuations**

Variation in the threshold voltage partly results from a nonuniform distribution of dopant atoms. As technology scales down, the influence and variation of the number of dopant atoms increases (because the total number of channel atoms also decreases) [74] [109]. In [74] it is shown, that random dopant fluctuations is responsible for more than 60 % of the  $V_{\rm th}$  mismatch of identically designed NMOS transistors in a 65 nm process. These results have been verified further in a 45 nm technology node. The variation on the threshold voltage based on RDF is mostly modeled by [106]

$$\sigma_{\rm rdf}(\Delta V_{\rm th}) = \Phi \cdot \frac{t_{\rm OX}}{\epsilon_{\rm OX}} \frac{\sqrt[4]{N}}{\sqrt{W_{\rm eff} L_{\rm eff}}},$$

(2.29)

where  $\Phi$  is a technology and temperature dependent constant,  $t_{\text{OX}}$  is the gate oxide thickness,  $\epsilon_{\text{OX}}$  is the oxide permittivity, N is the number of channel dopants, and  $W_{\text{eff}}$  and  $L_{\text{eff}}$  are the effective width and length of the channel respectively.

#### Line Edge and Width Roughness

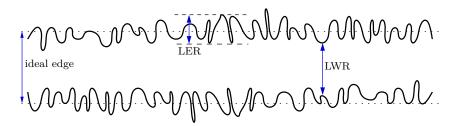

The effect of line edge roughness (LER) or line width roughness (LWR) is a result of sub-wavelength lithography, which essentially describes the fact that the wavelength, which is used in the lithography process, is larger than the developed device area. Sub-wavelength lithography is used since the 0.25 µm technology node, where a lithography wavelength of  $\lambda_{\rm lit} = 248\,\rm nm$  is used. Modern nodes below 130 nm use a light source achieving a  $\lambda_{\rm lit} = 193\,\rm nm$ , which is still used in 45 nm and below. LER describes the roughness of the edge of line, whereas LWR is the change in width of a line due to LER. Both mechanisms are depicted in Fig. 2.4.

## 2.2.4 Transient Degradation Effects

Transient effects occur after production, but do not depend on the actual operating time of the circuit but are transiently random. In general these modes are induced by

Figure 2.4: Line edge roughness and line width roughness [79].

external events, which affect the circuit at that specific time. Two major effects in this class are single event upsets (SEU) [66] and electromagnetic interference (EMI) [67]. An SEU is caused by single ionizing particles, such as ions, electrons, photons, etc. These particles enter a sensitive area in a CMOS device and change its state, e.g. flipping a bit. This change is induced through the charge, which is created by the ionization. The error seen at the device output is called an SEU or a soft error. EMI is a disturbance which is caused by emitted electromagnetic induction or electromagnetic radiation from an external source. In contrast to SEU, EMI can affect multiple devices at a time. Both SEU and EMI are not considered to permanently damage transistors and each of the effects can effect digital as well as analog circuits, but clocked gates are more prone to these modes.

## 2.2.5 Other Variability Sources

Despite the above mentioned sources of variability effects, several others have been identified in modern technology nodes, e.g. random discrete dopant (RDD) [123], metal gate granularity (MGG) [14] or layout dependence effect (LDD) [107]. No list would be able to accumulate every existing effect and the importance for each of them is highly dependent on the used technology node, circuit topology and the runtime environment.

# 2.3 Aging

In contrast to variability effects, degradation occurs after production and is a function of time. Degradation mechanisms, which depend on the operating time (despite being randomly distributed over time) are classified as aging. As seen in Fig. 2.3, there exist multiple aging mechanisms. Each of them acts with different spatial wavelength, or in other words, is active for different minimum channel lengths. In this section, each of these aging mechanism is explained by their physical origin and also how these are modeled in simulation environments.

2.3 Aging 17

## 2.3.1 Physical Origin of Aging Mechanisms

Aging or operating time-dependent degradation is perceived as a shift in a transistor parameter, where the magnitude of the shift changes over time. Degradation modes, which follow this definition are hot carrier degradation (HCD), bias temperature instability (BTI) (and its discrete variant random telegraph noise (RTN)) and time-dependent dielectric breakdown (TDDB). Each effect has different modeling approaches and varies in the impact on transistor parameters, but the physical origin is often overlapping or even identical. The most common physical degradation modes are interface state generation, electron or hole trapping and deep oxide traps, which are discussed in more detail in the following.

#### **Interface State Generation**

During the fabrication process of a MOS transistor, at some point the gate oxide is deposited over the channel area. The oxide consists of silicon dioxide (SiO<sub>2</sub>), which is often referred to as silicon oxide, and the bulk material consists of doped silicon (Si). Both of these crystalline structures differ in their geometrical configuration, e.g. different lattice constants. This leads to crystallographic defects along the interface of channel and gate. Consequently, some chemical bounds are not satisfied, which results in free carriers and also in so-called dangling bonds. Each dangling bond provides an extra energy state between the valence and conducting band, which are referred to as interface states. The number of interface states is given by  $N_{\rm it}$  and the change is given by the interface state generation  $\Delta N_{\rm it}$ .

#### Electron and Hole Trapping

If potential energy is supplied (e.g. through the gate potential  $V_{\rm G}$ ), free carriers will interact with interface states and get trapped. Depending on the type of carrier, this effect either is referred to as electron or hole trapping. The number of trapped charges in interface states is given by  $N_{\rm et}$  or  $N_{\rm ht}$ . As the channel reaches the state of inversion, even more free carriers are supplied, which fill up remaining traps. These traps accumulate a parasitic charge in the gate, which directly causes a shift in the threshold voltage. The number of production-induced interface states can be reduced, if the channel is exposed to hydrogen gas (H<sub>2</sub>) before the SiO<sub>2</sub> is grown on top. The hydrogen fills up dangling bonds and reduces the number of remaining interface states after the oxide is deposited.

#### Deep Oxide Traps

Crystallographic defects do not only occur at interfaces, but also within the material. During the epitaxial growth of the SiO<sub>2</sub> dielectric, deep oxide traps are generated. These deep traps are well beyond the reach of channel carriers and are only reached through carriers with high kinetic energy.

The following time-dependent degradation modes are all based on the above discussed physical mechanisms. Each mode differs in its excitation and also in its ability to be reversible or not.

# 2.3.2 Hot Carrier Degradation (HCD)

If a carrier is accelerated under an electric field and gains a higher kinetic energy than the lattice in thermal equilibrium, it is considered hot [21]. These hot carriers can cause a significant damage to a transistor, if injected into certain parts of the structure. Hot carriers, which are generated inside the channel of a MOS device, are referred to as channel hot carrier (CHC) [125]. Hot particles have enough energy to induce impact ionization, generation of interface states or even cause defects in the oxide structure of the insulator at the gate-channel interface. Some of these carriers are also trapped by other interface states. All of these mechanisms lead to a degradation of electrical parameters of a transistor, such as the threshold voltage  $V_{\rm th}$  or different transconductances like  $g_{\rm m}$  or  $g_{\rm ds}$ .

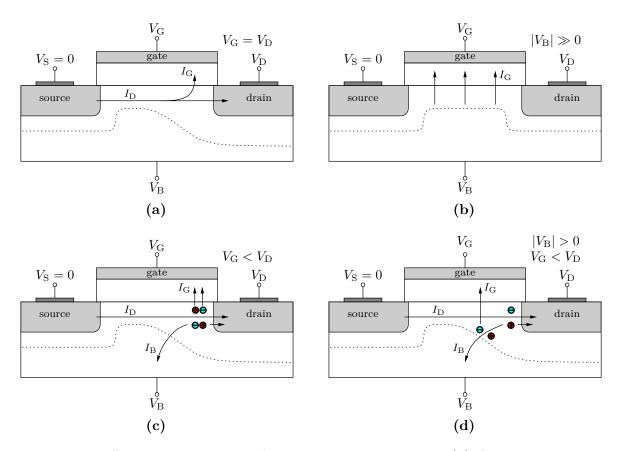

Hot carrier degradation is distinguished into four different mechanisms: channel hot electron (CHE) injection effect, drain avalanche hot carrier (DAHC) injection, secondary generated hot electron (SGHE) injection and substrate hot electron (SHE) injection [108] [29]. More recently these modes are separated into conductive and non-conductive hot carrier degradation [21], but the physical phenomenas are identical.

#### Channel Hot Electron (CHE)

The gate and drain potential  $V_{\rm G}$  and  $V_{\rm D}$  shall be equal in voltage, as depicted in Fig. 2.5a. In this state, only lucky-electrons are able to surpass the gate oxide and leave the channel, since for low voltages, no carriers are attracted to the gate and in the case of a high electric field at the drain DAHC is generated. Lucky-electrons are hot carriers, which have not been part of a particle collision inside the channel and are therefore able to continuously gain kinetic energy along the channel. These channel hot carrier result in a gate current  $I_{\rm G}$  or are eventually trapped in deep oxide traps. As holes have a larger effective mass than electrons, NMOS devices are more susceptible to CHE.

#### Substrate Hot Electron (SHE)

The exciting configuration for this mode is shown in Fig. 2.5b. If the bulk voltage  $V_{\rm B}$  is significantly positive or negative, depending on the device type, carriers in the channel gain energy and are more likely to pass the oxide barrier of the gate channel interface. This mechanism is independent of the drain and source potential and therefore uniformly distributed over the channel. This effect is mostly seen in circuits with a nonzero body bias. NMOS devices suffer from substrate hot electron injection, whereas in PMOS devices this effect is known as substrate hot hole (SHH) injection.

2.3 Aging 19

Figure 2.5: Different mechanisms of hot carrier degradation: (a) Channel hot electron (CHE). (b) Substrate Hot Electron (SHE). (c) Drain Avalanche Hot Carrier (DAHC). (d) Secondary Generated Hot Electron (SGHE).

#### Drain Avalanche Hot Carrier (DAHC)

If the transistor is operated in strong saturation, such that the drain voltage is high compared to the gate voltage, impact ionization occurs at the drain side of the channel, as shown in Fig. 2.5c. The generated electron hole pairs are now driven by the electric field inside the channel. Most carriers are attracted to the gate and cause further ionization or interface state generation. The remaining particles are accelerated along the channel according to their charge. Only few are drawn to the bulk and add to the bulk current  $I_{\rm B}$ .

#### Secondary Generated Hot Electron (SGHE)

Carriers, which have been generated from high energetic collisions, such as in the case of DAHC, are also able to cause further impact ionization events. The now generated particles are called secondary generated hot carrier. This mechanism shown in Fig. 2.5d only contributes in small amounts to the overall HCD effect.

#### Long Term Modeling

Each of the described mechanisms contributes to the overall hot carrier degradation, but each is only active at a specific state of the transistor. Recently, DAHC has been shown to be the most influencing contributor [29]. The long term shift in threshold voltage due to HCD is generally modeled using a power law [60] [72] [80] [57]

$$\Delta V_{\rm th} = A_{\rm hcd} \cdot t^n, \tag{2.30}$$

where n has a value of about 0.5 to 0.7. The generation of interface states is exponentially dependent on the oxide electric field  $E_{\rm OX}$ . The factor  $A_{\rm hcd}$  is further dependent on the maximum lateral electric field  $E_{\rm lat}$ , the temperature T and also the channel length L [60] [80] [120]:

$$A_{\rm hcd} \propto \frac{1}{\sqrt{L}} \exp\left(\alpha_1 \cdot E_{\rm OX}\right) \exp\left(\frac{\alpha_2}{E_{\rm lat}}\right)$$

(2.31)

where  $\alpha_1$  and  $\alpha_2$  are technology dependent parameters.

## 2.3.3 Bias Temperature Instability (BTI)

BTI induced degradation is usually perceived as a shift in  $V_{\rm th}$ , which is the result of high a bias voltage applied at the gate of a transistor. The impact of this effect is increased with a rise in temperature. Under normal conditions, the shift in threshold voltage can yield up to 30 mV, if a bias voltage is applied for more than 5 years (45 nm technology node [65]). BTI can also be responsible for a degradation in the carrier mobility  $\mu$  [100], however, this is negligible compared to the shift in  $V_{\rm th}$ .

There exist two types of BTI degradation: negative BTI (NBTI), which only occurs in PMOS devices and positive BTI (PBTI), which only occurs in NMOS devices. Both effects are controversially discussed in regards of the physical explanation and also the model to describe the degradation on transistor level. A general consensus has not been agreed on so far, however, several physical mechanisms have been identified to be responsible for NBTI and PBTI, which seem to be acknowledged and widely accepted by most authors. NBTI shall be the result of a combination of hole trapping  $\Delta N_{\rm ht}$  due to process related preexisting defects [6] [61] [92] and generation of interface states at the channel oxide interface  $\Delta N_{\rm it}$  [116] [71] [3] [19]. PBTI is believed to result from electron trapping in oxide traps in combination with trap generation [100] [64] [41]. Whereas NBTI is active for simple oxide gate dielectrics, PBTI only seems to be observed in high-k NMOS devices, where the impact is comparable or even worse than NBTI [42]. High-k metal gates (HKMG) NMOS and PMOS devices are used for technology nodes of 45 nm and beyond [82], which is also illustrated in Fig. 2.3 as a difference in NBTI and PBTI.

In contrast to HCD, BTI has the property to allow a relaxation or recovery of the shift in threshold voltage, if the applied gate potential is reduced. This phenomena is immediately revealed after the stress voltage is lowered [64]. Relaxation is unique to BTI and complicates modeling and extrapolation of BTI degradation. So far, it has not

2.3 Aging 21

been shown whether BTI is fully reversible or a permanent degradation remains [40], but most authors favor the idea of a permanent component [43].

#### Long term BTI model

In general BTI degradation is modeled following the approach of a recoverable and permanent component [78] [41] [79]:

$$\Delta V_{\rm th} \propto \left[\underbrace{\exp(\alpha_1 V_{\rm GS}) t^{n_{\rm P}}}_{\text{permament part}} + \underbrace{V_{\rm GS}^{\alpha_2}(C_{\rm R} + n_{\rm R} \log_{10}(t))}_{\text{recoverable part}}\right] \cdot \exp\left(-\frac{E_{\rm a}}{kT}\right), \qquad (2.32)$$

where  $\alpha_1$  and  $\alpha_2$  are technology-dependent voltage scaling parameters,  $C_R$ ,  $n_R$  and  $n_P$  are time exponents for the recoverable and permanent component respectively,  $E_a$  is the activation energy, and k is the Boltzmann constant. Note that the recoverable part in Eq. (2.32) is dependent on the duty cycle of the applied stress signal, which is modeled within  $C_R$  and  $n_R$ . BTI degradation has not shown to be dependent on frequency for measurements up to 3 GHz [97] [91].

## 2.3.4 Time Dependent Dielectric Breakdown (TDDB)

The insulator at the gate channel interface needs to separate charges accumulated in the channel and the gate plate. Each dielectric can sustain a certain maximum electric field. If the dielectric is exposed to higher fields, a dielectric breakdown occurs. This is referred to as a hard break down. At lower fields a time dependent wearout occurs, which eventually results in a time dependent dielectric breakdown (TDDB).

TDDB is a statistical process. Before the event of a breakdown a stress-induced leakage current (SILC) is observed through the gate [122] [18]. As the SILC increases, also the trap density increases until a critical limit is reach, which exhibits the breakdown. This behavior can be modeled through a Weibull probability distribution [122] [124]:

$$F(t_{\rm bd}) = 1 - \exp\left[-\left(\frac{t_{\rm bd}}{\alpha_{\rm bd}}\right)^{\beta_{\rm bd}}\right],\tag{2.33}$$

where  $F(t_{\rm bd})$  is the cumulative density function for time-to-breakdown event,  $\alpha_{\rm bd}$  and  $\beta_{\rm bd}$  are technology-dependent parameters.

## 2.3.5 Electromigration (EM)

The effect of material migration is caused by various transport processes in solids. The most common are chemical diffusion due to concentration gradients, temperature induced material migration, migration caused by mechanical stress, and material migration due to high electric fields [114]. The last one is often referred to as electromigration

and is supposed to be the most severe material process for integrated circuits. Electromigration usually occurs at grain boundaries of crystalline structures, where the crystal is inhomogeneously structured. At high currents, conducting electrons interact with atoms of the metal line structure and transport part of the line material in the direction of current flow, along the grain boundary [77]. A common measure for the degradation of a wire is the mean time to failure (MTTF), which in case of electromigration is modeled by Black's law [13]:

$$MTTF = \frac{A}{J^n} \exp\left(\frac{E_a}{kT}\right), \tag{2.34}$$

where A is a constant dependent on the cross section area of the conducting wire, J is the current density,  $E_a$  is the activation energy, k is the Boltzmann constant, T is the temperature, and n a scaling factor. Electromigration is extremely layout dependent. The relation in Eq. (2.34) gives several advices on how to reduce this degradation behavior, e.g. by lowering the temperature or allowing large cross sectional areas. Conducting wires should avoid sharp bends, as the current density is not uniform in cornered wires. Recent approaches have shown, that the effect of wide wires for avoiding EM is limited, which leads to innovative approaches in the layout, such as slotted wires [77] or even octahedron metal tracks [69].

# 2.4 Aging and Reliability Simulation

All of the above discussed effects influence the behavior of a circuit. The actual impact on circuit characteristics is computed using compact models, as it will be discussed in section 2.5. However, these models are most likely not solvable through standard solvers, such as SPICE, since the aging model equations are quite different from existing transistor compact models. Therefore, special simulators evolved within the last decades, which purely serve the need for simulating degradation effects in integrated circuits. The demand for reliability simulators has already started in the beginning of the 1990's. Many authors have proposed simulators, e.g. RELY [101], BERT [59] or HOTRON [9]. All of these simulators mainly covered HCD issues and were not commercially available. With the shrinking feature sizes of modern technology nodes and new degradation effects like BTI and TDDB, EDA manufacturers included reliability simulators into their portfolio. Three major reliability simulators have evolved, which are briefly discussed in the following sections.

## 2.4.1 Mentor Graphics ELDO

This simulator is based on the work from [86]. In contrast to most other reliability simulation schemes, this simulator is build directly into the Mentor SPICE engine called ELDO. The ELDO simulator provides information about circuit performance shifts due

to gradual transistor aging effects, specifically BTI and HCD. Sudden effects, such as TDDB are not supported. ELDO does not use predefined models, therefore the user (or the foundry) has to implement the according models using the user-defined reliability model (UDRM) interface.

In order to simulate the degradation of a circuit, at least a transient (.tran) or steady state (.sst) analysis has to be performed. The final operating time  $t_{age}$  is split into a natural number of smaller time steps  $t_i$ , which may be distributed in either linear or logarithmic form. During simulation the voltage at every node is used to compute a stress vector  $S_i$  for each transistor. The actual shift of transistor parameters, e.g.  $\Delta V_{th}$ , is computed based on  $S_i$  and extrapolated for the next simulation time step  $t_i$ . Both models, the computation of the stress vector  $S_i$  and the relation to the actual shift in transistor parameters, have to be provided within the UDRM interface. The simulation is repeated until the all time steps  $t_i$  have been simulated and the final operating time  $t_{age}$  has approached.

### 2.4.2 Synopsys MOSRA

The MOS reliability analysis (MOSRA) is included in HSPICE and CustomSim [115]. MOSRA is capable of simulating degradation caused by BTI and HCD only, but includes the possibility to account for a recovery effect in BTI. The simulation flow supports the use of user-defined models, but also offers predefined models, which can be adjusted through various reliability parameters. The use of predefined models reduces the effort for the foundry to support aging models, as only the specific reliability parameters have to be provided instead of a whole aging model.

A reliability simulation is performed within two phases. In the pre-stress phase, MOSRA calculates the electrical stress of selected transistors, which is based on the MOSRA aging models. The total stress for the operating time  $t_{\rm age}$  is computed by extrapolation of the simulation result. The resulting degraded circuit is evaluated in the post-stress phase.

## 2.4.3 Cadence RelXpert

The Cadence reliability expert (RelXpert) is included within the Virtuoso IC development suite. RelXpert supports Ultrasim and the analog design environment (ADE) and offers the simulation of BTI and HCD degradation modes by default. Other degradation modes as well as user-defined models for existing modes can be added via the user-defined reliability interface (URI). The BTI model does not support any recovery effect and is therefore comparable to implementation done in ELDO. The RelXpert simulator is basically a commercial implementation of the Berkley reliability tools (BERT) [59].

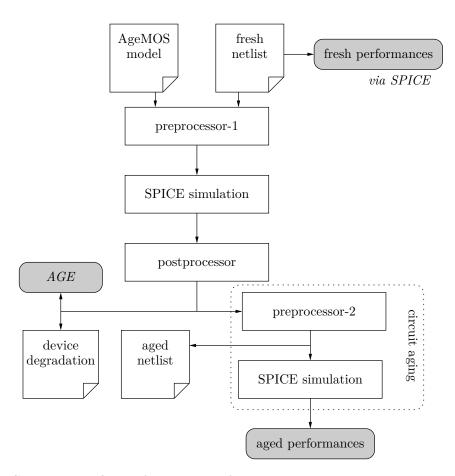

Throughout this work degradation simulation is performed using the RelXpert reliability simulator, which therefore is discussed in detail in the following sections. In section 2.4.4 the reliability simulation flow is covered, which is based on the calculation of a transistor specific AGE parameter. The calculation of this parameter is described in 2.5.3. RelXpert supports two different methods to model degradation modes for a specific technology: aged model files and the proprietary AgeMOS model.

#### Aged Model Files

Transistor model parameters (e.g. BSIM) are extracted for the fresh state and also at a number of different stress intervals. These fresh and aged model parameters form a set of aged model files. Each file represents the behavior of a transistor for a dedicated stress time, which in case of RelXpert, is expressed as certain AGE. The calculation of this term is described in section 2.5.3. During simulation, the AGE of each transistor in a circuit is calculated. The final aged model parameters are computed through regression and interpolation of the aged model files.

#### AgeMOS

In this analytical approach, each degradation effect is separately modeled. This model must be supplied by the foundry, as the model generation requires special tools, which are usually not available to the user. However, the user may also describe their own model using URI input mode. In case of a default AgeMOS simulation, the shift in transistor parameter  $\Delta P$  is described by

$$\Delta P = f(P_{\text{fresh}}, AGE, \vec{a}), \tag{2.35}$$

where  $P_{\text{fresh}}$  is the parameter at its fresh state, AGE is the transistor age as described in 2.5.3 and  $\vec{a}$  is a vector containing AgeMOS parameters. The model itself is not public and only the computation of the circuit lifetime parameter AGE is publicly available.

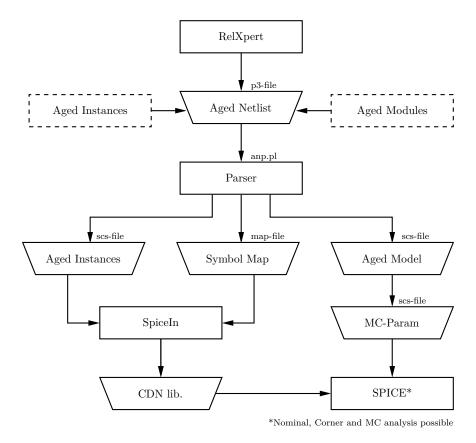

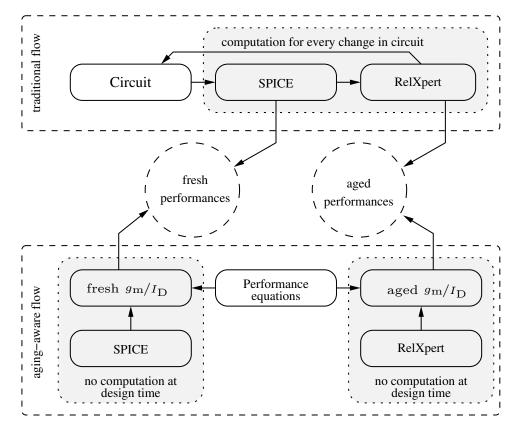

## 2.4.4 RelXpert Simulation Flow

The simulation flow of RelXpert is depicted in Fig. 2.6. In order to compute the degradation of a circuit, RelXpert needs two input data: the fresh netlist of a circuit and the degradation models, which in this case is provided through the internal AgeMOS models. A first preprocessor prepares the fresh netlist, parses the circuit and collects the information on the used degradation model. The circuit is simulated using a transient SPICE simulation. In this phase, the voltage and current signal on each node is saved and passed to post-processor This post-processor calculates the degradation (AGE) for each individual transistor and outputs a degradation table. This table is used by the second preprocessor to create an aged netlist. This aged netlist contains an individual degraded model set for each transistor. The preprocessor-2 additionally runs a final

**Figure 2.6:** Simulation flow of RelXpert for circuit degradation evaluation using the proprietary AgeMOS model [93].

SPICE simulation to simulate the degraded circuit performance after HCD and BTI stress.

## 2.5 Compact Modeling of Aging Mechanisms

In physical simulators, such as the *Technology Computer-Aided Design* (TCAD) from Synopsys [68] or the *COMSOL Multiphysics* toolbox [23], atomic simulation models can be used to identify a transistor's behavior concerning BTI, HCD or TDDB. Although the results of these simulations are accurate in terms of physical modeling, the computational efficiency is very low and also time consuming. Using these accurate models only allows a simulation time of several nano- or microseconds. The usual simulation time of interest in regards of reliability covers the whole life span of a device, which is likely to be in the range of several years. Therefore, in the case of a compact modeling approach, which is the basis for all SPICE related simulators, different model sets and simulation schemes have to used. The following described common compact modeling approaches are used in reliability simulators, specifically in RelXpert. Compact models for NBTI

and HCD are reviewed and also their implementation in RelXpert through a circuit lifetime model.

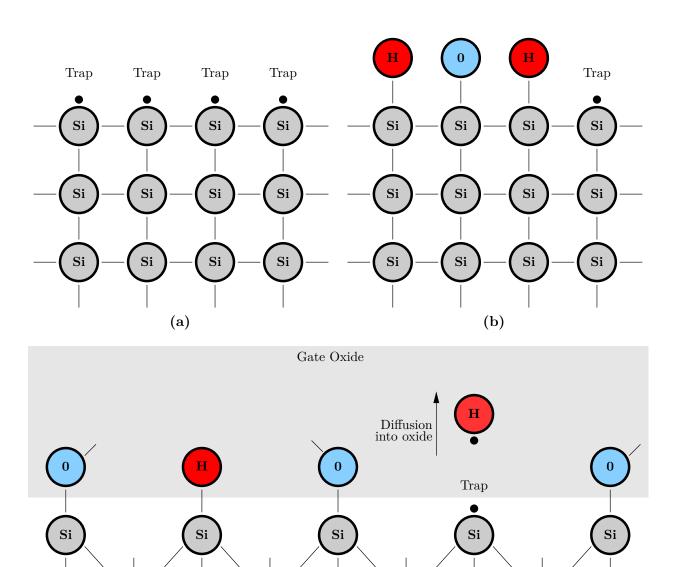

#### 2.5.1 Reaction-Diffusion Model for NBTI

The Reaction-Diffusion (RD) model describes NBTI as a thermally activated reaction of holes with Si-H bonds at the interface between substrate and gate-dielectric. A silicon bulk material is prone to unbound bonds at the surface, as it is shown in Fig. 2.7a. These traps catch free hydrogen and oxygen ions. Hydrogen is intentionally added through the CMOS production, in order to fill up open bonds. As hydrogen diffuses away from the interface, dangling bonds are generated at the interface, resulting in interface states at the substrate to dielectric barrier and also in an accumulation of positively charged hydrogen within the gate, which is shown in Fig. 2.7c. The mechanism describing the RD model has first been described in [62]. In its initial version the model was used to explain NBTI gate oxide field and temperature dependency. The model has been subsequently updated to include NBTI saturation for long stress times and also the independence on the input signal frequency [5] [4].

Within the RD model, NBTI is described as a hole-assisted breaking of Si–H (and also Si–O) bonds at the channel gate interface. This reaction is dependent on the electrical field and temperature. The rate at which traps at the interface are generated (reaction) is described by

$$\frac{dN_{it}}{dt} = k_{\rm F}(N_0 - N_{it}) - k_{\rm R}N_{\rm H}(0)N_{it}, \qquad (2.36)$$

where  $N_{\rm it}$  is the number of interface traps, which in this case are caused by broken Si–H bonds,  $N_0$  is the number of initially existing Si–H bonds,  $k_{\rm F}$  represents the oxide-field dependent forward dissociation constant,  $k_{\rm R}$  is the annealing rate constant and  $N_{\rm H}(0)$  is the concentration of hydrogen at the interface for x=0. The first term in Eq. (2.36) shows that the rate of  $N_{\rm it}$  is dependent on the number of broken bonds (at rate  $k_{\rm F}$ ), whereas the second terms describes the annealing of broken bonds with already released hydrogen atoms (at rate  $k_{\rm R}$ ). Released hydrogen atoms may not only anneal to broken bonds, but also diffuse into the gate dielectric (diffusion), which is described by

$$\frac{\mathrm{d}N_{\mathrm{H}}}{\mathrm{d}t} = D_{\mathrm{H}} \frac{\mathrm{d}^2 N_{\mathrm{H}}}{\mathrm{d}x^2},\tag{2.37}$$

where  $N_{\rm H}$  is the total hydrogen concentration in the oxide and  $D_{\rm H}$  is the diffusion constant. A closed form solution is obtained using the following assumptions:

1. The initial trap generation rate is small:

$$\frac{\mathrm{d}N_{\mathrm{it}}}{\mathrm{d}t} \approx 0. \tag{2.38}$$

Si

Figure 2.7: Silicon surface and dangling bonds. (a) Simple silicon structure as bulk material The surface atoms have unsatisfied bonds, which form traps. (b) Traps catch other carriers, such as hydrogen (H) or oxygen (O). (c) Silicon 111 structure at the bulk oxide interface. Difference in lattice geometry leaves spots, which are filled with H during process. Diffusion of H into oxide is part of BTI.

(c)

$\mathbf{Si}$

2. Initially, the number of generated traps  $N_{\rm it}$  is small compared to the number of available bonds to brake  $N_0$ :

$$N_{\rm it} \ll N_0 \approx 5 \cdot 10^{12} \,\rm cm^{-2}.$$

(2.39)

Therefore, Eq. (2.36) may be written as

$$N_{\rm H}(0)N_{\rm it} \approx \frac{k_{\rm F}}{k_{\rm R}}N_0.$$

(2.40)

After the initial startup, mainly the diffusion of hydrogen contributes to the trap generation process. The depth of diffusion (the distance from the channel interface into the gate, which has been covered by H atoms) is given by

$$X_{\rm DF}(t) = \sqrt{D_{\rm H} \cdot t}. \tag{2.41}$$

Since the number of diffusing H atoms increases with time, also the diffusion depth  $X_{\rm DF}$  is dependent on time. Additionally, the number of hydrogen atoms within the diffusion zone encountered between  $0 < x < X_{\rm DF}$  is equal to the number of generated interface traps  $N_{\rm it}$ , such that

$$N_{\rm it} = \int_0^{\sqrt{D_{\rm H} \cdot t}} N_{\rm H}(x, t) \, \mathrm{d}x = \frac{1}{2} N_{\rm H}(0) \sqrt{D_{\rm H} \cdot t}. \tag{2.42}$$

The solution from Eq. (2.42) is inserted into Eq. (2.36) and finally yields

$$N_{\rm it} = \left(\frac{k_{\rm F}}{k_{\rm R}} \frac{N_0}{2}\right)^{1/2} (D_{\rm H} \cdot t)^{1/4}. \tag{2.43}$$

The expression in Eq. (2.43) yields the number of generated interface traps  $N_{\rm it}$  for a given stress time t. Every diffused hydrogen causes a shift in threshold voltage, which in sum is equal to voltage on the oxide capacitance  $C_{\rm OX}$  induced by the total charge of the hydrogen:

$$\Delta V_{\rm th} = \frac{qN_{\rm it}}{C_{\rm OX}}. (2.44)$$