### Universität Bremen Fachbereich 3: Mathematik und Informatik Arbeitsgruppe Betriebssysteme und Verteilte Systeme Leiter: Prof. Dr. Jan Peleska

# Model-Based Scenario Testing and Model Checking with Applications in the Railway Domain

#### Dissertation

zur Erlangung des Doktorgrades Doktor der Ingenieurwissenschaften — Dr.-Ing. —

Helge Löding Bremen im September 2014

1. GUTACHTER: PROF. DR. JAN PELESKA

2. Gutachter: Prof. Dr.-Ing. Görschwin Fey

Datum des Promotionskolloquiums: 5. Februar 2015

### Abstract

This thesis introduces Timed Moore Automata, a specification formalism, which extends the classical Moore Automata by adding the concept of abstract timers without concrete delay time values, which can be started and reset, and which can change their state from running to elapsed. The formalism is used in real-world railway domain applications, and algorithms for the automated test data generation and explicit model checking of Timed Moore Automata models are presented.

In addition, this thesis deals with test data generation for larger scale test models using standardized modeling formalisms such as UML. An existing framework for the automated test data generation is presented, and its underlying work-flow is extended and modified in order to allow user interaction and guidance within the generation process. As opposed to specifying generation constraints for entire test scenarios, the modified work flow then allows for an iterative approach to elaborating and formalizing test generation goals.

# Acknowledgment

I would like to thank my supervisor Jan Peleska for his guidance as well as for his patience. His unique brand of directing overall content, of giving creative leeway and of petitioning me for palpable results has ensured, that this thesis would eventually come to be. As it stands, this thesis is the latest milestone in my professional career, which Jan Peleska has influenced as teacher, mentor and employer in its entirety.

Within this same vein, I owe thanks to the GESy graduate college for embedded systems, the Siemens railway automation graduate school and its respective members for constructive and insightful discussions during their combined workshops.

I would also like to thank the Siemens AG for their financial support. Their doctoral candidate scholarship has started me and this thesis on the right foot.

At Verified Systems Intl. GmbH, my work assignments and my colleagues in particular have helped me to gain valuable experience in the testing of real-world applications, software engineering best-practices and software quality in general.

Huge gratitude is owed to my family and friends, who have supported me throughout.

# Contents

| 1 Introduction |     |         |                                  | 4  |

|----------------|-----|---------|----------------------------------|----|

|                | 1.1 | Overv   | iew                              | 4  |

|                | 1.2 | Motiva  | ation                            | 5  |

|                | 1.3 | Main (  | Contribution                     | 8  |

|                | 1.4 | Relate  | ed Work                          | 9  |

|                |     | 1.4.1   | Model-Based Testing              | 9  |

|                |     | 1.4.2   | Model Checking                   | 11 |

|                |     | 1.4.3   | Constraint Solving               | 12 |

|                |     | 1.4.4   | Other Test Generation Techniques | 13 |

| 2              | Tim | ed Mo   | pore Automata                    | 14 |

|                | 2.1 | Classic | cal Moore Automata               | 14 |

|                |     | 2.1.1   | Abstract Syntax                  | 15 |

|                |     | 2.1.2   | Concrete Syntax                  | 16 |

|                |     | 2.1.3   | Static Semantics                 | 18 |

|                |     | 2.1.4   | Operational Semantics            | 18 |

|                |     | 2.1.5   | Determinism                      | 21 |

|                | 2.2 | Abstra  | act Timing for Moore Automata    | 23 |

|                                   |          | 2.2.1   | Informal Introduction to Timed Moore Automata | 23         |

|-----------------------------------|----------|---------|-----------------------------------------------|------------|

|                                   |          | 2.2.2   | Abstract Syntax Extensions                    | 26         |

|                                   |          | 2.2.3   | Concrete Syntax Extensions                    | 27         |

|                                   |          | 2.2.4   | Static Semantics Extensions                   | 29         |

|                                   |          | 2.2.5   | Operational Semantics Extensions              | 30         |

|                                   |          | 2.2.6   | Determinism                                   | 38         |

|                                   | 2.3      | Model   | Checking for Timed Moore Automata             | 38         |

|                                   |          | 2.3.1   | Construction of Kripke structures             | 38         |

|                                   |          | 2.3.2   | Computation Tree Logic                        | 47         |

|                                   |          | 2.3.3   | Model Checking CTL Properties                 | 50         |

|                                   |          | 2.3.4   | Checking for Live-Locks                       | 56         |

|                                   | 2.4      | Test I  | Data Generation for Timed Moore Automata      | 58         |

|                                   |          | 2.4.1   | Test Data Generation for Single Traces        | 58         |

|                                   |          | 2.4.2   | Trace Selection                               | 65         |

|                                   | 2.5      | Bench   | marks                                         | 68         |

|                                   | <b>.</b> | , •     |                                               | =0         |

| 3                                 | Inte     | eractiv | e Model-Based Testing                         | <b>7</b> 0 |

| 3.1 Model-Based Testing Framework |          |         | -Based Testing Framework                      | 70         |

|                                   |          | 3.1.1   | Intermediate Model Representation             | 71         |

|                                   |          | 3.1.2   | Operational Semantics                         | 72         |

|                                   |          | 3.1.3   | Generation Goals                              | 73         |

|                                   |          | 3.1.4   | Bounded Model Checking                        | 75         |

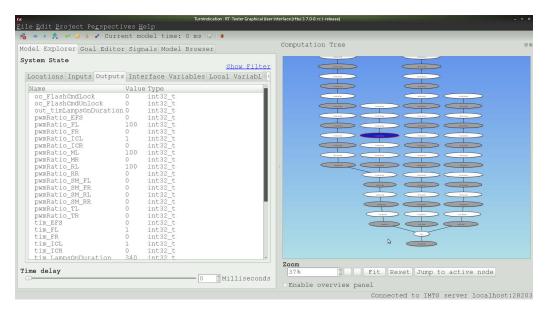

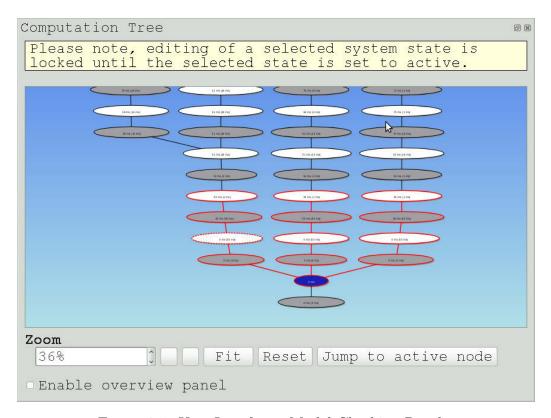

|                                   |          | 3.1.5   | Computation Tree                              | 76         |

|                                   |          | 3.1.6   | Concrete Interpreter                          | 77         |

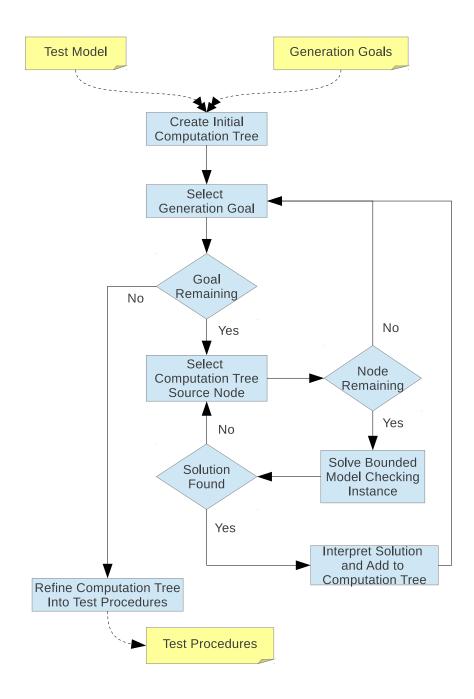

|                           |              | 3.1.7  | Generation Control Flow                             | . 77  |

|---------------------------|--------------|--------|-----------------------------------------------------|-------|

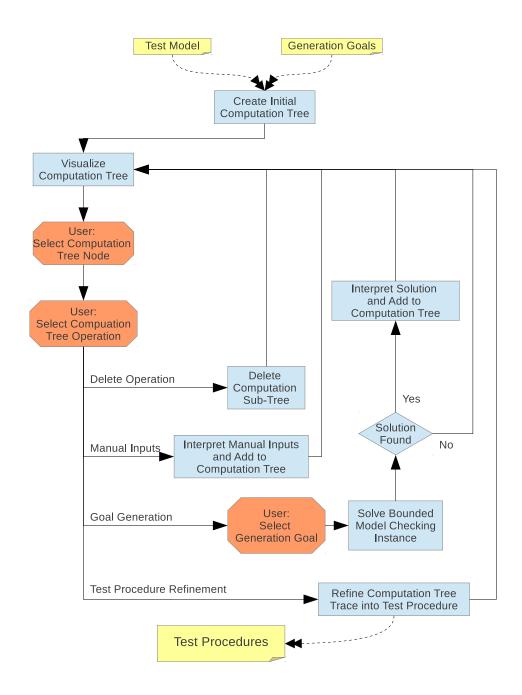

|                           | 3.2          | Intera | ctive Generation Paradigm                           | . 79  |

|                           |              | 3.2.1  | Critique of the Fully Automated Paradigm            | . 80  |

|                           |              | 3.2.2  | Modifications to the Generation Control Flow        | . 81  |

|                           |              | 3.2.3  | Model Checking for Computation Trees                | . 83  |

|                           |              | 3.2.4  | Manual Computation Tree Extension                   | . 84  |

|                           |              | 3.2.5  | Generation Goal driven Computation Tree Extension . | . 85  |

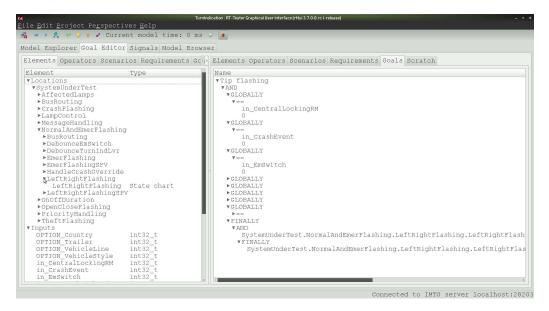

|                           | 3.3          | User I | nterface                                            | . 85  |

|                           |              | 3.3.1  | Goal Editor                                         | . 86  |

|                           |              | 3.3.2  | Model Explorer                                      | . 88  |

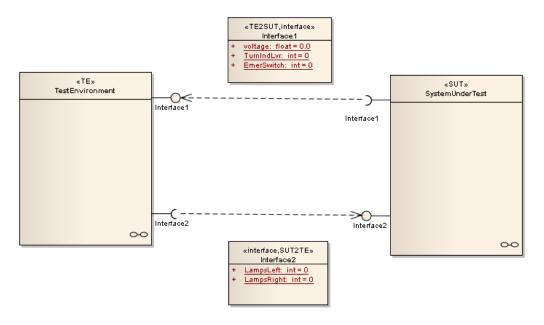

|                           | 3.4          | Case S | Study - Turn Indication                             | . 91  |

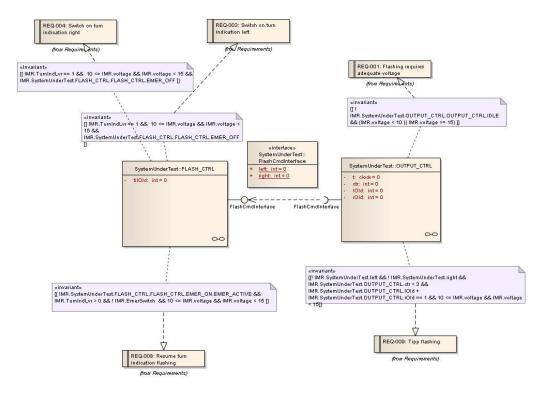

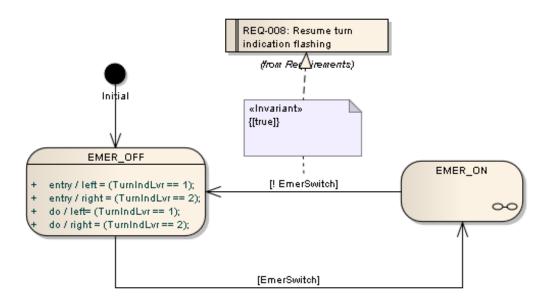

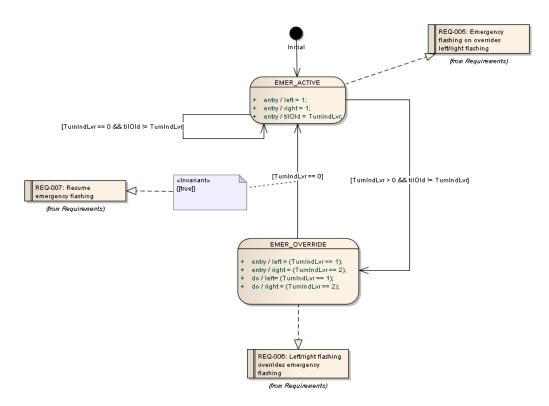

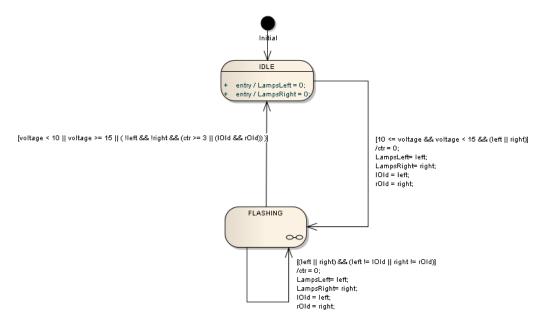

|                           |              | 3.4.1  | Test Model                                          | . 91  |

|                           |              | 3.4.2  | Example Scenarios                                   | . 96  |

|                           | 3.5          | Evalua | ation                                               | 103   |

| 4                         | Con          | clusio | n                                                   | 106   |

|                           | 4.1          |        | l Moore Automata                                    | . 106 |

|                           | 4.2          |        | ctive Model-Based Testing                           |       |

|                           |              |        |                                                     |       |

| Li                        | st of        | Figure | es                                                  | 111   |

| Li                        | st of        | Table  | 5                                                   | 112   |

| $\mathbf{B}_{\mathbf{i}}$ | Bibliography |        |                                                     |       |

# Chapter 1

# Introduction

This thesis elaborates and discusses different aspects and real-world challenges of model-based software testing on different scales and test integration levels. A domain-specific specification formalism used in the railway domain is introduced and defined. Algorithms for test data generation and explicit model checking are presented.

Additionally, an existing framework for fully automated model-based test data generation is introduced and analyzed. Thereupon the framework is extended to accommodate a more interactive approach to scenario testing.

#### 1.1 Overview

This chapter introduces the scope and context of the thesis. Specifically, section 1.2 explains the motivation for this work. In section 1.3, the main contribution of this thesis is discussed. Section 1.4 gives an overview over related research being done by others.

Chapter 2 introduces a real-world domain-specific formalism used for modeling safety-critical control systems in the railway domain. Algorithms used for test data generation and model checking of specifications using this formalism are presented.

Chapter 3 initially introduces a framework used for the automated generation of test data on the basis of test models specified using standardized specification formalisms. The framework is then extended to allow interactive

user-guidance of the generation process.

Finally, chapter 4 summarizes results and gives an outlook over possible future research topics and tool expansions.

#### 1.2 Motivation

Safety-critical systems are systems, which – upon failure –may cause human injury or death, loss of or catastrophic damage to equipment, or severe harm to the environment. As such, they are usually subject to rigid norms and regulations regarding their development and deployment.

Norms such as the RTCA DO-178C ([oR11]) for the aviation domain and the CENELEC EN-50128 ([Cen11]) for the railway domain prescribe software development processes, which are specifically tailored to ensure high software quality. While software quality attributes like functionality, availability, reliability, maintainability and efficiency certainly benefit from a well-defined development process, safety will usually be the main characteristic under consideration during the certification phase of a system for real-world deployment.

Within the domain of regulated safety-critical systems, all utilized software development processes, may they be of the waterfall-, V-, W- or iteration-based categories, will mandate some verification and validation activities for their development artifacts. Within this context, validation ensures, that each refinement step of a given development artifact into a more concrete form is a valid specialization. For example, given a system architecture document, all sub-system architecture documents must adhere to the overall architecture set forth in the source system architecture document. As such, validation is meant to ensure, that we are building the *right system*.

Conversely, verification is the process of showing, that we are building the system right. This entails providing sufficient proof to show, that the system under development is a correct implementation conforming to all specifications identified in all validated system specification documents.

Typically, each refinement of a system design into a more concrete specification will give rise to validation activities to ensure conformance of the specialization to the source abstraction. Additionally, each layer of abstraction will usually give rise to verification activities to ensure conformance between specification and implementation. System-, sub-system and module implementations will have to be evaluated against their respective system-, sub-system and module-specifications.

Verification methodology can roughly be split into static analysis and dynamic testing techniques, which evaluate system source code and system instances being executed respectively. While static approaches generally attempt to construct mathematical proofs of relevant properties on the basis of source code (or the respective development process artifacts of the abstraction layer under consideration), dynamic testing (which will simply be called testing from here on) will systematically stimulate a running instance of a system under test and evaluate the observed system responses against expected (specified) behavior.

It is not surprising, that the precision of all development, verification and validation activities heavily depend on the level of formalization of referenced or evaluated documents. However, a high level of formalization may be detrimental to maintainability, especially when using specification formalisms, which themselves lack readability. As a resulting trade-off, graphical specification formalisms with an underlying formal semantics have become the de-facto standard for specification purposes, and a range of computer-aided software engineering (CASE) tools, which support various graphical specification formalisms for modeling architecture and behavior on all system abstraction levels, exist.

The usefulness of formal models in the context of system verification is manifold. Within static analysis, models may be used as inputs for theorem provers, model checkers or other static analysis tools. For testing purposes, test models can typically serve two separate functions: They can be used to systematically generate stimulations to be applied to the system under test, and they can be used to assess the correctness of the observable system under test reactions to those stimulations.

Note, however, that care needs to be taken when selecting reference system models. Whenever, for example, the same model is used as a basis for generating source code and generating tests for that source code, the redundancy between system under test and tests for that system is lost. In such a scenario, not the system under test, but only the source code and test generation process is being evaluated.

Another trade-off to be considered is between standardized modeling formalisms and domain- or even application specific (graphical) languages. On the one hand, standardized formalisms such as the OMG UML ([OMG11a], [OMG11b]) provide common specification grounds for developers as well as verification and validation specialists, and a wide array of tools are available.

On the other hand, since standardized formalisms need to be broad and feature-rich enough for a multitude of applications and domains, their formal semantics are - if even available - usually very complex and difficult to deal with for model checkers and test data generators. In contrast, domain-specific languages allow practitioners to tailor specification formalisms specifically to their needs. As a result, the corresponding formal semantics will contain only the complexity needed by its application.

Note, that efforts such as UML2 Profiles are made to bridge this gap by providing facilities to restrict, customize and constrain features of generic specification formalisms. However, just as with domain-specific languages, practitioners still need to annotate profiles with formal semantics suitable for their application domain. As such, profiles are in large parts simply a more standardized way to create domain-specific languages.

This thesis elaborates two separate and very different model-based verification approaches, one dealing with a domain-specific specification formalism used in the railway domain, the other dealing with extensions made to a model-based testing framework used in conjunction with standardized specification formalisms.

Within the first part of the thesis, railway level crossing system component specifications using a domain-specific graphical notation and the corresponding system component implementations are given. Since all components are implemented separately, the graphical system component specifications can serve as test models.

It is assumed, that conformance of the specifications to functional requirements have already been validated in earlier phases. As such, the verification task at hand is to ensure conformance of the implementations to their respective specifications. The system components are considered to be white boxes, and structural coverage criteria are used to determine test end conditions.

Additionally, the domain-specific specification formalism used here lends itself to performing explicit model checking. The corresponding algorithms are elaborated and used to ensure some basic liveness properties.

In contrast, the second part of this thesis is concerned with test data generation for test models using standardized specification formalisms. Here, the

scope lies on a higher test integration level. Entire (sub-)systems are considered in a black-box testing context. The focus lies on how larger test models may be utilized to generate test data for scenarios reflecting functional requirements.

#### 1.3 Main Contribution

Within the first part of this thesis, a new graphical specification formalism used for modeling embedded controllers in the railway domain is introduced and elaborated. While this specification formalism called Timed Moore Automata has already been heavily used to specify expected behavior of real-world applications, verification of systems built from Timed Moore Automata specifications has previously been based on manually deriving test cases for the resulting source code. The thesis presents approaches and algorithms for performing model-checking and test data generation directly from test models specified using Timed Moore Automata.

Moreover, the presented specification formalism may be of general scientific interest. Timed Moore Automata introduce the concept of abstract timers. Abstract timers are not associated with concrete time durations, after which they must elapse. Rather, they provide the abstract notions of timer statuses timer running and timer elapsed as well as timer actions timer start and timer stop and the general semantic rules, under which timer actions and timer statuses may influence each other. As such, Timed Moore Automata may be useful as a further abstraction level between entirely timeless specification formalisms such as classical Moore Automata ([Moo56]) and timed formalisms based on concrete timer durations, such as the region graphs derived from Timed Automata ([AD94]).

In order to facilitate model-based scenario testing, the second part of this thesis builds upon an existing framework used for model-based test generation from larger scale test models. The framework can accommodate multiple standardized modeling formalisms, and for any test model, the test data generation process follows a generic and completely automated work-flow. The thesis discusses some weaknesses inherent in this paradigm and introduces a new interactive generation work-flow, which allows the user to visualize and influence each step of the generation process.

As such, the interactive test generation paradigm realized in this thesis may

serve as an exemplary prototype, which allows a user to inject application expertise into the model-based test generation process while still harvesting the power of fully automated test generation approaches. As a result, automated model-based test generation approaches can become valuable tools for developing test cases as well as test data intended for scenario testing.

#### 1.4 Related Work

Within this section, research related to the topics of this thesis being done by other researchers and groups is presented.

The following subsections list a number publications, which give overviews of different scope and detailing over the field of model-based testing. The most common tools and frameworks – including the framework used within this thesis – are enumerated and briefly summarized.

Furthermore, publications introducing the fundamental concepts of model checking and the model checking tools considered to be state of the art are given. Papers on various approaches regarding the interaction and interdependence between model checking and model-based testing are layed out additionally.

In a later subsection, the research landscape concerning constraint solving algorithms and corresponding solver implementations is sketched. Notably, this includes the constraint solver used at the heart of the model-based test generation framework used in the thesis.

Finally, notable papers from other sub-domains of model-based testing not immediately related to this thesis and the used model-based testing approach are briefly enumerated.

## 1.4.1 Model-Based Testing

As a position paper on model-based testing, [Utt08] gives a comprehensive summary over the field of model-based testing.

[Tre11] expands on this and gives a more formal overview for model-based testing in general, and for testing labeled transition systems in particular.

Another introduction into model-based testing with emphasis on the processes and characteristics of different approaches to model-based testing can be found in [UPL12].

In [Bel10], the author introduces JTorX, a testing tool for model-based test generation and execution. The tool compares a given labeled transition system specification to an implementation using the "ioco" implementation relation. The corresponding testing theory is set forth in [Tre08].

The MOTES tool [EKRV06] generates test date for extended finite state machines using the model checker UPPAAL Cora ([BLR05]) and various structural coverage criteria.

[DBI12] proposes another extension of finite state machine called "Stream X-machine" (SXM), where state machines can be annotated with data structures and functions to operate on that data. [DBI12] presents a testing theory and a corresponding testing tool JSXM for testing Stream X-machines.

The MaTeLo tool [DZ03] derives test cases in the TTCN-3 notation ([Din04]) from Markov chain usage models (MCUM) [Pro05] to perform model-based statistical testing. While MaTeLo automatically derives its MCUMs from different formal model descriptions, the JUMBL tool [Pro03] can be used to directly model MCUMs and generate test cases from it.

UPPAAL Cover/TRON [HLM<sup>+</sup>08] utilizes test models formulated as timed automata ([AD94]) and coverage criteria formulated in an observer language to generate test cases in the form of timed input sequences.

Using the UML2 Testing Profile ([BJ07]), the TTmodeler tool [PSK08] generates test cases in the TTCN-3 notation. Generation goals are modeled directly into the test model.

The Conformiq Qtronic tool [Hui07] accepts UML test models and yields TTCN-3 test cases as well. Additionally, Qtronic introduces the proprietary Qtronic Modeling Language (QML).

The Smartesting CertifyIt tool [BGLP08] is yet another test generator based upon UML. It allows usage of OCL constraints ([Obj10]) within the test model to guide the generation process.

The RT-Tester Model-Based Testing Extension [Pel13] utilizes an (internal) intermediate modeling language to incorporate multiple test model specification formalisms and their respective front-ends. Using the semantics of

Harel's state charts ([HN96]), test data can be generated for multiple test notations using corresponding back-ends. As a major prerequisite of this thesis, it is described in more detail in section 3.1.

Case studies for testing embedded systems using the above framework are given in [EP11] and [PHL+11] for the avionics and automotive domain respectively. The usage of the framework as part of model-driven software verification of synchronous components is published in [MGP+12].

Handling of aliasing problems within automated test generation based on control flow graphs is introduced in [LP08], and the further combination of these code-based test generation algorithms with static analysis methods is presented in [PLK07].

A model-based equivalence class testing strategy for test models using SysML semantics ([Hau06]) is presented in [HP13].

Transformations based on case grammar theory ([Coo89]) of controlled natural language requirements initially into an intermediate test model, and eventually into executable test cases is shown in [CBL<sup>+</sup>14].

A multitude of considerations and aspects of combining model-based testing with scenario testing, and of interactively injecting domain expertise into automated test generation processes can be found in [RK11], [AQ13], [DKT08], [DCT12], [CDJ11], [MLL09], [LK01], [CDKM11], [BW05], [GKP00] and [MFT12]. The evaluation section 3.5 of chapter 3 on interactive model-based testing summarizes these publications in more detail.

## 1.4.2 Model Checking

Foundations of model checking are comprehensively presented in [CGP99]. It introduces Kripke structures as basic data structures, temporal logics to express properties to be checked as well as the algorithms used.

Notable model checking tools are SPIN ([Hol03]), SMV and NuSMV ([CCGR00]), UPPAAL ([BDL+06]) and the Java Pathfinder ([HP00]).

An adaption of Tarjan's algorithm [Tar71] for the computation of strongly connected components - an algorithm at the heart of model checking - is used in [JM99] to perform test data generation.

Automatic test case generation for state charts using the CTL temporal

logic to formalize coverage criteria and the SMV model checker to construct reachability (counter-)witnesses is described in [HLSC01].

[CSE96] describes the use of counter-witness extracted from model checking to generate test cases for requirements specified in the LTL temporal logic.

As opposed to finding witnesses for reachability properties and transforming these into test cases, [ABM98] performs model mutations and uses model checking to construct witnesses, which distinguish the mutation from the original model.

[AB00] assess utilizing model checking for test generation using the MC/DC ([CM94]) coverage criterion. Additionally, they argue for the use of model checking for test set recognition.

In [AADO00], the authors elaborate, how model checking might be used to achieve specification-mutation coverage, full predicate coverage and transition-pair coverage.

In [FW08], a notion of property relevance of test cases is introduced in order to evaluate test suites against their ability to detect requirements violations.

In [Eng05], the authors evaluate trade-offs between model checking and static analysis when finding errors, particularly in file system code.

## 1.4.3 Constraint Solving

In constraint solving, the values of a set of variables are restricted using a set of constraints (equality, inequality, affiliation with a certain value domain, etc.). [RBW06] gives an overview over the field of constraint programming.

Integer programming and solving approaches such as the well-known simplex algorithm to solve problem instances initially known from operations research are presented in [Rav07].

Boolean satisfiability (SAT) solvers "have become the key enabling technology in automated verification" ([BHvMW09]). Biere et al. present a collection of papers on the theoretical and practical impact of SAT solving specifically on (bounded) model checking and program verification. In [DEFT09], this is expanded on to show, how SAT solvers can be utilized for automatic test pattern generation for hardware circuit verification.

Combining multiple solvers capable of handling different theories (e.g. integer programming, arithmetic, bit-vectors, etc.) with a SAT solver used to coordinate the (sub-)theory-solvers yields Satisfiability-Modulo-Theory (SMT) solvers, which are capable of solving sets of mixed constraints. [BSST09] takes a look at how to construct such SMT solvers.

The Satisfiability Modulo Theory Library (SMT-LIB) [BRST08] maintains a list of state-of the art SMT solvers and their references. These currently include: Alt-Ergo, Boolector, CVC4, MathSAT 5, MiniSmt, Mistral, SMT-Interpol, SONOLAR, UCLID, veriT, Yices 2, Z3.

The SONOLAR solver ([PVL11]) in particular is used as an integral part of the model-based testing framework [Pel13] expanded on within this thesis.

In addition to [Pel13], [AS05], [CIvdPS05] and [GMS98] all utilize constraint solving for model bases test generation, albeit with different intentions.

#### 1.4.4 Other Test Generation Techniques

Search-based test generation utilizes meta-heuristic search approaches such as genetic algorithms, simulated annealing or other probabilistic algorithms to solve the test generation problem. A selection of such approaches can be found in [ATF09], [HHL+07], [LHM08], [MS04] or [McM04].

In random testing, large numbers of test cases are created with little effort and little regard for the quality of single test cases. Rather, the sheer amount of test cases and their statistical distribution is assumed to detect a majority of faults. Among other considerations, [Pre06], ,[ODC06], [CLOM06] and [CLOM07] discuss the efficiency of random testing with regard to strength of resulting test suites and their cost-effectiveness.

Evolutionary testing – possibly as an extension of random testing – refines given test input data using mutations and fitness functions. Several approaches to evolutionary test generation can be found in [KG04], [HM07], [WS07], [Weg03], [WL05] or [WB04].

# Chapter 2

# Timed Moore Automata

This chapter introduces Timed Moore Automata, a real-world formalism used for modeling safety-critical control systems in the railway domain. In order to provide software verification and validation tool support for control systems modeled as Timed Moore Automata, algorithms for the automated generation of test data and the validation of required application properties were developed. While some results are already known from [LP10], this thesis greatly expands on and illuminates the material presented there.

Section 2.1 reviews the classical Moore Automata as introduced in [Moo56] with a special focus on applying the formalism to the specification of control systems. Section 2.2 extends classical Moore Automata to introduce Timed Moore Automata, a formalism, which introduces the notion of timers to Moore Automata.

In section 2.3 we describe a model checking approach used in checking instances of Timed Moore Automata specifically for live-locks. Section 2.4 introduces specialized algorithms used to generate test data for Timed Moore Automata. Section 2.5 presents achieved results for a real-world railway application.

#### 2.1 Classical Moore Automata

This section re-introduces the classical Moore Automata as invented in [Moo56]. While they are usually considered to be a computation model for recogniz-

ing regular expression languages, they can be viewed as a simple modeling formalism for specifying control systems.

Moore automata are simple finite-state machines (deterministic or not). Their defining characteristic is, that all outputs are determined only by the state they are in.

Within this thesis, we will ignore the notion of final (or accepting) states as introduced by Moore. Final states are significant when recognizing a word as belonging to a language. However, as this thesis has a bias towards controller specifications, we will ignore this since controllers are usually (conceptually) meant to run infinitely long and never terminate.

This section will first introduce the abstract and concrete syntax of classical Moore Automata. The subsection on static semantics will then introduce some additional constraints on well-defined automata. The following subsections will then introduce the operational semantics of classical Moore Automata and consider the notion of determinism for them.

#### 2.1.1 Abstract Syntax

In order to formally model the syntax of a given Moore Automaton, we need to define a mathematical structure, which can then contain all information from within the concrete (graphical) representation of an automaton.

Here, we define a tuple, which will contain locations, variable symbols, location transitions, guard conditions and entry actions. An instance of such a tuple will serve as a basis for defining the behavior of automata later.

**Definition 1.** The abstract syntax of any given classical Moore Automata consists of the 6-tuple:

$$(LOC, loc_0, VAR_{in}, VAR_{out}, L, R)$$

The elements of this tuple are given as:

- (1) LOC indicates the set of locations within the automaton.

- (2)  $loc_0 \in LOC$  denotes the initial location, which will be assumed upon start-up of the automaton.

- (3)  $VAR_{in}$  defines the input alphabet of the automaton. As such, it is formalized as a set of input variable symbols.

- (4)  $VAR_{out}$  denotes the output alphabet of the automaton. It is again defined as a set of output variable symbols.

- (5)  $L:LOC \longrightarrow VAR_{out}$  is a total labeling function, which assigns one output variable symbol to each location.

- (6)  $R:LOC \times VAR_{in} \times LOC$  is a location transition relation, which relates predecessor locations and input variable symbols to successor locations.

Note, that in contrast to the description of classical Moore Automata from [Moo56], we do not reference or define final/accepting locations. This is again due to the fact, that this study is focused mainly on controller implementations, which are – in concept – executed indefinitely.

#### 2.1.2 Concrete Syntax

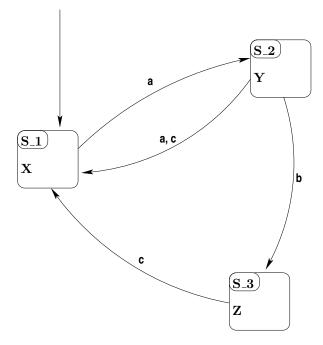

In order to illuminate the abstract syntax of classical Moore Automata, consider the graph representation of a Moore Automata from figure 2.1.

The set of locations LOC can be found simply by collecting the names of locations drawn in the graph. It is hence defined as the set:

$$LOC = \{S_1, S_2, S_3\}$$

The initial location  $loc_0$  is designated by the arrow without successor state. In the given automaton, this means:

$$loc_0 = S_1$$

The sets of input- and output variable symbols  $VAR_{in}$  and  $VAR_{out}$  can be found by collecting location entry actions and transition labels respectively:

$$VAR_{in} = \{a, b, c\}$$

$$VAR_{out} = \{X, Y, Z\}$$

Figure 2.1: Moore Automaton Example

The labeling of locations with output variable symbols L can be constructed by collecting all location entry actions individually. For the given automaton, the result is:

$$L = \{S_1 \mapsto X, S_2 \mapsto Y, S_3 \mapsto Z\}$$

The location transition relation R can be inferred from each arrow within the graph. Each arrow specifies a predecessor and a successor location as well as an input variable symbol associated with the respective arrow's location transition.

Note, that multiple input variable symbols associated with a single arrow are merely used as a shorthand for multiple arrows with identical predecessor and successor locations. Within the given automaton, the arrow labeled a, c thus stands for two separate location transitions.

The location transition relation from the given example looks as follows:

$$R = \{ (S_1, a, S_2), (S_2, a, S_1), (S_2, b, S_3), (S_2, c, S_1), (S_3, c, S_1) \}$$

#### 2.1.3 Static Semantics

In order for a given Moore Automaton ( $LOC, loc_0, VAR_{in}, VAR_{out}, L, R$ ) to be well defined, some constraints must hold for the 6-tuple:

Firstly, only a finite number of locations are allowed. Secondly, all symbolic sets must be pairwise disjoint, i.e. no symbol may appear in more than one of the sets LOC,  $VAR_{in}$  and  $VAR_{out}$ .

**Definition 2.** A classical Moore Automaton

$$(LOC, loc_0, VAR_{in}, VAR_{out}, L, R)$$

is well defined, iff the following holds:

$$| LOC | < \infty \qquad \land LOC \cap VAR_{in} = \emptyset \qquad \land LOC \cap VAR_{out} = \emptyset \qquad \land VAR_{in} \cap VAR_{out} = \emptyset$$

## 2.1.4 Operational Semantics

In order to define the behavior of an implementation of any given classical Moore Automaton, we consider the state-space S of an execution of the automaton. This state space is the conceptual set of execution states, which an automaton implementation must differentiate in order to provide a specific behavior.

Furthermore, for each predecessor execution state  $s \in S$  an automaton implementation must consider, which states  $s' \in S$  are possible successor execution states. An automaton implementation is then characterized by providing a

definite state transition relation T, which relates all predecessor and successor states for any given automaton.

The intended behavior of Moore Automata is then specified as a triple:

$$(S, s_0, T)$$

Within this triple, S is the state space,  $s_0$  is the initial execution state and T is the state transition relation.

Classical Moore Automata derive their importance in computer science precisely from the fact, that they are a class of automata, for which only the set of locations needs to be considered as state space. This is more commonly described as the property, that outputs of Moore Automata only depend on the location the automaton is in. The state space S is therefore defined as:

$$S = LOC$$

For each execution state  $s \in S$ , the visible output of the automaton is immediately defined as L(s) using the location labeling function L from definition 1.

The initial execution state  $s_0$  is trivial and can be taken directly from the syntax of a given automaton:

$$s_0 = l_0$$

The state transition relation T for classical Moore Automata must relate pairs of states and variable input symbols to successor states. As such, it is of the form:

$$T: S \times VAR_{in} \times S$$

The state transition relation T needs to contain all triples  $(s, v_{in}, s') \in S \times VAR_{in} \times S$ , which are already part of location transition labeling relation R from definition 1. Additionally, if for a given input a location has no matching emanating transition in R, the corresponding execution state must transition to itself.

We can now define the operational semantics for a classical Moore Automaton:

**Definition 3.** The operational semantics of a classical Moore Automaton  $(LOC, loc_0, VAR_{in}, VAR_{out}, L, R)$  is defined as triple:

$$(S, s_0, T)$$

The state space S is defined as:

$$S = LOC$$

The initial execution state  $s_0$  is defined as:

$$s_0 = l_0$$

The state transition relation T is defined as:

$$T: S \times VAR_{in} \times S$$

$$T = \{ (s, v_{in}, s') \in S \times VAR_{in} \times S \mid ((s, v_{in}, s') \in R) \vee ((\not \exists (\overline{s}, \overline{v_{in}}, \overline{s'}) \in R : (\overline{s} = s) \wedge (\overline{v_{in}} = v_{in})) \wedge (s = s')) \}$$

For any system state  $s \in S$ , the output can be calculated simply as L(s).

This definition is well formed in the sense, that each execution state will always have at least one successor state. In other words, the transition relation T is total.

*Proof.* Let  $(LOC, loc_0, VAR_{in}, VAR_{out}, L, R)$  be any well defined classical Moore Automaton.

Suppose, there exists an execution state  $\overline{s} \in S$ , such that  $\overline{s}$  has no successor state. Formally, suppose:

$$\exists \overline{s} \in S : \not\exists (s, v_{in}, s') \in T : \overline{s} = s$$

Consider  $\overline{s}$  and any input variable symbol  $\overline{v} \in V_{in}$ .

#### Case 1 – Existing location transition label:

Suppose:

$$\exists (s, v_{in}, s') \in R : (\overline{s} = s) \land (\overline{v} = v_{in})$$

Then:

$$(\overline{s}, \overline{v}, s') \in R$$

And by definition of T:

$$(\overline{s}, \overline{v}, s') \in T$$

This is a counter-example, since apparently:

$$\exists (s, v_{in}, s') \in T : s = \overline{s}$$

#### Case 2 – Non-existing location transition label:

Suppose:

$$\not\exists (s, v_{in}, s') \in R : (\overline{s} = s) \land (\overline{v} = v_{in})$$

We can augment this:

$$(\not\exists (s, v_{in}, s') \in R : (\overline{s} = s) \land (\overline{v} = v_{in})) \land (\overline{s} = \overline{s})$$

Then, by definition of T:

$$(\overline{s}, \overline{v}, \overline{s}) \in T$$

This is a counter-example, since apparently:

$$\exists (s, v_{in}, s') \in T : s = \overline{s}$$

#### 2.1.5 Determinism

In 2.1.4 it was proven, that the operational semantics for classical Moore Automata is well formed, i.e. does not cause any automaton execution to

fail due to a dead-lock. This was done by showing, that each execution state of any automaton always has at least one successor state.

Additionally a classical Moore Automaton is considered to be deterministic, if each execution state has exactly one successor state. This can be achieved by restricting the location transition labeling relation R from definition 1.

**Definition 4.** A classical Moore Automaton

$$(LOC, loc_0, VAR_{in}, VAR_{out}, L, R)$$

is deterministic, if the following constraint holds for location transition labeling function R:

$$\not\exists (s_1, v_1, s_1'), (s_2, v_2, s_2') \in R : (s_1 = s_2) \land (v_1 = v_2) \land (s_1' \neq s_2')$$

This restriction means, that R is now in fact a partial function:

$$R:LOC \times VAR_{in} \not\longrightarrow LOC$$

Accordingly, the state transition relation T then becomes a total function:

$$T: S \times VAR_{in} \longrightarrow S$$

*Proof.* In order to show, that state transition relation T for deterministic Moore Automata is a total state transition function, it needs to be shown, that:

$$\forall \overline{s} \in S, \overline{v} \in V_{in} : |\{(s, v_{in}, s') \in T \mid (\overline{s} = s) \land (\overline{v} = v_{in})\}| = 1$$

#### Case 1 – Existing location transition label:

Suppose:

$$\exists (s, v_{in}, s') \in R : (\overline{s} = s) \land (\overline{v} = v_{in})$$

Since R is now a partial function, this means:

$$\exists s' \in S : R(\overline{s}, \overline{v}) = s'$$

The successor state s' must be unique, again because R is a partial function.

#### Case 2 – Non-existing location transition label:

Suppose:

$$\not\exists (s, v_{in}, s') \in R : (\overline{s} = s) \land (\overline{v} = v_{in})$$

Since R is now a partial function, this means:

$$\not\exists s' \in S : R(\overline{s}, \overline{v}) = s'$$

As seen in the proof from 2.1.4, the state transition  $(\bar{s}, \bar{v}, \bar{s})$  is an element of T. Additionally, the state transition relation T from definition 3 ensures this to be the only element of the form  $(\bar{s}, \bar{v}, s')$ , since T explicitly enforces  $(\bar{s} = s')$ .

# 2.2 Abstract Timing for Moore Automata

This section introduces Timed Moore Automata. After an informal introduction, we discuss the extensions to classical Moore Automata needed to introduce the abstract notion of timers.

As such, this section is organized largely in analogy to the previous discussion of classical Moore Automata. Again, we consider abstract and concrete semantics, static and operational semantics and determinism.

#### 2.2.1 Informal Introduction to Timed Moore Automata

Timed Moore Automata are an extension of the classical Moore Automata in the sense, that they preserve the fundamental Moore Automata property: Outputs of an automaton are still only dependent on the current location of the automaton. Apart from this, several modifications and enhancements have been introduces in the Timed Moore Automata formalism in order to get closer to a practical embedded controller specification formalism.

While real-world controllers may internally defer computations to some synchronous processing mechanisms, it is uncommon for external controller input

interfaces to queue inputs as events to be processed since this might impede reaction time requirements.

Consequently, outputs are commonly published collectively at the external output interface of a controller for all who might be concerned. Again, producing outputs as a sequence of events is uncommon for external controller output interfaces since this might place too many restrictions on receivers as well as senders.

Classical Moore Automata processed their inputs and outputs in a synchronous fashion as queues of events. In contrast, Timed Moore Automata view inputs and outputs as vectors of signals with Boolean values to be processed in an asynchronous fashion. As such, they execute in a run-to-completion mode before accepting new inputs. As compared to the classical Moore Automata, which would accept a new input after each discrete transition, Timed Moore Automata perform discrete Transitions for as long as they are enabled and only accept new inputs when no more transitions are enabled.

The Timed Moore Automaton formalism is designed for modeling controllers as collections of automata running in parallel. As such, they could well have been designed to employ a synchronous execution semantics. However, the application domain necessitates, that collections of interacting automata can run in different processes or even on different computation nodes. As such, an asynchronous approach is more suited.

Safety-critical controllers are regularly required to behave deterministically with respect to any reproducible sequence of inputs. This can pose a modeling hazard when formulating guard conditions for a multitude of transitions leaving a specific location. In such a situation, it is not always trivial to see, whether all transition guards are pairwise preclusive. As a concession to model developers, Timed Moore Automata introduce the notion of unique transition priorities.

As the name might suggest, Timed Moore Automata introduce an abstract concept of timers. These timers are abstract in the sense, that no specific timer elapse time spans are ever specified. Instead, Timed Moore Automata only employ notions of timer actions and timer statuses. Timers may be (re)started or stopped, and they may be in a running or elapsed state. While timer actions start and stop are unremarkable when compared to other modeling formalisms, the notion of a timer elapse as a non-deterministic input free of any concept of time span makes this formalism special.

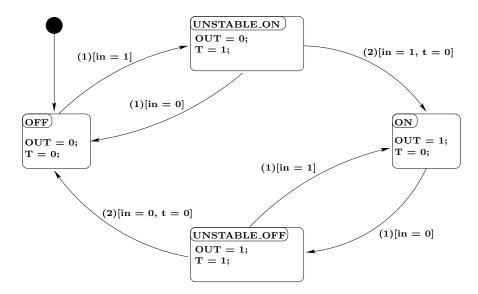

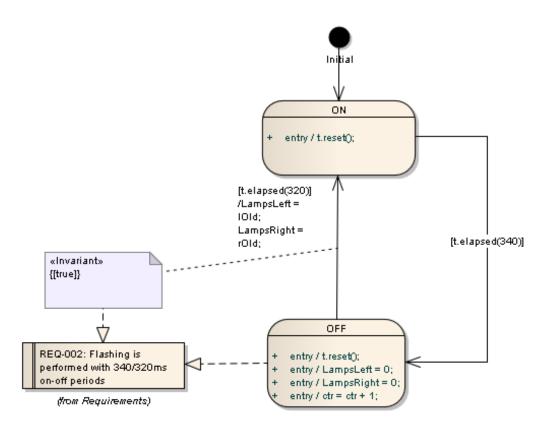

Figure 2.2: Timed Moore automaton for input debouncing

Timer actions are specified as entry action assignments to timer action variables. Starting a timer is done by assigning a value of 1 to its variable, an assignment of 0 stops the timer. Conversely, timer statuses can be evaluated using timer status variables. Here, a value of 1 denotes a running timer, while a value of 0 denotes an elapsed timer.

Consider the Timed Moore Automaton from figure 2.2, which specifies a simple input signal debouncing automaton. In locations ON and OFF, the input in is stably true or false, respectively. The output OUT reflects this in each location.

Whenever the input changes value, the automaton transitions to location  $UNSTABLE\_OFF$  or  $UNSTABLE\_ON$  respectively. Here, the timer T is started. Should the input revert back to its original value, the automaton transitions back to its previous location ON or OFF. However, should timer T elapse while the input remains different from the output, the automaton transitions to new stable output location OFF or ON respectively.

Note, that no timer elapse time span is specified for timer T and timer elapse variable t. Rather, t is a special (non-deterministic) input to the automaton.

#### 2.2.2 Abstract Syntax Extensions

As with classical Moore Automata, we need to define a mathematical structure to contain all relevant syntactical information for a given Timed Moore Automaton. This definition will largely resemble the earlier definition for the abstract syntax of classical Moore Automata from section 2.1.1 in the sense, that again locations, variable symbols, location transitions, guard conditions and entry actions are considered.

However, the definition of the abstract syntax for Timed Moore Automata will be extended to incorporate timer symbols and their appearance within guard conditions and entry actions.

**Definition 5.** The abstract syntax of a Timed Moore Automaton consists of the 10-tuple:

$$(LOC, loc_0, VAR_{in}, VAR_{out}, VAR_{ta}, VAR_{ts}, \beta, L_{out}, L_{ta}, R)$$

The elements of this tuple are now given as:

- (1) LOC indicates the set of locations within the automaton.

- (2)  $loc_0 \in LOC$  denotes the initial location, which will be assumed upon start-up of the automaton.

- (3)  $VAR_{in}$  defines the input alphabet of the automaton. As such, it is formalized as a set of input variable symbols.

- (4)  $VAR_{out}$  denotes the output alphabet of the automaton. It is again defined as a set of output variable symbols.

- (5)  $VAR_{ta}$  defines the set of timer activation symbols.

- (6)  $VAR_{ts}$  denotes the corresponding set of timer status symbols.

- (7)  $\beta: VAR_{ta} \longleftrightarrow VAR_{ts}$  is a bijection mapping timer activation variables and timer status variables to each other.

- (8)  $L_{out}: LOC \longrightarrow (VAR_{out} \longrightarrow \mathbb{B})$  is a labeling function, which for each location assigns Boolean valuations to each output variable.

- (9)  $L_{ta}: LOC \longrightarrow (VAR_{ta} \not\longrightarrow \mathbb{B})$  is a labeling function, which for each location may assign Boolean valuations to some timer activation variables.

- (10)  $R:LOC \longrightarrow (\mathbb{N} \not\longrightarrow ((VAR_{in} \cup VAR_{ts}) \not\longrightarrow \mathbb{B}) \times LOC)$  is the location transition relation, which relates predecessor and successor locations. More precisely, each predecessor location is mapped to a partial function, which maps transition priorities to pairs of corresponding guard conditions and successor locations. The guard conditions themselves are partial functions, which map input- and timer status variables to their required transition guard values.

#### 2.2.3 Concrete Syntax Extensions

The concrete syntax of Timed Moore Automata shows some key differences when compared to the concrete syntax of classical Moore Automata. Again consider the Timed Moore Automaton from figure 2.2.

As compared to classical Moore Automata, Timed Moore Automata locations do not merely list output symbols (and timer activation symbols), but assign them Boolean values. Consequently, transitions are guarded not only by input symbols (and timer status symbols), but are guarded by specific Boolean valuations.

This is due to the fact, that inputs and outputs are now processed as vectors of Boolean values rather than as input and output events. Another manifestation of this is the artificial initial location  $\bullet$ , which each Timed Automaton must furnish in order to provide a defined output state prior to automaton execution.

It is worth noting, that since Timed Moore Automata are extensions of the classical Moore Automata, each location must correspond to an entire output vector. It is therefore assumed, that all output variables not explicitly listed within a location shall have their values set to false. Note, that this is explicitly **not** true for timer activation variables, as timers may retain their status across multiple location transitions.

Timed Moore Automata provide transition priorities for all location transitions. For transitions emanating from a specific location, these are unique (usually consecutive) natural numbers intended to enforce deterministic modeling. Here, lower numbers mean higher transition priorities.

Finally, a subtle naming convention distinguishes input, output, timer activation and timer status variables. Input variables and timer status variables are always given in lower case. Output variables and timer activation variables are always given in upper case. Furthermore, timer activation variables will always begin with the letter 'T'. Their associated timer status variables will share the respective variable name, but be in lower case.

For the given automaton, the resulting abstract syntax instance looks as follows:

The set of locations is given as:

$$LOC = \{loc_0, ON, OFF, UNSTABLE\_ON, UNSTABLE\_OFF\}$$

Not surprisingly, the initial location of the automaton is the artificial initial location  $loc_0$ .

The variable symbol sets are:

$$VAR_{in} = \{in\}$$

$$VAR_{out} = \{OUT\}$$

$$VAR_{ta} = \{T\}$$

$$VAR_{ts} = \{t\}$$

The mapping between timer variables is then:

$$\beta = \{T \mapsto t\}$$

The location labeling functions look as follows:

$$L_{out} = \{ loc_0 \mapsto \{OUT \mapsto 0\}, \\ ON \mapsto \{OUT \mapsto 1\}, \\ OFF \mapsto \{OUT \mapsto 0\}, \\ UNSTABLE\_ON \mapsto \{OUT \mapsto 0\}, \\ UNSTABLE\_OFF \mapsto \{OUT \mapsto 1\} \}$$

$$L_{ta} = \{ loc_0 \mapsto \{T \mapsto 0\}, \\ ON \mapsto \{T \mapsto 0\}, \\ OFF \mapsto \{T \mapsto 0\}, \\ UNSTABLEON \mapsto \{T \mapsto 1\}, \\ UNSTABLEOFF \mapsto \{T \mapsto 1\} \}$$

Finally, the location transition relation is given as:

```

R = \{ loc_0 \mapsto \{ \\ ON \mapsto \{ \\ OFF \mapsto \{ \\ OFF \mapsto \{ \\ UNSTABLE\_ON \mapsto \{ \\ 1 \mapsto (\{in \mapsto 0\}, UNSTABLE\_OFF)\} \\ UNSTABLE\_ON \mapsto \{ \\ 1 \mapsto (\{in \mapsto 1\}, UNSTABLE\_ON)\} \\ 2 \mapsto (\{in \mapsto 0\}, OFF), \\ 2 \mapsto (\{in \mapsto 1, t \mapsto 0\}, ON)\} \\ UNSTABLE\_OFF \mapsto \{ \\ 1 \mapsto (\{in \mapsto 1\}, ON), \\ 2 \mapsto (\{in \mapsto 0, t \mapsto 0\}, OFF)\} \}

```

#### 2.2.4 Static Semantics Extensions

As with classical Moore Automata, some constraints must hold in order for a given Timed Moore Automaton to be well defined.

In accordance to classical Moore Automata, the number of locations must be finite. Again, all symbolic variable sets must be pairwise disjoint.

As we now have an artificial initial location, some additional constraints must hold for it. The initial location must have a single emanating transition, which must be unguarded. No transitions may have the initial location as their target.

Finally, for each location all emanating transitions must be attributed with unique priorities.

**Definition 6.** A Timed Moore Automaton

$$(LOC, loc_0, VAR_{in}, VAR_{out}, VAR_{ta}, VAR_{ts}, \beta, L_{out}, L_{ta}, R)$$

is well defined, iff the following holds:

(1) The number of locations is finite:

$$|LOC| < \infty$$

(2) All symbolic sets are pairwise disjoint:

$$LOC \cap VAR_{in} = \emptyset \qquad \wedge \\ LOC \cap VAR_{out} = \emptyset \qquad \wedge \\ LOC \cap VAR_{ta} = \emptyset \qquad \wedge \\ LOC \cap VAR_{ts} = \emptyset \qquad \wedge \\ VAR_{in} \cap VAR_{out} = \emptyset \qquad \wedge \\ VAR_{in} \cap VAR_{ta} = \emptyset \qquad \wedge \\ VAR_{out} \cap VAR_{ts} = \emptyset \qquad \wedge \\ VAR_{out} \cap VAR_{ts} = \emptyset \qquad \wedge \\ VAR_{out} \cap VAR_{ts} = \emptyset \qquad \wedge \\ VAR_{ta} \cap VAR_{ts} = \emptyset \qquad \wedge \\ VAR_{ta} \cap VAR_{ts} = \emptyset$$

(3) Only a single unguarded transition emanates from the initial location. It leads to another location.

$$\exists loc \in LOC : loc \neq loc_0 \land R(loc_0) = \{1 \mapsto (\emptyset, loc)\}\$$

(4) No transition has the initial location as target

$$\exists loc \in LOC, p \in \mathbb{N}, \gamma \in (VAR_{in} \cup VAR_{ts}) \not\longrightarrow \mathbb{B} : (loc \mapsto (p \mapsto (\gamma, loc_0))) \in R$$

Side note: For a given location the uniqueness of all emanating transition priorities is implicitly given, since prioritized transition labels are modeled as a (partial) function with priorities  $\mathbb{N}$  as its domain.

## 2.2.5 Operational Semantics Extensions

As before, we need to consider the state space S of Timed Moore Automata in order to define their behavior. Using a suitable definition for the state space, we can then specify, which predecessor execution states transition into which successor execution states.

As with classical Moore Automata, the current location of an automaton is sufficient to determine its output values, and we do not need to encapsulate output valuations within the state space. The set of locations LOC is therefore again part of the system state.

Additionally, since Timed Moore Automata perform their calculations in a run-to-completion mode, we need to keep track of input valuations. We employ valuation functions  $\Sigma_{in}: VAR_{in} \longrightarrow \mathbb{B}$  for this purpose.

Timer actions do not need to be kept within the state space, since they can be immediately inferred from the current location of a Timed Moore Automaton. However, timer statuses need to be considered, and we use Boolean valuation functions  $\Sigma_{ts}: VAR_{ts} \longrightarrow \mathbb{B}$  for this.

In order to determine whether an automaton is performing discrete transitions, or whether it is in a stable state, in which it can accept new inputs, an artificial variable  $stable \in \mathbb{B}$  is introduced into the state space.

As opposed to the classical Moore Automaton semantics, we need to consider multiple initial execution states  $S_0 \subset S$ . This is due to the fact, that all possible input valuations are valid prior to automaton execution. In contrast to this, no timers are running initially. As the automaton may have arbitrary input valuations, it is initially considered to be unstable  $(\neg stable)$ .

The state transition relation  $T: S \times S$  for Timed Moore Automata must consider three separate cases. Firstly, an automaton may perform a delay transition. Whenever an automaton is stable its location remains unchanged. New inputs may be assigned arbitrarily. Timers may elapse, but elapsed timers must remain so. All resulting execution states then become unstable in order to trigger a subsequent run to completion.

Secondly, an unstable state may perform a discrete transition. An automaton may change its current location if input- and timer status valuations enable a location transition. If multiple transitions are enabled, the automaton will perform the transition with the best priority. As a result, a successor execution state will be associated with the location transition's target location. While input valuations remain unchanged, the results of the target location's timer actions are reflected in successor state's timer status valuations. The successor execution state remains unstable, since additional location transitions may be possible.

Thirdly, an unstable automaton may become stable. This final discrete transition of a run to completion can only happen, if the automaton cannot perform any location transitions. The resulting execution state is identical to the predecessor state, except that it is stable.

**Definition 7.** The operational semantics of a Timed Moore Automaton

$$(LOC, loc_0, VAR_{in}, VAR_{out}, VAR_{ta}, VAR_{ts}, \beta, L_{out}, L_{ta}, R)$$

is defined as the triple:

$$(S, S_0, T)$$

The state space S is defined as:

$$S = LOC \times (VAR_{in} \longrightarrow \mathbb{B}) \times (VAR_{ts} \longrightarrow \mathbb{B}) \times \mathbb{B}$$

The set of initial states is given as:

$$S_{0} = \{ (loc, \sigma_{in}, \sigma_{ts}, stable) \in S \mid loc = loc_{0} \land \forall v \in VAR_{ts} : \neg \sigma_{ts}(v) \land \neg stable \}$$

For notation purposes we say, that a system state  $s \in S$  models a location  $loc' \in LOC$ , if loc' is the current location of s. Let  $s = (loc, \sigma_{in}, \sigma_{ts}, stable)$ . We define:

$$\forall loc' \in LOC : s \models loc' \Leftrightarrow loc' = loc$$

In analogy for variable valuations  $\sigma_{in}$  and  $\sigma_{ts}$ :

$$\forall v \in VAR_{in} : s \models v \Leftrightarrow \sigma_{in}(v)$$

$$\forall v \in VAR_{ts} : s \models v \Leftrightarrow \sigma_{ts}(v)$$

$$\forall stable' \in \mathbb{B} : s \models stable' \Leftrightarrow stable' = stable$$

An execution state s models a location transition guard  $\gamma$  under the following conditions:

$$\forall \gamma \in (VAR_{in} \cup VAR_{ts}) \not\longrightarrow \mathbb{B} :$$

$$(s \models \gamma \Leftrightarrow (\forall v \in VAR_{in} : v \not\in dom(\gamma) \lor s \models \gamma(v)) \land (\forall v \in VAR_{ts} : v \not\in dom(\gamma) \lor s \models \gamma(v)))$$

The state transition relation T can now be defined as:

$$T: S \times S$$

```

T = \{(s, s') \in S \times S \mid DISCTRANS_1(s, s') \land DISCTRANS_2(s, s') \land DELAYTRANS(s, s')\}

```

The predicates  $DISCTRANS_1$ ,  $DISCTRANS_2$  and DELAYTRANS are defined below.

Note, that  $\Pi_n$  is meant to denote the n-th element of a tuple.

(1) DISCTRANS<sub>1</sub>: An unstable execution state with enabled location transitions performs a discrete transition to a new unstable successor state. For multiple enabled location transitions, the transition with best priority is taken. The new execution state contains the transition target location as well as the results of all timer entry actions. Inputs remain unchanged.

```

DISCTRANS_{1}((loc, \sigma_{in}, \sigma_{ts}, stable), \\ (loc', \sigma'_{in}, \sigma'_{ts}, stable'))

=_{def}

(\exists p \in \mathbb{N} : (p \in dom(R(loc)) \land \\ (loc, \sigma_{in}, \sigma_{ts}, stable) \models \Pi_{1}(R(loc)(p)) \land \\ (loc, \sigma_{in}, \sigma_{ts}, stable) \models \Pi_{1}(R(loc)(p')) \land \\ (loc, \sigma_{in}, \sigma_{ts}, stable) \models \Pi_{1}(R(loc)(p')) \land \\ p' < p))) \land \\ \neg stable)

\implies \\ (loc' = \Pi_{2}(R(loc)(p)) \land \\ \sigma'_{in} = \sigma_{in} \land \\ (\forall v \in VAR_{ta} : \\ (v \not\in dom(L_{ta}(\Pi_{2}(R(loc)(p)))) \land \sigma'_{ts}(\beta(v)) = \sigma_{ts}(\beta(v))) \lor \\ (v \in dom(L_{ta}(\Pi_{2}(R(loc)(p)))) \land \sigma'_{ts}(\beta(v)) = L_{ta}(\Pi_{2}(R(loc)(p)))(v))) \land \\ \neg stable')

```

(2) DISCTRANS<sub>2</sub>: An unstable execution state with no enabled location transitions performs a discrete transition to a new stable successor state. The new execution state is identical to the predecessor state, except that it is

stable.

$$DISCTRANS_{2}((loc, \sigma_{in}, \sigma_{ts}, stable), \\ (loc', \sigma'_{in}, \sigma'_{ts}, stable'))$$

$$=_{def}$$

$$(\not\exists p \in \mathbb{N} : (p \in dom(R(loc)) \land \\ (loc, \sigma_{in}, \sigma_{ts}, stable) \models \Pi_{1}(R(loc)(p))) \land \\ \neg stable)$$

$$\Longrightarrow$$

$$(loc' = loc \land \\ \sigma'_{in} = \sigma_{in} \land \\ \sigma'_{ts} = \sigma_{ts} \land \\ stable')$$

(3) DELAYTRANS: A stable state performs a delay transition into an unstable state with unchanged location, free inputs and possible timer elapses:

$$DELAYTRANS((loc, \sigma_{in}, \sigma_{ts}, stable), \\ (loc', \sigma'_{in}, \sigma'_{ts}, stable'))$$

$$=_{def}$$

$$stable$$

$$\Longrightarrow$$

$$(loc' = loc \land \\ \forall v \in VAR_{ts} : \neg \sigma_{ts}(v) \Rightarrow \neg \sigma'_{ts}(v) \land \\ \neg stable')$$

For any system state  $(loc, \sigma_{in}, \sigma_{ts}, stable)$ , the outputs of an automaton can be calculated simply as  $L_{out}(loc)$ .

It is important to observe, that the above transition relation  $T: S \times S$  again constitutes a well formed semantics definition. There are (1) no spurious execution state transitions within the state transition relation, for which no constraints on the successor state exist. Additionally, (2) the definition ensures, that each execution state has at least one successor state.

To rephrase condition (1) in other words, every execution state  $s \in S$  fulfills at least one of the premises of predicates  $DISCTRANS_1$ ,  $DISCTRANS_2$  and DELAYTRANS, and its successor states are therefore liable to be constrained by at least one predicate conclusion. Moreover, each state s fulfills the premise of precisely one of the predicates.

*Proof.* Let

$$s = (loc, \sigma_{in}, \sigma_{ts}, stable)$$

.

## Case 1 – Stable state:

Suppose stable. Then neither premise of predicates  $DISCTRANS_1$  and  $DISCTRANS_2$  can hold, since they mandate  $\neg stable$ . However, the premise of predicate DELAYTRANS is precisely stable. DELAYTRANS is the one and only predicate, whose premise is fulfilled.

#### Case 2 – Unstable state:

Suppose  $\neg stable$ . The premise of predicate DELAYTRANS can then never be fulfilled, since it is precisely stable.

## Case 2.1 – Unstable state / enabled transitions

Suppose furthermore, that at least one location transitions emanating from loc is enabled. Then there exists at least one priority  $p \in \mathbb{N}$ , which is assigned to an enabled transition. Moreover, there must be a smallest priority p, which is assigned to an enabled transition. The premise of predicate  $DISCTRANS_1$  holds:

```

\exists p \in \mathbb{N} : (p \in dom(R(loc)) \land (loc, \sigma_{in}, \sigma_{ts}, stable) \models \Pi_1(R(loc)(p)) \land (\not\exists p' \in \mathbb{N} : (p' \in dom(R(loc)) \land (loc, \sigma_{in}, \sigma_{ts}, stable) \models \Pi_1(R(loc)(p')) \land p' < p))) \land \neg stable

```

The premise of predicate  $DISCTRANS_2$  does not hold, since it demands the non-existence of any priority p with enabled transition. In this case,  $DISCTRANS_1$  is the one and only predicate, whose premise is fulfilled.

## Case 2.2 – Unstable state / no enabled transitions

Suppose now, that no location transitions emanating from loc are enabled. Then there exists no priority  $p \in \mathbb{N}$ , which is assigned to an enabled transition. The premise of predicate  $DISCTRANS_2$  holds:

$$\exists p \in \mathbb{N} : (p \in dom(R(loc)) \land \\ (loc, \sigma_{in}, \sigma_{ts}, stable) \models \Pi_1(R(loc)(p))) \land \\ \neg stable$$

The premise of predicate  $DISCTRANS_1$  does not hold, since – among

other things – it demands the existence of such a priority p. In this case,  $DISCTRANS_2$  is the one and only predicate, whose premise is fulfilled.

Condition (2) from above necessitated, that transition relation  $T: S \times S$  be total. each execution state  $s \in S$  must have a successor state  $s' \in S$ . Taking condition (1) into account, this is now easy to see.

*Proof.* Consider the definition of transition relation  $T: S \times S$ :

$$T = \{(s, s') \in S \times S \mid DISCTRANS_1(s, s') \land DISCTRANS_2(s, s') \land DELAYTRANS(s, s')\}$$

Since each predicate is an implication with a premise formulated over s, and since any state s always fulfills precisely one premise, it remains to be shown, that for each predecessor state s there exists a successor state s', which fulfills the respective implication conclusion.

#### Case 1 – Stable state:

Stable states s fulfill the premise of predicate DELAYTRANS. A successor state s', which fulfills the predicate conclusion can always be constructed. Consider the relevant constraints for  $s' = (loc', \sigma'_{in}, \sigma'_{ts}, stable')$ :

$$loc' = loc \land \forall v \in VAR_{ts} : \neg \sigma_{ts}(v) \Rightarrow \neg \sigma'_{ts}(v) \land \neg stable'$$

As compared to the predecessor state, the successor location remains unchanged. No constraints are placed on the successor input valuation function, so such a function can exist. The only constraints placed on the successor timer status valuation function are, that no elapsed timers may start by themselves, and even predecessor  $\sigma_{ts}$  might be used as successor  $\sigma'_{ts}$ . Finally, the successor state must be unstable.

## Case 2.1 – Unstable state / enabled transitions

Unstable states s with enabled transitions fulfill the premise of predicate  $DISCTRANS_1$ . A successor state s', which fulfills the predicate conclu-

sion can always be constructed. Consider the relevant constraints for  $s' = (loc', \sigma'_{in}, \sigma'_{ts}, stable')$ :

```

loc' = \Pi_2(R(loc)(p)) \land

\sigma'_{in} = \sigma_{in} \land

(\forall v \in VAR_{ta} :

(v \notin dom(L_{ta}(\Pi_2(R(loc)(p)))) \land \sigma'_{ts}(\beta(v)) = \sigma_{ts}(\beta(v))) \lor

(v \in dom(L_{ta}(\Pi_2(R(loc)(p)))) \land \sigma'_{ts}(\beta(v)) = L_{ta}(\Pi_2(R(loc)(p)))(v))) \land

\neg stable'

```

As there must be an enabled transition with best priority p, p must be within the domain of R(loc). As such, loc' is simply the second element of tuple R(loc)(p). As compared to the predecessor state, the successor input valuations remain unchanged, and the only constraints placed on the timer status valuations are the effects of target location entry timer actions. As such, the successor timer status valuation function  $\sigma'_{ts}$  can be constructed directly from  $\sigma_{ts}$  and location labeling function  $L_{ta}(loc')$ . The successor state remains unstable.

## Case 2.2 – Unstable state / no enabled transitions

Unstable states s with no enabled transitions fulfill the premise of predicate  $DISCTRANS_2$ . A successor state s', which fulfills the predicate conclusion can always be constructed. Consider the relevant constraints for  $s' = (loc', \sigma'_{in}, \sigma'_{ts}, stable')$ :

$$loc' = loc \land$$

$$\sigma'_{in} = \sigma_{in} \land$$

$$\sigma'_{ts} = \sigma_{ts} \land$$

$$stable'$$

The successor state s' is identical to the predecessor state s with the exception, that s' is stable.

## 2.2.6 Determinism

All Timed Moore Automata show deterministic behavior with respect to any given sequence of inputs. While stable execution states may have multiple valid successor states due to new input and timer elapse valuations, any unstable predecessor state s can only have a single successor state s'.

*Proof.* In the case of an unstable predecessor state s without enabled transitions, the conclusion of predicate  $DISCTRANS_1$  immediately specifies the one and only successor state s', which is identical to s except for its stability.

In the case of an unstable predecessor state s with enabled transitions, the conclusion of predicate  $DISCTRANS_2$  immediately specifies the one and only successor state s', which is identical to s except for its timer status valuation function  $\sigma'_{ts}$ . However, since  $\sigma'_{ts}$  is directly constructed from  $\sigma_{ts}$ , and since  $L_{ta}$  is a function,  $\sigma'_{ts}$  is also unique.

# 2.3 Model Checking for Timed Moore Automata

This section deals with explicit model checking for Timed Moore Automata. Particularly, we consider the means necessary to detect the (non-)existence of live-lock situations within Timed Moore Automata.

This section firstly describes the algorithms necessary in order to explicitly construct Kripke structures over Timed Moore Automata. It then recites the needed prerequisites regarding Computation Tree Logic as well as our take on the well-established Computation Tree Logic model checking algorithms presented in [JGP99]. Finally, some consideration is given to optimizing model checking for live-lock situations in Timed Moore Automata.

# 2.3.1 Construction of Kripke structures

Model checking for Timed Moore Automata involves the explicit enumeration of all system states an automaton execution may adopt. Each system state must contain all information regarding current automaton location, input-, output-, timer activation- and timer status valuation as well as the automaton's current stability.

As such, the state space for explicit model checking is rather larger than the state space used in section 2.2.5 when defining the operational semantics. In an effort to somewhat combat the effects of the resulting state space explosion, we employ don't-care input- and timer status valuations for situations, where the evolution of states into successor states is independent of concrete valuations. These mechanisms are inspired by the notion of delayed non-determinism from [NS08].

The explicit state space  $S_{TMA}$  considered during model checking of Timed Moore Automata is defined as follows.

**Definition 8.** Given a Timed Moore Automaton

$$(LOC, loc_0, VAR_{in}, VAR_{out}, VAR_{ta}, VAR_{ts}, \beta, L_{out}, L_{ta}, R)$$

the explicit state space  $S_{TMA}$  is defined as:

$$S_{TMA} = LOC \times \\ (VAR_{in} \longrightarrow L(\mathbb{B})) \times \\ (VAR_{out} \longrightarrow \mathbb{B}) \times \\ (VAR_{ts} \longrightarrow L(\mathbb{B})) \times \\ (VAR_{ta} \longrightarrow \mathbb{B}) \times \\ \mathbb{R}$$

It consists of 6-tuples (loc,  $\sigma_{in}$ ,  $\sigma_{out}$ ,  $\sigma_{ts}$ ,  $\sigma_{ta}$ , stable) with the following elements:

- (1)  $loc \in LOC$  indicates the automaton's current location

- (2)  $\sigma_{in} \in (VAR_{in} \longrightarrow L(\mathbb{B}))$  is an input variable valuation function

- (3)  $\sigma_{out} \in (VAR_{out} \longrightarrow \mathbb{B})$  is an output variable valuation function

- (4)  $\sigma_{ts} \in (VAR_{ts} \longrightarrow L(\mathbb{B}))$  is a timer status variable valuation function

- (5)  $\sigma_{ta} \in (VAR_{ta} \longrightarrow \mathbb{B})$  is a timer action variable valuation function

(6)  $stable \in \mathbb{B}$  indicates, whether the automaton is currently stable and accepts new inputs

The set  $L(\mathbb{B})$  used above is a lattice to reflect don't-care-conditions for inputand timer status variable valuations. The element  $\top$  denotes a don't-carevaluation, i.e. a possible valuation of either true or false. The element  $\bot$  is required for  $L(\mathbb{B})$  to be a lattice. Finally,  $\sqsubseteq$  is the partial order relation for  $L(\mathbb{B})$ .

We define  $(L(\mathbb{B}), \sqsubseteq)$  as:

$$L(\mathbb{B}) = \{ \top, true, false, \bot \}$$

$$\sqsubseteq : L(\mathbb{B}) \times L(\mathbb{B})$$

$$\bot \sqsubseteq true \land$$

$$\bot \sqsubseteq false \land$$

$$\bot \sqsubseteq \top \land$$

$$true \sqsubseteq \top \land$$

$$false \sqsubseteq \top$$

The atomic propositions used for model checking of Timed Moore Automata involve an automaton's current location, input-, output-, timer activation- and timer status valuation as well as the automaton's stability. Variable symbols are already mapped to Boolean values, so they can immediately be considered to be atomic propositions. Locations can either be currently active or not, so again their symbols may immediately be used as atomic propositions. In order to capture the stability of a given system state, we introduce artificial atomic proposition *idle*.

**Definition 9.** Given a Timed Moore Automaton

$$(LOC, loc_0, VAR_{in}, VAR_{out}, VAR_{ta}, VAR_{ts}, \beta, L_{out}, L_{ta}, R)$$

the set of atomic propositions AP is defined as:

$$AP = LOC \cup VAR_{in} \cup VAR_{out} \cup VAR_{ta} \cup VAR_{ts} \cup \{idle\}$$

Using the above definitions, we may now introduce a labeling function  $L_{ap}$ . Its purpose is to enumerate all atomic propositions, which hold in a given system state s. Its definition is given below.

**Definition 10.** The atomic proposition labeling function  $L_{ap}$  is defined as:

$$L_{ap}: S_{TMA} \longrightarrow \mathbb{P}(AP)$$

$$L_{ap}((loc, \sigma_{in}, \sigma_{out}, \sigma_{ts}, \sigma_{ta}, stable)) = \{loc\} \cup \{v \in VAR_{in} \mid true \sqsubseteq \sigma_{in}(v)\} \cup \{v \in VAR_{ts} \mid true \sqsubseteq \sigma_{ts}(v)\} \cup \{v \in VAR_{ts} \mid true \sqsubseteq \sigma_{ts}(v)\} \cup \{v \in VAR_{ta} \mid true = \sigma_{in}(v)\} \cup \{idle \mid true = stable\}$$

Using the above definitions of explicit state space, atomic propositions and atomic proposition labeling function, we can finally define the Kripke structures employed to perform model checking for Timed Moore Automata.

**Definition 11.** Given a Timed Moore Automaton

$$(LOC, loc_0, VAR_{in}, VAR_{out}, VAR_{ta}, VAR_{ts}, \beta, L_{out}, L_{ta}, R)$$

the Kripke structure K(M) is defined as a 4-tuple:

$$K = (S_K, s_{K_0}, T_K, L_{ap})$$

Its elements are:

- (1) The set of all reachable system states  $S_K \subseteq S_{TMA}$

- (2) The initial system state  $s_{K_0} \in S_K$

- (3) The state transition relation  $T_K: S_K \times S_K$

- (4) The atomic labeling function  $L_{ap}: S_K \longrightarrow \mathbb{P}(AP)$