# A Framework for Model-based Testing of Integrated Modular Avionics

Dissertation zur Erlangung des Doktorgrades der Ingenieurwissenschaften (Dr.-Ing.)

vorgelegt von Christof Efkemann

Fachbereich 3

Informatik/Mathematik

## A Framework for Model-based Testing of Integrated Modular Avionics

Dissertation zur Erlangung des Doktorgrades der Ingenieurwissenschaften (Dr.-Ing.)

> vorgelegt von Christof Efkemann

im Fachbereich 3 (Informatik/Mathematik) der Universität Bremen im August 2014

Revision 205. Typeset with XAMTEX in Adobe Garamond Pro.

Eingereicht am 06. August 2014

Gutachter:

Prof. Dr. Jan Peleska (Universität Bremen) Prof. Dr. Anne E. Haxthausen (Technical University of Denmark)

#### Erklärung

| den keine anderen als | rtation wurde ohne fremde Hilfe angefertigt. Es wurdie angegebenen Quellen und Hilfsmittel benutzt. Alaus Veröffentlichungen entnommen wurden, sind als cht. |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datum                 | Unterschrift                                                                                                                                                 |

#### Zusammenfassung

In modernen Flugzeugen basiert das Design der Elektronik und der Steuerungssysteme auf dem Konzept der Integrierten Modularen Avionik (IMA). Obwohl dies diverse Vorteile mit sich bringt (Gewichtsreduktion, niedrigerer Strom- und Treibstoffverbrauch, geringere Entwicklungs- und Zertifizierungskosten und -aufwände), stellt die IMA-Plattform eine zusätzliche Komplexitätsebene dar.

Aufgrund der sicherheitskritischen Eigenschaften vieler Avionikfunktionen sind sorgfältige und akkurate Verifikation und Tests dieser Systeme zwingend erforderlich.

Diese Dissertation beschreibt Forschungsergebnisse bezüglich des modellbasierten Testens von IMA-Systemen, welche zum Teil im Rahmen des europäischen Forschungsprojekts SCARLETT erzielt wurden. Die Arbeit beschreibt ein vollständiges Rahmenwerk, welches es einem IMA-Domänenexperten ermöglicht, modellbasierte Tests auf Modul-, Konfigurations- sowie Anwendungsebene zu entwerfen und in einer standardisierten Testumgebung auszuführen.

Der erste Teil dieser Arbeit bietet Hintergrundinformationen zu den ihr zugrunde liegenden Themen: dem IMA-Konzept, domänenspezifischen Sprachen, modellbasiertem Testen und dem TTCN-3-Standard. Im zweiten Teil werden das Rahmenwerk der IMA-Testmodellierungssprache (ITML) und dazugehörige Komponenten eingeführt. Es wird eine hierfür maßgeschneiderte TTCN-3-Testumgebung mit passenden Adaptern und Codecs beschrieben. Basierend auf MetaEdit+ und dem Meta-Metamodell GOPPRR werden die drei Varianten der domänenspezifischen Sprache ITML definiert, jeweils mit abstrakter und konkreter Syntax sowie statischer und dynamischer Semantik. Die Generierung von Testprozeduren aus ITML-Modellen wird im Detail erklärt. Darüber hinaus werden das Design und die Entwicklung eines universellen Testagenten beschrieben. Zur Steuerung des Agenten wird ein dediziertes Kommunikationsprotokoll definiert.

Für den dritten Teil dieser Arbeit wurde eine Evaluation des Rahmenwerks durchgeführt. Es werden Einsatzszenarien im SCARLETT-Projekt beschrieben und Vergleiche zwischen ITML und verwandten Werkzeugen und Ansätzen gezogen. Außerdem wird auf die Vorteile der Benutzung des ITML-Rahmenwerks durch IMA-Domänenexperten eingegangen.

Der letzte Teil bietet eine Reihe von ITML-Beispielmodellen. Er enthält darüber hinaus Referenzmaterial, u. a. XML-Schemata, Quellcode des Rahmenwerks und Modellvalidatoren.

#### **Abstract**

In modern aircraft, electronics and control systems are designed based on the Integrated Modular Avionics (IMA) system architecture. While this has numerous advantages (reduction of weight, reduced power and fuel consumption, reduction of development cost and certification effort), the IMA platform also adds an additional layer of complexity.

Due to the safety-critical nature of many avionics functions careful and accurate verification and testing are imperative.

This thesis describes results achieved from research on model-based testing of IMA systems, in part obtained during the European research project SCARLETT. It presents a complete framework which enables IMA domain experts to design and run model-based tests on bare module, configured module, and application level in a standardised test environment.

The first part of this thesis provides background information on the relevant topics: the IMA concept, domain-specific languages, model-based testing, and the TTCN-3 standard. The second part introduces the IMA Test Modelling Language (ITML) framework and its components. It describes a tailored TTCN-3 test environment with appropriate adapters and codecs. Based on MetaEdit+ and its meta-metamodel GOPPRR, it defines the three variants of the domain-specific language ITML, each with its abstract and concrete syntax as well as static and dynamic semantics. The process of test procedure generation from ITML models is explained in detail. Furthermore, the design and implementation of a universal Test Agent is shown. A dedicated communication protocol for controlling the agent is defined as well.

The third part provides an evaluation of the framework. It shows usage scenarios in the SCARLETT project, gives a comparison to related tools and approaches, and explains the advantages of using the ITML framework for an IMA domain expert.

The final part presents several example ITML models. It also provides reference material like XML schemata, framework source code, and model validators.

#### **Acknowledgements**

Writing this thesis would not have been possible if it weren't for the support of a number of people. First of all, I would like to thank my advisor, Jan Peleska, for giving me the opportunity to work in his research group at the University of Bremen. Second, I am very grateful to have had the opportunity of being a part of the European research project SCARLETT. I enjoyed these three and a half years of my life, working with such a vast group of interesting and skilled people from all across Europe. Two people I would like to thank in particular: Florian Bommer for his strenuous efforts to make the I/O-intensive demonstration a success, and Arne Graepel for his very helpful support with the TTCN-3 test environment.

I would also like to thank my kind colleagues, both at the university as well as at Verified Systems. I very much enjoyed the pleasant working atmosphere and their constructive support. In particular, I would like to thank Uwe Schulze and Helge Löding for sharing their invaluable expertise on model-based testing and rtt-tcgen.

Not unmentioned shall go my two proofreaders: Oliver Meyer and Kai Thomsen. Thanks to their labour many a typo or inaccuracy could be eliminated—any remaining are entirely my own fault.

And last, but by no means least, I would like to thank my family and my friends for their love, their trust, and for believing in me.

# **Contents**

| Contents                           |                                                                                                                                     | 15                                                 |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| List of F                          | gures                                                                                                                               | 19                                                 |

| List of T                          | ables                                                                                                                               | 21                                                 |

| 1 Inti<br>1.1<br>1.2<br>1.3<br>1.4 |                                                                                                                                     | 23<br>24<br>24<br>25<br>25                         |

| Part I: I                          | Background                                                                                                                          |                                                    |

| 2 Into 2.1 2.2 2.3 2.4 2.5         |                                                                                                                                     | 29<br>30<br>31<br>32<br>33<br>34<br>34<br>36<br>36 |

| 3 Doi 3.1 3.2                      | main-specific Languages  Domain-specific Modelling  MetaEdit+  3.2.1 GOPPRR  3.2.2 Metamodelling  3.2.3 Modelling  3.2.4 Generators | 39<br>40<br>41<br>42<br>42<br>43<br>45             |

| 4 Mo                               | del-based Testing                                                                                                                   | 49                                                 |

#### **CONTENTS**

| 5   | TTCN-3                                      | 53    |

|-----|---------------------------------------------|-------|

|     | 5.1 Language Syntax                         | . 54  |

|     | 5.2 Components and Concurrency              |       |

|     | 5.3 Communication                           |       |

|     | 5.4 Runtime Architecture                    | . 59  |

|     |                                             |       |

| Par | II: Framework Architecture                  |       |

| 6   | Test Case Generation and Execution Process  | 63    |

| 7   | Test Agent                                  | 65    |

|     | 7.1 Test Agent Control Protocol             |       |

|     | 7.1.1 Layer 1                               |       |

|     | 7.1.2 Layer 2                               | . 68  |

|     | 7.1.3 Coding Example                        | . 72  |

|     | 7.2 Runtime Behaviour                       |       |

|     | 7.2.1 Initialisation                        |       |

|     | 7.2.2 Sequence Number Initialisation        |       |

|     | 7.2.3 Main Loop                             | . 74  |

|     | 7.2.4 Protocol Handling                     | . 75  |

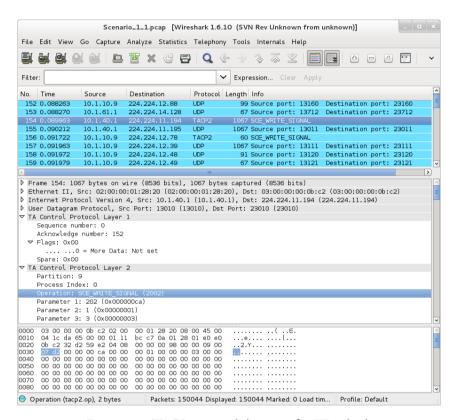

|     | 7.3 Wireshark TACP Dissector                | . 76  |

| 8   | TTCN-3 Environment                          | 79    |

|     | 8.1 Proxy SA                                |       |

|     | 8.2 TACP SA                                 |       |

|     | 8.3 TACP Protocol Handling                  | . 83  |

|     | 8.4 Test Procedures                         | . 84  |

| 9   | IMA Test Modelling Language                 | 85    |

|     | 9.1 Domain Analysis                         |       |

|     | 9.1.1 Bare Module Testing: Configuration    |       |

|     | 9.1.2 Bare Module Testing: Behaviour        | . 90  |

|     | 9.1.3 Bare Module Testing: Test Suite       |       |

|     | 9.1.4 Configured Module Testing             |       |

|     | 9.1.5 Hardware/Software Integration Testing | . 98  |

|     | 9.1.6 Design Considerations                 | . 106 |

|     | 9.2 ITML-B: Bare Module Testing             |       |

|     | 9.2.1 Configuration                         |       |

|     | 9.2.2 Behaviour                             |       |

|     | 9.2.3 Test Suite                            |       |

|     | 9.2.4 Dynamic Semantics                     |       |

|     | 9.3 ITML-C: Configured Module Testing       |       |

|     | 9.3.1 Behaviour                             |       |

|     | 9.3.2 Test Suite                            | . 124 |

#### CONTENTS

|                                            | 9.3.3 Dynamic Semantics                                                                                                                                                                                                                                                                         | 125<br>125<br>125<br>128<br>130<br>132                                    |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 10                                         | Test Generation  10.1 MERL Intermediate Format Generators  10.2 Generation of ITML-B and ITML-C Tests  10.2.1 ICD Generator  10.2.2 ICD Parser  10.2.3 TTCN-3 Code Generator  10.3 Generation of ITML-A Tests  10.3.1 Test Case Generator                                                       | 135<br>136<br>137<br>137<br>137<br>139<br>140                             |

| Par                                        | t III: Evaluation                                                                                                                                                                                                                                                                               |                                                                           |

| <ul><li>11</li><li>12</li><li>13</li></ul> | Usage in the SCARLETT Project  11.1 I/O-intensive Scenarios  11.1.1 Scenario 1  11.1.2 Scenario 2  11.1.3 Scenario 3  11.1.4 Scenario 4  11.1.5 Models  Comparison with Other Tools and Approaches  12.1 TTCN-3  12.2 CSP  12.3 UML Testing Profile  Conclusion  13.1 Results  13.2 Future Work | 147<br>148<br>148<br>149<br>149<br>151<br>151<br>152<br>153<br>155<br>156 |

| Par                                        | t IV: Appendices                                                                                                                                                                                                                                                                                |                                                                           |

| A                                          | Example Models  A.1 ITML-B  A.1.1 Intermediate XML Representation  A.1.2 TTCN-3 Code  A.2 ITML-A  A.2.1 Intermediate XML Representation  A.2.2 TTCN-3 Code                                                                                                                                      | 159<br>159<br>164<br>165<br>169<br>174<br>176                             |

#### **CONTENTS**

| В    | TA Auxiliary Functions                       | 189 |

|------|----------------------------------------------|-----|

|      | B.1 AUX_RESERVE_DATA_TABLE_ENTRY             | 189 |

|      | B.2 AUX_CLEAR_DATA_TABLE_ENTRY               | 190 |

|      | B.3 AUX_GET_DATA_TABLE_ENTRY                 | 190 |

|      | B.4 AUX_SET_DATA_TABLE_ENTRY                 | 190 |

| C    | TTCN-3 Framework Components                  | 193 |

|      | C.1 Proxy SA Implementation                  | 193 |

|      | C.2 TACP SA Implementation                   | 196 |

|      | C.3 TACP Codec Implementation                | 197 |

|      | C.4 Float Codec Implementation               | 204 |

|      | C.5 Common TTCN-3 Type Definitions           | 205 |

|      | C.6 TACP Protocol Handler                    | 221 |

| D    | Model Validity Checkers                      | 233 |

|      | D.1 Configuration Validator                  | 233 |

|      | D.2 Behaviour Validator                      | 234 |

|      | D.3 Test Suite Validator (ITML-B)            | 238 |

|      | D.4 Test Suite Validator (ITML-C)            | 239 |

|      | D.5 System Diagram Validator                 | 240 |

|      | D.6 Component Diagram Validator              | 241 |

|      | D.7 Statechart Validator                     | 243 |

| E    | MERL Intermediate Format Generators          | 245 |

|      | E.1 Configuration Export Generator           | 245 |

|      | E.2 Behaviour Export Generator               | 247 |

|      | E.3 Test Suite Export Generator (ITML-B)     | 250 |

|      | E.4 Test Suite Export Generator (ITML-C)     | 250 |

|      | E.5 System Diagram Export Generator (ITML-A) | 251 |

| F    | XML Schemata                                 | 257 |

|      | F.1 Configuration Schema                     | 257 |

|      | F.2 Behaviour Schema                         | 258 |

|      | F.3 Test Suite Schema (ITML-B)               | 263 |

|      | F.4 Test Suite Schema (ITML-C)               | 264 |

|      | F.5 System Diagram Schema (ITML-A)           | 265 |

| G    | List of Acronyms                             | 269 |

| Bibl | liography                                    | 271 |

# **List of Figures**

| 2.1<br>2.2<br>2.3                                           | AFDX frame                                                                                                                                                                                                                                                                                                              | 31<br>32<br>37                                                     |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                      | Comparison of abstraction levels  DSM Workflow  MetaEdit+ Object Tool  MetaEdit+ Graph Bindings  MetaEdit+ Graph Constraints  MetaEdit+ Diagram Editor                                                                                                                                                                  | 40<br>41<br>44<br>44<br>45<br>46                                   |

| 4.1                                                         | Example model: Turn indicator (UML)                                                                                                                                                                                                                                                                                     | 50                                                                 |

| 5.1                                                         | TTCN-3 System Architecture                                                                                                                                                                                                                                                                                              | 60                                                                 |

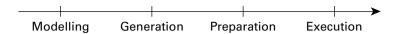

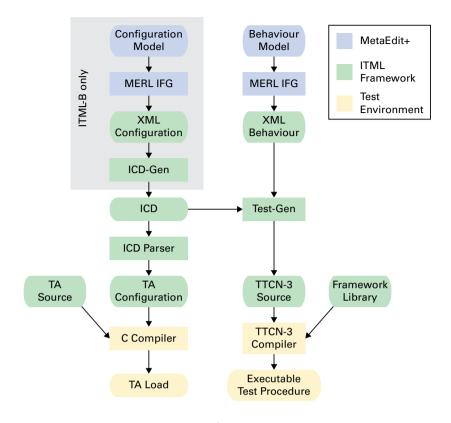

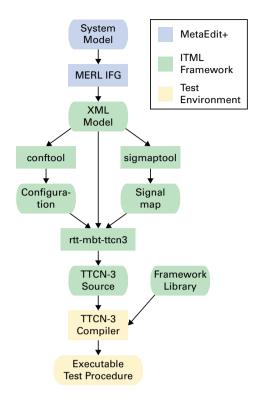

| 6.1                                                         | Test Case Generation and Execution Process                                                                                                                                                                                                                                                                              | 64                                                                 |

| 7.1                                                         | TACP protocol dissector for Wireshark                                                                                                                                                                                                                                                                                   | 77                                                                 |

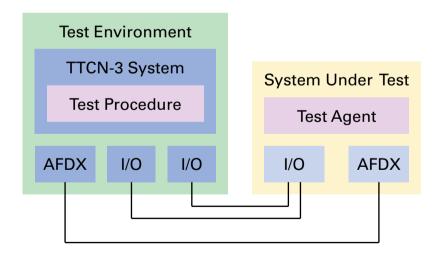

| 8.1                                                         | Test Environment and System Under Test                                                                                                                                                                                                                                                                                  | 79                                                                 |

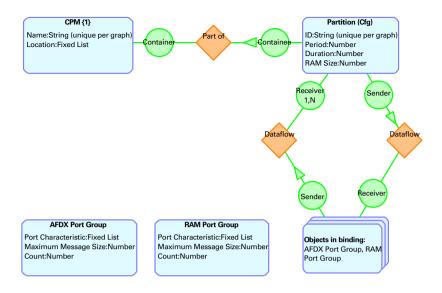

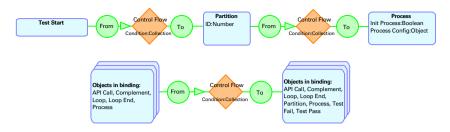

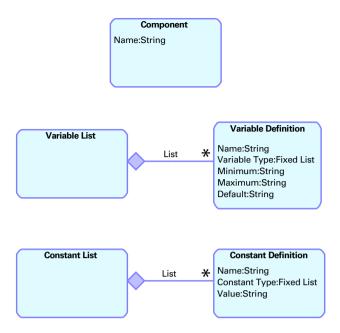

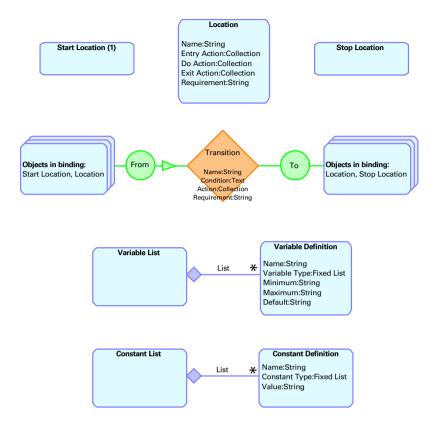

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9 | Abstract Syntax: Configuration Part Abstract Syntax: Behaviour Control Flow Behaviour Metamodel: Nodes Behaviour Metamodel: Parameters ITML-B Test Suite ITML-C Test Suite Abstract Syntax: System Diagram Abstract Syntax: System Diagram Decomposition Abstract Syntax: Component Diagram Abstract Syntax: Statechart | 108<br>110<br>111<br>112<br>116<br>124<br>126<br>127<br>129<br>130 |

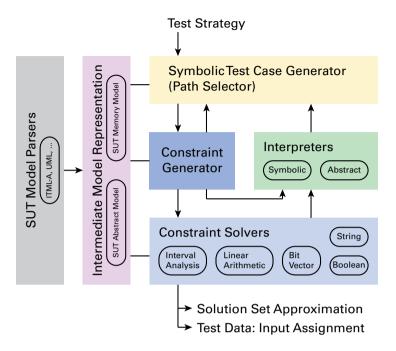

|                                                             | ITML-B and ITML-C generation process                                                                                                                                                                                                                                                                                    | 136<br>140                                                         |

#### List of Figures

| 10.3        | Test Case Generator architecture    | í1 |

|-------------|-------------------------------------|----|

| A.1         | Configuration model                 | 60 |

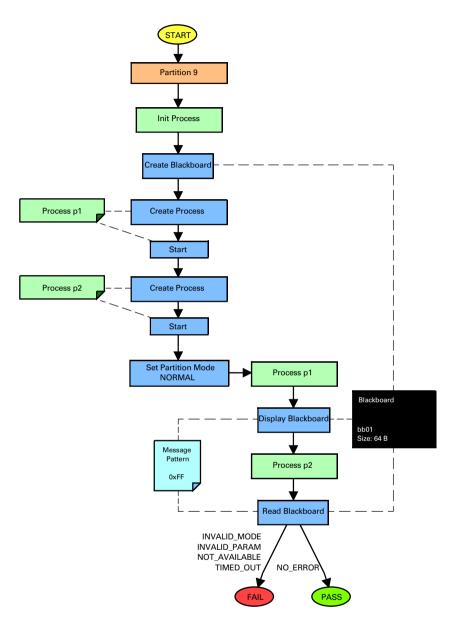

| A.2         | Blackboard API test model 10        | 51 |

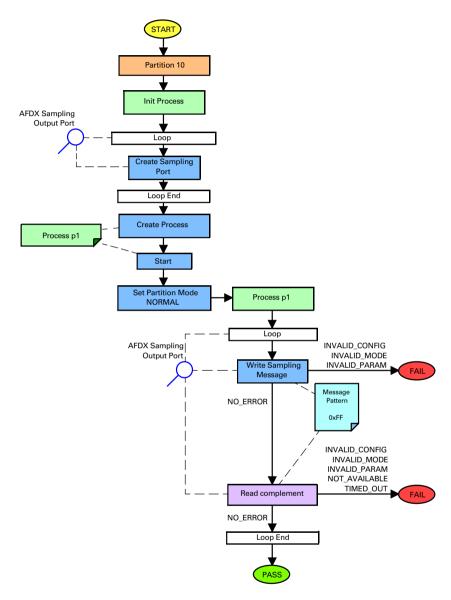

| A.3         | AFDX port API test model            | 52 |

| A.4         | RAM port API test model             | 53 |

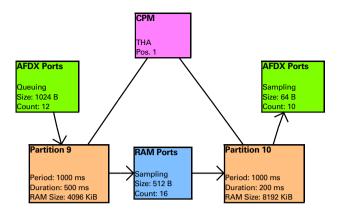

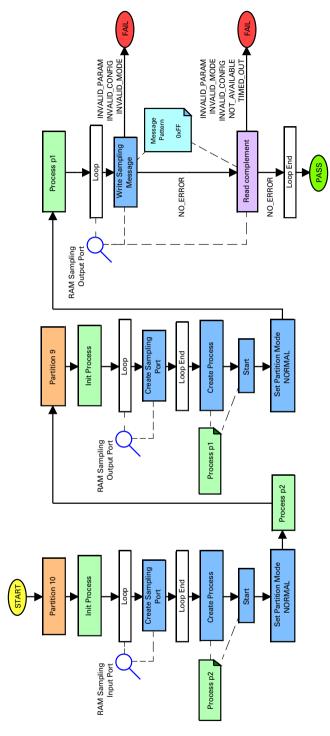

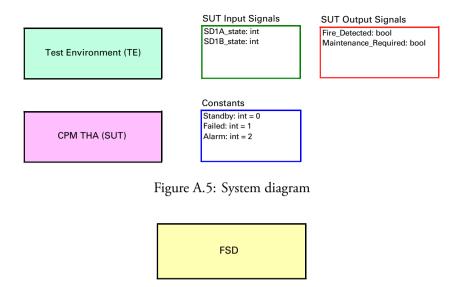

| A.5         | System diagram                      | 59 |

| A.6         | System Under Test component diagram | 59 |

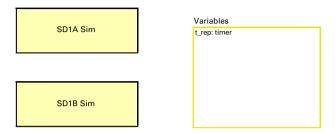

| <b>A.</b> 7 | Test Environment component diagram  | 70 |

|             | SD1 simulation component diagram    |    |

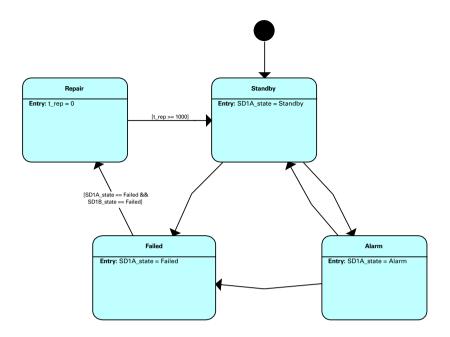

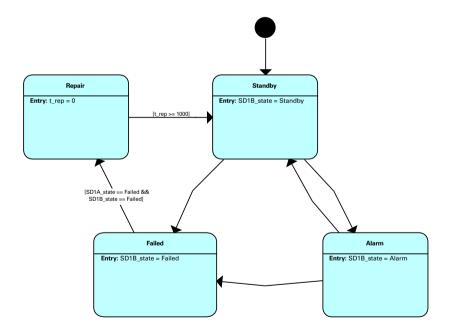

| A.9         | SD1A simulation statechart          | 71 |

| A.10        | SD1B simulation statechart          | 71 |

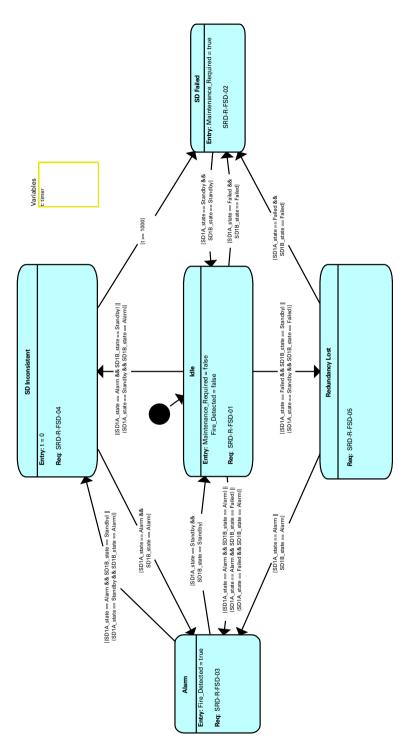

| A.11        | FSD application statechart          | 72 |

# **List of Tables**

| 2.1                                                | ARINC 653 communication methods                                                                                                                                                                                                                          |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1                                                | MERL metatype characters                                                                                                                                                                                                                                 |

| 5.1<br>5.2<br>5.3                                  | TTCN-3 Standard documents                                                                                                                                                                                                                                |

| 7.1<br>7.2<br>7.3<br>7.4                           | TACP Layer 1       67         TACP Layer 1 flags       68         TACP Layer 2       68         TACP Operations       69                                                                                                                                 |

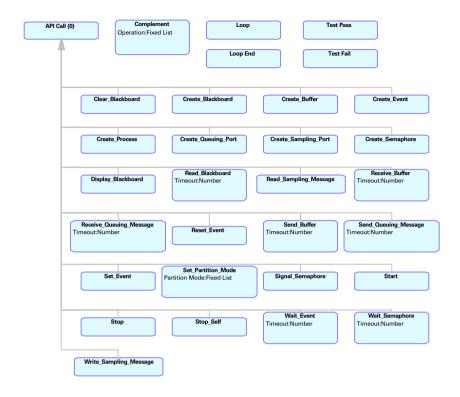

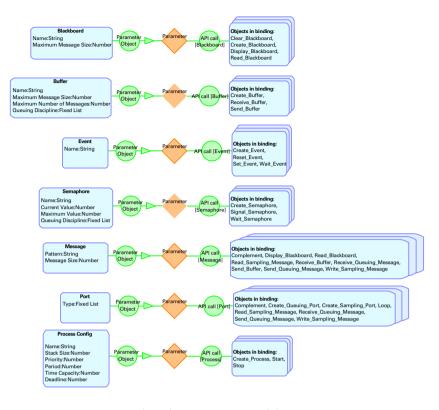

| 9.1.1<br>9.1.1<br>9.1.2<br>9.1.2<br>9.1.2<br>9.1.2 | Module       87         Partition       88         AFDX Ports       89         RAM Ports       90         Partition       91         Process Configuration       92         Process       92         Test Start       92         Test Pass/Fail       92 |

| 9.1.2<br>9.1.2<br>9.1.2<br>9.1.2                   | API Call 93 Complement 93 Message Pattern 94 Blackboard 94 Buffer 95                                                                                                                                                                                     |

| 9.1.2<br>9.1.2<br>9.1.2<br>9.1.2<br>9.1.3          | 2. Semaphore       95         2. Event       96         3. Port       96         3. Loop       97         4. Behaviour       97                                                                                                                          |

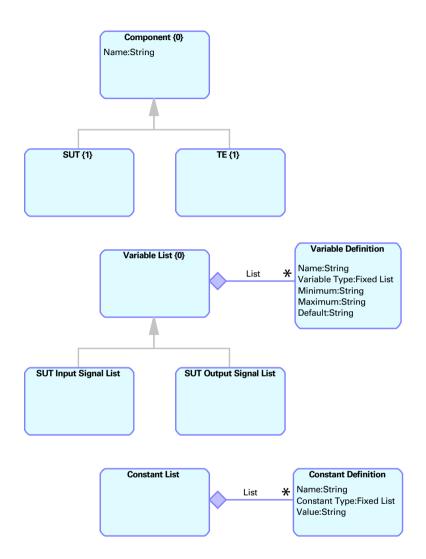

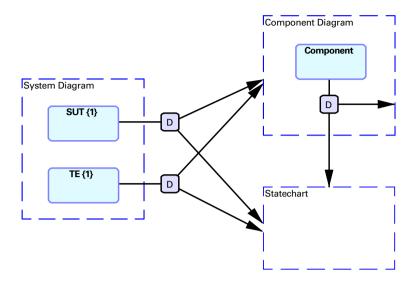

| 9.1.3<br>9.1.5                                     | Configuration                                                                                                                                                                                                                                            |

|                                                    |                                                                                                                                                                                                                                                          |

#### List of Tables

| 9.1.5 TE              |          |  |  |  |  |  |  |  |  | <br> |  | 100 |

|-----------------------|----------|--|--|--|--|--|--|--|--|------|--|-----|

| 9.1.5 Component .     |          |  |  |  |  |  |  |  |  | <br> |  | 100 |

| 9.1.5 Input Signals I | List     |  |  |  |  |  |  |  |  | <br> |  | 101 |

| 9.1.5 Output Signals  | s List . |  |  |  |  |  |  |  |  | <br> |  | 101 |

| 9.1.5 Variables List  |          |  |  |  |  |  |  |  |  | <br> |  | 102 |

| 9.1.5 Variable Defin  | ition .  |  |  |  |  |  |  |  |  | <br> |  | 102 |

| 9.1.5 Constants List  |          |  |  |  |  |  |  |  |  | <br> |  | 103 |

| 9.1.5 Constant Defin  | nition   |  |  |  |  |  |  |  |  | <br> |  | 103 |

| 9.1.5 Start Location  |          |  |  |  |  |  |  |  |  | <br> |  | 104 |

| 9.1.5 Stop Location   |          |  |  |  |  |  |  |  |  | <br> |  | 104 |

| 9.1.5 Location        |          |  |  |  |  |  |  |  |  | <br> |  | 105 |

| 9.1.5 Transition      |          |  |  |  |  |  |  |  |  | <br> |  | 106 |

CHAPTER

### Introduction

In today's world we find ourselves more and more surrounded by electronic devices. Laptop computers, smartphones, or satellite navigation systems are a part of our everyday life. They are useful tools and make our lives easier, provided they work properly. A malfunction of such a device is usually a mere nuisance.

On the other hand, electronic devices are employed in *safety-critical systems* like aircraft engine controllers, anti-lock braking systems, electronic signal boxes, and medical life-support systems. Here, a malfunction or failure has potentially catastrophic consequences and can result in loss of lives. Assuring the safety and reliability of such systems is therefore crucial.

In particular, the *Integrated Modular Avionics* (IMA) architecture provides an example of such a system from the aerospace domain. IMA modules can host crucial aircraft functions like flight control, fire and smoke detection, or braking control systems. A *partitioning* scheme allows for hosting of several aircraft functions safely on the same module. Apart from having numerous advantages, this architecture also comes with a higher level of integration and increased complexity. This makes the development of such systems an interesting and also very important research subject.

Domain-specific modelling (DSM) is a relatively new methodology that allows elements and concepts from a specific application domain to be used. In contrast to general-purpose modelling (e. g. UML), DSM is more intuitive in its application and allows a higher level of abstraction. This brings great advantages in usability as well as efficiency.

In *Model-based testing* (MBT), models are used as a means to specify or derive test cases. The goal is to generate executable test procedures automatically instead of writing them by hand. Models can represent nominal System Under Test (SUT) behaviour or desired testing strategies.

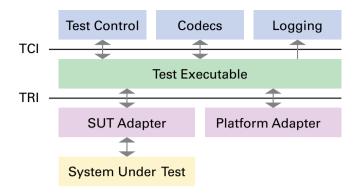

The *Testing and Test Control Notation Version 3* (TTCN-3) is a set of standards defining a language for test specification and the infrastructure of a runtime environment for the execution of tests. It is widely used in the area of communication testing and protocol testing. A major benefit of TTCN-3 is the *abstraction* it provides from concrete test environment hardware and interfaces.

Due to their complexity, testing of IMA modules requires considering different levels of module testing, from low-level *bare module tests* to *configured module tests* and *functional tests* (cf. section 2.4 for details).

#### 1.1 Goals

The main goal of this work is to provide a framework for model-based testing of Integrated Modular Avionics systems. The purpose of this framework is to provide the prospective IMA test engineer with a state-of-the-art toolbox that will support him during the design and execution of test suites for IMA-based systems.

#### 1.2 Main Contribution

In order to accomplish this goal, the following main contributions are presented in this dissertation:

- 1. A domain-specific modelling language specifically designed for the testing of IMA systems, called *IMA Test Modelling Language* (ITML)

- 2. A flexible and universal *Test Agent* (TA)

- 3. A TTCN-3-based test execution environment

The combination of these features constitutes a novel approach to IMA testing. They enable test designers to work on a higher level of abstraction, using elements of the application domain instead of concepts of a particular testing tool. They also allow them to specify test cases for bare and configured module tests in a very compact manner, without explicitly referring to the availability and distribution of system resources in the IMA module under test. A generator produces the concrete test procedure in TTCN-3 syntax. This procedure stimulates and controls distributed interactions between test agents on different partitions and modules. For this purpose, the generator evaluates both the test case specification and the IMA module configuration (which can also generated automatically under certain circumstances) and selects the concrete resources involved in compliance with the configuration.

For hardware/software integration tests with the application layer present in each IMA module which is part of the system under test (SUT), behavioural test models based on timed state machines can be used, and the generator

derives test cases, test data and test procedures from these models by means of a constraint solver.

A summary of parts of the research presented in this thesis has been published in [EP11].

#### 1.3 Related Work

Experiences in the field of bare and configured module testing result from earlier work in the VICTORIA research project [OH05, Ott07]. In this project, bare module tests were developed based on a library of formal Timed CSP specification templates [Sch00, Pel02]. Unfortunately, this approach requires both a substantial amount of manual programming effort as well as a deep understanding of CSP. As a result, domain experts without knowledge in the field of process algebras were unable to analyse the resulting test procedures. In contrast to that, the methodology presented here uses an intuitive graphic template formalism to describe patterns from which concrete test cases and test data can be derived and which are automatically converted into executable test procedures.

Moreover, the approach chosen in the VICTORIA project relied on specific test engine hardware and test execution software. Conversely, this work shows a method to achieve independence from specific test hardware by deploying a TTCN-3-based test environment [ETS]. The underlying techniques for model-based functional testing are described in more detail in [PVL11], where also references to competing approaches are given.

Domain-specific approaches to test automation are also promising in several other areas: In [Mew10], for example, Kirsten Mewes describes patterns for automated test generation in the railway control system domain, while in [Feu13], Johannes Feuser uses a domain-specific language to create an open model of ETCS. Timed Moore Automata (cf. [LP10]) can be used to model control logic of level crossing systems, on which model-checking and automatic test case generation can be performed. In [EH08] the authors describe a systematic approach for diagnosing errors in the context of hardware/software integration testing and explain this technique with an example from the avionics domain.

[PHL+11] gives an example of practical model-based testing efforts in the automotive domain, where in a collaborative effort from Daimler, Verified Systems, and University of Bremen, a benchmarking method on real-world models is proposed.

#### 1.4 Outline of this Document

This document is divided into four parts. The first part will familiarise the reader with the necessary background information concerning the topics covered in this dissertation. This includes an in-depth discussion of the applica-

tion domain as required for the next chapters as well as an introduction to the relevant methodologies and concepts as employed in the framework. General information on avionics systems and their development will not be discussed here, as this has already been done extensively, e. g. in [Ott07, ch. 1].

The second part provides an in-depth examination of the individual components that make up the model-based IMA testing framework. It describes the universal *IMA Test Agent* and its control protocol. The structure of the TTCN-3-based *test execution environment* is shown. Afterwards, the domain-specific modelling language for the testing of IMA systems, called *IMA Test Modelling Language*, is presented.

The third part provides an evaluation of the framework. It discusses usage examples, provides a comparison with other tools and approaches, and gives a comprehensive conclusion of the results elaborated in this thesis.

The fourth part provides a collection of detailed materials, including models and source code, for the individual components introduced in the second part.

# PART I

# **Background**

# **Integrated Modular Avionics**

The traditional *federated* aircraft controller architecture [Fil03, p. 4] consists of a large number of different, specialised electronics devices. Each of them is dedicated to a special, singular purpose (e. g. flight control, or fire and smoke detection) and has its own custom sensor/actuator wiring. Some of them are linked to each other with dedicated data connections. In the *Integrated Modular Avionics* (IMA) architecture this multitude of device types is replaced by a small number of modular, general-purpose component variants whose instances are linked by a high-speed data network. Due to high processing power each module can host several avionics functions, each of which previously required its own controller. The IMA approach has several main advantages:

- Reduction of weight through a smaller number of physical components and reduced wiring, thereby increasing fuel efficiency.

- Reduction of on-board power consumption by more effective use of computing power and electrical components.

- Lower maintenance costs by reducing the number of different types of replacement units needed to keep on stock.

- Reduction of development costs by provision of a standardised operating system, together with standardised drivers for the avionics interfaces most widely used.

- Reduction of certification effort and costs via incremental certification of hard- and software.

An important aspect of module design is *segregation*: In order to host applications of different safety assurance levels on the same module, it must be

ensured that those applications cannot interfere with each other. Therefore a module must support resource partitioning via memory access protection, strict deterministic scheduling and I/O access permissions. Bandwidth limitations on the data network have to be enforced as well.

The standard aircraft documentation reference for IMA is ATA chapter 42. The IMA architecture is currently in use in the Airbus A380, A400M, the future A350XWB, and Boeing 787 Dreamliner aircraft. Predecessors of this architecture can be found in so-called fourth-generation jet fighter aircraft like the Dassault Rafale.

#### 2.1 AFDX

A data network is required for communication between (redundant) IMA modules as well as other hardware. This role is fulfilled by the *Avionics Full DupleX Switched Ethernet* (AFDX) network. It is an implementation of the ARINC specification 664 [Aer09] and is used as high-speed communication link between aircraft controllers. It is the successor of the slower ARINC 429 networks [Aer04].

AFDX is based on 100 Mbit/s Ethernet over twisted-pair copper wires (IEEE 802.3u, 100BASE-TX). This means it is compatible with COTS Ethernet equipment on layers 1 and 2 (physical layer and link layer). Ethernet by itself is not suitable for real-time applications as its timing is not deterministic. Therefore AFDX imposes some constraints in order to achieve full determinism and hard real-time capability.

In AFDX, so called *Virtual Links* (VLs) are employed for bandwidth allocation and packet routing. Each VL has a 16-bit ID, which is encoded into the destination MAC address of each frame sent through this VL. For each VL, only one end system can send frames, while there can be one or more receivers (unidirectional multicast communication, similar to ARINC 429). AFDX switches use a pre-determined configuration to deliver frames based on their VL ID to a set of receiving end systems.

Each VL is allocated a part of the full bandwidth of an AFDX link. To that end, each VL has two attributes: a maximum frame length ( $L_{max}$ ) in bytes and a bandwidth allocation gap (BAG). The BAG value represents the minimum interval (in milliseconds) between two frames on that VL. Thus, the maximum usable bandwidth in bit/s of a VL can be calculated as:

$$b_{max} = L_{max} \cdot 8 \cdot 1000/BAG$$

End systems use a VL scheduler to ensure minimum latency and jitter for each VL.

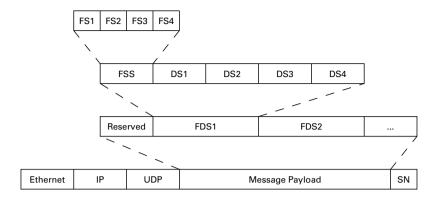

Figure 2.1 shows the composition of a complete AFDX frame. The UDP protocol is used on the transport layer, since protocols which rely on retransmission (e. g. TCP) are inadequate in a deterministic network. The message payload is organised into one or more Functional Data Sets (FDS). Each

Figure 2.1: AFDX frame

FDS comprises a functional status set (FSS) and up to four data sets (DS). The FSS is split into four functional status (FS) fields. Each FS field determines the validity of the data contained in a data set, similar to the SSM field of ARINC 429 labels. Data sets contain one or more primitive values, like integers, floats, or booleans.

In order to increase reliability, an aircraft data network consists of two independent switched networks. AFDX frames are sent on both networks. If no frame is lost, the other end systems will receive two frames. In order to identify matching frames sent over the redundant links, the message payload is followed by a sequence number field. Of two frames received on different networks with an identical sequence number, only the first is passed up the protocol stack.

#### 2.2 ARINC 653

As indicated before, an IMA module can host multiple avionics functions. The interface between avionics applications and the module's operating system conforms to a standardised API which is defined in the ARINC specification 653 [Aer05].

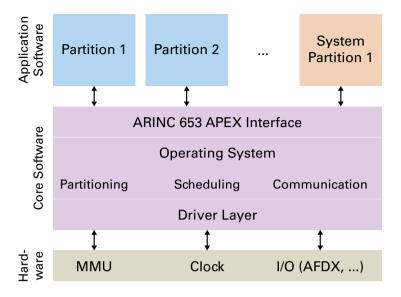

The system architecture of an IMA module is depicted in figure 2.2. A real-time operating system kernel constitutes the central component. It uses a driver layer for access to the module's I/O hardware (either solely AFDX, or other interfaces like Discretes, CAN, and ARINC 429 buses as well, depending on module type) [Aer05, p. 11].

Figure 2.2: IMA module system architecture

#### 2.2.1 Partitioning

In order to guarantee the same isolation of avionics functions residing on a shared module as a federated architecture would provide, it is the operating system's responsibility to implement a concept called *partitioning*. According to [RTC01], a partitioning implementation should comply with the following requirements:

- A software partition should not be allowed to contaminate another partition's code, I/O, or data storage areas.

- A software partition should be allowed to consume shared processor resources only during its period of execution.

- A software partition should be allowed to consume shared I/O resources only during its period of execution.

- Failures of hardware unique to a software partition should not cause adverse effects on other software partitions.

- Software providing partitioning should have the same or higher software level<sup>1</sup> than the highest level of the partitioned software applications.

<sup>&</sup>lt;sup>1</sup>as defined in [RTC92]

|                 | Intra-partition    | Inter-partition |

|-----------------|--------------------|-----------------|

| Queuing         | Buffer             | Queuing Port    |

| Non-Queuing     | Blackboard         | Sampling Port   |

| Synchronisation | Semaphore<br>Event | _               |

Table 2.1: ARINC 653 communication methods

On the IMA platform, a partition is a fixed set of the module's resources to be used by an avionics application. In particular, each partition is assigned a portion of the module's memory. The operating system ensures that other partitions can neither modify nor access the memory of a partition, similar to memory protection in a UNIX-like operating system. Each partition also receives a fixed amount of CPU time. The operating system's scheduler ensures that no partition can spend CPU time allotted to another partition [Aer05, p. 13].

Two kinds of partitions reside on a module:

**Application partitions** contain application code that makes up (part of) the implementation of an avionics function.

**System partitions** on the other hand provide additional module-related services like data loading or health monitoring.

Inside a partition there can be multiple threads of execution, called *processes*. Similar to POSIX threads, all processes within a partition share the resources allocated to the partition. Each process has a priority. A process with a higher priority pre-empts any processes with a lower priority. ARINC 653 defines a set of states a process can be in (Dormant, Waiting, Ready, Running) as well as API functions for process creation and management [Aer05, pp. 18–25].

#### 2.2.2 Communication

The operating system must provide a set of different methods of communication. All of them fall into either of two categories: intra-partition or interpartition communication. Intra-partition communication always happens between processes of the same partition, while inter-partition communication happens between processes of different partitions or even partitions on different modules. Table 2.1 provides an overview of different communication methods.

A *buffer* is a communication object used to send or receive messages between processes in the same partition. The messages are queued in FIFO

order. Messages can have variable size, but must not exceed the maximum message size specified at buffer creation. The maximum number of messages a buffer can hold is defined at buffer creation. When a process reads from a buffer, the oldest message is removed from it and returned to the process [Aer05, p. 36]. A *blackboard* is a similar communication object, but it does not queue messages. Instead, each new message overwrites the current one. A message can be read an arbitrary number of times by any process of the partition, until it is either cleared or overwritten [Aer05, p. 37].

Semaphores and events are communication objects that cannot be used to transport messages, but instead serve as synchronisation objects for processes. A semaphore has a counter. The operating system provides functions to increment and decrement the counter. If a process tries to decrement the counter while it is already at zero, the process is forced to wait until another process increments the counter [Aer05, p. 37]. An event object has a list of processes waiting for the event. As soon as the event is set to its signalled state, all waiting processes become ready again [Aer05, p. 38].

Sampling ports and queuing ports are used for inter-partition communication. A port is unidirectional (either Source or Destination). Messages sent over a port can have variable size, but must not exceed the defined maximum message size of the port. Ports as well as the communication channels they are connected to are defined at module configuration time. The application cannot influence the routing of messages at runtime. Similar to a buffer, a queuing port stores incoming messages up to a defined maximum number. Each message is removed from the port as it is read. When writing multiple messages to a queuing port, all of the messages will be sent in FIFO order. A sampling port, on the other hand, does not queue multiple messages, neither incoming nor outgoing. Instead, only the latest message is kept [Aer05, pp. 31–35].

#### 2.2.3 Initialisation

All the aforementioned communication objects as well as processes cannot be created during normal operation of a partition. Instead, they must be created during a special initialisation phase. During this phase an initialisation process is executed. Its task is the creation and initialisation of all required resources (processes, ports, buffers, semaphores, etc.) for the partition. Only when this phase is complete and the partition has switched to normal operation mode will the other processes start their execution. For that purpose ARINC 653 describes a set of states a partition can be in, as well as API functions for partition management [Aer05, pp. 15–17].

#### 2.3 Module Configuration

As indicated previously, an integral part of an IMA module is its configuration. In order to be suitable as a general-purpose platform for avionics functions it must be highly configurable to its specific scope of application. This makes the process of creating a configuration a matter of high complexity. In particular, multiple roles are involved in the process: Global module configuration data is managed by the module integrator<sup>2</sup>, while partition-specific configuration data are provided by the function suppliers<sup>3</sup> responsible for the implementation of each avionics function.

A complete module configuration consists of a set of data table files—a socalled Interface Control Document (ICD). The module integrator processes the ICD with a configuration tool to generate a binary representation, which is then loaded into the module along with the application software.

The global part of the configuration consists of tables covering the following module-global aspects:

- Physical RAM/ROM sizes and addresses

- CPU cache settings

- Scheduling: Minor Frame duration and number

- Health Monitoring recovery actions

- AFDX VL definitions

- Properties of other I/O hardware (if available)

Each partition has its own set of partition-specific configuration tables. They cover the following aspects of partition configuration:

- Memory allocation (code, data)

- Scheduling: Time slices assignment

- Definition of AFDX messages

- Definition of sampling and queuing ports

- Assignment of ports to communication channels (module-internal or via AFDX)

- Definition of messages for other message-based I/O hardware (if available, e. g. CAN or ARINC 429 bus)

The properties defined in partition-specific configuration are valid for one partition only and cannot have influence on other partitions. As there are cross-references between global and partition-specific configuration tables, it is the module integrator's responsibility to keep the overall configuration consistent and valid (at best using appropriate tool support).

<sup>&</sup>lt;sup>2</sup>The airframer

<sup>&</sup>lt;sup>3</sup>The airframer's subcontractors

#### 2.4 Testing IMA Systems

As described above, IMA components have a complex configuration. The fact that it covers many aspects like partitioning, resource allocation, scheduling, I/O configuration, network configuration and internal health monitoring makes the configuration an integral part of the system, and it must be taken into consideration during verification and certification [RTC92, RTC05]. As a result of these considerations, different levels of testing for IMA modules have been defined in a previous research project [Ott07]:

Bare Module Tests are designed to test the module and its operating system at API level. The test cases check for correct behaviour of API calls, while robustness test cases try to violate segregation rules and check that these violation efforts do not succeed. Bare module tests are executed with specialised module configurations designed for these application-independent test objectives. The application layer is substituted by test agents that perform the stimulations on the operating system as required by the testing environment and relay API output data to the testing environment for further inspection.

Configured Module Tests do not focus on the module and its operating system, but are designed to test application-specific configurations meant to be used in the actual aircraft. The test cases check that configured I/O interfaces are usable as defined. Again, the application layer is replaced by test agents.

**Functional Tests** run with the actual application layer integrated in the module and check for the behavioural correctness of applications as integrated in the IMA module.

#### 2.5 Research Project SCARLETT

SCARLETT (SCAlable & ReconfigurabLe elEctronics plaTforms and Tools) is a European research and technology project [SCA]. With 38 partner organisations (airframers, large industrial companies, SMEs and universities) it is a large-scale integrating project funded under the Seventh Framework Programme [FP7] of the European Commission, submitted to the Transport Call under the Area of Activity 7.1.3 – Ensuring Customer Satisfaction and Safety (Level 2). SCARLETT is a successor to several earlier European research projects in the field of avionics, like PAMELA, NEVADA and VICTORIA. Its goal is the development of a new generation of IMA (IMA2G) with increased scalability, adaptability and fault-tolerance, called *Distributed Modular Electronics (DME)*.

The DME concept aims at the separation of processing power from sensor/ actuator interfaces, thereby reducing the number of different component

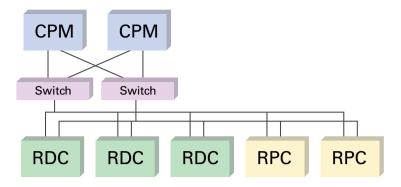

Figure 2.3: DME Architecture

types to a minimum. This also makes DME suitable for a wider range of aircraft types by giving system designers the possibility to scale the platform according to required hardware interfaces and computing power. Figure 2.3 shows an example of a network of components: two Core Processing Modules (CPM), three Remote Data Concentrators (RDC), and two Remote Power Controllers (RPC) linked via two redundant AFDX networks. The CPM components provide the computing power and host the avionics applications, but apart from AFDX they do not provide any I/O hardware interfaces. Instead, the RDC and RPC components provide the required number of sensor/actuator and bus interfaces.

The project also investigates ways of increasing fault tolerance through different reconfiguration capabilities, for example transferring avionics functions from defective modules to other, still operative modules. Finally, the design of a unified tool chain and development environment has led to improvements of the avionics software implementation process.

The research activities and achievements presented in this dissertation are the results of the author's work in the SCARLETT project, in particular in the work packages WP2.4 (Toolset & Simulators Development) and WP4.2 (I/O Intensive Capability Demonstration).

# **Domain-specific Languages**

Domain-specific Languages (DSLs) are programming languages which can be employed to solve problems of a particular application domain. Some well-known examples for DSLs are:

- SQL is supported by almost every database system to query, add or delete records.

- Regular Expressions are widely used to describe regular languages<sup>1</sup>. Implementations provide a means of matching (recognising) strings of text.

- VHDL is a standardised hardware description language employed for integrated circuits design.

What these languages have in common is that they were designed for a single purpose only. In contrast to general-purpose languages like C, Pascal, or Perl, each one of them cannot be used as a replacement for the others. While DSLs are not capable of solving every problem, a good DSL excels at solving problems of its domain.

A DSL employs concepts of its application domain. Its syntax and semantics are based on *domain knowledge*. For example, keywords and operations are named after objects or principles that occur in the problem domain. It also means that, while it is perfectly possible to write syntactically correct programs in general-purpose languages which do not make any sense on a semantic level, the grammar rules of a DSL can forbid such programs because the domain knowledge of what makes sense in a program is available at language design time.

<sup>&</sup>lt;sup>1</sup>Although many regular expressions libraries provide features that exceed the expressive power of regular languages.

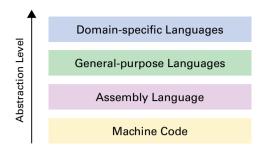

Figure 3.1: Comparison of abstraction levels

Experience shows that working on a higher level of abstraction provides an increase in productivity. Using a DSL means working on a higher level of abstraction compared to working with a general-purpose language (cf. figure 3.1). If the level of abstraction is raised high enough and no concepts of general-purpose programming are left in a DSL, simple knowledge of the domain is sufficient and no general-purpose programming skills are required any more.

However, the introduction of a DSL can only be profitable if the initial effort invested in its development can later be saved due to increased productivity. This means, a DSL can be employed successfully if a well-defined problem domain exists and the problems to be solved require changes to be made frequently to the program, but only infrequently to the DSL or its tools.

DSLs fall into two categories: internal and external DSLs. An internal DSL is embedded into a host language. It can, for example, make use of the host language's control flow features (e. g. loops) and data types. An external DSL, on the other hand, is built from scratch. Anything that is required must be defined anew. While this requires more effort during language design, it makes the language more flexible and expressive.

Further examples and information on DSLs can be found, for example, in [FP10].

## 3.1 Domain-specific Modelling

The ideas and principles of using DSLs instead of general-purpose languages can be applied to modelling as well: Instead of using a general-purpose modelling language (e. g. UML), a graphical domain-specific language, called a domain-specific modelling language (DSML), can be employed. A DSML uses graphical representations of objects and concepts from its designated problem domain. Therefore, models built from DSMLs can easily be understood, validated, and even created by domain experts without requiring

Figure 3.2: DSM Workflow

in-depth knowledge of software engineering principles [KT08]. Adequate tool support makes DSMLs intuitive to use and provides a much shallower learning curve than text-based DSLs (and, of course, general-purpose languages).

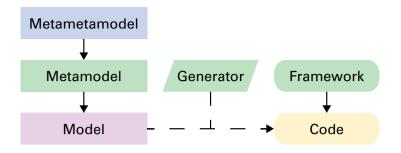

Models built from a DSML must adhere to the language syntax. In order to clearly define the syntax of a DSML, the language needs a formal definition. The language definition of a DSML is called a *metamodel*. The language in which a metamodel is defined is called a *meta-metamodel*. Figure 3.2 shows their relationship (cf. [KT08, ch. 4]).

The meta-metamodel is embedded in the DSM tool that is used to design the language. The language designer uses its features to build the metamodel. The metamodel defines all objects, their properties, and relationships that may occur in models of a particular DSML.

When the language designer has completed the metamodel, domain experts can start building models in the new language. They are supported in their task by the DSM tool, as the tool will make sure that only valid models (i. e. conforming to the metamodel) can be built.

Ultimately, the goal of modelling is the generation of code. To that end, apart from the metamodel, the language designer also provides a domain-specific *generator*. It is the generator's task to provide a mapping from the models of the language to the concrete code that can be compiled or interpreted in the target environment. The code generally relies on a domain-specific *framework*, for example a library of functions and some initialisation routines. Well-established principles of operation can be implemented here and therefore do not have to be modelled explicitly in the DSML. The framework is supplied together with the generator by the language designer.

### 3.2 MetaEdit+

The number of users of a DSML can be potentially very small, depending on the problem domain. It could, for example, be just a dozen employees working with a language used only in-house. It would be rather expensive to develop a complete set of tools specifically for each of those languages. Instead, a number of tools exist that support the design and usage of arbitrary domain-specific modelling languages. Apart from several Eclipse-based solutions, one of them is MetaEdit+ by MetaCase [MC]. MetaEdit+ was chosen for this work due to its ease of use as well as previous positive experiences.

### 3.2.1 GOPPRR

MetaEdit+ is based on the meta-metamodel "GOPPRR". Like its predecessors OPRR and GOPRR [Kel97, p. 239ff], it was designed specifically for the purpose of metamodelling. The name is an acronym of the elements the meta-metamodel provides. These elements, called metatypes, are used in MetaEdit+'s metamodelling mode to build metamodels, i. e. new DSMLs.

- **Graphs** are individual models, shown as diagrams. They consist of objects, relationships, and roles. Bindings define how objects can be connected via relationships and in which roles.

- **Objects** are the main elements of graphs. An object has a visual representation and a number of properties. The values of its properties can influence the visual representation of an object.

- **Properties** are attributes characterising objects, graphs, roles, or relationships. Their values are of a pre-defined type (text string, integer, enumeration value, etc.)

- Ports are optional connection points of an object to which a role can connect. Each port of an object has its own visual representation and position on the object. If an object has no ports, a role can connect to anywhere on the object (provided an appropriate binding rule exists).

- Roles connect objects into relationships. Each role can have its own visual representation (e. g. arrow head).

- **Relationships** connect two or more objects via a line and possibly additional visual elements. Each kind of relationship has a specific set of roles, and each role can have its own cardinality.

### 3.2.2 Metamodelling

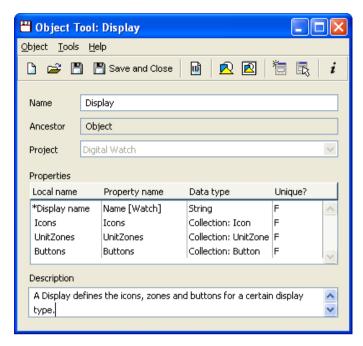

MetaEdit+ provides a metamodelling tool for each of GOPPRR's elements. A typical approach would be to start with the Object tool (figure 3.3) and create a new object type for each kind of object, giving them appropriate names and descriptions, then to create properties and add them to the objects. The next step would be to define relationships and roles using the respective tools. Finally, the Graph Tool is used to create graph types. This

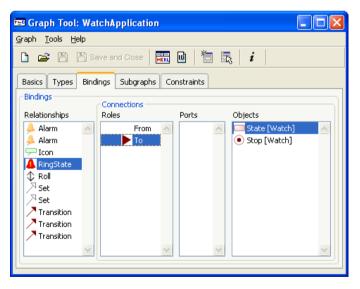

includes basic properties like a name and graph-level properties as well as the definition of which types of objects, relationships, and roles may appear in the graph. The most important part, however, is the definition of *bindings* [Kel95]. A binding stores the connection information of a relationship (it is not part of the relationship itself). More than one binding can be defined for each type of relationship. A binding B can be defined as a tuple consisting of a relationship type r and a connection set C:

```

\begin{split} B &= (r,C) \\ C &\subset (L \times R \times P \cup \{\bot\} \times O) \\ L &= \{(l_0,l_1) \mid l_0 \in \mathbb{N}, \ l_1 \in \mathbb{N}^+ \cup \{\infty\}, \ l_0 \leq l_1\} \end{split}

```

with r a relationship type

l<sub>0</sub> lower bound of cardinality

$l_1$  upper bound of cardinality

R set of all role types

P set of all port types

⊥ the "empty" port

O set of all object types

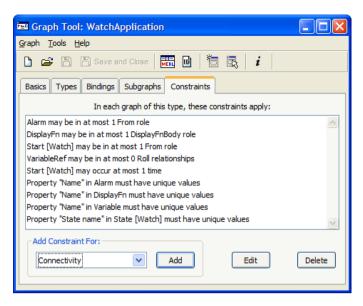

This makes it possible to precisely define constraints regarding the types of objects that can be in relationships with other object types as well as their cardinalities (figure 3.4). The Graph Tool provides two additional features: It is possible to define *nesting* of graphs, i. e. objects in a graph can decompose into graphs of the same or another type. Finally, graph-level constraints can be defined. Connectivity constraints limit the number of roles or relationships an object may be in. Occurrence constraints define a maximum number of occurrences for an object type. Uniqueness constraints require that a specific property is unique amongst all objects of a type in the graph (figure 3.5).

MetaEdit+ also provides a Symbol Editor. This tool is used to design the graphical representation of objects, ports, roles, and relationships. The values of object/port/role/relationship properties can be used as text elements. The visibility of certain parts of a symbol can be made to depend on property values.

### 3.2.3 Modelling

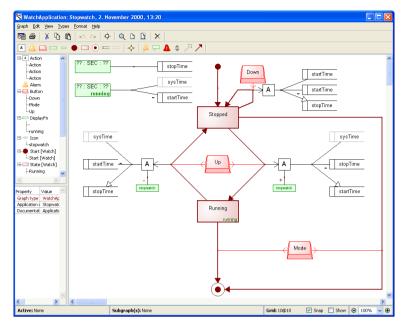

When the metamodelling is completed, the domain experts can use Meta-Edit+ in its modelling mode in order to create models. For each type of graph defined in the metamodel, MetaEdit+ provides a dedicated Diagram Editor (figure 3.6). Only the object and relationship types applicable to the

Figure 3.3: MetaEdit+ Object Tool

Figure 3.4: MetaEdit+ Graph Bindings

Figure 3.5: MetaEdit+ Graph Constraints

particular graph are made available to the modeller. Objects appear in their custom, domain-specific representation. Object properties can be edited via customised dialogue boxes. Objects can only be combined into relationships according to the defined bindings; the editor does not permit invalid connections. Compliance with graph-level constraints is guaranteed as well.

### 3.2.4 Generators

The last step is the generation of code based on the models the domain experts created. As described before, generators are required for this task. MetaEdit+supports the generation of code and other outputs via its integrated generator language: MERL (MetaEdit+ Reporting Language). MetaEdit+ provides an editor tool which is used to write MERL generators for code, generator-based text fields in symbols, and object identifiers.

In order to better understand MERL-based generators used in the following parts of this document, a quick overview of MERL syntax will be given here.

MERL was designed to navigate through design models and extract information from model elements. It is stack-based, with the current model element at the top of the stack. When a generator starts, the initial object on the stack is the graph that the generator is given to process. Most generators operate by looping over all or a subset of objects of a graph. This is possible with a foreach loop:

Figure 3.6: MetaEdit+ Diagram Editor

```

foreach .State

{

:name; newline

}

```

The foreach loop starts on the graph level and iterates over all objects of the given type, in this case all objects of type State<sup>2</sup>. Inside the loop body, the current State event becomes the top element on the object stack and it is possible to access its properties. In this case, the name property of each State object in the graph is output, followed by a newline.

From the current element it is possible to navigate through bindings to other objects:

```

do ~From>Link~To.State

{

:name; newline

}

```

Assuming the current object is a State (for example by placing this code into the loop body of the first example), the do loop iterates through all From roles of the current object which are part of a relationship of type Link and visits any State objects connected via a To role to that relationship. These,

<sup>&</sup>lt;sup>2</sup>Assuming such an object type was defined in the metamodel.

Table 3.1: MERL metatype characters

| Character | Metatype     |

|-----------|--------------|

| •         | Object       |

| :         | Property     |

| #         | Port         |

| ~         | Role         |

| >         | Relationship |

|           |              |

in turn, become the current objects for the body of the do loop. In other words, this code example outputs the names of all states that can be reached from the current state.

The strange-looking special characters prefixing the identifiers in the two examples serve a specific purpose: The character defines the kind of metatype that the name refers to (cf. table 3.1).

Loops can be combined with filtering and ordering expressions:

This example would loop over all atom objects which are radioactive, in order of ascending atomic number. Besides loops, if-else statements can be used as well. And, similar to function calls, a generator can also call subgenerators.

It is also important to note that apart from the logical connections between objects and relationships, in MERL it is also possible to obtain information about their positions and layout. You can retrieve an object's x and y coordinates as well as its width and height. Objects that are placed inside the area of the current object can be obtained via the contents keyword. Similarly, containers retrieves the set of all objects that contain the current object.

Since it is possible to access all information contained in a model, it quickly becomes obvious that MERL provides a very powerful and flexible approach to generating code and other data outputs from GOPPRR-based models. For a complete description of MERL and its syntax, see [MWUG, ch. 5].

# **Model-based Testing**

Model-based testing (MBT) is a process whose purpose is the generation of executable test procedures from models. Instead of writing tests manually, test cases are derived from models somehow related to the SUT [ZSM11b]. In this way MBT provides great potential for test automation. Consequently, as several studies show, the application of model-based testing results in a reduced effort and cost for testing activities [PPW+05, Bin12].

Two different kinds of models can be used as a basis for model-based testing: *System models* represent the desired behaviour of the SUT. They are abstractions of the actual SUT implementation. *Test strategy models*, on the other hand, are models that are created separately from a system model and describe some explicit testing strategy.

Apart from test selection criteria (e. g. structural model coverage, data coverage, requirements coverage or formal test case definitions), [ZSM11b] describes different test generation algorithms:

Random input generation is the simplest method: Random values from the input space of a system are selected and used as inputs. Unfortunately, the time it takes to achieve acceptable model coverage is not predictable.

**Graph coverage** involves graph search algorithms for finding paths that include all nodes or arcs (e. g. Chinese Postman algorithm) in order to reach sufficient model coverage.

**Model checking** is used to verify properties of a system. If test cases are specified as reachability properties, a model checker is able to generate traces that eventually reach a given state or transition.

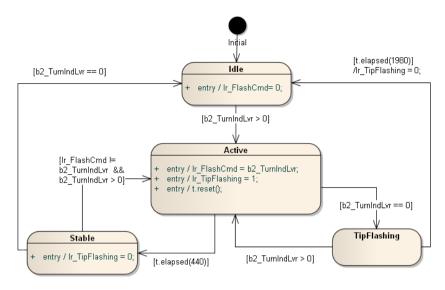

Figure 4.1: Example model: Turn indicator (UML). (Source: http://mbt-benchmarks.org/)

Symbolic execution involves the execution of a model (evaluation of expressions) not with actual, but with sets of input values. The result is a symbolic trace that can be instantiated with concrete values. Test cases can be specified as constraints that have to be respected during the symbolic execution.

In model-based testing, two different modes of test execution are possible: *Online testing* involves the evaluation of the model during the actual test execution. Here, the MBT tool interacts directly with the SUT. By contrast, the generation of "conventional" test procedures by an MBT tool and the execution of those procedures in a separate step is called *offline testing*.

As an example, figure 4.1 shows part of a real-world system model of a reactive system, in this case a subset of the functionality of a turn indicator control system is modelled as a UML [OMG11] state machine diagram (a variant of Harel Statecharts [Har87]). A state machine diagram consists of *states* (Idle, Active, Stable, TipFlashing), one of which is the initial state. Each state represents a qualitative aspect of the system's state space. *Extended state variables* capture quantitative aspects of the state space. Their existence avoids an explosion of the number of states in systems larger than any trivial examples. States can have entry and exit actions (lr\_FlashCmd = 0). States are linked by *transitions*. Each transition can have *guard conditions* (b2\_TurnIndLvr == 0) which must be satisfied for the transition to be taken, and it can also have *actions* (lr\_TipFlashing = 0). Guards and actions can be expressions over extended state variables as well as external

inputs and outputs of the system. This example models normal direction indication as well as "tip flashing" (lane change indicator).

Test case generation from such a model requires the ability to solve reachability problems [Huill, p. 30]. In order to travel a path along state machine transitions to reach a given target state, the guard conditions along this path represent constraints that must be solved. The solution is taken as a sequence of inputs to the SUT. The actions defined along the path in the model contain the observable outputs that must be checked by the generated test procedure in order to determine the test verdict.

An important aspect that must be noted is the fact that tests generated from models have the same level of abstraction as the models themselves. As a consequence, implementation details not covered in the model cannot be tested automatically.

For a more exhaustive introduction to model-based testing in the context of embedded systems, refer to [ZSM11a, UL07]. For more information on automated test case generation, see [LP10, Wei10, PVL11, Pel13].

## TTCN-3

The Testing and Test Control Notation Version 3 (TTCN-3) is a language designed for writing test specifications. It is based on the Tree and Tabular Combined Notation (TTCN, TTCN-2). While its predecessors were used mostly in telecommunication systems testing, TTCN-3 was developed to be a universal test language. Among its application areas are protocol testing (IPv6, GSM, and UMTS) and its use as a test environment for AUTOSAR [AUT] (a system architecture similar to IMA designed for the automotive domain).

TTCN-3 has been developed and standardised by the Methods for Testing and Specification Technical Committee (TC-MTS) of the European Telecommunications Standards Institute (ETSI). The standard itself is split across several documents, each covering different aspects of TTCN-3. Table 5.1 shows the most important documents. Other documents define alternative representations or extensions to the language. All documents are freely available from ETSI's TTCN-3 website [ETS].

Table 5.1: TTCN-3 Standard documents

| Document No. | Description           | Reference |

|--------------|-----------------------|-----------|

| ES 201 873-1 | Core Language         | [ETS09a]  |

| ES 201 873-4 | Operational Semantics | [ETS09b]  |

| ES 201 873-5 | Runtime Interface     | [ETS09c]  |

| ES 201 873-6 | Control Interface     | [ETS09d]  |

Table 5.2: TTCN-3 built-in simple types

| Name        | Description                       |

|-------------|-----------------------------------|

| boolean     | Truth values (true, false)        |

| integer     | Integral values of arbitrary size |

| float       | floating point values             |

| verdicttype | Test verdicts (none, pass,        |

|             | inconc, fail, error)              |

Table 5.3: TTCN-3 built-in string types

| Name                 | Description                        |

|----------------------|------------------------------------|

| charstring           | ASCII characters                   |

| universal charstring | Unicode characters                 |

| bitstring            | binary digits (arbitrary number)   |

| hexstring            | binary digits (multiple of 4 bits) |

| octetstring          | binary digits (multiple of 8 bits) |

### 5.1 Language Syntax

Test procedures are written in the TTCN-3 core notation [ETS09a]. This language, although designed specifically for testing, bears many similarities to common programming languages. For example, TTCN-3 provides a strong type system with many built-in types. Table 5.2 shows a list of simple types. New types can be created via aliasing and subtyping, e. g. by constraining an integer type to a range of values [WDT+05, pp. 127–132].

TTCN-3 provides several kinds of string types, for character as well as binary data. Their names are listed in table 5.3. Subtypes of strings can be created by restricting the allowed set of characters and by limiting the string length.

Similar to other languages, it is possible to declare user-defined types. These can be enumerations, records, unions, or sets [WDT+05, pp. 139–150]. While a record is equivalent to a struct type as known from C, a set is similar to them, but the order of its elements does not matter. Another specific feature is that records and sets can have optional elements. An optional element is not required to have an actual value. It is also possible to define lists and arrays of types. While the size of arrays is determined at compile time, the number of elements in a list can change dynamically at runtime. It is, however, possible to define list types with length constraints (similar to string lengths).

There is no implicit type conversion in TTCN-3. If a value of one type shall be used with a value of another type, one of them must be converted explicitly, for example using int2float or float2int. Variables are declared using the var keyword. Declarations can be at any scope level except at the top level. Therefore, global variables are not allowed<sup>1</sup>. Similarly, constants can be defined with the const keyword.

A speciality of TTCN-3 is its template system [WDT+05, pp. 173–192]. A template defines one or more values of a specific type. Templates are used when sending and receiving messages. They can define the expected contents of a message, e. g.:

```

type record SomeResponse {

integer errorcode;

charstring explanation;

};

template SomeResponse myTmpl := {

errorcode := (100, 200, 300),

explanation := ?

};

```

This defines a template myTmpl of the record type SomeResponse. The template matches any actual records that have an error code of 100, 200, or 300. The question mark implies that any (empty or non-empty) string is accepted in the explanation field.

Functions in TTCN-3 are defined using the function keyword. They can have a list of input and output parameters and a return value. A simple example function might look like this:

```

function myAdd(in int i, in float f) return float {

var float result;

result := int2float(i) + f;

return result;

}

```

Functions contain statements as commonly known from C or Pascal. Apart from assignments (:=) there are arithmetic (+, -, \*, /, mod, rem), relational (==, <, >, !=, >=, <=), logical (not, and, or, xor), and string (&, <<, >>, <@, >@) operators. for and while loops as well as if-else statements can be used just like in C.

One special statement is TTCN-3's alt statement [WDT+05, pp. 55–59]. It is used to provide a choice between several (blocking) operations. A typical example would look like this:

```

alt {

[] port1.receive(someData) {

```

<sup>&</sup>lt;sup>1</sup>This restriction avoids problems with distributed test components.

```

doSomething();

};

[] port2.receive(otherData) {

doSomethingElse();

};

[] myTimer.timeout {

setverdict(fail);

};

}

```

In this case, execution would block until data can be received from ports port1 or port2, or until the timer myTimer expires. someData as well as otherData would be templates (see above) that define the acceptable types and values to be received. In each case, execution would continue in the adjacent block.

As indicated in the previous example, TTCN-3 provides a timer mechanism. Each timer must be declared before use. Afterwards, it can be started with a specified timeout value. Then it can either be stopped (i. e. cancelled), or the timer creates a timeout event. For example, in order to create a delay of two time units, the following code might be used:

```