Large-Scale Parallel State Space Search Utilizing Graphics Processing Units and Solid State Disks

## Dissertation

zur Erlangung des Grades eines

Doktors der Naturwissenschaften

der Technischen Universität Dortmund an der Fakultät für Informatik

> von Damian Sulewski

> > Dortmund 2011

Tag der mündlichen Prüfung:

Dekanin: Pro Gutachter: Pro

Prof. Dr. Gabriele Kern-Isberner Prof. Dr. Stefan Edelkamp Prof. Dr. Bernhard Steffen

Gewidmet meiner Familie

v

vi

## Abstract

The evolution of science is a double-track process composed of theoretical insights on the one hand and practical inventions on the other one. While in most cases new theoretical insights motivate hardware developers to produce systems following the theory, in some cases the shown hardware solutions force theoretical research to forecast the results to expect.

Progress in computer science rely on two aspects, processing information and storing it. Improving one side without touching the other will evidently impose new problems without producing a real alternative solution to the problem. While decreasing the time to solve a challenge may provide a solution to long term problems it will fail in solving problems which require much storage. In contrast, increasing the available amount of space for information storage will definitively allow harder problems to be solved by offering enough time.

This work studies two recent developments in the hardware to utilize them in the domain of graph searching. The trend to discontinue information storage on magnetic disks and use electronic media instead and the tendency to parallelize the computation to speed up information processing are analyzed.

Storing information on rotating magnetic disk has become the standard way since a couple of years and has reached a point where the storage capacity can be seen as infinite due to the possibility of adding new drives instantly with low costs. However, while the possible storage capacity increases every year, the transferring speed does not. At the beginning of this work, solid state media appeared on the market, slowly suppressing hard disks in speed demanding applications. Today, when finishing this work solid state drives are replacing magnetic disks in mobile computing, and computing centers use them as caching media to increase information retrieving speed. The reason is the huge advantage in random access where the speed does not drop so significantly as with magnetic drives.

While storing and retrieving huge amounts of information is one side of the medal, the other one is the processing speed. Here the trend from increasing the clock frequency of single processors stagnated in 2006 and the manufacturers started to combine multiple cores in one processor. While a CPU is a general purpose processor the manufacturers of graphics processing units (GPUs) encounter the challenge to perform the same computation for a large number of image points. Here, a parallelization offers huge advantages, so modern graphics cards have evolved to highly parallel computing instances with several hundreds of cores. The challenge is to utilize these processors in other domains than graphics processing. One of the vastly used tasks in computer science is search. Not only disciplines with an obvious search but also in software testing searching a graph is the crucial aspect. Strategies which enable to examine larger graphs, be it by reducing the number of considered nodes or by increasing the searching speed, have to be developed to battle the rising challenges. This work enhances searching in multiple scientific domains like explicit state Model Checking, Action Planning, Game Solving and Probabilistic Model Checking proposing strategies to find solutions for the search problems.

Providing an universal search strategy which can be used in all environments to utilize solid state media and graphics processing units is not possible due to the heterogeneous aspects of the domains. Thus, this work presents a tool kit of strategies tied together in an universal three stage strategy. In the first stage the edges leaving a node are determined, in the second stage the algorithm follows the edges to generate nodes. The duplicate detection in stage three compares all newly generated nodes to existing once and avoids multiple expansions.

For each stage at least two strategies are proposed and decision hints are given to simplify the selection of the proper strategy. After describing the strategies the kit is evaluated in four domains explaining the choice for the strategy, evaluating its outcome and giving future clues on the topic.

viii

## Acknowledgments

In most cases a thesis would not exist without a Ph. D. Supervisor, but in this one the influence of Prof. Dr. Stefan Edelkamp, my supervisor, started much earlier. Being a diploma student he introduced me to the art of Model Checking. I do not know if it was because of *someone had to do the job* or because of *you are the right for the job* but he always motivated me. Prof. Dr. Edelkamp trusted me, much more then I could trust myself, and now you can read the results. Thanks for the endless discussions, on-and off-topic. Thanks for your time whenever I needed it. Thanks for the possibility to find oneself on the long line.

Special thanks go to Prof. Dr. Bernhard Steffen the man with the big picture. Although he never was the one I discussed implementation details with, he was always interested in my work and pushed me in the right direction when I stood at a forking way not knowing where to go. Thanks also for the warm place for my research.

I am also grateful to the other members of the committee: Prof. Dr. Jan Vahrenhold and Dr. Ingo Battenfeld for the help and support in the *last minutes*.

Thanks to all the coauthors who showed me the right way to write papers, thanks to Dragan Bosnacki, Pavel Šimeček, and especially to Shahid Jabbar. Pavel, perhaps one day we can play a second match *Czech Republic against Poland*?

When Stefan is my *Doctorvater* then Shahid certainly is my *Doktorbruder*. There are two images I see in front of me when thinking about him. I once came into his room and he was working on his thesis, he was adjusting a line in one picture, at the highest zoom level, moving it only some millimeters. It had to be perfect. The other image is a huge number of full and empty boxes in his room. I helped him to transport them to the local UPS store, the evening before his last flight to Sweden. Absolutely chaotic. This made him a human. Staying in the terms of a *Doktorfamilie* I will never forget my second *Doktorbruder* Peter Kissmann. Thanks for destroying my ideas at the right time. Peter is a gifted person in my eyes, his gift is to smell inconsistencies before his discussion partner has formulated the whole idea. It was not always funny to think a whole weekend on a particular algorithm and then see it collapse because of an overseen littleness. And of course thanks for the rigorous proof-reading of this work, I hope it makes it readable.

At this point it is time to thank the whole LS5 Team from the present and the past. I can not remember all the names due to a miserable memory, but i try to remember some. Thanks to the proof readers Julia Rehder, Falk Howar, Maik Merten and Johannes Neubauer. Thanks go to Thomas Wilk for showing me skills in table soccer I will never reach. Thanks to the, sporting ace Christian Wagner for motivation on this domain, and

Sven Jörges for the photo finish in submitting a dissertation.

All the time during this work, there was only one source of energy for me, this source was, is and will always be my family. I would like to return all of what you gave me, but I am sure I will never be able to. Names given in a text have to be in an order so I order them by age, but trust me Son, Wife, Mom and Dad I did all this for you, for you all.

Last but not least I would like to send special thanks to Cengizhan Yücel a long time student friend and the one of the most reliable persons i ever knew.

Finally a big thanks goes to the *Deutsche Forschungsgeselschaft* for financially supporting my research through the project *Modellprüfung auf Flashspeicher-Festplatte* und Grafikkarte.

# Contents

| 1 | Intr | oduction                                    | 1  |  |

|---|------|---------------------------------------------|----|--|

|   | 1.1  | Motivation                                  | 1  |  |

|   | 1.2  | State Space Exploration                     | 3  |  |

|   |      | 1.2.1 Introducing State Spaces              | 3  |  |

|   |      | 1.2.2 Example of a State Space              | 6  |  |

|   |      | 1.2.3 State Spaces in the Following Parts   | 7  |  |

|   | 1.3  | Graph Search Algorithms                     | 9  |  |

|   |      | 1.3.1 Blind Search                          | 10 |  |

|   |      | 1.3.2 External Search                       | 16 |  |

|   |      | 1.3.3 Parallel Graph Search                 | 18 |  |

|   | 1.4  | Duplicate Detection in Graph Search         | 21 |  |

|   |      | 1.4.1 Hash Based Duplicate Detection        | 21 |  |

|   |      | 1.4.2 Sorting Based Duplicate Detection     | 24 |  |

|   | 1.5  | Main Contributions                          | 25 |  |

|   | 1.6  | Organization of the Thesis                  | 26 |  |

| 2 | Har  | rdware and Programming Models 2             |    |  |

|   | 2.1  |                                             | 29 |  |

|   |      |                                             | 30 |  |

|   |      | · · ·                                       | 30 |  |

|   |      | 2.1.3 Solid State Disks                     | 30 |  |

|   | 2.2  |                                             | 34 |  |

|   |      | · ·                                         | 34 |  |

|   |      |                                             | 35 |  |

|   |      |                                             | 36 |  |

|   | 2.3  | 6 6                                         | 43 |  |

|   |      |                                             | 43 |  |

|   |      |                                             | 46 |  |

|   |      |                                             |    |  |

| I | Bre  | eadth-First Search utilizing Novel Hardware | 53 |  |

| 3 | Prer | requisites for GPU and SSD Utilization      | 55 |  |

|   | 3.1  | Work Distribution                           | 56 |  |

|    |       | 3.1.1 Independent Limited Memory Tasks                   | 57       |

|----|-------|----------------------------------------------------------|----------|

|    | 2.2   | 3.1.2 Unlimited Memory Tasks                             | 58       |

|    | 3.2   | Information Distribution                                 | 59       |

|    |       | 3.2.1 Constant Information                               | 59<br>60 |

|    |       | 3.2.2 Dynamic Information                                | 60       |

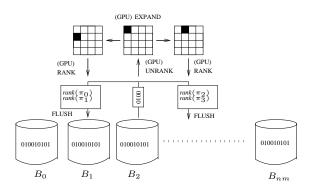

| 4  | GPU   | JSSD - Breadth-First Search                              | 63       |

|    | 4.1   | Basic Structure of the Algorithm                         | 63       |

|    | 4.2   | Strategies for Successor Generation                      | 65       |

|    |       | 4.2.1 Successor Counting                                 | 65       |

|    |       | 4.2.2 Successor Pointing                                 | 68       |

|    | 4.3   | Strategies for Duplicate Detection                       | 71       |

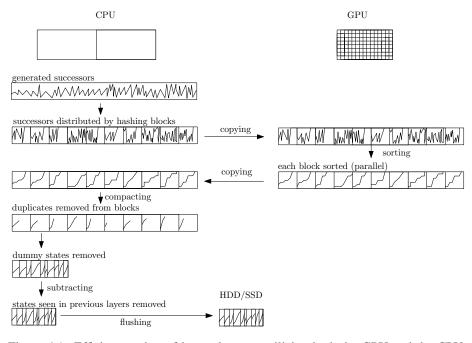

|    |       | 4.3.1 Sorting Based Duplicate Detection                  | 71       |

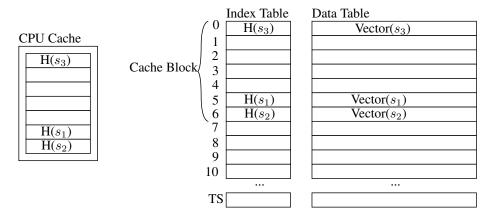

|    |       | 4.3.2 Parallel Hash Based Duplicate Detection            | 74       |

|    | 4.4   | External State Space Exploration on the GPU              | 76       |

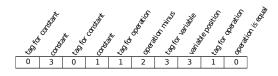

|    | 4.5   | Efficient Flat Representation of Formulas                | 77       |

|    | 4.6   | Summary                                                  | 78       |

|    |       |                                                          |          |

| II | Ex    | xplicit State Model Checking                             | 81       |

| 5  | Intro | oduction to Explicit State Model Checking                | 83       |

|    | 5.1   | Modeling of Concurrent Systems                           | 84       |

|    |       | 5.1.1 Concurrent Systems as Variables and Actions        | 84       |

|    |       | 5.1.2 Explicit State Model Checking                      | 85       |

|    |       | 5.1.3 Explicit State Model Checking Example              | 86       |

|    | 5.2   | Related Work                                             | 88       |

|    |       | 5.2.1 External Explicit State Model Checking Algorithms  | 88       |

|    |       | 5.2.2 Parallel Explicit State Model Checking             | 88       |

|    | 5.3   | Summary                                                  | 89       |

| 6  | SSD   | -Based Minimal Counterexamples Search                    | 91       |

|    | 6.1   | Semi-External LTL Model Checking                         | 91       |

|    |       | 6.1.1 Extending to Efficiently Support SSDs              | 96       |

|    | 6.2   | Externalizing the Perfect Hash Function                  | 97       |

|    | 6.3   | Summary                                                  | 98       |

| 7  | GPU   | J-Based Model Checking                                   | 99       |

|    | 7.1   | Parsing the DVE Language                                 | 99       |

|    |       | 7.1.1 Checking Enabledness on the GPU                    | 101      |

|    | 7.2   | Generating the Successors on the GPU                     | 102      |

|    | 7.3   | Duplicate Detection                                      | 103      |

|    |       | 7.3.1 Immediate Detection on (Multiple Cores of) the CPU | 103      |

|    |       | 7.3.2 Delayed Duplicate Detection on the GPU             | 104      |

|    | 7.4   | Summary                                                  | 104      |

|    |       | -                                                        |          |

xii

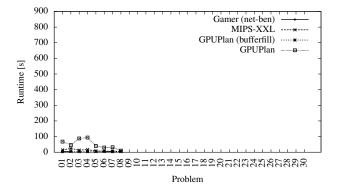

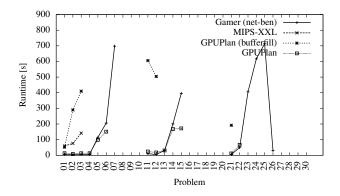

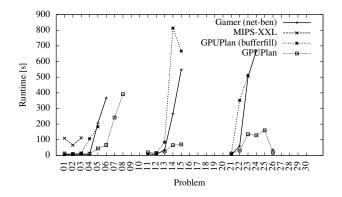

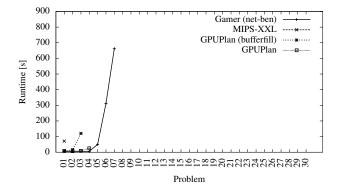

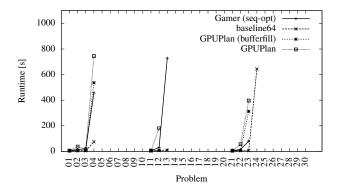

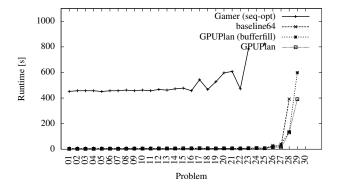

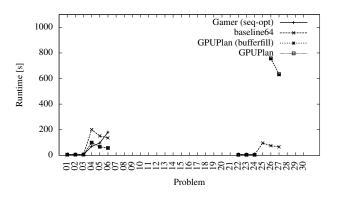

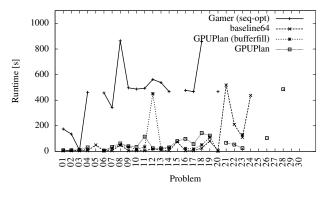

| 8  | Expe  | erimental Evaluation                               | 105 |

|----|-------|----------------------------------------------------|-----|

|    | 8.1   |                                                    | 105 |

|    |       |                                                    | 106 |

|    |       | 8.1.2 Flash-Efficient Model Checking               | 106 |

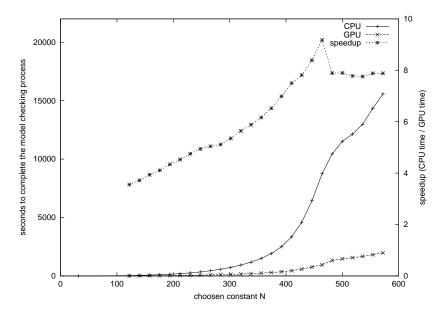

|    | 8.2   | Results for GPU-Based Model Checking               | 108 |

|    |       | 8.2.1 Evaluation of Immediate Duplicate Detection  | 108 |

|    |       | 8.2.2 Experiments with Delayed Duplicate Detection | 112 |

|    | 8.3   | Summary                                            | 114 |

|    |       |                                                    |     |

| Π  | I A   | ction Planning 1                                   | 115 |

| 9  | Intro | oduction to Action Planning                        | 117 |

|    | 9.1   | Modeling of Planning Problems                      | 117 |

|    | 9.2   | PDDL Example of the Thesis Problem                 | 119 |

|    | 9.3   | Related Work                                       | 119 |

|    | 9.4   | Summary                                            | 122 |

| 10 | Acti  | on Planning on the GPU                             | 123 |

|    |       |                                                    | 123 |

|    |       | -                                                  | 123 |

|    | 10.2  |                                                    | 124 |

|    |       | 0 0                                                | 124 |

|    | 10.3  | Summary                                            | 127 |

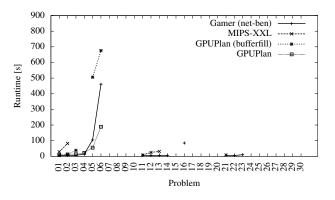

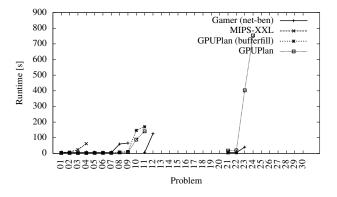

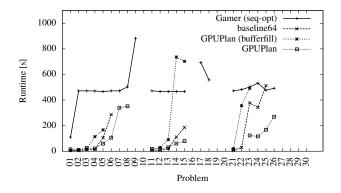

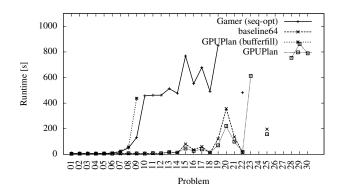

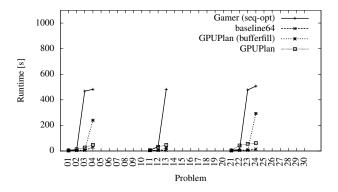

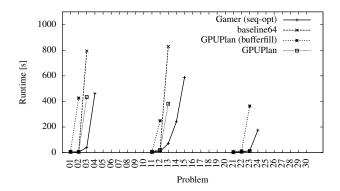

| 11 | Evn   | erimental evaluation                               | 129 |

| 11 | -     |                                                    | 129 |

|    |       |                                                    | 136 |

|    | 11.2  | Summary                                            | 150 |

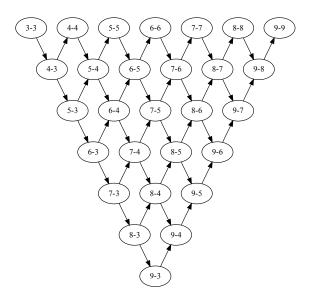

| IV | G     | ame Solving                                        | 137 |

| 12 | Intre | oduction to Game Solving                           | 139 |

| 14 |       |                                                    | 140 |

|    | 12.1  | -                                                  | 140 |

|    |       |                                                    | 140 |

|    |       |                                                    | 140 |

|    |       |                                                    | 140 |

|    |       |                                                    | 141 |

12.1.6

Nine-Men-Morris

141

12.2

Game Solving

142

12.3

Related Work

142

12.4

Summary

144

| Х | (111 |

|---|------|

|   |      |

| 13       | Perfect Hashing in Games                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 145                                                                                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 13.1 Properties of State Spaces in Games                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 145                                                                                                                                                                                 |

|          | 13.2 Ranking and Unranking in Permutation Games                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 146                                                                                                                                                                                 |

|          | 13.2.1 Reducing State Space in Permutation Games                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 148                                                                                                                                                                                 |

|          | 13.3 Binomial Coefficient for Single Player Games                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 149                                                                                                                                                                                 |

|          | 13.4 Multinomial Coefficient for Multi Player Games                                                                                                                                                                                                                                                                                                                                                                                                                                                | 150                                                                                                                                                                                 |

|          | 13.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 155                                                                                                                                                                                 |

| 14       | GPU Enhanced Game Solving using Perfect Hashing                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 157                                                                                                                                                                                 |

|          | 14.1 State Space Algorithms utilizing Perfect Hashing                                                                                                                                                                                                                                                                                                                                                                                                                                              | 157                                                                                                                                                                                 |

|          | 14.1.1 Two-Bit Breadth-First search                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 158                                                                                                                                                                                 |

|          | 14.1.2 One-Bit Reachability                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 159                                                                                                                                                                                 |

|          | 14.1.3 One-Bit Breadth-First search                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 159                                                                                                                                                                                 |

|          | 14.2 Porting Algorithms to the GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 161                                                                                                                                                                                 |

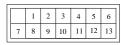

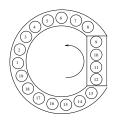

|          | 14.2.1 Case Study: Nine-Men-Morris                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 164                                                                                                                                                                                 |

|          | 14.3 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 167                                                                                                                                                                                 |

| 15       | Experimental evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 169                                                                                                                                                                                 |

|          | 15.1 Single-Agent Games                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 169                                                                                                                                                                                 |

|          | 15.2 Nine-Men-Morris                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 171                                                                                                                                                                                 |

|          | 15.3 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 172                                                                                                                                                                                 |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

| V        | Probabilistic Model Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 173                                                                                                                                                                                 |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                   |

|          | Introduction Probabilistic Model Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 175                                                                                                                                                                                 |

|          | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>175</b><br>175                                                                                                                                                                   |

|          | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic                                                                                                                                                                                                                                                                                                                                                             | <b>175</b><br>175<br>176                                                                                                                                                            |

|          | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL                                                                                                                                                                                                                                                                                                             | <b>175</b><br>175<br>176<br>176                                                                                                                                                     |

|          | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains                                                                                                                                                                                                                                                             | <b>175</b><br>175<br>176<br>176<br>178                                                                                                                                              |

|          | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL                                                                                                                                                                                                                                                                                                             | <b>175</b><br>175<br>176<br>176                                                                                                                                                     |

| 16       | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains                                                                                                                                                                                                                                                             | <b>175</b><br>175<br>176<br>176<br>178                                                                                                                                              |

| 16       | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary                                                                                                                                                                                                                                        | <b>175</b><br>175<br>176<br>176<br>178<br>178                                                                                                                                       |

| 16       | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         16.5 Summary         16.7 Summary         16.8 Algorithms for Model Checking         17.1 Jacobi Iterations.                                                                                                                   | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>178</li> <li>179</li> </ul>                                                                  |

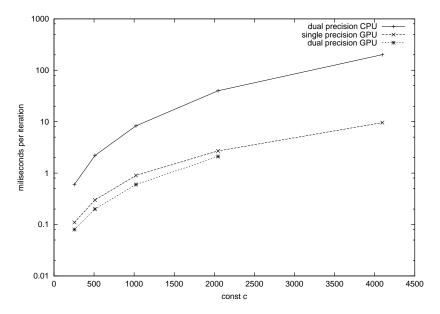

| 16       | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         GPU Enhanced Probabilistic Model Checking                                                                                                                                                                                      | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>178</li> <li>179</li> <li>179</li> </ul>                                                     |

| 16       | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         16.5 Summary         17.1 Jacobi Iterations.         17.2 Sparse Matrix Representation.                                                                                                                                        | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>179</li> <li>180</li> </ul>                                                                  |

| 16       | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         16.5 Summary         17.1 Jacobi Iterations.         17.2 Sparse Matrix Representation.         17.3 Algorithm Implementation.                                                                                                 | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>179</li> <li>180</li> <li>181</li> </ul>                                                     |

| 16<br>17 | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         16.5 Summary         17.1 Jacobi Iterations.         17.2 Sparse Matrix Representation.         17.3 Algorithm Implementation.         17.4 Extending the Algorithm to Multiple GPUs         17.5 Summary                      | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>179</li> <li>180</li> <li>181</li> <li>184</li> <li>186</li> </ul>                           |

| 16<br>17 | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         16.5 Summary         17.1 Jacobi Iterations.         17.2 Sparse Matrix Representation.         17.3 Algorithm Implementation.         17.4 Extending the Algorithm to Multiple GPUs         17.5 Summary                      | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>179</li> <li>180</li> <li>181</li> <li>184</li> <li>186</li> <li>187</li> </ul>              |

| 16<br>17 | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         16.5 Summary         17.1 Jacobi Iterations.         17.2 Sparse Matrix Representation.         17.3 Algorithm Implementation.         17.4 Extending the Algorithm to Multiple GPUs         17.5 Summary         17.8 Summary | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>179</li> <li>180</li> <li>181</li> <li>184</li> <li>186</li> <li>187</li> <li>187</li> </ul> |

| 16<br>17 | Introduction Probabilistic Model Checking         16.1 Discrete Time Markov Chains         16.2 Probabilistic Computational Tree Logic         16.3 Algorithms for Model Checking PCTL         16.4 Beyond Discrete Time Markov Chains         16.5 Summary         16.5 Summary         17.1 Jacobi Iterations.         17.2 Sparse Matrix Representation.         17.3 Algorithm Implementation.         17.4 Extending the Algorithm to Multiple GPUs         17.5 Summary                      | <ul> <li>175</li> <li>175</li> <li>176</li> <li>176</li> <li>178</li> <li>178</li> <li>179</li> <li>180</li> <li>181</li> <li>184</li> <li>186</li> <li>187</li> </ul>              |

#### xiv

| CONTENTS                       | XV    |

|--------------------------------|-------|

| VI Conclusions and Future Work | 193   |

| 19 Conclusion                  | 195   |

| 19.1 Conclusions               | . 195 |

| 19.2 Future Work               | . 198 |

xvi

# **List of Algorithms**

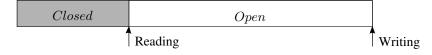

| 1.1  | Graph algorithm using an <i>Open</i> list                             | 10  |

|------|-----------------------------------------------------------------------|-----|

| 1.2  | Graph algorithm using an <i>Open</i> and a <i>Closed</i> list         | 11  |

| 1.3  | Breadth-First search                                                  | 12  |

| 1.4  | Depth-First search                                                    | 13  |

| 1.5  | Iterated Depth-First search                                           | 14  |

| 1.6  | Dijkstra's Algorithm                                                  | 15  |

| 1.7  | The External BFS algorithm                                            | 17  |

| 1.8  | Basic parallel search strategy                                        | 19  |

| 1.9  | Hash based parallel search strategy                                   | 19  |

| 2.1  | Matrix Vector Multiplication on the CPU                               | 40  |

| 2.2  | GPU-Kernel for the Matrix Vector Multiplication                       | 41  |

| 2.3  | Host algorithm for the Matrix Vector Multiplication                   | 41  |

| 4.1  | Basic GPU Parallel Search algorithm                                   | 64  |

| 4.2  | GPU-Kernel Determine Transitions for Successor Counting               | 66  |

| 4.3  | GPU-Kernel Generate Successors for Successor Counting                 | 67  |

| 4.4  | GPU-Kernel Determine Transitions for Successor Pointing               | 69  |

| 4.5  | GPU-Kernel Generate Successors for Successor Pointing                 | 70  |

| 4.6  | GPU-Kernel Sort buckets in sorting based duplicate detection          | 73  |

| 4.7  | GPU-BFS - Large-Scale Breadth-First search on the GPU                 | 77  |

| 6.1  | Minimal-Counterexample search                                         | 93  |

| 6.2  | <i>BFS-PQ</i> File-based 1-level-bucket priority queue                | 94  |

| 6.3  | Prio-min: Synchronized traversal in an 1-level-bucket priority queue. | 95  |

| 6.4  | SSD-LTL-Model-Check: Flash-efficient semi-external Model Checking     | 97  |

| 7.1  | GPU-Kernel Determine guard on a given state                           | 102 |

| 7.2  | GPU-Kernel Detect Duplicates via Sorting                              | 102 |

|      | Optimal Eager Buffer-Filling GPU Planning algorithm                   | 126 |

| 10.2 | GPU-Kernel Generate Successors in Planning                            | 127 |

|      | unrank(r) with parity derived on-the-fly                              | 147 |

| 13.2 | Binomial-Rank                                                         | 150 |

|      |                                                                       |     |

#### LIST OF ALGORITHMS

| 13.3 | Binomial-Unrank                                                 | 151 |

|------|-----------------------------------------------------------------|-----|

| 13.4 | Multinomial-Rank                                                | 152 |

| 13.5 | Multinomial-Unrank                                              | 154 |

|      |                                                                 |     |

| 14.1 | Two-Bit-Breadth-First search ( <i>init</i> )                    | 158 |

| 14.2 | One-Bit reachability ( <i>init</i> )                            | 159 |

| 14.3 | One-Bit-Breath-First search                                     | 160 |

| 14.4 | One-Bit reachability utilizing the GPU                          | 161 |

| 14.5 | GPU-Kernel Determine Transitions for One-Bit reachability       | 162 |

|      | GPU-Kernel Generate Successors for One-Bit reachability         | 163 |

| 14.7 | BFS for Phase I                                                 | 165 |

| 14.8 | Retrograde Analysis Phase I                                     | 166 |

|      |                                                                 |     |

| 17.1 | Jacobi iteration with row compression (as implemented in PRISM) | 182 |

| 17.2 | Host part of the Jacobi iteration, for unbounded until          | 183 |

| 17.3 | GPU-Kernel Jacobi iteration with row compression                | 184 |

| 17.4 | Host part of the Jacobi iteration for multiple GPUs             | 185 |

|      |                                                                 |     |

xviii

### Chapter 1

## Introduction

#### 1.1 Motivation

Time is a scarce resource, space is unlimited. This statement is becoming reality in the 64-bit era. Today, an ordinary personal computer utilizes up to 32 gigabyte of internal RAM storage, using server hardware even 256 gigabyte in one computer are possible. Utilizing external storage one can get 3 terabyte magnetic drives, so called *Hard Disk Drives* (HDDs) at nearly 100 € and continuously falling prices. An example of resource capabilities these days is the company *Google*, who is offering an Email service giving each user 7.44 gigabyte available space for their mails. In February 2010 the service had reported to have 170 million accounts<sup>1</sup> with an available space of 1,235,156.25 terabytes or 1.177 exabytes.

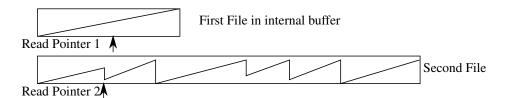

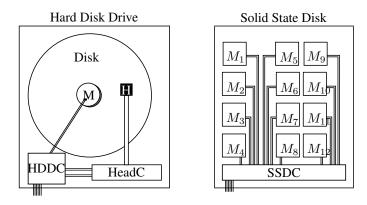

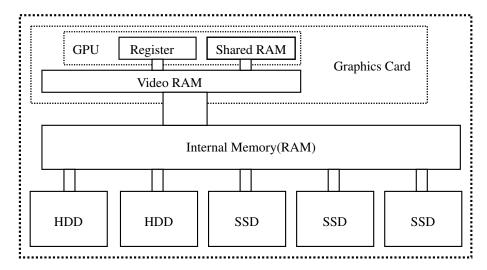

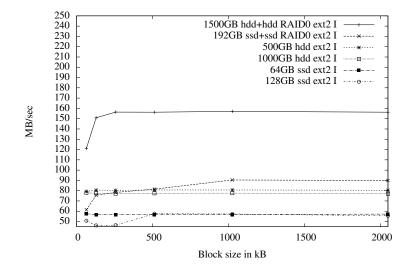

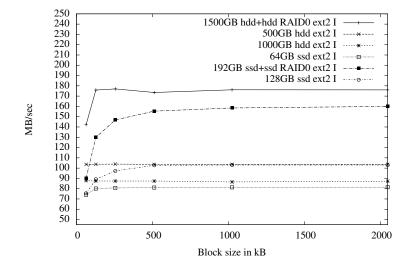

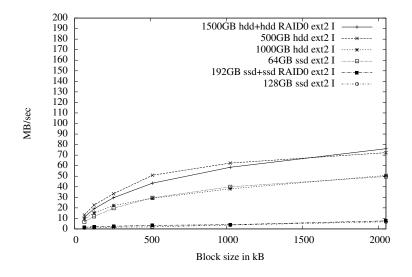

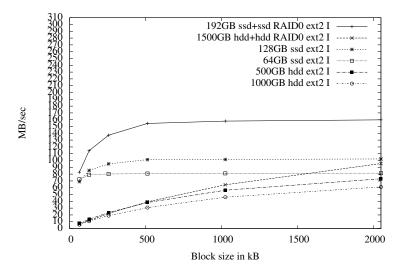

For applications where excessive random access to the data is mandatory and magnetic drives fail to reach appropriate speeds, solid state drives (SSDs) have entered the market. An SSD stores information on memory chips providing faster access to the data while consuming less power. A system with 256 GB of RAM costs about 4,500  $\in$  at today's prices while the same amount of SSD storage costs nearly 300  $\in$  utilizing a reading access speed of 255 MB/s (compared to about 100 MB/s on HDDs and 17 GB/s for RAM) and the possibility to be extended by adding more or larger devices. The characteristics of solid state media differ significantly from the ones of hard disk devices imposing new challenges on the developers of algorithms. While writing data to such a medium is done at a speed comparable to magnetic devices (being about 100 MB/s) the reading of random bits can be done with much higher efficiency. These characteristics, additionally with the possibility to even increase the throughput by combining several devices, make them perfect for storing random access structures which exceed the size of RAM.

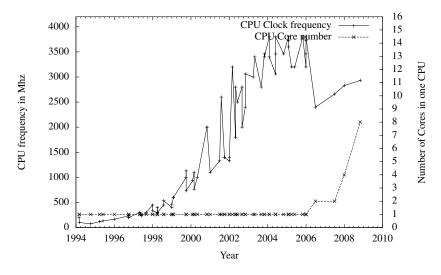

Rising storage capabilities do not necessarily require a change on the algorithmic level. In contrast to this, the switch from increasing the clock rate to assembling multiple cores in one central processing unit (CPU) demands for a parallelization on the algorithmic level. This change in design forces the algorithms to utilize the available

<sup>&</sup>lt;sup>1</sup>http://news.bbc.co.uk/2/hi/8506148.stm

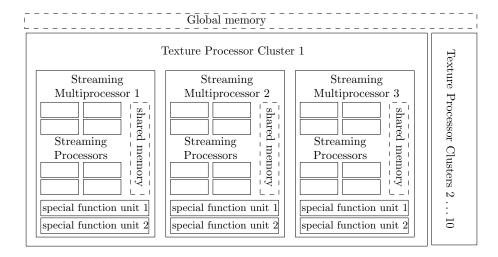

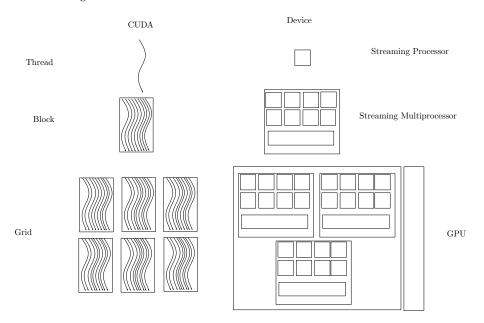

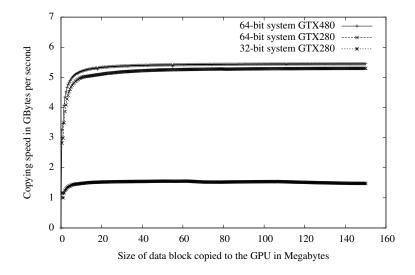

parallel computing power to gain profit from it and requires synchronization techniques and load balancing. The current maximum number of cores in one CPU is 8 which simulate 16 cores by utilizing two threads per core. Being confronted with a number of different tasks in parallel, the CPU cores are self-contained computing cores even able to increase the clock for one single core to speed up sequential computation. Simultaneously to the CPU the developers of the graphics cards increased the computation power by parallelization. Contrary to data processing a graphics processing unit (GPU) is used to compute the visualization for a large number of triangles representing a virtual world. Since the triangles are independent and the computation is equivalent for all of them, the parallelization used is the single instruction multiple data (SIMD) technique. Here a large number of processors manipulate data using the same instructions. Current GPUs utilize up to 1,024 processors in one graphics card (NVIDIA GTX 590) and up to 4 cards can be combined in one system.

This work utilizes recent developments in hardware to solve search problems in which the goal is to find a set of explicit nodes in a graph defined implicitly prior to the search. In an *implicit* definition just the starting node and a *transition function* transforming this node into new ones is given. The main challenge spreading over all implicit graph search problems is the *state space explosion problem*, which describes the potentially exponential development of node numbers in the graph. Even small changes in the transition function definition may increase the number of *reachable* nodes, on a path from the initial node, dramatically increasing the search time, which is mostly linear to this number.

Between all the available search challenges given in the scientific and non-scientific work, the four investigated domains represent a spectrum and give a starting point for investigation in many other research areas.

The first investigation on the usage of solid state drives and graphics processing units is Explicit State Model Checking (Clarke et al., 1999; Müller-Olm et al., 1999), where the demand for storage space and computation power increased dramatically with the introduction of parallel processors. It should be needless to say how important software verification has become in the last years. With the introduction of concurrent hardware at affordable prices for everyone, parallel programming has evolved to a standard technique to implement efficient algorithms. Not so long ago, only security related bugs were hunted, or bugs whose removal would directly avoid loosing equipment worth millions of dollars like an exploding space rocket. Today all companies search for efficient ways to verify their software because a bug can cause a significant loss of reputation resulting in the emigration of customers. The automobile constructor Mercedes-Benz learned their lesson when long term clients switched to other manufacturers because of small bugs in the car software. Even though the bugs were not dramatic, e.g., a not opening door when the remote was pressed, the damage to their reputation of being a premium manufacturer was worth millions of dollars due to decreasing sales.

The second chosen discipline is *Action Planning* (Russell and Norvig, 2002), where the goal is to find a plan fulfilling predefined conditions given a set of actions. The plan consists of a sequence of transition functions (here denoted as *actions*) which transform the initial state into a goal state. Prominent examples of planning are logistic domains as well as planning robots which perform various tasks efficiently. This work deals

#### 1.2. STATE SPACE EXPLORATION

with deterministic Action Planning where each action is fully defined.

A breadth-first state-space generation in the artificial intelligence (AI) branch *Game Solving* (van den Herik *et al.*, 2002) imposes new challenges on the SSD and GPU utilization. Problems in this domain are usually built up of a high number of available moves, e. g., all possible movements to the figures on a chess board, with only a small number of these being valid moves. While a check for a single move can be done very efficiently the high number of checks imposes a long searching time. An additional aspect of this problems is a large state description where an efficient compression is necessary to traverse the entire state space. Here the computation power of the GPU comes in handy since the decompression and the determination of valid movements can be done in parallel on a huge number of states.

*Probabilistic Model Checking* (Kwiatkowska *et al.*, 2007) has been proved to be a powerful framework for modeling various systems ranging from randomized algorithms via performance analysis to biological networks. Although solutions for Probabilistic Model Checking can also be obtained by a state space search for a specific state, this is not an efficient way. Here the satisfaction of properties is quantified with some probability in contrast to the previous disciplines. In a state space approach this maps to generating states and annotating them with a probability until the target is reached. Due to the high branching factor it is more efficient to choose a different approach i. e., using numerical methods which enforce different strategies to utilize the GPU and external media. In this discipline the GPU has to be used with the intention of solving linear equations, imposing new challenges on the algorithm development.

This work will investigate in using recent developments in hardware to allow for traversing larger graphs in less time in all these domains.

#### **1.2 State Space Exploration**

The connecting aspect of all analyzed problems is the traversal of a search graph defined only by a starting node and a transformation function. To understand the correlation exploited in this work we need to define the basics of the *state space exploration* and present a number of existing algorithms. The following sections will provide the necessary definitions to explore state spaces and to analyze the proposed algorithms.

#### 1.2.1 Introducing State Spaces

As this dissertation concentrates on *implicitly* given graphs where only a starting point and instructions how to traverse the graph are given we limit the definitions to those graph structures.

**Definition 1 (System)** A system is a problem definition in a given environment. It includes all the necessary information to solve the problem and can be expressed in a suitable description language.

A system usually consists of three aspects, a description of an environment, definitions of transformable elements in this environment and transition functions for these elements. Board games are systems where the board defines the environment and the pieces are placed or moved by transforming their position. The rulebook defines the transition functions by describing allowed moves.

**Definition 2 (State)** A state *s* is a description representing the overall configuration of a system at a specified point in time.

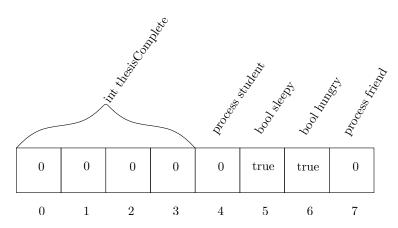

A state can be the concatenation of sub-states each describing a part of the system. To give an example take a look at the game checkers, here each piece can be a usual *men* or a *king*. One solution to store this difference in a state is to use different notations for this attribute. Another solution is to include this as a special variable representing this piece in the state. This variable is called *local state* since a change to this local state is only locally in the whole system.

**Definition 3 (Local state)** *The* local state *of an unique actor in a system is a variable describing the current condition of the actor.*

As an example, the local state of a piece denotes whether it is a men or a king and a state is the position of all pieces on the board in checkers. Replacing or removing pieces and changing a local state when reaching the appropriate position corresponds to transforming one state into another.

**Definition 4 (State Space)** A state space S, is the set of all possible configurations of a given system.

The state space S of the game chess consists of all the possible placements for all pieces. sinS is mapped to a node  $v \in V$  in the graph G = (V, E).

A subset of all states  $\hat{s} \in S$  identifies the *initial* states, defined entirely before the search. All systems analyzed in this work only have one single initial state. The set of *reachable* nodes is a subset  $r \subseteq S$  denoting all nodes connected from  $\hat{s}$ .

To define the remaining states the informal definition of the transition function is formalized and *transitions*, composed of a *precondition* and a *postcondition* are defined as follows,

**Definition 5 (Precondition)** A precondition of a transition defines conditions in the state to be true before transforming the state by applying a transition.

**Definition 6 (Transition)** A transition t in the set of all transitions T is a pair connecting one Boolean precondition and a set of postconditions. The transition is called active when the precondition evaluates to true.

A transition has to define the modifications to the state in a set of postconditions.

**Definition 7 (Postcondition)** *The* postconditions *define conditions in the state which have to be true after it has been transformed.*

A transition from  $s_1 \in S$  to  $s_2 \in S$  is similar to an edge in the directed graph G = (V, E) with V = S and  $E = (v_1, v_2)$  where  $v_1 = s_1 \wedge v_2 = s_2$ .

Both, the precondition and all postconditions may be empty, resulting in a transition applicable to all states or a transition transforming the state into its identity. While the identifier precondition is common in Action Planning the postconditions in Action Planning and Model Checking are called *effects*. The later additionally utilizes the term *guard* to denote a precondition. In Game Solving the preconditions are given as rules whether a move is valid or not, the postcondition is the result of executing a valid move. Probabilistic Model Checking is an exception where all preconditions are active with a given probability. Postconditions are applied when a precondition is chosen.

**Definition 8 (Parents and Successors)** When applying a transition the base state is called parent while the resulting state is called successor. Leaves are states without successors having no active transition.

**Definition 9 (Expansion / Generation)** During the expansion of a parent, or the generation of successors, the parent is expanded when all successors have been generated.

While definitions so far applied to single nodes in a graph, the following one will cover connected nodes.

**Definition 10 (Path)** A path is a sequence of states  $s_0, s_1, \ldots, s_n$  where an active transition exists for all pairs  $(s_i, s_{i+1})$  with  $0 \le i < n$ . The length of a path is n the number of states it contains.

Starting at an initial state and transforming it into a number of successors will generate a tree. To transform this tree into a graph *duplicates* have to be defined, describing states which are indistinguishable.

**Definition 11 (Duplicate)** Two states  $s_1$  and  $s_2$  reachable on different paths from the initial state  $(\hat{s} \dots s_1 \neq \hat{s} \dots s_2)$  are duplicates when their representations are identical (write  $s_1 = s_2$ ).

**Lemma 1** In two state spaces  $S_1$  and  $S_2$  using the same set of transitions T and duplicate initial states  $\hat{s}_1 = \hat{s}_2$ , for each state  $s' \in S_1$  exists a duplicate state  $s'' \in S_2$  so that s' = s'' and  $S_1 = S_2$ .

**Proof.** Since the representation of the duplicates  $\hat{s}_1 \in S_1$  and  $\hat{s}_2 \in S_2$  are identical the set of active transitions  $a \subseteq T$  (the set of non-active transitions  $\bar{a} : T/a$ ) is identical.

Applying the same postconditions of an active transition  $a_1 \in a$  to  $\hat{s}_1$  or  $\hat{s}_2$  results in a new duplicate successor s for every  $a' \in a$ . The same applies to every s further down the path.

Finally, after having introduced paths and duplicates the definition of a cycle can be given.

**Definition 12 (Cycle)** A cycle in a state space is a path of arbitrary length connecting two duplicates.

The shortest cycle is a path (s,s) formed by a transition without effects.

#### **1.2.2** Example of a State Space

This section introduces an example to sketch a state and the state space on a constructed problem.

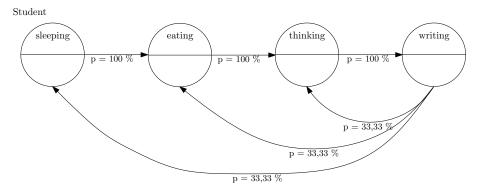

The problem is to finish a work denoted as *thesis* by a given actor called *student*. The student is supported by a variable number of *friends* to review the thesis and reduce its level of completeness by a given amount, due to pointing out errors and inconsistencies. The student alternates between *thinking* and *writing* of the thesis to complete it, but also has the necessity to *sleep* and *eat* during this process, while his friends are *enjoying time* or *correcting* the work.

To simplify the students life we set up some assumptions:

- After sleeping the student has to eat.

- Having eaten the student starts thinking on the thesis.

- The student immediately writes down her or his thoughts.

- If the student is neither hungry nor sleepy having finished writing a part he starts to think about further parts.

- Writing makes hungry.

- Eating makes sleepy.

- A friend can only review a thesis if something is written.

The question here could be if the work will be finished or how the number of reviewers influences the time to finish the work or to find a plan to distribute the thesis among friends efficiently.

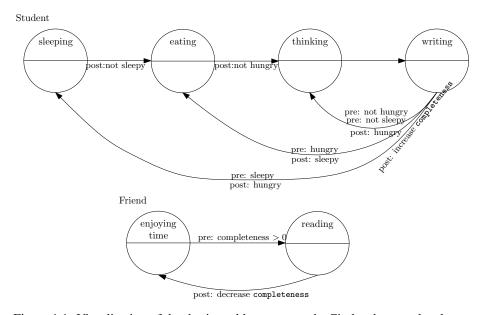

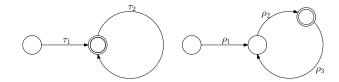

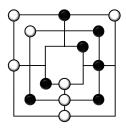

Figure 1.1 visualizes the student's and one friend's behavior as a directed graph. Each circle is a local state denoted with a name in the upper half. Edges represent transitions from the parent state to its successor. If a precondition for a transition exists it is given the prefix *pre*: above the corresponding edge. Postconditions are described under the edges and prefixed with a *post*. There is one global variable called completeness denoting the completeness of the work not visualized in the graph.

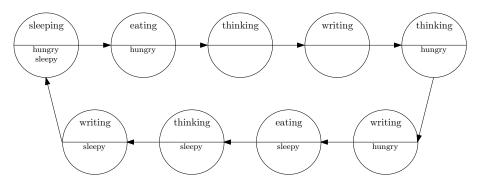

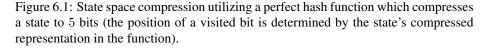

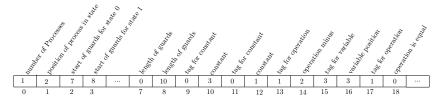

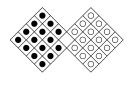

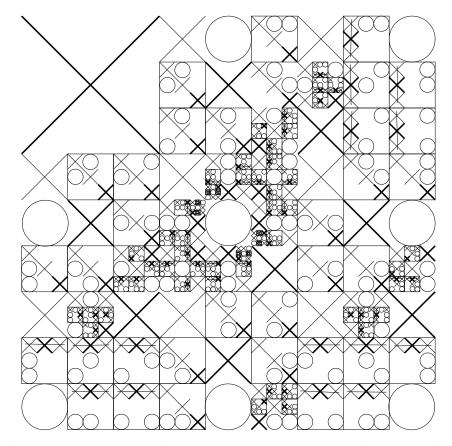

The state space of the student, depicted in Figure 1.2 shows a directed graph of all reachable states for the student, if no interaction with a friend appears. The name of the state is shown in the upper half, and the variables being true in a state are visualized in the bottom half of the circle. In contrast to Figure 1.1 states with similar names appear several times in the state space since the values of the variables in it differ. Figure 1.2 visualizes only the state space of the student omitting interventions of friends. A state space involving correction cycles is a cross product of the state spaces of all actors. So in each state the student is in the friend can be in an *enjoying time* or in a *correcting* state, increasing the number of states by a factor of two for each extra friend. Additionally, tracking the completeness variable in the state space by a factor of 100 making reduction and compression strategies essential.

Figure 1.1: Visualization of the thesis problem as a graph. Circles denote a local state the actor can be in. Each local state is denoted with a name in the upper half of the circle. Edges represent transitions from the parent to the successor with preconditions above it prefixed by *pre:* and postconditions by *post:*. The upper graph presents the transitions for the student and the lower one those for a friend.

Both examples sketch the roots of the states space explosion problem in a simplified manner and motivate the necessity for efficient state storage and processing strategies. While a naive implementation of the completeness variable would increase the state space by a factor of 100 the binary representation can reduce the factor to log(100) = 7. Additional reduction techniques are abstraction (Edelkamp and Lluch-Lafuente, 2004; Namjoshi and Kurshan, 2000) and compression (Lluch-Lafuente *et al.*, 2002; Clarke *et al.*, 1994; Korf, 2008b; Holzmann and Puri, 1999).

#### **1.2.3** State Spaces in the Following Parts

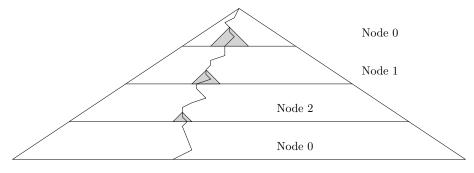

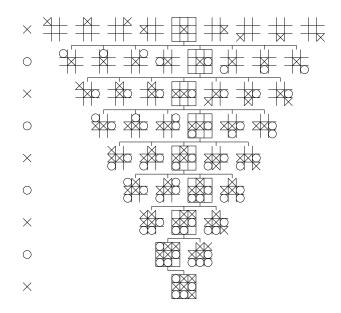

Although the following domains seem to be very different the strategy of state space exploration is the connecting aspect. Model checking, Action Planning, Game Solving and Probabilistic Model Checking are all search problems and easily mapped to a graph algorithm. The proposed technique to use recently developed hardware in graph searching is the roof standing on four pillars, depicted in the four disciplines. The next sections will sketch the mapping of each part to graph searching while a detailed mapping is given in each corresponding part.

Figure 1.2: The state space containing 9 states the actor *student* defined in the thesis problem can be in. The communication with friends, who correct the thesis, is avoided due to complexity of the visualization. When an additional actor (e.g., friend) is included each state is extended by a local state of the actor increasing the number of states by a factor corresponding to the number of local states the actor can be in. This simplification also abstracts from the *completion* variable in the states which would increase the number of states by a factor of 100 if used as a percent variable.

#### **Model Checking**

In *Model Checking* a model, describing a system and given in a description language is checked for a given property. Here, the system is defined prior to the search, given variables and processes as transformable elements, followed by transition functions denoted as *transitions*. Although the environment is not given explicitly it is given by the model checker who is handling the description language. The goal of finding states violating the property is achieved by checking each single state reachable from an initial state against it. To check lifeness properties a so called *lasso* path has to be found. Such a path consists of a cycle containing at least one special (in this discipline denoted as *active*) state and that must be reachable from the initial state and defined in the model description. For such a search, special graph traversal algorithms were developed and Part II will propose an extended algorithm. It uses a number of standard graph search algorithms to find the shortest lasso in a state space. The following chapter proposes an approach to efficiently utilize graphics cards when generating the state space in Model Checking.

#### **Action Planning**

Action Planning is a scientific domain for finding a plan in a given environment to achieve a defined goal. The system of Action Planning is an environment for an actor, e. g., a robot. The actor has to perform actions to find a sequence of actions, called plan, to put himself, into a given goal configuration. This plan can be mapped to a path in a graph, starting at an initial state and connecting it to a state where the goal is achieved. The initial state is defined prior to the search and transitions are given by actions in a description language. The way to find such a plan is to generate all states until the goal state is reached and then either search backwards to the initial state, for a plan

reconstruction, or store the plan while searching. Refined Action Planning uses *costs* which map each action to a value to generate a more realistic representation. Here, an exploration considering only the length of a path is not efficient and special graph algorithms (e.g., Dijkstra's Algorithm (Dijkstra, 1959)), are used. Part III presents a graphics card algorithm extended to support action costs and external media for a generation of the plan.

#### **Game Solving**

The system of a game in *Game Solving* is the state of the game at a specific stage. In board games it suffices to represent the board and the positions of all pieces on it in the system. The transitions are the rules of the game given prior to the search. The task to decide whether a given player can win the game at a given state is achieved by visiting every state and checking for a path to a winning state. One approach to solve a game is a two searches strategy. In the first *forward* search all states reachable from the initial state are generated and classified whether they are winning states for a player or not. The second backwards search starts at all winning states and propagates the information which player has won to the predecessors. In games with only one winning state, like one player combinatorial games, a forward search from the current state suffices to determine if the game can still be completed. In two player games all terminating winning states have to be identified by a forward search followed by a backward search from these to classify all states up to the initial state. Part IV proposes to compress each state to a number by using a permutation rank strategy or binomial and multinomial hashing to decompress the state on the graphics card and analyze it. This strategy can be evaluated efficiently due to the highly parallel processing power of this unit.

#### **Probabilistic Model Checking**

*Probabilistic Model Checking* avoids the preconditions of the state space search by replacing them with the probability of being active. The probabilities of all preconditions in one state sum up to 100%. On leafs this is achieved by adding an outgoing transition without postconditions having a probability of 100%. A naive graph theoretical approach to determine the probability of a property violation is to find a path from the initial state to a violating one and compute the probability along it. This approach can be very ineffective in terms of computation time and usually a different technique is used. The state space is mapped to a matrix with the probabilities given in that matrix and the probability is computed by solving a set of linear computations using a matrix-vector multiplication approach. Part V decreases the time to find a solution significantly by porting the solving process partially to the graphics card.

#### **1.3 Graph Search Algorithms**

Moving from node to node in a graph, respectively traversing a state space, requires a strategy, including a storage- and a decision-rule for the order the successors are generated in. This section will develop a basic algorithm and extend it to more sophisticated strategies optimizing it for different conditions like generating speed or search direction. The development starts with a *blind search*, not using information about the preferred transitions, and resorts to some form of cost-first shortest path path exploration, which requires costs assigned to the edges given in the graph description. Since state spaces can become arbitrarily large the section also introduces algorithms for *external search*, which utilizes external media like hard disks to store information, and *parallel search* utilizing parallel hardware.

#### 1.3.1 Blind Search

In blind search the order of state expansions is defined by the search algorithm, information about preferred transitions is omitted. While generating a state in a search algorithm the generated successors have to be stored for a potential expansion in the further traversal in a dedicated structure called *open list*.

**Definition 13 (Open list)** *The set of generated, but unexpanded states is called an Open list (or just Open) also denoted as a* working set.

Using only an *Open* list one can already form an algorithm which is *complete*, so it will visit all states in the given state space provided it is circle free.

| Algorithm 1.1: Graph algorithm using an Open list                  |                                     |                                               |

|--------------------------------------------------------------------|-------------------------------------|-----------------------------------------------|

| <b>Input</b> : $\hat{s} \in S$ initial state, T set of transitions |                                     |                                               |

| 1 $Open \leftarrow \hat{s}$ ;                                      |                                     | $\{\text{store } \hat{s} \text{ in } Open \}$ |

| 2 while $Open \neq \emptyset$ d                                    | lo                                  | {repeat until search terminates}              |

| 3 choose a state                                                   | $s \in Open;$                       | {usually the first one in the list}           |

| 4 expand success                                                   | sors $s \to s_1 \dots s_{\nu}$ ; {a | pply transitions to generate successors}      |

| 5 for $s_i$ ( $\forall i : 1 \leq $                                | $\leq i \leq  u)$ do                | {check each successor}                        |

| 6   <b>if</b> $s_i \notin Ope$                                     |                                     | $\{$ when not already in $Open \}$            |

| 7                                                                  | $\leftarrow s_i$ ;                  | $\{add it to Open \}$                         |

| 8 remove s from                                                    | Open ; {all succes                  | sors generated so state can be dropped}       |

After inserting the initial state into the *Open* list, Algorithm 1.1 generates the successors of a state by checking the preconditions and applying corresponding postconditions and stores them in *Open*. When all successors of a state are generated and inserted into *Open* the state is removed from the list.

### **Lemma 2** Algorithm 1.1 will terminate and expand all paths in the state space, visiting all states, if the state space is cycle free.

**Proof.** Each state remains in *Open* until all its successors are generated. Removing a fully expanded state is safe since all paths crossing this state to its successors are extended by at least one state. Leaves, states without successors, are end points of paths which cannot be extended and are removed from *Open* immediately when generated.

Since the state space is cycle free each path from  $\hat{s}$  has to end with a leaf forcing the algorithm to terminate.

For state spaces containing cycles Algorithm 1.1 has to be extended. Consider a transition set T with two transitions  $\{(\hat{s}, s), (s, \hat{s})\}$  from the initial state to a successor and back to the initial state. The algorithm will add the initial state to Open over and over again, being trapped in the cycle unable to terminate. To avoid this behavior an option is needed to decide whether a duplicate of a state was already removed from Open, thus the states removed from Open are stored in a separate structure.

**Definition 14 (Closed list)** When all successors of a state are generated it is moved to the Closed list (usually just Closed), also denoted as visited set.

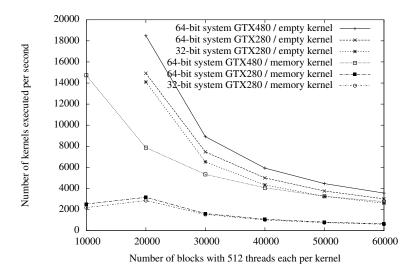

| Algorithm 1.2: Graph algorithm using an Open and a Closed list |                                                                    |                                               |