# QUANTUM MECHANICAL EFFECTS ON MOSFET SCALING LIMIT

A Dissertation Presented to The Academic Faculty

by

Lihui Wang

In Partial Fulfillment

of the Requirements for the Degree

DOCTOR OF PHILOSOPHY in the

School of ELECTRICAL AND COMPUTER ENGINEERING

Georgia Institute of Technology AUGUST 2006

# QUANTUM MECHANICAL EFFECTS ON MOSFET SCALING LIMIT

### Approved by:

Dr. James D. Meindl, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Russell Dupuis School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. William R. Callen School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Ian F Akyildiz School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Phillip First Physics Department Georgia Institute of Technology

Date Approved: July 6, 2006

| This Work Is Dedicated to | My Parents for Having Fa<br>Up on Myself | ith in Me and Never Letting Me Give |

|---------------------------|------------------------------------------|-------------------------------------|

|                           |                                          |                                     |

|                           |                                          |                                     |

|                           |                                          |                                     |

|                           |                                          |                                     |

|                           |                                          |                                     |

|                           |                                          |                                     |

#### **ACKNOWLEDGEMENTS**

This thesis is the result of six years of work whereby I have been accompanied and supported by many people. I am glad that I have now the opportunity to express my gratitude to all of them.

The first person I would like to thank is my advisor Dr. James D. Meindl. During these years, I have known Dr. Meindl as a knowledgeable and compassionate person. I owe him lots of gratitude for guiding me through the research, for his patience and for his understanding. Other than being an excellent advisor, Dr. Meindl is a good friend, giving me support throughout the course of this study.

I would like to thank Jennifer Root Tatham for keeping an eye on the progress of my work and motivating me to complete the work. Special thanks to Dr. Blanca Austin for being there when I needed her advises. I would also like to express my gratitude to committee members Dr. William Callen, Dr. Russell Dupuis, Dr. Ian Akyildiz and Dr. Phillip First for providing helpful suggestions for my thesis.

The work would not have been possible without the help from my fellow students and my friends. I thank them all for our many discussions and for having confidence in me.

Many thanks go to Semiconductor Reseach Corporation whose funding and assistance were vital for this research.

This has been a wonderful journey and I am grateful to all who had helped to make it that way.

### **TABLE OF CONTENTS**

|                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                               | iv                                                          |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                 | viii                                                        |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                | ix                                                          |

| LIST OF SYMBOLS AND ABBREVIATIONS                                                                                                                                                                                                                                                                                                                                                              | xiii                                                        |

| SUMMARY                                                                                                                                                                                                                                                                                                                                                                                        | xvi                                                         |

| CHAPTER 1 INTRODUCTION  1.1 Introduction and Background 1.2 Origin of the Problem 1.3 Historical Review of QME Modeling 1.3.1 Gate Direct Tunneling 1.3.2 Energy Quantization 1.3.3 Gate Capacitance Degradation 1.3.4 Threshold Voltage Shift 1.3.5 Short-Channel Effects and Quantum Mechanical Effects 1.3.6 I-V Characteristics 1.3.7 Scaling Limits Projection 1.4 Scope and Organization | 1<br>1<br>3<br>10<br>10<br>11<br>12<br>14<br>14<br>16<br>16 |

| CHAPTER 2 TUNNELING  2.1 Introduction and Background  2.2 Tunneling Theory  2.3 Tunneling in MOSFET  2.3.1 Electron Tunneling in MOS Structure  2.3.2 Hole Tunneling in MOS Structure  2.4 Tunneling in Different Regions  2.5 Tunneling with Polysilicon Gate  2.6 High-\(\kappa\) Gate Dielectrics  2.7 Band-to-Band tunneling (BTBT) in MOSFET  2.8 Conclusion                              | 20<br>20<br>21<br>23<br>25<br>38<br>40<br>46<br>48<br>50    |

| CHAPTER 3 QUANTIZATION MODEL  3.1 Introduction and Background 3.2 Basic Concept of Quantization 3.3 Quantization in MOSFET 3.3.1 Boundary Conditions 3.3.2 Solution by Variational Method 3.4 Quantum Mechanical C-V Model 3.4.1 Gate Capacitance Components 3.4.2 Classical Gate Capacitance Model                                                                                            | 56<br>56<br>57<br>59<br>68<br>70<br>77<br>77                |

| 3.4.3 Quantum Gate Capacitance Model 3.5 Conclusion                                                                  | 81<br>91       |

|----------------------------------------------------------------------------------------------------------------------|----------------|

| CHAPTER 4 QUANTUM MECHANICAL MOSFET MODEL 4.1 Introduction and Background 4.2 $V_{TH}$ Model for Long-Channel MOSFET | 93<br>93<br>94 |

| 4.3 S Model for Long-Channel MOSFET                                                                                  | 102            |

| 4.4 SCE Model for Short-Channel MOSFET                                                                               | 102            |

| 4.4 SCE Woder for Short-Channel WOSFET $4.4.1$ Short-Channel $V_{TH}$ Model                                          | 110            |

| 4.4.2 Short-Channel S Model                                                                                          | 112            |

| 4.5 QME on <i>I-V</i> Characteristics                                                                                | 117            |

| 4.5.1 Mobility Model                                                                                                 | 117            |

| 4.5.2 Quantum Mechanical Charge Model                                                                                | 118            |

| 4.5.3 Drain Current in the Triode Region                                                                             | 120            |

| 4.5.4 Drain Current in the Saturation Region                                                                         | 122            |

| 4.5.5 Drain Current in the Subthreshold Region                                                                       | 123            |

| 4.5.6 Case Study 4.6 Conclusion                                                                                      | 126<br>128     |

| CHAPTER 5 MOSFET SCALING LIMIT                                                                                       | 129            |

| 5.1 Introduction and Background                                                                                      | 129            |

| 5.2 Traditional Scaling Methods                                                                                      | 130            |

| 5.3 Scaling Limit by Device Leakage                                                                                  | 133            |

| 5.4 Scaling Limit by Circuit Performance and Power Dissipation                                                       | 136            |

| 5.5 Scaling Limits due to Parameter Variation                                                                        | 144            |

| 5.6 CMOS Scaling with Advanced Materials and Structures                                                              | 146            |

| 5.7 Conclusions                                                                                                      | 152            |

| CHAPTER 6 CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE WORK                                                            | 154            |

|                                                                                                                      | 154            |

| 6.1 Conclusions 6.1.1 Introduction                                                                                   | 154<br>154     |

| 6.1.2 Tunneling                                                                                                      | 155            |

| 6.1.3 Energy Quantization                                                                                            | 156            |

| 6.1.4 MOSFET Scaling                                                                                                 | 157            |

| 6.2 Recommendations for Future Work                                                                                  | 160            |

| Appendix A WKB METHOD                                                                                                | 161            |

| A.1 Hamilton-Jacobi Equation                                                                                         | 161            |

| A.2 Classical Limit                                                                                                  | 161            |

| A.3 ħ Expansion                                                                                                      | 162            |

| A.4 WKB Approximation                                                                                                | 163            |

| A.5 Validity of the WKB Approximation                                                                                | 164            |

| A.6 Matching                                                                                                         | 166            |

| A.7 Tunneling                                                                                                        | 168            |

| Appendix B TUNNELING THROUGH RECTANGULAR BARRIER                                                                     | 171            |

| Appendix C VARIATION METHOD                                                                                          | 175            |

| Appendix D CLASSICAL CHARGE MODEL | 177 |

|-----------------------------------|-----|

| REFERENCES                        | 180 |

## LIST OF TABLES

|                                                                 | Page |

|-----------------------------------------------------------------|------|

| Table 2.1 Parameters for electron tunneling and hole tunneling. | 39   |

| Table 2.2 Summary of gate dielectric parameters [74].           | 49   |

| Table 5.1 Traditional scaling methods [91].                     | 132  |

| Table 5.2 CMOS scaling predicted by the ITRS [2].               | 138  |

| Table 5.3 CMOS scaling beyond 65 nm [67].                       | 142  |

| Table 5.4 New materials for MOSFET transistor.                  | 147  |

## LIST OF FIGURES

|                                                                                                                                      | Page |

|--------------------------------------------------------------------------------------------------------------------------------------|------|

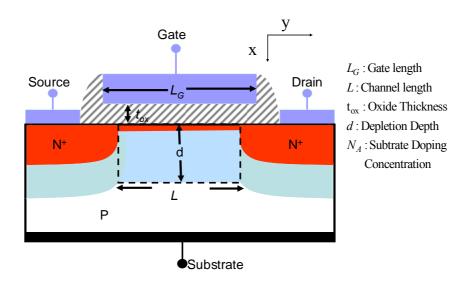

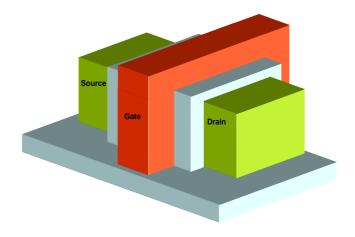

| Figure 1.1 Structure of a bulk MOSFET transistor.                                                                                    | 1    |

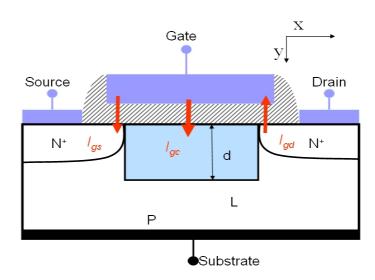

| Figure 1.2 Tunneling current in a MOSFET. $I_{gs}$ : tunneling between gate and source; $I_{gc}$ : tunneling between gate and drain. | 7    |

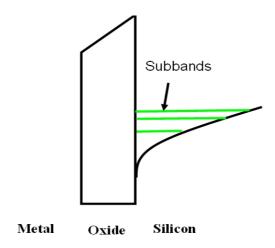

| Figure 1.3 Discrete energy levels due to quantization.                                                                               | 9    |

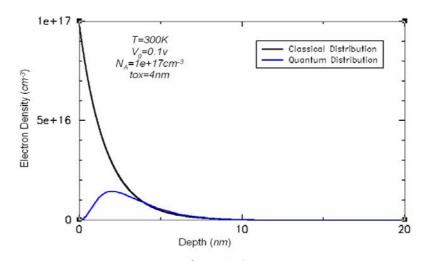

| Figure 1.4 Electron density profile calculated classically and quantum mechanically by SCHRED [32].                                  | 9    |

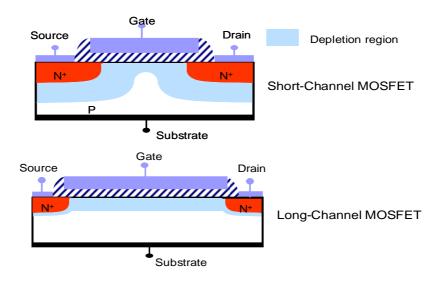

| Figure 1.5 Depletion charge distribution influenced by the source/drain in the short-channel MOSFET.                                 | 15   |

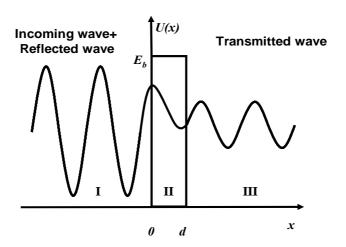

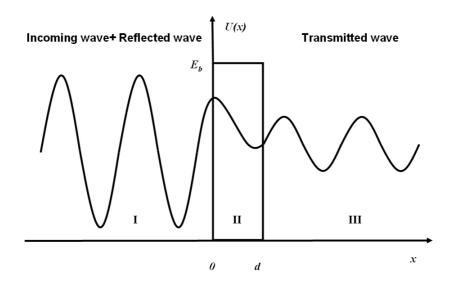

| Figure 2.1 Particle tunneling through a rectangular potential barrier of height $E_b$ and thickness $d$ .                            | 22   |

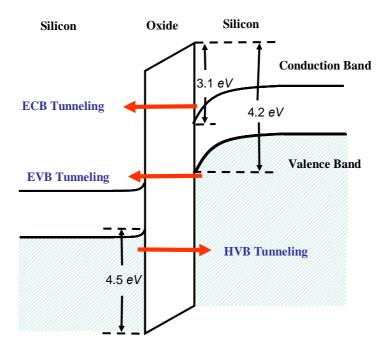

| Figure 2.2 Energy band diagram for tunneling components in an MOS structure.                                                         | 25   |

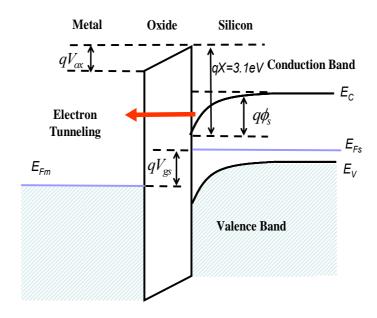

| Figure 2.3 Energy band diagram for electron tunneling in an MOS structure.                                                           | 26   |

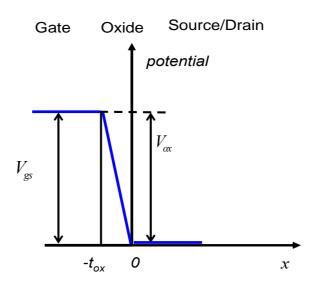

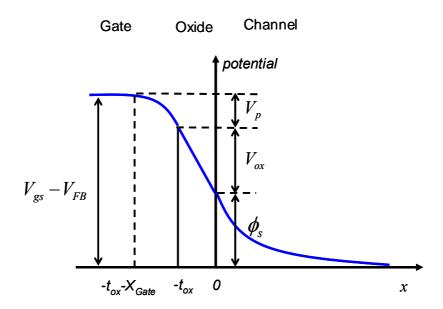

| Figure 2.4 Potential distribution in the gate-to-channel direction for a metal-gate MOSFET.                                          | 27   |

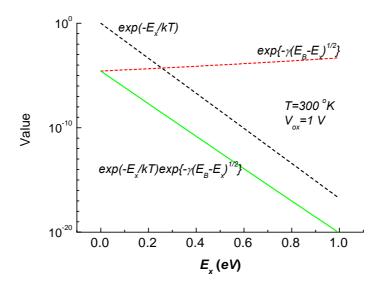

| Figure 2.5 Comparison of two terms in the tunneling integral of equation (2.34).                                                     | 34   |

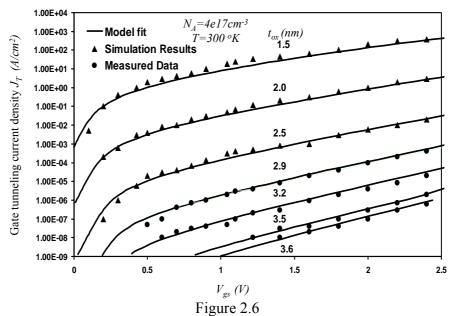

| Figure 2.6 Validation of the compact tunneling current model against numeric simulation and measurement [4, 5].                      | 37   |

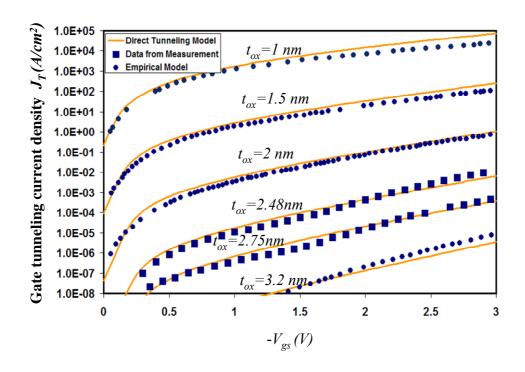

| Figure 2.7 Tunneling in the p-MOSFET (substrate doping $N_D = 4e17 \text{ cm}^{-3}$ ,                                                |      |

| $T = 300  ^{\circ} K$ ). The direct tunneling model is compared with an empirical model [15, 17] and measurement [15].               | 40   |

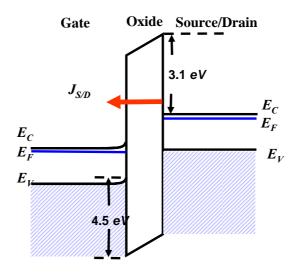

| Figure 2.8 Energy band diagram from the gate to the source/drain of an n-MOSFET.                                                     | 41   |

| Figure 2.9 Potential distribution from gate to source/drain.                                                                         | 42   |

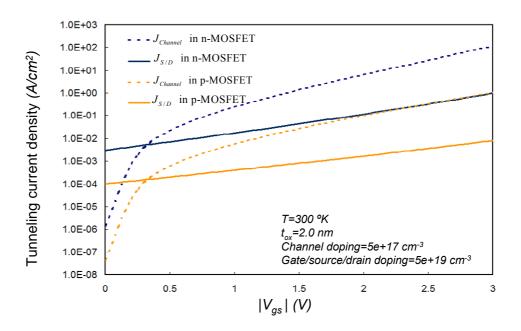

| Figure 2.10 Comparison of tunneling density in channel and source/drain region.                                                      | 44   |

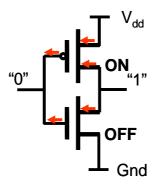

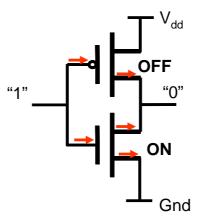

| Figure 2.11 Tunneling current in a CMOS inverter with a "0" input.                                                                   | 45   |

| Figure 2.12 Tunneling current in a CMOS inverter with a "1" input.                                                                   | 45   |

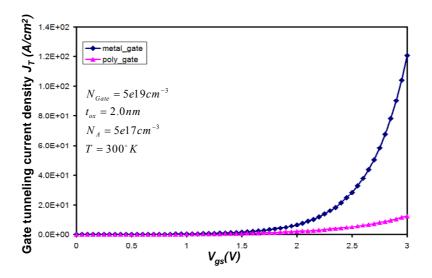

| Figure 2.13 Potential diagram for the poly-silicon gate MOSFET.                                                                      | 46   |

| Figure 2.14 Comparison of tunneling current density for aluminum gate and polycrystalline silicon gate.                              | 47   |

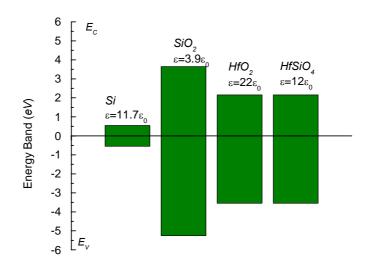

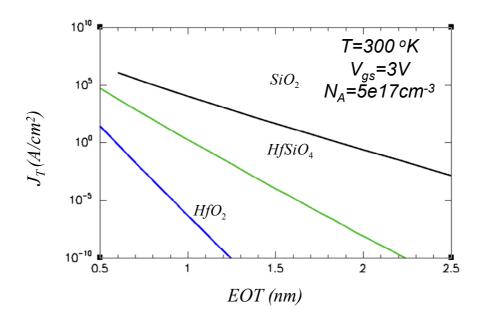

| Figure 2.15 Band gaps of high- $\kappa$ materials and silicon oxide [72].                                                            | 49   |

| Figure 2.16 Comparison of tunneling currents in different gate insulation materials: $SiO_2$ , $HfSiO_4$ , and $HfO_2$ .             | 50   |

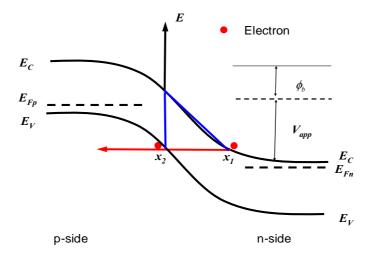

| Figure 2.17 Electron tunneling through the p-n junction from conduction band to valence band. $E_{Fn}$ and $E_{Fp}$ are referred to as Fermi energy levels in n-side and p-side semiconductors, respectively.                                                | 51 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

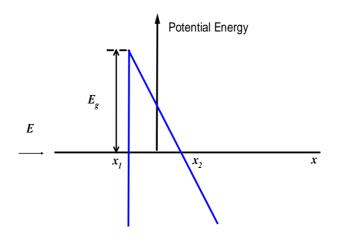

| Figure 2.18 Potential energy diagram for BTBT tunneling.                                                                                                                                                                                                     | 52 |

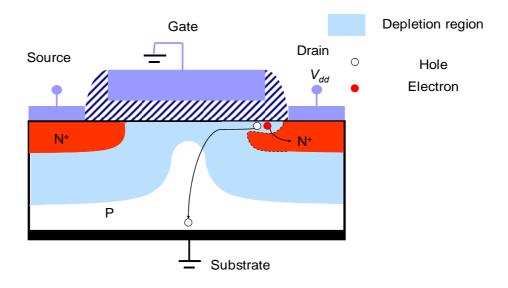

| Figure 2.19 Carriers generated by BTBT forming GIDL.                                                                                                                                                                                                         | 53 |

| Figure 2.20 Origins of gate-induced drain leakage: BTBT at the gate overlap of the heavily doped drain.                                                                                                                                                      | 53 |

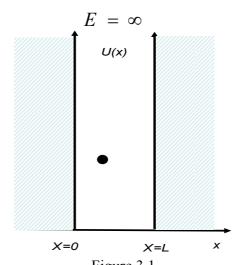

| Figure 3.1 A confined particle in an infinite potential well.                                                                                                                                                                                                | 58 |

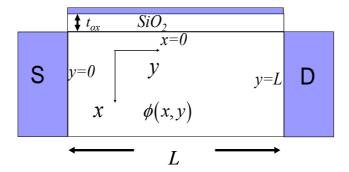

| Figure 3.2 Schematic view of MOSFET channel region.                                                                                                                                                                                                          | 60 |

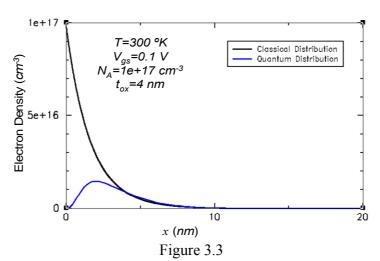

| Figure 3.3 Illustration of quantum and classical electron distributions along the channel depth direction using numeric simulation from SCHRED [32].                                                                                                         | 62 |

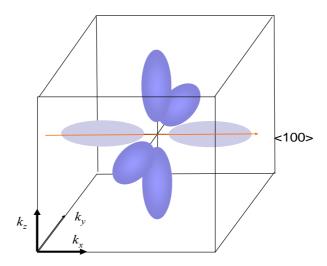

| Figure 3.4 Constant-energy surface forming six ellipsoids in a cubic crystal cell.                                                                                                                                                                           | 63 |

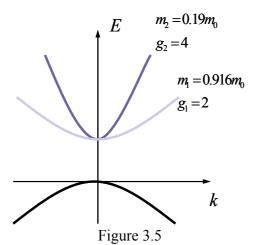

| Figure 3.5 Illustration of different effective electron masses in two conduction band valleys.                                                                                                                                                               | 64 |

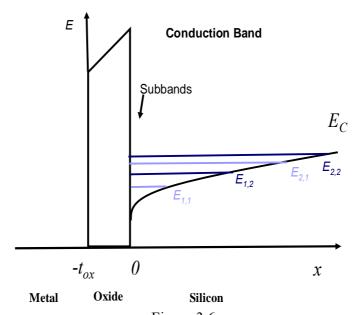

| Figure 3.6 Schematic diagram of typical subbands formation for electrons with different effective masses.                                                                                                                                                    | 65 |

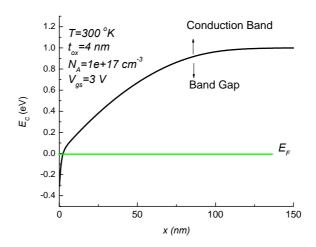

| Figure 3.7 Numerical results for conduction band bending in the <i>x</i> direction from SCHRED [32].                                                                                                                                                         | 66 |

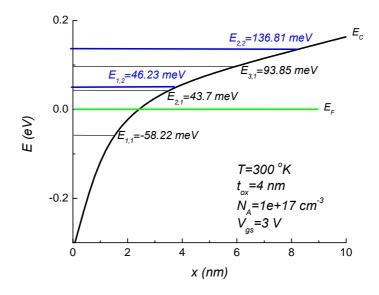

| Figure 3.8 Numerical results for subband energy levels from SCHRED [32].                                                                                                                                                                                     | 66 |

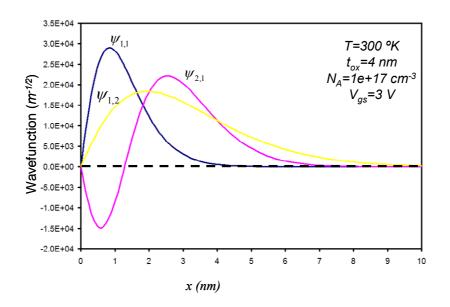

| Figure 3.9 Wavefunctions of subbands from simulation results of SCHRED [32].                                                                                                                                                                                 | 67 |

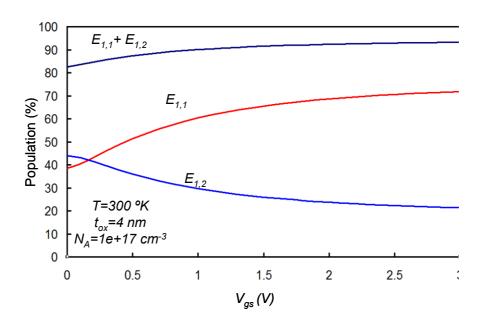

| Figure 3.10 Numerical results for carrier population on lowest two subbands from SCHRED [32].                                                                                                                                                                | 67 |

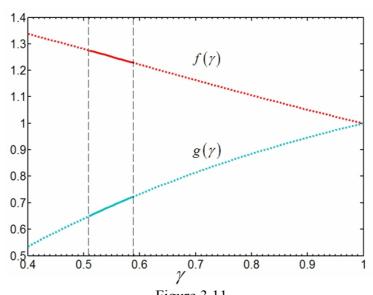

| Figure 3.11 Range of values for $f(\gamma)$ and $g(\gamma)$ .                                                                                                                                                                                                | 75 |

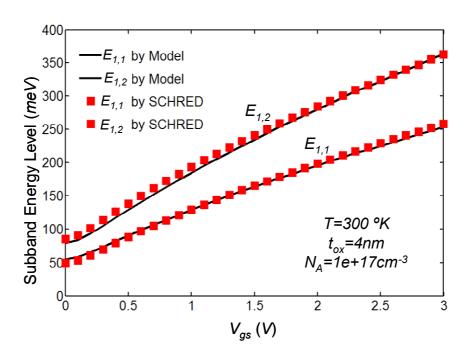

| Figure 3.12 Comparison of the quantized energy levels given by the model and by numerical simulation from SCHRED [32].                                                                                                                                       | 76 |

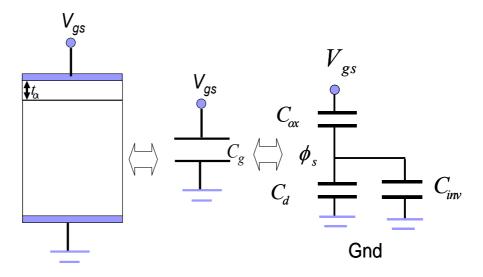

| Figure 3.13 Schematic view of the generic gate capacitance model.                                                                                                                                                                                            | 79 |

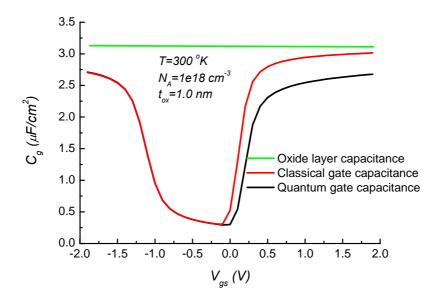

| Figure 3.14 Comparison of gate capacitance as predicted by the classical and quantum simulations with SCHRED [32]. A metal gate n-MOSFET with Fermi energy -4.0 <i>eV</i> referenced to vacuum is used here.                                                 | 81 |

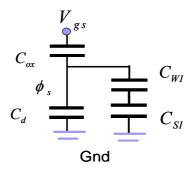

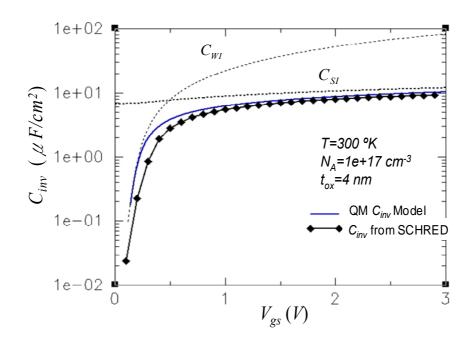

| Figure 3.15 Inversion layer capacitance $C_{inv}$ modeled as $C_{WI}$ and $C_{SI}$ in series.                                                                                                                                                                | 87 |

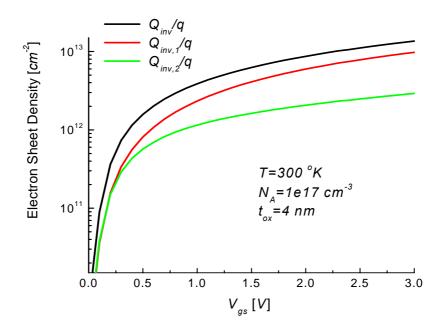

| Figure 3.16 Electron sheet density in the channel vs. $V_{gs}$ for n-MOSFET with metal gate workfunction -4.0 eV. Both substrate and drain are grounded.                                                                                                     | 89 |

| Figure 3.17 Inversion layer capacitance $C_{inv}$ and its components, $C_{WI}$ and $C_{SI}$ . An n-MOSFET with metal gate of -4.0 eV workfunction is considered here. Both substrate and drain are grounded. The $C_{inv}$ model is compared with simulation |    |

| results from SCHRED [32].                                                                                                                                                                                                                                    | 90 |

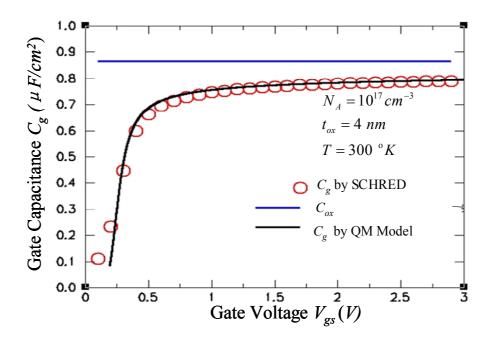

| Figure 3.18 Total gate capacitance $C_g$ dependency on gate voltage $V_{gs}$ , validated by SCHRED [32].                                                                           | 91  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

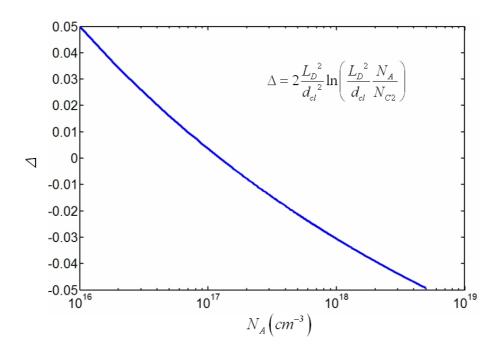

| Figure 4.1 Ratio of $2L_D^2 \ln \left( \frac{L_D^2}{d_{cl}} \frac{N_A}{N_{C2}} \right)$ and $d_{cl}^2$ as a function of doping.                                                    | 100 |

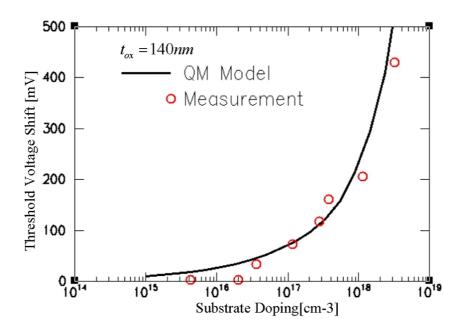

| Figure 4.2 Comparison of quantum mechanical threshold voltage shift model with measurement data [29].                                                                              | 102 |

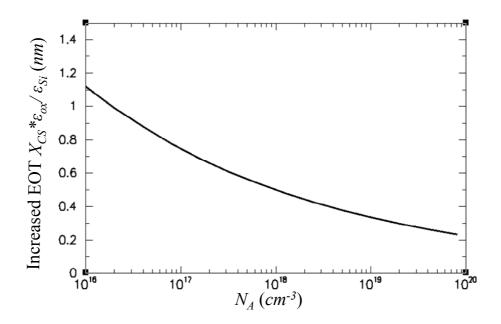

| Figure 4.3 Increased EOT from energy quantization of inversion charges.                                                                                                            | 106 |

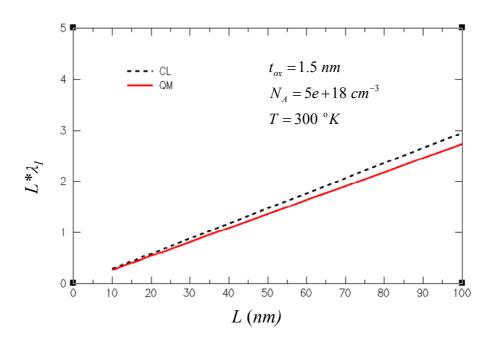

| Figure 4.4 Comparison of $L\lambda_1$ magnitudes in the quantum mechanical model and the classical model as a function of $L$ .                                                    | 110 |

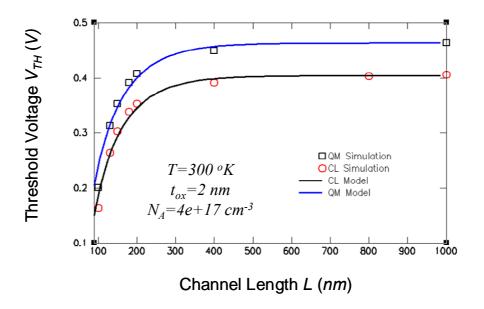

| Figure 4.5 Comparison of quantum mechanical threshold voltage model with simulation data from ISE TCAD as a function of $L$ [87].                                                  | 112 |

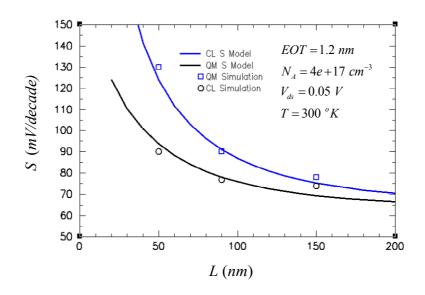

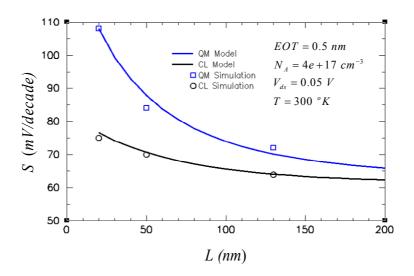

| Figure 4.6 <i>S</i> model including QMEs for short-channel devices of EOT= <i>1.2 nm</i> as 2004 technology. Simulation data from ISE TCAD [87].                                   | 116 |

| Figure 4.7 <i>S</i> model including QMEs for short-channel devices of EOT=0.5 <i>nm</i> as 2008 technology. Simulation data from ISE TCAD [87].                                    | 116 |

| Figure 4.8 Transregional current-voltage model [89] with quantum-mechanical modifications.                                                                                         | 124 |

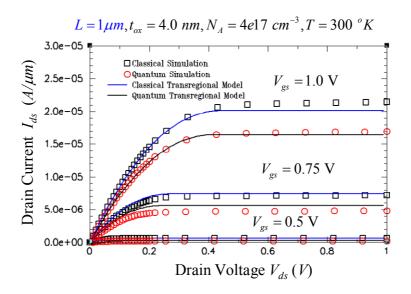

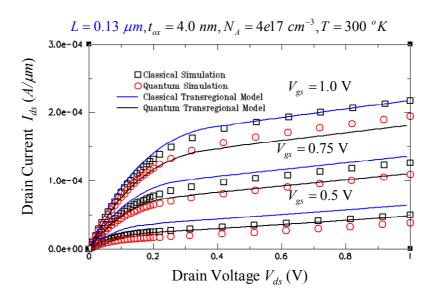

| Figure 4.9 Quantum mechanical drain current model compared with simulation data from ISE TCAD [87].                                                                                | 125 |

| Figure 4.10 Quantum mechanical drain current model compared with simulation data from ISE TCAD [87].                                                                               | 125 |

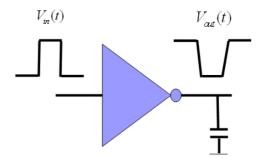

| Figure 4.11 Study of the inverter delay.                                                                                                                                           | 126 |

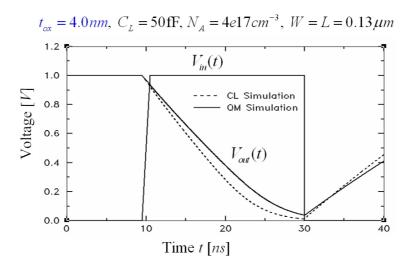

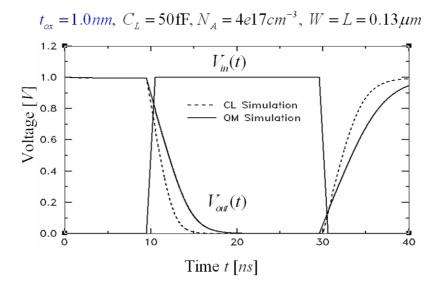

| Figure 4.12 Input/output waveform of the inverter with $t_{ox}$ =4.0 nm driving a fixed load capacitor. Propagation delay is measured as fall time from $V_{dd}$ to 0.5 $V_{dd}$ . | 127 |

| Figure 4.13 Input/output waveform of the inverter with $t_{ox}=1.0$ nm driving a fixed load capacitor. Propagation delay is measured as fall time from $V_{dd}$ to $0.5V_{dd}$ .   | 127 |

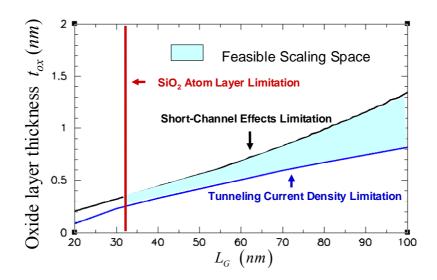

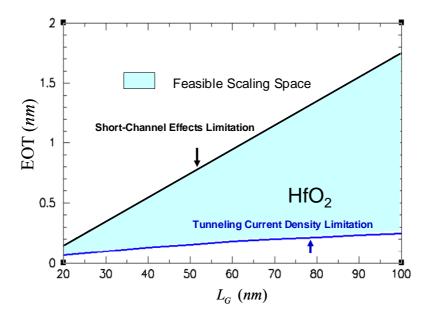

| Figure 5.1 Design space for conventional MOSFETs in future technology generations.                                                                                                 | 135 |

| Figure 5.2 Design space for MOSFETs using high- $\kappa$ gate dielectric in future technology generations.                                                                         | 135 |

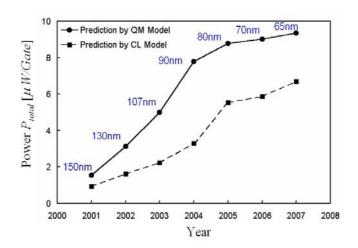

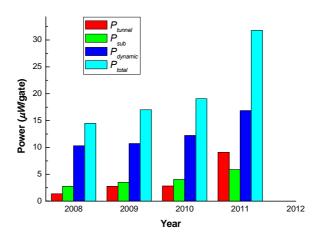

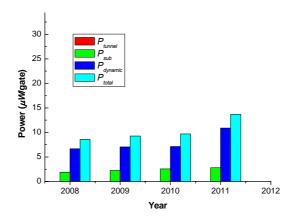

| Figure 5.3 Minimum total power $P_{total}$ ( $\mu w/gate$ ) projected by the performance-constrained Minimum Power Methodology [68].                                               | 139 |

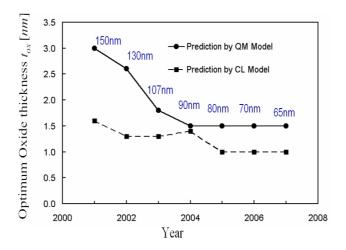

| Figure 5.4 Optimum gate oxide thickness projected by the performance-constrained Minimum Power Methodology [68].                                                                   | 139 |

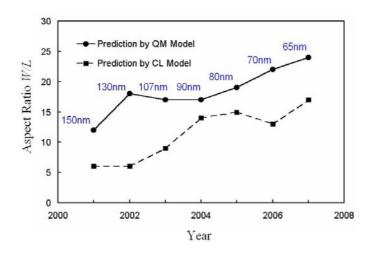

| Figure 5.5 Optimum aspect ratio projected by the performance-constrained Minimum Power Methodology [68].                                                                           | 140 |

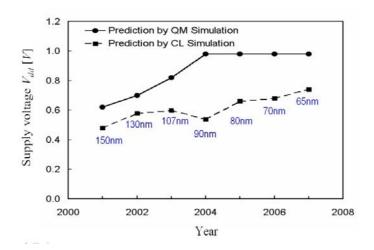

| Figure 5.6 Optimum supply voltage projected by the performance-constrained Minimum Power Methodology [68].                                           | 140 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.7 Power dissipation prediction for bulk MOSFETs with silicon oxide.                                                                         | 142 |

| Figure 5.8 Power dissipation predictions for bulk MOSFETs with high- $\kappa$ dielectrics.                                                           | 143 |

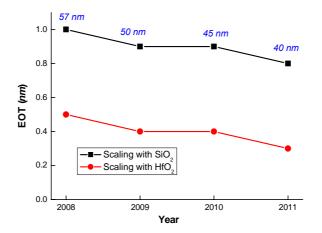

| Figure 5.9 EOT scaling with $SiO_2$ and $HfO_2$ gate dielectrics.                                                                                    | 143 |

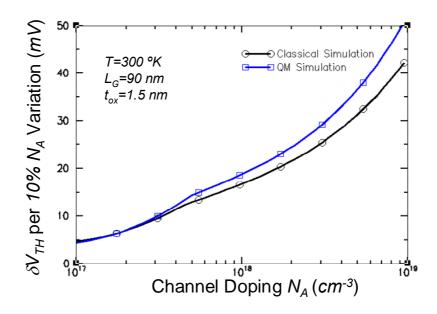

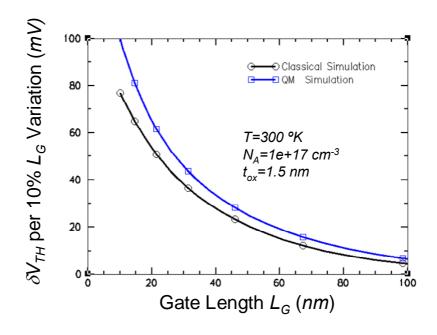

| Figure 5.10 Threshold voltage changes with 10% channel doping variation.                                                                             | 145 |

| Figure 5.11 Threshold voltage changes with 10% channel length variation.                                                                             | 145 |

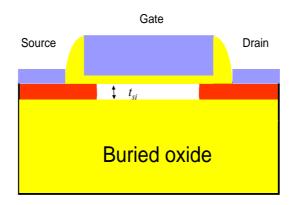

| Figure 5.12 Schematic of UTB SOI MOSFET structure.                                                                                                   | 148 |

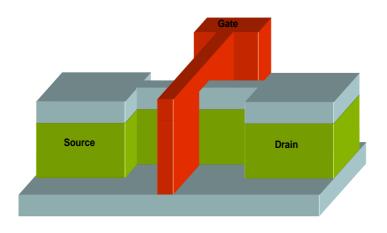

| Figure 5.13 FinFET structure.                                                                                                                        | 149 |

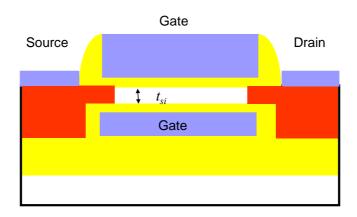

| Figure 5.14 Planer double-gate structure.                                                                                                            | 150 |

| Figure 5.15 Tri-gate structure.                                                                                                                      | 151 |

| Figure B.1 Diagram of wavefunction of a particle with energy $E$ tunneling through a rectangular potential barrier of height $E_b$ and thickness $d$ | 171 |

## LIST OF SYMBOLS AND ABBREVIATIONS

| d         | [cm] depletion depth                                                 |

|-----------|----------------------------------------------------------------------|

| $d_{cl}$  | [cm] depletion depth in classical model                              |

| $d_{qm}$  | [cm] depletion depth in quantum model                                |

| $g_m$     | transconductance                                                     |

| h         | Planck constant, 6.62617*10 <sup>-34</sup> J·s                       |

| k         | Boltzmann constant, 1.38066*10 <sup>-23</sup> J/K                    |

| m         | [g] mass                                                             |

| $m_0$     | electron rest mass, $0.911*10^{-27}g$                                |

| m*        | [g] effective mass                                                   |

| n         | free electron concentration                                          |

| $n_i$     | intrinsic electron density, $1.45*10^{10}$ cm <sup>-3</sup> at 300 K |

| q         | [C] electron charge                                                  |

| $t_{ox}$  | [cm] gate oxide thickness                                            |

| $t_{Si}$  | [cm] silicon body thickness                                          |

| $v_{sat}$ | [cm/s] saturation velocity                                           |

| $C_d$     | $[F/cm^2]$ depletion layer capacitance                               |

| $C_{inv}$ | $[F/cm^2]$ inversion layer capacitance                               |

| $C_g$     | $[F/cm^2]$ gate capacitance                                          |

| $C_{ox}$  | $[F/cm^2]$ oxide layer capacitance                                   |

| D         | tunneling probability                                                |

| $E_{Fm}$  | [eV] Fermi energy level of the gate material                         |

| $E_{Fs}$  | [eV] Fermi energy level of substrate                                 |

| $E_g$     | [ $eV$ ] silicon band gap, 1.12 $eV$ at 300 $K$                      |

| $E_b$     | [eV] potential barrier height                                        |

| $E_B$     | [eV] average barrier height                                          |

| $I_{ds}$               | [A] drain current                                                            |

|------------------------|------------------------------------------------------------------------------|

| $J_{sm}$               | $[A/cm^2]$ tunneling current density from channel to gate                    |

| $J_{ms}$               | $[A/cm^2]$ tunneling current density from gate to channel                    |

| $J_T$                  | $[A/cm^2]$ net tunneling current density                                     |

| L                      | [cm] channel length                                                          |

| $L_G$                  | [cm] gate length                                                             |

| $N_A$                  | [cm <sup>-3</sup> ] p-type doping concentration in substrate                 |

| $N_D$                  | [cm <sup>-3</sup> ] n-type doping concentration in substrate                 |

| $P_{dynamic}$          | [\(\mu W/gate\)] dynamic power                                               |

| $P_{static}$           | $[\mu W/gate]$ static power                                                  |

| $P_{sub}$              | $[\mu W/gate]$ subthreshold leakage power                                    |

| $P_{total}$            | $[\mu W/gate]$ total power consumption                                       |

| $P_{tunnel}$           | $[\mu W/gate]$ gate tunneling power                                          |

| $Q_{TH}$               | [cm <sup>-3</sup> ] sheet density of free carriers under threshold condition |

| S                      | [mV/decade] subthreshold swing                                               |

| T                      | [K] absolute temperature                                                     |

| $V_{ds}$               | [V] drain-to-source voltage                                                  |

| $V_{dsat}$             | [V] saturation voltage                                                       |

| $V_{FB}$               | [V] Flat-band voltage                                                        |

| $V_{gs}$               | [V] gate-to-source voltage                                                   |

| $V_{TH}$               | [V] threshold voltage                                                        |

| $V_{TH,CL}$            | [V] threshold voltage in classical model                                     |

| $V_{TH,QM}$            | [V] threshold voltage in quantum-mechanical model                            |

| $V_{\mathit{TH,long}}$ | [V] long-channel threshold voltage                                           |

| $\Delta V_{TH}$        | [V] threshold voltage roll-off                                               |

| $\Delta V_{TH,shift}$  | [V] threshold voltage shift                                                  |

| $arepsilon_0$          | dielectric constant of vacuum, $8.854*10^{-12} F*m^{-1}$                     |

| $\mathcal{E}_{Si}$            | [F/cm] dielectric constant of silicon, $11.8\varepsilon_0$        |

|-------------------------------|-------------------------------------------------------------------|

| $\mathcal{E}_{OX}$            | [F/cm] dielectric constant of silicon oxide, $3.9\varepsilon_0$   |

| $\phi_c$                      | [V] channel potential                                             |

| $\phi_{\scriptscriptstyle S}$ | [V] surface potential                                             |

| $\phi_B$                      | [V] difference between Fermi level and intrinsic level in silicon |

| $\mu_0$                       | $[cm^2/V \cdot s]$ low field mobility                             |

| $\mu_{	ext{eff}}$             | $[cm^2/V \cdot s]$ effective mobility                             |

| τ                             | [s] gate delay                                                    |

| χ                             | [V] modified electron affinity in silicon, 3.1 $V$                |

| Ψ                             | electron wavefunction                                             |

| ASIC                          | application-specific integrated circuit                           |

| BTBT                          | band-to-band tunneling                                            |

| CMOS                          | complementary metal oxide semiconductor                           |

| DIBL                          | drain induced barrier lowering                                    |

| FIBL                          | fringe induced barrier lowering                                   |

| GIDL                          | gate-induced drain leakage                                        |

| GSI                           | giga-scale integration                                            |

| MOS                           | metal oxide semiconductor                                         |

| MOSFET                        | metal-oxide-semiconductor field effect transistor                 |

| QME                           | quantum mechanical effect                                         |

| SCE                           | short-channel effect                                              |

| SDE                           | source and drain extension                                        |

| SOI                           | silicon-on-insulator                                              |

| UTB                           | ultra-thin-boday                                                  |

#### **SUMMARY**

As CMOS technology continuous to be aggressively scaled, it approaches a point where classical physics is insufficient to explain the behavior of a MOSFET. At this classical physics limit, a quantum mechanical model becomes necessary to provide thorough assessment of the device performance and scaling. This thesis describes advanced modeling of nanoscale bulk MOSFETs incorporating critical quantum mechanical effects such as gate direct tunneling and energy quantization of carriers.

In the gate tunneling analysis, an explicit expression of gate direct tunneling for thin gate oxides has been developed by solving the Schrödinger equation analytically. In addition, the impact of different gate electrode as well as gate insulation materials on the gate direct tunneling is explored. This results in an analytical estimation of the potential solutions to excessive gate leakage current.

The energy quantization analysis involves the derivation of a quantum mechanical charge distribution model by solving the coupled Poisson and Schrödinger equations. Based on the newly developed charge distribution model, threshold voltage and subthreshold swing models are obtained. A transregional drain current model which takes into account the quantum mechanical correction on device parameters is derived. Results from this model show good agreement with numeric simulation results of both long-channel and short-channel MOSFETs, thus validating the analysis

The models derived here are used to project MOSFET scaling limits. These limits of bulk MOSFETs are predicted according to various criteria, including circuit power and delay, device leakage current and the system uniformity requirement. Tunneling and quantization effects cause large power dissipation, low drive current, and strong sensitivities to process variation, which greatly limit CMOS scaling. Developing new materials and structures is imminent to extend the scaling process.

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Introduction and Background

For the last three decades, the semiconductor industry has strived to miniaturize the structure of the MOSFET, which is shown in Figure 1.1. Following Moore's Law [1], the size of the transistor is reduced by a factor of 0.7 each technology generation. According to the International Technological Roadmap for Semiconductors (ITRS) [2], the gate length ( $L_G$ ) of the MOSFET transistor will shrink to 30 nm in 2008, leading to 5 billion MOSFETs on one application-specific integrated circuit (ASIC) chip.

Figure 1.1 Structure of a bulk MOSFET transistor.

There are many reasons to pursue miniaturization including: (1) the cost per transistor is reduced as a MOSFET occupies less area; (2) more transistors can be

integrated on the chip, therefore, it can perform more complex functions; (3) capacitances are reduced, which in turn reduces the time and power required to switch a MOSFET. Despite its potential advantages, miniaturization presents a series of challenges to device design.

First, the power consumption of a system increases dramatically at high-frequency operation. Therefore, the heat generation by a high frequency silicon chip is tremendously high, and the cooling of the chip becomes difficult and, sometimes, practically impossible for some low-power applications. Supply voltage ( $V_{dd}$ ) reduction is an effective method to reduce the power consumption per device. However, lowering power supply voltage reduces the operational speed of MOSFETs. Hence, controlling power consumption has been a primary concern in MOSFET scaling. It has been found that in order to maintain the switching speed of a MOSFET, its threshold voltage ( $V_{TH}$ ) should be reduced at the same rate the supply voltage is reduced. However, low threshold voltage can lead to excessive subthreshold leakage current in a MOSFET. In addition, the threshold voltage is reduced by decreasing the oxide layer thickness ( $t_{ox}$ ) in a bulk MOSFET, which causes leakage through the gate oxide. Thus, the relationship between power consumption and operation speed is critical in obtaining optimal scaled devices.

Second, the MOSFET characteristics degrade with the reduction in size. Two key characteristics are threshold voltage ( $V_{TH}$ ) and subthreshold swing (S), known as short-channel effects (SCEs). Threshold voltage decreases and subthreshold swing increases because of two-dimensional (2-D) electrostatic charge sharing between the gate and the source-drain regions. Consequently, the on-to-off current ratio is reduced substantially, which results in a significant increase in standby power and compromised

overall performance. Additionally, SCEs exacerbate susceptibility to process variations. To scale down the channel length (L) without excessive SCEs, both the oxide thickness  $(t_{ox})$  and the gate-controlled depletion depth (d) should be reduced. For the 90 nm technology node,  $t_{ox}$  is 1.2 nm, corresponding to six atomic layers of silicon oxide [2, 3]. Further reducing  $t_{ox}$  is increasingly more difficult and will cause severe gate leakage [4-6].

Finally, classical physics is insufficient to understand fully the behavior of MOSFETs at small dimensions. The channel length of modern MOSFETs is approaching the mean distance between carrier collisions, with the oxide layer thickness reaching the dimension of a few atomic layers [4-7]. In this situation, significant deviation from the classical calculation is observed in the behavior of MOSFETs, which must be explained by quantum theory.

#### 1.2 Origin of the Problem

The fundamental distinction of quantum theory from classical physics is that infinitely small particles are treated as waves. Unlike the "solid billiards" with definite positions and velocities assumed in classical theory, particles in quantum theory are waves dispersed in space. This quantum mechanical description of a particle is represented by the wave function  $\psi(\vec{r})$ , such that the probability of finding the particle in the volume  $d\vec{r}^3$  is equal to  $|\psi(\vec{r})|^2 d\vec{r}^3$ . The wavefunction of a carrier in a semiconductor satisfies the Schrödinger Equation [8, 9]:

$$-\frac{\hbar^2}{2m_0}\nabla^2\psi + \left[U_C(\vec{r}) + V_E(\vec{r})\right]\psi(\vec{r}) = E\psi(\vec{r}), \tag{1.1}$$

where  $\hbar = h/\pi = 1.054 \times 10^{-34} J \cdot S$  is the reduced Planck constant,  $m_0 = 0.911 \times 10^{-27} g$  is the electron rest mass,  $U_C(\vec{r})$  is the periodic internal crystalline potential,  $V_E(\vec{r})$  is the external potential resulting from an applied electric field, and E is the energy of the carrier. If the dimension of the crystal is large compared to the atomic dimension, the external potential can be considered a small perturbation on the crystalline potential. Considering the crystalline potential only results in

$$-\frac{\hbar^2}{2m_0}\nabla^2\psi_C + U_C(\vec{r})\psi_C(\vec{r}) = E\psi_C(\vec{r}). \tag{1.2}$$

From Bloch's Theorem [9, 10], since  $U_C(\vec{r})$  is periodic with the periodicity of the lattice,  $U_C(\vec{r}) = U_C(\vec{r} + \vec{R})$ , there exists a wavevector  $\vec{k}$  (in  $[cm^{-1}]$ ) in the reciprocal lattice and a periodic function  $\varphi_k(\vec{r})$  such that  $\varphi_k(\vec{r}) = \varphi_k(\vec{r} + \vec{R})$  and  $\psi_C$  is of the form

$$\psi_C(\vec{r}) = \exp(i\vec{k}\cdot\vec{r})\varphi_k(\vec{k},\vec{r}).$$

(1.3)

The solution of equations (1.2) and (1.3) gives the relationship of energy versus the wavevector  $(E - \vec{k})$  relationship and, thereby, the band structure of semiconductors [9]. The movement of carriers follows the  $E - \vec{k}$  relationship, so that they can be considered as classical particles with the effective mass  $m^*$  (in [g]) given by

$$m^* = \frac{1}{\hbar^2} \left( \frac{d^2 E}{dk^2} \right)^{-1}.$$

(1.4)

With the effective mass, the motion of carriers under the applied field is handled by the classical method as

$$\vec{F} = -q\vec{E} = m^* \frac{d\vec{v}}{dt},\tag{1.5}$$

where the force  $\vec{F}$  (in [N]) is caused by the applied electric field,  $q = 1.602 \times 10^{-19} \ C$  is the electron charge,  $\vec{E}$  (in [V/cm]) is applied electric field,  $\vec{v}$  (in [cm/s]) is the velocity of an electron, and t (in [s]) is the time. Therefore, in a relatively weak external field, carriers comply with the classical theory from a macroscopic view and the quantum nature of the carriers is concealed by the effective mass approximation [9]. In this way, equation (1.1) is solved by two steps: numerically solving equation (1.2) for the  $E - \vec{k}$  relationship and the effective mass, and applying equation (1.5) for the motion of carriers in the external field.

However, such simplification does not apply when the dimension is extremely small and the external field is large. In this case, the external field cannot be considered as a small perturbation. Carriers exhibit their quantum mechanical properties in the external field and the wave-like behavior, such as tunneling through a potential barrier and energy quantization in a potential well, can be directly observed. Corrections should be introduced to account for these quantum-mechanical effects (QMEs) in the places where potential energy changes sharply. For that reason, it is necessary to deal with the external field quantum mechanically, which is given by [9] as

$$-\frac{\hbar^2}{2m^*}\nabla^2\psi_E + V_E(\vec{r})\psi_E(\vec{r}) = E\psi_E(\vec{r}). \tag{1.6}$$

Equation (1.1) is then simplified into two equations as

$$-\frac{\hbar^2}{2m_0}\nabla^2\psi_C + U_C(\vec{r})\psi_C(\vec{r}) = E\psi_C(\vec{r}), \qquad (1.7)$$

and

$$-\frac{\hbar^2}{2m^*}\nabla^2\psi_E + V_E(\vec{r})\psi_E(\vec{r}) = E\psi_E(\vec{r}). \tag{1.8}$$

Therefore, the quantum effects induced by the external fields can be handled separately from crystalline potential, and the simplicity of effective mass approximation is preserved.

As MOSFETs are scaled down for Giga-Scale Integration (GSI) [11], quantum effects need to be considered in MOSFET design and modeling [2]. In today's CMOS technology, the gate oxide thickness of a MOSFET is less than 1.5 nm, and the channel is doped as high as 1e18 cm<sup>-3</sup> [3, 12]. For MOSFETs with heavily doped channels and ultra-thin oxide layers, the field in the oxide can reach a maximum of 5 MV/cm, while the field in the silicon region routinely exceeds 1 MV/cm [6]. The combination of the ultra-thin oxide layer and the heavily doped channel invalidates the accurate modeling of MOSFETs solely by classical physics, and the QMEs of the device must be taken into account. The ultra-thin oxide layer reduces the width of the energy barrier that separates the gate from the channel, thus making it easier for electrons to tunnel through the insulator layer [13-20]. Tunneling also occurs at the source/drain extension region overlapping with the gate, making a leakage in addition to the subthreshold current, as shown in Figure 1.2. This direct gate tunneling current could be the dominant source of device leakage, leading to faulty circuit operation and the increase in standby power in the MOSFET. Additionally, band-to-band tunneling (BTBT) is caused by electrons crossing a reverse biased p-n junction from the p-side valence band to the n-side conduction band [21, 22]. In a MOSFET it is manifested both as gate-induced drain leakage (GIDL) in the drain-gate overlap region and reverse-biased junction leakage in the halo-implanted region [23, 24]. As the channel length is scaled down to 10 nm and

below, it is expected that the source-to-drain tunneling will dramatically affect performance. Theoretical studies and simulations show that the source-to-drain tunneling dominates off-current at  $L < 10 \ nm$  and sets an ultimate scaling limit [25, 26].

Figure 1.2 Tunneling current in a MOSFET.  $I_{gs}$ : tunneling between gate and source;  $I_{gc}$ : tunneling between gate and drain.

In addition, energy quantization occurs in the channel near the interface of the oxide layer and the silicon channel because of the presence of the strong electric field [5, 6, 27, 28]. As illustrated by Figure 1.3, quantization leads to the splitting of the continuous energy band and the formation of subbands with a two-dimensional (2-D) density of states in each one [4, 6, 28-31]. Because of the smaller density of states in the 2-D system, the net sheet charge density of carriers in the channel is lower than that calculated from the classical (3-D) case, as shown in Figure 1.4 [32]. Thus, it requires a

larger gate voltage to generate the same charge sheet density in the 2-D inversion layer as that in the corresponding 3-D case. Consequently, the threshold voltage increases when energy quantization is considered [29, 33]. The laws of quantum mechanics force the carrier density to vanish at the silicon/silicon oxide interface, whereas the carrier density reaches its peak value at the interface according to classical theory. Therefore, the overall distribution of carriers is effectively displaced toward the substrate by the quantization effect. This displacement results in a capacitance in series with the oxide layer capacitance. In sub-90 nm technologies, where the finite inversion layer thickness can be a significant fraction of the physical oxide thickness, the inversion layer capacitance causes a considerable discrepancy between the oxide capacitance and the measured gate capacitance [2]. For a MOSFET in the superthreshold region, the reduced gate capacitance [34] lowers the transconductance and the drive currents [35]. For MOSFETs in the subthreshold region, the reduced gate capacitance resulting from QME increases the short-channel effects. Therefore, since device behavior is noticeably affected, it is important to account for the quantum-mechanical effects in the design of sub-90 nm devices [36-39]. In this operational regime, classical models are inadequate and will lead to erroneous and misleading predictions of critical device structure and electrical behavior parameters, such as the physical oxide thickness, threshold voltage, drive current, gate capacitance, and subthreshold swing.

Figure 1.3 Discrete energy levels due to quantization.

Figure 1.4 Electron density profile calculated classically and quantum mechanically by SCHRED [32].

#### 1.3 Historical Review of QME Modeling

Accurately modeling tunneling and quantization in MOSFETs requires the multidimensional solution of the Schrödinger and Poisson equations. A lot of work [4, 5, 13, 40-45] has been devoted to develop algorithms for accurate numeric solutions of these equations. However, from a circuit modeling point of view, a one-dimensional analytical solution is sufficient to account for the quantum-mechanical correction in the classical transport framework of drift-and-diffusion models [46, 47]. Furthermore, analytical solutions are preferable because of their simplicity in format and fast computational speed. With these analytical solutions, compact physical models can be obtained that estimate QMEs on the device comprehensively, making it easy to predict device scalability and circuit performance for future technology generations.

#### 1.3.1 Gate Direct Tunneling

The gate direct tunneling problem in MOSFETs was first addressed by H. S. Momose et al. [48] in 1994 when a high-performance MOSFET was fabricated with a 1.5 nm thin oxide layer. Although high transconductance is obtained by reducing the gate oxide thickness in this device, large gate direct tunneling current is observed. Therefore, it is important to investigate the reduction of gate oxide thickness below the tunneling limit in small gate length MOSFETs, as it pertains to better current drive and transconductance [48].

Various gate direct tunneling models were developed using numeric methods such as Bardeen's approach [18], the resonant transfer matrix method [4, 5], and transparency-based approximations [16, 49]. All results reveal the exponential dependence of the gate direct tunneling on gate oxide thickness and show how the

standby power consumption restricts the gate direct tunneling current, presenting a severe limitation on the gate oxide thickness [6]. Although these models qualitatively indicate that excessive leakage aroused by gate direct tunneling potentially degrades circuit performance, their time-consuming numeric computations makes them impractical for a circuit simulation. Choi [13] studied in detail the impact of the tunneling current in different CMOS circuits by applying the macro-circuit model, which relies on the extracted tunneling current data from the device simulation of a single MOSFET. The results show increased delay and power consumption in both static and dynamic logic CMOS circuits. They also show erroneous switching in dynamic logic circuits caused by gate tunneling current. However, this model is inadequate for providing further information on how to optimize circuit and device design because of the time-consuming device simulation. Instead of using data extraction from numeric simulations, the semi-empirical tunneling model given in [14, 15, 50] is formulated as an analytical expression of terminal voltages. Although this model provides excellent accuracy for a large variety of operating conditions and is therefore convenient for circuit simulation and design, the empirical parameters are not consistent among technology generations. The deficiency of the detailed physics of tunneling makes these models unsuitable for long-term projection of the impact of gate direct tunneling on device scaling [51].

#### 1.3.2 Energy Quantization

The phenomenon of inversion charge quantization has been observed for decades, but its influence on device performance has been addressed only recently. Early research on quantization in the 1970s [52] focused on the computation of electron energy levels and the inversion charge distribution of the 2-D gas on subbands. Fang and Howard [53]

use the single-electron assumption that all electrons in the channel are deemed equal and the energy levels of the electron gas are the same as those of one electron by accounting for the applied field and electron-electron repulsion. This approach simplifies the calculation and the problem is reduced to calculating the single electron energy levels in a potential well. They also approximate the channel as a triangular potential well to simplify the calculation of the quantized levels, regardless of the fact that the triangular shape does not resemble the potential distribution in the channel in a MOSFET. Stern [52] uses a more accurate variational method to solve the coupled Schrödinger and Poisson's equations, giving the analytical expression of the quantized energy levels. Their results show the two distinctive differences of between the quantum-mechanical solution and the classical models: (1) the channel carriers are distributed among discrete energy levels with 2-D density of states instead of the single continuous energy band with 3-D density of states; (2) the peak of the space carrier concentration is located some distance away from the surface of the substrate, which leads to a finite thickness of inversion layer. Although these works elucidate the fundamental changes in the carrier distribution induced by the quantization effect, it is unclear how the performance of a MOSFET is affected. Further research is needed to extend this physical analysis into MOSFET voltage and current models for device and circuit design. Consequently, it is necessary to incorporate quantization analysis in the capacitance-voltage (C-V) and current-voltage (I-V) characteristics.

#### 1.3.3 Gate Capacitance Degradation

Inversion charges are characterized by the inversion layer capacitance  $C_{inv}$  (in  $[F/cm^2]$ ), which is defined as the variation of the inversion charge sheet density  $Q_{inv}$

(in  $[C/cm^2]$ ) with respect to the surface potential of the channel  $\phi_s$  (in [V]), i.e.  $C_{inv} = \frac{\partial Q_{inv}}{\partial \phi}$ . Classical theory assumes that inversion charges are concentrated beneath the gate oxide forming a very thin layer, so that  $C_{inv}$  is much larger than the gate oxide capacitance  $C_{ox}$  (in  $[C/cm^2]$ ). Consequently, the gate capacitance  $C_g$  (in  $[C/cm^2]$ ), the series combination of  $C_{inv}$  and  $C_{ox}$ , is almost equal to  $C_{ox}$ . However, it has been observed that  $C_g$  could be notably smaller than  $C_{ox}$  in MOSFETs with the ultra-thin oxide layers [28, 31, 35, 54]. This discrepancy can be explained by the highly reduced  $C_{inv}$ , which is induced by the finite inversion layer thickness, observed on the quantum mechanical analysis. It is proven by Takagi's experiments [54] that in strong inversion,  $C_{inv}$  changes linearly with only  $Q_{inv}^{-1/3}$ ,  $C_{inv} \propto Q_{inv}^{-1/3}$ , not following  $C_{inv} \propto Q_{inv}$  as predicted by the classical model [10]. The simulation results by Hareland [27, 55] coincide with the experiments. The gate capacitance attenuation in the superthreshold region is often referred to as transconductance  $(g_m)$  degradation [6, 31, 54-56], since  $g_m$ is approximately  $g_m = \frac{W}{L} \mu C_g$ . Similarly,  $C_g$  reduction is observed in the subthreshold region [30, 57, 58]. As a result, subthreshold swing (S) becomes larger, indicating worse turn-off characteristics.

An "effective oxide thickness" is introduced to compensate for the absence of inversion layer capacitance in current circuit simulation tools [2, 55, 59]. However, this effective oxide thickness is obtained from the measurement of the manufactured MOSFET and therefore it is difficult to project the future scalability of the device. Furthermore, such simplification fails to take into account the fact that  $C_{inv}$  varies with

gate voltage. An accurate physical model of  $C_{inv}$ , including the quantization effect, yields valuable insights, allowing for projections of the optimal scaling of device parameters such as voltage and oxide layer.

#### 1.3.4 Threshold Voltage Shift

The 2-D carrier distribution of the subbands and discrete energy levels lead to a reduced charge sheet density compared to the classical calculation. Therefore, extra band bending is required for an increase in channel carrier density. Van Dort [29] found that the calculated threshold voltage in highly doped MOSFETs deviates from experiments. He observed that this threshold voltage deviation results from the energy quantization in the highly doped channel. Specifically, he observed that the lowest quantized energy states for inversion charges rise up from the conduction band bottom, causing an effective "band-gap broadening" [29]. Although this model properly attributes the threshold voltage shift to the energy quantization, it still treats the inversion charges as a 3-D system. The decreased density of states for inversion charge, i.e., from the higher 3-D density to the lower 2-D density, has not been accounted for in his model.

#### 1.3.5 Short-Channel Effects and Quantum Mechanical Effects

When the channel length of the MOSFET is reduced, depletion charges in the channel region are apt to be influenced by the drain as much as by the gate, as shown in Figure 1.5. The barrier preventing the carriers in the source from leaking into the channel is lowered by the drain voltage, which is usually referred to as drain-induced barrier lowering (DIBL) [60, 61]. Because of the undesirable coupling between the channel and the drain region, the threshold voltage is reduced, and the subthreshold swing is increased

for a transistor with shorter channel length. Such short-channel effects, which degrade the off-state performance of MOSFETs and increase the sensitivity to dimensional variations, are critical to modern device design [6, 62, 63].

Figure 1.5

Depletion charge distribution influenced by the source/drain in the short-channel MOSFET.

The analysis of SCEs in miniaturized devices demands the 2-D electrostatic potential profile, which is obtained by solving the 2-D Poisson equation. Previous analytical solutions, without considering the QMEs [61, 63], indicate that the DIBL is highly dependent on the depletion depth and the gate oxide thickness. The energy quantization of carriers increases the depletion depth required at the threshold condition, giving rise to greater DIBL effects [64]. Although the 1-D solution of Poisson's equation and Schrödinger's equation leads to the predictive result that SCEs are influenced by the

presence of QMEs, quantitative analysis should deal with the 2-D Poisson equation while simultaneously considering the charge distribution quantum mechanically. The majority of the research on QMEs is based on the solution of the coupled 1-D Poisson equation and 1-D Schrödinger equation that does not handle the 2-D geometry of short-channel devices. Numeric solutions of the 2-D Poisson equation and Schrödinger equation [40, 44] provide results showing that QMEs aggravate SCEs quantitatively. However, there is still not enough insight into the interrelationship of QMEs and SCEs and their dependency on physical parameters.

#### 1.3.6 I-V Characteristics

Because of prominent changes in device characteristics resulting from QMEs, it is useful to develop a compact MOSFET drain current (I-V) model for circuit simulations which accounts for the underlying QMEs. Recent numerical simulations [41, 44, 57, 65] as well as theoretical studies [56] clearly show that QMEs change the charge distribution and, thereby, play an important role in drain current for a state-of-the-art MOSFET. Unfortunately, these works fail to provide an explicit expression for the drain current, making them difficult to employ for the circuit simulation of future technology generations. These works, however, show no obvious alteration for electron transport resulting from QMEs. Thus, it is reasonable to develop a quantum-mechanical I-V model by combining the quantum mechanical carrier distribution with the classical carrier transport based on the Boltzmann transport equation [46, 47, 66].

#### 1.3.7 Scaling Limits Projection

As predicted by the ITRS roadmap [67], the MOSFET must be scaled down by various modes to meet the continuous demand for higher speed, integratability, and lower

power consumption, etc. The ITRS [67] specifies the different design targets as low power, high speed, low standby power for different applications of future systems. Different scaling methodologies have been developed for each criterion. The Minimum Power Methodology [68] has been proposed to minimize the power consumption under the constraint of circuit delay. Frank [62] found the multiple device scaling limits by minimizing SCEs with various constraints of low, medium, and high power consumption. Following these methodologies and criteria, the device parameters in future technology generations can be predicted according to the projected circuit/system performance.

The absence of QMEs in the previous scaling methodologies makes them inappropriate for the projection of sub-90~nm technologies, in which QMEs become dominant impeditive factors. Energy quantization reduces the control of SCEs, leading to degradation of the performance including worse system uniformity and severe leakage in the VLSI system [6]. The conventional scaling method, shrinking the insulator layer to suppress SCEs [6, 11, 62, 63], induces the prohibitively large gate tunneling current in MOSFETs. Therefore, the circuit/system functionality and performance in future generations must be re-examined, including the influence of QMEs. New technologies, such as high-permittivity (high- $\kappa$ ) dielectrics, proposed to cope with excessive tunneling current and to extend the scaling limit of MOSFETs, can also be evaluated through quantum-mechanical models.

#### 1.4 Scope and Organization

With MOSFET scaling being challenged by quantum mechanical effects, nanoscale device modeling which incorporates them is critical to assist in device design as well as to understand the scaling limits. The compact physical model provides insight

into both the characteristics of modern semiconductor device and circuit performance under the influence of QMEs. Simulation based on the compact physical models reduces the cost of developing a novel technology and shortens the time-to-market. They may also be utilized to explore innovative device structures.

This thesis focuses on critical QMEs of bulk MOSFETs in the sub-90 nm regime. The main objective is to develop physics-based MOSFET device models including direct gate direct tunneling and energy quantization of the carriers. By applying the physical device models, we are able to investigate the impact of QMEs on device characteristics and circuit/system performance and therefore reveal the remaining potential of CMOS technologies under QMEs.

Chapter 2 is devoted to a thorough examination of gate tunneling in ultra-thin oxide MOSFETs. Gate tunneling equations are derived from the solution of the Schrödinger equation. This model considers both electron and hole tunneling in MOSFETs. In addition, the impact of the polysilicon gate depletion and high- $\kappa$  gate insulators on gate tunneling is discussed.

Chapter 3 describes the energy quantization of the carriers in the channel. The quantization model is based on the analytical solution of coupled Schrödinger and Poisson equations by the variational method. Enforced by the quantization effect, carriers are distributed on the discrete subbands instead of the continuous energy band depicted by classical theory. This deviation from the classical theory critically affects the relationship between the density profile of inversion charges and the gate electrode voltage. A compact model of the *C-V* characteristic is presented by considering the energy quantization effect on carrier distribution.

In Chapter 4, compact models of various device parameters incorporated with the energy quantization effect are derived. Key device parameters, such as threshold voltage and subthreshold swing, are rederived based on the quantum-mechanical distribution of carriers. Their susceptibility to energy quantization effects is discussed in long and short channel MOSFETs. The influence of the energy quantization on SCEs is revealed by comparing the performance of short-channel and long-channel devices. These models are subsequently integrated into the comprehensive *I-V* model.

In Chapter 5, the different criteria according to various limiting factors in MOSFET scaling are exploited to predict the minimum size of MOSFETs. The hierarchical scaling limits at the device, circuit, and system levels are investigated using a quantum mechanical model. Predictions based on the classical and quantum models are compared to unveil the roles played by QMEs in future technological generations. The high- $\kappa$  gate dielectric, which could potentially be used to reduce the tunneling current, is examined against silicon dioxide in MOSFET scaling. Extension of the scalability of bulk MOSFETs by adopting new materials and structures is also discussed.

Chapter 6 summarizes the findings of this research and suggests possible areas for further investigation.

#### **CHAPTER 2**

#### **TUNNELING**

#### 2.1 Introduction and Background

MOSFETs are scaled down with the purpose of enhancing performance and accommodating more devices within the same solid-state real estate. This increases the device capacity per wafer, which cuts the manufacturing cost per transistor resulting in higher profits. For over thirty years, the feature size of a MOSFET has been reduced thanks to the progress in lithography at the rate of  $0.7\times$  every three years [1, 39]. Such aggressive scaling of CMOS technology is becoming progressively more difficult because of undesirable physical effects in small devices.

The scaling of MOSFETs is performed in both the vertical and the lateral directions. The lateral shrinking is performed to obtain a shorter gate length and a higher packing density, while the vertical scaling is necessary to maintain the MOSFET's functionality in view of lateral scaling. When bulk CMOS technology evolves from one generation to the next, the channel doping concentration is increased and the gate oxide thickness is reduced to mitigate subthreshold leakage currents and manage SCEs [5, 69, 70]. This process of scaling CMOS has worked well for over the last couple of decades. For gate lengths below *90 nm*, the gate oxide thickness is estimated to be less than *2 nm* [2]. In a MOSFET with such ultra-thin oxides, the direct tunneling current is expected to contribute significantly to the leakage current [48].

In this chapter, an analytical model of gate direct tunneling is developed, for both electrons tunneling in the conduction band and the holes tunneling in the valence band. Section 2.2 introduces the basic theory of tunneling. In Section 2.3, the gate tunneling

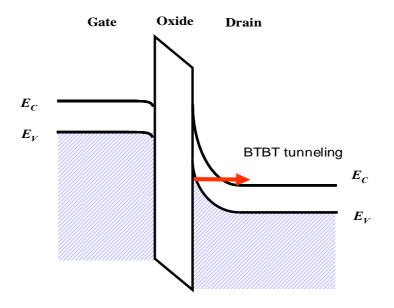

model in an MOS structure for both n-MOSFETs and p-MOSFETs is derived. Section 2.4 presents the detail tunneling profile in a MOSFET, specifying the tunneling in the channel region and the source/drain region. In Section 2.5, the tunneling currents of metal gate and polycrystalline silicon gates are compared. Section 2.6 examines the tunneling current in a MOSFET with a high-permittivity gate dielectric expected to be used in future technology generations. Section 2.7 investigates junction tunneling such as the band-to-band tunneling and the gate-induced drain leakage in MOSFETs. The conclusion is given in Section 2.8.

# 2.2 Tunneling Theory

The quantum-mechanical concept states that all matter, including electrons, behaves like both particles and waves [8]. Particles can be described by a wavefunction  $\psi(x,y,z)$ , such that the probability of finding a particle in the volume dxdydz is equal to  $|\psi(x,y,z)|^2 dxdydz$ . The electron wave function satisfies the Schrödinger equation,

$$-\frac{\hbar^2}{2m}\nabla^2\psi(x,y,z)+U(x,y,z)\psi(x,y,z)=E\psi(x,y,z),$$

(2.1)

where  $\hbar = h/2\pi$  is the reduced Planck constant, m is the electron mass, U is the potential energy, and E is the energy of the particle. The quantitative analysis of tunneling should be based on the solution of the Schrödinger equation. Figure 2.1 shows the simplest case where an electron of energy E is in the space with the rectangular potential barrier, where the barrier height is  $E_b$  (in [eV]) and the width is d (in [cm]). In the x direction, the Schrödinger equation can be written in different regions as follows:

$$d^2\psi / dx^2 + k_I^2 \psi = 0$$

for  $x < 0$  (2.2)

$$d^2\psi / dx^2 + k_{II}^2\psi = 0$$

for  $0 \le x \le d$  (2.3)

$$d^2\psi / dx^2 + k_{III}^2\psi = 0$$

for  $x \ge d$  (2.4)

where

$$k_I^2 = k_{III}^2 = \frac{2mE}{\hbar^2},$$

$$k_{II}^2 = n_b^2 k_I^2,$$

and

$$n_b^2 = \frac{(E - E_b)}{d}.$$

Figure 2.1 Particle tunneling through a rectangular potential barrier of height  $E_b$  and thickness d.

From the solution of the Schrödinger equation (see Appendix B), the tunneling probability is given by

$$D(E) = \exp\left\{\frac{-2[2m(E_b - E)]^{1/2} d}{\hbar}\right\}.$$

(2.5)

This formula shows that greater values of barrier height and width help to prevent tunneling, and particles with higher kinetic energy are more likely to tunnel through the barrier.

### 2.3 Tunneling in MOSFET

According to the tunneling theory, the width of the potential barrier is an important parameter determining the magnitude of the tunneling probability. In MOSFETs, the gate dielectric plays the role of a potential barrier separating the carriers in the channel from the gate. With a thick gate dielectric layer, the wavefunction of carriers cannot extend to the gate by penetrating the potential barrier. However, in MOSFET scaling the thickness of the gate dielectric must be decreased along with the channel length to enhance the gate control, avoiding short-channel effects and transconductance degradation. As devices continue to scale down, tunneling through the thin oxide has become a limiting factor. For the conventional bulk MOSFET using  $SiO_2$  as the gate dielectric, with oxides thinner than 2 nm, massive numbers of carriers can tunnel through and form a significant gate current. While the gate leakage current may be negligible compared to the drain current of a device, it will substantially increase the chip standby current [2, 6]. Moreover, gate tunneling occurs not only in the channel region, but also in the regions where gate overlaps with the source/drain regions. When the MOSFET is in the off-state, there is still considerable tunneling current along the leakage

path between the biased drain and gate electrodes. Such a leakage greatly degrades the performance of CMOS circuits [13, 15].

Figure 2.2 shows the three gate tunneling components as electron conduction band (ECB) tunneling, electron valence band (EVB) tunneling, and hole valence band (HVB) tunneling [14, 15]. ECB tunneling in the n-MOSFET and HVB tunneling in the p-MOSFET are the dominant tunneling sources, because electrons and holes are majority carriers in the inverted n-MOSFET and p-MOSFET channels, respectively [14]. EVB tunneling takes place only when the valence band transmitting the electrons overlaps with the conduction band receiving electrons, as indicated by Figure 2.2. The overlap requires a high gate voltage, exceeding the normal operating voltage of digital CMOS circuits [14, 15, 17], which makes EVB tunneling negligible for circuit simulation. Based on this reason, EVB tunneling is not included in the work presented in this thesis. For simplicity, ECB and HVB tunneling are simply referred to as electron and hole tunneling, respectively.

Figure 2.2 Energy band diagram for tunneling components in an MOS structure.

### 2.3.1 Electron Tunneling in MOS Structure

In this section, electron tunneling is analyzed from the channel to the gate in a metal-gate n-MOSFET. Tunneling in a polycrystalline silicon gate is discussed in section 2.5. The schematic potential diagram for electron tunneling is shown in Figure 2.3. The electron affinity, which is the energy difference between the conduction band edge ( $E_C$ ) and the vacuum level, is smaller for the oxide layer than for silicon and metal [18]. Therefore, the oxide layer is a potential barrier for electrons in the gate and channel regions. The potential barrier height at the  $Si/SiO_2$  interface is denoted by  $\chi$  ( $\chi = 3.1~V$ ) [16, 17], so that  $q\chi$  is the required energy to excite an electron from the silicon conduction band edge to the silicon oxide conduction band edge. Because of the

voltage drop across the gate oxide  $V_{ox}$  (in [V]), the potential barrier shape is trapezoidal. Therefore, as shown in Figure 2.4,  $V_{ox}$  is given by

$$V_{ox} = V_{gs} - V_{FB} - \phi_s \,, \tag{2.6}$$

where  $V_{gs}$  (in [V]) is the gate voltage referenced to the source,  $V_{FB}$  (in [V]) is the flat band voltage, and  $\phi_S$  (in [V]) is the surface potential of the channel. In addition, the gate bias  $V_{gs}$  causes a difference in the Fermi energy of the silicon channel  $E_{Fs}$  (in [eV]) and the Fermi energy of the metal  $E_{Fm}$  (in [eV]), which is determined by

$$qV_{gs} = E_{Fs} - E_{Fm}. {2.7}$$

Figure 2.3 Energy band diagram for electron tunneling in an MOS structure.

# Gate Oxide Channel $V_{gs}$ – $V_{FB}$ $\phi_s$ $\phi_s$

Figure 2.4

Potential distribution in the gate-to-channel direction for a metal-gate MOSFET.

Through the WKB method (see Appendix A), the tunneling probability associated with the trapezoidal potential barrier can be obtained from the integral

$$D(E_x) = \exp\left(-\frac{2}{\hbar} \int_{x_1}^{x_2} \sqrt{2m_{ox}(E_b(x) - E_x)} dx\right)$$

(2.8)

where  $m_{ox}=0.35m_0$  [71] is the effective electron mass in the oxide, and  $E_x$  is the electron kinetic energy in the x direction. As shown in Figure 2.3 and Figure 2.4, the turning points  $x_1$  and  $x_2$  are  $x_1=-t_{ox}$  and  $x_2=0$ , and the trapezoidal potential barrier is given by

$$E_b(x) = q\chi + qV_{ox} \cdot \frac{x}{t_{ox}}$$

(2.9)

The average barrier height  $E_B$  (in [eV]) over x can be expressed by

$$E_B = \frac{1}{t_{ox}} \int_{x_1}^{x_2} E_b(x) dx = q \chi - \frac{1}{2} q V_{ox}.$$

(2.10)

Thus, the integral in equation (2.8) can be approximated by

$$\int_{x_{1}}^{x_{2}} \sqrt{2m(E_{b}(x) - E_{x})} dx \approx \int_{-t_{ax}}^{0} \sqrt{2m(E_{B} - E_{x})} dx.$$

(2.11)

Substituting equation (2.11) into equation (2.8) results in

$$D(E_x) = \exp\left\{-\gamma (E_B - E_x)^{1/2}\right\},$$

(2.12)

where

$$\gamma = \frac{4\pi t_{ox}\sqrt{2m_{ox}}}{h} \,. \tag{2.13}$$