## Profiling and debugging by efficient tracing of hybrid multi-threaded HPC applications

Jean-Baptiste Besnard

### ▶ To cite this version:

Jean-Baptiste Besnard. Profiling and debugging by efficient tracing of hybrid multi-threaded HPC applications. Multiagent Systems [cs.MA]. Université de Versailles-Saint Quentin en Yvelines, 2014. English. <NNT : 2014VERS0007>. <tel-01133344>

## HAL Id: tel-01133344 https://tel.archives-ouvertes.fr/tel-01133344

Submitted on 19 Mar 2015  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THESIS SUBMITTED TO THE UNIVERSITY VERSAILLES SAINT-QUENTIN EN YVELINES

Specialised in

## **Computer Science**

at the École doctorale des Sciences et Technologies de Versailles (STV)

in total fulfillment of the requirements for the award of

## DOCTOR OF PHILOSOPHY

entitled

## Profiling and debugging by efficient tracing of hybrid multi-threaded HPC applications.

## by Jean-Baptiste Besnard

hosted by

## CEA, DAM, DIF F-91297 ARPAJON FRANCE

### Département des Sciences de la Simulation et de l'Information (DSSI)

Publicly defended the 16th of July 2014 in front of the following doctoral Committee:

| Pr. Alfredo GOLDMAN  | Professor at the University of São Paulo       | Jury President |

|----------------------|------------------------------------------------|----------------|

| Pr. Allen MALONY     | Professor at the University of Oregon          | Referee        |

| Pr. Michael KRAJECKY | Professor at the University of Reims           | Referee        |

| Pr. William JALBY    | Director of research, University of Versailles | Examiner       |

| Dr. Marc PÉRACHE     | Tutor, Research Engineer at CEA,DAM            | Examiner       |

### THÈSE DE DOCTORAT DE L'UNIVERSITÉ DE VERSAILLES SAINT-QUENTIN EN YVELINES

Spécialité

## Informatique

à l'École doctorale des Sciences et Technologies de Versailles (STV)

## présentée pour obtenir le grade de

## DOCTEUR de l'UNIVERSITÉ DE VERSAILLES

et intitulée

## Profilage et débogage par prise de traces efficaces d'applications hybrides multi-threadées HPC.

## par Jean-Baptiste Besnard

Organisme d'accueil :

## CEA, DAM, DIF F-91297 ARPAJON FRANCE

Département des Sciences de la Simulation et de l'Information (DSSI)

Soutenue publiquement le 16 Juillet 2014 devant le jury composé de :

| Pr. Alfredo GOLDMAN  | Professeur à l'université de São Paulo           | Président du jury |

|----------------------|--------------------------------------------------|-------------------|

| Pr. Allen MALONY     | Professeur à l'université d'Oregon               | Rapporteur        |

| Pr. Michael KRAJECKY | Professeur à l'université de Reims               | Rapporteur        |

| Pr. William JALBY    | Directeur de Recherche, université de Versailles | Examinateur       |

| Dr. Marc PÉRACHE     | Tuteur, Ingénieur de recherche au CEA,DAM        | Examinateur       |

## Abstract

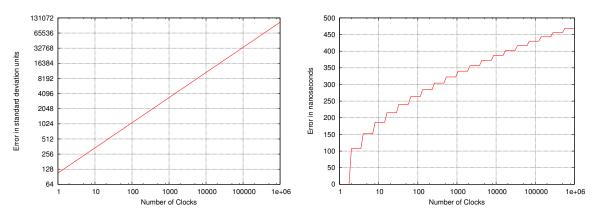

Supercomputers' evolution is at the source of both hardware and software challenges. In the quest for the highest computing power, the interdependence inbetween simulation components is becoming more and more impacting, requiring new approaches. This thesis is focused on the software development aspect and particularly on the observation of parallel software when being run on several thousand cores. This observation aims at providing developers with the necessary feedback when running a program on an execution substrate which has not been modeled yet because of its complexity. In this purpose, we firstly introduce the development process from a global point of view, before describing developer tools and related work. In a second time, we present our contribution which consists in a trace based profiling and debugging tool and its evolution towards an on-line coupling method which as we will show is more scalable as it overcomes IOs limitations. Our contribution also covers our time-stamp synchronisation algorithm for tracing purposes which relies on a probabilistic approach with quantified error. We also present a tool allowing machine characterisation from the MPI aspect and demonstrate the presence of machine noise for both point to point and collectives, justifying the use of an empirical approach. In summary, this work proposes and motivates an alternative approach to trace based event collection while preserving event granularity and a reduced overhead.

## Résumé

L'évolution des supercalculateurs est à la source de défis logiciels et architecturaux. Dans la quête de puissance de calcul, l'interdépendance des éléments du processus de simulation devient de plus en plus impactante et requiert de nouvelles approches. Cette thèse se concentre sur le développement logiciel et particulièrement sur l'observation des programmes parallèles s'exécutant sur des milliers de cœurs. Dans ce but, nous décrivons d'abord le processus de développement de manière globale avant de présenter les outils existants et les travaux associés. Dans un second temps, nous détaillons notre contribution qui consiste d'une part en des outils de débogage et profilage par prise de traces, et d'autre part en leur évolution vers un couplage en ligne qui pallie les limitations d'entrées-sorties. Notre contribution couvre également la synchronisation des horloges pour la prise de traces avec la présentation d'un algorithme de synchronisation probabiliste dont nous avons quantifié l'erreur. En outre, nous décrivons un outil de caractérisation machine qui couvre l'aspect MPI. Un tel outil met en évidence la présence de bruit aussi bien sur les communications de type point-à-point que de type collective. Enfin, nous proposons et motivons une alternative à la collecte d'événements par prise de traces tout en préservant la granularité des événements et un impact réduit sur les performances, tant sur le volet utilisation CPU que sur les entrées-sorties.

## Acknowledgement

These words end a three years adventure during which I met fascinating personalities and learned more than ever. First of all I want to thank Marc Pérache my industrial tutor who made everything possible, I hope this work matches the thrust he has placed in me. By its careful and constant guiding he helped me to learn from my mistakes without ever constraining my work or ideas in any manner. This remarkable freedom is at the core of this work as it allowed the springing of new ideas which became my contributions to the the performance tool field. This is this inspiring boldness which is required in the HPC context where legacy is mixed with novelty. I want to thank the CEA/DAM and my hierarchy who allowed me to work at largest scales on world class supercomputers without any form of limitation – allowing me to validate my work on representative cases. I also want to thank William Jalby who directed my work from an academic point of view. Thanks to both his original point of view and long experience in computer hardware architecture he opened new ways of thinking of my problematics through shrewd remarks. I am also grateful that he allowed me to join his team in order to pursue my work on parallel tools. During these years I met several colleagues and friends from CEA and university. I met trainees, doctoral candidates and post-doc from various horizons involved in every stage of the simulation chain: Marc W., Emmanuel, Emmanuel O., Bertrand, Alexandra, Alexandre, Xavier, Thomas, Nicolas, Jordan, Asma and so many more. This was an inciting interdisciplinary environment where we sharpened our point of views, shared good moments and supported each other. I want to thank particularly all the members of the MPC Team, Marc of course, Patrick, Julien J., Jean-Yves, Sébastien, Jérôme, Camille, Augustin, Aurèle, Sylvain, Julien A., Antoine, Emmanuelle and François for everything we shared during this adventure. I also want to thank my reviewers, Professor Krajecky and Malony who took the time to assess my work with interesting remarks in the light of their long experience. I'am also honored that Professor Goldman has accepted to preside my Jury. I want to express my gratitude to my family for its patience, particularly my wife Anaïs for her continous support. Eventually, as I believe that the transitioning to Exascale has just started, I am happy to be able to pursue my work in the HPC field at Paratools, for this I want to thank Mr Shende and Malony.

## Contents

| 1 | Inti              | roduction                                                                   | 13              |

|---|-------------------|-----------------------------------------------------------------------------|-----------------|

|   | 1.1               | The MultiProcessor Computing Runtime                                        | 14              |

|   | 1.2               | Requirements                                                                | 15              |

|   | 1.3               | Manuscript Outline                                                          | 15              |

| I | Со                | ntext                                                                       | 17              |

| 2 |                   |                                                                             | 19              |

| Z | 2.1               | esis Context Supercomputer Evolution Overview                               | 19<br>19        |

|   | $\frac{2.1}{2.2}$ | Supercomputer Evolution Overview                                            | 19<br>21        |

|   | $\frac{2.2}{2.3}$ |                                                                             | $\frac{21}{22}$ |

|   | 2.5               | Programming Models                                                          | $\frac{22}{23}$ |

|   |                   | 2.3.1       Shared Memory         2.3.2       Distributed Memory            | $\frac{23}{23}$ |

|   |                   | 2.3.2 Distributed Memory                                                    | 23<br>23        |

|   |                   | 2.3.4 Summary                                                               | 23<br>24        |

|   | 2.4               | Thesis Computing Environment                                                | 24<br>24        |

|   | 2.4               | 2.4.1         Description                                                   | $\frac{24}{25}$ |

|   |                   | 2.4.2 Node Description                                                      | $\frac{25}{25}$ |

|   |                   | 2.4.3 Network Topology                                                      | 26              |

|   | 2.5               | Summary                                                                     | 27              |

| 0 | D.                |                                                                             | 90              |

| 3 |                   | velopment Cycle                                                             | <b>29</b><br>29 |

|   | 3.1               | Classical Development Methodologies                                         | 29<br>29        |

|   |                   | 3.1.1 Constants in the Development Cycle                                    | 29<br>31        |

|   |                   | 3.1.2 Waterfall Model                                                       | $\frac{31}{32}$ |

|   |                   | 3.1.3       V-Model                                                         | 32<br>33        |

|   | <u>ว</u> ก        | 0                                                                           | 33<br>34        |

|   | 3.2               | Developing Against Complexity                                               | $\frac{34}{35}$ |

|   |                   | ······································                                      | 30<br>36        |

|   | 3.3               | 3.2.2 Catalysing Loops                                                      | 30<br>37        |

|   | <b>J.J</b>        |                                                                             | 38              |

|   |                   | 1                                                                           | 38<br>38        |

|   |                   | 1                                                                           | 38<br>39        |

|   |                   | 5                                                                           | 39<br>39        |

|   |                   | 1 0                                                                         | 39<br>39        |

|   |                   | 3.3.5Software ManagementSoftware Management3.3.6OverviewSoftware Management | 39<br>39        |

|   |                   |                                                                             | บฮ              |

|    | 3.4        | Summary                                   | <b>4</b> 0 |

|----|------------|-------------------------------------------|------------|

| 4  | Rol        | e of Performance and Debugging Tools      | <b>£1</b>  |

|    | 4.1        | Performance Metrics                       | 41         |

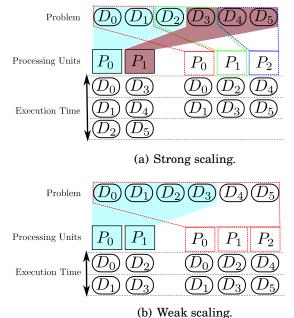

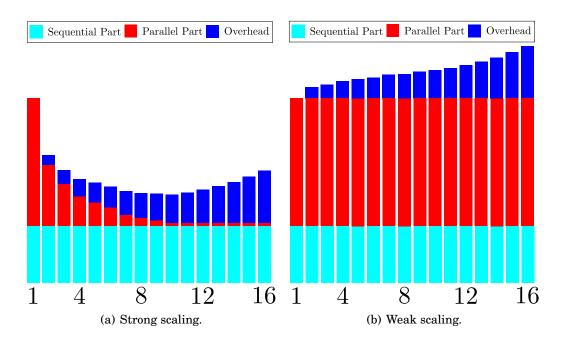

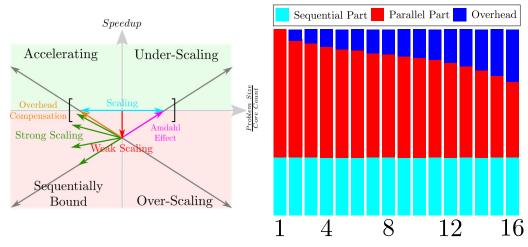

|    |            | 4.1.1 Strong and Weak Scaling             | 41         |

|    |            | 4.1.2 Canonical Speedup                   | 42         |

|    |            | 4.1.3 Scaling Bounds                      | 43         |

|    |            | 4.1.4 Acceleration versus Scaling         | 44         |

|    |            | 4.1.5 Summary                             | 46         |

|    | 4.2        | Programs Correctness                      | 47         |

|    |            |                                           | 17         |

|    |            | 4.2.2 Quality Process                     | 48         |

|    | 4.3        | Summary                                   | 50         |

| II | Ke         | ey Concepts and Related Work 5            | 51         |

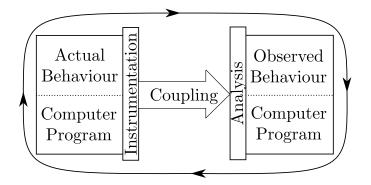

| 5  | Arc        |                                           | 53         |

|    | 5.1        |                                           | 53         |

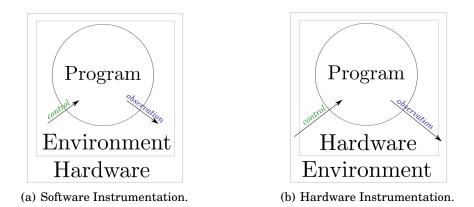

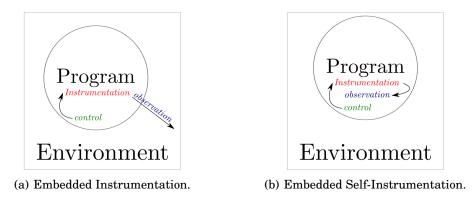

|    | 5.2        | Instrumentation Approaches                | 54         |

|    |            | 5.2.1 External Instrumentation            | 54         |

|    |            | 5.2.2 Embedded Instrumentation            | 55         |

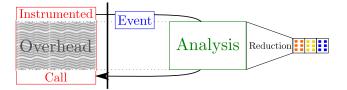

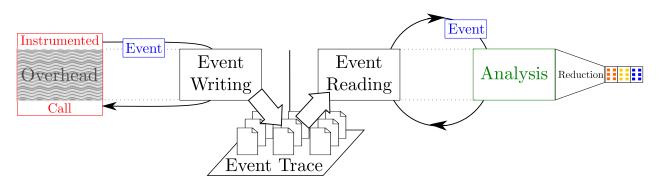

|    | 5.3        | Coupling Methods                          | 56         |

|    |            | 5.3.1 In-Place                            | 56         |

|    |            | 5.3.2 Post-Mortem                         | 57         |

|    |            |                                           | 57         |

|    | 5.4        | Performance Event Analysis                | 58         |

|    | 5.5        | -                                         | 59         |

| 6  | Rol        | ated Work                                 | 31         |

| U  |            | Developer Tools                           |            |

|    | 0.1        | 6.1.1 Debuggers                           |            |

|    |            |                                           | 51<br>52   |

|    |            |                                           | 52<br>37   |

|    | 6.2        |                                           | 58         |

|    | 0.2        | 1 0                                       | 70         |

|    |            |                                           | 70<br>70   |

|    |            | -                                         | 70<br>71   |

|    |            | 5                                         |            |

|    | <i>c</i> 0 | 1                                         | 71         |

|    | 6.3        |                                           | 71         |

|    | 0.4        |                                           | 72         |

|    | 6.4        | 5                                         | 73         |

|    |            |                                           | 73         |

|    |            |                                           | 74         |

|    |            |                                           | 75         |

|    |            | 6.4.4 Tree-Based Overlay Networks (TBONS) | 75         |

| Π | IC         | ontribution                                       | 77       |

|---|------------|---------------------------------------------------|----------|

| 7 | MP         | I Runtime Characterisation                        | 79       |

|   | 7.1        | Tool Architecture                                 | 79       |

|   | 7.2        | Measurement Process                               | 80       |

|   |            | 7.2.1 Point to Points                             | 80       |

|   |            | 7.2.2 Collectives Operations                      | 80       |

|   | 7.3        | Report Analysis                                   | 81       |

|   |            | 7.3.1 Point to Points                             | 81       |

|   |            | 7.3.2 Collective Operations                       | 83       |

|   | 7.4        | Summary                                           |          |

| 0 | <b>T</b> • |                                                   | 05       |

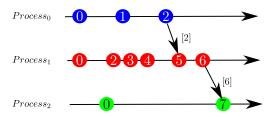

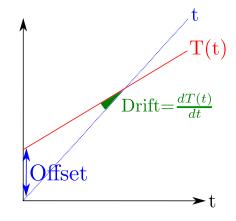

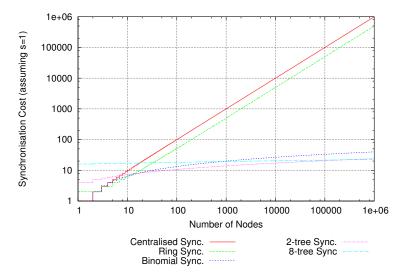

| 8 |            | nestamp Synchronisation                           | 85       |

|   | 8.1        | Synchronisation Principle                         | 85       |

|   | 8.2        | Distributed Synchronisation                       | 86       |

|   |            | 8.2.1 Notations and Methodology                   | 86       |

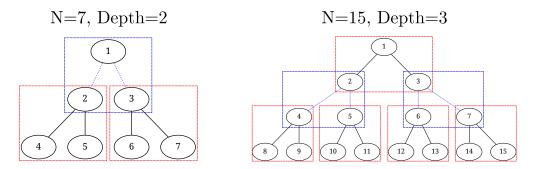

|   |            | 8.2.2 Centralised Topology                        | 87       |

|   |            | 8.2.3 k-tree Topology                             | 87       |

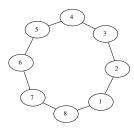

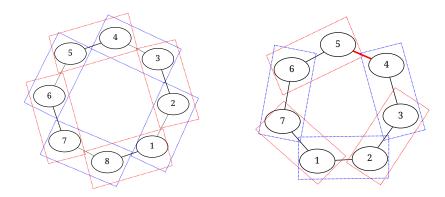

|   |            | 8.2.4 Ring Topology                               | 88       |

|   |            | 8.2.5 Binomial Tree Topology                      | 89       |

|   |            | 8.2.6 Summary                                     | 89       |

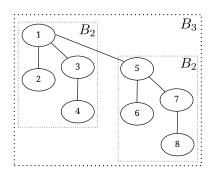

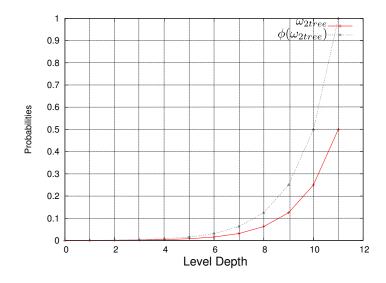

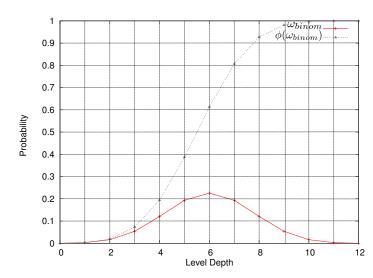

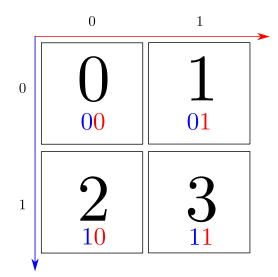

|   | 8.3        | Depth Distribution in 2-trees and Binomial Trees  | 91       |

|   |            | 8.3.1 Notations and Methodology                   | 91       |

|   |            | 8.3.2 2-tree                                      | 91       |

|   |            | 8.3.3 Binomial Tree                               | 91       |

|   |            | 8.3.4 Summary                                     | 93       |

|   | 8.4        |                                                   | 93       |

|   | 0.4        | 8.4.1 Round-trip Error Distribution               | 93       |

|   |            |                                                   | 93<br>97 |

|   | 0 5        | 8.4.2 Error Propagation                           |          |

|   | 8.5        | Summary                                           | 98       |

| 9 |            | ce Based Approach                                 | 101      |

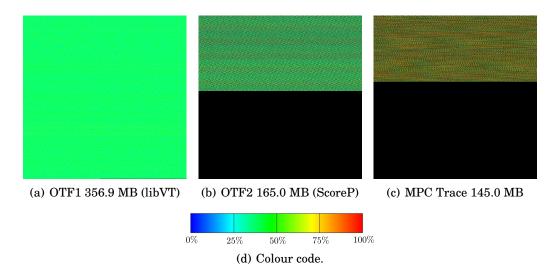

|   | 9.1        | Limitations of Existing Trace Formats             |          |

|   | 9.2        | Proposed Architecture                             | 102      |

|   | 9.3        | Instrumentation                                   | 102      |

|   |            | 9.3.1 MPI Profiling Interface                     | 103      |

|   |            | 9.3.2 Compiler Level Instrumentation              | 103      |

|   |            | 9.3.3 Direct Instrumentation                      | 104      |

|   |            | 9.3.4 Library Interposition                       |          |

|   |            | 9.3.5 Instrumentation Summary                     |          |

|   | 9.4        | Trace Library                                     |          |

|   | 0.1        | 9.4.1 Topology Management                         |          |

|   |            | 9.4.1 Topology Management 9.4.2 Event Description |          |

|   |            |                                                   |          |

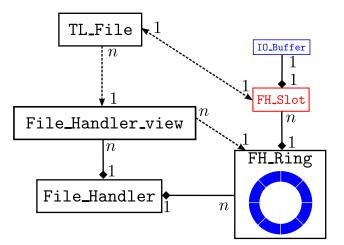

|   |            | 9.4.3 File Descriptor Handling                    |          |

|   |            | 9.4.4 Debug Buffers                               |          |

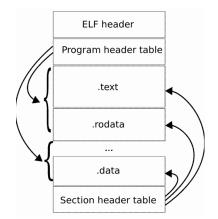

|   |            | 9.4.5 Symbol Extraction                           |          |

|   |            | 9.4.6 Compression                                 |          |

|   | 9.5        | Trace Reader                                      | 118      |

|    |              | 9.5.1  | Trace Read   | der Arch | itectu     | re      |     |    |     |     |     |     |     |     |     |     | • |     |     | 119 |

|----|--------------|--------|--------------|----------|------------|---------|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|---|-----|-----|-----|

|    |              | 9.5.2  | Trace Read   | der Inte | rface .    |         |     |    |     |     |     |     |     |     |     |     | • |     |     | 119 |

|    |              | 9.5.3  | Sample To    | ol       |            |         |     |    |     |     |     |     |     |     |     |     | • |     |     | 120 |

|    |              | 9.5.4  | Performan    |          |            |         |     |    |     |     |     |     |     |     |     |     | • |     |     | 120 |

|    | 9.6          | Limita | tion         |          |            |         |     |    |     |     |     |     |     |     |     |     | • |     |     | 121 |

|    | 9.7          | Summ   | ary          |          |            | •••     |     |    |     |     |     |     |     |     |     |     | • |     |     | 121 |

|    |              |        |              |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

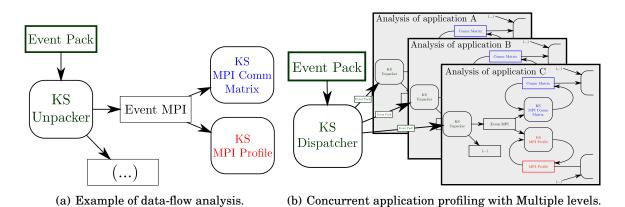

| 10 |              |        | ace Analys   |          | . 1        |         |     |    |     |     |     |     |     |     |     |     |   |     |     | 123 |

|    |              |        | ig to On-lin |          | -          |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

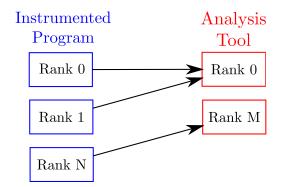

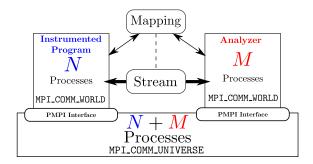

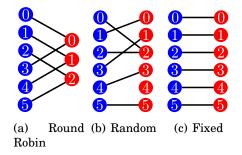

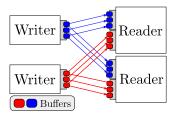

|    | 10.2         | -      | ng Multipl   |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Transpare    |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Mappings     |          | _          |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Communio     |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | 1 to N Cou   |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Runtime-C    |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Summary      |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

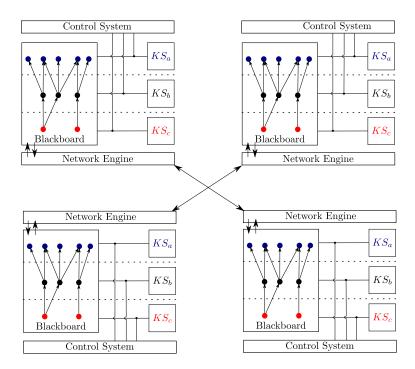

|    | 10.3         |        | oard         |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Blackboar    | -        |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              | 10.3.2 | Limitation   | <b>s</b> |            | • • • • |     |    |     |     | ••• |     |     |     |     |     | • |     |     | 135 |

|    |              | 10.3.3 | Summary      |          |            | •••     |     |    |     |     |     |     |     |     |     |     | • |     |     | 136 |

|    | <b>D</b> • 4 | •1     | 1 . 1 .      | 1.0      | <b>1</b> 4 | • •     |     |    | DM  |     |     |     |     |     |     |     |   |     |     | 105 |

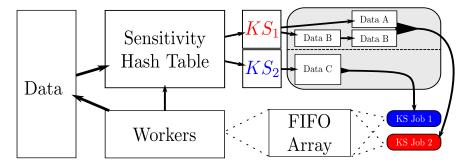

| 11 |              |        | d Analysis   |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     | 137 |

|    |              |        | tions        |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    | 11.2         |        | ecture       |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

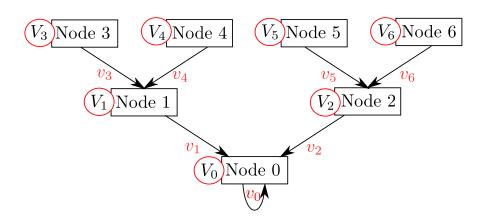

|    |              |        | Fixed Topo   | 0.       |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

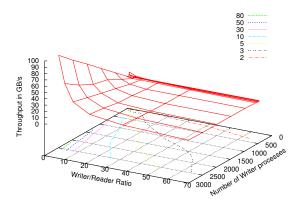

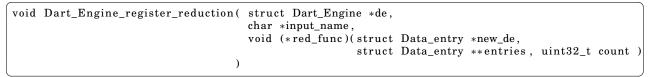

|    |              |        | Network E    | -        |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | ice and Pro  | •        | 0          | -       |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

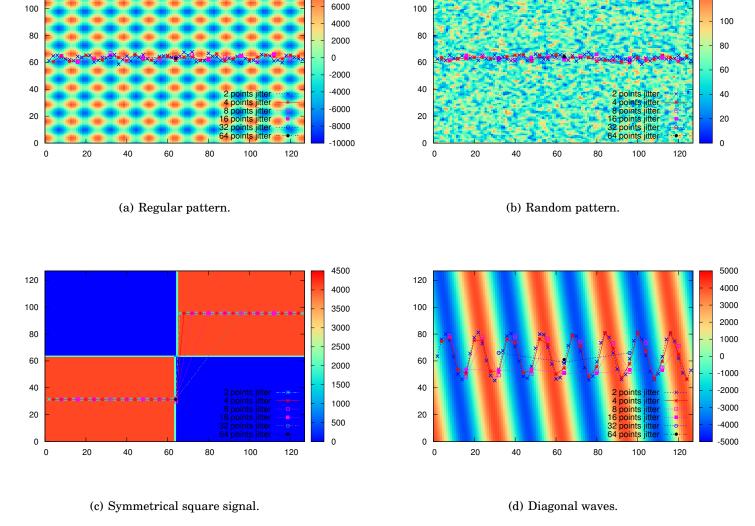

|    | 11.4         | -      | sis Projects |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Continuou    | _        | -          | -       |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

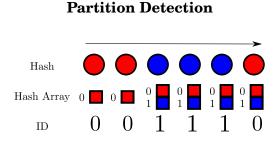

|    |              |        | Phase Bas    |          | 0          |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | tions        |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    | 11.6         | Summ   | ary          |          |            | •••     | ••• | •• | ••• | ••• | ••• | ••• | ••• | ••• | ••• | ••• | • | ••• | ••• | 152 |

| 19 | Ano          | lysis  |              |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     | 153 |

| 14 |              |        | Programs     |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Based Deb    |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    | 12.2         |        | Architectu   | 00       |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Interactive  |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Hybrid De    |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | ·            |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Trace-Base   |          |            | -       |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    | 10.0         |        | Trace-Base   |          |            | -       |     |    | 0   |     |     |     |     |     |     |     |   |     |     |     |

|    | 12.3         | -      | ing          |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Measure C    |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    | 10 /         |        | Module Ex    | -        |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    | 12.4         |        | ng           |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | Profiles .   |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              |        | MPI Comm     |          |            |         |     |    |     |     |     |     |     |     |     |     |   |     |     |     |

|    |              | 12.4.3 | Wait State   | Analys   | is         |         |     |    |     |     |     |     |     |     |     |     | • |     |     | 164 |

|    | 12.4.4 Time Matrix12.4.5 MPI Quadrant12.4.6 Spatial Analysis12.5 Online Trace Analysis Overhead12.6 Summary                                                                                                                 | $170 \\ 170 \\ 171$             |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| IV | V Conclusion and Perspectives                                                                                                                                                                                               | 175                             |

| 13 | 3 Conclusion                                                                                                                                                                                                                | 177                             |

|    | 14.1 Analysis                                                                                                                                                                                                               | 180                             |

| Aŗ | ppendices                                                                                                                                                                                                                   | 197                             |

| Α  | Instrumentation Filtering at Compiler-LevelA.1 Existing Filtering                                                                                                                                                           |                                 |

| В  | B.1       MPC Extended TLS         B.2       Launch Hooks         B.3       Instrumentation Points         B.3.1       MPI Profiling Interface         B.3.2       Thread Spawning         B.3.3       Lock Instrumentation | 201<br>202<br>202<br>202<br>202 |

|    | B.4 Topology Getters                                                                                                                                                                                                        | 200                             |

CONTENTS

### CHAPTER 1

## Introduction

As numerical simulation is becoming an important tool for scientific competitiveness with various applications ranging from fundamental science (Quantum Physics) to industry (Aeronautic and automotive design), simulation codes have to be seen from the modelling process macroscopic point of view. When dealing with high-end supercomputers, simulation programs cannot be viewed as a tool which punctually validates an hypothesis. On the contrary, the program becomes a constituting part of the simulation process which is aimed at providing measurements matching an experiment. Therefore, although we often picture physicists in their laboratory, performing precise measurements with bounded error rates, nowadays, science is often seen through the lens of a computer program. Moreover, as we will further develop in this thesis, computer programs have few in common with high level equations which describe an objectified reality, instead, they describe an operational reality with iterative and alternative behaviours. This, while coping with evolving execution substrates.

This thesis acknowledges this context and aims at providing developers with the necessary feedback when using supercomputers. Because of their complexity, supercomputers are somehow unpredictable as parallel interactions and contention on shared resources creates a combinatory number of states, sometimes reached randomly because of freedom degrees in the scheduling. Therefore, despite being formally defined at sequential level, parallel execution is sometimes not predictable from the code alone. In the absence of model, a common approach is then to process empirical measurements in order to observe how a code behaves on the execution substrate, approach that we adopted in this thesis by setting up a measurement and analysis framework. The object of this work is then to explore the possibilities of profiling and debugging for production grade applications (million lines of codes) at supercomputer scale (thousands of cores) in an hybrid context. Where, profiling is the examination of a program's performance on a given execution substrate whereas debugging is more concerned by the correctness of the solution or faulty program state (crashes) investigation. The hybrid aspects comes from one of the parallel execution runtime which is targeted by our analysis: the Multi-Processor Computing runtime (MPC). It is a runtime which combines several parallel programming models over an unified scheduler in order to allow their efficient mixing in purpose of taking advantage of upcoming supercomputer architectures. We will pursue this introduction with a brief presentation of the MPC framework insisting on how it constrained our tool implementation. Then, we define our requirements more formally and provide an outline of the organisation of this document.

### **1.1 The MultiProcessor Computing Runtime**

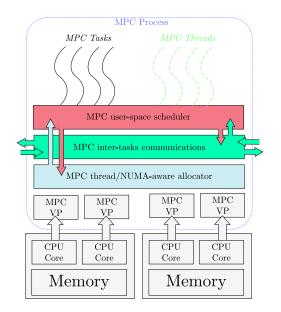

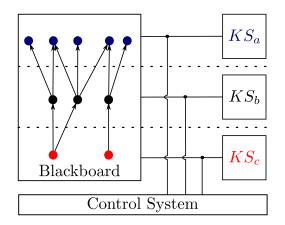

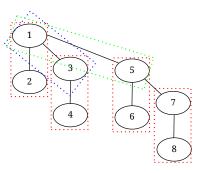

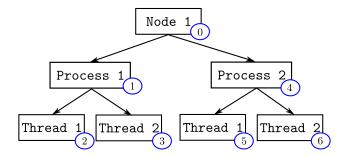

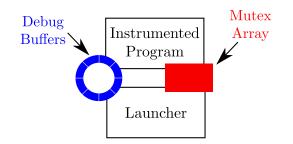

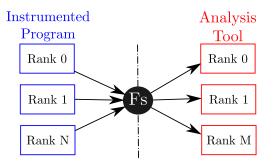

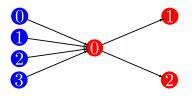

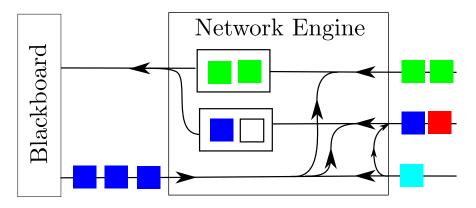

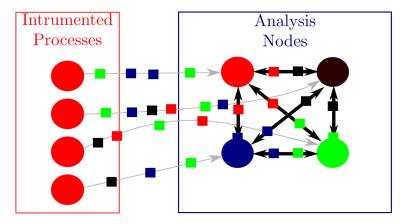

MPC [Pér06, PJN08] aims at providing an unified framework to run massively parallel applications on clusters of (very) large multi-core numa nodes. It supports MPI 1.3, OpenMP 2.5 and POSIX threads interfaces over an unified runtime which is designed to mix those standards in an efficient way [CPJ10]. One particularity of MPC is that MPI processes are running within user-level threads, allowing fine grained scheduling and optimisations such as busy-waiting removal. MPC supports Infiniband and TCP networks with a fully MPI thread multiple support. It is built to allow communication overlapping [DCPJ12] and reduces the overall memory consumption [PCJ09] by factorising process level resources thanks to extended thread local storage [CPJ11] and efficient memory management directives [TCP12]. It is shipped with a patched GCC compiler, allowing both compilation of OpenMP programs and automatic privatisation of global variables in purpose of eventually running program within user-level threads. It also features a patched GDB, allowing transparent debugging of userlevel threads [PCJ10] and has been supported in commercial debuggers such as DDT. MPC has evolved drastically since 2006 and is under constant evolution to alleviate the upcoming challenges of many-core architectures. Being used in production on the Tera 100 supercomputer, it reached the petaflopic scale with a competitive memory footprint and a reduced launch time [PCDJ12]. These gains come from the thread based nature of MPC which allows both resource factorisation and reduces the number of MPI processes to launch by a factor which is equal to the number of cores per node (32 on tera 100). Consequently, MPC requires only 4370 processes instead of 140 000 for the whole Tera 100 computer, therefore, drastically reducing launch time<sup>1</sup>. Figure 1.1 presents the Multi-Processor Computing Runtime architecture. As it is a thread based MPI, ranks which are commonly located in distinct processes, are now in user-level threads. This configuration, reduces memory requirements and restores fairness inbetween threads which can run on the same scheduler. This avoids for example busy waiting and opens opportunities when mixing programming models.

Figure 1.1: Overview of the MPC runtime.

<sup>5000</sup> MPI processes is a classical payload on Tera 100 whereas 140 000 is not.

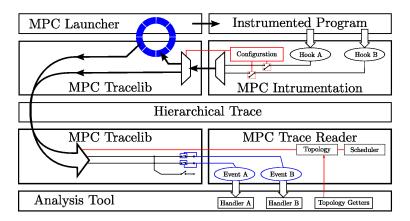

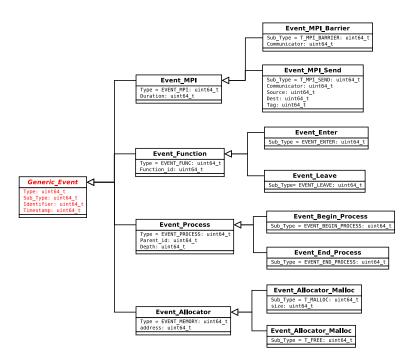

From an instrumentation point of view, supporting MPC has some challenging aspects as it requires a careful handling of parallelism (at task level) and extend the classical process hierarchy (Cluster  $\mapsto$  Node  $\mapsto$  Process(Ranks)  $\mapsto$  Thread) to include the task level (Cluster  $\mapsto$  Node  $\mapsto$  Process  $\mapsto$  Tasks(Ranks)  $\mapsto$  Thread), requiring a particular attention when handling program state. Those, parallelism and topology requirements led to the development of our own trace format (chapter 9), allowing, in complement of MPI programs, MPC programs instrumentation which as we will further develop was not practical with existing formats. Consequently, our support of the MPC framework yielded a certain number of requirements which led to the design of our first implementation of a trace analysis framework called the MPC Trace Library (chapter 9). In a second time, these requirements were relaxed when our tool moved to an on-line approach to become MALP (chapter 10), work which has been published in an article [BPJ13].

### **1.2 Requirements**

As described in Chapter 3, managing simulation programs is a challenging task as it adds the classical difficulties of programming with the complexity of modelling. Moreover, the transition toward Exascale which is expected around 2015–2020 [MSDS93] (see figure 2.1) will be more than an hardware problem. Indeed, the increasing number of core per processor (since  $\approx$  2002) already impacted programs as they now have to rely on hybrid approaches. But, current trends, paving the way to Exascale by favouring many-cores and accelerators pose new problematics as they require a dramatic shift in programs architecture — causing close to a complete rewriting of simulation codes. For example the Tianhe-II supercomputer which is at the moment the largest supercomputer includes Intel Xeon Phi for a total of 3,120,000 cores only achieves an efficiency of 62.3 %<sup>2</sup> on the Linpack Benchmark [DLP03], emphasising the arduousness associated with the programming of such demanding architectures. Consequently, porting simulations programs to next generation machines will be a challenging task which requires (1) the capacity of instilling transition by questioning local maximums (or stratification) and (2) the availability of means of measure and control to guide developer teams in the maze of Exascale simulation. This thesis is focused on a small subset of this problem: measure. Our purpose is to provide developers with metrics of their programs in purpose of guiding their choice in-between design alternatives (trial & error). In complement, our tools shall be able to *continuously* qualify programs fitting relatively to performance criteria to build a *management metric* — more likely to positively influence developer teams. Dealing with reliability, we also have to explore solutions to describe faulty program states in the context of production jobs (particularly long running batch job) and unpredictable crashes which can be hard to diagnose. Requirements which conducted this thesis to explore both profiling and debugging aspects over a common tracing framework while developing corollary notions such as time-stamp synchronisation and performance modelling.

### **1.3 Manuscript Outline**

In Part I, we first present in more detail the context of this thesis in terms of supercomputer evolution, architecture and their associated programming models. Then, Chapter 3 contextualises the development task in terms of classical management processes (development cycle),

$<sup>^2</sup>$  Tera 100 has an efficiency of 83.6 %.

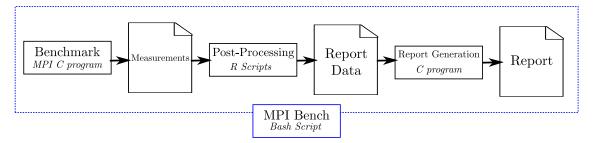

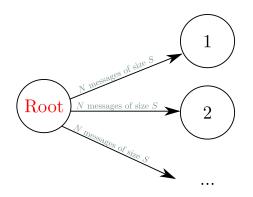

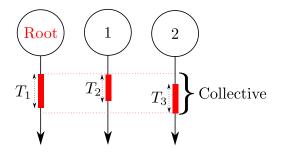

outlining the recursive roles and duties of each of its actors. Followingly, Chapter 4 introduces the role of performance and debugging tools in the light of this development cycle. In Part II, we begin by a brief description of developer tools' architecture before detailing in Chapter 6 work related to our subject. In part III, our contribution starts by presenting our machine characterisation tool, called "MPI Bench" (Chapter 7). It describes which performance can be expected from a given machine from the MPI point of view, measures which can be used by developers to privilege most scalable MPI calls. Then, Chapter 8 introduces the principle of our clock synchronisation algorithm which is needed to restore time coherence within distributed measurement, opening opportunities for time-based analysis. Then, we present the two main parts of our contribution which are associated with two different data management methods: trace-based (chapter 9) and on-line coupling (chapter 10). The trace-based approach is described and contrasted with existing trace formats while introducing its support for debugging. Then, the on-line approach is described as a more efficient coupling method which bypasses the IO bottleneck while providing analysis with enhanced parallelism. Analysis which are covered in Chapter 12 through several modules which were, for most of them, ported from the original trace-based approach to the new on-line trace analysis, demonstrating both debugging (back-traces, deadlock detection, ...) and profiling facilities. Eventually, Part IV, sums up our contribution and conclude this manuscript before outlining our future work.

# PART I Context

CHAPTER 2

## **Thesis Context**

This chapter provides some context on High Performance Computing, focusing on supercomputers' architecture and their evolution. We will start by a brief reminder on supercomputers evolution trends with a description of current hardware followed by an introduction of existing programming models. Our purpose is to insist on the complexity arising from parallel computers as it is at the root of usability problems programmers now encounter.

### 2.1 Supercomputer Evolution Overview

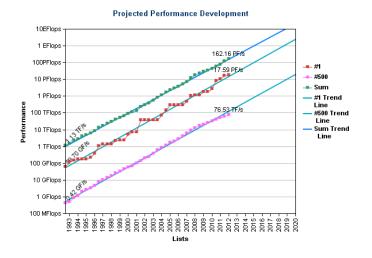

Supercomputers are known for their rapid evolution, such trend can be witnessed thanks to the well known top500.org website [MSDS93] which ranks the world largest supercomputers relatively to the top performance obtained over the *Linpack* [Don87] benchmark. This benchmark, performing linear algebra operations characterises the ability of a given supercomputer to solve numerical problems. Supercomputers are then ranked according to two measurements in FLoating-point OPerations per Second or Flops: R<sub>Peak</sub> and R<sub>Max</sub>. Where R<sub>Peak</sub> is the cumulative peak performance of processing units as stated by manufacturers and  $R_{Max}$  the operation throughput achieved on the Linpack benchmark. Although the Linpack benchmark gives some insight on "real-world" problems, it does not describe applications in general [DLP03] as for example they might stress the interconnection network by performing massive IOs or communications. To address Linpack's limitations, a complementary benchmark graph 500.org [BBK $^+10$ ] has been proposed, more focused on data management as it solves graph related problems [FGMM06] and yields results in Traversed Edges Per Second (TEPS). Schematically, real HPC applications are somewhere in-between those two extremes as they perform floating point operations (top500) while managing large data-sets (graph500). Despite aforementioned limitations, top500 is still at the moment the reference source for supercomputer ranking. Figure 2.1 is from the top500 website, it depicts the computing power evolution since 1993 and projects its evolution until 2020. Exponential evolution of computing power is clearly visible with approximately a tenfold increase every tree years. Moreover, looking at projections, Exaflop shall be reached around year 2020 but not without efforts [BBC<sup>+</sup>08]. Although an exponential computing power growth has been maintained over the years, supercomputers' taxonomy has evolved drastically, starting in the 1960s with the first supercomputer designed by Saymour Cray where architectures relied mainly on specifically tailored vectorial computing units and a small number of processors, until the 1990s where machines with thousands of processors appeared. At this point programming models migrated from intensive vectorisation (mainly in Fortran) to distributed memory paradigm over MPI or PVM in purpose of taking advantage of the computing power provided by interconnected nodes. From

**Figure 2.1:** Evolution and projected performance development of supercomputers as displayed on the top500.org website. (Source : top500.org [MSDS93].)

then until today, most supercomputers started to rely on more standard components (mostly high-end x86 processors) to reduce production costs, MPI took the advantage over PVM and the number of cores started its quick increase until reaching the million with the IBM Sequoia supercomputer and later on several millions with Tianhe-II.

This spectacular increase in the number of cores finds its root in hardware limitations. Until recently, Moore's Law [Moo65] stating the the number of transistors in a given surface doubles every two years has been the main source of computing power improvement as microprocessors were becoming more efficient. Thus, thanks to the increase of processors' frequencies, the 'same work' could be done faster with virtually no application modification. But this trend came to and end around year 2002 when physical limitations (mainly power dissipation) started to slowdown frequency increase, thus, limiting sequential performance gains. Nonetheless, processors manufacturers managed to overcome this limitation, sustaining the exponential performance increase, not in frequency but by multiplying the number of cores. Creating a singularity in code development trends where parallelism became compulsory to get performance improvements — situation which was summed up by the well known "Free Lunch Is Over" [Sut05] quotation.

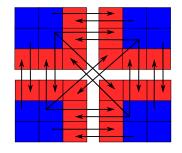

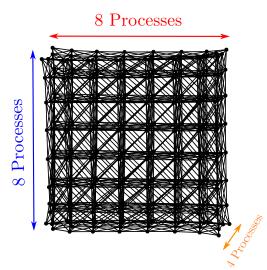

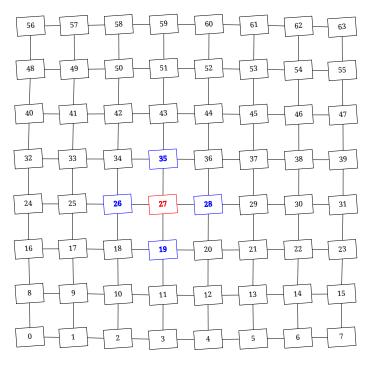

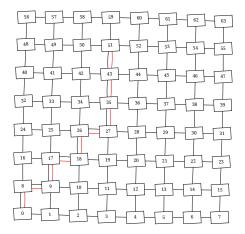

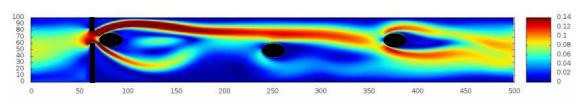

Figure 2.2: Sample communication scheme for ghost cells synchronisation.

Because of the rapid increase in the number of cores per node, memory per core decreased and programs were forced to combine both shared and distributed memory parallelism. Indeed, on a given node, using distributed memory parallelism leads to data duplication not only by multiplying processes and their associated file descriptors but also at program level. Figure 2.2 exemplifies this situation with a simple simulation code . It relies on a 2D-mesh and duplicates the same cell up to four times for synchronisation in-between ghost cells (in red) and real cells in blue. This imposed shift to mixed programming requires important program evolution, forcing programs to work at multiple parallelism granularities. In this challenging context, performance tools can provide important feedback to users, helping them to understand and project design choices.

### 2.2 Supercomputer Architecture and Performance

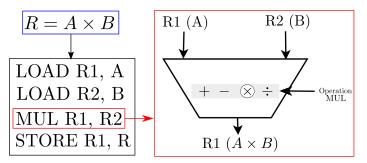

Since the 1990s, supercomputers gather several computing nodes interconnected by a high performance network. A consequence of cores multiplication, is the hierarchical aspect of processing capabilities. Figure 2.3 presents a simplified assembler code corresponding with a single multiplication (blue box). It can be seen that the operands (A and B) have to be loaded in registers before being processed by the Arithmetic and Logical Unit (ALU, red box) which produces a result which can be stored in the main memory by the "store" instruction. Naturally current processors are much more complex (addressing types, prefetching, branch prediction, ...) and won't be covered in this introduction. But this simple load and store model is sufficient to show that computation is done by combining data (operands/data-set) with data (program). Consequently, it is the memory bandwidth and scattering which "shapes" calculation by defining how programs operate on data-sets within machines memory constraints. Therefore, we start by exposing how data can move in current supercomputers (massive clusters) before exposing some of the programming models being used to exploit them.

Figure 2.3: Simple representation of an ALU (Arithmetic and Logical Unit) performing a multiplication on two scalar operands. The left part presents a simplified assembler code performing the multiplication of two scalar values A and B and their storage in R.

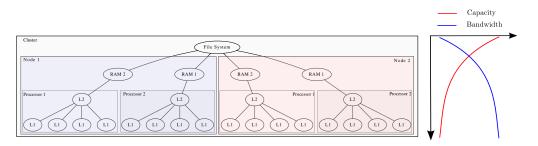

In current supercomputers, multiple data states can be identified both at a given distance in time (or latency) from processing units and with a fixed symbol throughput (or bandwidth). We define a cluster of machines as a group of computing nodes interconnected by a high performance network with a fixed topology. Each node at its turn groups several processing units (or cores each with an ALU) following a topology shaped by their local memory (as known as Non Uniform Memory Access (NUMA) architectures). Context in which some accesses are done to local memory banks and others to distant ones with variable costs. Figure 2.4 illustrate this trade-off between available memory and bandwidth. It can be seen that when moving closer to processing units, data containers become faster but smaller. Whereas, when moving away from processing units data-stores become larger but slower until reaching file system level.

Figure 2.4: Schematic and effective memory hierarchy.

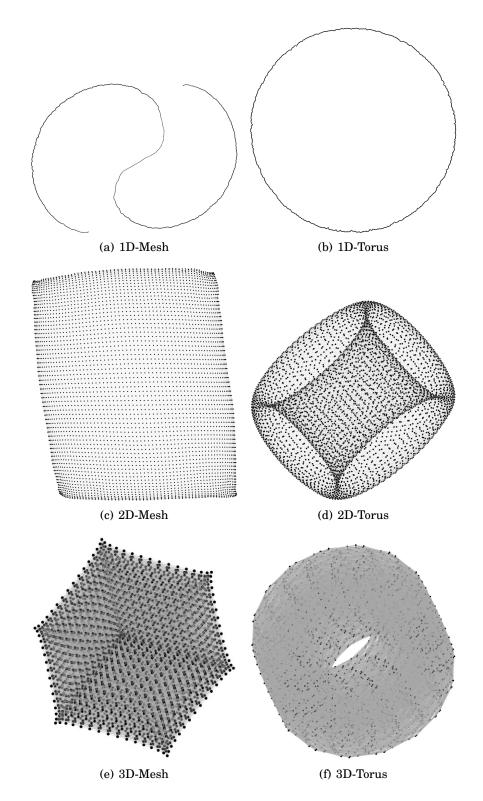

As presented in figure 2.5, data can reside in various containers which expose different characteristics, one of the biggest challenge of parallel programming is to actually distribute data according to this topology in order to fully exploit the hardware. Consequently, data have to be distributed evenly among the processing units in chunks which fit into the lowest caches. In this context, two different level of parallelism have to be identified, (1) distributed parallelism in-between the nodes which are connected through the network; (2) Shared memory parallelism which takes place within nodes, where multiple threads access the same memory area. To express parallel computations in these two contexts, several programming models are available each with its own semantic and syntax. Moreover, as aforementioned, memory limitations are forcing programmers to adopt a mixed approach, combining coarse and fine grained parallelism for respectively distributed and shared memory contexts.

### 2.3 Programming Models

As we developed in previous section, supercomputers parallelism tends to rank memory, complicating memory management and stressing parallel programming models adaptability. Leading to the development of several programming models, each directed towards a particular level of parallelism. This section introduces main approaches, starting by shared memory parallelism approaches, before describing distributed memory parallelism and accelerators.

| Data State        | Volume          | Throughput                 | Resilient | User Managed          |

|-------------------|-----------------|----------------------------|-----------|-----------------------|

| Long Term Storage | Very Large (PB) | Low (less than a GB/s)     | yes       | no (Storage policy)   |

| File-System       | Large (TB)      | Low (less than a GB/s)     | yes       | yes (IO calls)        |

| Remote Memory     | Medium (GB)     | Medium (network bandwidth) | no        | yes (Network calls)   |

| Memory            | Medium (GB)     | High (GB/s)                | no        | yes (Allocator calls) |

| Caches            | Low (MB and KB) | Very High (GB/s)           | no        | no (processor level)  |

Figure 2.5: List of common data states in HPC clusters (relatively to a single node).

#### 2.3.1 Shared Memory

Shared memory is the most common parallelism approach where multiple processing share the same address space, allowing 'direct' data exchanges. Pthread is the most widespread parallel programming interface as it has been standardised in the POSIX standard, becoming basic a block of higher level programming models. Threads are execution streams which can overload the available number of computing units, in other words, operating systems feature a scheduler which role is to switch in-between threads, evenly allocating computing power to each stream. Thanks to this functionality, multitasking is possible even on a single core, using a time-sharing approach. However, as the scheduler is located in the kernel, switching between threads requires a context switch. Therefore, alternatives were developed in order to build user-level threads, able to run multiple threads on top of a single execution stream. Such threads are called user-level threads and can be scheduled very efficiently. Several libraries feature user threads, for example, Marcel [DMN99, Nam01], MPC [PJN08] and GNU portable threads [Eng03]. Relying on threads, several higher level approaches have been developed in order to simplify parallelism expression, featuring various run-times and programming interfaces, ranging from compiler pragmas to dedicated programming languages. A common way of parallelising existing programs is OpenMP [DM98] which relies on compiler pragmas, extracting the parallelism from for loops while providing a task model. Numerous other parallel run-times have also been developed including StarSS [PBAL09], Kaapi [GBP07] in conjunction with a wide range of programming approaches such as Charm++ [KK93] or Cilk [BJK<sup>+</sup>95] recursive functions.

### 2.3.2 Distributed Memory

Dealing with distributed-memory parallelism, the reference programming model is the Message Passing Interface (MPI) [MF08] which relies on messages in-between distributed processes. Several MPI implementations are available including: OpenMPI [GFB+04], MPICH [GLDS96], MVAPICH [KJP08]... MPI generally relies on a combination of both high performance networks and shared memory segments, respectively providing parallelism inside and outside nodes boundaries. One advantage of MPI is its immediate support for NUMA platforms as data replication is enforced by programming model. However, these replications and message buffers overhead, inevitably lead to an increased memory usage. As a consequence, in order to face the rapid increase in terms of number of cores, MPI is often used in conjunction with OpenMP in a mixed programming approach. Limiting the number of processes per node, but, hardening program development. An alternative to message passing is the Partitioned Global Address Space (PGAS) method which consists in splitting memory over threads or distributed processes while providing a transparent access to remote data. Several PGAS implementations are available with for example UPC [EGS06], Chapel [CCZ07], X10 [CGS<sup>+</sup>05]...

### 2.3.3 Accelerators

A recent evolution in parallel computing is the advent of accelerators which are complementary devices speeding up computation thanks to a data-flow approach. Such devices generally use the Single Instruction Multiple Data (SIMD) paradigm which applies the same operation to a large data vector. Accelerators were firstly derived from graphic card and programmed through low level graphic calls (shaders), however, the growing popularity of these devices led to the development of dedicated languages, greatly simplifying development: CUDA [Nvi11] for Nvidia cards and OpenCL [M<sup>+</sup>09] for both ATI and Nvidia cards. Such devices rely on a large number of simple 'cores', decreasing energy consumption per floating point operation when compared to classical processors. This allowed supercomputers powered with Graphical Processing Units(GPUs) to dominate the Green 500 [SF12] which lists the most power efficient machines. One difficulty of GPUs is that they rely on vendor specific languages, and thus, create an adherence between codes and devices. To face this limitation, several run-times were developed among which are StarPU [ATNW11,Aug11], StarSS [Lab10], HMPP [DBB07] or the recently standardised OpenACC [Ope11] which aims at providing accelerators with a pragma based programming model. More recently, Intel released its Xeon Phi, finding a trade off between GPUs and classical processors by relying on several simple x86 processors (atom like) with extended vectorial operations (AVX) — simplifying code porting but requiring an important optimisation effort.

### 2.3.4 Summary

This section briefly introduced the variety of approaches which were developed to take advantage of supercomputers and parallel computing units. We have seen that several hardware and software approaches were developed. Some of them being vendor specific and requiring a partial code rewrite associated with a constant optimisation effort. Consequently, parallel programs have to cope with the rapid evolution of both hardware and programming models which necessarily impact simulation codes while requiring a questioning of development habits.

### 2.4 Thesis Computing Environment

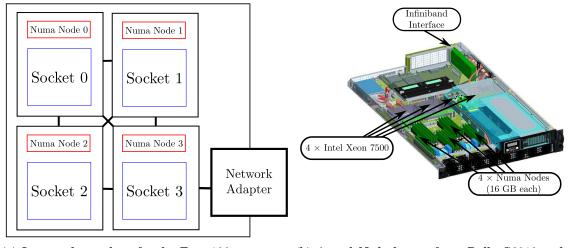

All this thesis measurements were done on two petaflopic range supercomputers. The first one is Tera 100 [TOP10, Vet13](p. 45) (figure 2.6(a)) which belongs to the CEA (Commisariat à l'Énergie Atomique et aux énergies alternatives) which use it for defence applications. The second one is Curie [TOP12] (figure 2.6(b)) which is funded by GENCI and aims at providing the french industrial tissue and research with efficient simulation tools. These two machines are manufactured by Bull SA, featuring a similar designs (see figure 2.7) although Curie uses more recent processors (Sandy Bridge) than Tera 100 (Nehalem), thus, achieving higher performances.

(a) Tera 100 Supercomputer

(b) Curie Supercomputer

Figure 2.6: Views of Tera 100 and Curie supercomputers.

| Characteristic        | Tera 100        | Curie              |  |  |  |

|-----------------------|-----------------|--------------------|--|--|--|

| R <sub>peak</sub>     | 1254.5 TFlop/s  | 1667.2 TFlop/s     |  |  |  |

| R <sub>max</sub>      | 1050.0 TFlop/s  | 1359.0 TFlop/s     |  |  |  |

| Processor type        | Intel Xeon 7500 | Intel Xeon E5-2680 |  |  |  |

| Total Number of cores | 138368          | 77184              |  |  |  |

| Total Memory          | 276736 GB       | 308736 GB          |  |  |  |

| Memory per core       | 2 GB            | 4 GB               |  |  |  |

| Operating System      | Linux (Redhat)  | Linux (Redhat)     |  |  |  |

| Interconnect          | Infiniband QDR  | Infiniband QDR     |  |  |  |

| Network Topology      | Fat-tree        | Fat-tree           |  |  |  |

Figure 2.7: Characteristics of both Tera 100 and Curie supercomputers.

#### 2.4.1 Description

These two supercomputers can be qualified as *generalist* ones as they provide powerful computing units and relatively high volumes of memory per core. They also feature very efficient Inputs and Outputs<sup>1</sup>(IOs) and legacy operating systems (Redhat Linux). Other TOP 500 machines adopted different approaches, for example, the IBM BlueGene line, favours a high number of cores with less memory per core (between 512 MB and 1 GB per core) and until recently (BlueGenes moved to linux) specifically tailored operating systems. Therefore, these two generalist machines are able to run moderately parallel payload with acceptable performance, approach not possible with architecture requiring more parallelism because of lower sequential performance. In complement of supporting a wider application spectrum, generalist supercomputers have many advantages, for example relatively to legacy codes as they are easier to port. They also have negative consequences as they do not enforce strict parallelism in the development process as such ideal machines somehow maintain the "free lunch" illusion. Moreover, this adaptability requires consequent engineering and administration efforts to hide complexity from the end user, efforts which might not suffice with next generation machines which will feature millions of cores — eventually requiring efforts from end-users. It is already the case at Petascale with supercomputers being less used as tool in a *feed-forward* fashion but be included in the simulation process as an evolving tool which requires tradeoffs and *feedback*. Evolution testified by the development of several optimisation tools. Our thesis work acknowledges this context and proposes to develop an optimisation tools which is integrated in the development process, providing constant feedback on program's performance and positively influencing their adaptation to evolving execution substrates.

#### 2.4.2 Node Description

As presented in figure 2.8(a), a Tera 100 node consists in four NUMA sockets with 16 GB of local memory for a total of 64 GB per node. Each socket hosts an eight core Intel Xeon 7500 processor cadenced at 2.27 GHz, yielding a total of 32 cores with 2 GB of memory per core. Nodes have a single Infiniband [Pfi01,  $A^+01$ ] Quad Data Rate(QDR, 3.2 GB/s) card <sup>2</sup> located nearby a single socket. This configuration creates Non-Uniform Input/Outputs Access (NUIOA) effects [MGN10, Mor11] where one socket has a privileged network access compared

<sup>&</sup>lt;sup>1</sup> Tera 100 had upon its release a record IO throughput of 500 GB/s.

<sup>&</sup>lt;sup>2</sup> Each node also feature a Gigabit ethernet interface for administration puposes.

(a) Intra-node topology for the Tera 100 supercom- (b) Actual Node layout for a Bullx S6010 node in 1.5U (3D rendering is from S6010 support page [Bul10]).

to the three others. All these components fit in a Bullx Super-Node 6010 of 1.5 Rack Unit(U). Allowing when L-shaped blade are stacked top-to-tail at a high density of 64 cores in 3U.

### 2.4.3 Network Topology

Figure 2.9: Overview of Tera 100 node (Bullx Super-Node 6010) topology.

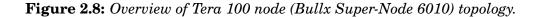

Tera 100 topology [Vet13](p. 53) is derived from a fat tree [Lei85, Gra03]. As presented in figure 2.9(a), in a fat-tree routers are connected with an increasing number of links which role is to compensate the loss of locality in terms of bandwidth (not in latency as the number of hops increases). Fat-tree topologies also have the propriety of being able to efficiently convey any communication topology with a satisfying efficiency [Lei85]. Propriety which can be understood by looking at bandwidth scattering: thanks to the increasing number of links when climbing the tree, any partition of nodes is guaranteed to reach the full bisection bandwidth. Therefore, different topologies can run over a fat tree with limited performance impact on bandwidth, whereas latency is only impacted logarithmically when the number of nodes in-

creases (tree-based topology). Fat-trees are then interesting topologies for generalist machines which want to be able to run a wide range of codes.

However, if we look more closely at Tera 100 network, it uses a *pruned* version of the fat tree, in order to reduce both network costs and complexity while preserving performances. As presented in figure 2.9(b), computing nodes are regrouped in thirteen *island* of 324 nodes around the same Infiniband router. Therefore, each island gathers  $324 \times 4 \times 8 = 10368$  cores in a star topology. Moreover, several island are interconnected with smaller routers (36 ports) to form the whole 140 000 core machine. As depicted in figure 2.9(b), total leaf bandwidth  $(324 \times 3 = 972 \text{ GB/s})^3$  is six times greater than the up-link bandwidth  $(162 \text{ GB/s})^4$  because of *pruning*. This  $\frac{1}{6}$  pruning ratio reduced costs and network complexity while preserving correct performance for regular jobs and full machine runs. More importantly, as most jobs are in the 1000-10000 range, they can take advantage of a regular star topology, while relying on the up-link solely for Inputs and Outputs.

### 2.5 Summary

This section presented the quickly evolving supercomputing context in which simulation codes which generally evolve at a slower pace have to constantly adapt themselves to new hardware constraints and programming models. We insisted on the topology of supercomputer which has a direct impact over computation scattering and therefore has to be taken into account by developers. We ended this chapter with a presentation of the two machines which are used in the rest of this document. They both feature several cores per node with a nonuniform memory architecture and a high performance Infiniband network relying on a fat-tree network. In the light of this brief introduction, we have seen that these rapidly evolving and complex architectures are very challenging and therefore require a constant effort to be used productively. Effort which we aim at supporting with the tools developed during this thesis.

<sup>&</sup>lt;sup>3</sup> '3' is approximately the Infiniband QDR (4X) data-rate in GB.

$<sup>^4</sup>$  Note that the "service island" has a higher up-link bandwidth of 648 GB/s (216 imes 4X).

### CHAPTER 3

## **Development Cycle**

"**Don't gather requirements — Dig for them** Requirements rarely lie on the surface. They're buried deep beneath layers of assumptions, misconceptions and politics."

> Hunt and Thomas in the Pragmatic Programmer [HT99] (Quick Reference Guide)

After we introduced supercomputers and current and upcoming challenges they are associated with, this section briefly introduces software development methodologies which give context to the use of the tools we developed during this thesis. After introducing the purpose of adopting a development methodology, we present classical approaches followed by an outline of several requirements associated with development in complex environment. Eventually, we finish up by exposing advantages which can be provided by tools when being used as heuristics.

### 3.1 Classical Development Methodologies

A development methodology can be seen as a management approach which aims at coordinating software developers, their managers and clients in a facilitating environment focused on optimising the production of better software. Several organisation models were developed in order to facilitate complex objects conception. Interestingly, all those models feature the same basic blocks, differing more in their usage than in their strict organisation. This section first describes the basic blocks being used in each process from an operative point of view. Then, we present in order of appearance the three classical development cycle.

### 3.1.1 Constants in the Development Cycle

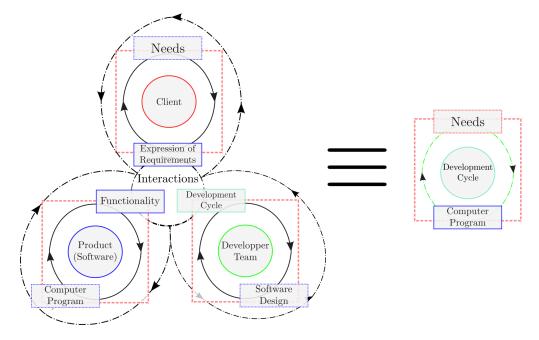

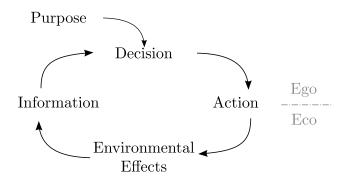

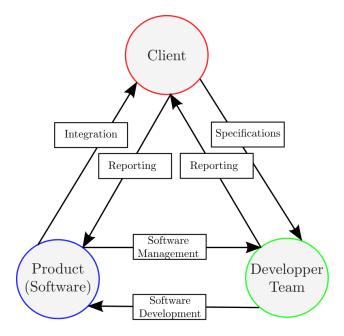

Development cycle purpose is to formalise the relationship between three entities (1) the client, (2) a development team and (3) the code itself. This first section describes those entities in an empirical context in order to introduce the development process and its goals. To do so, we describe in a methodology agnostic manner some expectations and duties for each of those actors as follows:

• **The client** is at requirements source as he originally formulated them according to his needs. He generally expresses them to potential developers (often through a documen-

tary process) and selects a solution *rationally* (quality of the solution, maintainability, overall costs, ...) suiting his demand after reviewing preliminary design proposals (Client  $\leftrightarrow$  Developer iteration). Omitting, intermediate Developer  $\leftrightarrow$  Client iteration we are going to analyse from a developer point of view, the client is eventually in charge of judging product quality, attesting that it effectively satisfies his requirements. This last phase, involves, for example, demonstrations, integration tests (...) and eventually leads to the effective deployment at client's site (Progam  $\leftrightarrow$  Client iteration).

- The development team is central to the development process as it is in charge of (1) understanding the client's need, formulating them as a potential design (Client ↔ Developer iteration) and (2) expressing this design as a program which fits client's requirements (Developer ↔ Program iteration). Programmers are therefore an interface between codes and clients, understanding needs and transposing them in a program which exactly<sup>1</sup> fulfils their requirements (generally with design constraints: architectural, costs and design trade-offs, ...). This, while remaining in client's acceptance range.

- The program is the development effort final product, supposed to fulfil every requirements while guaranteeing several qualities such as reliability, maintainability, code readability (...). In other words, client's requirements have to be transposed in the program in terms of features (Progam ↔ Client iteration). However, this process complexity must remain manageable by developers, supposing a known and suitable design (Progam ↔ Developer iteration).

Development cycle aims at defining interactions between this trinity in purpose of maximising their efficiency. It supposes an ability for each of those entities to maintain a constant coupling in purpose of maintaining mutual understanding. For example, the solution space satisfying a given need is generally very wide (choice of languages, definition of the interface, usage patterns, autonomy level, ....). Possibly requiring several client intervention in the design process. Similarly, programmers have to maintain their program in control for example by setting a suitable environment for *monitoring* its features and reliability. Moreover, the development team itself has to be structured (from a management point of view) to face common conception risks (individual cognitive limitations, knowledge dilution, responsibility dilution, ...) and requirements (manageability, planning, productivity, ...). Consequently, it can be seen that the development process involves multiple intricate level of representation with varying constraints. Those levels are connected by several interactions (documentary, oral, formal or not, ...) which can be equally bounded by either communications hazards or phenomenon complexity. From this point of view the development cycle can be seen as an heuristic which codifies interactions in the process leading from a need to a solution. In this purpose, it defines communication templates, efficiency metrics and methods, helping developers to face the complexity of their work.

After this high level development process contextualisation, we will now focus on the main existing models. It shall be noted that such model can be very normative, detailing each document, scheduling interactions, (...). Comparatively, our descriptions will remain brief, as it solely aims at providing a sufficient context to the description of our work in the rest of this

<sup>&</sup>lt;sup>1</sup> Here *exactly* shall be understood as minimising development costs relatively to classical management metrics (costs, time, workload, risks,...). The development team is supposed to furnish a *rational* solution focused on *satisfying* the requirements, not an ideal solution (see H.A. Simon who develops these notions in [Sim97]).

document. We will try to reference complementary documents providing a wider view on the subject for readers interested in details.

#### 3.1.2 Waterfall Model

The waterfall project management model introduced by Royce [Roy70] is the most "natural" development model anyone would adopt when required to fulfil a requirement. It sequentially goes from gathering requirements to the integration and maintenance of the new product.

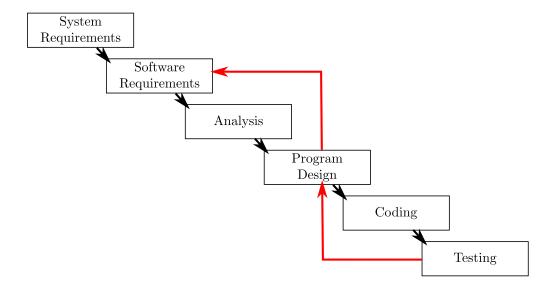

**Figure 3.1:** Original waterfall model as introduced by Royce in [Roy70], including feedback loops.

This process is generally described as a sequential process where phases succeed to each other after a careful validation. In this context, as presented in Figure 3.1, needs and design are both carefully expressed long before the coding phase. This model requires important documentary efforts at each phase, so that clients remain informed of project evolution. Such cycle is also often cited to have the drawback of freezing the design too early in the development process [Mar99, Rot11], neglecting unplanned requirement shifts or unplanned constraints. This effect is called the tunnel effect, after specification phase, clients have "no news" from the developer team until seeing the effective product. This augments the risk of not fulfilling needs because of a communication lack and late risk factor identification as sometimes they can only be identified when implementation begun.

Waterfall was very common in the 80's as it happened to be advocated by large industries [Dep85, Dep88] as the reference model. However, its limitations led to new development approaches which favour a more iterative approach. Nonetheless, it shall be noted that Royce in its original paper [Roy70] already promoted an iterative approach (see Figure 3.1 with feedback loops in red), he even required the waterfall approach to be done twice (p. 7) recognising that some requirement can be sensed only when actually implementing a product. Therefore, even if misapplied as a sequential process, the waterfall model clearly sets the canonical process of a project management model in term of control and reporting but lacks of adaptability when dealing with the development process itself. Nonetheless, it is still widely used (in modified forms as detailed in the next section), mainly for large industrial or building projects which can reasonably express requirement early in the development cycle. However, software design which is subject to evolving constraints had to rely on iterative methods which eventually led to *agile methods*.

### 3.1.3 V-Model

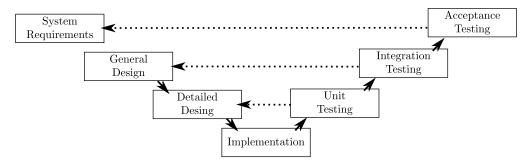

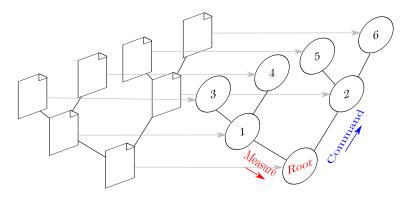

Figure 3.2: Example of V-Model development cycle.

The V-Model can be seen as a derivation of the waterfall model where testing phases are designed symmetrically with conception phases. Despite its V shape, this process is still linear and therefore falls in the pitfalls of the linear waterfall model (tunnel effect). Moreover, there are a wide range of interpretation of the V-model featuring different verbosity<sup>2</sup> levels while preserving original waterfall steps. Another ambiguity is in the links between testing and design phases, are they bidirectional or unidirectional ? Again, varying answers can be found. However, V-models are widely adopted for large project management being featured in several methodologies (naturally with variations): the German V-Model [IAB95], United States Department of Transportation guidelines [Uni07], Great Britain Office of Government Commerce PRINCE2 methodology [oGC02]...

As a consequence, the V-Model can be described as an advantaging method in terms of outsourcing as from a management point of view, specification and integration phases are covered. However, dealing with implementation phase itself, it is generally depicted as a single step, the bottom of the V, as far as possible from clients. On implementation side, methods are always iterative as developers progressively fulfil requirements. They might have new interrogations as they get a better understanding of the project, but how does the client answer them in a V process ? Implementing a software project is being able to both understand and fulfil clients' needs. This supposes that the client is able to *express* (specifications) and *judge* (acceptance) the product while developers *understand* (design) and *satisfy* (integration) requirements. In the V-Model this coupling happens only once (and leads to the V shape), whereas, developers and clients might need a stronger coupling to face evolving needs or constraints, observation which led to an iterative development process which aims at preventing tunnel effects by enforcing communication.

<sup>&</sup>lt;sup>2</sup> An image search of 'V-Model' on any search engine can illustrate this variety.

#### 3.1.4 Agile Methods

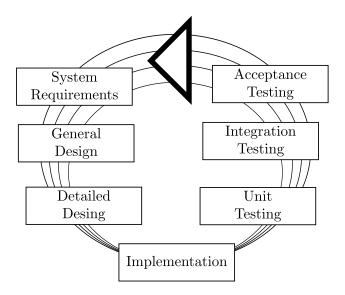

Figure 3.3: Example of agile development cycle.

In opposition with classical project methodologies we developed in previous paragraphs, agile methods are profoundly iterative. Their purpose is to prevent tunnel effect by involving clients in development phases in order to confirm requirements and diagnose possible risks early in the development. As presented in Figure 3.3, this process can be seen as an iterative V-process which purpose is to couple client and developers through *control* (requirements) and *measure* (tests) (similar to the Wiener feedback loop of Figure 3.6). Agile methods as introduced in the agile manifesto [BBvB<sup>+</sup>01] feature a lightweight project methodology, reducing documentary process to a minimum while privileging communication. In that sense, they are more focused on the actual development process than on managing the outsourcing process. For example, developers are able to iterate on technical aspects (for example through intermediate versions) before delivering the final product — guaranteeing client needs are actually understood and satisfied [Rot11].

> "Individuals and interactions over processes and tools Working software over comprehensive documentation Customer collaboration over contract negotiation Responding to change over following a plan

That is, while there is value in the items on the right, we value the items on the left more."

#### **Figure 3.4:** Four main values quoted from the agile manifesto as found on $[BBvB^+01]$ .

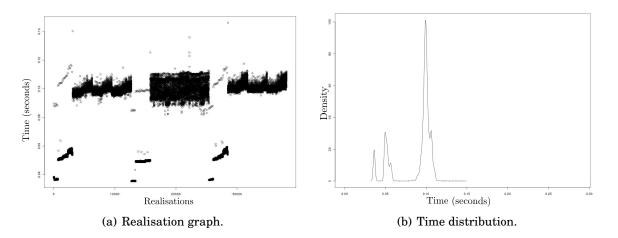

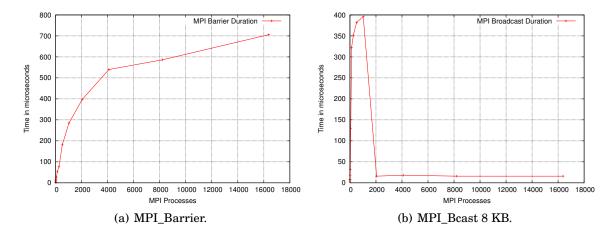

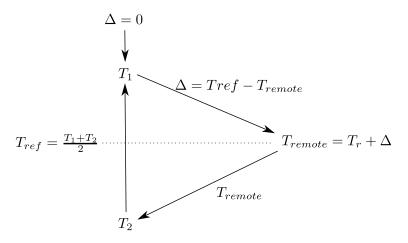

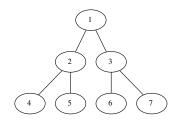

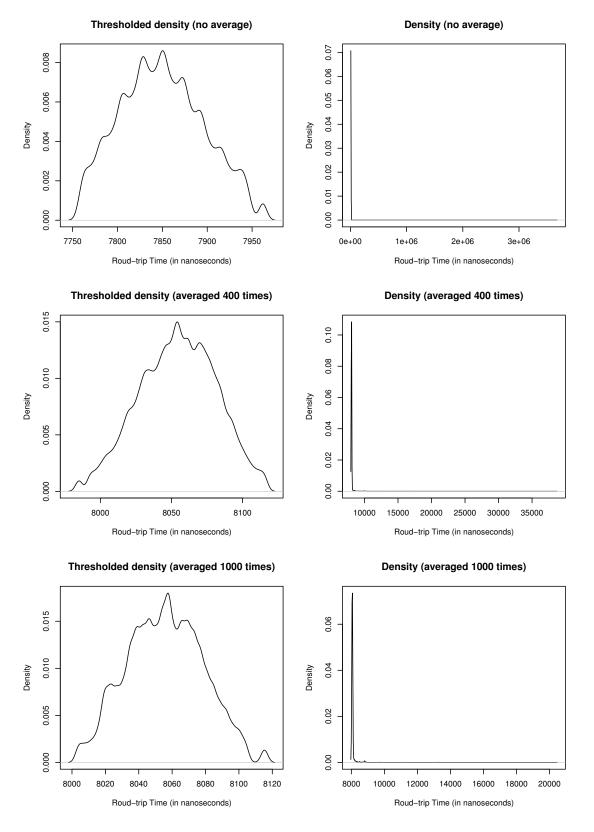

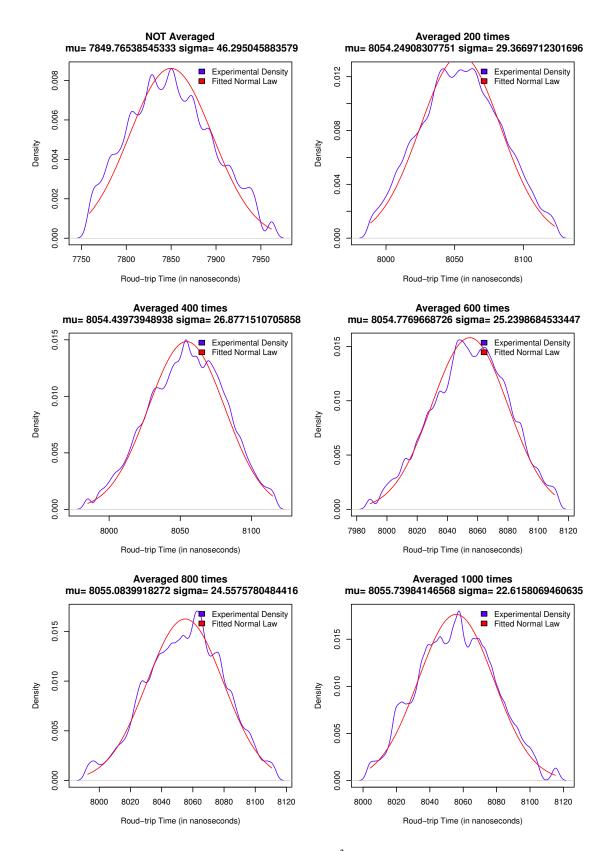

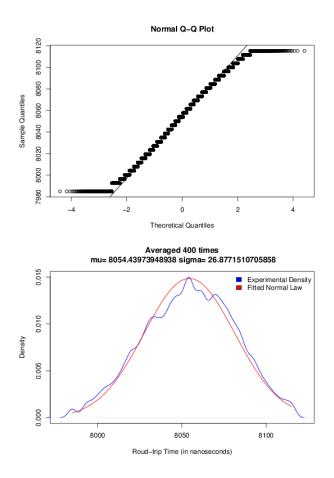

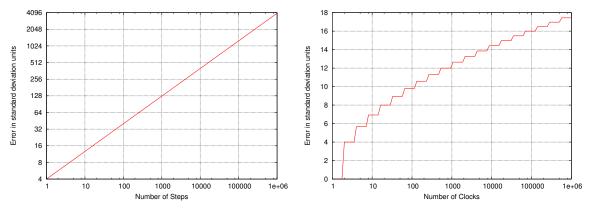

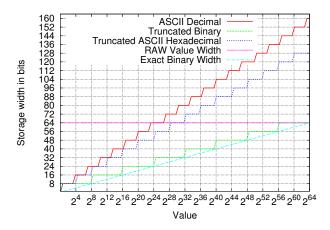

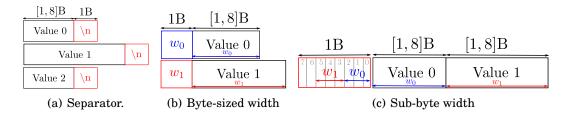

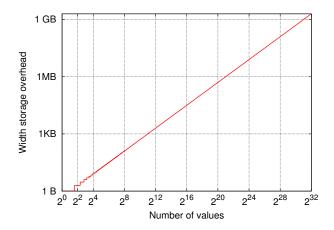

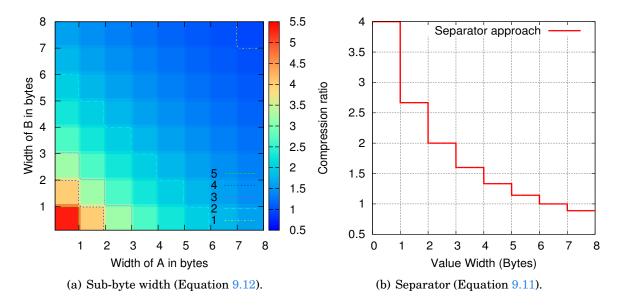

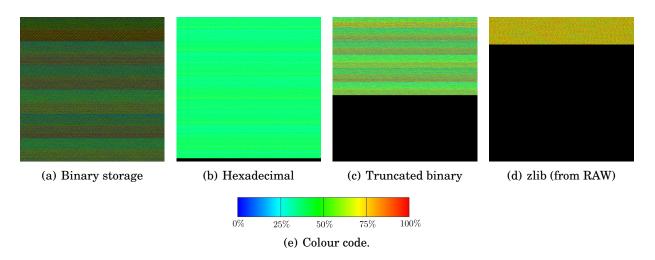

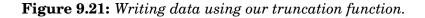

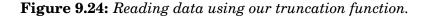

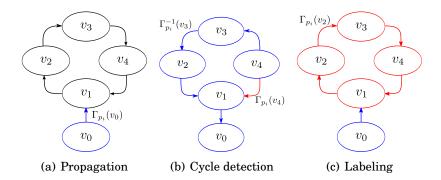

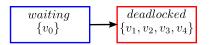

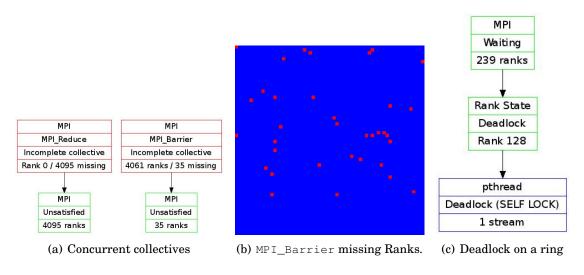

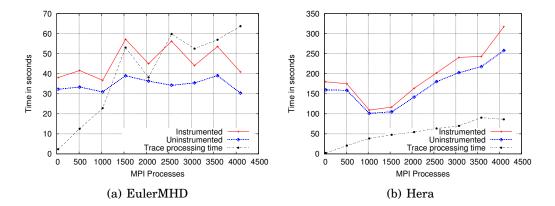

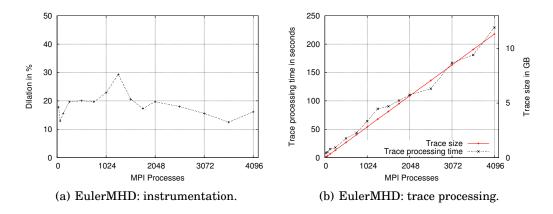

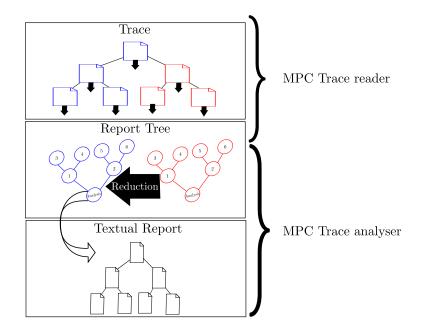

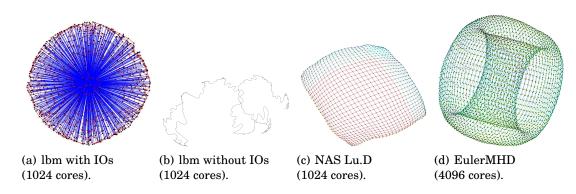

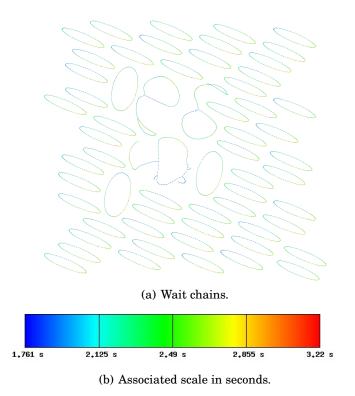

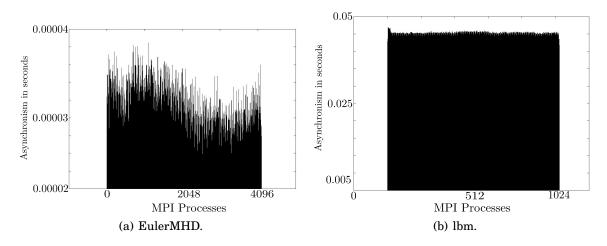

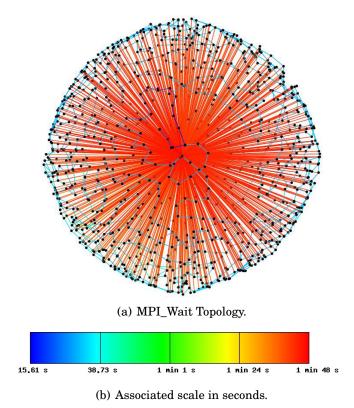

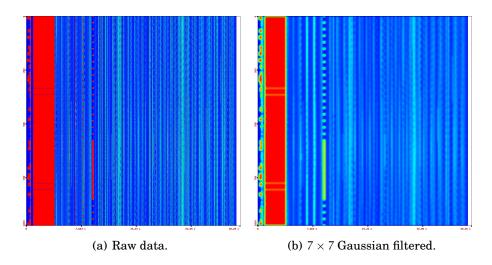

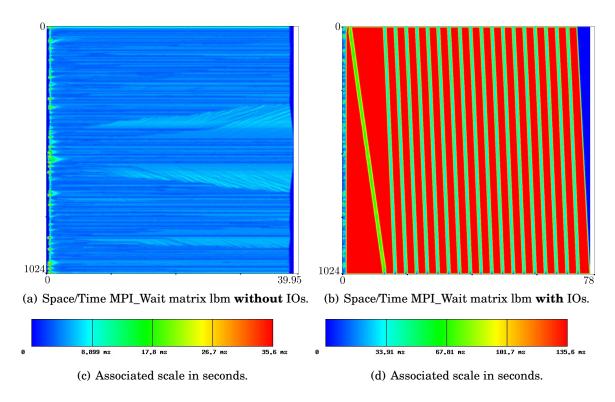

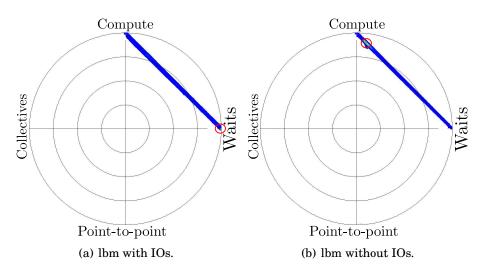

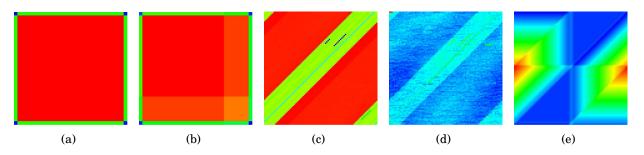

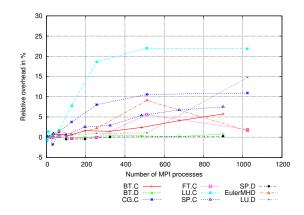

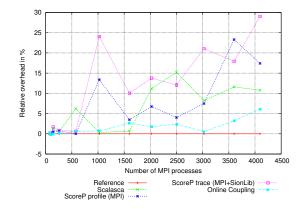

The agile manifesto [BBvB<sup>+</sup>01], which is quoted in Figure 3.4 insists on four main values which gave origin to a wide range of agile programming models with varying methods: Adaptive Software Development (ASD) [Hig00], Crystal Clear [Coc04], Dynamic Software Development Method (DSDM) [Con08], Rapid Application Development (RAD) [Mar91],