# Sécurisation de programmes assembleur face aux attaques visant les processeurs embarqués

Nicolas Moro

#### ▶ To cite this version:

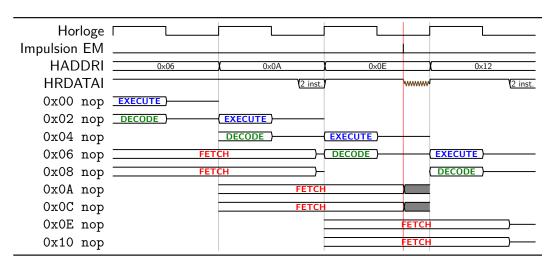

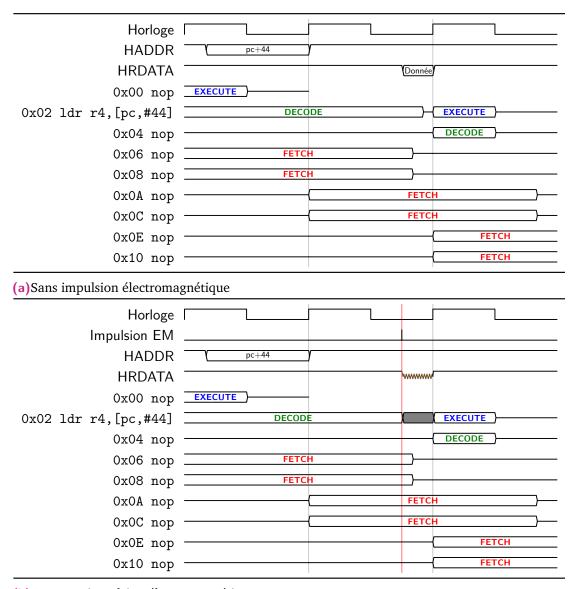

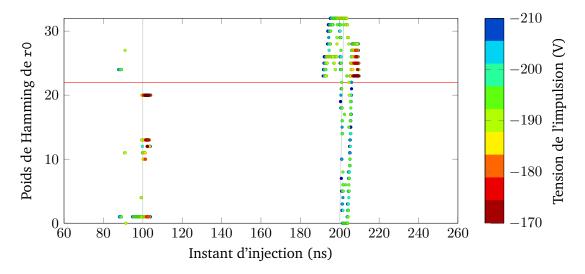

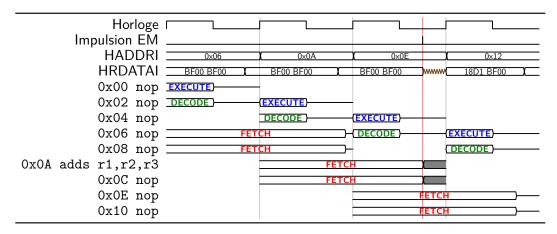

Nicolas Moro. Sécurisation de programmes assembleur face aux attaques visant les processeurs embarqués. Cryptographie et sécurité [cs.CR]. Université Pierre et Marie Curie - Paris VI, 2014. Français. <NNT: 2014PA066616>. <tel-01147122>

HAL Id: tel-01147122

https://tel.archives-ouvertes.fr/tel-01147122

Submitted on 29 Apr 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

### Spécialité

#### Informatique

École doctorale Informatique, Télécommunications et Électronique (Paris)

Présentée par

#### **Nicolas MORO**

Pour obtenir le grade de

### DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

Sujet de la thèse:

# Sécurisation de programmes assembleur face aux attaques visant les processeurs embarqués

Soutenue à Paris le 13 novembre 2014

| M.  | Pascal Berthomé       | Rapporteur   | INSA Centre Val de Loire, Bourges |

|-----|-----------------------|--------------|-----------------------------------|

| M.  | Jean-Louis LANET      | Rapporteur   | INRIA, Rennes                     |

| M.  | Jean-Claude BAJARD    | Examinateur  | UPMC, Paris                       |

| M.  | Christophe GIRAUD     | Examinateur  | Oberthur Technologies, Bordeaux   |

| M.  | Sylvain GUILLEY       | Examinateur  | Telecom ParisTech, Paris          |

| M.  | Jean-François LALANDE | Examinateur  | INSA Centre Val de Loire, Bourges |

| M.  | Pascal PAILLIER       | Invité       | CryptoExperts, Paris              |

| Mme | Emmanuelle Encrenaz   | Directrice   | UPMC, Paris                       |

| M.  | Bruno Robisson        | Co-directeur | CEA, Gardanne                     |

| Mme | Karine HEYDEMANN      | Encadrante   | UPMC, Paris                       |

# Remerciements

Le lecteur averti aura noté un nombre anormalement élevé de logos en première page, et pourrait se demander pourquoi tant d'encre couleur a été utilisée. Si ce même lecteur effectue une recherche sur Internet et tombe sur mon CV, il risque de se poser quelques questions... une thèse CEA à Gardanne, dans une équipe d'abord rattachée au LETI de Grenoble, puis ensuite rattachée à la division CEA-Tech PACA de Cadarache, tout en étant inscrit comme étudiant de l'Université Pierre et Marie Curie à Paris et pour au final travailler à l'École des Mines de Saint-Étienne... mais pas à Saint-Étienne. La quintessence de la complexité administrative à la française! Mais concrètement, j'ai passé le plus clair de mon temps à Gardanne et ce manuscrit de thèse représente l'aboutissement de 6 années passées (dont 3 comme élèveingénieur) sur le site Georges Charpak de l'École des Mines de Saint-Étienne, à Gardanne.

Après cet avant-propos nécessaire pour clarifier un peu ma situation, je souhaiterais tout d'abord remercier Pascal Berthomé et Jean-Louis Lanet pour avoir accepté d'être rapporteurs pour ce travail de thèse. Un grand merci également à Jean-Claude Bajard, Christophe Giraud, Sylvain Guilley, Jean-François Lalande et Pascal Paillier pour avoir accepté de faire partie de mon jury de thèse. J'adresse également mes remerciements à Jean-Luc Danger et Franck Wajsbürt, qui avaient bien généreusement accepté d'être les membres de mon jury d'évaluation de mi-thèse.

Ensuite, je souhaiterais bien évidemment remercier tous ceux qui, par leur soutien, ont contribué à la réussite de cette thèse. En premier lieu, je pense en particulier à Bruno Robisson, qui m'a accompagné au quotidien pour mes travaux pendant ces 3 années, ainsi qu'Emmanuelle Encrenaz qui, malgré la distance, a toujours assuré un excellent suivi de mes travaux et m'a beaucoup aidé notamment pour tout ce qui concerne la vérification formelle. Je les remercie tous deux pour la confiance qu'ils m'ont accordée et pour avoir dirigé mes travaux pendant ces trois années. Un remerciement spécial va à Karine Heydemann, qui a également encadré cette thèse pendant les deux dernières années, avec qui j'ai beaucoup apprécié travailler et pour qui l'art de la compilation ou la transformation de code assembleur n'ont plus de secrets, en plus d'être au moins aussi perfectionniste que moi dans la rédaction d'articles. Je souhaite par ailleurs remercier également Bruno, Emmanuelle et Karine pour leurs relectures attentives des différentes versions de ce manuscrit et sans

qui celui-ci serait de bien moindre qualité. Un autre remerciement très spécial va à Amine Dehbaoui, avec qui j'ai également beaucoup apprécié travailler et qui a été pendant près de deux ans mon co-encadrant *de facto*, grand virtuose du banc d'injection électromagnétique qui connaît à peu près tout ce qui va du silicium au buffer overflow.

Je remercie également tous ceux qui ont partagé mon quotidien pendant ces années, qui ont partagé une bière au Tibbar avec moi ou m'ont écouté leur parler longuement de ma vision de l'organisation de l'école ou encore des plans machiavéliques de l'association des anciens. Ce sont d'autres thésards, d'anciens professeurs, des stagiaires, et plus généralement des personnes qui ont contribué à rendre fort sympathique le quotidien à l'école. Je pense notamment à Olivier Vallier, Guillaume Reymond (qui a la réponse à toutes les questions du type "Comment on fait pour faire proprement ...?"), Jacques Fournier, Jean-Max Dutertre, Driss Aboulkassimi, Amir-Pasha Mirbaha, Jean-Pierre Nikolovski, Philippe Maurine, Laurent Freund, Jérôme Quartana, Anne-Lise Ribotta, Jean-Baptiste Rigaud (quand il est énervé, on entend la marche impériale), Romain Wacquez, Kamil Gomina, Alexandre Sarafianos, Cyril Roscian, Florian Praden (alias JJ, un danger perpétuel pour tout système sécurisé qui tombe entre ses mains), Franck Courbon (comme quoi on peut être thésard et bien habillé), Stéphan De Castro, Sébastien Tiran (qui m'impressionne par sa zénitude face aux débats de ses voisins de bureau), Yanis Linge, Maxime Lecomte (un Breton pas chauvin, si, ça existe), Nicolas Borrel, Clément Champeix, Alexis Krakovinski, Serge Seyroles, Thierry Vaschalde, Claire Pechikoff, Loïc Lauro, Romain Ferrand, Marie Paindavoine, Jean-Yves Zie, Victor Murillo, Assia Tria, Marc Ferro (mon adversaire de baby-foot préféré), Cassandre Vuillaume, Scherrine Tria, Eloise Bihar, Manuelle Bongo, Pierre Leleux, David Elbaze, David Cambon, Thomas Lonjaret, Sylvain Blayac, Clément Talagrand, Henda Basti, Etienne Drahi, Mathieu Leroux, Thierry Camilloni, Oussama Benzaim, Cyril Calmes, Roger Delattre, Jean-Michel Li, Philippe Lalevée, Bénédicte Franceschi, Catherine Dessi, Christian Buatois, François Jaujard, Pascal Gelly, Karine Canivet, Michel Fiocchi, Véronique Villaréal, Georges Loubière, Jean-Michel Li, Nabil Absi, Dominique Feillet, Claude Yugma, Stéphane Dauzère-Pérès, Hervé Jacquemin, Jakey Blue, Gracien Counot, Manon Leoni, Florent Bitschy, Sabine Salmeron, Richard Lagaize, Michelle Gillet, Thierry Ricordeau, Phillipe Caillouet, Pierre Joubert... et j'en oublie très certainement! Et bien entendu, il n'y avait pas que des thésards ou des professeurs dans cette école : il y avait aussi des élèves-ingénieurs. Je pense notamment à Stéphane Collot, Bertrand Rossignol, Erwan Henry, Laurent Legrigeois, Charles Nguyen, Geoffrey Walter, Mikael Marin, Ludovic Lourenço, Kévin Arth, Vincent Caravéo, Loïc Bois, Franck Valdenaire, Margaux Raffoul, Umar Saleem, Louiza Khati, Eleonore Hardy, ... bref, à tous ceux avec qui j'ai pris beaucoup de plaisir à refaire le monde au Tibbar tous les jeudis soirs pendant deux ans (et j'en oublie encore!). Parmi les personnages marquants de ces six années passées à l'école, je me dois également de remercier Bernard Dhalluin, qui m'a fourni de précieux

conseils sur le monde de la recherche alors que j'étais encore élève-ingénieur et avec qui j'ai beaucoup aimé collaborer dans le cadre de l'association des anciens, ainsi que Jean-Paul Ramond également pour ses conseils sur la thèse et en partie grâce à qui j'ai pu effectuer mon stage de dernière année d'école à Taïwan. Cette thèse aurait également été bien plus difficile sans d'abord Bénédicte Messina, puis ensuite Patricia Murrisch, qui m'ont aidé à m'y retrouver dans les strates administratives plus que nombreuses du CEA et qui ont toujours fait preuve d'une grande patience face à mes appels au secours ou mes formulaires mal remplis.

Un remerciement spécial également à Hélène Le Bouder et Ronan Lashermes (nos deux Bretons un peu chauvins sur les bords) ainsi qu'à Thomas Sarno (mon grand adversaire de débats idéologiques sur à peu près tous les sujets), Marc Lacruche (ouais ouais ouais) et Ingrid Exurville (championne du monde du macaron au caramel et beurre salé). Ah, et j'allais justement oublier Patrick Haddad, notre fournisseur officiel de saucissons et de petits coussins lyonnais! Je tiens également à remercier tous les proches et amis qui n'étaient pas présents au quotidien mais à qui j'ai tellement parlé de ce fameux quotidien que c'est un peu comme si finalement ils y avaient été. Je pense en particulier à Adrien, Pierre-Yves, Béné, Gaby, Laure, Sophie, . . . mais là, si je dois tous les lister ça risque de prendre encore plusieurs pages.

J'aimerais également remercier tout particulièrement les membres de ma famille, pour m'avoir toujours accompagné et soutenu pendant toutes ces années d'études supérieures et qui m'ont toujours permis de suivre la voie que je désirais. Je pense bien évidemment tout particulièrement à mes parents et mes deux frères Arnaud et Mr Big, ainsi que mes grand-parents et ma grand-mère, toutes ces personnes à qui je dois beaucoup et sans qui je ne serais pas là où j'en suis aujourd'hui.

Enfin, mes tous derniers remerciements ne peuvent qu'aller à Loïc et Yuting. Pendant ces trois années de thèse, Loïc a occupé à la fois les casquettes de co-thésard, voisin de bureau, colocataire et bien entendu interlocuteur privilégié pour refaire le monde (avec quand même une petite touche de mauvaise foi quant au tapis de la salle de bains)... bref, heureusement qu'il était là ! Et Yuting, bien évidemment, que je remercie pour son soutien pendant toutes ces années, d'abord depuis Taïwan puis directement en France. Je sais que ces années de thèse auraient été beaucoup plus difficiles si elle n'avait pas été là. Et maintenant que la thèse est finie, comme elle me dit si souvent... « Il faut travailler le Chinois ! »

# Résumé

Cette thèse s'intéresse à la sécurité des programmes embarqués face aux attaques par injection de fautes. La prolifération des composants embarqués et la simplicité de mise en œuvre des attaques rendent impérieuse l'élaboration de contre-mesures.

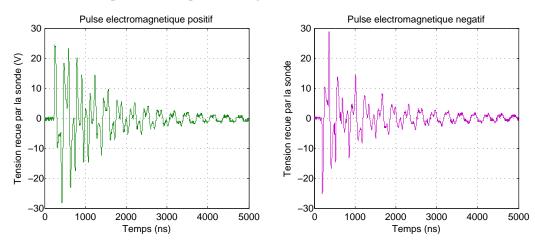

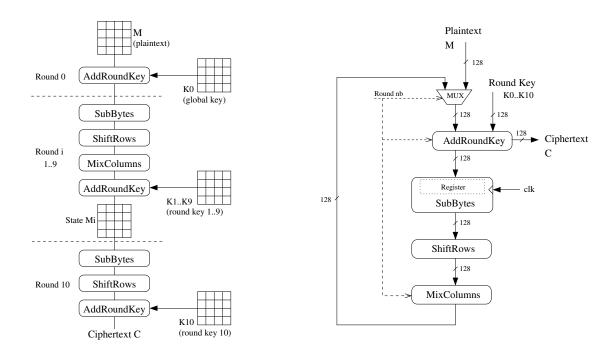

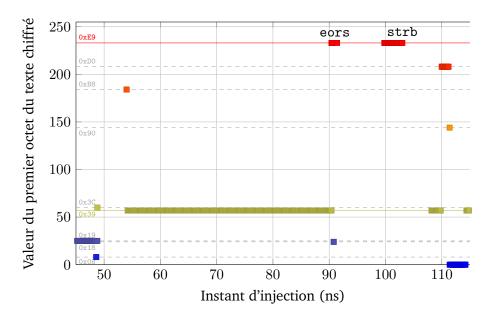

Un modèle de fautes par l'expérimentation basé sur des attaques par impulsion électromagnétique a été élaboré. Les résultats expérimentaux ont montré que les fautes réalisées étaient dues à la corruption des transferts sur les bus entre la mémoire Flash et le pipeline du processeur. Ces fautes permettent de réaliser des remplacements ou des saut d'instructions ainsi que des modifications de données chargées depuis la mémoire Flash.

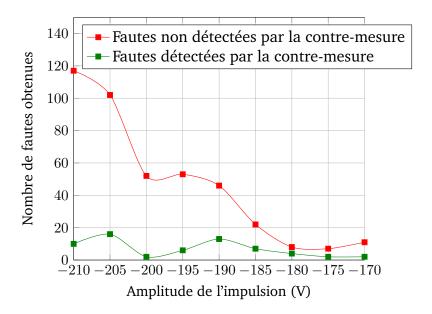

Le remplacement d'une instruction par une autre bien spécifique est très difficile à contrôler ; par contre, le saut d'une instruction ciblée a été observé fréquemment, est plus facilement réalisable, et permet de nombreuses attaques simples. Une contre-mesure empêchant ces attaques par saut d'instruction, en remplaçant chaque instruction par une séquence d'instructions, a été construite et vérifiée formellement à l'aide d'outils de model-checking.

Cette contre-mesure ne protège cependant pas les chargements de données depuis la mémoire Flash. Elle peut néanmoins être combinée avec une autre contre-mesure au niveau assembleur qui réalise une détection de fautes. Plusieurs expérimentations de ces contre-mesures ont été réalisées, sur des instructions isolées et sur des codes complexes issus d'une implémentation de FreeRTOS. La contre-mesure proposée se révèle être un très bon complément pour cette contre-mesure de détection et permet d'en corriger certains défauts.

**Mots-clés**: attaques par injection de fautes ; injection électromagnétique ; modèle de fautes ; contre-mesures vérifiées ; assembleur ; saut d'instruction

# **Abstract**

This thesis focuses on the security of embedded programs against fault injection attacks. Due to the spreadings of embedded systems in our common life, development of countermeasures is important.

First, a fault model based on practical experiments with a pulsed electromagnetic fault injection technique has been built. The experimental results show that the injected faults were due to the corruption of the bus transfers between the Flash memory and the processor's pipeline. Such faults enable to perform instruction replacements, instruction skips or to corrupt some data transfers from the Flash memory.

Although replacing an instruction with another very specific one is very difficult to control, skipping an instruction seems much easier to perform in practice and has been observed very frequently. Furthermore many simple attacks can carried out with an instruction skip. A countermeasure that prevents such instruction skip attacks has been designed and formally verified with model-checking tool. The countermeasure replaces each instruction by a sequence of instructions.

However, this countermeasure does not protect the data loads from the Flash memory. To do this, it can be combined with another assembly-level countermeasure that performs a fault detection. A first experimental test of these two countermeasures has been achieved, both on isolated instructions and complex codes from a FreeRTOS implementation. The proposed countermeasure appears to be a good complement for this detection countermeasure and allows to correct some of its flaws.

$\textbf{Keywords:} fault injection \ attacks: electromagnetic injection: fault model: verified \ countermeasures: assembly: instruction skip$

# Table des matières

| Re | emerc  | iement  | cs                                                            | i    |

|----|--------|---------|---------------------------------------------------------------|------|

| Ré | ésumé  | 5       |                                                               | v    |

| ΑI | ostrac | ct      |                                                               | vii  |

| In | trodu  | ction g | générale                                                      | xiii |

| 1  | Con    | texte e | et motivations                                                | 1    |

|    | 1.1    | Introd  | luction                                                       | 1    |

|    | 1.2    | Princi  | pes généraux des attaques physiques                           | 2    |

|    |        | 1.2.1   | Cryptographie embarquée                                       | 2    |

|    |        | 1.2.2   | Canaux auxiliaires et grandeurs observables                   | 3    |

|    |        | 1.2.3   | Canaux auxiliaires utilisés pour la réalisation d'attaques    | 3    |

|    | 1.3    | Attaqı  | ues par observation et contre-mesures                         | 3    |

|    |        | 1.3.1   | Données observables par un attaquant                          | 4    |

|    |        | 1.3.2   | Modèles de consommation                                       | 8    |

|    |        | 1.3.3   | Exploitation des données obtenues                             | 10   |

|    |        | 1.3.4   | Rétro-ingéniérie                                              | 14   |

|    |        | 1.3.5   | Contre-mesures                                                | 15   |

|    | 1.4    | Attaqı  | ues par injection de faute et contre-mesures                  | 17   |

|    |        | 1.4.1   | Moyens d'injection de faute                                   | 18   |

|    |        | 1.4.2   | Modèles de fautes                                             | 21   |

|    |        | 1.4.3   | Exploitation des données obtenues                             | 23   |

|    |        | 1.4.4   | Contre-mesures                                                | 24   |

|    | 1.5    | Object  | tifs de la thèse et approche choisie                          | 26   |

|    |        | 1.5.1   | Objectifs                                                     | 26   |

|    |        | 1.5.2   | Approche choisie                                              | 27   |

|    | 1.6    | Concl   | usion                                                         | 27   |

| 2  | Con    | ceptior | n d'un banc d'injection de fautes pour processeur ARM Cortex- |      |

|    | M3     |         |                                                               | 29   |

|    | 2.1    | Introd  | luction                                                       | 29   |

|    | 2.2    | Proces  | sseur ARM Cortex-M3                                           | 30   |

|    |        | 2 2 1   | Iou d'instructions                                            | 21   |

|   |      | 2.2.2  | Registres                                                      | 32 |

|---|------|--------|----------------------------------------------------------------|----|

|   |      | 2.2.3  | Modes d'exécution                                              | 34 |

|   |      | 2.2.4  | Exceptions matérielles                                         | 34 |

|   |      | 2.2.5  | Pipeline et exécution des instructions                         | 35 |

|   |      | 2.2.6  | Mémoires d'instructions et de données                          | 36 |

|   |      | 2.2.7  | Bus de données et d'instructions                               | 36 |

|   |      | 2.2.8  | Préchargement d'instructions depuis la mémoire                 | 37 |

|   |      | 2.2.9  | Chaîne de compilation                                          | 37 |

|   | 2.3  | Dispos | sitif expérimental d'injection de fautes                       | 39 |

|   |      | 2.3.1  | Montage expérimental d'injection                               | 39 |

|   |      | 2.3.2  | Processus expérimental                                         | 41 |

|   |      | 2.3.3  | Bilan sur le dispositif expérimental utilisé                   | 43 |

|   | 2.4  | Expéri | imentations sur une implémentation de l'algorithme AES         | 44 |

|   |      | 2.4.1  | Advanced Encryption Standard (AES)                             | 44 |

|   |      | 2.4.2  | Attaque sur l'incrémentation du compteur de ronde              | 45 |

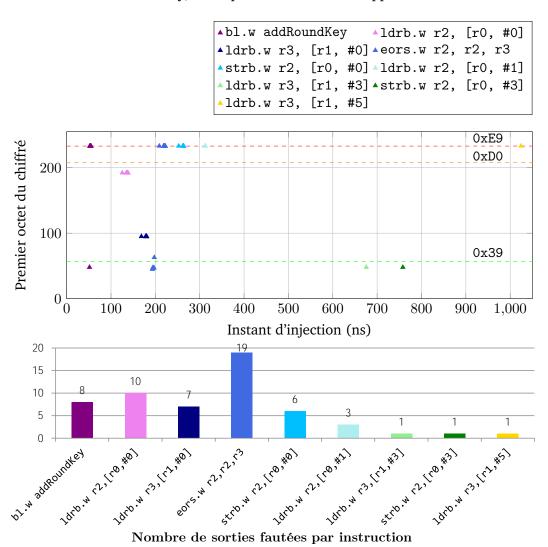

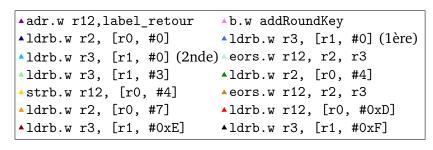

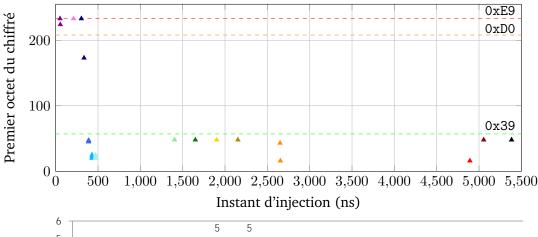

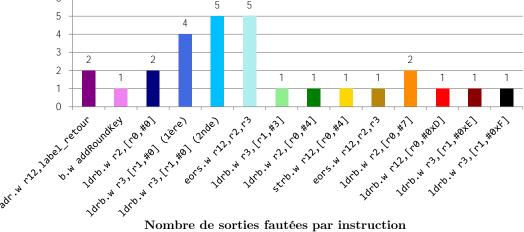

|   |      | 2.4.3  | Attaque sur la fonction d'addition de clé de ronde             | 48 |

|   | 2.5  | Concl  | usion                                                          | 51 |

| _ |      |        |                                                                |    |

| 3 |      |        | d'un modèle de fautes au niveau assembleur                     | 53 |

|   | 3.1  |        | uction                                                         | 53 |

|   | 3.2  |        | expérimentale des paramètres d'injection de fautes             | 54 |

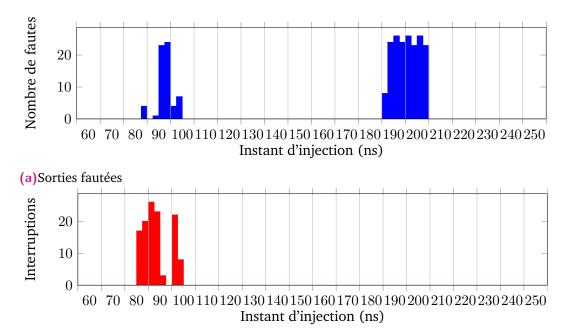

|   |      | 3.2.1  | Répétabilité des fautes injectées                              | 55 |

|   |      | 3.2.2  | Instant d'injection                                            | 55 |

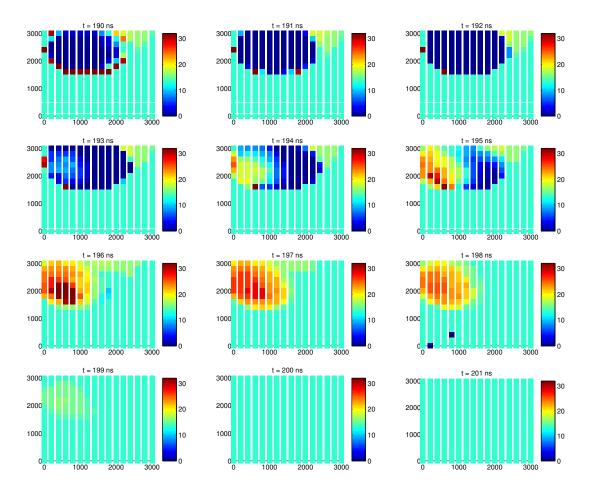

|   |      | 3.2.3  | Position de l'antenne d'injection                              | 56 |

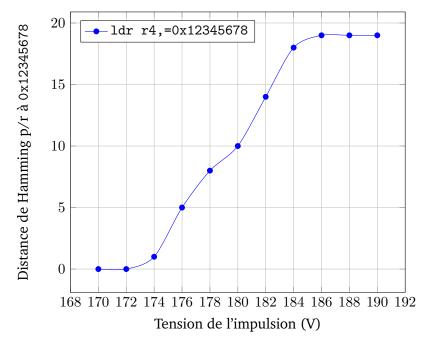

|   |      | 3.2.4  | Tension d'injection                                            | 57 |

|   | 3.3  |        | ptions de données et d'instructions                            | 58 |

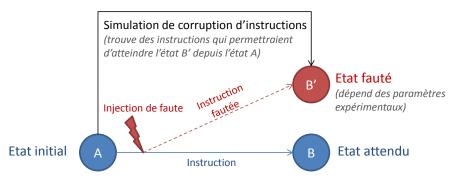

|   |      | 3.3.1  | Simulation de corruption d'instructions                        | 59 |

|   |      |        | Résultats expérimentaux                                        | 61 |

|   |      |        | Besoin d'une analyse à un niveau RTL (Register-Transfer Level) |    |

|   | 3.4  |        | e de fautes au niveau RTL                                      |    |

|   |      | 3.4.1  | Chargement d'instructions                                      | 64 |

|   |      | 3.4.2  | Chargement de données                                          | 65 |

|   | 0 -  |        | Validation expérimentale de ce modèle RTL                      | 65 |

|   | 3.5  |        | e de fautes au niveau assembleur                               | 68 |

|   |      | 3.5.1  | Validité du modèle de saut d'instruction                       | 68 |

|   | 0.6  | 3.5.2  | Hypothèses pour expliquer les effets de sauts d'instructions   | 71 |

|   | 3.6  | Concl  | usion et perspectives                                          | 74 |

| 4 | Défi | nition | et vérification d'une contre-mesure logicielle                 | 77 |

| • | 4.1  |        | uction                                                         | 77 |

|   |      |        | ntation du schéma de contre-mesure                             | 78 |

|   | 1.4  |        | Classes d'instructions                                         | 70 |

|    |       | 4.2.2 Séquences de remplacement par classe d'instructions 7              |

|----|-------|--------------------------------------------------------------------------|

|    |       | 4.2.3 Bilan sur les classes d'instructions définies                      |

|    | 4.3   | Vérification formelle du schéma de contre-mesure                         |

|    |       | 4.3.1 Préambule sur la vérification formelle                             |

|    |       | 4.3.2 Modélisation et spécification à prouver 9                          |

|    |       | 4.3.3 Vérification formelle de séquences de remplacement 9               |

|    | 4.4   | Application automatique de la contre-mesure                              |

|    |       | 4.4.1 Algorithme d'application automatique                               |

|    |       | 4.4.2 Résultats en termes de surcoût                                     |

|    | 4.5   | Conclusion et perspectives                                               |

| 5  |       | uation expérimentale de la contre-mesure proposée 10                     |

|    | 5.1   | Introduction                                                             |

|    | 5.2   | Évaluation expérimentale face aux injections de faute                    |

|    |       | 5.2.1 Contre-mesure de détection de fautes                               |

|    |       | 5.2.2 Définition d'une métrique de robustesse                            |

|    |       | 5.2.3 Paramètres expérimentaux utilisés pour l'évaluation 11             |

|    |       | 5.2.4 Évaluation expérimentale de la robustesse sur une instruction 11   |

|    |       | 5.2.5 Évaluation expérimentale sur une implémentation de FreeRTOS11      |

|    |       | 5.2.6 Bilan sur l'évaluation des contre-mesures                          |

|    | 5.3   | Application combinée des deux contre-mesures                             |

|    |       | 5.3.1 Présentation de l'implémentation à renforcer                       |

|    |       | 5.3.2 Évaluation préliminaire de l'implémentation non renforcée 12       |

|    |       | 5.3.3 Application de la contre-mesure de tolérance au saut d'une         |

|    |       | instruction                                                              |

|    |       | 5.3.4 Renforcement à l'aide de la contre-mesure de détection de fautes12 |

|    |       | 5.3.5 Bilan sur l'application combinée des deux contre-mesures 12        |

|    | 5.4   | Étude de vulnérabilité face aux attaques par observation                 |

|    |       | 5.4.1 Paramètres utilisés                                                |

|    |       | 5.4.2 Résultats expérimentaux                                            |

|    |       | 5.4.3 Bilan                                                              |

|    | 5.5   | Conclusion et perspectives                                               |

| 6  | Con   | clusion et perspectives 13                                               |

|    | 6.1   | Conclusion                                                               |

|    | 6.2   | Perspectives                                                             |

| A  | Mor   | ntage expérimental pour processeur ATmega128 13                          |

| Ré | féren | nces bibliographiques 14                                                 |

| Bi | bliog | raphie personnelle 15                                                    |

| Ta | ble d | les figures 15                                                           |

|    |       |                                                                          |

| Liste | des tableaux  | 157 |

|-------|---------------|-----|

| Liste | des acronymes | 159 |

# Introduction générale

Cette thèse s'intéresse à la sécurité des processeurs embarqués et s'inscrit dans le cadre de la protection de ceux-ci face aux attaques physiques.

La sécurité des systèmes embarqués représente un enjeu majeur voire critique pour un grand nombre de secteurs de l'industrie ou d'organisations étatiques. Ce sous-domaine du vaste ensemble qu'est la sécurité des systèmes d'informations s'intéresse au cas particulier de la protection des systèmes embarqués face aux attaques dont ils peuvent faire l'objet. De par leur statut d'*embarqués*, les systèmes à protéger peuvent se retrouver entre les mains d'éventuels attaquants, qui chercheront à porter atteinte à la confidentialité, à l'intégrité ou à l'authenticité de données protégées. De tels systèmes peuvent alors être l'objet d'attaques dites *physiques* qui visent à exploiter des faiblesses dans leur implémentation.

Le principal marché concerné par les problématiques liées à la sécurité des systèmes embarqués est pour l'instant celui de la carte à puce, avec ses nombreuses déclinaisons comme les cartes de paiement, les cartes SIM ou la télévision à péage (Pay-TV). De par l'utilisation de la carte à puce dans des domaines toujours plus nombreux, d'après (Eurosmart, 2012) les ventes de carte à puce devraient atteindre 7 milliards d'unités en 2013, soit une croissance de 8% par rapport à leur niveau de 2012, avec une croissance de 25% en ce qui concerne les cartes à puce munies d'une technologie sans contact.

Toutefois, la carte à puce n'est pas le seul secteur pour lequel une vulnérabilité matérielle peut s'avérer critique : l'utilisation d'attaques physiques a montré son efficacité dans le débridage (plus connu sous le nom anglais de *jailbreak*) de produits grand public comme l'iPhone d'Apple <sup>1</sup> ou la console XBOX 360 de Microsoft <sup>2</sup>, pouvant ainsi entraîner des préjudices financiers importants aux industriels dont les produits présentent des vulnérabilités exploitables.

À ces besoins en systèmes sécurisés sont venus s'ajouter d'autres utilisations des cartes à puce ces dernières années, avec la généralisation de l'ajout de composants électroniques sécurisés aux documents d'identité. En France, cette numérisation des pièces justificatives d'identité a d'abord commencé avec l'utilisation de la carte à

<sup>1.</sup> Full hardware unlock, 2007

<sup>2.</sup> DeBusschere et McCambridge, 2012.

puce comme document pour l'assurance maladie (Carte Vitale, 1998). Plus tard, les passeports (2005) et permis de conduire (2013) ont également été numérisés et utilisent des circuits sécurisés proches de ceux de la carte à puce. Enfin, les cartes nationales d'identité devraient également être concernées par cette numérisation dans les prochaines années.

L'ajout de modules de communication basés sur des technologies sans contact de radio-identification (plus connues sous l'acronyme RFID, Radio Frequency IDentification) a également entraîné l'utilisation de circuits sécurisés pour de nouveaux usages comme les titres de transport ou autres badges d'accès. L'apparition de nouvelles vulnérabilités exploitables face à ces circuits a donc logiquement suivi, avec par exemple le cassage des cartes MIFARE Classic dès 2008 (vendues à plus d'un milliard d'exemplaires aujourd'hui et encore largement utilisées pour du contrôle d'accès).

Parmi les attaques physiques que peut subir un circuit, les attaques par injection de fautes visent à modifier son comportement en injectant une faute lors d'un calcul. Ces attaques par injection de fautes peuvent être utilisées sur des implémentations cryptographiques mais également sur d'autres parties de circuits de sécurité, par exemple pour contourner des tests de code PIN ou empêcher l'exécution de fonctions essentielles. La définition de contre-mesures face à ces attaques physiques est difficile car elle requiert une bonne estimation des moyens d'un éventuel attaquant. Dans le cas particulier des attaques par injection de faute, l'effet lui-même de certains moyens couramment utilisés pour injecter des fautes reste assez mal connu. Il est donc extrêmement difficile d'avoir de bons modèles qui représentent l'ensemble des fautes qui peuvent être produites par un attaquant.

Cette thèse se place dans le cas de programmes embarqués et vise à améliorer leur résistance face à des attaques visant les processeurs qui les exécutent. Pour cela, une bonne connaissance du modèle de fautes réalisables par un éventuel attaquant est indispensable. Une présentation du contexte d'étude ainsi qu'un état de l'art des différentes méthodes d'attaque de circuits de sécurité et des contre-mesures existantes sont présentés dans le chapitre 1. Nous y précisons également les objectifs de la thèse. Le chapitre 2 présente ensuite le montage expérimental d'attaque utilisé dans cette thèse, ainsi que plusieurs résultats préliminaires d'utilisation de ce dispositif. Le chapitre 3 présente ensuite une étude détaillée des effets du dispositif expérimental utilisé sur le processeur embarqué choisi pour cette thèse. Le chapitre 4 propose ensuite une contre-mesure au niveau assembleur basée sur le modèle défini dans le chapitre précédent. Enfin, le chapitre 5 propose une première évaluation expérimentale de la contre-mesure proposée sur plusieurs exemples de codes embarqués.

Une partie des travaux présentés dans cette thèse apparaissent dans les publications suivantes : (Dehbaoui, Mirbaha et al., 2013), (Moro, Dehbaoui et al., 2013),

(Moro, Heydemann, Encrenaz et al., 2014), (Moro, Heydemann, Dehbaoui et al., 2014).

Contexte et motivations

1

| · · | om   | m | 21 | rΔ |

|-----|------|---|----|----|

| יט  | UII. |   | aı | ı  |

|     |      |   |    |    |

| 1.1 | Introdu | uction                                                     | 1  |

|-----|---------|------------------------------------------------------------|----|

| 1.2 | Princip | oes généraux des attaques physiques                        | 2  |

|     | 1.2.1   | Cryptographie embarquée                                    | 2  |

|     | 1.2.2   | Canaux auxiliaires et grandeurs observables                | 3  |

|     | 1.2.3   | Canaux auxiliaires utilisés pour la réalisation d'attaques | 3  |

| 1.3 | Attaqu  | es par observation et contre-mesures                       | 3  |

|     | 1.3.1   | Données observables par un attaquant                       | 4  |

|     | 1.3.2   | Modèles de consommation                                    | 8  |

|     | 1.3.3   | Exploitation des données obtenues                          | 10 |

|     | 1.3.4   | Rétro-ingéniérie                                           | 14 |

|     | 1.3.5   | Contre-mesures                                             | 15 |

| 1.4 | Attaqu  | es par injection de faute et contre-mesures                | 17 |

|     | 1.4.1   | Moyens d'injection de faute                                | 18 |

|     | 1.4.2   | Modèles de fautes                                          | 21 |

|     | 1.4.3   | Exploitation des données obtenues                          | 23 |

|     | 1.4.4   | Contre-mesures                                             | 24 |

| 1.5 | Object  | ifs de la thèse et approche choisie                        | 26 |

|     | 1.5.1   | Objectifs                                                  | 26 |

|     | 1.5.2   | Approche choisie                                           | 27 |

| 1.6 | Conclu  | sion                                                       | 27 |

# 1.1 Introduction

Cette thèse étudie le cas des attaques physiques, pour lesquelles un attaquant dispose d'un accès au circuit, celui-ci devant continuer à assurer ses propriétés d'intégrité, de confidentialité et d'authenticité en cas d'attaque. Ce chapitre commence tout d'abord par présenter une classification des types d'attaques et une brève description des techniques expérimentales existantes pour l'attaque de circuits en 1.2. Un état de l'art sur les attaques par observation et leurs contre-mesures est présenté en 1.3 suivi d'un état de l'art sur les attaques par injection de faute et leurs protections en 1.4. Enfin, le chapitre s'achève sur une présentation des objectifs de la thèse et de l'approche choisie pour les atteindre en 1.5.

# 1.2 Principes généraux des attaques physiques

Tous les algorithmes cryptographiques reposent sur des propriétés mathématiques qui ramènent la cryptanalyse à un problème reconnu comme mathématiquement difficile. Ce type de construction garantit ainsi la sécurité théorique des données chiffrées. Toutefois, la résistance théorique d'un algorithme ne garantit pas l'absence de failles concernant le circuit sur lequel il est implémenté. Dans cette thèse, on utilisera pour désigner les attaques qui exploitent ce type de vulnérabilités les expressions d'attaques par canaux auxiliaires ou d'attaques physiques. Le but de ces attaques physiques est généralement d'obtenir une donnée secrète comme une clé de chiffrement, ou bien d'obtenir des informations sur un circuit dans un but de rétro-ingéniérie, ou encore de contourner une protection comme un contrôle d'accès. Certaines attaques nécessitent également la réalisation préalable d'une étape de préparation du composant. Celle-ci consiste généralement en une ouverture du boîtier à l'aide d'acide. Selon le type d'attaque qui sera réalisé ensuite, la préparation peut également impliquer la pose de micro-sondes ou encore l'ouverture du boîtier en face arrière.

Cette section présente plusieurs principes généraux liés aux attaques physiques et commence par une présentation du cas de la cryptographie embarquée en 1.2.1. Ensuite, les canaux auxiliaires pouvant être utilisés pour des attaques sont présentés en 1.2.3. Enfin, les principes généraux utilisés pour les différentes attaques physiques existantes sont présentés en 1.2.2.

# 1.2.1 Cryptographie embarquée

La cryptologie se définit étymologiquement comme la science du secret. Elle regroupe deux disciplines liées : la cryptographie, étudiant l'écriture de messages secrets, et la cryptanalyse, visant au déchiffrement de messages secrets sans posséder la clé de chiffrement. La cryptographie est utilisée depuis l'antiquité, bien qu'elle soit restée principalement dans le domaine militaire jusqu'au milieu du vingtième siècle (STERN, 1998). A titre d'exemple, en France la cryptographie a été considérée comme une arme jusqu'à très récemment : il a fallu attendre 1999 pour que son usage soit autorisé aux particuliers. La deuxième moitié du vingtième siècle a vu l'émergence de nouveaux principes cryptographiques sur lesquels reposent les algorithmes modernes. Parmi ceux-ci, on peut notamment citer la sécurité théorique absolue (SHANNON, 1949), les protocoles d'échanges de clés (DIFFIE et HELLMAN, 1976) ou la cryptographie à clé publique (RIVEST et al., 1978).

La cryptographie moderne utilise plusieurs types de briques de base qui sont utilisées dans des cryptosystèmes plus complexes. Parmi ces briques de base, on peut mentionner les fonctions de hachage, les générateurs de nombres aléatoires, les algorithmes de chiffrements dits à *clé secrète* (également appelés algorithmes *symétriques*) et ceux dits à *clé publique* (également appelés algorithmes *asymétriques*). Certains

algorithmes ont acquis à la suite de concours internationaux le statut de standard (DES, AES, DSA, SHA-3), mais beaucoup d'autres algorithmes non-standardisés ont été publiés et sont couramment utilisés (RC4, RSA, MD5, SHA-1, ...). Néanmoins, un grand nombre d'algorithmes propriétaires dont la sécurité repose en partie sur la non-connaissance de l'algorithme par un attaquant sont encore largement utilisés.

### 1.2.2 Canaux auxiliaires et grandeurs observables

Les attaques physiques exploitent les failles dans le circuit sur lequel est implémenté un algorithme. Pour cela, elles se basent sur la mesure par un attaquant d'une grandeur relative aux données manipulées par le circuit. Dans la suite de cette thèse, on utilisera pour désigner cette grandeur les termes de *grandeur observable* ou de *grandeur mesurable*. La consommation de courant ou encore un résultat fauté après une injection de fautes peuvent par exemple être des grandeurs observables. De même, les données internes au circuit auquel l'attaquant n'a pas d'accès direct seront appelées *grandeurs internes*.

La notion de *canal auxiliaire* indique l'existence d'une relation entre une grandeur interne visée par un attaquant et une grandeur observable. Cette relation n'a pas forcément une expression mathématique et peut être dépendante du circuit visé ou des conditions expérimentales dans lesquelles l'attaque est réalisée. Elle peut néanmoins être approchée à l'aide de modèles. Ces modèles sont utilisés par un attaquant pour représenter le lien entre les grandeurs observables à sa disposition et les grandeurs internes visées par l'attaque. Ensuite, une technique d'exploitation du canal auxiliaire basée sur ce modèle est utilisée afin d'extraire les grandeurs internes visées. Les techniques d'exploitation des différents canaux auxiliaires seront présentées plus en détails dans les parties 1.3 et 1.4.

# 1.2.3 Canaux auxiliaires utilisés pour la réalisation d'attaques

D'une manière générale, il existe un aspect bidirectionnel pour les canaux utilisés pour réaliser des attaques physiques, et la plupart des canaux utilisés pour une attaque par injection de fautes peuvent également être utilisés d'une façon différente dans le cas d'une attaque par observation. Plus précisément, le tableau 1.1 présente plusieurs canaux physiques qui peuvent être utilisés pour les deux types d'attaque.

# 1.3 Attaques par observation et contre-mesures

La notion d'attaque par observation a été introduite dans la communauté scientifique à la fin des années 1990, d'abord en utilisant le temps d'exécution d'un programme (Kocher, 1996) comme canal auxiliaire, puis la consommation de courant (Kocher et al., 1999). Si certaines attaques par observation peuvent nécessiter une décapsulation préalable du circuit, la majorité de celles présentées dans la littérature ne

Table 1.1. : Exemples de canaux physiques pouvant être utilisés pour des attaques

|                   | Observation                  | Injection de fautes          |

|-------------------|------------------------------|------------------------------|

| Alimentation du   | Mesure du courant            | Perturbation de la tension   |

| circuit           | consommé                     | d'alimentation               |

| Temps             | Mesure du temps d'exécution  | Perturbation du signal       |

|                   |                              | d'horloge et violation des   |

|                   |                              | contraintes temporelles      |

| Rayonnement       | Analyse des émissions élec-  | Injection électromagnétique  |

| électromagnétique | tromagnétiques               |                              |

| Lumière           | Analyse des émissions de     | Lumière blanche focalisée ou |

|                   | photons                      | laser                        |

| Température       | Analyse de la température du | Chauffage du circuit         |

|                   | circuit                      |                              |

| Ondes acous-      | Analyse du bruit émis par le | (Pas encore de technique     |

| tiques            | circuit                      | d'exploitation proposée)     |

requiert aucune modification, diminuant donc le coût de ces attaques et les rendant donc possibles pour un plus grand nombre d'attaquants potentiels. Cette section commence par lister les grandeurs observables par un attaquant pour réaliser des attaques par observation et expliciter le lien entre celles-ci et certaines grandeurs internes du circuit en 1.3.1. La réalisation d'une attaque par observation peut nécessiter le choix d'un modèle de consommation. Les principaux modèles de consommation utilisés dans la littérature scientifique sont présentés en 1.3.2. Ensuite, les techniques connues d'exploitation de ces données mesurées, pour obtenir une grandeur secrète comme une clé de chiffrement sont présentées en 1.3.3. Ces données mesurées peuvent également être utilisées dans un but de rétro-ingéniérie, ce cas est présenté en 1.3.4. Enfin, les différentes approches à la base des contre-mesures face aux attaques par observation sont présentées en 1.3.5.

# 1.3.1 Données observables par un attaquant

Les paragraphes qui suivent présentent les différentes grandeurs observables, explicitent leurs liens avec certaines grandeurs internes du circuit et présentent les différents moyens d'observation de ces grandeurs.

#### 1.3.1.1. Sondage d'une donnée

La mesure directe par l'attaquant d'une donnée sur un des fils du circuit est appelée *sondage*, mais l'expression *micro-probing* est couramment utilisée. Dans ce type de procédé expérimental, l'attaquant vient placer une aiguille métallique sur un ou plusieurs des fils du circuit attaqué (généralement sur les bus) afin de pouvoir directement obtenir les valeurs logiques qui y transitent (ANDERSON et M. KUHN, 1996; KÖMMERLING et M. G. KUHN, 1999).

#### 1.3.1.2. Consommation de courant

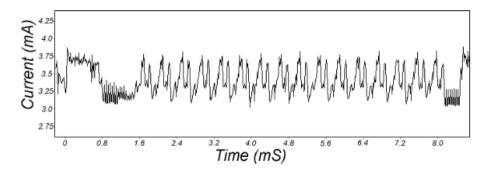

La mesure de la consommation de courant peut se faire en insérant une résistance de *shunt* (dont la valeur est connue) en série avec le composant entre celui-ci et la masse. La tension entre les bornes de cette résistance, qui peut être mesurée par un oscilloscope, est ainsi directement proportionnelle à l'intensité du courant consommé par celui-ci.

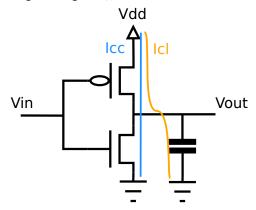

Une grande majorité des circuits intégrés actuels sont fabriqués à l'aide de la technologie Complementary Metal-Oxyde Semiconductor (CMOS). En technologie CMOS, la porte logique élémentaire NOT est réalisée à l'aide de deux transistors, un transistor NMOS et un transistor PMOS. En régime statique, cette porte logique a une consommation de courant  $I_{stat}$ . Le fait de positionner un 1 logique en entrée d'une telle porte met le transistor PMOS à l'état bloqué et le NMOS à l'état passant, reliant donc la sortie à l'état logique bas correspondant à la valeur 0. Inversement, dans le cas d'un 0 logique en entrée, l'état logique haut correspondant à un 1 logique se retrouve relié à la sortie. Toutefois, la transition entre un état logique et son complémentaire peut entraîner un léger pic sur la consommation de courant, comme expliqué dans (Guilley, Hoogvorst et al., 2004). Ce pic peut être la conséquence de deux courants :

- Un courant de court-circuit  $I_{cc}$

- Un courant de charge de ligne  $I_{cl}$

Figure 1.1. : Courants de charge de ligne et de court-circuit sur un inverseur CMOS

Ces deux courants à l'origine de pics sur la consommation de courant sont présentés sur la figure 1.1.

Au cours d'une transition de la sortie d'une porte logique, il existe un très bref instant pendant lequel les deux transistors laissent passer du courant, entraînant donc un léger court-circuit dû au passage d'un courant entre  $V_{dd}$  et la masse. Ce courant est appelé  $I_{cc}$ . Il apparaît indifféremment pour les deux types de transitions possibles.

La connexion entre la sortie de la porte NOT et une éventuelle porte suivante, ainsi que la proximité des lignes de connexion entraîne l'apparition de phénomènes capacitifs généralement modélisés par un condensateur parasite en sortie de l'inverseur.

Lors d'une transition entre un 0 et un 1 logique sur la sortie  $V_{out}$ , ce condensateur se retrouve connecté au  $V_{dd}$  et se charge, entraînant une légère surconsommation de courant.

Ainsi, au niveau d'une porte CMOS élémentaire, un attaquant capable de mesurer la consommation de courant globale de la porte est également capable :

- de distinguer une transition d'une absence de changement sur la sortie

- de distinguer une transition de 0 vers 1 d'une transition de 1 vers 0

Un circuit intégré étant constitué d'un ensemble de portes logiques, la consommation instantanée de courant du circuit est la somme des consommations de courants de chacune de ses portes logiques.

#### 1.3.1.3. Rayonnements électromagnétiques

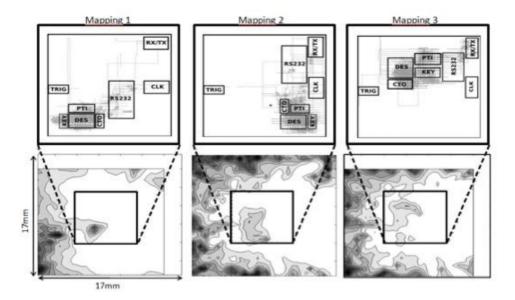

Les rayonnements électromagnétiques émis par un circuit peuvent être mesurés en champ proche. (Gandolfi et al., 2001) et (Quisquater et Samyde, 2001) ont été les premiers articles à obtenir des résultats expérimentaux qui utilisent ce type de canal auxiliaire. La mesure des rayonnements électromagnétiques permet d'obtenir des mesures physiques plus localisées par rapport à la mesure de courant, mais cet effet localisé de l'analyse ajoute une contrainte liée au positionnement de la sonde électromagnétique. Pour définir quelles parties du circuit émettent des rayonnements électromagnétiques pouvant être utilisés pour une attaque, l'attaquant doit réaliser des cartographies spatiales en faisant varier la position de la sonde (Dehbaoui, Ordas et al., 2010), comme illustré sur la figure 1.2. Cette figure représente une cartographie des rayonnements électromagnétiques pour différents circuits intégrés. Elle montre également que les rayonnements mesurés sont liés à la position des blocs fonctionnels du circuit visé.

L'émission de rayonnement électromagnétique est une conséquence de plusieurs phénomènes, notamment la commutation des portes logiques. Celle-ci suit la loi de Lenz-Faraday. La rapide variation du courant s'accompagne d'une variation du champ magnétique (qui entraîne elle-même une variation du champ électrique) mesurable par l'attaquant en champ proche. Pour réaliser ces mesures, la littérature scientifique propose l'utilisation de sondes électromagnétiques qui peuvent être des boucles (PEETERS et al., 2007) ou des solénoïdes (MOUNIER et al., 2012).

#### 1.3.1.4. Temps d'exécution

Le concept d'attaque temporelle a été introduit par (KOCHER, 1996). Il consiste à mesurer le temps d'exécution de l'algorithme voire, selon les implémentations et le degré de connaissance de l'attaquant, le temps d'exécution de certaines sous-fonctions. Par exemple, lors d'un branchement conditionnel, deux branches différentes de code

**Figure 1.2.** : Exemple de cartographie des rayonnements électromagnétiques pour plusieurs circuits intégrés (DEHBAOUI, ORDAS et al., 2010)

peuvent être appelées : une branche de code qui correspond au cas où la condition est vérifiée et une autre branche de code qui correspond au cas où la condition n'est pas vérifiée. Ces deux branches de code peuvent néanmoins présenter des différences de temps d'exécution. Un tel cas est illustré dans l'algorithme 1, où deux additions sont réalisées si la condition n=0 est vérifiée et une seule addition sinon. Dans un tel cas de figure et pour un attaquant qui connaîtrait l'algorithme visé, la mesure du temps d'exécution de la fonction permet de savoir quelle branche de code a été exécutée et donc de connaître la valeur de la condition n=0. Le temps d'exécution d'un algorithme peut également être lié à l'utilisation de mémoires cache par un processeur qui en est équipé. Ces mémoires cache peuvent introduire des différences de temps d'accès qui dépendent des données lues depuis la mémoire (BERNSTEIN, 2005 ; BERTONI et al., 2005).

```

Algorithme 1 : Exemple d'algorithme qui présente un déséquilibre du graphe de flot de contrôle

```

```

Data : x, y, z, n

1 if n == 0 then

2 | x = x + 1

3 | y = y + 1

4 else

5 | z = z + 1

```

La mesure du temps d'exécution peut être réalisée à l'aide d'un chronomètre déclenché automatiquement lors d'une requête au circuit et arrêté lors de la réponse de celui-ci. Elle peut également être réalisée indirectement en observant les émissions du circuit sur un autre canal auxiliaire. Par exemple, l'observation de la consommation de courant peut permettre de repérer des motifs correspondant à certaines étapes importantes de l'algorithme. Un exemple d'utilisation de la consommation de courant pour repérer l'intervalle d'exécution d'un algorithme cryptographique est présenté en 1.3.4.1.

#### 1.3.1.5. Émissions de photons

Très récemment, des travaux ont montré qu'il était possible d'utiliser les émissions de photons du circuit comme canal auxiliaire (SCHLÖSSER et al., 2012). Les auteurs de cette méthode proposent un modèle dans lequel le nombre de photons émis au niveau d'un transistor en technologie CMOS dépend de la tension appliquée à la grille du transistor. L'effet est davantage marqué sur les transistors NMOS. Plus précisément, un mouvement des porteurs de charge entre le drain et la source, qui intervient lorsque le transistor fonctionne en mode passant ou saturé, est accompagné d'une émission de photons. Ainsi, la quantité de photons émise dépend des données en entrée des portes logiques CMOS. Les auteurs mesurent les photons émis en face arrière du circuit à l'aide d'un capteur de type Charge-Coupled Device (CCD) et d'une photodiode.

#### 1.3.1.6. Température

L'utilisation de la température comme grandeur mesurable a également été proposée à plusieurs reprises dans la littérature scientifique (BROUCHIER et al., 2009). Néanmoins, la première caractérisation de ce canal auxiliaire a été proposée récemment dans (SCHMIDT et HUTTER, 2013). Dans cet article, les auteurs utilisent une mesure de température sur des microcontrôleurs AVR et PIC et montrent qu'il existe une dépendance linéaire entre l'activité du circuit et les rayonnements thermiques émis par celui-ci.

#### 1.3.1.7. Ondes acoustiques

Très récemment, des attaques acoustiques visant l'implémentation Rivest Shamir Adleman (RSA) du programme GnuPG ont été proposées dans (GENKIN et al., 2013). En raison de l'augmentation de la température à l'intérieur du circuit lors de calculs, une contrainte mécanique est appliquée à certains éléments du circuit et celle-ci entraîne l'émission d'ondes acoustiques qui peuvent être mesurées.

#### 1.3.2 Modèles de consommation

La réalisation d'attaques par observation peut nécessiter le choix d'un modèle de consommation par l'attaquant. Ce modèle de consommation a pour but d'estimer

à l'aide d'une relation mathématique le lien entre une grandeur observable et une grandeur interne. La représentativité de chacun de ces modèles dépend du type de canal auxiliaire observé et de l'architecture du circuit ciblé. Le terme de *consommation* renvoie aux premières attaques pour lequel ces modèles ont été utilisés, qui se basaient sur une observation de la consommation de courant d'un circuit. Toutefois, ces modèles dits de *consommation* peuvent être utilisés pour d'autres grandeurs observables comme par exemple les rayonnements électromagnétiques (PEETERS et al., 2007), la température (SCHMIDT et HUTTER, 2013) voire le temps de calcul (LI et al., 2010). Dans la littérature scientifique, trois modèles de consommation sont couramment utilisés (PEETERS et al., 2007). Ces trois modèles sont présentés dans les paragraphes qui suivent.

#### 1.3.2.1. Poids de Hamming

Le poids de Hamming d'un octet correspond au nombre de bits à 1 de l'octet.

$$hw(X) = \sum_{i=1}^{n} (X_i)$$

(1.1)

Ce modèle suppose que la consommation de courant associée à la manipulation d'un octet par le circuit est proportionnelle au nombre de bits à 1 de l'octet manipulé. Il suppose donc que la manipulation d'un 1 logique induit une consommation supérieure à la manipulation d'un 0 logique. Le modèle néglige également la consommation de courant associée aux transitions. Le poids de Hamming est généralement un modèle pertinent pour les circuits qui possèdent un bus préchargé.

#### 1.3.2.2. Distance de Hamming

La distance de Hamming entre deux octets correspond au nombre de bits distincts entre ces deux octets.

$$hd(X,Y) = \sum_{i=1}^{n} (X_i \oplus Y_i)$$

(1.2)

Ce modèle suppose que le courant associé à l'inversion de la valeur d'un bit est supérieur à celui associé au maintien d'un bit à sa valeur précédente. Pour ce modèle, la consommation de courant liée à la manipulation d'un 1 logique ou un 0 logique est donc négligée au profit du nombre de transitions. A titre d'exemple, la distance de Hamming est souvent utilisée dans le cas d'une analyse de la consommation ou des rayonnements électromagnétiques émis par le composant.

#### 1.3.2.3. Valeur de l'octet

Dans (GIERLICHS et al., 2008), les auteurs proposent également un autre modèle pour lequel la consommation du circuit pour effectuer un traitement sur un octet est modélisée directement par la valeur numérique de l'octet.

#### 1.3.2.4. Bilan

Ces modèles de consommation permettent à l'attaquant de définir, pour un texte clair et une clé donnés, une estimation de la consommation ou de l'émission de rayonnements électromagnétiques. Lors d'une attaque sur un circuit pour lequel l'attaquant ne possède pas d'informations détaillées sur l'implémentation, le choix d'un modèle pour réaliser une attaque par canaux auxiliaires peut se faire de façon très empirique. Il existe plusieurs modèles communément admis dans la littérature, et l'attaquant peut tout simplement essayer successivement avec chacun de ceux-ci jusqu'à trouver un modèle qui lui permettra de mener à bien son attaque.

### 1.3.3 Exploitation des données obtenues

Une fois la phase d'acquisition d'une grandeur observable réalisée, une étape d'exploitation des données obtenues permet de finaliser l'attaque. Les différentes techniques d'exploitation permettant de retrouver une grandeur secrète sont présentées dans les paragraphes qui suivent.

#### 1.3.3.1. Analyse simple

Les analyses simples permettent d'obtenir des informations sur une grandeur secrète d'un algorithme en cours d'exécution par une observation des émissions sur certains canaux auxiliaires. Dans le meilleur des cas, ces analyses simples peuvent permettre de réaliser une attaque à l'aide d'une seule acquisition d'une grandeur observable.

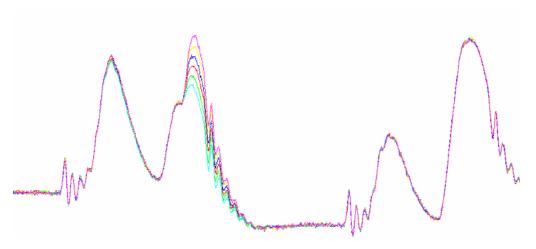

Consommation de courant L'analyse simple de la consommation, ou Simple Power Analysis (SPA), a été introduite par Kocher en 1999 (Kocher et al., 1999). Celle-ci vise à déterminer directement, à partir d'une observation de la consommation de courant lors d'une exécution normale de l'algorithme, des informations sur le calcul effectué ou les données manipulées. A titre d'illustration, la figure 1.3 présente six courbes de consommation correspondant à la manipulation d'une variable prenant six valeurs différentes. Les six courbes de consommation peuvent aisément être distinguées sur l'un des pics de consommation. Leur observation peut donc permettre d'obtenir des informations sur les données manipulées par le circuit.

Figure 1.3. : Consommations de courant lors de la manipulation d'une variable pour 6 valeurs différentes (CLAVIER, 2007a)

**Temps d'exécution** Les premiers cas pratiques d'utilisation du temps d'exécution pour réaliser une attaque ont été présentés dans (Kocher, 1996). Dans (Dhem et al., 1998), l'attaque vise une implémentation de l'algorithme RSA et a été réalisée sur la fonction d'exponentiation rapide (ou  $Square\ and\ Multiply$ ). Cette fonction d'exponentiation rapide est présentée dans l'algorithme 2. L'attaque se base sur le fait que dans le cas d'une implémentation logicielle de cet algorithme, la condition n est pair revient à considérer la valeur du bit de poids faible de n. Si le bit de poids faible de n vaut 0, l'algorithme effectue une exponentiation. En revanche, si le bit de poids faible de n vaut 1, l'algorithme effectue une exponentiation et une multiplication. L'algorithme s'exécute donc plus rapidement si le bit de poids faible vaut 0.

```

Algorithme 2: Algorithme d'exponentiation rapide

```

```

Data : x, n

Result : y = x^n

1 if n = 1 then

2 | return x

3 if n est pair then

| /* Une exponentiation */

4 | return exponentiation(x^2, n/2)

5 else

| /* Une exponentiation et une multiplication */

6 | return x \times exponentiation(x^2, n/2)

```

#### 1.3.3.2. Analyse différentielle

L'analyse différentielle de consommation, ou Differential Power Analysis (DPA) a été introduite par Kocher *et al.* (Kocher et al., 1999) puis appliquée à d'autres canaux

(QUISQUATER et SAMYDE, 2001 ; AGRAWAL et al., 2003 ; GIERLICHS et al., 2008). Une analyse différentielle peut être réalisée en 5 étapes, qui sont présentées dans les paragraphes qui suivent.

**1ère étape : Acquisition de courbes** La première étape consiste à réaliser un ensemble d'acquisitions sur le circuit ciblé en faisant varier le message à chiffrer sur un ensemble T. Pour chaque chiffrement, la courbe correspondant à la grandeur observée est enregistrée. L'attaquant obtient donc une matrice de mesures M constituée de |T| lignes, chaque ligne correspondant à une courbe d'acquisition de la grandeur observée lors d'un chiffrement. Le nombre de colonnes de M correspond au nombres d'instants échantillonnés lors de la mesure de la grandeur observée.

**2ème étape : Prédiction de valeurs intermédiaires** La deuxième étape consiste à choisir une valeur intermédiaire v du chiffrement qui dépend du texte clair  $^1$  et d'un nombre limité de bits de la clé. Le nombre limité de valeurs que peuvent prendre ces bits de la clé définit un ensemble K de clés partielles. La valeur v est alors calculée pour l'ensemble T des textes clairs utilisés lors de l'étape d'acquisition et l'ensemble K des clés partielles. Une matrice V dont les coefficients sont les valeurs intermédiaires v est alors constituée.

**3ème étape : Choix d'un modèle de consommation** Cette étape consiste à choisir un modèle de consommation noté mc, qui est généralement choisi parmi les modèles présentés en 1.3.2. Ce modèle de consommation est utilisé pour lier les valeurs prédites lors de la deuxième étape de l'attaque à une estimation de la grandeur observable utilisée pour l'attaque. L'attaquant obtient donc une matrice de prédictions P avec  $P_{i,j} = mc(V_{i,j})$ . Dans l'attaque DPA de Kocher et al., le modèle de consommation utilisé correspond simplement à la valeur du bit choisi lors de l'étape de prédiction des valeurs intermédiaires ; ce bit est appelé bit de sélection.

**4ème étape : Comparaison entre mesures et prédictions** La quatrième étape consiste à appliquer un opérateur statistique de similarité pour comparer les valeurs de la matrice de prédictions P à celles de la matrice de mesures M. Pour les courbes correspondant à une mauvaise hypothèse de clé partielle, les prédictions et les mesures ont un degré de similarité faible. Inversement, pour la courbe correspondant à la bonne hypothèse de clé partielle, les prédictions et les mesures ont une bonne similarité. L'attaquant obtient alors une matrice de résultats R où, pour chaque instant d'échantillonnage un scalaire mesurant la similarité est associé à chaque hypothèse de clé. L'attaque DPA de Kocher  $et\ al$ . utilise comme opérateur statistique une différence entre la moyenne des courbes pour lesquelles  $P_{i,j}=1$  et celles pour lesquelles  $P_{i,j}=0$  pour chaque hypothèse de clé partielle de l'ensemble K. Des variantes de l'analyse DPA ont ensuite été proposées. Elles mettent en œuvre d'autres

<sup>1.</sup> Le texte chiffré peut également être utilisé à la place du texte clair s'il est connu de l'attaquant, la valeur intermédiaire sera alors choisie dans les dernières étapes du chiffrement.

opérateurs et d'autres modèles. Parmi les opérateurs statistiques couramment utilisés, on trouve notamment la corrélation de Pearson (BRIER et al., 2004) ou l'information mutuelle (GIERLICHS et al., 2008).

**5ème étape : Détection de la valeur maximale de la matrice de résultats** La matrice R obtenue précédemment définit un ensemble de courbes de corrélation, avec une courbe de corrélation pour chaque hypothèse de clé. La figure 1.4 montre des exemples de courbes de corrélation pour trois hypothèses de clé (qui correspondent aux trois courbes du bas sur la figure). Sur la figure, la courbe associée à la première de ces hypothèses de clé montre un « pic de similarité » pour le résultat de l'opérateur statistique utilisé. L'attaquant peut en déduire que cette hypothèse de clé correspond à la clé partielle utilisée sur le circuit attaqué.

Figure 1.4.: Résultats d'analyse DPA pour trois hypothèses de clé (KOCHER et al., 1999)

#### 1.3.3.3. Analyse par template

Les attaques par *template*, introduites par (CHARI et al., 2003), exploitent également des données obtenues via des canaux auxiliaires. Dans ce type d'attaque, l'attaquant réalise préalablement un ensemble de mesures sur un composant identique au composant ciblé tout en faisant varier un nombre de bits restreint de la clé de chiffrement. A partir de cet ensemble de mesures, il construit pour chaque hypothèse de clé un dictionnaire, ou *template*. Celui-ci est constitué de deux éléments : la

moyenne des courbes de consommation associées à la clé, et une information sur le bruit des mesures (sous la forme d'une matrice de covariance). Il réalise ensuite des mesures sur le circuit attaqué et recherche dans les *templates* constitués les échantillons les plus proches.

### 1.3.4 Rétro-ingéniérie

Des attaques par observation peuvent également être réalisées dans un but de rétroingéniérie pour retrouver des informations sur un circuit. Les paragraphes qui suivent en présentent quelques exemples.

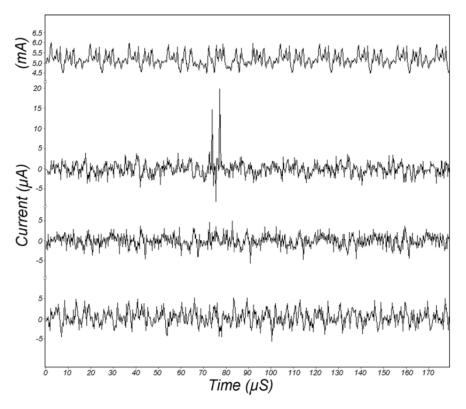

#### 1.3.4.1. Analyses simples

L'analyse SPA peut être utilisée pour permettre à un attaquant d'isoler une fenêtre temporelle pendant laquelle a lieu la partie du calcul visée. L'analyse SPA s'applique ainsi très bien au cas des algorithmes cryptographiques symétriques : ceux-ci ont des traces de consommation facilement reconnaissables de par leur structure qui consiste à répéter un certain nombre de fois une ronde de chiffrement. Un exemple de consommation de courant d'un circuit exécutant un chiffrement Data Encryption Standard (DES) à 16 rondes est présenté sur la figure 1.5. A partir de cette trace de consommation, il est possible d'en déduire la position des différentes rondes de chiffrement. Une application du principe de l'analyse SPA a également été proposée dans (Novak, 2003). L'auteur utilise des mesures effectuées lors de chiffrements pour retrouver les valeurs de tables de substitution d'un algorithme dont une partie de la sécurité repose sur sa non-connaissance. Cette attaque a ensuite été améliorée dans (Clavier, 2004), où l'auteur propose une construction sous forme de graphe permettant également de retrouver la clé de chiffrement en plus des valeurs des tables de substitution.

Figure 1.5. : Consommation de courant d'un circuit exécutant un chiffrement DES à 16 rondes (Kocher et al., 1999)

#### 1.3.4.2. Analyses par template

En utilisant le principe des attaques par *template*, un attaquant peut identifier une partie des instructions exécutées par un microcontrôleur. La figure 1.6 présente un exemple de construction de *template* sur des traces de courant pour deux suites d'instructions assembleur. Une telle approche a été proposée par (GOLDACK, 2008) puis (EISENBARTH et al., 2010). Dans ces deux articles, le programme exécuté par le microcontrôleur est décrit sous la forme d'un modèle de Markov caché, et les auteurs utilisent plusieurs algorithmes pour retrouver le flot d'exécution le plus probable à partir des *templates* constitués sur un modèle de référence du microcontrôleur ciblé. A partir de leurs mesures, ils sont ainsi capables de retrouver jusqu'à 70% des instructions réellement effectuées par le microcontrôleur.

**Figure 1.6. :** Exemple de traces de courant utilisées pour la rétro-ingéniérie d'un programme assembleur (EISENBARTH et al., 2010)

#### 1.3.5 Contre-mesures

Les contre-mesures face aux attaques par observation visent à réduire le rapport entre le signal transmis et le bruit. Pour cela, deux types d'approches peuvent être utilisées : celles consistant à réduire le signal transmis sur un canal auxiliaire (présentées en 1.3.5.1) et celles consistant à ajouter du bruit (présentées en 1.3.5.2).

#### 1.3.5.1. Réduction du signal

De nombreuses techniques permettent de réduire le signal transmis sur un canal auxiliaire. Les paragraphes qui suivent présentent les principales techniques utilisées dans la littérature scientifique.

**Équilibrage au niveau du graphe de flot de contrôle** Pour contrer les attaques par analyse du temps d'exécution, les contre-mesures visent à équilibrer le graphe de

flot de contrôle des portions sensibles de l'algorithme en cours d'exécution. Pour atteindre ce but, une approche consiste à élaborer un code source présentant un graphe de flot de contrôle équilibré et pour lequel la compilation n'apporte pas de modification à cet équilibre (MOLNAR et al., 2006). Une autre approche consiste à modifier directement le compilateur de façon à permettre au programmeur d'annoter les portions de code sensible et ainsi de signaler les portions de code pour lesquelles devra être généré un code machine présentant un graphe de flot de contrôle équilibré (COPPENS et al., 2009). Dans le cas des analyses du temps de consommation qui exploitent les optimisations apportées par les mémoires caches, une solution possible consiste à désactiver toute utilisation de mémoire cache.

**Équilibrage au niveau des données** Les codages 1 parmi n sont une approche possible pour équilibrer le poids de Hamming des données manipulées. Dans un codage 1 parmi n, un seul fil est actif pour représenter une donnée, le poids de Hamming est donc constant. Un codage 1 parmi 2 (également appelé double-rail) est couramment utilisé dans la littérature scientifique (TIRI et VERBAUWHEDE, 2004). Afin d'équilibrer également les distances de Hamming au niveau des transitions, une phase dite de précharge peut être ajoutée avant chaque cycle de calcul. Cette phase de précharge consiste à placer les deux fils correspondant à un signal à une valeur définie (0 ou 1). Ensuite, lors de la phase de calcul, une seule transition est alors réalisée sur un des fils pour chaque signal. Plusieurs exemples de logiques double-rail à précharge sont présentés dans (GUILLEY, SAUVAGE et al., 2008) ou (DANGER et al., 2009). Au niveau des programmes embarqués, il est possible d'utiliser une variante du principe des logiques double-rail. Une telle approche a été proposée récemment dans (RAUZY, GUILLEY et NAJM, 2014). Pour cela, les auteurs décomposent chaque opération sous la forme d'une suite d'opérations élémentaires bit à bit. Chacune de ces opérations élémentaires charge ensuite ses résultats depuis une table précalculée en mémoire au lieu de faire appel à l'unité arithmétique et logique du processeur.

#### 1.3.5.2. Ajout de bruit

Les paragraphes qui suivent présentent les principales techniques connues dans la littérature scientifique pour augmenter le bruit des signaux transmis via les canaux auxiliaires.

**Ajout d'instructions factices** L'ajout d'instructions factices permet de modifier le temps d'exécution ou la consommation de courant d'une portion de code embarqué. Une approche possible est de repérer les instructions les plus vulnérables aux attaques par consommation, puis de rajouter du bruit sous la forme d'instructions factices autour de ces instructions sensibles. Une telle approche est par exemple présentée dans (BAYRAK et al., 2011).

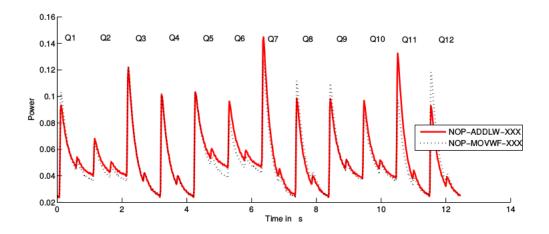

Code auto-modifiant et polymorphisme Des approches à base de code auto-modifiant peuvent également être utilisées pour ajouter du bruit sur un code embarqué. Un code auto-modifiant est un programme qui peut modifier à la volée des parties de son code. Pour cela, une approche possible est de définir un schéma à base de recompilation dynamique directement sur le processeur en utilisant des classes d'équivalence pour différentes instructions. Ce type de protection permet au processeur de compiler différentes séquences d'instructions pour réaliser une opération (AGOSTA et al., 2012). Une autre approche possible est d'éviter une recompilation réelle sur le processeur et lui faire choisir une version du code parmi celles dont il dispose en mémoire pour réaliser une opération bien définie. Cette approche a par exemple été appliquée à une implémentation de l'algorithme Advanced Encryption Standard (AES) dans (AMARILLI et al., 2011).

**Modification de la tension ou du signal d'horloge** Pour un circuit CMOS synchrone, la tension d'alimentation ou le signal d'horloge peuvent subir de petites variations sans que des fautes apparaissent dans les calculs. Une légère jigue sur la tension ou une légère désynchronisation du signal d'horloge peuvent par exemple être utilisées pour rendre plus difficile la réalisation pratique d'attaques par observation (GIRAUD et THIEBEAULD, 2004).

**Masquage** Le masquage consiste à appliquer un masque aléatoire aux données en entrée d'un algorithme. Le circuit applique alors une variante de l'algorithme en question à ces données masquées. Enfin, le masque est à nouveau appliqué au résultat de l'algorithme pour obtenir le résultat non-masqué. Cette contre-mesure rend caduques les prédictions faites par un attaquant lors d'une analyse DPA. Elle peut s'appliquer directement à tout algorithme linéaire mais doit nécessiter certaines modifications de fonctions dans le cas d'algorithmes non-linéaires. Cette technique de masquage a été utilisée pour renforcer de nombreuses implémentations cryptographiques (MESSERGES, 2001 ; JOYE et al., 2005 ; FUMAROLI et al., 2010).

# 1.4 Attaques par injection de faute et contre-mesures

Les attaques par injection de faute ont été introduites par Boneh *et al.* en 1997 (Boneh et al., 1997). Cette section commence par présenter les différents moyens d'injection de fautes connus en 1.4.1. Ensuite, la notion de *modèle de fautes*, qui fait le lien entre l'injection de fautes à l'aide de moyens physiques et la définition d'attaques et contre-mesures à un niveau d'abstraction supérieur, est présentée en 1.4.2. Les techniques d'exploitation des données obtenues à la suite d'une injection de fautes sont présentées en 1.4.3. Enfin, les différentes approches pour la définition de contre-mesures sont présentées en 1.4.4.

#### 1.4.1 Moyens d'injection de faute

Divers phénomènes physiques permettent d'insérer une faute lors d'un calcul. Les moyens d'injection de faute connus et référencés par la communauté scientifique sont le rayonnement lumineux, la température, la perturbation du signal d'horloge, la perturbation de la tension d'alimentation ou encore l'injection électromagnétique (BARENGHI, BREVEGLIERI, KOREN et NACCACHE, 2012). Ces différents moyens d'injection sont présentés plus en détail dans les paragraphes qui suivent.

#### 1.4.1.1. Rayonnement lumineux

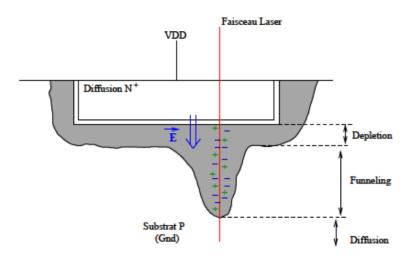

Un rayonnement lumineux émis par un laser ou une source lumineuse focalisée peut être utilisé pour injecter des fautes dans un circuit. Un tel dispositif d'injection de fautes nécessite une ouverture du boîtier, comme illustré sur la figure 1.7.

Figure 1.7. : Injection de fautes par laser sur un circuit intégré ouvert

L'énergie du rayonnement lumineux utilisé est absorbée par le silicium du circuit. Lorsque l'énergie transmise est supérieure au seuil permettant à des électrons de passer dans la bande de conduction du silicium, des paires électrons-trous sont alors créées le long du faisceau lumineux (ROSCIAN et al., 2013 ; J.-M. DUTERTRE, FOURNIER et al., 2011). Ce phénomène est illustré sur la figure 1.8. Ces paires électrons-trous peuvent aboutir à l'apparition d'un courant photoélectrique au niveau d'un transistor. Ce courant entraîne alors l'apparition d'un pic de tension qui peut se propager dans des blocs de logique combinatoire. Ce phénomène de propagation d'un pic de tension à travers la logique combinatoire est appelé Single Event Transient (SET). Le pic de tension induit peut entraîner l'apparition d'une faute s'il est échantillonné par un élément mémoire comme un registre.

Dans (S. P. Skorobogatov et Anderson, 2003), les auteurs décrivent une attaque basée sur l'utilisation de l'effet photoélectrique pour insérer des fautes dans un circuit : ils utilisent ainsi un flash d'appareil photo contre une cellule de mémoire Static Random Access Memory (SRAM). Plus récemment, dans (SCHMIDT et HUTTER,

Figure 1.8. : Apparition de paires électrons-trous lors d'un tir laser sur une jonction PN (CYRIL ROSCIAN, 2013)

2007), les auteurs ont utilisé une fibre optique afin de mieux focaliser la source de lumière blanche sur la cellule de SRAM visée. Dans (ROSCIAN et al., 2013), les auteurs ont utilisé une source laser pour injecter une faute dans une cellule SRAM. Par rapport à l'utilisation de lumière concentrée, le laser permet une bien plus grande précision lors d'une injection de faute (CANIVET et al., 2010). Des effets sur certains blocs de logique d'un microcontrôleur ont également été obtenus dans (TRICHINA et KORKIKYAN, 2010), ceux-ci ont permis de fauter l'exécution d'instructions assembleur sur le microcontrôleur ciblé.

#### 1.4.1.2. Température

Les circuits intégrés sont conçus pour fonctionner dans une certaine plage de température. Un attaquant peut faire chauffer certains éléments du circuit en dehors de leurs conditions normales de fonctionnement et ainsi créer des fautes à l'intérieur du circuit. Dans (S. Skorobogatov, 2009), l'auteur a utilisé une modification de la température du circuit afin d'injecter des fautes dans des mémoires EEPROM et Flash. Plus récemment, dans (Schmidt et Hutter, 2013), les auteurs ont attaqué une implémentation de l'algorithme RSA sur un microcontrôleur ATmega162 en faisant chauffer le circuit sur une plaque chauffante.

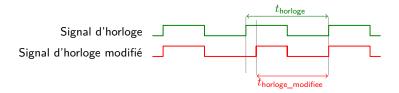

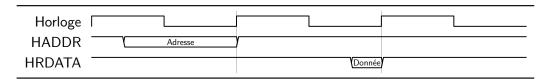

#### 1.4.1.3. Perturbation du signal d'horloge

Les circuits synchrones cadencés par un signal d'horloge ont une fréquence de fonctionnement maximale. Celle-ci est définie en considérant la durée maximale d'un transfert de données entre deux éléments de mémorisation. Si l'attaquant réussit à forcer une fréquence d'horloge supérieure à cette fréquence maximale (on parle alors d'overclocking), la période d'horloge devient alors plus courte que la durée de certains

transferts dans la logique combinatoire. Dans ce cas, des valeurs incorrectes sont échantillonnées par certains éléments de mémorisation. Ce procédé d'*overclocking* peut être appliqué de façon à induire des fautes sur un seul cycle d'horloge. On parle alors de perturbation transitoire du signal d'horloge (couramment appelée *clock glitch*) (AGOYAN et al., 2010). La figure 1.9 présente un exemple de signal d'horloge modifié pouvant être utilisé pour une telle attaque.

Figure 1.9. : Signal d'horloge modifié pouvant être utilisé pour une attaque

#### 1.4.1.4. Perturbation de la tension d'alimentation

Les modifications de la tension d'alimentation ont des effets sur la vitesse de cheminement de données dans la logique combinatoire entre des éléments de mémorisation (Zussa, J.-m. Dutertre et al., 2012). En modifiant la valeur de tension utilisée pour alimenter un circuit, un attaquant peut donc induire des fautes dans les calculs qui sont effectués. Afin d'injecter une faute à un instant précis, un attaquant peut réaliser une perturbation transitoire de la tension d'alimentation (couramment appelée *power glitch*) afin de temporairement modifier la vitesse de circulation des données entre deux éléments de mémorisation (CARPI et al., 2013).

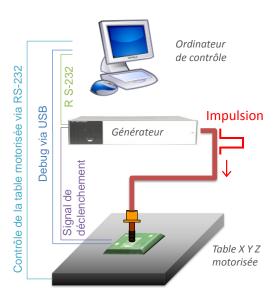

#### 1.4.1.5. Injection électromagnétique

Le couplage électromagnétique entre une antenne et certains éléments du circuit visé peut provoquer des courants sur certains fils du circuit. Plusieurs types d'antennes peuvent être utilisées pour cela. Dans (Schmidt et Hutter, 2007), les auteurs ont utilisé un solénoïde. Dans (Dehbaoui, J.-M. Dutertre, Robisson, Orsatelli et al., 2012), les auteurs ont ajouté un matériau ferromagnétique comme cœur du solénoïde. La figure 1.10 présente quelques antennes qu'il est possible d'utiliser pour réaliser une injection électromagnétique de fautes. Dans la littérature scientifique, l'injection électromagnétique a été utilisée principalement sous forme harmonique ou bien sous forme d'impulsions. La première, notamment présentée dans (Poucheret et al., 2011) ou (Markettos, 2011), a principalement été utilisée pour perturber des générateurs de nombres aléatoires et y introduire un biais statistique qui peut alors être utilisé par un attaquant. La seconde, introduite dans (Quisquater et Samyde, 2001) et présentée dans (Schmidt et Hutter, 2007), (Dehbaoui, J.-M. Dutertre, Robisson et Tria, 2012) et (Dehbaoui, J.-M. Dutertre, Robisson, Orsatelli et al., 2012) a été utilisée pour réaliser des injections de fautes sur des implémentations

matérielles et logicielles d'algorithmes cryptographiques. Par rapport à l'injection harmonique, l'injection de fautes par impulsion permet de viser un instant particulier de l'exécution de l'algorithme ciblé.

Figure 1.10. : Exemples de sondes d'injection électromagnétique (Dehbaoui, 2011)

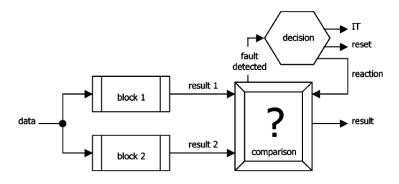

#### 1.4.2 Modèles de fautes