## Conception et développement d'un circuit multiprocesseurs en ASIC dédié à une caméra intelligente

Mohamed Amine Boussadi

#### ▶ To cite this version:

Mohamed Amine Boussadi. Conception et développement d'un circuit multiprocesseurs en ASIC dédié à une caméra intelligente. Autre [cond-mat.other]. Université Blaise Pascal - Clermont-Ferrand II, 2015. Français. <NNT: 2015CLF22552>. <tel-01155511>

HAL Id: tel-01155511

https://tel.archives-ouvertes.fr/tel-01155511

Submitted on 26 May 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : D. U : 2552

EDSPIC: 690

#### UNIVERSITE BLAISE PASCAL - CLERMONT II

École Doctorale Sciences Pour l'Ingénieur de Clermont-Ferrand

### Thèse

présentée par :

#### **Mohamed Amine Boussadi**

pour obtenir le grade de

## **DOCTEUR D'UNIVERSITÉ**

Spécialité: Vision pour la Robotique

Titre de la thèse :

## Conception et développement d'un circuit multiprocesseurs en ASIC dédié à une caméra intelligente

Soutenue publiquement le : 25 février 2015 devant le jury :

M. Dominique Houzet Rapporteur et Président

M. Gilles Sassatelli Rapporteur

M. François Berry Examinateur

M. Maxime Pelcat Examinateur

M. Jean-Pierre Dérutin Directeur de thèse

M. Alexis Landrault Co-encadrant

$\grave{A}$  mes parents

#### Remerciements

Je remercie Jean-Pierre Dérutin, professeur de l'université Blaise Pascal, d'avoir accepté de diriger mes travaux de recherche. Je le remercie pour ses conseils, son encadrement et pour la confiance qu'il m'a accordée durant ces trois années de thèse pour mener à bien ces travaux de recherche.

Je remercie Alexis Landrault, maître de conférence de l'université Blaise Pascal, pour son encadrement sans faille et ses nombreux conseils qui m'ont permis d'avancer et mener à bien ces travaux de recherche.

Je remercie Thierry Tixier, ingénieur de recherche à l'Institut Pascal, de m'avoir transmis son expérience et ses connaissances. Grâce à son implication et ses conseils avisés, il a largement contribué au bon aboutissement de ce projet.

Je tiens également à remercier l'ensemble des membres de mon jury d'avoir accepté de juger et d'évaluer ces travaux de thèse. Je remercie Gilles Sassatelli, directeur de recherche CNRS au LIRMM, et Dominique Houzet, professeur à Grenoble-INP, et président du jury pour l'attention qu'ils ont accordée à la lecture de ce manuscrit ainsi que pour leur participation au jury en tant que rapporteurs. Je remercie François Berry, maître de conférence HDR de l'université Blaise Pascal, et Maxime Pelcat, maître de conférences de Institut National des Sciences Appliquées de Rennes, d'avoir pris de leur temps et d'avoir participés au jury en tant qu'examinateurs.

Enfin, je tiens à remercier toutes mes connaissances de m'avoir accompagnés et aidés pendant mes années d'études.

#### Résumé

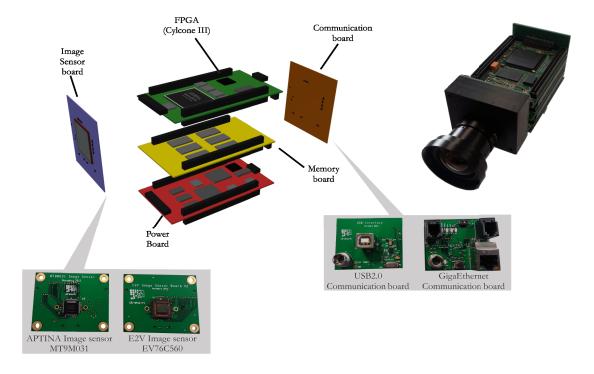

Les capteurs intelligents de nos jours nécessitent des composants de traitement dotés d'une puissance suffisante pour exécuter les algorithmes à la cadence de ces capteurs d'images performants, tout en gardant une faible consommation d'énergie. Les systèmes monoprocesseur n'arrivent plus à satisfaire les exigences de ce domaine. Ainsi, grâce aux avancées technologiques et en s'appuyant sur de précédents travaux sur les machines parallèles, les systèmes multiprocesseurs sur puce (MPSoC) représentent une solution intéressante et prometteuse. Dans de précédents travaux à cette thèse, la cible technologique pour développer de tels systèmes était les FPGA. Or les résultats ont montré les limites de cette cible en terme de ressource matérielles et en terme de performance (vitesse notamment). Ce constat nous amène à changer de cible c'est-à-dire à passer sur cible ASIC nécessitant ainsi de retravailler profondément l'architecture et les IPs qui existaient autour de la méthode existante (appelée HNCP, pour Homogeneous Network of Communicating Processors).

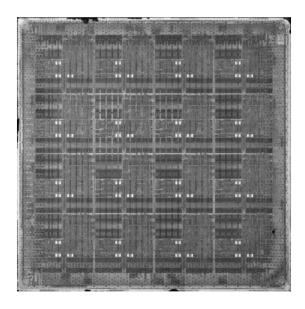

Afin de bénéficier de la performance offerte par la cible ASIC, les systèmes multiprocesseurs proposés s'appuient sur la flexibilité de son architecture. Combinés à des squelettes de parallélisation facilitant la programmabilité de l'architecture, les circuits proposés permettent d'offrir des systèmes supportant le portage en temps réels de différentes classes d'algorithme de traitement d'images. Le résultat de ce travail a abouti à la fabrication d'un circuit intégré à base d'un seul processeur et de ses périphériques en technologie ST CMOS 65nm dont la surface est d'environ 1  $mm^2$  et à la définition de 2 architectures multiprocesseurs flexibles basées sur le concept des squelettes de parallélisation (une architecture de 16 cœurs de processeur en technologie ST CMOS 65 nm et une deuxième architecture de 64 cœurs de processeur en technologie ST CMOS FD-SOI 28 nm).

Mots-clés : Architecture parallèle, Traitement d'images en temps réel, Caméra intelligente, Système embarqué, MPSoC, ASIC, FPGA, 65nm CMOS, 28nm CMOS FD-SOI.

#### Abstract

Smart sensors today require processing components with sufficient power to run algorithms at the rate of these high-performance image sensors, while maintaining low power consumption. Monoprocessor systems are no longer able to meet the requirements of this field. Thus, thanks to technological advances and based on previous works on parallel computers, multiprocessor systems on chip (MPSoC) represent an interesting and promising solution. Previous works around this thesis have used FPGA as technological target. However, results have shown the limits of this target in terms of hardware resources and in terms of performance (speed in particular). This observation leads us to change the target from FPGA to ASIC. This migration requires deep rework at the architecture level. Particularly, existing IPs around the method (called HNCP for Homogeneous Network of Communicating Processors) have to be revisited.

To take advantage of the performance offered by the ASIC target, proposed multiprocessor systems are based on the flexibility of its architecture. Combined with parallel skeletons that ease programmability of the architecture, the proposed circuits allow to offer systems that support various real-time image processing algorithms. This work has led to the fabrication of an integrated circuit based on a single processor and its peripheral using ST CMOS 65nm technology with an area around 1  $mm^2$ . Moreover, two flexible multiprocessor architectures based on the concept of parallel skeletons have been proposed (a 16 cores 65 nm CMOS multiprocessors and a 64 cores 28 nm FD-SOI CMOS multiprocessors).

**Keywords**: Parallel architecture, Real-time image processing, Smart camera, Embedded system, MPSoC, ASIC, FPGA, 65nm CMOS, 28nm CMOS FD-SOI.

| 18 | able            | des ma   | tteres                                                             | 1  |

|----|-----------------|----------|--------------------------------------------------------------------|----|

| Ta | able            | des fig  | ures                                                               | 7  |

| In | $\mathbf{trod}$ | uction   |                                                                    | 11 |

| 1  | Le              | context  | te de la thèse                                                     | 15 |

|    | 1.1             | Introd   | uction                                                             | 15 |

|    | 1.2             | Archit   | ecture dédiée à la vision                                          | 15 |

|    | 1.3             | Les ca   | méras intelligentes                                                | 16 |

|    |                 | 1.3.1    | Principe du capteur d'image                                        | 16 |

|    |                 | 1.3.2    | Caméras intelligentes dans la littérature                          | 16 |

|    |                 | 1.3.3    | Caméra intelligente utilisée dans le cadre de ces travaux          | 16 |

|    |                 | 1.3.4    | Impact de la haute résolution sur le traitement                    | 18 |

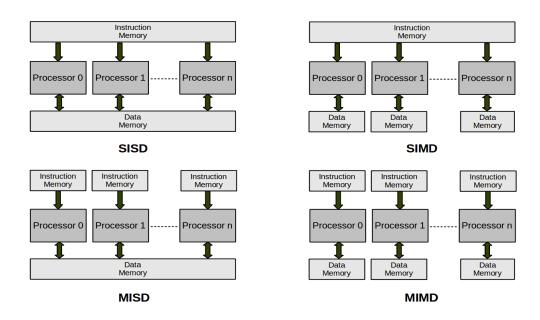

|    | 1.4             | Archit   | ectures parallèles pour la vision artificielle                     | 18 |

|    | 1.5             | Les sy   | stèmes sur puce                                                    | 20 |

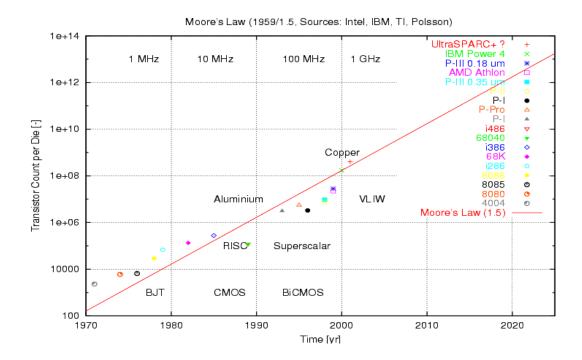

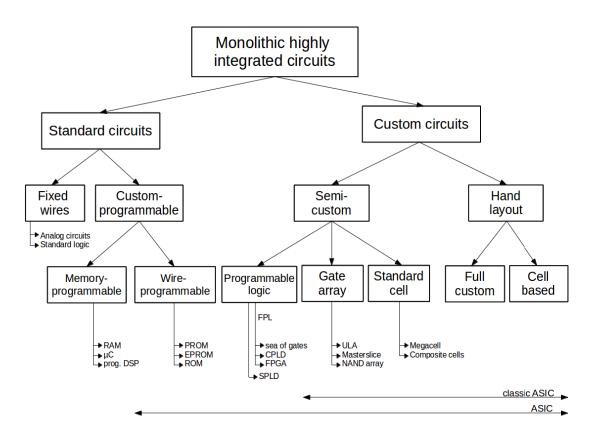

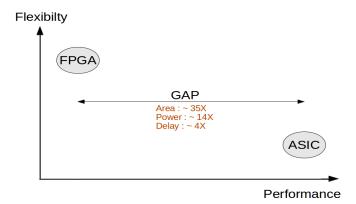

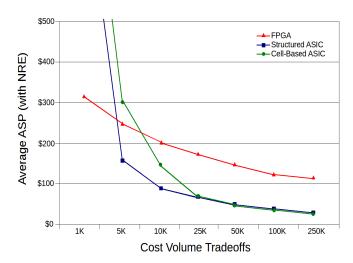

|    | 1.6             | Les cil  | oles technologiques                                                | 22 |

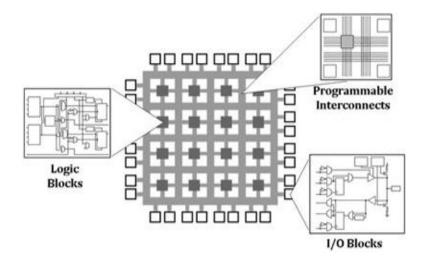

|    |                 | 1.6.1    | Les FPGAs                                                          | 23 |

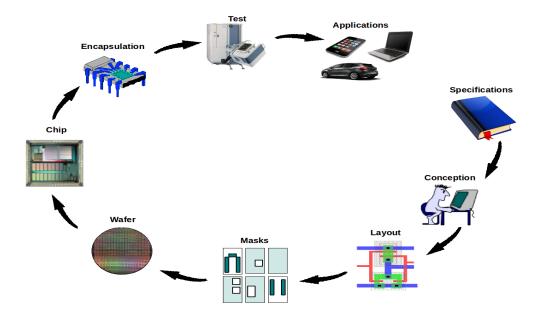

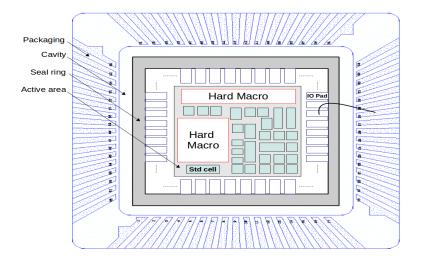

|    |                 | 1.6.2    | Les ASICs                                                          | 24 |

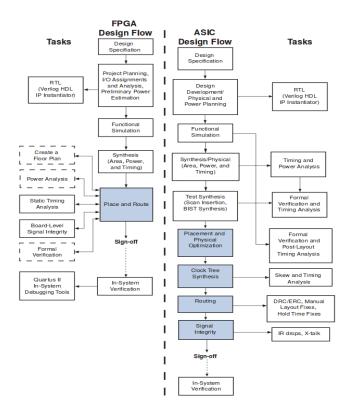

|    |                 | 1.6.3    | Flot de conception sur FPGA et sur ASIC                            | 25 |

|    | 1.7             | FPGA     | vs ASIC                                                            | 27 |

|    | 1.8             | Solution | ons de traitement pour la complexité croissante des applications . | 29 |

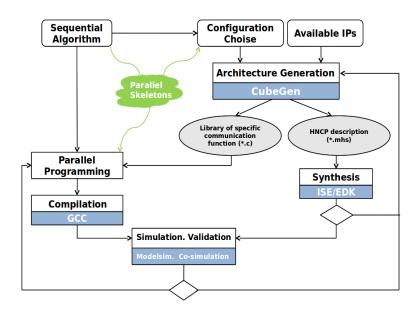

|    | 1.9             | HNCF     | ': Une méthodologie de prototypage rapide                          | 29 |

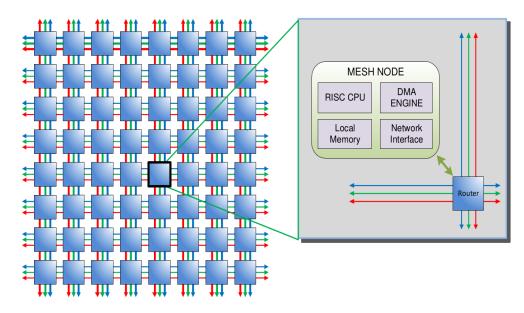

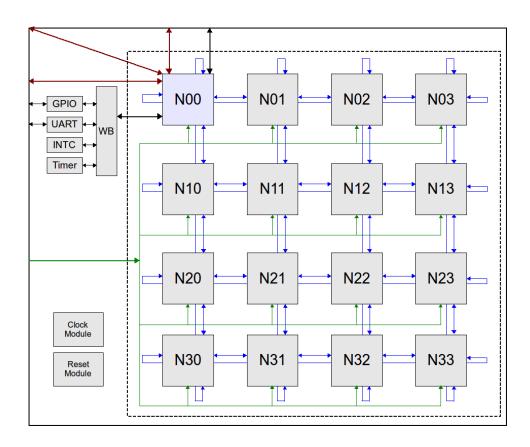

|    |                 | 1.9.1    | Présentation de la méthodologie                                    | 29 |

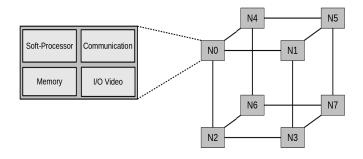

|    |                 | 1.9.2    | Aspect matériel de la méthodologie                                 | 30 |

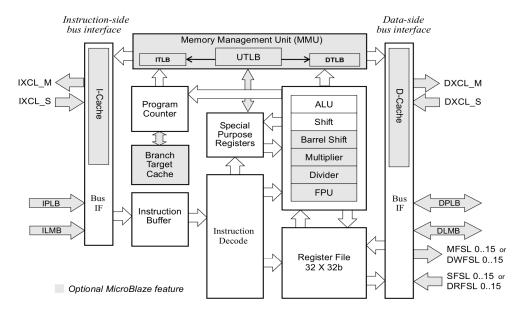

|    |                 |          | 1.9.2.1 Unité de calcul (processeur)                               | 31 |

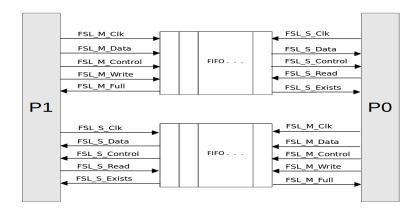

|    |                 |          | 1.9.2.2 Unité de communication                                     | 31 |

|    |                 |          | 1.9.2.3 Unité de mémoire                                           | 33 |

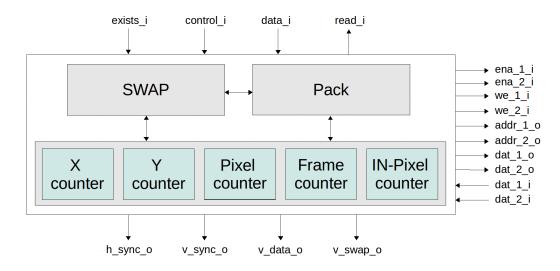

|    |                 |          | 1.9.2.4 Unité de gestion du flot vidéo                             | 33 |

|    |                 | 1.9.3    | Aspect logiciel de la méthodologie                                 | 33 |

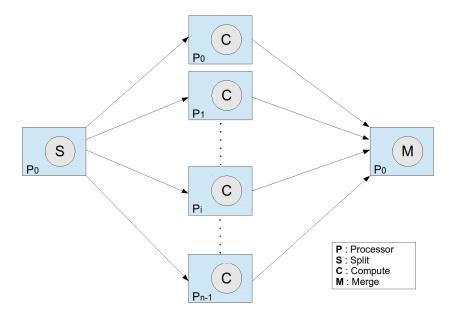

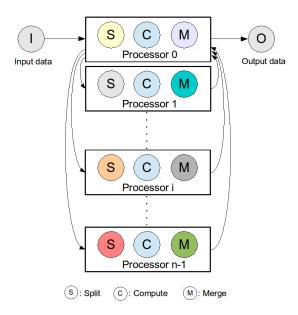

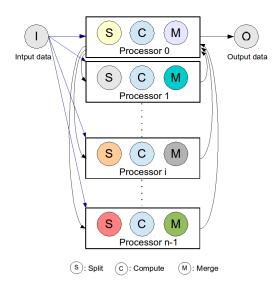

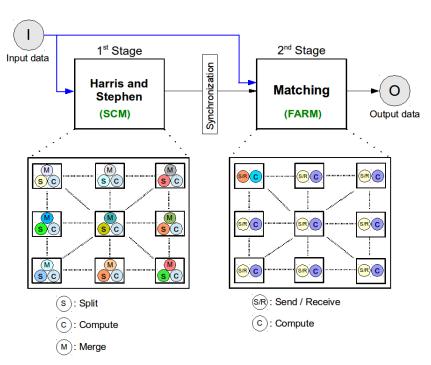

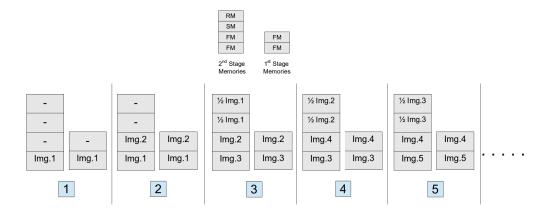

|    |                 |          | 1.9.3.1 Le squelette SCM (Split, Compute and Merge)                | 33 |

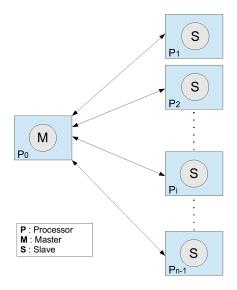

|    |                 |          | 1.9.3.2 Le squelette FARM                                          | 35 |

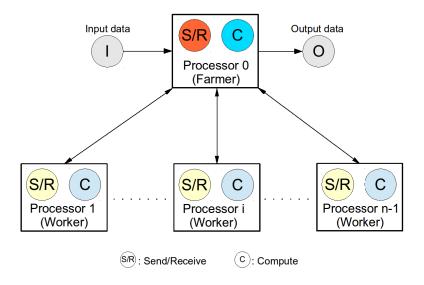

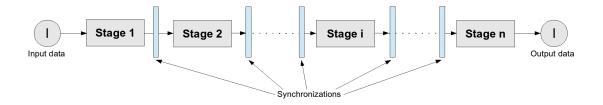

|    |                 |          | 1.9.3.3 Le squelette PIPE                                          | 36 |

|    |                 | 1.9.4    | L'outil CubeGen                                                    | 37 |

|          |      | 1.9.5 Les nimites de l'arcintecture et de l'approche FFGA 5              |            |

|----------|------|--------------------------------------------------------------------------|------------|

|          | 1.10 | Passage de FPGA vers ASIC                                                |            |

|          | 1.11 | Conclusion                                                               | 3          |

| <b>2</b> | Tag  | restère as reviltimes assesses intérnés sur pues                         | 1          |

| 4        |      | systèmes multiprocesseurs intégrés sur puce 4                            |            |

|          | 2.1  | Introduction                                                             |            |

|          | 2.2  | Les MPSoC (Multi-Processor System-on-Chip)                               |            |

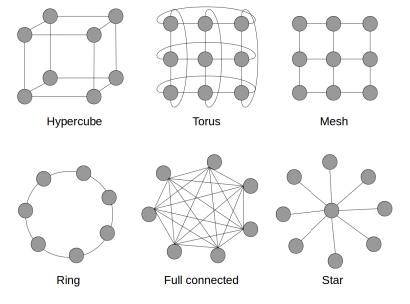

|          | 2.3  | Les topologies                                                           |            |

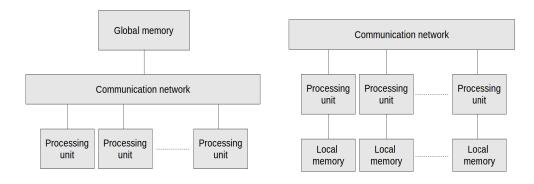

|          | 2.4  | La hiérarchie de la mémoire                                              |            |

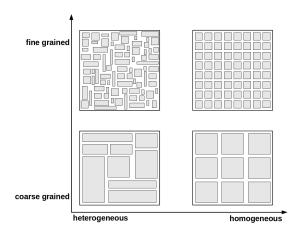

|          | 2.5  | Homogénéité vs. Hétérogénéité                                            |            |

|          | 2.6  | État de l'art sur les MPSoC                                              |            |

|          |      | 2.6.1 RAW (MIT en 1997)                                                  | 1          |

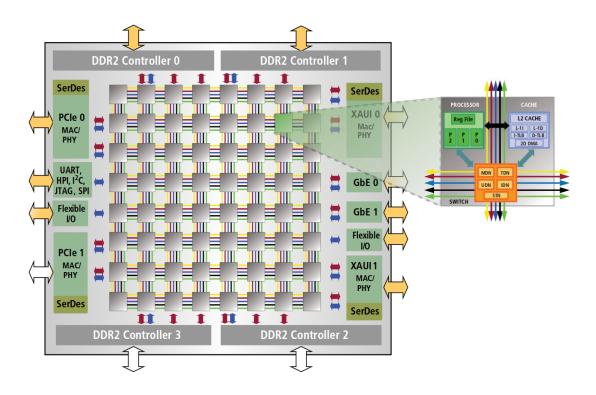

|          |      | 2.6.2 Tile64 (Par Tilera en 2006)                                        | 7          |

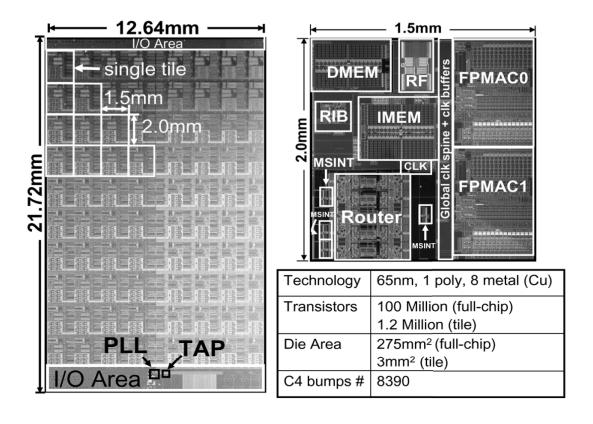

|          |      | 2.6.3 Teraflops (Intel en 2007)                                          | 8          |

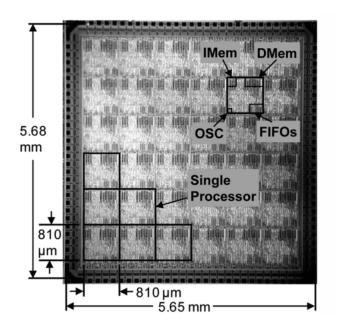

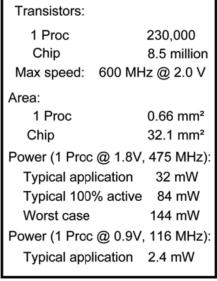

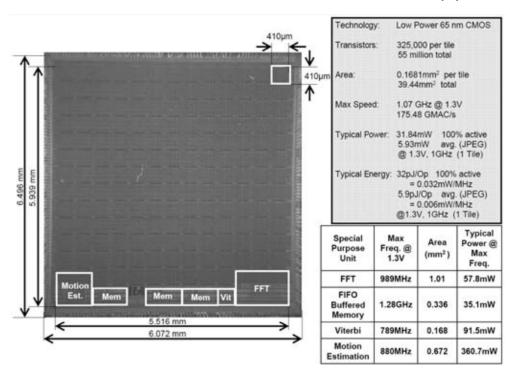

|          |      | 2.6.4 AsAP 1 (Univ. Californie en 2008)                                  | (          |

|          |      | 2.6.5 AsAP 2 (Univ. Californie en 2009)                                  | (          |

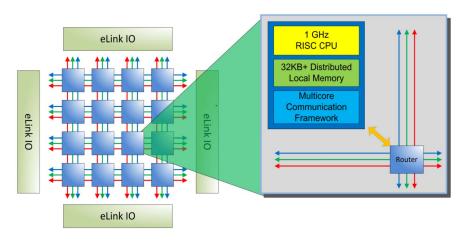

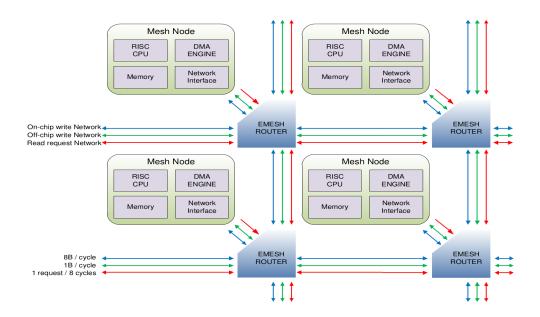

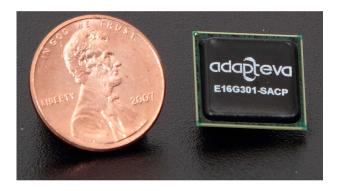

|          |      | 2.6.6 EpiphanyIII (Adapteva en 2011)                                     | [[         |

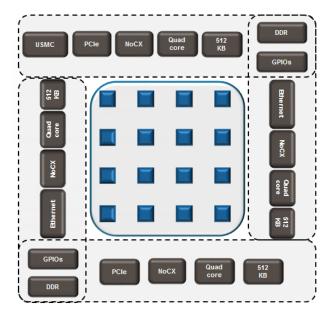

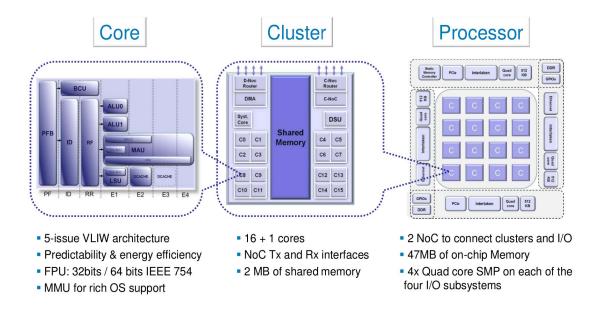

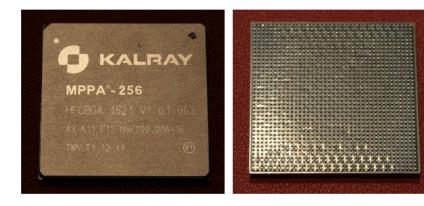

|          |      | 2.6.7 MPPA 256 (Kalray en 2012)                                          | ;          |

|          |      | 2.6.8 EpiphanyIV (Adapteva en 2014)                                      | 6          |

|          |      | 2.6.9 MPPA-512 et MPPA-1024 (Kalray en 2015) 5                           | j(         |

|          | 2.7  | Situation du projet HNCP                                                 | 7          |

|          | 2.8  | Conclusion                                                               | 36         |

|          |      |                                                                          |            |

| 3        |      | age FPGA-ASIC : création du nœud de base du MPSoC 5                      |            |

|          | 3.1  | Introduction                                                             |            |

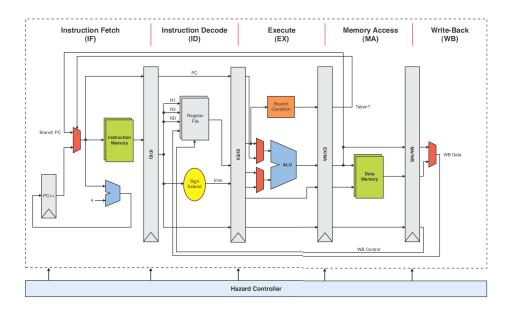

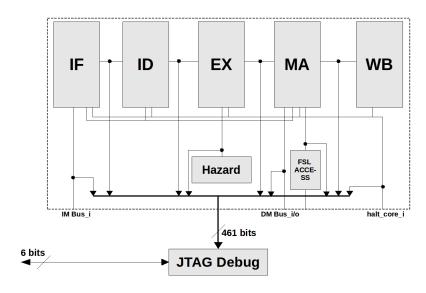

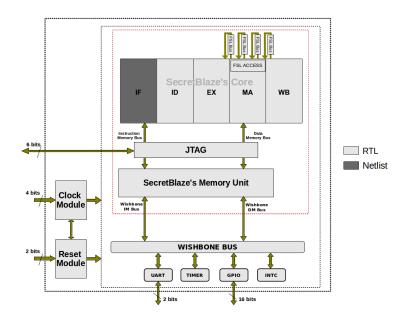

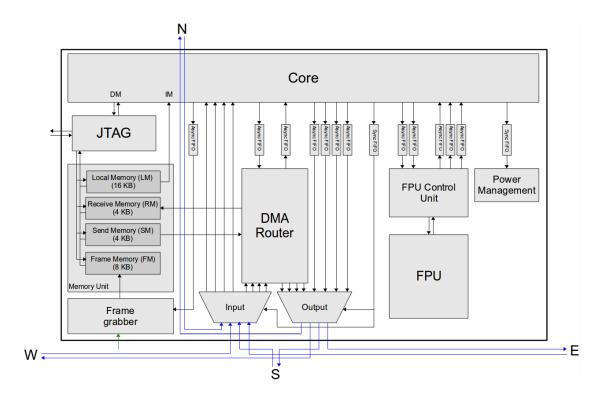

|          | 3.2  | Le cœur du processeur                                                    |            |

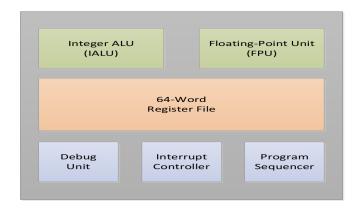

|          |      | 3.2.1 État de l'art sur les processeurs dans la communauté libre $6$     |            |

|          |      | 3.2.2 Description du SecretBlaze 6                                       |            |

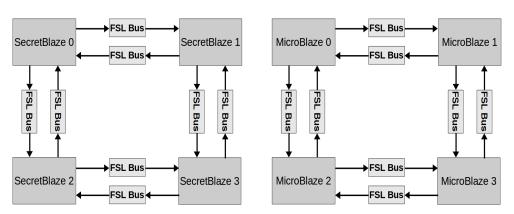

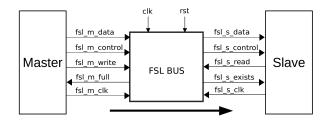

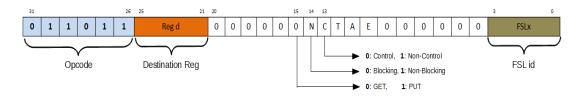

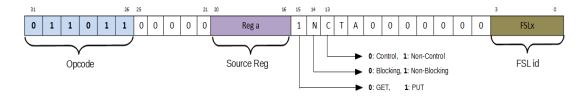

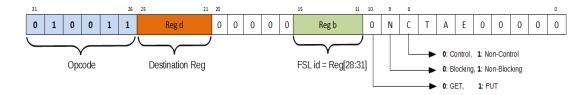

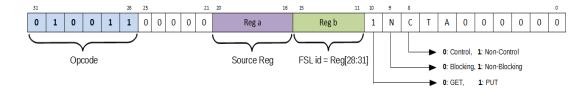

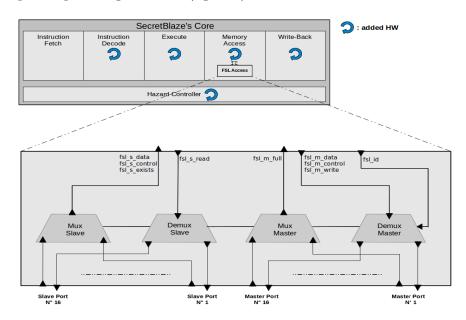

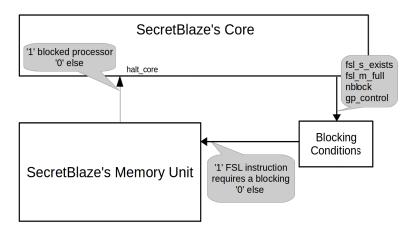

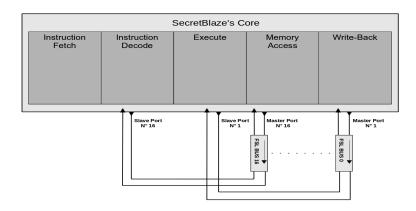

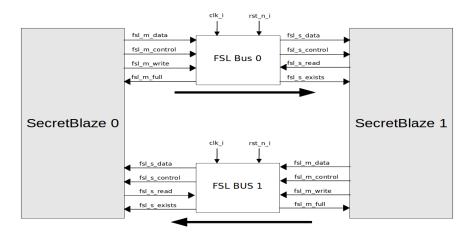

|          | 3.3  | Amélioration de la communication par l'ajout d'instructions FSL 6        |            |

|          |      | 3.3.1 Résultats d'implantations 6                                        | ;          |

|          |      | 3.3.2 Comparaison avec les instructions FSL de MicroBlaze 6              | ;          |

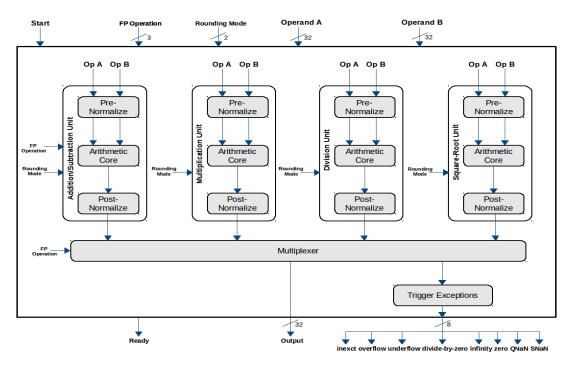

|          | 3.4  | Amélioration de la performance par l'ajout d'unité à virgule flottante 6 | <b>;</b> 4 |

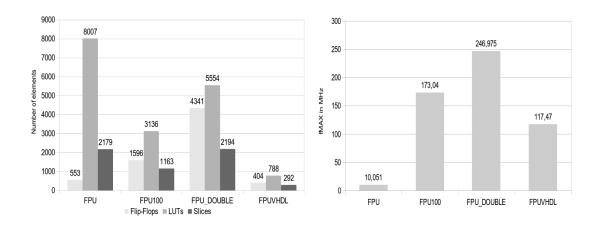

|          |      | 3.4.1 État de l'art sur les unités à virgule flottante 6                 | ;[         |

|          |      | 3.4.2 L'unité à virgule flottante choisie 6                              | ;7         |

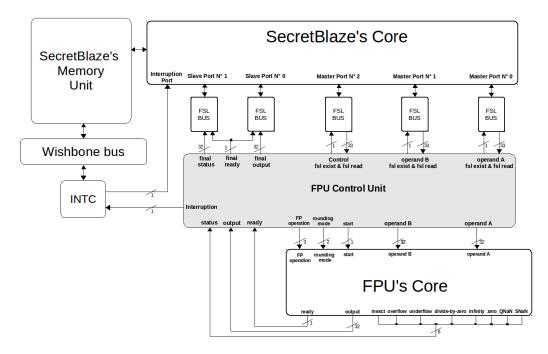

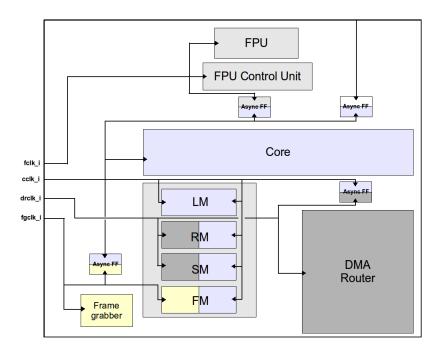

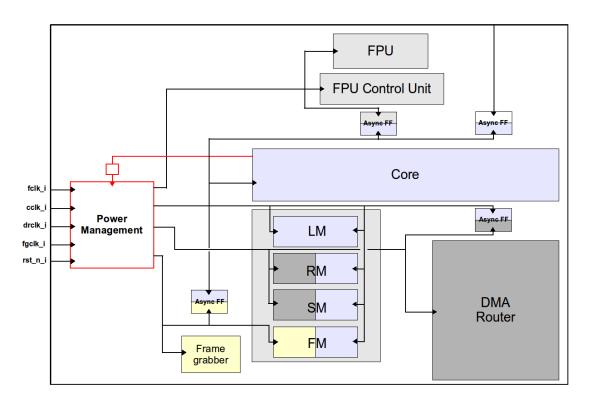

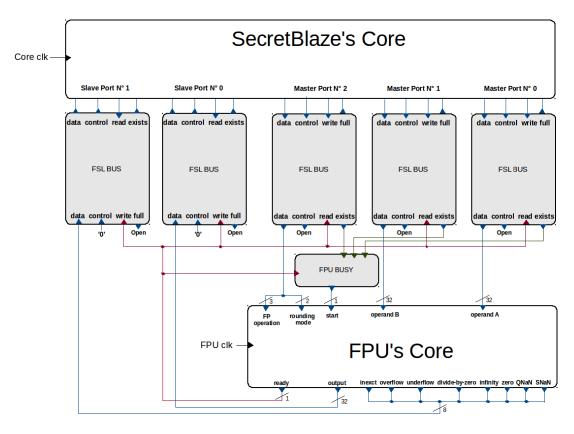

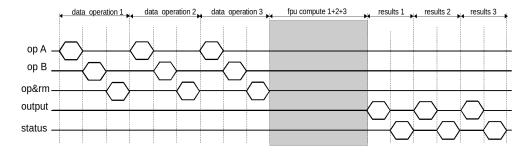

|          |      | 3.4.3 Intégration de la FPU dans le système 6                            | 36         |

|          |      | 3.4.4 Comparaison avec la FPU du MicroBlaze 6                            | 36         |

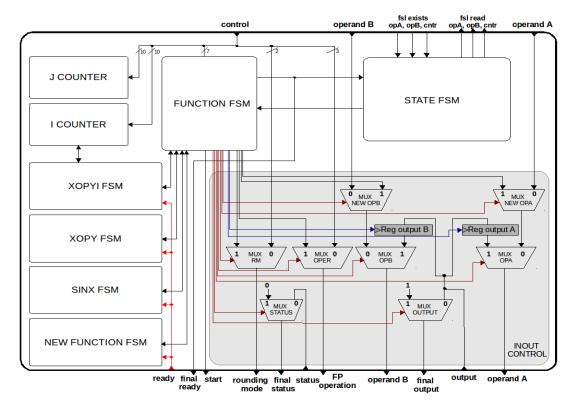

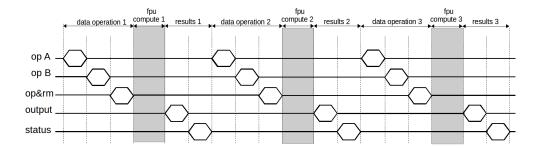

|          |      | 3.4.5 L'unité de contrôle FPU                                            | <b>'</b> ( |

|          |      | 3.4.5.1 Méthode d'implantation de fonctions spécifiques 7                |            |

|          |      | 3.4.5.2 Exemples de fonctions mises en œuvre                             |            |

|          |      | 3.4.5.3 L'architecture de l'unité de contrôle FPU                        |            |

|          |      | 3.4.5.4 Résultats d'implantation                                         |            |

|          |      | 3.4.5.5 Comment ajouter des nouvelles fonctions?                         |            |

|          | 3.5  | L'organisation de la mémoire                                             |            |

|          | 0.0  | 9                                                                        |            |

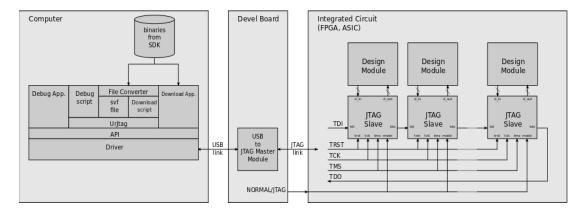

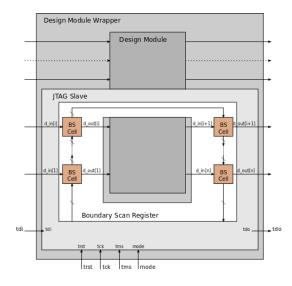

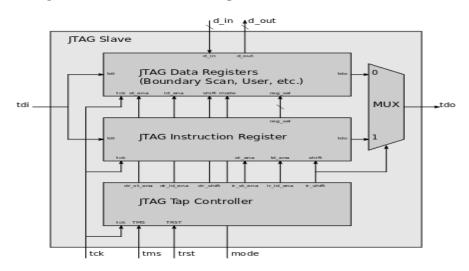

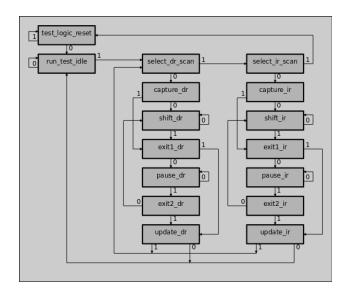

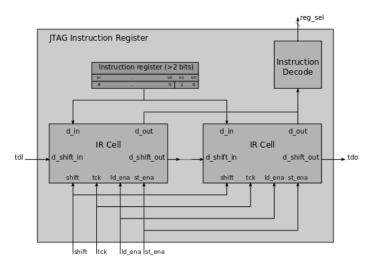

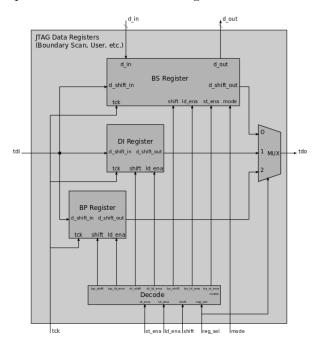

|          | 3.6  | Ajout du JTAG: un moyen de programmation et de debug                     | r          |

|   |      | 3.6.1  | Résultats d'implantations                                        |

|---|------|--------|------------------------------------------------------------------|

|   | 3.7  | Proto  | coles de communication                                           |

|   |      | 3.7.1  | Protocole de communication par bus FSL                           |

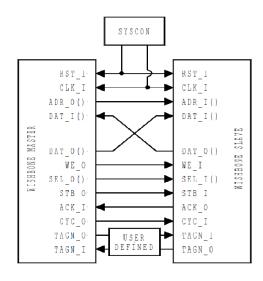

|   |      | 3.7.2  | Protocole de communication par bus Wishbone                      |

|   |      | 3.7.3  | Résultats d'implantation                                         |

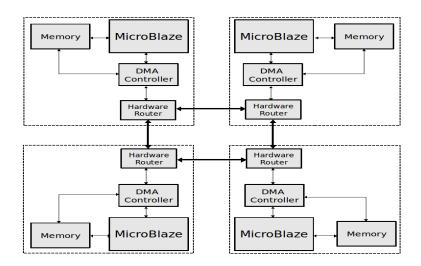

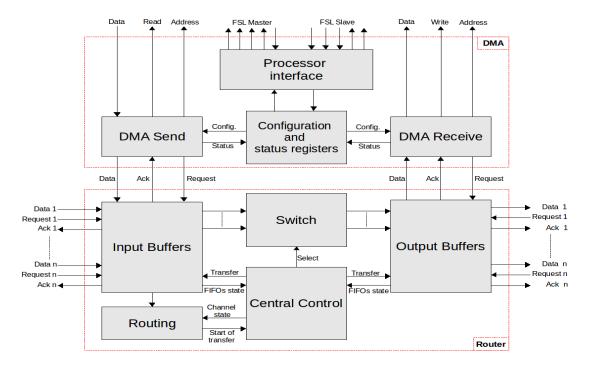

|   | 3.8  | Le DN  | MA-Routeur                                                       |

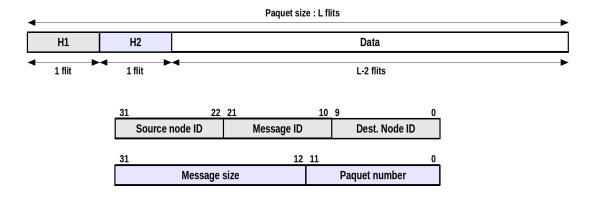

|   |      | 3.8.1  | Principe de fonctionnement du DMA-Routeur                        |

|   |      | 3.8.2  | Architecture du DMA-Routeur                                      |

|   |      |        | 3.8.2.1 Architecture du DMA                                      |

|   |      |        | 3.8.2.2 Architecture du Routeur                                  |

|   |      | 3.8.3  | Ajout de deux nouvelles topologie : grille et tore               |

|   |      | 3.8.4  | Ré-usinage du code                                               |

|   |      | 3.8.5  | Évaluation des performances                                      |

|   |      | 3.8.6  | Résultats d'implantation                                         |

|   |      | 3.8.7  | Les fonctions logiciels du DMA-Router                            |

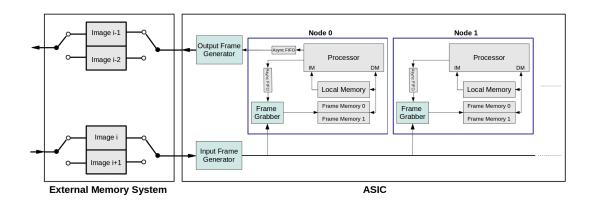

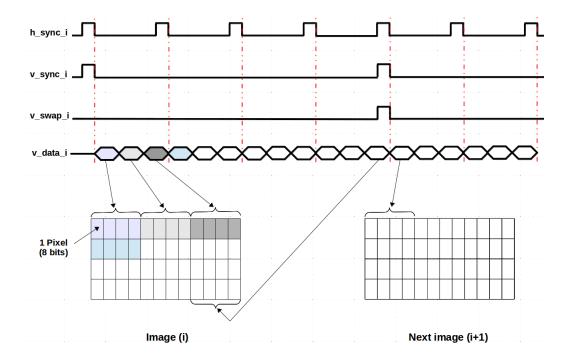

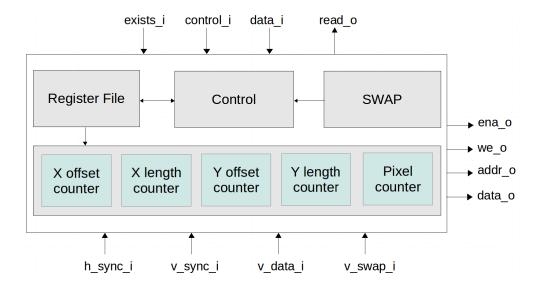

|   | 3.9  | Gestic | on du flot vidéo                                                 |

|   |      | 3.9.1  | Transport de l'information vidéo                                 |

|   |      | 3.9.2  | Au niveaux nœud : frame grabber                                  |

|   |      | 3.9.3  | Au niveaux circuit : frame generator                             |

|   |      | 3.9.4  | Résultats d'implantation                                         |

|   |      | 3.9.5  | Un système incluant une mémoire externe pour sauvegarder l'image |

|   |      |        | globale                                                          |

|   | 3.10 | Concl  | usion                                                            |

| 4 | HN   | CP-I · | conception du nœud de base en technologie ST 65nm CMOS 9         |

| • | 4.1  |        | luction                                                          |

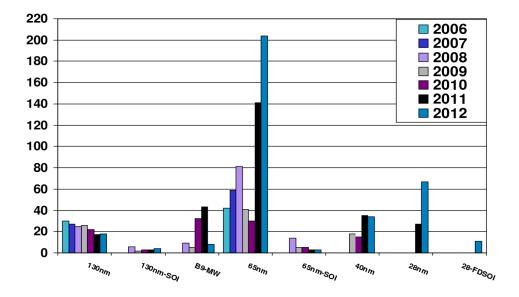

|   | 4.2  |        | de la technologie                                                |

|   | 4.3  |        | e et choix de l'architecture du RUN                              |

|   | 4.4  |        | odologie utilisée pour le test du circuit                        |

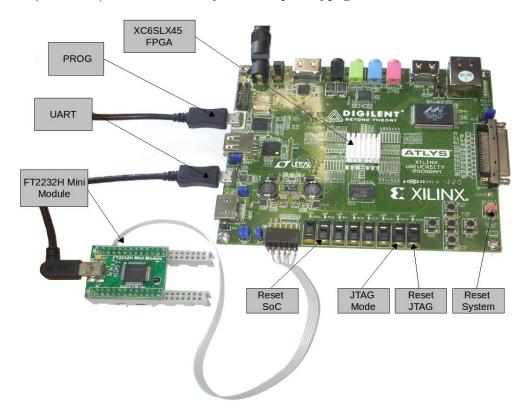

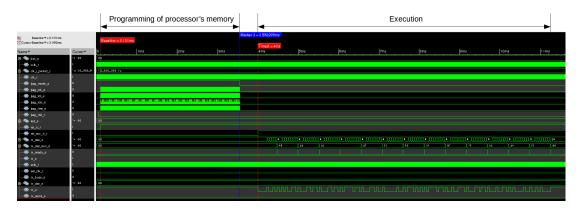

|   | 4.5  |        | ototypage sur FPGA                                               |

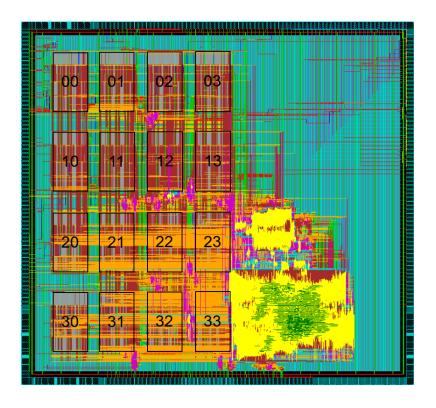

|   | 4.6  | _      | eption de l'ASIC                                                 |

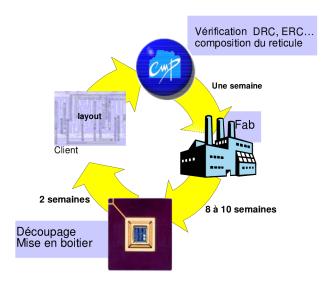

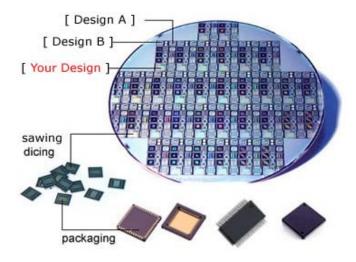

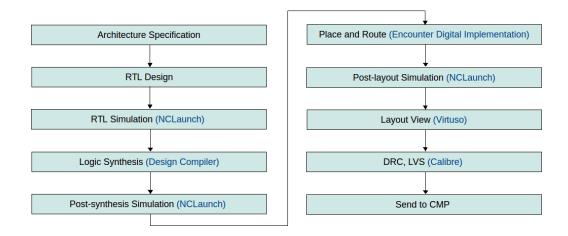

|   | 1.0  |        | Flot et outils de conception du premier RUN                      |

|   |      | 4.6.2  | Approche utilisée pour la migration du code RTL pour la cible    |

|   |      | 1.0.2  | ASIC                                                             |

|   |      | 4.6.3  | La synthèse logique                                              |

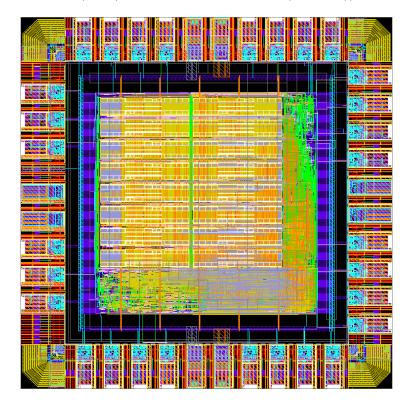

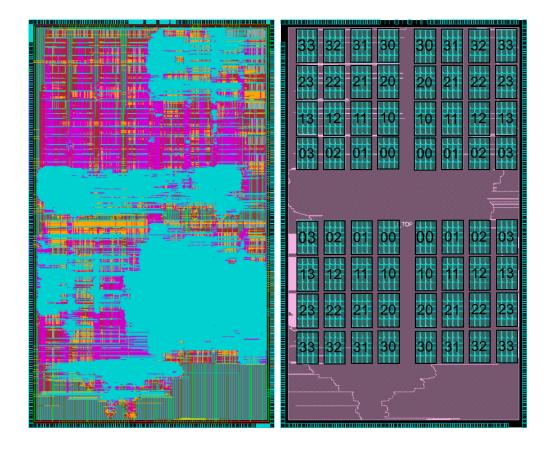

|   |      | 4.6.4  | Le placement-routage                                             |

|   |      | 4.6.5  | Les simulations                                                  |

|   |      | 4.6.6  | Vérification physique et envoi du circuit                        |

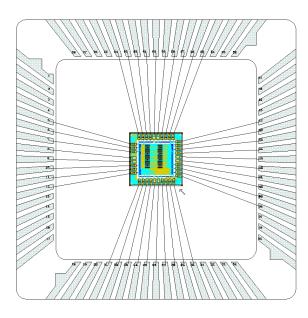

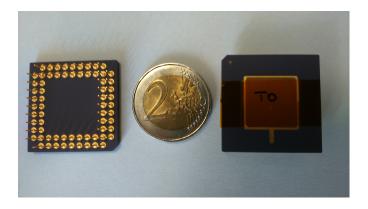

|   |      | 4.6.7  | Mise en boîtier du circuit                                       |

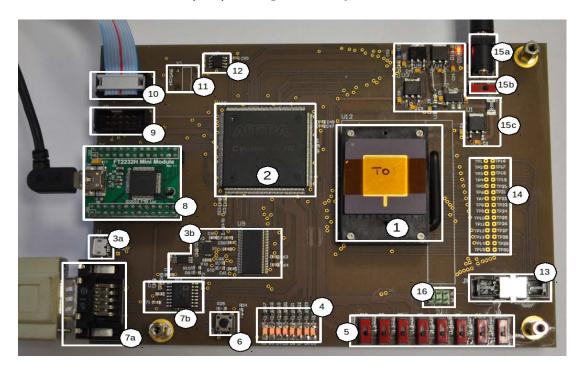

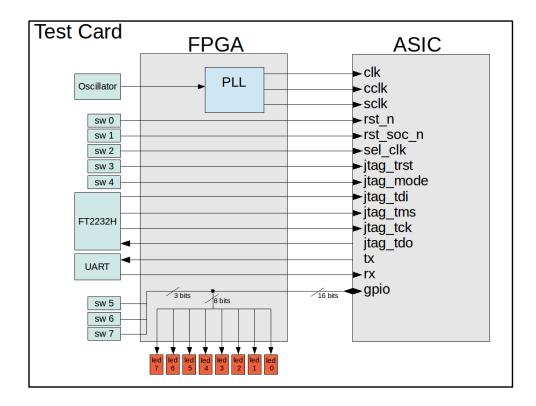

|   | 4.7  | Carte  | de test                                                          |

|   | 4.8  |        | lu circuit                                                       |

|   | 4.9  | Concl  |                                                                  |

|   |      |        |                                                                  |

| <b>5</b> | HN  | CP-II   | : une architecture multiprocesseurs homogènes communi                | i–         |

|----------|-----|---------|----------------------------------------------------------------------|------------|

|          | can | ts à 16 | cœurs en technologie ST 65nm CMOS                                    | 109        |

|          | 5.1 | Introd  | uction                                                               | 109        |

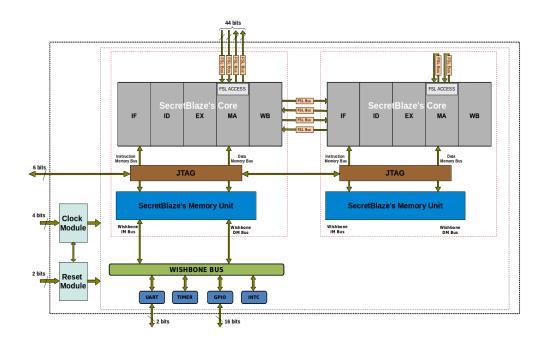

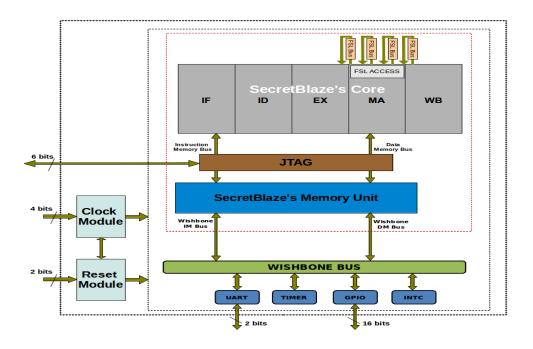

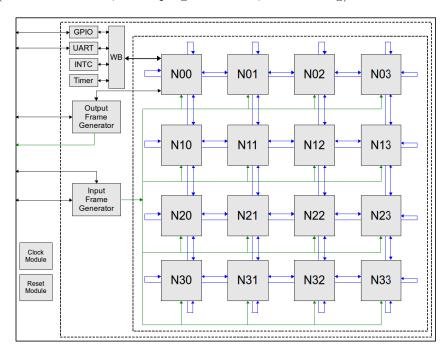

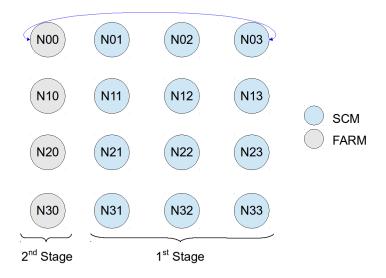

|          | 5.2 | Archit  | ecture proposée du HNCP-II                                           | 110        |

|          |     | 5.2.1   | Architecture du circuit                                              | 110        |

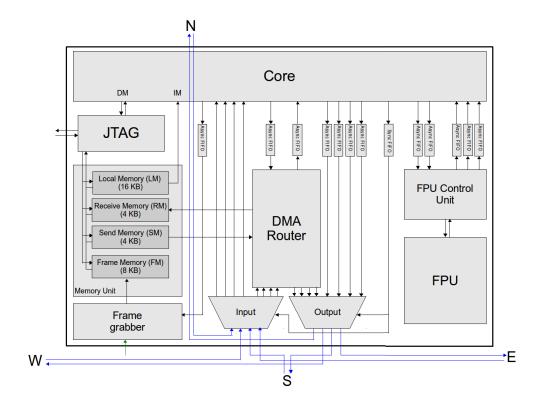

|          |     | 5.2.2   | Architecture du nœud                                                 | 111        |

|          |     | 5.2.3   | Domaine d'horloge                                                    | 113        |

|          |     | 5.2.4   | La problématique de la taille de l'image à traiter                   | 114        |

|          | 5.3 | Impla   | ntation sur FPGA                                                     | 114        |

|          | 5.4 | Implai  | ntation sur ASIC                                                     | 115        |

|          |     | 5.4.1   | Résultats après l'étape de synthèse logique                          | 115        |

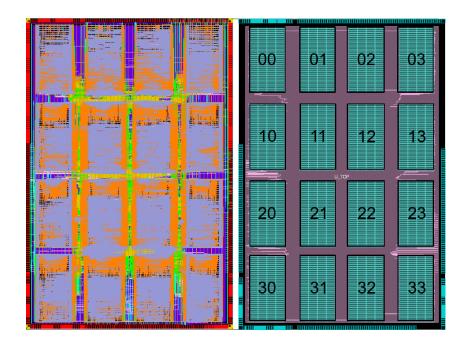

|          |     | 5.4.2   | Résultats après l'étape de placement-routage                         | 116        |

|          | 5.5 | Valida  | tions algorithmiques                                                 | 117        |

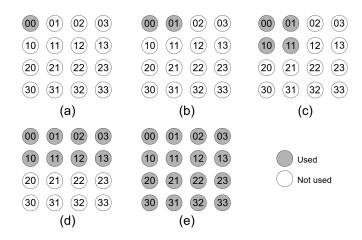

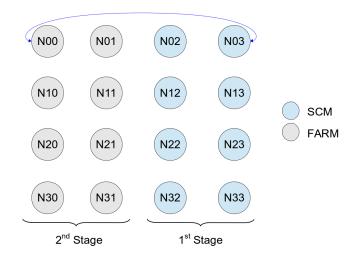

|          |     | 5.5.1   | Configurations architecturales d'évaluations                         |            |

|          |     | 5.5.2   | Validation du squelette SCM sur l'architecture proposée              | 119        |

|          |     |         | 5.5.2.1 Principe de fonctionnement en mode SCM                       |            |

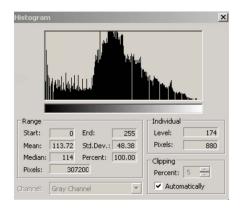

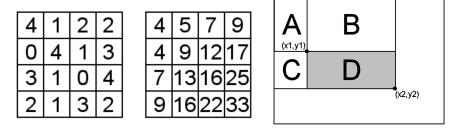

|          |     |         | 5.5.2.2 Algorithme de calcul d'Histogramme                           |            |

|          |     |         | 5.5.2.3 Résultats d'exécution                                        |            |

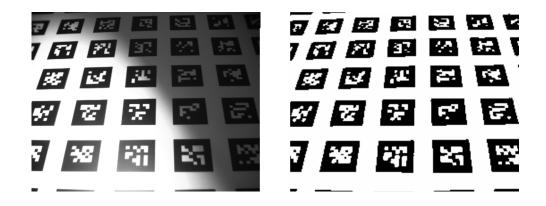

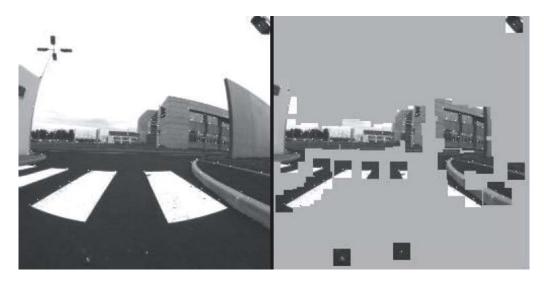

|          |     |         | 5.5.2.4 Algorithme du seuillage adaptatif                            | 123        |

|          |     |         | 5.5.2.5 Résultats d'exécution                                        |            |

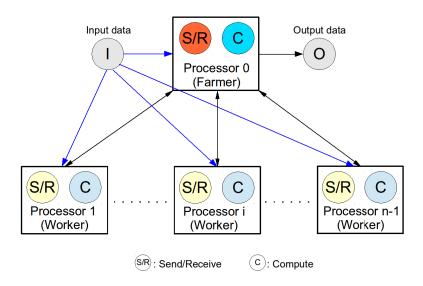

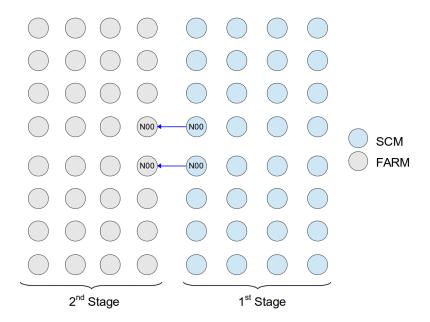

|          |     | 5.5.3   | Validation du squelette FARM sur l'architecture proposée             |            |

|          |     |         | 5.5.3.1 Principe de fonctionnement en mode FARM                      |            |

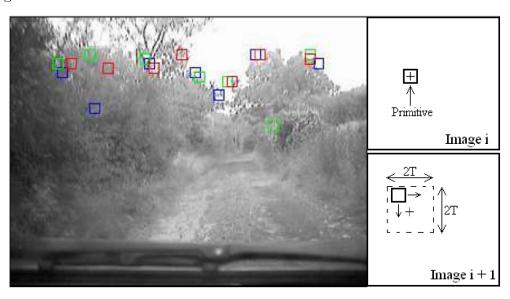

|          |     |         | 5.5.3.2 Algorithme de mise en correspondance de primitives           |            |

|          |     |         | 5.5.3.3 Résultats d'exécution                                        |            |

|          |     | 5.5.4   | Validation du squelette PIPE sur l'architecture proposée             |            |

|          |     |         | 5.5.4.1 Algorithme d'Harris et Stephen                               |            |

|          |     |         | 5.5.4.2 Résultats d'exécution                                        |            |

|          |     |         | 5.5.4.3 Implantation d'un pipeline de 8 nœuds en SCM suivis          |            |

|          |     |         | de 8 nœuds en FARM                                                   | 131        |

|          |     |         | 5.5.4.4 Nouvelle proposition d'implantation de pipeline de 4         |            |

|          |     |         | nœuds en SCM suivis de 12 nœuds en FARM                              | 133        |

|          | 5.6 | Concl   |                                                                      |            |

|          | 0.0 |         |                                                                      |            |

| 6        | HN  | CP-III  | I : une architecture multiprocesseurs homogènes communi              | i <b>–</b> |

|          | can | ts à 64 | cœurs en technologie ST 28nm FD-SOI                                  | 137        |

|          | 6.1 | Introd  | uction                                                               | 137        |

|          | 6.2 | La tec  | hnologie ST 28 nm FD-SOI                                             | 138        |

|          | 6.3 | Résult  | ats d'implantation du HNCP-II en technologie $28~\mathrm{nm}$ FD-SOI | 139        |

|          |     | 6.3.1   | Résultats après l'étape de synthèse logique                          | 139        |

|          |     | 6.3.2   | Résultats après l'étape de placement-routage                         |            |

|          |     | 6.3.3   | Estimations des temps d'exécution de l'HNCP-II en technologie        |            |

|          |     |         | ST 28 nm FD-SOI                                                      | 142        |

|          |     | 6.3.4   | Comparaison de l'implantation en 65 nm et en 28 nm                   | 142        |

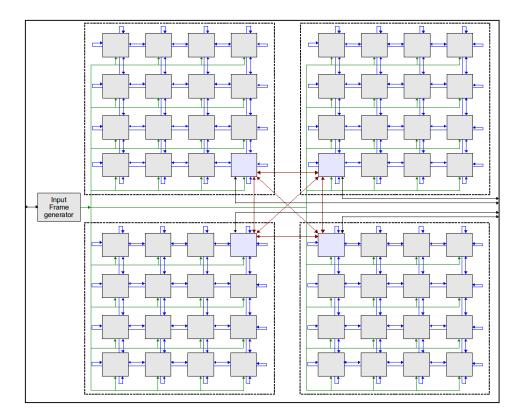

|          | 6.4 | Archit  | ecture proposée du HNCP-III                                          |            |

|         |      | 6.4.1                                                | Architec                                                                                                                                                                                 | ture du circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 144                                                                                             |

|---------|------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|         |      | 6.4.2                                                | Architec                                                                                                                                                                                 | ture du cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 145                                                                                             |

|         |      | 6.4.3                                                | Architec                                                                                                                                                                                 | ture du nœud                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 146                                                                                             |

|         |      | 6.4.4                                                | Domaine                                                                                                                                                                                  | e d'horloge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 146                                                                                             |

|         | 6.5  | Problé                                               | matique o                                                                                                                                                                                | du prototypage sur FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 147                                                                                             |

|         | 6.6  | Résult                                               | ats d'imp                                                                                                                                                                                | olantation du HNCP-III en technologie ST 28 nm FD-SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OI 148                                                                                            |

|         |      | 6.6.1                                                | Résultat                                                                                                                                                                                 | s après l'étape de synthèse logique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 148                                                                                             |

|         |      | 6.6.2                                                | Résultat                                                                                                                                                                                 | s après l'étape de placement-routage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 149                                                                                             |

|         | 6.7  | Valida                                               | tions algo                                                                                                                                                                               | orithmiques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 150                                                                                             |

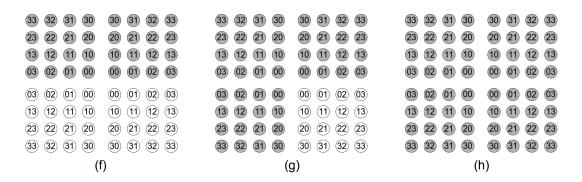

|         |      | 6.7.1                                                | Configur                                                                                                                                                                                 | rations architecturales d'évaluations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 150                                                                                             |

|         |      | 6.7.2                                                | Validatio                                                                                                                                                                                | on du squelette SCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 151                                                                                             |

|         |      |                                                      | 6.7.2.1                                                                                                                                                                                  | Résultats d'exécution de l'algorithme du calcul d'histo-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                   |

|         |      |                                                      |                                                                                                                                                                                          | gramme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                   |

|         |      |                                                      | 6.7.2.2                                                                                                                                                                                  | Résultats d'exécution de l'algorithme du seuillage adap-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                   |

|         |      |                                                      |                                                                                                                                                                                          | tatif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 152                                                                                             |

|         |      | 6.7.3                                                | Validatio                                                                                                                                                                                | on du squelette FARM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 152                                                                                             |

|         |      |                                                      | 6.7.3.1                                                                                                                                                                                  | Résultats d'exécution de l'algorithme de mise en corres-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                   |

|         |      |                                                      |                                                                                                                                                                                          | pondance de primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 152                                                                                             |

|         |      | 6.7.4                                                | Validatio                                                                                                                                                                                | on du squelette PIPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 153                                                                                             |

|         |      |                                                      | 6.7.4.1                                                                                                                                                                                  | Résultats d'exécution de l'algorithme de Harris et Steph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | en153                                                                                             |

|         |      |                                                      | 6.7.4.2                                                                                                                                                                                  | Exemple de pipeline : 32 nœuds en SCM suivis de 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                 |