# Authenticated Encryption on FPGAs from the Reconfigurable Part to the Static Part

Karim Moussa Ali Abdellatif

### ▶ To cite this version:

Karim Moussa Ali Abdellatif. Authenticated Encryption on FPGAs from the Reconfigurable Part to the Static Part. Cryptography and Security [cs.CR]. Université Pierre et Marie Curie - Paris VI, 2014. English. <NNT: 2014PA066660>. <tel-01158431>

HAL Id: tel-01158431

https://tel.archives-ouvertes.fr/tel-01158431

Submitted on 1 Jun 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

Spécialité: Informatique, Télécommunication et Électronique

École Doctorale Informatique, Télécommunication et Électronique

Présentée par:

Karim Moussa Ali Abdellatif

Pour obtenir le grade de

Docteur de l'Université Pierre et Marie Curie

### CHIFFREMENT AUTHENTIFIÉ SUR FPGAS DE LA PARTIE RECONFIGURABLE À LA PARTIE STATIC

Soutenue le 07/10/2014

devant le jury composé de:

| M.   | Bruno Robisson       | ENSM.SE/CEA               | Rapporteur           |

|------|----------------------|---------------------------|----------------------|

| M.   | Lilian Bossuet       | Laboratoire Hubert Curien | Rapporteur           |

| M.   | Jean-Claude Bajard   | LIP6                      | Examinateur          |

| M.   | Hayder Mrabet        | FLEXRAS                   | Examinateur          |

| M.   | Olivier Lepape       | NanoXplore                | Examinateur          |

| M.   | Habib Mehrez         | LIP6                      | Directeur de thèse   |

| Mme. | Roselyne.Chotin-Avot | LIP6                      | Encaderante de thèse |

# Ph.D. THESIS OF THE PIERRE AND MARIE CURIE UNIVERSITY

Departament: Electronics, Telecommunications and Computer Science

### Presented by:

Karim Moussa Ali Abdellatif

Submitted to obtain the Ph.D. degree from:

University of Pierre and Marie Curie

### Authenticated Encryption on FPGAs from the Reconfigurable Part to the Static Part

Defense date: 07/10/2014

Committee in charge:

| M.   | Bruno Robisson       | ENSM.SE/CEA               | Reviewer          |

|------|----------------------|---------------------------|-------------------|

| M.   | Lilian Bossuet       | Laboratoire Hubert Curien | Reviewer          |

| M.   | Jean-Claude Bajard   | LIP6                      | Examiner          |

| M.   | Hayder Mrabet        | FLEXRAS                   | Examiner          |

| M.   | Olivier Lepape       | NanoXplore                | Examiner          |

| M.   | Habib Mehrez         | LIP6                      | Thesis Advisor    |

| Mme. | Roselyne.Chotin-Avot | LIP6                      | Thesis Co-Advisor |

# Abstract

Communication systems need to access, store, manipulate, or communicate sensitive information. Therefore, cryptographic primitives such as hash functions and block ciphers are deployed to provide encryption and authentication. Recently, techniques have been invented to combine encryption and authentication into a single algorithm which is called Authenticated Encryption (AE). Combining these two security services in hardware produces better performance compared to two separated algorithms since authentication and encryption can share a part of the computation. Because of combining the programmability with the performance of custom hardware, FPGAs become more common as an implementation target for such algorithms.

The first part of this thesis is devoted to efficient and high-speed FPGA-based architectures of AE algorithms, AES-GCM and AEGIS-128, in order to be used in the reconfigurable part of FPGAs to support security services of communication systems. Our focus on the state of the art leads to the introduction of high-speed architectures for slow changing keys applications like Virtual Private Networks (VPNs). Furthermore, we present an efficient method for implementing the GF(2<sup>128</sup>) multiplier, which is responsible for the authentication task in AES-GCM, to support high-speed applications. Additionally, an efficient AEGIS-128 is also implemented using only five AES rounds. Our hardware implementations were evaluated using Virtex-5 and Virtex-4 FP-GAs. The performance of the presented architectures (Thr./Slices) outperforms the previously reported ones.

The second part of the thesis presents techniques for low cost solutions in order to secure the reconfiguration of FPGAs. We present different ranges of low cost implementations of AES-GCM, AES-CCM, and AEGIS-128, which are used in the static part of the FPGA in order to decrypt and authenticate the FPGA bitstream. Presented ASIC architectures were evaluated using 90 and 65 nm technologies and they present better performance compared to the previous work.

**Keywords**– Authenticated Encryption, FPGAs, ASIC, Secure Reconfiguration.

To the memory of my father ..

# Acknowledgements

After seemingly endless days of typing and correcting, the time has come to write the last part of this thesis. I will take this opportunity to thank several people who have greatly influenced the journey leading to this dissertation.

First of all, great appreciation goes to my supervisors Prof. Habib Mehrez and Dr. Roselyne Chotin-Avot for giving me the chance to do the PhD degree in LIP6. I am grateful for the freedom I have been given during my research and the guidance provided when needed.

I would like to extend my gratitude to Prof. Hesham Hamed, Prof. Hassan Aboushady, Dr. Alp Kilic and Vinod Pangracious for their valuable support along the way. A great thank you goes to Akram Malak, Dr. Raouf Khalil, Yasser Yousry, Tamer Badran, Alhassan Sayed, Mohamed Shaaban, and Mootaz Allam for making working hours more enjoyable.

Besides my colleagues, I appreciate the care and support of my good friends, who always managed to move my thoughts away from work when needed like Ahmed Nabil, Mahmoud Borcan, Ahmed Nadi, and Bahaa Elmasry.

Finally, I would like to thank my parents to whom I owe a great deal. To my late father Moussa Abdellatif, thank you for showing me that the key to immortality is to live a life worth remembering. Very special thanks and a lot of love go to my wife Nouranne Fahhim who always motivated and supported me with great enthusiasm.

For all our freedom martyrs, Egypt 25/01/2011

# Contents

| A            | bstra  | act                                  | i   |

|--------------|--------|--------------------------------------|-----|

| A            | ckno   | wledgements                          | iv  |

| $\mathbf{C}$ | onter  | nts                                  | v   |

| Li           | ist of | Figures                              | vii |

| Li           | ist of | Tables                               | ix  |

| 1            | Intr   | roduction                            | 1   |

|              | 1.1    | Motivation                           | 1   |

|              |        | 1.1.1 Authenticated Encryption       | 1   |

|              |        | 1.1.2 FPGAs                          | 3   |

|              | 1.2    | Contributions                        | 6   |

|              | 1.3    | Thesis organization                  | 8   |

| Ι            | Hi     | gh Speed FPGA-based AE Architectures | 10  |

| 2            | Aut    | thenticated Encryption               | 11  |

|              | 2.1    | Introduction                         | 11  |

|              | 2.2    | Advanced Encryption Standard (AES)   | 12  |

|              |        | 2.2.1 Algorithm specifications       | 12  |

|              |        | 2.2.2 Hardware implementation        | 16  |

|              | 2.3    | AES-CCM                              | 19  |

|              |        | 2.3.1 Algorithm specifications       | 19  |

|              |        | 2.3.2 Hardware implementation        | 21  |

|              | 2.4    | AES-GCM                              | 22  |

|              |        | 2.4.1 Algorithm specifications       | 23  |

|              |        | 2.4.2 Hardware implementation        | 25  |

|              | 2.5    | AEGIS                                | 30  |

|              |        | 2.5.1 Algorithm specifications       | 30  |

*Contents* vi

|   | 2.6  | Conclusion                                                                        | 36        |

|---|------|-----------------------------------------------------------------------------------|-----------|

| 3 | App  | ch Speed Authenticated Encryption for Slow Changing Key<br>plications Using FPGAs | <b>37</b> |

|   | 3.1  | Introduction                                                                      | 37        |

|   | 3.2  | High Speed AES-GCM Architectures Using FPGAs                                      | 38        |

|   |      | 3.2.1 Efficient Parallel AES-GCM cores                                            | 44        |

|   | 3.3  | Bitstream security of the proposed architectures                                  | 49        |

|   | 3.4  | Hardware comparison                                                               | 51        |

|   | 3.5  | Conclusion                                                                        | 54        |

| 4 |      | cient and High Speed Key-Independent AES-Based Au-                                |           |

|   | the  | nticated Encryption Architectures Using FPGAs                                     | 55        |

|   | 4.1  | Introduction                                                                      | 55        |

|   | 4.2  | Efficient KOA-Based GHASH                                                         | 56        |

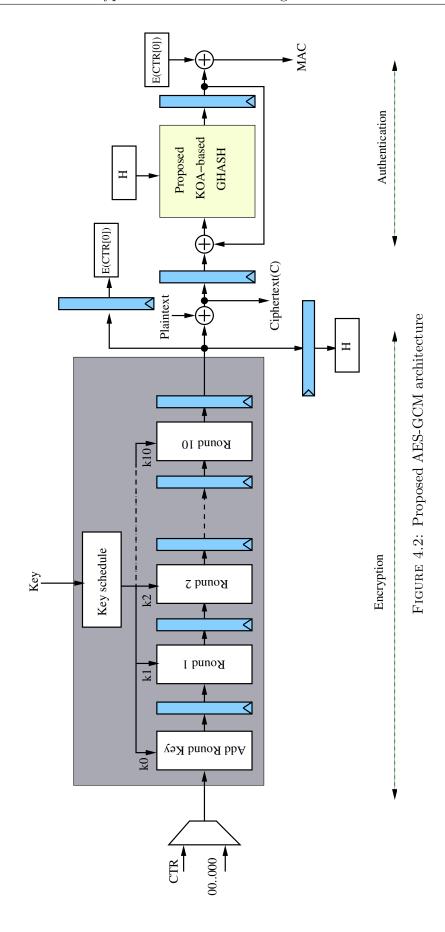

|   | 4.3  | High speed AES-GCM                                                                | 61        |

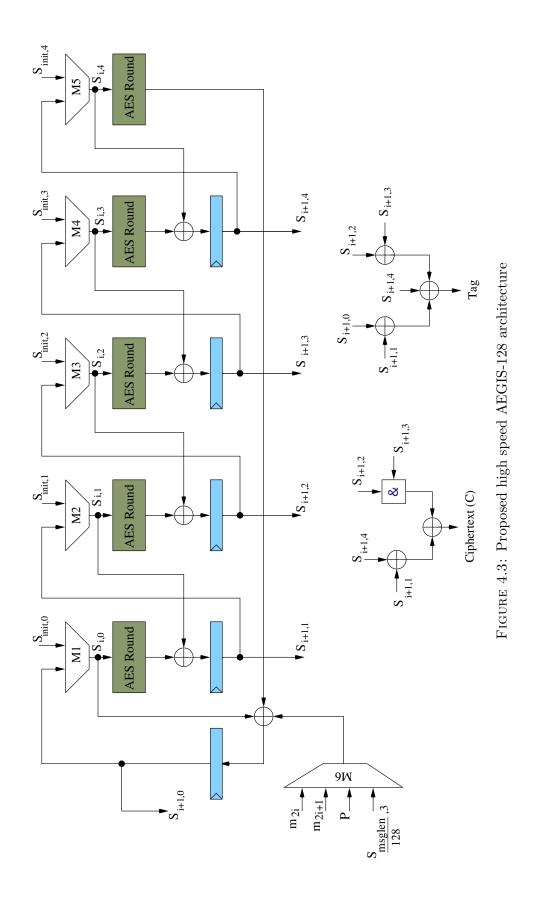

|   | 4.4  | Efficient hardware implementation for AEGIS-128                                   | 63        |

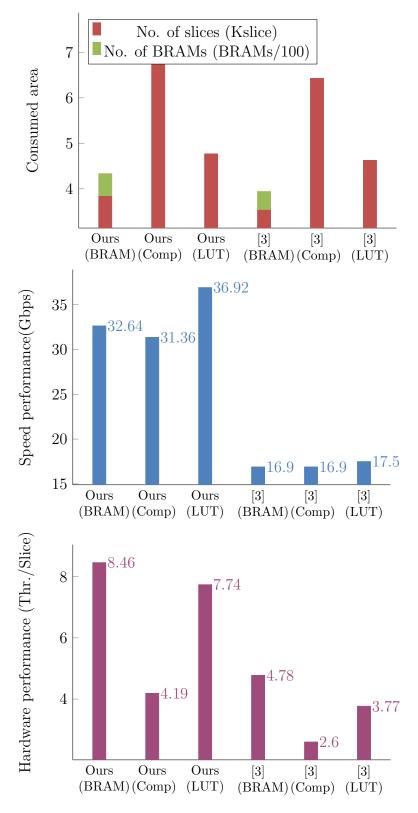

|   | 4.5  | Hardware comparison                                                               | 66        |

|   | 4.6  | Conclusion                                                                        | 70        |

|   | tior |                                                                                   | 71        |

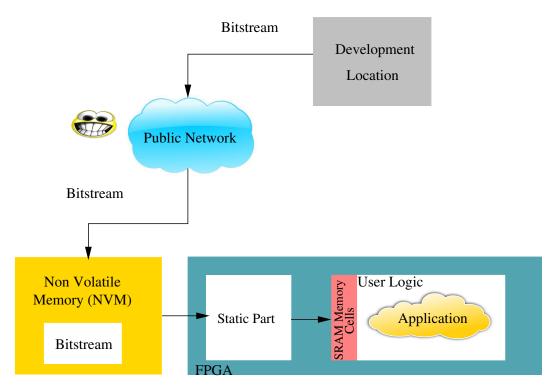

| 5 |      | w Cost Solutions for Secure FPGA Reconfiguration                                  | <b>72</b> |

|   | 5.1  | Introduction                                                                      | 72        |

|   | 5.2  | FPGA reconfiguration                                                              | 73        |

|   | 5.3  | Previous work                                                                     | 75        |

|   | 5.4  | Low cost AE architecture for secure reconfiguration                               | 81        |

|   |      | 5.4.1 Proposed AES-CCM                                                            | 83        |

|   |      | 5.4.2 Proposed AES-GCM                                                            | 87        |

|   |      | 5.4.3 Proposed AEGIS-128                                                          | 92        |

|   | 5.5  | Hardware comparison                                                               | 97        |

|   | 5.6  | Conclusion                                                                        | 100       |

| 6 | Sun  | nmary and Future Work                                                             | 102       |

|   | 6.1  | Thesis Summary                                                                    | 102       |

|   |      | Future work                                                                       |           |

# List of Figures

| 1.1 | Two separated algorithms for encryption and authentication . 2            |

|-----|---------------------------------------------------------------------------|

| 1.2 | Authenticated encryption                                                  |

| 1.3 | Reprogrammability using bitstream                                         |

| 1.4 | Reconfigurable part (user part) architecture                              |

| 1.5 | FPGA reconfiguration using NVM                                            |

| 1.6 | Thesis contribution                                                       |

| 2.1 | AES algorithm                                                             |

| 2.2 | Key expansion of AES-128                                                  |

| 2.3 | (a) Iterative design. (b) Pipelined design                                |

| 2.4 | AES-CCM                                                                   |

| 2.5 | AES-GCM                                                                   |

| 2.6 | Polynomial Multiplication using KOA                                       |

| 2.7 | (a) KOA based GHAH. (b) Pipelined KOA based GHASH 28                      |

| 2.8 | The state update function of AEGIS-128                                    |

| 3.1 | Key-synthesized AES                                                       |

| 3.2 | SubBytes implementation with BlockRAMs (a), with LUTs (b),                |

|     | with composite field approach (c)                                         |

| 3.3 | $GF(2^{128})$ multiplier proposed by [1]                                  |

| 3.4 | Proposed key-synthesized AES-GCM                                          |

| 3.5 | GHASH operation                                                           |

| 3.6 | Proposed parallel GHASHs with fixed operand during running time operation |

| 3.7 | 4-parallel AES-GCM using key-synthesized method 48                        |

| 3.8 | Secure bitstream communication                                            |

| 3.9 | Hardware comparison on Virtex4                                            |

| 4.1 | Proposed pipelined KOA-based GHASH                                        |

| 4.2 | Proposed AES-GCM architecture                                             |

| 4.3 | Proposed high speed AEGIS-128 architecture                                |

| 4.4 | Hardware comparison on Virtex-5                                           |

| 5.1 | Remote reconfiguration                                                    |

| 5.2 | Cloning attack                                                            |

List of Figures viii

| 5.3  | Reverse engineering attack                                  | 75  |

|------|-------------------------------------------------------------|-----|

| 5.4  | Tampering attack                                            | 75  |

| 5.5  | Bitstream encryption/decryption by [2]                      | 77  |

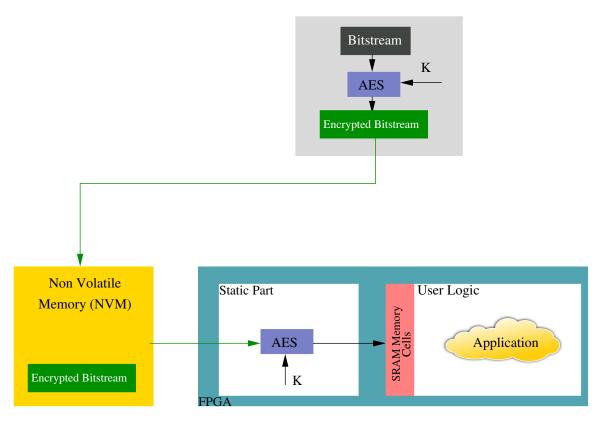

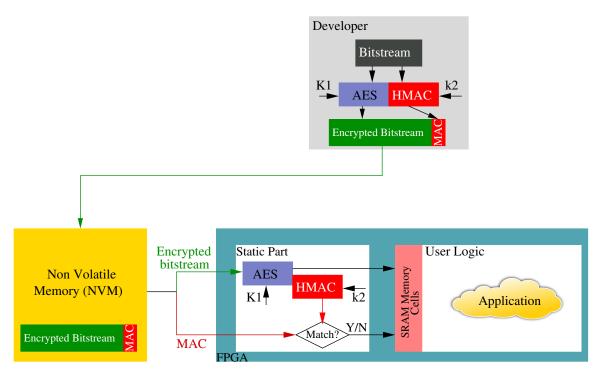

| 5.6  | Bitstream encryption                                        | 79  |

| 5.7  | Bitstream encryption and authentication in Virtex6          | 80  |

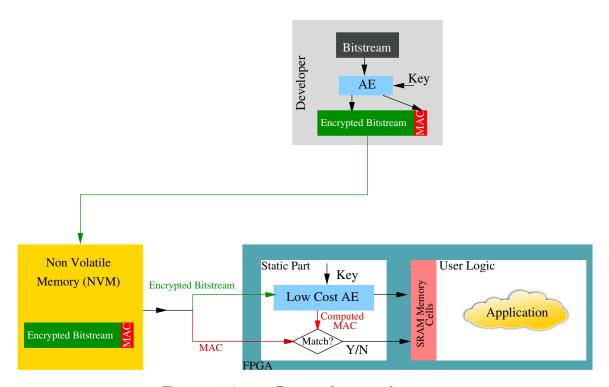

| 5.8  | our Proposed approach                                       | 83  |

| 5.9  | 1/4 round-based AES                                         | 84  |

| 5.10 | Proposed AES-CCM (encryption and authentication)            | 85  |

| 5.11 | Proposed AES-CCM (decryption and authentication)            | 86  |

| 5.12 | Proposed $GF(2^{128})$ multiplier                           | 88  |

| 5.13 | Proposed AES-GCM (encryption and authentication)            | 89  |

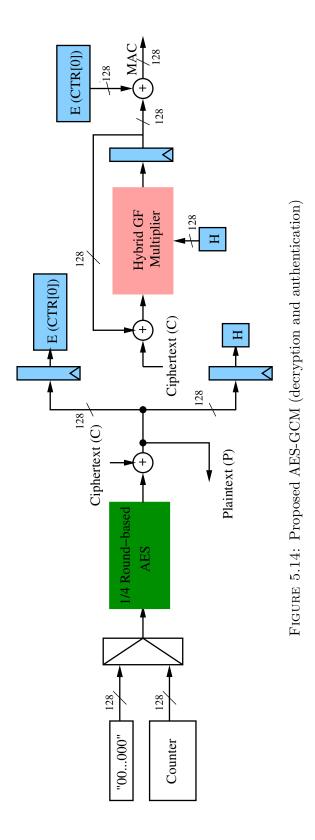

| 5.14 | Proposed AES-GCM (decryption and authentication)            | 91  |

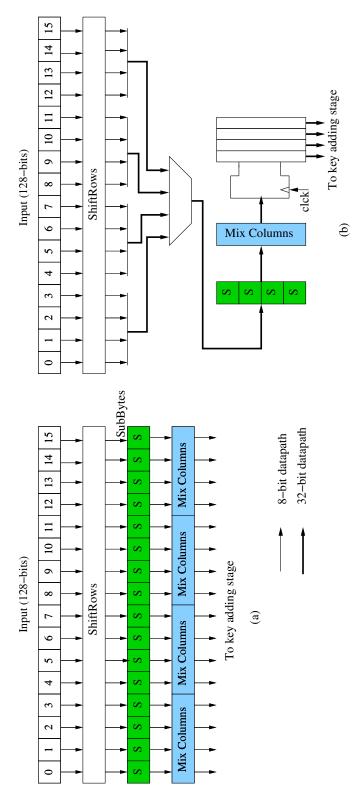

| 5.15 | (a) Full AES-round. (b) (1/4) AES-round                     | 93  |

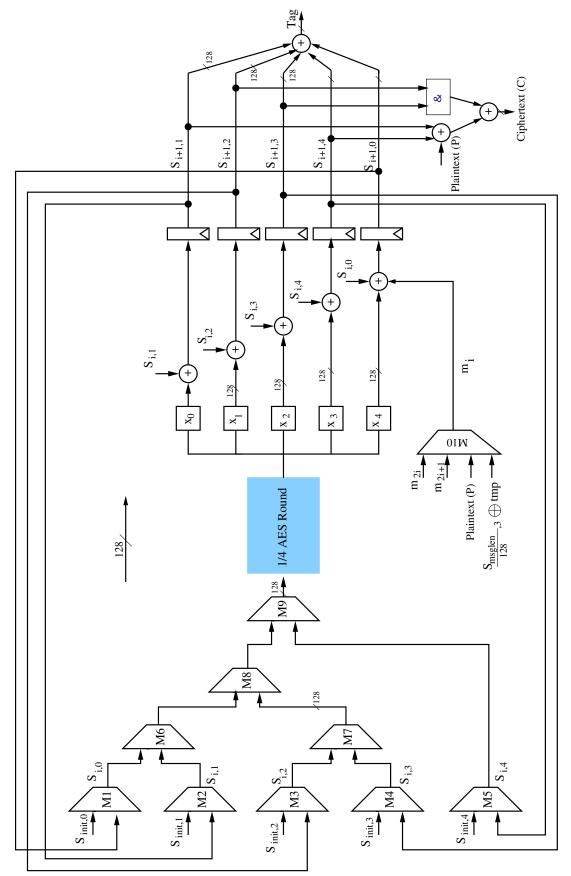

|      | Proposed AEGIS-128 architecture (encryption and authentica- |     |

|      | tion)                                                       | 95  |

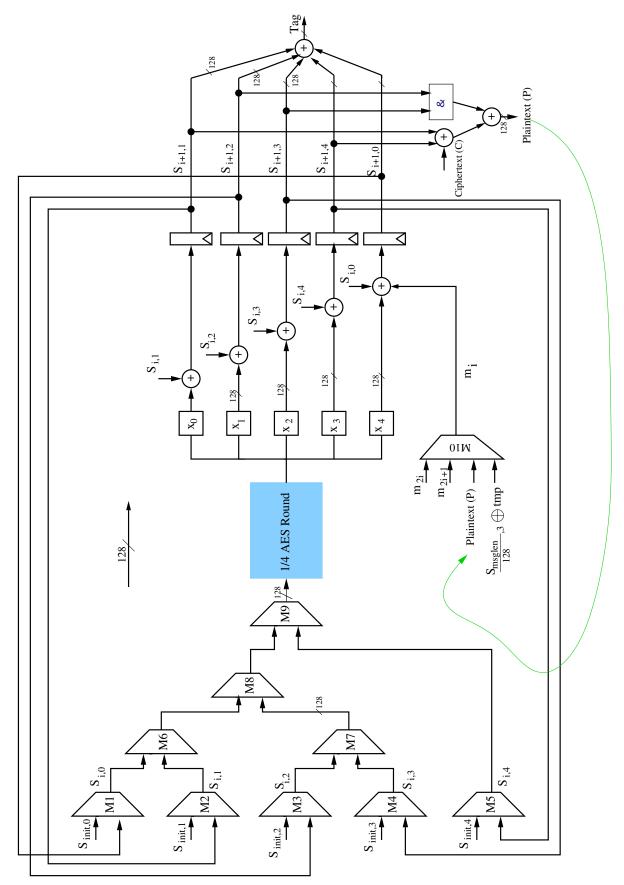

| 5.17 | Proposed AEGIS-128 architecture (decryption and authentica- |     |

|      | tion)                                                       | 96  |

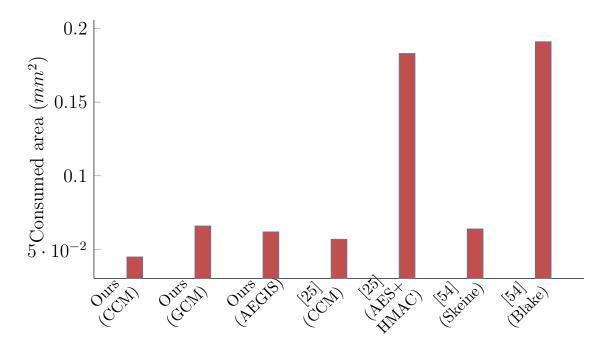

| 5.18 | Area Comparison using 90 nm technology                      | 100 |

# List of Tables

| 2.1 | Hardware comparison                                                | 19  |

|-----|--------------------------------------------------------------------|-----|

| 2.2 | Hardware comparison of the previous AES-CCM architectures          | 22  |

| 2.3 | Data flow control for GHASH calculation by [3]                     | 29  |

| 2.4 | Hardware comparison of the previous AES-GCM architectures on FPGAs | 31  |

| 3.1 | Precomputed round keys                                             | 39  |

| 3.2 | Hardware comparison                                                | 52  |

| 4.1 | Hardware comparison                                                | 67  |

| 5.1 | Hardware comparison                                                | 81  |

| 5.2 | Previous work summery                                              | 82  |

| 5.3 | Hardware comparison                                                | 98  |

| 5.4 | Configuration throughput of some FPGA family members               | 100 |

# Chapter 1

# Introduction

In this chapter, we introduce the overall motivation for this work and describe the contributions. Furthermore, we outline the principal organization of the core chapters.

### 1.1 Motivation

# 1.1.1 Authenticated Encryption

In our growing world of technology, the amount of information that we share with the rest of the digital universe is constantly increasing. Our demands to conceal confidential data are therefore being strongly needed and become very important. The protection of a message includes the protection of confidentiality and authenticity. There are two main approaches to authenticate and encrypt a message:

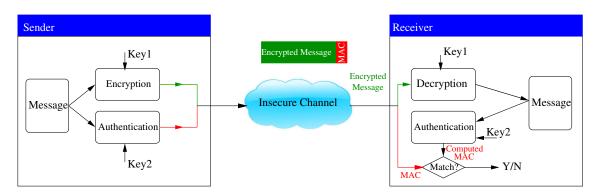

1. The first approach is to treat the encryption and the authentication separately. A block cipher or stream cipher is used to encrypt the plaintext, and a Message Authentication Code (MAC) is used to authenticate the

message as shown in Fig. 1.1. For example, we may use Advanced Encryption Standard (AES) [4] for encryption, and then apply Pelican Message Authentication Code (Pelican-MAC) [5] or Hash Message Authentication Code (HMAC) [6] to the message to generate the MAC. The encryption algorithm encrypts the message using a certain key (key1) to provide the encrypted message. The authentication algorithm generates the MAC using another key (key2) to provide the receiver with the entity of the sender (authentication). The receiver decrypts the encrypted message with the same key (key1) and authenticates the message (MAC computation) using key2 to compare it with the sent MAC in order to detect if they are equal or not.

FIGURE 1.1: Two separated algorithms for encryption and authentication

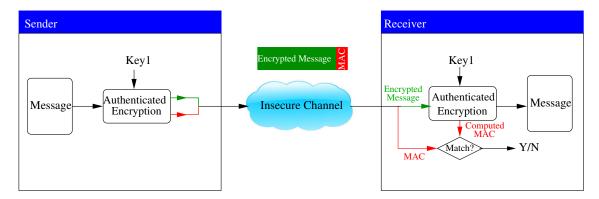

2. Another approach is to apply an integrated Authenticated Encryption (AE) algorithm to the message to provide both encryption and authentication. One can expect that this is more efficient since encryption and authentication can share a part of the computation. AE algorithms use only one key for encryption and authentication as shown in Fig. 1.2. Therefore, the key exchange and storage issues are better compared to using two separated algorithms.

AE has been used in many widely standards such as Secure Shell (SSH) [7], Secure Sockets Layer / Transport Layer Security (SSL/TLS) [8], IPsec [9], and IEEE 802.11 (Wi-Fi) [10]. This has made AE very important in protocols to secure the fundamentals of the information and communication infrastructure.

Figure 1.2: Authenticated encryption

There are now two NIST recommended modes of operation for authenticated encryption, namely, Counter with Cipher Block Chaining Mode (CCM) [11] and Galois Counter Mode (GCM) [12]. Quite some AE schemes have been proposed, and more are expected to join the ranks with the ongoing CAE-SAR<sup>1</sup>. The CAESAR competition is a move towards selecting a portfolio of AE schemes that should improve upon the state of the art. AEGIS [13] is considered one of the submitted proposals to CAESAR.

Software realizations of such algorithms have the advantage that they are portable to multiple platforms. In general, they have a fast time to market. However, they can be applied in systems with limited traffic at low encryption rates. Moreover, software-based applications are not power efficient compared to specialized hardware architectures. Speed and power are two major drawbacks that motivate the hardware design exploitation of cryptographic primitives.

#### 1.1.2 FPGAs

The increasing costs of silicon technology have put considerable pressure on developing dedicated SoC solutions. This means that the technology will be used increasingly for high-volume or specialist markets. Recently, Field Programmable Gate Arrays (FPGAs) have been proposed as a hardware technology for communication systems as they offer the capability to develop the

<sup>&</sup>lt;sup>1</sup>Competition for Authenticated Encryption: Security, Applicability, and Robustness.

most suitable circuit architecture of the application in a similar way to SoC systems. Compared to a full custom ASIC design, they are cost efficient, easier to manage and can immediately be put into operation. Furthermore, they can continuously be reprogrammed during and after the design.

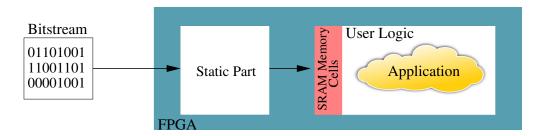

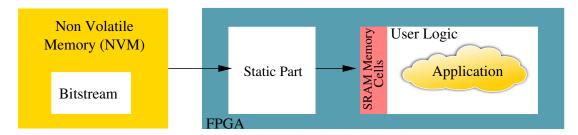

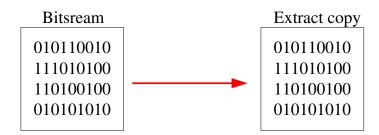

In order to redefine the functionality of the FPGA, a bitstream configuration file is uploaded on the FPGA. The reconfiguration includes downloading this bitstream file which contains the new design on the FPGA. As shown in Fig. 1.3, the bitstream is processed by the static part (configuration logic) which is not programmable. After that, the Static Random Access Memory (SRAM) is programmed by the processed bitstream. By programming SRAM cells, the functionality on the FPGA reconfigurable part (user part) can be tailored to implement the new design.

Figure 1.3: Reprogrammability using bitstream

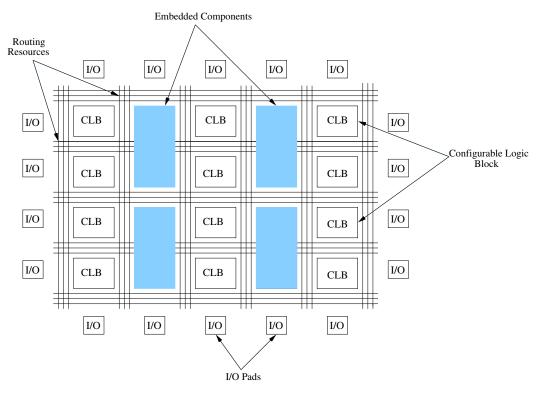

Configurable Logic Blocks (CLBs), interconnections, and embedded components (like Block Rams (BRAMs) and Digital Signal Processing (DSP) units) shown in Fig. 1.4 are established by programming SRAM cells to connect fabricated routing wires together.

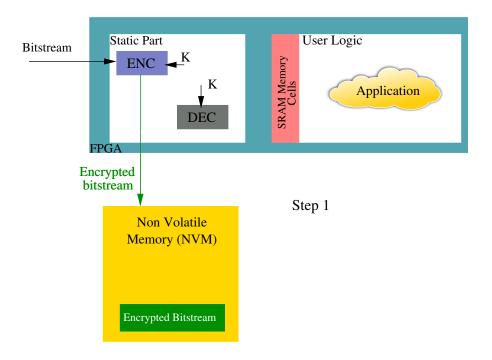

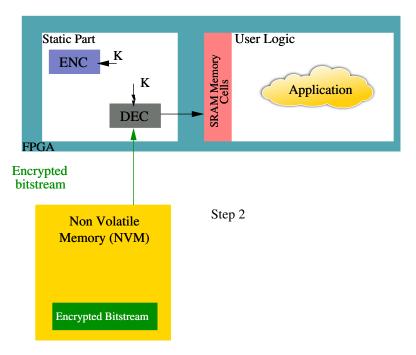

SRAM-based FPGAs such as those manufactured by Xilinx and Altera comprise the largest fraction of the overall market. Because SRAM memory is volatile, SRAM cells must be loaded with configuration data each time the device powers up. Configuration data is typically transmitted from an external memory source (Non Volatile Memory (NVM)) (see Fig. 1.5), such as a flash memory or a configuration device, to the FPGA.

In recent years, FPGAs manufacturers have come closer towards filling the performance gap between FPGAs and ASICs, enabling them, not only to serve as fast prototyping but also to become active players as components in

FIGURE 1.4: Reconfigurable part (user part) architecture

FIGURE 1.5: FPGA reconfiguration using NVM

embedded systems. As an example, Virtex-5 family [14] of FPGAs has 2400-25920 CLBs, 1152-11664 Kb BRAMs, 8-24 multi-Gigabit transceivers, 32-640 DSP slices, 4-12 digital clock managers, and 2-6 PLL clock generators. Thus, FPGAs are integral parts in embedded system design.

### 1.2 Contributions

This thesis deals principally with the design of efficient hardware implementations of cryptographic algorithms for encryption and authentication. We propose FPGA and application-specific ASIC implementations that target a wide range of different applications.

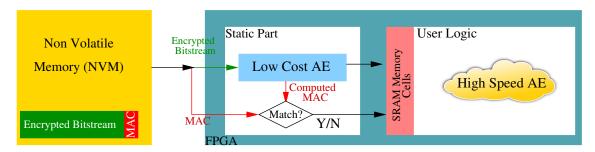

In particular, we focus on the hardware design of current AE algorithms. Fig. 1.6 shows the main contributions of this thesis. We investigate new efficient and high speed FPGA-based architectures of AE algorithms which will be in the user part (reconfigurable part) of the FPGA. Also, with the gathered knowledge, we define a framework to present different ranges of low cost ASIC architecture of AE algorithms which are inserted in the static part in order to protect the Intellectual Property (IP) of FPGA Bitstreams.

FIGURE 1.6: Thesis contribution

The contributions of this thesis can be summarized in the following points:

#### High speed AE for slow changing key applications on FPGAs

- Algorithms for authenticated encryption are the most suitable solution to reliably secure a network link. AES-GCM has been utilized in various security-constrained applications. VPNs are widely employed to connect private local area networks to remote locations. VPNs use AES-GCM for encryption and authentication. Current commercial security appliances of VPNs allow a throughput from 40 to 60 Gbps [15, 16]. We describe the benefits of VPNs as being a slow changing key environment in order to design efficient high speed architectures. In addition, we present a solution for the

parallelization of AES-GCM cores in order to support applications up to 100 Gbps. Moreover, we present a protocol to secure the reconfiguration of the proposed architectures on FPGAs.

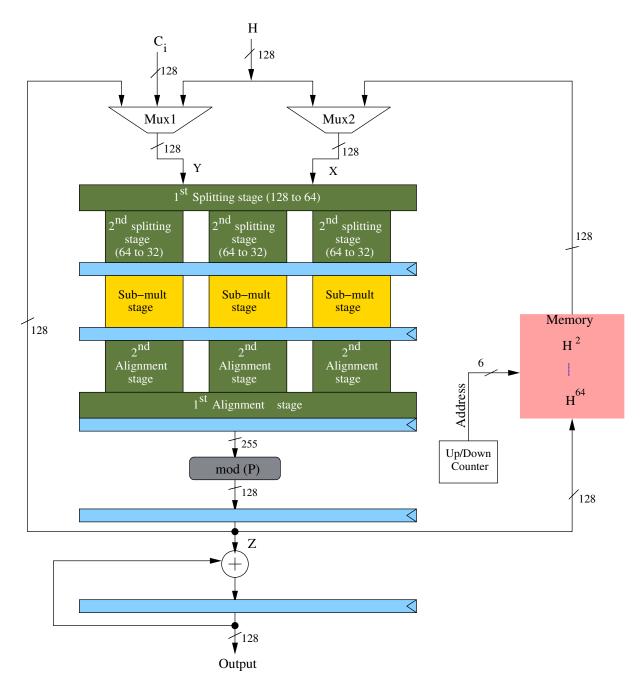

# • FPGA-based high performance AES-GCM using Efficient $GF(2^{128})$ multiplier

The performance of AES-GCM is always determined by the GF(2<sup>128</sup>) multiplier (authentication part) because of the inherent computation feedback. We introduce an efficient pipelined Karatsuba Ofman Algorithm (KOA) for the GF(2<sup>128</sup>) multiplier to support high speed applications. In particular, the computation feedback is removed by analyzing the complexity of the computation process. The proposed GF(2<sup>128</sup>) multiplier is evaluated with the pipelined AES in order to support high speed applications.

### • Efficient hardware implementation for AEGIS

- Pushed by our involvement into the hardware design of efficient AE algorithms, we decided to follow the CAESAR competition by designing high speed architecture of AEGIS which was accepted to the first round of the CAESAR competition.

All presented architectures in these contributions aim at applications with high demands for data throughput and performance. For these designs, we primarily employ Xilinx Virtex-4 and Virtex-5 FPGAs as an implementation target. Our proposed high speed architectures provide most savings in logic and routing resources with the highest data throughput on FPGAs compared to previous work reported in open literature.

### • Low cost solutions for IP protection of FPGA bitstreams

- IPs loaded on the FPGAs represent a kind of investment that requires protection especially in case of remote reconfiguration. Therefore, the FPGA must accept encrypted bitstreams from authorized entities. We present different low cost solutions for performing decryption and authentication of bitstreams. Efficient and compact ASIC AE architectures, AES-CCM, AES-GCM, and AEGIS, are added in the static part of the FPGA to support encrypted and authenticated bitstreams.

Presented ASIC architectures were evaluated by using 90 and 65 nm technologies. Our comparison to previous work reveals that our architectures are more area-efficient.

# 1.3 Thesis organization

The outline of this thesis is as follows:

- Chapter 2 gives detailed overview about current AE algorithms. AES-CCM, AES-GCM, and AEGIS are discussed in detail. Later in the chapter, we highlight the previous work that covers the hardware implementations of AE algorithms.

- Chapter 3 is entirely dedicated to high speed AES-GCM architectures for slow changing key applications like VPNs. It presents an efficient method for the parallelization of AES-GCM cores on FPGAs. Furthermore, we propose a protocol to protect the bitstream of the proposed architectures on FPGAs.

- Chapter 4 presents an efficient method for the  $GF(2^{128})$  multiplier used in AES-GCM. By focusing on the drawbacks of the previous architectures of  $GF(2^{128})$  multipliers, we propose an efficient method to remove the computation feedback in the  $GF(2^{128})$  multiplier. This is accomplished by the presented pipelined Karatsuba Ofman Algorithm (KOA)-based  $GF(2^{128})$ . Finally, an efficient high speed architecture of AEGIS is also presented in this chapter.

- Chapter 5 starts with an overview of security issues used in reconfiguration of FPGAs and analyze how well they are suited to IP protection of FPGA bitstreams. Later in this chapter, low cost implementations of AE algorithms are presented for FPGA bitstreams protection.

• Chapter 6 summarizes the thesis and points out some future work.

# Part I

# High Speed FPGA-based AE Architectures

# Chapter 2

# **Authenticated Encryption**

### 2.1 Introduction

Originally, confidentiality and authenticity services have been implemented separately, by using two different algorithms. Encryption algorithms are used to ensure confidentiality while Message Authentication Codes (MACs) can be used to provide authentication. When two separated algorithms are used to provide independent security services, it is considered cryptographically secure to use separated keys for each algorithm. Recently, techniques have been invented to combine encryption and authentication into a single algorithm which is called Authenticated Encryption (AE). Combining these two security services in hardware might support the following advantages:

• Area requirement for a single algorithm could be smaller compared to two separated algorithms because encryption and authentication can share a part of the computation.  A slight advantage regarding key management and key storage issues because AE needs only a single key for both encryption and authentication.

The following is a brief overview of the most popular AE algorithms that have been developed as a result of the current research. The aim is to provide the details of AE algorithms to allow the reader to understand and analyze each algorithm. Also, for each algorithm, we present the previous work in terms of the hardware implementation in order to highlight the current challenges of the state of the art.

The most common way of constructing an AE scheme is a mode of operation for a block cipher, like AES [4]. Therefore, in order to discuss AE algorithms clearly, it is useful to highlight AES because it is common in all AE schemes that we will present.

# 2.2 Advanced Encryption Standard (AES)

For the drawbacks of the previous symmetric-key cryptographic standards such as the DES and the 3DES, they have been replaced by the Advanced Encryption Standard (AES) [4]. In particular, the AES has overcome the drawbacks of the previous standards in terms of vulnerability to brute force attacks and slow software implementations. The AES was accepted by the National Institute of Standards and Technology (NIST) in 2001 and since its acceptance, it has been utilized in a variety of security-constrained applications like IEEE 802.11i standard [17]. It is considered by industry and government environments as the essential scheme to protect sensitive information.

# 2.2.1 Algorithm specifications

The AES algorithm is a symmetric-key cipher, in which both the sender and the receiver use a single key for encryption and decryption. The data block length is fixed to be 128 bits, while the key length can be 128, 192, or 256

bits. It is an iterative algorithm. Each iteration can be called a round, and the total number of rounds, N, is 10, 12, or 14, when the key length is 128, 192, or 256 bits, respectively.

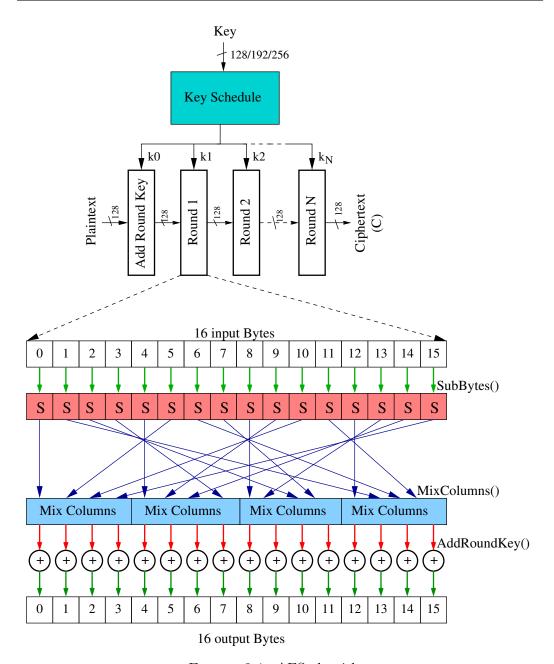

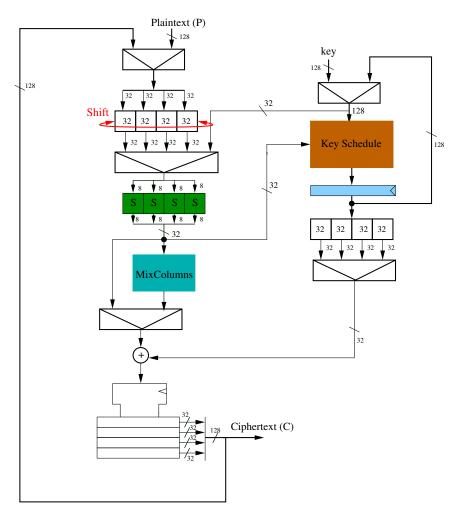

The 128-bit data block is divided into 16 bytes. These bytes are mapped to a  $4 \times 4$  array called the State, and all the internal operations of the AES algorithm are performed on the State. Each byte in the State is detonated by  $S_{(i,j)}$  ( $0 \le i \le 3, 0 \le j \le 3$ ) and is considered as an element of  $GF(2^8)$  with  $P(x) = x^8 + x^4 + x^3 + x + 1$  as an irreducible polynomial. Fig. 2.1 shows the block diagram of the AES algorithm.

In the encryption of the AES algorithm, each round except the final round consists of four transformations in a fixed order:

1. **SubBytes** is a non-linear transformation that substitutes the bytes of the state independently, using a s-box built over two steps: computation of the multiplicative inverse in the Galois field  $GF(2^8)$  followed by an affine transformation in GF(2). The SubBytes can be described as follows:

$$S(i,j) = MS_{i,j}^{-1} + C (2.1)$$

where M is an  $8 \times 8$  binary matrix,  $S^{-1}$  is the multiplicative inverse of the input, and C is an 8-bit binary vector with only 4 nonzero bits.

- 2. **ShiftRows** is a simple shifting transformation. The first row of the State does not change, while the second, third and fourth rows cyclically shift one byte, two bytes and three bytes to the left, respectively

- 3. **MixColumns** multiplies in  $GF(2^8)$  each column of the of the State (4 bytes) with a(x) modulo  $x^4 + 1$  where

$$a(x) = 03x^3 + 01x^2 + 01x + 02. (2.2)$$

4. AddRoundKey adds a round key to the state in GF(2).

FIGURE 2.1: AES algorithm

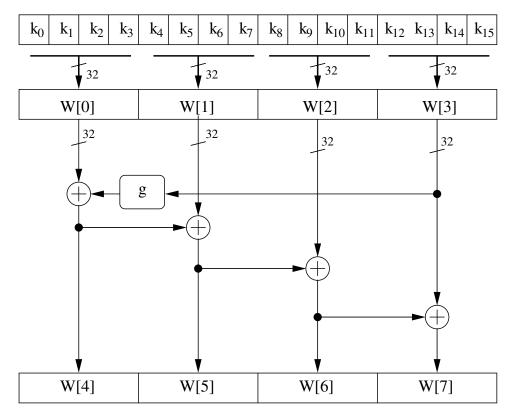

The AES round is completed with the key expansion (see Fig. 2.2), which generates the round keys from the original key. This expansion is defined on 4-bytes words and mainly uses the transformations of the round. A single round key is made up by four words and is updated to the next round key using **g** function which combines the SubWord (s-box over a 4-byte input) and RotWord (word shift) functions. The rest of the key parts are generated using XOR function.

Figure 2.2: Key expansion of AES-128

The transformations in the decryption process perform the inverse of the corresponding transformations in the encryption process.

1. **InvSubBytes** performs the inverse of the SubBytes stage as follows:

$$S(i,j) = (MS_{i,j}^{-1} + C)^{-1}.$$

(2.3)

- 2. **InvShiftRows** does not change the first row, while the rest of the rows are cyclically shifted to the right by the same offset as that in the ShiftRows.

- 3. **InvMixColumns** multiplies the polynomial formed by each column of the State with  $a(x)^{-1}$  modulo  $x^4 + 1$ , where

$$a(x) = 0bx^3 + 0dx^2 + 09x + 0e. (2.4)$$

4. AddRoundKey adds a round key to the state in GF(2), while the round keys are computed in the reverse order within the key expansion process.

### 2.2.2 Hardware implementation

After the standardization of AES, several research contributions focusing on hardware implementations of the algorithm have been presented. Nowadays, almost each possible AES architecture, covering the entire design space (both in ASIC and FPGA), has been investigated. Companies and federal organizations have plenty of choice in selecting the suitable design.

We list the major components and strategies that characterize the AES hardware design:

- Datapath: AES is defined by 128-bit state with 8-bit operations. As a result, the designer has the choice to adapt or shrink the datapath of his architecture according to the system specification. Typical datapath widths are 128, 64, 32, 16, or 8 bits. The datapath size affects directly the area occupation and the final throughput of the AES core. It represents a sort of area/speed trade-off. In [18], the authors analyze different-datapath implementations on FPGAs.

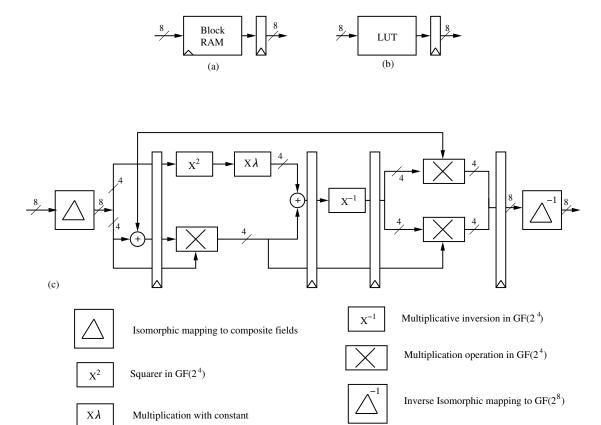

- Round components: The SubBytes transformation is the most costly (both in size and propagation delay) component of the AES round. In terms of the ShiftRows operation, it does not consume any logic because it is implemented as a straightforward routing of the signals without any specific hardware component, while the most efficient strategy to realize MixColumns is with the combinational logic as shown in [19]. Several approaches to design the SubBytes have been developed and implemented. We describe briefly three main solutions:

#### 1. Block Random Access Memory (BRAMs)

The s-box is implemented as a Look Up Table (LUT) and stored in a dedicated memory. This approach is particularly suitable for

modern FPGAs, which contain BRAMs. This approach saves the logic area because the most consuming part (s-boxes) are implemented as BRAMs (see [20])

#### 2. Composite field

In [21], composite field arithmetic is employed to reduce the area requirements, and different implementations for the inversion in subfield  $GF(2^4)$  are compared. This reduction to composite fields brings significant improvement in flexibility and in the area costs of SubBytes.

### 3. FPGA LUT

The third approach is dedicated only to FPGA devices. The s-box can be directly instantiated in LUTs located in the FPGA logic elements. As example, the basic logic elements of Xilinx FPGAs are called slices and each slice comprises a different number of LUTs depending on the selected device. In a Xilinx Virtex-5 chip a single s-box is implemented on 32 6-input LUTs because of 6-input LUT technology (see [22]).

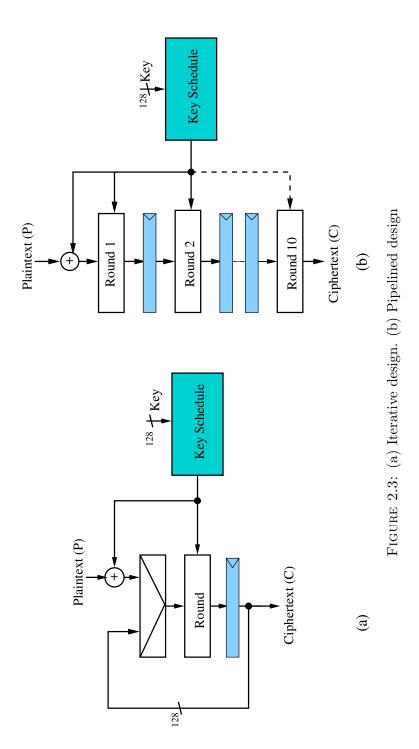

• Rolled or unrolled: The operation mode of AES influences remarkably the performance of the implementation. Feedback modes like Cipher Block Chaining (CBC) mode [23] lead to iterative designs, where single round is considered to be the most efficient solution. Fig. 2.3(a) shows the iterative design using only one round. An example of the iterative design is shown in [22]. Because of using only one round, the throughput of the iterative design of AES-128 presented by [22] is as follows:

$$Throughput(Mbps) = \frac{F_{max}(Mhz) \times 128}{10}.$$

(2.5)

Full unrolled architectures combined with pipelining (Fig. 2.3(b)) can be exploited only by the feedback-free modes [23] like Electronic Codebook (ECB) and Counter (CTR) mode. Unrolled designs with pipelining are able to achieve 20-30 Gbps, simply by putting a pipeline stage between the rounds. To further increase the speed, pipelining can also be implemented inside the round and the SubBytes operation (see [18]). The throughput of the pipelined design is calculated as follows:

$$Throughput(Mbps) = F_{max}(Mhz) \times 128.$$

(2.6)

Table 2.1 shows the hardware hardware comparison between the iterative design and the pipleined design. It is clear that the pipelined design consumes more area compared to the iterative design, while the speed is higher.

Throughput Design **FPGA** Area (slices) Frequency GbpsMhz Iterative [22] Vertex-E 2257 169 2.1Pipelined [18] Spartan-III 17425 196.1 25.1

Table 2.1: Hardware comparison

After giving an overview of AES, the following sections present the current AE algorithms and how they are implemented on FPGAs and ASIC.

### 2.3 AES-CCM

Counter with Cipher Block Chaining Mode (CCM) [24] can be used in conjunction with any approved 128-bit block cipher like AES. CCM has been specified in the draft IEEE 802.11i standard for wireless networks. It has also been specified in IEEE 802.15 (Wireless Personal Area Networks) and 802.16 (Broadband Wireless Metropolitan Area Networks) standards. It is designed for packet environment, where all the data is available in storage before the processing. This implies that it is not online.

### 2.3.1 Algorithm specifications

#### Variables:

N: 128-bit Valid nonce

A: 128-bit Associated data

P: 128-bit Plaintext C: 128-bit Ciphertext

MAC: 128-bit Message Authentication Code

L : Message length Key:128-bit Key

#### **Specifications:**

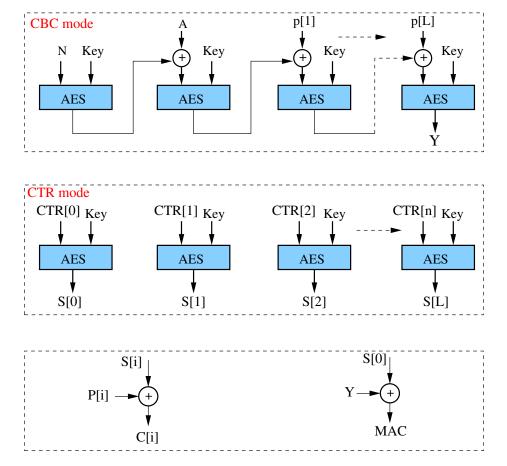

AES-CCM has four inputs: an AES key, N, P, and A. AES-CCM generates two outputs: C and MAC. N and A are used to verify the correctness of the MAC. Fig. 2.4 shows the block diagram of CCM. It depends on the block cipher AES in two modes. Cipher Block Chaining (CBC) mode for the authentication, while the encryption is performed by Counter (CTR) mode. A and N are not encrypted but they are authenticated in order to verify the correctness of authentication.

#### Encryption and MAC generation:

- 1. The plaintext P is stored in a memory.

- 2. N, A, and P are loaded to AES in CBC mode to generate Y, this value is used for authentication.

- 3. The first value of the counter is encrypted (CTR mode) to be S[0] which is mixed with Y through XOR operation in order to generate the final MAC.

- 4. Encryption is performed by CTR mode.

#### Decryption and MAC verification:

- 1. Decryption is performed by XORing C[i] with the values of the encrypted counter S[i] to give P.

- 2. N, A, and P are loaded to AES in CBC mode to generate Y.

- 3. Y is XORed with S[0] to generate the MAC.

- 4. MAC verification is computed.

FIGURE 2.4: AES-CCM

## 2.3.2 Hardware implementation

There are some research contributions focusing on the hardware implementations of AES-CCM on FPGAs and ASIC. Because of being feedback-based algorithm (it depends on CBC mode), iterative design of AES is always used in the hardware implementation.

In [25], iterative AES (one round) was used to implement the architecture of AES-CCM on FPGAs and ASIC. The proposed architecture in [25] used one AES block for doing both authentication and encryption. This manner decreases the consumed area because there is only one AES architecture that is used for the two modes, CBC and CTR modes. As a result the speed of the architecture is reduced by 2 compared to the use of two AES architectures. Two

iterative components of AES were implemented for both encryption and authentication on FPGAs in [26]. In [27], FPGA-based AES-CCM was presented by using two blocks of AES and they are 32-based datapath architectures.

From the previous discussion, it is clear that AES-CCM is a feedback-based algorithm because it depends on the CBC mode in terms of performing the authentication task. Therefore, only iterative-based designs of AES are applicable to CCM, while using pipelined designs is not. As a result, the overall speed is limited as shown in Table 2.2.

| Design         | Implementation | Area                   | Frequency | Throughput |

|----------------|----------------|------------------------|-----------|------------|

|                | platform       |                        | Mhz       | Mbps       |

| $\boxed{[25]}$ | 90 nm          | $0.057 \ mm^2$         | 148       | 434        |

| [26]           | Spartan-3      | 633 slices             | 100.08    | 1051.5     |

|                | (90  nm)       |                        |           |            |

| [27]           | Spartan-3      | 487  slices + 4  BRAMs | 247       | 687.3      |

|                | (90  nm)       |                        |           |            |

Table 2.2: Hardware comparison of the previous AES-CCM architectures

### 2.4 AES-GCM

Galois Counter Mode (GCM) [28] is an AE algorithm. It is well-suited for wireless, optical, and magnetic recording systems due to its multi-Gbps authenticated encryption speed, outstanding performance, minimal computational latency as well as high intrinsic degree of pipelining and parallelism. New communication standards like IEEE 802.1ae [29] and NIST 800-38D have considered employing GCM to enhance their performance.

It simultaneously provides confidentiality, integrity and authenticity assurances on the data. It can be implemented in hardware to achieve high speeds with low cost and low latency. It was designed to meet the need for an authenticated encryption mode that can efficiently achieve speeds of 10 Gbps and higher in hardware.

### 2.4.1 Algorithm specifications

### **Operations:**

The following operations are used in AES-GCM:

$\oplus$ : bit-wise exclusive OR

: concatenation

#### Variables:

IV: 96-bit Initialization Vector

A: 128-bit Associated data

P: 128-bit Plaintext

C: 128-bit Ciphertext

L: Message length

MAC: Message Authentication Code

Key:128-bit Key

#### **Specifications:**

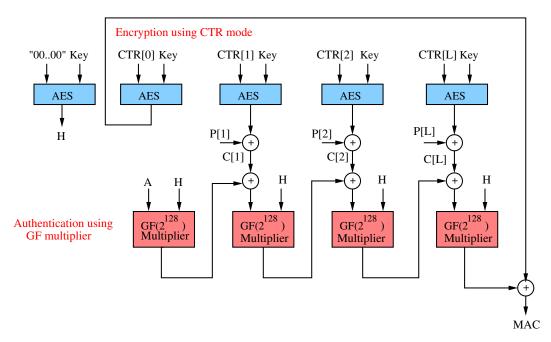

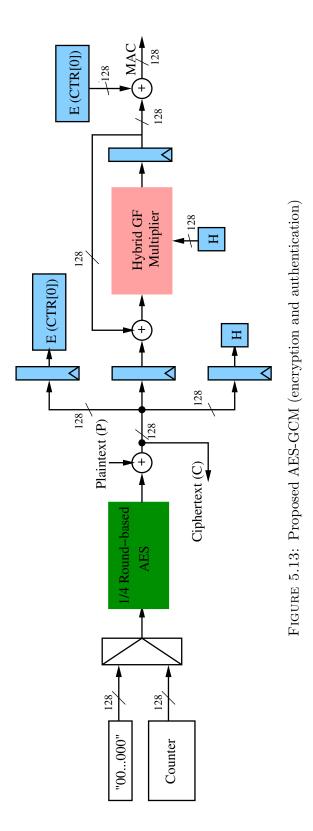

AES-GCM accepts four inputs: an AES key, IV, P, and A. AES-GCM generates two outputs: C and MAC. A is used to verify the correctness of the MAC. Fig. 2.5 shows the block diagram of AES-GCM. It contains an AES engine in CTR mode for encryption, while the authentication is performed by the Galois Hash (GHASH) which is composed of chained GF(2<sup>128</sup>) multipliers.

### Encryption and MAC generation:

1. Generation of H by encrypting  $0^{128}$  block

$$H = E(Key, 0^{128}). (2.7)$$

2. Assigning the first value of the counter (CTR[0]) as follows:

FIGURE 2.5: AES-GCM

$$CTR[0] = \begin{cases} IV \parallel 0^{31}1 & If(length(IV) = 96) \\ H \times IV & otherwise \end{cases}$$

where the multiplication between H and IV is a  $GF(2^{128})$ -based multiplication.

- 3. Encryption is performed by AES in CTR mode.

- 4. Authentication is computed by the  $GF(2^{128})$  multipliers chain and the output is XORed with the encrypted value of CTR[0] in order to obtain the final MAC.

### Decryption and MAC verification:

- 1. Generation of H by encrypting  $0^{128}$  block (Equation 2.7).

- 2. Assigning the first counter value (step 2 in encryption stage)

- 3. Decryption is performed by XORing the encrypted values of the counter with C to obtain P.

4. MAC verification is accomplished by the same scenario of the encryption process.

#### 2.4.2 Hardware implementation

As we presented before, two main components in AES-GCM are an AES engine and a  $GF(2^{128})$  multiplier. Also, the main goal of AES-GCM is to support high speed applications (10 Gbps and higher in hardware). Therefore, most of the previous hardware architectures were proposed to support high speed applications. As a result, the pipelined AES (pipelined AES implementation has been discussed in Section 2.1) is used to perform the encryption task of AES-GCM [3, 30, 31]. The second important part of AES-GCM is the GHASH which depends on the inherent feedback operations chain of the  $GF(2^{128})$  multipliers. Therefore, the system performance is always determined by the  $GF(2^{128})$  multiplier.

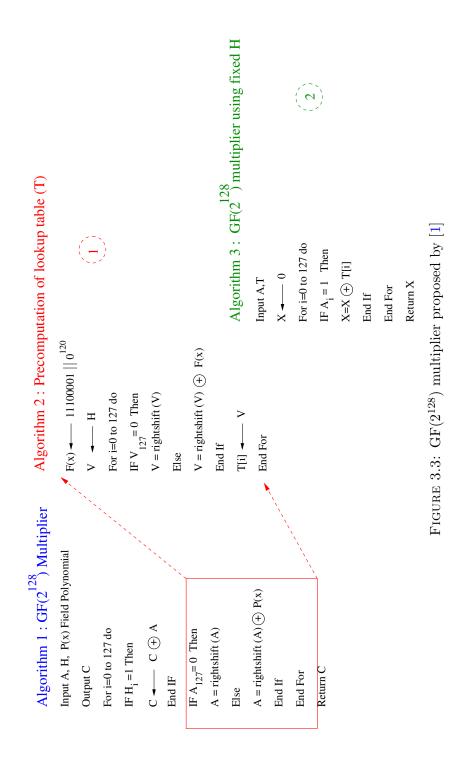

The  $GF(2^{128})$  multiplier uses irreducible polynomial  $P(x) = x^{128} + x^7 + x^2 + x + 1$  to compute the multiplication between A and H as shown in **Algorithm** 1.

#### Algorithm 1 $GF(2^{128})$ multiplier

```

1: Input A, H \in GF(2^{128}), P(x) Field Polynomial

2: Output X

3: X=0

4: for i = 0 to 127 do

if A_i = 1 then

5:

X \longleftarrow X \oplus H

6:

end if

7:

if H_{127} = 0 then

8:

H \longleftarrow rightshift(H)

9:

10:

H \longleftarrow rightshift(H) \oplus P(x)

11:

end if

12:

13: end for

14: Return X

```

In [32], [33], and [34], the multiplication was performed using bit-parallel, digit-serial, and hybrid multipliers. Supporting high speed applications motivates using the parallel version which performs the multiplication in only one

clock cycle. In **Algorithm 1**, if H is fixed, the multiplier is called a fixed operand  $GF(2^{128})$  multiplier as shown by [1]. This design proposed by [1] can be used efficiently (smaller area) on FPGAs as the circuit is specialized for H. The drawback in [1] is the need for a new reconfiguration in case of changing the key.

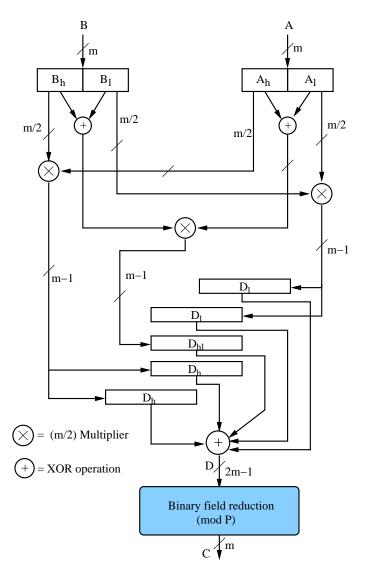

Karatsuba Ofman Algorithm (KOA) [35] is used to reduce the complexity (consumed area) of the  $GF(2^{128})$  multiplier. More precisely, the single step KOA algorithm splits two m bit inputs A and B into four terms  $A_h$ ,  $A_l$ ,  $B_h$ ,  $B_l$  which are m/2 bit terms. The 1-step iteration of KOA shown in Fig. 2.6 can be described as:

$$\begin{cases}

D_l = A_l \times B_l \\

D_{hl} = (A_h \oplus A_l) \times (B_h \oplus B_l) \\

D_h = A_h \times B_h \\

D = D_h X^m \oplus X^{m/2} (D_h \oplus D_{hl} \oplus D_l) \oplus D_l.

\end{cases} (2.8)$$

After the multiplication stage is processed using KOA, the binary field reduction step is used to convert the length of the vector from 2m-1 to m as shown in Equation 2.9.

$$C(x) = D \mod P(x) \tag{2.9}$$

where P(x) is the field polynomial used for the multiplication operation.

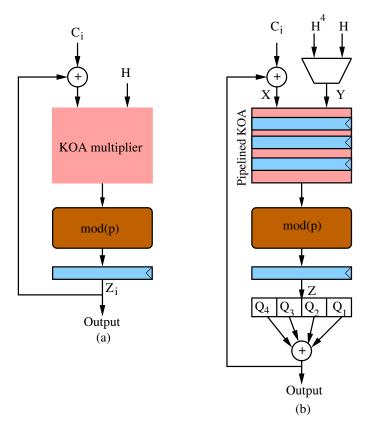

KOA was used by [30] to reduce the complexity (consumed area) of the  $GF(2^{128})$  multiplier as shown in Fig. 2.7(a). Because the GHASH is a chain of the  $GF(2^{128})$  multipliers, the GHASH output (Fig. 2.7(a)) is calculated as follows:

$$Output = (C_i \oplus Z_{i-1}) \times H. \tag{2.10}$$

The drawback of the architecture presented in [30] is the critical delay resulting from the multiplication stage. In order to reduce the data path (critical delay)

Figure 2.6: Polynomial Multiplication using KOA

of the KOA multiplier, pipelining concept was accomplished by [3] as shown in Fig. 2.7(b). Equation 2.10 was written by [3] as follows:

$$Output = Q_1 \oplus Q_2 \oplus Q_3 \oplus Q_4, where \tag{2.11}$$

$$Q1 = (((C_1 \times H^4 \oplus C_5) \times H^4 \oplus C_9) \times H^4 \oplus ....) \times H^4$$

(2.12)

$$Q2 = (((C_2 \times H^4 \oplus C_6) \times H^4 \oplus C_{10}) \times H^4 \oplus ....) \times H^3$$

(2.13)

FIGURE 2.7: (a) KOA based GHAH. (b) Pipelined KOA based GHASH

$$Q3 = (((C_3 \times H^4 \oplus C_7) \times H^4 \oplus C_{11}) \times H^4 \oplus ....) \times H^2$$

(2.14)

$$Q4 = (((C_4 \times H^4 \oplus C_8) \times H^4 \oplus C_{12}) \times H^4 \oplus ....) \times H.$$

(2.15)

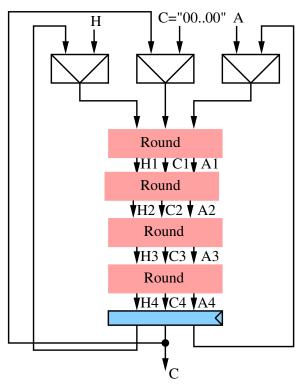

The hardware architecture proposed by [3] (Fig. 2.7(b)) is a 4-stage pipelined KOA-based GHASH. An example of data flow control for the GHASH is shown in Table 2.3, where C1 ....  $C_8$  is the input sequence and "-" denotes "don't care". At the beginning,  $H^4$  is passed to port Y. After the input of  $C_6$ , H is passed to port Y. The partial GHASH values  $Q_1$ ,  $Q_2$ ,  $Q_3$ , and  $Q_4$  are ready at the  $9^{th}$ ,  $15^{th}$ ,  $18^{th}$ , and  $12^{th}$  clock, respectively. As shown from Table 2.3, the multiplier output resulting from 8 frames of 128-bit is ready after 19 clock cycles. Therefore, the real throughput is calculated as follows:

| Clock | $C_i$ | X                                          | Y     | Z                                          | Comment   |

|-------|-------|--------------------------------------------|-------|--------------------------------------------|-----------|

| 1     | $C_1$ | $C_1$                                      | $H^4$ | 0                                          |           |

| 2     | $C_2$ | $C_2$                                      | $H^4$ | 0                                          |           |

| 3     | $C_3$ | $C_3$                                      | $H^4$ | 0                                          |           |

| 4     | $C_4$ | $C_4$                                      | $H^4$ | 0                                          |           |

| 5     | $C_5$ | $(C_1 	imes H^4) \oplus C_5$               | $H^4$ | $C_1 \times H^4$                           |           |

| 6     | $C_6$ | $(C_2 \times H^4) \oplus C_6$              | H     | $C_2 \times H^4$                           |           |

| 7     | $C_7$ | $(C_3 	imes H^4) \oplus C_7$               | H     | $C_3 \times H^4$                           |           |

| 8     | $C_8$ | $(C_4 \times H^4) \oplus C_8$              | H     | $C_4 \times H^4$                           |           |

| 9     | -     | -                                          | _     | $((C_1 \times H^4) \oplus C_5)H^4$         | $z = Q_1$ |

| 10    | 0     | $((C_2 \times H^4) \oplus C_6) \times H$   | H     | $((C_2 \times H^4) \oplus C_6) \times H$   |           |

| 11    | 0     | $((C_3 \times H^4) \oplus C_7) \times H$   | H     | $((C_3 \times H^4) \oplus C_7) \times H$   |           |

| 12    | 0     | -                                          | _     | $((C_4 \times H^4) \oplus C_8) \times H$   | $z = Q_4$ |

| 13    | 0     | -                                          | _     | -                                          |           |

| 14    | 0     | $((C_2 \times H^4) \oplus C_6) \times H^2$ | H     | $((C_2 \times H^4) \oplus C_6) \times H^2$ |           |

| 15    | -     | -                                          | _     | $((C_3 \times H^4) \oplus C_7) \times H^2$ | $z = Q_2$ |

| 16    | -     | -                                          | _     | -                                          |           |

| 17    | _     | -                                          | _     | -                                          |           |

| 18    | -     | -                                          | _     | $((C_2 \times H^4) \oplus C_6) \times H^3$ | $z = Q_3$ |

| 19    | -     | -                                          | _     | -                                          | GHASH     |

Table 2.3: Data flow control for GHASH calculation by [3]

$$Throughput(Mbps) = F_{max(MHz)} \times 128 \times (\frac{8}{19}). \tag{2.16}$$

The last component of Equation 2.16 is  $(\frac{8}{19})$ , it is called the reduction factor and the authors of [3] neglected this component in their throughput calculation. Therefore, their presented design of GHASH has not increased the throughput as they claimed.

Henzen et al. [31] proposed 4-parallel AES-GCM using pipelined KOA. Their design achieved the authentication of 18 frames of 128-bits in 11 clock cycles because of the latency resulting from the pipelined KOA. As a result, their throughput is calculated as follows:

$$Throughput(Mbps) = F_{max(MHz)} \times 128 \times \frac{18}{11}.$$

(2.17)

The authors of [31] neglected this component  $(\frac{18}{11})$  in their throughput calculation and replaced it by 4. Hence, their presented parallel design of GHASH has not increased the throughput by 4 as shown in Equation 2.17.

Table 2.4 shows the hardware comparison of the current AES-GCM cores on FPGAs. It is clear that the maximum throughput resulting from implementing single AES-GCM core on FPGAs (Virtex-5) is 17.9 Gbps with 4628 slices ([3]). In terms of the parallel cores, the maximum throughput is 48.8 Gbps ([31]).

#### 2.5 AEGIS

The field of AE has received more interest in the light of the recently announced CAESAR (Competition for Authenticated Encryption: Security, Applicability, and Robustness). CAESAR will define a portfolio of AE algorithms that offer advantages over AES-GCM. Secure and efficient algorithms for specific or possibly multiple environments will be presented.

There are some AE schemes have been proposed, and more are expected to join the ranks with the ongoing CAESAR. In this section, we present an overview on AEGIS [36] which is considered one of the candidates to CAESAR. It is constructed from the AES encryption round function (not the last round). AEGIS is a stream cipher with a large state which is updated continuously. Therefore, the attacks against a block cipher cannot be applied directly to it. The goal of AEGIS is to achieve high performance and strong security as outlined in [36]. AEGIS-128 processes a 16-byte message block with five AES-round functions, and AEGIS-256 uses 6 AES round functions. More precisely, we will highlight AEGIS-128 because the thesis concentrates on 128-based AE algorithms.

#### 2.5.1 Algorithm specifications

#### **Operations:**

$\oplus$  : bit-wise exclusive OR

& : bit-wise AND

| : concatenation

#### Variables and constants:

TABLE 2.4: Hardware comparison of the previous AES-GCM architectures on FPGAs

|                         |           | <b>T</b>           |             |                          |         |          | 1     |            |

|-------------------------|-----------|--------------------|-------------|--------------------------|---------|----------|-------|------------|

|                         | FPGA type | Design             | SubBytes    | SubBytes   Area (slices) | m BRAMs | Max-Fred |       | Thr./Slice |

|                         |           |                    |             |                          |         | m MHz    | _     | Mbps/Slice |

| 3                       | Virtex4   | AES-GCM            | BRAM        | 7712                     | 82      | 285      | 15.4  | 1.99       |

| $\overline{\mathbb{S}}$ | Virtex4   | AES-GCM            | Comp.       | 14349                    | 0       | 277      | 14.9  | 1.04       |

| 3                       | Virtex5   | AES-GCM            | BRAM        | 3533                     | 41      | 314      | 16.9  | 4.78       |

| $^{\circ}$              | Virtex5   | AES-GCM            | Comp        | 6492                     | 0       | 314      | 16.9  | 2.60       |

| 3                       | Virtex5   | AES-GCM            | $_{ m TUT}$ | 4628                     | 0       | 324      | 17.5  | 3.77       |

| [32]                    | Virtex4   | AES-GCM            | BRAM        | 13200                    | 114     | 110      | 14    | 1.07       |

| [32]                    | Virtex4   | AES-GCM            | Comp.       | 21600                    | 0       | 06       | 11.52 | 0.53       |

| [31]                    | Virtex5   | 4-parallel AES-GCM | BRAM        | 9561                     | 450     | 233      | 48.8  | 5.1        |

| [31]                    | Virtex5   | 4-parallel AES-GCM | Comp        | 18505                    | 0       | 233      | 48.8  | 2.64       |

| [31]                    | Virtex5   | 4-parallel AES-GCM | LUT         | 14799                    | 0       | 233      | 48.8  | 3.29       |

The following variables and constants are used in AEGIS-128:

$IV_{128}$ : The 128-bit initialization vector

$\begin{array}{lll} \mathbf{P} & : & 128\text{-bit plaintext} \\ \mathbf{C} & : & 128\text{-bit ciphertext} \\ m_i & : & 128\text{-bit data block} \end{array}$

const0 : The first 16 bytes of const const1 : The second 16 bytes of const

$K_{128}$  : The 128-bit key

msglen : The bit length of the plaintext

AEGIS depends on the **AESRound** (**A,B**), where A is the 16-byte state, B is the 16-byte round key. It is performed using the AES round functions (ShiftRows, SubBytes, MixColumns, and AddRoundKey). With a 128-bit key and a 128-bit initialization vector, AEGIS-128 encrypts and authenticates a message with length less than 2<sup>64</sup> bits. The authentication MAC length is less than or equal to 128 bits. It is strongly recommend the use of a 128-bit MAC.

#### The state update function of AEGIS-128:

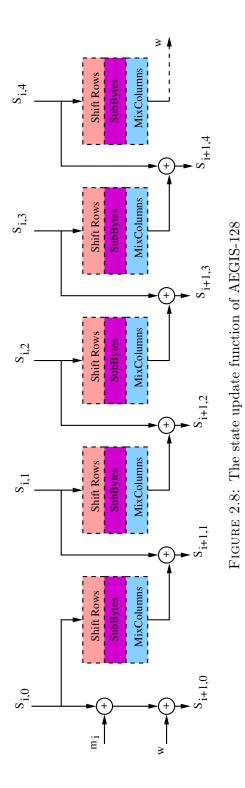

The state update function shown in Fig. 2.8 updates the 80-byte state  $S_i$  with a 16-byte message block  $m_i$ .

$S_{i+1} = StateUpdate128(S_i, m_i)$  is given as follows:

$$S_{i+1,0} = AESRound(S_{i,4}, S_{i,0} \oplus m_i)$$

$$S_{i+1,1} = AESRound(S_{i,0}, S_{i,1})$$

$$S_{i+1,2} = AESRound(S_{i,1}, S_{i,2})$$

$$S_{i+1,3} = AESRound(S_{i,2}, S_{i,3})$$

$$S_{i+1,4} = AESRound(S_{i,3}, S_{i,4}).$$

(2.18)

#### The initialization of AEGIS-128:

The initialization of AEGIS-128 consists of loading the key and IV into the state, and running the cipher for 10 steps with the key and IV being used as message.

1. Load the key and IV into the state as follows:

$$S_{-10,0} = IV_{128}$$

$$S_{-10,1} = Const1$$

$$S_{-10,2} = Const0$$

$$S_{-10,3} = K_{128} \oplus Const0$$

$$S_{-10.4} = K_{128} \oplus Const1.$$

2. For

$$i = -5$$

to  $-1$ ,  $m_{2i} = K_{128}$ ,  $m_{2i+1} = K_{128} \oplus IV_{128}$ .

3. For

$$i = -10$$

to  $-1$ ,  $S_{i+1} = StateUpdate128(S_i, m_i)$ .

#### The encryption of AEGIS-128:

After the initialization, at each step of the encryption, a 16-byte plaintext block  $P_i$  is used to update the state, and  $P_i$  is encrypted to  $C_i$ . If the size of the last message block is less than 128 bits, it is padded with 0 bits to a full block, and the padded full block is used to update the state.

- 1. If the last plaintext block is not a full block, use 0 bits to pad it to 128 bits.

- 2. For i = 0 to  $(\frac{msglen}{128} 1)$ , the state is updated to perform encryption.

$$C_i = P_i \oplus S_{i,1} \oplus S_{i,4} \oplus (S_{i,2} \& S_{i,3})$$

$S_{i+1} = StateUpdate128(S_i, P_i).$  (2.19)

#### The finalization of AEGIS-128 (MAC generation):

After encrypting all the plaintext blocks, the authentication MAC is generated using seven more steps. The message being used at this stage is part of the state at the end of the encryption, together with the length of the associated data and the length of the message.

- 1. Let tmp = lenA || msglen, where lenA and msglen are represented as 64-bit integers

- 2. For  $i=\left(\frac{msglen}{128}\right)$  to  $\left(\frac{msglen}{128}+6\right)$ ,  $m_i=S_{\frac{msglen}{128},3}\oplus tmp$

- 3. For i=  $(\frac{msglen}{128})$  to  $(\frac{msglen}{128} + 6)$ , the state is updated:  $S_{i+1} = StateUpdate128(S_i, P_i)$

- 4. The authentication MAC is generated from the state  $\frac{msglen}{128} + 7$  as follows:

$$MAC = \bigoplus_{i=0}^{4} (S_{(\frac{msglen}{128} + 7),i}).$$

(2.20)

#### The decryption and verification of AEGIS-128:

The exact values of the key and the IV should be known to the decryption and verification process. The decryption is similar to encryption, and it is described below:

1. For i = 0 to  $(\frac{msglen}{128} - 1)$ , the state is updated to perform the decryption.

$$P_{i} = C_{i} \oplus S_{i,1} \oplus S_{i,4} \oplus (S_{i,2} \& S_{i,3})$$

$$S_{i+1} = StateUpdate128(S_{i}, P_{i}).$$

(2.21)

2. The finalization in the decryption process is the same as that in the encryption process (authentication).

In terms of the hardware implementation, to our knowledge, there is no any current hardware implementation for AEGIS.

#### 2.6 Conclusion

In this chapter, we highlighted current AE algorithms, AES-CCM, AES-GCM, and AEGIS. Each algorithm was presented in detail and also followed by the current hardware implementations. Regarding AES-CCM, we showed the disadvantages of AES-CCM. It is not suitable for online applications as the message must be stored first before performing the authentication and the encryption. Also, it is not suited to high-speed implementations, because CBC-MAC is neither pipelinable nor parallelizable (see Table 2.2). In terms of AES-GCM, four different FPGAs-based architectures have been presented in the open literature ([32],[30],[3],[31]). It is clear that these contributions do generally have common challenge related to the throughput of their architectures (see Equation 2.16, Equation 2.17, and Table 2.4). Additionally, we presented an overview of AEGIS which is considered one of the candidates to CAESAR. Till now, there is no any hardware implementation for AEGIS.

#### Chapter 3

## High Speed Authenticated Encryption for Slow Changing Key Applications Using FPGAs

#### 3.1 Introduction

Virtual Private Networks (VPNs) offer an economic alternative to leased lines for building a private network. It is set up by allowing users to tunnel through the public network in a manner that manages the tunnel participants to enjoy a secure connection if they are on a typical private network. VPN tunnels can be either static (between two routers) or dynamic (between end-users and routers). VPNs use AES-GCM as a solution for protecting confidentiality and authenticity. Commercial security appliances of VPNs allow a throughput from 40 to 60 Gbps [37, 38]. Recently, the Cisco ASR 1000 Series Embedded Services Processors (ESPs) are used to support high throughput VPNs up to 200 Gbps [39]. The secret key used for encryption and authentication in these networks is changed weekly, monthly or yearly. Therefore, they are considered infrequent-key based applications.

This chapter describes the benefits of VPNs feature as an infrequent-key environment in order to design efficient and high speed AES-GCM. As the targeted platform is FPGA, FPGA-specific properties are considered for performance

improvement such as programmability, BRAMs, and LUT technology. The main contributions of this chapter are as follows:

- 1. As a first step towards an efficient high speed AES-GCM for VPNs, which are considered as an infrequent-key application, the key used for encryption and authentication is synthesized into the module structure of AES-GCM. This is achieved by combining the proposed keysynthesized AES (encryption) with the GF(2<sup>128</sup>) multiplier (authentication) proposed by [1] in order to improve the hardware performance (Thr./Slice) of AES-GCM compared to [3, 30, 32].

- 2. We propose an efficient method for implementing parallel AES-GCM cores. The proposed method improves the performance (Thr./Slice) of the parallel hardware architectures compared to [31].

- 3. Because of being key-synthesized architectures, we present a protocol to secure the reconfiguration of the proposed architectures on FPGAs.

## 3.2 High Speed AES-GCM Architectures Using FPGAs

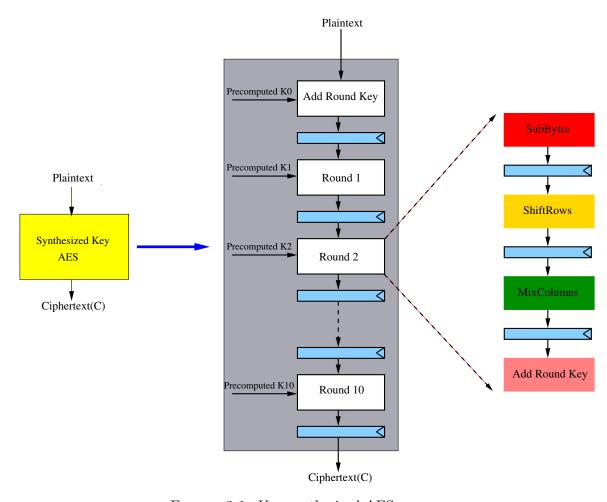

AES has a key expansion or key schedule operation, which takes the main key and derives from it subkeys  $K_r$  (10, 12, and 14 for AES-128, AES-192, and AES-256, respectively), where  $\mathbf{r}$  denotes the corresponding round number. For our case, we concentrate on AES-128.

VPNs are considered as a slow key changing application. Therefore, implementing the key expansion is particularly expensive in terms of hardware cost in case of using FPGAs. By getting the benefit of being programmable devices, the key used for encryption in synthesized into the architecture in order to obtain better performance regarding the consumed area and the throughput.

In the proposed hardware architecture, constant key specialization in the FPGA is used. The precomputed keys are generated using a C code as shown in Table 3.1. After, these keys are synthesized into the architecture of AES.

As a result, the key expansion scheme is reduced from the architecture of AES. Because of the high throughput target, pipelined AES is used to obtain high throughput. Fig. 3.1 shows the proposed key-synthesized AES, where all keys are precomputed and synthesized into the architecture.

| Main Key        | $000102030405060708090 \\ a0b0c0d0e0f$               |

|-----------------|------------------------------------------------------|

| Precomputed k0  | $000102030405060708090 \\ a0b0c0d0e0f$               |

| Precomputed k1  | d6aa74fdd2af72fadaa678f1d6ab76fe                     |

| Precomputed k2  | b692cf0b643dbdf1be9bc5006830b3fe                     |

| Precomputed k3  | b6ff744ed2c2c9bf6c590cbf0469bf41                     |

| Precomputed k4  | 47f7f7bc95353e03f96c32bcfd058dfd                     |

| Precomputed k5  | 3caaa3e8a99f9deb50f3af57adf622aa                     |

| Precomputed k6  | 5 e 390 f 7 d f 7 a 69296 a 7553 d c 10 a a 31 f 6 b |

| Precomputed k7  | 14f9701ae35fe28c440adf4d4ea9c026                     |

| Precomputed k8  | 47438735a41c65b9e016baf4aebf7ad2                     |

| Precomputed k9  | 549932 d1 f08557681093 ed9 cbe2 c974 e               |

| Precomputed k10 | 13111 d7 fe 3944 a 17 f 307 a 78 b 4 d2 b 30 c5      |

| Precomputed H   | c6a13b37878f5b826f4f8162a1c8d879                     |

Table 3.1: Precomputed round keys

The SubBytes transformation can be implemented either by BRAMs, composite field or direct Look Up Tables (LUT). Modern FPGAs contain Block-RAMs. Therefore, implementing SubBytes using BRAMs decreases the consumed slices of the FPGA. The LUT approach is especially interesting on Virtex-5 devices because 6-input Look-Up-Tables (LUT) combined with multiplexors allow an efficient implementation of the AES SubBytes stage. Composite field approach uses the multiplicative inverse of GF(2<sup>8</sup>) and it is efficient for memoryless platforms (see Fig. 3.2).

As a result of using key-synthesized AES, the operand H of the GHASH function  $(GF(2^{128}))$  multiplier is also fixed because it is generated by applying the block cipher to the zero block. Therefore, the proposed multiplier by [1] is very suitable because it is a fixed operand multiplier. In [1], the multiplication was performed as follows (Fig. 3.3):

#### 1. Algorithm 1 is divided into Algorithm 2 and Algorithm 3.

FIGURE 3.1: Key-synthesized AES

- 2. **Algorithm 2** is used to precompute the lookup table (T) which is based on a fixed *H*.

- 3. Performing the multiplication using the lookup table (T) (see Algorithm 3).

The lookup table generated by **Algorithm 2** contains 128 vectors of 128 bits. This table is synthesized into the architecture of the multiplier by **Algorithm 3** to compute the  $GF(2^{128})$  multiplication. Synthesizing binary 1 values of table T directly perform logic and binary 0 values do not perform logic because of XOR operation as shown in **Algorithm 3**. Therefore, the consumed area and the datapath are reduced.

Figure 3.2: SubBytes implementation with BlockRAMs (a), with LUTs (b), with composite field approach (c)

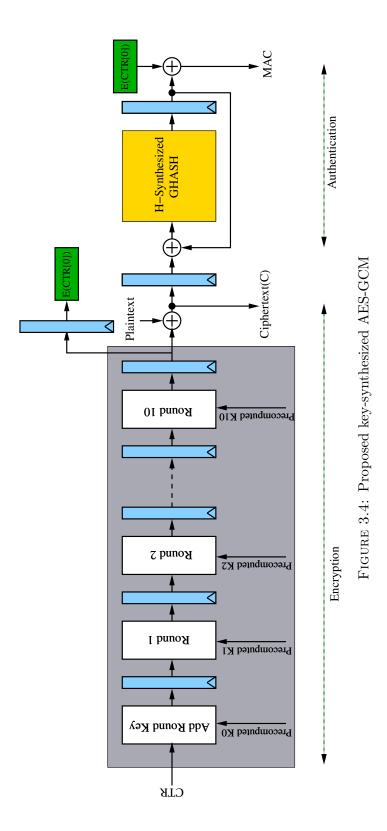

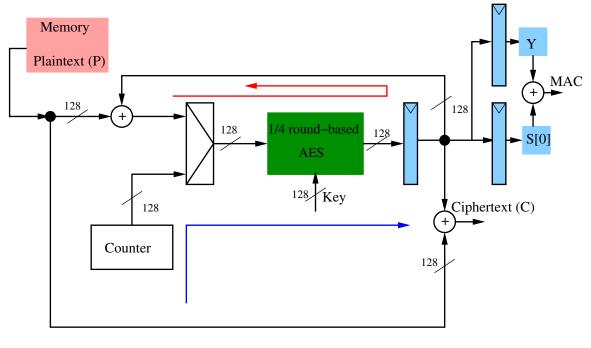

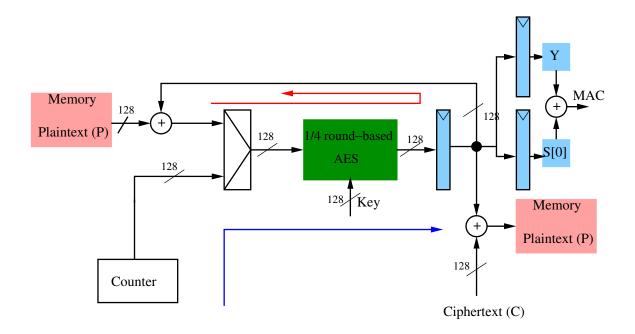

The overall architecture of AES-GCM is presented in Fig. 3.4. The value of CTR[0] is encrypted and stored because it will be used for MAC generation. After that, the encryption process is performed using CTR mode, where the CTR values are encrypted and XORed with the Plaintext (P). Encrypted frames are then processed by the H-synthesized GHASH till the end of the data. After processing all the data frames, the last output of the GHASH is XORed with E(CTR[0]) in order to generate the MAC.

From Fig. 3.4, it is clear that the encryption and the authentication in GCM are performed using the AES in CTR mode and the H-synthesized GHASH, respectively. Therefore, the proposed architecture could also be tuned to handle the decryption and the authentication. Precisely, Ciphertext (C) is XORed with the output of the pipelined AES for performing the decryption and also is passed to the H-synthesized GHASH for MAC generation.

The proposed architecture limits the logic utilization by specializing the core of AES-GCM on a per key. VPNs infrastructure can benefit from our key-synthesized AES-GCM implementation due to the nature of slow changing key operation.

#### 3.2.1 Efficient Parallel AES-GCM cores

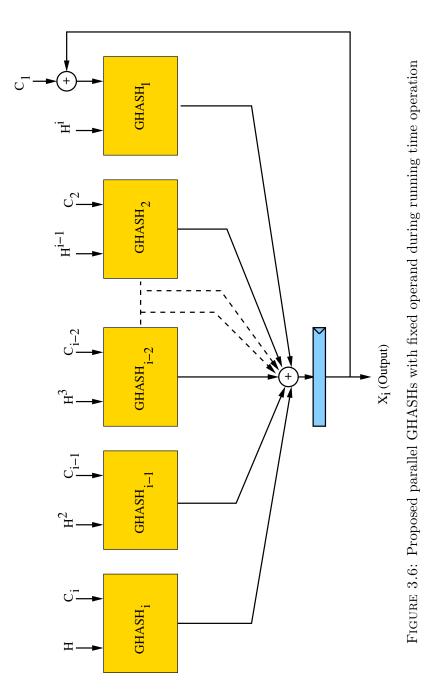

In order to implement parallel architectures of AES-GCM using key-synthesized method, parallel GHASHs must be constructed to meet the requirement of the key-synthesized nature (i.e, one of the two operands of each GHASH must be fixed).

Previous parallel schemes of GHASH [31, 34] are not suitable because the two operands of each GHASH are varied during the running time operation. As a result, their architectures are not suitable for key-synthesized approach. Also, they have the same common problem in the throughput reduction factor (described in Chapter 2). Therefore, constructing parallel GHASHs which have a fixed operand for each GHASH multiplier is very important for high speed applications.

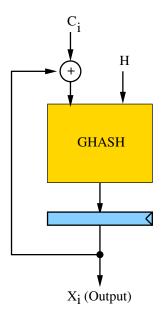

FIGURE 3.5: GHASH operation

Fig. 3.5 shows the  $GF(2^{128})$  multiplication (GHASH) between **H** and a 128-bit input value  $C_i$ .  $GHASH_H$  function for block i is defined in Equation 3.1.

$$X_i = (C_i \oplus X_{i-1}) \times H \tag{3.1}$$

In order to construct parallel GHASHs which have a fixed operand for each GHASH multiplier, we have to first analyze the processing equation of the GHASH. As shown in Equation 3.1, the the GHASH output is calculated by the multiplication between H and the result of XORing the input  $C_i$  with the previous output  $X_{i-1}$ . We propose writing Equation 3.1 as follows:

$$X_{i} = (C_{i} \oplus X_{i-1}) \times H$$

$$= (C_{i} \times H) \oplus (X_{i-1} \times H)$$

$$= (C_{i} \times H) \oplus [(C_{i-1} \oplus X_{i-2}) \times H^{2}]$$

$$= (C_{i} \times H) \oplus (C_{i-1} \times H^{2}) \oplus [(C_{i-2} \oplus X_{i-3}) \times H^{3}]$$

$$= (C_{i} \times H) \oplus (C_{i-1} \times H^{2}) \oplus (C_{i-2} \times H^{3})$$

$$\oplus [(C_{i-3} \oplus X_{i-4}) \times H^{4}]$$

$$= (\underbrace{(C_{i} \times H)} \oplus \underbrace{(C_{i-1} \times H^{2})} \oplus \underbrace{(C_{i-2} \times H^{3})} \oplus \underbrace{(C_{i-3} \times H^{4})} \dots \oplus \underbrace{(C_{2} \times H^{i-1})} \oplus \underbrace{(C_{1} \times H^{i})}.$$

$$(3.2)$$

It is clear from Equation 3.2 that each input from  $C_1$  to  $C_i$  is multiplied with a fixed value from  $H^i$  to H. For example (see Fig. 3.6),  $GHASH_i$  has H as an operand,  $GHASH_{i-1}$  has  $H^2$ , ...., and  $GHASH_1$  has  $H^i$ .

Unlike previous work, this method makes the parallel architecture of GHASHs suitable for the key-synthesized approach as we can get these values  $(H^i, H^{i-1}, \ldots, H)$  synthesized into the parallel architecture.

In terms of the throughput, from Fig. 3.6, it is obvious that only one clock cycle is needed for performing the parallel GHASHs output (there is no pipeline). Therefore, the throughput is calculated as follows:

$$Throughput(Mbps) = F_{max(MHz)} \times 128 \times i \tag{3.3}$$

where i is the number of the parallel GHASHs.

From Equation 3.3, it is clear that there is no reduction factor in the throughput calculation compared to [31, 34].

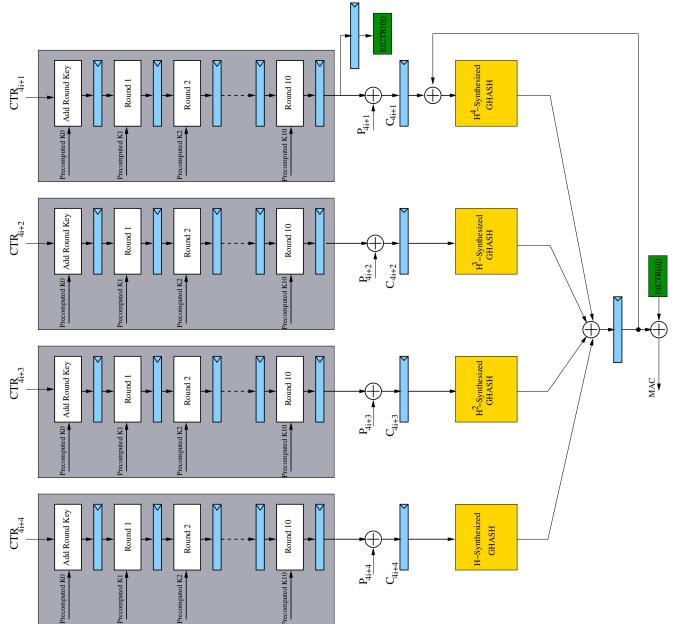

In order to support high speed requirements up to 100 Gbps, we are forced to construct 4-parallel AES-GCM cores. Fig. 3.7 shows the presented 4-parallel AES-GCM using key-synthesized method.

In terms of the parallel pipelined AES, we instantiated four parallel AES cores which have the same key. Therefore, the round keys are precomputed and synthesized into the four cores. The resulting multi-core design is thus able to process a 512-bit block (4128 bits) of plaintext every clock cycle. The ciphertext is generated directly by XORing the four 128-bit blocks ( $P_{4i+1}$ ,  $P_{4i+2}$ ,  $P_{4i+3}$ , and  $P_{4i+4}$ ) with the output strings resulting from encrypting the counter values.

In order to combine the authentication core with the multi-core AES, a design solution based on four parallel GHASHs has been investigated. From Equation 3.2, in order to construct 4-parallel GHASHs, the operands  $(H, H^2, H^3, H^4)$  are precomputed and synthesized into the architecture. The multi-core GHASH is able to process a 512-bit block (4128 bits) every clock cycle. Therefore the final overall throughput of the 4-parallel AES-GCM is as follows:

$$Throughput(Mbps) = F_{max(MHz)} \times 128 \times 4. \tag{3.4}$$

The presented architecture does not contain any reduction factor compared to [31, 34]. Also, it could be tuned to handle the decryption and authentication as we described before in the single architecture.

All the previous proposed architectures in this chapter are considered as FPGA-based architectures because of using the programmability of FPGAs in order to change the key. More precisely, in case of changing the key, a new bitstream is uploaded on the FPGA with the new key-synthesized specialization. Therefore, it is important to present how these architectures are uploaded on the FPGA in a secure manner in case of changing the key because the bitstream is considered a key-based bitstream.

FIGURE 3.7: 4-parallel AES-GCM using key-synthesized method

### 3.3 Bitstream security of the proposed architectures

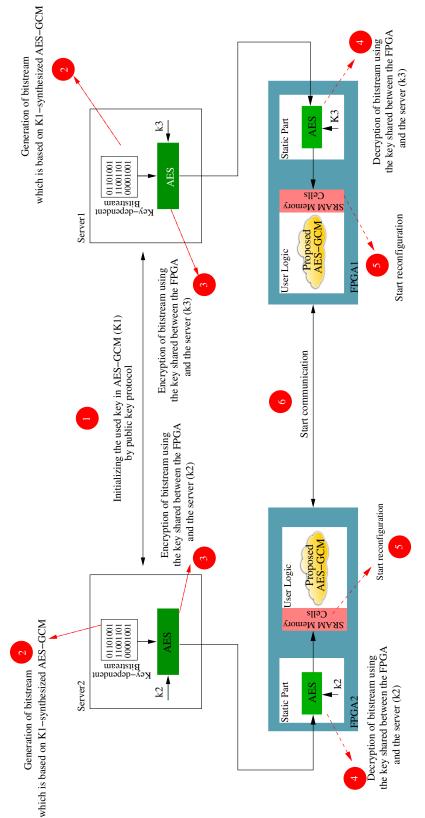

As a result of synthesizing the key into the architecture, the generated bitstream is a key-dependent. Hence, the bitstream must be sent in a secure way to the FPGA in case of changing the key. Our analysis focuses on securing the key exchange and the implementation of the key-dependent bitstream on the FPGA.

Fig. 3.8 shows the proposed protocol which is used to perform the key exchange and the reconfiguration process between two FPGAs in a secure way. Our scheme assumes that two FPGAs in two different networks are involved in a communication and the proposed AES-GCM is implemented. In case of changing the key to be k1, the protocol will be as follows:

- 1. The two servers are communicating in order to initialize the key (k1) of AES-GCM. This initialization is performed using public key cryptography.

- 2. The two servers generate the bitstream file which is k1-synthesized.

- 3. Server1 shares k3 with FPGA1 for secure reconfiguration. This key (k3) is used to encrypt the k1-synthesized bitstream. The same will be with server2 which shares k2 with FPGA2. Thanks to Xilinx because Virtex-5 and Virtex-4 contain an AES engine for supporting secure reconfiguration, in case of Virtex-6, the bitstram can be also authenticated because Virtex-6 has an on chip MAC for supporting authentication.

- 4. The two FPGAs decrypt the encrypted bitstream.

- 5. The k1-synthesized bitstream which defines the new key-based AES-GCM is implemented on the user logic.

- 6. The communication between the two FPGAs is achieved with the new key k1.

Figure 3.8: Secure bitstream communication

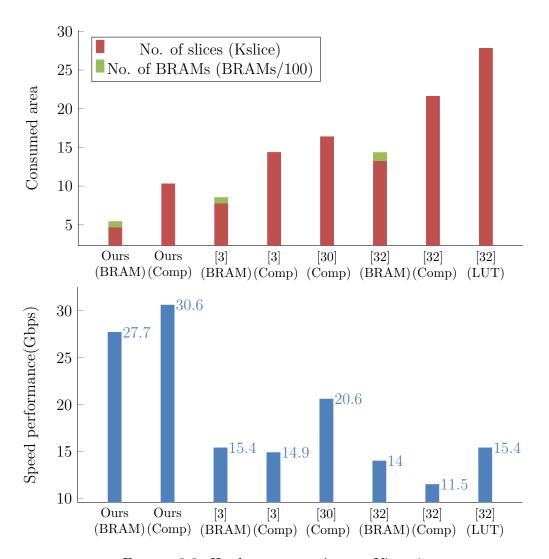

#### 3.4 Hardware comparison

We coded our proposed schemes (AES-GCM and 4-parallel AES-GCM) in VHDL and targeted to Virtex-4 (V4LX60ff668-11) and Virtex-5 (XC5VLX220). ModelSim 6.5c was used for simulation. Xilinx Synthesize Technology (XST) is used to perform the synthesize and ISE9.2 was adopted to run the Place And Route (PAR).

Table 3.2 shows the hardware comparison between our results and previous work. Note the filled dots in the "Key" column. Key is synthesized into the architecture when denoted by  $\circ$ , otherwise, the key schedule is implemented when denoted by  $\bullet$ .

On Virtex-4 platform, our key-synthesized AES-GCM core reaches the throughput of 27.7 Gbps with the area consumption of 4652 slices and 80 BRAMs. In case of using composite field SubBytes, it consumes twice more slices, however no BRAMs are required. On Virtex5, the most efficient implementation reaches the throughput 30.9 Gbps with 2478 slices and 40 BRAMs. Our implementations are technology independent and can be implemented to other FPGA devices.