## Assisting the Design of Secured Applications for Embedded Systems

Gabriel Pedroza

#### ▶ To cite this version:

Gabriel Pedroza. Assisting the Design of Secured Applications for Embedded Systems. Computer Aided Engineering. Télécom ParisTech, 2013. English. <NNT : 2013-ENST-001>. <tel-01185312>

## HAL Id: tel-01185312 https://pastel.archives-ouvertes.fr/tel-01185312

Submitted on 19 Aug2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Doctorat ParisTech**

## THÈSE

pour obtenir le grade de docteur délivré par

## **TELECOM** ParisTech

## Spécialité: Télécommunications et Electronique

présentée et soutenue publiquement par

Juan Gabriel PEDROZA BERNAL

le 10 janvier 2013

## **Conception Assistée des Logiciels Sécurisés**

## pour les Systèmes Embarqués

Prof. Jean-Louis LANET **Prof. Frédéric CUPPENS** Dr. Luca COMPAGNA Prof. Mireille BLAY-FORNARINO Université de Nice (UNSA) Dr. Ludovic APVRILLE Prof. Renaud PACALET

Jury

Université de Limoges Télécom Bretagne SAP Research Center S.A. Télécom ParisTech Télécom ParisTech

Rapporteur Rapporteur Examinateur Examinateur Directeur de Thèse Co-Directeur de Thèse

To my loved ones To my mentors and sponsors

#### Acknowledgements

I would like to express my thankfulness to the persons that helped me to obtain my Ph.D. Initially, to my supervisors Renaud Pacalet and Ludovic Apvrille who led me during almost four years. Secondly, to the jury members, in particular to Jean-Louis Lanet and Frédéric Cuppens, the reviewers of my thesis. A huge thanks for the fruitful discussions with colleagues, friends, and researchers from the System-on-Chip laboratory and Eurecom. To keep it short, I will avoid listing all them but they already occupy a place in my memory. An important part of my work was conducted in the scope of the EVITA project. It was certainly an outstanding opportunity and an amazing experience for collaborating and learning. I sincerely express to all EVITA partners my gratitude. Special thanks to Hendrik Schweppe, Yves Roudier, Hagen Platzdasch, Hervé Seudié, Wolfgang Wiewesiek, Franz Pirklbauer, Timo Gendrullis, Sigrid Gürgens, and Andreas Fuchs. The Eurecom staff kindly hosted me during these years and I want to say thanks a lot for the permanent and awesome support. I am truly lucky to have met all those persons. Last but not least, I would like to recognize the funds and support received via the following institutions:

- Government of France

- Institut de Mines Télécom/Télécom ParisTech

- European Commission FP7

- National Council for Science and Technology of México (CONACyT)

Their support was essential to accomplish this objective.

#### Abstract

The Intelligent Transport Systems (ITS) arose several years ago pursuing the introduction of smarter in-vehicle systems in order to assist drivers and make roads safer. From the ITS perspective, vehicles are seen as mobile communicating hubs inside a large, diversified, complex, and easily accessible network. Consequently, the deployment and operation of on-board architectures shall face a wide variety of threats that may endanger vehicle safety and human being lives.

A vast majority of distributed embedded systems is also concerned by security risks. The fact that the applications may result poorly protected is partially due to methodological lacks in the engineering development process. More specifically, consider security as an after thought is not as effective as its early introduction during system conception stages. Since formal methodologies have been successfully applied to ensure properties of concurrent systems, we believe that their appropriate integration into the engineering development process may help to ensure security of applications. Methodologies targeting formal verification may lack support to certain phases of the development process. Particularly, system modeling frameworks may be complex-to-use or not address security at all. Along with that, testing is not usually addressed by verification methodologies since formal verification and testing are considered as exclusive stages. Nevertheless, we believe that platform testing can be applied to ensure that properties formally verified in a model are truly endowed to the real system.

Our contribution is made in the scope of a model-driven based methodology that, in particular, targets secure-by-design embedded systems. The methodology is an iterative process pursuing coverage of several engineering development phases and that relies upon existing security analysis techniques. Still in evolution, the methodology is mainly defined via a high level SysML profile named Avatar. The contribution specifically consists on extending Avatar so as to model security concerns and in formally defining a model transformation towards a verification framework. This contribution allows to conduct proofs on authenticity and confidentiality and also provides a basis to later support proofs on other security properties. We illustrate how an automotive cryptographic protocol is partially secured by applying several methodology stages like System Analysis, Threats Analysis, Requirements Structuring, Properties Modeling, System Design, Formal Verification, and Coverage Assessment. In addition, it is described how Security Testing was conducted on an embedded prototype platform within the scope of an automotive project and relying upon state of the art techniques.

# Contents

| 1 | Intr                        | oducti                                             | on                                                                                                                                          | 1 |  |  |  |

|---|-----------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

|   | 1.1                         | Contex                                             | xt                                                                                                                                          | 1 |  |  |  |

|   | 1.2                         | Proble                                             | matic                                                                                                                                       | 2 |  |  |  |

|   | 1.3                         | Contri                                             | butions                                                                                                                                     | 3 |  |  |  |

|   |                             | 1.3.1                                              | Objective                                                                                                                                   | 3 |  |  |  |

|   |                             | 1.3.2                                              | Thesis Approach Synopsis                                                                                                                    | 4 |  |  |  |

|   | 1.4                         | Outlin                                             | e                                                                                                                                           | 4 |  |  |  |

| 2 | Secu                        | urity a                                            | nd Vehicular Applications                                                                                                                   | 5 |  |  |  |

|   | 2.1                         | Vehicu                                             | lar Applications Evolution and Security                                                                                                     | 5 |  |  |  |

|   |                             | 2.1.1                                              | 80's Decade Developments                                                                                                                    | 5 |  |  |  |

|   |                             | 2.1.2                                              | 90's Decade Developments                                                                                                                    | 6 |  |  |  |

|   |                             | 2.1.3                                              | 2000's Decade Developments                                                                                                                  | 7 |  |  |  |

|   |                             | 2.1.4                                              | From 2010 Up to Now Developments                                                                                                            | 9 |  |  |  |

|   | 2.2                         | Currer                                             | t Vehicles Architecture                                                                                                                     | 1 |  |  |  |

|   | 2.3                         | Uncov                                              | ered Security Aspects $\ldots \ldots 1^4$ | 4 |  |  |  |

|   |                             | 2.3.1                                              | Critical Security Aspects                                                                                                                   | 4 |  |  |  |

|   |                             | 2.3.2                                              | Known Attacks and Potential Impact                                                                                                          | 6 |  |  |  |

|   |                             | 2.3.3                                              | Hypothetical Automotive Attack 18                                                                                                           | 8 |  |  |  |

|   | 2.4                         | Conclu                                             | 1sions                                                                                                                                      | 0 |  |  |  |

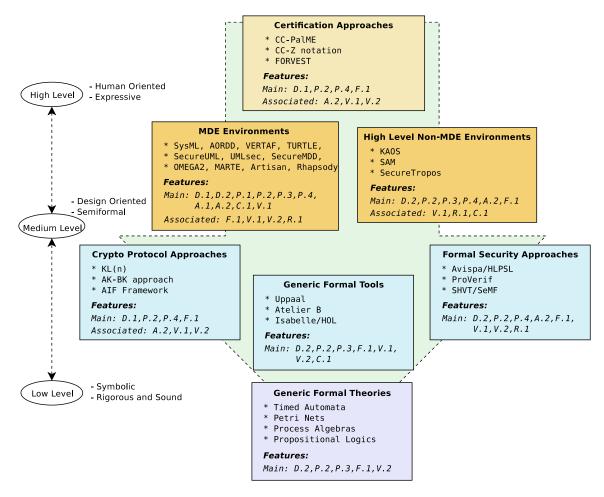

| 3 | Met                         | Methodologies for Embedded Systems Verification 23 |                                                                                                                                             |   |  |  |  |

|   | 3.1                         | Verific                                            | ation Methodologies Survey                                                                                                                  | 5 |  |  |  |

|   |                             | 3.1.1                                              | Generic Formal Theories                                                                                                                     | 5 |  |  |  |

|   |                             | 3.1.2                                              | Generic Formal Based Tools                                                                                                                  | 6 |  |  |  |

|   |                             | 3.1.3                                              | Formal Security Oriented Methodologies                                                                                                      | 8 |  |  |  |

|   |                             | 3.1.4                                              | Cryptographic Protocol Oriented Approaches                                                                                                  | 0 |  |  |  |

|   |                             | 3.1.5                                              | Model Driven Engineering Environments                                                                                                       | 1 |  |  |  |

|   |                             | 3.1.6                                              | High Level Non-MDE Environments                                                                                                             | 4 |  |  |  |

|   |                             | 3.1.7                                              | Certification Oriented Approaches                                                                                                           | 6 |  |  |  |

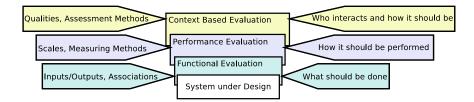

|   | 3.2                         | Qualit                                             | ative Evaluation of Verification Approaches                                                                                                 | 7 |  |  |  |

|   |                             | 3.2.1                                              | Features by Category                                                                                                                        | 8 |  |  |  |

|   |                             | 3.2.2                                              | Pros and Cons of Verification Methodologies                                                                                                 | 9 |  |  |  |

|   |                             | 3.2.3                                              | Properties Support and Framework Usability 42                                                                                               | 2 |  |  |  |

|   | 3.3 Summary and Conclusions |                                                    |                                                                                                                                             | 5 |  |  |  |

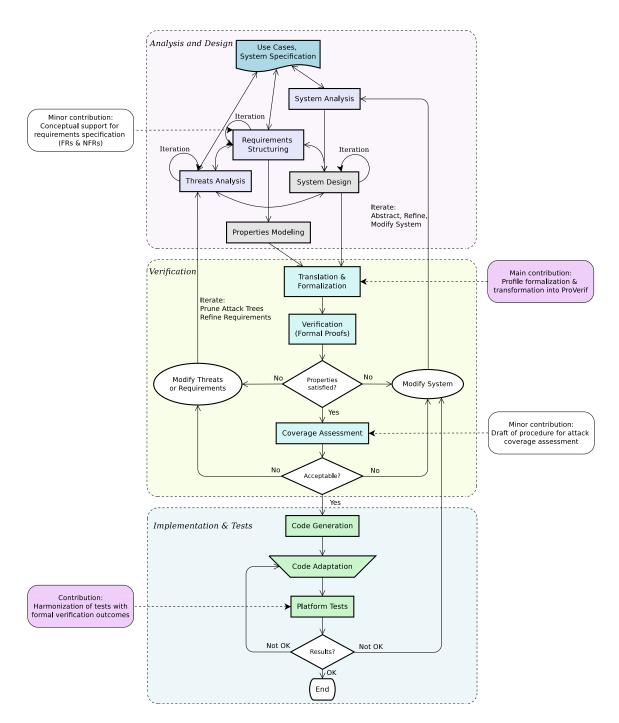

| 4 | Pro | posed   | Methodology for Verifying Critical Embedded Systems | 49    |

|---|-----|---------|-----------------------------------------------------|-------|

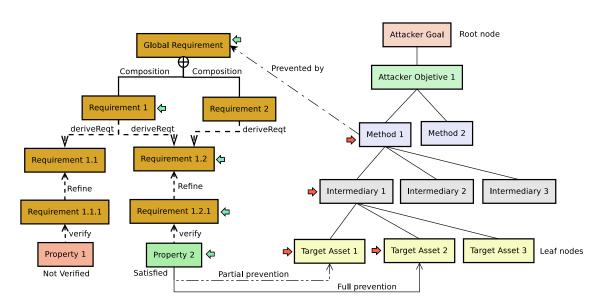

|   | 4.1 | Contri  | ibutions and Methodology Overview                   | . 49  |

|   | 4.2 | Metho   | bodology Description                                | . 53  |

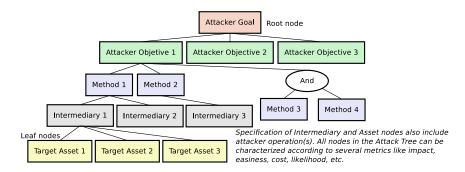

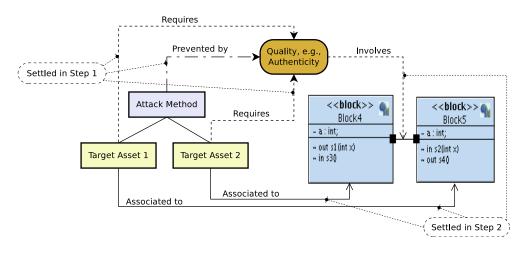

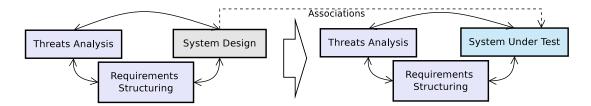

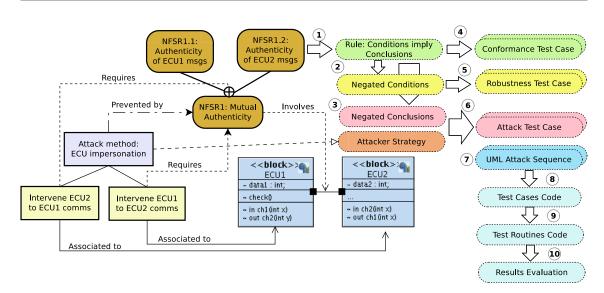

|   |     | 4.2.1   | Threats Analysis                                    | . 53  |

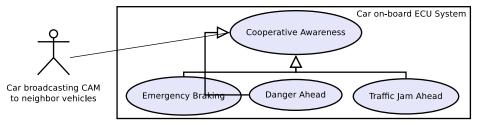

|   |     | 4.2.2   | System Analysis                                     | . 56  |

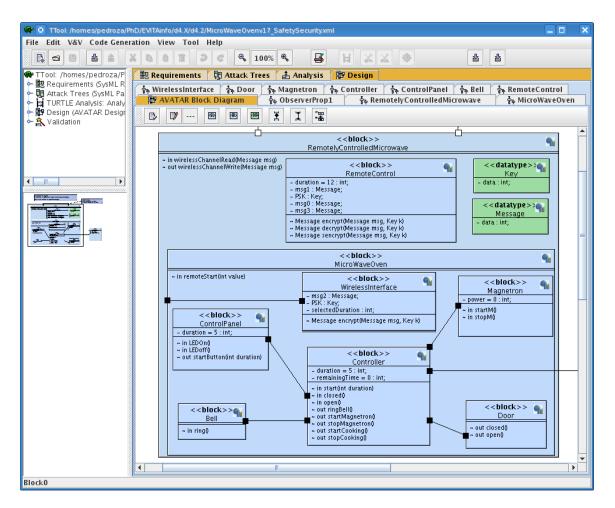

|   |     | 4.2.3   | System Design                                       | . 58  |

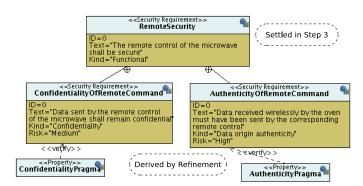

|   |     | 4.2.4   | Requirements Structuring                            | . 61  |

|   |     | 4.2.5   | Properties Modeling                                 | . 66  |

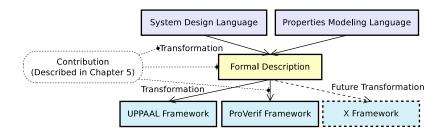

|   |     | 4.2.6   | Formalization and Verification                      | . 69  |

|   |     | 4.2.7   | Coverage Assessment                                 |       |

|   |     | 4.2.8   | Code Generation and Adaptation                      |       |

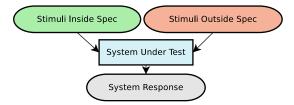

|   |     | 4.2.9   | Platform Tests                                      |       |

|   | 4.3 | Conclu  | usions                                              | . 82  |

| 5 | Ass | isted I | Design with Avatar                                  | 83    |

|   | 5.1 | The A   | vatar Design Framework: An Overview                 | . 84  |

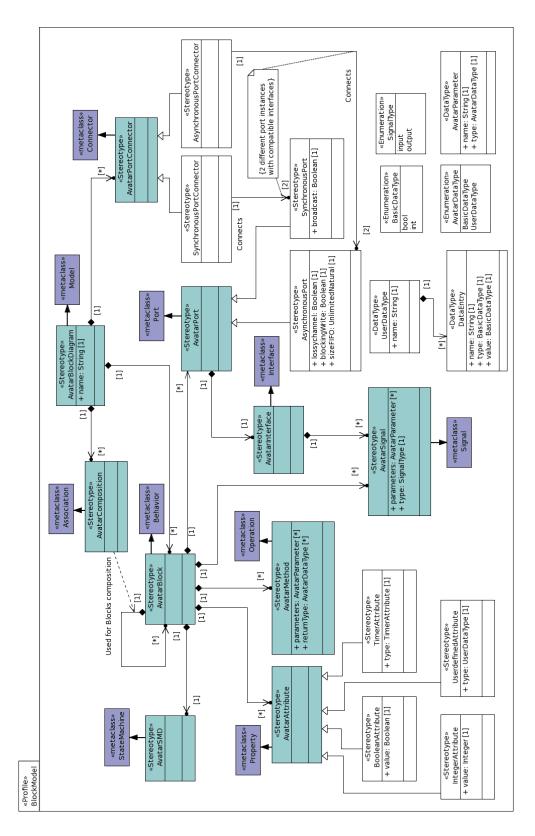

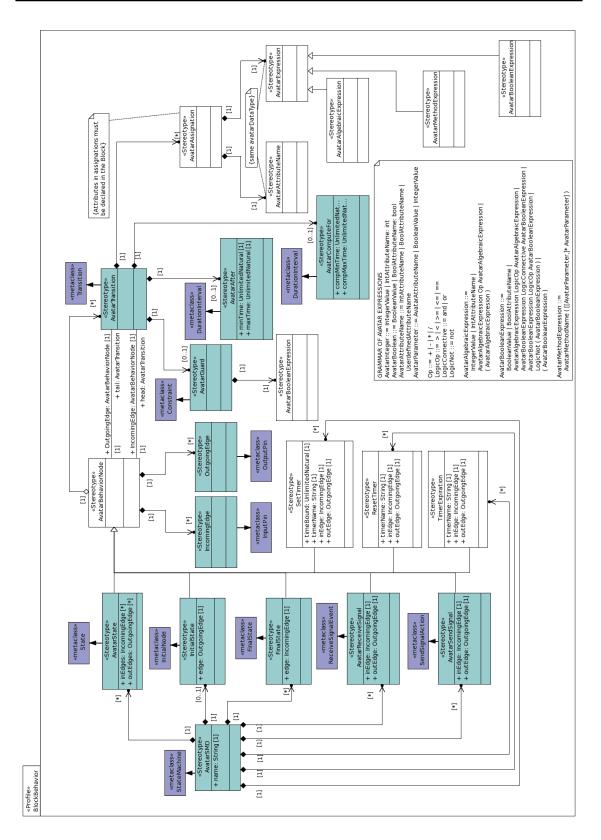

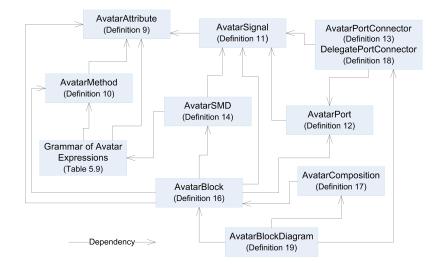

|   |     | 5.1.1   | Avatar Design Metamodel                             | . 84  |

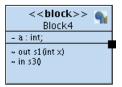

|   |     |         | 5.1.1.1 Block Metamodel Components                  | . 86  |

|   |     |         | 5.1.1.2 SMD Metamodel Components                    | . 88  |

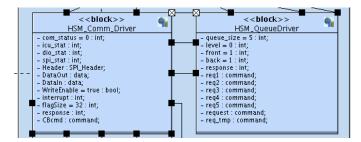

|   |     | 5.1.2   | Avatar Design Framework Implementation              | . 91  |

|   | 5.2 | Exten   | ding Avatar Design Profile                          | . 94  |

|   |     | 5.2.1   | Avatar Design Limitations                           | . 95  |

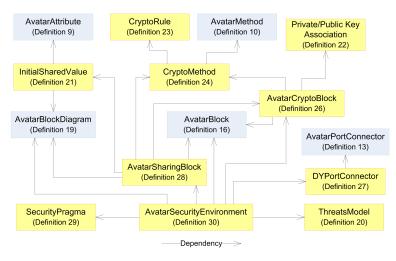

|   |     | 5.2.2   | Avatar Extensions: The Avatar Security Environment  | . 97  |

|   | 5.3 | Attack  | ning a Formal Semantics to AvatarSE                 | . 101 |

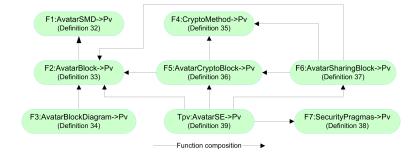

|   |     | 5.3.1   | Avatar & AvatarSE Formal Descriptions               | . 102 |

|   |     |         | 5.3.1.1 Avatar Formal Description                   | . 103 |

|   |     |         | 5.3.1.2 AvatarSE Formal Description                 |       |

|   |     | 5.3.2   | AvatarSE-to-ProVerif Transformation                 | . 111 |

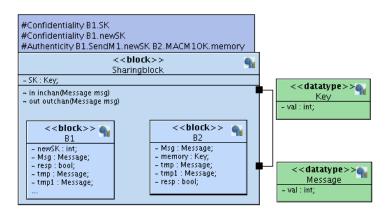

|   |     | 5.3.3   | Example of Transformation                           |       |

|   | 5.4 | Appro   | ach Limitations and Conclusions                     | . 119 |

|   |     | 5.4.1   | Approach Limitations                                | . 121 |

|   |     | 5.4.2   | Conclusions                                         | . 122 |

| 6 | Cas | e Stud  | ly: Securing and Testing EVITA Architecture         | 125   |

|   | 6.1 | Securi  | ng EVITA Symmetric Keying Protocol                  | . 126 |

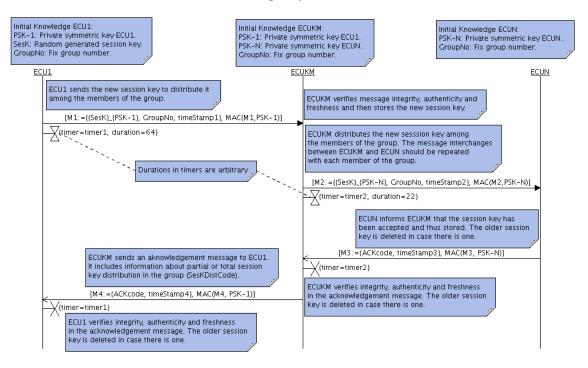

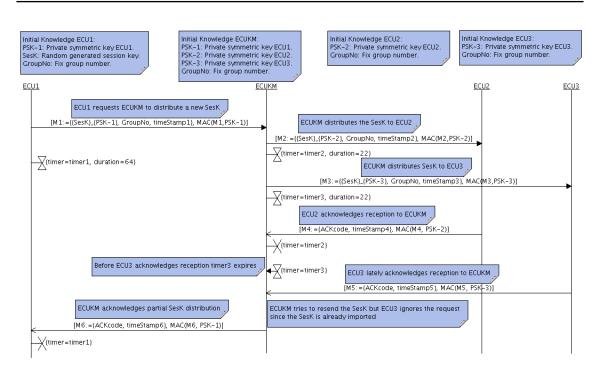

|   |     | 6.1.1   | Initial System Analysis                             |       |

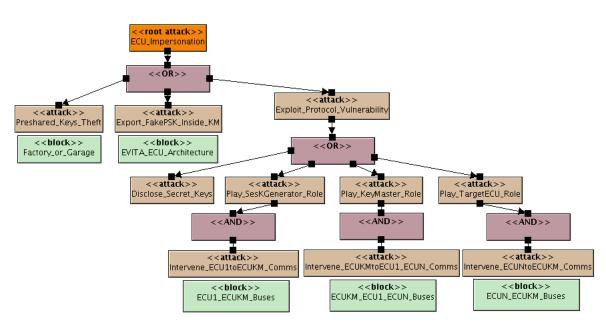

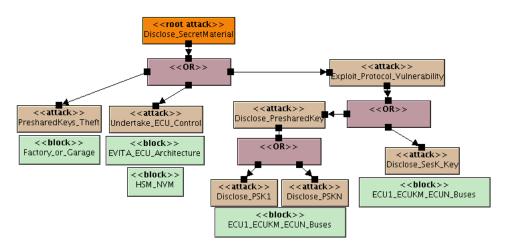

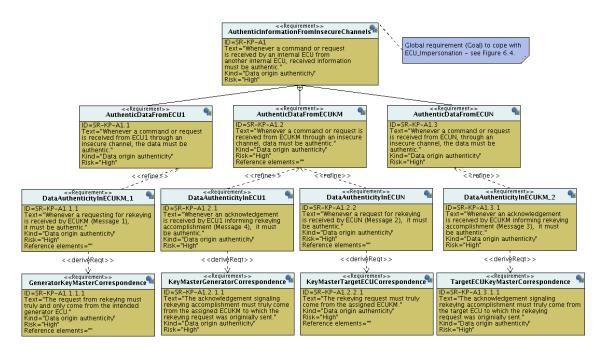

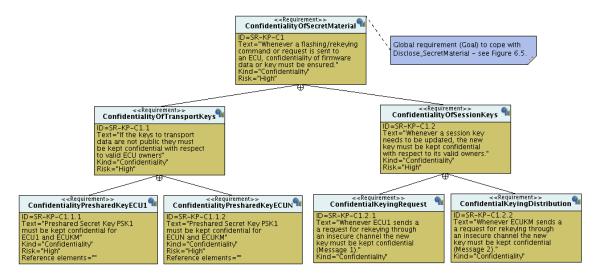

|   |     | 6.1.2   | Threats and Requirements Analyses                   | . 129 |

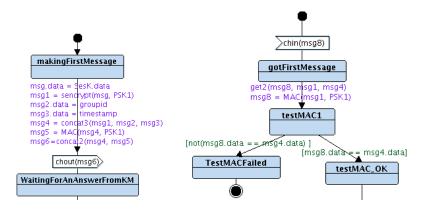

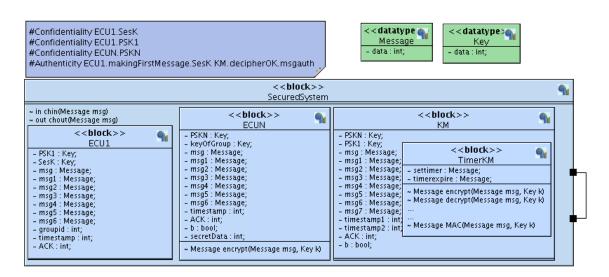

|   |     | 6.1.3   | Design and Verification                             |       |

|   |     | 6.1.4   | Attack Coverage Assessment                          | . 135 |

|   |     | 6.1.5   | Conclusions: Case Study I                           | . 138 |

|   | 6.2 | EVITA   | A HSM Driver Tests                                  | . 140 |

|   |     | 6.2.1   | HSM Driver Context                                  | . 140 |

|   |     | 6.2.2   | Driver Test Method                                  | . 141 |

|   |     | 6.2.3   | Driver Testing Environment                          | . 142 |

|   |     | 6.2.4   | Results and Discussion                              |       |

|   |     | 6.2.5   | Conclusions: Case Study II                          | . 145 |

| 7  | Conclusions and Perspectives                  | 147 |

|----|-----------------------------------------------|-----|

|    | 7.1 Initial Findings                          | 147 |

|    | 7.2 Contributions and Conclusions             | 148 |

|    | 7.3 Discussion: Shortcomings and Perspectives | 150 |

| Α  | Underlying Formal Backend                     | 153 |

|    | A.1 ProVerif                                  | 153 |

| Bi | ibliography                                   | 173 |

## List of abbreviations

| ACC Adaptive Cruise Control                                                                             |                                                                              |  |  |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| ACP                                                                                                     | Algebra of Communicating Processes                                           |  |  |

| API                                                                                                     | Application Programming Interface                                            |  |  |

| ASIC                                                                                                    | Application Programming Internace<br>Application-Specific Integrated Circuit |  |  |

| AvatarRD                                                                                                |                                                                              |  |  |

| AvatarSE                                                                                                | Avatar Security Environment                                                  |  |  |

| CAM                                                                                                     | Cooperative Awareness Message                                                |  |  |

| CAN                                                                                                     | Controller Area Network                                                      |  |  |

| CASE                                                                                                    | Computer Aided Software Engineering                                          |  |  |

| CC                                                                                                      | Common Criteria                                                              |  |  |

| CCU                                                                                                     | Communication Control Unit                                                   |  |  |

| CSP                                                                                                     | Communication Control Cint<br>Communicating Sequential Processes             |  |  |

| CTL                                                                                                     | Computational Tree Logic                                                     |  |  |

| TCTL                                                                                                    | Timed CTL                                                                    |  |  |

|                                                                                                         |                                                                              |  |  |

| <ul><li><b>DoS</b> Denial of Service</li><li><b>DSRC</b> Dedicated Short-Range Communications</li></ul> |                                                                              |  |  |

| 0                                                                                                       |                                                                              |  |  |

| <ul><li>EAL Evaluation Assurance Level</li><li>EBCM Electronic Brake Control Module</li></ul>           |                                                                              |  |  |

| EBCMElectronic Brake Control ModuleECUElectronic Control Unit                                           |                                                                              |  |  |

| ECUElectronic Control UnitEMIElectromagnetic Interference                                               |                                                                              |  |  |

| EVITA                                                                                                   | E-safety Vehicle Intrusion Protected Applications                            |  |  |

| FPGA                                                                                                    | Field Programmable Gate Array                                                |  |  |

| FIFO                                                                                                    | First In/First Out                                                           |  |  |

| FR                                                                                                      | Functional Requirement                                                       |  |  |

| FSR                                                                                                     | Functional Security Requirement                                              |  |  |

| FSP                                                                                                     | Functional Security Property                                                 |  |  |

| FP                                                                                                      | Functional Property                                                          |  |  |

| GPS                                                                                                     | Global Positioning System                                                    |  |  |

| HMAC                                                                                                    | Hash-Based MAC                                                               |  |  |

| НМІ                                                                                                     | Human-Machine Interface                                                      |  |  |

| HOL                                                                                                     | High Order Logic                                                             |  |  |

| HSM                                                                                                     | Hardware Security Module                                                     |  |  |

| IT Information Technology                                                                               |                                                                              |  |  |

| ITS                                                                                                     | Intelligent Transport Systems                                                |  |  |

| LIN Local Interconnect Network                                                                          |                                                                              |  |  |

| <b>LLD</b> Low Level Driver                                                                             |                                                                              |  |  |

| LTL Linear Temporal Logic                                                                               |                                                                              |  |  |

| LTS                                                                                                     | Labeled Transition System                                                    |  |  |

| MAC Message Authentication Code                                                                         |                                                                              |  |  |

| MAC Media Access Control                                                                                |                                                                              |  |  |

| MDE                                                                                                     | Model Driven Engineering                                                     |  |  |

| MOST                                                                                                    | Multimedia Oriented Systems Transport                                        |  |  |

| NFP                                                                                                     | Non-Functional Property                                                      |  |  |

| NFR                                                                                                     | Non-Functional Requirement                                                   |  |  |

| NFSR Non-Functional Security Requirement                                                                |                                                                              |  |  |

| NFSP                                                                                                    | Non-Functional Security Property                                             |  |  |

|                                                                                                         |                                                                              |  |  |

<u>x</u>\_\_\_\_\_

| 001                                               |                                                                     |  |

|---------------------------------------------------|---------------------------------------------------------------------|--|

| OCL                                               | Object Constraint Language                                          |  |

| OEM                                               | Original Equipment Manufacturer                                     |  |

| <b>OS</b> Operating System                        |                                                                     |  |

| PKI Public-Key Infrastructure                     |                                                                     |  |

| <b>RF</b> Radio Frequency                         |                                                                     |  |

| RSU Road-Side Unit                                |                                                                     |  |

| SAM                                               | Software Architecture Modeling                                      |  |

| SeMF                                              | Security Modeling Framework                                         |  |

| SMD                                               | State Machine Diagram                                               |  |

| SMV                                               | Symbolic Model Verifier                                             |  |

| SPI                                               | Serial Peripheral Interface                                         |  |

| ST Security Target                                |                                                                     |  |

| SysML Systems Modeling Language                   |                                                                     |  |

| TCB Trusting Computing Base                       |                                                                     |  |

| <b>TEPE</b> Temporal Property Expression Language |                                                                     |  |

| <b>ToE</b> Target of Evaluation                   |                                                                     |  |

| ТРМ                                               | Trusted Platform Module                                             |  |

| TTA                                               | Time Triggered Architecture                                         |  |

| UML                                               | Unified Modeling Language                                           |  |

| UMTS Universal Mobile Transmission System         |                                                                     |  |

| UTC                                               | •                                                                   |  |

| V2I                                               |                                                                     |  |

| V2V                                               | Vehicle to Vehicle                                                  |  |

| V2X                                               | Vehicle to Vehicle $(V2V)$ and/or Vehicle to Infrastructure $(V2I)$ |  |

| VANET                                             | Vehicular Ad-Hoc Network                                            |  |

|                                                   |                                                                     |  |

.

# Chapter 1 Introduction

#### 1.1 Context

The Intelligent Transport Systems (ITS) arose several years ago impelling the design of new applications in the automotive industry. The ITS paradigm envisages a wide network of mobile vehicles and fixed architecture to exchange information so as to make roads more coordinated. The architecture not only for in-car exchanges but also for vehicle and road side architecture communications should still be developed. The ITS network pursues several objectives many of which are in the scope of driver safety:

- 1. Assist driver/car in emergency maneuvers, e.g., to reduce impact in collisions.

- 2. Broadcast warning messages, e.g., drivers are warned of road dangers ahead.

- 3. Provide toll services, e.g., automatic emergency call after a crash.

- 4. Lead to interactive road side architecture, e.g., radars enforce speed limits.

- 5. Improve traffic flow, e.g., driver is assisted in seeking for alternative routes.

Several challenges should be faced before ITS becomes a viable alternative. For instance, the creation of new standards is necessary to regulate/harmonize implementations. Harmonization is a mean to achieve interoperable technology across countries. Standardization may demand that a wide range of topics be addressed: from technical aspects up to legal ones. To ensure interoperability, agreements between involved countries seem mandatory. Moreover, vehicles should be equipped with reliable and secure ITS implementations. Thus, car makers, service providers, and developers are highly concerned with embedded systems dependability. ITS deployment strongly depends upon the level of trustiness achieved in automotive applications.

Designers have started to consider security from the very first design stages by imposing stringent requirements. It is generally accepted that for achieving security and technical objectives, hardware and software threats should be identified, analyzed, and prevented. To do so, external communication (V2X) as well as internal on-board architecture need to be secured. Indeed, exchanges over public communication channels are typical targets of attackers. Hostile actions may threaten not only wireless vehicle exchanges (V2X communication) but also wired links, i.e., exposed buses and ports inside the vehicle (in-car communication). As referred in several works, current automotive embedded systems may be the target of a variety of attacks [121], [123], [181], [156], [46], [202], [47], [179], [25], [217], [29]. The technology and resources required to threaten vehicles are sophisticated but eventually accessible. It means that a skilled and motivated hostile party has chances of overtaking on-board systems and compromising vehicle operation. The impact of attacker actions may even endanger driver safety and human being lives [121], [123]. Also, the privacy of drivers may be compromised via vehicles tracking [25], [217]. Along with that, as recently occurred [47], poorly protected systems may lead to vehicles theft what damages owners' economy.

Improve in-car applications so as to better protect them against the hostile environment is imperative in order to achieve ITS objectives. The correct operation of safety critical applications like braking strongly depends upon trusted exchanges. Also, facilities that warn drivers must be trusted so as to properly enlarge driver's view ahead. Introduced facilities may prevent casualties or reduce their impact, e.g., passengers injuries, car damages, thus improving vehicular safety [199], [212].

#### 1.2 Problematic

Many distributed embedded systems are threatened by hazards similar to the ones in the automotive domain. To achieve a certain level of SW/HW applications protection, formal verification has been proposed and successfully used, see [102]. Thus, formal techniques may also help to improve ITS development [135], [50]. However, the adequate integration of formal techniques into the engineering development process needs to be thoroughly addressed. Several approaches applied for securing vehicle architectures are empirical and limited to undertake certain issues. In particular, some proposals only protect the system against specific attack cases, e.g., [89], [215], [124]. In others, the effectiveness of security countermeasures is not proved against any adversary, e.g., [114], [99], [140]. Securing applications only considering specific hazards may be ineffective with respect to real hostile environment [97]. Relying upon a local-view paradigm strengthens certain aspects of the engineering development process whereas other critical concerns may remain barely or not addressed at all. We believe that adopting a global-view may help to better identify methodological lacks that have led to poorly protected applications.

Security of distributed embedded systems is a vast and highly complex problem. To our knowledge, there is neither master guide nor golden rule that provides security and ensures overall system protection. So far, we aim to improve certain methodological issues:

- 1. To some extent, several automotive applications are currently vulnerable to attacks. Those cases show that the engineering development process may produce poorly protected systems. Thus, the support provided to certain development phases should be improved.

- 2. Several system development approaches have mainly focused in functional aspects and security was rather an afterthought. Those approaches have resulted ineffective for achieving system protection.

- 3. An adequate framework for modeling complex embedded systems is crucial. Many frameworks are engineer-oriented but unfortunately informal. On the contrary, many methodologies that introduce formal techniques are too complex what compromises

their usability. Adequate integration of formal techniques into the engineering design process is an important task to be addressed.

- 4. A verification methodology capable of addressing the whole set of requirements of typical specifications is worth having. Verification methodologies usually focus on a certain kind of requirements. Nonetheless, development of critical embedded systems may demand evaluation of time, functional, and security features.

- 5. Many verification methodologies introducing formal techniques do not support automated proofs. Modeling and verifying formal models by hand may be complex, time consuming, and prone to error.

In addition, a modeling framework should effectively consider constraints imposed by embedded in-car systems:

- *Real time constraints*: Applications should act-react according to time constraints imposed by critical scenarios, e.g., car braking in a collision scenario.

- *Resource constraints*: Embedded systems are constrained by limited hardware resources, e.g., by memory, CPU power, and/or bus capacity.

- Complex heterogeneity: In-car infrastructure is quite heterogeneous and complex. A car embedded system is integrated by several kinds of HW and SW modules: processors, memories, software drivers, operating systems, user applications, security protocols, etc.

- *Complex communication:* Exchanges in distributed embedded applications are supported by complex bus policies and protocols. Overall system operation strongly depends upon them.

#### 1.3 Contributions

#### 1.3.1 Objective

Based upon identified issues, a methodology to conduct formal verification of concurrent embedded systems with respect to functional and non-functional requirements is targeted. Our main contribution is made in the scope of that methodology. Our approach adopts a global view of the engineering development process as a way to identify lacks in methodological support. Thus, the aspects to be particularly addressed are:

- a. *Modeling of embedded systems (HW-SW):* To ensure its usability, a modeling framework should ease integration of formal languages and be also adequate for analyzing features of embedded systems.

- b. *Modeling of functional and non-functional requirements:* Development of automotive embedded systems often demands verification of time, functional, and also security requirements. A framework suitable for those tasks is worth having.

- c. *Representation of threats model required in security proofs:* System features are proved against an attacker model. The effectiveness of achieved system protection strongly depends upon threats model accuracy.

- d. *Framework formalization and verification:* In order to keep our approach engineer oriented, formal issues are not introduced at modeling level. Instead, formalization is made by model transformation and verification is carried out at backend level exploiting formal based tools.

- e. Assessment of attack protection: A stage that precises the extent of verification results is proposed. A post-verification analysis is introduced in order to show satisfied/unsatisfied requirements as well as respective covered attacks.

- f. *Functional and non-functional tests:* Code is automatically generated from verified models. However, handmade code may be integrated so as to execute the application inside a host platform. A stage is proposed to validate final implementation features.

#### 1.3.2 Thesis Approach Synopsis

First, a set of uncovered security aspects in automotive embedded systems is precised. To do so, the development of in-car embedded applications in the last decades is exposed what shows how security has been addressed. Several aspects that have been barely or not covered at all are thus identified. Afterwards, the support offered by current verification methodologies to the engineering development process is analyzed. The objective is to identify/precise lacks that may impede effective protection of embedded systems. The analysis is conducted as follows. Several verification methodologies are reviewed, their main features exhibited, and the support provided to the engineering development phases evaluated. Since lacks are identified in several phases, an overall methodology is accordingly proposed. Methodology relies upon existing security analysis techniques. Thesis contribution is made in the scope of proposed methodology. Indeed, it introduces means pursuing both missing support and effective protection against attacks. The problematic aspects signaled in section 1.2 aim to be undertaken. In particular, the design framework is extended so as to model security concerns. This contribution endows the environment with a formal semantics and makes it adequate for proving security properties. The methodology is suitable for verification of embedded systems in general. Its applicability has been partially shown in an industrial automotive project [77]. Also, some results of this work have been published [159], [160].

#### 1.4 Outline

This manuscript is structured as follows. In chapter 2 a state of the art of embedded automotive applications is exposed. Among others, the chapter shows several aspects that have impeded appropriate embedded systems protection. Chapter 3 evaluates the features offered by several verification methodologies and shows the lack of support to certain engineering development phases. Justifications to thesis contributions are precised in this chapter. The global methodology that aims to undertake identified issues is shown in chapter 4. Stages introducing a contribution are accordingly highlighted. A main contribution consists in introducing formal techniques without compromising modeling framework usability. Chapter 5 is dedicated to show it. To show approach applicability, the methodology is applied in an industrial automotive case study that is exposed in chapter 6. Since the methodology supports both safety and security analyses, two instances are respectively targeted. The conclusions and work perspectives are finally provided in chapter 7.

# Chapter 2 Security and Vehicular Applications

In this chapter we precise several aspects that may render vehicle applications not enough secured. To do so, a survey on vehicular applications evolution is first shown. This survey provides an explanation about why security became a trendy topic of research in the automotive domain. It shows the late introduction of security in applications development, and the initial efforts performed for securing. The main goal consists in assessing to which extent security protections may nowadays result ineffective. Afterwards, a typical mobile architecture is described what exhibits the complexity of current on-board in-car systems. Complexity of embedded architectures is a challenge for achieving security goals since it notably increases the difficulty of system analyses during development [120]. A reference automotive architecture is mostly taken from an European project that targeted security of distributed on-board applications [77]. Several threats in vehicular networks are summarized relying upon the reference architecture. More particularly, infrastructure weaknesses, threats, and potential impact are shown. The conclusions summarize our findings and justify the need for improving certain aspects in methodological support.

#### 2.1 Vehicular Applications Evolution and Security

#### 2.1.1 80's Decade Developments

At early eighties, several proposals were published pursuing remote control of vehicles from a traffic center. For instance in [17], vehicles receive control signals via rail guides connected to Radio Frequency (RF) antennas. Several in-vehicle functions are directly programmed on microprocessors and many of those functions target vehicle safety. Indeed, speed control, collision avoidance, and emergency braking applications receive guideway inputs and react in consequence. Even if safety was stated among the general objectives, the main goal was traffic improvement by settling policies according to transport demand in real time. However, no security aspect is considered at all and the approach focused only on functional aspects.

Focusing on functional concerns is a tendency observed in many efforts published during mid and late 80's. Some standalone applications delivered as a vehicle add-on roughly addressed security. On the contrary, in many other instances security is not addressed at all. For example in [16], a technology for vehicle identification based upon RF is presented. The system pursued identification and location of vehicles with a fixed schedule, e.g., buses, trucks or even rail guided cars. It is recognized that communication between RF

readers and vehicle's card may be perturbed by physical factors - like Electromagnetic Interference (EMI) [221]. However, it is claimed that the system can be applied in sensitive services like toll payment, even if no security analysis is conducted [16].

In late 80's, in-vehicle systems conception evolves towards a more autonomous approach. Instead of envisaging a remote automated control of vehicles, driver's role is kept whereas in-car applications only assist the driver. Since developing in-car applications became challenging and costly, the communication between vehicles and outside world should be first justified [220]. The in-car architecture evolved from being a set of standalone application-oriented controllers, to an internal network of processing units. As explained in [80], increasing the number and complexity of in-car applications would likely increase the number of transfers. Thus, a message in-car network is proposed as an efficient solution to avoid bottlenecks. The envisaged network is composed by a Master Station that provides global facilities and controls a two-wire bus to which Control Units are connected. Control Units are in charge of a wide range of dedicated devices, like sensors, display, wipers, lights, and also generic device arrays. A diagnostic Station is introduced for monitoring and storing overall bus exchanges and other critical device operations, e.g., in engine control unit. Such facility is intended to perform off-service vehicle diagnostics by wired connection. Among the benefits of this in-car network are easier installation and reconfiguration, and the ability for supporting more advanced subsystems [80]. Nonetheless, the approach does not address any security aspect and development objectives remained functional and safety oriented.

#### 2.1.2 90's Decade Developments

In early 90's, technologies became more specialized leading to a growing complexity. Along with that, drawbacks and challenges of in-car networks are pointed out. As stated in [135], a failure in a complex inter-connected system may affect several components. Oppositely to previous standalone architectures, in-vehicle networks target reconfiguration and scalability what also increases complexity. Thus, even typical components with a very good record of failures became inter-dependent what impacted overall system reliability [135]. Consequently, other requirements than purely functional ones arose. In the work presented in [135], possible sources of failure are classified: Random Failures, due to physical misbehaviour or damage, Systematic Errors, due to wrong HW or SW designs, and Intermittent Failures, due to environmental conditions. To cope with those failures, redundancy in system components is proposed, e.g., double or triple processor architectures in charge of equivalent functions. Nevertheless, redundancy is not enough to cope with Systematic Errors, since they mainly depend upon faulty system specification or design [135]. Even if formal verification is mentioned as a mean to ensure correctness no formal analysis is conducted.

A milestone for consolidation of in-vehicle networks was the development of communicating protocols. Several efforts were conducted to deploy not only in-car but also V2I and V2V communications. This tendency was greatly motivated by projects launched during late eighties like PROMETHEUS and DRIVE. Those projects mainly targeted traffic management and control. As mentioned in [66], roadside communication architecture mostly remained local. More intelligence and computing power were settled in on-board systems. Rather than proposing new applications, many efforts were dedicated to deploy prototypes of proposed embedded systems, e.g., the one in [66].

Two domains integrating vehicle architectures are clearly identified: one for the in-car network (on-board) and the other for the envisaged overall network of vehicles and roadside architecture - also referred as vehicular or off-board network. Nodes within in-vehicle network are modular SW/HW components named Electronic Control Unit (ECU)s. They support local and distributed vehicle applications. ECUs are interconnected via a variety of buses and links. It is observed that industry and academy progressively changed the objectives of both in-car and off-board networks. Rather than an automated control of traffic, ameliorate vehicular safety became a major concern [15]. A way to improve vehicular safety is to virtually increase driver vision ahead, e.g., by implementing advisory warning systems. An example of those systems is thoroughly specified in [15].

At mid and late 90's, consolidation and spreading of internet architectures, and more specifically the IEEE 802.x family became evident - e.g., [106]. That tendency likely influenced the introduction of wireless technology in vehicular networks. Along with that, security requirements were finally considered in the development of systems. Nonetheless, analyses were not yet thoroughly performed [50]. Two main trends are identified [50]: define protocols only when necessary and be aware of potential applications integration in the future. Even if formal techniques are not applied, the need of formal methods for proving final implementations is recognized [50]. The growing interest upon in-vehicle applications, like autonomous intelligent cruise controls, collision reduction, and collision warning radar systems is observed. Maturity in those applications is such that integration into high-end vehicles is considered as imminent [70]. Even if many safety critical applications were under development, only a few measures were taken with regard to potential impact of security threats.

#### 2.1.3 2000's Decade Developments

By early 2000's, research in vehicular domain is rather focused on improvement of technology via system design. As mentioned in [118], challenges in development of in-vehicle systems are compared to those faced in other safety critical areas like aerospace, medical, and nuclear power. Vehicular networks have critical characteristics since they are dynamic, time-sensitive, and potentially large [118]. Neighbour vehicles change over the time and a trade-off between the need for mutual authentication and privacy arose. Since exchanges between vehicles may be safety critical, their processing becomes highly time-constrained, e.g., for collision avoidance systems. Time-critical applications made clear the need for means that ensure efficient communication and processing. As a consequence, priority, schedule, and hybrid based communication buses were introduced. More precisely, the Controller Area Network (CAN), Time Triggered Architecture (TTA), Local Interconnect Network (LIN), and FlexRay protocols are applied in on-board architectures [118]. Afterwards, a variety of wired and wireless based technologies were developed so as to extend and improve protocol capabilities. For instance, the TT-CAN [144] targets fault tolerance - i.e., overcome from messages collision -, determinism in transmission - i.e., ensure upper time bounds -, higher bandwidth, and more flexibility - i.e., bus policies adapted to applications changes.

As can be noticed from several works [155], [97], security is not anymore an add-on but a mandatory aspect for ensuring critical safety goals. Along with inherent lossy characteristics of transmission channels, messages can also be intentionally corrupted or modified by hostile parties [155]. As summarized in [51], vehicles became "communications hubs with multiple wireless connections". In-car applications are capable of communicate with remote servers via roadside architecture - i.e., V2I - and also with other vehicles - i.e., V2V. Such distributed mobile approach imposed new security challenges to the on-board network. It is recognized that traditional security solutions resulted unpractical for the limited resources offered by embedded systems [51]. A taxonomy of hazards threatening vehicle domain is accordingly elaborated. The taxonomy categorizes attackers and techniques, system targets and vulnerabilities, and the impact of hostile actions. Security gaps in embedded systems like vulnerable crypto protocols [48] and invasive attacks [125] are mentioned as trend topics. It is highlighted that the side effects in case of system misbehaviour, failure, or attack may even endanger human lives [119].

The ECU architecture became a target of security analyses. Weaknesses of embedded platforms even in lower layers - e.g., network layer - may also compromise ITS operation. As discussed in [97], several security vulnerabilities were identified in ad-hoc routing protocols like AODV [161], DSR [65] and wireless Media Access Control (MAC) IEEE 802.11 [107]. Assuming a cooperative environment is among the causes of identified vulnerabilities [97]. A malicious router node can alter or drop packets in order to deviate, generate loops, divide the network and isolate vehicles. In addition, a malicious party can pervasively inject junk packets thus flooding network resources. The introduction of an attacker to conduct security analyses is highlighted [97]. Vulnerability analyses revealed several security concerns in the whole ECU stack. They range from physical up to application layers, e.g., preventing Denial of Service (DoS), protecting MAC, and routing protocols, securing end-to-end communications, preventing viruses, protect applications, etc. Security became a primary concern that was undertaken via platform services [97] that pursue authenticity, confidentiality, integrity, anonymity, and availability. Hash-Based MAC (HMAC) and digital signatures are proposed as protections for network layer. A Public-Key Infrastructure (PKI) is suggested as a suitable mean to perform secure V2V and/or V2I (V2X) communications, even if it demands more on-board computing power. It is recognized that proposed security solutions do not cover all possible operation scenarios, e.g., protocols may be exploited by unanticipated attacks. In addition, no effective solution is recognized for certain attacks like DoS [167] even if they are recognized as critical [61]. The deployment of evaluation methodologies and toolkits is suggested as a way to effectively secure vehicle embedded applications.

The fact that several security issues were initially not thoroughly addressed motivated new initiatives from industry and academy. In particular, the efforts targeting development of ITS architectures were strongly oriented by security concerns. The design of secure automotive systems is conducted relying upon model-based approaches [110]. Rather than considering security as an afterthought, systems should be secure by design. A common method for securing is identified in several initiatives [124], [156], [157]: first, the need for security is identified. A threats model representing some generic or specific threats is elaborated. Afterwards, requirements are elicited so as to cope with identified threats. Finally, the functions, mechanisms, and countermeasures that aim to fulfill requirements are deployed, what defines final ECU architecture. In [124], the authors consider that "intelligent attackers" have not been yet introduced in design of vehicular networks. A multidefense paradigm is proposed for designing secured on-board and off-board applications. The design process consists of several protection phases applied at different platform layers. Several approaches addressing criteria for securing vehicular applications followed similar paradigms, e.g., [227], [156], [182].

By late 2000's, several questions raised with respect to the gap between required and achieved security. Even if several standalone off-the-shelf applications are secured, it is recognized that in-vehicle distributed applications may still be compromised. Consequently, safety sensitive applications may misbehave [156]. Since ITS failures may impact stakeholders safety and economy, ITS trustworthiness is still at stake.

#### 2.1.4 From 2010 Up to Now Developments

At late 2000's and early 2010's, several projects were launched to boost and harmonize development, implementation, and deployment of ITS technologies [158]. Many of those projects were funded by international organizations interested on deployment of ITS at large scale. A tendency to standardize not only applications but also deployment processes is observed [158]. Thus, several specifications and designs were developed based upon commonly accepted approaches like the Model Driven Engineering (MDE) [5]. Launched projects progressively precised and targetted significant issues, e.g., [173]. Protection of sensitive in-vehicle and driver data is mandatory so as to avoid disclosure of secret material. Also, on-board diagnostic applications, like flashing SW images, face a landscape of cyber threats including viruses and spyware [158]. It is highlighted that V2X facilities open a window to dangerous remote attacks that may compromise driver safety, economy, authority, and privacy [156]. Along with security, other characteristics are evaluated like platform functionality, performance, buses bandwidth, and cost [158]. Since interoperability across countries is pursued, technology integration and applications standardization are relevant aspects to be discussed. Table 2.1 shows a summary of projects leading the development of vehicle on-board and off-board networks. It summarizes some initiatives launched to address several ITS concerns like on-board and off-board security, large scale implementation, technology interoperability, and tests under real conditions.

Table 2.1: Projects pursuing development and deployment of offboard and on-board networks

| Project                                      | Main Goal                                                                    |  |

|----------------------------------------------|------------------------------------------------------------------------------|--|

| NoW                                          | Definition of communication protocols and data security for V2V and V2I      |  |

| 2004-2008                                    | applications. A bench for functional tests was provided [145]                |  |

| SEVECOM                                      | Achieve overall security of V2X communications. Specified architecture       |  |

| 2006-2009                                    | considers a threats model and targets authenticity, integrity and privacy of |  |

|                                              | over-the-air exchanges. $[173]$ .                                            |  |

| EVITA                                        | Specify, design, verify, prototype, and test a prototype architecture for    |  |

| 2008-2011                                    | securing in-car applications. A threats model, security requirements, formal |  |

|                                              | verification, and functional tests were conducted relying upon a Hardware    |  |

| Security Module (HSM) based prototype. [77]. |                                                                              |  |

| Continued on next page                       |                                                                              |  |

| Project    | Main Goal                                                                       |  |  |

|------------|---------------------------------------------------------------------------------|--|--|

| GEONET     | Provide the technology for scalable and reliable distribution of information    |  |  |

| 2008-2011  | to concerned vehicles on a geo-region. The project provided a scheme            |  |  |

|            | and protocol for intelligent message forwarding and distribution for safety     |  |  |

|            | applications [88]. Security is not addressed.                                   |  |  |

| SimTD      | Specify and implement the in-car and roadside architecture for realizing        |  |  |

| 2008-2012  | V2X communication in a large-scale real scenario. The vehicular network is      |  |  |

|            | evaluated in terms of reliability and efficiency. Political and legal aspects   |  |  |

|            | are also addressed [174].                                                       |  |  |

| OVERSEE    | Specify an open architecture for execution of Original Equipment Manu-          |  |  |

| 2010-2012  | facturer (OEM) and no-OEM applications offering a single access point for       |  |  |

|            | internal and external communications. A virtualized architecture is proposed    |  |  |

|            | in combination with a $HSM$ to achieve security goals [153].                    |  |  |

| DRIVE-C2X  | Settle the foundation for rolling out automotive cooperative systems in         |  |  |

| 2011-2013  | Europe. Several V2X technologies will be tested - e.g., SimTD - in a multi-     |  |  |

|            | country scenario and results will serve as underpinnings for future standards.  |  |  |

|            | In particular, privacy in communications is addressed [73].                     |  |  |

| PRECIOSA   | Prove from a prototype, that a pan-European vehicular architecture can be       |  |  |

| 2011-2014  | implemented protecting sensitive information of drivers and vehicles. Results   |  |  |

|            | should provide models, ontology, and verifiable architecture for protecting     |  |  |

|            | privacy of individuals in vehicles [164].                                       |  |  |

| PRESERVE   | Design, implement, and test an integrated V2X architecture satisfying se-       |  |  |

| 2011 -2014 | curity, cost, and performance requirements. The ECU-HSM architecture            |  |  |

|            | prototyped in the EVITA project should become as close as possible to an        |  |  |

|            | off-the-shelf product. The platform is tested under realistic conditions [165]. |  |  |

| C2C-CC     | Organization targetting the development and release of ITS standards. Along     |  |  |

| 2004-?     | with validation of V2I architectures, it also pushes the harmonization of       |  |  |

|            | V2V standards worldwide [186].                                                  |  |  |

After a brief projects reviewing, we observe that the the gap between secure prototype platforms and off-the-shelf products is being filled [165]. Also, the structure of ITS on-board and off-board architectures is more clearly specified - see [77], [174]. Nevertheless, development of embedded systems still faces some challenges. For instance, increase computing power improves on-board throughput but it is costly, and faulty or inefficient SW designs may easily vanish benefits of HW acceleration [111]. Moreover, since automotive applications are distributed at both on-board and off-board levels, estimate realistic upper bounds for response delays may be difficult or even impossible [111]. Thus, to develop safety/time critical applications, the fulfillment of respective constraints must be first ensured.

Along with adequate throughput, the protection of sensitive material - e.g., private keys - stored inside the vehicle is a major challenge. Indeed, PKI schemes do not only demand more computing power but also require secure storing and controlled access. Even if efforts were conducted to reinforce security and to adapt existent security modules - like the Trusted Platform Module (TPM) [194] -, certainty about requirements fulfillment is not yet achieved [82]. Inadequate HW performance, limited set of crypto functions, non-scalable configuration, and high cost are mentioned as main drawbacks of existent security modules. As explained in [198], an overall protection for in-vehicle ECUs needs to be specified. To achieve this objective, an HSM-based solution is proposed. The HSM follows a modularized approach and plays the role of trusted security anchor within the ECU stack. This

ECU/HSM solution is specified at three architectural levels covering different needs in HW acceleration, crypto algorithms, and internal processing modules. Tamper protection shields are also settled in order to avoid unauthorized data manipulation. HSM-based solutions combine modularized and scalable architecture that can be implemented in a cheap application oriented circuitry, e.g., Application-Specific Integrated Circuit (ASIC). The use of HSM modules has been considered in several works and projects, e.g., [181], [153], [164]. Even so, security modules and top embedded applications are also concerned with fault injection and side channel threats, i.e., the ones introducing/sensing electromagnetic perturbations in/from physical layer. In particular, as explained in [75], fault injections targeting clock cycles or memory cells operation may provoke applications misbehavior so as to undermine security shields deployed in HW or SW. Such kind of security cracks may not only be provoked by electromagnetic sources but also emulated by SW [130]. It implies that SW viruses are also capable of reproduce/emulate certain fault injection threats.

We finalize our survey presenting some tendencies in development of in on-board and off-board vehicle technology. It is commonly accepted that car accidents and severity can be decreased by endowing vehicles with a variety of driver assistance applications. As explained in [78], many safety applications are currently integrated in vehicles. Some off-the-shelf instances are Forward Collision Warning, Adaptive Cruise Control (ACC), Collision Mitigation Brakes, Low Speed ACC, Night Vision, Lane-passing Alarm, and Brake Assist with Navigation Link. The recent introduction of technologies for enlarging buses bandwidth - like Multimedia Oriented Systems Transport (MOST), offering up to 24.8 Mbps - speeds up the operation of on-board distributed applications what improves systems availability and security. A broad consensus exists on the fact that upcoming technologies and deployments require security in order to ensure their operability in real hostile environments [78]. Among the main challenges faced by embedded systems engineering are an adequate elicitation of safety and security requirements. It is agreed that requirements elicitation has not been sufficiently addressed [78]. Overall embedded systems protection should still be thoroughly addressed by development methodologies [91].

#### 2.2 Current Vehicles Architecture

This section presents a fine grained view of current automotive architectures. The architectural description is taken as a reference to show associated security concerns. Uncovered security aspects are described in next subsection 2.3. Some parts of the technology are currently under development and still need to be secured and tested.

Current in-vehicle networks exhibit general characteristics of standard computer networks. An in-car network counts dozens of interconnected nodes named ECUs supporting thousands of inter-dependent SW applications which are composed by gigabytes of code [166]. In addition to existent on-board applications, several off-board facilities are being developed in order to communicate vehicle with outside world. The ECU nodes are linked via a variety of buses like CAN, MOST, FlexRay, LIN or Byteflight. ECUs are HW/SW components integrated by modules that are structured by layers. ECUs play dedicated roles within the network: they may be sensors, gateways, routers, actuators, etc. Along with a generic role, ECUs also support a variety of high level applications. ITS deployment shall introduce new safety-critical applications, e.g., emergency braking systems, operating in parallel with non-safety critical ones, e.g., infotainment media. The introduction of X-by-wire technology [118] shall allow ECUs to fully or partially automate a variety of mechanical systems like those controlling brakes or accelerator, e.g., Brake-by-wire. Recently, the steering-by-wire technology was introduced in commercial vehicles by the first time ever [143].

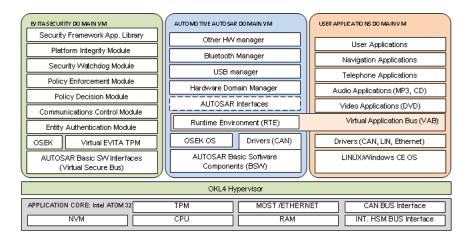

Several principles are being applied to secure embedded systems. As suggested in [85], the use of virtualization techniques may help to deal with interactions from attackers. By categorizing and separating ECU applications according to their exposure to threats, their exchanges can be better controlled and the system protected. It is considered [85] that Virtual Machines can be used to enforce security requirements in combination with tamper resistant modules like the TPM [194] or the HSM [198]. Just referred modules are the basis upon which ECU security is built since both can play the role of security anchors: they provide mechanisms to enforce platform integrity, authenticity, confidentiality, and freshness. Even so, TPM and HSM own different features. In particular, the TPM is standardized what favorably impacts applications development and portability. The HSM is not standardized but provides HW acceleration, modular architecture, more cryptographic primitives, and a Coordinated Universal Time (UTC) clock, all not supported by the TPM. Figure 2.1 shows the crosslayer modular composition of an ECU supporting security, safety, and user oriented applications. This architecture specification is borrowed from [13].

Figure 2.1: Modular structure of an applications ECU stack

Figure 2.1 shows applications separation what allows to sanitize exchanges from untrusted sources. The architecture is composed by three virtual machines controlled by a central hypervisor named OKL4 [150]. A virtual machine is settled for containing SW modules in charge of overall security - leftmost box. The AUTOSAR [37] machine is in charge of standard automotive and safety oriented applications - box in the middle. Finally, user oriented and other untrusted applications are embedded in a separated machine rightmost box. On-board and off-board communicating facilities can also be installed within the user oriented virtual machine. To protect overall ECU architecture a security anchor is proposed. The root of trust enabling security for the ECU is the HSM proposed in [198]. Just described complexity is a challenge for achieving required applications performance, temporal constraints fulfillment, and also security. Platform complexity may impose difficulties to adequately analyze, design, and implement embedded systems [120]. ECU nodes distribution and configuration vary upon carmakers. Next paragraphs present two complementary on-board architectures that are under deployment and test. The SimTD initiative specifies ECUs architecture for achieving off-board communication, i.e., V2X communication. Complementary, the EVITA approach specifies on-board network mainly targetting secure in-car applications.

The SimTD architecture [181] is intended for large scale vehicular communication networks. The architecture is divided in two parts, one harmonizing in-vehicle service components, and the second one comprising the infrastructure for services provided offboard. Thus, on-board architecture is mainly integrated by three interconnected ECUs with a modular crosslayer composition:

- **CCU:** The Communication Control Unit (CCU) that provides a link between on-board and off-board networks. Along with V2V facilities, the CCU provides Global Positioning System (GPS), Universal Mobile Transmission System (UMTS), WLAN and G5a,b connections for external services. For exchanges between internal components, the CCU supports CAN and Ethernet LAN protocols. The CCU behaves as a router directing incoming and outgoing message flows.

- AU: The Applications Unit consists of safety and non-safety related applications on the top of the crosslayer component. Middleware layer relies upon the Java/OSGI platform [152] and supports security modules, communication, navigation, and other services. Lower layer is the host Operating System (OS) Windows XP Embedded that holds the whole stack.

- **HMI:** The Human Machine Interface receives input from safety and non-safety applications in the AU. It provides driver with information via graphical and sound interfaces. Thus, Human-Machine Interface (HMI) is tightly coupled to AU operation.

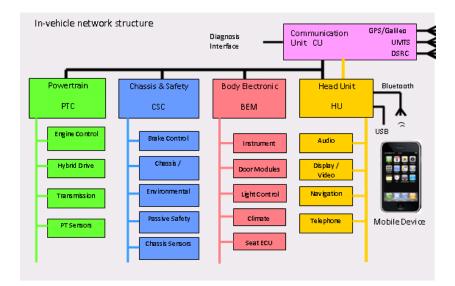

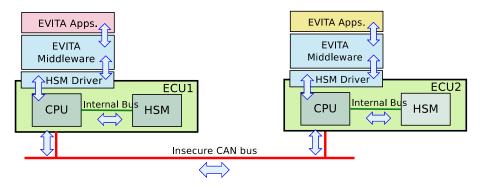

Figure 2.2: Reference architecture for developing secure in-vehicle applications in the EVITA project

The goal of SimTD architecture is to achieve an efficient platform for long distance wireless communication - WiMax, Long-range WiFi, GPS, Vehicular Ad-Hoc Network (VANET) - necessary for safety oriented applications. On the contrary, the EVITA architecture specifies a secured platform mainly targetting on-board wired services. EVITA is aware about the integration of V2X technology. Thus, EVITA also supports short distance wireless communication like Dedicated Short-Range Communications (DSRC) and Bluetooth. The reference architecture for applications deployment is presented in figure 2.2. The reference architecture is a network of ECUs grouped in application-oriented domains. Each colored rectangle in figure 2.2 corresponds to an ECU. The domains contain a master ECU and several specific oriented sensor and actuator ECUs. The master ECU controls the domain and plays the role of gateway. The CCU links on-board architecture with external services, roadside communication architecture, and vehicles. Thus, CCU incorporates DSRC, UMTS, GPS/Galileo, and 802.x antennas. The CCU routes internal and external message flows by interacting with respective master ECUs and gateways. Many applications in charge of safety critical tasks like braking or vehicle steering are installed in Powertrain and Chassis and Safety ECUs, i.e., PTC and CSC, respectively. The Body Electronic Module ECU (BEM) includes applications usually activated/deactivated by the driver like lights, wipers, climate, and door locks. Infotainment applications are supported by the Head Unit ECU (HU). In addition, the HU may be in charge of safety critical applications and tasks like alert displaying and automatic emergency calls. EVITA architecture shows the complexity of current on-board networks.

#### 2.3 Uncovered Security Aspects

In previous section an overview of automotive architectures was presented. This section highlights some uncovered security aspects taking the automotive architecture as reference. Since, uncovered security aspects may render automotive architectures vulnerable, several attacks are documented and explained. The respective impact of security vulnerabilities is also shown.

#### 2.3.1 Critical Security Aspects

Security aspects that need to be considered in development and deployment of embedded applications are described in next items.

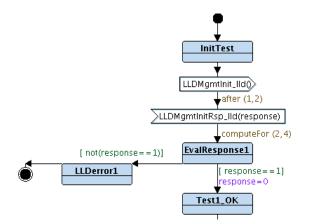

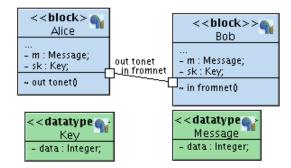

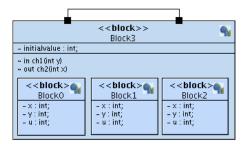

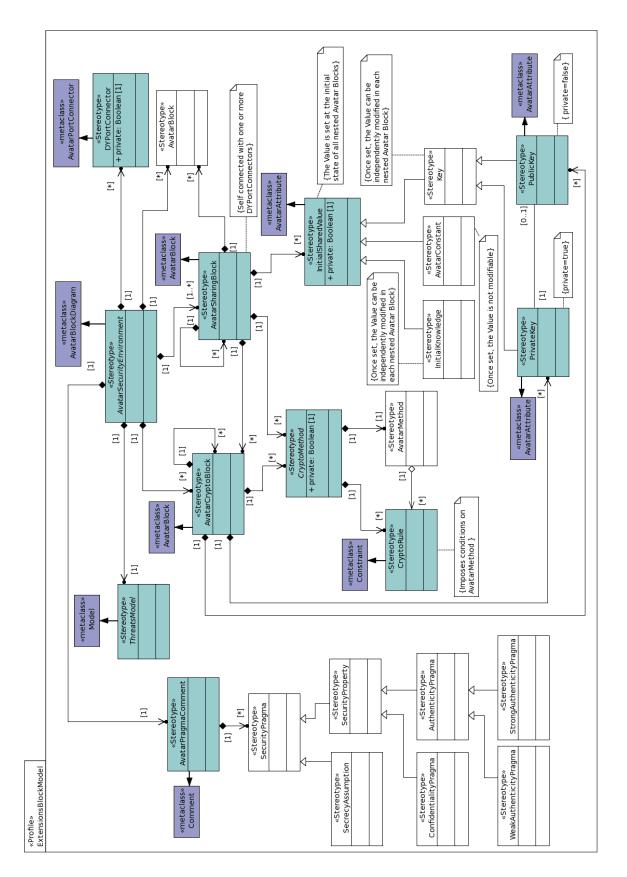

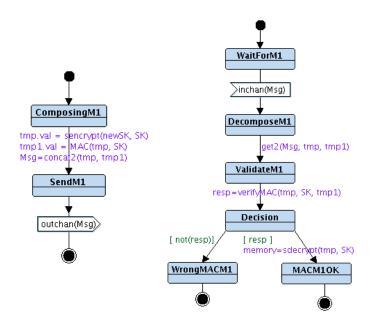

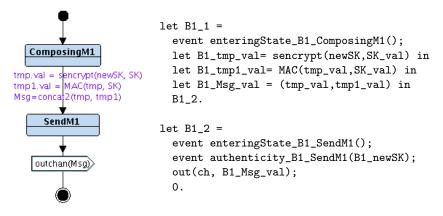

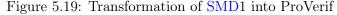

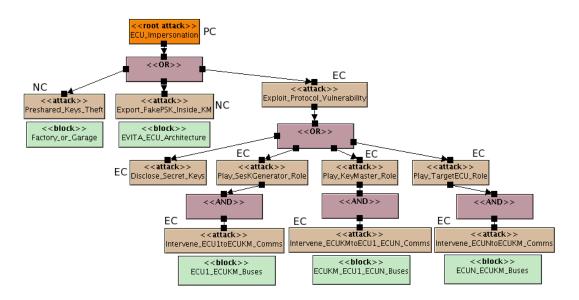

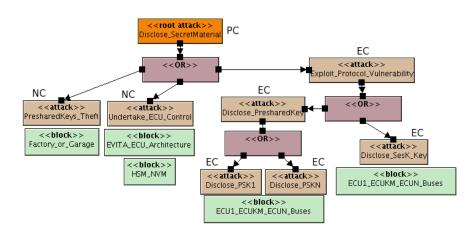

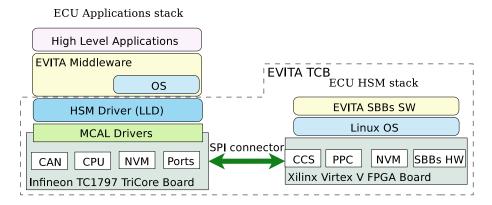

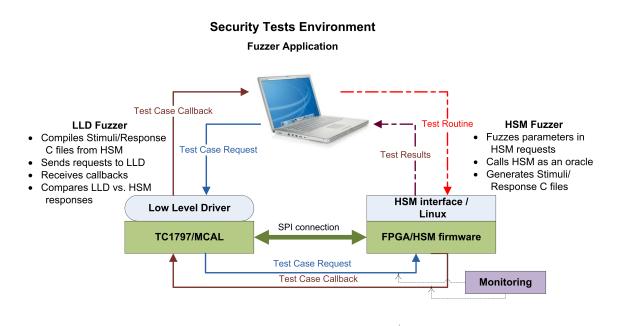

Insecure Wired Channels: On-board buses like CAN, FlexRay, and Ethernet are open and accessible, e.g., by on-board ports connection. Above mentioned links are mainly conceived to fulfill functional and performance criteria but do not consider possible security threats. In particular, communicating protocols were originally deployed without assuming a hostile environment and little or no effort was put on securing [118]. Thus, packets can be seen and analyzed by whoever accessing the bus. Moreover, toolkits ease analysis of exposed material what underpins subsequent hacking procedures, e.g., via CarShark [121] and Wireshark [197]. Once a bus is sniffed, respective analyses can be conducted so as to assess scenarios and possible system vulnerabilities. Other advanced techniques like reverse engineering can be applied so as to reproduce code that emulates ECU applications. Among others, emulation code can be used for probing more elaborated attack scenarios and exploiting vulnerabilities. Also, techniques like random packet injection, replaying, and fuzzing may be enough for disturbing, disrupting or flooding on-board resources. The opportunities for a hostile party targetting wired on-board channels depend upon physical access to non-protected links. Security protocols like IPsec [68] may provide certain protection to wired in-vehicle channels.