## Infrastructures and Compilation Strategies for the Performance of Computing Systems

Erven Rohou

### ▶ To cite this version:

Erven Rohou. Infrastructures and Compilation Strategies for the Performance of Computing Systems. Other [cs.OH]. Université de Rennes 1, 2015. <tel-01237164>

HAL Id: tel-01237164 https://hal.inria.fr/tel-01237164

Submitted on 2 Dec 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## HABILITATION À DIRIGER DES RECHERCHES

présentée devant

L'Université de Rennes 1 Spécialité : informatique

par

## Erven Rohou

Infrastructures and Compilation Strategies for the Performance of Computing Systems

## soutenue le 2 novembre 2015 devant le jury composé de :

| Mme   | Corinne Ancourt         | Rapporteur  |

|-------|-------------------------|-------------|

| Prof. | Stefano Crespi Reghizzi | Rapporteur  |

| Prof. | Frédéric Pétrot         | Rapporteur  |

| Prof. | Cédric Bastoul          | Examinateur |

| Prof. | Olivier Sentieys        | Président   |

| M.    | André Seznec            | Examinateur |

# Contents

| 1        | Intr              | roduction                                   | 3 |

|----------|-------------------|---------------------------------------------|---|

|          | 1.1               | Evolution of Hardware                       | 3 |

|          |                   | 1.1.1 Traditional Evolution                 | 4 |

|          |                   | 1.1.2 Multicore Era                         | 4 |

|          |                   | 1.1.3 Amdahl's Law                          | 5 |

|          |                   | 1.1.4 Foreseeable Future Architectures      | 6 |

|          |                   | 1.1.5 Extremely Complex Micro-architectures | 6 |

|          | 1.2               | Evolution of Software Ecosystem             | 7 |

|          |                   | 1.2.1 Evolving Ecosystem                    | 7 |

|          |                   | 1.2.2 Extremely Complex Software Stacks     | 8 |

|          |                   | · · · · · · · · · · · · · · · · · · ·       | 8 |

|          | 1.3               |                                             | 9 |

|          |                   |                                             | 9 |

|          |                   | 1.3.2 Alternatives to Static Compilation    | 9 |

|          | 1.4               | Contributions                               | 0 |

| <b>2</b> | Stat              | tic Compilation 1                           | 1 |

| 4        | 2.1               | On-demand Alias Analysis                    |   |

|          | $\frac{2.1}{2.2}$ | GCDS – Global Constraints Driven Strategy   |   |

|          | $\frac{2.2}{2.3}$ | Iterative Compilation                       |   |

|          | $\frac{2.3}{2.4}$ | Real-Time Considerations                    |   |

|          | $\frac{2.4}{2.5}$ |                                             | _ |

|          | 2.5               | Impact and Perspectives                     | _ |

| 3        | Jus               | t-in-Time Compilation 2                     | 5 |

|          | 3.1               | Split-Compilation                           | 7 |

|          | 3.2               | Real-Time Considerations                    | 3 |

|          | 3.3               | Just-in-Time Obfuscation                    | 7 |

|          | 3.4               | Impact and Perspectives                     | 9 |

| 4        | Dvi               | namic Analysis and Optimizations 4          | 1 |

| _        | 4.1               | Motivation                                  | 1 |

|          |                   | 4.1.1 Why Dynamic Optimizations?            |   |

|          |                   | 4.1.2 Why Binary Optimizations?             |   |

|          | 4.2               | Re-optimization of Vectorized Code          |   |

|          | 1.4               | The optimization of vectorized code         | _ |

|   | 4.3<br>4.4 | Function Memoization                                            | 47<br>50 |

|---|------------|-----------------------------------------------------------------|----------|

| 5 | Inte       | Interpreters                                                    |          |

|   | 5.1        | Performance of Interpreters                                     | 54       |

|   | 5.2        | Branch Prediction and Performance of Interpreters – Don't Trust |          |

|   |            | Folklore                                                        | 55       |

|   | 5.3        | Vectorization Technology to Improve Interpreters                | 59       |

|   | 5.4        | Impact and Perspectives                                         | 64       |

| 6 | Des        | ign and Development of Infrastructures and Tools                | 65       |

|   | 6.1        | Salto – Optimizing Assembly Language                            | 66       |

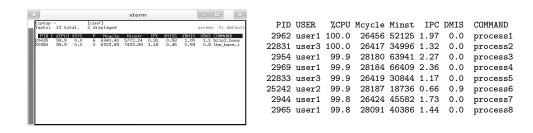

|   | 6.2        | Tiptop – Monitoring Hardware Counters                           | 67       |

|   | 6.3        | If-memo – Function Memoization                                  | 68       |

|   | 6.4        | Padrone – Dynamic Binary Rewriter                               | 69       |

|   | 6.5        | Benchmarks                                                      | 70       |

|   | 6.6        | Industrial Developments                                         | 71       |

|   |            | 6.6.1 LxBE – VLIW Compilation                                   | 71       |

|   |            | 6.6.2 Processor Virtualization                                  | 71       |

|   | 6.7        | Impact                                                          | 73       |

| 7 | Con        | aclusion and Perspectives                                       | 77       |

# Chapter 1

# Introduction

No other industry has boomed as fast as the computer industry. Hardware and software are everywhere and we rely on them every day. As a corollary of Moore's law<sup>1</sup>, the performance of computers has evolved at an exponential pace, for decades! We now live in a world where billions of sensors, actuators, and computers play a crucial role in our life: flight control, nuclear plant management, defense systems, banking, of health care. This has solved many problems, created new opportunities, and introduced new threats.

Durig this long period of time, many things have changed: form factors, constraints, even users' expectations. What remains, though, is the need for performance.

In this document, we are interested in the performance of computer systems, and in particular how software is processed to run efficiently on hardware, and how it must adapt to continuously changing features. We discuss various aspects of compilation, interpretation, and optimizations.

This chapter briefly describes recent evolution of the hardware and software ecosystems, and presents our assumptions on future computing systems. The rest of the document describes our main contributions to the field of compilation.

## 1.1 Evolution of Hardware

Software runs on hardware. Ideally, hardware and software should evolve in synergy. Unfortunately, most of times, hardware evolves on its own. This is due to many constraints, involving technology, time-to-market, business opportunities, company organizations...) Eventually, software adapts.

<sup>&</sup>lt;sup>1</sup>Gordon E. Moore is a co-founder of Intel in 1968. In 1965 he observed [Moo65] the exponential growth of the number of transistors on a chip. Performance is directly linked to the number of transistors.

#### 1.1.1 Traditional Evolution

For decades, the performance of microprocessors has followed an incredible exponential pace (Moore's law). Since the 1970s, the performance has been doubling every 18 months. The Cray-1, first installed 1976, with its 80 Mflop/s is now outperformed by modern smart-phones, sometimes by an order of magnitude.<sup>2</sup>

The most advertised metric by silicon and PC vendors used to be the clock frequency. The clock contributes only partly to the performance increase, and improvements in micro-architecture also plays a significant role. Intel reported  $[BDK^+05]$  in 2005 that the clock frequency represented 80% of the performance gains to date. It is representative of the general trend of computing systems: from 20 MHz in 1990 to 2 GHz in 2000.

Other improvements in micro-architecture include, for example, pipelining, better cache hierarchy, branch prediction, prefetch, out-of-order execution, register renaming. They are transparent to the software in the sense that code can be functionally correct, even though it ignores the underlying details. Performance, however, can be impacted, and compilers must do their best to exploit the hardware at its best.

Evolution in architecture cannot be ignored, in particular additions to the instruction set. Each new generation of processor often comes with new features, such as floating point unit, SIMD extensions, or fused multiply-add (FMA). Code generation must adapt to take advantage of the potential additional performance, sometimes at a significant effort.

#### 1.1.2 Multicore Era

Since 2002 however, despite considerable industrial effort, the frequency has been plateauing. Silicon vendors have hit a new wall: the "power wall". Power consumption has always been an issue for embedded systems. It became a concern for general purpose processors.

The dynamic power consumption is given by  $P = \alpha V_{dd}^2 f$ , where f is the operating frequency, and  $V_{dd}$  the voltage. Design constraints also make the voltage proportional to the frequency. As a rule of thumb, the power is a cubic function of the frequency. Intel's Fred Pollack illustrated the problem in a famous MICRO 1999 keynote [Pol99], comparing the power density (in  $W/cm^2$ ) of processors to various objects, ranging from a hot plate to the sun's surface. The hot plate was approached by the PentiumPro and surpassed by the Pentium II manufacturing process at 0.5  $\mu$ m, the nuclear reactor corresponds to 0.1  $\mu$ m lithography. Current process targets 22 nm! Quite a number of techniques have been proposed to address the power wall, such as dynamic voltage and frequency scaling DVFS (aka Intel SpeedStep, Turbo Boost).

Moore's law, however, is still true. More and more transistors are integrated in processors. Advances in technology and micro-architecture now translate into more parallelism. The dual core was introduced in 2006, the quad core in 2008, the hexa

<sup>&</sup>lt;sup>2</sup>Performance of supercomputers is typically evaluated by the Linpack benchmark. Android Apps are available to run it on smart-phones.

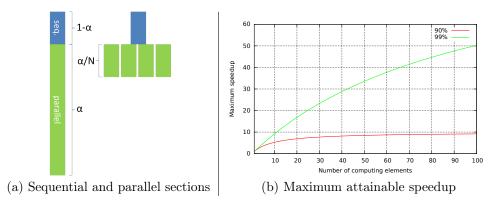

Figure 1.1: Amdahl's Law

core was available in 2010. Prototypes have been demonstrated with up to 48 and 80 cores. Kalray announced the first samples of its MPPA 256 product in 2012. Intel's Xeon Phi processors feature 50+ physical cores.

High degrees of parallelism is not new. But they used to be for experts running scientific workloads on highly expensive supercomputers. Moderate amounts of parallelism now sell at the local supermarket.

#### 1.1.3 Amdahl's Law

The consequences of this evolution on the software industry are dramatic: most existing software has been designed with a sequential model in mind, and even parallel applications contain residual sequential sections. The performance of these applications will ultimately be driven by the performance of the sequential part (as stated by Amdahl's law [Amd67]).

For simplicity, consider that a fraction  $\alpha$  of a computation can be "perfectly" parallelized on N processors, and the rest is sequential (see Figure 1.1 (a)). The overall speedup is given by

$$S_N = \frac{1}{1 - \alpha + \frac{\alpha}{N}}$$

and  $\lim_{N \to \infty} S_N = \frac{1}{1 - \alpha}$

Maximum attainable speedups for  $\alpha = 0.9$  and  $\alpha = 0.99$  are shown on Figure 1.1 (b). Assuming that 99% of an application is parallel – an overly optimistic hypothesis – speedup will never exceed  $100\times$ . While this is certainly a great speedup, 100 cores can only achieve half of it.

A more in-depth analysis of the implications of Amhdahl's law for symmetric and asymmetric multicores is developed by Hill and Marty [HM08].

#### 1.1.4 Foreseeable Future Architectures

Several studies and technology roadmaps [ABC $^+$ 06, Com07, DBLM $^+$ 07] predict that it will be feasible to integrate thousands of cores on a chip by 2020. Amdahl's law makes symmetric many-core processors less attractive for many applications, because such a high number of cores will expose the sequential bottleneck. At the same time, Intel estimates [BDK $^+$ 05] that 10-20% of applications are easily parallelizable, 60% with effort, and the rest very hard.

There are a number of factors that help us envision what future computing environments will be.

**Asymmetry** Due to Amdahl's law and the amount of legacy sequential software, we envision that future architectures will consist of many simple cores for efficient execution of parallel sections, but also a few very aggressive complex cores to execute sequential sections.

**Dark Silicon** Technology makes it relatively easy to manufacture a large number of transistors. But, due to power constraints, they cannot all be used at the same time. The large available silicon area makes it sensible to specialize parts of the chip for dedicated application domains (e.g. DSP, GPU, various accelerators) as long as they are not activated simultaneously.

Yield Manufacturing technology imposes another constraint. Design shrinks comes with increasing process variability. This means that it becomes increasingly difficult to guarantee that processors produced on the same manufacturing line are strictly identical. Large die areas make this effect even more pronounced. Vendors still need to maintain an acceptable *yield* (volume of "good" products), and thus sell most of the processors. A solution is to sort all products by functionality and performance (a process called *binning*) and sell them at difference price ranges.

All these factors call for a large diversity of upcoming processors, as well as the impossibility to predict what their characteristics will be, even few years from now.

#### 1.1.5 Extremely Complex Micro-architectures

Micro-architectures have become extremely complex, and they usually do a very good job at executing fast a given sequence of instructions. When they occasionally fail, however, the penalty is severe. Pathological behaviors often have their roots in very low-level details of the micro-architecture, hardly available to the programmer.

For example, high-end processors have dedicated hardware for floating point computations. Some Intel processors however handle denormal numbers [IEE08] thanks to a sequence of micro-operations. It is described as "extremely slow compared to regular FP execution" in the Intel Optimization Reference Manual [Int14]. We observed that a simple computation on the x86 architecture can perform up to  $87\times$  worse than expected for pathological parameters, because of micro-operations [Roh12]. A real world application suffers a  $17\times$  slowdown.

Another example relates to the SSE and AVX SIMD extensions of x86 architectures. Due to very low-level design details, mixing them results in severe penalty, typically 75 cycles [Int14]. A compiler is unlikely to produce such a situation, however, it may happen with hand-written code or when linking with legacy libraries.

These are only two examples. Intel released [Int14] a 600+ page document, filled with techniques to help programmers get the most from their processors.

## 1.2 Evolution of Software Ecosystem

The amount of software-controlled systems has never been so large. Systems of medium complexity typically consist of millions of lines of code. Legacy is more important than ever.

Thanks to binary compatibility, the continuous "automagic" increase of performance has been a very good news for software developers and users. In 1998, Todd Proebsting estimated the respective contributions of hardware and compilation technology to the performance of computing systems. His findings, sometimes referred to as Proebsting's Law [Pro98, Sco01], show that compilers double the performance of the code they generate every 18 years. Nicholas FitzRoy-Dale repeated the experiment a decade later [FD09] and obtained slightly more pessimistic results.

Still, state-of-the-art static compiler typically provide  $2\times$  to  $4\times$  speedups when optimizations are enabled, and most programmers would not forego this additional performance, especially when it comes for free. Exceptions include developers of real-time systems where the worst-case execution time is more important than the average case. In this field, optimizations may degrade the estimate because they lose critical semantic information.

Others [Pug00] have proposed to take advantage of the extra performance to recover the penalty induced by higher-level programming models and languages.

Above all, what this seemingly pessimistic law hides, is that the compiler community has been able to keep up with all architectural and micro-architectural evolutions, as well as the increasing complexity of programming languages (e.g. C++). Research in compilation during these years produced many optimizations targeted at various aspects of the architectures and micro-architectures [Muc97, App98, ASU88]. For example, deeper memory hierarchies were introduced to deal with the so-called "memory wall" because the memory subsystem could not sustain fast increase of clock rates. Numerous articles have been published on codes transformations that deal well with caches and prefetch.

### 1.2.1 Evolving Ecosystem

Programming parallel systems used to be for computer scientists, or experts in specific domains (such as physicists developing demanding applications for supercomputers). The most visible evolution of hardware in the last decade is the introduction of parallelism in commodity systems. Everyone now gets a parallel system, at the local store, for a few hundred euros. Yet, parallel programming is considerably more difficult than sequential programming.

In parallel to this evolution, many scientific disciplines have developed a digital dimension [Inr12] (computational medicine, computational biology, computational archaeology...) Domain scientists develop applications in less traditional languages, favoring productivity-friendly environments (Python, R, Matlab...), but still run computationally heavy workloads.

A steady trend is that the lifetime of many software is long, much longer than the hardware for which they are initially designed. If binary portability (i.e. the portability of the functionality) is likely to be preserved, the portability of the performance is at risk. Contrarily to what we have been used to (performance increases with the clock frequency at each new generation of hardware), performance will no longer scale automatically with the number of cores.

Processors are not the only moving target of computing systems, the entire computing environment becomes dynamic. Two relatively recent paradigms drastically changed the ecosystem: the cloud, and mobile Apps.

Cloud computing consists in using computing resources provided by a vendor, typically at a remote location, over a network. Computation can be seen as a utility — similar to gas, water or electricity. The advantage for users is the ability to provision resources (and pay for them) only when needed. The drawback is that actual hardware on which an application runs is rarely known beforehand, and often shared with other users. In the (likely) case these nodes are not identical, developers target the least capable node, and often run under-optimized code. Even during execution, other jobs can start and compete for resources at any time.

Smart-phone Apps constitute another very diverse and rapidly moving target for application developers.

#### 1.2.2 Extremely Complex Software Stacks

Taking advantage of the available compute power, software has also grown extremely complex. Real-world systems consist of many layers: hypervisor, operating system, runtimes, libraries, compilers... Each of these layers is a considerable effort. GCC, for example, has grown to more than 15 million lines of code, excluding libraries, LLVM has a few millions. Operating systems are even larger: Linux is approaching 20 million lines, while Microsoft Windows is likely closer to 100 million lines.

#### 1.2.3 Summary

To summarize, the evolution of processors recently started changing in new ways. the most radical one being the introduction of parallelism to general purpose processors. Parallelism is now for everybody, not just HPC experts. The characteristics of the architecture we envision for the mid-term future are the following: highly parallel, with many simple cores (thousands of cores will be feasible by 2020); heterogeneous, with a few very aggressive sequential cores, and various accelerators. They will be very diverse, and it will also be difficult to anticipate the characteristics of the next generation from a current state-of-the-art. Applications running on top of these processors will be large, probably old, and largely unoptimized for the current target.

## 1.3 Executing Code

## 1.3.1 Static Compilation

Compilation can be broadly defined as the translation of a program from a high-level language to a low-level language. "High" and "low" are obviously loosely defined. The C language is high-level for embedded system and operating systems developers where some pieces of code are still written in assembly language. For developers used to object-oriented programming, software components, and functional languages, the C language will appear rather low-level, and used only to address system level layers. In most of this document, compilation refers to the translation of the C language to assembly, or bytecode to assembly (sometimes, C to bytecode).

In these terms, writing a compiler for a simple language targeting a simple assembly language is a moderate effort. This is a typical assignment for groups of final-year students at engineering schools. Compilers, however, must provide much more than a simple translation, including debug support, separate compilation, packaging (libraries), profiling... And finally, compilers also optimize the code to exploit the underlying hardware as well as possible. As mentioned before, industry-grade compiler are made of several million lines of code.

Compilation technology goes back to the 1950's. Since then, an incredible body of work has been produced, from low-level code generation techniques to supporting very high-level programming languages. Entire books have been written to describe the optimizations that transform a *correct* program into a *fast* program. Optimizations are the building blocks of a compiler. Much effort has produced a wide spectrum of techniques. However, since the 1990's, except for specialized processors with dedicated instruction sets, few optimizations were able to yield more than a few percents of performance. Moreover, combining several optimizations, or running them in the wrong order, often degrades performance. And even when they do well, there is often room for improvement.

#### 1.3.2 Alternatives to Static Compilation

Static compilation is only one way to produce executable code. To facilitate the deployment of applications to diverse targets, the community has adopted bytecode representations. The ability to run Java applets in browsers made bytecode popular in the mid-1990s. Bytecodes are not natively executable by a processor, some mechanism is necessary. Several approaches exist. Historically, interpreters have been first proposed: they are simple to develop, easily portable to different hosts, but they are slower than native execution. Bytecodes can also be compiled to native code, on the target machine. This is sometimes referred to as load-time compilation: the entire application is translated at user invocation. The resulting code is close to what a static compiler would have produced, but execution incurs an initial overhead. Alternatively, install-time compilation processes the bytecode when it is first deployed, and the system keeps a native representation on non-volatile storage. Just-in-time compilation provides an interesting trade-off where the bytecode is compiled when needed, but at the granularity of a function. Overheads

are limited to processing a function, instead of the entire application, and this offers the opportunity to recompile functions over time at different optimization levels. Finally, regardless of how the native code has been produced, it can still be re-optimized by dynamic binary optimizers.

Interestingly, interpreters have seen a renewed interest in the recent years, due to the spread of languages such as Python, whose dynamic nature makes JIT compilation complicated.

### 1.4 Contributions

This document presents our main contributions to the field of compilation, and more generally to the quest of performance of computing systems.

It is structured by type of execution environment, from static compilation (execution of native code), to JIT compilation, and purely dynamic optimization. We also consider interpreters. In each chapter, we give a focus on the most relevant contributions.

Chapter 2 describes our work about static compilation. It covers a long time frame (from PhD work 1995–1998 to recent work on real-time systems and worst-case execution times at Inria in 2015) and various positions, both in academia and in the industry.

My research on JIT compilers started in the mid-2000s at STMicroelectronics, and is still ongoing. Chapter 3 covers the results we obtained on various aspects of JIT compilers: split-compilation, interaction with real-time systems, and obfuscation.

Chapter 4 reports on dynamic binary optimization, a research effort started more recently, in 2012. This considers the optimization of a native binary (without source code), while it runs. It incurs significant challenges but also opportunities.

Interpreters represent an alternative way to execute code. Instead of native code generation, an interpreter executes an infinite loop that continuously reads a instruction, decodes it and executes its semantics. Interpreters are much easier to develop than compilers, they are also much more portable, often requiring a simple recompilation. The price to pay is the reduced performance. Chapter 5 presents some of our work related to interpreters.

All this research often required significant software infrastructures for validation, from early prototypes to robust quasi products, and from open-source to proprietary. We detail them in Chapter 6.

The last chapter concludes and gives some perspectives.

# Chapter 2

# Static Compilation

In this chapter, we are interested in the translation of source code (written in a language such as C, C++) to assembly. The basic process involves parsing the input program, usually building an intermediate representation, and emitting assembly code. However, compilers doing just that produce poor code, similar to what most compilers produce when no optimization is applied (optimization level -00). Optimizations are the key to performance.

Hundreds of optimizations have been developed over the last decades, and are covered in the literature [ASU88, Muc97, App98]. Each optimization tries to improve performance by focusing on a particular aspect: removing spurious dependencies, eliminating redundant computations, improving usage of resources...

Unfortunately, many problems are NP-complete – register allocation [CAC<sup>+</sup>81, BDGR07] and alias analysis [Hor97] in many cases, or instruction scheduling [HG83], to name a few. Carefully tuned heuristics play a critical role in the efficiency of compilers.

Moreover, the order in which optimizations are applied also drastically impact performance. This is well known in the community as the *phase ordering problem*. And to make things worse, many optimizations are parametric (unrolling factor, size of tiles, inlining depth...) Exhaustive exploration of all cases is simply intractable.

Our research was not about proposing new optimization techniques. Instead, our approach consisted in considering the large set of existing optimizations, and in proposing alternative ways to benefit from them. Section 2.1 presents on-demand alias analysis, our proposal developed in the context of an industrial compiler to limit the cost of memory disambiguation to where it is really needed by optimizations. We then introduce GCDS in Section 2.2: a study that takes global interactions in consideration, a domain where compilers typically under-perform. Section 2.3 introduces iterative compilation, a pioneering step to overcome the phase ordering problem when long compilation times are acceptable. Finally, we contributed to the field of real-time systems, by proposing to trace necessary source-level annotations down to binary code through optimizations (Section 2.4). Section 2.5 discusses perspectives and impact.

## 2.1 On-demand Alias Analysis

On-demand alias analysis was developed while at STMicroelectronics, in collaboration with Politecnico di Milano and Harvard University. Other participants include Marco Garatti, Roberto Costa, Stefano Crespi Reghizzi, Marco Cornero. Details can be found in the following publications:

- [GCCRR02] Marco Garatti, Roberto Costa, Stefano Crespi Reghizzi, and Erven Rohou. The impact of alias analysis on VLIW scheduling. In ISHPC, 2002. LNCS 2327.

- [CGRCR04] Roberto Costa, Marco Garatti, Erven Rohou, and Stefano Crespi Reghizzi. Hardware parameters of VLIW cores and code quality factors affecting alias analysis impact. ST Journal of Research, 1(2), 2004.

VLIW stands for *Very Long Instruction Word*. It refers to a class of processor architectures where instructions are scheduled entirely statically, and execution is fully in-order. This drastically reduces the complexity of the hardware, compared to out-of-order engines. The burden of extracting instruction level parallelism is thus pushed onto the compiler, making memory disambiguation of utmost importance.

When optimizing code, compilers often need to check whether two pointers refer to the same location. When they do, they are said to *alias*. Alias analysis (aka disambiguation) is the process of proving the relationship of two references. When we can show that they always refer to the same object, the relation is a *must-alias*. Conversely, if they are guaranteed to never refer to the same object, it is a *no-alias*. Otherwise, the relationship is classified as *may-alias*.

Alias analysis is an expensive analysis, both in terms of computation time and allocated memory. It needs to track all the possible values of pointers. For each pointer, it must identify all the possible objects that can be referenced. As the compiler optimizes the program, the internal representation changes, sometimes in radical ways. The analysis must then either continuously update its information, or recompute it regularly. Since alias analysis operates on pairs of pointers, the number of queries is also quadratic in the number of memory references.

We proposed *on-demand* alias analysis [GCCRR02] to limit the cost of computations, and illustrated it in relation with instruction scheduling for a VLIW processor. The alias analysis phase can be seen as a server, and optimizations needing information about memory references are the clients making the queries.

The performance of the generated code is dictated by the critical path of the data dependence graph (DDG) – the longest path between any two instructions. When a memory-induced dependence is on the critical path, the scheduler invokes the disambiguator. If such memory references can be proved *no-alias*, the corresponding edge is deleted, and the critical path shortened. Edges that are not on the critical path need not be checked, since deleting them would not contribute any shorter schedule. We proposed two heuristics to select when the disambiguator is invoked.

Static criterion: all queries are made on the original DDG, before the scheduler starts. With this criterion, we consider edges on the critical path, and invoke the analyzer as long as the length is reduced. The process then repeats with the new critical path. The queries are independent of the chosen scheduling

algorithm, because it operates on the original DDG. However, this approach cannot take resource conflicts into account and may produce less efficient schedules.

**Dynamic criterion:** queries are made while the scheduler progresses. When checking for ready-instructions, it also consider instructions that have only memory-related dependencies. Depending on the respective priorities of the instructions, we may invoke the disambiguator and try to delete an edge in the DDG.

Our analysis is intraprocedural and flow sensitive. It disambiguates structure fields, but not elements within an array (transformations involving arrays are typically performed at a higher level of representation, earlier in the compilation flow).

We first implemented [GCCRR02] our approach in the SUIF [WFW<sup>+</sup>94]/Machine SUIF [SH02] compiler infrastructure targeting a fictitious 4-issue VLIW processor (similar to the STMicroelectronics' ST200 family [FBF<sup>+</sup>00]). We experimented with several benchmark suites (SPEC 95, Mediabench, PtrDist). We observed that disambiguating only few edges, in the order of 20%, benefit the scheduler. The dynamic criterion also generates much fewer requests, yet achieves nearly the same speedup. We also confirmed that only optimized code really benefits from alias analysis.

We also experimented [CGRCR04] our approach on top of the industrial, fully optimizing C compiler LxBE (described in Section 6.6.1), targeting the ST200. We considered two components of the compiler: partial redundancy elimination (PRE) [KCL<sup>+</sup>99] and three instruction schedulers: pre-scheduling is performed before register allocation to avoid false dependencies. Post-scheduling executes after register allocation to handles potential spill code. A modulo scheduler [LF02] also optimizes eligible loops. In addition to dependence information, the latter also requires distance information. Schedulers need no-alias information to delete spurious dependences; PRE needs must-alias to identify redundancy.

We studied the impact of architectural parameters, as well as the effect of compiler optimizations. Unsurprisingly, the general trend is that more hardware resources make alias analysis more beneficial. Additional load/store units make it more important, as well as increased issue width. Even though the ST200 already features a sizable register file, additional registers (we experimented with up to 512 registers) reduce the amount of spill code and thus decrease the impact of alias analysis, but only marginally.

Many compiler optimizations remove redundant computations and cause memory instructions to be on the critical path. In this case, alias analysis contributes to the final performance by letting the schedulers move them easily across each other. Certain optimizations eliminate memory instructions (such as scalarization, or load-store elimination). In such cases, the impact of alias analysis is clearly reduced. Overall, disabling optimizations in the compiler halves the speedup brought by alias analysis, from  $5.2\,\%$  down to  $2.7\,\%$  on the reference ST200, and from  $9.1\,\%$  down to  $4.4\,\%$  on a fictitious 8-wide machine with 512 registers and two load/store units.

## 2.2 GCDS – Global Constraints Driven Strategy

GCDS was developed at IRISA, within the framework of the FP5 European project OCEANS. Other participants include André Seznec, François Bodin and Christine Eisenbeis. Details can be found in the following publications:

- [RBES00] Erven Rohou, François Bodin, Christine Eisenbeis, and André Seznec. Handling global constraints in compiler strategy. IJPP, 28(4):325– 345, 2000.

- [Roh98] Erven Rohou. Infrastructures et Stratégies de Compilation pour Parallélisme à grain fin. PhD thesis, University of Rennes 1, Nov 1998.

Compilers excel at local optimizations; but they have a hard time making global decisions. Traditional compilers process fragments of an application at various granularities (files, functions, regions, basic blocks...), but sequentially. Some compilers apply inter-procedural or link-time optimizations to re-optimize some parts of the program, but goal is to propagate information, such as constants, across classical optimization boundaries. And while ordering of optimizations has received a lot of attention, global interactions have remained mostly unexplored. Still, fragments are not – by far – unrelated. Many metrics, including code size, execution time, or register pressure, depend on the inter-relations of many fragments. It happens frequently that improving a metric on one fragment degrades another metric on the same fragment or on another one.

The structure of conventional compilers is not appropriate for dealing globally with issues such as code size and execution time. A built-in strategy locally applies a set of heuristics on code fragments in order to optimize the execution time. However, most optimizations that attempt to improve performance also increase code size [BGS94], therefore increase the overall instruction cache footprint of the program. Some code generation decision which seemed to *locally* conduct to a performance increase may result in a *global* net performance loss due to a raise of instruction cache misses. Final code generation decision should be taken globally rather than locally!

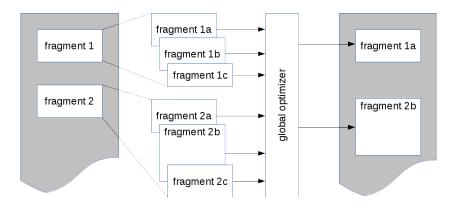

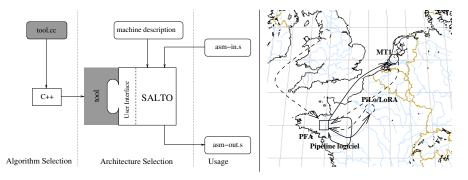

We proposed a global approach named GCDS (Global Constraints Driven Strategy) [RBES00], and we demonstrated it on the global trade-off performance vs. code size: relevant code fragments are identified through profiling and each fragment is optimized several times, in different ways. The individual characteristics of all resulting code are measured and fed to a global solver that optimizes for one criterion under constraints (see Figure 2.1). We focused on finding the best possible performance given a maximum code size, but other trade-offs can be possible.

We experimented with the Philips TriMedia TM-1000 [Cas94], a 5-issue VLIW processor dedicated to high-performance multimedia applications, featuring guarded instructions, latencies of one, two, three, and seventeen cycles, and a 3-cycle delay slot. Benchmarks consist in video decoders for two standards: *H263*, with six different input bitstreams; and MPEG2, with five different video sequences.

We selected five standard optimization sequences for VLIW processors.

$S_0$  applies the minimal set of transformations: local scheduling followed by register allocation.

- $U_n$  applies loop unrolling (n times), followed by superblock formation, and elimination of conditional jumps thanks to the insertion of predicates. Instruction scheduling and register allocation finalize the code generation.

- $U'_n$  is similar to  $U_n$  but register allocation is performed before scheduling. This decreases the code compaction potential, but usually requires fewer registers.

- SP applies software pipeline to single basic block loops. [Lam88, RBES00].

- I causes the function calls to be inlined. The large resulting body is scheduled before register allocation is performed. Inlining results in a larger block with more potential parallelism. It can also enable further transformations prevented by the function call, for instance software pipelining.

For each optimized fragment, we measured the resulting code size directly on the assembly file. Performance is estimated thanks to a linear cost model, simple yet sufficient for VLIW architectures. Trips counts are collected from profiling information. The selection of the best overall optimization sequence for each fragment is modeled as an integer linear programming problem, fed into a Simplex solver.

The optimizations are implemented within our Salto framework (see Section 6.1). We used  $lp\_solve$  to solve to ILP problem. We identified six loops from H263 and five loops from mpeg2play which account for more than 40% of the total running time.

Figure 2.2 shows the performance achieved by GCDS under various code size constraints on our benchmarks. For selected performance points of mpeg2play, we also report the selected sequence for each loop. Despite the small number of loops and transformations involved, a large number of optimal design points are produced. This reflects the intrinsic complexity of the interactions at play between optimizations, and hints at the difficulty to achieve good performance with only a local view.

To better emphasize the importance of considering global impact, we also report the results of the following experiments.

Figure 2.1: GCDS Principle

Figure 2.2: GCDS Results: best performance under code size constraint

- For each fragment, we select the best performing (local) optimization sequence, regardless of code size. Corresponding results are reported on Figure 2.2 with the label [1].

- For each fragment, we choose the transformation with the best asymptotic performance. No profiling is used, but loop bounds known at compile-time are exploited. Loop unrolling is constrained to choose higher unrolling factors only if they increase performance by at least 10%. Lack of profiling information may cause inefficiencies, for example by invoking the modulo scheduler, despite the fact that the minimum number of iterations is not reached. This configuration is similar to a static compiler with local view only. It is reported as label [2] on Figure 2.2.

The analysis showed that even a very limited number of fragments is enough to generate very complex interactions. Using the GCDS approach, we were able to compute much more sensible solutions than the reference industrial compiler, for example by reducing the code size by  $50\,\%$ , while maintaining the performance level at  $99\,\%$  of the maximum.

## 2.3 Iterative Compilation

Iterative compilation was developed at IRISA, in collaboration with the University of Manchester and the University of Leiden, within the framework of the FP5 European ESPRIT project OCEANS. Other participants: André Seznec, François Bodin, Mike O'Boyle, Toru Kisuki, and Peter Knijnenburg. Details can be found in the following publications:

- [BKK+98] François Bodin, Toru Kisuki, Peter M. W. Knijnenburg, Mike F. P. O'Boyle, and Erven Rohou. Iterative compilation in a non-linear optimisation space. In Workshop on Profile and Feedback-Directed Compilation, in conjunction with PACT, 1998.

- [vdMRB<sup>+</sup>99] Paul van der Mark, Erven Rohou, François Bodin, Zbigniew Chamski, and Christine Eisenbeis. Using iterative compilation for managing software pipeline-unrolling tradeoffs. In SCOPES, 1999.

- [Roh98] Erven Rohou. Infrastructures et Stratégies de Compilation pour Parallélisme à grain fin. PhD thesis, University of Rennes 1, Nov 1998.

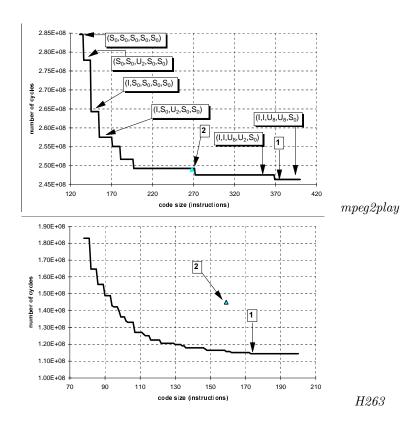

Compiler optimizations have been studied for decades. Ultimately, their goal is improve the performance of the code, based primarily on static analysis, possibly with the help of profiling information. However, actual performance depends on many fine grain details of the micro-architecture, and often also on input parameters. In the presence of hundreds of optimizations (some of them parametric), analytical models can hardly predict what the final performance will be, or even how to reach it.

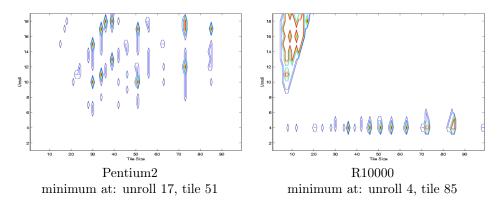

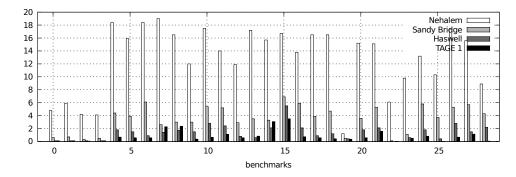

We showed [BKK<sup>+</sup>98, Roh98] that two optimizations only are enough to produce a very irregular transformation space. Figure 2.3 represents how the execution time of matrix multiplication on the Philips TriMedia TM-1000 processor (z-axis) varies when loop unrolling and tiling change their parameters (respectively unrolling factor

Figure 2.3: Iteration space on TM-1000, varying unrolling factor and tile size

and tile size). Such spaces are also highly dependent on the target architecture. As an example, Figure 2.4 graphically identifies the portion of the search space within  $20\,\%$  of the absolute minimum, for two architectures: Intel PentiumPro and MIPS R10000. The PentiumPro has a more dispersed range of minima, the R10000 has most of its points close to the minimum.

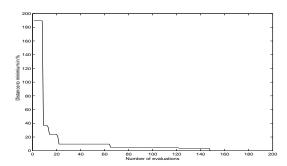

Given the shape and the irregularity of the search space, static and analytical model can hardly find the best combination of parameters. We proposed *iterative compilation* to search through this space for "good" local minima by compiling and running several versions of an application, and using actual running time as a feedback. This is possible only if the compilation time constraint is relaxed, but this is typically not a problem in many scenarios, especially for embedded systems, scientific libraries, etc.

The search algorithm was not focus of our research. We used a simple algorithm that visits a number of points at spaced intervals. Points between the current global minimum and the average are added to a queue. Elements are iteratively taken from the queue, and their neighborhood is visited, at spaced intervals. The algorithm stops when a given number of points have been visited.

Figure 2.5 illustrates the convergence of our algorithm on the R10000 architecture. The behavior is identical on all architectures. In the case of the R10000, the absolute minimum is found in 150 iterations, but it reaches 10% of the best per-

Figure 2.4: Local Minima for Intel PentiumPro and MIPS R10000

Figure 2.5: Successive performance points, for R10000

formance in 21 iterations. In the case of large transformation spaces, we achieved 0.3% of best performance by visiting less than 0.25% of the whole space, and we found the absolute minimum after visiting less than 1% of space.

Existing static analyses are still very relevant, as they can provide initial seed points to start the iterative search.

We also showed that adding a third optimization – padding, with size from 1 to 10 – invalidates the findings of two optimizations. As an example, without padding, the best transformations on a Sun UltraSparc are for unroll = 3. When padding is also considered, however, none of the points within  $20\,\%$  of the minima have an unroll factor of 3. This demonstrates the close connection of transformations and the error introduced when considering them separately.

We also applied iterative compilation [vdMRB<sup>+</sup>99] to the exploration of tradeoffs between loop unrolling and software pipelining, and the combination of highlevel transformations with low-level optimizations. This pioneering step in the late 1990s eventually developed into a rich field (see Section 2.5).

## 2.4 Real-Time Considerations

This research is being conducted at Inria, with the framework of the ANR project 12-INSE-0001 WSEPT, and the PhD of Hanbing Li. Other participants include Isabelle Puaut. Details can be found in the following publications:

- [LPR14] Hanbing Li, Isabelle Puaut, and Erven Rohou. Traceability of flow information: Reconciling compiler optimizations and WCET estimation. In RTNS, 2014.

- [LPR15] Hanbing Li, Isabelle Puaut, and Erven Rohou. Tracing flow information for tighter WCET estimation: Application to vectorization. In International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), 2015.

Real-time systems have become ubiquitous. For this class of systems, correctness implies not only producing the correct result, but also doing so within specified timing constraints. Designers are required to estimate the worst-case execution time (WCET) of their systems to guarantee that all applications meet their time constraints. Many WCET estimation methods have been proposed, operating through static code analysis, measurements, or a combination of both. By definition, the estimate must be safe, i.e. it must be an upper bound of the time required to execute a given task on a given hardware platform, in any condition. To be useful, WCET estimates shall be as tight as possible, i.e. as close as possible to the actual worst-case. This second property is useful to avoid over-provisioning the system.

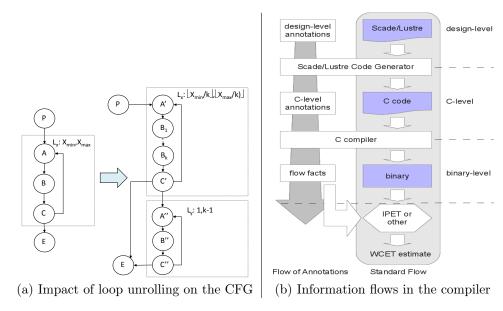

WCET estimation tools take into account any possible flow of execution in the control flow graph, regardless of actually semantically feasible flows. Additional information that limits the set of possible flows of control (the so-called *flow information*) improves the tightness of WCET estimates. Flow information, either produced automatically or inserted manually through annotations, is typically inserted at source code level. On the other hand, WCET analysis must be performed at machine code level. Most tools propagate high-level information to low-level code by building the corresponding control flow graphs and matching them. Between these two levels, hundreds of compiler optimizations – some very aggressive – may have a dramatic effect on the structure of the code, resulting in the impossibility to match the control flow graphs, hence a loss of useful information. See, for example, the impact of loop unrolling alone on Figure 2.6 (a). For this reason, many existing WCET tools for real-time systems turn off compiler optimizations when computing WCET.

We proposed [LPR14] a framework to trace and maintain flow information from source code to machine code to benefit from optimizations, yet improving the WCET estimates. Instead of considering the compiler as a black-box and trying to match its input and output, we modified each optimization of the compiler to systematically update flow information. What is crucial is that transforming the flow information is done within the compiler, in parallel with transforming the code (as illustrated in Figure 2.6 (b)). There is no guessing what flow information have become, it is transformed along with the code they describe. Back to Figure 2.6 (a),  $X_{max}$  being the maximum trip count of the original loop, we can guarantee that the first

21\_\_\_\_\_

Figure 2.6: Traceability of flow information

loop (unrolled k times) iterates maximum  $\lfloor X_{max}/k \rfloor$  and the second loop (handling remaining iterations when  $X_{max}$  is not a multiple of k) iterates maximum k-1 times. In case the optimization is too complex to update the information, we always have the option to drop it. The result would then be safe, even though it would probably result in a loss of precision. However, we can also notify the programmer (or the compiler developer) that this optimization causes problems in a real-time context, making it possible to disable it. Note that only problematic optimizations must be disabled, as opposed to all of them in most current real-time systems.

Our framework considers flow information as linear constraints on the execution frequency of basic blocks. For each code optimization, it defines a set of rules that specify how constraints must be updated to reflect the transformed code. The implementation currently handles loop bounds, and we support most optimizations of LLVM, including aggressive transformations such as vectorization [LPR15].

Our implementation in the LLVM compiler shows that we can improve the WCET estimates of Mälardalen benchmarks [GBEL10] by  $60\,\%$  on average, and up to  $86\,\%$ . We also provide new insight on the impact of existing optimizations on the WCET.

Future work might consider even more complex optimizations, such as the polyhedral model. Another interesting directions consists in investigating how to trace other kinds of flow information, such as infeasible (mutually exclusive) paths.

## 2.5 Impact and Perspectives

By definition, static compilation cannot take into account varying input, or varying hardware. At most, a compiler can rely on multiversioning to handle critical versions: it then generates several versions of the most important pieces of code. The approach is however inherently limited by the code size explosion. Auto-tuning helps chose the best parameters for performance among predetermined values. Profiling can be used to specialize for a given (set of) input(s). This is effective when the chosen inputs have similar characteristics, but not reliable when the relevant inputs vary too much. From an industrial point of view, profiling is also complicated to integrate in production cycles: it requires running the workloads. The teams in charge of developing applications and doing the final integration of all software components are often different. Profiling feedback would incur a feedback also at the level of the company, between teams, with a significant organizational overhead, and thus cost.

Our research on static compilation did not attempt to develop new optimizations, or try to address particular features of architectures. Instead, our approach consisted in considering optimizations as building blocks of compilers, taking a higher level view, and tackling complex interactions of optimizations.

We showed that the cost of memory disambiguation can be lowered by focusing the analysis to the dependences that matter. In spite of the industrial environment, we obtained and published a few new results about alias analysis [GCCRR02, CGRCR04] for VLIW processors.

Iterative compilation was pioneering work that eventually yielded to a rich field, still explored today (see for example the outcome of European projects such as ACOTES [MAB+11]). To the best of our knowledge, we wrote the first publication on this topic [BKK+98] (111 citations according to Google Scholar, at the time of writing). Since then, this approach has been extended and applied to various contexts. The cluster Adaptive Compilation of the European Network of Excellence HiPEAC is partially dedicated to this topic. The Interactive Compilation Interface (ICI) is also a descendant of the initial iterative compilation proposal. It lets compiler developers interact with the compiler internals and experiment with new strategies. ICI was used in the EU project MILEPOST. It is supported by many partners, both academic and industrial (Chinese Academy of Science, NXP, Mandriva, Univ. of Edinburgh, INRIA) The Nano2012 and Nano2017 Mediacom collaborative projects between STMicroelectronics and INRIA also includes iterative compilation among the promising approaches to be considered. It is also a component of an ANR proposal currently under submission.

Interestingly, iterative compilation was motivated by the difficulty to accurately predict performance on a particular processor. The situation is much worse today than in 1998, making the approach still very relevant. In fact, the topic is still being explored, better search algorithms have been proposed, as well as coupling with machine learning techniques. Guillon et al. [GMVK13] at STMicroelectronics are also developing an approach to reduce the cost of the exploration, yet outperforming the production compiler on performance and code size.

Hardware, on the other hand, has the visibility on runtime conditions. Aggressive out-of-order processors schedule instructions based on accurate information. The downside is that they have limited visibility on the future: the reorder buffer only contains at best a few hundred instructions. Still, out-of-order processor tend to make compiler optimizations less critical than on VLIW processors. Unfortunately, they also make the behavior unpredictable and performance assessment difficult. An extreme case is reported by Hundt et al. [HRTV11] where the mere insertion of NOP instructions improves performance by visible amounts.

Just-in-time compilation and dynamic binary optimization provide interesting points to (re-)optimize applications. We discuss our contributions in Chapters 3 and 4 respectively.

# Chapter 3

# Just-in-Time Compilation

Just-in-time (JIT) compilation refers to a process where the generation of machine code happens just before it is needed – that is, after the execution of the program has started, from an input program not in native binary form. This is the typical execution setup of Javascript in web browsers (sent in source format), or Java (sent in Java bytecode).

JIT compilation goes back to the 1960's. A brief history can be found in Aycock [Ayc03]. According to him, the first occurrence is due to McCarthy for his work with Lisp on IBM 704. Significant successful works include Smalltalk in the 1980's, and Self. But JIT compilation really blossomed with the release of Java [CFM<sup>+</sup>97]. The ability to deploy programs expressed in bytecodes as *applets* that run in a browser, regardless of the underlying processor and operating system was the key enabler for this technology. Since then, a number of bytecodes and JIT technologies have appeared, for example: CLI (supported by Microsoft's .NET as well as Mono, ILDJIT, Portable.NET), LLVM, Google's NaCl, or more recently Facebook's PHP JIT

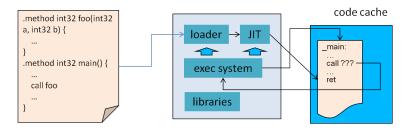

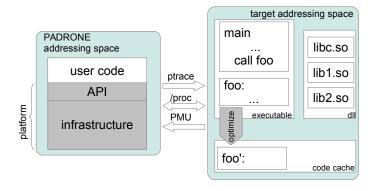

When a program is deployed in bytecode, a JIT compiler is in charge of translating bytecode to machine code as needed. The resulting code is placed in a so-called  $code\ cache$ . Figure 3.1 illustrates a high-level view of such a system. At its first invocation, a function f is compiled. Functions called by f, however, are not compiled, and call sites are replaced by trampolines, i.e. calls to the runtime system. Whenever the call happens, the system will take over, generate machine code, fix the call site, and resume execution. A function that is never called is never compiled. The name  $code\ cache$  derives from the fact that this location behaves as a hardware cache: due to the limited size, older entries must be evicted to make room for newer ones.

JIT compilation has a number of advantages over classical (or  ${

m AOT}$  – Ahead of Time) compilation.

• Only executed functions are compiled, thus reducing the memory footprint, and the overhead of code generation.

Figure 3.1: Code cache

- Profiling information can be collected before actual compilation happens, for example by relying on an interpreter for the first few calls (see for example Sun/Oracle's HotSpot [PVC01]). Collected data then drives the compilation heuristics.

- Actual parameter values are observable. Functions can be specialized, without the overhead of multiversioning, because pseudo-constants are known.

- Actual hardware is known, making it possible to generate the best possible code for a particular architecture, instead of binary compatible code that can be deployed at large, but is under-optimized on most machines.

- Re-optimization is possible. This is interesting when the context of optimization changes (such as pseudo-constant parameter that drove function specialization changes). Conversely when a function has been called a large number of times, it also makes sense to re-optimize at a higher optimization level: there is hope to recoup a higher overhead when the better function will be called many times in the future.

On the flip side, JIT compilation also has drawbacks.

- 1. Compile-time is now part of the user-visible run-time, and memory is also shared between the JIT compiler and the application being run. This is somewhat mitigated by the fact that only hot functions are optimized, and the empirical "90/10" rule (90% of the time is spent in 10% of the code) promises that the overhead will be well spent. Still, JIT compilers are limited in the aggressiveness of the optimizations they apply.

- 2. The system as a whole is more dynamic and less predictable: machine code is produced at the user/customer end, hence difficult to validate. The limited size of the code cache may force evictions, and future re-compilations. These events depend on execution patterns at the user/customer end, and are hardly predictable. This is a very serious limitation for real-time systems.

- 3. Programs to be executed under the control of a JIT compiler are typically deployed in bytecode format. The most widespread bytecodes (Java, CLI, LLVM) rely on strongly typed, high level representations of the program that

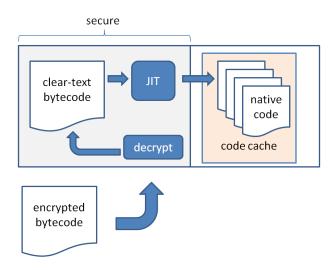

is fairly readable, easily reverse engineered, and reveal much more information than plain machine code. This may be a threat for industrials trying to protect their intellectual property, and a number of obfuscation techniques have been developed to mitigate this risk.

In the rest of this chapter, we describe three contributions related to the draw-backs of JIT compilation. First, split-compilation (Section 3.1) is a high-level proposal targeted at unleashing the potential of JIT compilation by taking the best of the two worlds: offline and online stages. We illustrate it on split-vectorization, a concrete application to vectorization: a notoriously complex yet powerful optimization. Second, we present a first step towards reconciling JIT compilation and real-time systems in Section 3.2. Third, we show how dynamic code generation and frequent recompilation can turn JIT compilers into an advantage to harden code obfuscation (Section 3.3).

## 3.1 Split-Compilation

This research has been started at STMicroelectronics, then pursued at Inria, in particular within the context of the Nano2012 and Nano2017 collaborative programs. Other participants include: Albert Cohen, David Yuste Romero, Kevin Williams from Inria, and Dorit Nuzman, Ayal Zaks, Sergei Dyshel, Ira Rosen from IBM. Details can be found in the following publications:

- [CR10] Albert Cohen and Erven Rohou. Processor virtualization and split compilation for heterogeneous multicore embedded systems. In DAC, 2010.

- [NDR+11] Dorit Nuzman, Sergei Dyshel, Erven Rohou, Ira Rosen, Kevin Williams, David Yuste, Albert Cohen, and Ayal Zaks. Vapor SIMD: Autovectorize once, run everywhere. In CGO, 2011.

- [RDN+11] Erven Rohou, Sergei Dyshel, Dorit Nuzman, Ira Rosen, Kevin Williams, Albert Cohen, and Ayal Zaks. Speculatively vectorized bytecode. In *HiPEAC*, 2011.

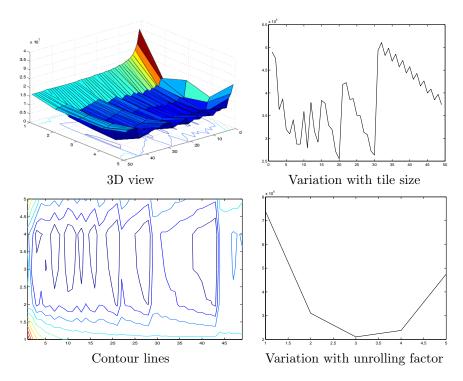

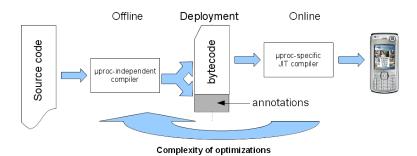

We proposed split-compilation [CR10] as a way to mitigate some of the short-comings of JIT compilation. Leveraging the multi-stage compilation (such as source-to-bytecode followed by bytecode-to-native, but other variants are possible), the key idea is to split the compilation process in two steps — offline and online, and to off-load as much of the complexity as possible to the offline step to keep the online step as lean and efficient as possible. Figure 3.2 illustrates this principle.

Offline This step occurs on the developer's workstation. Resources are virtually unlimited. Ideally, all the work should be done here. However, target and execution environment are unknown. Target-dependent optimizations are impossible – or risky at the best. Dynamic events are also unknown (program inputs, competing processes on a server), causing missed opportunities.

Online This step occurs on the user's device, at run-time. In case of an embedded system, resources are much more limited that the offline step. But the actual target system (hardware and computing environment) is known, enabling much more focused and precise optimizations.

Figure 3.2: Principle of split-compilation

| 1 [AY] 1 [AY] [AY]                                                                                     | 1 [31] 1 [31] [31]                                   |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| $\mathbf{char} \ \mathbf{a}[\mathrm{N}] \ , \ \mathbf{b}[\mathrm{N}] \ , \ \mathbf{c}[\mathrm{N}] \ ;$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| <b>for</b> ( i =0; i <1024; i++) {                                                                     | $for(i=0; i<1024; i+=4)$ {                           |

| a[i] = b[i] & c[i];                                                                                    | a[ii+3] = b[ii+3] & c[ii+3];                         |

| }                                                                                                      | }                                                    |

| (a) Scalar code                                                                                        | (b) Vectorized (pseudo) code                         |

Figure 3.3: Vectorization

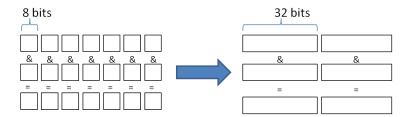

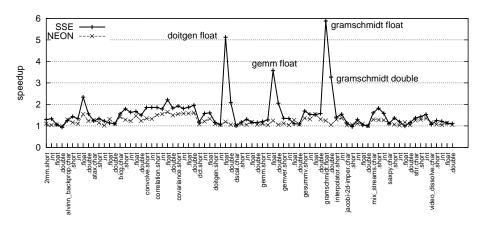

Vectorization at a Glance. In brief, vectorization is a compiler optimization. It consists in recognizing patterns of repetitive operations applied to adjacent values and packing them into larger containers (i.e. vectors). The optimized code applies the same operation in parallel to all elements of the vector. This is also referred to as SIMD parallelism (Single Instruction Multiple Data). As an example, consider the code of Listing 3.3. The original loop applies the bitwise AND (&) operator to all elements of arrays b and c. This is illustrated on the left part of Figure 3.4. The optimized loop (pseudo C code in Figure 3.3-b) loads four elements of each array at a time in a regular 32-bit register, applies the bitwise operation on the  $2 \times 4$  elements, and stores the four elements. Note also the new loop increment (i+=4).

Advantages of vectorization include fewer executed instructions, fewer memory accesses that take advantage of the wide memory bus, and fewer loop iterations. All silicon vendors now provide dedicated instructions – SIMD extensions – to manipulate vectors.

Figure 3.4: Vectorization illustrated

Vectorization can deliver high speedups when the conditions are met. Unfortunately, SIMD extensions are very diverse, in terms of vector width, supported data types, alignment constraints, supported idioms. This makes it difficult to design a multi-platform auto-vectorizer. Vectorization also relies complex and expensive data dependence analyses, as well as preparation code transformations. As an illustration, GCC-4.9 has 32,000 lines of code only for the vectorizer proper. This motivates a split compilation approach in which the identification of vectorization opportunities and their safety conditions are prepared offline.

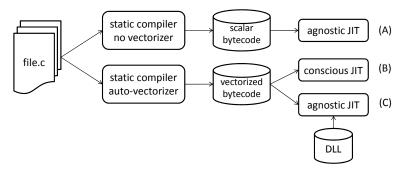

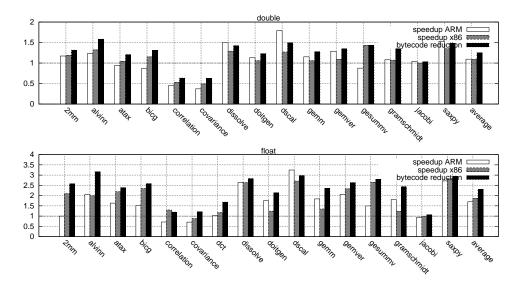

**Split-vectorization.** We proposed Vapor SIMD [RDN<sup>+</sup>11, NDR<sup>+</sup>11], developed in collaboration with IBM Haifa Research Lab. The bytecode is speculatively vectorized, in a way that is straightforward for a JIT to generate native SIMD instructions when available, yet easy to revert to scalar code when SIMD is not available.

Being a split-compilation approach, the crux of Vapor SIMD is to move as much complexity as possible from the online stages to the offline ones. Offline stages are responsible for all target independent optimizations; expensive analyses can be run, and the results encoded in the bytecode. Online stages later use these encodings to both reduce compilation time and increase code quality. Aggressive offline stages address the difficulties of automatic vectorization. Online stages allow for fine adjustments to the actual instruction set.

Our abstraction layer is built on top of the CLI format. It consists in idioms that can be translated into efficient code on any targeted SIMD ISA, yet encompass the whole spectrum of instruction sets, targeting the greatest common denominator of all platforms. We handle alignment constraints, interleaving, initialization of constant vectors, scatter/gather operations, widening, and reduction operations of basic arithmetic and more complex ones such as dot products [NDR+11]. The offline stage is implemented in GCC4CLI, our port of GCC for the CLI format (see Section 6.6.2). As far as online stages are concerned, we considered two kinds of execution systems: JIT compilers, including Microsoft .NET and Mono's open source solution, as well as a static compiler. The purpose of the latter is to compensate for Mono's limited capabilities, a more recent and less mature software than static compilers. For this, we relied on a CLI front-end for GCC that converts CLI to GCC's internal representation and the leverages all the GCC optimizations.

We define a *conscious-JIT* as a JIT that is aware of the naming convention used by the offline compiler to convey vectorization opportunities, and can generate efficient SIMD instructions accordingly. Conversely, an *agnostic-JIT* is any JIT that can process the same standard bytecode but is unaware of this naming convention or cannot make use of it to generate SIMD instructions (e.g. due to lack of hardware support).

Our flow is illustrated on Figure 3.5. We experimented with various architectures and JIT technologies. Configuration A deals with scalar code and constitutes our reference. Conscious JITs (configuration B) consist in:

- Mono for Linux on Intel Core2 Duo;

- Mono for Linux on PowerMac, with SIMD support enabled.

Figure 3.5: Scenarios: (A) regular flow; (B & C) Vapor SIMD flows

Agnostic JITs (configuration C) include:

- Microsoft .NET on Windows XP Pro on Intel Core2 Duo;

- Mono on Linux with SIMD support (SSE) disabled on Intel Core2 Duo;

- Mono on Linux for TI UltraSPARC;

- Mono on Linux for PowerMac with SIMD support (AltiVec) disabled.

Since agnostic JITs are unaware of the newly introduced naming convention, we provide an implementation in a separate dynamic library. For this purposed we relied on Mono.Simd.dll which we extended to cover all needed idioms.

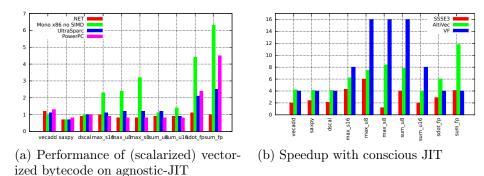

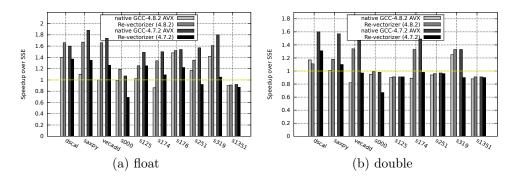

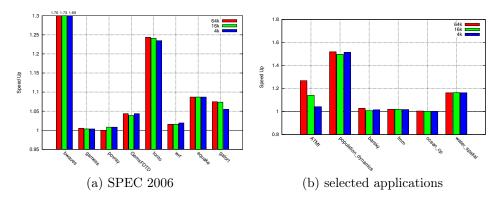

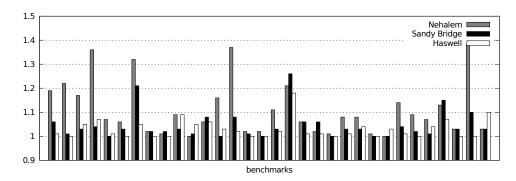

**Risk.** We first validated that our approach is risk-free, i.e. agnostic JITs incur only minor penalties. Figure 3.7-(a) reports the performance (higher is better) of configuration C with respect to configuration A. These numbers confirm that the penalty of running vectorized bytecode through an agnostic-JIT is limited. Moreover, in many cases performance even improves.

Looking at overall averages, only the .NET platform exhibits performance degradation of 7% on average. The internals of the .NET platform are not documented and its performance is difficult to analyze. However, the JIT is reported to have a low code size threshold for inlining [Nor03]. Even though the arithmetic operations in the DLL are small, they might not be inlined.

Several kernels compute reductions. The effect of scalarizing vectorized reduction code (with the arithmetic operation inlined) is similar to loop unrolling followed by modulo variable expansion (MVE). The code sample of Figure 3.6 illustrates this effect. Here we can see the critical path in the scalar loop is the circular data dependence on the accumulator. In the scalarized loop, it has been split into four independent components, thus improving performance. However, this transformation may result in aggressive unrolling (the char and short kernels are unrolled 16 and 8 times respectively) spilling of intermediate values, and in turn additional memory traffic. On PowerPC this additional memory traffic is the key factor behind

31\_\_\_\_\_

Figure 3.6: Effect of unrolling and modulo variable expansion

Figure 3.7: Performance of agnostic and conscious JIT compilers

the performance degradation of the integer kernels. The x86 platform is less sensitive to the additional memory traffic, but benefits from the relaxed dependencies due to the MVE effect.

**Efficiency.** The efficiency objective refers to performance improvements delivered by a conscious-JIT when SIMD support is available. Figure 3.7-(b) reports how the conscious JITs perform, along with the vectorization factor.

The observed speedups on PowerPC are mostly in line with the expected speedups from vectorization: they are comparable to the Vectorization Factor (VF), minus the usual overheads of vectorization (handling misaligned accesses, initializing vectors of constants, reduction prologue and epilogue, etc). However, code generation issues related to the actual JIT used in the experiment offset the results in some cases.

The vectorization impact on PowerPC is between VF/2 and VF with the exception of a few super-linear speedups. The vectorized reduction kernels suffer from the lack of global vector register allocation in Mono, which results in loading and storing of the reduction variable in each iteration of the vectorized loop. This explains the reduced speedups on the integer reduction kernels. Mono also does not perform global register allocation for (scalar) floating point registers, resulting in even more redundant loads and stores in the scalar code than in the vectorized code, which explains the super-linear speedups

Similar trends are observed on the x86 platform, however scaled down by half. Again, this is due to Mono's poor register allocation capabilities: more variables

Figure 3.8: Speedup with conscious JIT, depending on SSE level

are needed in the vectorized version (e.g. additional induction variable to advance addresses by the vector width), which on x86 with its few available registers results in register spilling. These code generation issues are not inherent to JITs in general, and work is undergoing on Mono's development branch to improve its register allocator. This would allow the benefit of vectorization to manifest itself also on targets that do not have many registers, such as PowerPC.

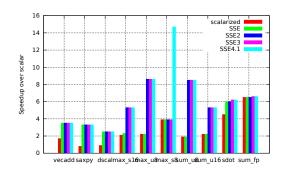

**Future-proof.** One of the motivations of our work is to support evolutions of architectures. We take a closer look at the behavior of the same vectorized bytecode on successive versions of the SSE family: SSE, SSE2, SSE3, SSE3, SSE4.1 and SSE4.2. Figure 3.8 summarizes the run times of all kernels for each supported SSE level. Relative performance is computed as the speedup over the scalar implementation.

The main observation is that speedups increase monotonically with the SSE level. The JIT compiler automatically takes advantage of the available hardware support to provide acceleration, and falls back to scalarized code for unsupported features. This is especially visible in the case of  $max\_s8$  and  $max\_u8$ , which are identical except for the signedness of the max operator. The signed max on packed bytes is introduced only in SSE4.1, whereas unsigned max first appeared in SSE2.

The horizontal add instruction was added in SSE3. It is used by sdot and sum\_fp, but only for the final reduction in the loop epilogue after the main computation loop, hence the limited impact on performance. The code size, however, is reduced.

**Summary.** We have proposed split-compilation as a way to facilitate the adoption of aggressive optimizations in the context of constrained JIT compilers. By splitting the optimization flow into two separate steps – offline and online – we can are able to make powerful analyses and transformations viable at runtime. We demonstrated our approach in the notoriously complex case of vectorization. Not only can vectorized bytecode be efficiently processed by both agnostic and conscious JIT compilers, but the performance also scales with the evolution of SSE extensions.

## 3.2 Real-Time Considerations

This research was developed at Inria, in the context of the internship of Adnan Bouakaz. Other participants include Isabelle Puaut. Details can be found in the following publications, as well as in Adnan's final report [Bou10]:

- [BPR11] Adnan Bouakaz, Isabelle Puaut, and Erven Rohou. Predictable binary code cache: A first step towards reconciling predictability and just-in-time compilation. In *RTAS*, 2011.

- [EEMR+14] Sara Elshobaky, Ahmed El-Mahdy, Erven Rohou, Layla AA El-Sayed, and Mohamed Nazih ElDerini. A lightweight incremental analysis and profiling framework for embedded devices. In SCOPES, 2014.

Virtualization and just-in-time (JIT) compilation have become important paradigms in computer science to address application portability without deteriorating average-case performance. Unfortunately, JIT compilation raises predictability issues, which currently hinder its dissemination in real-time applications. We proposed [BPR11] to start reconciling the two domains, i.e. to take advantage of the portability and performance provided by JIT compilation, while providing some predictability guarantees.

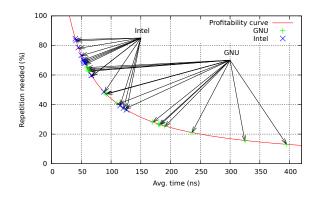

As a first step towards reconciling JIT compilation and real-time systems, we focused on the behavior of the code cache (illustrated in Figure 3.1, in previous section). Its size is limited. Similarly to a hardware cache, when no room is available for a new entry, some other entries must first be evicted. Note that arbitrarily complex cache structures and replacement policies can be used since the cache is implemented in software. In our case, cache entries are entire functions. Because they are of different sizes, memory fragmentation might be introduced.

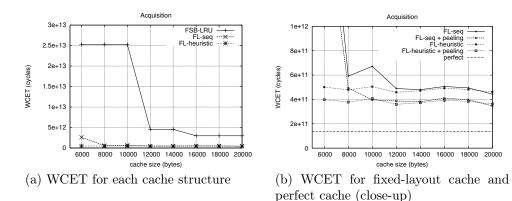

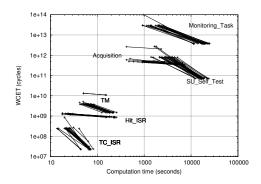

We study two structures of code caches and demonstrate their predictability. On the one hand, the studied binary code caches avoid too frequent function recompilations, providing good average-case performance. On the other hand, and more importantly for the system determinism, we show that the behavior of the code cache is predictable: a safe upper bound of the number of function re-compilations can be computed, enabling the verification of timing constraints. We explored two cache structures.

Fixed-size blocks with LRU replacement (FSB-LRU). For this first structure, the code cache is decomposed in fixed-size blocks. The block size is equal to the size of the largest binary code of all program functions. The rationale behind the selection of a fixed size for cache blocks is to eliminate external fragmentation, possibly at the cost of increased internal fragmentation. The replacement policy for this cache structure is the LRU (Least Recently Used), selecting the least recently executed function in case of eviction. LRU is known to be the most amenable to accurate analysis [RGBW07].