## Methodology of Multi-FPGA Prototyping Platform Generation

Qingshan Tang

#### ▶ To cite this version:

Qingshan Tang. Methodology of Multi-FPGA Prototyping Platform Generation. Hardware Architecture [cs.AR]. Université Pierre et Marie Curie - Paris VI, 2015. English. <NNT: 2015PA066016>. <tel-01256510>

HAL Id: tel-01256510

https://tel.archives-ouvertes.fr/tel-01256510

Submitted on 15 Jan 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

### Spécialité

### **Informatique**

École doctorale Informatique, Télécommunications et Électronique (Paris)

Présentée par

## **Qingshan TANG**

Pour obtenir le grade de

#### DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

Sujet de la thèse :

## MÉTHODOLOGIE DE GÉNÉRATION DE PLATEFORME DE PROTOTYPAGE À BASE DE MULTI-FPGA

Soutenue le 13 Janvier 2015

Devant le jury composé de :

| M.   | Laurent FESQUET | MCF        | HDR Lab TIMA         | Rapporteur            |

|------|-----------------|------------|----------------------|-----------------------|

| M.   | Adel BAGANNE    | MCF        | HDR Lab-STICC        | Rapporteur            |

| M.   | Omar HAMMAMI    | MCF        | HDR ENSTA ParisTech  | Examinateur           |

| M.   | Gérard SOU      | MCF        | HDR UPMC             | Examinateur           |

| Mme. | Helena KRUPNOVA | PhD        | Synopsys             | Examinateur           |

| M.   | Habib MEHREZ    | Professeur | UPMC                 | Directeur de thèse    |

| M.   | Matthieu TUNA   | PhD        | Flexras Technologies | Co-Directeur de thèse |

### Ph.D THESIS OF PIERRE-AND-MARIE-CURIE UNIVERSITY

### Department:

### **Computer Science**

École Doctorale Informatique, Télécommunications et Électronique (Paris)

Presented by

## **Qingshan TANG**

Thesis submitted to obtain the degree of

#### Ph.D OF PIERRE-AND-MARIE-CURIE UNIVERSITY

# METHODOLOGY OF MULTI-FPGA BASED PROTOTYPING PLATFORM GENERATION

Defense date: 13 January 2015

Committee in charge:

| M.   | Laurent FESQUET | MCF        | HDR Lab TIMA         | Rapporteur            |

|------|-----------------|------------|----------------------|-----------------------|

| M.   | Adel BAGANNE    | MCF        | HDR Lab-STICC        | Rapporteur            |

| M.   | Omar HAMMAMI    | MCF        | HDR ENSTA ParisTech  | Examinateur           |

| M.   | Gérard SOU      | MCF        | HDR UPMC             | Examinateur           |

| Mme. | Helena KRUPNOVA | PhD        | Synopsys             | Examinateur           |

| M.   | Habib MEHREZ    | Professeur | UPMC                 | Directeur de thèse    |

| M.   | Matthieu TUNA   | PhD        | Flexras Technologies | Co-Directeur de thèse |

#### Résumé

Face à la difficulté grandissante de l'intégration matériel/logiciel, le prototypage à base de cartes multi-FPGA devient obligatoire dans l'arsenal des techniques de vérification pré-silicium. Les plateformes de prototypage multi-FPGA peuvent être classées en trois catégories: sur étagère, sur mesure et câblées. La plateforme sur étagère se compose d'une carte multi-FPGA prêt à l'emploi et générique. Toutes les connexions inter-FPGA sont fixées et réalisées à l'aide de pistes sur le PCB. La plateforme sur mesure se compose d'une carte multi-FPGA conçue spécifiquement pour un design donné. Les connexions inter-FPGA sont également réalisées à l'aide de pistes PCB. Les plateformes câblées, qui se composent de plusieurs cartes mono-FPGA prêt à l'emploi, sont connectées grâce à des câbles peuvent être connectées/déconnectées à volonté. Elles peuvent être considérées comme "semi-sur étagère" par le fait qu'elles sont constituées de plusieurs cartes prêt à l'emploi, et "semi-sur mesure" par le fait que les connexions entre FPGAs sont définies par l'utilisateur et adaptées au design testé.

Nous avons dégagé dans ce manuscrit trois problèmes majeurs en matière de prototypage à base de cartes multi-FPGA: (1). L'évolution des FPGA tend à faire des entrées/sorties (E/S) une ressource rare, aggravant le problème de bande passante inter-FPGA génération après génération. En effet, les plateformes multi-FPGA souffrent des délais de communication importants inter-FPGA par rapport aux délais intra-FPGA. Par conséquent, il devient de plus en plus difficile de prototyper un design SoC/ASIC à des performances intéressantes. (2). 70% des plateformes de prototypage multi-FPGA sont des plateformes sur mesure en raison des besoins de performance et de coût. Néanmoins, la définition d'une plateforme sur mesure est aujourd'hui un processus majoritairement manuel et chronophage. Ainsi, l'exploration de cartes avec des types de FPGA différents, qui permettrait aux ingénieurs de concevoir une plateforme de prototypage optimale, ne peut pas être faite. Comme le rapport entre la capacité logique et le nombre d'E/S des FPGA est en augmentation à un rythme quasi-exponentiel, il devient de plus en plus difficile de concevoir une plateforme sur mesure performante. (3). La plateforme câblée bénéficie de la disponibilité et de la personnalisation. Les performances d'une plateforme câblée dépendent de la distribution des câbles et du placement des interfaces externes. Néanmoins, il n'existe pas d'outil permettant d'obtenir automatiquement une solution pour la distribution des câbles. Une distribution de câbles permettant d'obtenir des fréquences de fonctionnement élevées devient de plus en plus difficile à atteindre en raison de la limitation des E/S. Par rapport aux plateformes sur étagère, la valeur ajoutée, en terme de performance, des plateformes câblées et sur mesure peuvent être fortement dégradée par une définition des interconnexions entre FPGA inefficace.

Les contributions de ce manuscrit sont: (1). Un nouvel algorithme de routage exploitant les pistes multi-points connectant plus de deux FPGA, permettant ainsi d'augmenter les performances. (2). Un flot de conception automatique permettant de créer une plateforme sur mesure, augmentant ainsi la productivité et permettant l'exploration de cartes. (3). Une architecture de plateforme câblée est proposée ainsi qu'un algorithme permettant automatiquement de trouver une solution pour la distribution des câbles. (4). Finalement une comparaison entre ces différentes plateformes est réalisée d'un point de vue quantitatif et qualitatif.

Mots-clés: Circuit Intégré, Vérification, Multi-FPGA, Prototypage, Sur Mesure, Câblée

#### **Abstract**

Multi-FPGA based prototyping is no longer optional for hardware/software integration. We can classify multi-FPGA prototyping platforms in three categories: off-the-shelf, custom and cabling. The off-the-shelf platform consists of a ready-made generic multi-FPGA board, where all the inter-FPGA connections are fixed and realized using PCB traces. The custom platform consists of a build-your-own multi-FPGA board tailored for a specific design, where all the inter-FPGA connections are realized using PCB traces as well. The cabling platform consists of multiple ready-made FPGA boards connected by cables and connectors. The cabling platform is semi off-the-shelf due to that it consists of multiple ready-made boards, and semi custom due to that its connections inter FPGAs as well as connections to external interfaces are user-defined and tailored for a specific design.

There are three existing problems regarding to multi-FPGA based prototyping: (1). FPGA I/Os are becoming a scarce resource, worsening the inter-FPGA bandwidth generation after generation. Unfortunately, multi-FPGA platforms suffer from large timing delays in inter-FPGA communication compared to intra-FPGA net delays. Therefore, it becomes more and more difficult to prototype an SoC/ASIC design at proper performance. (2). 70% of multi-FPGA prototyping platforms are home-made custom platforms due to performance requirement, external interfaces, and cost. Nevertheless, crafting a home-made custom multi-FPGA platform is today a manual process, thus, time-consuming. The board exploration with different FPGA types, which helps the engineers to design an optimum prototyping platform, can not be done. As the ratio between the logic capacity and the number of FPGA I/Os is increasing at an exponential rate, it becomes more and more challenging to design a high-performance custom multi-FPGA platform. (3). The cabling platform benefits from the availability and the customization. The performance of the cabling platform depends on the distribution of the cables and the placement of the external interfaces. Nevertheless, there is no tool to automatically have a solution for the cable distribution and external interface placement. A high-performance cables distribution becomes more and more difficult to be achieved due to the pin limitation. Compared to the off-the-shelf platform, the added value, in terms of performance, of cabling or custom platforms can be heavily impaired by an inefficient board design.

The contributions of the manuscript are: (1). A new routing algorithm is proposed to spare FPGA I/Os by exploiting multi-point tracks that connect more than two FPGAs, thus increasing the performance. (2). An automatic design flow for creating a custom platform is proposed, thus increasing the productivity, enabling the board exploration, and optimizing cost and performance. (3). The cabling platform is proposed where one board is composed of one FPGA and several connectors. The connections between FPGAs as well as the connections to external interfaces can be added or removed by only connecting or disconnecting the cables (resp. daughter boards) with or from the connectors. Then, an algorithm is proposed to automatically find a solution for the cable distribution. (4). Thanks to the developed automatic tools, the achieved performances for a set of designs mapped on the three different categories of multi-FPGA platforms are compared. The performance gains between these platforms are quantified.

**Keywords:** Integrated Circuit, Verification, Multi-FPGA, Prototyping, Custom, Cabling

à mes parents

#### Remerciements

Je souhaite remercier en premier lieu mon directeur de thèse, M. Habib MEHREZ, professeur et responsable de l'équipe CIAN du département SoC du LIP6 de UPMC, pour m'avoir accueilli au sein de son équipe.

J'adresse mes remerciements les plus chaleureux à M. Matthieu TUNA, PhD ingénieur de la société Flexras Technologies, pour tous les précieux conseils qu'il m'a donnés, pour la confiance qu'il m'a témoigné et sans qui ce travail n'aurait pas vu le jour. Je lui sui également reconnaissant pour sa disponibilité, ses qualités pédagogiques et scientifiques. J'ai beaucoup appris à ces côtés et je lui adresse toute ma gratitude.

Je voudrais remercier les rapporteurs de cette thèse M. Laurent FESQUET, maître de conférence au laboratoire TIMA, et M. Adel BAGANNE, maître de conférence au laboratoire STICC, pour l'intérêt qu'ils ont porté à mon travail.

J'associe à ces remerciements M. Omar HAMMAMI, maître de conférence à ENSTA Paristech, M. Gérard SOU, maître de conférence à UPMC, et Mme. Helena KRUPNOVA, PhD chef de projet chez Synopsys, pour avoir accepté d'examiner mon travail.

Je tiens à remercier tous mes camarades de la société Flexras Technologies, M. Hayder MRA-BET, M. Matthieu TUNA, M. Zied MARRAKCHI, M. Christophe ALEXANDRE, M. Ramsis FARHAT, M. Fathi LAYOUNI, M. Christian MASSON, pour avoir eu la patience d'écouter et de répondre à toutes mes questions techniques, et pour nos longues conversations sur la vie.

J'exprime ma gratitude aussi à mes collègues du LIP6, en particulier à Mme. Mariem TURKI, M. Alp KILIC, et M. Vinod PANGRACIOUS, pour leur soutien et leur bonne humeur.

Enfin je remercie mes parents pour leur soutien au cours de ces longues années d'études et sans lesquels je n'en serai pas là aujourd'hui.

## **Contents**

| Re | Résumé |         |                                               |    |  |

|----|--------|---------|-----------------------------------------------|----|--|

| Al | bstrac | :t      |                                               | v  |  |

| Re | emerc  | iements |                                               | ix |  |

| 1  | Intr   | oductio | n                                             | 7  |  |

|    | 1.1    | Thesis  | Motivation                                    | 7  |  |

|    |        | 1.1.1   | Design Verification                           | 7  |  |

|    |        | 1.1.2   | Different Verification Techniques Pre-Silicon | 8  |  |

|    |        | 1.1.3   | FPGA-Based Prototyping                        | 10 |  |

|    |        | 1.1.4   | Multi-FPGA Platform                           | 11 |  |

|    | 1.2    | Proble  | ms                                            | 12 |  |

|    |        | 1.2.1   | Pin Limitation Problem                        | 12 |  |

|    |        | 1.2.2   | Problem of Crafting a Custom Platform         | 13 |  |

|    |        | 1.2.3   | Problem of Cabling Paradigm                   | 14 |  |

|    | 1.3    | Thesis  | Contributions                                 | 14 |  |

|    | 1.4    | Thesis  | Organization                                  | 15 |  |

| 2  | Bacl   | kground | d                                             | 17 |  |

|    | 2.1    | Introd  | uction                                        | 17 |  |

|    | 2.2    | State o | of the Art                                    | 18 |  |

|    |        | 2.2.1   | Hardwired Off-the-Shelf Multi-FPGA Platform   | 18 |  |

|    |        | 2.2.2   | Hardwired Custom Multi-FPGA Platform          | 23 |  |

|    |        | 2.2.3   | Cabling Multi-FPGA Platform                   | 27 |  |

|    |        | 224     | Comparison of Different Multi-EPGA Platforms  | 32 |  |

xii CONTENTS

|   |     | 2.2.5   | Conclusion of the State of the Art                   | 33  |

|---|-----|---------|------------------------------------------------------|-----|

|   | 2.3 | Inter-F | PGA Communication Architectures                      | 34  |

|   |     | 2.3.1   | Time-Division-Multiplexing                           | 34  |

|   |     | 2.3.2   | Logic Multiplexing                                   | 36  |

|   |     | 2.3.3   | ISERDES/OSERDES                                      | 37  |

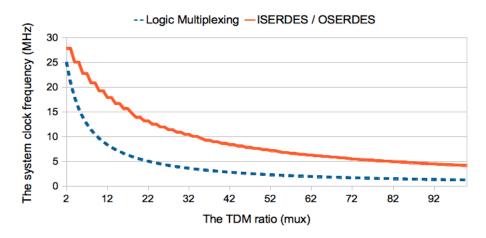

|   |     | 2.3.4   | Logic Multiplexing VS ISERDES/OSERDES                | 39  |

|   |     | 2.3.5   | Conclusion of Inter-FPGA Communication Architectures | 41  |

|   | 2.4 | Conclu  | ision                                                | 42  |

| 3 | Har | dwired  | Off-the-Shelf Multi-FPGA Platform                    | 43  |

|   | 3.1 | Introdu | action                                               | 43  |

|   | 3.2 | Platfor | m Overview                                           | 43  |

|   | 3.3 | Impler  | nentation Flow of Multi-FPGA Platforms               | 44  |

|   | 3.4 | Logic   | Synthesis                                            | 46  |

|   | 3.5 | Design  | Partitioning                                         | 46  |

|   | 3.6 | Design  | Routing                                              | 48  |

|   |     | 3.6.1   | Multi-Terminal Net Routing                           | 48  |

|   |     | 3.6.2   | Routing Algorithm                                    | 50  |

|   |     | 3.6.3   | Performance Evaluation                               | 54  |

|   | 3.7 | Experi  | ments                                                | 55  |

|   |     | 3.7.1   | Targeted Platform                                    | 55  |

|   |     | 3.7.2   | Results                                              | 55  |

|   | 3.8 | Conclu  | ısion                                                | 59  |

|   |     |         |                                                      | - 4 |

| 4 |     |         | Custom Multi-FPGA Platform                           | 61  |

|   | 4.1 |         | action                                               | 61  |

|   | 4.2 |         | m Overview                                           | 62  |

|   |     | 4.2.1   | Specific Design                                      | 62  |

|   |     | 4.2.2   | Typical Flow for Creating a Custom Platform          | 63  |

|   | , - | 4.2.3   | Problem                                              | 65  |

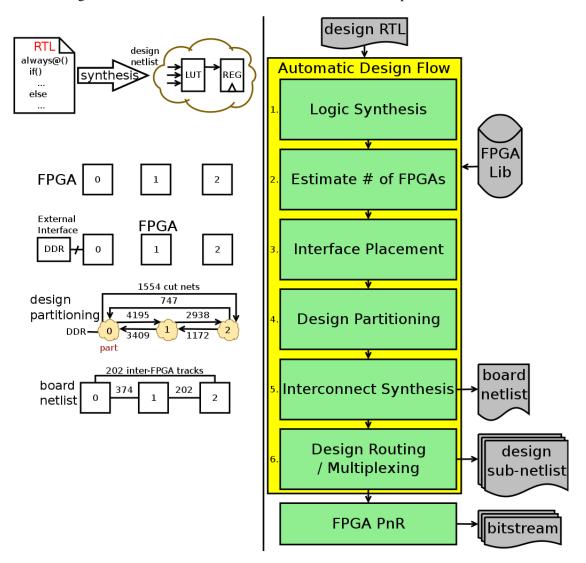

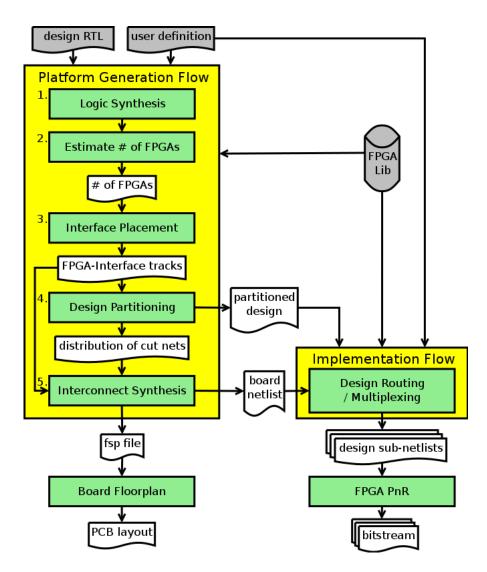

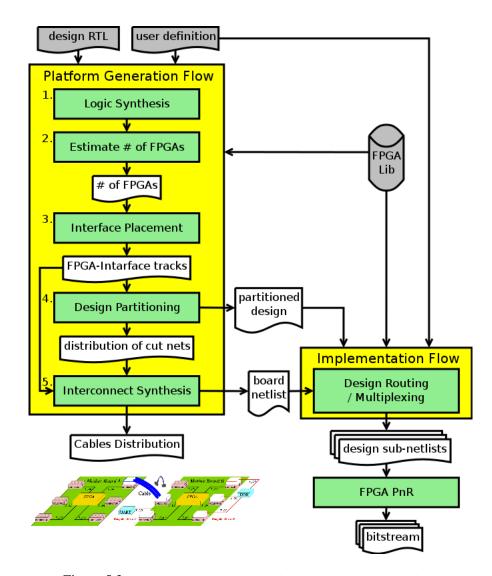

|   | 4.3 |         | verview of the Automatic Design Flow                 | 66  |

|   |     | 4.3.1   | FPGA Lib                                             | 67  |

|   | 4.4 | Logic   | Synthesis                                            | 68  |

*CONTENTS* xiii

| 4.5  | Estima  | te the number of FPGAs                                                      | 68  |

|------|---------|-----------------------------------------------------------------------------|-----|

| 4.6  | Extern  | al Interface Placement                                                      | 68  |

|      | 4.6.1   | All the External Interfaces connected to the same FPGA                      | 70  |

|      | 4.6.2   | Each External Interface connected to a different FPGA                       | 71  |

|      | 4.6.3   | Other cases                                                                 | 72  |

|      | 4.6.4   | Conclusion                                                                  | 74  |

| 4.7  | Design  | Partitioning                                                                | 74  |

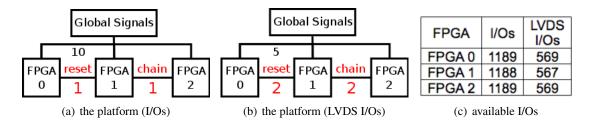

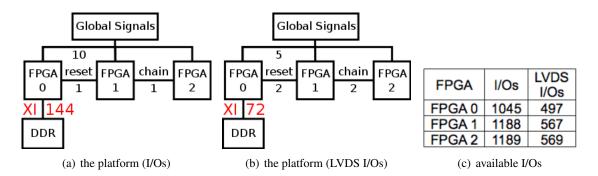

|      | 4.7.1   | Reservation of I/Os for Global Signals, Reset Chain and External Interfaces | 75  |

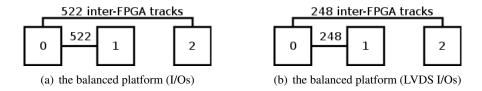

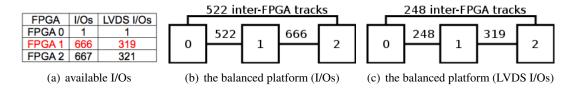

|      | 4.7.2   | Generation of the Temporary Balanced Platform                               | 78  |

|      | 4.7.3   | Conclusion                                                                  | 79  |

| 4.8  | Interco | onnect Synthesis                                                            | 80  |

|      | 4.8.1   | Generation of the Custom Platform with Only 2-Point Tracks                  | 82  |

|      | 4.8.2   | Generation of the Custom Platform with 2- and Multi-Point Tracks            | 85  |

|      | 4.8.3   | Conclusion                                                                  | 87  |

| 4.9  | Autom   | atic Design Flow for Creating a Custom Platform                             | 87  |

|      | 4.9.1   | Cost Evaluation                                                             | 90  |

|      | 4.9.2   | Performance Evaluation                                                      | 91  |

|      | 4.9.3   | Time of Availability Evaluation                                             | 92  |

|      | 4.9.4   | Conclusion                                                                  | 93  |

| 4.10 | Board   | Exploration                                                                 | 93  |

| 4.11 | Experi  | ments                                                                       | 94  |

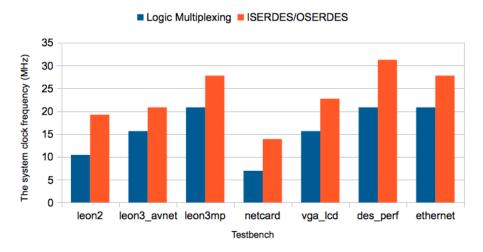

|      | 4.11.1  | Logic Multiplexing VS ISERDES/OSERDES                                       | 95  |

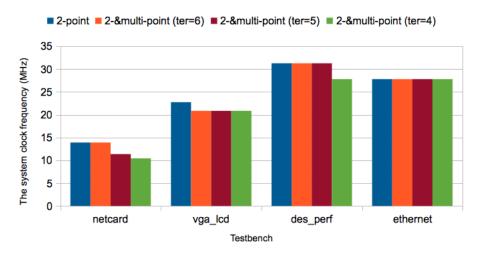

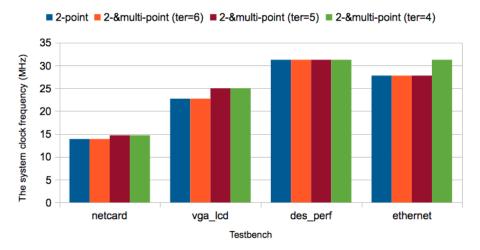

|      | 4.11.2  | "Platform with Only 2-Point Tracks" VS "Platform with 2- and Multi-         |     |

|      |         | Point Tracks"                                                               | 96  |

|      |         | Board Exploration                                                           | 98  |

| 4.12 | Conclu  | ision                                                                       | 101 |

| Cab  | ling Mu | lti-FPGA Platform                                                           | 103 |

| 5.1  | Introdu | action                                                                      | 103 |

| 5.2  | Platfor | m Overview                                                                  | 103 |

| 5.3  | Autom   | atic Design Flow for Creating a Cabling Platform                            | 106 |

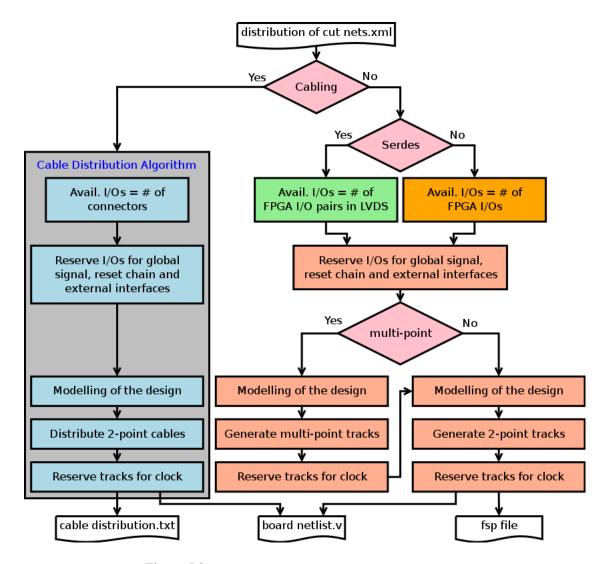

|      | 5.3.1   | Cable Distribution Algorithm                                                | 108 |

|      | 5.3.2   | Performance Evaluation                                                      | 111 |

5

XiV CONTENTS

|     |                 | 5.3.3    | Time of Availability Evaluation                          | 112 |  |  |

|-----|-----------------|----------|----------------------------------------------------------|-----|--|--|

|     | 5.4             | Optima   | al Width of Connectors                                   | 112 |  |  |

|     | 5.5             | Propos   | ed Cabling Platform                                      | 114 |  |  |

|     | 5.6             | Conclu   | ision                                                    | 115 |  |  |

| 6   | Con             | ıparisoı | n of the Different Platforms                             | 117 |  |  |

|     | 6.1             | Introdu  | action                                                   | 117 |  |  |

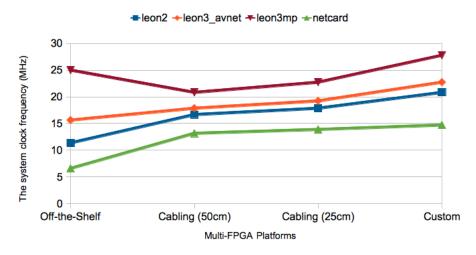

|     | 6.2             | Perfor   | mance Comparison of Different Multi-FPGA Platforms       | 117 |  |  |

|     | 6.3             | Quanti   | tative and Qualitative Comparison of Different Platforms | 119 |  |  |

|     |                 | 6.3.1    | Cabling vs Off-the-Shelf                                 | 120 |  |  |

|     |                 | 6.3.2    | Custom vs Off-the-Shelf                                  | 120 |  |  |

|     |                 | 6.3.3    | Custom vs Cabling                                        | 121 |  |  |

|     | 6.4             | Conclu   | ision                                                    | 121 |  |  |

| 7   | Con             | clusion  | and Future Work                                          | 123 |  |  |

|     | 7.1             | Summ     | ary of the Thesis                                        | 123 |  |  |

|     | 7.2             | Future   | Work                                                     | 126 |  |  |

|     |                 | 7.2.1    | Evolution of FPGAs and Analysis                          | 126 |  |  |

|     |                 | 7.2.2    | Future Research                                          | 127 |  |  |

| Lis | st of I         | Publicat | ions                                                     | 129 |  |  |

| Bi  | Bibliography 13 |          |                                                          |     |  |  |

# **List of Figures**

| 1.1  | Overall design cost                                     | 7  |

|------|---------------------------------------------------------|----|

| 1.2  | Verification technology                                 | 8  |

| 1.3  | Emulator versus FPGA-based prototype in form factor     | 10 |

| 1.4  | Three different multi-FPGA prototyping platforms        | 12 |

| 1.5  | The ratio FPGA logic capacity over I/Os                 | 13 |

| 2.1  | The off-the-shelf multi-FPGA platform                   | 19 |

| 2.2  | The typical implementation flow                         | 19 |

| 2.3  | The direct architecture                                 | 20 |

| 2.4  | The proposed routing algorithm                          | 21 |

| 2.5  | The indirect architecture                               | 22 |

| 2.6  | The hybrid architecture                                 | 22 |

| 2.7  | Create a Custom Platform for a specific design          | 24 |

| 2.8  | The typical design flow for creating a custom platform  | 25 |

| 2.9  | Cadence's design flow for creating a custom platform    | 26 |

| 2.10 | Multi-FPGA Platform: SpringBok                          | 28 |

| 2.11 | A photo of Kulmala's quasi cabling platform             | 29 |

| 2.12 | proFPGA                                                 | 30 |

| 2.13 | Synopsys HAPS                                           | 30 |

| 2.14 | The typical design flow for creating a cabling platform | 31 |

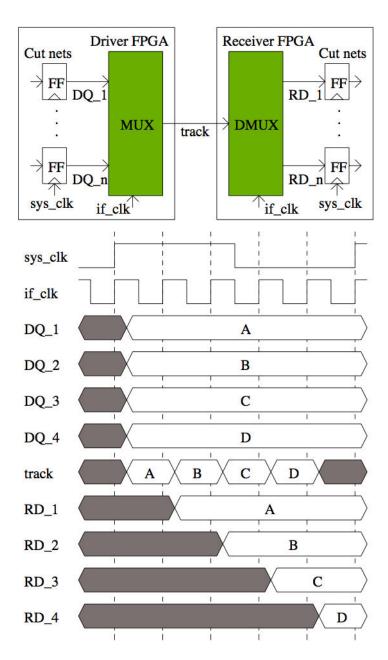

| 2.15 | The basic Time-Division-Multiplexing architecture       | 35 |

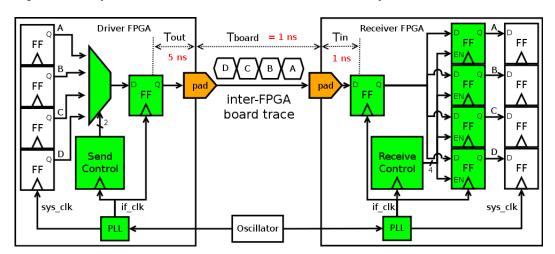

| 2.16 | Logic Multiplexing for Multi-FPGA Prototyping           | 36 |

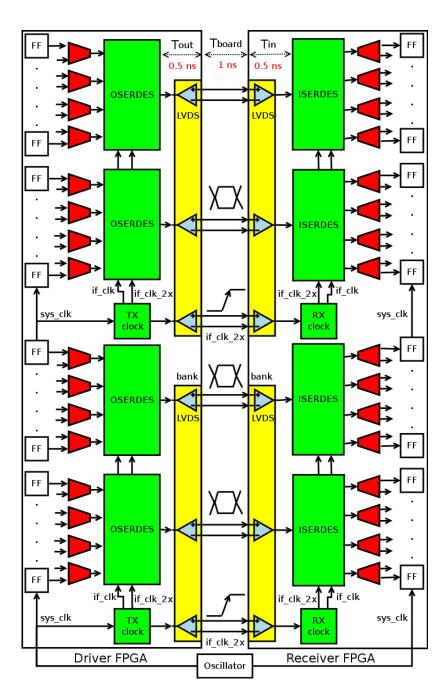

| 2.17 | ISERDES/OSERDES for Multi-FPGA Prototyping              | 38 |

| 2.18 | The DNV7F2A board                                       | 40 |

| 2.19 | Logic Multiplexing VS ISERDES/OSERDES                   | 4] |

| 3.1  | The off-the-shelf multi-FPGA platform                                              | 44 |

|------|------------------------------------------------------------------------------------|----|

| 3.2  | Typical implementation flow for multi-FPGA platforms                               | 45 |

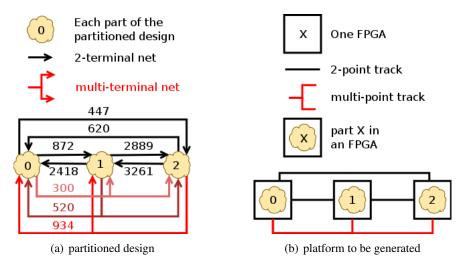

| 3.3  | The partitioned design and the corresponding multi-FPGA platform                   | 49 |

| 3.4  | Routing a multi-terminal net in 2-point tracks                                     | 49 |

| 3.5  | Routing a multi-terminal net in a multi-point track                                | 50 |

| 3.6  | The proposed routing algorithm                                                     | 51 |

| 3.7  | Routing a multi-terminal net in a multi-FPGA board                                 | 52 |

| 3.8  | Routing in 2-point tracks                                                          | 53 |

| 3.9  | routing hops in Logic Multiplexing                                                 | 54 |

| 3.10 | routing hops in ISERDES/OSERDES                                                    | 55 |

| 3.11 | The architecture of DN9000K10PCI                                                   | 56 |

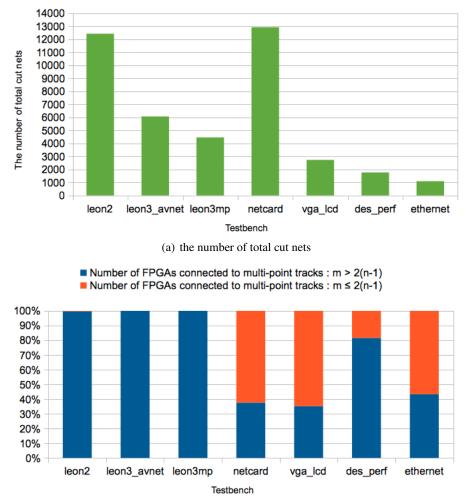

| 3.12 | The partitioning results                                                           | 57 |

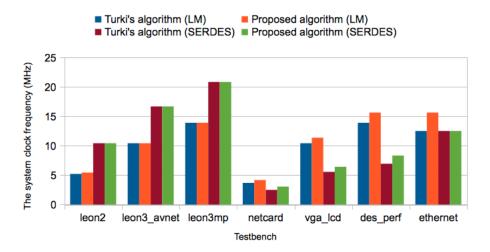

| 3.13 | The achieved performance in the off-the-shelf platform                             | 58 |

| 4.1  | Create a Custom Platform for a specific design                                     | 63 |

| 4.2  | The design flow overview for creating a custom platform                            | 66 |

| 4.3  | All the External Interfaces connected to the same FPGA                             | 70 |

| 4.4  | Each External Interface connected to a different FPGA                              | 71 |

| 4.5  | Other cases                                                                        | 72 |

| 4.6  | The temporary balanced platform generation algorithm                               | 75 |

| 4.7  | Global signals (i.e. global clock and global reset)                                | 76 |

| 4.8  | The platform after assigning global signals                                        | 76 |

| 4.9  | Global signal tracks VS multi-point tracks                                         | 76 |

|      | The reset chain                                                                    | 77 |

| 4.11 | The platform after assigning the reset chain                                       | 78 |

| 4.12 | The platform after assigning the external interfaces                               | 78 |

|      | The generation of the balanced platform in the custom platform design flow: Step 1 | 79 |

|      | The generation of the balanced platform in the custom platform design flow: Step 2 | 79 |

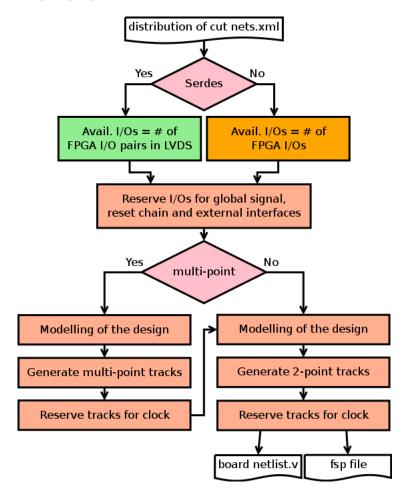

| 4.15 | The interconnect synthesis algorithm                                               | 80 |

| 4.16 | An example of the partitioned design                                               | 81 |

|      | The modelling of the design                                                        | 82 |

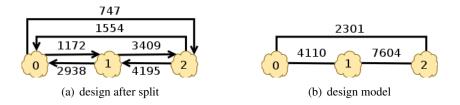

|      | The generation of the custom platform: Step 1                                      | 83 |

|      | The generation of the custom platform: Step 2                                      | 83 |

|      |                                                                                    |    |

| 4.20 | the custom platform in ISERDES/OSERDES                          | 84  |

|------|-----------------------------------------------------------------|-----|

| 4.21 | Comparison with the generic platform                            | 84  |

| 4.22 | The modelling of the design                                     | 85  |

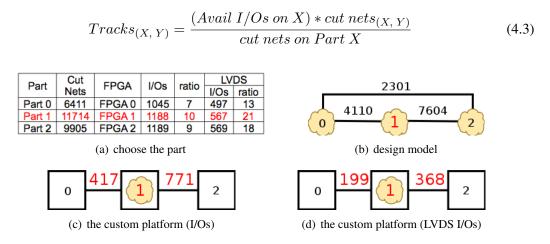

| 4.23 | Generation of multi-point tracks                                | 86  |

| 4.24 | result of the platform                                          | 87  |

| 4.25 | The automatic design flow for creating a custom platform        | 88  |

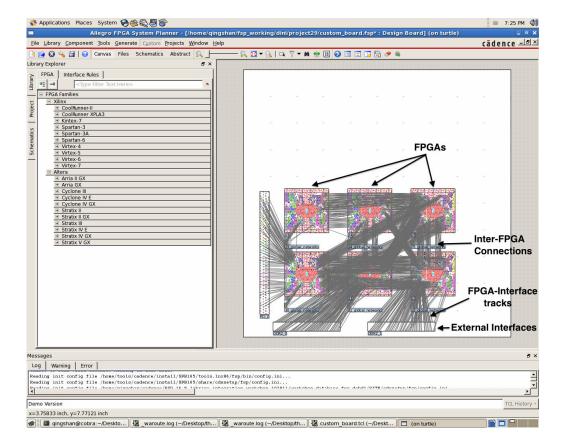

| 4.26 | The generated results loaded in the Floorplan tool Allegro      | 90  |

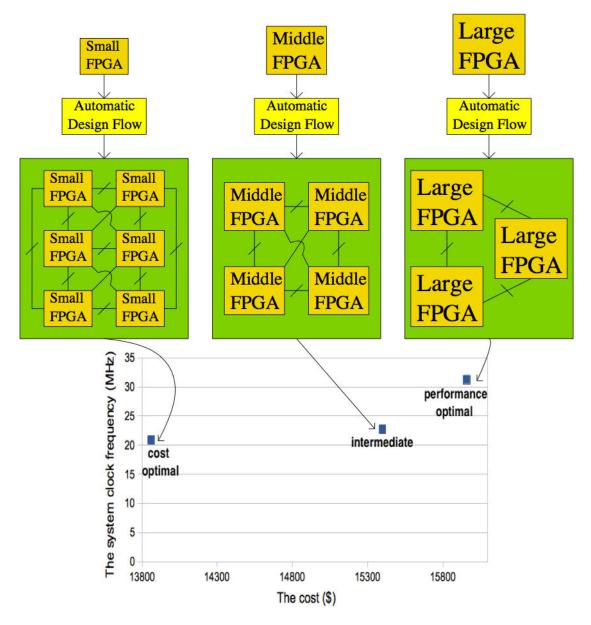

| 4.27 | Board exploration                                               | 94  |

| 4.28 | Logic Multiplexing VS ISERDES/OSERDES                           | 96  |

| 4.29 | Scene 1: 2-point tracks VS 2- and multi-point tracks            | 97  |

| 4.30 | Scene 2: 2-point tracks VS 2- and multi-point tracks            | 98  |

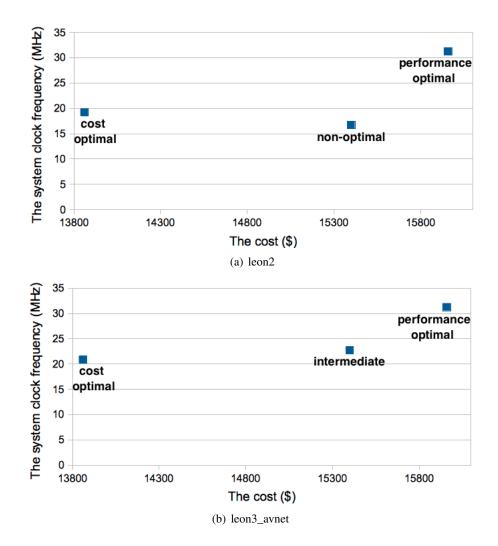

| 4.31 | Board exploration (optimal solutions)                           | 101 |

| 5.1  | The width of connectors in the cabling platform                 | 105 |

| 5.2  | The automatic design flow for creating a cabling platform       | 107 |

| 5.3  | The enhanced interconnect synthesis algorithm                   | 109 |

| 5.4  | After assigning the global signals, the reset chain and the XIs | 110 |

| 5.5  | The generation of the platform: Step 1                          | 110 |

| 5.6  | The generation of the platform: Step 2                          | 111 |

| 5.7  | The influence of the width of connectors in performance         | 113 |

| 5.8  | The cabling multi-FPGA platform                                 | 115 |

| 6.1  | The workflow of the performance comparison                      | 117 |

| 6.2  | Comparison of the performance                                   | 119 |

| 7.1  | MGT in an FPGA                                                  | 126 |

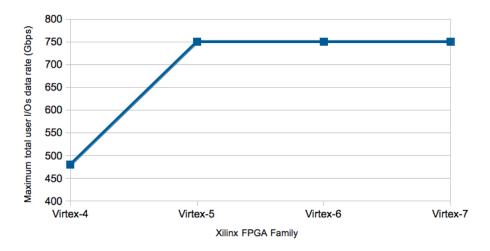

| 7.2  | Evolution of the maximum total user I/Os data rate              | 127 |

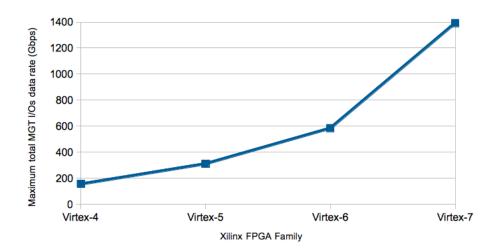

| 7.3  | Evolution of the maximum total MGT I/Os data rate               | 127 |

## **List of Tables**

| 2.1 | Comparison of Different Multi-FPGA Prototyping Platforms                     | 32  |

|-----|------------------------------------------------------------------------------|-----|

| 2.2 | Logic Multiplexing VS ISERDES/OSERDES                                        | 39  |

| 3.1 | Partitioning results of testbenches                                          | 56  |

| 3.2 | The comparison of routing results with different algorithms                  | 58  |

| 4.1 | Logic capacity, I/O capacity and estimated price of different FPGA types     | 67  |

| 4.2 | Main costs associated with custom platform development                       | 90  |

| 4.3 | Time spent for typical tasks of custom platforms                             | 92  |

| 4.4 | Logic Multiplexing VS ISERDES/OSERDES                                        | 95  |

| 4.5 | Scene 1: 2-point track VS 2- and multi-point track                           | 97  |

| 4.6 | Scene 2: 2-point track VS 2- and multi-point track                           | 98  |

| 4.7 | Board Exploration                                                            | 99  |

| 6.1 | Performance Comparison of Different Platforms                                | 118 |

| 6.2 | Updated Qualitative Comparison of Different Multi-FPGA Prototyping Platforms | 119 |

6 CONTENTS

## **Chapter 1**

## Introduction

#### 1.1 Thesis Motivation

The continuous improvement of integrated circuit technologies leads to develop more complex and higher performance circuits. As a consequence, more and more efforts are required for their verification.

#### 1.1.1 Design Verification

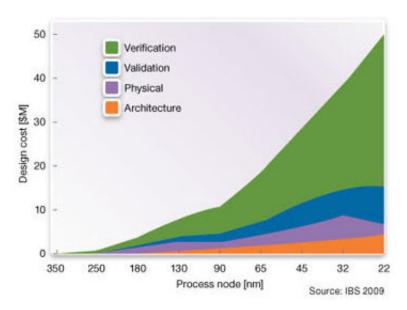

According to International Business Strategies, Inc. (IBS [IBS, 2009]), the cost of verification is growing at an exponential rate and has already been the highest portion of the overall design cost (~ 70%) as shown in the Figure 1.1.

Figure 1.1: Overall design cost

#### 1.1.2 Different Verification Techniques Pre-Silicon

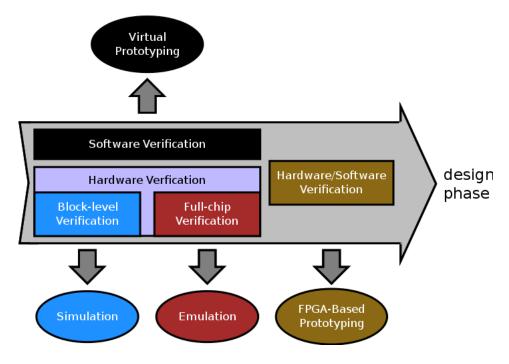

There are four main verification techniques pre-silicon: simulation, emulation, virtual prototyping and FPGA-based prototyping. Each method plays its own role in the verification process as shown in Figure 1.2:

Figure 1.2: Verification technology

- Simulation: Simulators are being relegated to verifying design functionality at the block level of an SoC/ASIC (Block-level Verification). This technique offers full-visibility into the RTL, the set-up for implementation is instantaneous and the cost is about thousands of dollars. Nevertheless, the execution speed is very limited (~ 1KHz). Simulators are software tools on a host PC. The three major existing software simulators are Cadence Incisive Enterprise Simulator [Incisive, 2014], Mentor Graphics ModelSim/SE [ModelSim, 2014], and Synopsys VCS [VCS, 2014].

- Emulation: Emulators are deployed to simulate an entire SoC/ASIC (Full-chip Verification) and thereby address the limitations of simulators. In the emulation, the RTL is still unstable (and therefore requires detailed debug analysis and frequent overnight recompiles). This technique provides high-visibility into the RTL and has much faster execution speed than the simulation (~ 1MHz). Nevertheless, it is the most expensive (about millions of dollars) and takes several days to several weeks for set-up. Emulators are hardware platforms as shown in Figure 1.3. The three major existing hardware emulator platforms are Cadence Palladium emulator [Palladium, 2014], Mentor Graphics Veloce Emulation Systems [Veloce, 2014], and Synopsys EVE ZeBu Emulation [ZeBu, 2014].

- Virtual Prototyping: Virtual prototype is the earliest available Software Verification in the project, permitting co-development of hardware along with early software (i.e. If the virtual prototype shows that there is not enough processing bandwidth for concurrent applications, extra or different CPUs might be added). This technique represents fully functional software models of SoC/ASICs, boards, virtualized I/Os, external interfaces, all running on a host PC. But these software models are loosely-timed. Virtual prototyping offers good system visibility and control, which is especially useful for debug. Nevertheless, due to that it is not cycle-accurate, it can not ensure the functionality of the software in the hardware. As simulators, virtual prototypes are software tools on a host PC. The three major existing virtual prototype tools are Cadence Virtual System Platform [Virtual, 2014], Mentor Graphics Vista [Vista, 2014], and Synopsys Virtualizer [Virtualizer, 2014].

- FPGA-Based Prototyping: FPGA-based prototypes permit to run the software at almost real-time speed in a cycle-accurate and bit-accurate model of the SoC/ASIC (Hardware/Software Verification). In the FPGA-based prototyping, the SoC/ASIC RTL is relatively stable. This technique is the one that offers the best execution speed (~ 10MHz) but the least visibility compared to other hardware-related verification techniques. It costs about ten thousands of dollars and takes several weeks to several months for set-up. Different from the Simulation/Emulation, FPGA-Based prototyping enables "real world" testing. The prototyped SoC/ASICs are put into actual hardware and real external interfaces (such as DDR, PCI, Ethernet and etc.) are used. Implementing a design into a FPGA-based platform is a challenging process. As emulators, FPGA-based prototypes are hardware platforms as shown in Figure 1.3. Nevertheless, it is smaller in form factor, which makes it useful for software developers. One or several software developers can have one in each desktop. The major existing FPGA-based prototype providers are:

- Cadence Protium Rapid Prototyping Platform [Protium, 2014] affords both the hardware platform and the implementation tool.

- Synopsys supplies both the hardware platform HAPS [HAPS, 2014] and the implementation tool ProtoCompiler [ProtoCompiler, 2014].

- S2C [S2C, 2014] sells both the hardware platform and the implementation tool.

- Dini Group produces only the hardware platform [DINI, 2014].

- HyperSilicon offers only the hardware platform [HyperSilicon, 2014].

- Auspy accommodates only the implementation tool [Auspy, 2014].

- Flexras Technologies provides only the implementation tool Wasga [Flexras, 2014].

Figure 1.3: Emulator versus FPGA-based prototype in form factor

#### 1.1.3 FPGA-Based Prototyping

As the complexity of System on Chip (SoC) circuits and the quantity of software to be developed are increasing, the software developers can no longer wait for the chip to be fabricated for the integration of the hardware/software phase in order to meet the ever-shrinking time-to-market window [Huang et al., 2011]. The resulting trend is that FPGA-based prototyping is no longer optional [Amos et al., 2011].

#### 1.1.3.1 Advantages of FPGA-based prototyping

#### High performance and timing-accuracy

Only FPGA-based prototyping provides both the speed and timing-accuracy necessary to properly test many aspects of the SoC/ASIC design (such as: real-time dataflow, hardware/software integration).

- Real-time dataflow: One of the reason that verifying an SoC is hard is due to that its state

depends on many variables, including its previous state, the sequence of inputs and the

wider system effects (and possible feedback) of the SoC outputs. Running the SoC design

at almost real-time speed connected into the rest of the system (with "real world" interfaces)

allows us to see the immediate effect of real-time conditions, inputs and system feedback

when they change.

- Hardware/Software integration: Due to that software has already come to dominate SoC development effort, it is increasingly common that the software effort is on the critical path of the project schedule. FPGA-based prototyping offers a hardware model, the closest to the future silicon for testing hardware/software integration.

#### **High mobility**

Due to the small form factor of FPGA-based prototyping and its ability to work standalone, it has high mobility. It is often used for pre-production demonstration of new product capabilities at trade shows.

#### 1.1.3.2 Disadvantages of FPGA-based prototyping

#### Low visibility

Even though there are many ways to instrument an FPGA in order to gain some visibility into design's functionality, it is still only a fraction of the information that is readily available in a simulator or an emulator. Therefore, we should always wait until the SoC/ASIC designs' RTL is fairly mature in simulation or emulation before passing it over to the FPGA-based prototyping.

#### Long set-up time

Due to that SoC/ASIC designs are often FPGA-hostile, the RTL modifications for FPGA-based prototyping need to be done as follows:

- The top-level pads of SoC/ASICs need to be adapted for the FPGA tool flow.

- The gated-clock and the complex generated clocks in SoC/ASICs need to be converted in FPGAs.

- Deal with some SoC design elements that are not available in FPGAs such as analog circuitry, BIST, SoC primitive and third party IP.

- Memories in SoC/ASICs need to be handled with FPGA memory resources (i.e. block RAM and distributed RAM) or external memory resources.

Therefore, the set-up time is long for FPGA-based prototyping.

Even though FPGA-based prototyping is not ideal, it provides a unique pre-silicon model of target silicon, allowing the software to be introduced to a cycle-accurate and high performance model of the hardware as early as possible.

#### 1.1.4 Multi-FPGA Platform

Due to that the silicon area overhead of FPGA versus ASIC technology has been measured to be about 40x [Kuon and Rose, 2010], FPGA technology requires that an ASIC logic design should be partitioned across multiple FPGA devices to achieve the necessary logic capacity. The number of FPGAs depends on the size of the prototyped SoC/ASIC, ranging from a few [Krupnova, 2004] up to 60 FPGAs [Asaad et al., 2012].

According to their role and characteristics, we have classified the multi-FPGA prototyping platforms in three major categories:

- Hardwired Off-the-Shelf Platform [DINI, 2014] [GiDEL, 2014] [POLARIS, 2014] (abbreviation: off-the-shelf): consists of a ready-made generic multi-FPGA board, where all the inter-FPGA connections are fixed and realized using PCB traces. The connections to external interfaces are also fixed but can be realized using PCB traces or connectors.

- Hardwired Custom Platform [ReFLEX, 2014] (abbreviation: custom): consists of a build-your-own specific multi-FPGA board, where all the inter-FPGA connections are realized using PCB traces as well. Different from the off-the-shelf platform that has generic and balanced connections, the connections inter FPGAs as well as the connections to external interfaces of the custom platform are user-defined and tailored for a specific design.

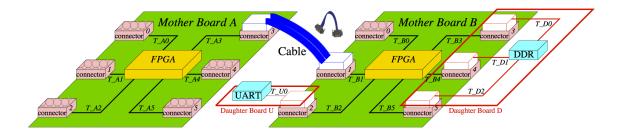

- Cabling Platform [HAPS, 2014] [Prodesign, 2014]: which is a relatively new notion compared to other two platforms, consists of multiple ready-made FPGA boards connected by cables and connectors. The cabling platform, which is in between the off-the-shelf and the custom platform as shown in Figure 1.4, is semi off-the-shelf due to that it consists of multiple ready-made boards, and semi custom due to that its connections inter FPGAs as well as connections to external interfaces are user-defined and tailored for a specific design. Nevertheless, all the inter-FPGA connections are realized using cables and connectors instead of PCB traces.

Figure 1.4: Three different multi-FPGA prototyping platforms

#### 1.2 Problems

#### 1.2.1 Pin Limitation Problem

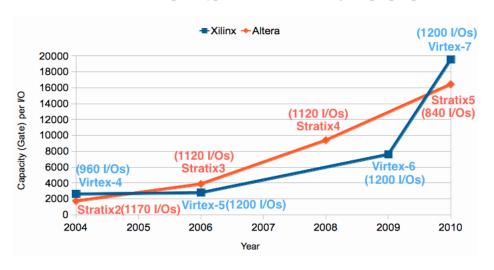

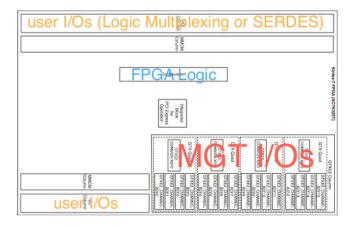

Mapping multi-million gates SoCs into any kind of the multi-FPGA platform is very challenging. The mapping process can be divided in two main steps. The first step is the partitioning of the design, meaning that the design is divided into several parts. Each part fits in the logic capacity of a single FPGA. The signals crossing design's parts located in different FPGAs are called cut nets. The second step routes the cut nets, meaning that a cut net is allocated to an inter-FPGA track on the platform. One should note that even though the logic capacity and the number of FPGA I/Os are increasing generation after generation, the logic capacity increases at a much higher rate than the number of FPGA I/Os [Schirrmeister, 2014]. Figure 1.5 shows the ratio between the logic capacity and the number of I/Os for each FPGA generation from Virtex-4 to Virtex-7 in Xilinx

1.2. PROBLEMS

Virtex Family and from Stratix2 to Stratix5 in Altera Stratix Family [DINI, 2014]. About 2000 gates are trying to get through one FPGA I/O in Virtex-4 or Stratix2. In the case of the latest generation Virtex-7 (resp. Stratix5), this is almost 20000 (resp. 16000) gates. This means that FPGA I/Os are becoming a scarce resource, worsening the inter-FPGA bandwidth generation after generation. Unfortunately, multi-FPGA platforms suffer from large timing delays in inter-FPGA communication compared to intra-FPGA net delays [Amos et al., 2011]. Therefore, this trend has a direct impact on multi-FPGA system performance (in terms of the system clock frequency) and makes it more and more difficult to prototype an SoC/ASIC design at proper performance.

Figure 1.5: The ratio FPGA logic capacity over I/Os

#### 1.2.2 Problem of Crafting a Custom Platform

70% of multi-FPGA prototyping platforms are home-made custom platforms due to performance requirement, external interfaces, and cost. Indeed home-made custom platforms are tailored for a specific design and external interfaces, and the cost decreases as more platforms are needed. Nevertheless, crafting a home-made custom multi-FPGA platform is today a manual process. Therefore, three critical aspects exist:

- Productivity: Crafting a home-made custom multi-FPGA platform is a time-consuming process (about 9 months [Sekhar, 2014]). The performance and the cost of the platform lie on the FPGA expertise and SoC DUT knowledge of the prototyping team.

- Exploration: There are many different FPGA types (i.e. vendor: Xilinx [Xilinx, 2014] or Altera [Altera, 2014], family: Virtex-7 or Stratix5, device: 2000T or GXAB, and package: FLG1925 or F1932), and different FPGA types have different logic capacity and numbers of FPGA I/Os. For a given design, the FPGA type chosen by the engineers influences the achieved performance and cost. The tradeoff between the performance and the cost exists due to that the performance of multi-FPGA platforms is limited by the inter-FPGA

communications [Amos et al., 2011]. The board exploration with different FPGA types, which helps the engineers to design an optimum prototyping platform, can not be done.

Performance: As the ratio between the logic capacity and the number of FPGA I/Os is increasing at an exponential rate, it becomes more and more challenging to keep performance as it was in multi-FPGA platform.

#### 1.2.3 Problem of Cabling Paradigm

The cabling platform benefits from the availability and the customization. The performance of the cabling platform depends on the distribution of the cables and the placement of the external interfaces. Nevertheless, there is no tool to automatically have a solution for the cable distribution. Today, the cables (resp. the external interfaces) are distributed (resp. placed) according to the experience of board designers. A high-performance cables distribution becomes more and more difficult to be achieved due to the pin limitation.

Compared to the off-the-shelf platform, the added value, in terms of performance, of cabling or custom platforms can be heavily impaired by an inefficient board design.

#### 1.3 Thesis Contributions

In order to solve the problems presented above, the major contributions of the manuscript include the following:

- A new routing algorithm is proposed to spare FPGA I/Os by exploiting multi-point tracks that connect more than two FPGAs, thus increasing the performance.

- An automatic design flow for creating a custom platform is proposed, thus increasing the productivity, enabling the board exploration, and optimizing cost and performance.

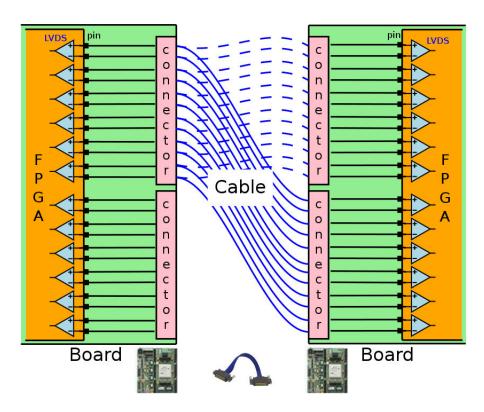

- The cabling platform is proposed where one board is composed of one FPGA and several connectors. The connections inter FPGAs as well as the connections to external interfaces can be added or removed by only connecting or disconnecting the cables (resp. daughter boards) with or from the connectors. Then, an algorithm is proposed to automatically find a solution for the cable distribution.

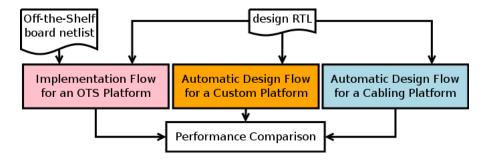

- Thanks to the developed automatic tools, the three different categories of multi-FPGA platforms (off-the-shelf, custom, and cabling) are compared. The performance gains between these platforms are quantified.

### 1.4 Thesis Organization

The rest of this manuscript is organized as follows.

Chapter 2 studies the state of the art of multi-FPGA prototyping platforms and details the inter-FPGA communication architectures. As there are three different multi-FPGA prototyping platforms, the state of the art is classified into four parts: Hardwired off-the-shelf multi-FPGA platform, Hardwired custom multi-FPGA platform, Cabling multi-FPGA platform, and Comparison of different platforms. Then, the inter-FPGA communication architectures are discussed due to that they are the critical path of all the multi-FPGA prototyping platforms.

Chapter 3 focuses on the off-the-shelf platform. An overview of multi-FPGA off-the-shelf platforms and the implementation flow are presented. There are two types of inter-FPGA tracks: 2-point tracks that connect two FPGAs and multi-point tracks that connect more than two FPGAs. A new routing algorithm of routing cut nets in 2- and multi-point tracks is proposed.

Chapter 4 focuses on the custom platform. First, an overview of the custom platform is presented. Then, the automatic design flow for creating a custom platform is proposed. Different steps of the proposed automatic design flow are explored in order to achieve lower cost and higher performance. With the proposed automatic design flow, board exploration (exploring different FPGA types for the given design) has been addressed. Plenty of feasible solutions can be generated in board exploration and board designers can make the tradeoff between cost and performance.

Chapter 5 focuses on the cabling platform. A cabling platform is proposed with an algorithm to automatically find a solution for the cable distribution.

Chapter 6 compares the achieved performances for a set of designs mapped on the three different categories of multi-FPGA platforms. The performance gains between these platforms are quantified.

Finally, Chapter 7 concludes the manuscript and suggests topics for future work.

## Chapter 2

## **Background**

#### 2.1 Introduction

The previous Chapter has presented the different multi-FPGA prototyping platforms and the difficulties using them optimally. The purpose of this Chapter is to give to the user the necessary background to understand the rest of this manuscript. This Chapter is organized as follows:

- Section 2.2 discusses the state of the art of multi-FPGA prototyping platforms.

- Section 2.3 details the inter-FPGA communication architectures, which are the critical path of all the multi-FPGA prototyping platforms in performance (in terms of the system clock frequency).

#### 2.2 State of the Art

Despite the fact that hardware/software integration is a more and more concerning problem, few papers have been published regarding multi-FPGA prototyping platforms. As there are three different multi-FPGA prototyping platforms, the study of the related work is classified into four parts:

- Hardwired off-the-shelf multi-FPGA platform

- Hardwired custom multi-FPGA platform

- Cabling multi-FPGA platform

- Comparison of different platforms

#### 2.2.1 Hardwired Off-the-Shelf Multi-FPGA Platform

The related work of the hardwired off-the-shelf multi-FPGA platform contains two parts:

- The platform overview that presents the definition of the off-the-shelf platform

- The state of the art in the implementation flows, more specifically the state of the art in the routing algorithms

#### 2.2.1.1 Platform Overview

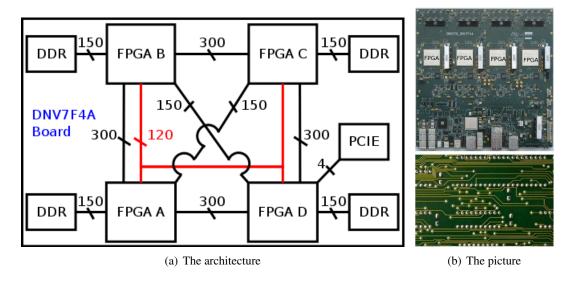

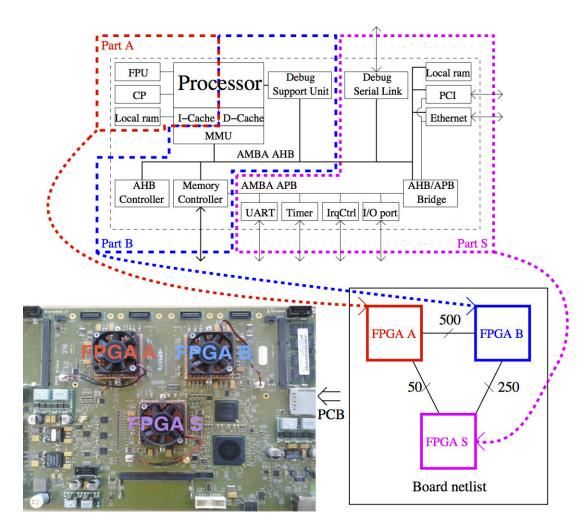

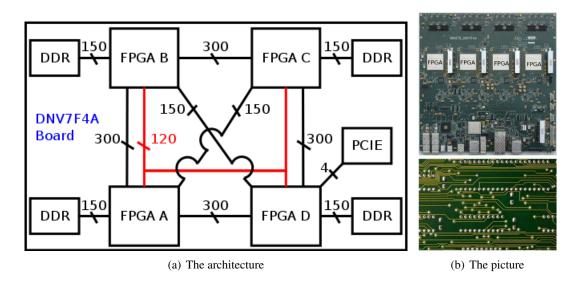

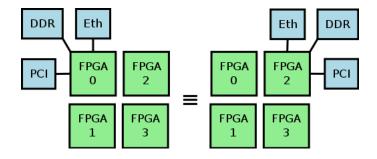

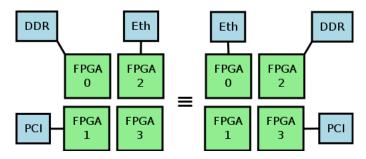

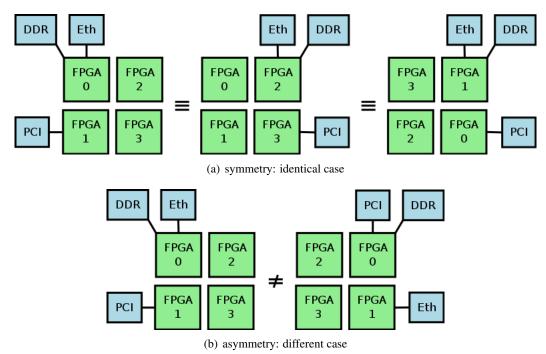

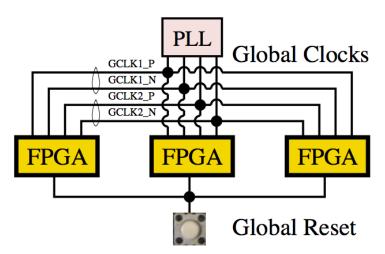

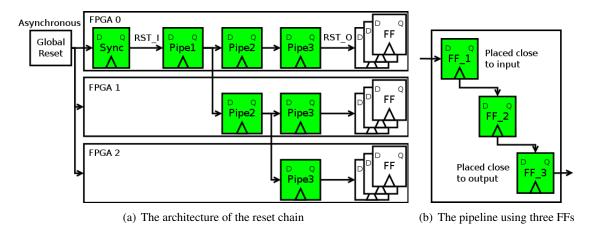

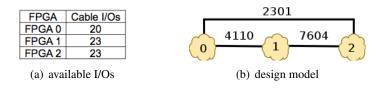

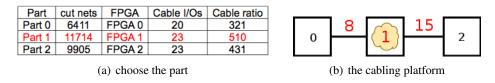

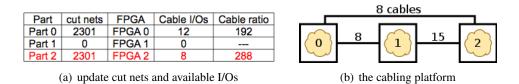

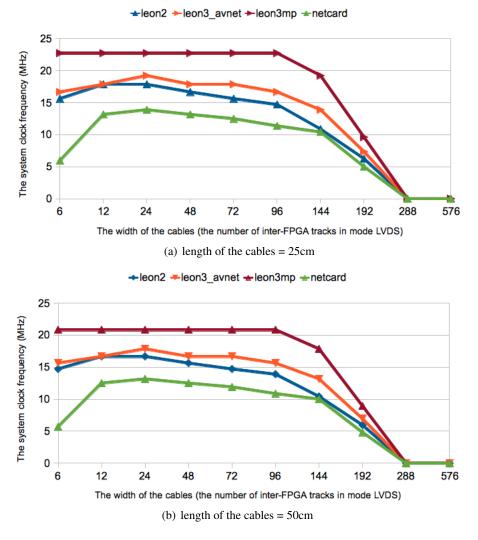

In this manuscript, the off-the-shelf platform consists of a ready-made generic multi-FPGA board, where all the inter-FPGA connections are fixed and realized using PCB traces. The connections to external interfaces are also fixed but can be realized using PCB traces or connectors (connected to daughter boards). An example of such platform is the commercial platform DNV7F4A as shown in Figure 2.1, which is the latest platform from Dini Group [DINI, 2014]. The platform uses four FPGAs of the latest Xilinx FPGA (family: Virtex-7, device: 2000T, and package: FLG1925, thus FPGA type: XC7V2000TFLG1925). Each FPGA is connected with a DDR by connectors. Only the FPGA D is connected with a PCIE by connectors. The connectors are fixed and specific. This means that the connectors to one type of the external interface (i.e. DDR) can not be transferred to the connectors to another type of the external interface (i.e. PCIE). If the prototyped design has less than 4 DDRs, several FPGA I/Os connected with DDRs are wasted. If the prototyped design has a PCIE, the PCIE part of the prototyped design is forced to be placed in FPGA D. These constraints add to the complexity of the design partitioning and may reduce the performance. The number of inter-FPGA tracks is shown in Figure 2.1(a). All the inter-FPGA tracks are fixed. There are two types of inter-FPGA tracks in the multi-FPGA prototyping platform: 2-point tracks and multi-point tracks. The number of multi-point tracks in the example is 120. The number of 2-point tracks between a pair of FPGAs are generic and balanced: 300 connections in all the horizontal and vertical pairs, and 150 connections in all the diagonal pairs. When implementing a specific design, these generic and balanced connections constraint the performance. Figure 2.1(b) shows the picture of the platform and the PCB traces.

Figure 2.1: The off-the-shelf multi-FPGA platform

Major existing commercial off-the-shelf platforms are Cadence Protium Rapid Prototyping Platform [Protium, 2014], Dini Group [DINI, 2014], S2C [S2C, 2014], and HyperSilicon [HyperSilicon, 2014].

#### 2.2.1.2 Implementation Flow of Multi-FPGA Platforms

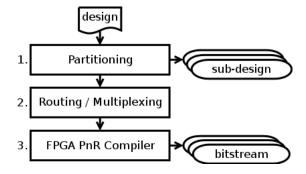

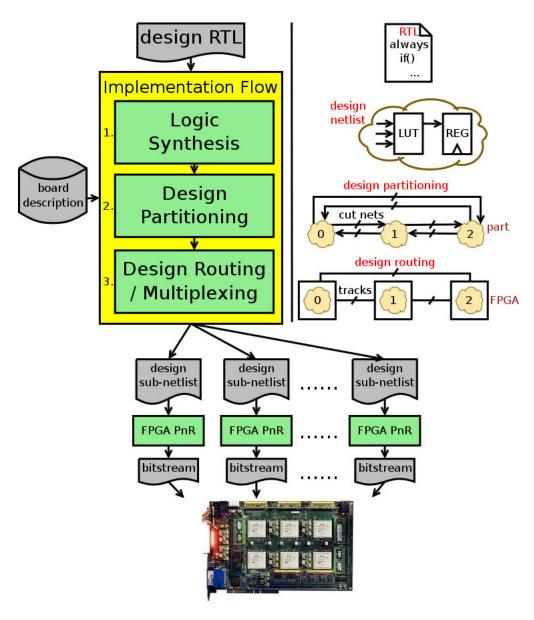

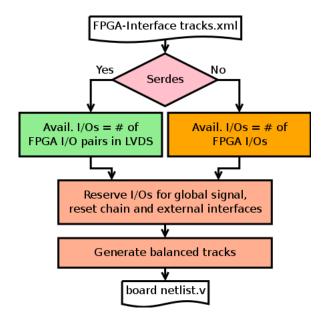

Implementing multi-million gates SoCs into multi-FPGA platforms is very challenging. The implementation flow as shown in Figure 2.2, which starts by inputting the design RTL, can be divided in three main steps:

Figure 2.2: The typical implementation flow

Partitioning: As the SoC/ASIC design is bigger than the FPGA, the design is partitioned into several parts according to the number of FPGAs in the platform. Each part's capacity fits in a single FPGA. The signals crossing design's parts located in different FPGAs are called cut nets.

- 2. Routing / Multiplexing: The cut nets are routed meaning that a cut net is allocated to an inter-FPGA track in the platform. As there are fewer available inter-FPGA tracks than the number of cut nets, several cut nets need to be multiplexed and sent together onto a single track on the platform.

- 3. FPGA PnR Compiler: The bitstream for each FPGA is generated from the sub-design. Then, the generated bitstreams are downloaded into the platform to model the design.

Nowadays, there are four commercial implementation flow tools: Cadence Protium tool [Protium, 2014], Synopsys ProtoCompiler tool [ProtoCompiler, 2014], Auspy tool [Auspy, 2014], S2C tool [S2C, 2014], and Flexras Wasga tool [Flexras, 2014], targeting at automatizing the implementation flow.

This manuscript will study the process of the routing and propose an improved routing algorithm. The state of the art of the routing algorithms is discussed in the following. Routing algorithms for multi-FPGA platforms heavily depend on the underlying hardware routing architectures. Thus, they can be classified according to the routing architectures.

### **Direct architecture**

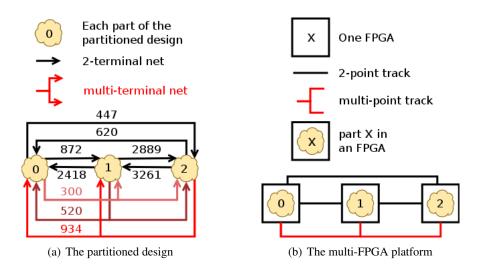

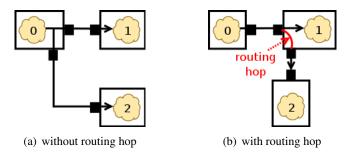

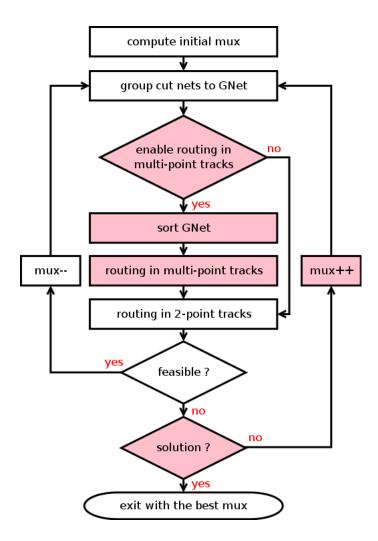

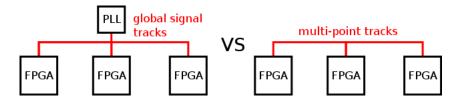

All the FPGAs are directly interconnected [Walters, 1991] as shown in Figure 2.3. These direct inter-FPGA tracks can be divided into two categories: 2-point tracks directly connect one FPGA to another, and multi-point tracks connect several FPGAs together.

Figure 2.3: The direct architecture

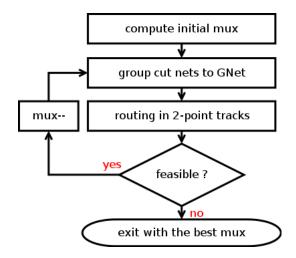

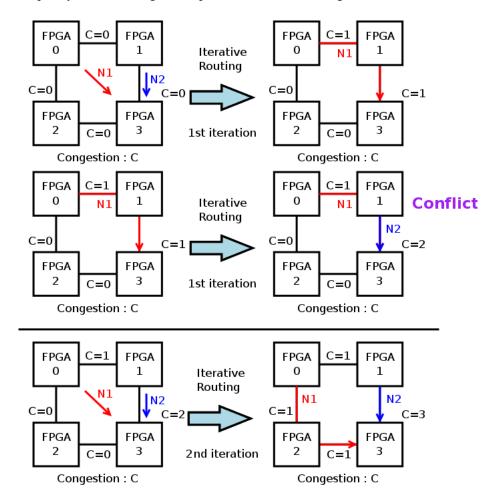

An iterative, congestion-aware routing algorithm is provided by [Turki et al., 2013] as shown in Figure 2.4. Nevertheless, the algorithm only uses 2-point tracks and routes multi-terminal nets through a sequence of 2-point tracks. The routing algorithm is detailed as follows.

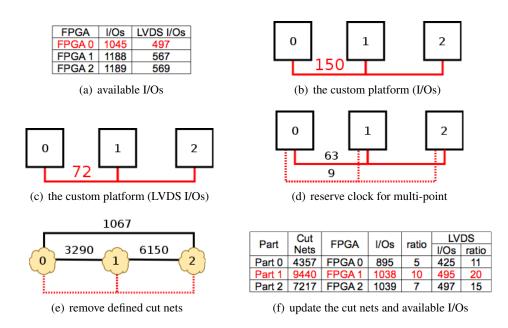

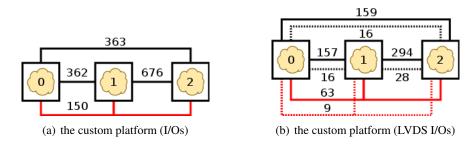

21

Figure 2.4: The proposed routing algorithm

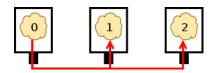

• Compute the initial maximum number of cut nets passing through one multiplexer (noted as mux).

After loading the partitioned design and the multi-FPGA platform architecture, the algorithm will calculate initial mux by obtaining the maximum ratio of cut nets and inter-FPGA tracks between each pair of FPGAs.

### • Group cut nets to GNet

The cut nets, which have the same driver FPGA and the same receiver FPGAs, are grouped together. The group, which is called GNet, will be put in one track. Each GNet contains a maximum of mux cut nets.

### • Routing in 2-point tracks

PathFinder [McMurchie and Ebeling, 1995] was used primarily for routing intra-FPGA nets. It is adapted to deal with GNets and routes GNets in 2-point tracks. An iterative negotiation-based approach is used in PathFinder. During the first routing iteration, GNets are freely routed without paying attention to track sharing. Individual GNets are routed using Dijkstra's shortest path algorithm [Cormen et al., 2009]. At the end of the first iteration, tracks may be congested because multiple GNets try to use one track. During subsequent iterations, the cost of using a track is increased, based on the number of GNets that share the track, and the history of congestion on that track. Thus, GNets are forced to negotiate for tracks. If a track is highly congested, GNets which can use lower congestion alternatives are forced to do so. On the other hand, if the alternatives are more congested than the track, then a GNet may still use that track. Due to that one track can only contain one GNet, if there are two GNets in one track in the result of PathFinder, there is a conflict. A routing result is feasible only when the number of conflicts is 0.

• The proposed algorithm tries to minimize mux. If feasible, decrease the mux and iterate the previous steps beginning from grouping cut nets with the new mux. If not feasible, exit with the best mux.

Nevertheless, this algorithm does not exploit multi-point tracks, which may waste FPGA I/Os.

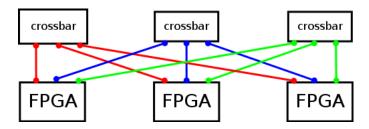

### **Indirect architecture**

All the FPGAs are interconnected through partial crossbars [Varghese et al., 1993] as shown in Figure 2.5.

Figure 2.5: The indirect architecture

Multi-terminal nets routing, through partial crossbars, is discussed in [Mak and Wong, 1997] [Song et al., 2003] [Ejnioui and Ranganathan, 2003]. Even though multi-terminal nets routing on indirect architectures spares FPGA I/Os, multi-FPGA platforms performance is tied to inter-FPGA delays, and this kind of architecture worsens this effect as nets are routed through at least 2 inter-FPGA tracks plus the crossbar component. Moreover, if most of cut nets are 2-terminal nets, this architecture will waste FPGA I/Os. Therefore, this architecture is not used for FPGA-based prototyping.

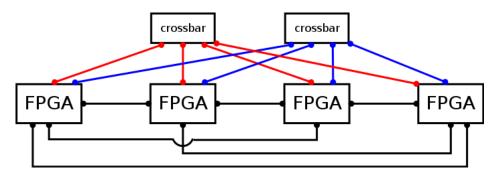

### Hybrid architecture

A mixture of direct connections and partial crossbars are used in [Khalid, 1999] [Khalid and Rose, 2000] as shown in Figure 2.6.

Figure 2.6: The hybrid architecture

The routing algorithm in [Jain et al., 2002] proposes the use of a crossbar to route multiterminal nets and direct connections to route 2-terminal nets. However, this kind of architecture suffers of the same performance degradation as the indirect architecture and is not used for FPGAbased prototyping.

### Conclusion

Industrial multi-FPGA prototyping platforms (Cadence Protium Platform [Protium, 2014], Dini Group Platform [DINI, 2014] and Reflex FPP Platform [ReFLEX, 2014]) have adopted direct architecture for performance motivation. They afford 2- and multi-point tracks. Nevertheless, the existing tools do not automatically route and multiplex cut nets in multi-point tracks, which waste FPGA I/Os that are already a scarce resource. In Chapter 3, which focuses on the off-the-shelf platform, we will target the direct architecture and we propose to spare FPGA I/Os by automatically routing and multiplexing multi-terminal nets over multi-point tracks.

### 2.2.2 Hardwired Custom Multi-FPGA Platform

The related work of the hardwired custom multi-FPGA platform contains two parts:

- The platform overview that presents the definition of the custom platform

- The state of the art of the design flows for creating a custom platform

### 2.2.2.1 Platform Overview

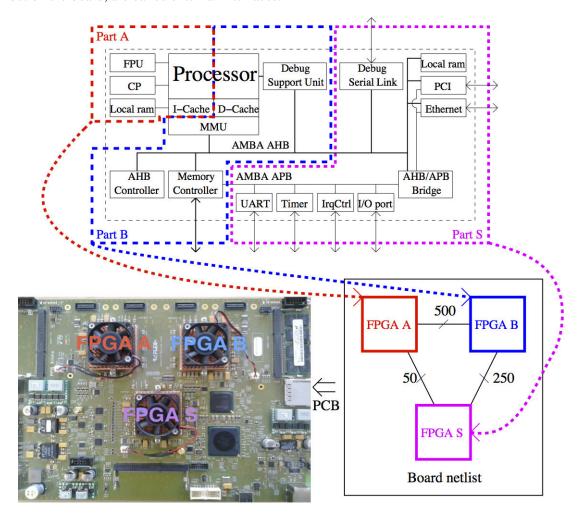

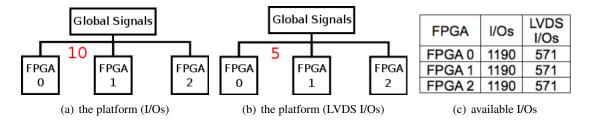

The custom platform consists of a build-your-own specific multi-FPGA board, where all the inter-FPGA connections are realized using PCB traces as well. The advantage of the custom platform is that it is tailored for a specific design. An example is shown in Figure 2.7. The design is bigger than the largest FPGA available and three of them are needed. There are many signals crossing from Part A to Part B but only few from Part A to Part S. Therefore, more inter-FPGA tracks are allocated between FPGA A and FPGA B than between FPGA A and FPGA S. In terms of external interfaces, there is only 1 DDR in the example. Therefore, 1 DDR is reserved only for FPGA B that contains the memory controller.

Figure 2.7: Create a Custom Platform for a specific design

Different from the off-the-shelf platform, which has generic and balanced connections as shown in Figure 2.1, tracks of the custom platform are user-defined and tailored for the given design to achieve higher performance. Different from the off-the-shelf platform, which has 1 DDR reserved for each FPGA as shown in Figure 2.1 and wastes FPGA I/Os due to that there is only 1 DDR in the example, the tracks to external interfaces of the custom platform are tailored for the given design and no FPGA I/O is wasted. Therefore, the design partitioning is facilitated due to that the DDR is connected to the FPGA where the memory controller logic is placed in the custom platform, thus higher performance can be achieved. Nevertheless, 4-7 months are needed for the PCB layout and the PCB fabrication.

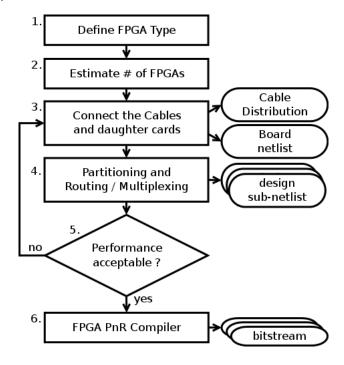

### 2.2.2.2 Design Flow for Creating a Custom Platform

### Typical design flow

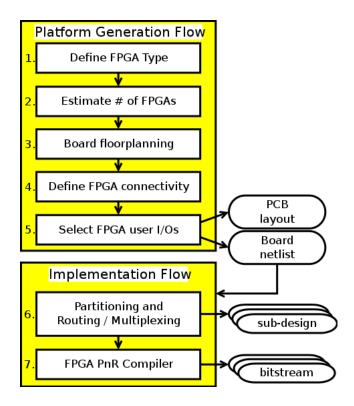

The typical design flow as shown in Figure 2.8 for creating a home-made custom multi-FPGA platform is detailed as follows:

25

Figure 2.8: The typical design flow for creating a custom platform

- 1. Choose the FPGA type (i.e. vendor: Xilinx [Xilinx, 2014] or Altera [Altera, 2014], family: Virtex-7 or Stratix5, device: 2000T or GXAB, and package: FLG1925 or F1932).

- 2. Estimate the minimum number of FPGAs required in the platform (according to the logic capacity of the input design, the logic capacity of the chosen FPGA type, and the maximum FPGA logic capacity utilization).

- 3. Floorplan FPGAs and external interfaces on the Printed Circuit Board (PCB).

- 4. Define the FPGA connectivity (FPGA-to-External-Interface and inter-FPGA tracks).

- 5. Select FPGA I/Os. The I/O DRC rules (such as clock capability, clock region and I/O standard voltage reference levels) are considered, when choosing I/Os for each track. Then, a board netlist and a PCB layout are generated.

- 6. Map the SoC/ASIC design on this latter board, meaning that the design is partitioned and routed into each FPGA. As there are fewer available inter-FPGA tracks than the number of cut nets, several cut nets need to be multiplexed and sent together onto a single track on the platform.

- 7. Run the PnR Compiler with the design sub-netlists to generate the bitstreams for each FPGA. Then, the generated bitstreams are downloaded into the platform to model the design.

The typical design flow is mainly manual and iterative. Therefore, this process is time-consuming, and the optimization of the cost and the performance depends on the designers' experience.

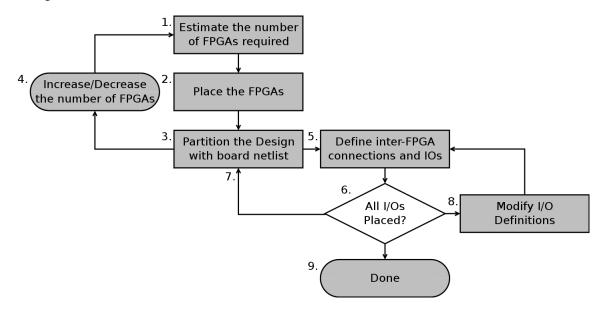

### Cadence design flow

In [Cadence, 2011], a design flow for creating a custom platform is proposed, but only the process of selecting FPGA user I/Os is automated (by the Cadence FSP tool [FSP, 2014]) as shown in Figure 2.9.

Figure 2.9: Cadence's design flow for creating a custom platform.

- 1. Estimate the minimum number of FPGAs required for partitioning the design RTL according to the chosen FPGA type.

- 2. Place the FPGAs on the Allegro FPGA System Planner canvas [FSP, 2014] and generate a Verilog board netlist with the FPGAs,

- 3. Use a partitioning tool to ensure that the RTL can be partitioned within the selected number of FPGAs.

- 4. If the selected number of FPGAs is not reasonable, increase or decrease the number of FPGAs and iterate the previous processes.

- 5. Use the top level of the partitioned RTL to define the connections required among the different FPGAs.

- 6. Once the I/O synthesis is completed in Allegro FPGA System Planner, the Verilog board connectivity file can be generated. Some iterations with the I/O definitions may be needed to ensure that all the I/Os can be placed on the different FPGAs.

- 7. Use this connectivity file once again in the RTL partitioning tool. The RTL partitioning tool can now map the wires in the top level to ports/traces on the board

- 8. In some cases, it may be required to iterate a bit to get to successful results, analyze results of the partitioning tools and make the required changes to the FPGA board architecture.

- 9. Once all the requirements are met, the board layout can be generated.

Even though the proposed point tool Cadence FSP automatically selects FPGA user I/Os, the Cadence design flow for creating a custom platform is still mainly manual and iterative. Therefore, this process is time-consuming, and the optimization of the cost and the performance depends on the designers' experience.

### Conclusion

The existing design flows are mainly manual and iterative, thus creating a custom platform is time-consuming and the optimization of the cost and the performance depends on the designers' experience.

In Chapter 4, which focuses on the custom platform, we propose an automatic design flow for creating a custom multi-FPGA platform. The proposed automatic design flow reduces the time-to-market of new products and lowers the entry barrier of board designers while optimizing the cost and the performance. With the proposed automatic design flow, board exploration (exploring different FPGA types for the given design) has been addressed. Plenty of feasible solutions can be generated in board exploration and board designers can make the tradeoff between cost and performance.

### 2.2.3 Cabling Multi-FPGA Platform

The related work of the cabling multi-FPGA platform contains two parts:

- The platform overview that presents the definition of the cabling platform

- The state of the art of the design flows for creating a cabling platform

### 2.2.3.1 Platform overview

The cabling platform, which is a relatively new notion compared to other two platforms, consists of multiple ready-made FPGA boards connected by cables and connectors. In between the off-the-shelf and the custom platform, the cabling platform is semi off-the-shelf as it is ready-made, and semi custom as the inter-FPGA connections can be changed by connecting or disconnecting the cables in order to be tailored for the given design.

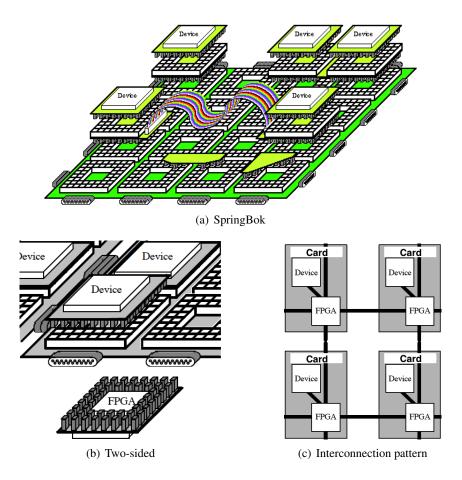

### The hybrid cabling platform

In [Hauck, 1995], a hybrid cabling platform as shown in Figure 2.10(a) is proposed. The inter-FPGA tracks are realized by a hybrid of the cables and the PCB traces. To allow a specific circuit to be implemented in this structure, the SpringBok system is composed of a baseplate with sites for cards. The cards in the platform as shown in Figure 2.10(b) are large enough to contain an arbitrary device on the top, as well as an FPGA on the bottom. Note that the device can be a chip, or external interfaces (such as PCI, DDR). The inter card routing structure is a mesh as shown in Figure 2.10(c) and the connections are fixed. There is the potential that the simple connections will not be able to accommodate all the logic or routing assigned to a given location (Intermediate FPGAs are needed from the driver FPGA to the destination FPGA, which degrades the performance). However, as opposed to the off-the-shelf platform, "extender" cards can be inserted between a card and the baseplate to deal with these problems. For signals that must go long distances in the array, sets of "extender" cards with cables can be inserted to carry these long-distance wires. Nevertheless, the inter-FPGA tracks in the hybrid cabling platform is not fully customized for the given design due to that several inter-FPGA tracks are realized by fixed PCB traces. Therefore, the achieved performance is limited.

Figure 2.10: Multi-FPGA Platform: SpringBok

29

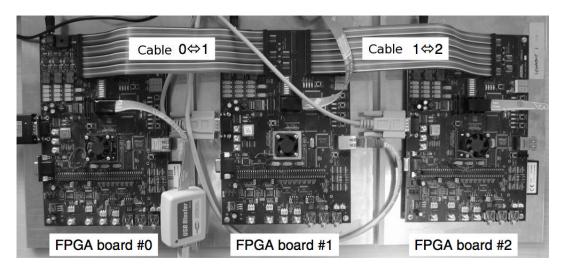

### The quasi cabling platform

In [Kulmala et al., 2007] and IBM [Asaad et al., 2012], a cabling platform is used as shown in Figure 2.11. All the inter-FPGA tracks are realized by cables, but the connections to external interfaces are realized using PCB traces. The inter-FPGA tracks can be changed in order to be tailored for the given design. Due to that the cabling platform is ready-made, the connections to external interfaces may be not tailored for the given design. Thus, FPGA I/Os occupied by external interfaces may be wasted. Moreover, there is no discussion about the cable distribution. The cable distribution and the external interface placement, which are essential to the achieved performance in the cabling platform, depend on the experience of board designers.

Figure 2.11: A photo of Kulmala's quasi cabling platform

### The cabling platform

The cabling platform consists of multiple ready-made FPGA boards connected by cables and connectors. Almost all the FPGA I/Os are used for FPGA-to-connector connections. The connections between FPGAs as well as the connections to external interfaces can be added or removed by only connecting or disconnecting the cables (resp. daughter boards) with or from the connectors in order to be tailored for the given design.

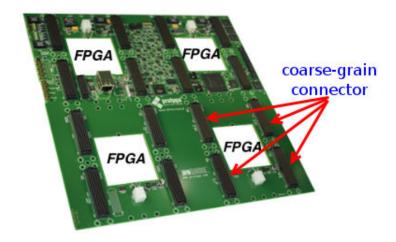

The proFPGA cabling platform as shown in Figure 2.12 is proposed in [Prodesign, 2014]. For each FPGA, there are only 4 connectors. The width of connectors is defined as the pairs of tracks passing through this connector. Among the four connectors, three of them have 148 pairs of tracks, and the rest one has 98 pairs of tracks. Nevertheless, the coarse-grained connector may waste FPGA I/Os when external interfaces do not occupy so many FPGA I/Os but need at least one connector. Moreover, there is no tool to automatically have a solution for the cable distribution. The cable distribution and the external interface placement, which are essential to the achieved performance in the cabling platform, depend on the experience of board designers.

Figure 2.12: proFPGA

The HAPS cabling platform as shown in Figure 2.13 is proposed by Synopsys [HAPS, 2014]. For each FPGA, there are 23 connectors. Each connector has 24 pairs of tracks. Comparing to proFPGA, the connector in HAPS is fine-grained. For example, the external interface DDR3 that occupies 72 pairs of tracks, covers 3 connectors in HAPS. Therefore, no FPGA I/O is wasted. In proFPGA, this DDR3 covers the connector with 98 pairs of tracks and 26 pairs of FPGA I/Os are wasted. Again, there is no tool to automatically have a solution for the cable distribution. Therefore, the cable distribution and the external interface placement, which are essential to get higher performance in the cabling platform, depend on the experience of board designers.

Figure 2.13: Synopsys HAPS

31

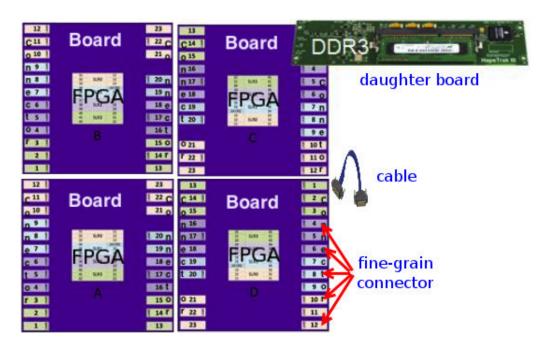

### 2.2.3.2 Design Flow for Creating a Cabling Platform

The typical design flow as shown in Figure 2.14 for creating a cabling multi-FPGA platform is detailed as follows:

Figure 2.14: The typical design flow for creating a cabling platform

- 1. Choose the FPGA type (i.e. vendor: Xilinx [Xilinx, 2014] or Altera [Altera, 2014], family: Virtex-7 or Stratix5, device: 2000T or GXAB, and package: FLG1925 or F1932).

- 2. Estimate the minimum number of FPGAs required in the platform (according to the logic capacity of the input design, the logic capacity of the chosen FPGA type, and the maximum FPGA logic capacity utilization.

- Manually find a solution of the distribution of the cables and the external interface daughter boards. Then, the cables and external interface daughter boards are connected. Finally, a board netlist is generated.

- 4. Map the SoC/ASIC design on this latter board, meaning that the design is partitioned and routed into each FPGA. As there are fewer available inter-FPGA tracks than the number of cut nets, several cut nets need to be multiplexed and sent together onto a single track on the platform.

- 5. Evaluate the performance. If the performance is acceptable, pass to the next step. If not, iterate the previous step from re-connecting the cables and external interface daughter boards.

- 6. Run the PnR Compiler with the design sub-netlists to generate the bitstreams for each FPGA. Then, the generated bitstreams are downloaded into the platform to model the design.

The typical design flow is mainly manual and iterative. Therefore, this process is time-consuming, and the optimization of the performance depends on the designers' experience.

### 2.2.3.3 Conclusion

According to our knowledge, there is no tool to automatically have a solution for the cable distribution. In Chapter 5, which focuses on the cabling platform, we propose a cabling platform with an algorithm to automatically optimize the cable distribution and the external interface placement. Nowadays, the two existing cabling platforms (proFPGA and Synopsys HAPS) have different width granularity of the connectors (resp. cables). With the proposed algorithm, the optimal width of connectors in terms of performance is explored.

### 2.2.4 Comparison of Different Multi-FPGA Platforms

Combining [Amos et al., 2011] [Cadence, 2011], these three different platforms are compared qualitatively in terms of availability, performance, flexibility, and cost as shown in Table 2.1.

| Multi-FPGA    |               | Performance |              |             | Cost  |            |

|---------------|---------------|-------------|--------------|-------------|-------|------------|

| Prototyping   | Availability  | Inter-FPGA  | tracks       | Flexibility | Unit  | Deployment |

| Platforms     |               | data rate   | distribution |             | Price | Cost       |

| Hardwired     | instantaneous | high        | generic &    | medium      | low   | high       |

| Off-the-Shelf |               |             | balanced     |             |       |            |

| Cabling       | 1-2 months    | high        | designers'   | high        | low   | high       |

|               |               |             | experience   |             |       |            |

| Hardwired     | 4-7 months    | designers'  | designers'   | low         | high  | low        |

| Custom        |               | experience  | experience   |             |       |            |

Table 2.1: Comparison of Different Multi-FPGA Prototyping Platforms

The availability is the time to get access to the platform. The off-the-shelf platform is available instantly. For the cabling platform, 1-2 months are needed to find an optimal cable distribution. For the custom platform, 4-7 months are needed to find a good solution due to that the PCB layout and the PCB fabrication is needed. The achieved performance of multi-FPGA platforms depends on the inter-FPGA data rate and inter-FPGA tracks distribution. For the off-the-shelf and the cabling platform, the data rate is high due to that they are ready-made by the FPGA experts in the commercial companies. For the custom platform done by the in-house team, it depends on designers' experience on how to design high-speed signaling, high performance multiplexing and so forth. For the off-the-shelf platform, the inter-FPGA tracks distribution is generic and balanced. For the cabling and the custom done by the in-house team, it depends on the designers' experience on how to distribute inter-FPGA tracks in order to achieve higher performance. Naturally, the custom platforms should achieve highest performance because it is tailored for the given design.

33

Unfortunately, the performance of the cabling and the custom platform heavily depend on designers' experience because designing such platforms is still a manual process. Therefore, not so good performance platforms can be often seen. The flexibility of the platform is its ability to be tailored for different designs. The cabling platform has the highest flexibility due to that the same platform can be tailored for different designs by only re-connecting the cables. The off-the-shelf platform has medium flexibility due to its generic and balanced connections. The custom platform has the lowest flexibility due to that one custom platform tailored for one design may be not tailored for another design. The unit price for the custom platform is high as it integrates the development cost. The deployment cost corresponds to the quantity of platforms needed. This cost for custom platforms is low because it consists of the Bill-Of-Material (BOM) plus the production cost.

### 2.2.5 Conclusion of the State of the Art

Different kinds of platforms are widely used: off-the-shelf [Hyder and Wawrzynek, 2005], custom [Krupnova, 2004], and cabling [Kulmala et al., 2007] [Asaad et al., 2012]. The contributions of this manuscript are classified into four parts: Firstly, a new routing algorithm is proposed to spare FPGA I/Os by exploiting multi-point tracks. Secondly, an automatic design flow for creating a custom platform is proposed. Thirdly, the cabling platform and an algorithm to automatically optimize the cable distribution and the external interface placement, are proposed. Finally, the achieved performances are compared when a set of designs are mapped on the three platforms. The performance gains between these platforms are quantified.

Even though the three platforms are different, they all have their performance limited by the inter-FPGA connections. Different inter-FPGA communication architectures, more or less complex, can be implemented leading to different achieved performances. Before exploiting different multi-FPGA platforms, we have to explain these different architectures.

### 2.3 Inter-FPGA Communication Architectures

According to [Amos et al., 2011] [Pinmux, 2014], inter-FPGA tracks are the critical path of all the multi-FPGA prototyping platforms in performance. Therefore, inter-FPGA communication architectures need to be detailed in order to understand the rest of this manuscript.

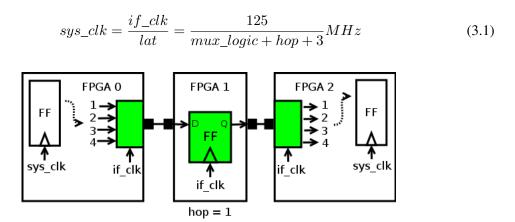

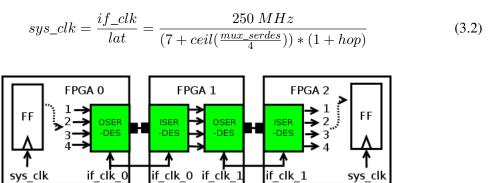

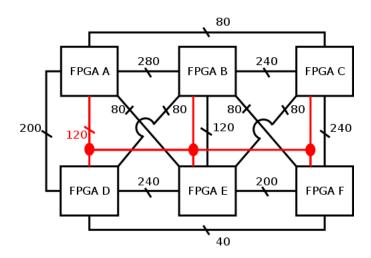

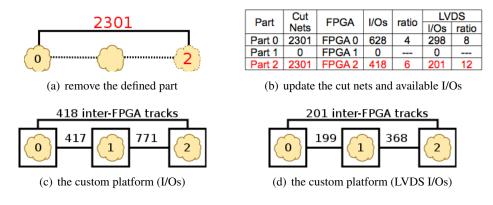

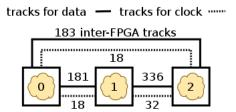

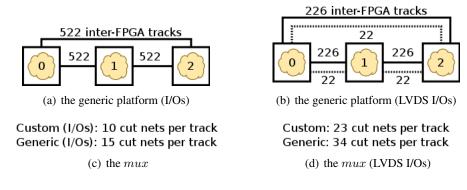

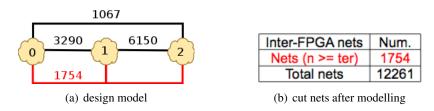

### 2.3.1 Time-Division-Multiplexing