# Conception et test des circuits et systèmes numériques à haute fiabilité et sécurité

Giorgio Di Natale

#### ▶ To cite this version:

Giorgio Di Natale. Conception et test des circuits et systèmes numériques à haute fiabilité et sécurité. Micro and nanotechnologies/Microelectronics. Université de Montpellier II, 2014. <tel-01276281>

HAL Id: tel-01276281

https://hal-lirmm.ccsd.cnrs.fr/tel-01276281

Submitted on 19 Feb 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Habilitation à Diriger les Recherches

# Giorgio Di Natale

Chargé de Recherche CNRS - Section 7

# Conception et test des circuits et systèmes numériques à haute fiabilité et sécurité

# Jury:

Matteo Sonza Reorda - Professeur à Politecnico di Torino, Italie

Jean-Luc Danger - Directeur d'études de Telecom ParisTech

Régis Leveugle - Professeur à Grenoble INP

Guy Gogniat - Professeur à l'Université de Bretagne-Sud

Bruno Rouzeyre - Professeur à l'Université de Montpellier II

Lionel Torres - Professeur à l'Université de Montpellier II

Marie-Lise Flottes - Chargé de Recherche CNRS

# **Table of Contents**

| Chapter I: Summary                                                       | 5  |

|--------------------------------------------------------------------------|----|

| 1. Curriculum Vitae                                                      | 6  |

| 1.1. Personal Information                                                | 6  |

| 1.2. Cursus                                                              | 6  |

| 1.3. Research Interests                                                  | 6  |

| 1.4. Summary of the hot points                                           | 7  |

| 2. Summary of scientific activities                                      | 8  |

| 2.1. Preamble                                                            | 8  |

| 2.2. Current research activities                                         | 8  |

| 2.3. Students                                                            | 11 |

| 2.4. Scientific Projects                                                 | 11 |

| 2.5. Teaching activities                                                 | 13 |

| 2.6. Cooperations                                                        | 14 |

| 2.7. Dissemination of knowledge                                          | 15 |

| 2.8. Publications                                                        | 16 |

| Chapter II: Details                                                      | 18 |

| 3. Research activities                                                   | 19 |

| 3.1. Memory BIST and BISR (Master thesis)                                | 20 |

| 3.2. Software Implemented Hardware Fault Tolerance (PhD Thesis)          | 21 |

| 3.3. Memory Test (Post-Doc at Politecnico di Torino, Italy)              | 23 |

| 3.4. Programming by Contracts (Post-Doc at Politecnico di Torino, Italy) | 24 |

| 3.5. Reliability of the AES (Post-Doc at CNRS)                           | 25 |

| 3.6. Manufacturing Test for Secure Devices                               | 30 |

| 3.7. Fault Attacks                                                       | 47 |

| 3.8. Test of 3D-Stacked Integrated Circuits                              | 51 |

| 3.9. Reliability of Microprocessor-based Systems                         | 53 |

| 4. Students                                                              | 55 |

| 4.1. Master students                                    | 55 |

|---------------------------------------------------------|----|

| 4.2. PhD Students                                       | 56 |

| 4.3. PostDoc Students                                   | 60 |

| 5. Teaching activities                                  | 62 |

| 6. Funded Projects                                      | 64 |

| 7. Cooperations                                         | 70 |

| 8. Dissemination of knowledge and scientific excellence | 72 |

| Chapter III: Perspectives                               | 76 |

| 9. Perspectives on Security                             | 78 |

| 9.1. Asset Attacks                                      | 78 |

| 9.2. IP Attacks                                         | 79 |

| 9.3. Tampering Attacks                                  | 80 |

| 10. Perspectives on Test                                | 81 |

| 11. Perspectives on Dependability                       | 82 |

| Chapter IV: Publications                                | 84 |

| 12. Book chapters                                       | 85 |

| 13. Journals                                            | 85 |

| 14. Conferences, Symposium, Workshops, Presentations    | 86 |

| 15. Patent                                              | 91 |

| Chapter V: Selection of 5 best papers                   | 93 |

# Chapter I: Summary

# 1. Curriculum Vitae

#### 1.1. Personal Information

Name: Giorgio DI NATALE

• Date and Place of Birth: 10 February 1975, Torino (Turin, Italy)

• Nationality: Italian

• Personal address: 5, rue du Lauzas, 34380 Mas De Londres, France

• Current position: "Chargé de Recherche 1ère classe", CNRS

• Work address: LIRMM, UMR 5506, 161 rue Ada, 34392 Montpellier Cedex 5, France

Work phone: 04. 67. 41. 85. 01Fax: 04. 67. 41. 85. 00

• Email: giorgio.dinatale@lirmm.fr

#### 1.2. Cursus

- 1994: High School degree (Computer Science Technical Institute, score 59/60), Turin, Italy

- 1999: Master degree in Computer Engineering (score summa cum laude), Politecnico di Torino, Italy

- 1999: National Engineering habilitation exam, Turin, Italy

- 2003: Ph.D. degree in Computer Engineering, Title: "Software-Implemented System Dependability for Safety Critical Applications", (score Excellent), Politecnico di Torino, Italy

- 2003-2006: Post-doc position, Topic: "Reliability and Test of Digital Systems", Politecnico di Torino, Italy

- 2006-2007: Post-doc position, Topic: "Design and Test of Secure Circuits", LIRMM Montpellier, France

- 2007: Qualification MCF, Section 61, n° 07261174644

- From 2007: Chargé de Recherche 1ère classe, CNRS

#### 1.3. Research Interests

- Memory Testing

- Digital Testing and Design for Testability

- Fault Tolerance and Reliability

- Computer-Aided Design Tools

- Design, Test and Reliability of Secure Devices

- Hardware Security and Trust

- Test of TSV-based 3D Stacked Integrated Circuits

- Dependability of microprocessor-based systems

# 1.4. Summary of the hot points

- Co-author of 2 book chapters, 18 international journal papers and more than 90 papers and presentations in international conferences, 1 patent

- Co-supervisor of 12 PhD students, 2 Post-Doc students and more than 30 master students.

- Action Chair of the COST Action IC1204 (TRUDEVICE) on Trustworthy Manufacturing and Utilization of Secure Devices

- Scientific leader (for the CNRS) of the FP7 European Project CLERECO (Cross-Layer Early Reliability Evaluation for the Computing cOntinuum)

- Participation to overall 13 european- and national-funded projects (since 2000)

- Associate Editor of the journal "Information Security Journal: A Global Perspective"

- Guest Editor of the journal "IEEE Design & Test"

- Guest Editor of the journal "IEEE JETTA: Journal of Electronic Testing Theory and Applications"

- Chair of IEEE Computer Society European TTTC

- Database and Web chair of the TTTC and several test-related conferences

- Vice Chair of the Technical Activity "Hardware Security and Trust" of the IEEE Computer Society TTTC

- Co-Chair of the Technical Activity on "Embedded System Security" of GDR (Groupe de Recherche) SoC-SiP of CNRS

- Member of the program committee of several international conferences and reviewers for several journals

- Participation to the company MoleSystems for the development of a peer-review system

- General Chair of TRUDEVICE'13, Vice-Program Chair of DTIS'14, Program-Chair of DTIS'15, Vice Program Chair of ETS'15, Co-General Chair of ISVLSI'15

- Review Chair of DATE conference (since 2012)

- Publication chair of ETS'12, ETS'13, ETS'14, VTS'13, VTS'14

- Publicity chair of the TTEP

- PC Member of: VTS, ETS, IOLTS, DSD, LATW, DCIS, AQTR, EUC

- IEEE Computer Society Golden Core Member

- "Meritorious Service Award in recognition of more than 8 years of significant services for TTTC Electronic Media"

- Senior Member of IEEE

# 2. Summary of scientific activities

#### 2.1. Preamble

I have carried out all my studies in Italy. Moreover, after a PhD in Computer Engineering in the domain of the dependability of digital systems at the Politecnico di Torino (Italy), I pursued 4 years of post-doc research at the same institute in the domain of reliability and test of digital systems. Thanks to cooperations between the Politecnico di Torino and the LIRMM of Montpellier, I had the opportunity to obtain a post-doc position in France. There, in addition to the topics which were already familiar to me (i.e., reliability and test), I had the occasion to explore a new application domain: the secure devices. At LIRMM I have kept on working on test and reliability, with a particular focus on secure devices. My scientific results, students I have supervised, my teaching activities, and in general my research projects directly reflects my career path.

#### 2.2. Current research activities

Research activities I carried on after my nomination as *Chargé de Recherche* deal with the definition of methodologies and tools for the design, the test and the reliability of secure digital circuits and trustworthy manufacturing. More recently, we have started a new research activity on the test of 3D stacked Integrated Circuits, based on the use of Through Silicon Vias. Moreover, thanks to the relationships I have maintained after my post-doc in Italy, I have kept on cooperating with Politecnico di Torino on the topics related to test and reliability of memories and microprocessors.

#### 2.2.1. Secure and Trusted Devices

Security is a critical part of information and communication technologies and it is the necessary basis for obtaining confidentiality, authentication, and integrity of data. The importance of security is confirmed by the extremely high growth of the smart-card market in the last 20 years. It is reported in "Le monde Informatique" in the article "Computer Crime and Security Survey" in 2007 that financial losses due to attacks on "secure objects" in the digital world are greater than \$11 Billions. Since the race among developers of these secure devices and attackers accelerates, also due to the heterogeneity of new systems and their number, the improvement of the resistance of such components becomes today's major challenge.

Concerning all the possible security threats, the vulnerability of electronic devices that implement cryptography functions (including smart cards, electronic passports) has become the Achille's heel in the last decade. Indeed, even though recent crypto-algorithms have been proven resistant to cryptanalysis, certain fraudulent manipulations on the hardware implementing such algorithms can allow extracting confidential information. So-called Side-Channel Attacks have been the first type of attacks that target the physical device. They are based on information gathered from the physical implementation of a cryptosystem. For instance, by correlating the power consumed and the data manipulated by the device, it is possible to discover the secret encryption key. Nevertheless, this point is widely addressed and integrated circuit (IC) manufacturers have already developed different kinds of countermeasures.

More recently, new threats have menaced secure devices and the security of the manufacturing process. A first issue is the trustworthiness of the manufacturing process. From one side, secure devices must assure a very high production quality in order not to leak confidential information due to a malfunctioning of the device. Therefore, possible defects due to manufacturing imperfections must be detected. This requires high-quality test procedures that rely on the use of test features that increases the controllability and the observability of inner points of the circuit. Unfortunately, this is harmful from a security point of view, and therefore the access to these test features must be protected from unauthorized users. Another harm is related to the possibility for an untrusted manufacturer to do malicious alterations to the design (for instance to bypass or to disable the security fence of the system). Nowadays, many steps of the production cycle of a circuit are outsourced. For economic reasons, the manufacturing process is often carried out by foundries located in foreign countries. The threat brought by so-called Hardware Trojan Horses, which was long considered theoretical, begins to materialize.

A second issue is the hazard of faults that can appear during the circuit's lifetime and that may affect the circuit behavior by way of soft errors or deliberate manipulations, called Fault Attacks. They can be based on the intentional modification of the circuit's environment (e.g., applying extreme temperature, exposing the IC to radiation, X-rays, ultra-violet or visible light, or tampering with clock frequency) in such a way that the function implemented by the device generates an erroneous result. The attacker can discover secret information by comparing the erroneous result with the correct one. In-the-field detection of any failing behavior is therefore of prime interest for taking further action, such as discontinuing operation or triggering an alarm. In addition, today's smart cards use 90nm technology and according to the various suppliers of chip, 65nm technology will be effective on the horizon 2013-2014. Since the energy required to force a transistor to switch is reduced for these new technologies, next-generation secure systems will become even more sensitive to various classes of fault attacks.

Based on these considerations, within the group I work with, we have proposed new methods, architectures and tools to solve the following problems:

- Test of secure devices: unfortunately, classical techniques for digital circuit testing cannot be easily used in this context. Indeed, classical testing solutions are based on the use of Design-For-Testability techniques that add hardware components to the circuit, aiming to provide full controllability and observability of internal states. Because crypto-processors and others cores in a secure system must pass through high-quality test procedures to ensure that data are correctly processed, testing of crypto chips faces a dilemma. In fact design-for-testability schemes want to provide high controllability and observability of the device while security wants minimal controllability and observability in order to hide the secret. We have therefore proposed, form one side, the use of enhanced scan-based test techniques that exploit compaction schemes to reduce the observability of internal information while preserving the high level of testability. From the other side, we have proposed the use of Built-In Self-Test for such devices in order to avoid scan chain based test.

- Reliability of secure devices: we proposed an on-line self-test architecture for hardware implementation of the Advanced Encryption Standard (AES). The solution exploits the inherent spatial replications of a parallel architecture for implementing functional redundancy at low cost.

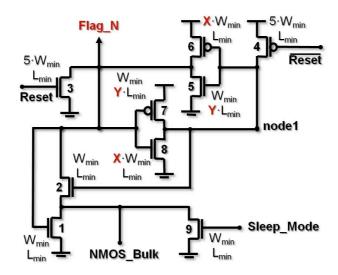

- Fault Attacks: one of the most powerful types of attack for secure devices is based on the intentional injection of faults (for instance by using a laser beam) into the system while an encryption occurs. By comparing the outputs of the circuits with and without the injection of the fault, it is possible to identify the secret key. To face this problem we have analyzed how to use error detection and correction codes as counter measure against this type of attack, and we have proposed a new code-based architecture. Moreover, we have proposed a bulk built-in current-sensor that allows detecting the presence of undesired current in the substrate of the CMOS device.

- Fault simulation: to evaluate the effectiveness of countermeasures against fault attacks, we developed an open source fault simulator able to perform fault simulation for the most classical fault models as well as user-defined electrical level fault models, to accurately model the effect of laser injections on CMOS circuits.

- Side-Channel attacks: they exploit physical data-related information leaking from the device (e.g. current consumption or electro-magnetic emission). One of the most intensively studied attacks is the Differential Power Analysis (DPA) that relies on the observation of the chip power fluctuations during data processing. I studied this type of attack in order to evaluate the influence of the countermeasures against fault attack on the power consumption of the device. Indeed, the introduction of countermeasures for one type of attack could lead to the insertion of some circuitry whose power consumption is related to the secret key, thus allowing another type of attack more easily. We have developed a flexible integrated simulation-based environment that allows validating a digital circuit when the device is attacked by means of this attack. All architectures we designed have been validated through this tool. Moreover, we developed a methodology that allows to drastically reduce the time required to validate countermeasures against this type of attack.

#### 2.2.2. TSV- based 3D Stacked Integrated Circuits Test

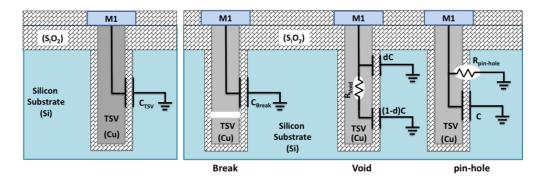

The stacking process of integrated circuits using TSVs (Through Silicon Via) is a promising technology that keeps the development of the integration more than Moore's law, where TSVs enable to tightly integrate various dies in a 3D fashion.

Nevertheless, 3D integrated circuits present many test challenges including the test at different levels of the 3D fabrication process: pre-, mid-, and post- bond tests. Pre-bond test targets the individual dies at wafer level, by testing not only classical logic (digital logic, IOs, RAM, etc) but also unbounded TSVs. Mid-bond test targets the test of partially assembled 3D stacks, whereas finally post-bond test targets the final circuit.

The activities carried out within this topic cover 2 main issues:

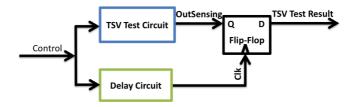

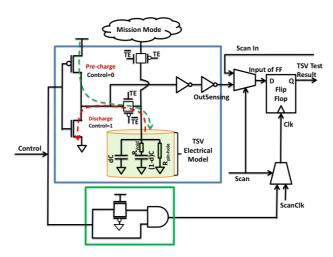

- Pre-bond test of TSVs: the electrical model of a TSV buried within the substrate of a CMOS circuit is a capacitance connected to ground (when the substrate is connected to ground). The main assumption is that a defect may affect the value of that capacitance. By measuring the variation of the capacitance's value it is possible to check whether the TSV is correctly fabricated or not. We have proposed a method to measure the value of the capacitance based on the charge/ discharge delay of the RC network containing the TSV.

- Test infrastructures for 3D stacked Integrated Circuits: testing a die before stacking to another die introduces the problem

of a dynamic test infrastructure, where test data must be routed to a specific die based on the reached fabrication step.

New solutions are proposed in literature that allow reconfiguring the test paths within the circuit, based on on-the-fly

requirements. We have started working on an extension of the IEEE P1687 test standard that makes use of an automatic

die-detection based on pull-up resistors.

#### 2.2.3. Memory and Microprocessor Test and Reliability

Thanks to device shrinking and miniaturization of fabrication technology, performances of microprocessors and of memories have grown of more than 5 magnitude order in the last 30 years. With this technology trend, it is necessary to face new problems and challenges, such as reliability, transient errors, variability and aging.

In the last five years I've worked in cooperation with the Testgroup of Politecnico di Torino (Italy) to propose a new method to on-line validate the correctness of the program execution of a microprocessor. The main idea is to monitor a small set of control signals of the processors in order to identify incorrect activation sequences. This approach can detect both permanent and transient errors of the internal logic of the processor.

Concerning the test of memories, we have proposed a new approach to automatically generate test programs starting from a functional description of the possible faults in the memory.

Moreover, we proposed a new methodology, based on microprocessor error probability profiling, that aims at estimating fault injection results without the need of a typical fault injection setup. The proposed methodology is based on two main ideas: a one-time fault-injection analysis of the microprocessor architecture to characterize the probability of successful execution of each of its instructions in presence of a soft-error, and a static and very fast analysis of the control and data flow of the target software application to compute its probability of success.

#### 2.3. Students

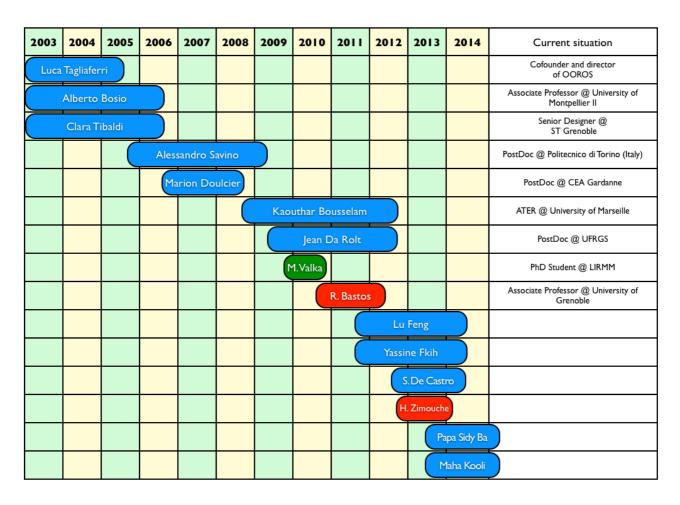

After my Ph.D. I have co-supervised 2 post-doc student, 10 Ph.D. students, 1 post-master student, and 32 master students. Table 1 summarizes post-doc (in red), Ph.D. (in blue) and post-master (in green) students in chronological order. Master students are not listed in this table for sake of simplicity. Section 4 of Chapter 2 will describe the work of each student in detail.

Table 1: Summary of the students

# 2.4. Scientific Projects

Starting from my Ph.D., I have actively cooperated to national- and european-funded scientific projects. The following list summarizes, for each project, the period, the project type and the type of involvement. Details concerning each project are given in Section 6 of Chapter II.

- 2013-2016: Scientific Leader (for the CNRS) of the European FP7 Project (STREP) called **CLERECO**, which is devoted to the early evaluation of the reliability of complex digital systems based on micro-processors, for both embedded systems and High Performance Computers.

- 2012-2016: Action Chair (i.e., project leader) of the COST Action IC1204, **TRUDEVICE**: "Trustworthy Manufacturing and Utilization of Secure Devices". This COST action aims at creating a European network of competence and experts on all aspects of hardware security including design, manufacturing, testing, reliability, validation and utilization. The network will

play a key role in developing solutions responding to the hardware security challenges, hence strengthening the position of Europe in the field. I am the coordinator of the whole Action.

- 2012-2015: Participation to the project **MASTER 3D**, which is devoted to the study of 3D Stacked Integrated Circuits. The project is funded by the European CATRENE program.

- 2012-2015: Participation to the project **HOMERE**, which is devoted to the study of Hardware Trojans. The project is funded by the General Directorate for Competitiveness, Industry and Services (DGCIS) and it is sponsored by the "Secure Communications Solutions" competitiveness cluster.

- 2012-2015: Participation to the ANR project **LIESSE**, which is devoted to the study of vulnerabilities of the physical implementation of cryptographic algorithms (CMOS 65, 40, and 28 nm). My group is the leader of the project

- Modeling work laser effects on circuits will be conducted. The resulting models will be used to develop simulators representing physical effects. This project should enable a better understanding of the physical phenomena involved and their experimental application. Its purpose is to propose new principles of security evaluation circuit vis-à-vis these attacks and validate against-measures..

- 2011-2014: Participation to the work package 4 of the project **CALISSON 2**, which aims to unite research efforts in order to improve the security of integrated circuits for the components market which provides security functions. The project is funded by the General Directorate for Competitiveness, Industry and Services (DGCIS) and it is sponsored by the "Secure Communications Solutions" competitiveness cluster.

- 2010-2013: Participation to the Work Packages 2 and 6 (related to test and security) of the project **PROSECURE**, that targets the design and development of an embedded secure microprocessor. This project is funded by the French Languedoc-Roussillon region.

- 2008-2011: Participation to **TOETS** project (European CATRENE CT302) that has the ambition to create a breakthrough in methods and flows used by the test technologies by considering the test in the whole value chain from Design to Application. A strong consortium composed of European Semiconductor industries, Academics and Small and Medium Enterprises has grouped their competences to successfully address this challenge.

- 2007-2010: Participation to the work package 3 of the project **CALISSON**, to enhance the security of electronic devices by developing new design flows in order to reduce the overall design cost and to increase the Time to Market. The project is funded by the General Directorate for Competitiveness, Industry and Services (DGCIS) and it is sponsored by the "Secure Communications Solutions" competitiveness cluster.

- 2004-2006: Participation to **TReDiCo** within the framework of the Protocol for scientific and technological collaboration between the Republic of Italy and Slovak Republic.

- 2001/03: Leader of the Work Package 2 Task 1 ("BISR for SRAM memories") of the project called "**TestDOC**: Quality and Reliability of System-on-chip" funded by the Istituto Superiore M. Boella (<a href="www.testgroup.polito.it/tdoc">www.testgroup.polito.it/tdoc</a>)

- 2001/03: Participation to the **GRAAL** project. The goal of this project was the implementation of a tool targeting the automatic generation of highly dependable SRAMs. It has been developed under the project S167P founded by the Italian Ministry of the University and Technological and Scientific Research

- 2000/02: Participation to the framework of the "Giovani Ricercatori" (Young Researchers) project at Politecnico di Torino. The goal of the project was the development of new methodologies to increase the dependability of space applications using software techniques.

# 2.5. Teaching activities

Starting from my Ph.D. studies, I have performed various teaching activities at different levels: engineering students of the Politecnico di Torino and the Engineering School of the University of Montpellier 2, master students of the military school of the University of Torino, students of private institutions, as well as embedded tutorials on specific scientific topics in international conferences. Table 2 summarizes my pedagogical activities. The column dedicated to the time spent for each subject is classified in 3 set: lectures (i.e., "Cours magistraux"), tutorials (i.e., "Travaux dirigés"), and practical work (i.e., "Travaux pratique").

| Subject                | Period  | Hours    |           |           | Location                                        |  |  |

|------------------------|---------|----------|-----------|-----------|-------------------------------------------------|--|--|

| Subject                | Periou  | Lectures | Tutorials | Practical | Location                                        |  |  |

| Automatic Processes    | 2005/06 | 42       |           |           | Lipit rareity of Tarina                         |  |  |

| Automatic Processes    | 2004/05 | 42       |           |           | University of Torino                            |  |  |

| _                      | 2006/07 |          | 10        | 15        |                                                 |  |  |

|                        | 2002/03 |          | 20        | 30        | Politecnico di Torino                           |  |  |

|                        | 2001/02 |          | 20        | 30        | - Officering at forms                           |  |  |

|                        | 2000/01 |          | 20        | 30        |                                                 |  |  |

| Operating              | 2013/14 | 12       |           |           | -                                               |  |  |

| Systems                | 2012/13 | 24<br>12 |           |           | University of Montpellier 2 (UFR)               |  |  |

| Cysterns               | 2011/12 | 12       |           | 15        | -                                               |  |  |

| _                      | 2007/08 |          |           | 15        |                                                 |  |  |

| _                      | 2005    | 60       |           | 40        | Private institution (ENAIP Torino)              |  |  |

|                        | 2004    | 16       |           | 16        | Private institution (ACME Consulting Torino)    |  |  |

|                        | 2005/06 |          | 20        | 30        |                                                 |  |  |

|                        | 2004/05 |          | 10        | 15        |                                                 |  |  |

|                        | 2003/04 |          | 10        | 15        | Politecnico di Torino - C                       |  |  |

|                        | 2002/03 |          | 10        | 15        | T Officer floor of Torrito                      |  |  |

|                        | 2001/02 |          | 20        | 30        |                                                 |  |  |

| -                      | 2000/01 | 4.5      | 10        | 15        |                                                 |  |  |

| -                      | 2013/14 | 15       | 40        | 45        | -                                               |  |  |

| -                      | 2012/13 |          | 40        | 30<br>45  | -                                               |  |  |

| Programming Languages  | 2010/11 |          | 40        | 60        | University of Montpellier 2 (Polytech) - C, ASM |  |  |

| Trogramming Languages  | 2009/10 |          | 40        | 60        | -                                               |  |  |

|                        | 2008/09 |          |           | 80        | 1                                               |  |  |

|                        | 2005    | 50       | 50        | 50        | Private institution (ENAIP) - JAVA              |  |  |

|                        | 2003    | 10       | 15        | 15        | Private institution (ACME) - Visual Basic       |  |  |

|                        | 2003    | 15       |           | 15        | Private institution (CTS Ivrea) - VHDL          |  |  |

|                        | 2002    | 10       | 15        | 15        | Private institution (Mezzelani Rome) - C++      |  |  |

|                        | 2012/13 | 12       |           |           | University of Montpellier 2 (Polytech)          |  |  |

| Databassa              | 2005/06 |          | 10        | 15        |                                                 |  |  |

| Databases              | 2004/05 |          | 10        | 15        | Politecnico di Torino                           |  |  |

| [                      | 2001/02 |          | 10        | 15        | 1 Ontect lico di Totilio                        |  |  |

|                        | 2000/01 |          | 10        | 15        |                                                 |  |  |

|                        | 2012/13 | 12       |           |           | University of Montpellier 2 (Polytech)          |  |  |

| 5. 5. 6. 6. 5. 6.      | 2006/07 | 15       | 10        |           | Politecnico di Torino                           |  |  |

| Digital System Testing |         |          |           |           | Master CICA Cardonna                            |  |  |

| I                      | 2009    | 6        |           |           | Master SISA - Gardanne                          |  |  |

Table 2: Summary of the teaching activities

# 2.6. Cooperations

Table 3 summarizes the main cooperations I had since I started my PhD. I showed only cooperations that led to either a publication, or a common research or networking project.

|        |                              |                       | Memory<br>Test | μProcessor<br>Test | Reliability | Security | 3D Test | Dissemination of knowledge |

|--------|------------------------------|-----------------------|----------------|--------------------|-------------|----------|---------|----------------------------|

|        |                              | Paolo Prinetto        | ✓              | ✓                  | ✓           |          |         |                            |

|        |                              | Alfredo Benso         | ✓              | ✓                  | ✓           |          |         |                            |

|        | Politecnico di               | Silvia Chiusano       | ✓              |                    |             |          |         |                            |

|        | Torino                       | Stefano Di Carlo      | ✓              | ✓                  | ✓           |          |         |                            |

|        |                              | Angelo Serra          |                | ✓                  |             |          |         |                            |

| U      |                              | Matteo Sonza Reorda   |                |                    |             |          |         | ✓                          |

| N      | UBS                          | Guy Gogniat           |                |                    |             |          |         | ✓                          |

| V      | TIMA                         | Paolo Maistri         |                |                    |             |          |         | ✓                          |

| E<br>R | Paderborn<br>University      | Sybille Hellebrand    | ✓              |                    |             |          |         | ✓                          |

| 1      | Slovak Academy of<br>Science | Elena Gramatova       | ✓              |                    |             |          |         |                            |

| T      | University of                | M. Hosseinabady       |                |                    | ✓           |          |         |                            |

| E      | Tehran                       | Z. Navabi             |                |                    | ✓           |          |         |                            |

| S      | University of<br>Passau      | Ilia Polian           |                |                    |             | ✓        |         | ✓                          |

|        | TU Delft                     | Said Hamdioui         |                |                    |             | ✓        |         |                            |

|        | KUL                          | Ingrid Verbauwhede    |                |                    |             | ✓        |         |                            |

|        | ENMSE                        | Jean Max Dutertre     |                |                    |             | ✓        |         |                            |

| C      | Siemens                      | Monica Lobetti Bodoni | ✓              |                    |             |          |         |                            |

| M<br>P | CEA                          | Pascal Vivet          |                |                    |             |          | ✓       |                            |

| A<br>N | Yogitech                     | Riccardo Mariani      |                | ✓                  |             |          |         |                            |

| I      | Mentor                       | Schloeffel Juergen    |                |                    |             |          | ✓       |                            |

| S      | DGA                          | Denis Real            |                |                    |             | ✓        |         |                            |

Table 3: Summary of cooperations

# 2.7. Dissemination of knowledge

#### **Executive and Organizing committees**

- TRUDEVICE Workshop: General Chair (2013)

- Design and Test of Integrated Circuits (DTIS): Vice-Program Chair (2014) and Program Chair (2015)

- Design, Automation and Test in Europe Conference (DATE): Review Chair (from 2012)

- VLSI Test Symposium (VTS): Publication Chair (from 2012), Publicity and Web Chair (from 2006 to 2013)

- European Test Symposium (ETS): Vice-Program Chair (ETS'15), Publication Chair (from 2012)

- Latin American Test Workshop (LATW): Publicity Chair (from 2011)

- South European Test Seminar (SETS): General Chair (2007)

#### Program committee and reviewer

- Associate Editor of the journal: "Information Security Journal: A Global Perspective"

- Guest Editor of the journal "IEEE Design & Test"

- Guest Editor of the journal "IEEE JETTA: Journal of Electronic Testing Theory and Applications"

- Reviewer for the following Journals: IEEE Transaction on VLSI, IEEE Transaction on Computer, IEEE Transactions on Emerging Topics in Computing, IEEE Transactions on Embedded Computing Systems, Journal of Cryptographic Engineering, IEEE Journal of Electronic Testing - Theory and Applications, IEEE Transactions on Circuits and Systems, Microprocessors and Microsystems, IET Computers & Digital Techniques, International Journal of Communications, Network and System Sciences, IEEE Design and Test of Computers

- Program Committee: DATE (from 2008 to 2011), LATW (from 2012), VTS (from 2007), IOLTS (from 2010), ETS (from 2007), DSD (from 2009), DCIS (from 2006), AQTR (from 2004), EAC (from 2014)

- Reviewer for the following conferences: DAC (2013), ITC (from 2008)

#### **GDR SoC-SiP**

• Co-Chair of the Technical Activity on "Embedded System Security" of GDR (Groupe de Recherche) SoC-SiP of CNRS, from 2009 to 2013.

#### TTTC

- Chair of the European "Test Technology Technical Council" (www.etttc.org) of IEEE Computer Society (from 2014)

- Vice-Chair of the European "Test Technology Technical Council" (www.etttc.org) of IEEE Computer Society (2010-2013)

- Chair of the Database Group of the "Test Technology Technical Council" (TTTC) of IEEE Computer Society (from 2012)

- TTTC Test Technology Educational Program (TTEP): Publicity Chair (from 2012)

- Vice-Chair of the Technical Activity on "HARDWARE SECURITY AND TRUST" of IEEE Computer Society TTTC (from 2011)

- Web Master of the "Test Technology Technical Council" (tab.computer.org/tttc) of IEEE Computer Society (from 2004)

#### **Awards and Certificates**

- Best paper (Transaction on Computer), awarded by a movie published at "Computing Now" (http://www.computer.org/ portal/web/computingnow/1211/whatsnew/tc)

- "IEEE Computer Society Golden Core Member" (2011)

- "Meritorious Service Award in recognition of more than 8 years of significant services for TTTC Electronic Media" (2007)

- "Certificate of Appreciation from IEEE Computer Society for serving as TTTC Webmaster in 2006/2007" (2007)

- "Certificate of Appreciation from IEEE Computer Society for serving as TTTC Webmaster in 2004/2005" (2005)

#### 2.8. Publications

Table 4 summarizes the number of my publications for each year, classified by book chapters, journal papers (with review process), papers published in official proceedings (coming from conferences, symposia or workshops with review process), and presentations given in national and international events without official proceedings.

|       | Book    | Journal | Proceedings |           |          | Presentations |          |          |        | Total |     |

|-------|---------|---------|-------------|-----------|----------|---------------|----------|----------|--------|-------|-----|

| Year  | Chapter |         | Conference  | Symposium | Workshop | Invited       | Workshop | Tutorial | Poster | Demo  |     |

| 2000  | 0       | 0       | 2           | 0         | 2        | 0             | 0        | 0        | 0      | 0     | 4   |

| 2001  | 0       | 1       | 2           | 2         | 2        | 0             | 0        | 0        | 0      | 0     | 7   |

| 2002  | 0       | 1       | 2           | 1         | 0        | 0             | 0        | 0        | 0      | 0     | 4   |

| 2003  | 0       | 2       | 1           | 3         | 1        | 0             | 0        | 0        | 0      | 0     | 7   |

| 2005  | 0       | 0       | 2           | 1         | 2        | 0             | 0        | 0        | 0      | 0     | 5   |

| 2006  | 0       | 0       | 3           | 5         | 2        | 0             | 0        | 0        | 0      | 0     | 10  |

| 2007  | 0       | 1       | 0           | 2         | 1        | 0             | 3        | 0        | 0      | 0     | 7   |

| 2008  | 0       | 2       | 1           | 5         | 1        | 0             | 5        | 0        | 0      | 2     | 16  |

| 2009  | 0       | 1       | 0           | 0         | 1        | 0             | 0        | 2        | 0      | 0     | 4   |

| 2010  | 1       | 1       | 0           | 3         | 0        | 0             | 2        | 1        | 0      | 2     | 10  |

| 2011  | 1       | 1       | 1           | 3         | 2        | 0             | 1        | 0        | 0      | 0     | 9   |

| 2012  | 0       | 2       | 0           | 3         | 1        | 0             | 4        | 0        | 1      | 0     | 11  |

| 2013  | 0       | 5       | 2           | 3         | 3        | 2             | 6        | 0        | 0      | 0     | 21  |

| 2014  | 0       | 1       | 1           | 0         | 0        | 0             | 0        | 0        | 0      | 0     | 2   |

| Total | 2       | 18      | 62          |           |          | 35            |          |          |        |       | 117 |

Table 4: Summary of publications

The complete list of publications is given in Chapter 4. The most cited publications are shown in the following list, leading to an H-index of 15:

- 1) [J2] --> 48 citations

- 2) [S5] --> 37 citations

- 3) [W1] --> 34 citations

- 4) [C1] --> 34 citations

- 5) [S1] --> 31 citations

- 6) [C7] --> 27 citations

- 7) [S23] --> 22 citations

- 8) [W2] --> 22 citations

- 9) [J4] --> 20 citations

- 10) [S3] --> 19 citations

- 11) [S18] --> 17 citations

- 12) [C5] --> 16 citations

- 13) [S14] --> 15 citations

- 14) [S7] --> 15 citations

- 15) [J3] --> 15 citations

# Chapter II: Details

# 3. Research activities

This section summarizes the research activities I carried out starting from my master thesis in 1999.

#### Research activities at Politecnico di Torino

Since 1999, I worked in the area of digital systems dependability for safety-critical applications at the Politecnico di Torino (Italy), in cooperation with Prof. Paolo Prinetto's research group. His research activity mainly focused on the definition of new methodologies and the implementation of tools able to improve the development of highly dependable systems, at different levels: for basic digital components, for systems on chip, up to microprocessor-based systems. My research activity, developed during 1 year of master thesis, plus 3 years of PhD and 4 years of PostDoc focused on fault tolerance, reliability and test of digital systems. In particular I worked on the following topics:

- Definition of functional fault models for memories RAM and automatic generation of test sequences (Sections 3.1 and 3.3);

- Software Implemented Hardware Fault Tolerance methods (Section 3.2);

- Implementation of a software techniques based on the "Programming by Contract" paradigm for the protection of the application data (Section 3.4).

#### Research activities at LIRMM

Starting from December 2006 I started working at LIRMM by focusing mainly on the security of hardware devices.

In the last decade, integrated systems are being increasingly deployed in many security-critical infrastructures such as sensitive governmental organizations, military, and financial/banking systems, where the impact and consequences of attacks could be catastrophic. Several types of attacks have been proposed in literature. Among the most known attacks in literature, we have focused on all aspects of the security that either impact or influence the manufacturing testing, or that require the same skills and knowledge strictly related to test and reliability. In particular we worked on the following topics:

- Reliability of the AES (Section 3.5);

- Manufacturing Test of Secure Devices (Section 3.6);

- Fault attacks (Section 3.7)

Besides the activities on hardware security, we have recently addressed the new challenges related to the test of 3D-SIC (Stacked Integrated Circuits). The stacking process of integrated circuits using TSVs (Through Silicon Via) is a promising technology that keeps the development of the integration more than Moore's law, where TSVs enable to tightly integrate various dies in a 3D fashion. The problem of testing 3D-SIC and some solutions are described in Section 3.8.

Finally, in cooperation with the Politecnico di Torino, we propose a new method to on-line validate the correctness of the program execution of a microprocessor, as well as a methodology based on microprocessor error probability profiling that aims at estimating fault injection results without the need of a typical fault injection setup. This activity is described in Section 3.9.

# 3.1. Memory BIST and BISR (Master thesis)

During my master thesis I explored an architecture able to increase the reliability of a memory, based on self-repair features. The process of repairing a RAM can be divided into several steps. In a first phase, a test algorithm is executed on the memory array. If a fault is detected, it is necessary to locate it (diagnosis) and to allocate redundant memory space to replace the faulty cell. When these operations are built-in the RAM architecture, the steps are named: BIST (Built-In Self-Test), BISD (Built-In Self-Diagnosis), BIRA (Built-In Redundancy-Allocation), BISR (Built-In Self-Repair).

I proposed an innovative architecture for SRAM, characterized by BISR capabilities based on cell-only redundant space allocation at the user level. The memory is not electrically repaired, but spare cells replace faulty ones, using an on-line address re-mapping scheme. The repair process is transparent to the user, and is independent from the memory physical implementation. Moreover, the self-repair architecture is coupled with an ad-hoc defined on-line transparent BIST algorithm, thus implementing a BISTAR (Built-In Self-Test and Repair) approach. The on-line BIST is therefore executed concurrently with the memory normal behavior, and is able to detect the appearance of a wide range of faults, including coupling faults, usually not detectable during end-of-production or power-up tests.

The conceptual idea underlying the proposed approach is to couple an on-line transparent BIST algorithm with a "functional self-repair" architecture in the same BISTAR logic. "Functional self-repair" means that a faulty cell must be replaced by a spare one using an address re-mapping scheme. The BIST part of the logic executes an on-line test, based on a linear algorithm, to detect single stuck-at, transition, coupling, and address faults. Fig. 1 is a conceptual view of the BISTAR architecture. The self-repair logic is based on a CAM used to re-map the address of the faulty cells. The BISTAR controller is in charge of executing the test algorithm and controlling the repair procedures.

The BISR strategy aims at keeping constant the memory storing-capability seen by the user. Faulty cells are functionally replaced by spare ones via a dynamic on-the-fly reconfiguration of the memory-addressing space. From an external user point of view, the memory has a nominal addressing space of N cells, of m-bits each. The actual memory module, instead, has an effective storage capacitance of N+K cells. To optimize the allocation of the redundant memory space, the approach is based on a cell-only repair strategy: when a fault is detected in a cell, instead of repairing an entire row or column, only the faulty cell is re-mapped on a spare one.

Address re-mapping is achieved by a K-lines CAM. In particular, the i<sup>th</sup> line of the CAM stores the address of the i<sup>th</sup> faulty cell, that is replaced by the first i<sup>th</sup> spare cell. This solution allows reducing the area and the routing overhead. Instead of using an additional register into the CAM in which is stored the address of the redundant cell, the association between the line position and the redundant cell is hardwired. Whenever a cell of the memory is accessed, its address is first looked up in the CAM. Two cases can occur:

- If it has been previously detected faulty (or is currently a cell under test), its address has been stored in the CAM. Then, when accessed, the CAM reacts with a hit, and outputs the address of the replace cell, and a proper multiplexer routes it to the memory array. Any operation on the faulty cell is thus performed on its replacement

- If a spare cell does not currently replace the target cell, its address, not being stored in the CAM, is directly transferred to the memory array.

During testing, the cell under test is isolated by replacing it with a spare one: the original content is copied into the spare cell and the CAM content updated for address re-mapping. The test algorithm is then executed on the cell. If no faults are detected, the original content is restored and its re-mapping address in the CAM removed.

This work and its extensions are published in [J1], [J2], [J4], [C1], [C3], [W1], [W2].

# 3.2. Software Implemented Hardware Fault Tolerance (PhD Thesis)

The PhD thesis has been carried out in the field of safety critical applications that require high dependability. The work focused on the definition of software techniques that guarantee the correctness of the system (both hardware and software) even in presence of faults.

Electronic systems used in military, avionics and aerospace require high reliability and availability. Fault-tolerance has always been an essential attribute of these systems to keep them operational in harsh environments. For example, electromagnetic interference, power glitches and radiations can cause transient faults in electronic systems. Such faults can cause abnormal behavior of computer systems. For example, in radiation environment, alpha-particles, cosmic rays and solar wind flux can cause a Single Event Upset (SEU), which is one of the major sources of bit-flips in digital electronics. A bit-flip is an undesired change in the state of a memory cell; a SEU can cause the state of a memory cell to change from 0 to 1 or 1 to 0, or, in combinational circuits, e.g., an arithmetic logic unit, can lead to incorrect computation results. Besides, devices miniaturization, increasing clock frequencies and the introduction of microprocessors into electrically active environments increase the incidence of SEU also in every day life environments.

Commercial components are usually designed to function in an environment different from that of safety critical applications, thus without fault tolerance capability. If commercial components have to be used for critical applications with no change in hardware, fault tolerance should be provided through software techniques. Software Implemented Hardware Fault Tolerance (SIHFT) detects or tolerates faults in the hardware by software method without any dedicated hardware for error detection or fault tolerance. The benefit of employing SIHFT is that we can improve the availability of the system using the existing design of the hardware available in the market.

To understand the behavior of a computer-based system affected by a SEU when software is running, we have to model and define the errors that occur during program execution. A program can be considered as a sequence of instructions, and the execution of the program can be viewed as executing instructions in a desired sequence. For a more precise description, we define a basic block as a sequence of instructions without any branching inside or outside except for the last instruction; then, a program can be represented by a program graph, which consists of basic blocks and directed edges connecting the basic blocks. If the correct execution sequence in the program graph is broken, it is a Control Flow error. If the information stored in memory is corrupted, it is a Memory error. For example, one of the control flow errors is a branch creation; the correct execution sequence among basic blocks is broken. An example for memory error is the case in which the content of a variable is changed because of a bit-flip.

During my PhD, I developed several innovative SIHFT techniques for the control flow checking and for errors in the memories:

- Reliable C/C++ Code Compiler for dependable applications (RECCO), to check memory errors. The technique is based on a C/C++ Source-to-Source Compiler able to increase the dependability properties of a given application. The adopted strategies are based on code re-ordering and variable duplication/triplication. The approach can be applied to any C/C++ source code, and introduces code modifications that are transparent to the original program functionality. Moreover, it is portable to any platform. The RECCO tool, which fully automates the process, allows the user to trade-off between the level of dependability improvement and the performance degradation due to the code modification;

- A methodology to compute the criticality of variables in a software application. Instead of resorting to time consuming fault injection experiments, the proposed solution is based on the run/time analysis of the variables' behavior logged during the execution of the application under different workloads;

- A detailed error analysis and classification of the behavior of an open-source router, when affected by SEU. The performed experiments allow identifying the most critical router variables according to their impact on system dependability and to validate the strategies employed in the RECCO tool to analyze a C software;

- Control Flow Checking via Regular Expressions, to check the control flow of a program. The check has inserted at sourcecode level using a signature methodology based on regular expressions. The signature checking is performed without

dedicated watchdog processor but resorting to inter-process communication (IPC) facilities offered by most of the modern

Operating Systems;

- A static executable code analysis methodology able to compute, depending on the target microprocessor platform, the upper-bound probability that a given application incurs in a Control Flow Error;

- Interposition agents to "wrap" the application software and transparently code all the communications between the application and the surrounding hardware and software environment.

The results of the works carried out during my PhD thesis have been published in the papers [J3], [C2], [C5], [C6], [C9], [S1], [S4], [S5], [S9], [S1], [W3], [W4], [W5], [W7], [P1] referenced in the Publication list. Moreover, part of the work on memory test has been performed in the context of the project "Giovani Ricercatori" (see section 6).

# 3.3. Memory Test (Post-Doc at Politecnico di Torino, Italy)

The main issue in memory testing is to define comprehensive fault models able to carefully represent the most common defects occurring in the production phase of the chips. Along with fault models, new test algorithms have to be developed. Among the different types of algorithms proposed to test Static Random Access Memories (SRAMs), March Tests have proven to be faster, simpler and regularly structured.

A large number of March Tests with different fault coverage have been published; most of them have been generated by hand. The rapid grow of the memory production technologies introduce new classes of faults, such as Dynamic Memory Faults, making the task of hand writing test algorithms harder and it may lead to non-optimal results.

Although some hand-made March Tests to deal with these new faults have been published, the problem of comprehensive automatically generating March Tests for memory, for classic and new fault models, also easy to extend to user-defined models, was not yet addressed when I started my post-doc.

I proposed a new approach to automatically generate March Tests, starting from a formal model to represent faulty behavior in a memory that allows treating the most important classes of memory faults (Dynamic Faults, Static Faults and also Linked Faults). The formal model is based on Functional Fault Model that is a deviation of the memory behavior from the expected one under a set of performed operations. The memory is modeled resorting to a digraph where nodes represent the memory states whereas arcs represent read and write operations. The automatic generation is based on a visit of the graph, without resorting to exhaustive search. Experimental Results show that newly generated march test can reduce the test complexity, and therefore the test time with respect to the state of the art memory tests published before 2005.

The results of the works carried out have been published in the papers [J5], [J6], [J7], [C4], [C7], [C8], [C10], [S2], [S3], [S7], [S8], [S11], [W8], [W9], [P3], [P4] referenced in the Publication list. Moreover, part of the work on memory test has been performed in the context of the project "TestDOC" (see Section 6).

# 3.4. Programming by Contracts (Post-Doc at Politecnico di Torino, Italy)

In this field we developed a C++ library called PROMON that encapsulates software techniques to intercept faults that may occur during the execution of the application and, block the execution; the innovative aspect of the approach is that the implemented methodology relies on the principle of Programming by contract, and on the use of common assertions, pre and post-conditions, to ensure that the code follows its expected behavior.

The principle of Design by contract affirms that the interface among the different software modules of a system must be regulated by precise specifications, similar to the human contracts: the contract has to cover the obligations (preconditions), the benefits (post conditions) and the consistence among the limits (invariant).

Pre and post-conditions can be manually setup by an expert programmer or can be automatically extracted from the analysis of the behavior of each variable during a set of fault-free executions of the application. Pre and post conditions are extracted in three phases:

- 1. Code instrumentation: in the first step the source code of the application is instrumented so that a set of selected critical variables are "redefined" so that, during the software execution, their behavior can be traced on a log file. Obviously all the variables can be redefined but this would in a real case cause an unacceptable overhead.

- 2. Golden executions: in this phase the user has to run the application with different workloads. During each execution the value of each protected variable is logged for later analysis. The choice of the workloads to apply in order to create the logs, from which the assertions will be extracted, is a very critical task. In general, the more workloads are used, the more the extracted assertions will be precise and less probable to generate "false negatives" (errors not recognized as such);

- 3. Assertion extraction: in the last phase, all the log files are analyzed and, for each variable, a set of assertions is extracted. In this phase the user can also provide PROMON with a set of "user-defined" assertions, maybe difficult to extract but known as true by the programmer.

At that point, the value of each protected variable is validated, at run-time, using the extracted assertions; if PROMON finds any kind of violation an exception is raised and the execution is stopped. The experiments showed that the technique results in a significant increase of the benchmarks reliability; on the other hand the time overhead introduced by the extra computation can increase rapidly depending on the number of the monitored variables.

The results of the works carried out have been published in the papers [C6], [W5], [W6] referenced in the Publication list.

# 3.5. Reliability of the AES (Post-Doc at CNRS)

Standard cryptographic functions such as the Advanced Encryption Standard (AES) are today implemented in a wide range of devices targeting various application domains with security requirements. In addition to the inherent property of these devices, allowing storage and transmission of sensitive information across insecure networks, many applications require high reliability for guarantying a proper digital security. Consequently, as other parts of the system, crypto-cores must be carefully designed in order to provide reliable processing of sensible data. Design for on-line testability of such cores prevents structural failures to cause loss of service and compromise the security.

Fault detection and tolerance schemes for various implementations of cryptographic algorithms have been recently considered. Mainly, two approaches have been developed: based on information redundancy (e.g. the use of codes) or functional redundancy.

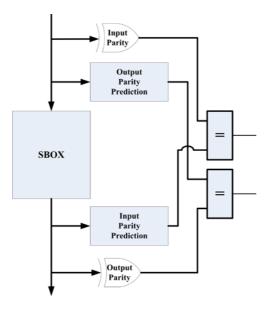

All the techniques based on codes add some bits to the original data word in order to check its validity. The main issue in these approaches is the prediction of the value of the code on an output, given the input value and the executed operation. For instance, the prediction of a parity bit is almost straightforward for the ShiftRows, MixColumns and AddRoundKey operations performed in the AES because these transformations are either linear or they just perform some bit permutations. Conversely, the prediction of the parity bit is not trivial for the SubBytes operation performed by the so-called S-Boxes. As a consequence, the parity prediction requires larger circuitry. Solutions based on parity codes lead to an overhead of about 20% and high single fault detection. However they are not effective in case of multiple faults or single faults that lead to an even number of errors. Other solutions based on the use of more complex codes such as CRC or systematic nonlinear robust codes lead to higher fault coverage in case of multiple faults but at the expense of a significant area overhead (> 60%).

Functional redundancy can be used whenever encryption and decryption modules are implemented on the same circuit. Each encoding phase is followed by a decoding and compare phase in order to check if the resulting decoded text matches with the initial plaintext. A similar procedure is employed when the circuit is used for decoding a cipher-text.

Conversely to most of the previously proposed approaches that focus on the S-Boxes only (dominant component, counting up to 75% of the circuit area), we proposed a low cost self-test architecture for detecting single and multiple faults in most of the AES hardware. The form of testing is accomplished using duplication and comparison. The main idea is to implement the datapath in such a way that several identical blocks can be defined. With an additional block, online pair wise comparisons of blocks are implemented to check the functionality of the AES hardware. Efficiency and low area overhead are achieved by exploiting the spatial duplication inherent to the parallel implementation of the algorithm.

The technique we proposed is designed for all the AES cores (encryption and decryption) that use 16 S-Box repetitions. We did not consider low-area implementations, where there is only one S-Box at the cost of several clock cycles for completing one encryption/decryption round.

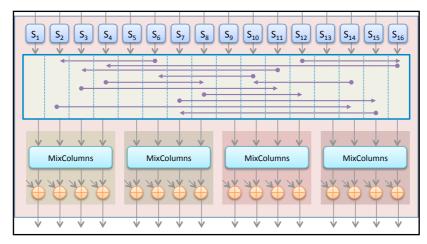

Typical hardware architecture of the AES with 16 S-Boxes is sketched in Figure 2.1. Here, sixteen 8-bit registers feed the 16 identical S-Boxes (S). Shiftrows involves only wires for shifting the bytes of the State, it operates on 128 bits. Four identical MixColumns blocks operate on 32 bits each.

Our goal is to identify a partitioning of the circuit that allows a repetition of identical sub-blocks. These sub-blocks will be compared two-by-two for on-line fault detection thanks to the implementation of an extra sub-block. In the classical architecture depicted in Figure 2.1, ShiftRows unfortunately prevents such a partitioning since it operates on all the 128 bits. However by inspecting the AES algorithm, it can be seen that SubBytes and Shiftrows functions can be switched. We thus propose to perform ShiftRows before SubBytes, and even before loading the registers. Therefore, the datapath can be divided in 4 identical slices that operate on 32 bits each, and that we called RSMA (32-bits Register, 4 S-Boxes, 1 Mixcolumns and 32 xor for the Addroundkey operation).

Figure 2.1: Typical AES Datapath

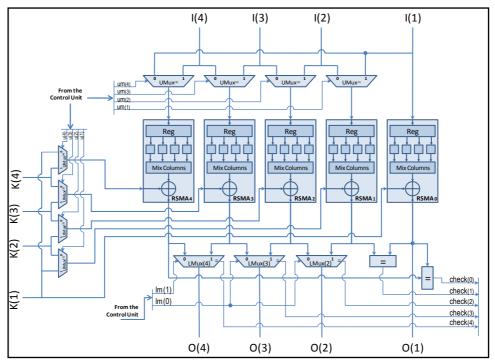

The main idea of the proposed approach is to use one additional RSMA block, and to compare a pair of RSMA blocks at each clock cycle. In particular, at each clock cycle two blocks are fed by the same inputs and the related outputs are compared in order to detect possible faults. Figure 2.2 details the behavior of a part of the circuit where one extra RSMA block has been added. In this figure, LMux(2), LMux(3) and LMux(4) are multiplexers with an additional output that is asserted whenever the two inputs are equal (i.e., a multiplexer with a comparator). Table 2.1 details the signals controlled and observed by the control unit. For instance, when RSMA4 and RSMA3 work together, the UMux(3) let the input I(4) go into the RSMA3. Among the five signals coming from the comparators, only one at a time is considered by the control unit. For example, in the above case, the check(4) signal is verified, i.e., the two related RSMA blocks are checked.

| Compared     | Um   | Lm | To check |

|--------------|------|----|----------|

| RSMA4, RSMA3 | 1000 | 11 | check(4) |

| RSMA3, RSMA2 | 1100 | 01 | check(3) |

| RSMA2, RSMA1 | 1110 | 00 | check(2) |

| RSMA1, RSMA0 | 1111 | 00 | check(1) |

| RSMA0, RSMA4 | 0000 | 11 | check(0) |

Table 2.1: Control Signals

The scheduling of the comparisons of a pair of RSMA blocks is a very important issue of the proposed method. One AES encryption lasts 10 clock cycles and there are 5 different configurations. Therefore it's possible to use each of the 5 configurations twice during one encryption. Through the 5 configurations, each RSMA block is compared twice (once with the left block, once with the right block). Thus, if the 5 configurations are activated twice, each RSMA block is compared 4 times during one encryption. A counter is in charge of the test configuration scheduling.

To validate the proposed architecture, we implemented it in VHDL and we synthesized it using Synopsys Design Compiler , and a 130nm CMOS library provided by STM. We considered that all the keys used in the AddRoundKey step (see Annex I) are pre-computed and stored in the circuit. The area of the original circuit is 52961  $\mu$ m² (corresponding to 9660 logic cells) while the area of the proposed architecture is 71357  $\mu$ m² (corresponding to 13084 logic cells and 34.7% of area overhead).

Concerning the efficiency of the proposed architecture with respect to the fault detection, our functional redundancy strategy differs from the classical Double Modular Redundancy (DMR) scheme. A classical DMR architecture allows detecting all the faults (single and multiple) that lead to an error (i.e., a difference at the output of one of the duplicated modules). Starting from the moment of appearance of the fault, the fault latency depends on the inputs applied to the circuit, only. In other words, the fault is detected as soon as the input vector can sensitize the fault and propagate it up to the output of the

module (i.e., the input of the comparator between the two modules). Anyway, a system based on classical DMR scheme does not deliver faulty responses without noticing it (unless in case of equivalent faults in the two modules).

Figure 2.2: AES Architecture with RSMA duplication and comparison

This technique is able to detect any single or multiple faults leading to a wrong RSMA output value (as for the classical DMR) but only when the affected RSMA is compared with another one. Conversely to DMR, the dynamic reconfiguration of the modules leads to a comparison of each module twice every 5 clock cycles. Therefore it can happen that the system produces erroneous responses without noticing it even in presence of a single stuck-at.

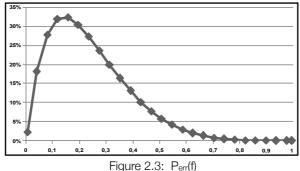

We questioned the probability to get an error on the AES output and to not detect it. This probability can be analyzed by computing the probability  $P_{err}(f)$  of not detecting an error on the circuit's outputs while a given fault f affects the circuits. For this analysis we focused on single stuck-at faults only.

$P_{err}(f)$  is the probability that the fault f is activated (i.e. sensitized and propagated in such a way that it leads to an error) during at least one of the 6 clock-cycles during which the faulty RSMA is not compared, and it is not activated during the 4 clock cycles when the RSMA is compared. Let denote  $p_f$  the probability of activation of a fault f into an RSMA module, i.e., the probability that for a random input pattern the fault is sensitized and the error is propagated to its output. In the hypothesis to have several distinct functional inputs, we can consider that the device is fed by a random source. In addition, the inherent properties of the AES makes that the sequence of input values that are applied to consecutive rounds of the same encryption can be considered as random. Therefore, the probability  $p_f$  is equal to the ratio of input vectors that test f over the number of possible input vectors. The number of possible input vectors for the RSMA, is  $2^{32}$ . Since fault simulation cannot be applied in exhaustive way, we split the problem in two parts. From one side, S-Boxes have 8 input bits only, consequently exhaustive analysis is possible and  $p_f$  can be obtained for each fault through simulation. Since MixColumns and AddRoundKey are invertible functions, all the errors appearing on the output of the S-Boxes propagate through the functions to the comparator. From the other side,  $p_f$  of the MixColumns has been calculated thanks to its modular structure involving 4 identical 8-bit inputs sub-functions ( $2^8$  combinations). Finally, the AddRoundKey operations involve only xor operations and are very easily tested.

For the proposed architecture, the probability that f is not activated during the clock-cycles of comparison is equal to  $(1-p_f)^4$  while the probability that f is activated during at least one of the clock-cycles without comparison is equal to  $1-(1-p_f)^6$ . Finally, it comes:

$$P_{err}(f) = (1 - p_f)^4 \times (1 - (1 - p_f)^6)$$

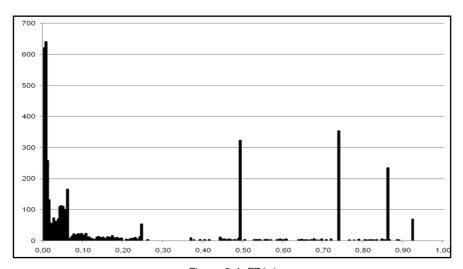

Figure 2.3 represents  $P_{err}(f)$  in function of  $p_f$ . Hard-to-test faults ( $p_f \approx 0$ ) and the easy-to-test faults ( $p_f \approx 1$ ) are not those that most likely produce undetected errors. On the contrary, the maximum value (32.57%) corresponds to faults with  $p_f$  equals to 0.14.

rigure 2.3: Perr(I)

In order to calculate the error probability of the whole circuit (actually 97% of the circuit, being MixColumns omitted), we fault simulated the Sboxes to determine the distribution of probabilities of activation of the faults. Basically, we calculated how many faults are activated by one test pattern ( $p_f = 1/256$ ), how many faults are activated by 2 patterns ( $p_f = 2/256$ ), and so on. Figure 2.4 summarizes, for each probability pf, the number FD(pf) of faults with that activation probability.

Figure 2.4: FD(p<sub>f</sub>)

Assuming that each fault has the same probability to appear in the circuit, the overall error probability PERR of the RSMA is calculated as the weighted average of the values Perr(f) according to the distribution FD(p):

$$P_{ERR} = \frac{1}{\#Faults} \sum_{i=1}^{256} \left\{ \left[ FD\left(\frac{i}{256}\right) \right] \times \left[ \left(1 - \frac{i}{256}\right)^4 \times \left(1 - \left(1 - \frac{i}{256}\right)^6\right) \right] \right\}$$

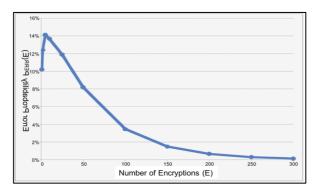

It comes that PERR is equal to 10.18%, i.e. the architecture has a probability of 89.82% to detect any fault in a single encryption (10 clock cycles). We also analyzed the evolution of this probability based on the number of encryptions. When we perform E encryptions, an RSMA block is compared 4·E clock cycles, while it is not compared 6·E clock cycles. The error probability can therefore be rewritten as follows:

$$P_{err}(E,f) = (1-p_f)^{4-E} \times (1-(1-p_f))^{6-E}$$

Considering the fault distribution FD given in Figure 2.5, we can re-calculate the overall error probability  $P_{ERR}$  of the RSMA block in function of the number of encryptions (Figure 7). As can be seen, the error probability slightly increases up to 14% for 5 encryptions, while for higher encryption numbers it tends to 0. Namely, for 300 encryptions, the reliability probability is equal to 99.9%.

Figure 2.5: Error probability w.r.t. the number of encryptions

To conclude, we proposed a low cost architecture for detecting single and multiple faults in the hardware implementation of the Advanced Encryption Standard (AES) during its mission mode. The solution, based on spatial redundancy, reorders the AES algorithm subtasks. This modification does not influence the actual encryption function and it allows the implementation of 4 identical blocks working on 32-bits each. Thanks to this parallel and duplicated architecture, only one additional 32-bits block is added in the circuit leading to 4 tests per encryption cycle for every block. The solution is very effective in terms of fault latency and fault coverage while keeping the area overhead very low (about 34.7%).

The results of the works carried out have been published in the papers [J8], [S13], [S15], [P6], [p7] referenced in the Publication list.

# 3.6. Manufacturing Test for Secure Devices

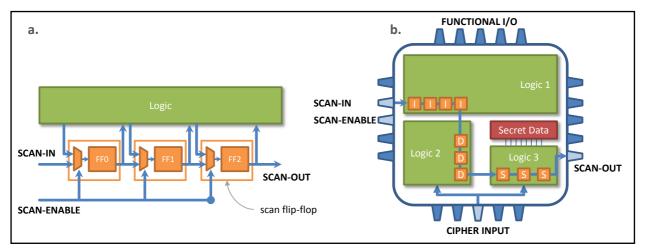

Structural testing is one important step in the production of integrated circuits. Indeed, the fabrication of CMOS devices is not a totally controlled process and some of the manufacturing chips may not work properly. Testing is therefore essential to sort faulty and good circuits and thus ensure the quality of the products. The increasingly test cost of new technologies demands the insertion of test-oriented structures early in the circuit design, which is call Design-for-Testability (DfT). These structures aims at improving the testability (mainly the capacity to detecting the presence of faults), diagnostics, test time and reducing the number of required test pins.

The most common DfT technique is the insertion of scan chains, which increases the observability and the controllability of the circuit's internal nodes, increasing then the testability. Nevertheless, malicious users can use the scan chains to observe confidential data stored in devices implementing cryptographic primitives. Therefore, scan chains inserted in secure ICs can be considered as a source of information leakage. However, testing cannot be simply avoided in secure products for two main reasons: first possible non- tested errors may compromise the system's security and as for any other IC, the test ensures the quality of the product.

Besides the security threat that lies in the scan chains, standard test interfaces such as JTAG and IEEE 1500 can also be maliciously exploited. These test interfaces that initially developed for testing printed circuit boards (JTAG) or System-on-Chip internal modules (IEEE 1500), can be used nowadays for debugging purposes. Easy access to debug ports and module's test structures can be used by hackers to steal the contents of on-chip memories (intellectual property) and to modify the firmware/software so that the device executes a function which was not initially conceived by the designer. In order to protect intellectual property the security of these ubiquitous test interfaces must be improved.

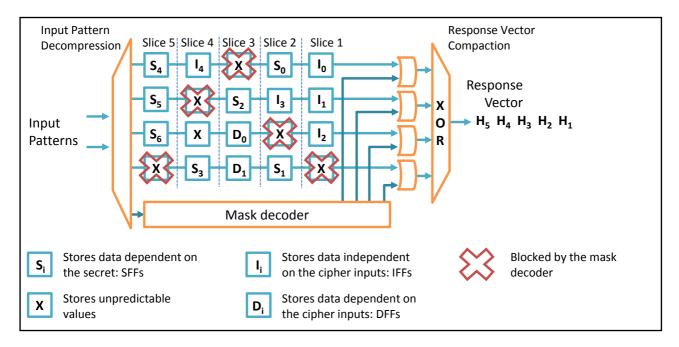

In the last 5 year we have analyzed the weaknesses of standard DfT architectures based on the use of scan chains, and we have proposed new countermeasures to cope with this hazard. The following subsections will summarize our main contributions. The rest of the section is structured as follows:

- 1. a description of the basic approach the allows successful scan attacks, followed by new attacks we proposed;

- 2. the countermeasures we have proposed to cope with those attacks. We have investigated solutions based on Built-In Self-Test, on the internal comparison of test and expected responses, the implementation of a smart controller, and the enhancement of the security of the JTAG standard.

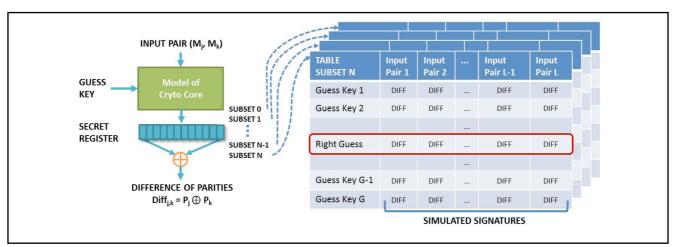

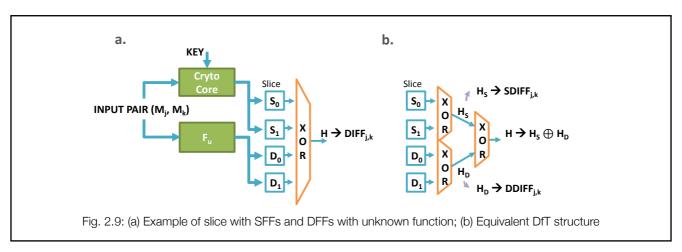

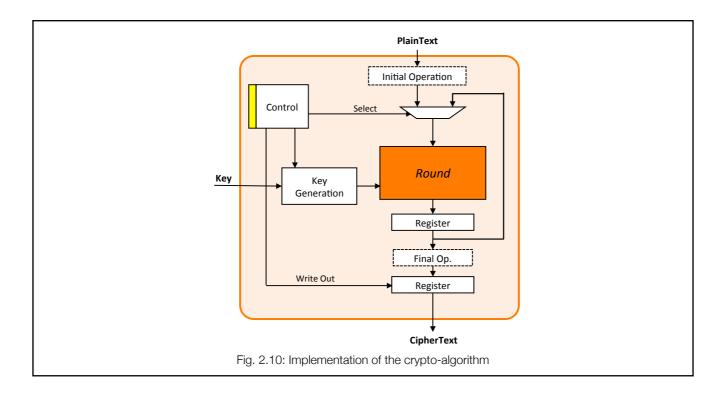

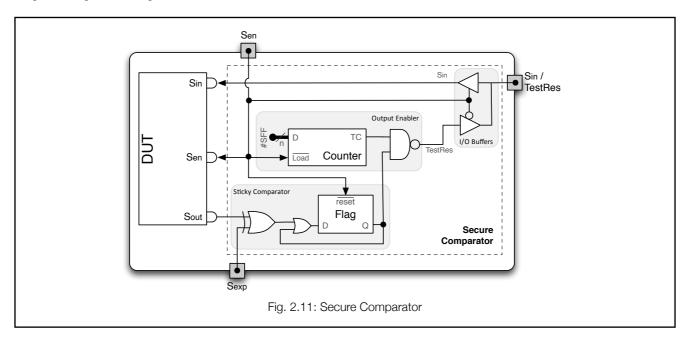

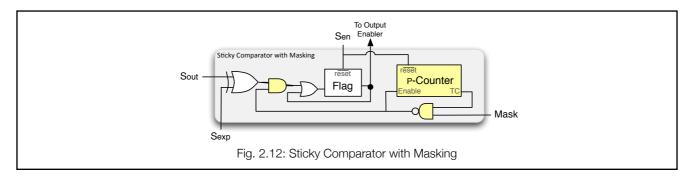

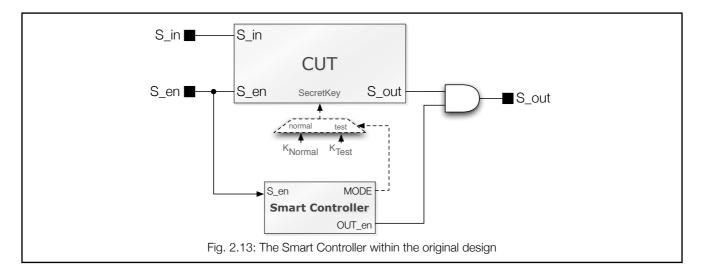

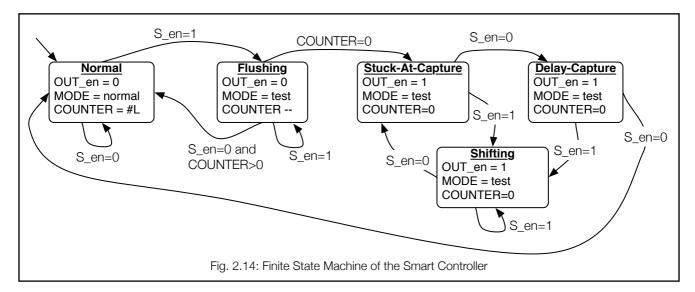

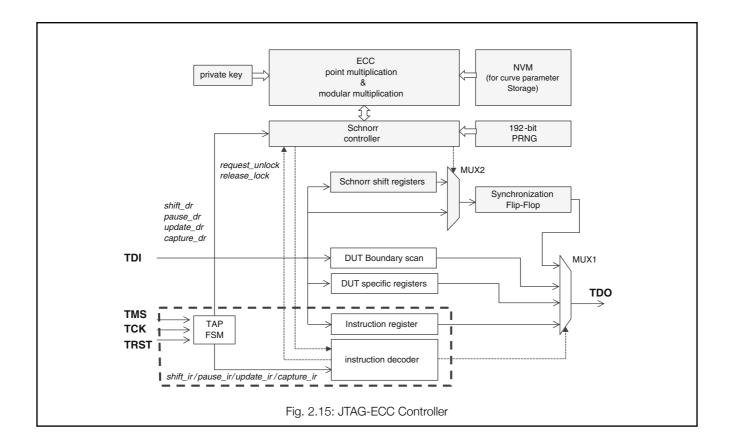

#### 3.6.1. Scan Attacks