# Combining static and dynamic approaches to model loop performance in HPC

Vincent Palomares

# ▶ To cite this version:

Vincent Palomares. Combining static and dynamic approaches to model loop performance in HPC. Hardware Architecture [cs.AR]. Université de Versailles-Saint Quentin en Yvelines, 2015. English. <NNT : 2015VERS040V>. <tel-01293040>

# HAL Id: tel-01293040 https://tel.archives-ouvertes.fr/tel-01293040

Submitted on 24 Mar 2016  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Université de Versailles Saint-Quentin-en-Yvelines

École Doctorale "STV"

# Combiner Approches Statique et Dynamique pour Modéliser la Performance de Boucles HPC

# Combining Static and Dynamic Approaches to Model Loop Performance in HPC

# THÈSE

présentée et soutenue publiquement le 21 Septembre 2015

pour l'obtention du

# Doctorat de l'Université de Versailles Saint-Quentin-en-Yvelines (spécialité informatique)

par

Vincent Palomares

Composition du jury

| Président :          | François Bodin                        | - Professeur, Université de Rennes                                                         |

|----------------------|---------------------------------------|--------------------------------------------------------------------------------------------|

| Rapporteurs :        | Denis Barthou<br>Henri-Pierre Charles | <ul><li> Professeur, Université de Bordeaux</li><li> Directeur de Recherche, CEA</li></ul> |

| Examinateurs :       | Alexandre Farcy<br>David J. Kuck      | - CPU Architect, Intel<br>- Fellow, Intel                                                  |

| Directeur de thèse : | William Jalby                         | - Professeur, Université de Versailles                                                     |

## Thanks

I would first like to thank William Jalby, my advisor, for the help and guidance he provided throughout these past few years. His healthy doses of both optimism and skepticism motivated me to keep aiming higher.

I would also like to thank David Wong and David Kuck, with whom collaborating was very pleasant and stimulating. Working on Cape with them was an enriching experience.

I am grateful to Denis Barthou and Henri-Pierre Charles, the reporters, for reviewing my work and making suggestions on how to improve my manuscript. Their input was very helpful and contributed to making this document clearer.

My thesis work was extremely fun, in no small part thanks to Zakaria Bendifallah and José Noudohouenou. We certainly had our share of good laughs in our office. Let's just hope the quotations we've collected along the years<sup>1</sup> never get in the wrong hands.

I would like to thank all the members of the lab for their dynamism, competence and friendliness. I do not want to make a comprehensive list here (for fear I may forget a name or two<sup>2</sup> and cause jealousy between those mentioned and those not). Surely, a blanket statement should be enough to prevent that?! Some of them are however definitely worthy of a special mention. First, Emmanuel Oseret, with whom I often discussed microarchitectural details on Intel CPUs,

Oseret, with whom I often discussed microarchitectural details on intel CPUs, and who agreed to implement some features in his CQA tool that were specially tailored to my needs. He also proofread my manuscript, helping me rid it of various mistakes. I also want to mention Mathieu Tribalat, who helped me navigate some of MAQAO's intricacies, and whose work in taking over DECAN made getting application measurements considerably easier.

The end-of-thesis rush and the tension that came with it were made easier by chatting (and complaining!) with other students in the same situation. I want to thank Nicolas Triquenaux for finding and sharing information about thesis completion procedures, and Zakaria (once again), whose perpetual struggle with paperwork made it easier to see mine was quite mild after all.

On a more personal side, I would like to thank Anna Galusza, my fiancée, for supporting me throughout the writing of this manuscript and reviewing some of its key parts, as well as my parents and the rest of my family for helping me get this far.

Finally, I would like to thank you, the reader: you are the reason why I wrote this manuscript<sup>3</sup>. This is particularly true if you read it until the end, at which point you should feel free to fill the following blank with your name<sup>4</sup>: THANK YOU, !

<sup>&</sup>lt;sup>1</sup> Some quotations? What quotations? Move along, there is nothing to see here!

$<sup>^2</sup>$  Or three...

$<sup>^3</sup>$  You, and getting my Ph.D., that is.

<sup>&</sup>lt;sup>4</sup> NB: Not all libraries are very fond of this practice, so you might want to be discreet if using a borrowed copy.

Fluffy Canary I am told I can do anything I want with the Thanks section... Let's see if it's true!

#### Résumé:

La complexité des CPUs s'est accrue considérablement depuis leurs débuts, introduisant des mécanismes comme le renommage de registres, l'exécution dans le désordre, la vectorisation, les préfetchers et les environnements multi-coeurs pour améliorer les performances avec chaque nouvelle génération de processeurs. Cependant, la difficulté a suivi la même tendance pour ce qui est a) d'utiliser ces mêmes mécanismes à leur plein potentiel, b) d'évaluer si un programme utilise une machine correctement, ou c) de savoir si le design d'un processeur répond bien aux besoins des utilisateurs.

Cette thèse porte sur l'amélioration de l'observabilité des facteurs limitants dans les boucles de calcul intensif, ainsi que leurs interactions au sein de microarchitectures modernes.

Nous introduirons d'abord un framework combinant CQA et DECAN (des outils d'analyse respectivement statique et dynamique) pour obtenir des métriques détaillées de performance sur des petits codelets et dans divers scénarios d'exécution.

Nous présenterons ensuite PAMDA, une méthodologie d'analyse de performance tirant partie de l'analyse de codelets pour détecter d'éventuels problèmes de performance dans des applications de calcul à haute performance et en guider la résolution.

Un travail permettant au modèle linéaire Cape de couvrir la microarchitecture Sandy Bridge de façon détaillée sera décrit, lui donnant plus de flexibilité pour effectuer du codesign matériel / logiciel. Il sera mis en pratique dans VP3, un outil évaluant les gains de performance atteignables en vectorisant des boucles.

Nous décrirons finalement UFS, une approche combinant analyse statique et simulation au cycle près pour permettre l'estimation rapide du temps d'exécution d'une boucle en prenant en compte certaines des limites de l'exécution en désordre dans des microarchitectures modernes.

**Mots Clés:** codelet, analyse de boucle, analyse statique, analyse dynamique, calcul intensif, HPC, optimisation, modélisation rapide, performance, exécution dans le désordre, simulation au cycle près

#### Abstract:

The complexity of CPUs has increased considerably since their beginnings, introducing mechanisms such as register renaming, out-of-order execution, vectorization, prefetchers and multi-core environments to keep performance rising with each product generation. However, so has the difficulty in making proper use of all these mechanisms, or even evaluating whether one's program makes good use of a machine, whether users' needs match a CPU's design, or, for CPU architects, knowing how each feature really affects customers.

This thesis focuses on increasing the observability of potential bottlenecks in HPC computational loops and how they relate to each other in modern microarchitectures.

We will first introduce a framework combining CQA and DECAN (respectively static and dynamic analysis tools) to get detailed performance metrics on small codelets in various execution scenarios.

We will then present PAMDA, a performance analysis methodology leveraging elements obtained from codelet analysis to detect potential performance problems in HPC applications and help resolve them.

A work extending the Cape linear model to better cover Sandy Bridge and give it more flexibility for HW/SW codesign purposes will also be described. It will be directly used in VP3, a tool evaluating the performance gains vectorizing loops could provide.

Finally, we will describe UFS, an approach combining static analysis and cycleaccurate simulation to very quickly estimate a loop's execution time while accounting for out-of-order limitations in modern CPUs.

**Keywords:** codelet, loop analysis, static analysis, dynamic analysis, HPC, optimization, fast modeling, performance, out-of-order, cycle-accurate simulation

# Contents

| 1        | Intr | oducti  | on                                | 1         |

|----------|------|---------|-----------------------------------|-----------|

|          | 1.1  | High F  | Performance Computing (HPC)       | 1         |

|          | 1.2  | Object  | tives and Contributions           | 2         |

|          | 1.3  | Overvi  | iew                               | 2         |

| <b>2</b> | Bac  | kgrour  | ıd                                | <b>5</b>  |

|          | 2.1  | Recent  | t Microarchitectures              | 5         |

|          |      | 2.1.1   | Sandy Bridge                      | 5         |

|          |      | 2.1.2   | Ivy Bridge                        | 10        |

|          |      | 2.1.3   | Haswell                           | 10        |

|          |      | 2.1.4   | Silvermont                        | 12        |

|          | 2.2  | Perfor  | mance Analysis                    | 14        |

|          |      | 2.2.1   | Static Analysis                   | 15        |

|          |      | 2.2.2   | Dynamic Analysis                  | 16        |

|          |      | 2.2.3   | Simulation                        | 18        |

|          | 2.3  | Using   | Codelets                          | 21        |

|          |      | 2.3.1   | Codelet Presentation              | 21        |

|          |      | 2.3.2   | Artificial Codelets               | 22        |

|          |      | 2.3.3   | Extracted Codelets                | 23        |

| 3        | Cod  | lelet P | erformance Measurement Framework  | <b>25</b> |

|          | 3.1  | Introd  | uction                            | 25        |

|          | 3.2  | Target  | Loops: Numerical Recipes Codelets | 26        |

|          |      | 3.2.1   | Obtention and Target Properties   | 26        |

|          |      | 3.2.2   | Presentation and Categories       | 27        |

|          | 3.3  | Measu   | rement Methodology                | 29        |

|          |      | 3.3.1   | Placing Probes                    | 29        |

|          |      | 3.3.2   | Measurement Quality and Stability | 30        |

|          |      | 3.3.3   | CQA Reports                       | 32        |

|          | 3.4  | Varyin  | g Experimental Parameters         | 32        |

|          |      | 3.4.1   | DECAN Variants                    | 33        |

|          |      | 3.4.2   | Data Sizes                        | 33        |

|          |      | 3.4.3   | Machines and Microarchitectures   | 34        |

|          |      | 3.4.4   | Frequencies                       | 35        |

|          |      | 3.4.5   | Memory Load (using Memload)       | 36        |

|          |      | 3.4.6   | Overall Structure                 | 38        |

|          | 3.5  | Result  | s Repository: PCR                 | 38        |

|          |      | 3.5.1   | Features                          | 40        |

|          |      | 3.5.2   | Technical Details                 | 41        |

|          |      | 3.5.3   | Acknowledgments                   | 41        |

|          | 3.6  | Relate  | d Work                            | 41        |

|          | 3.7  |         | e Work                            | 41        |

|          | 3.8  | Conclu  | 1sion                             | 42        |

| 4 |     | MDA:<br>alysis | Performance Assessment Methodology Using I       | Dif | fer | er | nti | ial | 43 |

|---|-----|----------------|--------------------------------------------------|-----|-----|----|-----|-----|----|

|   | 4.1 | v              | luction                                          |     |     |    |     |     | 43 |

|   | 4.2 |                | ating Example                                    |     |     |    |     |     | 45 |

|   | 4.3 |                | lients: Main Tool Set Components                 |     |     |    |     |     | 47 |

|   | 1.0 | 4.3.1          | MicroTools: Microbenchmarking the Architecture . |     |     |    |     |     | 48 |

|   |     | 4.3.2          | CQA: Code Quality Analyzer                       |     |     |    |     |     | 48 |

|   |     | 4.3.3          | DECAN: Differential Analysis                     |     |     |    |     |     | 48 |

|   |     | 4.3.4          | MTL: Memory Tracing Library                      |     |     |    |     |     | 49 |

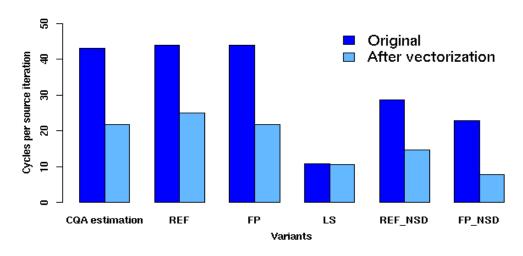

|   | 4.4 |                | e: PAMDA Tool Chain                              |     |     |    |     |     | 50 |

|   |     | 4.4.1          | Hotspot identification                           |     |     |    |     |     | 50 |

|   |     | 4.4.2          | Performance overview                             |     |     |    |     |     | 51 |

|   |     | 4.4.3          | Loop structure check                             |     |     |    |     |     | 51 |

|   |     | 4.4.4          | CPU evaluation                                   |     |     |    |     |     | 52 |

|   |     | 4.4.5          | Bandwidth measurement                            |     |     |    |     |     | 53 |

|   |     | 4.4.6          | Memory evaluation                                |     |     |    |     |     | 53 |

|   |     | 4.4.7          | OpenMP evaluation                                |     |     |    |     |     | 54 |

|   | 4.5 | Exper          | imental results                                  |     |     |    |     |     | 54 |

|   |     | 4.5.1          | PNBench                                          |     |     |    |     |     | 54 |

|   |     | 4.5.2          | RTM                                              |     |     |    |     |     | 56 |

|   | 4.6 | Relate         | ed Work                                          |     |     |    |     |     | 58 |

|   | 4.7 | Ackno          | owledgments                                      |     |     |    |     |     | 58 |

|   | 4.8 |                | usion and Future Work                            |     |     |    |     |     | 59 |

| 5 | Ext | ending         | g the Cape Model                                 |     |     |    |     |     | 61 |

| 0 | 5.1 | -              | ntation of Cape                                  |     |     |    |     |     | 61 |

|   | 0.1 | 5.1.1          | Core Principles                                  |     |     |    |     |     | 61 |

|   |     | 5.1.2          | Identifying Nodes and their Bandwidths           |     |     |    |     |     | 62 |

|   |     | 5.1.3          | Getting Node Capacities                          |     |     |    |     |     | 62 |

|   |     | 5.1.4          | Isolating the Memory Workload                    |     |     |    |     |     | 62 |

|   |     | 5.1.5          | Saturation Evaluation                            |     |     |    |     |     | 63 |

|   |     | 5.1.6          | Cape Inputs                                      |     |     |    |     |     | 63 |

|   | 5.2 |                | AN Variant Refinements                           |     |     |    |     |     | 63 |

|   |     | 5.2.1          | Tackling Partial Vector Register Loads           |     |     |    |     |     | 64 |

|   |     | 5.2.2          | The Case of Floating Point Divisions             |     |     |    |     |     | 64 |

|   | 5.3 | Front-         | End Modeling Subtleties                          |     |     |    |     |     | 65 |

|   |     | 5.3.1          | Accounting for Unlamination                      |     |     |    |     |     | 65 |

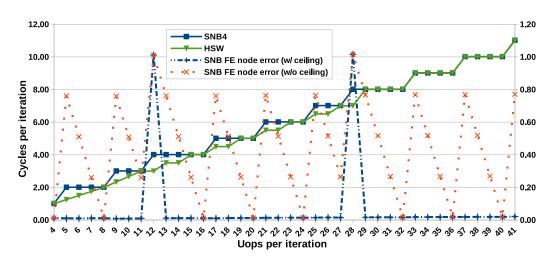

|   |     | 5.3.2          | Ceiling Effect                                   |     |     |    |     |     | 67 |

|   |     | 5.3.3          | New Front-End DECAN Variant                      |     |     |    |     |     | 67 |

|   | 5.4 | Back-          | End Modeling Improvements                        |     |     |    |     |     | 68 |

|   |     | 5.4.1          | Dispatch                                         |     |     |    |     |     | 69 |

|   |     | 5.4.2          | Functional Units                                 |     |     |    |     |     | 69 |

|   |     | 5.4.3          | Memory Hierarchy                                 |     |     |    |     |     | 70 |

|   | 5.5 | Handl          | ling Unsaturation                                |     |     |    |     |     | 74 |

|   |     | 5.5.1          | Definition and Effect of Unsaturation            |     |     |    |     |     | 74 |

|   |     | 5.5.2          | Overlooked or Mismodeled Nodes                   |     |     |    |     |     | 75 |

|   |     | 5.5.3          | Buffer-Induced Unsaturation                      |     |     |    |     |     | 75 |

|   | 5.6 | Relate         | ed Work                                          |     |     |    |     |     | 75 |

|   | 5.7 | Futur          | e Work                                           |     |     |    |     |     | 77 |

|   | $5.8 \\ 5.9$      |                    | weldgments                                          |   | 78<br>78     |

|---|-------------------|--------------------|-----------------------------------------------------|---|--------------|

| 6 | $\mathbf{VP}^{2}$ | <sup>3</sup> : A V | vectorization Potential Performance Prototype       |   | 79           |

|   | 6.1               | Introd             | luction                                             |   | 79           |

|   | 6.2               | Tool (             | Operation                                           |   | 81           |

|   |                   | 6.2.1              | General Objectives for Prediction Tools             |   | 81           |

|   |                   | 6.2.2              | Tool Output                                         | • | 82           |

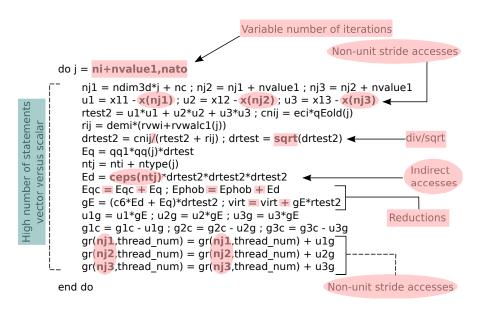

|   | 6.3               | Exper              | imental Results                                     |   | 83           |

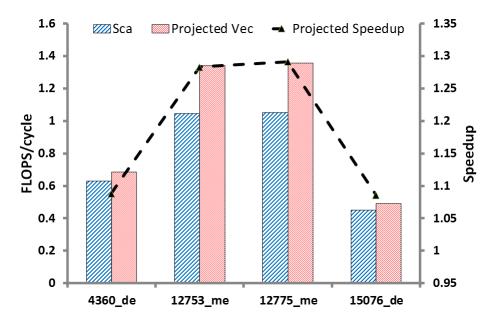

|   |                   | 6.3.1              | Motivating Example                                  |   | 83           |

|   |                   | 6.3.2              | $VP^3$ on YALES2                                    | • | 84           |

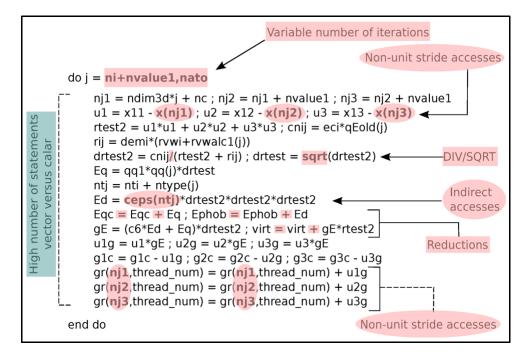

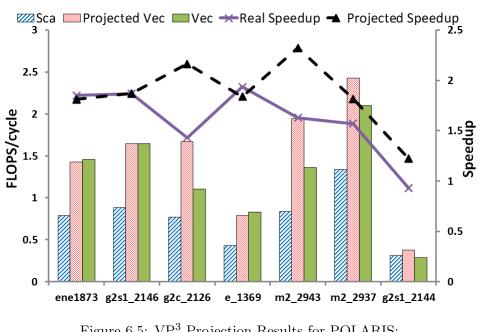

|   |                   | 6.3.3              | $VP^3$ on POLARIS(MD)                               | • | 85           |

|   | 6.4               | Tool I             | Principles                                          | • | 86           |

|   |                   | 6.4.1              | FP/LS Variants Generation and Measurement           |   | 88           |

|   |                   | 6.4.2              | Static Projection of FP/LS Operations               |   | 88           |

|   |                   | 6.4.3              | Refinement of Static Projection of LS Operations    |   | 88           |

|   |                   | 6.4.4              | Combining FP/LS Projection Results                  |   | 89           |

|   |                   | 6.4.5              | Tool Speed                                          |   | 90           |

|   | 6.5               |                    | ation                                               |   | 90           |

|   |                   | 6.5.1              | Methodology, Measurements and Experimental Settings |   | 90           |

|   |                   | 6.5.2              | Error Analysis                                      |   | 91           |

|   | 6.6               |                    | sions                                               |   | 92           |

|   | 6.7               |                    | ed Work                                             |   | 92           |

|   | 6.8               | Conclu             | usions                                              | • | 93           |

| 7 | Uop               | o Flow             | Simulation                                          |   | 95           |

|   | 7.1               | Introd             | luction                                             |   | 95           |

|   |                   | 7.1.1              | On Model Accuracy                                   | • | 96           |

|   |                   | 7.1.2              | On Buffer Sizes                                     | • | 96           |

|   |                   | 7.1.3              | On Uop Scheduling                                   | • | 97           |

|   |                   | 7.1.4              | Out-of-Context Analysis                             |   | 97           |

|   |                   | 7.1.5              | Motivating Example: Realft2_4_de                    | • | 97           |

|   |                   | 7.1.6              | Alternative Motivating Example: Realft_4_de         |   | 98           |

|   | 7.2               |                    | standing Out-of-Order Engine Limitations            |   | 101          |

|   |                   | 7.2.1              | In-Order Issue and Retirement                       |   | 101          |

|   |                   | 7.2.2              | Finite Out-of-Order Resources                       |   | 102          |

|   |                   | 7.2.3              | Dispatching Heuristics                              |   | 102          |

|   |                   | 7.2.4              | Inter-iteration Dependencies                        |   | 103          |

|   | 7.3               | -                  | Resource Sizes                                      |   | 105          |

|   | 7.4               | -                  | ne Model                                            |   | 106          |

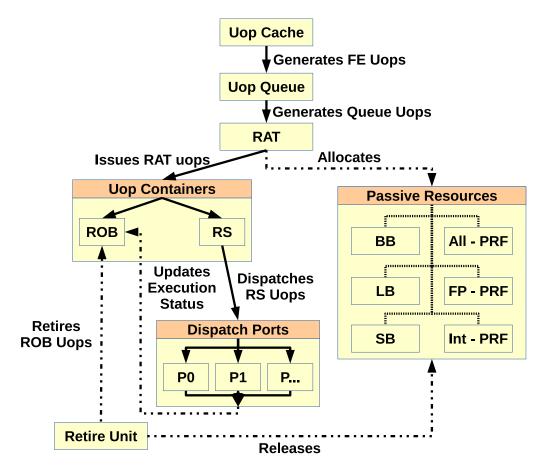

|   |                   | 7.4.1              | Principles                                          |   | 106          |

|   |                   | 7.4.2              | Engine                                              |   | 108          |

|   |                   | 7.4.3              | Simplified Front-End                                |   | 108          |

|   |                   | 7.4.4              | Resource Allocation Table (RAT)                     |   | 109          |

|   |                   | 7.4.5<br>7.4.6     | Out-of-Order Flow       Retirement                  |   | $112 \\ 114$ |

|   |                   | 7.4.0<br>7.4.7     |                                                     |   | $114 \\ 114$ |

|   |                   | 7.4.7<br>7.4.8     | Things Not Modeled                                  |   | $114 \\ 116$ |

|   | 7.5               |                    | Ad-Hoc L1 Modeling                                  |   |              |

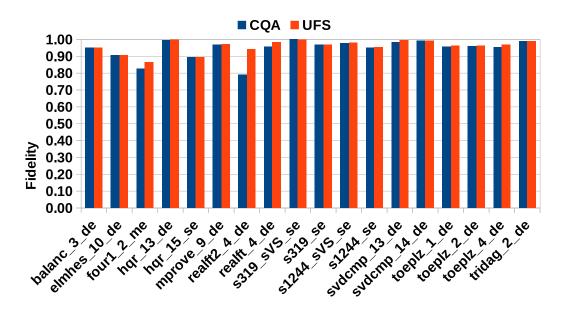

|   | 1.0               | v anuð             | 101011 · · · · · · · · · · · · · · · · ·            | • | 110          |

|              |       | 7.5.1 Another Look at our Motivating Examples                                                                    | 117 |

|--------------|-------|------------------------------------------------------------------------------------------------------------------|-----|

|              |       | 7.5.2 In Vitro Validation                                                                                        | 118 |

|              |       | 7.5.3 In Vivo Validation                                                                                         | 122 |

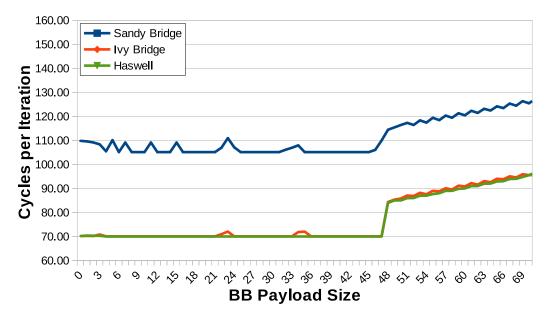

|              |       | 7.5.4 Simulation Speed $\ldots$ | 124 |

|              | 7.6   | Related Work                                                                                                     | 128 |

|              | 7.7   | Future Work                                                                                                      | 129 |

|              | 7.8   | Acknowledgements                                                                                                 | 129 |

|              | 7.9   | Conclusion                                                                                                       | 129 |

| 8            | Con   | clusion                                                                                                          | 131 |

|              | 8.1   | Contributions                                                                                                    | 131 |

|              | 8.2   | Publications                                                                                                     | 131 |

|              | 8.3   | Future Work                                                                                                      | 131 |

|              |       | 8.3.1 Differential Analysis                                                                                      | 132 |

|              |       | 8.3.2 Cape Modeling                                                                                              | 132 |

|              |       |                                                                                                                  | 132 |

| $\mathbf{A}$ | Qua   | ntifying Effective Out-of-Order Resource Sizes                                                                   | 133 |

|              | A.1   |                                                                                                                  | 133 |

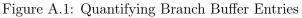

|              | A.2   | Quantifying Branch Buffer Entries                                                                                | 134 |

|              | A.3   | Quantifying Load Buffer Entries                                                                                  | 136 |

|              | A.4   | Quantifying PRF Entries                                                                                          | 137 |

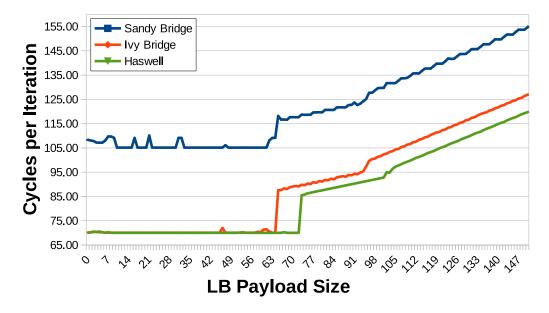

|              |       | A.4.1 Quantifying FP PRF Entries                                                                                 | 137 |

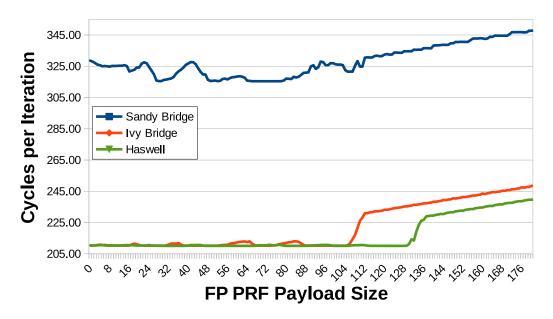

|              |       | A.4.2 Quantifying Integer PRF Entries                                                                            | 139 |

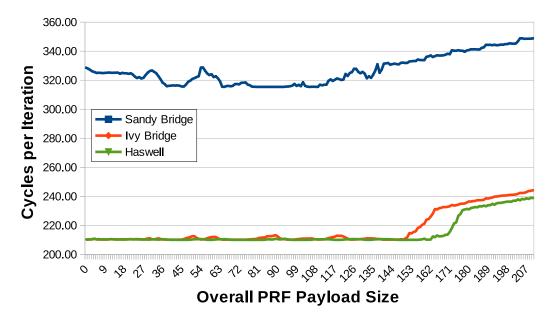

|              |       | A.4.3 Quantifying Overall PRF Entries                                                                            | 140 |

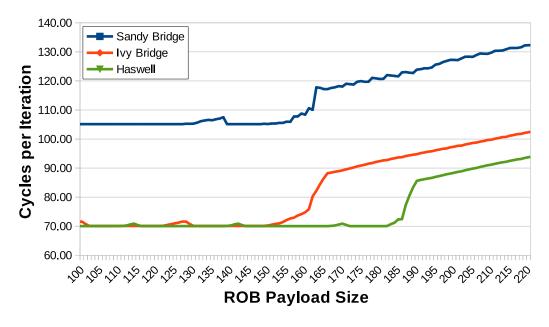

|              | A.5   | Quantifying ROB Entries                                                                                          | 140 |

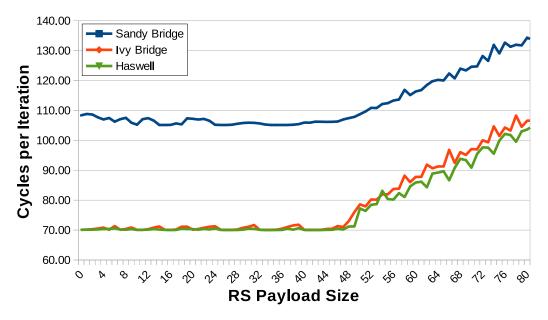

|              | A.6   | Quantifying RS Entries                                                                                           | 143 |

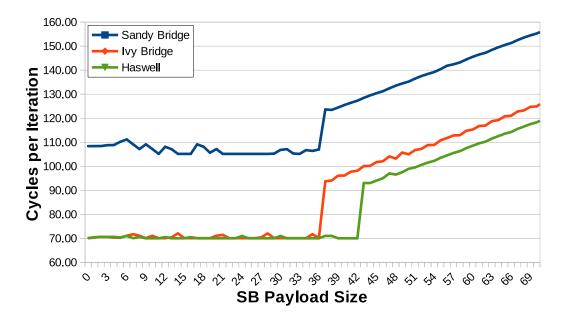

|              | A.7   | Quantifying Store Buffer Entries                                                                                 | 145 |

|              | A.8   | Impact of Microfusion on Resource Consumption                                                                    | 145 |

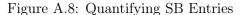

|              |       | A.8.1 ROB Microfusion                                                                                            | 146 |

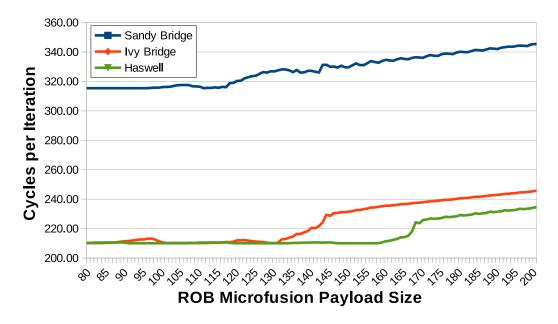

|              |       | A.8.2 RS Microfusion                                                                                             | 146 |

| в            | Not   | e on the Load Matrix                                                                                             | 151 |

|              | B.1   | Load Matrix Presentation                                                                                         | 151 |

|              | B.2   | Quantifying Load Matrix Entries                                                                                  | 151 |

| B            | bliog | graphy                                                                                                           | 153 |

# List of Figures

| 2.1        | Simplified Sandy Bridge Front-End                                                                                                | 6           |

|------------|----------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.2        | Simplified Sandy Bridge Execution Engine                                                                                         | 7           |

| 2.3        | Simplified Sandy Bridge Memory Hierarchy                                                                                         | 9           |

| 2.4        | Simplified Haswell Execution Engine                                                                                              | 11          |

| 2.5        | Simplified Silvermont Front-End                                                                                                  | 12          |

| 2.6        | Simplified Silvermont Execution Engine                                                                                           | 14          |

| 2.7        | Simplified Silvermont Memory Hierarchy                                                                                           | 15          |

| 2.8        | Example of DECAN Loop Transformations                                                                                            | 19          |

| 3.1        | Codelet Structure and Probe Placement                                                                                            | 32          |

| 3.2        | DECAN Performance Decomposition Example (balanc_3_de)                                                                            | 34          |

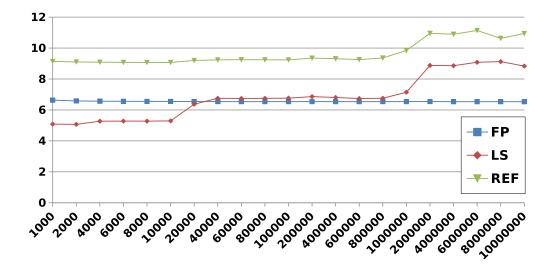

| 3.3        | Example of Codelet Behavior Across Dataset Sizes (toeplz_4_de) .                                                                 | 35          |

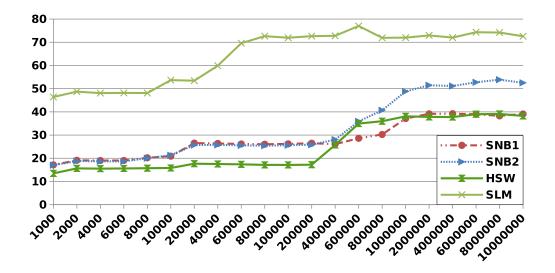

| 3.4        | Behavior across Machines (toeplz 1 de)                                                                                           | 36          |

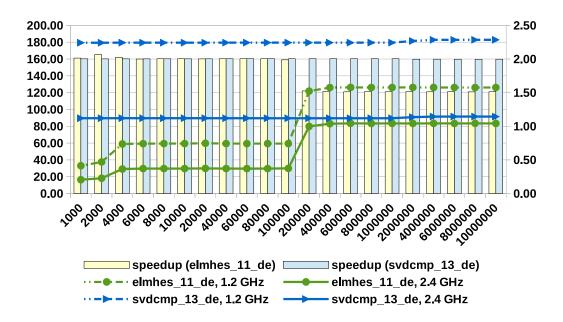

| 3.5        | Frequency Scaling Example (elmhes_11_de and svdcmp_13_de)                                                                        | 37          |

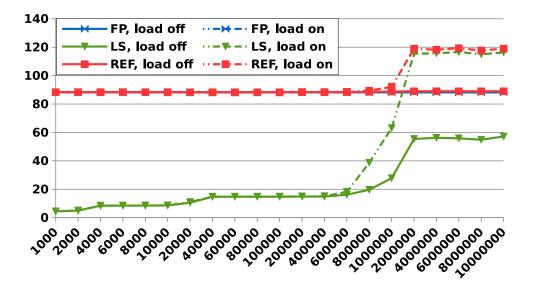

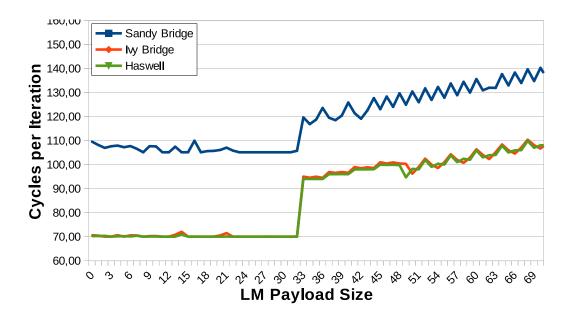

| 3.6        | Memory Load Example (svdcmp_14_de)                                                                                               | 38          |

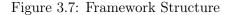

| 3.7        | Framework Structure                                                                                                              | 39          |

| 4.1        | Polaris Source Code Sample                                                                                                       | 46          |

| 4.2        | DECAN Analysis Example                                                                                                           | 47          |

| 4.3        | Low-Level CQA Output                                                                                                             | 49          |

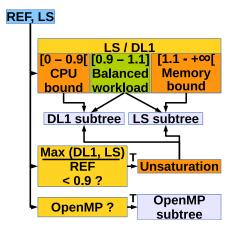

| 4.4        | PAMDA Overview                                                                                                                   | -1 <i>5</i> |

| 4.4        | Performance Investigation Overview                                                                                               | 50<br>51    |

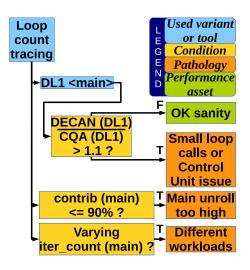

| 4.5<br>4.6 | Detecting Structural Issues                                                                                                      | 51<br>52    |

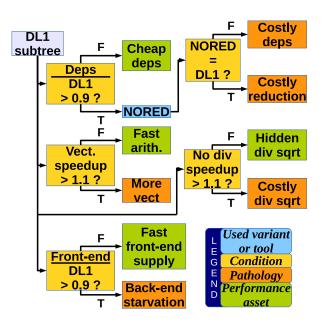

| 4.0<br>4.7 | DL1 Subtree: CPU Performance Evaluation                                                                                          | 52<br>52    |

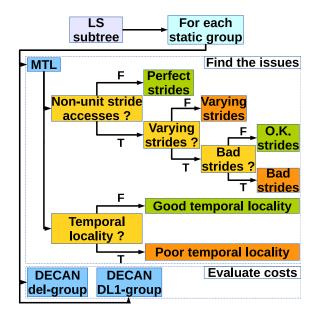

|            |                                                                                                                                  |             |

| 4.8        | LS Subtree: Memory Performance Evaluation                                                                                        | 53          |

| 4.9        | OpenMP Performance Subtree                                                                                                       | 54          |

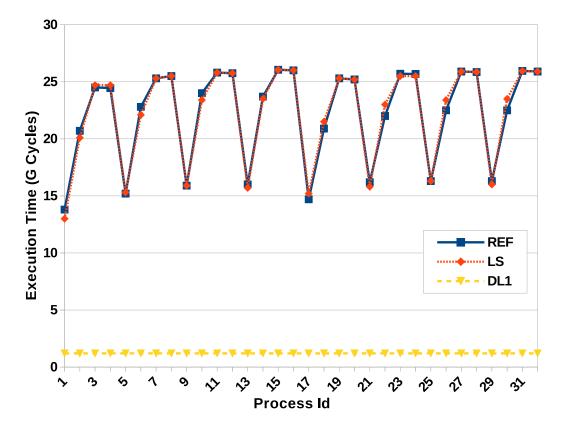

| 4.10       |                                                                                                                                  | 55          |

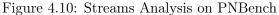

|            | Group cost analysis on PNBench                                                                                                   | 56          |

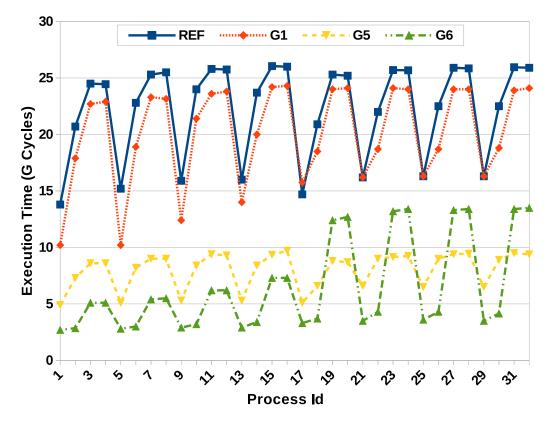

| 4.12       | Evaluation of the Cost of Cache Coherence Protocol                                                                               | 57          |

| 5.1        | Exposing the Front-End Ceiling Effect                                                                                            | 68          |

| 5.2        | Modeling the FP Add Functional Unit                                                                                              | 70          |

| 5.3        | Modeling the Store Functional Unit                                                                                               | 71          |

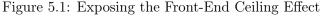

| 5.4        | Impact of TLB Misses                                                                                                             | 73          |

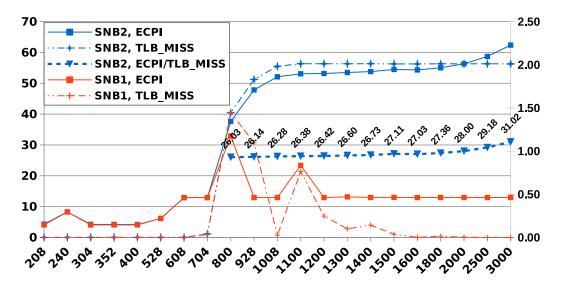

| 5.5        | DECAN-level System Saturation                                                                                                    | 76          |

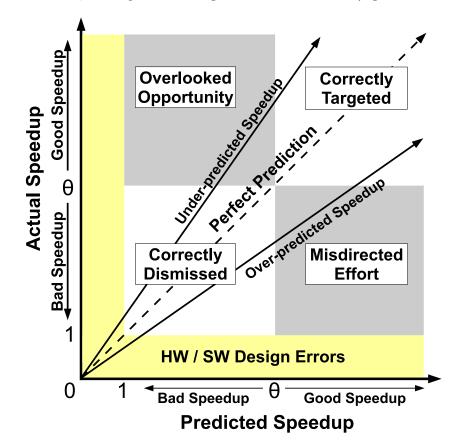

| 6.1        | Operating Space of a Performance Prediction Tool                                                                                 | 81          |

| 6.2        | YALES2 loop example                                                                                                              | 83          |

| 6.3        | VP <sup>3</sup> Projection Results for YALES2: Low Prospects for Vectorization                                                   |             |

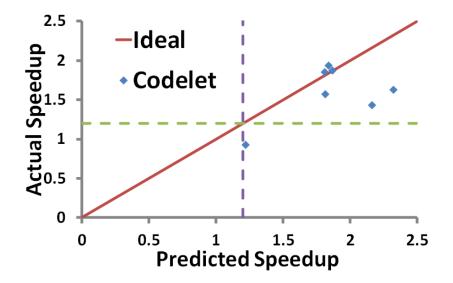

| 6.5        | $VP^3$ Projection Results for POLARIS: $VP^3$ vs. Measurements                                                                   | 86          |

| 6.6        | Operating Space of VP <sup>3</sup> on POLARIS ( $\theta = 1.2$ )                                                                 | 86          |

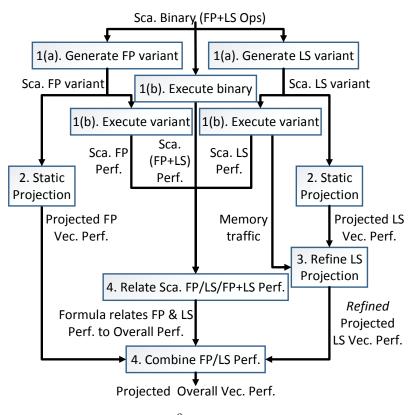

| 6.7        | $VP^3$ Vec. Projection Steps                                                                                                     | 87          |

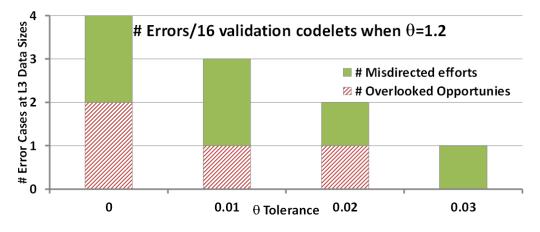

| 6.8        | Error Cases/16 Validation Codelets vs. $\theta$ Tolerance                                                                        | 91          |

|            |                                                                                                                                  |             |

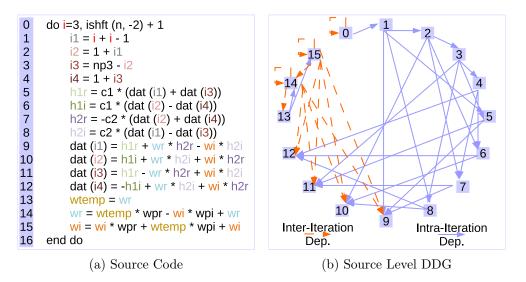

| 7.1        | Realft2_4_de Codelet                                                                                                             | 98          |

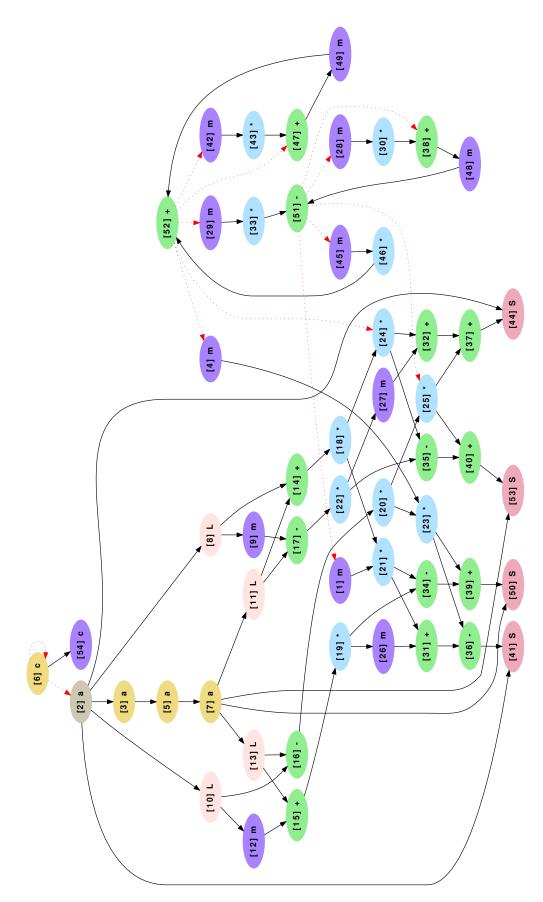

| 7.2        | $Realft2\_4\_de DDG \dots \dots$ | 100         |

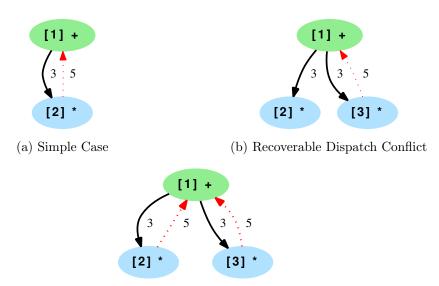

| 7.3  | Inter-Iteration Dependency Cases                                     |

|------|----------------------------------------------------------------------|

| 7.4  | UFS Uop Flow Chart                                                   |

| 7.5  | In Vitro Validation for FP [SNB] 120                                 |

| 7.6  | In Vitro Validation for LS [SNB]                                     |

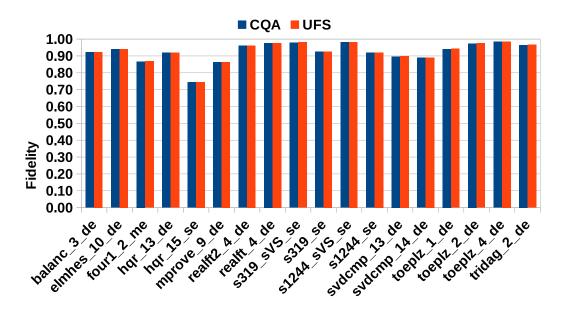

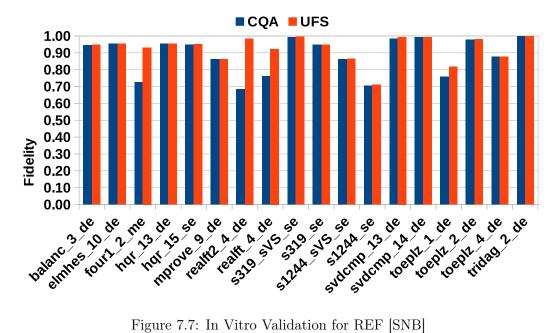

| 7.7  | In Vitro Validation for REF [SNB]                                    |

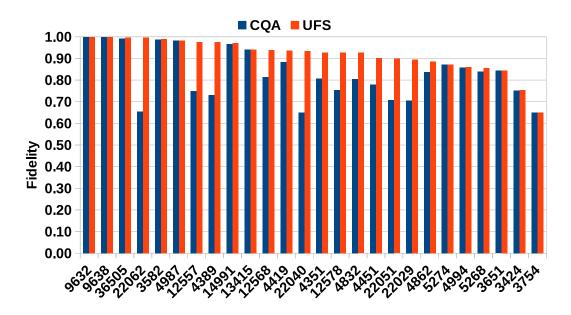

| 7.8  | In Vivo Validation for DL1: Y2 / 3D Cylinder [SNB]                   |

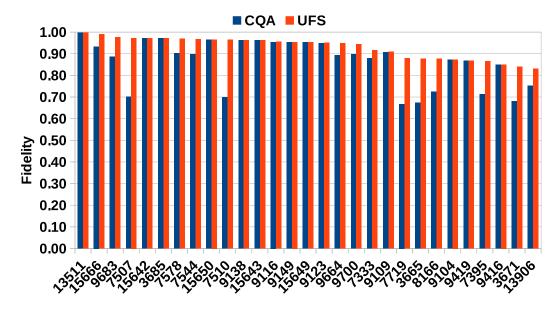

| 7.9  | In Vivo Validation for DL1: AVBP [SNB]                               |

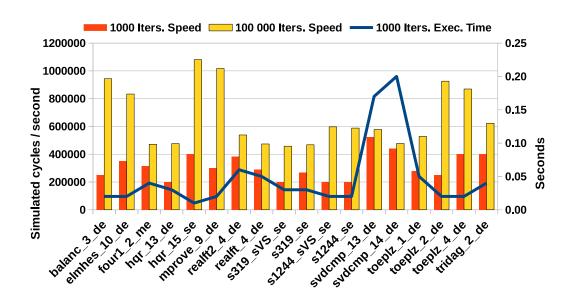

| 7.10 | UFS Speed Validation for NRs and Maleki Codelets (REF Variant) . 125 |

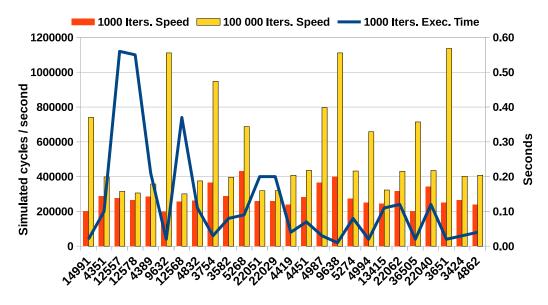

| 7.11 | UFS Speed Validation for YALES2: 3D Cylinder 126                     |

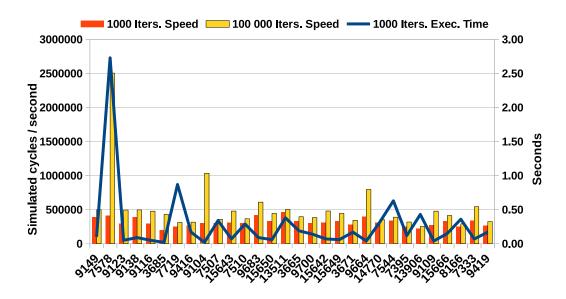

| 7.12 | UFS Speed Validation for AVBP 127                                    |

|      |                                                                      |

| A.1  | Quantifying Branch Buffer Entries                                    |

| A.2  | Quantifying Load Buffer Entries                                      |

| A.3  | Quantifying FP PRF Entries                                           |

| A.4  | Quantifying Integer PRF Entries                                      |

| A.5  | Quantifying Overall PRF Entries                                      |

| A.6  | Quantifying ROB Entries                                              |

| A.7  | Quantifying RS Entries                                               |

| A.8  | Quantifying SB Entries                                               |

| A.9  | ROB Microfusion Evaluation                                           |

| A.10 | RS Microfusion Evaluation                                            |

|      |                                                                      |

| B.1  | Quantifying Load Matrix Entries                                      |

# List of Tables

| $3.1 \\ 3.2$                                                        | NR Codelet Suite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28<br>33                                                         |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.4                                            | A few typical performance pathologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>50<br>53<br>55                                             |

| $5.1 \\ 5.2 \\ 5.3$                                                 | Finding Unlamination Rules       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 66<br>67<br>72                                                   |

| 6.1                                                                 | BW Scaling Factors (BW Vector / BW Scalar)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 89                                                               |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10 | Realft2_4_de: Measurements and CQA ErrorRealft2_4_de Assembly InstructionsRealft_4_de: Measurements and CQA ErrorExposing Pseudo FIFO limitations: Assembly Code for "rs_pb"Exposing Pseudo FIFO limitations: Experimental ResultsExperimental Resource Quantifying SummaryPartial UFS Loop Input Example (Realft2_4_de)Needed Resources for Queue Uop Types and Outputs (SNB)Realft2_4_de: UFS Validation (SNB)Realft2_4_de UFS Trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98<br>99<br>101<br>104<br>104<br>106<br>107<br>111<br>117<br>119 |

|                                                                     | Realft_4_de: UFS Validation (SNB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 120                                                              |

|                                                                     | Resource Quantifying Experiment Example $\dots \dots \dots \dots \dots$<br>Resource Quantifying Experiment Example for the BB (P = 2) $\dots$<br>BB Size: Measured vs. Official $\dots \dots \dots \dots \dots \dots \dots \dots$<br>Resource Quantifying Experiment Example for the LB (P = 2) $\dots$<br>LB Size: Measured vs. Official $\dots \dots \dots \dots \dots \dots \dots \dots \dots$<br>Resource Quantifying Experiment Example for the FP PRF (P = 4)<br>FP PRF Size: Measured vs. Official $\dots \dots \dots \dots \dots \dots \dots \dots \dots$<br>Resource Quantifying Experiment Example for the Integer PRF (P                                                                                                                                                                                                                                                                                                                                                                | 134<br>135<br>135<br>136<br>136<br>137<br>139                    |

| A.9<br>A.10                                                         | $\begin{array}{l} Hesselfee Qualitying Experiment Example for the integer 1 for (if = 4) $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 139<br>140<br>141<br>141                                         |

| A.13<br>A.14                                                        | RQ Experiment Example for the ROB $(P = 4)$ ROB Size: Measured vs. OfficialRQ Experiment Example for the RS $(P = 4)$ RS Size: Measured vs. Official                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 142<br>143<br>143<br>144                                         |

| A.16<br>A.17                                                        | $\vec{B}$ RQ Experiment Example for the SB (P = 4) $\dots \dots \dots \dots \dots \dots$<br>SB Size: Measured vs. Official $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 145<br>145                                                       |

|                                                                     | B Microfusion Evaluation Experiment for the ROB $(P = 4)$ ROB Microfusion Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 147<br>148                                                       |

| A.20 | Microfusion Evaluation Experiment for the RS $(P = 4) \dots \dots \dots$ | 148 |

|------|--------------------------------------------------------------------------|-----|

| A.21 | RS Microfusion Evaluation                                                | 149 |

|      |                                                                          |     |

| B.1  | Resource Quantifying Experiment Example for the LM $(P = 2)$             | 151 |

| B.2  | LM Size: Measured vs. Official                                           | 152 |

# List of Algorithms

| 1 | Simplified Front-End Algorithm | 110 |

|---|--------------------------------|-----|

| 2 | Issue Algorithm                | 112 |

| 3 | Port Binding Algorithm         | 112 |

| 4 | Dispatch Algorithm             | 113 |

The growing complexity behind modern CPU microarchitectures [1, 2] makes performance evaluation and modeling a very complex task. Indeed, modern CPUs will typically implement features such as pipelining, register renaming, speculative and out-of-order execution, data prefetchers, vectorization, virtual memory, caches and multiple execution cores. While each of them can be beneficial to performance, they also make performance analysis more difficult.

On the consumer side of the CPU design process, users want to know which product fits their needs best in terms of performance, energy consumption and/or price. Software developers will be more concerned with adjusting their applications to make the best use of existing features, especially when performance represents a direct competitive advantage.

On the designer side, CPU manufacturers need to build microarchitectures offering the characteristics wanted by users while keeping costs low. Furthermore, as product improvements may have to rely on complex mechanisms, they have to guide software developers on how to use them while also having the contrary objective of preventing competitor plagia by controlling the exposure of their performance recipes.

In this context, performance modeling can be used to cost-effectively:

- 1. Help users find out which hardware would best fit their applications (without actually buying all the considered hardware first).

- 2. Expose optimization opportunities to software developers (without first testing them).

- 3. Offer CPU architects insights on which hardware improvements would speed user applications the most (without first implementing them).

This chapter will describe why performance modeling is important in the field of High Performance Computing (HPC) and proceed to present the objectives and contributions of this thesis. It will also provide a quick overview of the document.

# 1.1 High Performance Computing (HPC)

HPC represents the use of large-scale machines called *supercomputers* to process compute workloads extremely quickly. It is used (and needed) in areas as diverse as aerodynamic simulations, cryptanalysis, engine design, oil and gas exploration, molecular dynamics or weather forecasting.

It is an environment with very interesting characteristics:

1. Performance is a primary objective and can result in hefty monetary gains. For instance, a faster numerical simulator will be able to provide more results, or/and results of a better quality, in domains as various as the design of cars, plane wings, nuclear plants or the development of new drugs.

- 2. The used supercomputers can have millions of execution cores [3], offering potentially tremendous calculation speeds and making energy consumption an unavoidable (and expensive) concern: a poorly used machine is a costly machine.

- 3. Users and software developers can be strongly tied, or even be the same entities. It creates an interesting dynamic where developers are strongly motivated to optimize their code to make the best use of existing resources, and may also have a say in which machines to buy next.

As HPC applications typically spend very large amounts of time in computational loops due to processing large data sets, loop analysis is a primary go-to approach for HPC performance analysis, optimization and modeling.

## **1.2** Objectives and Contributions

This thesis focuses on increasing the cost-effective observability of potential bottlenecks in HPC computational loops and how they relate to each other. It aims to do so by combining static and dynamic approaches to identify, quantify, and model both the bottlenecks and their interactions.

Its main contributions are:

- 1. PAMDA, a performance evaluation methodology using a blend of static and dynamic analyses to find bottlenecks and quantify their impact. Its main purpose is to expose optimization opportunities.

- 2. An adaptation of the Cape linear model to the Sandy Bridge microarchitecture as well as a direct application thereof with VP3, a vectorization gain predictor.

- 3. Uop Flow Simulation (UFS), a loop performance modeling technique combining static analysis and cycle-level simulation to account for out-of-order limitations at a very low execution cost.

Other less significant contributions include:

- 1. A loop performance measurement framework combining static and dynamic analysis tools to evaluate loop performance from different angles.

- 2. An empirical approach to quantify out-of-order resources.

### 1.3 Overview

Chapter 2 will present some background information to familiarize readers with CPU microarchitectural details and nomenclature, performance analysis approaches and tools, as well as with the use of small benchmarks called *codelets*.

We will introduce a framework combining CQA and DECAN (respectively static and dynamic analysis tools) in Chapter 3. Its objective is to get detailed performance metrics on small codelets given various execution scenarios.

We will then present PAMDA, a performance analysis methodology, in Chapter 4. It leverages elements obtained from codelet analysis to detect potential performance problems in HPC applications and help resolve them. Chapter 5 will describe a work extending the Cape linear model to better cover Sandy Bridge and give it more flexibility for HW/SW codesign purposes. It will be directly used in Chapter 6 with VP3, a tool evaluating the performance gains vectorizing loops could provide.

Chapter 7 will introduce UFS, an approach combining static analysis and cycleaccurate simulation to very quickly estimate a loop's execution time while accounting for out-of-order limitations in modern CPUs, and better identifying out-of-order related issues than PAMDA or Cape modeling.

We will finally conclude in Chapter 8, summarizing our contributions and presenting future work.

This chapter will focus on presenting the technical context for this thesis and introduce some of the nomenclature used throughout this manuscript.

It will first describe modern Intel microarchitectures detailedly, before presenting different performance analysis approaches and tools. It will also explain some of the advantages and limitations of *codelets*, small benchmarks which we will use for modeling purposes in later chapters.

# 2.1 Recent Microarchitectures

Microarchitectures are the result of different design choices and incremental improvements carried over CPU generations. They are typically pipelined and feature the following components:

- 1. Front-End (FE): component of reading and decoding instructions, making them available to the rest of the execution pipeline.

- 2. Back-End (BE): executes the instructions provided by the Front-End.

- 3. Memory Hierarchy: caches can be used to improve the effective speed of memory accesses for both data and instructions.

We will present some of the microarchitectures particularly relevant to HPC here, using information from official sources [4, 5, 6, 7, 8], technical news articles [9, 10, 11, 12, 13, 14, 15], test-based reports [16] and our own observations.

### 2.1.1 Sandy Bridge

Sandy Bridge (SNB) is a microarchitecture used in the performance-oriented Big Core family of Intel CPUs. It is a tock in the manufacturer's tick-tock development cycle [17], meaning it keeps the same 32 nm lithography as its Westmere predecessor, but brings important microarchitectural changes.

It will be the microarchitecture this thesis most focuses on. We will present it in details and later use it as a base point to describe the incremental improvements brought by its *Ivy Bridge* and *Haswell* successors.

SNB Stock Keeping Units (SKUs) can have from 1 to 6 cores.

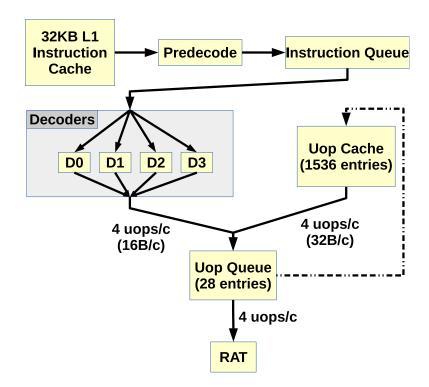

### 2.1.1.1 Front-End

Sandy Bridge's decode pipeline (also called *legacy decode pipeline*) is in charge of fetching instructions from the memory hierarchy and decoding them, producing uops more easily interpretable by the Back-End. It is the component the most directly affected by the complexity of the x86 instruction sets, and can produce up to 16 bytes of uop *or* 4 uops per cycle, whichever is the most restrictive. Furthermore, it has branch prediction abilities, and can decode and provide uops speculatively.

While it can typically only decode up to 4 instructions per cycle, it implements extra features to increase its effective bandwidth:

- 1. Macrofusion: allows a simple integer instruction and a following branch instruction to be decoded as a single uop in certain circumstances. This actually brings the maximum theoretical number of decoded instructions to 5 per cycle in favorable corner cases.

- 2. Microfusion: complex instructions may need to get divided in smaller logical operations (or *components*) when decoded to simplify the Back-End's work. Microfusion allows instructions having both an arithmetic and a memory components to be fit in a single uop for part of the pipeline despite this constraint, potentially doubling the effective FE bandwidth. For instance, *MULPD (%rax), %xmm0* will occupy a single uop slot until each component needs to be executed separately.

Figure 2.1: Simplified Sandy Bridge Front-End

Sandy Bridge's Front-End can produce up to 4 uops using any of three different generation mechanisms: the decoders (legacy pipeline), the Uop Cache and the Uop Queue (when iterating over small loops). Only one uop source may be active at a time.

Furthermore, as decoding is a slow and expensive process, Intel CPU architects designed extra mechanisms to prevent instructions from having to be constantly re-decoded, reducing the pressure on the legacy pipeline and increasing the FE's bandwidth (see Figure 2.1):

The uop queue: queues uops right before the RAT, allowing some FE or Back-End stalls to be absorbed. A loop detection mechanism called Loop Stream Detector detects when uops currently in the queue are part of a loop, and can decide to a) stop taking uops from the legacy pipeline, b) not destroy the uops it sends to the Back-End and c) replay them as many times as necessary. While its peak bandwidth is still 4 uops per cycle, there is no limit on the number of transferred bytes anymore, increasing the effective FE bandwidth when lengthy uops are present.

It has a maximum capacity of 28 uops on SNB.

2. The *uop cache* (or *Decoded ICache*): it saves uops decoded by the legacy pipeline, and can serve as an alternative uop provider for the uop queue. As with the legacy pipeline and the uop queue, its peak bandwidth is 4 uops per cycle, though with a maximum of 32 bytes of uop being generated per cycle.

It is extremely large compared to the uop queue's capacity and can contain up to 1536 uops in ideal conditions.

#### 2.1.1.2 Execution Engine

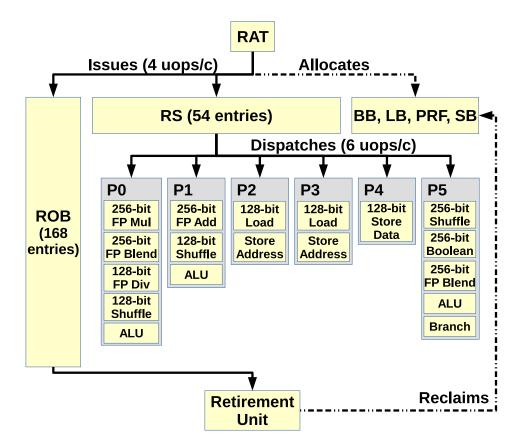

Figure 2.2: Simplified Sandy Bridge Execution Engine

The RAT issues uops from the Front-End to the Back-End after having allocated the necessary out-of-order resources and renamed their operands.

The ROB keeps track of all in-flight uops (both those pending execution and the ones waiting for retirement), while other resources are more specific (e.g. the LB keeps track of load entries). All resources are allocated at issue time and only reclaimed at retirement, with the notable exception of RS entries (which are released once uops are dispatched to compatible execution ports).

The RS can dispatch up to 6 uops per cycle (one to each port) out-of-order.

The Resource Allocation Table (RAT) is the gateway component between the

Front-End the FE to the Back-End. It *issues* uops in-order, performs register renaming and allocates the resources necessary to their out-of-order execution. While all uops need an entry in the ReOrder Buffer (ROB) to be issued, other out-of-order buffers are allocated on a per-case basis.

Interestingly, not all uops need to be sent to the Reservation Station to wait for execution: Sandy Bridge processes *nop* uops (which have no input nor output) and *zero-idioms* (whose output is always zero, and hence have no relevant input) directly in the RAT.

Other resources such as the Branch Buffer, Load Buffer, Physical Registers and Store buffer are intuitively only allocated for respectively branches, loads and software prefetches, uops with a register output and stores.

Furthermore, with the exception of Reservation Station entries, resources are only released at the retirement step.

The Reservation Station holds uops until their input operands are ready, and then *dispatches* them to adequate execution ports. The latter will forward them to the proper Functional Units where they will begin their *execution*.

Most Functional Units are fully pipelined, often giving them a throughput of 1 uop per cycle.

Fully executed uops are *retired* in-order, at which point their output is committed to the architectural state and their resources freed.

Figure 2.2 summarizes our description of Sandy Bridge's execution engine.

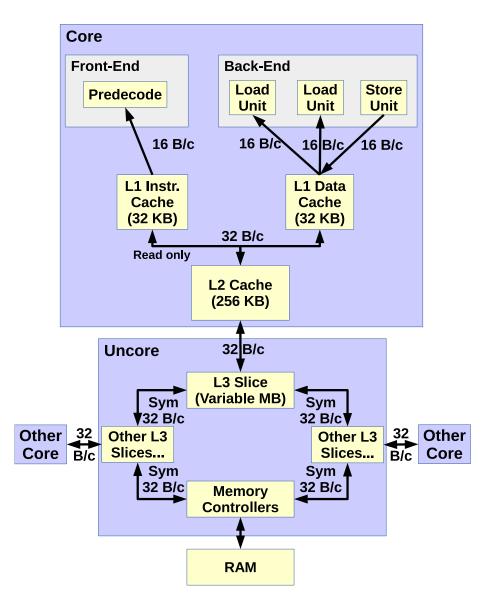

#### 2.1.1.3 Memory Hierarchy

The role of the memory hierarchy is to dampen the impact of RAM's limited bandwidth and latency by acting as intermediaries to the main (RAM) memory. Indeed, caches can be much faster than RAM in both regards due to their being much smaller: as a general rule, the smaller the memory unit is, the faster it can perform. CPUs may consequently have several levels of cache, each offering different levels of capacity and performance.

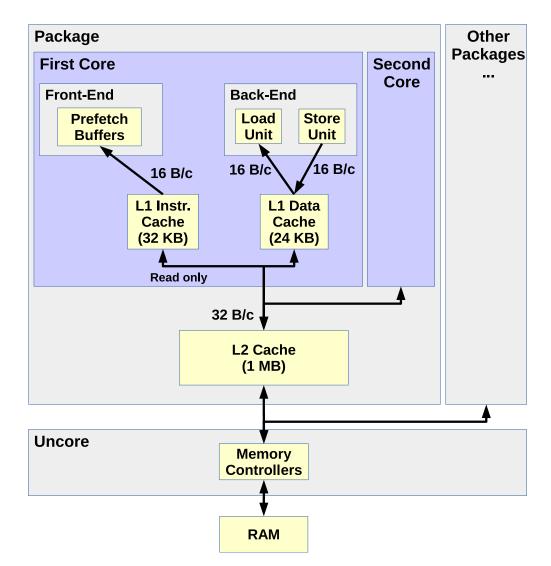

Sandy Bridge's memory hierarchy is summarized in Figure 2.3.

Load and Store Units can each transfer up to 16 bytes from/to the L1 data cache per cycle, though there are 2 of the former and only 1 of the latter. While they can work concurrently (for an aggregated bandwidth of 24 bytes per cycle), this can only be achieved when using AVX 32-byte vector transfers due to port restrictions (32-byte transfers keep memory units busy for 2 cycles, allowing store address uops to use ports 2 and 3 without penalizing loads).

All of Sandy Bridge's data caches are write-back: upper cache levels are only made aware of memory writes (or *stores*) when cache lines from lower levels are evicted. Sandy Bridge's 32-KB L1 data cache is 8-way associative and virtually indexed. Its 256-KB L2 cache also has an associativity of 8, but is physically indexed and interestingly neither inclusive nor exclusive in regards to L1. The L3's size is SKU-dependent and can range from 1 to 20 MB. Its associativity is also variable, and is between 12 and 16 depending on the model.

All three cache levels use an NRU (*Not Recently Used*, a variant of *Least Recently Used*) replacement policy.

Four data prefetchers are also present, whose role is to predict which cache lines are going to be needed in the future and request them ahead of time:

Figure 2.3: Simplified Sandy Bridge Memory Hierarchy

The data L1 has a combined bandwidth of 48 bytes per cycle, as load and store accesses can be performed in parallel. The L2's 32 bytes per cycle bandwidth is shared for all fetch and store accesses from the L1s. However, only the data L1 can write data back to the L2. Each L3 slice also has a dedicated bandwidth of 32 bytes per cycle which is shared for read and write accesses from the L2.

The L3 is distributed over all the cores, allowing each core to have their own dedicated access to L3. The bi-directional data ring connecting the slices allows each core to access the entirety of L3, though latency may vary a bit depending on far the relevant slice is.

L3 slices share the same memory controllers for RAM accesses.

- 1. The *DCU Prefetcher* (operates in L1): detects ascending-address loads within the same cache line and fetches the following cache line.

- 2. The *Instruction-Pointer-based Prefetcher* (operates in L1): detects access stride patterns for individual load instructions and fetches cache lines accordingly.

- 3. The Spatial Prefetcher (or Adjacent Cache Line Prefetcher; operates in L2): pairs contiguous cache lines in 128-byte blocks. Accesses to the first cache line trigger the fetching of the whole block.

- 4. The *Stream Prefetcher* (operates in L2): tries to predict and fetch futurelyused cache lines based on previous accessed addresses. It can keep track of up to 32 different access patterns.

Sandy Bridge has a 2-level Translation Lookaside Buffer system:

- The L1-TLB is 4-way associative, and can contain up to 64 4KB page entries, 32 2MB entries and 4 1GB entries.

- 2. The L2-TLB is also 4-way associative, and can contain up to 512 4KB page entries. It cannot hold larger page entries.

#### 2.1.2 Ivy Bridge

Ivy Bridge is the tick improvement of Sandy Bridge, carrying the microarchitecture to a 22 nm lithography but only bringing moderate microarchitectural changes.

IVB CPUs feature from 1 to 15 cores.

#### 2.1.2.1 Front-End

Sandy Bridge's uses two physical 28-entry uop queues to support hyper-threading. Ivy Bridge improves over it by fusing the queues into a single physical one with 56 entries, and virtually splitting it only when hyper-threading is actually used. It improves its ability to absorb pipeline stalls and increases the maximum size of loops replayable with the Loop Stream Detector, helping improve performance and lower power consumption.

#### 2.1.2.2 Execution Engine

Ivy Bridge introduces 0-latency register moves: in some cases, register moves can be achieved by merely making the named register point to the source physical register, which can be done by the RAT.

The architects also improved the divider / square root unit, likely taking advantage of the finer lithography to widen it and improve its bandwidth significantly (as well as its latency to a lesser extent).

#### 2.1.2.3 Memory Hierarchy

While the sizes of L1 and L2 are the same for IVB as for SNB, the maximum L3 size was increased from 20 MB to 37.5.

Furthermore, L3 seems to use an adaptive replacement policy [18].

Ivy Bridge also introduces the *Next-Page Prefetcher* (NPP), which detects memory accesses nearing the beginning or the end of a page to fetch the matching page translation entry. It is not clear whether the NPP fetches entries to the L2 data cache or directly to the TLBs, though Intel patent [19] suggests the latter.

#### 2.1.3 Haswell

Haswell is the tock after Ivy Bridge, focusing once again on microarchitectural changes and still using the same 22 nm lithography.

#### 2.1.3.1 Front-End

Haswell's Front-End is largely the same as Ivy Bridge's.

#### 2.1.3.2 Execution Engine

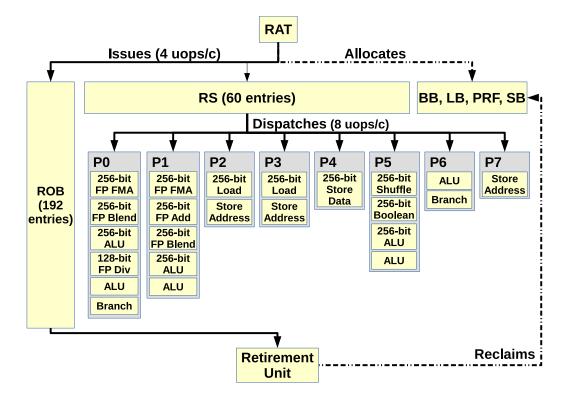

Figure 2.4: Simplified Haswell Execution Engine

The Haswell execution engine brings various improvements over Sandy Bridge, such as more execution ports, new Fused Multiply-Add functional units, larger outof-order buffers and memory units able to process 32-byte transfers in a single cycle.

The execution engine has some important changes, which are summarized in Figure 2.4. Some of the most important ones include:

- 1. There now being 8 dispatch ports (against 6 previously), one of which is dedicated to handle store address uops.

- 2. Pipelined Fused Multiply-Add units being placed behind ports 0 and 1, doubling the potential number of FP operations per cycle. Indeed, they can each execute vector operations such as result = vector1 \* vector2 + vector3 with a throughput of 1 per cycle (note: in Haswell's implementation, the result register must be one of the inputs).

- 3. The sizes of most out-of-order resources are increased.

#### 2.1.3.3 Memory Hierarchy

The L1 bandwidth is doubled, allowing the two load units and the store unit to each transfer up to 32 bytes per cycle (for a combined bandwidth of 96 bytes per cycle).

The L2 bandwidth was also doubled, allowing a full cache line (64 bytes) to be transferred between L1 and L2 every cycle.

The minimum and maximum L3 sizes were increased to reach respectively 2 MB and 45 MB.

Furthermore, some SKUs are equipped with *Crystalwell* embedded DRAM acting as a 128MB L4 victim cache, providing important bandwidth and latency bonuses.

### 2.1.4 Silvermont

Unlike SNB, IVB and HSW, *Silvermont* (SLM) is a microarchitecture used for *Atom* processors, for which emphasis is on low power consumption. Its *Bay Trail* variant targets the mobile sector, while *Avoton* micro-server versions were also designed.

Silvermont uses a 22 nm lithography, just like main line processor, and comprises between 1 (in Bay Trail) and 8 cores (in Avoton).

It is a particularly interesting x86 microarchitecture due to how energy consumption considerations impacted its design. Furthermore, future high-performance *Knights Landing* chips will feature around 70 Silvermont-inspired cores, making it very relevant in the HPC sphere.

#### 2.1.4.1 Front-End

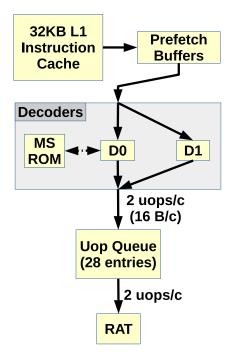

Figure 2.5: Simplified Silvermont Front-End

Silvermont's Front-End can provide the RAT with up to 2 uops per cycle. However, its decoders are limited, and D1 can only decode simple instructions.

A feature called Loop Stream Detector can help compensate for the decoders' weaknesses when executing loops with small loop bodies, pinning down uops in the Uop Queue and replaying them for as long as possible. The Front-End can then consistently reach its peak bandwidth.

Silvermont's Front-End supports speculative execution and branch prediction. It is 2-wide (see Figure 2.5), meaning it can decode and provide up to 2 uops to the Back-End per cycle. This is twice less than what Big Core microarchitectures can do, and is further aggravated by SLM's individual instruction decoders being less potent than those in the main line products. They are however more power-efficient.

There is also a Loop Stream Detector in the uop queue, which takes a very high importance due to the decoders' weaknesses. While for SNB/IVB/HSW using the LSD is done rather opportunistically, it is an important factor for SLM performance.

#### 2.1.4.2 Execution Engine

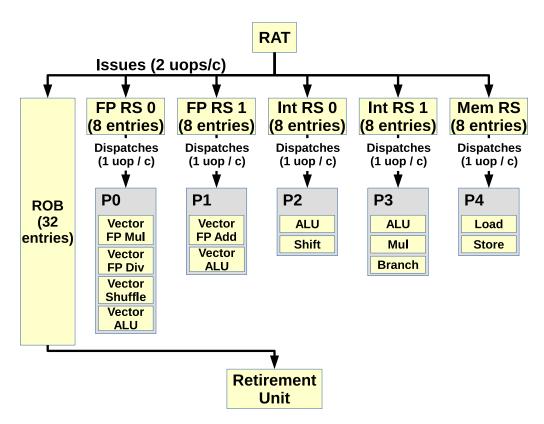

The RAT / Allocation / Rename cluster bridges the FE with the BE, inserting uops in-order after a) allocating some of the necessary resources for their execution and b) renaming their input and output registers.

All uops need an entry in the ROB. It is also not clear when other resources (e.g. Load Buffer) are allocated, as Intel claims Silvermont uses a late allocation / early resource reclamation scheme [20].

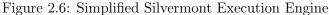

The scheduler system is distributed over different Reservation Stations, each handling a specific execution port (see Figure 2.6), and their own in-order or outof-order dispatch policy:

- 1. FP RS 0: handles FP and vector additions, as well as some other arithmetic and logic operations. Dispatches uops in-order (only in regards to uops in FP-RS-1).

- 2. FP RS 1: handles FP and vector multiplications, divisions, shuffles and other operations. Dispatches uops in-order (only in regards to uops in FP-RS-2).

- 3. Int RS 0: handles integer arithmetic, logic and shift operations. Dispatches uops out-of-order.

- 4. Int RS 1: handles integer arithmetic and logic as well as branches. Dispatches uops out-of-order.

- 5. Mem RS: handles address generations, loads and stores. Dispatches uops inorder, but allows accesses to complete out-of-order to absorb latency.

Fully executed uops are retired and committed in-order.

#### 2.1.4.3 Memory Hierarchy

Silvermont has a 24KB L1 with an associativity of 6. The load and store units can transfer up to 16 bytes per cycle from/to it, though they likely cannot do so simultaneously (as only one address per cycle can be generated for loads and stores). It adopts a random cache line replacement policy.

Single-core Silvermont SKUs have a 512KB L2.

SKUs with more than 1 core are organized in pairs of cores called *modules*, with each module having 1 MB of dedicated 16-way associative L2. The overall cache size for 8-core Silvermont CPUs hence reaches 4 MB, though each core is constrained to only use the L2 slice from its own package.

The L1 and the L2 can exchange up to 32 bytes per cycle, though this link is shared with all the cores in the package. It uses an NRU cache line replacement policy.

The L1 and L2 caches are both write-back.

There are two data prefetchers, the L1 Spatial Prefetcher and an L2 "advanced" prefetcher. They are likely respectively inspired by the L1 DCU and the L2 Streamer prefetchers from the Big Core CPUs, but not many details are given.

Unlike Big Core microarchitecture, there is no unified reservation station. Furthermore, each small RS acts with its own rules:

- 1. The FP Reservation Stations have to dispatch their uops in-order.

- 2. The Mem RS also has to dispatch uops in-order (to help memory scheduling be as simple as possible), but they are non-blocking and can be be completed out-of-order.

- 3. Integer Reservation Stations can dispatch uops out-of-order.

The ports presented here might not actually have a discrete existence, (as absent from any official documentation we could find), but we decided to put them here anyway to simplify the figure. We labelled them in a manner consistent with Big Core CPUs.

Silvermont also has a 2-level TLB cache:

- 1. The L1 TLB has 48 4KB entries and is fully associative.

- 2. The L2 TLB has 128 4KB entries and 16 2MB entries, and is 4-way associative. It is not inclusive (nor exclusive) in regards to the L1.

Figure 2.7 summarizes this memory hierarchy.

## 2.2 Performance Analysis

Different approaches can be adopted to analyze performance, each working with their own tradeoffs. This section will present some of them.

Figure 2.7: Simplified Silvermont Memory Hierarchy

The Load and the Store units cannot access L1 in parallel, so the data L1's bandwidth is of 16 bytes per cycle.

The L2 cache space and bandwidth are shared between cores from a same package.

Finally, the memory controllers are shared by all cores on the CPU.

#### 2.2.1 Static Analysis

Static analysis consists in evaluating software without executing it. This offers the advantage of being particularly fast, at the cost of working with a limited amount of information.

We will present tools using this approach in this section.

#### 2.2.1.1 Code Quality Analyzer (CQA)