## Architecture FPGA amelioree et flot de conception pour une reconfiguration materielle en ligne efficace

Christophe Huriaux

#### ▶ To cite this version:

Christophe Huriaux. Architecture FPGA amelioree et flot de conception pour une reconfiguration materielle en ligne efficace. Architectures Matérielles [cs.AR]. Université Rennes 1, 2015. Français. <NNT: 2015REN1S140>. <tel-01253498v3>

HAL Id: tel-01253498

https://hal.inria.fr/tel-01253498v3

Submitted on 27 Jun 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

### DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention: Traitement du Signal et Télécommunications

### École doctorale MATISSE

présentée par

# Christophe Huriaux

préparée à l'unité de recherche IRISA (UMR 6074) Institut de Recherche en Informatique et Systèmes Aléatoires École Nationale Supérieure de Sciences Appliquées et de Technologie

Enhanced FPGA

Architecture

and CAD Flow

for Efficient

Runtime Hardware

Reconfiguration

Thèse soutenue à Lannion le 2 Décembre 2015

devant le jury composé de :

Lorena Anghel

Professeur, Grenoble INP Phelma, TIMA

Présidente du jury

Antoine Courtay

Maître de conférence, Université de Rennes 1, IRISA

Co-directeur de thèse

Guy Lemieux

Professeur, University of British Columbia, Canada

Rapporteur

Philippe MILLET

Thales Resarch and Technology

Examinateur

Olivier Sentieys

Directeur de recherche, Inria

Directeur de thèse

Russell Tessier

Professeur, University of Massachusetts, État-Unis

Examinateur

Lionel Torres

Professeur, Université de Montpellier 2, LIRMM

Rapporteur

## REMERCIEMENTS

Je tiens avant toute chose à remercier mes directeurs de thèse, Olivier SENTIEYS et Antoine Courtay, de m'avoir offert la possibilité d'effectuer cette thèse et de m'avoir impliqué dans un projet intéressant et enrichissant à tous points de vue. Leur encadrement, leur expérience et leur bonne humeur m'ont accompagné durant ces trois années et j'ai découvert avec eux les joies de la recherche et la rigueur scientifique propre à ce métier. Leurs conseils avisés et leur patience m'ont permis d'aboutir aux travaux présentés dans ce document et à m'intégrer dans une communauté riche.

Les travaux décrits dans ce document ne sauraient être complets sans la participation des membres du jury de soutenance. Je remercie les professeurs Guy LEMIEUX et Lionel TORRES d'avoir accepté de relire mes travaux et de m'avoir fournis des conseils et remarques enrichissants. Je remercie en outre les examinateurs : Lorena Anghel, en tant que présidente du jury, Philippe MILLET qui m'a aussi enrichi au cours de notre collaboration durant le projet FlexTiles, et Russell Tessier qui m'a accueilli à bras ouverts lors de mon séjour de trois mois au sein de son équipe de recherche à Amherst aux États-Unis, et m'a toujours fait profiter de son expérience et de son sens critique.

Merci à tous les membres des équipes Cairn et Granit avec lesquels j'ai passé des moments agréables lors de nos pauses journalières. La bonne humeur et les bons mots étaient de mise et ont contribué à leur manière à enrichir mon esprit et mon vocabulaire. En particulier, merci à Arnaud et Daniel pour le temps passé à m'inculquer les subtilités des dossiers de qualification. Par ailleurs, merci aux deux meilleures assistantes d'équipe du monde, Nadia et Angélique, pour leur bonne humeur et leur disponibilité.

Je remercie aussi ceux qui m'ont soutenu durant ces trois ans. Merci à Mickaël pour avoir co-fondé la réunion hebdomadaire du CST qui a vu naître nos initiatives schtroumpfesques. Merci à Cédric pour ses talents inimitables en matière de doublesens et ses références cinématographiques douteuses. Merci à Karim pour son humour malgré ses 7 054 698 169 phrases entamées dont on ne connaîtra jamais la fin, et à Julie pour finir lesdites phrases. Merci à university booth Nicolas d'avoir sû être Nicolas et de m'avoir exposé avec verve les subtilités de la Bretagne de 1437 à nos jours.

Je remercie mes parents, Jean-Paul et Marie, de m'avoir poussé à aller au bout de mes envies et de m'avoir soutenu tout au long de mes études.

Je garde le meilleur pour la fin en dédiant ce dernier paragraphe à celle dont la patience et le soutien m'ont accompagné pendant les bons comme les mauvais moments, à celle qui a vécu ces trois ans de thèse au même rythme soutenu que moi, et à celle qui a su rassurer mes doutes et calmer mes humeurs. Aussi surprenant que cela puisse paraître, ce ne sont en fait qu'une seule et même personne : merci Kathleen.

# RÉSUMÉ

Avec l'introduction de capacités d'auto-reconfiguration dans les FPGAs (Field-Programmable Gate Arrays), de nouveaux domaines de recherche ont émergé autour du placement dynamique de modules matériels à l'exécution. Les architectures commerciales disponibles et les outils ont évolué pour fournir des flots de reconfiguration partielle aboutis qui sont toutefois limités dans leurs fonctionnalités. L'objectif principal des travaux de cette thèse est de proposer de nouvelles approches pour faciliter une gestion en ligne flexible d'accélérateurs matériels dans les FPGAs, à la fois au niveau de l'évolution de son architecture et de son flot de conception.

Les architectures de FPGA modernes les plus avancées comportent une profusion de blocs hétérogènes destinés à fournir des performances plus élevées aux applications : des mémoires RAM, des accélérateurs arithmétiques, des émetteurs-récepteurs rapides, etc. La diversité et l'hétérogénéité de ces blocs induit une difficulté plus importante pour les algorithmes de placement en réduisant le nombre de positionnements possibles pour une tâche matérielle donnée. Dans cette thèse, une amélioration du réseau d'interconnexion de l'architecture du FPGA est proposée afin de réduire les contraintes sur le placement des tâches. Des résultats expérimentaux menés sur cette architecture montrent une augmentation de la flexibilité de placement des tâches, au détriment du délai du chemin critique.

Deuxièmement, le concept de flux de configuration indépendant de sa position finale, le Virtual Bit-Stream (VBS), est proposé pour répondre à un problème majeur des mécanismes de relogement de tâche : le stockage d'une unique configuration de tâche pour réduire l'empreinte mémoire et pour accroître la réutilisabilité des modules matériels générés. Les Virtual Bit-Streams sont élaborés grâce à une représentation abstraite de l'architecture du FPGA cible, ce qui les rend indépendants de leur position finale sur la surface logique. Grâce au format de codage du VBS, le volume de données binaires ainsi créé pour représenter une tâche matérielle peut être jusqu'à un ordre de grandeur plus petit qu'un flux de configuration conventionnel équivalent. À partir de ce concept, un flot de conception dédié à la génération des VBS est détaillé, ainsi que le contrôleur responsable du décodage en ligne de ces données. Plusieurs implémentations matérielles de l'algorithme de décodage du VBS sont présentées, permettant d'atteindre des fréquences de reconfiguration similaires à celles des FPGA commerciaux.

Finalement, une méthode permettant de définir une zone reconfigurable dynamique dans le chemin de configuration d'un FPGA est proposée, ce qui permet un

placement de tâches à l'exécution dont la flexibilité va au-delà de la définition de zones de reconfiguration partielle lors de la phase de conception. Ce mécanisme, associé à d'autres améliorations proposées dans cette thèse, facilite le développement d'une architecture FPGA reconfigurable dynamiquement et capable de charger des tâches matérielles à l'exécution à partir d'un flux de configuration indépendant de la position finale, sur une surface logique flexible.

La plupart des méthodes et techniques décrites dans cette thèse ont fait l'objet d'une implantation dans le contexte du projet Européen FP7 FlexTiles, qui a pour but le développement d'une architecture multi-cœurs hétérogène reconfigurable dynamiquement, et embarquant un FPGA embarqué (eFPGA) offrant des capacités de chargement dynamique de tâches matérielles.

# ABSTRACT

With the introduction of self-reconfiguration capabilities in Field-Programmable Gate Arrays (FPGA), new research topics have emerged around the dynamic placement of hardware modules at runtime. The commercially available architectures and tools evolved to provide mature partial reconfiguration flows which are nonetheless limited in functionality. The main objective of this PhD thesis is to propose new approaches for FPGAs to seamlessly handle the flexible runtime loading of hardware accelerators, both from the architecture level and from the tool-flow point of view.

The most advanced modern FPGA architectures features a profusion of different fixed-functions blocks aimed to provide the application with superior performance: Random-Access Memories (RAM), arithmetic accelerators, transceivers, etc. The diversity and heterogeneity of these blocks create more difficulties for placement algorithms by reducing the number of target positions for a given hardware task. In this thesis, an interconnect architecture enhancement is proposed to lessen those constraints on task placement. Experimental results using this system show an increase on the task placement flexibility at the cost of a delay overhead.

Secondly, the concept of position-independent Virtual Bit-Streams (VBS) is proposed to answer a key problem in task relocation mechanisms: the storage of only one task configuration in order to reduce memory and to increase the re-usability of generated hardware modules. Virtual Bit-Streams are built upon an abstract representation of the target FPGA logic and routing architecture, which makes them dissociated from their final position on the fabric. Thanks to the intrinsic format of the VBS, the resulting binary configuration data can be up to an order of magnitude smaller than their raw equivalent. Based on this concept, a accompanying Computer-Aided Design (CAD) tool-flow to generate VBS is demonstrated, as well as the online controller responsible for their online manipulation. Several possible implementations of the VBS decoding algorithm of this controller are presented, capable to attain a reconfiguration frequency comparable to commercial FPGAs.

Finally, a method to enclose a specific reconfiguration area in the configuration path of an FPGA is proposed, which enables the runtime placement of tasks beyond the definition of partially-reconfigurable regions at design time. This mechanism, associated with the other improvements offered in this thesis, facilitates the development of a dynamically reconfigurable FPGA architecture capable of loading hardware tasks at runtime from a position-independent configuration bit-stream,

onto a flexible logic fabric.

Most of the methods and techniques described in this thesis were put in use in the context of the European FP7 project *FlexTiles*, which aimed to propose a 3-D stack manycore architecture featuring an embedded FPGA (eFPGA) offering dynamic hardware task loading capabilities.

# Contents

| $\mathbf{R}$ | Remerciements |                                                                   |            |  |  |

|--------------|---------------|-------------------------------------------------------------------|------------|--|--|

| $\mathbf{R}$ | ésui          | mé                                                                | v          |  |  |

| $\mathbf{A}$ | bstr          | ract                                                              | vii        |  |  |

| 0            |               | Résumé étendu                                                     | 1          |  |  |

|              | 1             | Architectures reconfigurables                                     | 1          |  |  |

|              |               | 1.1 Des circuits programmables au matériel reconfigurable         | 1          |  |  |

|              |               | 1.2 Les FPGAs                                                     | 2          |  |  |

|              |               | 1.3 Tâches matérielles : configuration du FPGA                    | 4          |  |  |

|              | 2             | Tâches matérielles relogeables                                    | 5          |  |  |

|              |               | 2.1 Abstraction des données de routage                            | 6          |  |  |

|              |               | 2.2 Flot de conception amélioré                                   | 8          |  |  |

|              |               | 2.3 Intégration à l'architecture cible                            | 8          |  |  |

|              | 3             | Support matériel de l'hétérogénéité                               | 9          |  |  |

|              |               | 3.1 Relogement entre régions hétérogènes                          | 9          |  |  |

|              |               | 3.2 Architecture améliorée pour le relogement hétérogène          | 9          |  |  |

|              | 4             | Organisation mémoire améliorée pour la configuration partielle    | 11         |  |  |

|              | 5             | Le projet Européen FlexTiles                                      | 13         |  |  |

|              |               | 5.1 eFPGA et le support de la reconfiguration matérielle à l'éxe- |            |  |  |

|              |               | cution                                                            | 13         |  |  |

|              |               | 5.2 Simulation et validation de la surface reconfigurable         | 15         |  |  |

|              | 6             | Contributions                                                     | 15         |  |  |

|              | 7             | Conclusion                                                        | 16         |  |  |

| In           | tro           | duction                                                           | 19         |  |  |

|              | 1             | Context of the work                                               | 19         |  |  |

|              | 2             | Contributions                                                     | 20         |  |  |

|              | 3             | Organization of the document                                      | 21         |  |  |

| Ι            | $\mathbf{R}$  | ackground                                                         | 23         |  |  |

| 1            | ט             | acigi ouiid                                                       | <b>4</b> 0 |  |  |

| 1            |               | FPGA Architecture                                                 | 25         |  |  |

|              | 1             | (Re)configurable Hardware                                         | 26         |  |  |

|              |               | 1.1 Programmable Logic Devices                                    | 26         |  |  |

|              |               | 1.2 Reconfigurable devices                                        | 27         |  |  |

|   |   | 1.3   | Advent of Field-Programmable Gate Arrays                      | 27 |

|---|---|-------|---------------------------------------------------------------|----|

|   | 2 | Progr | amming technology                                             | 28 |

|   |   | 2.1   | Antifuse                                                      | 29 |

|   |   | 2.2   | Static memory                                                 | 30 |

|   |   | 2.3   | EEPROM / Flash                                                |    |

|   |   | 2.4   | Summary                                                       | 31 |

|   | 3 |       | array                                                         | 32 |

|   |   | 3.1   | Computing element                                             |    |

|   |   |       | 3.1-1 Logic blocks trade-offs                                 | 33 |

|   |   |       | 3.1-2 Look-up tables                                          | 34 |

|   |   |       | 3.1-3 Towards complex logic                                   | 35 |

|   |   | 3.2   | Memory                                                        | 38 |

|   |   | 3.3   | Arithmetic accelerators                                       |    |

|   |   | 3.4   | General purpose processors                                    | 39 |

|   |   | 3.5   | Summary                                                       | 40 |

|   | 4 | Routi | ng architecture                                               | 40 |

|   |   | 4.1   | Segmented routing                                             | 40 |

|   |   |       | 4.1-1 Interconnect depletion                                  | 41 |

|   |   |       | 4.1-2 Segmented routing                                       | 41 |

|   |   | 4.2   | Interconnect organization                                     | 42 |

|   |   |       | 4.2-1 Hierarchical architecture                               | 43 |

|   |   |       | 4.2-2 Island-style architecture                               | 44 |

|   |   | 4.3   | Routing structure                                             | 45 |

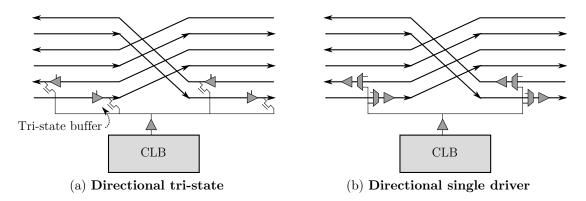

|   |   |       | 4.3-1 Bi-directional routing                                  | 45 |

|   |   |       | 4.3-2 Unidirectional routing                                  | 46 |

|   | 5 | Concl | usion                                                         | 47 |

|   |   |       |                                                               |    |

| 2 |   |       | ne Reconfiguration and Routing of FPGAs                       | 49 |

|   | 1 |       | me reconfiguration                                            | 51 |

|   |   | 1.1   | Reconfigurability of Field-Programmable Gate Arrays (FPGAs)   |    |

|   |   | 1.2   | Early work on runtime reconfiguration                         |    |

|   |   | 1.3   | Partial reconfiguration in modern devices                     | 52 |

|   | 2 |       | relocation/migration                                          | 53 |

|   |   | 2.1   | Vendor-supported partial reconfiguration                      | 53 |

|   |   | 2.2   | On hacks of modern devices                                    | 53 |

|   |   |       | 2.2-1 Relocation on homogeneous fabric                        | 53 |

|   |   | _     | 2.2-2 Handling heterogeneous architectures                    | 54 |

|   | 3 |       | time routing and communications                               | 57 |

|   |   | 3.1   | Bus macro                                                     | 57 |

|   |   | 3.2   | Configurable communication network                            | 58 |

|   |   | 3.3   | Bit-stream merging                                            | 58 |

|   |   | 3.4   | Just-in-time routing                                          | 58 |

|   |   | 3.5   | Conclusion                                                    | 59 |

|   | 4 |       | ment and routing for FPGAs                                    | 59 |

|   |   | 4.1   | High-level synthesis and non architecture-dependent optimiza- |    |

|   |   |       | tions                                                         | 60 |

|    |   | 4.2      | 11 0                                         | 61 |

|----|---|----------|----------------------------------------------|----|

|    |   | 4.3      |                                              | 61 |

|    |   | 4.4      | 9                                            | 62 |

|    |   |          | 0                                            | 63 |

|    |   |          | O                                            | 65 |

|    |   | 4.5      |                                              | 66 |

|    |   |          | 8                                            | 67 |

|    |   |          | 11                                           | 68 |

|    | 5 | Concli   | asion                                        | 69 |

| II |   | Contril  | outions 7                                    | 71 |

| 3  |   | Position | n-independent tasks: Virtual Bit-Streams     | 73 |

|    | 1 | Motiva   | ation for position-independent bit-streams   | 74 |

|    | 2 | Virtua   | l Bit-Stream concept                         | 75 |

|    |   | 2.1      | Interconnect abstraction                     | 75 |

|    |   | 2.2      | Route modeling                               | 79 |

|    |   | 2.3      | Coding the Virtual Bit-Stream                | 79 |

|    |   |          | 2.3-1 Metadata                               | 80 |

|    |   |          | 2.3-2 Macro-cells                            | 81 |

|    |   |          | 2.3-3 Overview                               | 83 |

|    | 3 | Cluste   | ring                                         | 84 |

|    | 4 | Virtua   | l Bit-Stream generation tools                | 85 |

|    |   | 4.1      | Design flow overview                         | 86 |

|    |   |          | 4.1-1 Outputs of the Verilog-To-Routing flow | 87 |

|    |   |          | 4.1-2 Virtual Bit-Stream generation          | 89 |

|    |   |          | 4.1-3 Decoding check                         | 90 |

|    |   | 4.2      |                                              | 90 |

|    |   |          |                                              | 91 |

|    |   |          | 4.2-2 Model array                            | 92 |

|    |   |          |                                              | 93 |

|    | 5 | A Virt   | cual Bit-Stream powered architecture         | 94 |

|    |   | 5.1      | <del>-</del>                                 | 96 |

|    |   |          | ~                                            | 96 |

|    |   |          | 5.1-2 De-virtualizer                         | 97 |

|    |   |          |                                              | 97 |

|    | 6 | Limita   | 9 11                                         | 98 |

| 4  |   |          | 8                                            | 99 |

|    | 1 |          |                                              | 00 |

|    |   | 1.1      | Organization of the de-virtualizer           |    |

|    |   | 1.2      | Real-time considerations                     |    |

|    | 2 |          | 0 0                                          | 01 |

|    |   | 2.1      | LUT-based decoder                            |    |

|    |   | 2.2      | State-machine decoder                        |    |

|    |   | 2.3      | Comparison                                   | 06 |

|   |   | 2.4    | Implementation results                                   | 106 |

|---|---|--------|----------------------------------------------------------|-----|

|   | 3 | Comr   | pression effect of the Virtual Bit-Stream                |     |

|   |   | 3.1    | Experimental methodology                                 |     |

|   |   | 3.2    | Results                                                  |     |

|   |   | 3.3    | On the effect of clustering                              |     |

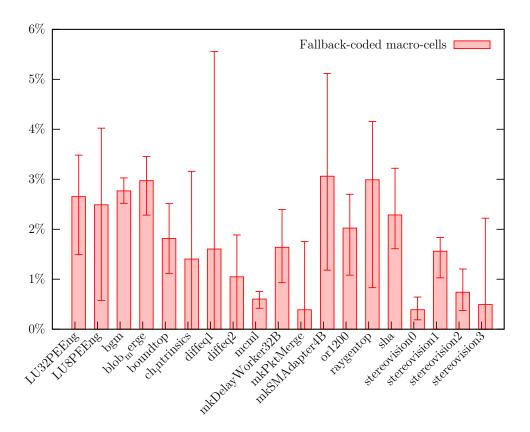

|   |   | 3.4    | Fallback coding: to the limits of the Virtual Bit-Stream |     |

|   |   | 0.2    | 3.4-1 Analysis of the decoding failures                  |     |

|   |   |        | 3.4-2 Experimental results                               |     |

|   | 4 | Concl  | lusion                                                   |     |

| 5 |   | Archit | tecture Enhancements                                     | 117 |

|   | 1 | Task   | migration with heterogeneous blocks                      | 118 |

|   |   | 1.1    | Hard blocks abstraction                                  |     |

|   |   |        | 1.1-1 Routing network separation                         |     |

|   |   | 1.2    | Partitioning                                             |     |

|   |   | 1.3    | Task model                                               |     |

|   | 2 | Exper  | rimental methodology                                     |     |

|   |   | 2.1    | Modeling in VPR                                          |     |

|   |   |        | 2.1-1 Architecture                                       |     |

|   |   |        | 2.1-2 Routing abstraction                                |     |

|   |   | 2.2    | Benchmarks                                               |     |

|   | 3 | Resul  | lts                                                      | 125 |

|   |   | 3.1    | Logic array size                                         |     |

|   |   | 3.2    | Critical delay                                           |     |

|   |   | 3.3    | Routing resources                                        |     |

|   |   |        | 3.3-1 Effect of the enhanced routing architecture        |     |

|   |   |        | 3.3-2 Limitations of the enhanced model within VPR       |     |

|   | 4 | Concl  | lusion                                                   |     |

| 6 |   | Enhan  | ncing the Virtual Bit-Stream Architecture                | 131 |

|   | 1 | Intro  | 9                                                        | 132 |

|   |   | 1.1    | Bit-stream loading methods                               | 132 |

|   |   |        | 1.1-1 Word addressing                                    |     |

|   |   |        | 1.1-2 Scan-path: serial loading                          | 133 |

|   |   |        | 1.1-3 Hybrid loading                                     |     |

|   |   | 1.2    | Multi context configuration memory                       | 136 |

|   |   | 1.3    | Summary of memory organizations                          |     |

|   | 2 | Enha   | anced scan-path                                          |     |

|   |   | 2.1    | Organization of the configuration memory                 | 139 |

|   |   |        | 2.1-1 Configuration routing element                      | 140 |

|   |   |        | 2.1-2 Configuration path                                 |     |

|   |   | 2.2    | Runtime dynamic partitioning                             |     |

|   |   |        | 2.2-1 Configuring the configuration path                 |     |

|   |   |        | 2.2-2 Overhead and delay considerations                  |     |

|   |   | 2.3    | Results                                                  |     |

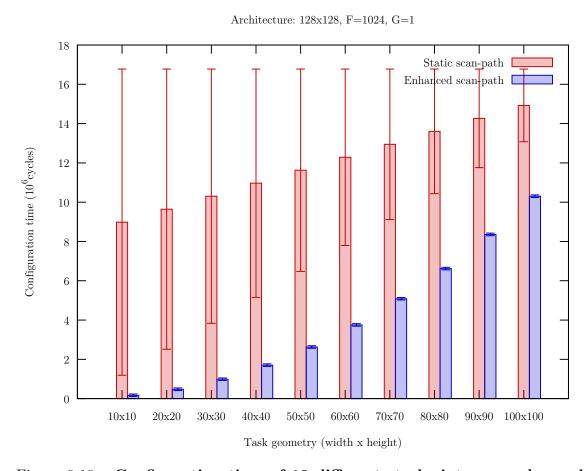

|   |   |        | 2.3-1 Configuration time                                 | 144 |

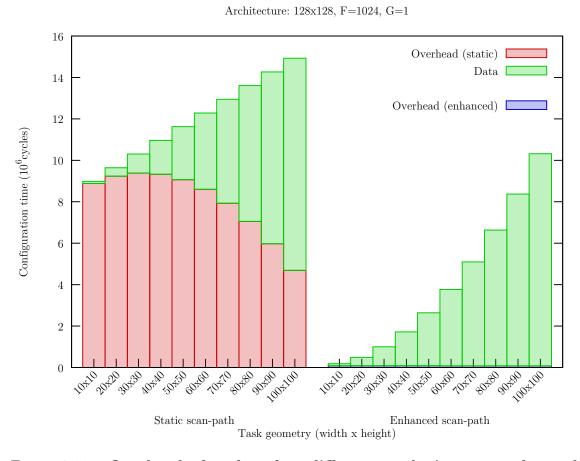

|          |               | 2.3-2 Padding data overhead                         | 146   |

|----------|---------------|-----------------------------------------------------|-------|

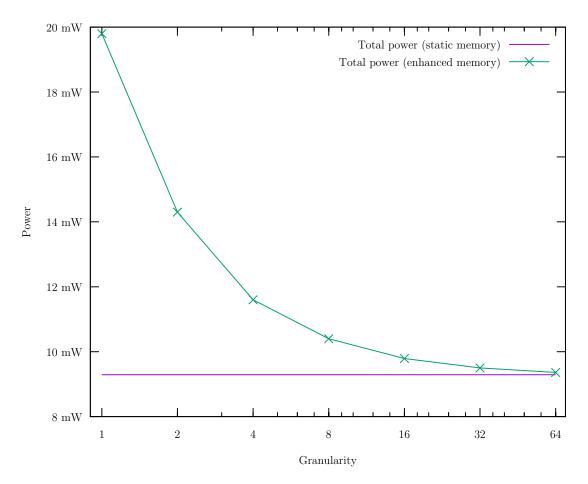

|          |               | 2.3-3 Energy consumption                            | 147   |

|          | 3             | Conclusion                                          | 148   |

| 7        |               | The FlexTiles platform                              | 151   |

|          | 1             | Overview of the FlexTiles project                   | 152   |

|          |               | 1.1 Global architecture                             |       |

|          |               | 1.2 Programming model                               |       |

|          |               | 1.3 Virtualization layer                            |       |

|          | 2             | Embedded FPGA accelerators                          | 154   |

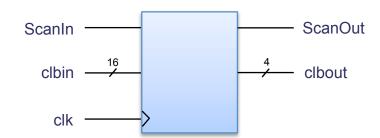

|          |               | 2.1 Overview of the embedded FPGA                   | 154   |

|          |               | 2.2 eFPGA architecture                              | 155   |

|          |               | 2.3 Hardware tasks                                  | 156   |

|          | 3             | Implementation of a dynamically reconfigurable FPGA | 157   |

|          |               | 3.1 RTL model                                       | 157   |

|          |               | 3.1-1 Generation of the RTL model                   | 157   |

|          |               | 3.2 eFPGA testbench                                 | 158   |

|          |               | 3.2-1 Testbench implementation                      | 159   |

|          |               | 3.2-2 User interaction                              | 160   |

|          | 4             | Conclusion                                          | 160   |

| C        | onc           | lusion and Perspectives                             | 163   |

|          | 1             | Overview                                            |       |

|          | 2             | Perspectives                                        |       |

|          |               | •                                                   |       |

| II       | Ι             | Appendices                                          | 169   |

| <b>A</b> |               | Handman and Gastians of the aEDCA                   | 1 7 1 |

| A        | 1             | Hardware specifications of the eFPGA                | 171   |

|          | $\frac{1}{2}$ | Logic macro-cell                                    |       |

|          | 2             | Logic blocks                                        |       |

|          |               | 2.1 Complex Logic Block                             |       |

|          |               |                                                     |       |

|          |               | 2.3 Memory block                                    |       |

|          | 9             |                                                     |       |

|          | 3             | Logic fabric organization                           |       |

|          |               | 3.1 Synthesis results                               |       |

|          |               | 3.2 I roposed organization                          | 100   |

| В        | _             | Simulation of the eFPGA reconfiguration controller  | 183   |

|          | 1             | Task synthesis and bit-stream generation            |       |

|          | 2             | Model configuration and shell connection            |       |

|          | 3             | Adder loading                                       |       |

|          | 4             | Adder test                                          |       |

|          | 5             | Multiplier loading                                  |       |

|          | 6             | Multiplier test                                     | 188   |

## CONTENTS

| Publications    | 191 |

|-----------------|-----|

| Bibliography    | 193 |

| List of Figures | 203 |

| List of Tables  | 206 |

| Acronyms        | 207 |

# CHAPITRE ZÉRO

# RÉSUMÉ ÉTENDU

| Contents |                                                                     |  |

|----------|---------------------------------------------------------------------|--|

| 1        | Architectures reconfigurables                                       |  |

|          | 1.1 Des circuits programmables au matériel reconfigurable . 1       |  |

|          | 1.2 Les FPGAs                                                       |  |

|          | 1.3 Tâches matérielles : configuration du FPGA 4                    |  |

| 2        | Tâches matérielles relogeables                                      |  |

|          | 2.1 Abstraction des données de routage 6                            |  |

|          | 2.2 Flot de conception amélioré 8                                   |  |

|          | 2.3 Intégration à l'architecture cible 8                            |  |

| 3        | Support matériel de l'hétérogénéité                                 |  |

|          | 3.1 Relogement entre régions hétérogènes 9                          |  |

|          | 3.2 Architecture améliorée pour le relogement hétérogène 9          |  |

| 4        | Organisation mémoire améliorée pour la configuration partielle . 11 |  |

| 5        | Le projet Européen FlexTiles                                        |  |

|          | 5.1 eFPGA et le support de la reconfiguration matérielle à          |  |

|          | l'éxecution                                                         |  |

|          | 5.2 Simulation et validation de la surface reconfigurable 15        |  |

| 6        | Contributions                                                       |  |

| 7        | Conclusion                                                          |  |

#### 1 ARCHITECTURES RECONFIGURABLES

## 1.1 DES CIRCUITS PROGRAMMABLES AU MATÉRIEL RECONFI-GURABLE

Les architectures configurables font partie intégrante du paysage des circuits intégrés depuis la fin des années 1970 avec l'émergence de composants logiques programmables (PLDs) comme les PALs (*Programmable Array Logic*) et les GALs (*Generic Array Logic*). Ces composants proposent, à l'origine, des capacités de configuration plutôt primitives si on les compare à des puces modernes : ils sont constitués de portes logiques de base (NON, ET, OU) qui sont connectées électriquement via une phase de programmation pour réaliser la tâche désirée par le concepteur.

Si l'on n'évoque alors pas encore le terme d'architecture reconfigurable à proprement parler, c'est parce que l'opération de programmation de ces composants n'était à leur début possible qu'une seule fois : on parle alors de circuit One-Time Programmable (OTP). La révolution apportée par les circuits effaçables par rayons ultraviolets (UVPROM), puis électriquement effaçables et programmables (EEPROM) a permis l'essor des composants reconfigurables, dont la fonction pouvait être changée à volonté, in situ.

L'évolution des technologies des circuits intégrés a par la suite permis aux constructeurs de proposer des composants beaucoup plus complexes, reposants non pas sur des éléments logiques fixes dont on programme l'interconnexion, mais sur des éléments logiques configurables à plus gros grain placés sur un réseau de routage : ce sont les composants logiques programmables complexes (CPLDs). Les CPLDs sont composés de macrocellules qui peuvent elles-mêmes être assimilées aux GALs cités précédemment. Un circuit typique peut contenir jusqu'à 10 000 de ces macrocellules, ouvrant la voie à des applications beaucoup plus complexes.

#### 1.2 LES FPGAS

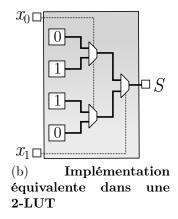

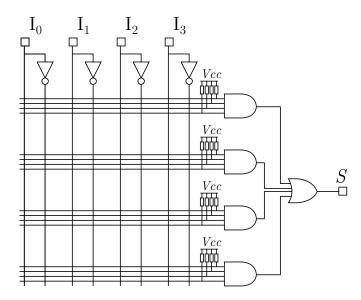

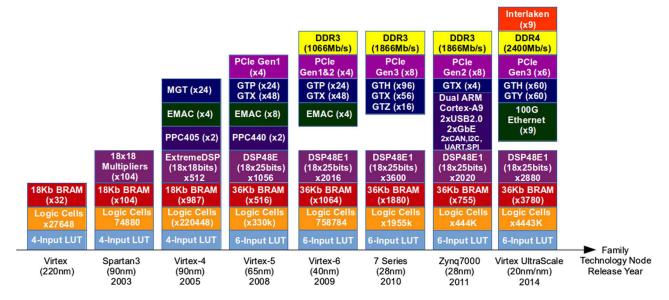

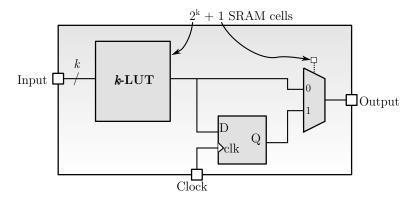

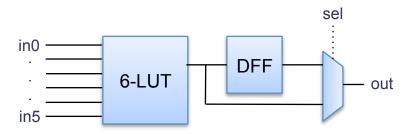

Xilinx a commercialisé ses premiers Field- $Programmable\ Gate\ Arrays\ (FPGAs)$  en 1985, ils sont alors similaires par leur structure aux CPLDs mais leur composition interne en font rapidement des circuits de premier choix. En particulier, l'utilisation de cellules mémoires volatiles à base de RAM statique (SRAM) leur a permis de réduire la surface occupée par les éléments configurables (les transistors à grille flottante utilisés pour une cellule EEPROM occupant plus de surface qu'une cellule SRAM), et donc d'obtenir une meilleure intégration. La cellule logique à la base d'une architecture FPGA permet aussi une configuration plus fine de la fonction désirée, au travers de l'utilisation d'une table de correspondance à k entrées (k-LUT).

|   | $x_0$ | $x_1$  | $\mid S \mid$ |

|---|-------|--------|---------------|

|   | 0     | 0      | 0             |

|   | 0     | 1      | 1             |

|   | 1     | 0      | 1             |

|   | 1     | 1      | 0             |

| ( | a) Ta | ble d  | e vé-         |

| r | ité d | l'un i | XOR           |

| à | deu   | x ent  | rées          |

|   |       |        |               |

FIGURE 0-1 – Implémentation d'une fonction logique à deux entrées dans la table de vérité d'un FPGA.  $S = x_0 \oplus x_1$ .

Une k-LUT permet de réaliser n'importe quelle fonction logique à k entrées, comme illustré dans la Figure 0-1 avec une fonction XOR. Cette cellule logique a

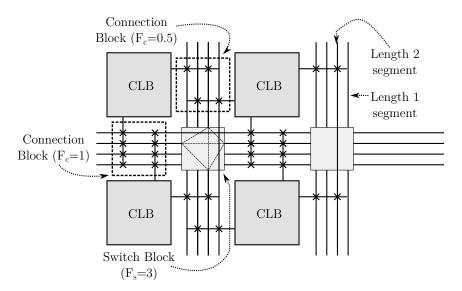

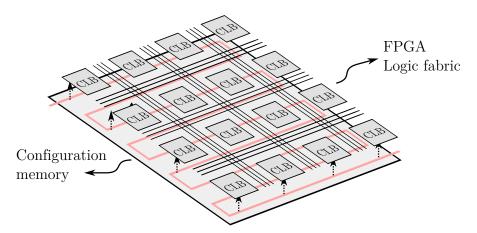

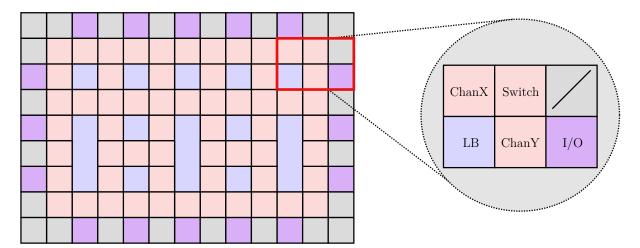

FIGURE 0-2 – Représentation schématique du réseau de routage d'un FPGA.

évolué au fil du temps, les FPGAs prenant au fur et à mesure une place prépondérante dans l'univers des circuits logiques programmables. Pendant longtemps en effet, l'implémentation d'un algorithme complexe se voyait limitée à deux extrêmes. D'une part, l'implémentation logicielle de l'application permettant une grande flexibilité mais contrainte par un processeur énergivore. D'autre part, une implantation matérielle sur un circuit intégré spécifique (ASIC), avec une consommation plus maîtrisée et une optimisation spatiale de l'application offrant des performances supérieures, mais dont le coût est élevé et la fonctionnalité est figée. Les alternatives aux processeurs et aux ASICs (par. ex. les Mask-Programmable Gate Array (MPGA)) ne permettant pas alors de gros gains financiers et/ou de performances sur des petites séries. Les FPGAs sont venus offrir une alternative fiable permettant une grande flexibilité et des performances nettement supérieures à des implémentations logicielles.

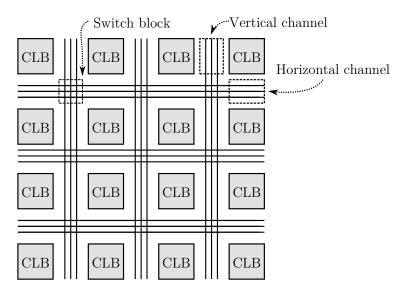

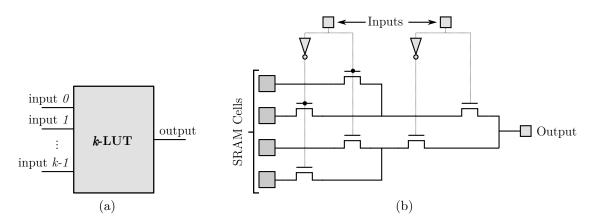

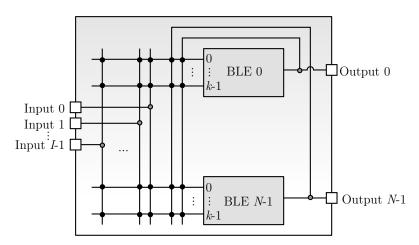

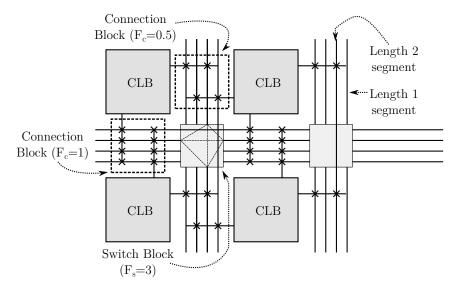

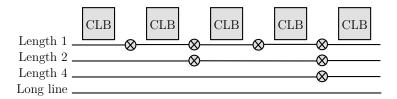

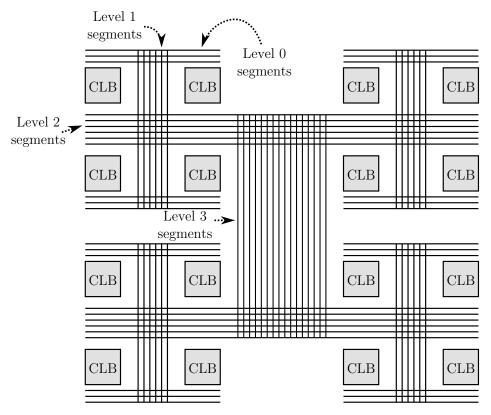

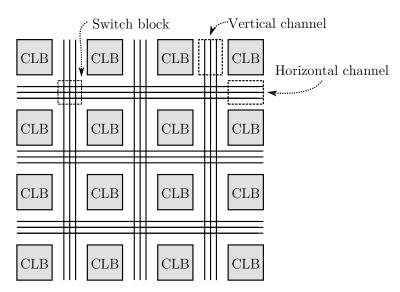

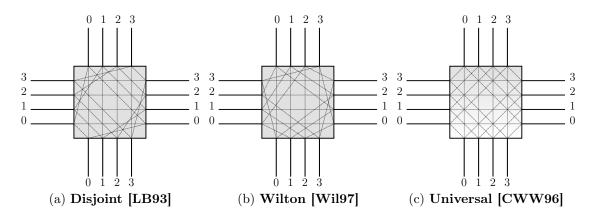

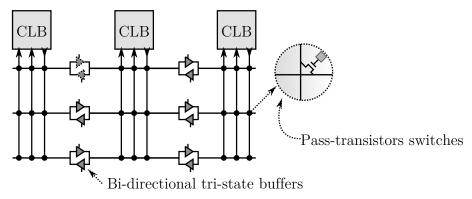

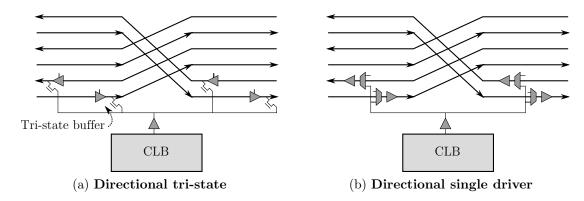

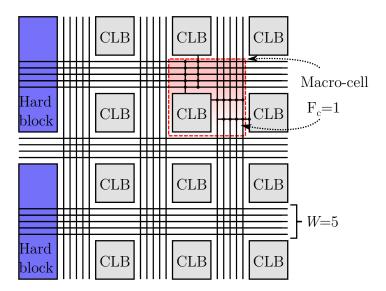

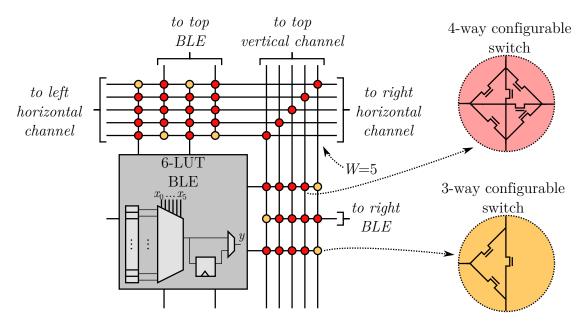

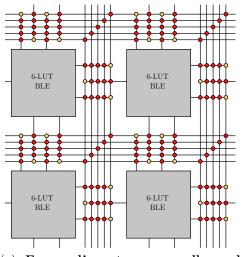

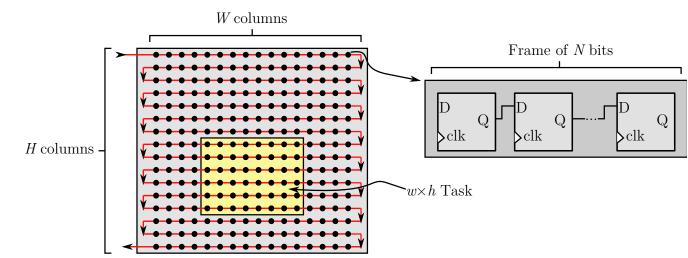

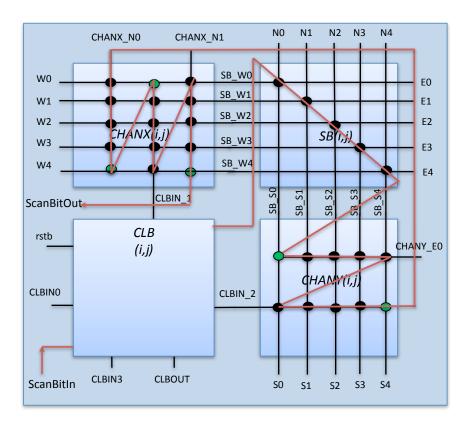

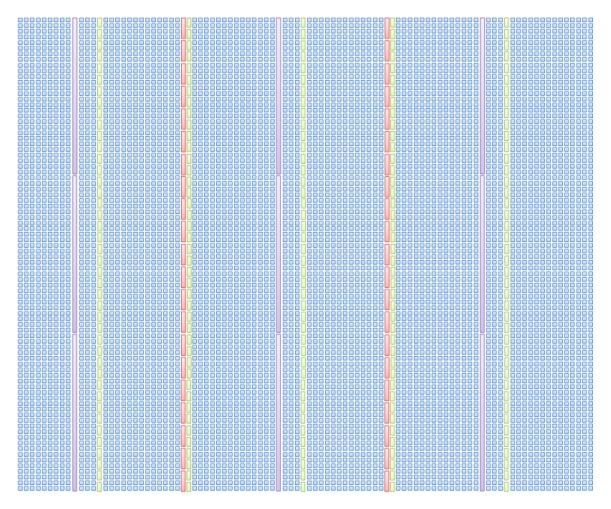

L'architecture des FPGAs a beaucoup évolué au fil des générations de ces circuits, tant au niveau des fonctionnalités logiques que de leur réseau d'interconnexion. La Figure 0-2 illustre ce réseau d'interconnexion complexe. Il se compose de canaux de routage horizontaux et verticaux contenant W segments, ces canaux étant interconnectés entre eux par des switch boxes. La connexion entre les éléments logiques et les canaux de routage se fait au travers de connection boxes. Un facteur  $F_c$  détermine le nombre de segments auxquels sont connectés les entrées/sorties des éléments logiques. De même, un facteur  $F_s$  conditionne le nombre de segments atteignables par un segment donné dans une switch box, souvent égal à 3 dans les topologies modernes. Le réseau d'interconnexion lui-même peut être organisé de manière variable, les plus populaires étant les organisations hiérarchiques et en îlots. L'organisation en îlots est l'organisation intuitive du réseau de routage, où les canaux horizontaux et verticaux entourent les éléments logiques de manière régulière et homogène, comme décrit dans la Figure 0-3.

FIGURE 0-3 - Organisation en îlots du réseau d'interconnexion du FPGA.

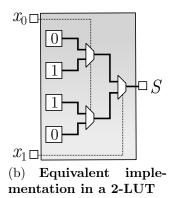

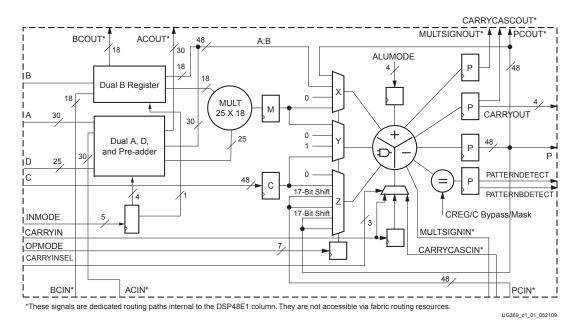

Les éléments logiques du circuit ont eux aussi évolué. Si les premiers FPGAs ne contenaient que des LUTs, les architectures actuelles comportent un nombre croissant d'éléments hétérogènes. Ces éléments comprennent notamment des mémoires de plusieurs mégabits qui visent à remplacer l'utilisation des LUTs comme mémoires distribuées et à fournir des espaces de stockage dynamiques en lecture et en écriture. Des accélérateurs arithmétiques sont désormais aussi inclus dans les surfaces logiques des FPGAs : ils viennent optimiser l'implantation de chemins de données complexes en intégrant des opérateurs comme des multiplieurs ou des additionneurs/soustracteurs. Chaque nouvelle fonctionnalité implémentée comme un bloc hétérogène vient augmenter les capacités du circuit en réduisant le nombre d'éléments logiques purs utilisés pour réaliser un algorithme donné, ce qui augmente de la même manière les performances de l'application implantée.

#### 1.3 Tâches matérielles : configuration du FPGA

Les FPGAs, forts de leur matrice de configuration SRAM, ont toujours profité d'une capacité de reconfiguration depuis leur création. Cette reconfiguration s'entend en revanche au sens du changement de la fonctionnalité du circuit entier au travers du chargement d'un nouveau flux de configuration (bit-stream) complet pour l'ensemble du circuit.

Dans le cadre d'applications dynamiques, et afin d'optimiser l'utilisation des ressources logiques du composant, il peut être préférable de configurer des parties du FPGA, indépendamment du fonctionnement du reste du circuit. Cette technique de reconfiguration partielle a été explorée dès les débuts des FPGAs, et notamment sur le XC6200 de Xilinx, afin d'offrir des paradigmes proches du monde logiciel. Une application logicielle peut en effet être stockée dans un média de masse jusqu'à ce que son chargement soit demandé par l'utilisateur ou le système, auquel cas le système d'exploitation s'occupe de la réservation d'un espace mémoire pour charger le code de

l'application et de la faire exécuter par le processeur. Il est difficile d'appliquer cette même flexibilité dans un composant matériel reconfigurable comme un FPGA, en partie à cause l'hétérogénéité des éléments logiques, et surtout parce que les chaînes de développement actuelles ne permettent que la création d'un flux de configuration pour une position donnée dans le FPGA.

Les contraintes actuelles des flots de développement fournis par les constructeurs obligent à définir, au moment de la conception de l'application, des zones de reconfiguration partielles prédéfinies (PRRs)  $\{PRR_1, PRR_2, \dots PRR_N\}$  puis des ensembles de flux de configuration partiels pour chacune de ces zones. Un flux de configuration  $BS_k$  destiné à une zone de reconfiguration  $PRR_k$  ne peut en aucun cas être chargé sur une autre zone reconfigurable. Le concept de tâche matérielle reste donc cantonné à la définition d'un flux de configuration associé à une zone définie. La seule possibilité de placer un flux de configuration  $BS_k$  sur plusieurs zones  $\{PRR_1, PRR_2, \dots PRR_N\}$  différentes est de générer autant de flux de configuration  $\{BS_{k1}, BS_{k1}, \dots BS_{kN}\}$  que nécessaire, ce qui d'une part limite la flexibilité de l'application lors de son utilisation en ligne, et d'autre part requiert une grande quantité de mémoire pour stocker ces configurations.

Différents travaux de l'état de l'art se sont confrontés au problème de définir une tâche matérielle par un seul flux de configuration qui se voit placé à des positions différentes au moment de son chargement. La plupart s'intéressent à des architectures existantes, notamment par le biais de modules de réécriture à la volée du flux de configuration pour l'adapter à des zones reconfigurables différentes, en imposant une contrainte sur l'utilisation seule d'éléments logiques purs. Le placement dynamique de tâches matérielles ayant recours à des éléments hétérogènes a été relativement peu étudié. La composition intrinsèque du flux de configuration des FPGAs du commerce n'étant pas connue, les techniques de réécriture doivent se limiter à la modification des éléments connus de la configuration : des champs indicateurs de la colonne cible du flux de configuration ou à la vérification de sa validité (CRC).

## 2 TÂCHES MATÉRIELLES RELOGEABLES

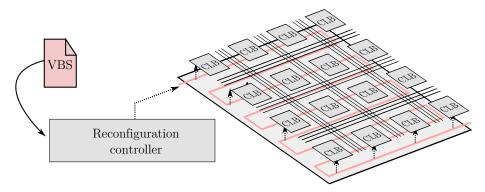

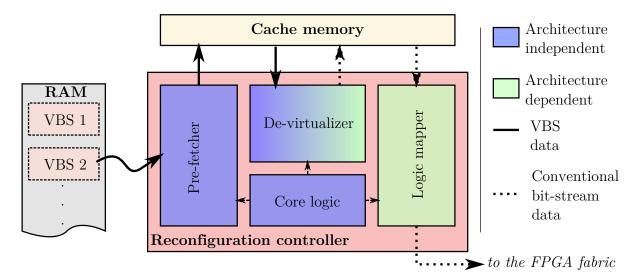

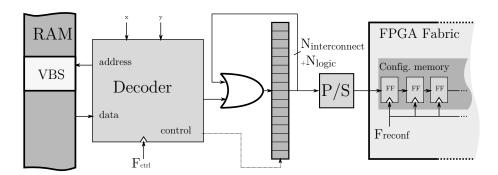

Dans cette thèse, une représentation alternative des données du flux de configuration est explorée afin de rendre les données de configuration d'une tâche matérielle indépendantes de leur placement final sur l'architecture reconfigurable. Ces Virtual Bit-Streams (VBS) reposent sur une description abstraite des données d'interconnexion contenues dans le flux de configuration. Cette description est finalisée au moment de la décision de placer la tâche à une position (x,y) par un contrôleur de reconfiguration faisant l'interface entre les Virtual Bit-Streams et la mémoire de configuration de l'architecture reconfigurable.

(b) Abstraction Virtual Bit-Stream correspondante

| De             | À      |

|----------------|--------|

| WC1            | EC1    |

| WC0            | SL1    |

| WL0            | EC2    |

| SC2            | WL0    |

| (c) <b>Lis</b> | te des |

| connexio       | ns     |

FIGURE 0-4 – L'abstraction du *Virtual Bit-Stream*, de l'architecture à la liste de connexions.

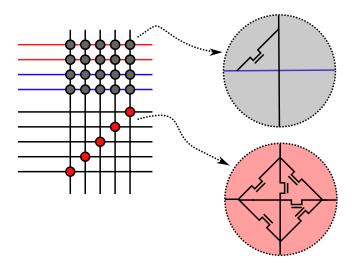

#### 2.1 Abstraction des données de routage

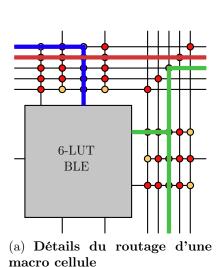

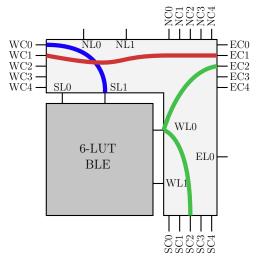

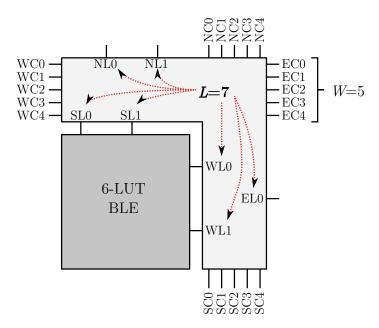

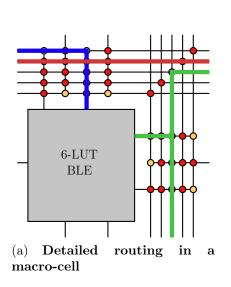

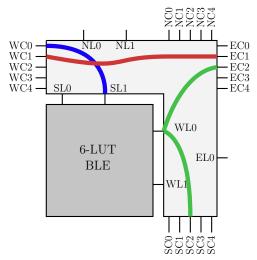

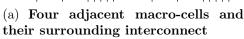

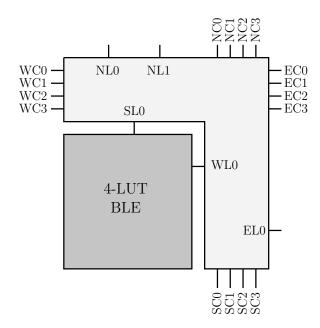

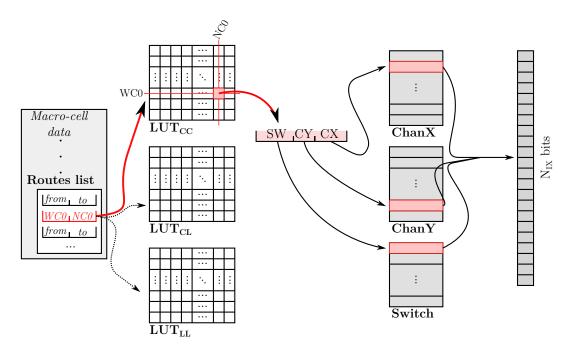

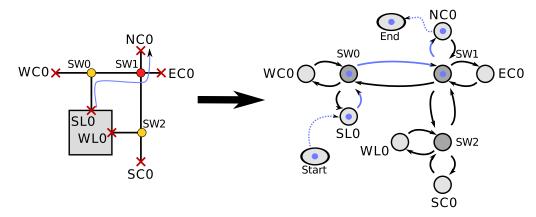

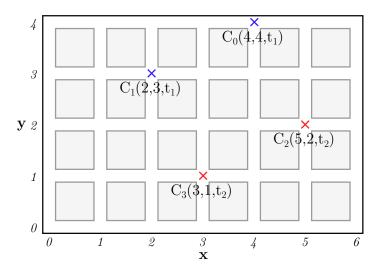

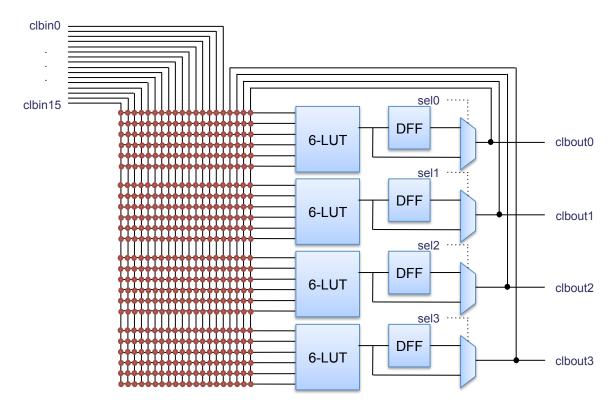

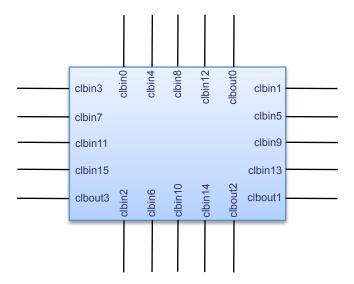

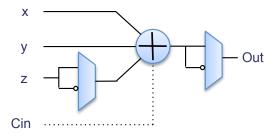

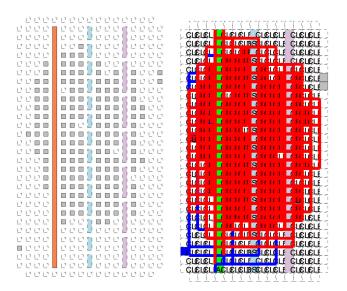

L'abstraction du flux de configuration des détails de l'architecture cible est effectuée au niveau d'une macro cellule, l'élément répétable de la surface logique. Cette macrocellule se compose d'un élément logique de l'architecture ainsi que des canaux de routage et  $switch\ box$  adjacents, comme illustré dans la Figure 0-4a. Chacun des éléments de la macrocellule nécessite plusieurs bits de configuration. La majeure partie du volume de données de configuration est occupée par le réseau d'interconnexion de la macrocellule. L'exemple de la Figure 0-4 présente une macrocellule contenant W=5 canaux de routage, et L=7 connexions à l'élément logique local, qui est représenté ici par une seule 6-LUT.

En utilisant un modèle abstrait des macrocellules d'une architecture, tel que celui présenté dans la Figure 0-4b, les données de configuration du réseau d'interconnexion ne sont plus représentées par une liste d'états des éléments de routage du réseau mais par une liste des connexions point-à-point réalisées dans le réseau d'interconnexion local de la macrocellule. L'exemple donné dans le Tableau 0-4c correspond à la liste des connexions réalisées dans la Figure 0-4a, en utilisant la nomenclature des

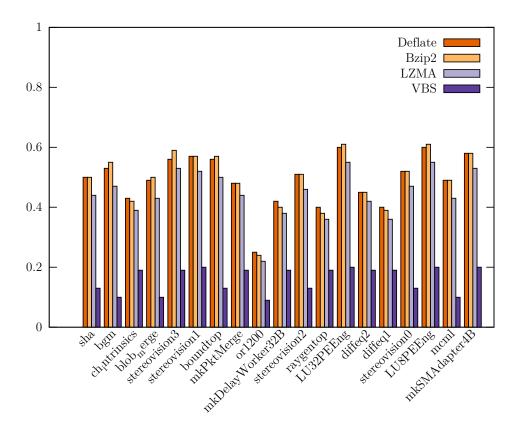

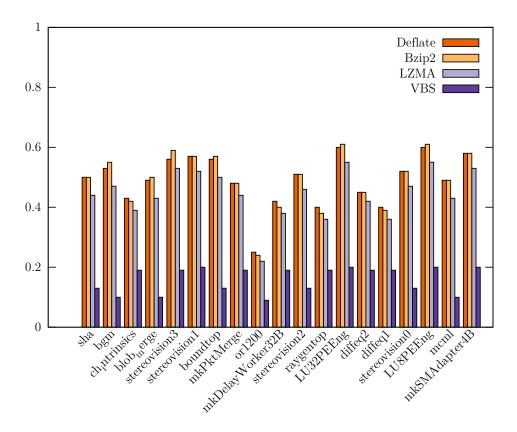

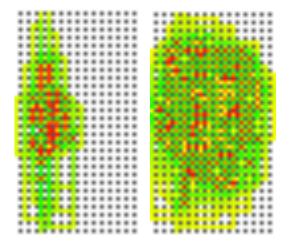

FIGURE 0-5 – Ratio de compression normalisé à la taille du flux de configuration brut des compresseurs Deflate, Bzip2 et LZMA, comparés au format de représentation *Virtual Bit-Stream*..

entrées/sorties du modèle abstrait de la Figure 0-4b.

Cette abstraction a deux conséquences. Premièrement, puisque les données de routage ainsi décrites ne sont pas dépendantes du réseau d'interconnexion sous-jacent, elles peuvent être finalisées pour des positions différentes de l'architecture qui ne possèdent pas exactement la même organisation des ressources. Deuxièmement, cette méthode de représentation permet aussi de décrire les données de routage de manière compressée par rapport à une représentation brute. En effet, des taux de compression pouvant atteindre  $11\times$  ont été observés lors des tests de cette méthode de représentation, comme illustré par la Figure 0-5.

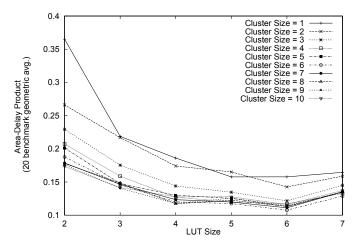

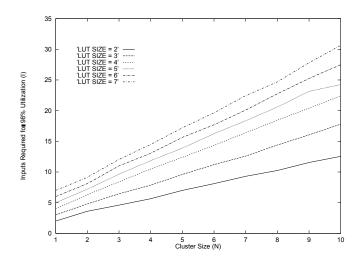

Une exploration du grain d'abstraction de la réprésentation Virtual Bit-Stream a par ailleurs été menée, afin de déterminer les bénéfices du codage des routes de plusieurs macrocellules combinées en une grappe, plutôt que d'une seule à la fois. Les résultats, résumés dans le Tableau 0-1, présentent un effet bénéfique des petites tailles de grappe sur notre jeu d'applications de référence, qui est à rapprocher des tailles moyennes des routes des tâches placées et routées.

Table 0-1 – Effet du regroupement des macrocellules sur la taille du  $Virtual\ Bit-Stream$

| Taille de grappe | Min. [kbits] | Max. [kbits] | Moye | enne [kbits]   |

|------------------|--------------|--------------|------|----------------|

| 1                | 2            | 906          | 128  | $(6.31\times)$ |

| 2                | 3            | 847          | 120  | $(6.47\times)$ |

| 3                | 4            | 831          | 120  | $(6.42\times)$ |

| 4                | 3            | 858          | 122  | $(6.26\times)$ |

| 5                | 4            | 816          | 121  | $(5.89\times)$ |

| 6                | 6            | 829          | 124  | $(5.89\times)$ |

#### 2.2 FLOT DE CONCEPTION AMÉLIORÉ

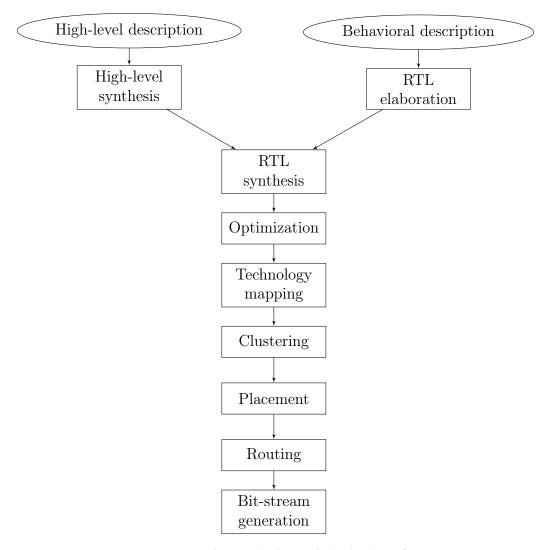

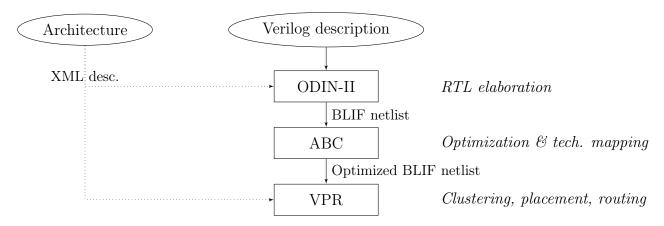

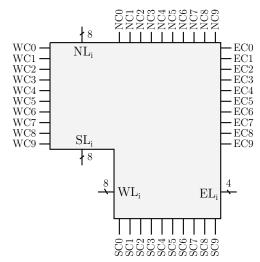

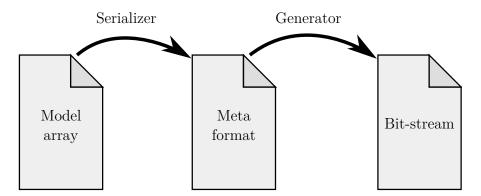

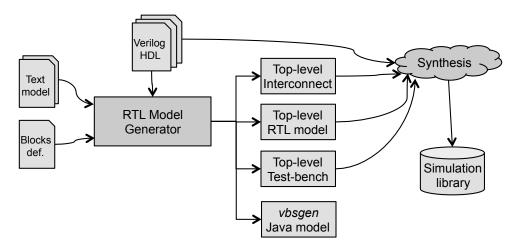

L'implémentation et la validation de la méthode de représentation Virtual Bit-Stream a été effectuée par le biais du développement d'un flot de conception amélioré, basé sur le flot Verilog-To-Routing (VTR). Ce flot open-source réalise les opérations classiques d'un flot de développement FPGA, de l'élaboration de la description matérielle Verilog en entrée, jusqu'au placement-routage final de l'application sur une architecture virtuelle. Cette architecture, modélisée au moyen d'un balisage XML propre au flot VTR, est caractérisée par un ensemble d'éléments logiques répartis sur une grille et interconnectés par un réseau de routage, lui aussi défini par le concepteur.

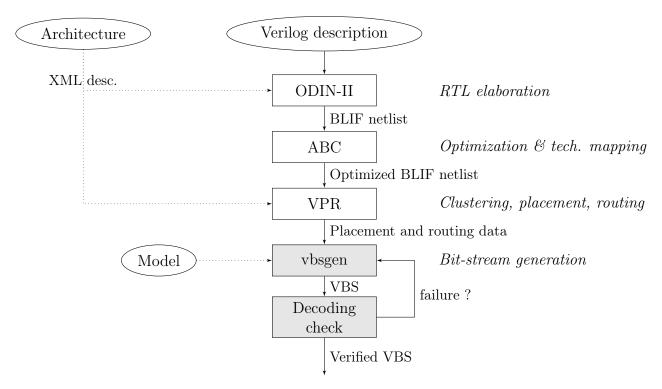

L'outil développé dans le cadre de cette thèse, vbsgen, est à la fois une structure logicielle permettant de décrire l'architecture cible avec plus de détails que celle proposée par VTR, et aussi un outil de création des Virtual Bit-Stream dédiés à cette architecture. Un modèle objet est fourni pour représenter divers éléments classiques d'une architecture FPGA afin de faciliter la création de nouvelles architectures. Ce modèle contient notamment des éléments supplémentaires non pris en compte dans le flot VTR, en particulier des informations sur la structure de la mémoire de configuration de l'architecture, sa composition et sa méthode de programmation.

L'ensemble du flot se compose du flot VTR générant des informations de placement-routage à partir d'une description matérielle Verilog de l'application et d'une description de l'architecture, puis de l'outil *vbsgen* qui ré-utilise les données de placement-routage pour les intégrer au modèle d'architecture considérée, afin de générer à la fois des flux de configuration bruts et des *Virtual Bit-Streams*.

#### 2.3 Intégration à l'architecture cible

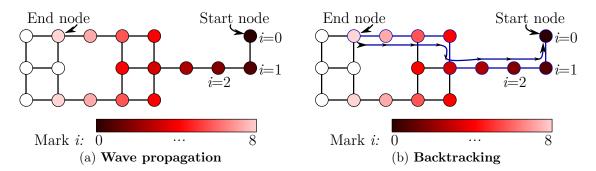

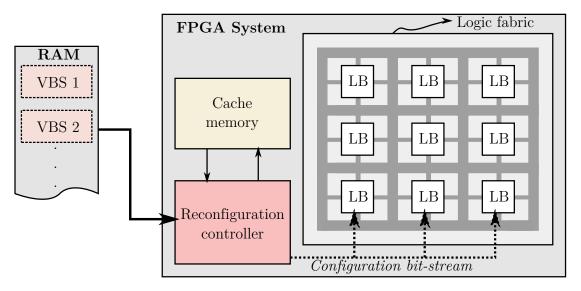

La méthode de représentation *Virtual Bit-Stream*, couplée à un flot de développement complet utilisant l'outil *vbsgen*, autorise la création de tâches matérielles, sous la forme de fichiers *Virtual Bit-Stream*. Ces données doivent être décodées en ligne, au moment du placement final de la tâche matérielle. Afin de respecter les contraintes temporelles inhérentes à l'implantation matérielle d'un contrôleur décodant les *Vir*-

tual Bit-Stream en flux de configuration bruts compatibles avec l'architecture cible, deux algorithmes spécifiques ont été mis au point.

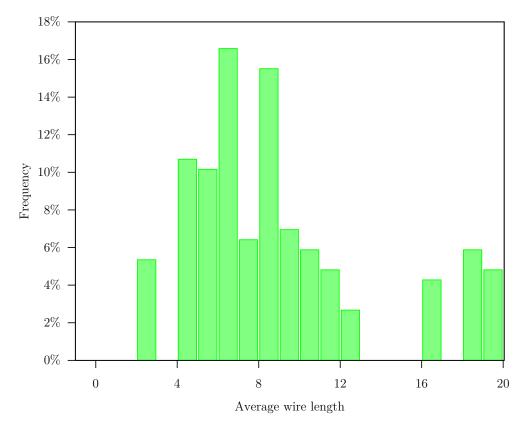

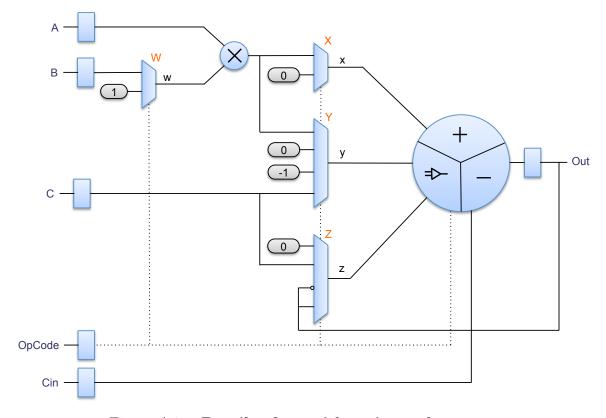

Un premier algorithme se base sur une table de correspondance pour décoder les différentes routes listées pour chaque macrocellule. Le second utilise une machine d'état spécifique à l'architecture du réseau de routage des macrocellules ciblées afin de fournir progressivement l'état de chaque élément de routage pour une route donnée. Les deux algorithmes ont des objectifs différents. Le premier, plus rapide, permet de décoder la représentation abstraite de macrocellules de taille raisonnables compte tenu de l'empreinte mémoire de la table de correspondance. Le second permet l'évolution vers des tailles beaucoup plus conséquentes de macrocellules, au prix d'une dépendance de ses performances à la longueur moyenne des routes de l'application.

Dans les deux cas, la complexité des algorithmes permet d'atteindre une contrainte de génération du flux de configuration de 1600Mbps, suffisante pour être transparents au regard des technologies de reconfiguration actuellement implantées dans les FPGA récents.

### 3 SUPPORT MATÉRIEL DE L'HÉTÉROGÉNÉITÉ

#### 3.1 Relogement entre régions hétérogènes

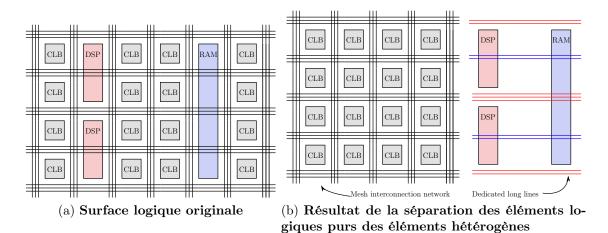

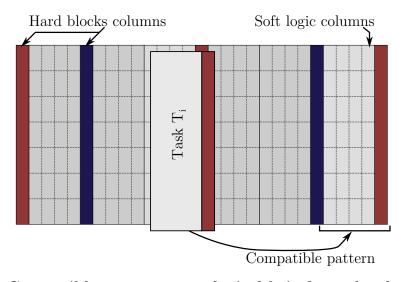

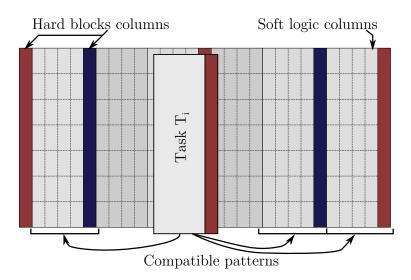

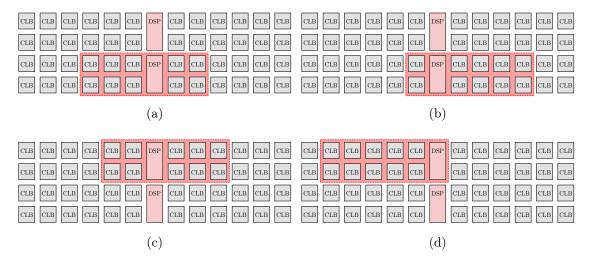

Les architectures FPGA en îlots organisent les éléments hétérogènes comme les mémoires et les accélérateurs arithmétiques en colonnes afin d'en simplifier l'agencement et de faciliter la combinaison de plusieurs blocs en une seule ressource fonctionnelle. L'allocation de ces blocs hétérogènes répartis sur la surface logique de l'architecture FPGA complique le relogement de tâches. Une tâche matérielle placée à une position donnée sera difficilement relogeable à une autre position de la surface logique puisqu'il faudra trouver une région disposant du même jeu de ressources que la région originale. Les ressources de la région cible doivent en outre être placée à une position identique à celle de la région originale, sans quoi un flux de configuration équivalent entre les deux zones ne pourra être trouvé qu'au prix d'un nouveau routage complet.

## 3.2 ARCHITECTURE AMÉLIORÉE POUR LE RELOGEMENT HÉ-TÉROGÈNE

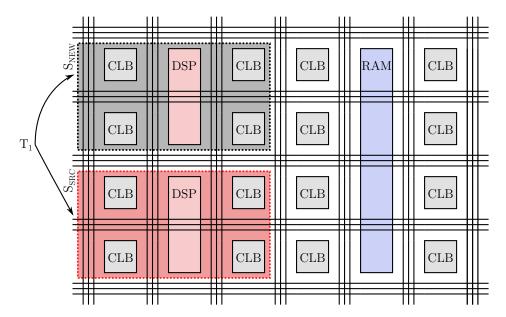

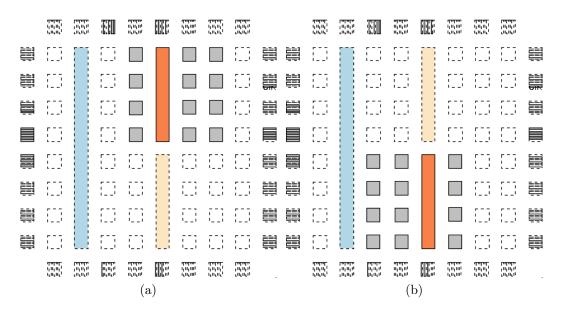

Pour pallier le problème du relogement de tâche hétérogènes, nous avons proposé dans ce travail des améliorations de l'architecture FPGA permettant aux connexions vers les éléments hétérogènes de *glisser* horizontalement, notamment afin d'améliorer la flexibilité du placement dans cette direction.

FIGURE 0-6 – Abstraction des ressources hétérogènes de la surface reconfigurable.

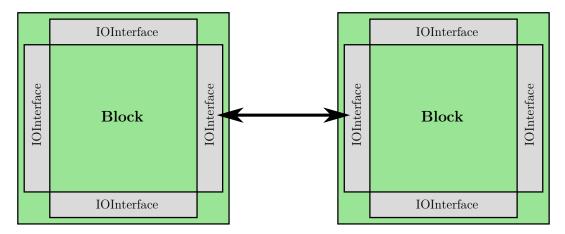

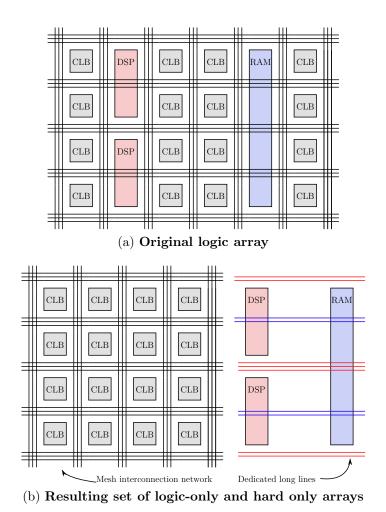

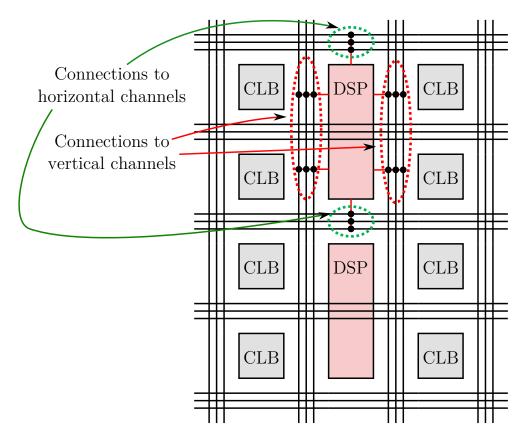

Cette flexibilité est apportée par une séparation du réseau d'interconnexion primaire des éléments logiques purs d'une part, et d'un réseau secondaire dédiée aux éléments hétérogènes d'autre part. Alors que le réseau d'interconnexion primaire reste identique à celui d'une architecture en îlots classiques, à l'exception des éléments hétérogènes, le réseau secondaire est matérialisé par un ensemble de lignes longues traversant des parties de l'architecture. Chaque ligne longue est dédiée à une entrée/sortie spécifique d'un élément hétérogène du FPGA. Ces lignes longues sont ensuite reliées, à intervalles réguliers, aux switch boxes du réseau primaire, au travers desquelles la connexion entre les éléments logiques purs et les éléments hétérogènes sera réalisée.

L'abstraction entre les éléments logiques purs et les éléments hétérogènes de l'architecture permet notamment de briser la contrainte obligeant à trouver des ressources identiques d'une région à l'autre pour reloger une tâche. En utilisant la séparation des deux réseaux de routage il est possible, dans un premier lieu, de placer les éléments logiques purs sur l'architecture puis, dans un second temps, de réaliser, w après le placement, les connexions entre le réseau primaire et le réseau secondaire. Une tâche matérielle n'est donc plus représentée par un ensemble hétérogène d'éléments logiques, mais par un ensemble homogène d'éléments logiques purs et des connexions à des éléments hétérogènes, ces connexions étant à réaliser au travers des *switch boxes* entre les deux réseaux de routage.

Une intégration approfondie dans l'outil académique de placement-routage Versatile Place-and-Route (VPR) a été effectuée afin d'intégrer cette séparation des réseaux d'interconnexions qui n'est pas supportée à l'origine. La technique a été évaluée sur un ensemble d'applications de référence afin notamment d'évaluer son impact sur le délai critique des tâches placées et routées sur ce type d'architecture, limité en moyenne à une augmentation de 10% de sa valeur de base. L'évolution de la quantité de ressources de routage a en outre été étudiée pour chiffrer les conséquences d'une telle abstraction entre les éléments homogènes et hétérogènes de l'architecture, qui dépends en partie de la taille de partition considérée et du nombre d'éléments

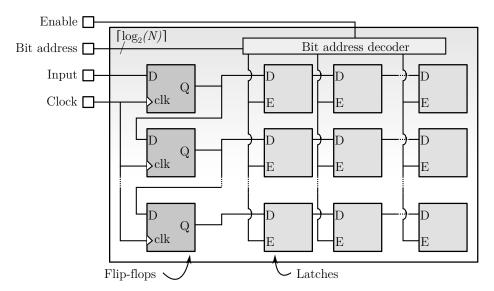

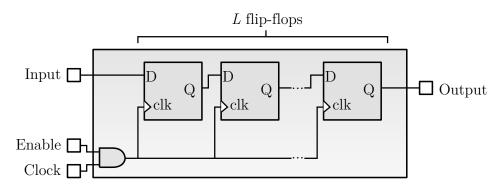

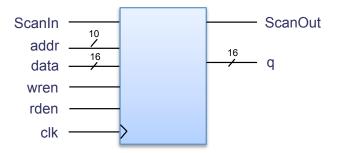

FIGURE 0-7 – Hybride entre un registre à décalage et une mémoire adressée par mots [RGM01].

hétérogènes dans celle-ci.

## 4 ORGANISATION MÉMOIRE AMÉLIORÉE POUR LA CONFI-GURATION PARTIELLE

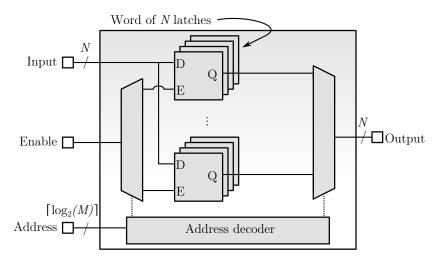

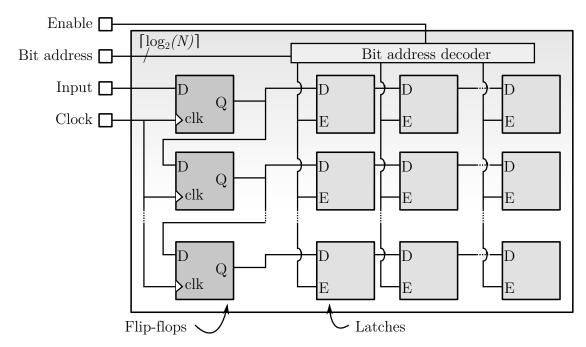

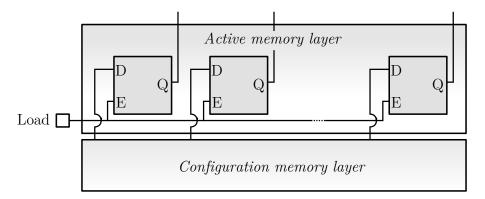

Les travaux de cette thèse se sont concentrés jusqu'à présent sur des améliorations de la flexibilité des composants reconfigurables au niveau architectural. Un autre aspect de la reconfiguration n'est pas à négliger : la mémoire de configuration du circuit. C'est en effet elle qui conditionne les capacités de dynamisme et de flexibilité de l'architecture. Si l'organisation de la mémoire de configuration ne permet pas la reconfiguration partielle de certaines zones du circuit logique, il est impossible d'utiliser les techniques citées dans les sections précédentes pour améliorer le support des applications dynamiques et du chargement en ligne de tâches matérielles.

Une étude des organisations possibles de la mémoire de configuration a été menée afin de déterminer les avantages et les inconvénients de chacune d'entre elles au niveau de leur consommation, de leur surface occupée et de leur vitesse de fonctionnement. Le bilan fait état des capacités intéressante d'une organisation hybride entre un registre à décalage et une mémoire adressée par mots, illustrée par la Figure 0-7. Cette organisation permet notamment de réduire significativement la consommation dynamique au pire-cas de la mémoire d'un facteur  $\frac{1}{N}$ , N étant la taille des mots de la mémoire, par rapport à une organisation en registre à décalage, tout en réduisant la surface occupée par la partie décodage d'adresse d'une mémoire adressable.

L'inconvénient d'une telle organisation mémoire, par rapport à une mémoire adressable, est l'impossibilité de charger des données à une position paramétrable de la mémoire hybride. Cela empêche par ailleurs de reconfigurer partiellement une

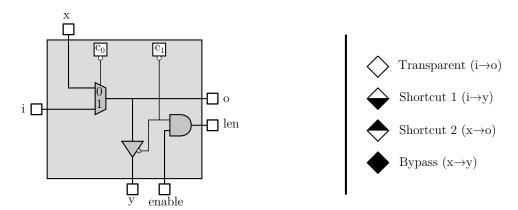

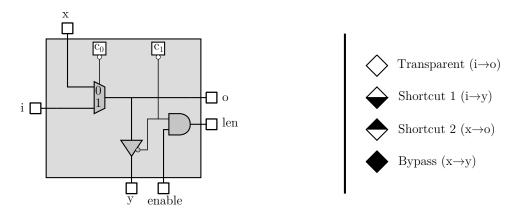

FIGURE 0-8 – Élément de routage de la mémoire de configuration améliorée.

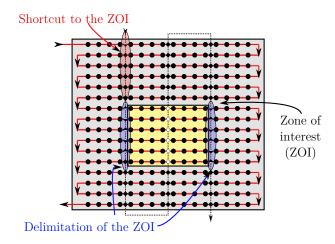

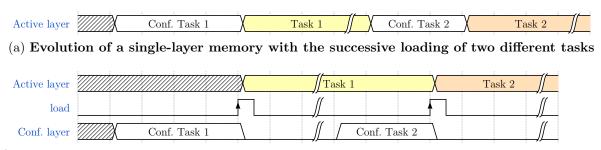

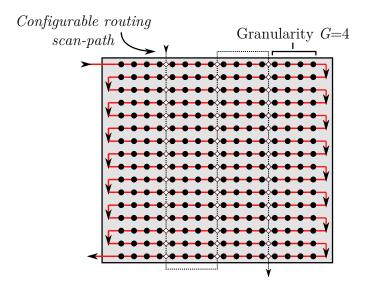

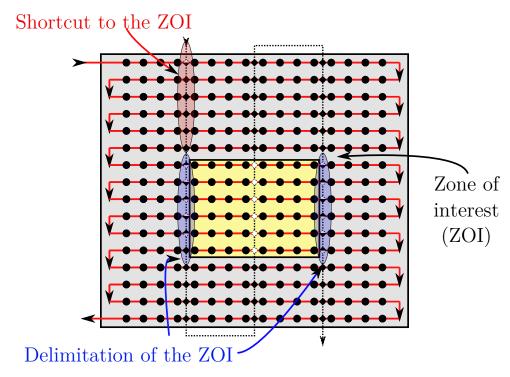

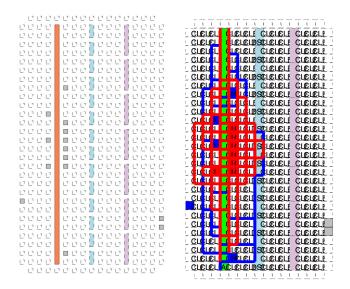

FIGURE 0-9 – Utilisation du registre à décalage amélioré lors de l'insertion d'un tâche de taille  $8 \times 4$  frames.

architecture reconfigurable utilisant ce type d'organisation pour sa mémoire de configuration. Il serait en effet nécessaire pour cela de remplir, dans tous les cas, l'intégralité du registre à décalage.

La technique proposée optimise les organisations mémoires chaînées afin de proposer une insertion plus rapide des tâches à un endroit donné de la mémoire de configuration. D'autre part, cela permet d'optimiser l'insertion de la configuration d'une tâche en délimitant la zone cible à configurer pour réduire le volume de donnée de bourrage à insérer pour aligner les données de la tâche sur sa position cible lors du décalage dans le registre.

Pour cela, des éléments de routage, détaillés dans la Figure 0-8, sont placés dans le registre à décalage à intervalles réguliers afin de contrôler le sens du flux de configuration dans le registre et de le raccourcir en cas de besoin.

Lors de l'insertion des données de configuration d'une tâche jusqu'à sa zone de reconfiguration partielle (ZOI) comme illustré sur la Figure 0-9, l'ensemble des éléments de routage est d'abord configuré pour diriger le flux de données jusqu'à la zone cible : c'est le raccourci (shortcut) qui évite l'insertion de données de bourrage pour décaler les données de la tâche jusqu'à sa zone cible. En deuxième lieu,

la configuration des éléments de routage permet aussi de délimiter, avec une précision dépendante du grain G de placement des éléments, la zone de reconfiguration partielle elle-même. La délimitation des éléments permet par ailleurs de réduire l'activité des parties du registre à décalages mises à l'écart, ce qui influe directement sur la consommation dynamique de celle-ci.

L'étude menée sur cette organisation améliorée de la mémoire de configuration montre une réduction dans tous les cas du volume de données à insérer dans le registre à décalage, notamment par la réduction au minimum des données de bourrage utilisées. L'utilisation des éléments de routage introduit en revanche une évolution dynamique du chemin critique du registre à décalage, dont la fréquence maximale de fonctionnement deviens alors assujettie au nombre de ces éléments de routage consécutifs pour une configuration donnée de la mémoire de configuration.

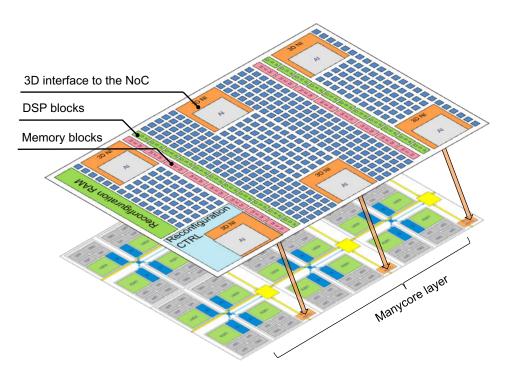

## 5 LE PROJET EUROPÉEN FLEXTILES

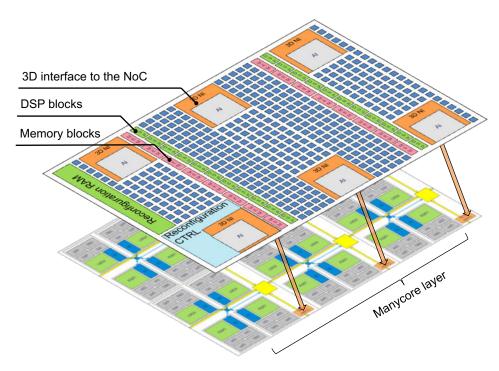

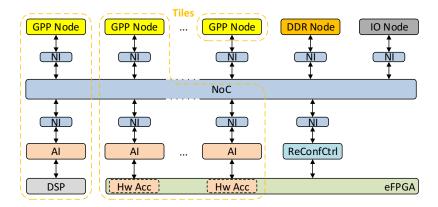

Le projet Européen FP7 FlexTiles, achevé en 2015, vise à produire une architecture 3-D multi-cœurs hétérogène, adaptative et reconfigurable dynamiquement. La Figure 0-10 illustre l'organisation générale de la plateforme FlexTiles. L'architecture s'organise autour du concept de tuiles, des éléments virtuels regroupant un processeur généraliste (GPP) et un ou plusieurs éléments hétérogènes de la plateforme parmi les processeurs de traitement du signal (DSP) et des tâches matérielles chargées sur la surface logique reconfigurable d'un FPGA embarqué, le eFPGA. Ces éléments communiquent entre eux par le biais d'un réseau sur puce (NoC) reliant à la fois les processeurs généralistes et les accélérateurs.

L'ensemble de la plateforme est gérée par une couche logicielle de virtualisation gérant la répartition des ressources au sein de l'application ainsi que la gestion globale de l'architecture.

## 5.1 EFPGA ET LE SUPPORT DE LA RECONFIGURATION MATÉ-RIELLE À L'ÉXECUTION

Certaines innovations apportées par les travaux conduits dans le cadre de cette thèse ont été intégrées au sein de la plateforme FlexTiles, et notamment le concept de Virtual Bit-Streams. L'utilisation de cette représentation alternative des données de configuration d'une tâche matérielle est associée à l'intégration d'un contrôleur de reconfiguration intégré au circuit du eFPGA pour gérer le décodage des Virtual Bit-Streams. Ce contrôleur de reconfiguration intègre notamment les algorithmes de décodage décrits précédemment.

Les spécificités de cette architecture reconfigurable embarquée, en comparaison avec les architectures FPGA courantes du marché, sont nombreuses. Les communications entre les tâches matérielles chargées sur le eFPGA et le reste du système se font uniquement au travers d'interfaces normalisées communes à tous les accélérateurs

FIGURE 0-10 – La plateforme 3-D FlexTiles.

Table 0-2 – Résultats de synthèse des éléments logiques du eFPGA sur des technologies 65nm et 28nm

| Élément     | Surface 65nm $(\mu m^2)$ | Surface 28nm $(\mu m^2)$ | par rap. au CLB |

|-------------|--------------------------|--------------------------|-----------------|

| CLB         | 9,929                    | 3,309                    | $1 \times$      |

| Acc. Arith. | 13,055                   | 4351                     | $1.31 \times$   |

| RAM         | 21,134                   | $7044^\dagger$           | $2.13 \times$   |

| 3DNI        | 354,617                  | 118,205                  | $35.71 \times$  |

<sup>† :</sup> Projection du 65nm au 28nm

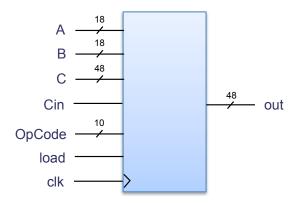

de la plateforme FlexTiles. Ces interfaces, les AIs, sont couplées à une interface de communication avec le réseau sur puce, les NIs, eux-mêmes associés à des éléments physiques de communications entre les deux circuits superposés. L'ensemble forme un 3DNI, géré du point de vue de l'architecture FPGA comme un des éléments hétérogènes de la surface logique. Le reste de la surface logique intègre des RAM et des accélérateurs arithmétiques, ainsi que des éléments logiques formés de grappes de 6-LUT.

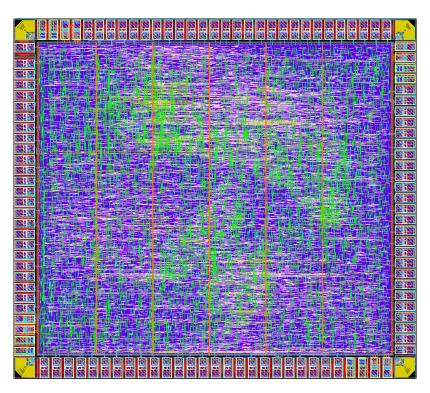

Pour déterminer l'agencement final des éléments sur la surface logique (leur nombre et leur taille relative), chacun d'entre eux a été développé en Verilog en intégrant les contraintes de reconfiguration et de la technique du *Virtual Bit-Stream*. Le Tableau 0-2 résume les résultats en surface de la synthèse de ces éléments sur des technologies 65nm et 28nm de STMicroeletronics.

## 5.2 SIMULATION ET VALIDATION DE LA SURFACE RECONFIGU-RABLE

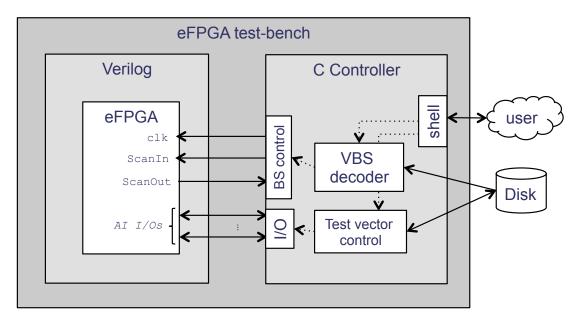

La simulation et la validation de l'ensemble du circuit eFPGA, comprenant le contrôleur de reconfiguration ainsi que le modèle Register Transfer Level (RTL) de l'architecture FPGA, a été réalisée en co-simulation Verilog et C. Pour des raisons de flexibilité de l'implémentation du contrôleur de reconfiguration, les spécifications de celui-ci ont été développées en C et intégrées au modèle RTL de la surface logique reconfigurable. Le contrôleur s'occupe ainsi de la lecture des flux de configuration, de leur décodage, puis du chargement des tâches dans la mémoire de configuration du modèle RTL.

Cette simulation a permis de valider les concepts introduits par ces travaux de thèse dans le cadre de la plateforme FlexTiles, à la fois au sens implémentation matérielle des méthodes décrites jusqu'ici, et aussi par le biais du flot de développement associé au *Virtual Bit-Stream*, lui aussi intégré à la suite d'outils utilisés par la plateforme FlexTiles.

## 6 Contributions

Les contributions de ce travail sont résumées ci-dessous.

- Nous avons proposé un concept de flux de configuration abstraits, indépendants de leur position final et pré-routés, le *Virtual Bit-Stream*. Cette représentation des données d'une tâche matérielle est privée de toute information relative aux détails de l'architecture reconfigurable ciblée. Les *Virtual Bit-Streams* sont ensuite décodés à l'exécution pour reconstruire un flux de configuration conventionnel spécifique à une position donnée de la surface logique, qui peut ensuite être chargé dans la mémoire de configuration. En plus de l'indépendance de cette représentation vis-à-vis de sa position finale, nous avons observé une réduction de la taille du flux de configuration jusqu'à 89% par rapport à un flux de configuration conventionnel.

- Deux algorithmes permettant le décodage en temps réel des *Virtual Bit-Streams* précédemment évoqués sont présentés. Ces algorithmes sont destinés à être intégrés dans le contrôleur de reconfiguration en ligne de l'architecture responsable du décodage, du placement et de la configuration des flux de configuration. Un débit élevé, comparable à celui utilisé pour la configuration des FPGAs modernes, a été fixé comme contrainte temps-réel à atteindre pour ces algorithmes. Cette contrainte peut être atteinte pour les deux algorithmes.

- Un flot de conception, basé sur le flot VTR, a été développé pour générer les Virtual Bit-Streams. Ce flot de conception se base sur les données de placementroutage générées par VTR pour créer et vérifier des flux de configuration abstraits et conventionnels. De cette manière, la partie hors ligne de la technique

du *Virtual Bit-Stream* garantit la production des flux de configuration valides qui seront décodables en ligne.

- Pour pallier les problèmes d'hétérogénéité dans les FPGAs lors du placement de tâches matérielles, une architecture améliorée est proposée. Cette architecture offre des lignes de routage dédiées aux éléments hétérogènes de la surface logique, séparées du réseau d'interconnexion des éléments logiques purs. La séparation des réseaux d'interconnexion permet un placement en deux temps à l'exécution. En premier lieu, les éléments logiques purs sont configurés et routés sur la surface logique. En second lieu, les connexions aux éléments hétérogènes au travers de leurs lignes longues dédiées sont réalisées dans les switch boxes. Cela permet notamment d'offrir une flexibilité horizontale à grain fin lors du placement des tâches matérielles. L'impact sur le délai de la solution proposée est une augmentation de 10% en moyenne du délai du chemin critique.

- Une mémoire de configuration améliorée et évolutive autorisant le placement à grain fin de tâches matérielles est présentée. Cette organisation de la mémoire de configuration permet le placement de tâches au-delà de la définition, à l'étape de conception, de régions partiellement reconfigurables fixes, et offre une alternative flexible pour la reconfiguration de zones finement définies de la surface logique du FPGA.

### 7 CONCLUSION

Dans ce travail, nous avons proposé une représentation alternative du flux de configuration d'une surface reconfigurable, afin de fournir une représentation intermédiaire de tâches matérielles, abstraite de la position finale de la tâche. Nous avons montré qu'une telle représentation permet par ailleurs une compression intelligente des données, plus performante que des compresseurs classiques. Deux implantations matérielles pour le décodage temps-réel de cette représentation ont été proposées et évaluées en termes de complexité, et nous avons démontré leur applicabilité selon les contraintes fixées.

Une architecture de FPGA améliorée a été détaillée, afin de répondre au problème de la gestion des éléments hétérogènes lors du relogement de tâches, tout en gardant des conséquences faibles sur le délai du chemin critique d'une application. Nous avons aussi proposé une évolution des organisations de la mémoire de configuration basées sur des registres à décalage, notamment pour offrir plus de flexibilité lors de l'insertion des données d'une tâche à un endroit donné. La solution proposée permet en outre une réduction importante du nombre de cycles nécessaires à la configuration partielle du registre à décalage par rapport à un registre classique.

Enfin, certaines de ces solutions ont été mises à contribution dans le cadre d'un projet européen, FlexTiles, pour proposer une surface logique reconfigurable de FPGA permettant le chargement dynamique de tâches matérielle à l'exécution. Cette surface logique a par ailleurs été modélisée et validée dans le cadre de ce projet.

## INTRODUCTION

## 1 Context of the work

Field-Programmable Gate Arrays (FPGAs) have become mainstream for most complex digital circuit designs over the last decade. Their versatility brings the power of custom hardware seen in Application-Specific Integrated Circuits (ASICs) at a fraction of the development and design costs, mainly aimed to the cost of developing the chip masks. The fast pace of evolution in the semiconductor industry allowed FPGAs to become increasingly complex, integrating heterogeneous accelerators and embedded processors to support the market needs.

Modern-day applications targeting FPGA devices progressively move towards increasingly dynamic designs. The recent process and voltage scaling demonstrated the failure of Dennard Scaling, leveraging a problem in multicore processors known as dark silicon. Dark silicon refers to the circuit area which cannot be powered-on at its nominal voltage without breaking the chip Thermal Design Power (TDP), to counteract the sharp increase of power densities in recent technology nodes. The threat of this power wall is an opportunity for more energy-efficient reconfigurable multicore architectures. Indeed, FPGA systems offer increased reconfiguration capabilities, allowing dynamic designs to maximize the FPGA resource utilization while keeping a lower power budget than with general purpose processors.

However, the constant addition of heterogeneous accelerators in FPGA architectures hampers the practicality of flexible reconfiguration schemes. Indeed, accelerators in FPGAs significantly improve the energy efficiency of functional designs in comparison with soft-logic implementations, but restrict the architecture flexibility in case of relocation. Task relocation allows for a maximum flexibility of a reconfigurable architecture by optimizing at runtime the spatial and temporal scheduling of an application. To a lesser extent, relocation would also enable a hardware task to be reused over multiple compatible platforms, in the same manner as a software task. Seamless runtime hardware task placement on FPGAs has nevertheless been put aside with modern FPGAs, due to their complex architectures and the lack of software support in most FPGA vendors Computer-Aided Design (CAD) tool-flows.

Figure 0-11 – Overview of an FPGA architecture and its configuration mechanism

#### 2 Contributions

The contributions of this work have been conducted to focus around multiple aspects of both an enhanced FPGA architecture and its accompanying CAD flow to propose a concept of an efficient runtime hardware reconfiguration. Figure 0-11 illustrates a typical FPGA logic fabric architecture, along with its reconfiguration memory, here arranged as a contiguous scan-path. Flexible reconfiguration techniques hits a wall on multiple aspects on such an architecture. First, as vendors CAD flows only support the generation of a bit-stream associated to given Partially-Reconfigurable Regions (PRRs), it is necessary to resort to online bit-stream modifications such that it can be placed on multiple locations. Second, although on-the-fly bit-stream modifications techniques have been researched, they are severely limited by the FPGA architecture itself, whose heterogeneity impedes the association of a single hardware task to multiple positions on the logic fabric. Eventually, the configuration method of modern FPGA devices as well as their intrinsic configuration memory usually operate on pre-defined, fixed regions which hampers a finer-grain placement and configuration of a hardware task.

The work of this thesis focuses on these particular issues of FPGA dynamic reconfiguration schemes. The specific contributions of this work are enumerated as follows.

- A concept of pre-routed, position-independent abstracted bit-streams, the Virtual Bit-Stream (VBS), is proposed [HCS15]. This representation of a hardware task data is deprived of any knowledge about the final FPGA detailed architecture. The Virtual Bit-Streams are then decoded at runtime to reconstruct a conventional bit-stream dedicated to a specific location, which can then be loaded into the logic fabric. Along with the position-independence of this representation, allowing to place it anywhere on a logic fabric, we observed a size reduction of up to 89% in comparison to a conventional bit-stream.

- Two algorithms allowing a real-time decoding of the aforementioned Virtual

Bit-Streams are presented. These algorithms are to be integrated in the online controller of the architecture responsible for the decoding, placement and configuration of the bit-streams. A high-throughput target speed, similar to modern FPGA reconfiguration, has been fixed as the real-time constraint to meet for these algorithms, which can be attained in both cases.

- A CAD flow, based on the Verilog-To-Routing (VTR) framework, has been developed to generate the Virtual Bit-Streams. This CAD flow relies on the placement and routing data generated by Versatile Place-and-Route (VPR) to create and verify the bit-streams abstraction and their equivalent conventional raw bit-streams. The offline part of the Virtual Bit-Stream technique is thus ensured to offer a compatible working bit-stream to the online controller.

- To circumvent the FPGA heterogeneity issues regarding flexible placement of hardware tasks, an enhanced architecture is proposed [HST14]. This architecture exposes dedicated routing lines for heterogeneous hard-blocks of the FPGA logic fabric, separated from the soft-logic interconnection network. The separation of the interconnection networks allows a two-step placement at runtime. First, the soft logic elements are configured and routed on the logic fabric. In a second step, the connections to the heterogeneous elements through their dedicated long lines are made in switch boxes. This enables a fine-grain horizontal flexibility of placement for hardware tasks. The delay impact of the proposed solution is an increase of 10% of the critical path delay in average.

- A scalable and finely-grained configuration memory suitable for the placement

of hardware tasks is presented. This organization of the configuration memory

enables the task placement to go beyond the fixed regions defined at design

time and offers a more flexible alternative to reconfigure finely-grained portions

of the FPGA logic fabric.

- Some methods and techniques described have been implanted and validated in the context of the European project FlexTiles [Jan+15]. In particular, a Register Transfer Level (RTL) model of an FPGA architecture featuring the Virtual Bit-Stream technique and its reconfiguration controller was developed and simulated. The CAD flow has been put in use within the project to generate relocatable hardware tasks to be dynamically placed, at runtime, on the reconfigurable logic fabric RTL model.

### 3 Organization of the document

The thesis is organized as follows. The first part introduces the state-of-the-art pertaining to this work. A background on FPGA architectures is given in Chapter 1. The historical evolution of programmable devices is presented. The various programming technologies used in FPGA configuration memories are detailed. The modern trends and advances of the logic fabric and routing architecture of FPGAs

are presented and detailed to serve as the general background of this thesis on FPGA devices.

Chapter 2 presents a detailed state-of-the-art on multiple aspects of the work conducted during this thesis. The tasks relocation problem is exposed through the prisms of vendors' CAD flows and bit-stream manipulation tools. Details on runtime routing in dynamically reconfigurable architectures are given. The chapter ends with a state-of-the-art of placement and routing tools for FPGAs.

The second part of the thesis details the contributions of this work. In Chapter 3, the concept of Virtual Bit-Streams is thoroughly presented. A description of the representation is given from the interconnect abstraction in macro-cells to the generation of the final bit-stream. A study on the effects of clustering multiple macro-cells together is studied. The tool-flow associated with the offline generation of the Virtual Bit-Streams is described, and the principles of operation of the proposed back-end bit-stream generation tool *vbsgen* are explained. A description of a Virtual Bit-Stream compatible architecture is presented, along with a description of the reconfiguration controller functions. The limitations of the Virtual Bit-Stream technique are also mentioned.

Chapter 4 focuses on the online implementation of the Virtual Bit-Stream method. The real-time constraints to be attained are described, and modern FPGA reconfiguration schemes are studied. Two specific algorithms for decoding the bit-stream representation detailed in Chapter 3 are proposed and compared to a generic mazerouting algorithm. Eventually, an analysis of the compression effect of the Virtual Bit-Stream representation is conducted on a set of large benchmarks.

In Chapter 5, FPGA architecture enhancements to ease flexible task placement are detailed. A method for separating the routing networks of soft-logic and heterogeneous hard blocks is proposed. The experimental methodology used to explore this routing architecture is thoroughly presented along with the set of benchmarks used for the experiments. An analysis of the results of these experiments in terms of delay and routing resources closes the chapter.

Chapter 6 explores the integration of a configurable reconfiguration method. Several state-of-the-art bit-stream loading methods are presented and compared in term of delay and area occupancy. An enhanced configuration method is proposed for flexible fine-grain hardware task loading, and discussed in comparison to fixed partially reconfigurable regions schemes.