# Unified system of code transformation and execution for heterogeneous multi-core architectures.

Pei Li

## ▶ To cite this version:

Pei Li. Unified system of code transformation and execution for heterogeneous multi-core architectures.. Software Engineering [cs.SE]. Université de Bordeaux, 2015. English. <NNT : 2015BORD0441>. <tel-01342119>

# HAL Id: tel-01342119 https://tel.archives-ouvertes.fr/tel-01342119

Submitted on 5 Jul 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE

POUR OBTENIR LE GRADE DE

# **DOCTEUR DE**

# L'UNIVERSITÉ DE BORDEAUX

École Doctorale de Mathématiques et Informatique SPÉCIALITÉ: Informatique

Par Pei Li

# Système unifié de transformation de code et d'exécution pour un passage aux architectures multi-coeurs hétérogènes

Sous la direction de : Raymond Namyst Encadrante de thèse : Elisabeth Brunet

Soutenue le 17 Décembre 2015

Membres du jury : M. ROMAN Jean Professeur Institut Polytechnique de Bordeaux Président M. MEHAUT Jean-François Université de Grenoble 1 Professeur Rapporteur Université Pierre et Marie Curie M. SENS Pierre Professeur Rapporteur M. CARRIBAULT Patrick Chercheur CEA Examinateur M. NAMYST Raymond Professeur Université de Bordeaux 1 Directeur de thèse Mme. BRUNET Elisabeth Maître de conférence Institut Télécom SudParis Encadrante de thèse

# Remerciement

Cette thèse est le fruit de travail qui appartient non seulement à moi, mais aussi à tous les personnes qui m'a supporté mon travail et ma vie pendant ces 3 ans de thèse. Je profite de cette occasion ici pour exprimer ma sincère gratitude.

Je tiens à remercier en tout premier lieu mon encadrant Elisabeth Brunet. Je vous remercie de m'avoir proposé ce sujet de thèse, m'avoir fait confiance et m'avoir accueilli au sein de votre équipe. Grace à vous, j'ai pu entrer dans un nouveau monde où je n'avais jamais exploré. Quand j'ai rencontré des problèmes sur mes recherches, vous étiez toujours la première personne qui m'a encouragé et m'a donné la suggestion. Je remercie également mon directeur de thèse Raymond Namyst. Vous m'avez guidé la direction de recherche pendant ma thèse. Sans votre conseil, tous ce travail n'aurait pas été possible! Je vous remercie aussi de m'avoir accueilli au sein de l'équipe Runtime d'INRIA Bordeaux, j'ai donc pu profiter la ressource de recherche et les équipements de expérimentation de très haute qualité.

Je remercie chaleureusement les membres de mon jury de thèse. Je remercie tout d'abord mes rapporteurs Jean-François Mehaut et Pierre Sens pour avoir pris le temps d'évaluer mon travail. Je remercie Jean Roman et Patrick Carribault pour avoir accepté mon invitation et participer au jury.

Je remercie tous les membres et les doctorants de département informatique de TELE-COM SudParis. Un grand merci à François Trahay, Gaël Thomas et Christian Parrot qui m'ont beaucoup aidé et m'ont beaucoup inspiré pendant la préparation de thèse. Un énorme merci à Brigitte Houassine qui m'a aidé sur tous les démarches administratives. Je remercie Alda Gancarski, Chantal Taconet, Denis Conan, Sophie Chabridon, Olivier Berger, Christian Bac, Amel Mammar et tous les autres que je n'ai pas cités ici. Je remercie tous les membres de l'équipe Runtime de Inria Bordeaux, particulièrement, merci à Denis Barthou, Samuel Thibault, Marie-Christine Counilh et Sylvain Henry pour m'avoir enseigné les reconnaissances sur StarPU runtime.

Je remercie mes anciens collègues Rachid Habel, Alain Muller, Soufiane Baghadadi pour avoir partagé leurs connainssances sur la compilation. Un énorme merci à tous mes co-bureaux qui m'ont supporté pendant ces trois ans. Je également remercie Fabienne Jézéquel et Mounira Bachir qui m'ont encadré mon stage de Master et m'ont proposé à mon encadrant actuel.

Enfin, Je remercie les membres de ma famille pour leur aide et soutien. J'ai commencé mes études en France depuis le 3 septembre 2009. Pendant ces 6 ans, j'ai eu très peu de l'occasion de leur rendre visite, mais vous m'avez toujour supporté et m'avez encouragé. Vous êtes toujour les personnes plus importantes dans ma vie.

# Résumé

# Résumé en français :

Les travaux de recherche présentés dans cette thèse se positionnent dans le domaine du calcul haute performance; plus particulièrement dans la démocratisation de l'exploitation efficace des plates-formes de calcul hétérogènes. En effet, les exigences de performance des applications de simulation scientifique mènent à une quête perpétuelle de puissance de calcul. Actuellement, le paysage architectural des plates-forme est tourné vers l'exploitation de co-processeurs, tels les GPU et les Xeon Phi, matériel satellite du processeur principal aux performances surpuissantes sur des cas d'utilisation idoines. Depuis 2007, les GPU (pour *Graphical Processing Unit*) intègrent des milliers de coeurs au design peu sophistiqué capables de traiter efficacement simultanément des milliers de tâches. Plus récemment est apparu le Intel Xeon Phi, co-processeur qualifié de many-core car il possède plus de coeurs, plus de threads et des unités d'exécution vectorielles plus larges que le processeur Intel Xeon, son homologue standard. Les coeurs du Intel Xeon Phi sont certes moins rapides si on les considère individuellement mais la performance cumulée est bien supérieure si l'ensemble des ressources est correctement mobilisée à l'exécution d'une application parallèle. Le duo de tête Tianhe-2/Titan du Top500 de ces deux dernières années, classement recensant les 500 machines les plus puissantes, atteste cette tendance : Tianhe-2 est un super-calculateur hétérogène composé de 32.000 processeurs Intel Xeon et de 48.000 co-processeurs de type Xeon Phi, tandis que Titan voit ses 18688 AMD processeurs secondés par 18688 Nvidia Telsa GPU.

Au niveau applicatif, l'exploitation conjointe de ces ressources de calcul aux profils hétérogènes est un réel défi informatique que ce soit en terme de portabilité logicielle, aux vues de la diversité de modèles de programmation de chaque matériel, ou de portabilité de performances avec notamment les coûts de déport de calcul sur de telles ressources. La portabilité logicielle pourrait passer par l'utilisation de standards de programmation tels OpenCL ou OpenACC, qui permettent d'exploiter conjointement l'ensemble des ressources d'une machine, à savoir les processeurs principaux et leurs co-processeurs. Cependant, leur modèle de programmation est statique. C'est à l'utilisateur de décrire quel calcul exécuter sur quelle ressource. L'équilibrage de charge entre les ressources hétérogènes est donc laissé à la charge du programmeur. Ainsi, même si la portabilité logicielle est assurée d'une plate-forme à l'autre, le changement du nombre de ressources ou de leur capacité de calcul impliquent le re-développement de l'application. Il existe des environnements d'exécution qui interfacent les différents co-processeurs et prennent en charge la

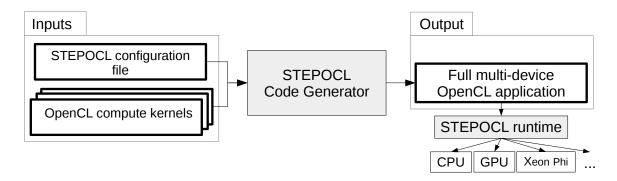

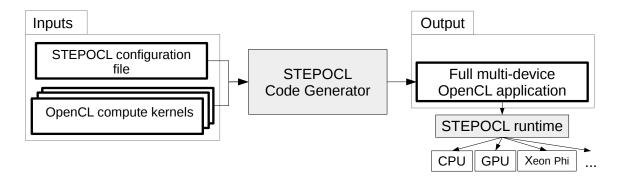

FIGURE 1 – Vue globale de STEPOCL.

dimension équilibrage de charge tels StarPU [6].

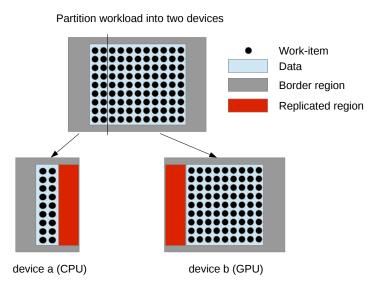

Cependant, les outils existants ne reconsidèrent pas la granularité des tâches de calcul définies par le programmeur alors que les données à traiter sont toujours massives et qu'il est de plus en plus fréquent d'avoir plusieurs co-processeurs au sein d'une même machine. Dans ce contexte, il devient intéressant de considérer la distribution d'un calcul sur plusieurs ressources de calcul hétérogènes, d'autant que les calculs adaptés à une exécution sur co-processeur sont généralement massivement parallèles. Plusieurs aspects non-fonctionnels sont à prendre en charge par le programmeur comme déterminer le partitionnement de charge de travail suivant les capacités de calcul des ressources devant participer au traitement, le maintien de la cohérence des données, l'échange de données intermédiaires, etc. Leur mise en ouvre de manière portable et efficace est indéniablement fastidieuse et sujette à erreur pour un programmeur même expérimenté. C'est pourquoi l'objectif de cette thèse est de proposer une solution de programmation parallèle hétérogène qui permet de faciliter le processus de codage et garantir la qualité du code. Nous proposons ici un nouvel outil STEPOCL qui comporte deux volets, comme illustré par la Figure 3.6 : un générateur de code conçu pour générer une application OpenCL complète capable d'exploiter des architectures hétérogènes à partir de noyaux de calcul et de leur description basique écrite grâce à un DSL (Domain Specific Language); un environnement d'exécution capable de gérer dynamiquement des problèmes comme l'équilibre de charge, la distribution de noyaux de calcul sur plusieurs co-processeurs, la gestion des communications et synchronisation, maintien de la cohérence de données, etc.

Le générateur de code de STEPOCL prend en entrée des noyaux de calcul écrits en OpenCL et un fichier de configuration écrit grâce à un DSL basé sur XML afin de générer une application OpenCL complète faisant appel au support d'exécution de STEPOCL. Le DSL de STEPOCL permet de décrire tous les aspects non-fonctionnels des calculs à réaliser comme la façon dont doivent être subdivisées les données (par exemple, si elles doivent l'être et si oui, suivant quels axes), leur taille, le flot de contrôle attendu entre les différents noyaux de calcul, etc. dans l'application à générer. Le code source généré est un application OpenCL capable d'exploiter plusieurs *device* OpenCL, code que le programmeur est ensuite libre de modifier. Après une phase d'initialisation de l'environnement OpenCL, le code commence par la détection des ressources de calcul effectives auxquelles sont associées un facteur de performance, facteur positionné grâce à un module d'échantillonnage hors ligne. Vient ensuite la phase de déploiement des données et des calculs sur les ressources sélectionnées. La distribution des calculs est déterminée à partir de la taille des données à traiter, de la forme de partitionnement des calculs donnée dans le fichier de configuration et des capacités de calcul de chacune. Les données nécessaires au calcul de chaque partition sont identifiées grâce à une analyse polyédrique des accès aux données assurée par le compilateur PIPS avant d'être copiées dans leurs mémoires locales respectives. Les données sont par la suite maintenus au maximum en mémoire locale. Seules les données frontières sont communiquées aux ressources qui en ont besoin. Ces données frontières sont également identifiées grâce aux analyses de données produites par PIPS et sont transférées grâce aux mécanismes de copies d'OpenCL via la mémoire globale. Une fois les calculs achevés, les données sont collectées en mémoire globale afin de produire le résultat. Au delà du calcul des régions suivant le nombre effectif de participants au calcul et de l'échange des données au cours de l'exécution, le support d'exécution de STEPOCL s'occupe d'équilibrer dynamiquement la charge de travail des applications itérant sur un même noyau de calcul en monitorant le temps d'exécution de chaque itération sur chaque ressource de calcul.

STEPOCL a donné lieu à deux publications d'intérêt qui ont mis en relief bien des pistes d'amélioration et perspectives à long terme. En premier lieu, il s'agira de pousser la simplification à l'extrême du fichier de configuration en utilisant des outils d'analyse de flot de contrôle à la compilation et des outils de profiling d'exécution permettant d'affiner la granularité des noyaux de calcul. À plus long terme, le contexte d'utilisation de STEPOCL pourra être élargi afin de cibler des objectifs applicatifs différents, comme la réduction d'énergie, avec l'utilisation d'autres stratégies d'ordonnancement et le passage à des architectures différentes.

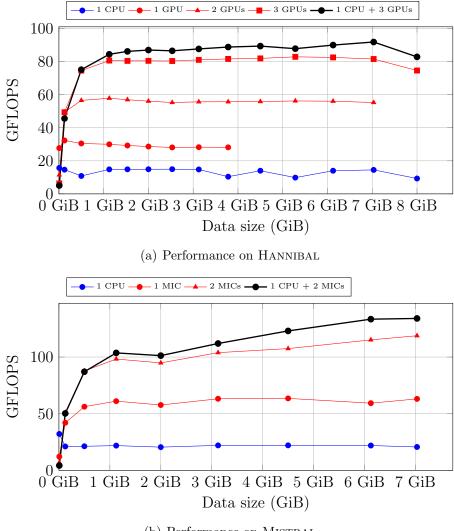

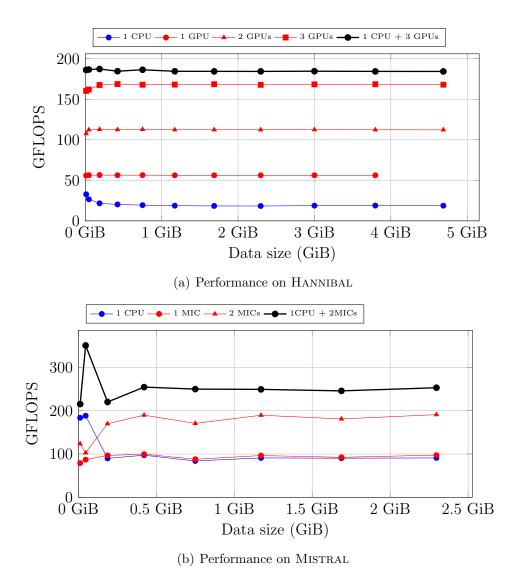

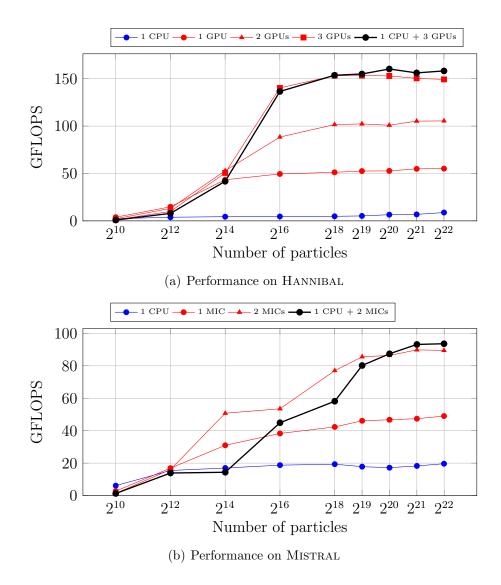

STEPOCL a été évalué sur trois cas d'application classiques : un stencil 2D 5 point, une multiplication de matrices et un problème à N corps, chacun présentant des noyaux de calcul adaptés à une exécution sur accélérateurs de type GPU ou Xeon Phi car fortement parallèles. En terme de répartition des données, le stencil et la multiplication de matrice sont des cas assez similaires dans le sens où les données vont pouvoir être distribuées sur les ressources; alors que dans le cas du N-Body, la réplication de la structure de données stockant les particules est nécessaire. Pour chacun de ces cas test, différents points d'évaluation ont été considérés. En premier lieu, est comparé le volume du code généré par STEPOCL à partir d'un noyau de calcul donné et du fichier de configuration associé afin de produire une application OpenCL *multi-device* complète en comparaison de celui de l'application mono-device de référence tirée de benchmarks de la littérature. Le fichier de configuration étant massivement plus court et plus simple à écrire que toute la machinerie nécessaire à l'utilisation d'un environnement OpenCL, STEPOCL simplifie le cycle de développement d'une application OpenCL complète en apportant en supplément une dimension multi-device. STEPOCL est ensuite évalué suivant des critères de performance en temps d'exécution. Les évaluations ont été menées sur deux plates-formes matérielles hétérogènes différentes. La première HANNIBAL allie la force de calcul de trois GPU de type NVidia Quadro FX5800 à un biprocesseur quad-coeur Intel Xeon X5550; tandis que sur la seconde, le surpuissant processeur principal, un bi-processeur Intel Xeon E5-2670 comptant 2 fois 10 coeurs de calcul, est équipé de deux accélérateurs de type Intel Xeon Phi offrant chacun 61 coeurs. Chacune de ces ressources est exploitée au travers de l'implémentation OpenCL fournie par Intel à l'exception des GPU qui est adressé grâce au support OpenCL dédié de NVidia. Tout d'abord, l'application produite par STEPOCL

est comparée à sa version de référence dont le noyau de calcul a été extrait et utilisé pour la génération du code. Pour les trois cas tests, les performances du code OpenCL généré par STEPOCL s'exécutant sur un seul et même accélérateur sont comparables à celle de la version originale. Ainsi, STEPOCL permet de produire un code OpenCL complet aux performances satisfaisantes ayant le potentiel de distribuer les calculs sur plusieurs ressources et ce, avec un effort de programmation moindre. Les codes générés sont ensuite exécutés sur les ressources hétérogènes des plates-formes de test. Chaque application est évaluée sur des configurations où seul le processeur principal est activé, puis seul un coprocesseur, puis deux pour enfin arriver à l'exploitation totale des ressources hétérogènes de la machine. L'équilibrage de charge de calcul réalisé à partir de l'échantillonnage horsligne de STEPOCL permet d'exploiter de manière conjointe toutes les ressources dans les trois cas applicatifs. De plus, dans le cas du stencil et de la multiplication de matrices, le fait que les données puissent être distribuées sur les différentes ressources permet de traiter des jeux de données plus larges en parallèle. Avec l'application originale, seule une exécution sur le processeur hôte de la plate-forme HANNIBAL permettait de mener à bien le calcul car la taille de la mémoire des GPU est trop limitée.

Mots-clés : Calcul Haute Performance, Parallélisme, Architectures hétérogènes, OpenCL, génération de code, équilibrage de charge

# Résumé en Anglais:

Heterogeneous architectures have been widely used in the domain of high performance computing. However developing applications on heterogeneous architectures is time consuming and error-prone because going from a single accelerator to multiple ones indeed requires to deal with potentially non-uniform domain decomposition, inter-accelerator data movements, and dynamic load balancing.

The aim of this thesis is to propose a solution of parallel programming for novice developers, to ease the complex coding process and guarantee the quality of code. We lighted and analysed the shortcomings of existing solutions and proposed a new programming tool called STEPOCL along with a new domain specific language designed to simplify the development of an application for heterogeneous architectures. We evaluated both the performance and the usefulness of STEPOCL. The result show that: (i) the performance of an application written with STEPOCL scales linearly with the number of accelerators, (ii) the performance of an application written using STEPOCL competes with an handwritten version, (iii) larger workloads run on multiple devices that do not fit in the memory of a single device, (iv) thanks to STEPOCL, the number of lines of code required to write an application for multiple accelerators is roughly divided by ten.

**Keywords:** High-Performance Computing, Parallelism, Heterogeneous Architectures, OpenCL

# Contents

| 1 | Intr | oducti | ion                                                            | 1        |

|---|------|--------|----------------------------------------------------------------|----------|

|   | 1.1  | Object | tive of thesis                                                 | 2        |

|   | 1.2  | Outlin | e and contribution                                             | 3        |

| 2 | The  | rise o | f heterogeneous computing                                      | <b>5</b> |

|   | 2.1  | Hetero | ogeneous platforms                                             | 5        |

|   |      | 2.1.1  | Multi-core processor                                           | 6        |

|   |      | 2.1.2  | GPU computing                                                  | 6        |

|   |      | 2.1.3  | Intel Xeon Phi                                                 | 7        |

|   |      | 2.1.4  | AMD APU                                                        | 8        |

|   | 2.2  | Exploi | itation of heterogeneous architectures                         | 9        |

|   |      | 2.2.1  | Computing on CPUs                                              | 9        |

|   |      | 2.2.2  | Computing on accelerators                                      | 13       |

|   |      | 2.2.3  | Computing on heterogeneous architectures                       | 16       |

|   | 2.3  | Conclu | usion                                                          | 21       |

| 3 | STH  | EPOCI  | L                                                              | 23       |

|   | 3.1  | Progra | amming on heterogeneous multi-device architectures in OpenCL . | 24       |

|   |      | 3.1.1  | Background of OpenCL                                           | 24       |

|   |      | 3.1.2  | Challenge of using multiply compute devices                    | 27       |

|   | 3.2  | Comp   | onent of STEPOCL                                               | 30       |

|   |      | 3.2.1  | Compute kernels                                                | 31       |

|   |      | 3.2.2  | STEPOCL configuration file                                     | 32       |

|   |      | 3.2.3  | STEPOCL Output of OpenCL application                           | 34       |

|   | 3.3  | STEP   | POCL internal mechanism                                        | 35       |

|   |      | 3.3.1  | Automatic device management                                    | 35       |

|   |      | 3.3.2  | Automatic workload partition                                   | 36       |

|   |      | 3.3.3  | Automatic adjusting workload                                   | 37       |

|   |      | 3.3.4  | Automatic data consistency management                          | 37       |

|   | 3.4  | Conclu | usion                                                          | 37       |

| 4 | Imr  | lemen  | tation                                                         | 39       |

| - | 4.1  |        | sis of region                                                  | 39       |

|   |      | 4.1.1  | PIPS                                                           | 40       |

|   |      | 4.1.2  | Analysis of regions with PIPS                                  | 40       |

|   |      | 4.1.3  | Analysis of OpenCL kernel                                      | 42       |

|              | 4.2  | Offline profiling                          | 44 |

|--------------|------|--------------------------------------------|----|

|              | 4.3  | Workload partition                         | 45 |

|              |      | 4.3.1 Data space partition                 | 46 |

|              | 4.4  | Workload balancing                         | 48 |

|              | 4.5  | Data transmission between multiple devices | 50 |

|              | 4.6  | Generation of Host code                    | 52 |

|              | 4.7  | Conclusion                                 | 53 |

| <b>5</b>     | Eva  | luation                                    | 55 |

|              | 5.1  | Test cases                                 | 56 |

|              | 5.2  | Volume of the generated source code        | 61 |

|              | 5.3  | Performance evaluation                     | 63 |

|              |      | 5.3.1 Experimental platforms               | 63 |

|              |      | 5.3.2 Evaluation of the profiler           | 64 |

|              |      | 5.3.3 Comparison with the reference codes  | 64 |

|              |      | 5.3.4 Stencil                              | 64 |

|              |      | 5.3.5 Matrix multiplication                | 66 |

|              |      | 5.3.6 N-body                               | 67 |

|              | 5.4  | Analysis of overhead of communication      | 68 |

|              | 5.5  | Conclusion                                 | 70 |

| 6            | Cor  | nclusion                                   | 71 |

|              | 6.1  | Contribution                               | 72 |

|              | 6.2  | Limitations                                | 72 |

|              | 6.3  | Perspectives                               | 73 |

| $\mathbf{A}$ | ppen | dices                                      | 79 |

# Appendices

# List of Figures

| 1   | Vue globale de STEPOCL.                                                      | 4  |

|-----|------------------------------------------------------------------------------|----|

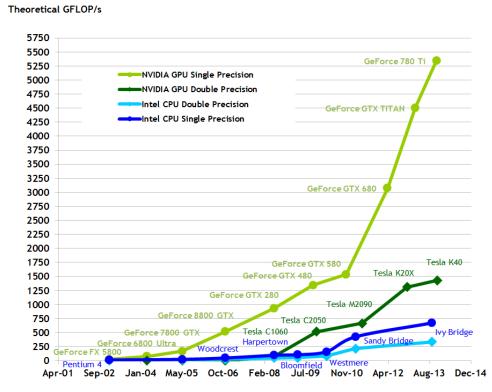

| 2.1 | A basic diagram of a dual-core processor                                     | 6  |

| 2.2 | Floating-Point Operations per Second for the CPU and GPU.                    | 7  |

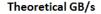

| 2.3 | Memory bandwidth for the CPU and GPU.                                        | 8  |

| 2.4 | The GPU devotes more transistors to data processing.                         | 9  |

| 2.5 | Intel Xeon Phi microarchitecture.                                            | 11 |

| 2.6 | Theads model                                                                 | 12 |

| 2.7 | Host-accelerator model                                                       | 13 |

| 2.8 | Data Partitioning in homogeneous way                                         | 19 |

| 2.9 | Comparison of original kernel and partitioned kernel                         | 20 |

| 3.1 | OpenCL Platform Model (image source: KHRONOS group)                          | 24 |

| 3.2 | OpenCL Work-Groups and Work-Items.                                           | 25 |

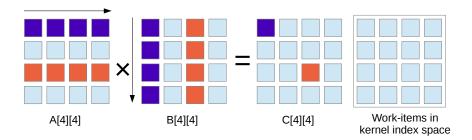

| 3.3 | Matrix production on single device                                           | 28 |

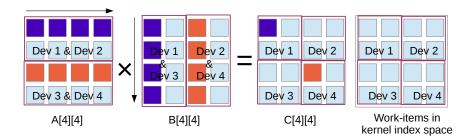

| 3.4 | Matrix production on multiple device                                         | 29 |

| 3.5 | Data consistency                                                             | 29 |

| 3.6 | Overview of the STEPOCL environment.                                         | 31 |

| 3.7 | Device management: using different kernel                                    | 35 |

| 3.8 | Device management: using a common kernel                                     | 36 |

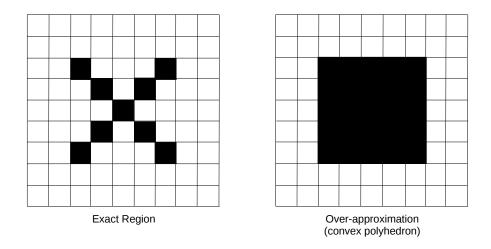

| 4.1 | Over-approximated analysis                                                   | 40 |

| 4.2 | Workload partitioning for multi-device platform with single context $\ldots$ | 45 |

| 4.3 | Workload partitioning for multi-device platform with multiply contexts .     | 45 |

| 4.4 | Available data partitioning over multiple devices                            | 46 |

| 4.5 | Data partition with ghost region                                             | 47 |

| 4.6 | The process of Data partition                                                | 48 |

| 4.7 | Overview of the load balancing algorithm used in the STEPOCL runtime.        | 49 |

| 4.8 | Ping-pong effect of workload adjustment.                                     | 49 |

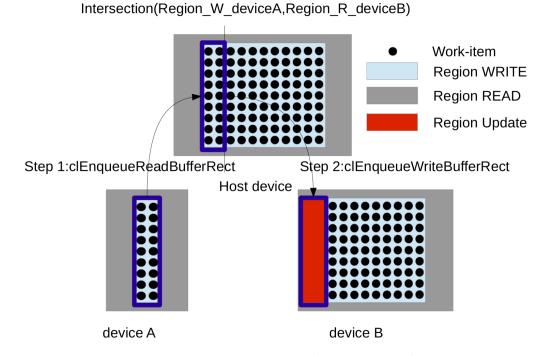

| 4.9 | Data transmission between two devices                                        | 51 |

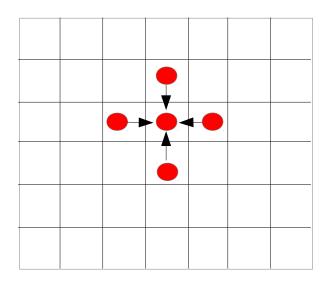

| 5.1 | 5-point 2D-stencil computation                                               | 56 |

| 5.2 | the structure of generated 2D stencil code                                   | 63 |

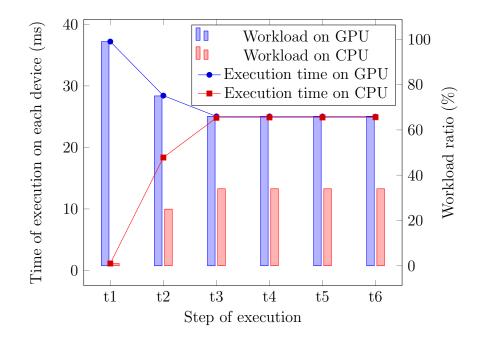

| 5.3 | Workload adjustment performance of the 3D-stencil application                | 65 |

| 5.4 | Performance of the 5-point 2D-stencil application. The horizontal axis       |    |

|     | corresponds to the size the input and output matrices required to solve      |    |

|     | the problem.                                                                 | 66 |

| 5.5 | Performance of the matrix multiplication application. The horizontal axis |    |

|-----|---------------------------------------------------------------------------|----|

|     | corresponds to the summed size of the $A, B$ , and $C$ matrices           | 67 |

| 5.6 | Performance of the N-body application.                                    | 68 |

| 5.7 | Partitioning data by column                                               | 69 |

| 5.8 | Partitioning data by row                                                  | 69 |

| 5.9 | Data partition of a 2D table                                              | 70 |

| 6.1 | Distributions of a 2D table on 4 devices                                  | 73 |

# List of Tables

| 4.1 | PIPS overview                                                               | 40 |

|-----|-----------------------------------------------------------------------------|----|

| 4.2 | OpenCL scalar data type                                                     | 42 |

| 4.3 | OpenCL vector data type                                                     | 43 |

| 4.4 | Get information about an OpenCL device                                      | 44 |

| 4.5 | read and write buffer objects                                               | 50 |

| 5.1 | Generated STEPOCL code size (in lines)                                      | 62 |

| 5.2 | Distribution of the lines of code of the generated 2D stencil application . | 62 |

| 5.3 | Experimental platform outline.                                              | 64 |

| 5.4 | Relative performance of STEPOCL as compared to a native OpenCL              |    |

|     | implementation on HANNIBAL.                                                 | 65 |

# Chapter 1 Introduction

Que peu de temps suffit pour changer toutes les choses.

-Victor Hugo

| Contents |                          |   |

|----------|--------------------------|---|

| 1.1      | Objective of thesis      | 2 |

| 1.2      | Outline and contribution | 3 |

Since the first general-purpose electronic computer ENIAC was created in 1946, scientists have never stopped the pace of creating new computers with higher performance and computational power. Scientists had kept enhancing the performance by increasing CPU frequency and complexity of CPU architecture until they meet the bottleneck of heat dissipation. Meanwhile, integrated circuit transistor technology has almost reached its physical limit. The number of transistors contained in processor chip can be used as a rough estimate of its complexity and performance. *Moore's law* which is an empirical observation states that the number of transistors of a typical processor chip doubles every 18 to 24 months. However today, there is not much space for increasing the density of transistors in a single CPU chip, because extreme miniaturization of electronic gates makes the effects of phenomena like electromigration and subthreshold leakage become much more significant [24]. These factors make scientist to investigate new solutions: parallelism.

Instead of using single high frequency unit, the trend of computer architecture has turned to use more but relatively slow processing units (multi-core processors). In the early 2009s, most desktop CPUs have become multi-cores. Since then, more and more types of multi-core processor have been used in general purpose computing and heterogeneous architectures which are usually composed of a host multi-core processor (CPU) and some auxiliary specially designed processors (called accelerators, such as GPU and Intel Xeon Phi) have become very important in the domain of high performance computing. In Top500 [5] fastest supercomputer lists of 2015, both Tianhe-2 (ranked as No. 1) and Titan (ranked as No. 2) used different type of processors: Tianhe-2 consists of 32,000 Intel Xeon CPUs and 48,000 Intel Xeon Phi coprocessors; Titan consists of 18,688 AMD Opteron CPUs and 18,688 Nvidia Tesla GPUs. Compared to homogeneous architectures, heterogeneous architectures have greater advantage on computing performance. These systems gain performance not just by adding cores, but also by incorporating specialized processing capabilities to handle particular tasks. Heterogeneous architectures utilize multiple processor types to benefit the best of each devices. For example, GPU processing, apart from its well-known 3D graphics rendering capabilities, can also perform mathematics computations on very large data sets, while CPUs can run the operating system and perform traditional serial tasks, such as data transfer management. Moreover, GPU and Xeon Phi have vector processing capabilities that enable them to perform parallel operations on very large sets of data at much lower power consumption relative to the serial processing of similar data sets on CPUs. Followed with the rise of heterogeneous architectures, applications such as augmented reality, rich media composition, numerical simulations makes heterogeneous architectures usage more productive.

However the development of such applications is a challenge due to the usage of various hardware and many APIs (application program interface) together with a goal for power-performance efficiency. Designing applications for multi-accelerator heterogeneous systems requires that developers have rich experience of parallel programming and some strong knowledge of architectures. Firstly, developers need to choose the most appropriate set of computing devices for a given application. Then they have to write compute kernels optimized for the selected accelerators. In order to achieve the best possible performance, the developer has to identify an efficient partitioning of the workload among the accelerators. This efficient partitioning is not only related to the theoretical performance of the accelerator, but also to the actual application and its workload. Then, the developer has to write code to coordinate the execution of multiple kernels running on different devices, to partition the workload among them and to perform data movements and synchronization between them. Implementing these features is time-consuming and error-prone. Moreover, the developer often implements these features for a specific hardware and has to drastically modify his code for a different target.

As we will present in this documents, existing programming tools for heterogeneous architectures typically define APIs to deploy and execute *compute kernels* on the processing units of accelerators, however, none of these programming tools are tailored for multi-accelerator application development. The challenges mentioned above are still left for developers to resolve.

# 1.1 Objective of thesis

The main objective of this thesis is to study heterogeneous computing at programming level and to propose a unified system that could automatically generate code for heterogeneous multi-device architectures. We want to relief the developers from tedious and time consuming coding process, and make them more focus on solving the problem itself.

More specifically, this thesis will focus on studying how to solve following problems:

- How to split and distribute a parallel task to multiple devices;

- How to automatically balance the workload of whole system and manage the communications between devices;

• How to automatically generate the whole application without too much coding effort.

# **1.2** Outline and contribution

Chapter 2 introduces the state of the art of heterogeneous computing including the computing devices equipped on current heterogeneous architectures and programming tools for developing applications.

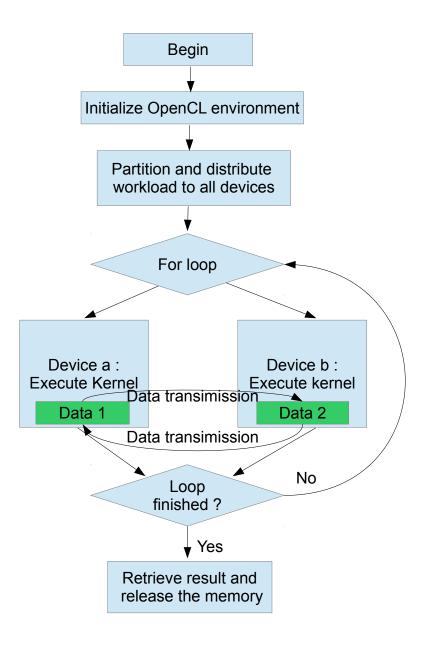

In Chapter 3, we first introduced the background of OpenCL which is the basis of our main work. Then we presented our contribution: a new programming tool called STEPOCL. STEPOCL separates the functional aspects of the code, *i.e.*, the compute kernels, from the non-functional ones. The non-functional aspects of the code are described in a domain specific language. It mainly consists in describing the data layout and the kernel of the application. Using a domain specific language improves the productivity of the developer by decreasing the number of lines of codes required to implement a full multi-device application. Moreover, the code written in the domain specific language is not limited to a specific hardware setting, which increases the portability of the code. Finally, it also has the advantage of avoiding many errors caused by the use of a low-level language. Based on the compute kernels and on the description of the non-functional aspects, STEPOCL automatically generates a full OpenCL application, but also an offline profiler for this application. The profiler computes an efficient workload partitioning for a specific set of accelerators and a specific workload. The generated application handles the initialization of the OpenCL environment, which includes the discovery of the accelerators, the mapping of the data to the accelerators according to the offline profiling results, and the launch of the kernels over the accelerators. During execution, the generated application also automatically exchanges the data between the accelerators to maintain the data consistency thanks to a polyhedral data analysis, and, at the end of the execution, the generated application retrieves the results from the accelerators.

Chapter 4 introduces the implementation of main modules of STEPOCL including analysis of region, offline profiling, runtime system and code generation. These modules ensure that the generated applications can profit the full potential of any multiple devices heterogeneous architectures.

Chapter 5 presents the evaluation of generated applications. We evaluate STEPOCL with three application kernels (a 5-point 2D-stencil, a matrix multiplication and an N-body application) on two multi-device heterogeneous machines that combine CPUs with different accelerators: CPU+GPUs and CPU+Xeon Phis. Our main results show that:

- When running on multiple heterogeneous devices <sup>1</sup>, the performance of the code generated by STEPOCL scales linearly with the number of devices.

- As compared to the same applications written directly in OpenCL and provided with the OpenCL version of AMD, the applications written with STEPOCL have similar performance.

- Thanks to STEPOCL, we are able to run large workloads on multiple devices that do not fit in the memory of a single device.

<sup>&</sup>lt;sup>1</sup>A device is either a CPU or an accelerator.

• As compared to the generated code, STEPOCL is able to divide by ten the number of lines of code of the application. Also as compared to the native OpenCL applications, STEPOCL is able to divide by five their number of lines of code. Furthermore, while the applications shipped with the OpenCL version of AMD only runs on a single device, the STEPOCL applications are able to run on multiple heterogeneous devices.

At last, chapter 6 concludes the whole works of this thesis and presents future work.

# Chapter 2

# The rise of heterogeneous computing

Essayez de ne pas devenir un homme de succès, mais plutôt essayez de devenir un homme de valeur.

—Albert Einstein

## Contents

| 2.1        | Hete            | erogeneous platforms                     | 5         |

|------------|-----------------|------------------------------------------|-----------|

|            | 2.1.1           | Multi-core processor                     | 6         |

|            | 2.1.2           | GPU computing                            | 6         |

|            | 2.1.3           | Intel Xeon Phi                           | 7         |

|            | 2.1.4           | AMD APU                                  | 8         |

| <b>2.2</b> | $\mathbf{Expl}$ | oitation of heterogeneous architectures  | 9         |

|            | 2.2.1           | Computing on CPUs                        | 9         |

|            | 2.2.2           | Computing on accelerators                | 13        |

|            | 2.2.3           | Computing on heterogeneous architectures | 16        |

| 2.3        | Cone            | clusion                                  | <b>21</b> |

This chapter introduces heterogeneous computing from two aspects: hardware architecture and programming on heterogeneous architectures.

# 2.1 Heterogeneous platforms

A computer is usually equipped with two types of processor: CPU (central processing units) and GPU (graphics processor unit). Before the 1990s, CPUs still play important role in massive computing while GPUs are merely displaying the monitor. In order to improve the performance of computers, engineers focused on improving the performance of CPU mainly by increasing in the frequency and complicating the architecture (mainly by using more transistors on a CPU die). However, if the frequency gets too high, the

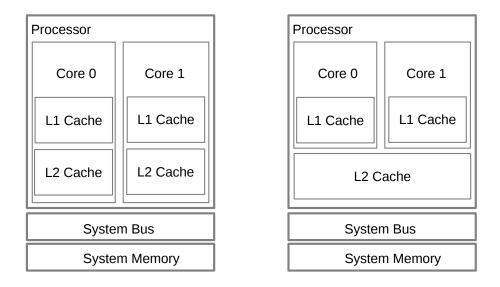

(a) Multi-core processor seperate L2

(b) multi-core processor shared L2

chip will melt by the extreme heat. That's the reason why most current CPUs runs about 2 GHz to 3 GHz, but not more than 4GHz. Meanwhile, due to the physical limit, increasing the density of transistor on a single chip also meet the bottleneck.

### 2.1.1 Multi-core processor

In order to keep improving the performance over the last 10 years, engineers found other ways – using more CPU cores on the same CPU chip. Figure 2.1 presents two typical multi-core processor architectures. The advantage of multi-core processors is that multiply tasks (such as running a software or scientific computation) can be dispatched to different CPU core, each core can work at relatively low frequency but we can still get a faster experience. The dual core CPUs and quad core CPUs on the market today are good enough for regular tasks in daily life. However, for scientists and engineers, CPUs are still not powerful enough. Meanwhile, GPUs, due to their special architecture and extraordinary data parallel processing ability, have become very important in the domain of high performance computing.

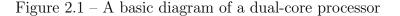

## 2.1.2 GPU computing

The original GPUs were designed to rapidly render images in a frame buffer intended for output to a display. In the last 20 years, the improvement of GPUs have been primarily driven by the demand for realtime, high-definition graphic, the evolution of GPU hardware architecture has gone from a specific single core, function hardware pipeline implementation made only for graphics, to a set of parallel and programmable cores for more general purpose computations [22]. Modern GPU has become a highly parallel, multithreaded, manycore processor with tremendous computational horsepower and very high memory bandwidth, as illustrated by Figure 2.2 and Figure 2.3.

Figure 2.2 – Floating-Point Operations per Second for the CPU and GPU.

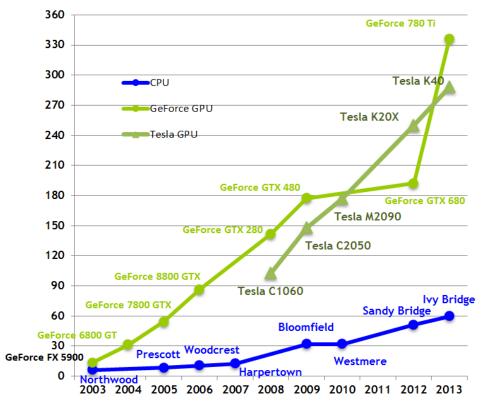

The reason behind the difference of floating-point capability between the CPU and the GPU is that the architecture of modern GPU is specialized for compute-intensive, highly parallel computation – exactly what graphics rendering is about – and therefore designed such that more transistors are devoted to data processing rather than data caching and flow control, as illustrated by Figure 2.4.

More specifically, the GPU is well designed for dealing with the problems that can be expressed as data-parallel computations (the same program is executed on many data elements in parallel). Because the same program is executed for each data element, there is a lower requirement for sophisticated flow control and because it is executed on many data elements and has high arithmetic intensity, the memory access latency can be hidden with calculations instead of big data caches. Many applications that process large data sets can use a data-parallel programming model to speed up the computations, from image rendering or signal processing to physics simulation or computational biology. The success of GPU computing opened a new page of heterogeneous computing, and new accelerators (such as Intel Xeon Phi [26]) begin to emerge.

## 2.1.3 Intel Xeon Phi

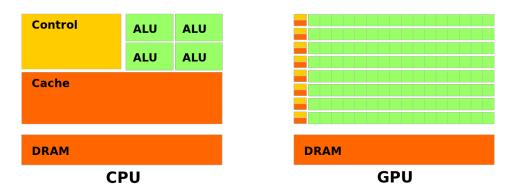

Intel Xeon Phi Coprocessor is the brand name for all Intel Many Integrated Core Architecture (Intel MIC Architecture) based products. The Intel Xeon Phi coprocessors are

Figure 2.3 – Memory bandwidth for the CPU and GPU.

designed to extend the reach of applications that have demonstrated the ability to fully utilize the scaling capabilities of Intel Xeon processor-based systems and fully exploit available processor vector capabilities or memory bandwidth. Compared to traditional Intel Xeon processor, the Intel Xeon Phi coprocessors provide extra power-efficient scaling, vector support, and local memory bandwidth. Each Intel Xeon Phi coprocessor equips more than 50 cores (it varies between generations) interconnected by a high-speed bidirectional ring as presented in Figure 2.5. Each core has four hardware threads and clocked at 1 GHz or more. The many core architecture makes Intel Xeon Phi coprocessors competitive with GPUs on the performance of parallel computing. Moreover, Intel Xeon Phi coprocessor offers more programmability. Applications that show positive results with GPUs should always benefit from Intel Xeon Phi coprocessors because the same fundamentals of vectorization or bandwidth must be present. The opposite is not true, the flexibility of an Intel Xeon Phi includes support for applications that cannot run on GPUs [18].

## 2.1.4 AMD APU

Current CPUs and GPUs have been designed as separate processing elements, each has a separate memory space. In order to launch an execution on GPU, the required data located on CPU memory needs to explicitly be copied to GPU memory and then copied

Figure 2.4 – The GPU devotes more transistors to data processing.

back again. AMD Accelerated Processing Unit (APU) used **Heterogeneous System Architecture (HSA)** that integrates CPU and GPU on the same bus with unified shared main memory. As a result, APU performs zero data movement between CPU, GPU and other accelerators. The design of unified memory reduces communication latency between CPU and other accelerators. Moreover, unified memory is more practical on programming level.

# 2.2 Exploitation of heterogeneous architectures

Since heterogeneous architectures become more and more popular, the computing community is building tools and libraries to ease the use of these heterogeneous systems.

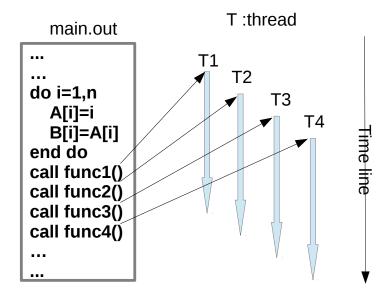

## 2.2.1 Computing on CPUs

The parallelism of a computer program on multi-core CPUs can be achieved through using threads model. In threads model, a parallel main program can have multiple concurrent execution paths, and each path is executed by a thread. In Figure 2.6, program **main.out** initializes two arrays, and then creates four tasks (threads), each tasks will be scheduled and run by operating system concurrently. Each thread has local data and shares a global memory. The synchronization mechanism are usually applied to avoid the conflict of operation on same global memory address, such as avoiding that several threads update the same global address at same time.

#### Pthreads

**Pthreads** is a POSIX (Portable Operating System Interface) standard [4] for threads. It provides an API (Application Programming Interface) for creating and manipulating threads. **Pthreads** is implemented in a pthread.h header and a thread library. Although **Pthreads** only supports C language, it is available on many mainstream operating systems such as FreeDSB, Linux, Mac OS x and Windows.

The example in Listing 2.1 creates 4 threads with *pthread\_create* function, and each thread prints its own *id*. Listing 2.2 shows the execution result in Listing 2.2.

Listing 2.1 – Pthreads application in C

```

#include <pthread.h>

#include <stdio.h>

#define NUM_THREADS 4

void *print_thread_id(void *argument)

{

long thread_id;

thread_id = (long) argument;

printf("I_am_thread_%ld!\n", thread_id);

pthread_exit(NULL);

}

int main(int argc, char *argv[])

{

pthread_t thread [NUM_THREADS];

int err;

long t;

for (t=0; t < NUMLTHREADS; t++)

{

printf("Creating_thread_%ld! n", t);

err = pthread_create(&thread[t],NULL,print_thread_id,(void *)t);

if(err){

printf("ERROR! \ n");

exit(-1);

}

}

pthread_exit (NULL)

}

```

Listing 2.2 – Execution result

|  | Creating thread 0! |  |

|--|--------------------|--|

|  | Creating thread 1! |  |

|  | I am thread 0!     |  |

|  | Creating thread 2! |  |

|  | Creating thread 3! |  |

|  | I am thread 1!     |  |

|  | I am thread 2!     |  |

|  | I am thread 3!     |  |

|  |                    |  |

Figure 2.5 – Intel Xeon Phi microarchitecture.

## OpenMP

OpenMP is an API that supports multi-platform shared memory multiprocessing programming in C, C++ and Fortran. As an industrial standard, OpenMP can run on most platforms including Linux, Mac OS X and Windows platforms. OpenMP program is composed of a set of compiler directives, runtime library routines and environment variables. OpenMP uses the fork-join model of parallel execution. At the beginning, OpenMP program starts as a single thread: the master thread. The master thread executes sequentially until it reaches the parallel region construct. The master thread then creates a group of parallel threads to execute the statements that are enclosed in parallel region construct. Once the group of threads finish the execution of the statements in parallel region construct, they will be synchronized and deleted, leaving only a master thread.

OpenMP directives can be inserted directly into serial code and achieve a considerable improvement of performance. Listing 2.3 presents a program that initiates a table with multiple threads. The number of threads used can be defined as environment variables. Listing 2.4 presents an example of setting OpenMP environment. In this case, eight threads will be used to initialize in parallel *tableA* of Listing 2.3.

Listing 2.4 – Setting OpenMP environment variables

| L1501115 2.4             | betting Openiui |  |

|--------------------------|-----------------|--|

| export OMP_NUM_THREADS=8 |                 |  |

Figure 2.6 – Theads model

OpenMP is well suited for shared memory multi-core architectures. However, if programmers want to use more computing resources such as multiple nodes on large-scale clusters, they have to use other APIs, such as MPI [11] (Message Passing Interface), to manage computation and communication on distributed memory environment.

#### STEP and dSTEP

STEP [23] is an OpenMP directives based programming tools that transforms a program into an MPI source program and produces MPI code close to hand-written MPI code. It is developed by HP2 (Haute Performance et Parallélisme) team of TELECOM SudParis. The programmer adds OpenMP directives and then STEP generates a MPI program automatically. STEP extends the usage of OpenMP (which is restricted to

Listing 2.3 – Initializing a table in parallel

shared-memory architectures) to distributed-memory architectures such as clusters of many-cores. Thanks to the region analysis of compiler PIPS [16], STEP can efficiently generate the communications between devices. Habel et al. improved the data partitioning module of STEP, and named the new tool as dSTEP [13]. dSTEP provides a large set of distribution types for data partitioning. These distribution types are unified in a "dstep distribute" directive. It also provide a "dstep gridify" directive to express the computation distribution and the schedule constraints of loop iterations.

At the beginning of this thesis, the main limitation of STEP and dSTEP is that they do not fully support the computation on the accelerators such as GPUs and Intel Xeon Phi (dSTEP supports CUDA). Besides, the data partitioning of dSTEP is homogeneous: every sub-data has same size. Considering the varieties of hardware performance of computing devices, a homogeneous data partitioning may lead to poor performance.

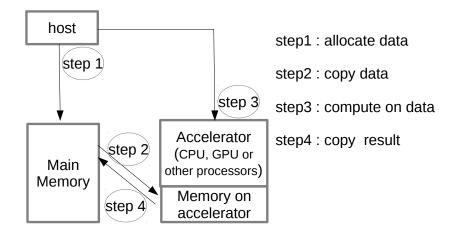

### 2.2.2 Computing on accelerators

Some programming platforms provide accessibility to multiple type accelerators such as GPU and co-processors. Different from multi-core CPU architecture, the memory on the accelerator may be completely separated from main memory (which is shared by multi-core CPU). Most of programming platforms for diverse computing resources use an *offload* model which includes a single **host** and one or more **accelerators** which can be any kind of processor (CPU, GPU and Xeon Phi etc.). Figure 2.7 presents a processing flow of an *offload* model. First of all, developers allocate data region on main memory (host memory). Then data region are transferred from main memory to remote memory on accelerators. In the third step, the host instructs the process to accelerators, accelerators execute computing functions submitted from host. At last, the results are copied to main memory. Due to the fact that accelerators do not share a common memory, programmers have to manually maintain the consistency of data in each remote memory.

Figure 2.7 – Host-accelerator model

Listing 2.5 – The syntax of OpenACC directives

```

#define SIZE 1000

float a[SIZE];

float b[SIZE];

int main()

{

int i;

// Initialize arrays.

for (i = 0; i < SIZE; ++i) {

a[i] = (float)random()\%1000;

b[i] = 0.0 f;

}

// 1D stencil computing

#pragma acc kernels copyin(a) copy(b)

for (i = 1; i < SIZE - 1; ++i) {

b[i] = (a[i-1]+a[i]+a[i+1])/3

}

return 0;

}

```

### CUDA

CUDA (Computer Unified Device Architecture) is a parallel computing platform and programming model created by NVIDIA [1]. It allows software developers to benefit the computing performance of CUDA-enable GPU for general purpose processing.

The CUDA platform is composed of CUDA libraries and compiler directives. CUDA supports several industry-standard programming language including C, C++ and Fortran. Unlike OpenMP which achieves parallelism by inserting directives on serial code, CUDA users need to define specific functions (called kernel) for GPU computing. A kernel is executed by a number threads, each having a unique *threadID*. CUDA organizes threads into a hierarchy of a grid of thread blocks. A grid contains a set of thread blocks with unique *bockID*, and each blocks contains same amount of threads. The threads in a block can access to a shared memory space private to the block and can be synchronized through synchronization function.

CUDA supports most of operating systems such as Microsoft Windows, Linux and Mac OS. However, CUDA only works with Nvidia GPUs.

### **OpenACC**

OpenACC (Open Accelerators) [29] is a programming standard for programming on heterogeneous CPU/GPU systems in C/C++ and FORTRAN. OpenACC standard is developed by Nvidia, Cray, CAPS and PGI. Similar to OpenMP, OpenACC provides a set of compiler directives to specify parallel regions, control flow instructions on accelerators and manages data movements on remote memory of accelerators.

Listing 2.5 presents an example of an OpenACC program that performs a 1D 3-points stencil computation with *offload* mode. The OpenACC directives in Listing 2.5 tells the

```

numgpus = acc_get_num_devices( acc_device_nvidia );

#pragma omp parallel num_threads(numgpus)

{

gpunum = omp_get_thread_num();

acc_set_device_num( gpunum, acc_device_nvidia );

#pragma acc data copy( x[0:n] )

{

// thread tnum copies x to GPU gpunum

... ...

}

}

... ...

}

```

compiler following information:

- #pragma acc: This is an OpenACC directive.

- *kernels*: This is a parallel regions (also called kernel region), which contains work-sharing loops.

- copyin(a): Array a needs to copied from the host memory to the device memory.

- copy(b): Array b needs to copied from the host memory to the device memory, and the assigned value of array b on device memory needs to be copied back to the host.

As we can see from Listing 2.5, OpenACC eases the way we program on heterogeneous architectures. However, OpenACC is not suited to multiply device programming. In order to concurrently use multiple GPUs on a machine, programmers have to mix OpenACC with other API (such as OpenMP or MPI [11]). Listing 2.6 presents an example of OpenACC program using multiple Nvidia GPU. By using OpenMP directives, each OpenMP thread uses a different GPU. Then, programmers have to manage workload balancing, data movement and communications with hybrid directives (OpenMP and OpenACC directives) which is quite confusing and error-prone.

#### OpenCL

OpenCL is designed for writing programs that execute across heterogeneous platforms consisting of CPUs, GPUs, field-programmable gate arrays (FPGAs) and other processors. As an open standard maintained by Khronos Group, OpenCL is supported by most of hardware manufacturers such as Apple, IBM, Intel, Nvidia, Qualcomm, Samsung, etc. OpenCL is also supported by most computer systems, such as Windows, Linux and Unix.

OpenCL also defines computing functions as *kernels* for the execution on *compute* device. A work-item in OpenCL plays the same role as a thread in CUDA. Work-items

are organised into work-groups. OpenCL achieves parallelism by simultaneously executing kernel by each work-item. A main purpose of OpenCL is to unify the programming model of heterogeneous platforms. OpenCL views a processor of any type (CPU, GPU, FGPAs ...) on a machine as a *compute device*. All devices are logically defined a common abstract memory hierarchy. Thus an OpenCL program is portable across different platforms, although the performance has not necessarily the same portability. Our main works in this thesis are based on the OpenCL framework and our primary objective is to improve the portability of performance of OpenCL applications. More details about OpenCL is presented in Section 3.1.

### 2.2.3 Computing on heterogeneous architectures

Although some programming languages can natively support using multiple computing resources, many studies further provide facility to exploit full power of heterogeneous architecture.

#### Bolt C++ Template Library

Bolt [2] is an OpenCL-based C++ template library optimized for GPUs. Compared to Standard OpenCL API, Bolt provides a more simplified STL-like interface, it can directly interact with host memory structures such as *std::vector* or host arrays (e.g. float\*). Bolt also provides common optimized routines like sort(), reduce(). The library itself can select automatically where to execute such a routine (GPU or CPU). No OpenCL API calls are required since Bolt library handles all initialization of the OpenCL environment and the communication between devices. Listing 2.7 presents how to use Bolt to sort a random array. However, the usage of Bolt is limited to built-in routines and it is only available on AMD devices.

Listing 2.7 – Sort a random array with Bolt

```

#include <bolt/cl/sort.h>

#include <vector>

#include <algorithm>

int main()

{

// generate a random array on host

std::vector<int> array(1024);

std::generate(array.begin(), array.end(), rand);

// sort, run on best device in the platform

bolt::cl::sort(array.begin(), array.end());

return 0;

}

```

#### Boost.Compute

Boost.Compute [3] is a GPU/parallel-computing library for C++ based on OpenCL. It provides an STL-like C++ interface which is very similar to Bolt. It contains common algorithms (e.g. transform(), sort()) along with common containers (e.g. vector<T>,

flat\_set<T>). In Boost.Compute, the interaction between host and computing devices is managed by an object of the *command\_queue* class which corresponds *clCommandQueue* in standard OpenCL. Listing 2.8 presents how to use Boost.Compute to sort a random array. Boost.Compute as well as Bolt is very well suited for implementing data initializations or launching tasks with existed built-in routines. However, expressing some tasks which require more complicated data structures cannot be supported. The studies of Peter et al. [25] also prove that Boost.Compute and Bolt provide high compute performance for simple tasks, but very low performance for complex tasks.

Listing 2.8 – Sort a random array with Boost.Compute

```

#include <vector>

#include <algorithm>

#include <boost/compute.hpp>

namespace compute = boost :: compute;

int main()

{

// get the default compute device

compute::device gpu = compute::system::default_device();

// create a compute context and command queue

compute::context ctx(gpu);

compute::command_queue queue(ctx, gpu);

// generate random numbers on the host

std::vector<float> host_vector(1024);

std::generate(host_vector.begin(), host_vector.end(), rand);

// create vector on the device

compute::vector<float> device_vector(1024, ctx);

// copy data to the device

compute::copy(host_vector.begin(), host_vector.end(),

device_vector.begin(), queue);

// sort data on the device

compute::sort(device_vector.begin(),

device_vector.end(), queue);

// copy data back to the host

compute::copy(device_vector.begin(), device_vector.end(),

host_vector.begin(), queue);

return 0;

}

```

#### BOAST

BOAST [10] is an automatic source-to-source transformation tool which optimizes loop structures in order to find the best performance configuration for a given type of computing resource. According to the configurations which are defined by users, BOAST can generate code in C or Fortran. The main interest for our work is the idea of architecturespecific optimization used in BOAST. Due to the difference of hardware features on heterogeneous architectures, the generic methods of code transformation may lead to a poor performance. In order to optimize the performance for a specific architecture, we have to tune the code accordingly. The techniques of code transformation could also be used for the optimization of OpenCL kernel in our future works.

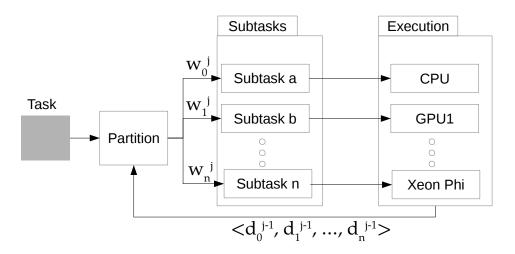

#### StarPU

StarPU [6] is a software that helps programmers to exploit the computing power of heterogeneous multi-device architectures. StarPU is a C library. The core component of StarPU is a run-time support library which is used for scheduling the tasks on heterogeneous multi-core systems. An execution of StarPU is defined by two data structures: **codelet** and **task**. A **codelet** describes a computational kernel and indicates runnable architectures such CPUs or GPUs. A **task** describes which data can be accessed by **codelet**. Once a **task** is submitted, StarPU will automatically assess accessibility of computing resources and will schedule the task to ensure load balancing over heterogeneous systems.

StarPU has implemented a rich set of scheduling policies such as **eager**, **random** and **heft** (heterogeneous earliest finish time), etc. These features provide great facility for the implementation of task-parallel applications. However, StarPU is not perfect at partitioning data-parallel tasks. StarPU provides an interface which can partition a data region homogeneously, however a perfect partition should consider the diversity of performance of available computing devices, then partition the data region in appropriate proportion. Moreover, programmers still have to manually manage communication and consistency of data which is time-consuming and error-prone.

StarPU provides an OpenCL extension called SOCL [14]. Unlike a standard OpenCL application, SOCL is not dedicated to a specific kind of device nor to a specific hardware vendor, it virtualizes all existing available devices (CPUs and GPUs) as one unique OpenCL device on a unified OpenCL Platform. Thus, programmers no longer need to create extra OpenCL context and OpenCL command queues for each CPU or GPU, all computing kernel just go to only one command queue which is responsible for the execution on virtual machine. Once computing kernels are submitted, SOCL transparently distributes computing kernels over physical devices at runtime.

As an extension of StarPU, SOCL provides powerful automatic scheduling abilities on heterogeneous architectures and simplified the programming interface of OpenCL. But the key issues are still unsolved. SOCL is still not able to handle workload partition of data-parallel tasks and manage the data consistency between devices.

#### libWater

libWater [12] is a C/C++ library-based extension of the OpenCL programming model that aims to alleviate programming process on large-scale clusters. libWater simplified the programming interface of OpenCL and introduces a new device query language (DQL) for accessing distributed devices on different compute nodes. Listing 2.9 presents the basic syntax of DQL.

|           | Listing 2.9 – DQL of indwater   |

|-----------|---------------------------------|

| SELECT    | [ALL   TOP k   POS i]           |

| FROM NODE | [n [,]]                         |

| WHERE     | [restrictions attribute values] |

| ORDER BY  | [attribute [,]]                 |

Listing 2.9 – DQL of libWater

libWater eliminates and replaces some redundant OpenCL instruction ( such as the initialization of OpenCL platforms and contexts) by its own API which allows programmers to more focus on the development of computing kernels. Meanwhile, the distributed runtime system of libWater dispatches the OpenCL commands to the addressed devices and transparently moves data across the cluster nodes. libWater also enhances the event system of OpenCL by enabling inter-context and inter-node device synchronization and improves the efficiency of runtime system by analysing the collected event information. Although libWater provides a convenient interface to access the distributed devices and dispatch the work task on large-scale clusters, it has not yet provided any solution for workload partition which is also a big problem for programmers.

#### Kim's framework for multiple GPUs

Kim et al.[20] propose an OpenCL framework to manage multiple GPUs within a node. This OpenCL framework combines multiple GPUs as a virtual single GPU. Programmers only need to provide an application for single GPU, the framework takes in charge the deployment of the code on the multiple GPUs transparently by partitioning the workload equally among the different devices. In order to partition the workload precisely, the runtime system applies a run-time memory access range analysis to the kernel by performing a sampling run and identifies an optimal workload distribution for the kernel. The sampling code is generated from the OpenCL kernel code by using a OpenCL-C-to-C translator, it only accesses to memory and performs no computation. Meanwhile, the runtime maintains virtual device memory that is allocated in the main memory and keeps it consistent to the memories of the multiple GPU devices. They also use an OpenCL-Cto-CUDA-C translator to generates the CUDA kernel code for the distributed OpenCL kernel.

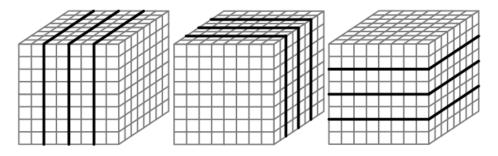

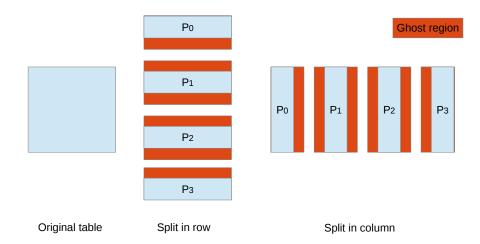

Figure 2.8 – Data Partitioning in homogeneous way

However Kim et al. only focuse on homogeneous multiple device systems and data independent tasks. Their OpenCL framework can not work with heterogeneous devices. Due to the diversity of performance between devices, an equal data partitioning (such as Figure 2.8) can not efficiently exploit full computing power of heterogeneous multi-device systems. Moreover the overhead of sampling run and the overhead of translation from OpenCL-C kernel to CUDA are not negligible.

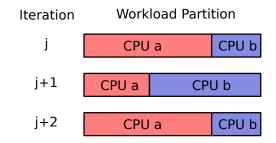

#### SKMD

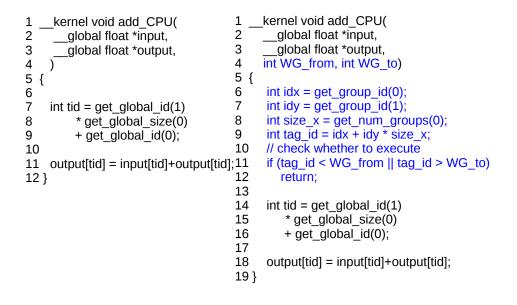

Lee Janghaeng et al. propose a tool, called SKMD, that generates multi-device source code from a single-device kernel [17]. This system transparently orchestrates collaborative execution of a single data-parallel kernel across multiple asymmetric CPUs and GPUs. The programmer is responsible for developing a single data-parallel kernel in OpenCL, while the system automatically partitions the workload across an arbitrary set of devices, generates kernels to execute the partial workloads, dynamically adjusts the workload across devices and merges the partial outputs together.

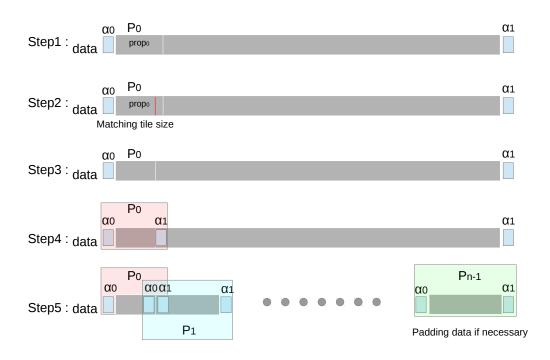

SKMD implements workload partition through assigning partial work-group on original kernel. As showed in figure 2.9, SKMD adds two parameters  $WG\_from$  and  $WG\_to$  to represent a target range of work-group index to be computed on a device. In other world, each computing device only runs ( $WG\_from - WG\_to + 1$ ) work-groups of the kernel. At end of the execution, SKMD also utilises these two parameters to retrieve the computing result from discrete device memory.

Figure 2.9 – Comparison of original kernel and partitioned kernel

To do so, SKMD duplicates all data on every device. Thus each device needs to allocate all the data, even if the device will not use it. This unnecessary memory redundancy for the whole system limits the problem size.

#### InsiemeTP

Klaus Kofler et al. [21] propose an approach to automatically optimize task partitioning for different problem sizes and different heterogeneous architectures. They use the Insieme[19] source-to-source compiler to translate a single device OpenCL program into a multi-device OpenCL program.

The architecture of their framework consists of two main phases: *training* and *deployment*. At the training phase, a set of applications is executed with different partitioning strategies. The statistics (including static program features, runtime feature and the time of execution) of each execution is used for building a task partitioning prediction model. The prediction model is based on Artificial Neural Networks approach. At the deployment phase, the Insieme compiler analyse the static feature of input code and translate it into a multi-device version. After analysing the static feature of input code, prediction model will predict the best task partitioning, and the runtime system will take charge of the remaining execution.

However, due to the limitation of training set, the prediction model still need to be improved. Moreover, The framework proposed by Klaus Kofler et al. didn't provide any mechanism to ensure data consistency.

# 2.3 Conclusion

In this chapter, we have introduced existing standard programming languages and programming tools for heterogeneous architectures. Considering the performance and portability [28, 7, 27] of existing programming language, only OpenACC and OpenCL are supported by many vendors. However OpenACC is not suited to multi-accelerator architectures. Most of existing programming tools are designed for one specific problem which is not convenient enough for novice programmers. In our research, we proposed a programming tool STEPOCL that generates optimised OpenCL code for heterogeneous multi-device architectures. STEPOCL guarantees the portability and performance of OpenCL applications.

# Chapter 3 STEPOCL

L'homme qui sait réféchir est celui qui a la force illimitée.

*—Honoré de Balzac*

### Contents

| 3.1 Programming on heterogeneous multi-device architectures |       |                                             |           |

|-------------------------------------------------------------|-------|---------------------------------------------|-----------|

|                                                             | in O  | penCL                                       | <b>24</b> |

|                                                             | 3.1.1 | Background of OpenCL                        | 24        |

|                                                             | 3.1.2 | Challenge of using multiply compute devices | 27        |

| 3.2                                                         | Con   | ponent of STEPOCL                           | 30        |

|                                                             | 3.2.1 | Compute kernels                             | 31        |

|                                                             | 3.2.2 | STEPOCL configuration file                  | 32        |

|                                                             | 3.2.3 | STEPOCL Output of OpenCL application        | 34        |

| 3.3                                                         | STE   | POCL internal mechanism                     | 35        |

|                                                             | 3.3.1 | Automatic device management                 | 35        |

|                                                             | 3.3.2 | Automatic workload partition                | 36        |

|                                                             | 3.3.3 | Automatic adjusting workload                | 37        |

|                                                             | 3.3.4 | Automatic data consistency management       | 37        |

| 3.4                                                         | Con   | clusion                                     | 37        |

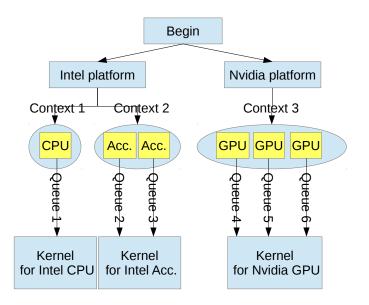

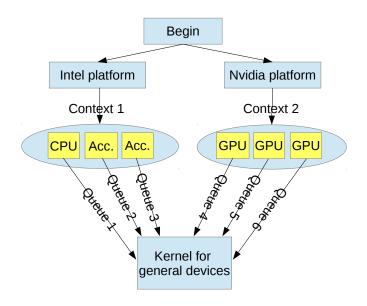

In this chapter, we present more details about programming on heterogeneous multidevice architectures in OpenCL. Then, we introduce our contribution STEPOCL, which is an OpenCL based programming tool, along with a new domain specific language designed for simplifying the development of an application for heterogeneous multi-device architectures.

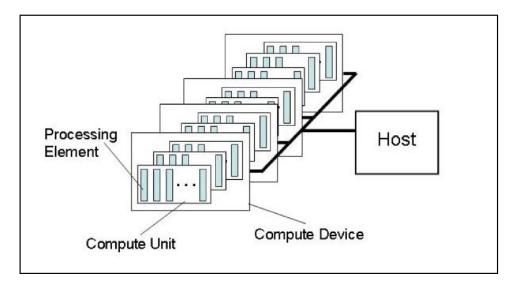

Figure 3.1 – OpenCL Platform Model (image source: KHRONOS group).

## 3.1 Programming on heterogeneous multi-device architectures in OpenCL

As we presented in Chapter 2, OpenCL provides portability and performance across heterogeneous platforms. It combines a unified programming interface with a variant of the C language to use different parallel processing devices together (e.g. CPU, GPU and Xeon Phi).

### 3.1.1 Background of OpenCL

Before further investigating programming on multi-device architecture, we briefly introduce some basic concepts of OpenCL.

### Platform mode

The platform model of OpenCL consists of a host (a CPU) connected to one or more OpenCL compute devices. A device can be a CPU, a GPU or any other processor supported by the OpenCL vendor. The OpenCL devices are further divided into *compute units* which are further divided into one or more *processing element* (PEs) where the computations on a device occur. Figure 3.1 shows an overview of the OpenCL platform model.

### Programming model

OpenCL program consists of two parts: a host code and a computing function. The developer first defines a computing function, called a *kernel*, a basic unit of executable code which is executed on an OpenCL device. In *host code*, developer sets up the environment for the execution of kernel and orchestrates the copy of the data used by the kernel on the device before launching the execution of kernel on a chosen device. When

Figure 3.2 – OpenCL Work-Groups and Work-Items.

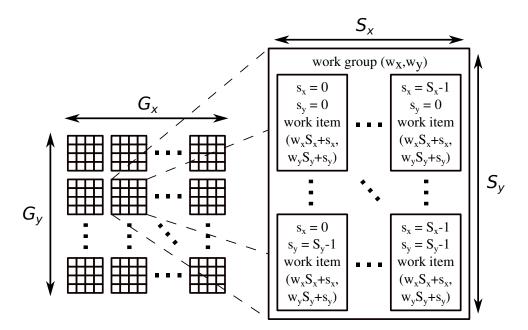

a kernel is submitted for execution by the host, an index space is defined. Each point in this index space presents an instance of executing kernel. In OpenCL, an instance of executing kernel is called a *work-item*. Work-item is identified by its coordinates in index space. These coordinates are the global ID for work-item which is given by a specific OpenCL primitive (the get\_global\_id primitive). Work-items are organized into work-groups. The work-groups provide a more coarse-grained decomposition of the index space. Work-groups are assigned a unique work-group ID with the same dimensionality as the index space used for the work-item. In each work-group, work-items are assigned a unique local ID, thus a single work-item can be uniquely identified by its global ID or by a combination of its local ID and work-group ID.

Figure 3.2 illustrates this notion of *work-group*: a 2D-kernel index space is split into  $Gx \times Gy$  work-groups, each of which consists of  $Sx \times Sy$  work-items.

### **OpenCL** context and command-queue

OpenCL context defines the environment of kernel's execution. An OpenCL context consists of following components:

- Devices: a set of OpenCL devices to be used by the host.

- Kernels: the computing functions that run on OpenCL devices.

- Program objects: the source code program of kernel.

- Memory objects: the objects that contain data which are visible to all devices within a context.

*Command-queue* is used for the interactions between the host and the OpenCL devices. Each OpenCL device is attached by a command-queue after the definition of context. With command-queue, host can deliver the commands, such as kernel execution, memory movement and synchronization, through command-queue.

### Memory model

The memory model of OpenCL defines four distinct memory regions:

- *Host memory*: Host memory region is visible only to the host. OpenCL defines only how the host memory interacts with OpenCL objects and constructs.

- *Global memory*: This memory region is visible for all work-items. Every work-item can do the read or write action on any element in global memory.

- Local memory: This memory region is local to a work-group. The elements in local memory are only shared by the work-items in that work-group. For the local memory, OpenCL provides efficient synchronization mechanisms to guarantee the values seen by a set of work-items in a work-group are consistent.

- *Private memory*: This memory region is private to a work-item. The elements in one work-item's private memory are not visible to other work-items.

The OpenCL device memory and host memory supports global memory. The interaction between host memory and global memory can be achieved by *copying* data (clEnqueueRead/WriteBuffer) or by *mapping* and *unmapping* regions of a memory object (clEnqueueMapBuffer/clEnqueueUnmapObject).

Meanwhile, OpenCL defines four address space qualifiers: **\_\_global**, **\_\_local**, **\_\_constant** and **\_\_private**. These qualifiers, used in variable declaration, specify the region of memory that is used to allocate the object.

- The **\_\_global** address space name is used to indicate that a variable is allocated on global memory.

- The **\_\_local** address space name is used to indicate that a variable will be allocated in local memory, it will be shared by all work-items of a work-group.

- The <u>constant</u> address space name is used to indicate that a variable is allocated on global memory but in read-only mode.

- The other unqualified variables inside a kernel function are **\_\_private**, these variables are only performed **READ/WRITE** by actual work-items.

### Parallel models

OpenCL supports two different parallel programming models: data parallelism and task parallelism.

Data-Parallel Programming Model The basic idea of data-parallel programming is operating concurrently on a collection of data elements. When an OpenCL kernel is launched by host code, OpenCL index space automatically maps onto OpenCL memory objects, which means the identification of each work-item (global ID or local ID) also maps onto memory objects. If the kernel doesn't contain any branch statements, each work-item will execute identical operations on a subset of data items (depends on its global ID). If branch statements exist in a kernel, each work-item still execute the same program, but may accomplish different computing tasks. OpenCL also defines vector instructions and types to support Single Instruction Multiple Data (*SIMD*) models.

Task-Parallel Programming Model OpenCL permits that several submitted kernels can be executed at the same time. In this case, programmers must define and manipulate the execution of concurrent tasks for each computing devices. Because the tasks and the computing capacities of devices vary widely, distributing them so that they all finish at about the same time can be difficult.

In this thesis, we focus on dealing with massive data-parallel tasks which are too large for single computing device's memory. We split large tasks into several small subtasks. Then we use task-parallel programming model to schedule the execution of subtasks. Based on this idea, we developed STEPOCL. It can generate workload partitioning and scheduling modules automatically in C language.

### Execution of OpenCL program

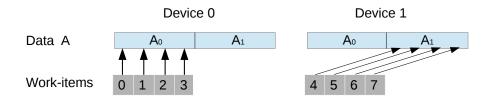

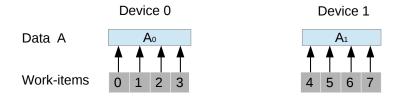

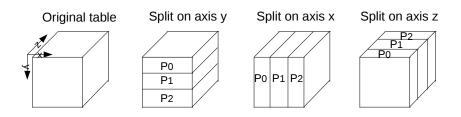

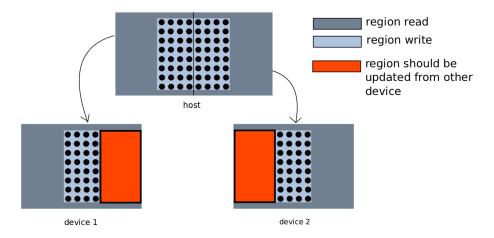

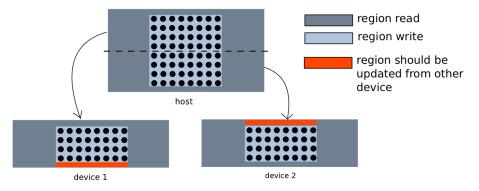

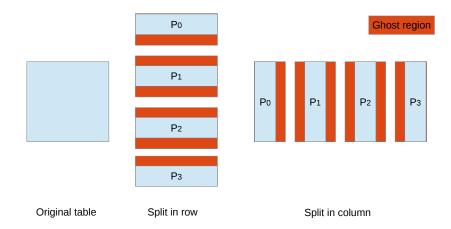

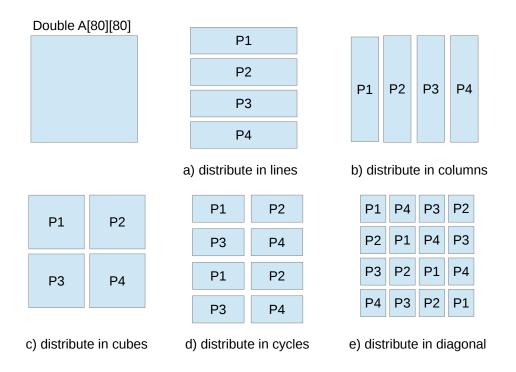

Overall, a typical execution of an OpenCL application should be follows the steps below: