# Vectorial measurement methods for millimeter wave integrated circuits

Vipin Velayudhan

## ▶ To cite this version:

Vipin Velayudhan. Vectorial measurement methods for millimeter wave integrated circuits. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2016. English. <NNT: 2016GREAT035>. <tel-01345155>

HAL Id: tel-01345155

https://tel.archives-ouvertes.fr/tel-01345155

Submitted on 13 Jul 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Optique et Radiofréquences

Arrêté ministériel : 7 août 2006

Présentée par

# Vipin VELAYUDHAN

Thèse dirigée par **Jean-Daniel ARNOULD** et codirigée par **Emmanuel PISTONO**

préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale Électronique, Électrotechnique, Automatique et Traitement du signal (EEATS)

# Méthodes de Mesure pour l'Analyse Vectorielle aux Fréquences Millimétriques en Technologie Intégrée

Thèse soutenue publiquement le « 10 Juin 2016 », devant le jury composé de :

M, JunWu, TAO

Professeur, INP Toulouse, Rapporteur

M, Didier, VINCENT

Professeur, Université Jean Monnet, Rapporteur

M. Alain SYLVESTRE

Professeur des universités, Grenoble, Invité

M. Jean-Marc DUCHAMP

Maître de Conférences, Grenoble, Invité

M. Jean-Daniel ARNOULD

Maître de Conférences. Grenoble. Directeur de thèse

M. Emmanuel PISTONO

Maître de conférences, Grenoble, Co-directeur de thèse

# Résumé

Cette thèse porte sur l'étude des méthodes de mesure pour l'analyse vectorielle des circuits microélectroniques en technologie intégrée aux fréquences millimétriques. Pour réussir à extraire les paramètres intrinsèques de circuits réalisés aux longueurs d'ondes millimétriques, les méthodes actuelles de calibrage et de de-embedding sont d'autant moins précises que les fréquences de fonctionnement visées augmentent au-delà de 100 GHz notamment. Cela est d'autant plus vrai pour la caractérisation des dispositifs passifs tels que des lignes de propagation. La motivation initiale de ces travaux de thèse venait du fait qu'il était difficile d'expliquer l'origine exacte des pertes mesurées pour des lignes coplanaires à ondes lentes (lignes S-CPW) aux fréquences millimétriques. Etait-ce un problème de mesure brute, un problème de méthode de-embedding qui sous-estime les pertes, une modélisation insuffisante des effets des cellules adjacentes, ou encore la création d'un mode de propagation perturbatif?

Le travail a principalement consisté à évaluer une dizaine de méthodes de de-embedding au-delà de 65 GHz et à classifier ces méthodes en 3 groupes pour pouvoir les comparer de manière pertinente. Cette étude s'est déroulée en 3 phases.

Dans la première phase, il s'agissait de comparer les méthodes de de-embedding tout en maitrisant les modèles électriques des plots et des lignes d'accès. Cette phase a permis de dégager les conditions optimales d'utilisation pour pouvoir appliquer ces différentes méthodes de de-embedding.

Dans la deuxième phase, la modélisation des structures de test a été réalisée à l'aide d'un simulateur électromagnétique 3D basé sur la méthode des éléments finis. Cette phase a permis de tester la robustesse des méthodes et d'envisager une méthode de-embedding originale nommée Half-Thru Method. Cette méthode donne des résultats comparables à la méthode TRL, méthode qui reste la plus performante actuellement. Cependant il reste difficile d'expliquer l'origine des pertes supplémentaires obtenues notamment dans la mesure des lignes à ondes lentes S-CPW.

Une troisième phase de modélisation a alors consisté à prendre en compte les pointes de mesure et les cellules adjacentes à notre dispositif sous test. Plus de 80 structures de test ont été conçues en technologie AMS  $0.35~\mu m$  afin de comparer les différentes méthodes de de-embedding et d'en analyser les couplages avec les structures adjacentes, les pointes de mesure et les modes de propagation perturbatifs.

Finalement, ce travail a permis de dégager un certain nombre de précautions à considérer à l'attention des concepteurs de circuits microélectroniques désirant caractériser leur circuit avec précision audelà de 110 GHz. Il a également permis de mettre en place la méthode de de-embedding Half-Thru Method qui n'est basée sur aucun modèle électrique, au contraire des autres méthodes.

**Mots clés :** Méthodes de de-embedding, mesures de paramètres S aux fréquences millimétriques, modélisation électrique et electromagnétique

# **Vectorial Measurement Methods for Millimeter Wave Integrated Circuits**

# **Abstract**

This thesis focuses on the study of vectorial measurement methods for analysing microelectronic circuits in integrated technology at millimeter wave frequencies. Current calibration and de-embedding methods are less precise for successfully extracting the intrinsic parameters of devices and circuits at millimeter wave frequencies, while the targeted operating frequencies are above 100 GHz. This is especially true for the characterization of passive devices such as propagation lines. The initial motivation of this thesis work was to explain the exact origin of the additional loss measured in Slow-Wave Coplanar Waveguides (S-CPW) lines at millimeter wave frequencies. Was it a problem of raw measurement or a problem of de-embedding method, which underestimates the losses? Or was it a problem of insufficient modeling of the effects of adjacent cells, or even the creation of a perturbation mode of propagation?

This work consists of estimating many de-embedding methods beyond 65 GHz and classifies these methods into three groups to be able to compare them in a meaningful way. This study was conducted in three phases.

In the first phase, we compared all the de-embedding methods with known electrical model parasitics of pad/accessline. This phase identifies the optimal conditions to use and apply these de-embedding methods.

In the second phase, the modeling of test structures is performed using a 3D electromagnetic simulator based on finite element method. This phase tested the robustness of the methods and considered an original de-embedding method called Half-Thru de-embedding method. This method gives comparable results to the TRL method, which remains the most effective method. However, it remains difficult to explain the origin of additional losses obtained in measured S-CPW line.

A third modeling phase was analysed to take into account the measurement of probes and the adjacent cells near our device under test. More than 80 test structures were designed in AMS 0.35  $\mu$ m CMOS technology to compare the different de-embedding methods and analyse the link with adjacent cells, measuring probes and perturbation mode of propagation.

Finally, this work has identified a number of precautions to consider for the attention of microelectronic circuit designers wishing to characterize their circuit with precision beyond 110 GHz. It also helped to establish Half-Thru Method de-embedding method, which is not based on electrical model, unlike other methods.

**Keywords:** De-embedding methods, S-parameter measurements at millimeter frequencies, electrical and electromagnetic modeling

# Acknowledgements

It is my pleasure and privilege to thank the many individuals who made this thesis possible. First, I would like to express my sincere gratitude to my director of the thesis Dr. Jean-Daniel Arnould and my co-director of the thesis Dr. Emmanuel Pistono for providing me an opportunity to work for a Ph.D. in IMEP-LAHC, Universite Grenoble-Alpes. They have guided me during my thesis with his patience. I express my sincere thanks to them for his advice, consistent encouragement, and understanding throughout my thesis.

I would like to thank my Ph.D. thesis reviewers, Prof. Didier Vincent from Université Jean Monnet and Prof. JunWu Tao from INP Toulouse, for having accepted to examine this work and for their valuable insights. Thanks to Prof. Alain Sylvestre and Dr. Jean-Marc Duchamp being part of my thesis committee as well as accepting my invitation to become part of my jury as well. I express my thanks to Prof. Pascal Xavier, the member of my thesis committee. Their advice and suggestions are helped me to improve my thesis. Also, I express my sincere thanks to the Guy Vitrant, director of école doctorale EEATS, for his support during the thesis.

I would like to acknowledge Prof. Philippe FERRARI, without him I would not be in IMEP-LAHC. I contacted Philippe in 2012 for a Ph.D. opportunity and he directed me to Jean-Daniel. I express my sincere thanks to Philippe for giving me a great opportunity to be a part of IMEP-LAHC, also the advice and suggestions from his side. I am also grateful to Nicolas CORRAO for measuring my integrated devices, many times according to understand the real problems in which are mentioned in the thesis. Thank you a lot Nicolas for your time to time help, and each and every information that you provided to me regarding measurements. Thanks to Alexander Chagoya, for his help on the design kits and conversations during my stay in IMEP.

I thank from the bottom of my heart Dr. Mohanan Pezholil, Professor, Department of Electronics, Cochin University of Science and Technology, for directing me into the RF/Microwave research domain. His guidance and encouragement, tremendous technical and mental support have been inspired me. I express my sincere thanks to my mentors and guides, Prafull Sharma, Dr. Aparna C. Sheila-Vadde, Manoj Kumar KM, Dr. Suma MN and Dr. Rajesh Langoju, GE- Global Research Centre, John F Welch Technology Centre, India, for supporting and encouraging me to apply for Ph.D. The motivations and guidance from you keep me helped a lot to reach the target. Also, my sincere thanks to MPFM team and NDE-lab members.

My special thanks and appreciation goes to Sujith Raman, Divya Unnikrishnan, Vinod VKT, Sony T George, Arun Kesavan for their valuable support. My words are boundless to thank Alejandro Niembro, Ines Kharatt and François Burdin for helping to settle in Grenoble. My sincere thanks to Ayssar for helping me to fabricate my devices, n- number of active technical discussions, suggestions, advice and all the help. Special thanks to Ossama, NASA Jet Propulsion Laboratory (JPL), United States for the technical discussions, running days, coffee time, help and advice.

I express my gratitude towards Prof. Jean-Michel Fournier for his suggestions, advice, and great support. Special and very big thanks to our neighbour, Prof. Tan Phu, who has always some treats, or a big bonjour to share with our office. I take this opportunity to Florence Podevin, Sylvain Bourdel, Estelle Lauga-Larroze, Fabien Ndagijimana, Yannis Le Guennec, Laurent Montes, Daniel Bauza, RFM team and all IMEP-LAHC members. I thank Serge and Luc for their time to time help with solving the problems with the simulation server. I take this opportunity to thank Dalhila, Chahla, Joel, Valérie, Annaïck and Isabelle for the administrative help.

I acknowledge my friends Sriharsha and Lahari for their help, drinks, dinner and outings throughout the life in Grenoble. Thank you for suffering me all the time. Thanks to Vân, Victoria, Alex, Ines and the people from A440 for your support and long discussions. Special thanks to Vân N and Malaurie for motivating me to learn French. Thanks to Matthieu for the active discussions, suggestions, coffees and hikes in Grenoble. Thanks to Fred and Ekta for their daily visits at A440. Thanks a lot to the plants in my office for providing me a great environment.

I am thank full to José, Walid, Anne-Laure, Farid, Vlad, Madam Phuong, Isaac, Anh Tu, Nimisha, Mukta, Vishakha, Narendra, Carlos, Luca, Jerome, Kawtar, Fanyu, Elodie, Pierre, Ramin, Tapas, Dimitrios, Sotiris, Licinius, Deepak, Zyad, Hamza, Mahdi, Aziz, Cyril, Nikolaus, Vicky, Quentin, Cica, Isabelle, Carlos, Nata, Kaya, Milovan, Fabio, Elisa, Evan, etc.. Soorej M Basheer, Prem Prabhakar, Saijo Thomas, Shynu, Dinesh R Nair, Nijas, Vinesh PV, Vivek, Lindo, Ullas, Jinesh, Sreenath Atholi, Sarin, Sreejith, Lailamiss, Abhilash, Vinu, Sooraj, Rajeev, Sumesh, all my friends that I could not mention personally one by one. I sincerely thank all my teachers for their unconditional support and love without this wonderful journey would not have been real.

Last, but definitely not least, I thank my parents for all their sacrifices and moral support and my brother, sister and all family members for their encouragements and understanding. Their unconditional support and love gave me the courage to complete this work. Finally, I would like to thank everybody who was important to the successful realization of the thesis, as well as expressing my apology that I could not mention personally one by one.

Vipin VELAYUDHAN

# Contents

| Gene | ral Intro | duction  |                                                                                     | 1            |

|------|-----------|----------|-------------------------------------------------------------------------------------|--------------|

|      | Outli     | ne and a | im of the thesis                                                                    | 2            |

| 1.   | Millin    | neter Wa | ave Device Measurement and Characterization in Silicon Integrated Circuits          | 5            |

|      | 1.1       | State    | of the Art and Problem Description                                                  | 5            |

|      |           | 1.1.1    | Transmission Lines for Millimeter-Wave and Sub-Millimeter-Wave Frequencies and Appl | ications . 6 |

|      |           | 1.1.2    | Slow-Wave Coplanar Waveguide (S-CPW) Transmission Line                              | 6            |

|      |           | 1.1.3    | Motivation: Applications at Millimeter-Wave Frequencies and Above                   | 8            |

|      |           | 1.1.4    | Electromagnetic Modeling and Measurement Uncertainties                              | 10           |

|      |           | 1.1.5    | De-embedding and Challenges                                                         | 12           |

|      |           | 1.1.6    | De-embedding with and without Interconnect/Accesslines                              | 15           |

|      |           | 1.1.7    | Bended-Accessline De-embedding                                                      | 15           |

|      |           | 1.1.8    | Excessive Losses at Millimeter Wave Frequencies and Above                           | 16           |

|      |           | 1.1.9    | Other Measurement Challenges                                                        | 17           |

|      |           | 1.1.10   | Conclusion of State of the Art and Problem Description                              | 17           |

|      | 1.2       | On-W     | afer Measurement and Challenges at Millimeter Wave Frequencies                      | 18           |

|      |           | 1.2.1    | Calibration and Challenges                                                          | 19           |

|      |           | 1.2.2    | RF Probes                                                                           | 20           |

|      | 1.3       | Conclu   | ısion                                                                               | 22           |

|      | 1.4       | Refere   | ences                                                                               | 24           |

| 2.   | De-er     | mbeddin  | g Methods                                                                           | 29           |

|      | 2.1       | Classif  | ication of De-embedding Methods                                                     | 29           |

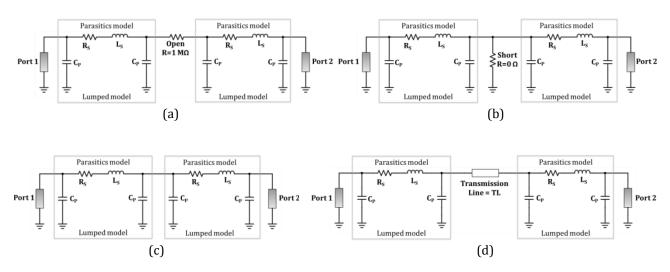

|      |           | 2.1.1    | Lumped Equivalent Circuit Model                                                     | 30           |

|      |           | 2.1.2    | Cascaded Matrix Based Models                                                        | 32           |

|      |           | 2.1.3    | Cascaded Matrix with Lumped Equivalent Models                                       | 36           |

|      |           | 2.1.4    | Conclusion and Further studies of Classification of De-embedding Methods            | 38           |

|      | 2.2       | ВіСМО    | OS 55 nm Silicon Technology                                                         | 39           |

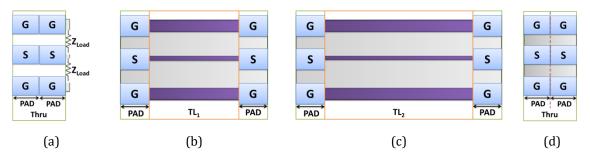

|      | 2.3       | Proof    | of Concept with ADS                                                                 | 40           |

|      |           | 2.3.1    | Pad-Acceslines Parasitics Models                                                    | 41           |

|      |           | 2.3.2    | De-embedding Structures: Known Parasitics De-embedding                              | 43           |

|      |           | 2.3.3    | Analysis of Lumped Equivalent Circuit Model De-embedding Methods                    | 44           |

|      |           | 2.3.4    | Analysis of Cascaded Matrix Based Model De-embedding Methods                        | 46           |

|      |           | 2.3.5    | Analysis of Hernandez Method                                                        | 48           |

|    |        | 2.3.6   | Analysis of Cascaded Matrix with Lumped Equivalent Model De-embedding Methods | 49 |

|----|--------|---------|-------------------------------------------------------------------------------|----|

|    |        | 2.3.7   | Conclusion of Proof of Concept with ADS                                       | 50 |

|    | 2.4    | Proof   | of Concept with HFSS                                                          | 52 |

|    |        | 2.4.1   | Parasitics Model: Unknown Parasitics De-embedding                             | 53 |

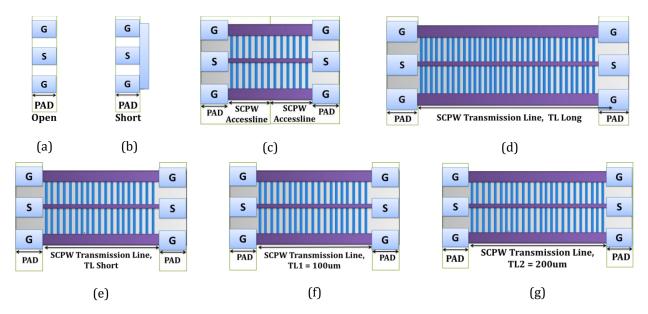

|    |        | 2.4.2   | De-embedding Structures                                                       | 53 |

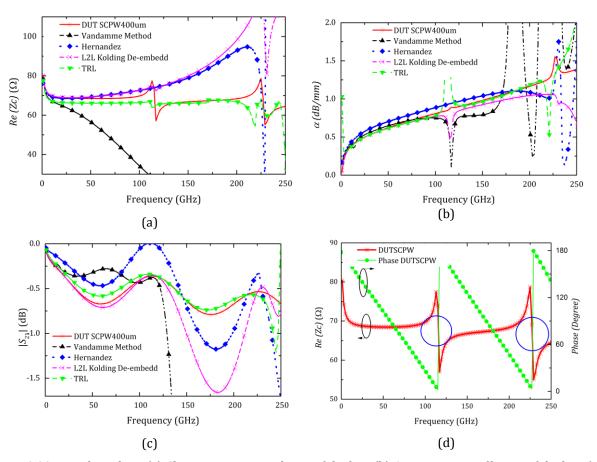

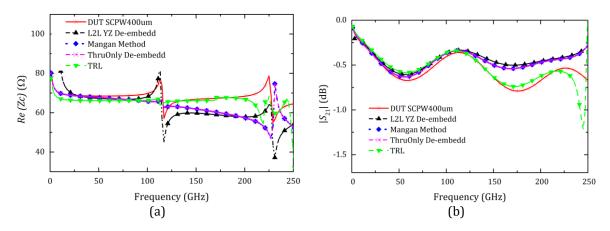

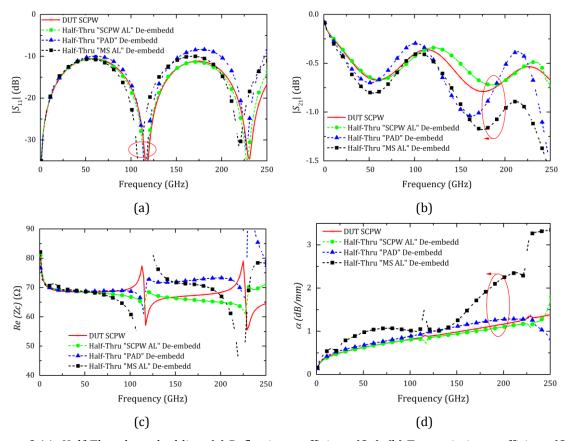

|    |        | 2.4.3   | Benchmarking and Comparison of De-embedding Methods                           | 54 |

|    | 2.5    | Conclu  | usion                                                                         | 56 |

|    | 2.6    | Refere  | ences                                                                         | 59 |

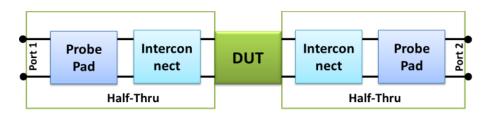

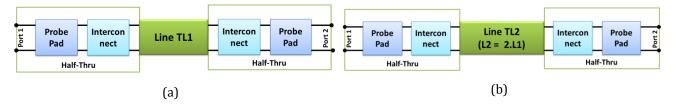

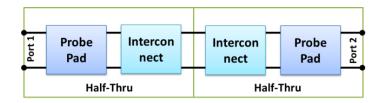

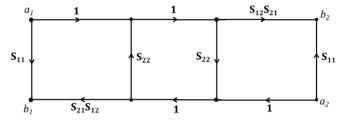

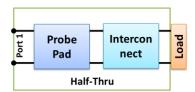

| 3. | Half-T | hru De- | embedding                                                                     | 61 |

|    | 3.1    | Half-T  | hru De-embedding                                                              | 61 |

|    | 3.2    | Theore  | etical Analysis                                                               | 62 |

|    | 3.3    | Proof   | of Concept with Known Electrical Model Parasitics                             | 64 |

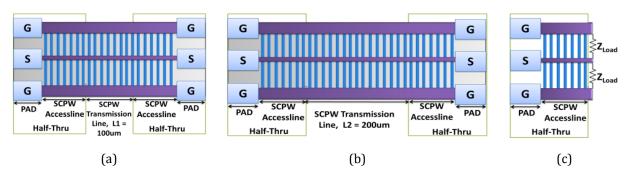

|    |        | 3.3.1   | Simulation and De-embedding Results with Known Parasitics using ADS           | 64 |

|    |        | 3.3.2   | Conclusion of Proof of Concept with ADS                                       | 66 |

|    | 3.4    | Proof   | of Concept with Unknown EM Model Parasitics                                   | 67 |

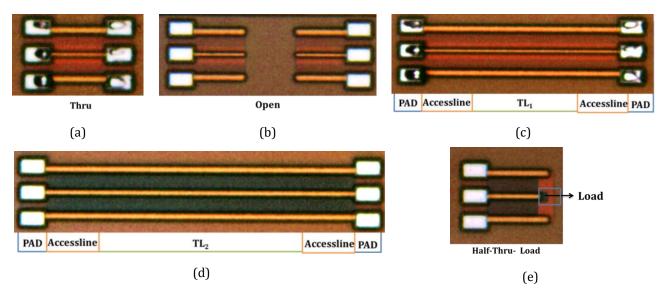

|    |        | 3.4.1   | Measurement Setup and De-embedding Structures                                 | 67 |

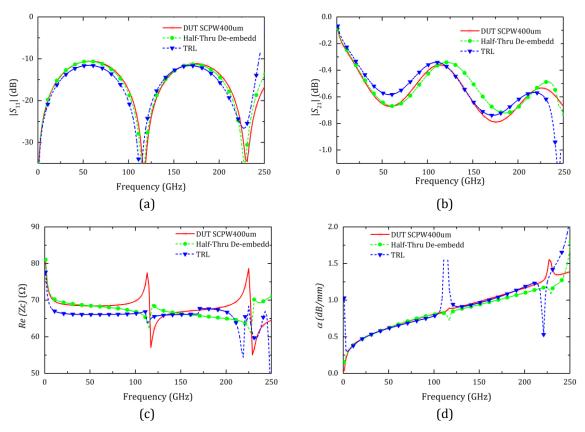

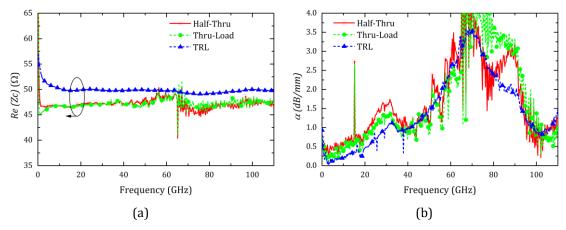

|    |        | 3.4.2   | Simulation and Results: Benchmarking and Comparison with TRL                  | 68 |

|    |        | 3.4.3   | Simulation with and without accessline                                        | 69 |

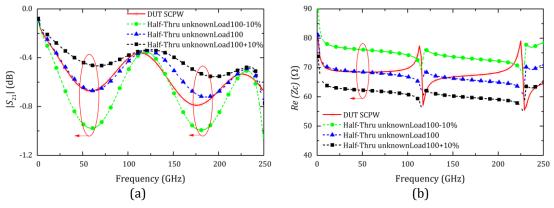

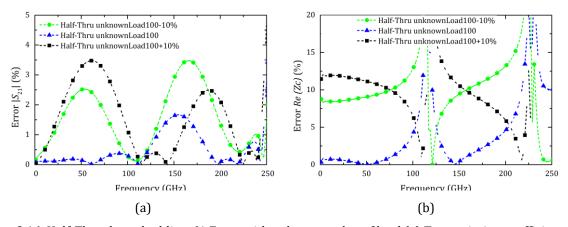

|    |        | 3.4.4   | Effect of the Load Value Analysis                                             | 71 |

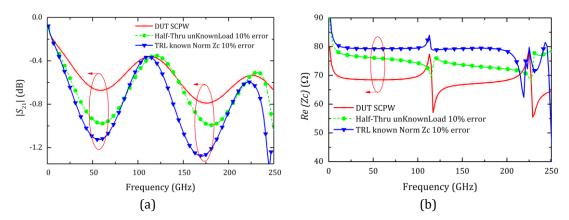

|    |        | 3.4.5   | Comparison with Effect of the Characteristic Impedance of the Line of the TRL | 72 |

|    |        | 3.4.6   | Conclusion of Proof of Concept with HFSS                                      | 73 |

|    | 3.5    | Extrac  | tion of the Load value for Half-Thru De-embedding                             | 73 |

|    |        | 3.5.1   | Open De-embedding                                                             | 74 |

|    |        | 3.5.2   | Open-Short De-embedding                                                       | 74 |

|    |        | 3.5.3   | Load value extraction with Kolding's Method                                   | 75 |

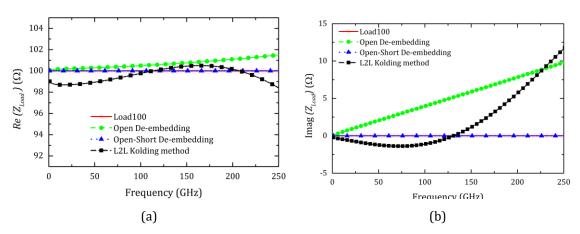

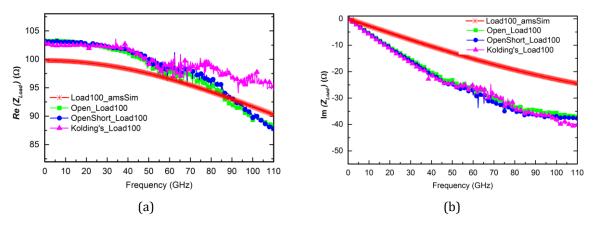

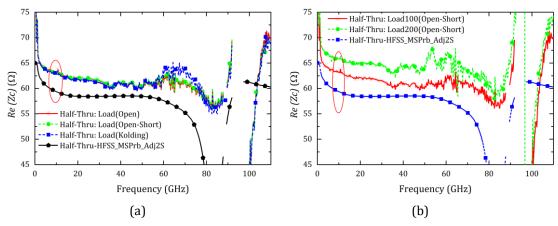

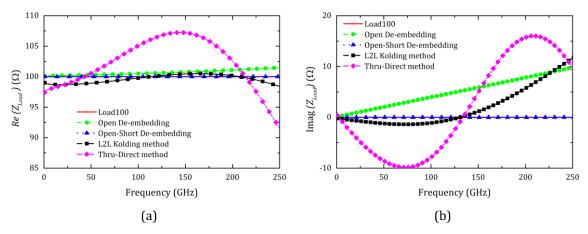

|    |        | 3.5.4   | Simulation and Results of Load Extraction Methods                             | 76 |

|    |        | 3.5.5   | Half-Thru De-embedding with Different Load Extraction Methods                 | 77 |

|    |        | 3.5.6   | Conclusion of Extraction of Load Value for Half-Thru De-embedding             | 78 |

|    | 3.6    | Simpli  | fied Half-Thru De-embedding: Thru-Load De-embedding                           | 78 |

|    |        | 3.6.1   | Simulation and Comparison with Half-Thru De-embedding                         | 78 |

|    | 3.7    | Conclu  | usion                                                                         | 79 |

|    | 3.8    | Refere  | ences                                                                         | 81 |

| 4. | Meası  | urement | ts and Electromagnetic Modeling Analysis of De-embedding Methods              | 83 |

|    | 4.1    | AMS 0   | ).35 μm CMOS Technology                                                       | 83 |

|    | 4.2    | Fabric  | ation Map                                                                     | 84 |

|    | 4.3    | Compa   | arison of Half-Thru De-embedding and TRL                                      | 84 |

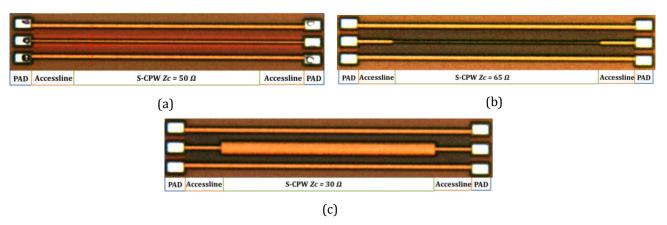

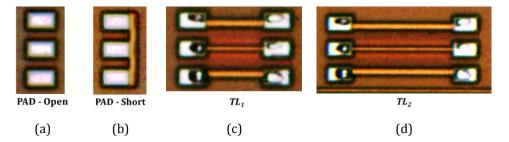

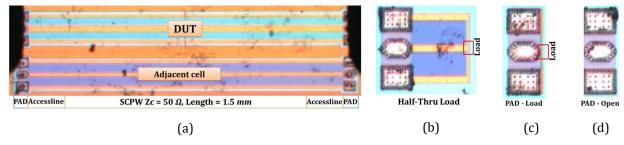

|    |        | 121     | DLITE and Do embedding Structures                                             | 05 |

|         |          | 4.3.2    | Load value Extraction                                                                     | 85     |

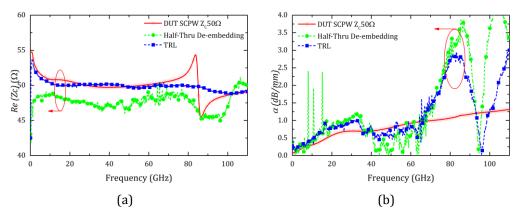

|---------|----------|----------|-------------------------------------------------------------------------------------------|--------|

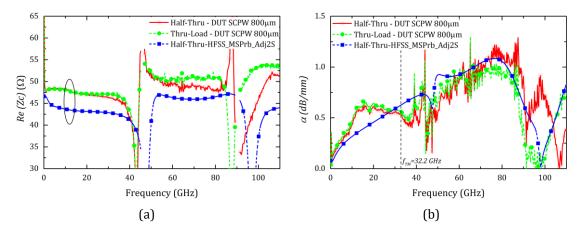

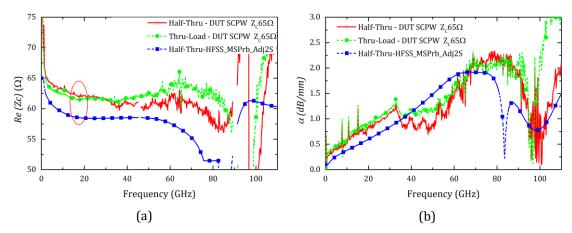

|         |          | 4.3.3    | Comparison of Half-Thru De-embedding and TRL                                              | 87     |

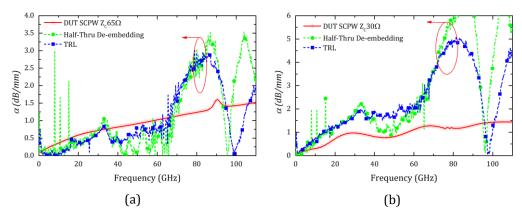

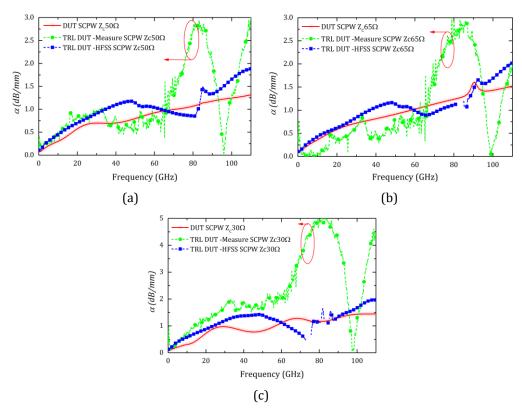

|         |          | 4.3.4    | Analysis of Excessive loss in S-CPW of 65 $\Omega$ and 30 $\Omega$                        | 88     |

|         |          | 4.3.5    | Impact of EM-Model in De-embedding.                                                       | 89     |

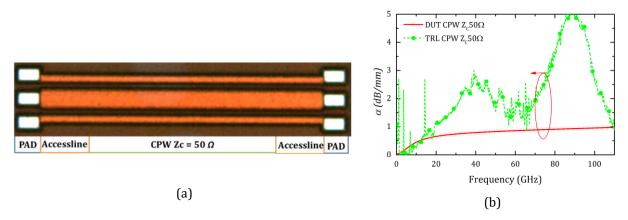

|         |          | 4.3.6    | De-embedding: CPW Transmission Line as DUT                                                | 90     |

|         |          | 4.3.7    | Conclusion of Comparison of Half-Thru De-embedding and TRL                                | 91     |

|         | 4.4      | ЕМ-Мс    | odel Issues and Analysis                                                                  | 91     |

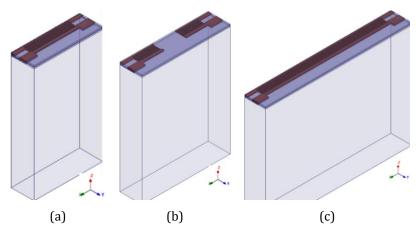

|         |          | 4.4.1    | On-wafer: Fabricated Transmission Lines                                                   | 92     |

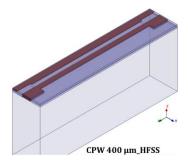

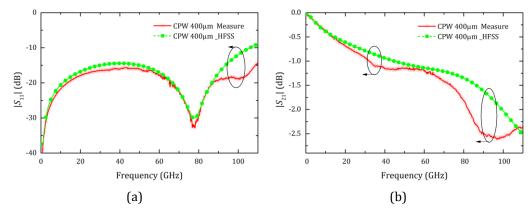

|         |          | 4.4.2    | EM – Model of Measured CPW transmission line                                              | 92     |

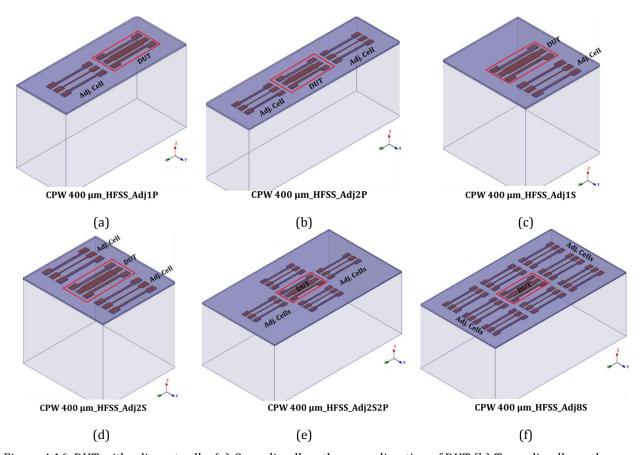

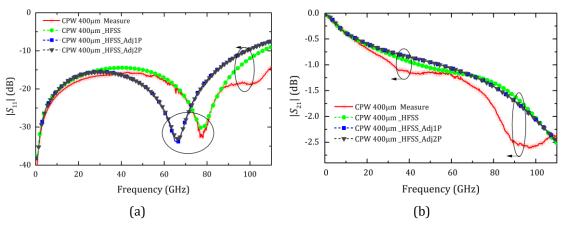

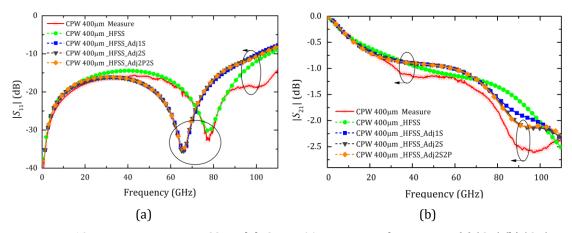

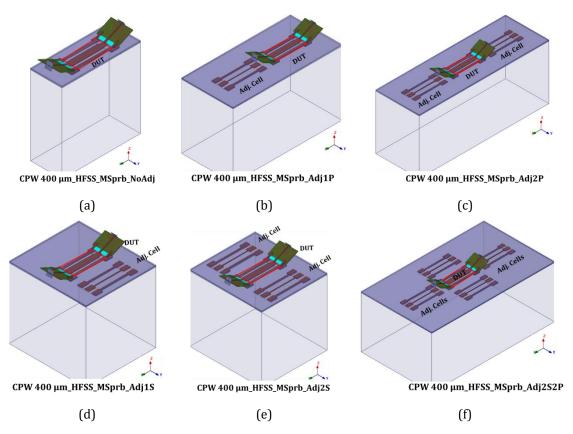

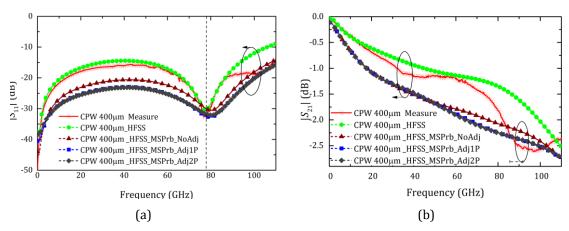

|         |          | 4.4.3    | EM – Model of Measured CPW transmission line with adjacent cells                          | 93     |

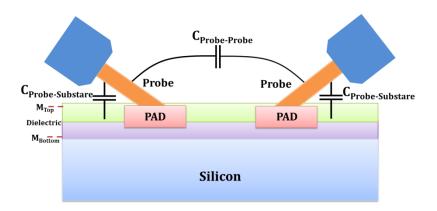

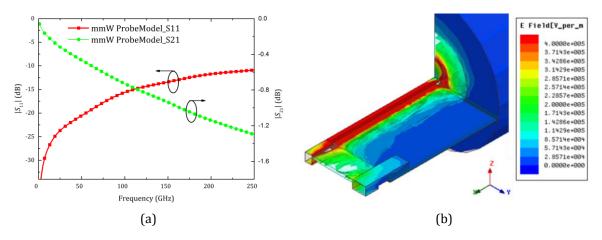

|         |          | 4.4.4    | EM - Model of Millimeter Wave Probe                                                       | 95     |

|         |          | 4.4.5    | EM - Model of measured CPW transmission line with Millimeter Wave Probe Model and A       | •      |

|         |          | 4.4.6    | De-embedding with the realistic EM- Model                                                 | 98     |

|         |          | 4.4.7    | Reasons of Excessive Loss                                                                 | 99     |

|         |          | 4.4.8    | Other Possible Losses                                                                     | 100    |

|         |          | 4.4.9    | Conclusion of EM-Model Issues and Analysis                                                | 101    |

|         | 4.5      | Solutio  | ns                                                                                        | 102    |

|         |          | 4.5.1    | Conclusion of On-wafer Measurement Issues and Possible Solutions                          | 102    |

|         | 4.6      | Half-Th  | nru De-embedding and Thru-Load De-embedding Analysis                                      | 103    |

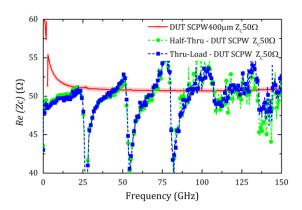

|         |          | 4.6.1    | De-embedding with Different Length of the DUT                                             | 103    |

|         |          | 4.6.2    | De-embedding with Different Characteristic Impedance of DUT                               | 104    |

|         |          | 4.6.3    | Half-Thru De-embedding with Different Load Extraction Methods and with Different Load Val | ues105 |

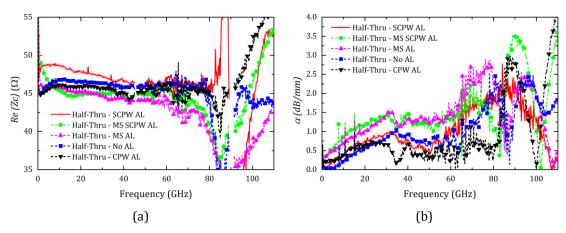

|         |          | 4.6.4    | De-embedding with Different Accessline Topology                                           | 106    |

|         |          | 4.6.5    | Comparison and Benchmarking of de-embedding methods                                       | 107    |

|         |          | 4.6.6    | De-embedding with Bended-Accessline Model                                                 | 108    |

|         |          | 4.6.7    | Conclusion of Half-Thru De-embedding and Thru-Load De-embedding Analysis                  | 109    |

|         | 4.7      | Half-Th  | nru de-embedding and Thru-Load de-embedding in B55 nm Technology                          | 110    |

|         | 4.8      | Conclus  | sion                                                                                      | 110    |

|         | 4.9      | Refere   | nces                                                                                      | 112    |

| Conclus | sion and | l Perspe | ective                                                                                    | 115    |

|         | Perspe   | ctives   |                                                                                           | 118    |

|         | Referer  | nces     |                                                                                           | 119    |

| APPENI  | DIX - A  |          |                                                                                           | 121    |

| APPENI  | DIX - B  |          |                                                                                           | 125    |

| APPENI  | DIX - C  |          |                                                                                           | 127    |

# **General Introduction**

The evolution of Silicon technologies, like Complementary Metal Oxide Semiconductor (CMOS) and Bipolar CMOS (BiCMOS) technologies, achieve a great place in the millimeter wave integrated circuits. It has many advantages such as low manufacturing cost, high integration density and low power consumption. These technologies driven RF applications into millimeter and sub-millimeter wave frequency range. In RF/Microwave, there are many applications serving each and every domain of science and technology, such as telecommunications (video-streaming (57-66 GHz), automotive radar (76-81 GHz)), imaging (around 140 GHz, 220 GHz, ...)), security, medicine, environmental, etc. The development of the silicon technology causes the reduction in size of the devices and circuits, especially in millimeter wave integrated circuits. These devices have to be measured and characterized, before its implementation on the circuits or systems. Therefore, a dedicated measurement and characterization of these devices at millimeter and sub-millimeter wave frequency range should be required to ensure the best performance.

Generally, the silicon-based devices are measured on-wafer with the help of probe station and vector network analyser. The measurement of the device includes additional parasitic effects from the pads and interconnecting lines, which are used to connect the device for the measurement. This affects the actual characteristics of the device and this should be subtracted from the measured results to get the actual characteristics of the device. The process of mathematically removing these unwanted parasitic effects is called "De-embedding". The calibration of the vector network analyser and de-embedding are highly required for the devices and systems working at millimeter wave and sub-millimeter wave range. A good calibration can be obtained for example by using LRRM (Line-Reflect-Reflect-Match) calibration with the Cascade Microtech systems for on-wafer measurement. After the calibration, measurement of the device and de-embedding should be performed to extract the actual characteristics of the device.

Currently, most of the de-embedding methods are investigated until millimeter wave frequencies, i.e. up to 60 GHz or 110 GHz. However, in the current scenario, more importance is given to develop the devices and applications at millimeter wave and sub-millimeter wave frequencies. So the development of de-embedding methods is quite challenging. There are many methods available at low frequency range. Most of the de-embedding methods are developed by considering the parasitics effects of pads and accesslines as lumped models or cascaded elements or the combination of both. Considering the high frequency and thus the small size of the devices, efficient de-embedding methods must be

considered to obtain accurate measurement results. TRL (Thru-Reflect-Line) algorithm is considered as a very good de-embedding method for high frequencies. Nevertheless, the few limitations restrict the TRL, such as the band limited operation and the value of characteristic impedance of the transmission line used to set the reference plane. This increases the complexity and number of deembedding structures, thus increasing the cost for wide band de-embedding. In addition, many other de-embedding methods are not evaluated for the higher frequencies. In this thesis, we apply the efforts to analyse different de-embedding methods for millimeter wave and sub-millimeter wave frequencies. In addition, we develop new methods employing no unknown terms and good accuracy over a wide band de-embedding.

Beyond millimeter wave frequencies, the environmental measure around the device under test is very critical and the effects of the pads and the substrate are no longer simple localized parasitic elements. To understand these effects, an extensive study on both the measurement and modeling is required. These make DUT characterization and de-embedding at millimeter wave frequencies and above highly challenging. Accurate characterization and de-embedding of the devices in silicon technologies can enable greater performance over the circuits that are implemented. In addition, the accurate extraction of the characteristics of the device reduces the modeling efforts of IC design, thus the time and cost. Therefore, a need for an accurate and reliable de-embedding method to characterize the device at millimeter wave and sub-millimeter wave frequency is required.

## Outline and aim of the thesis

In this thesis, we will study and develop de-embedding methods by considering S-CPW (Slow-Wave Coplanar Wave Guides) transmission line as the device under test. S-CPW transmission line is a miniaturized transmission line topology exhibiting a high quality factor compared to classical transmission lines like microstrip and CPW. IMEP-LAHC is developing applications and passive devices based on S-CPW transmission line until sub-millimeter wave frequency range. Therefore, it is important to characterize the S-CPW transmission line to ensure the best performance of the devices and applications. This work is performed in AMS  $0.35~\mu m$  and BiCMOS 55~n m technology and focuses on the development of de-embedding methods to characterize the device, mainly transmission lines beyond 100~GHz. Thus, first we benchmark and explain different de-embedding methods for millimeter wave transmission line de-embedding other than proposing a new de-embedding method.

**Chapter 1** gives a review of the state of the art of passive device measurements and characterization for millimeter wave and sub-millimeter wave frequency range. It includes the review about S-CPW transmission line and its applications in millimeter wave and sub-millimeter wave. Further, it describes the different problems in the electromagnetic modeling, de-embedding challenges and other issues on on-wafer measurement at millimeter wave frequencies and above.

**Chapter 2** reviews and benchmarks the current de-embedding methods. It includes classification according to the de-embedding strategies and explanation of de-embedding methods. These methods are utilized to de-embed the devices, according to the size of the DUT and the range of frequency. This chapter benchmarks all the de-embedding methods, by considering first electrical modeling and second 3D electromagnetic (EM) modeling using simulation tool Ansys HFSS. In addition, the chapter explains the different limitations and different characteristics needed for a good de-embedding method for a wide band up to millimeter wave and sub-millimeter wave frequency range.

Chapter 3 explains the studies on novel de-embedding method called "Half-Thru De-embedding". This method has been developed to overcome the limitations of other de-embedding methods. Half-Thru de-embedding method has been developed to characterize the devices at millimeter wave and sub-millimeter wave frequency range. This chapter includes the theoretical analysis and proof of the method at millimeter wave and sub-millimeter wave frequencies. The method is tested for 3D EM models of S-CPW transmission lines, which are modeled in Ansys HFSS. Further, we explain the restrictions of this method and the solutions for it. Apart from the Half-Thru de-embedding method, we present a simplified method of Half-Thru de-embedding method called Thru-Load de-embedding method. Benchmarking and comparison with TRL are presented in this chapter.

Chapter 4 compares both simulated and actual de-embedding results from the measurements, where the DUT and the de-embedding structures were fabricated in the AMS  $0.35~\mu m$  CMOS technology and BiCMOS 55~nm technology. The uncertainties in the measured de-embedding results and the excessive loss happening beyond millimeter wave frequencies are explained based on a new realistic EM simulation model by taking of all possible parasitics from the on-wafer measurement into account. Finally, we compare and benchmark the different de-embedding methods with Half-Thru de-embedding and the Thru-Load de-embedding methods.

Finally, the results of this thesis are summarized and the future perspectives are presented.

# 1. Millimeter Wave Device Measurement and Characterization in Silicon Integrated Circuits

In the present and future, there are large number of applications in the millimeter and sub-millimeter wave frequency range such as video streaming (57-66 GHz), automotive radar (76-81 GHz) and medical imaging (around 140 GHz). The rapid growth and development in the millimeter wave technology cause miniaturization of components and circuits especially in millimeter wave integrated circuits. As the frequency of operation increases, the size of the devices reduces from millimeter to micrometer and nanometer. An increasing number of applications in the millimeter wave and sub-millimeter wave ranges and the reduced size of the devices require accurate measurement to ensure the best performance.

This chapter gives a review of the state of the art of passive device measurements and characterization for millimeter wave and sub-millimeter wave frequency range. It includes the review about S-CPW transmission line and its applications in millimeter wave and sub-millimeter wave. Further, it describes the different problems in the electromagnetic modeling, de-embedding challenges and other issues on on-wafer measurement at millimeter wave frequencies and above.

# 1.1 State of the Art and Problem Description

With the continuously emerging technologies and development of many applications in the millimeter wave and THz applications, design and characterization of the device become critical. The evaluation of silicon technologies [1], like Complementary Metal Oxide Semiconductor (CMOS) and the Bipolar CMOS (BiCMOS) technologies, leads the commercial RF and millimeter wave applications. Silicon integrated circuits are empowering the semiconductor growth in the past half a century. This exponential growth often referred to Moore's law and the cut-off frequencies of silicon transistors are reached above 100 GHz along with applications even at higher frequencies. Due to size reduction in the device geometries and technology improvement, it is possible to achieve operating frequencies up to THz in these technologies. The passive devices/structures serve a greater portion in all applications [2]. The main utilized passive structures in millimeter wave circuits are inductors, capacitors, transmission lines, transformers, etc. Transmission lines serve an important role to connect each device in all RF and millimeter-wave applications. The modeling and characterization of the

transmission lines are important for the millimeter wave applications and beyond, because its characteristics can vary beyond the normal expectation values.

# 1.1.1 Transmission Lines for Millimeter-Wave and Sub-Millimeter-Wave Frequencies and Applications

In general, a transmission line is a media that can carry or guide the electromagnetic energy between a generator and a load. There are many types of transmission lines available for guiding the signals, like twisted pairs, coaxial cables, optical fibers, strip line, microstrip transmission lines, coplanar transmission lines, etc. [3], [4]. These transmission lines are used for different applications according to their features, range of frequency and compatibility. Here we deal with the planar transmission lines such as Microstrip lines, Strip lines and Coplanar Wave Guides (CPW) that can be easily integrated in silicon technology.

RF microelectronics research started emerging with the development and use of planar transmission line / propagation structures, because of its features, like ease of fabrication, miniaturization and adaptability for both active and passive devices. With the increase in frequency, applications and the development of novel substrates led microstrip and CPW to widely used as transmission lines for RF applications[3]-[10]. Recently, **Slow-Wave Coplanar Wave Guides (S-CPW)**, a novel structure developed to use instead of microstrip and CPW. In this thesis, we characterize the emerging topology S-CPW along with coplanar waveguide transmission lines and microstrip transmission lines.

## 1.1.2 Slow-Wave Coplanar Waveguide (S-CPW) Transmission Line

S-CPW was introduced [11]-[15] to miniaturize and to improve the quality factor (Q-factor) of the passive structures. The major drawbacks of the microstrip transmission lines and the CPW transmission lines in the silicon-integrated technologies are their size and poor quality factor. There are different approaches that have been done to miniaturize the transmission lines, by using high permittivity substrates and lumped or semi-lumped components [15], but these are restricted to apply in the silicon integrated technologies. In the silicon integrated technologies the classical transmission lines such as CPW have high losses when the frequency increases, due to its dielectric loss effects in the low-resistivity silicon substrate and the conductive loss. Concerning microstrip lines, losses are limited because, the ground plane prohibiting the electromagnetic field to go through the low-resistivity substrate. Nevertheless, due to a low effective dielectric constant, a low Q- factor can be achieved.

The standard approach to miniaturize the transmission line is by increasing relative dielectric permittivity  $\varepsilon_r$  of the substrate, which eventually reduces the phase velocity,  $v_p = c/\sqrt{\varepsilon_r}$ . The "Slow wave" transmission line uses the principle of separating the electric and magnetic energy, to reduce

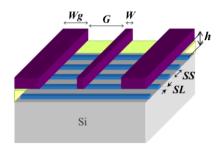

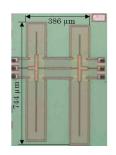

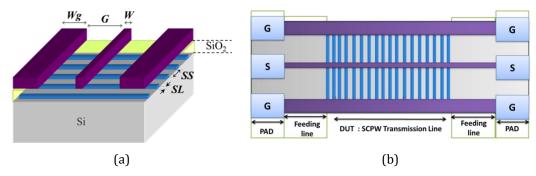

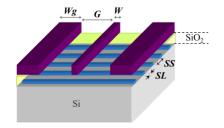

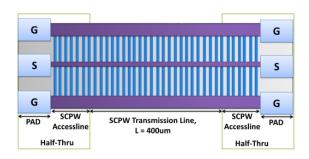

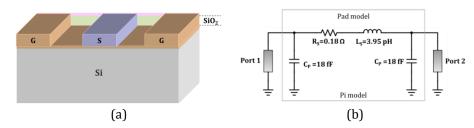

the phase velocity instead of using a high dielectric permittivity  $\varepsilon_r$  substrate. S-CPW are based on conventional CPW with floating metallic strips underneath the line as shown in Figure 1.1.

Figure 1.1. S-CPW Structure

Consider a classical S-CPW configuration, where W is the width of the signal strip G is the gap between signal and ground, Wg is the ground plane width, SL is the floating strips length, SS is floating strips space and h is dielectric thickness between floating strips and the CPW lines.

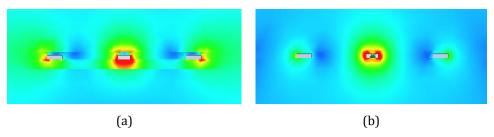

The electric and magnetic field propagation modes of S-CPW simulated using a 3D electromagnetic solver Ansys HFSS [16] are shown in Figure 1.2. In Figure 1.2 signal strip is in the center with two ground strips on both sides, like conventional CPW and with horizontal floating strip to reduce the phase velocity.

Figure 1.2. S-CPW line: (a) E-Field (b) H-Field

From the S- CPW line in Figure 1.2(a), the fingers of length SL with a space of SS are created as a shield against the low resistivity substrate. If we use a whole ground instead of floating fingers (such as microstrip lines), we induce eddy currents in the thin lower metal layer and it would increase the significant conductive loss. In S-CPW, the transversal arrangement of the floating fingers prevents the currents flowing longitudinally to the signal propagation. Moreover, if fingers gap SS is optimized the electric field is confined between the signal and grounds of S-CPW. Since there is no electric field in the lossy silicon substrate, the losses due to the low resistivity silicon substrate are reduced. Hence S-CPW losses are comparable to microstrip line losses and lower than CPW ones. Finally, the floating shield results in the significant increase of the capacitance per unit length  $C_l$  compared to CPW. As shown in Figure 1.2(b) the magnetic field passes through the patterned ground, hence the inductance per unit length  $L_l$  is quite unchanged compared to CPW lines.

Thanks to the increase of the capacitance, the phase velocity in the S-CPW (1.2) decreases as compared to the CPW transmission line. Therefore, it is "Slow-Wave" coplanar waveguide. Due to this we can obtain (1.2) a high relative effective permittivity.

$$v_p = \frac{1}{\sqrt{L_l \cdot C_l}} \tag{1.1}$$

$$\varepsilon_{reff} = C_0^2 . L_l . C_l \tag{1.2}$$

Also the quality factor [17] expressed as,

$$Q = \frac{\beta}{2\alpha} \tag{1.3}$$

The advantages of S-CPW lines are easy miniaturization and higher quality factor, about 2 to 3 times higher than the classical transmission lines in CMOS/BiCMOS technologies [15].

# 1.1.3 Motivation: Applications at Millimeter-Wave Frequencies and Above

The transmission lines are an essential passive component for any device/application from the low frequency to the high frequency. Concerning the applications of millimeter and sub-millimeter wave frequency circuits (Video-streaming 57-66 GHz, 76-81 GHz automotive radar, medical imaging 140 GHz, etc.) the need and characterization of the transmission lines are very important. Transmission lines are used in wide variety of passive and active applications such as interconnection for the circuits, calibration and de-embedding circuits from vector network analyser (VNA) to devices, filters, baluns, power dividers, couplers, power amplifiers, detectors, mixers, antennas, trans receivers etc. They serve a major role in every two ports and multiport devices.

Some applications/devices using microstrip transmission lines and CPW Transmission lines are shown in Figure 1.3. Figure 1.3 (a) shows 60 GHz MM BPF[18] using a microstrip lines, Figure 1.3(b) is a Power Amplifier matching network using Microstrip Stubs [21], Figure 1.3(c) shows a chip microphotograph of the 30-GHz CPW filter[19] and Figure 1.3(d) shows a chip microphotograph of the 3-stage 60-GHz CPW amplifier [19].

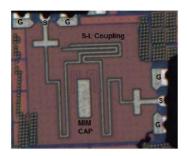

Since S-CPW transmission lines have many advantages over microstrip and CPW transmission lines, they can be widely used in many passive and active circuits/applications. IMEP-LAHC is developing applications specifically based on S-CPW topologies. Figure 1.4(a) shows Band Pass Filter (Dual Behaviour Resonator (DBR) type) which uses S-CPW lines, [20], further examples with the power splitter and power dividers with S-CPW transmission lines [22], [15], which are shown in Figure 1.4(b)

and Figure 1.4(c) and finally the matching network of a power amplifier is changed from microstrip to S-CPW [21] shown in Figure 1.4(d).

(a) 60 GHz MM BPF[18]

(b) Power Amplifier matching network Using

Microstrip Stubs[21]

(c) Chip microphotograph of the 30-GHz CPW filter[19]

(d) Chip microphotograph of the 3-stage 60-GHz CPW amplifier[19]

Figure 1.3. Different RF/millimeter wave applications utilize Microstrip and CPW transmission lines

(a) Band pass Filter (DBR type)[20]

(b) Power splitters[15]

(c) Power divider balun[15]

(d) Power Amplifier matching network using S-CPW[21]

Figure 1.4. Different RF/millimeter wave applications utilize S-CPW transmission lines

The motivations of this Ph.D. thesis are to develop the de-embedding methods to characterize the transmission lines, especially, **S-CPW** at millimeter wave and sub-millimeter wave frequencies. Also analyse the various issues for **S-CPW**, CPW and microstrip transmission lines at millimeter wave and sub-millimeter wave frequencies and provide the solutions to overcome it [3]-[15].

### 1.1.4 Electromagnetic Modeling and Measurement Uncertainties

Considering the transmission line modeling, circuit designers use electrical scalable models (Using Agilent ADS or other circuit simulators) or electromagnetic (EM) models (Ansys HFSS, CST Microwave Studio, COMSOL Multiphysics...) to understand its characteristics.

Considering electrical scalable model and with its optimization, it is difficult to analyse the design problems at higher frequencies, especially when the targeting applications are in millimeter and sub-millimeter wave frequencies. The electrical scalable models are easy to use for designing and optimizing transmission lines. But considering all the parasitic and coupling elements of a transmission line model, especially at the millimeter wave frequency range, it is difficult and in many cases not even possible. It has the disadvantages of analysing proper electromagnetic behaviour of the transmission lines and difficulty to understand the radiation effects, higher order transmission modes, etc. [23]. Therefore, we need to have an EM (electromagnetic) model to characterize them properly for the different applications [24]. EM modeling helps to analyse all the physical effects of passive structures/devices such as losses, fields, radiation effects, higher order transmission modes, etc. The EM simulation is time consuming, but it gives more accurate results than the electrical scalable models.

Many 3D full wave Electromagnetic simulators are commercially available (Ansys HFSS, CST Microwave Studio, COMSOL Multiphysics...). These simulators use different mathematical techniques to solve and characterize electromagnetic structures. We utilize an industry-standard simulation tool Ansys HFSS (High Frequency Structure Simulator) [16]. This software is a 3D full wave frequency domain electromagnetic field solver based on the finite element method (FEM). HFSS automatically generates mesh and solves Maxwell's equations at several nodes of the meshing; also it allow us to generate our own strict meshing for the electromagnetic structures.

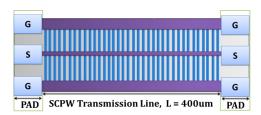

Consider a S-CPW transmission line [11]-[15] as shown in Figure 1.5(a) as a Device under Test (DUT) . The transmission line is excited with wave port having an impedance of  $50\,\Omega$  and with all the boundary conditions. The realistic measurement structure includes the pads and interconnects/accesslines to connect the DUT with the signal. Figure 1.5 (b) shows the actual measurement model of the S-CPW transmission line. The important factors for a realistic design of on-wafer passive structures are, to have a proper pad configuration (GS, GSG, GSSG, etc.) with a proper

probe pitch. In addition, pad size can vary with different probes, so it is better to have a minimum/proper pad size according to the probe used for the measurement.

Figure 1.5. (a) S-CPW alone (b) S-CPW under on-wafer measurement

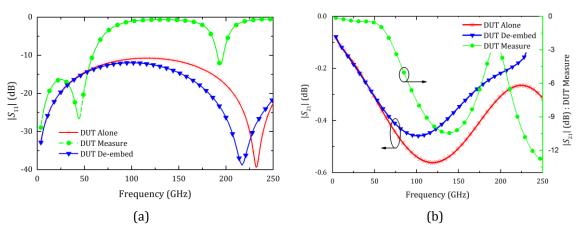

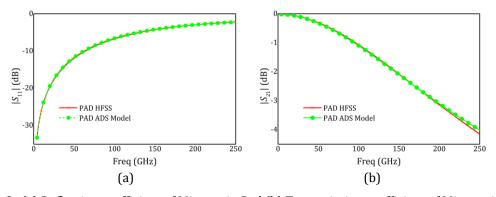

Figure 1.6. (a)  $|S_{11}|$ : reflection coefficient (b)  $|S_{21}|$ : transmission coefficient

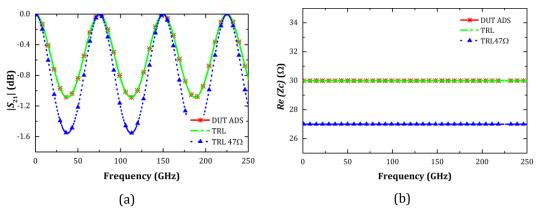

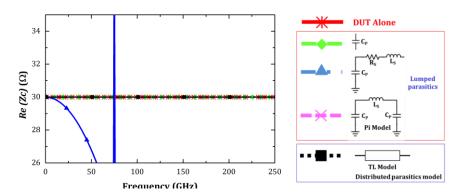

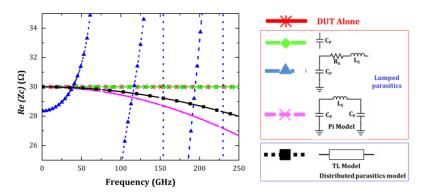

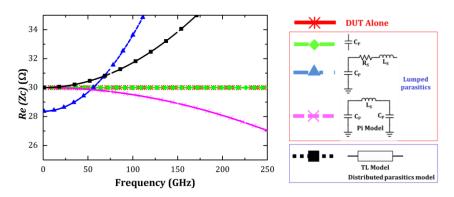

The above S-CPW transmission lines are simulated up to 250 GHz using HFSS. The magnitude of the transmission and reflection coefficients ( $S_{21}$  and  $S_{11}$ ) of the S-CPW transmission line are given in Figure 1.6(a) and Figure 1.6(b) respectively. DUT alone is S-CPW transmission line without pad and accesslines simulated in Ansys HFSS and DUT measure is the realistic measurement model with pad and accessline. As shown in Figure 1.6, the characteristics of the device alone and the actual measurement device (before de-embedding) are different. It is because of the parasitic effects from the pad and the interconnecting lines. We need to mathematically eliminate these effects from the measurement to know the actual device characteristics of the DUT. There are different mathematical methods, which are used to eliminate these parasitics from the measurement that is called dembedding. Here we present the de-embed results using a general two transmission lines dembedding method (Mangan method [28], [41]), which is also shown in the Figure 1.6. It shows the variations with the DUT alone >60 GHz in magnitude of  $S_{21}$  and  $S_{11}$ . So we need to investigate or develop new methods to characterise devices at millimeter wave and sub-millimeter wave frequencies.

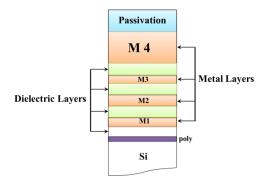

The simulation and the fabrication of components in the silicon technology include different Back End of Lines (BEOL) for different technologies [1], [11], [15]. Consider a general BEOL stack of a CMOS technology shown in Figure 1.7. This consists of several metal layers, which are submerged in multiple layers of dielectric material. The dielectric material may have different dielectric permittivities depending on each layer. The dimensions depend on the technology used.

Figure 1.7. BEOL stacks of a Silicon Technology

The process variation and design rule densities of the silicon technologies can affect the electromagnetic modeling. In the electromagnetic modeling, we do not consider the metal density rules, and we use an effective dielectric permittivity of the substrate in the different stacks, this may create a variation in the electromagnetic design with the actual characteristics. This is not true in a modern CMOS process, where the permittivity can vary with the process. Generally, the materials used have a lower dielectric permittivity ( $\varepsilon_r$ ) to reduce capacitive coupling between metal layers.

Actual CMOS processes require a certain percentage of metal in each metal layer. The Design Rule Check (DRC) checks these density rules. In order to satisfy the density requirements, most of the circuit is filled with metal-dummies. The metal-dummies can affect the performance and RF characteristics, which may introduce new parasitic effects and degradation in the quality factor of the passive structures by increasing the coupling losses at high frequencies. The other performance factors includes for a passive structure design is substrate conductivity, which increases the losses. Apart from the electromagnetic modelling, the major challenges for a millimeter-wave device characterisation are the measurement and the extraction of parasitic effects.

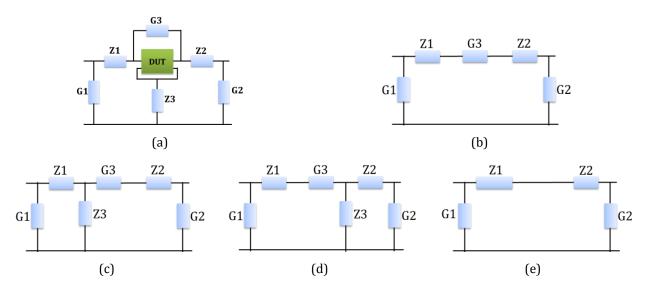

# 1.1.5 De-embedding and Challenges

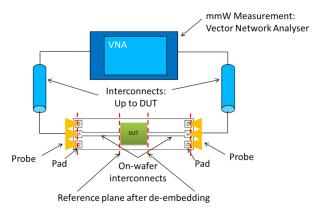

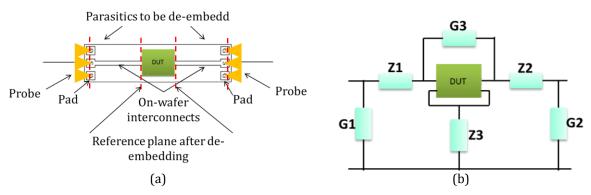

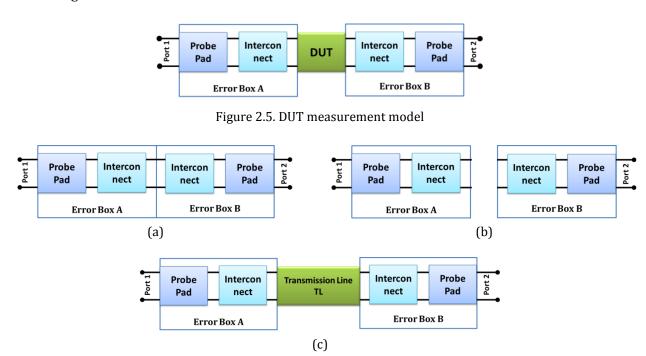

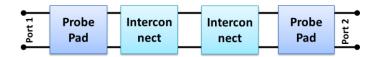

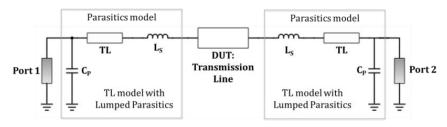

The measurement model of device under test is shown in Figure 1.8. The DUT is connected with on-wafer interconnects and the pads for the measurement. Calibrating the vector network analyser, allows eliminating the effects of interconnects from VNA and probes, and setting the reference place at the probe tips. The measurement of the DUT includes the parasitic effects of the pads and interconnecting lines. These effects should be subtracted from the measured results to get the actual characteristics of the device. The process of mathematically removing the unwanted parasitic effects is

called "De-embedding" [26] -[44]. Thus, a de-embedding step must be performed to obtain the intrinsic parameters of the DUT. When we use the general calibration algorithms like Line-Reflect-Reflect-Match (LRRM), Thru-Reflect-Line (TRL), etc., the on-wafer de-embedding can often name as "On-Wafer Calibration". Generally, de-embedding is performed after the VNA calibration.

Similar to the calibration of the VNA, de-embedding is performed by measuring the various test structures like *Open, Short, Load, Line* and *Thru*, etc. depending on the method [25] - [40]. After De-embedding, the actual characteristic of the device is obtained. The reference plane de-embedding is shown in the Figure 1.8. Apart from the frequency and accuracy of the de-embedding method, it is important to use less number of de-embedding structures to reduce the cost. Also, it is important to reduce the number of steps to perform the de-embedding. A good de-embedding method should able to take care of the parasitic effects from the pads, interconnects and substrate coupling. Generally, a de-embedding method must be accurate, cost effective and reliable.

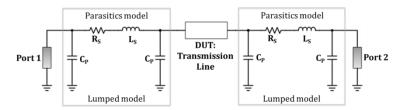

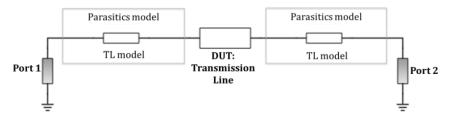

Figure 1.8. Measurement model: Reference plane after De-embedding

The de-embedding method can be modeled in many ways, like purely lumped, distributed microwave network parameter based, like *S, ABCD*, or *T-matrix* based on the combination of both lumped and distributed. Even different calibration techniques are also widely used to de-embed the parasitics. TRL is the most common and considered as a "standard" de-embedding/on-wafer calibration method [25], [26]. Considering the de-embedding methods, lumped de-embedding techniques were introduced first, in which the parasitic effects are considered as parallel and series lumped elements. This fundamental method is extended to "three-step" and improved "three-step" methods [30] - [33]. These methods are analysed from very low frequency to high frequencies. According to the frequency and the device model, there are different combinations of de-embedding structures are used, like *open*, *short* and *thru*. For higher frequencies, several steps of de-embedding have to be performed to achieve better characteristics of the device [27]. In the literatures, lumped methods are used for de-embedding both active and passive devices such as transistors, transmission lines, inductors, etc. [27]-[36]. Apart from lumped methods there are de-embedding methods based on distributed microwave network parameter based methods [37]-[40]. Mainly these methods consider the pad or pad interconnects

parasitics in to single to multiple cascaded based matrices. These types of methods are basically used to extract the characteristics of passive devices. TRL is considered as a cascaded matrix based method. Also, there are methods based on both lumped and distributed network based matrices [41] - [44]. These different types of methods and the limitations are explained in next chapter.

Nowadays there are many de-embedding methods available to de-embed the device. There are many de-embedding methods which will work for few "GHz" band. The important fact is that many methods are limited to the frequency. When the frequency increases to millimeter-wave, the parasitics cannot be localized only in to pad and interconnect. There are other parasitics associated with the on-wafer measurement environment, which can also affect measurement and de-embedding. Most of the de-embedding methods are investigated until millimeter wave frequencies, say 60 GHz to max 110 GHz. Currently there are methods which can provide good de-embedding up to 100GHz. It is important to develop the de-embedding methods beyond 100GHz, because of the emerging applications in the range of millimeter wave and sub-millimeter wave frequencies.

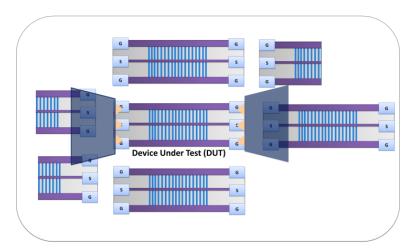

De-embedding methods have many limitations and challenges apart from the frequency limitation. The limitations of de-embedding methods are deeply involved in the test structures used, mathematical methods, and its mathematical limitations. Also on an on-wafer measurement, the parasitics are appearing not only from pads and interconnects from the DUT but there is also parasitics from the substrate, the adjacent cells, other coupling effects between probe-to-probe, probes to substrate, etc. In ideal, the parasitics are only from the pad and its interconnecting lines, but in an actual measurement of a device includes many adjacent devices as shown in Figure 1.9.

Figure 1.9. Actual measurement model of the DUT with adjacent devices

Generally, the calibration is performed until the probe tips. However, when you measure the DUT with probes, the probe can be coupled with substrate or can be coupled with other devices on the wafer. This creates other parasitic effects and losses [45]-[48]. Also the transition [40] from pad to interconnect and from the interconnect to DUT may make changes in the de-embedding. It is because

of the difference in the impedance at transition, further followed by a change in the parasitic variation, which may find difficult to calculate by de-embedding methods.

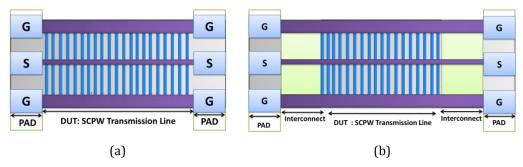

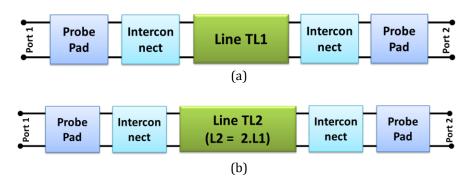

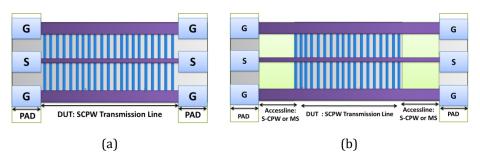

# 1.1.6 De-embedding with and without Interconnect/Accesslines

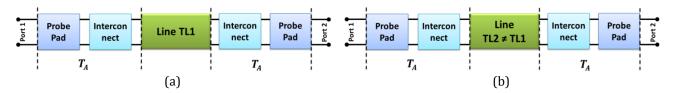

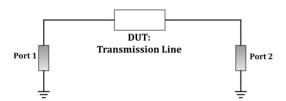

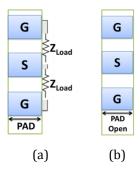

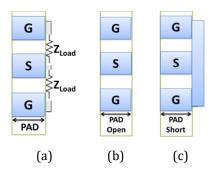

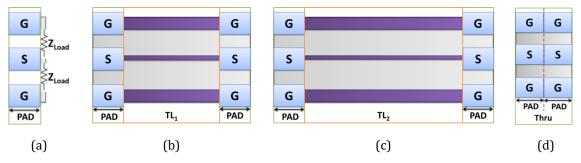

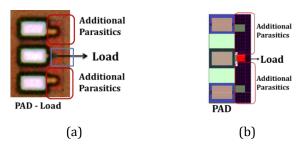

The measurement model of the DUT can be modeled in different ways. There are two kinds of de-embedding devices in the literature; (1) the DUT is directly connected to the PAD [41], [44], which is shown in Figure 1.10 (a), and (2) the DUT is connected to the PAD with interconnecting lines, which is shown in Figure 1.10(b) [32], [43].

Figure 1.10. (a) DUT: Directly connected to the PAD (b) DUT: Connected with both PAD and interconnect

These models can affect the de-embedding results. However, our DUT is a planar transmission line structure we can use either one of them. If we try to de-embed a transistor or any small passive device, it is necessary to have an accessline to avoid the cross coupling in the measurement and to establish the correct EM propagation mode. Until now, there is no proper definition for a de-embedding measurement model in transmission line de-embedding. It is important to understand whether the direct connection/interconnect parasitics affects the transmission line de-embedding at millimeter wave frequencies or not.

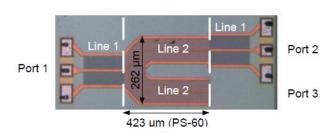

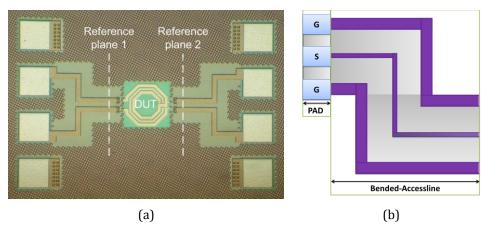

### 1.1.7 Bended-Accessline De-embedding

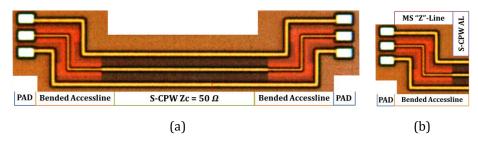

Bended-accesslines are used to interconnect the devices [49]. Mainly 4-port DUTs use Bended-accessline, an example is shown in Figure 1.11(a). The bended-accessline structure is shown in Figure 1.11(b). These kinds of lines are difficult to de-embed for very high frequency. Presently, lumped methods and TRL are used to de-embed these lines. Lumped methods are limited to the lower frequencies. The unknown line parameter (characteristic impedance) and the fact that more than one line is required to cover the entire frequency band up to millimeter wave are the disadvantages of TRL method. This increases the area and cost, so there is a need for better de-embedding method, which is applicable for these kinds of accesslines.

Figure 1.11. (a) Bended-Accessline used in a 4-port DUT [49] (b) Model of Bended-Accessline

# 1.1.8 Excessive Losses at Millimeter Wave Frequencies and Above

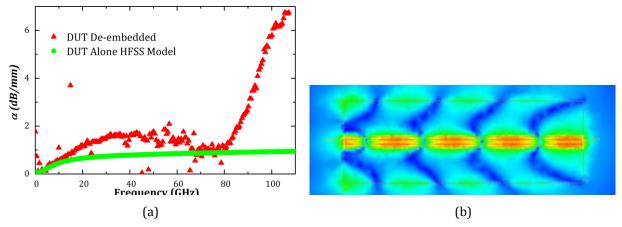

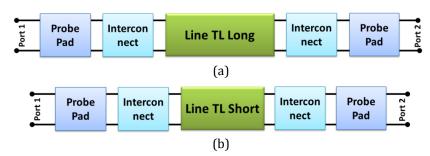

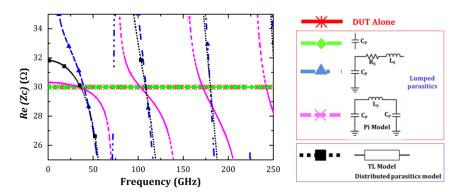

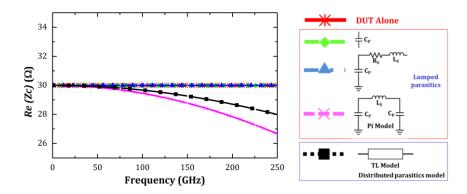

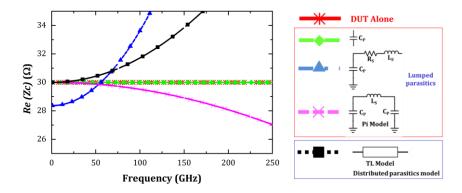

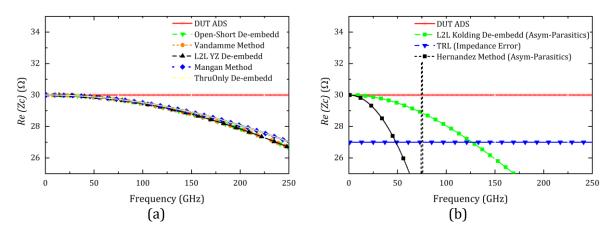

The studies by A.L. Franc [11] identified the excessive loss happening for measurement above 60GHz for S-CPW. In most of the de-embedding methods, it remains the same. The methods are not able to take care of this specific problem. In addition, the same problem exists in the CPW transmission line (DUT De-embedded) and homogenous CPW transmission line (DUT Alone HFSS Model) as shown in Figure 1.12(a).

Figure 1.12. (a) Attenuation of a CPW de-embedded line and CPW HFSS model (b) Parallel plate propagation in a CPW line [47]

The major reasons for the excessive loss are higher order modes, which introduces additional propagation of electromagnetic waves, into the lossy substrate, and to the adjacent devices. These propagations may happen with the potential difference of the probe and the conductors on the substrate. This introduces the parallel plate propagation [46], [47] as shown in Figure 1.12(b).

At low frequencies, the conventional transmission line supports quasi-TEM mode but at higher frequencies, these non-TEM modes may induce extra losses [14]. These losses are additive phenomena, apart from the normal conductive and dielectric losses. Thus, one of the important goal of this thesis is to analyse and identify the reasons and suggests the solutions for this problem.

# 1.1.9 Other Measurement Challenges

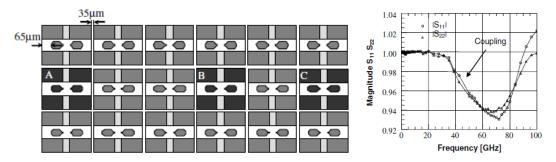

The results of the recent studies explain that there can be a possibility of coupling due to the adjacent structures on on-wafer measurement [48], [50]-[52] (see Figure 1.13).

Figure 1.13. Measurement model: problem of adjacent cell coupling [48]

This shows a strong coupling from the adjacent cells near the DUT. All the studies show a strong influence from the substrate and the adjacent cells. There are different solutions to avoid the coupling between the adjacent cells. The best solution is to separate the adjacent cells far as about >250  $\mu$ m, which is practically impossible, because of the large area required on the wafer and increased cost.

Apart from measurement and de-embedding challenges, on-wafer measurement environment and calibration can affect the accuracy of the de-embedding and characterization of the device. This explains in the section of on-wafer measurement and challenges at millimeter wave frequencies.

### 1.1.10 Conclusion of State of the Art and Problem Description

Section 1.1 explains the state of the art and the problem description. With the technology advances and applications in millimeter wave and sub-millimeter wave frequency makes the devices smaller. Thus, measurement and characterization of these devices are important to ensure the best performance. Generally, a device (in our case: S-CPW transmission line) on wafer cannot be measured easily. DUT requires additional parasitics such as pad and interconnects for measurement. To know the actual characteristics of the device, the parasitics should be removed mathematically, this is called de-embedding. But current de-embedding methods are limited by frequency. Beyond 100 GHz, still there are methods to investigate and develop for the future, because of the large number of applications at millimeter wave and sub-millimeter wave band. A new de-embedding method faces many challenges at this frequency. We describe the problem of different type of interconnecting line for example bended-accessline. In the measurement, there are other problems such as the excessive loss at higher frequencies and the coupling between the adjacent measurement cells, etc. These make DUT characterization and de-embedding at millimeter wave frequencies and above highly challenging.

# 1.2 On-Wafer Measurement and Challenges at Millimeter Wave Frequencies

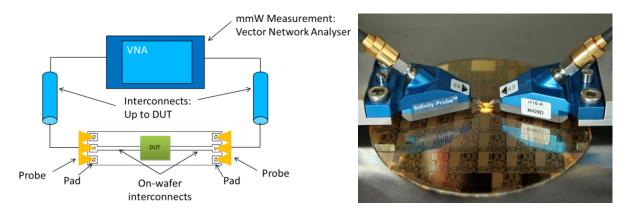

De-embedding and characterization challenges are not only limited to the DUT, different type of interconnecting lines and adjacent devices problems. The characterization of the DUT beyond millimeter wave frequencies may affect the environment of the on-wafer measurement, such as on-wafer measurement setup, probes, the calibration substrate and algorithm. On-wafer measurement setup of a "complex system" is shown in Figure 1.14. This is developed by Cascade Microtech [53]. This system includes Probe station, VNA, measurement device on wafer, probes for measurement and interconnecting cables. The probe station also includes the on-wafer test chunks, micro-chamber, probe positioner for the positioning of the test wafer with DUT, microscope for viewing the test DUT, and other system controls. VNA used to measure the electromagnetic signals from the DUT and probes used for the measurement of the DUT.

Figure 1.14. On-Wafer Measurement Setup (Cascade Microtech Probe Station)

The simplified on-wafer measurement of a passive device (transmission line) is shown in Figure 1.15. This includes VNA, interconnects to the DUT, and the probes for the measurement. Generally the device is fabricated on a silicon wafer along with other devices. Considering the complexity of the system, the accurate measurement requires many corrections in the measuring setups and measured data [23].

Consider the above measurement setup of the DUT as shown in the Figure 1.15. To get the accurate measurement of the DUT, we need to eliminate the major errors occurring from the measurement setup, such as

- Error from the cables, which are using to connect the VNA

- Errors from the Pad and Interconnects

- Coupling between the Probes

Calibration of the VNA will eliminate the errors till the probe tips [54]-[56]. To eliminate the pad, interconnect errors and the coupling between the probes, we have to apply certain mathematical corrections called de-embedding, which are explained earlier.

Figure 1.15. Simplified measurement setup of a device under test

# 1.2.1 Calibration and Challenges

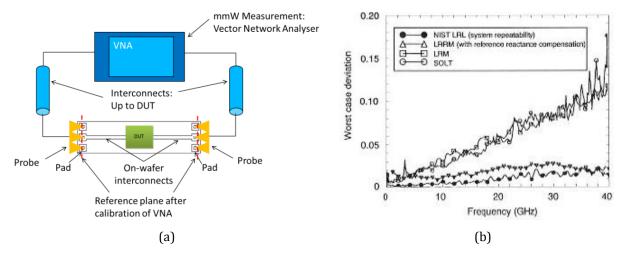

Calibration is defined as the "set of operations that establish under specified conditions, the relationship between values of quantities indicated by a measuring instrument or measuring system, or values represented by a material measure or a reference material, and the corresponding values realized by standards" [57]. Calibration is critical for a VNA to make good S-parameter measurements [54]. Calibrating the VNA with standards at the probe tips allows to remove the repeatable errors from the VNA, cable, and probe losses and reflections. The calibration process utilizes the technique of vector error correction, in which error terms are calculated from measurement of known standards, these errors can be removed from actual measurements. There are different types of possible calibration algorithms that are available according to the number of error terms, and type of standards used to perform the calibration. Many of them are implemented within VNAs. SOLT, LRM, LRRM, and TRL are the four most commonly used wafer probe calibrations [54], [59]-[63]. In the case of on-wafer measurement, we perform calibration on the probe tip. After the calibration, the reference plane is moved to the end of the probe tip, which is shown in the Figure 1.16(a). Cascade Microtech utilizes LRRM method for probe tip calibration. The Figure 1.16(b) describes LRRM calibration that can be comparable with TRL calibration methods. While the frequency increases, the parasitics due to the environment is important, including the mechanical support on which the calibration set and the wafer is placed [64].

Figure 1.16. (a) Measurement set up: Calibration reference of the Vector Network Analyser (b) Comparison of probe tip calibration methods [56]

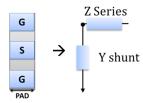

Contact substrate and calibration substrate are also used in calibration procedure. [58]. Calibration substrate or Impedance Standard Substrate (ISS) is used to perform the standard measurements and obtain the error terms for calibration. ISS uses alumina as a substrate because of its low loss characteristics. The commonly used calibration standards are *open, short, load, thru,* and *line* standards. These standards are often realized in the CPW design. Calibration accuracy depends on the calibration method, the probes used, probe tip physical placement accuracy and the ISS used.

### 1.2.2 RF Probes

There are different types of RF probes (shown in the Figure 1.17) available according to their use and frequency of operation. The features of a probe include the coaxial connector, probe body, probe tip, and the contacts at the probe tip end. The transition from coaxial line to a conventional transmission line is made within the probe. Since the electric field distributions are different from coaxial to the conventional transmission line used in the probe tip, the only difficulty is the transition at high frequencies. A good wafer probe has a good matching between the coax-conventional probe tips, and proper conversion of the electromagnetic energy between different propagation modes. For a good DUT measurement the electric field patterns at the probe tip are similar to the field patterns in the DUT and then there will be minimum parasitic coupling to the probe [65]-[68].

When high frequency probes are used for on-wafer measurement it is important that what is measured at the probe tips contact. This includes the parasitics from pad, and other parasitics associated with the on-wafer interconnects and other devices on your substrate. Measurements are sensitive to contact resistance by the probe tip. Conventionally tungsten tips are used in the RF probes, but tungsten tips increase the contact resistance with aluminium pad, because tungsten oxidizes and the aluminium easily accumulates on the probe tips. This results in poor measurement repeatability. A poor on-wafer probing causes more implications like inconsistent measurements, contact resistance

issues, often re-probing, and pad damage. It limits the re-probing, increase of the number of tests, time, cost and reduction in productivity. So considering the on-wafer measurement the major challenges for RF probes can be described as,

- Frequency limitations of the probe

- High measurement accuracy, reliability and repeatability

- Stable contact resistance between the probe tip and the pad, it should be very low for better performance

- Good crosstalk characteristics

- Less unwanted coupling between probe and the wafer, probe and the nearest devices

The three major RF probes are described by considering the frequency of usage, different applications and the probe tip configuration (See Figure 1.17).

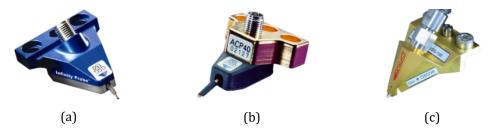

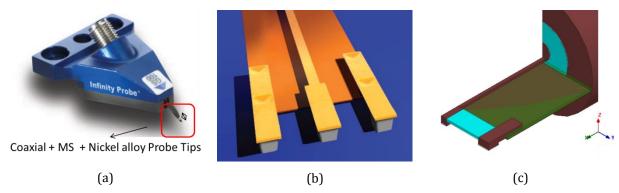

Figure 1.17. Different types of RF probes (a) Infinity Probe (b) Air Coplanar Probe (ACP) (c) |Z| Probe

Infinity probe: The model of the Infinity probe is shown in the Figure 1.17(a). Infinity probes are developed for high frequency characterizations of the RF devices. Infinity probe uses microstrip transmission lines to carry the signal between the co-axial connector to the probe tips. The transmission lines on the Infinity thin-film technology gives more confined fringing fields than conventional coplanar tips. The contact area of the probe tip is  $12x12 \, \mu m$

<u>Air Coplanar Probe (ACP):</u> The model of Air Coplanar Probe is shown in the Figure 1.17(b). The Air Coplanar Probe is a rugged microwave probe with a compliant tip for accurate and repeatable measurements on-wafer [67]. Air Coplanar Probes have excellent probe-tip visibility, lowest loss and good electrical performance.

**[Z] Probe:** The model of the |Z| Probe is shown in the Figure 1.17(c). It has a robust design for coplanar structures with long probe lifetime. The |Z| Probe has high impedance control with perfectly symmetrical coplanar contact structure, which eliminates the signal distortion. In |Z| probe the RF/Microwave signal is shielded and completely air isolated in the probe body which gives excellent performance even in vacuum environments.

Comparisons between three major RF probes are described in Table 1.1

| Infinity Probes                              | Air Coplanar Probes           | Z  Probes                                    |  |

|----------------------------------------------|-------------------------------|----------------------------------------------|--|

| ■ From 40GHz to 325 GHz                      | ■ From DC to 110 GHz          | ■ From DC to 67 GHz                          |  |

| ■ Low contact resistance,                    | ■ Approximately 0.1 Ω on Al   | <ul><li>Low contact resistance</li></ul>     |  |

| $< 0.05 \Omega$ on Al, $< 0.02 \Omega$ on Au | ■ Stable and repeatable over- | $\sim 0.05~\Omega$ on Al                     |  |

| ■ High RF measurement                        | temperature measurements      | ■ High-accuracy measurements                 |  |

| accuracy and Highly reliable                 | ■ May be couplings to nearby  | <ul><li>May be couplings to nearby</li></ul> |  |

| ■ Reduced unwanted couplings                 | devices and transmission      | devices and transmission                     |  |

| to nearby devices and                        | modes because of coplanar     | modes because of coplanar                    |  |

| transmission modes                           | structure                     | structure                                    |  |

| ■ Excellent crosstalk                        | ■ Excellent crosstalk         | ■ Excellent crosstalk                        |  |

| characteristics                              | characteristics               | characteristics                              |  |

| Only on-wafer/planar surface                 | ■ Great compliance for        | ■ Both planar and non-planar                 |  |

| ■ Maximum temperature 125°C                  | probing non-planar surface    | surface                                      |  |

| ■ Typical probe life time >                  | ■ Temperature from -65 ° C to | ■ Maximum temperature 300° C                 |  |

| 250,000                                      | + 200° C                      | ■ Typical probe life time >                  |  |

|                                              | ■ Typical probe life time >   | 1,000,000                                    |  |

|                                              | 500,000                       |                                              |  |

Table 1.1 Comparison between different RF Probes

## 1.3 Conclusion

The environment of on-wafer measurement including RF probes, calibration algorithms and calibration substrate can affect the device de-embedding and characterization.

In RF/Microwave/Millimeter-Wave circuit design, the characterization and de-embedding of the transmission line over millimeter and sub-millimeter wave frequencies are critical. As we explained above, currently there are good de-embedding methods, which will work for lower frequency and up to 100GHz. There are methods to investigate and develop beyond 100 GHz for the future, because of the large number of applications at millimeter wave and sub-millimeter-wave band. A good de-embedding method should eliminate all the parasitics. It should be accurate over wide band, reliable and cost effective. There are excessive losses at higher frequencies possibly due to higher order modes, surface waves, parallel plate propagation, and coupling, etc. So we need to investigate a good on-wafer model which can be free from all these unwanted parasitics, hence we can improve the measurement accuracy and able to characterize a device properly.

Next chapter reviews and benchmarks the current de-embedding methods. The chapter classifies and explains the current de-embedding methods according to various types, the size of the DUT and the range of the frequency. The chapter benchmarks all the de-embedding methods, by considering both electrical (controlled parasitics) and 3D EM simulation tool Ansys HFSS (realistic parasitics). The chapter also explains different limitations and different characteristics needed for a good de-embedding method for a wide band up to millimeter wave and sub-millimeter wave frequency range.

## 1.4 References

- [1] A. Cathelin and J. J. Pekarik, "Silicon Technologies to Address mm-Wave Solutions," in *mm-Wave Silicon Technology*, A. M. Niknejad and H. Hashemi, Eds. Springer US, pp. 25–57, 2008.

- [2]A. Hamidian, "60 GHz transceiver circuits in SiGe-HBT and CMOS technologies.", phdthesis, Technischen Universität Berlin, 2014

- [3] D. M. Pozar, "Microwave Engineering", 4th Edition Dec. 2011.

- [4] R.Orta, "Lecture Notes on Transmission Line Theory", Nov. 2012.

- [5] D. D. Grieg and H. F. Engelmann, "Microstrip-A New Transmission Technique for the Klilomegacycle Range," *Proc. IRE*, vol. 40, no. 12, pp. 1644–1650, Dec.1952.

- [6] Jia-Sheng Hong, M. J. Lancaster, "Microstrip Filters for RF / Microwave Applications", 2nd Edition, Dec .2001

- [7] I. J. Bahl and D. K. Trivedi, "A Designer's Guide to Microstrip Line," *Microwaves*, pp. 174–182. May 1977.

- [8] C. P. Wen, "Coplanar Waveguide: A Surface Strip Transmission Line Suitable for Nonreciprocal Gyromagnetic Device Applications," *IEEE Trans. Microwave Theory Tech.*, Vol. 17, No. 12, pp. 1087-1090, Dec. 1969.

- [9] R.N. Simons "Coplanar Waveguide Circuits, Components, and Systems", Wiley-IEEE Press, April. 2001.

- [10] R. E. Collin, "Foundations for Microwave Engineering", 2nd Edition., Dec. 2000.

- [11] A.-L. Franc, "Lignes de propagation intégrées à fort facteur de qualité en technologie CMOS. Application à la synthèse de circuits passifs millimétriques," phdthesis, Université de Grenoble, 2011.

- [12] D. Kaddour, H. Issa, A.-L. Franc, N. Corrao, E. Pistono, F. Podevin, J. M. Fournier, J. Duchamp, and P. Ferrari, "High-Q Slow-Wave Coplanar Transmission Lines on 0.35 m CMOS Process," *IEEE Microw. Wirel. Compon. Lett.*, vol. 19, no. 9, pp. 542–544, Sep. 2009.

- [13] A.-L. Franc, E. Pistono, and P. Ferrari, "Design guidelines for high performance slow-wave transmission lines with optimized floating shield dimensions," in *Microwave Conference (EuMC), 2010 European*, pp. 1190–1193, 2010.

- [14] Ø. Bjørndal, "Millimeter wave interconnect and slow wave transmission lines in CMOS," Masters thesis, Universitetet i Oslo, 2013.

- [15] F. Burdin, "Nouvelles Topologies des diviseurs de puissance, balun et déphaseurs en bandes RF et millimétiques, apport des lignes à ondes lentes," phdthesis, Université de Grenoble, 2013.

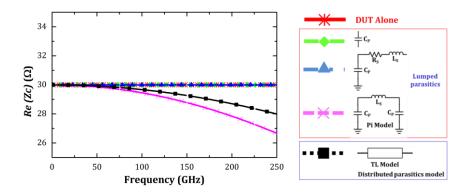

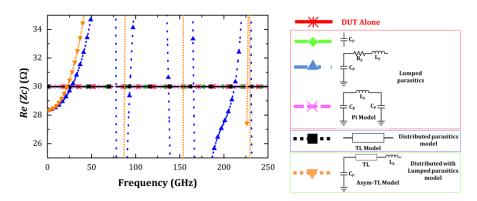

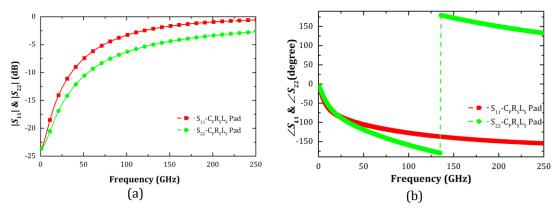

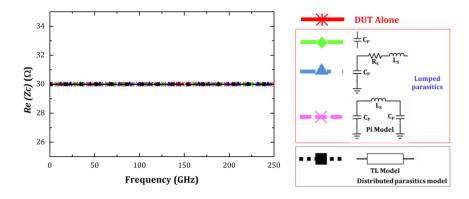

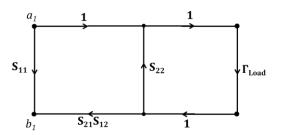

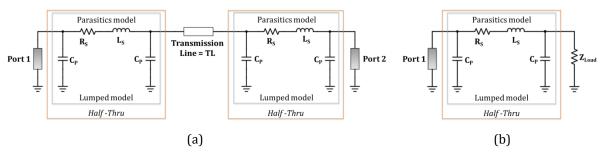

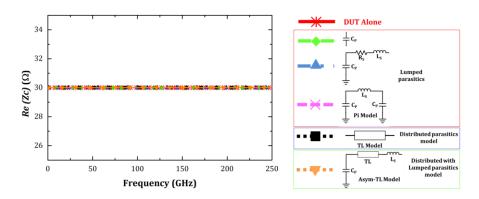

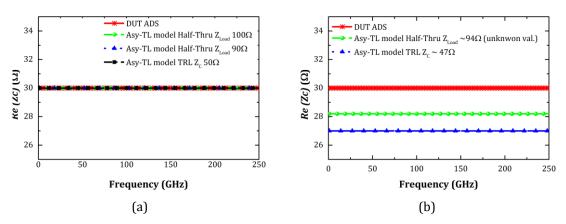

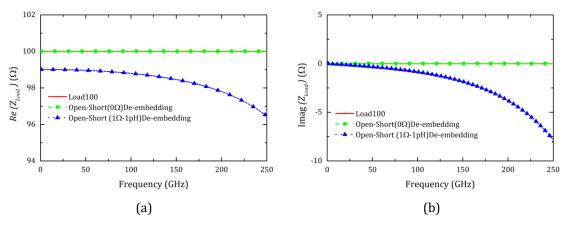

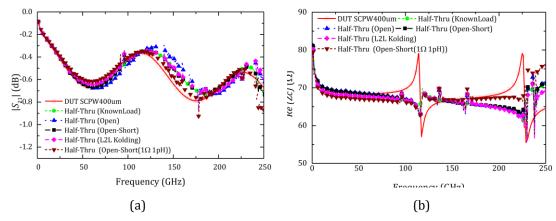

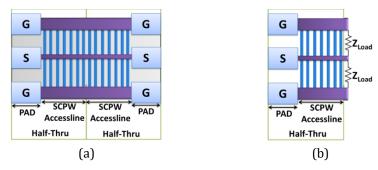

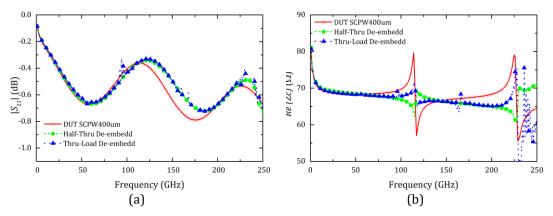

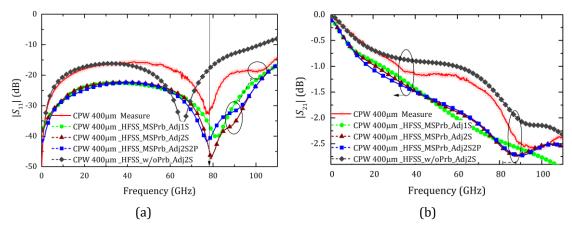

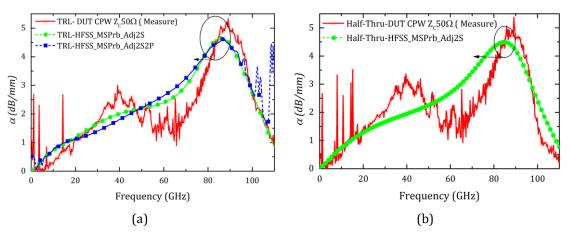

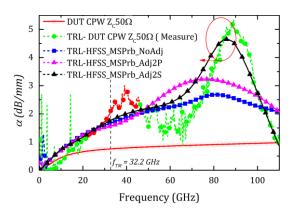

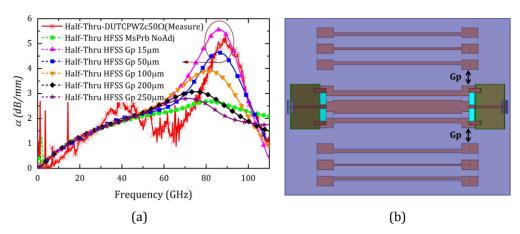

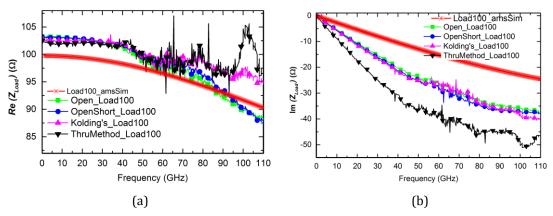

- [16] ANSYS® HFSS, Release 14.0, ANSYS, Inc.