# **Circuit Level Techniques for Power and Reliability Optimization of CMOS Logic**

A Dissertation Presented to the Academic Faculty

By

#### Abdulkadir Utku Diril

In Partial Fulfillment

Of the Requirements for the Degree

Doctor of Philosophy in

Electrical and Computer Engineering

Georgia Institute of Technology May 2005

Copyright © 2005 by Abdulkadir Utku Diril

# **Circuit Level Techniques for Power and Reliability Optimization of CMOS Logic**

#### Approved by:

Dr. Abhijit Chatterjee, Chair School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Madhavan Swaminathan School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Hsien-Hsin S. Lee School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Vijay K. Madisetti School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Adit D. Singh Department of Electrical Engineering Auburn University

Date Approved: April 14, 2005

my wife Aytül, my parents Umut and Nuran Diril, and my sister Ayşegül

#### **ACKNOWLEDGEMENTS**

I am grateful to my research advisor Prof. Abhijit Chatterjee for his support and guidance. He has been a mentor to me all the time. I am also thankful to Prof. Adit Singh. The discussions we made had a profound effect on the direction of my research.

During the course of my stay at Georgia Institute of Technology, I had the chance to interact with many distinguished faculty members. I would like to thank Prof. Sean Lee for the insights he gave about the semiconductor industry. I would like to thank Prof. John Uyemura, Prof. Phillip Allen, Prof. Vincent J. Mooney, and Prof. Scott Wills for the experience they shared with me through classes and discussions.

The six months internship that I did at NVIDIA really speeded up my research. The skills that I developed while I was working there were very useful to me when I came back to complete my degree. I would like to thank David Dignam, Andrew Bell, Venkat Kommu, John Robinson, and Brian Hutsell at NVIDIA.

I would like to thank my beautiful wife Aytül for her support and love. Her love made me stronger. I would also like to thank my parents Nuran and Umut and my sister Ayşegül for always believing in me.

I want to thank Yuvraj S. Dhillon for being a great lab-mate and friend to me.

Also I want to thank everyone in our lab for providing a nice environment.

I would like to thank Börteçene Terlemez for his support in almost every issue during my stay in Atlanta. I also would like to thank all the present and past members of the Atlanta Turkish Folk Dances Group and all of my friends including but not limited to Orkun Karadenizli, Doğa Özyürekli, Emre Ersin, Güçlü Onaran, Sermet Akbay, Oğuz

Ergin, Gökhan Mergen, Prof. Ahmet Erbil, Mazlum Koşma, Faik Başkaya, Özgür Çelebican, Engin Erdoğan, Hamza Kurt, Berk Gencülgen, Emrah Kotan, and İlkay Yavrucuk.

### TABLE OF CONTENTS

| ACKN   | NOWLEDGEMENTS                                                                          | iv   |

|--------|----------------------------------------------------------------------------------------|------|

| LIST ( | OF TABLES                                                                              | ix   |

| LIST ( | OF FIGURES                                                                             | X    |

| NOMI   | ENCLATURE                                                                              | xii  |

| SUMN   | //ARY                                                                                  | xiii |

| СНАР   | TER I - INTRODUCTION                                                                   | 1    |

| 1.1    | MOTIVATION                                                                             | 1    |

| 1.2    | THESIS ORGANIZATION                                                                    | 3    |

|        | TER II - EFFECTS OF TECHNOLOGY SCALING TRENDS TER CONSUMPTION AND SOFT ERROR TOLERANCE |      |

| 2.1    | Power Consumption Trends in Microprocessors                                            | 5    |

| 2.2    | EFFECTS OF SCALING ON SOFT ERROR RATES IN MICROPROCESSORS                              | 10   |

| CHAP   | TER III - MODELING CMOS GATES                                                          | 12   |

| 3.1    | OPERATION OF A CMOS GATE                                                               | 12   |

| 3.2    | SPICE MODELING OF CMOS GATES                                                           | 16   |

| 3.2    | 2.1 Calculating the Delay of a Circuit                                                 | 20   |

| 3.2    | 2.2 Calculating the Energy Consumption of a Circuit                                    | 22   |

|        | TER IV - LOW POWER DUAL SUPPLY VOLTAGE CMOS                                            |      |

| 4.1    | REVIEW OF POWER REDUCTION TECHNIQUES                                                   | 24   |

| 4.1    | .1 Dynamic Power Reduction Techniques                                                  | 24   |

|        | 4.1.1.1 Decreasing Switched Capacitance                                                | 24   |

|        | 4.1.1.2 Decreasing Supply Voltage                                                      | 25   |

| 4.1.2       | Stati           | c Power Reduction Techniques                                                | 27   |

|-------------|-----------------|-----------------------------------------------------------------------------|------|

| 4.1.        | .2.1            | Increasing Threshold Voltage                                                | 27   |

| 4.1.        | .2.2            | Using Transistor Stacks                                                     | 29   |

| 4.2 I       | Level           | -SHIFTER FREE DESIGN OF DUAL SUPPLY DIGITAL CIRCUITS                        | . 30 |

| 4.2.1       | Pseu            | do Dual Supply Voltage Domino Logic Design                                  | 30   |

| 4.2.        | .1.1            | Design Strategy with NPD1 Type Gates                                        | 33   |

| 4.2.        | .1.2            | Design Strategy with NPD2 Type Gates                                        | 35   |

| 4.2.        | .1.3            | Algorithm for Power Optimization using NPD Gates                            | 38   |

| 4.2.        | .1.4            | Results of PPD-NPD Replacement                                              | .41  |

| 4.2.2       | Dual            | Supply Voltage CMOS Design                                                  | 45   |

| 4.2.        | .2.1            | CMOS Gate Design with Built-in Level Shifting Capability                    | 48   |

|             | .2.2<br>gic Gat | Algorithm for Dual Supply Voltage Assignment Using Level Shifting CMC es    |      |

| 4.2.        | .2.3            | Results for Gate-Level Dual Supply Voltage CMOS Implementation              | 56   |

| 4.2.<br>Lev |                 | Improvement Obtained by Using Level Shifting Logic Gates over Regular fters | 59   |

| 4.2.        | .2.5            | Complexity Analysis of Dual Supply Voltage Assignment Algorithm             | .61  |

| _           |                 | - IMPROVING SOFT ERROR TOLERANCE OF<br>ONAL CMOS CIRCUITS                   | . 64 |

| 5.1         | GLITCI          | H TOLERANCE CHARACTERISTICS OF INDIVIDUAL GATES                             | . 66 |

| 5.2         | SOFT E          | ERROR RATE MONITORING                                                       | . 70 |

| 5.2.1       | Inde            | pendent SER Sensors                                                         | 71   |

| 5.2.2       | Emb             | edded Concurrent Error Detectors                                            | 72   |

| 5.3         | Circu           | IT SOFT ERROR TOLERANCE ESTIMATION                                          | . 74 |

| 5.3.1       | Estir           | mating the Logical Masking                                                  | 75   |

| 5.3.2       | Estir           | mating the Electrical Masking                                               | 76   |

| 5.3.3       | Estir           | nating the Latching-Window Masking                                          | 78   |

| REFE | REFERENCES                                                    |      |  |

|------|---------------------------------------------------------------|------|--|

| APPE | NDIX B - BUBBLE PUSHING AND DUPLICATION                       | .95  |  |

| APPE | NDIX A - TOPOLOGICAL SORTING                                  | .94  |  |

| 6.2  | FUTURE DIRECTIONS                                             | . 93 |  |

| 6.1  | Conclusions                                                   | . 90 |  |

| СНАР | TER VI - CONCLUSION AND FUTURE RESEARCH                       | .90  |  |

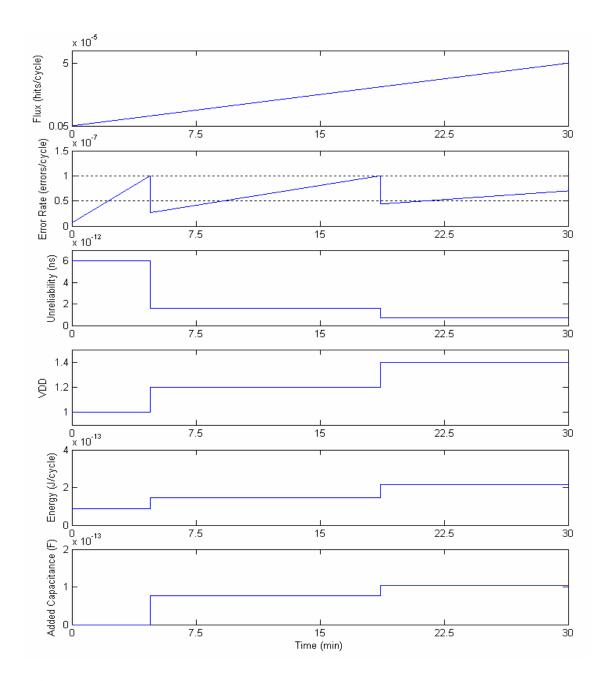

|      | EXPERIMENTAL RESULTS FOR DYNAMIC SOFT ERROR TOLERANCE CONTROL |      |  |

| 5.5  | IMPLEMENTATION OF THE CONTROL TECHNIQUE                       | . 82 |  |

| 5.4  | DYNAMIC SOFT ERROR TOLERANCE CONTROL                          | . 79 |  |

## LIST OF TABLES

| 1 | Results for NPD1 replacement scheme when the extra NMOS transistor is sized to be $1.08\mu$ .                                                          | 44 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | Results for NPD2 replacement scheme when the second threshold voltage is chosen to be 0.85 V.                                                          | 44 |

| 3 | Results of dual supply voltage assignment for input switching activity of 0.1.                                                                         | 57 |

| 4 | Comparison of energy savings when dual supply voltage assignment is done (i) using level shifting logic gates and (ii) using dedicated level shifters. | 60 |

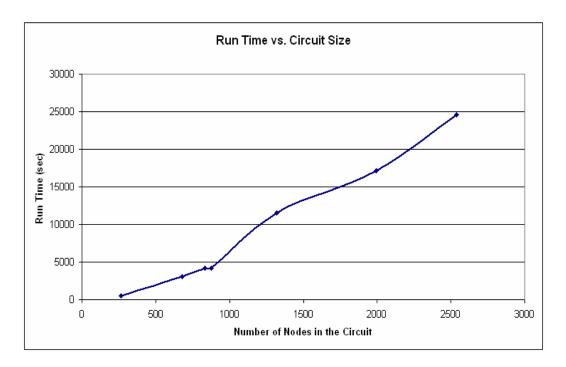

| 5 | Run time of the low supply voltage assignment algorithm for ISCAS'85 benchmark circuits.                                                               | 62 |

| 6 | Results of dynamic soft error tolerance control scheme for (a) 30fF limit and (b) no limit on added capacitance.                                       | 87 |

## LIST OF FIGURES

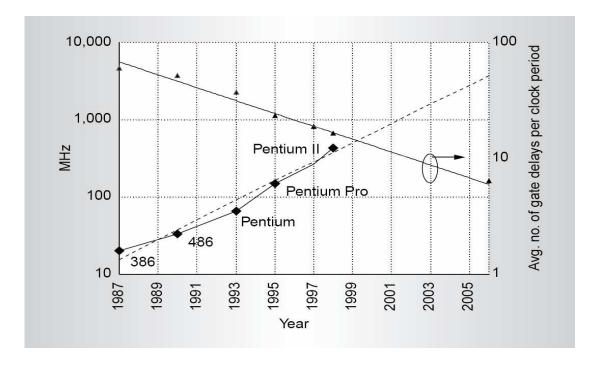

| 1  | Processor frequency and average number of gate delays per clock period for various Intel processors.                                         | 6  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------|----|

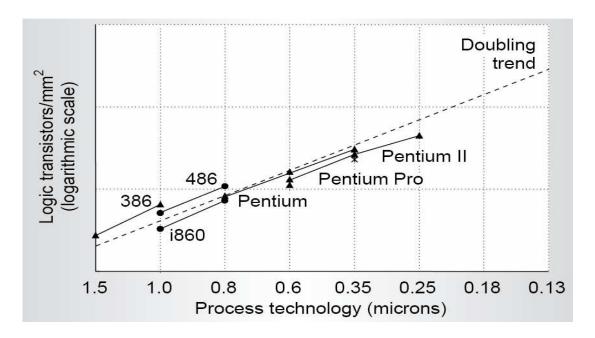

| 2  | Transistor density for various Intel processors.                                                                                             | 7  |

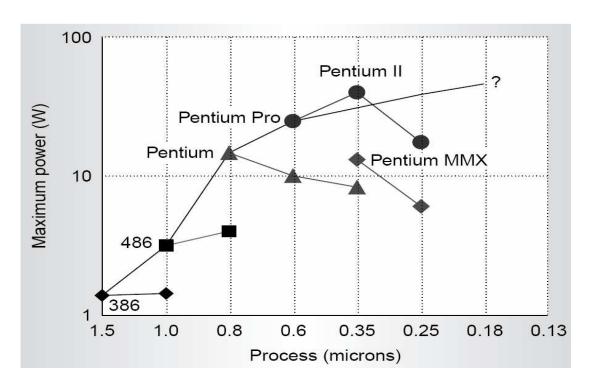

| 3  | Maximum thermal power dissipation for various Intel processors.                                                                              | 8  |

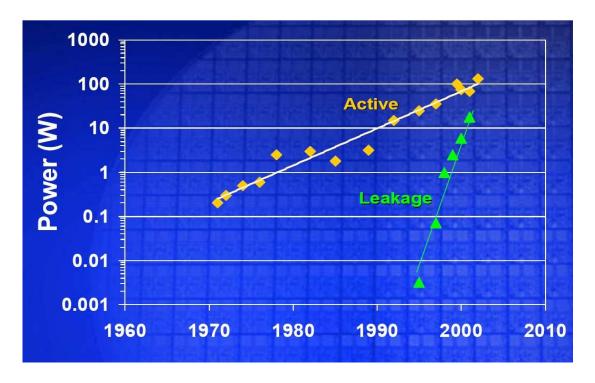

| 4  | The change in active (dynamic) and leakage power consumptions for<br>the past Intel processors.                                              | 9  |

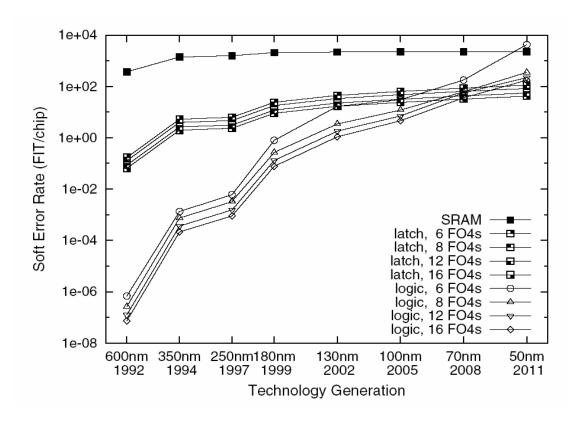

| 5  | SER/chip for SRAM/latches/logic.                                                                                                             | 11 |

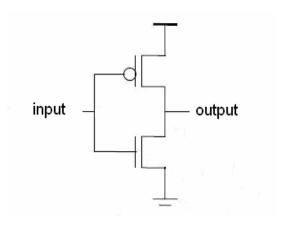

| 6  | CMOS Inverter circuit.                                                                                                                       | 12 |

| 7  | The Components of static energy dissipation.                                                                                                 | 15 |

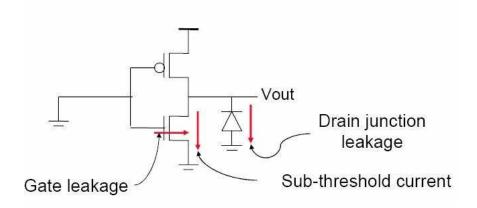

| 8  | Domino Logic 3-input AND gate.                                                                                                               | 31 |

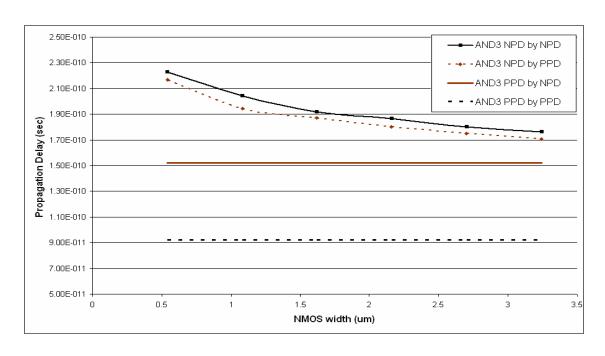

| 9  | Variation of propagation delay for NPD1 AND gate with width of extra NMOS transistor.                                                        | 34 |

| 10 | Variation of E010 for NPD1 AND gate with width of extra NMOS transistor.                                                                     | 34 |

| 11 | Variation of E00 for NPD1 AND gate with width of extra NMOS transistor.                                                                      | 35 |

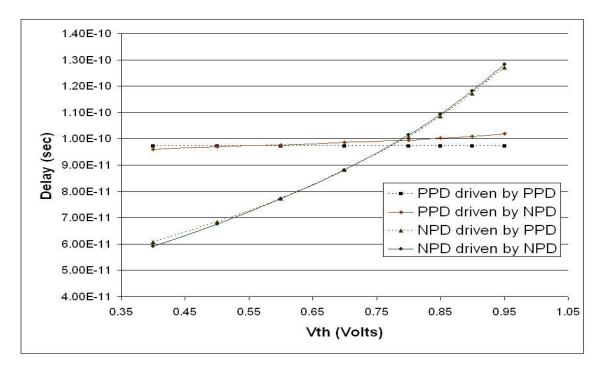

| 12 | Variation of propagation delay for AND3 gates with threshold voltage of inverter PMOS transistor.                                            | 36 |

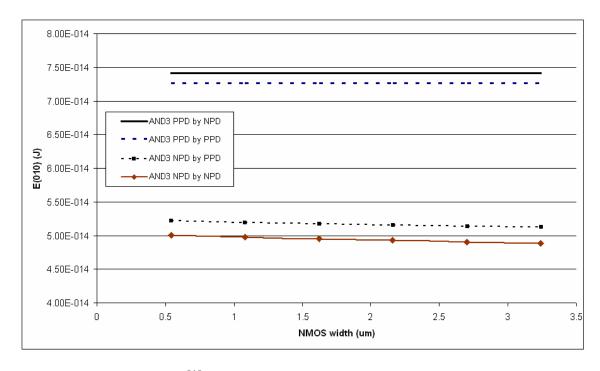

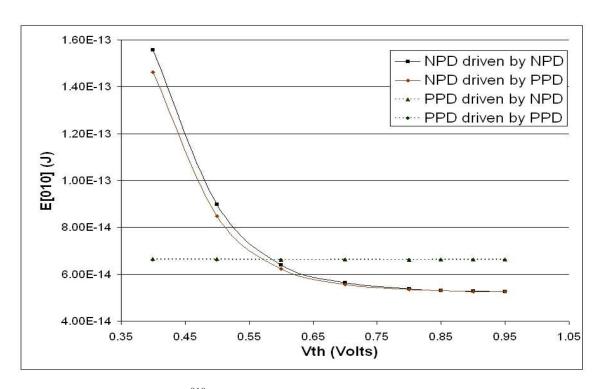

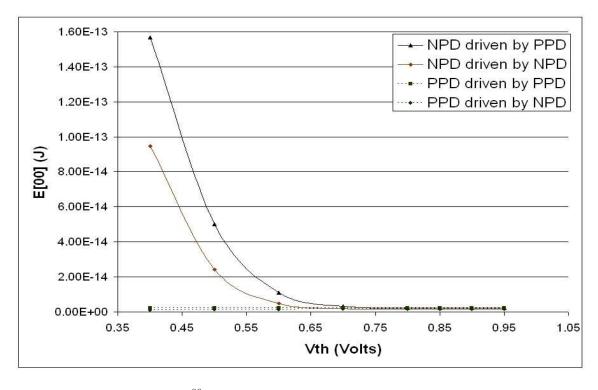

| 13 | Variation of E010 for AND3 gates with threshold voltage of inverter PMOS transistor.                                                         | 37 |

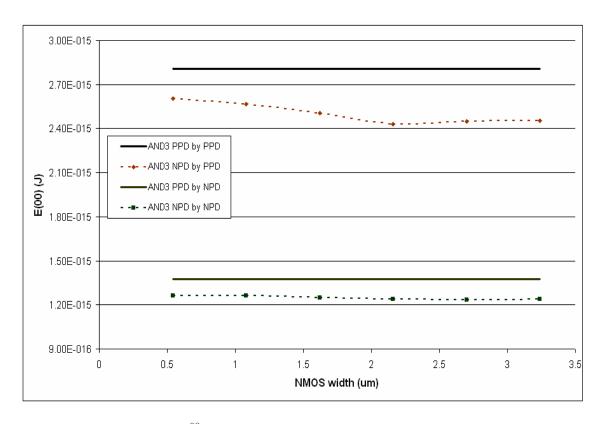

| 14 | Variation of E00 for AND3 gates with threshold voltage of inverter PMOS transistor.                                                          | 37 |

| 15 | Algorithm for PPD-NPD replacement.                                                                                                           | 39 |

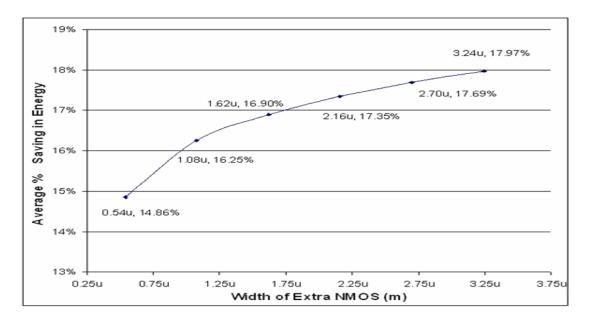

| 16 | Variation of average energy savings with width of extra NMOS transistor for ISCAS'85 benchmark circuits for NPD1 replacement.                | 43 |

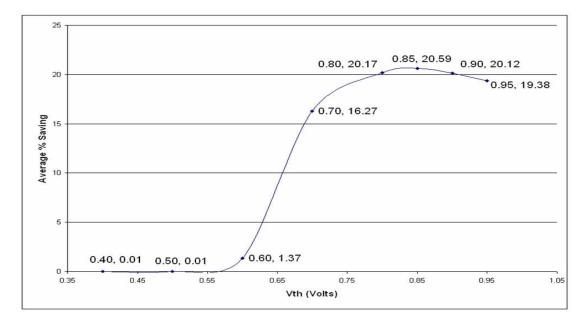

| 17 | Variation of average energy savings with threshold voltage of inverter PMOS transistor for ISCAS'85 benchmark circuits for NPD2 replacement. | 43 |

| 18 | A low voltage inverter driving a high voltage inverter.                                                                                      | 47 |

| 19 | Level shifting NAND2 gate with one high voltage and one low voltage                                                                          | 49 |

| inputs. M1 l | has higher | threshold | voltage | magnitude | than M2. |

|--------------|------------|-----------|---------|-----------|----------|

|--------------|------------|-----------|---------|-----------|----------|

| 20 | A regular level shifter.                                                                                                         | 49 |

|----|----------------------------------------------------------------------------------------------------------------------------------|----|

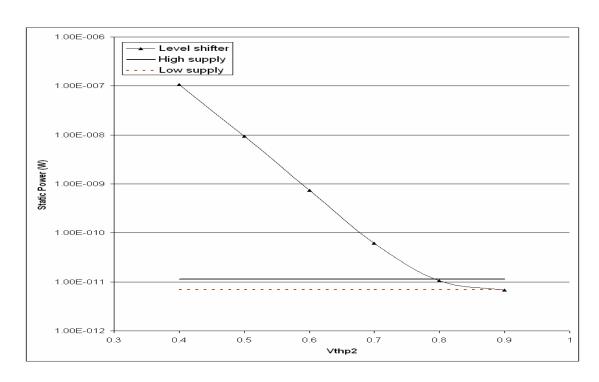

| 21 | Static power dissipation of high voltage, low voltage, and level shifting NOT gates for different Vthp2 values.                  | 51 |

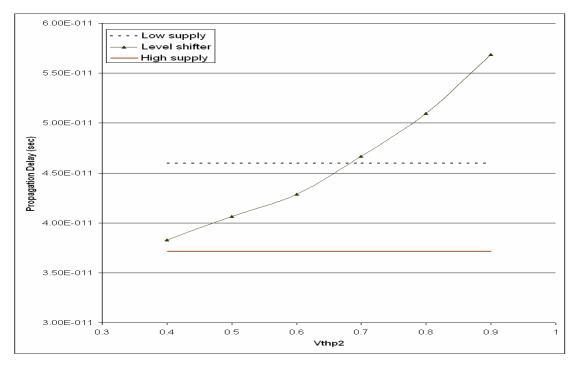

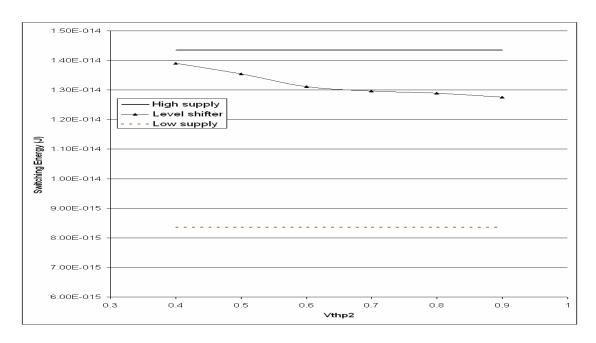

| 22 | Propagation delay of high voltage, low voltage, and level shifting NOT gates for different Vthp2 values.                         | 51 |

| 23 | Switching energy of high voltage, low voltage, and level shifting NOT gates for different Vthp2 values.                          | 52 |

| 24 | Algorithm for VDDH-VDDL replacement.                                                                                             | 55 |

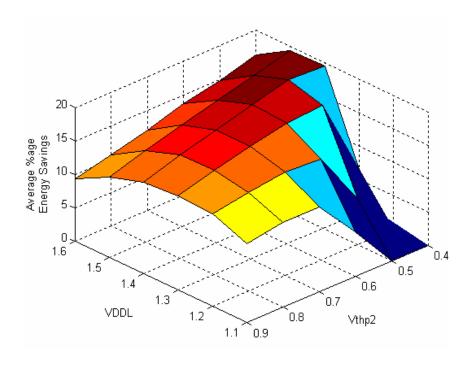

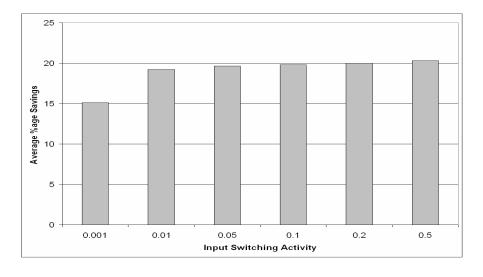

| 25 | Variation of average energy savings with varying Vthp2 and VDDL for switching activity = $0.1$ .                                 | 58 |

| 26 | Average energy savings obtained for different switching activities with circuits optimized for switching activity of 0.1.        | 58 |

| 27 | Run time of the low supply voltage assignment algorithm plotted against the number of nodes.                                     | 63 |

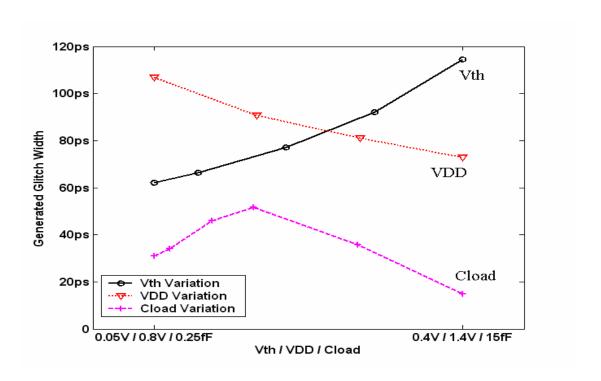

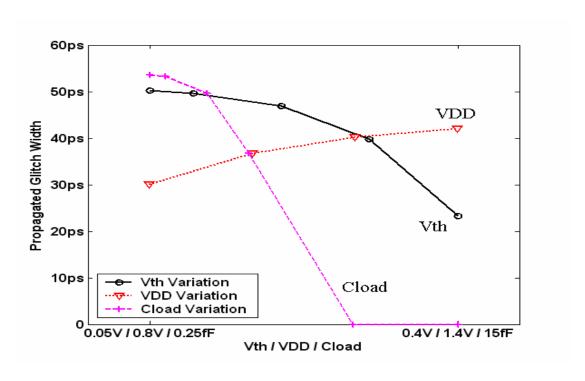

| 28 | Glitch generation characteristics for an inverter for an injected charge of 16fC at its output.                                  | 69 |

| 29 | Glitch propagation characteristics of an inverter for an input glitch of duration 50ps.                                          | 69 |

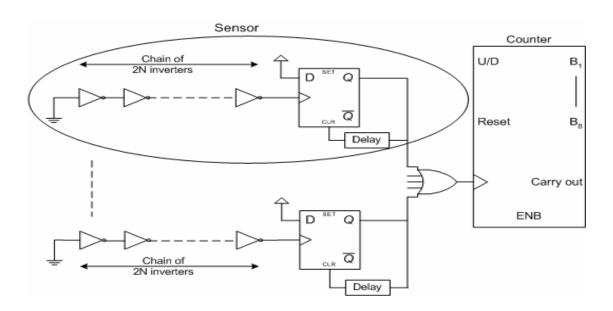

| 30 | Inverter chain setup for monitoring SER.                                                                                         | 71 |

| 31 | Shadow latch setup for monitoring SER.                                                                                           | 72 |

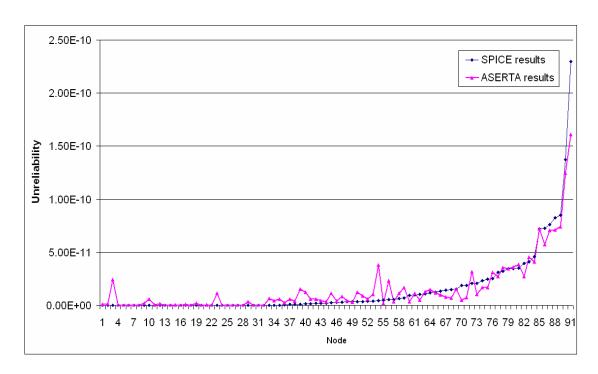

| 32 | Unreliability values obtained by SPICE and ASERTA for nodes in c432.                                                             | 79 |

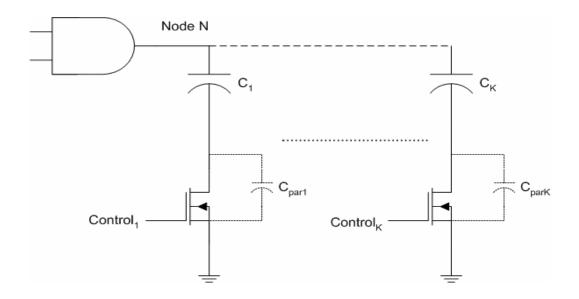

| 33 | Node capacitance control using NMOS switches.                                                                                    | 80 |

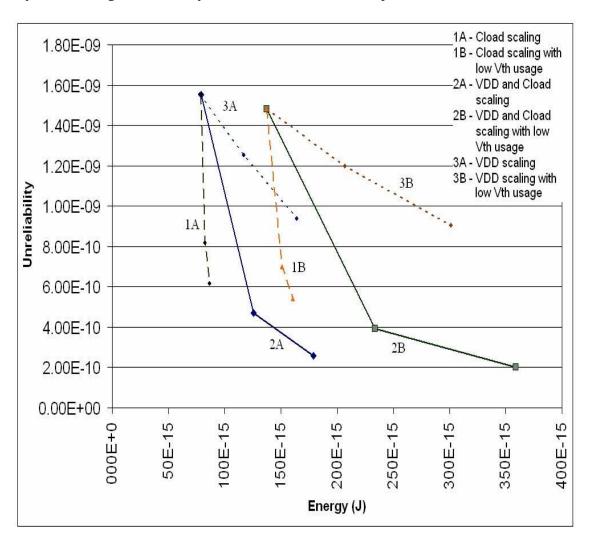

| 34 | Effect of VDD scaling, Cload scaling and Vth scaling on unreliability and energy of c432.                                        | 85 |

| 35 | Matlab simulation of control methodology on c432 assuming the system is ascending to 10000 feet from ground level in 30 minutes. | 88 |

| 36 | Algorithm for topological sorting.                                                                                               | 94 |

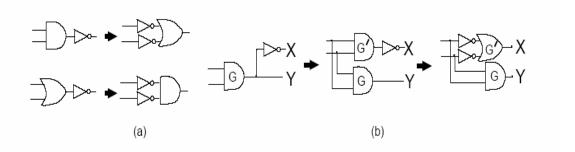

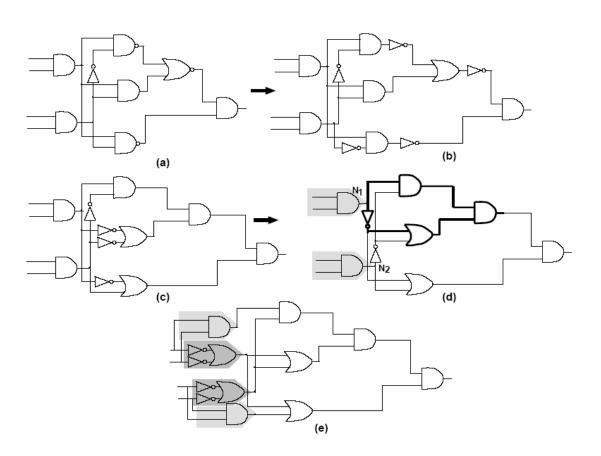

| 37 | Propagating an inverter through logic gate (a) without fanout (b) with fanout.                                                   | 95 |

| 38 | Backward propagation of inverters to obtain inverter-free logic.                                                                 | 96 |

#### **NOMENCLATURE**

**CAD** Computer aided design

**CED** Concurrent error detection

**CMOS** Complementary metal oxide semiconductor

CVS Clustered voltage scaling

**DAG** Directed acyclic graph

**DSM** Deep sub-micron

**ECC** Error correcting code

**FO4** Fanout of four

**HDL** Hardware description language

MIM Metal insulator metal

MLVS Module level voltage scaling

**MOSFET** Metal oxide semiconductor field effect transistor

NMOS Negative channel metal oxide semiconductor

**NPD** NMOS pull-up domino

**PI** Primary input

**PMOS** Positive channel metal oxide semiconductor

**PO** Primary output

**PPD** PMOS pull-up domino

**RBB** Reverse body bias

**SER** Soft error rate

**SPICE** Simulation program with integrated circuit emphasis

**SRAM** Static random access memory

STA Static timing analysis

V<sub>DD</sub> Supply voltage value

$egin{array}{lll} egin{array}{lll} egin{arra$

V<sub>Th</sub> Threshold voltage value

#### **SUMMARY**

Technology scaling trends lead to shrinking of the individual elements like transistors and wires in digital systems. The main driving force behind this is cutting the cost of the systems while the systems are filled with extra functionalities. This is the reason why a 3 GHz Intel processor now is priced less than what a 50MHz processor was priced 10 years ago. As in most cases, this comes with a price. This price is the complex design process and problems that stem from the reduction in physical dimensions.

As the transistors became smaller in size and the systems became faster, issues like power consumption, signal integrity, soft error tolerance, and testing became serious challenges. There is an increasing demand to put CAD tools in the design flow to address these issues at every step of the design process. First part of this research investigates circuit level techniques to reduce power consumption in digital systems. In second part, improving soft error tolerance of digital systems is considered as a trade off problem between power and reliability and a power-aware dynamic soft error tolerance control strategy is developed.

The objective of this research is to provide CAD tools and circuit design techniques to optimize power consumption and to increase soft error tolerance of digital circuits. Multiple supply and threshold voltages are used to reduce power consumption. Variable supply and threshold voltages are used together with variable capacitances to develop a dynamic soft error tolerance control scheme.

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

Technology scaling brought new challenges for the designers in deep sub-micron (DSM) technologies. As transistors became smaller and more transistors are integrated into chips, issues like lowering power consumption, increasing soft error tolerance, and coping with the design complexity became serious challenges, especially for microprocessor manufacturers. New design approaches should be taken to address these problems. The focus of this research is to develop computer-aided design (CAD) tools for addressing some of the aforementioned design challenges facing the digital design community in the DSM era. Reducing power consumption and increasing soft error tolerance are the main subjects of interest.

Power consumption is one of the biggest bottlenecks for high-density chip designers. As the complexity and the transistor count increase, both dynamic and leakage power consumption became significant bottlenecks in the design process. Usage of multiple supply voltages in a digital circuit is studied in academia as an effective way of reducing dynamic power consumption resulting from the quadratic relation of supply voltage to dynamic power consumption [1]-[7]. Even though multiple power supplies can also reduce the leakage power consumption, the most effective approach for leakage power consumption reduction is using multiple threshold voltages in the circuit because of the exponential relation of threshold voltage to leakage power consumption [8]-[10].

Both approaches rely on the fact that there are many gates in a circuit that have enough slack to accommodate the increase in the gate delay resulting from a lower supply voltage and/or higher threshold voltage. Many commercial products are already employing gate-level multiple threshold voltages to decrease leakage power consumption. However, multiple supply voltage usage is still limited to applying different voltages to large portions of the chip. This is partly due to the lack of efficient gate-level CAD tools for design, optimization, verification, and layout of multiple supply voltage circuits, and partly to the overhead of generation and routing of a second supply voltage. However, it can be expected to see more chip producers employ this technique as the research on this subject matures.

Decrease in soft error tolerance in digital systems is another negative side effect of technology scaling. Soft error tolerance of digital circuits decreases significantly because of the reduction in transistor sizes. Reduction in circuit dimensions reduces the capacitance of the circuit nodes, thereby leading to an increase in the voltage magnitude of the glitches caused by a noise source such as  $\alpha$ -particles or cosmic rays [11]. Improving the sequential elements has been the main approach taken for increasing the soft error tolerance of the chips. However, as the circuits' operating frequencies increase and the logic depths in pipeline stages decrease, soft errors seen in combinational circuits will increase and become a significant portion of the total soft errors [12]. Currently, a notebook computer with 256 MB memory which is operated in an airplane at 35000 feet altitude has a failure in every 5 hours because of the particle strikes [13]. With technology scaling, the soft errors in combinational logic will be even worse than this. For systems with variable environmental conditions, designing for the worst case of

particle flux will result in significant energy and/or area, and/or delay overhead. For such systems, adaptability will be an important design parameter. An ideal system should be able to reduce the mentioned overheads when it is not exposed to the worst case environmental conditions.

The challenges introduced by technology scaling trends to designing low power and reliable systems are the primary motivation for this work.

#### 1.2 Thesis Organization

In this work, the problem of static dual supply voltage assignment to combinational circuits and the problem of dynamic soft error tolerance of combinational circuits are addressed. Chapter 2 discusses the effects of technology scaling on power consumption and soft error tolerance of digital systems. It is shown that both issues are posing important challenges to the design community in the deep sub-micron (DSM) era. Chapter 3 explains the circuit modeling approach used in the simulation steps of the developed optimizations. After giving standard analytical models for the energy consumption and delay of a single gate, the SPICE look-up table based approach is explained. The static timing analysis approach used to find the delay of the whole circuit using the single gate characteristics is also explained.

Chapter 4 explains the power consumption reduction techniques developed during this research. First, a review of the power reduction techniques is given. The second part of this chapter explains the low power pseudo dual supply voltage design scheme which is developed for domino logic circuits. This method reduces the power consumption of the domino logic gates using a "dual supply voltage assignment" like design approach, but without using a second supply voltage. The last part of this chapter explains the low

power CMOS circuit design technique using dual supply voltages. A novel level shifting logic gate structure is explained. Then, an algorithm for dual supply voltage assignment using the developed level shifting logic gates is given. The improvement obtained by using the developed level shifting logic gates instead of the standard level shifters is also discussed.

Chapter 5 explains the dynamic soft error tolerance control scheme that is developed for circuits that operate under changing environmental conditions. The chapter starts with the detailed examination of a single gate associated with particle strikes. This examination leads to a soft error tolerance optimization method, which can significantly improve the tolerance of a circuit when the environmental particle flux level is increased.

Finally, in Chapter 6, a brief summary of the research is presented with suggestions on future work. The conclusion also includes the discussions on the major contributions of this work.

#### **CHAPTER 2**

# EFFECTS OF TECHNOLOGY SCALING TRENDS TO POWER CONSUMPTION AND SOFT ERROR TOLERANCE

#### 2.1 Power Consumption Trends in Microprocessors

Scaling of transistors in CMOS technology is the underlying factor for the improvement of digital systems in terms of speed of execution and complexity of tasks the systems are capable of running. The industry is following closely, if not exactly, the trends anticipated by Gordon Moore [14]. Mainly, technology scaling has three goals for every new technology generation [15]:

- Reduce gate delay by 30% (increase the operating frequency by 43%).

- Double transistor density.

- Reduce energy per transistor by about 65%, power consumption by about 50%.

These goals are closely related to each other and they are the results of scaling transistor dimensions. In theory, a new technology generation with transistor width, length, and oxide thickness scaled down by 30% will accomplish all of these three goals. Real data for past Intel microprocessors show that the frequency doubled with each new technology generation, more than the anticipated 43% [15]. This is mainly due to the increased pipeline depths of the microprocessors, leading to less number of gate delays per clock period. The clock period for current Intel processors is close to 10 gate delays, which is almost equal to the optimal logic depth per pipeline stage that is given as six to eight FO4 (fan-out 4) inverter delays in [16]. It can be assumed that the increase in

frequency for future technology generations will be less than two because there is not enough room for designers to scale up frequency by increasing pipeline depth any further. Figure 1 shows a plot of processor frequencies and gate delays per pipeline stage for past Intel processors.

**Figure 1.** Processor frequency and average number of gate delays per clock period for various Intel processors.

Transistor density, however, increased less than the anticipated rate of 50% per technology generation. Even though the goal is met when an existing processor is shrunk using the next process technology, a new processor implemented in the same new process technology shows a drop in density [15]. This may be due to the increased complexity of the new microarchitecture. Figure 2 shows a plot of transistor density for past Intel processors.

Scaling was done keeping the voltage constant until reaching 0.8µ feature size.

This approach keeps the dynamic power consumption resulting from

charging/discharging of capacitances per transistor the same for different technologies, as seen in Equation 1.

$$Power \propto 0.7 \cdot C \cdot V_{DD}^{2} \cdot \frac{1}{0.7} \cdot f = C \cdot V_{DD}^{2} \cdot f$$

(1)

Figure 2. Transistor density for various Intel processors.

This approach led to a dramatic increase in power consumption as the transistor count and design complexity (and therefore switching activity) increased. For that reason, after 0.8µ technology, constant electric field scaling instead of constant voltage scaling was employed. In constant electric field scaling, supply voltage is scaled down by the same amount as the feature size. So, for a 0.7 scaling factor, this approach leads to a ~50% reduction in power consumption per transistor, as seen in Equation 2.

$$P \ o \ w \ e \ r \ \propto \ 0 \ .7 \cdot C \cdot 0 \ .7^{\ 2} \cdot V_{DD}^{\ 2} \cdot \frac{1}{0 \ .7} \cdot f = 0 \ .49 \cdot C \cdot V_{DD}^{\ 2} \cdot f$$

(2)

**Figure 3.** Maximum thermal power dissipation for various Intel processors.

Figure 3 shows the maximum thermal power dissipation for various Intel processors. Different markers represent different processors. As seen from the figure, the rate of increase in power consumption (in logarithmic scale) dropped after constant electric field scaling was applied. Also seen from the figure is the trend that processors ported to new technologies after 0.8µ show a reduction in maximum power consumption.

Even though the logarithmic rate of increase in power consumption decreased after constant electric field scaling, power consumption increase is still an alarming issue for designers. As the transistor count, design complexity, and operating frequency increase, power consumption continues to increase dramatically, which adversely affects reliability, cooling costs, and - especially for portable systems - battery life [17].

Even though reduced power supply voltages decreased dynamic power consumption per transistor, the trend of reducing power supply voltage led to a

significant increase in the leakage power consumption because of the necessity to reduce threshold voltages in order to compensate the drive loss caused by the reduced supply voltage. As a common practice, threshold voltage for a process is usually chosen to be smaller than one quarter of the supply voltage value to ensure that performance does not suffer excessively [18]. This approach, combined with the exponential relationship of leakage current to threshold voltage, led to a significant increase in the percentage of leakage power consumption in total system power consumption. Figure 4 shows this trend. If this trend continues, the leakage power consumption will be equal to the dynamic power consumption in a couple of technology generations. Since the leakage energy is in a sense "wasted" energy, half of the energy dissipation will be waste in the future technologies if significant improvements in device, circuit, architecture, and software are not introduced.

**Figure 4.** The change in active (dynamic) and leakage power consumptions for the past Intel processors.

Reducing leakage and dynamic power consumption constitute one of the biggest design challenges for chip makers today. Therefore, great emphasis is given to low power research both in academia and in industry.

#### 2.2 Effects of Scaling on Soft Error Rates in Microprocessors

Soft errors (SEs) are becoming an increasing concern in electronic devices as the operating voltages and device sizes decrease. A reduction in circuit dimensions reduces the capacitance of the circuit nodes, thereby leading to an increase in the voltage magnitude of the glitches caused by a noise source such as α-particles or cosmic rays [11]. It also increases the susceptibility of circuits to hard-to-verify design/layout errors such as those that result from increased crosstalk and increased susceptibility to power supply and ground bounce. Low noise margins resulting from reduced operating voltages further aggravate the problem by allowing even small glitches to propagate.

The main contribution to the soft error rate (SER) comes from the memory cells and sequential circuits in current microprocessors. A soft error in these circuits may result in a bit flip in the saved state, which may lead to wrong execution. The SER for memories decreased dramatically after the introduction of error-correcting codes (ECC) [12][19].

The error rate in sequential circuits remains the same, while the error rate in combinational circuits increases linearly with increasing operating frequencies [20]. It is shown in [12] that this trend will lead to comparable SERs in combinational and sequential circuits for the 70 nm technology generation, as seen in Figure 5, where expected SERs are given for SRAM (without ECC), latches, and combinational logic. SER values are given for different pipeline stage delays (in terms of Fan-out four inverter

delay) for combinational logic and latches. A single SER curve is given for SRAM because the change in SER for SRAM is negligible for changing pipeline stage delay. The FIT term in Figure 5 denotes *failures in time*. An FIT of 1 means a failure is observed every 10<sup>9</sup> hours. The chip that is used to get the data for Figure 5 is the Alpha 21264 microprocessor. It has 15.2 million transistors on the die in 350 nm technology. Number of transistors is assumed to be doubling in every new technology generation. Combinational logic occupies 20% of the die area. The rest is occupied by memory and sequential elements. For systems in which ECC is employed for memories, the SER of combinational logic might start dominating the chip SER sooner than 70 nm technology.

Figure 5. SER/chip for SRAM/latches/logic [12].

#### **CHAPTER 3**

#### **MODELING CMOS GATES**

This chapter focuses on basic characteristics of CMOS gates. Certain parameters of CMOS gates such as propagation delay, dynamic energy consumption, static energy consumption, and input capacitance are needed to be modeled with respect to design variables so that the effects of the optimizations can be validated by simulations. Design variables for a single gate are size, output capacitance, input signal ramp, supply voltage, and threshold voltage.

#### 3.1 Operation of a CMOS Gate

To understand the basic operation of a CMOS gate, let's examine the simplest CMOS gate, the inverter. An inverter, which consists of a PMOS and an NMOS transistor, generates the logical inverse of the input signal at its output. Figure 6 shows the circuit for CMOS inverter.

Figure 6. CMOS Inverter circuit.

The circuit operates as follows: When the input is high, the PMOS transistor is turned off and the NMOS transistor is turned on. If the output voltage is already low, circuit remains as it is. If the output voltage is greater than zero (i.e. output capacitance has charge), the charge in the output capacitance is drained to the ground through the NMOS transistor. The speed of the discharge depends on the resistance of the NMOS transistor and the initial total charge on the output capacitance. When the input is low, the opposite happens and the output capacitance is charged through the PMOS transistor. At the high level, if the delay of the gate is taken as the average of charging and discharging times, it is seen that the delay of a gate depends on the size of the transistors (influences the resistance on which the charging/discharging happens and contributes to the output capacitance), output capacitance (influences the amount of charge to charged/discharged), threshold voltages of the transistors (influences the resistance of the transistors), and supply voltage applied to the gate (influences the resistance of the transistors and determines the amount of charge the output capacitance holds). As a first order approximation, if we model the transistors as resistances, delay of a gate can be written as  $K \cdot \tau$  where K is a constant and  $\tau$  is the time constant of the RC network, which is given as follows:

$$\tau = R \cdot C = \frac{V_{DD}}{k \cdot \left(\frac{W}{L}\right) \cdot \left(V_{DD} - V_{Th}\right)^{\alpha}} \cdot C \tag{3}$$

where k is a process dependent constant,  $V_{DD}$  is the supply voltage value,  $V_{Th}$  is the threshold voltage value, W/L is the aspect ratio of the transistors, and  $\alpha$  is the velocity saturation coefficient [21]. C is the total output capacitance including both the load capacitance and the parasitic capacitance of the gate. It is observed that the ramp of the

input signal also affects the delay of the gate. If a slowly changing signal is applied to the gate, the output changes slowly as well.

As in the case for delay, energy consumption of a gate also is influenced by the supply and threshold voltage values, output capacitance, transistor sizes, and input signal ramp. Two types of energy dissipation is observed during the operation of a CMOS gate. These are dynamic energy consumption and static energy consumption. Dynamic energy consumption is the energy consumed during transition of the input and output nodes. Main portion of the dynamic energy consumed is because of the charging/discharging of the capacitances. In the case of an inverter, the output capacitance is charged to hold  $C \cdot V$  amount of charge when the input is at low voltage. When the input switches to high voltage, this charge is drained to the ground through the NMOS transistor and this leads to a total energy loss of  $C \cdot V^2$  for a charge-discharge cycle. Half of this energy is dissipated during charging of the capacitor on the PMOS transistor, the other half is stored in the capacitor. When the capacitor is discharging, the stored half is dissipated on the NMOS transistor. In addition to the charging/discharging energy dissipation, there is also short-circuit energy dissipation, which is regarded as a part of the dynamic energy dissipation since it is observed when the input to the gate is switching. A short circuit current flows from the supply voltage to the ground during input switching when both the transistors are on. Short circuit energy consumption (E<sub>sc</sub>) is about 10% of the dynamic energy consumption [18][22]. For high  $V_{Th}$  circuits ( $V_{Th} > \frac{1}{4} V_{DD}$ ),  $E_{sc}$  is negligible [22]. Equation 4 shows the dynamic energy consumption for a CMOS gate:

$$E_{dynamic} = 0.5 \cdot C \cdot V_{DD}^{2} \cdot S + E_{sc}$$

(4)

where C is the total capacitance,  $V_{DD}$  is the supply voltage value, and S is the total number of switching observed at the gate's output during the time period of interest.

Static energy consumption is the energy loss in the gate when the gate is not operational. It is composed of three components, as seen in Figure 7: subthreshold leakage, drain junction leakage, and gate leakage. Subthreshold leakage is the dominant factor for today's technologies. Equation 5 gives the equation for energy dissipation resulting from subthreshold leakage:

$$E_{sub-vth} = V_{DD} \cdot I_{S} \cdot e^{\frac{V_{GS}-V_{Th}}{n\cdot v_{T}}} \cdot \left(1 - e^{\frac{V_{DS}}{v_{T}}}\right) \cdot T$$

(5)

where  $I_S$  is a circuit and process dependent constant, n is the subthreshold swing coefficient,  $v_T$  is the thermal voltage  $(k \cdot T/q)$ ,  $V_{Th}$  is the threshold voltage,  $V_{DD}$  is the supply voltage, and T is the duration of idleness. Subthreshold leakage is likely to increase in the future because of the exponential relationship of subthreshold current to threshold voltage. Subthreshold current increases about 10 times for every 0.1V reduction in threshold voltage.

**Figure 7.** The Components of static energy dissipation.

Gate oxide leakage is becoming a significant contributor to the total static energy consumption because of supply voltages being scaled less than the amount necessary for maintaining a constant electric field across the gates of the transistors. Supply voltage scales down by only 15% per generation (not 30% as dictated by constant field scaling predictions) in order to sustain high transistor performance [23]. This leads to an increase in the electric field across the gate dielectric per technology generation [24], leading to an increase in the gate oxide leakage. As the physical gate oxide thickness approaches sub 10 Angstroms, gate oxide leakage becomes larger than 100A/cm² because of direct band-to-band tunneling. Gate oxide leakage increases weakly with temperature, but it increases exponentially with an increase in supply voltage at a rate of two times larger leakage for every 100 mV increase in supply voltage. Since the supply voltage is not scaled down as much as the feature sizes, as gate oxide thickness decreases, gate oxide leakage becomes more important. New high-K dielectrics as gate dielectric material are needed to reduce gate oxide leakage energy.

#### 3.2 SPICE Modeling of CMOS Gates

In order to optimize circuits for power consumption and soft error tolerance, the ability to simulate circuits fast and accurately is needed. Since the techniques used in the optimizations modify one or more of the design parameters ( $V_{DD}$ ,  $V_{Th}$ , size, output capacitance) for the gates in the circuit, the effects of these modifications to the overall circuit delay and energy consumption should be considered during the optimizations. The fastest way is to use equations similar to the ones given in Section 3.1 [25]-[27]. Even though this will result in faster simulation of the circuit, the results will not be accurate enough. The main reason for the inaccuracy is the lack of compact analytical models that

include input signal ramp as a variable. Even when the input signal ramp is considered as a variable [21][28], these models mostly fall short of modeling the output signal ramp in a way that can be used to make calculations for a logic network. Also, the models in the literature are mostly generated for single supply voltage circuits. Therefore, they lose accuracy when a gate is driven by a voltage source that is different from the supply voltage of that gate. As the analytical models are made more accurate, the models become more complex and the advantage of using them diminishes.

Using SPICE simulations will give the best accuracy for approximating delay and energy consumption of the circuit. However, simulating complete circuits consisting of hundreds of gates with SPICE will be very time consuming. It is impossible to use SPICE simulations in an iterative kind of optimization because of the long simulation times.

To get both accuracy and speed, circuit simulations are done using SPICE look-up tables for individual gates. Gates are simulated using SPICE for various values of supply voltage, threshold voltage, gate size, input signal ramp, output capacitance, and input signal magnitudes. For gates with multiple inputs, only one input is changed and the others are applied the sensitizing logic values during simulations. The following parameters are extracted from SPICE simulations:

- Propagation delay: It is calculated to be the average of propagation delays for rising and falling outputs.

- Dynamic energy: The energy dissipated during output is rising and falling is calculated by multiplying the supply voltage value by the total charge drawn from the supply during rising output and falling output. These values are denoted by  $E^{01}$  and  $E^{10}$ , respectively.

- Static power: The power consumed when the gate's output is stable at logic one and logic zero is calculated by multiplying the supply voltage value by the stable current value. These values are denoted by P<sup>1</sup> and P<sup>0</sup>, respectively.

- Input capacitance: The input capacitance  $(C_{in})$  of a gate was measured by applying a voltage pulse of amplitude V with rise and fall time T to the gate and measuring the average current flowing into  $(I_{in})$  or out of  $(I_{out})$  the gate.  $C_{in}$  is then taken as the average of  $\frac{I_{in} \cdot T}{V}$  and  $\frac{I_{out} \cdot T}{V}$ .

- Output ramp: Output ramp is taken to be the average of the slopes of rising and falling output signals.

Average energy dissipation of a gate per clock cycle is calculated by the following equation:

$$E = T_{clock} \cdot \left( prob^{0} \cdot P^{0} + prob^{1} \cdot P^{1} \right) + Activity \cdot \left( \frac{E^{01} + E^{10}}{2} \right)$$

(6)

where  $prob^0$  and  $prob^1$  are the static probabilities of the output of the gate being 0 and 1 respectively and Activity is the switching activity at the gate output.

Modeling domino logic gates is slightly different from the static CMOS gates. The difference comes from the fact that domino logic belongs to dynamic logic family. A domino logic gate has two phases of operation. In the precharge phase, the output node of the gate is charged to logic one. In the evaluate phase, the output node either remains at high voltage value or it is discharged to zero depending on the inputs. Because of this precharge-evaluate style of operation, the calculation of energy consumption and delay differs for domino logic gates compared to static logic gates, as follows:

- Delay: In the evaluate phase, the output of a domino gate either remains high, or it is discharged to zero through the NMOS network. The delay of a domino gate is the propagation delay when the output is falling. Instead of input signal ramps (as in the case of static CMOS gates), the driving strength of the predecessor is used to index the look-up tables. As will be explained in Section 4.2.1, two different structures of gates having different driving strengths are considered in optimizations.

- Energy consumption: Because every evaluate phase is followed by a precharge phase, the output node either does a one to zero transition followed by a zero to one transition (if the inputs are such that the output evaluates to zero) or no transition at all (if the inputs are such that the output evaluates to one). Therefore, two values are extracted from the SPICE simulations to calculate the energy consumption (dynamic + static) of the gate. These are E<sup>010</sup> and E<sup>00</sup>, where the superscript numbers represent the transitions observed at the output node. Average energy consumption of a domino gate per clock cycle is then calculated by the following equation:

$$\overline{E} = prob^{0} \cdot E^{00} + prob^{1} \cdot E^{010}$$

(7)

where  $prob^0$  and  $prob^1$  are the static probabilities of the output of the gate being evaluated to 0 and 1 respectively.

The SPICE loop-up tables are used during the circuit optimization to find the circuits' energy consumption and delay. Gates in a circuit are represented as nodes in a directed acyclic graph (DAG) and the wires are represented as edges. The DAG is then topologically sorted such that in the topologically sorted list L, for any gate  $G_i$ , all the

nodes that are driven by  $G_i$  are located after  $G_i$  in the list. As the list is traversed in order, topologically sorted list structure guarantees that when a node is visited, all of its predecessors are visited. This simplifies the delay calculation for the circuit. Topological sorting is explained in Appendix A.

#### 3.2.1 Calculating the Delay of a Circuit

Delay of the circuit is calculated using static timing analysis (STA) [29][30][31]. To simplify the analysis, two dummy nodes are inserted to the graph, a dummy primary input node that is driving all the real primary inputs and a dummy primary output node that has all the primary outputs as inputs. Both of these nodes have zero delay. To perform STA, some parameters are defined for each node [32].

*Early start time:* The early start time for a node is based on the logical requirement that a node can begin only when all its predecessors have been completed.

*Early Start Time = Latest(Finish Time* for all predecessors)

When all predecessors are assumed to finish as early as possible then:

*Early Start Time = Latest(Early Finish Time* for all predecessors)

*Early Start Time* = *Max*(*Early Finish Time* for all predecessors)

Early finish time: The early finish time is the early start time plus the delay for the node.

<u>Latest finish time</u>: The latest finish time for a node is based on the logical requirement that a node must end before any of its successors may be begin.

*Latest Finish Time = Earliest(Start Time* for all successors)

When all successors are assumed to start as late as possible then:

*Latest Finish Time = Earliest(Latest Start Time* for all successors)

*Latest Finish Time* = *Min(Latest Start Time* for all successors)

<u>Latest start time</u>: The latest start time is simply the latest finish time less the delay for the node.

<u>Slack:</u> The slack time is the difference between late and early start times.

#### STA is performed as follows:

- Circuit is topologically sorted from primary inputs to primary outputs.

- Nodes are visited one by one starting from the dummy primary input node. This node has an early start time and early finish time of zero. For all the other nodes, early start time is calculated to be the maximum of early finish times of its predecessor. Early finish time is simply the early start time plus the delay for that node. When delay for that node is calculated, the output signal ramp of the node with the maximum early finish time is used as the input signal ramp for the node.

- When all the nodes are visited, the early finish time of the dummy primary output is equal to the circuit's delay.

- To find the slacks of all the nodes, nodes are visited in the reverse order, starting from the dummy primary output node.

- The latest start and latest finish times of the dummy primary output node are assigned to be equal to the circuit delay.

- For the rest of the nodes, latest finish time is calculated to be the minimum of latest start times of its successors. Latest start time is simply the latest finish time minus the delay for that node. Slack is the difference between late and early start times.

#### 3.2.2 Calculating the Energy Consumption of a Circuit

Energy consumption of the circuit is obtained by adding the individual energy consumption values of all the gates using equations 6 and 7. The static probabilities and switching activities of the internal nodes are obtained for specific values of input switching activities and static probabilities using Synopsys Design Analyzer tool. Dynamic energy and static power values are obtained from the SPICE look-up tables. Only the energy spent to charge and discharge the output capacitance of the node is considered when the energy consumption is calculated for that node. The charging and discharging of the node's input is automatically taken care of when the energy consumption of its predecessor is calculated since the input capacitances of the nodes serve as output capacitances to their predecessors.

Static power consumption of a gate rather than the static energy consumption is found using SPICE. Then, depending on the circuit that this gate is used in, this value is multiplied by the clock period to obtain the static energy consumption for the gate in a clock cycle. The static power for a gate obtained by SPICE simulations is a single value, which incorporates all types of static power that is consumed in the gate, including subthreshold power and gate leakage power.

#### **CHAPTER 4**

#### LOW POWER DUAL SUPPLY VOLTAGE CMOS DESIGN

Power consumption increase in digital systems is one of the main bottlenecks for chip designers. Improvement to power consumption of digital systems in every level of design is needed to combat this problem. Even though software and architectural level techniques have the most dramatic effect on power consumption reduction for a specific system in consideration, circuit level techniques are very important since they provide general methods which can be applied to a spectrum of different architectures and systems. Multiple supply voltage usage and multiple threshold voltage usage in dynamic circuits are effective methods to reduce dynamic and static power consumption. These methods are general methods which can be applied to various kinds of digital systems. However, there are practical limitations for these methods especially for the usage of multiple supply voltages. In CMOS circuits, for example, the need for additional level shifting circuitry when a high voltage gate is driven by a low voltage gate is one of the most important limitations. Domino logic, however, does not require level shifting due to the lack of the PMOS tree in the domino gates. Unfortunately, the necessity to generate and route the additional supply voltages remains.

A key goal of this part of the research is to provide techniques to deal with the practical limitations of multiple supply voltage usage such as overhead of level shifters. The issues addressed in this chapter are as follows:

- Developing circuit design techniques for domino logic circuits to exploit the benefits of dual supply voltage usage without the need for a second supply voltage, to obtain pseudo dual supply voltage operation.

- Developing methods to overcome the limitations caused by the necessity of level shifter usage in CMOS circuits to increase dynamic energy consumption reduction by dual supply voltage usage.

### 4.1 Review of Power Reduction Techniques

### **4.1.1** Dynamic Power Reduction Techniques

Equation 4 in Section 3.1 gives the formula for dynamic energy consumption. As seen from the equation, dynamic energy consumption of a circuit can be reduced by decreasing switched capacitance ( $C \times S$ ) or decreasing supply voltage ( $V_{DD}$ ).

## **4.1.1.1** Decreasing Switched Capacitance

The most obvious method for dynamic power reduction is to eliminate unnecessary switching activity in the circuit. Clock gating is the most commonly used technique for this purpose. By gating the clock to specific flip-flops, the activity in unused modules is eliminated. Clock gating can be applied in both fine grain and coarse grain. Some commercial tools [33][34] can automatically apply fine grain clock gating to the design where the tool finds some predetermined constructs in the system description (verilog HDL or VHDL description), but coarse grain application of clock gating needs the input from the designer. Clock gating is a circuit-level technique and it is usually applied close to the end of the design process, so the benefits obtainable by this method are limited. Techniques applied at higher levels of abstraction such as architectural changes and/or

algorithmic changes have more potential to decrease the unnecessary switching in the circuit. Therefore, power consumption reduction must be an important goal for the designers in every level of the design.

#### **4.1.1.2** Decreasing Supply Voltage

Supply voltage is the most influential parameter for power reduction because of the quadratic relationship of power consumption to the supply voltage. This relationship is exploited by the designers in many ways. Dynamic supply voltage scaling and multiple supply voltage usage are the most popular methods targeting the  $V_{DD}^2$  term in Equation 4.

If a circuit has delay constraints varying in time, dynamic voltage and frequency scaling is used to put the circuit in a high delay/low power mode when the constraint is relaxed and in a high power/low delay mode when the constraint is tight. There may be several other intermediate modes between these two ends. Today, most of the portable processors come with this capability such as Intel's XScale [35], AMD's K6-IIIE [36], and Transmeta's Crusoe [37]. In most of the current processors with dynamic voltage/frequency scaling, the control is done by the operating system, running software, or the users themselves. Thermal conditions of the processor or the remaining battery level can also force a change in the mode of operation. Once the control signal is generated to change the operating voltage, the voltage source is given the necessary inputs to change the voltage and the PLLs are reprogrammed to the predetermined frequency values for that operating voltage. An overhead in terms of power consumption and delay is involved with every mode change of the processor. As an example, AMD's PowerNow technology takes 200 µsec for stabilizing supply voltage and PLL frequency [36]. Apart from software-controlled voltage scaling, there are preliminary studies for hardware controlled dynamic voltage scaling as well. RAZOR system [38] tunes the supply voltage by monitoring the error rate during circuit operation, thereby eliminating the need for voltage margins and exploiting the data dependence of the circuit delay. The feedback loop is controlled by the number of errors resulting from timing violations caused by the slowdown in the circuit. When the error rate is above a predetermined threshold, the operating voltage is increased and the voltage is reduced if the error rate is below the threshold. Up to 64.2% energy savings for a full custom multiplier and a SPICE-level Kogge-Stone adder was achieved with a 3% delay overhead.

Static multiple voltage assignment is also used to reduce power consumption. Given a timing constraint, some parts of the hardware are assigned to run with the regular supply voltage, while other parts are assigned to run with a lower supply voltage, reducing power consumption. The granularity of voltage assignment and the method for assigning the voltages vary in the literature. But all of them assign lower supply voltage to the portions of the circuit with enough slack as a gate's delay increases with decreasing supply voltage, as seen from Equation 3.

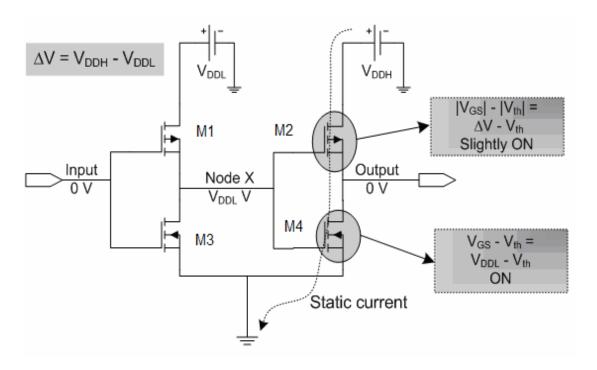

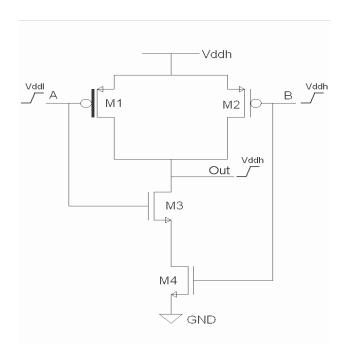

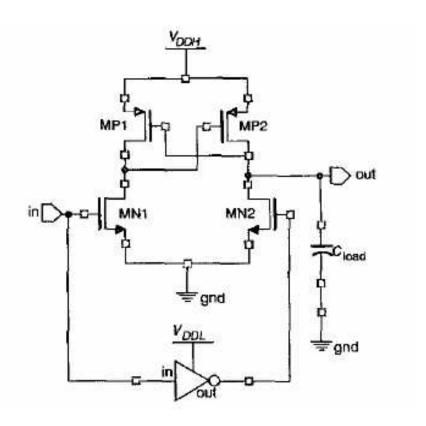

There are some important issues to deal with if dual/multiple supply voltages are to be used in a circuit. Gate-level dual supply voltage usage in CMOS circuits may suffer from excessive leakage power if low voltage gates directly drive high voltage gates. In these situations, the PMOS transistor in the high voltage gate is not turned off completely with the low voltage "logic high" input signal. This leads to the use of level shifters wherever low voltage gates drive high voltage gates. To reduce or eliminate the delay, area, and energy overhead of the level shifters, clustered voltage scaling (CVS) [39][40] and Module Level Voltage Scaling (MLVS) [6][41] were proposed. In CVS, low voltage

clusters are constructed in the circuit in such a way that there is no low voltage gate driving a high voltage gate and level shifting is only done in sequential elements. This is done by assigning low supply voltage to the gates starting from the circuit outputs depending on their slacks. MLVS assigns the dual supply voltages to relatively large partitions of the circuit. This reduces the number of level shifters needed. Both methods limit the obtainable power savings by introducing constraints to the low voltage assignment process.

There has also been research in the use of gate-level dual supply voltages where level shifters are being used whenever a low voltage gate drives a high voltage gate [42]-[44]. In [42] and [43], graph-theoretic algorithms are employed to apply dual supply voltages at the gate level while keeping the delay constant. The technique in [44] is an extension to CVS, where level shifters are not restricted to be only in sequential elements. The energy consumption overhead of the level shifters is found to be 8% in [44]. The high cost of level shifters in terms of delay and energy consumption reduces the achievable energy consumption reductions by these techniques.

#### **4.1.2** Static Power Reduction Techniques

Static power consumption per gate can be reduced by increasing the threshold voltage  $(V_{Th})$  of the transistors or by using transistor stacks in the pull-down and/or pull-up networks.

### **4.1.2.1 Increasing Threshold Voltage**

Because of the exponential relationship of static power consumption to the threshold voltage, increasing the threshold voltage is an effective way of decreasing the static power consumption. Dynamic threshold voltage adjustment and static assignment of multiple threshold voltages are methods used to decrease static power consumption.

Similar to dynamic supply voltage scaling, dynamic threshold voltage adjustment can be used for systems with performance requirements varying in time. Delay of the circuit increases and static energy consumption decreases as the threshold voltage value is increased, as seen in Equations 3 and 5. Reverse body bias (RBB) can be applied to the transistors to increase their threshold voltages when the system is idle or performance requirements are reduced [24][45]. In the sub-100nm technology generation, approximately a 2-3X reduction in leakage is achievable by the RBB technique [24]. However, effectiveness of RBB decreases as channel lengths become smaller or V<sub>Th</sub> values are lowered. The V<sub>Th</sub> modulation capability of RBB weakens as short-channel effects become worse or body effect diminishes because of lower channel doping [24].

A dynamic threshold voltage adjustment scheme for SRAMs is given in [46]. Using the temporal and spatial locality of cache access, the threshold voltages of active lines are lowered to meet performance requirements, while the threshold voltages of the inactive cache lines are increased by controlling the back bias, reducing static energy consumption. If a line is not accessed for a predetermined time (30-100 μsec), the threshold voltage for that line is increased. The threshold voltage is decreased back after that line is accessed. For an area overhead of 15% and a performance overhead of 1%, static power dissipation is reduced by 72% in an SRAM of size 64 KB.

Static assignment of multiple threshold voltages can save up to 80% [47] of the static power dissipation in CMOS circuits without decreasing the performance of the circuit. Low threshold voltages are assigned to the gates on the critical paths to keep the

delay unchanged, while high threshold voltages are assigned to the gates on the off-critical paths to reduce the static power dissipation. The optimum high threshold voltage is different for different circuits but is usually more than 100 mV higher than the low threshold voltage value, leading to a >10X decrease in static power consumption in the high threshold gates. Multiple threshold voltage implementation is relatively easy compared to multiple supply voltage implementations. An additional mask is added to the fabrication process to achieve a second threshold voltage. Layouts of the gates need not be changed, which simplifies the design process.

## **4.1.2.2** Using Transistor Stacks

The leakage of a two-transistor stack is an order of magnitude less than the leakage in a single transistor [48]. Therefore, the static current through a gate depends on the inputs to that gate. This makes the total leakage current of a circuit dependent on the states of the primary inputs [49]. The optimal input vector for a circuit for minimum static power dissipation may be determined and applied to the circuit when the circuit is idle to decrease the static power dissipation.

An additional transistor may also be used to force the stacking effect when the circuit is in standby mode. For the gates with high subthreshold leakage in non-critical paths, a leakage control transistor can be inserted in series and can be turned off during the standby mode [49]. This technique can effectively reduce the leakage current using single threshold voltage.

## 4.2 Level-Shifter Free Design of Dual Supply Digital Circuits

#### 4.2.1 Pseudo Dual Supply Voltage Domino Logic Design

Domino logic is used extensively in high-speed circuit design. The main reason for the higher performance of domino logic compared to static CMOS is the reduced input capacitance seen by driver gates in domino logic. In CMOS, both PMOS and NMOS transistors are driven at the input stage whereas in domino logic, only NMOS transistors are driven. The higher performance of domino logic comes at the expense of a higher power consumption. The switching activity in domino circuits is, on the average, double that in CMOS circuits. Higher switching activity together with the clock power dissipation leads to a higher power consumption in domino gates compared to CMOS gates.

Due to the lack of PMOS network, gate-level multiple supply voltage assignment can be done to domino circuits without the need for level shifters [50][51]. However, the overhead of generating and routing an additional power supply voltage remains. Shieh et. al. [50] use dual supply voltages, gate sizing, and a contention-alleviated static keeper (CASK) to reduce power consumption in domino circuits while keeping the delay fixed. This approach needs two separate supply voltages for the gates and a bias voltage for the CASK circuitry, which is used to speed up V<sub>DDL</sub> to V<sub>DDH</sub> interfaces. Jung et. al. [51] use dual supply voltages and dual threshold voltages together with a low voltage swing clock in order to reduce power consumption of domino circuits. A separate back-biasing voltage is also used to turn off the pull-up PMOS completely when low voltage swing clock is applied to a gate with high supply voltage. Both these approaches suffer from the complexity of generating and routing additional voltages therefore it is not feasible to

implement these approaches to a circuit which is fabricated without a second supply voltage.

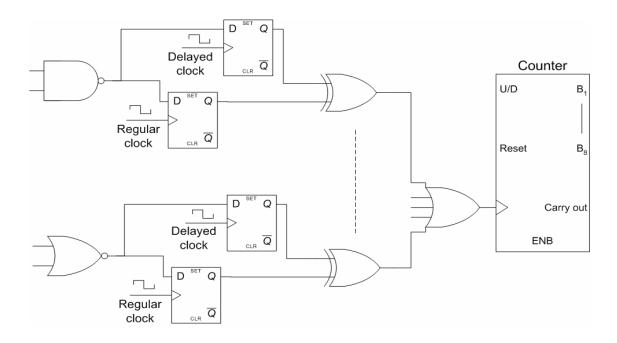

Figure 8. Domino Logic 3-input AND gate

(a) PPD (PMOS pull-up Domino), (b) NPD1 (NMOS Pull-up Domino with extra NMOS between source of PMOS in inverter and power supply), (c) NPD2 (NMOS Pull-up Domino with high |Vth| PMOS in the inverter).

A pseudo dual supply voltage assignment scheme without the need for an additional power supply to lower the power consumption of combinational domino logic blocks while maintaining the performance is developed [52][53]. The basic idea is to replace the standard domino gates [referred to as PPD (PMOS Pull-up Domino) gates from now on] on the off-critical paths by low-power (but higher delay) domino gates. The low-power domino gates use a novel technique to effectively operate at a lower supply voltage. The PMOS pull-up transistor in Figure 8a is replaced by an NMOS transistor (Figures 8b and 8c), which leads to a reduced voltage swing at the input of the output inverter. This node (Node X in Figure 8) has a high capacitance in domino logic gates to eliminate problems resulting from charge sharing. So, reducing the voltage applied to this node reduces the energy consumption when that node is charged and discharged. If the energy consumed for one charging-discharging of the node capacitance at Node X is assumed to be  $K \cdot V_{DD}^2$  for a regular domino gate, it is  $K \cdot V_{DD} \cdot V_{swing}$  for an NMOS Pull-up domino gate, where  $V_{swing}$  is  $V_{DD} - V_{Thn} - \Delta V_{Thn} < V_{DD}$  because of the limitation of the NMOS transistor when passing a "high" voltage. The  $\Delta V_{Thn}$  term is the threshold voltage modification seen on the NMOS pull-up transistor due to the body-bias effect. Note that an inverted clock signal is applied as the precharge signal to the NMOS pull-up transistor in NPD gates.

However, reducing the voltage at the input of the CMOS inverter in the domino gate leads to high static current in the inverter due to the non-zero voltage between PMOS gate and source when the inverter input is high. Two ways to reduce this static current are developed. One way is to use an always on NMOS, whose gate is tied to power supply, between power supply and the source of the PMOS in the inverter. This

brings the source voltage of the PMOS in the inverter down because of the NMOS pass transistor, making the PMOS gate to source voltage close to zero. This type of NMOS Pull-up Domino gates will be referred to as NPD1 from now on. The second way is using a high threshold PMOS in the inverter. This way, the current flow through the PMOS transistor when its gate to source voltage is not zero is reduced, reducing the static current flow when input of the inverter is high. This type of NMOS Pull-up Domino gates will be referred to as NPD2 from now on. Both NPD1 and NPD2 types of gates have lower energy consumption but higher delay compared to PPD type gates.

## **4.2.1.1** Design Strategy with NPD1 Type Gates

The primary design parameter is the size of the diode connected NMOS transistor when NPD1 type domino gates are used in a circuit. Figures 9, 10 and 11 show the SPICE simulation results of the variation of the delays and energy consumption values respectively for a 3 fan-in, 1 fan-out AND NPD1 gate with different values of NMOS transistor width and with different drivers (NPD1 and PPD). The delay and energy of the corresponding PPD gate are also shown. As seen from the plots, increased size improves both the energy consumption and delay of an NPD1 gate. The price is the increased area. Also seen from the plots is the effect of the driving gate on the delay and energy consumption characteristics of the driven gate. A gate operates faster if it is driven by a PPD gate because a PPD gate provides a higher voltage value at its output which reduces the resistive effects of the NMOS transistors in the driven gate compared to the NMOS transistor driven by an NPD1 gate. The output of an NPD1 gate swings from zero to  $V_{DD} - V_{Thn} - \Delta V_{Thn}$  leading to reduced driving strength. The simulations are done using Level 49 SPICE models for 0.18 $\mu$  technology generation [54] using HSPICE.

**Figure 9.** Variation of propagation delay for NPD1 AND gate with width of extra NMOS transistor.

**Figure 10.** Variation of E<sup>010</sup> for NPD1 AND gate with width of extra NMOS transistor.

**Figure 11.** Variation of  $E^{00}$  for NPD1 AND gate with width of extra NMOS transistor.

## **4.2.1.2 Design Strategy with NPD2 Type Gates**

The primary design parameter is the threshold voltage value to be used in the inverter PMOS when NPD2 type domino gates are used in a circuit. If the magnitude of  $V_{thp}$  is small, the leakage current is large and if the magnitude of  $V_{thp}$  is large, gate delay becomes large. Figures 12, 13, and 14 show SPICE simulation results of the variation of delay and energy consumption values respectively for a 3 input AND NPD2 gate with different values of threshold voltage of inverter PMOS transistor and with different drivers (NPD2 and PPD). The simulations are done using Level 49 SPICE models for 0.18 $\mu$  technology generation [54] using HSPICE. The delay and energy consumption of the corresponding PPD gate are also shown. The supply voltage is 1.8V and the load capacitance is 3fF for all the cases. The regular threshold voltage value is 0.4 V. The

trends seen in the plots are similar for the other gate types and loads, but the intersection points of the curves vary. Note that for  $V_{thp}$  values of ~0.6V to ~0.75V, the NPD2 AND3 gate is both faster and lower energy than the PPD AND3 for a load of 3fF. This threshold voltage range for which an NPD gate is better than its PPD counterpart differs for different gate types and different loads (for example, delay of an NPD gate increases more rapidly with increasing load capacitance compared to a PPD gate). Therefore, replacing all the PPD gates in a circuit by NPD gates with a specific value of  $V_{thp}$  will not, in general, make the entire circuit both faster and lower energy. When choosing the second threshold voltage, the circuit should be considered as a whole. As it will be shown in the results, choice of the second threshold voltage significantly effects the achieved energy consumption reduction.

**Figure 12.** Variation of propagation delay for AND3 gates with threshold voltage of inverter PMOS transistor.

**Figure 13.** Variation of E<sup>010</sup> for AND3 gates with threshold voltage of inverter PMOS transistor.

**Figure 14.** Variation of E<sup>00</sup> for AND3 gates with threshold voltage of inverter PMOS transistor.

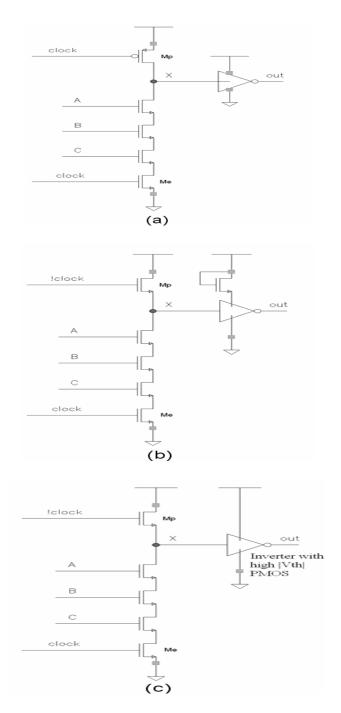

## 4.2.1.3 Algorithm for Power Optimization using NPD Gates

To reduce the energy consumption of domino logic circuits, PPD gates on the non-critical paths are replaced with slower, lower energy NPD gates. The total delay of the circuit remains the same as the original circuit which has only PPD gates. The algorithm explained in this section applies to both PPD-NPD1 and PPD-NPD2 replacement.

The circuit is represented as a directed acyclic graph (DAG), G(V,E). If the circuit has multiple primary inputs (PIs), a dummy PI vertex,  $PI_d$ , is created which fans-out to the original PIs. Underlying this is the assumption that all inputs arrive simultaneously. Similarly for POs, a dummy PO vertex,  $PO_d$ , is created which has fan-ins from the original POs. Each vertex 'v' of the DAG has associated with it the following information:

- 1. The logic function computed by the gate corresponding to the vertex.

- 2. Structure of the gate (NPD or PPD).

- 3. The current delay (v.delay), energy (v.energy), time slack (v.ts), early start time (v.es), early finish time (v.ef), latest start time (v.ls) and latest finish time (v.lf) of the vertex at any stage of the replacement process. The delay and energy consumption values for PPD and NPD gates of different fan-ins, fan-outs, gate types, and sizes when driven by a PPD gate or an NPD gate are obtained from SPICE simulations to form look-up tables. These look-up tables are used to obtain delay and energy consumption values of the gates. These values are updated for a gate whenever the gate or its driver gates change from type PPD to NPD. The dummy vertices have zero delay and energy consumption.

```

Algorithm PPD-NPD replacement

Inputs: Topologically sorted list of circuit vertices, V<sup>s</sup>;

Output: Circuit with off-critical path PPD gates replaced with NPD gates.

for as many times as number of vertices {

Let v be the vertex with maximum metric value.

Map v to be of structure NPD.

low energy←0

for every predecessor p of v {

Depending on whether p is mapped to PPD or NPD, look-up "pin energy" as the

energy for this gate when it is driven by p, using SPICE look-up tables and

switching activities.

low energy← low energy+pin energy

high delay←delay of v when it driven by the predecessor p with maximum early

finish time. Found using SPICE look-up tables.

low_energy←low_energy/(No. of predecessors p of v)

if((high_delay-v.delay)≤v.ts) { // Check if PPD-NPD replacement violated time

// slack of v.

flag \leftarrow 0

for every successor p of v {

Compute largest delay of p with v mapped to a NPD gate. Let this be

"p delay".

if((v.es+high_delay)≥p.es) { // Check if replacing v with its NPD equivalent

// violates time slack of any of its successors.

if((v.es+high\_delay+p\_delay)>p.lf) flag\leftarrow 1,break.

else if((p_delay-p.delay)>p.ts) flag\leftarrow 1,break.

if(flag=0) {

Map v to a NPD gate.

v.delay← high_delay

v.energy← low energy

v.metric←-2

Update Time Slacks(V<sup>s</sup>)

else v.metric←-1

Map v back to PPD

else v.metric←-1

Map v back to PPD

```

Figure 15. Algorithm for PPD-NPD replacement.

The algorithm for replacing PPD gates with NPD equivalent gates consists of two steps:

- 1. Initialization: In this step, the DAG is topologically sorted to get the sorted vertex list, V<sup>s</sup>. V<sup>s</sup> is used to compute the total circuit delay, T, of the baseline circuit in which each vertex is mapped to a PPD gate. In this step, the initial total energy of the baseline circuit with all PPD gates is also computed. Delay and energy consumption calculations are done as explained in Section 3.2.

- 2. PPD to NPD replacement: First, with each vertex mapped to a PPD gate, an energy metric for each vertex is computed. The metric is the energy saving obtainable if the vertex gate is changed from PPD to NPD. This metric is -1 for a vertex if either (i) the delay increase of the vertex due to the change is greater than the vertex's time slack or (ii) the delay increase of any of the driven gates (because of the reduction in drive strength) is greater than its time slack. In case all the delay increases are less than the corresponding time slacks, the change in energy of the driven gates is also included in the metric for the driver gate. The metric value might still be negative (if energy is increased due to change from PPD to NPD), but it will be greater than -1 and hence the vertex will have higher priority for changing from PPD to NPD over vertices which have metric -1.

Next, every vertex is visited in decreasing order of the energy metric, and it is attempted to replace the gate corresponding to the vertex with the NPD equivalent. This might not always be possible, even for a vertex with non-negative metric value, because the metric for the vertex was computed under the assumption that all other vertices are mapped to PPD gates and hence the vertex had a lot of slack. As the

replacement proceeds, the slack available to a vertex keeps on reducing and might not be sufficiently large to allow PPD-NPD replacement. After every replacement, the slacks for all gates are recomputed using the function Update\_Time\_Slacks(V<sup>s</sup>). The whole procedure is repeated till all vertices have been visited. Figure 15 gives the details of the algorithm used in this step.

After step 2 has been carried out, some PPD gates on off-critical paths have been replaced by NPD gates. This step does not change the total circuit delay since only those gates which have sufficient time-slack are replaced by NPD gates.

### 4.2.1.4 Results of PPD-NPD Replacement