## THE SYSTEM-ON-A-CHIP LOCK CACHE

A Thesis

Presented to

The Academic Faculty

by

Bilge Ebru Saglam Akgul

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology April 2004

# THE SYSTEM-ON-A-CHIP LOCK CACHE

Approved by:

Professor Vincent J. Mooney III, Committee Chair

Professor Douglas M. Blough

Professor James O. Hamblen

Professor John F. Dorsey

Professor Umakishore Ramachandran

Date Approved: 04/09/2004

$To\ my\ mother,\ Mihrican\ Saglam,$

and

my father, Mustafa Saglam,

for their love, support and selfless sacrifices.

## **ACKNOWLEDGMENTS**

I am grateful to everyone who made this Ph.D. thesis possible. First, I owe special thanks to my supervisor, Professor Vincent Mooney, for his patience and guidance from the very beginning until the end. Also, I would like thank everyone in the Hardware/Software Codesign Group at Georgia Tech for their important feedback. Finally, special thanks to my husband Tankut whose love and support enabled me to complete this work.

# TABLE OF CONTENTS

| DE  | EDIC                    | ATIO   | N                                     | iii  |

|-----|-------------------------|--------|---------------------------------------|------|

| AC  | CKN                     | OWLE   | DGMENTS                               | iv   |

| LIS | ST O                    | F TAE  | BLES                                  | viii |

| LIS | ST O                    | F FIG  | URES                                  | ix   |

| SU  | $\overline{\mathbf{M}}$ | ARY .  |                                       | xii  |

| Ι   | IN                      | TROI   | DUCTION                               | 1    |

|     | 1.1                     | Proble | em Statement                          | 1    |

|     | 1.2                     | Thesis | s Contributions                       | 3    |

|     | 1.3                     | Thesis | s Organization and Roadmap            | 5    |

| II  | $\mathbf{B}_{I}$        | ACKG   | ROUND AND PREVIOUS WORK               | 6    |

|     | 2.1                     | Lockin | ng Schemes                            | 6    |

|     |                         | 2.1.1  | Hardware Instructions for Locking     | 8    |

|     |                         | 2.1.2  | Traditional Spin-Lock                 | 10   |

|     | 2.2                     | Hardw  | ware Based Synchronization Mechanisms | 13   |

|     |                         | 2.2.1  | Cache Based Synchronization           | 13   |

|     |                         | 2.2.2  | Transactional Memory                  | 14   |

|     |                         | 2.2.3  | Speculative Lock Elision              | 15   |

|     |                         | 2.2.4  | Speculative Synchronization Unit      | 17   |

|     |                         | 2.2.5  | Speculative Lock Reordering           | 18   |

|     |                         | 2.2.6  | Summary of Hardware Based Mechanisms  | 18   |

|     | 2.3                     | Softwa | are Based Synchronization Mechanisms  | 19   |

|     |              | 2.3.1   | Spin on Read                                             | 19 |

|-----|--------------|---------|----------------------------------------------------------|----|

|     |              | 2.3.2   | Ticket Lock                                              | 20 |

|     |              | 2.3.3   | Anderson's Array Based Locks                             | 2  |

|     |              | 2.3.4   | Graunke and Thakkar's Locks                              | 22 |

|     |              | 2.3.5   | Queue Based Locks                                        | 22 |

|     |              | 2.3.6   | Reactive Synchronization                                 | 25 |

|     |              | 2.3.7   | Summary of Software Based Mechanisms                     | 25 |

|     | 2.4          | Perfor  | rmances of the Mechanisms                                | 26 |

|     |              | 2.4.1   | Benchmark Programs                                       | 26 |

|     |              | 2.4.2   | Performance Results                                      | 27 |

|     | 2.5          | Blocki  | ing versus Non-blocking Synchronization                  | 29 |

|     | 2.6          | Priorit | ty Inversion                                             | 30 |

|     | 2.7          | Summ    | nary                                                     | 3. |

| III | $\mathbf{B}$ | ASIC I  | LOCK CACHE DESIGN AND OPERATION                          | 33 |

|     | 3.1          | Metho   | odology                                                  | 33 |

|     | 3.2          | SoCLO   | C Hardware                                               | 37 |

|     |              | 3.2.1   | Control Logic                                            | 41 |

|     |              | 3.2.2   | Overview of SoCLC operation for Short CSes and Long CSes | 44 |

|     | 3.3          | Short   | Critical Sections                                        | 47 |

|     |              | 3.3.1   | SoCLC Hardware Mechanism for Short CSes                  | 49 |

|     |              | 3.3.2   | SoCLC Interrupt Mechanism for Short CSes                 | 50 |

|     | 3.4          | Long    | Critical Sections                                        | 57 |

|     | 3.5          | Summ    | nary                                                     | 64 |

| IV  | LC           | оск с   | CACHE PRIORITY INHERITANCE                               | 65 |

|     | 4.1          | The P   | Priority Inversion Problem                               | 65 |

|     | 4.2          | Solutio | on: Priority Inheritance                                 | 67 |

|     | 4.3          | Priorit | ty Inheritance in Hardware                               | 70 |

|              |                  | 4.3.1  | Atalanta RTOS Priority Inheritance vs. SoCLC Priority Inheritance | 70  |

|--------------|------------------|--------|-------------------------------------------------------------------|-----|

|              |                  | 4.3.2  | Priority Inheritance Hardware Architecture                        | 73  |

|              | 4.4              | Summ   | nary                                                              | 79  |

| $\mathbf{V}$ | $\mathbf{P}^{A}$ | ARLAI  | K LOCK CACHE SYNTHESIS                                            | 81  |

|              | 5.1              | Lock ( | Cache Generator                                                   | 82  |

|              |                  | 5.1.1  | PARLAK                                                            | 82  |

| VI           | ΕΣ               | KPERI  | IMENTAL RESULTS                                                   | 91  |

|              | 6.1              | Exper  | imental Platform                                                  | 91  |

|              | 6.2              | Basic  | Lock Cache Experimental Results                                   | 97  |

|              |                  | 6.2.1  | Microbenchmark                                                    | 97  |

|              |                  | 6.2.2  | False Sharing Experiment                                          | 99  |

|              |                  | 6.2.3  | Effect of Critical Section Length on Performance                  | 100 |

|              |                  | 6.2.4  | Effect of Memory Latency on Performance                           | 102 |

|              |                  | 6.2.5  | Database Example                                                  | 103 |

|              | 6.3              | Priori | ty Inheritance Experimental Results                               | 108 |

|              | 6.4              | PARL   | AK Lock Cache Synthesis Results                                   | 114 |

|              |                  | 6.4.1  | SoCLC Hardware Synthesis Results                                  | 114 |

|              |                  | 6.4.2  | SoCLC with Priority Inheritance Hardware Synthesis Results        | 117 |

| VI           | I C              | ONCL   | USION                                                             | 120 |

| RE           | FER              | ENCE   | ES                                                                | 124 |

# LIST OF TABLES

| Table 1  | Specifications of Seamless CVE's MPC755 PSP that we used in our experiments                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2  | Specifications of the L1 caches and the ARM9TDMI PSP that we used in our experiments                                                                      |

| Table 3  | Microbenchmark simulation results                                                                                                                         |

| Table 4  | False sharing effect on locking performance                                                                                                               |

| Table 5  | CS length effect on locking performance                                                                                                                   |

| Table 6  | SoCLC speedup over spin-lock and MCS locks for different CS lengths.102                                                                                   |

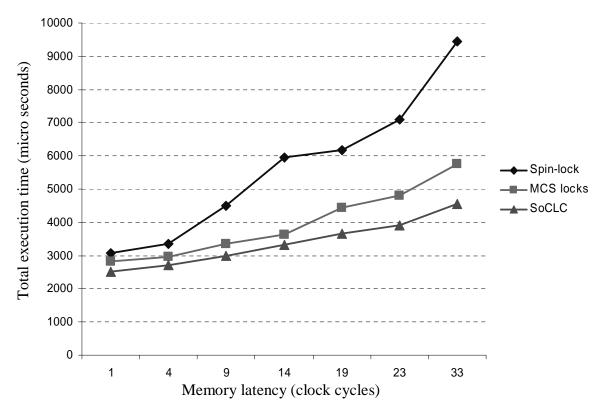

| Table 7  | Microbenchmark total execution times for different memory latencies and the corresponding SoCLC speedup over spin-lock and MCS locks.104                  |

| Table 8  | Database application simulation results                                                                                                                   |

| Table 9  | Simulation results of the robot application                                                                                                               |

| Table 10 | Task worst-case response times (WCRT) and actual completion times.113                                                                                     |

| Table 11 | SoCLC hardware with priority inheritance logic synthesis results. (Note that the area results include sum of memory-only area and non-memory logic area.) |

| Table 12 | SoCLC hardware with priority inheritance logic synthesis results with 10ns clock period                                                                   |

| Table 13 | An estimate hardware cost of an example SoC including SoCLC 119                                                                                           |

# LIST OF FIGURES

| Figure 1  | Shared data structures may cause contention in a shared-memory multiprocessor system                                                                                                                                | 2  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | MIPS assembly code for test-and-set functionality that is implemented using the LL/SC pair of instructions                                                                                                          | 10 |

| Figure 3  | Spin-lock algorithm using test-and-set instruction                                                                                                                                                                  | 11 |

| Figure 4  | MCS algorithm pseudo code.                                                                                                                                                                                          | 24 |

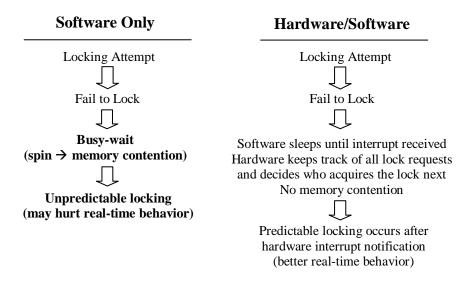

| Figure 5  | Software only solution vs. hardware and software solution                                                                                                                                                           | 36 |

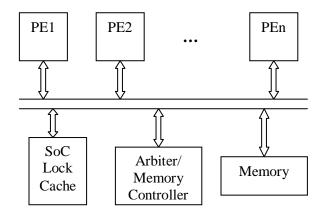

| Figure 6  | Hardware system architecture with SoC Lock Cache. (Note: Hardware not drawn to scale; e.g., PE1 is at least a factor of ten larger than the SoC Lock Cache.)                                                        | 38 |

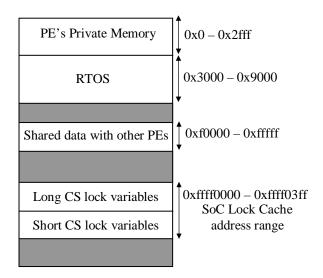

| Figure 7  | PE address space mapping example                                                                                                                                                                                    | 39 |

| Figure 8  | Basic units of the SoCLC hardware                                                                                                                                                                                   | 40 |

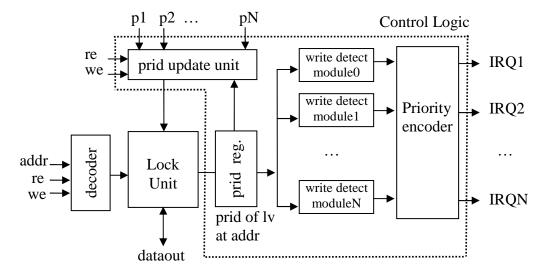

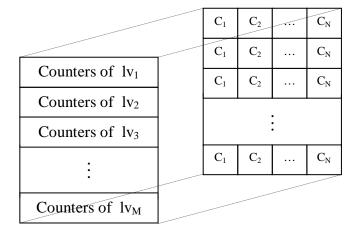

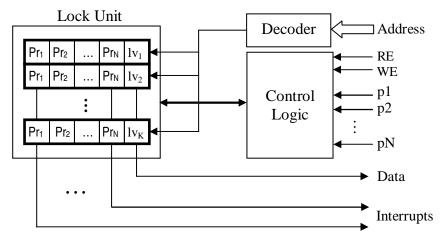

| Figure 9  | SoCLC basic control logic hardware architecture                                                                                                                                                                     | 43 |

| Figure 10 | SoCLC Lock Unit contains counters for long CS locks                                                                                                                                                                 | 45 |

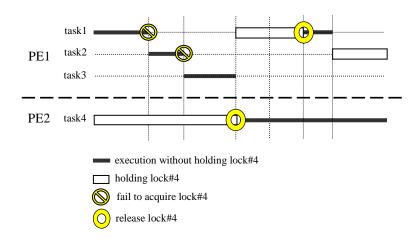

| Figure 11 | An example with four tasks running on two PEs                                                                                                                                                                       | 46 |

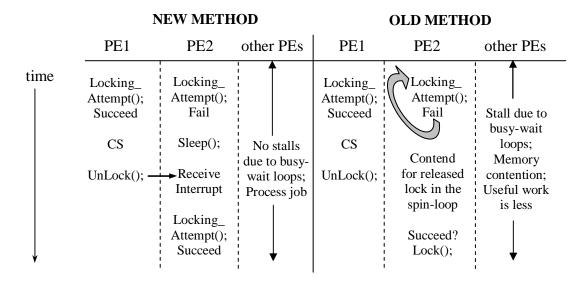

| Figure 12 | C and MIPS assembly codes of lock acquire function in the (a) traditional spin-lock and (b) SoCLC mechanism                                                                                                         | 48 |

| Figure 13 | SoCLC (new) mechanism and spin-lock (old) mechanism                                                                                                                                                                 | 49 |

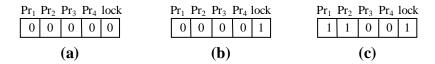

| Figure 14 | <ul><li>(a) Initial condition of lock and Pr bit locations in a four-PE system.</li><li>(b) Bit values after PE3 has acquired the lock.</li><li>(c) Bit values after both PE1 and PE2 have read the lock.</li></ul> | 52 |

| Figure 15 | ISR assembly code for MPC755                                                                                                                                                                                        | 52 |

| Figure 16 | Basic units of the SoCLC hardware.                                                                                                                                                                                  | 54 |

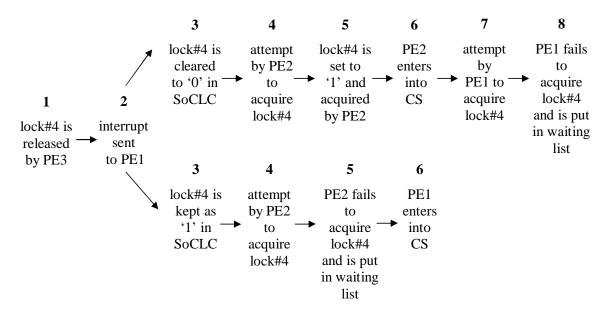

| Figure 17 | The event flow occurring in action (1) – top flow – and the event flow occurring in action (2) – bottom flow                                                                                                        | 56 |

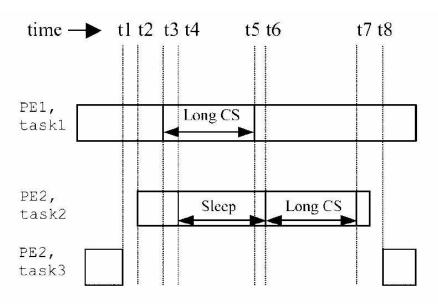

| Figure 18 | Disallowing preemption for long CSes may cause inefficient CPU utilization among tasks                                                                                                                                                                                                                                                                                   | 58 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

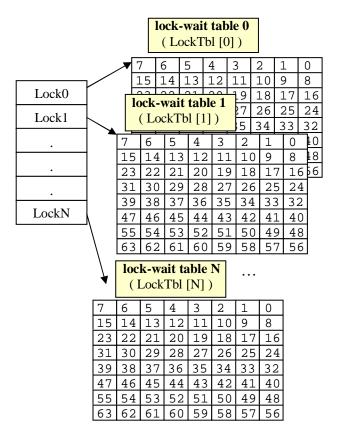

| Figure 19 | Lock-wait tables                                                                                                                                                                                                                                                                                                                                                         | 59 |

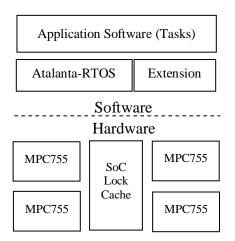

| Figure 20 | Hardware/software architecture with RTOS extension                                                                                                                                                                                                                                                                                                                       | 60 |

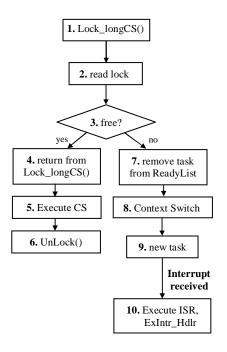

| Figure 21 | Flowchart illustrating the long CS locking steps in software                                                                                                                                                                                                                                                                                                             | 61 |

| Figure 22 | LOCK struct type                                                                                                                                                                                                                                                                                                                                                         | 62 |

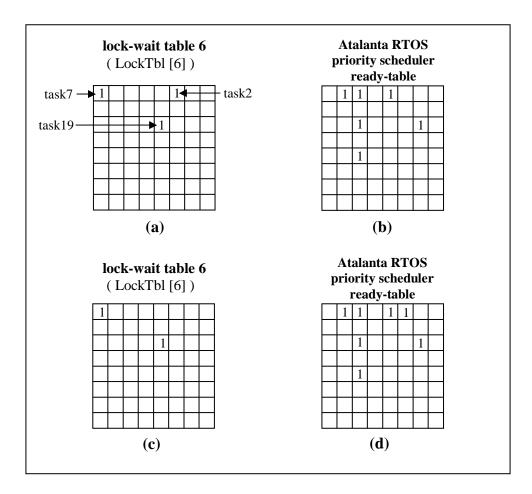

| Figure 23 | Lock-wait table states and the RTOS scheduler ready list states. (a) Tasks 2, 7, and 19 are waiting for lock#6 to be freed. (b) Tasks 3, 5, 6, 17, 21 and 37 are ready in the Atalanta RTOS priority scheduler ready table. (c) Task2 bit location in the lock-wait table 6 is cleared by the ExIntrHdlr function. (d) Task2 bit location in the ready table is set to 1 | 63 |

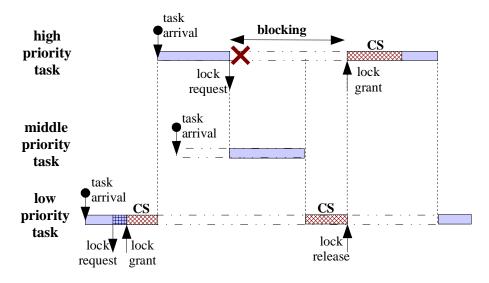

| Figure 24 | Priority inversion problem                                                                                                                                                                                                                                                                                                                                               | 66 |

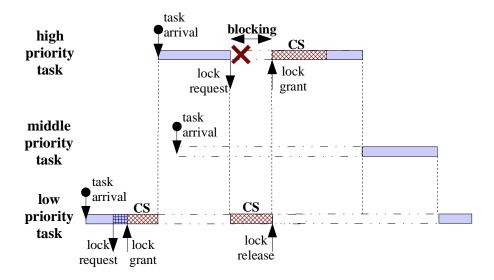

| Figure 25 | Priority inheritance protocol (PIP) prevents unbounded blocking                                                                                                                                                                                                                                                                                                          | 68 |

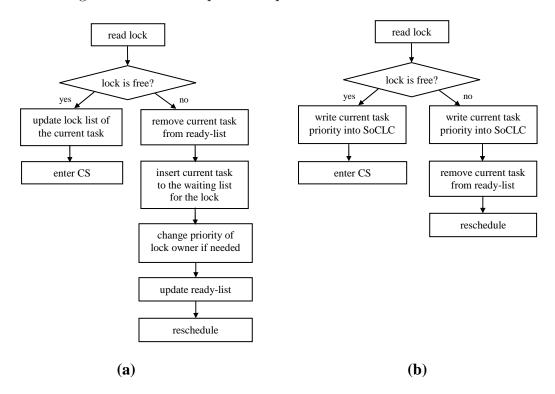

| Figure 26 | Flow charts of locking operation for (a) Atalanta RTOS priority inheritance mechanism, (b) SoCLC priority inheritance mechanism.                                                                                                                                                                                                                                         | 71 |

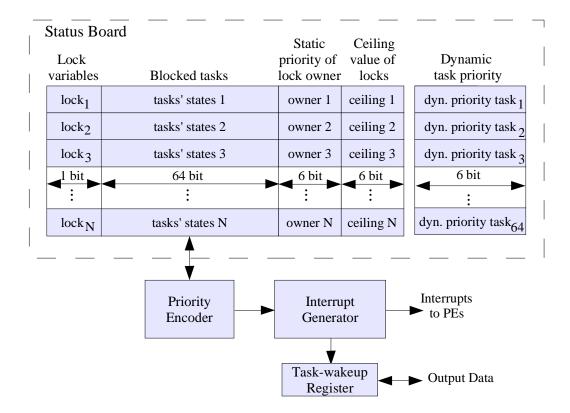

| Figure 27 | Priority inheritance hardware components in the SoCLC                                                                                                                                                                                                                                                                                                                    | 73 |

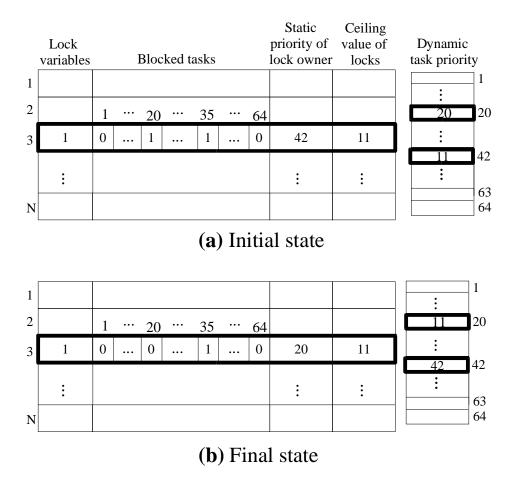

| Figure 28 | Status board corresponding to the (a) initial and (b) final states as described in Example 4.3.1                                                                                                                                                                                                                                                                         | 75 |

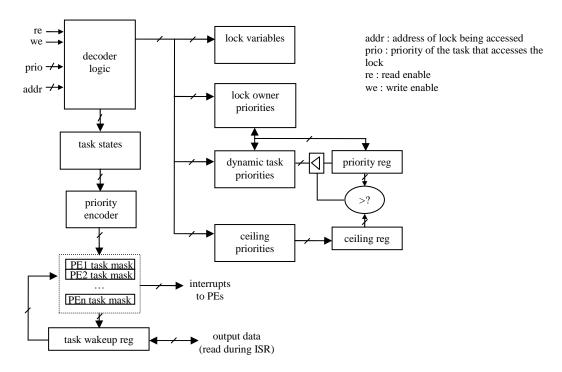

| Figure 29 | Hardware architecture of SoCLC priority inheritance unit                                                                                                                                                                                                                                                                                                                 | 77 |

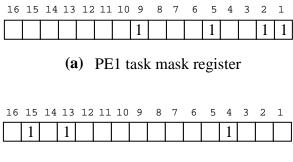

| Figure 30 | (a) PE1 task mask register contents, and (b) PE2 task mask register contents of Example 4.3.2                                                                                                                                                                                                                                                                            | 78 |

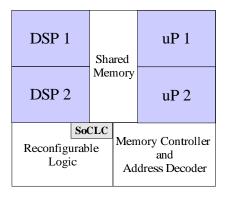

| Figure 31 | A typical target SoC architecture                                                                                                                                                                                                                                                                                                                                        | 82 |

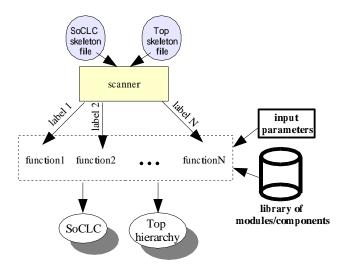

| Figure 32 | PARLAK building blocks                                                                                                                                                                                                                                                                                                                                                   | 85 |

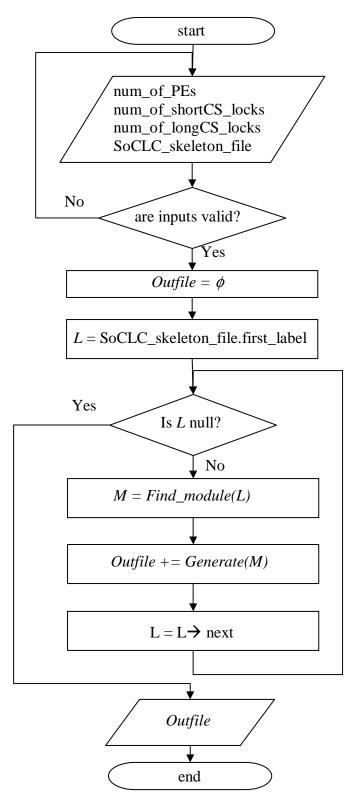

| Figure 33 | Pseudo algorithms of code generation                                                                                                                                                                                                                                                                                                                                     | 86 |

| Figure 34 | (a) An example SoCLC skeleton file with three labels. (b) The corresponding SoCLC output file after labels of the skeleton file are scanned and the codes at the corresponding labels are generated                                                                                                                                                                      | 87 |

| Figure 35 | Flowchart of code generation with PARLAK                                                                                                                                                                                                                                                                                                                                 | 88 |

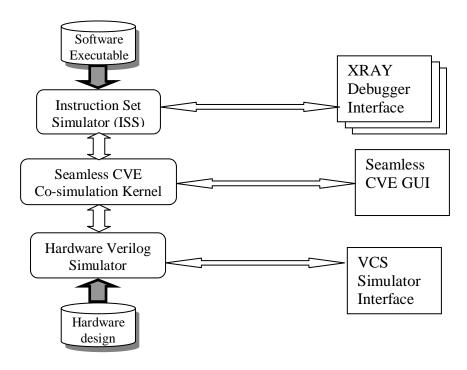

| Figure 36 | Seamless CVE tool components                                                                                                                                                                                                                                                                                                                                             | 92 |

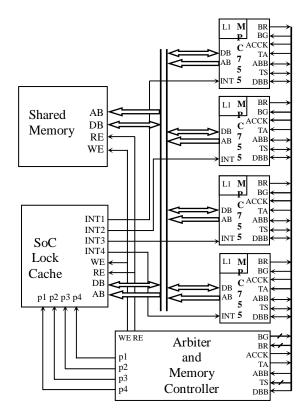

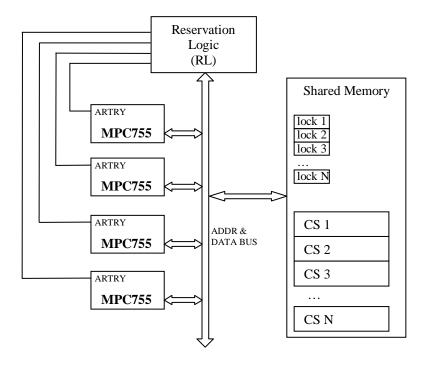

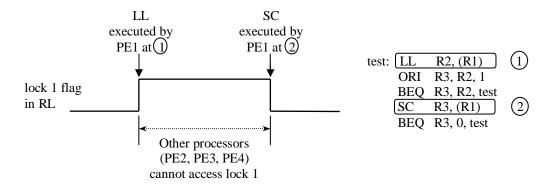

| Figure 37 | Hardware architecture setup with MPC755 processors                                                                                                                                                                                                                                                                                                                       | 93 |

| Figure 38 | Reservation Logic (RL) connected to the system bus                                                                                                                                                                                          |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 39 | Reservation Logic operation between LL and SC instructions 98                                                                                                                                                                               |

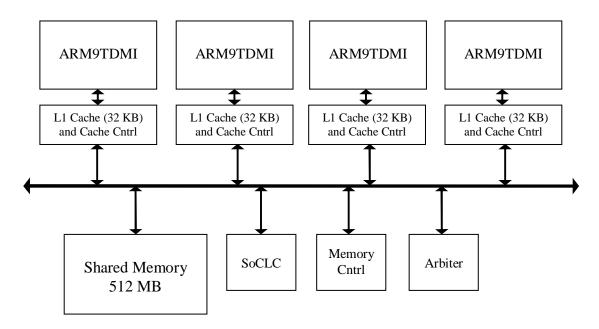

| Figure 40 | Hardware architecture setup with ARM9TDMI processors 96                                                                                                                                                                                     |

| Figure 41 | Microbenchmark program pseudo code                                                                                                                                                                                                          |

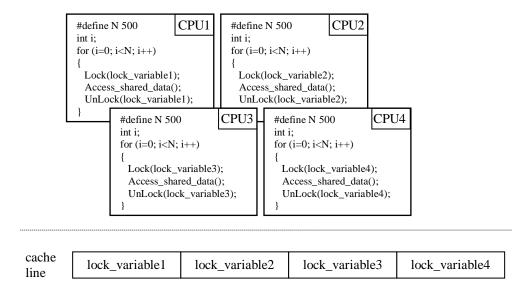

| Figure 42 | Microbenchmark codes used for the false sharing experiment 100                                                                                                                                                                              |

| Figure 43 | Microbenchmark total execution times for different memory latencies. 103                                                                                                                                                                    |

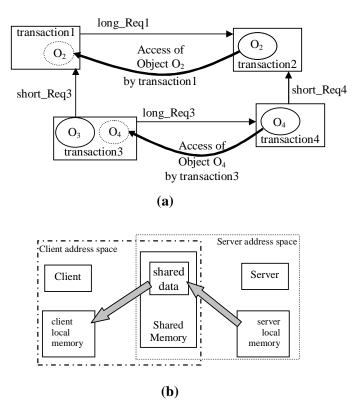

| Figure 44 | Database example (a) transactions and (b) object-copy 106                                                                                                                                                                                   |

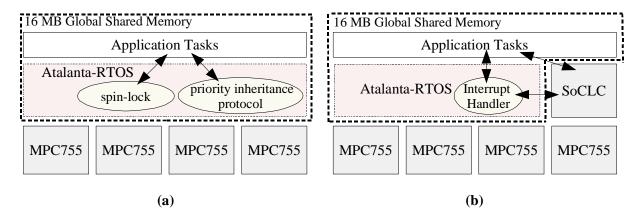

| Figure 45 | Hardware/software architectures used in our experiments. (a) Atalanta RTOS handles the priority inheritance and the spin-lock mechanisms in software. (b) SoCLC handles the priority inheritance and lock-based synchronization in hardware |

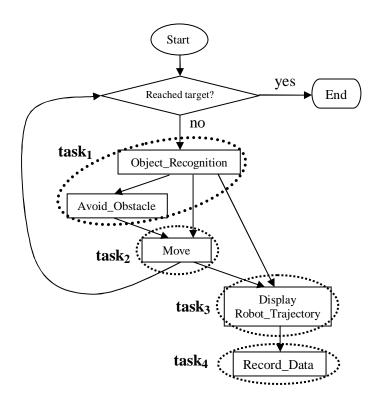

| Figure 46 | Robot application model and job-partitioning among tasks 112                                                                                                                                                                                |

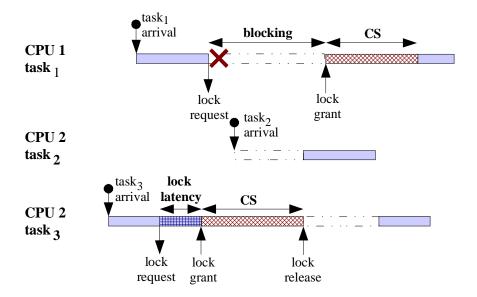

| Figure 47 | $Task_3$ inherits $task_1$ 's priority during the time that $task_3$ executes its CS. After completing its CS, $task_3$ yields the CPU2 to $task_2$ 113                                                                                     |

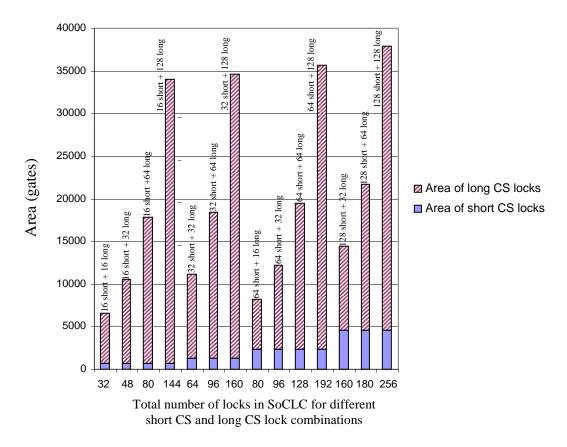

| Figure 48 | Synthesis results for several number of lock combinations in the So-CLC. Number of PEs is equal to 4 and clock period is 10ns 115                                                                                                           |

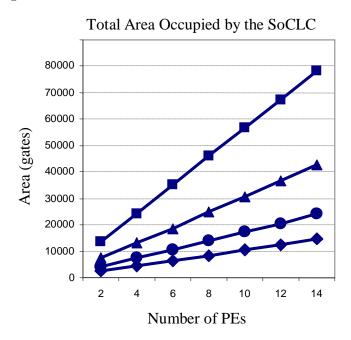

| Figure 49 | Synthesis results of the total area of the SoCLC for increasing number of PEs for number of locks = 32, 64, 128 and 256. Clock period is 50ns                                                                                               |

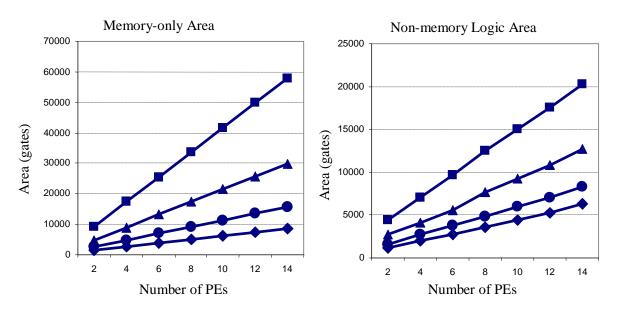

| Figure 50 | (a) Memory-only area of the SoCLC. (b) Non-memory area of the SoCLC. Clock period is 50ns                                                                                                                                                   |

## **SUMMARY**

The objective of this thesis is to implement efficient lock-based synchronization by a novel, high performance, simple and scalable hardware technique that is easily applicable to a shared-memory multiprocessor System-on-a-Chip (SoC). Our solution is provided in the form of an intellectual property (IP) hardware unit which we call the SoC Lock Cache (SoCLC). The SoCLC provides effective lock hand-off by reducing on-chip memory traffic and improving performance in terms of lock latency, lock delay and bandwidth consumption.

In our methodology, lock variables are accessed via SoCLC hardware. The SoCLC consists of one-bit registers to store lock variables and associated control logic to effectively implement the lock hand-off via interrupt generation, which eliminates busy-wait problems. In this way, the SoCLC eliminates the use of the main memory bus for unnecessary spinning and thus enables the memory bandwidth to be available for other useful work.

On the other hand, unlike the related previous work in the literature, the SoCLC does not require any special atomic assembly instructions (e.g., compare-and-swap, test-and-set, load-linked/store-conditional instructions), extended cache protocol(s), extra cache lines/tags or any other architectural modifications/extensions to the processor core. Rather, the SoCLC methodology is a processor/memory/cache-hierarchy independent solution.

Our experimental results indicate that SoCLC can achieve 37% overall speedup over traditional locking mechanism in a microbenchmark program with a high contention condition for four processor system. Moreover, with increased memory latency, the speedup of SoCLC for the same microbenchmark is also increased, achieving up to 107% speedups for a memory latency of 33 clock cycles. We also examine the false sharing effect as well as increased CS length effect on locking performance. Another set of experiments have been conducted with a database application program for which SoCLC has been shown to achieve speedup of 31% in the overall execution time.

To automate SoCLC design, we have also developed an SoCLC-generator tool, PARLAK, that is capable of generating parametrized, synthesizable and user specified configurations of a custom SoCLC. Using PARLAK with .25 $\mu$  TSMC technology and a 10ns clock period, we have generated customized SoCLCs from a version for two processors to a version for four processors occupying up to 37,940 gates of area for 256 lock variables. We have also generated customized SoCLCs for larger number of

processors with a 50ns clock period; e.g., an SoCLC version for 14 processors occupied 78,240 gates of area for 256 lock variables.

Furthermore, the SoCLC mechanism has been extended to support priority inheritance with an immediate priority ceiling protocol (IPCP) implemented in hardware, which enhances the hard real-time performance of the system. The experimental results indicate that the SoCLC can achieve up to 43% overall speedups on practical applications. Furthermore, it has been shown in a robot application that with the IPCP mechanism integrated into the SoCLC, all of the tasks could meet their deadlines (e.g., a high priority task with  $250\mu s$  worst case response time could complete its execution in  $93\mu s$  with SoCLC, however the same task missed its deadline by completing its execution in  $283\mu s$  without SoCLC). Therefore, with IPCP support, our solution can provide better real-time guarantees for real-time systems.

## CHAPTER I

## INTRODUCTION

## 1.1 Problem Statement

Synchronization has always been a fundamental problem in multiprocessor systems. As multiprocessors run multitasking application software with a real-time operating system (RTOS), important shared data structures, also called critical sections (CSes), are accessed for inter-process communication and synchronization events occurring among the tasks/processors in the system. The consistency of the critical sections can be guaranteed by a lock variable whose use allows only one execution unit at a time to access the shared data. However, given the limited communication resources (e.g., a single memory bus), the locks may easily become a bottleneck of the system: processors spin on the lock, i.e., busy-wait, until the lock is released. During this busy-wait time, the amount of useful work is degraded; and, even worse, the lock owner processor contends with the other spinning processors for the memory bus and hence the time at which the lock owner releases the lock is delayed, causing

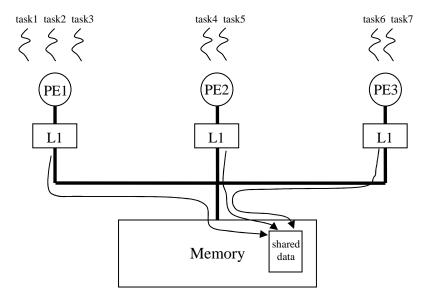

**Figure 1:** Shared data structures may cause contention in a shared-memory multiprocessor system.

additional unpredictable stalls in the system. Figure 1 illustrates typical resource contention among processing elements (PEs) in a system.

On the other hand, the length of a CS – whether it is *long* or *short* – affects system behavior. In case the CS is long, the locking mechanism should allow the lock requester task to yield the processor to another task – via a context switch (i.e., preemption) – because the lock would be busy for a long time. In case the CS is short, in which case switching context would be relatively expensive, the locking mechanism should avoid a context switch and hence spin until the lock is released. Therefore, it is essential to identify these two (short and long) types of CSes and develop effective locking mechanisms for both.

As for the long CSes, where context switching is allowed, the *priority inversion* problem arises. Priority inversion occurs when a higher priority task is blocked on a

lock owned by a lower priority task. Because the blocking time is unbounded, i.e., unpredictable, it is vital to prevent priority inversion in a real-time system so that real-time guarantees can still be achieved.

One other aim is to have the solution be processor-/cache-independent. Unlike previous work that requires special synchronization instruction support, special caches or special micro-architectural extensions to the processor core, we aim to develop a hardware solution that works with different types of processors (i.e., for heterogeneous multi-processor systems), even with processors that do not have special synchronization instructions or even with processors having no caches at all. Moreover, the hardware solution needs to be reusable, scalable, customizable and reconfigurable in a time-efficient way for a target SoC.

## 1.2 Thesis Contributions

This thesis presents a hardware solution to lock synchronization in a shared-memory multiprocessor SoC. Our solution is provided in the form of an intellectual property (IP) hardware unit which we call the SoC Lock Cache (SoCLC). The SoCLC resolves critical section interactions among multiple PEs/tasks, provides an effective lock hand-off, eliminates the need for special synchronization instructions or for specialized caches/micro-architectural units, provides a more predictable real-time solution and improves the performance criteria in terms of lock latency, lock delay and bandwidth consumption in the system.

Moreover, the SoCLC can be easily integrated into an SoC via the system bus. Unlike the previous work presented in Chapter 2, the SoCLC does not require any special assembly instructions, extended cache protocol, extra cache lines/tags or any other architectural modifications/extensions to the processor core. Rather, SoCLC is a PE/memory/cache-hierarchy independent solution.

One other contribution of this thesis is the priority inheritance (with immediate priority ceiling protocol) implementation which is employed into the SoCLC mechanism in hardware. Our implementation improves the performance of the system, prevents unbounded blockings and chained blockings. Furthermore, our implementation is ported to custom application specific interface (API) calls within the RTOS; therefore, from the application programmer's perspective, our custom SoCLC with priority inheritance looks like any other RTOS component.

We also measure the area cost of our hardware mechanism. We address customizability/reusability problems with the SoCLC hardware mechanism and, for this purpose, present the parametrized lock cache generator, which we call PARLAK. PARLAK is an IP-generator tool that can be used to generate custom, synthesizable SoCLC architectures for a target SoC. Two experimental configurations with (1) multiple Motorola PowerPC755 processors and with (2) multiple ARM9TDMI processors connected to the SoCLC via the system bus have been set up and simulated. Performance results of our approach are given for this experimental setup. Several synthesizable versions of the SoCLC architecture have been generated using

PARLAK. The output files generated by PARLAK have been directly synthesized by the Synopsys Design Compiler, and the relevant area results of these configurations are presented in Chapter 6.

In short, SoCLC is a high performance hardware solution that addresses lock-based synchronization for a shared-memory multiprocessor SoC. Furthermore, using the PARLAK tool, scalable, easily applicable, customizable versions of the SoCLC can be generated for a target SoC.

## 1.3 Thesis Organization and Roadmap

This thesis is organized as follows. Chapter 2 presents lock-based synchronization primitives, software and hardware based synchronization schemes in previous work and describes other operating system related issues such as blocking/non-blocking synchronization and the priority inversion problem. Chapter 3 presents our methodology and the basic SoCLC hardware mechanism. Chapter 4 presents our priority inheritance hardware support as part of the SoCLC. Chapter 5 presents an IP-generator tool that can generate synthesizable SoCLC architectures. Chapter 6 presents the performance results of the basic SoCLC mechanism and the priority inheritance hardware mechanism as well as SoCLC synthesis results using PARLAK. Finally, Chapter 7 summarizes the thesis.

## CHAPTER II

### BACKGROUND AND PREVIOUS WORK

Locks are associated with shared/critical data that needs to be kept consistent among multiple tasks/processes executing on one or more processing elements (PEs). If one of the PEs wants to access a shared data, the PE first has to acquire a lock variable and only then will the PE modify/read the shared data. If there are other PEs requiring access to the same shared data, then they have to busy-wait to acquire the lock. Busy-waiting occurs when PEs continuously poll a lock variable – thus using up valuable communication bandwidth – until they acquire the lock themselves. As such, the consistency of the shared data is preserved at a cost of increased contention among the PEs and decreased amount of useful work in the system.

## 2.1 Locking Schemes

Before proceeding further, we define two important performance criteria often used to compare locking schemes: lock delay and lock latency. Definition 2.1.1 Lock Delay. Given one or more PEs waiting for a lock, lock delay is the time between when the lock is released and when the next spinning or otherwise waiting PE acquires the lock. □

Example 2.1.1 Consider a web-server application program which consists of multiple client threads Ci (i=1,2,...,n) and server threads Sj (j=1,2,...,m). Let's say a lock is being held by S1. Also assume that there are 10 client threads, C1,C2,C3,...,C10 that attempt to acquire the same lock in order to safely read from the shared memory space of the server S1. Clearly, the clients will fail to acquire the lock. When the server thread S1 releases the lock, one client thread, say C3 will contend with the other waiting clients (C1,C2,C4,...,C10) and will acquire the lock first. The lock delay time spent by C3 is the time between when S1 releases the lock and when C3 acquires the lock.  $\Box$

**Definition 2.1.2 Lock Latency.** The time required for a PE to acquire a lock in the absence of contention. □

Example 2.1.2 Again consider the same application in Example 1, but where the lock is available (the lock is not in use and there is no request to acquire the lock). If client C3 attempts to acquire the lock, C3 will be successful. The lock latency is the time between when C3 attempts to acquire the lock and when C3 acquires the lock.

Next we present the common hardware instructions that can be used to implement the traditional locking mechanism in software.

#### 2.1.1 Hardware Instructions for Locking

A PE that performs a locking operation reads a lock value and checks whether the lock is free or not. If the lock is free, then the PE can acquire the lock by setting the lock value to a '1'. Because the lock variable itself is a shared resource, its access should be mutually exclusive, so as to provide coherent locking of the lock variable among multiple requesters.

To guarantee that only one PE is able to obtain the lock, special hardware instructions can be used to implement mutually exclusive lock access. In the next subsections, we examine the two types of these hardware instructions: (1) a single test-and-set instruction and (2) a load-linked/store-conditional pair of instructions.

#### 2.1.1.1 Test-and-Set Instruction

The accesses to lock variables can be made completely atomic by use of a special instruction ensuring consistent updates on a lock variable. A test-and-set instruction is a primitive hardware instruction that serves this purpose. The test-and-set instruction reads the value at a location of a lock variable in memory and, if the lock is available, writes a value to the location atomically such that the lock is now acquired.

All practical implementations (more than five) of the test-and-set instruction examined by the author of this thesis use a '0' to indicate that the lock is free and a '1' to indicate that the lock is busy. Furthermore, each read of the lock variable is always followed unconditionally by a write of a '1', i.e., regardless of the lock value read out. In other words, the read and the write accesses to that location are successive and

indivisible. The read access corresponds to the test operation and the write access corresponds to the set operation of the test-and-set instruction, respectively. Note that the test-and-set instruction returns the original value read. If a processor reads '0' (test) from a location using a test-and-set instruction, then the successive write (set) operation sets the lock variable to a '1'. Because the value returned is '0', the lock is acquired. However, if the processor reads '1' (test), then test-and-set returns '1', in which case the processor fails to acquire the lock.

#### 2.1.1.2 LL/SC Instructions

General purpose processors like MIPS, Alpha AXP and PowerPC¹ architectures support the LL/SC (load linked/store conditional) pair of instructions. The LL and SC instructions are paired in such a way that both of them must reference the same physical address – effective address (EA) – location in memory, otherwise execution of these instructions is undefined. Moreover, their execution establishes a breakable link between the two instructions. The status of the link (whether the link exists or not) between LL and SC is kept in a special LL/SC register of each processor. If an external device (e.g., a second processor) has modified the value stored at the EA or an exception has occurred in the meanwhile (i.e., after LL but before SC), the link between LL and the subsequent SC will be broken and the special LL/SC register (which holds the status of the link between LL and the subsequent SC) is cleared.

<sup>&</sup>lt;sup>1</sup> "LDQ-L" and "STQ-C" instructions in Alpha AXP and "lwarx" and "stwcx." instructions in PowerPC.

In this case, the SC instruction fails to execute. If the link is not broken, the SC instruction will succeed.

With the functionality brought by these special instructions, traditional synchronization operations have been developed in software, such as test-and-set, compare-and-swap, fetch-and-increment and fetch-and-add [30]. Figure 2 depicts an example usage of LL/SC instructions in the MIPS instruction set [15] implementing the functionality of the test-and-set instruction.

```

test: LL R2, (R1); read lock

ORI R3, R2, 1;

BEQ R3, R2, test; spin if lock is busy

SC R3, (R1); try to acquire lock

BEQ R3, 0, test; spin if SC fails

```

**Figure 2:** MIPS assembly code for test-and-set functionality that is implemented using the LL/SC pair of instructions.

#### 2.1.2 Traditional Spin-Lock

The traditional spin-lock mechanism is the lock acquire mechanism that uses the test-and-set algorithm. Figure 3 depicts a spin-lock using a test-and-set instruction, and Figure 2 depicts a spin-lock using the LL/SC pair of instructions.

The LL/SC instructions are used to test the lock value – whether it is free or busy – and atomically set the lock in case it is free or go back to test again in case it is busy. If all attempts to acquire the lock always make appropriate use of LL and

SC instructions, this prevents more than one processor from modifying the lock at the same time. In this way, the mutual exclusion of lock access is guaranteed.

#### Lock\_acquire:

while(test-and-set(lock)==1);

Figure 3: Spin-lock algorithm using test-and-set instruction.

In Figure 2, the LL instruction simply loads the lock value into the register R2 and sets a special LL/SC register for the EA of the lock; here, the EA of the lock is the address stored in the register R1. Thus, R2 will have the lock value which will be '0' if the lock is free or '1' if lock is busy. Next, R3 is set to '1' by the ORI instruction and then compared with R2 by the BEQ instruction. If R2 were '1', meaning the lock is busy, then the program will continue from the **test:** label, beginning with the LL instruction again. However, if R2 were '0', then program would continue with the SC instruction. The SC instruction will store '1' into the EA location (which is pointed by R1) only if the special LL/SC register is still set. If the link register is cleared, which implies that another PE has written to the same EA location, SC does not store a '1' to the EA. The target register, R3, will indicate if the SC has failed (R3 == 0) or succeeded (R3 == 1). If SC has failed, the subsequent instruction, BEQ R3, R2, **test**, causes the program to loop back to the **test** label again; otherwise, the lock has been held and the PE can access the shared data.

Looping back and reading the lock value to test the lock value again can dramatically increase memory traffic. This increase is due to lock releases followed by cache invalidations invoking all the spinning processors unnecessarily to update their cache

lines having the old copy of the lock. These invalidations cause waste of memory bus cycles (bandwidth consumption) and prevent other PEs from using the memory bus to do useful work. Even worse, spinning may cause an extra delay for the lock holder after it decides to release the lock, because the lock holder also contends for the bus with the other spinning processors. In a multi-stage network, such a condition may result in the so-called "hot-spot" problem; i.e., one specific memory unit (that contains the lock variable) becomes the hot node in the network, which causes congestion on the interconnect of the hot node and, therefore, severe performance degradation in the affected system [36].

To prevent limited memory and/or communication resources from becoming bottlenecks, effective synchronization mechanisms are necessary. These mechanisms can be categorized into two groups: (1) hardware-based solutions and (2) software-based solutions. The hardware-based solutions include cache-based mechanisms, queue-based mechanisms and several speculative locking schemes. Software-based solutions, on the other hand, include several spin-lock alternatives such as spin-on-read and delayed spin loops. Software-based solutions also include several queue-based algorithms such as Anderson's array-based locks [5], Graunke and Thakkar's locks [13], MCS locks [28] and LH-and-M locks [25]. The following sections explain these synchronization mechanisms and discuss their drawbacks and/or limitations.

## 2.2 Hardware Based Synchronization Mechanisms

It has been shown that a hardware solution brings a much better performance improvement [17], [18] than the algorithmic locking alternatives developed in software. Several cache-based locking primitives were developed and evaluated [12], [40], [41] as a hardware solution to the synchronization problem. These different approaches examine synchronization in terms of busy-waiting of the processors, intrinsic latency for accesses to the synchronization variables in the memory and the bus and/or network contention generated by these accesses. There have been other hardware approaches to address the synchronization problems speculatively, such as transactional memory [17], speculative lock elision [38] and speculative synchronization [26]. However, most of the hardware solutions introduced are nothing but improvements on processor caches in the form of special caches with a new cache protocol and/or modifications and extensions to the processor core.

#### 2.2.1 Cache Based Synchronization

As a hardware solution, one previous work concentrates on special cache schemes where they implement hardware FIFO queues of the lock requesters using cache lines [41]. Their work combines synchronization with the cache coherency protocol, which allows local spinning in the cache. However, the implementation requires extra states in the cache controller. For instance, the lock variables and the state information of these lock variables have to be kept in the cache lines, which requires a larger cache tag and brings a further complexity in the cache/memory system design.

There has been other previous work implementing queues in hardware such as queue on lock bit (QOLB)<sup>2</sup> [12], [19]. QOLB keeps the waiting processors as a queue in the cache line and enables local spinning on cache. One feature of QOLB is to take advantage of collocation so that the critical section, i.e., the shared data can be transferred to the waiting processor at the same time with the lock hand-off. However, QOLB requires extra hardware mechanisms, such as direct cache-to-cache transfer during hand-off and queue states to be kept in the cache lines. QOLB also assumes that the coherency protocol is not activated when multiple processor nodes operate on the same address location. Moreover, the benefit of collocation is dependent on the cache line size; if the shared data does not fit in the cache line, that shared data will not benefit from collocation [18].

#### 2.2.2 Transactional Memory

Transactional memory (TM) is a generalization of the LL/SC pair of instructions [17]. A transaction is a finite sequence of instructions executed by a single process *speculatively* until an access conflict is detected (resulting in a squash and a roll-back) or until the transaction is validated/committed. In the conventional scheme, LL/SC provides an atomic access to a single shared-memory location. TM, however, requires special assembly instructions by which atomic accesses to multiple independent addresses can be performed. As such, a critical section does not need to be protected by a lock variable any more (enabling a lock-free synchronization).

<sup>&</sup>lt;sup>2</sup>Originally called queue on synch bit (QOSB).

However, the consistency of the shared data within a critical section is provided by the special transactional memory instructions operating on the shared data addresses. As such, the shared data in the critical section can themselves be accessed atomically using the special transactional memory instructions. The cost of TM is that it needs (1) special processor instruction support to handle speculative execution and (2) a separate cache (inside the processor and other than the regular Level one (L1) cache) with an extended cache coherency protocol to support the transactional memory operations for detecting access conflicts and buffering the speculative data. These inflexible requirements make it expensive to apply the TM approach, for instance, to a heterogeneous multiprocessor SoC consisting of different types of general purpose processors: the TM approach requires modifications to the processor instruction set and the cache hierarchy of each processor in the SoC. Other drawbacks of the TM approach are that it requires a significant programming effort and it does not guarantee forward progress, which might be a serious problem for long transactions having large data sets (e.g., long critical sections).

#### 2.2.3 Speculative Lock Elision

Similar to TM, speculative lock elision (SLE) can provide, in certain situations, speculative synchronization without acquiring the lock (i.e., in a lock-free manner); however, in the worst case SLE requires the acquisition of a lock [38]. SLE is advantageous over TM in that the SLE mechanism is transparent to the programmer (there is no programming effort) and SLE does not require special instructions or dedicated

cache/cache-coherency protocol. Note that, however, SLE assumes an invalidationbased cache protocol to detect atomicity violations.

However, SLE does not guarantee forward progress without roll-back either, and the write-buffer/cache size required to hold the speculatively accessed data is still a concern. Forward progress guarantee is important, as the data conflicts or resource limitations cause squashes, in which case the SLE mechanism will be reduced to the traditional spin-lock mechanism. Therefore, SLE does not perform well in the presence of data conflicts. Moreover, SLE requires a hardware support within the processor core: modifications on the write-buffer and a dedicated hardware unit to detect misspeculations.

Note that an extension to SLE has been proposed by the same authors: transactional lock removal (TLR) [39]. In the TLR approach, the tasks execute speculatively (using the SLE mechanism) and the speculative data is buffered locally in a write buffer. If any data conflicts occur (e.g., a cache miss) during the speculative execution, then these conflicts are resolved dynamically using timestamps. All speculative data requests (e.g., due to a cache miss) between processor caches are assigned timestamps. The processor with the earliest timestamp wins the conflict and commits the speculative data from its write buffer into its cache. (Note that the speculative data committed into the cache is kept coherent at all levels of caches from L1 to L2,...,Ln among the PEs in the system by use of a cache coherency protocol.) The processors with older timestamps lose the conflict and restart.

The cost of TLR (in addition to the cost of SLE – TLR requires SLE support) is a hardware queue for buffering the incoming timestamped requests, a new cache state to distinguish the speculative data being processed under TLR and finally dedicated TLR hardware support within the cache coherence controller. Also note that TLR assumes ability to retain an exclusive ownership of a cache block.

#### 2.2.4 Speculative Synchronization Unit

A speculative synchronization unit (SSU), on the other hand, is differentiated from SLE and TM in that SSU guarantees forward progress [26]. However, SSU is not a lock-free mechanism because it requires lock acquisition, which may cause convoying problems as the speculative tasks cannot commit before the lock holder releases the lock.

Note that an adaptive extension of SSU that can utilize the benefits of SLE is discussed in [27]. The adaptive approach may implement lock-based synchronization in the presence of conflicts/overflows and may implement the lock-free synchronization in the absence of conflicts/overflows [27].

As far as the hardware cost is concerned, the SSU mechanism also imposes modifications to the memory hierarchy in the form of special cache tags/bits, an extra cache line for speculative synchronization variables and some hardware logic to be integrated into the cache hierarchy of each processor in the system.

#### 2.2.5 Speculative Lock Reordering

One other speculative approach, speculative lock reordering (SLR) [43], exploits the fact that the critical sections guarded by the same lock can execute out-of-order. SLR allows the tasks to execute CSes speculatively and records any data dependency violations during this speculative execution. Then, using the record of dependency violations, SLR detects the data dependencies among the tasks and determines a commit order that would enable a smaller number of tasks to be squashed/restarted. This scheme is implemented with a speculation co-processor connected to the caches and to the CPU core, speculation hardware support within the caches and a commit order generator hardware unit connected to each processor [43].

Also note that the SLR approach is similar to TLR in that they can both resolve conflicts and hence avoid unnecessary squashes/restarts. However, while TLR solves this problem by using timestamps, SLR solves the problem by reordering the tasks: the reordering is determined by finding the data dependencies among tasks.

#### 2.2.6 Summary of Hardware Based Mechanisms

In general, the hardware approaches solve the problem of spin-lock overhead by allowing the PEs spin locally in their caches and by implementing the lock hand off via special cache schemes (e.g., cache-to-cache transfer and extra cache states to keep track of lock requests) [19], [41]. Dedicated hardware to detect data violations in case of speculative approaches is also required [27], [38], [39]. In short, these approaches impose modifications to the caches/cache protocols in the system and require special

microarchitectural extensions to the processor core, which restricts the applicability of these approaches into general purpose processors. Our approach (described later in Chapter 3), on the other hand, does not require any modifications to the processor core but rather is a custom hardware unit that can be used even with a primitive microcontroller with no caches at all while still achieving performance similar to that of the other hardware approaches presented in this section.

Next, we present the software-based synchronization mechanisms.

# $2.3 \quad Software \ Based \ Synchronization \ Mechanisms$

### 2.3.1 Spin on Read

To reduce the burden on the memory bus during spinning and busy-waiting, the spin-on-read (also called test-and-test-and-set) construct has been proposed [42]. In spin-on-read, each PE spins locally on its cache for the lock variable (i.e., test), before actually attempting to acquire the lock (i.e., test-and-set). As such, the bus consumption can be reduced during spinning. However, as far as the lock hand-off is concerned, the PEs still cause unnecessary memory traffic. The spinning PEs are invoked by the cache-invalidations upon a lock release and contend with each other to acquire the lock by executing test-and-set. However, only one of the PEs acquires the lock, while the rest of the PEs cause waste of bus cycles. Especially for small critical sections, spin-on-read can render similar performance characteristics as the spin-lock (Figure 3).

To remedy this problem, exponential/proportional back off has been applied into the spin loops [5], [28]. Delays can be inserted after noticing the release of a lock or between each reference to the lock variable. As such, the PEs are delayed before actually attempting to acquire the lock resulting in reduced contention. However, the delays in the spin loops may cause the lock latency to be high, which is not advantageous for low-contention conditions. Nevertheless, with its relatively easy implementation, spin-on-read with/without back off has been popular and evaluated in the literature as a base technique.

#### 2.3.2 Ticket Lock

In case of spin-on-read, although all spinning PEs crowd on the released lock, only one PE will acquire the lock and the rest will be wasting communication bandwidth by performing a test-and-set. To decrease the effects of invalidations, the *ticket lock* approach has been introduced [28]. The ticket lock mechanism uses two counters: one counter is used to count the number of releases of a lock and the other counter is used to count the number of locking requests. When a PE releases a lock, the release counter of the lock is incremented. When a PE attempts to acquire a lock, it performs a fetch-and-increment operation on the request counter of the lock and thereby obtains a request number (the current value of the request number). Each spinning PE compares its request number with the release counter: if the release counter equals the PE's request number, then the PE can stop spinning and acquire

the lock. Note that, unlike spin-on-read, the ticket lock supports a first-come-first-out (FIFO) based acquisition, providing a fair lock hand-off.

However, the ticket lock mechanism still causes traffic due to polling a common memory location: the release counter. To reduce this traffic, proportional delay has been inserted into the spin loops between the references to the release counter. The delay is set proportional to the difference between the values of the request and release counters. However, the delay time cannot be optimally determined due to unpredictable critical section lengths.

#### 2.3.3 Anderson's Array Based Locks

Anderson proposed an array-based queuing algorithm that allows each PE to spin on a different memory location; thus, PEs spin locally on their caches without using the memory bus [5]. The array based queuing algorithm also requires the fetch-and-increment primitive for the PEs to obtain a sequence number (which is incremented by each newly arriving PE) to atomically enqueue themselves into a chain of waiting PEs. A PE releases a held lock by notifying the next PE in the chain of that lock. The cost of lock hand-off is an invalidation and a read miss by the next PE before acquiring the lock.

One drawback of this approach is that it requires a fixed memory space per lock (i.e., space due to the distinct memory locations dedicated to each PE for local spinning). Moreover, because the queuing/dequeuing operations take time, the algorithm

performs poor in terms of lock latency, which makes array-based queuing unattractive for low contention conditions.

#### 2.3.4 Graunke and Thakkar's Locks

Independent from Anderson, a similar array-based queuing algorithm has been developed by Graunke and Thakkar [13]. The difference is in the implementation their algorithm. The algorithm represents the PEs in an array such that each element of the array flags whether the corresponding PE is the owner of the lock or not. Each lock requester PE spins on the array element that belongs to the PE ahead of itself. Upon a lock release, the owner PE updates its array element (on which the next PE is spinning) and thereby invokes the next PE. Note that Graunke and Thakkar's locks require the fetch-and-store primitive (instead of fetch-and-increment used in Anderson's locks).

The drawbacks of this approach are the same as with Anderson's approach: fixed memory space required to enable local spinning at distinct addresses and poor lock latency for low contention conditions.

#### 2.3.5 Queue Based Locks

#### 2.3.5.1 MCS Locks

Mellor-Crummey and Scott (MCS) introduce an algorithm that generates a unique linked-list queue – per lock – for the PEs holding and waiting for each lock [28]. The MCS algorithm uses the fetch-and-store primitive and the compare-and-swap

primitive to guarantee atomic FIFO ordering of the lock requesters. The fetch-andstore and the compare-and-swap primitives can be implemented using the LL/SC instructions as described previously in Chapter 2.1.1.2.

Figure 4 shows the MCS algorithm pseudo code. The lock requester PEs are linked to each other via software pointers. Each PE holds a record (of type MCSnode in Figure 4) that consists of a flag variable on which the PE spins locally and a software pointer pointing to the record of the next PE.

Similar to array based mechanisms, PEs spin locally on their flags. Upon a lock release call, the lock holder PE unsets the flag of the processor behind itself, invoking the next PE to acquire the lock. Note that the MCS algorithm requires less memory space than the array-based alternatives.

MCS is a scalable algorithm; it retains a good performance behavior when there is contention in the system. However, the lock latency is high, showing a constant software overhead due the complexity of the algorithm. Also, note that the lock hand-off strictly obeys a FIFO order, so lock hand-off cannot be prioritized among PEs nor can fast arbitrary (i.e., non-FiFO and non-priority) lock acquisition (especially if parallelism is high) be realized. (Note that as described in version (1) of Chapter 3.3.2, our approach can support fast arbitrary lock acquisition.)

MCS seems to be one of the best software locking algorithms appearing in the literature. Therefore, we compare SoCLC approach with MCS locks later in Chapter 6

```

1 type MCSnode{

MCSnode *next;

WORD flag;

3

4 };

5

6 MCSnode* lock = NULL; //initialize lock to NULL

8~\mathrm{MCS\_LockAcquire}(\mathrm{MCSnode}^{**}~\mathrm{lock},~\mathrm{MCSnode}^{*}~\mathrm{mynode})

9 {

MCSnode *prevnode;

10

mynode -> next = NULL;

//mynode becomes the last in queue

11

prevnode = fetch_and_store(lock, mynode); //atomically do the following:

12

//prevnode = lock

13

//lock = mynode

14

IF prevnode != NULL THEN //if lock is busy

15

mynode -> flag = TRUE;

16

prevnode -> next = mynode;

17

while(mynode->flag); //spin until lock is released

18

ENDIF

19

20 }

21

22 MCS_LockRelease(MCSnode** lock, MCSnode* mynode)

23 {

IF mynode -> next == NULL THEN

24

IF compare_and_swap(lock,mynode,NULL) THEN

25

return;

26

ENDIF

27

while(mynode->next==NULL);

28

ENDIF

29

mynode - > next - > flag = FALSE;

30

31 }

```

Figure 4: MCS algorithm pseudo code.

quantitatively. However, note that it has been shown in [49] that MCS does worse than tournament barriers for a cache-only memory architecture (COMA) based system.

### 2.3.5.2 LH and M Locks

LH and M locks are also implemented using a similar method to MCS locks, except that LH and M locks use the compare-and-swap primitive and, as claimed in [25], LH locks perform better than MCS locks in the presence of contention at a cost of increased lock latency (note that the increased lock latency problem is reduced in the case of M locks, but with a more complex algorithm).

### 2.3.6 Reactive Synchronization

A reactive synchronization mechanism has been introduced in [24]. In this approach, different software based mechanisms have been dynamically interchanged depending on the contention level of the system. For example, during a low contention execution, the test-and-set with exponential back off is used and during a high contention execution, queue based locking is used.

### 2.3.7 Summary of Software Based Mechanisms

In summary, test-and-set or spin-on-read mechanisms suffer from wasting useful bus cycles due to hold-cycles (i.e., cache response time due to simultaneous cache invalidations in case of a lock release). Therefore, test-and-set and spin-on-read both generate unnecessary memory traffic and thus do not scale well under contention.

The array- and queue-based algorithms, on the other hand, allow each PE to spin on its local address (rather than a single effective address) and provide a FIFO based notification between the lock releaser and the lock requester that is at the head of the queue when a lock is released. These queue-based alternatives bring better performance for high contention systems; however, they introduce large overheads in cases without contention and cause an increase in lock latency. Furthermore, as discussed in [5], queuing in shared memory has other negative effects such as convoying. For example, if a task holding a lock is preempted, every other task spinning behind the preempted task in the chain will have to wait for the preempted task to be rescheduled to release the lock. Also, note that queue-based alternatives require a specific atomic instruction (fetch-and-store, compare-and-swap) and a complex algorithmic implementation.

## 2.4 Performances of the Mechanisms

### 2.4.1 Benchmark Programs

Some of the application programs used in the previous work in evaluating the performance of the mechanisms have been chosen from the SPLASH/SPLASH-II benchmark suite (which includes scientific parallel applications developed for shared memory multiprocessors) [45], [52] and from Olden [9]. Microbenchmark programs, including spin-loop benchmark and counting, producer/consumer, doubly-linked list benchmarks, have also been used. In evaluating SoCLC approach, we have chosen the spin-loop microbenchmark program (and measured performance under varying

parameters such as CS length and memory latency), a multi-tasking database application and a robot application, all of which will be described later in Chapter 6. Similar to the benchmarks used by the previous approaches, our benchmarks include high contention scenarios that can be used to measure locking performance.

#### 2.4.2 Performance Results

Among the software solutions outlined in Chapter 2.3, MCS has been one of the most popular algorithms showing relatively better performance when compared to the other software based approaches described in Sections 2.3.1 through 2.3.3. For this reason, MCS has been used as a competitive mechanism for its hardware counterparts [19], [39]. On the other hand, the test-and-test-and-set mechanism (described in Section 2.3.1) and test-and-set with exponential back off have also been cited in the literature as the best approaches for performance comparison purposes. However, because MCS has been shown to perform better than these approaches, we compare against MCS rather than compare against test-and-test-and-set or test-and-set with exponential back off.

In this thesis, as presented in Chapter 6, we evaluate the performance of our approach when compared to the traditional spin-lock mechanism implemented with LL/SC instructions and when compared to MCS locks.

On the other hand, although each previous work has different simulation environments and application sets, albeit early, it may be remarkable to report here that QOLB has been shown to achieve 1.5X speedup<sup>3</sup> [19]; SSU has been shown to achieve 1.08X speedup – 7.4% reduction as indicated in [27] – when compared to the traditional spin-lock and the combined support of SLE and TLR for a 16 processor system has been shown to achieve up to 1.47X speedup [39] when compared to the spin-on-read mechanism. As it will be shown in Chapter 6, our results for a four-processor system show similar performance speedups (e.g., up to 1.37X) without using extensive in-processor hardware modifications at all.

Our approach constitutes a paradigm shift in the context of lock-based synchronization for multiprocessor shared memory systems. SoCLC approach eliminates the busy-wait overheads due to polling via a simple, stand-alone hardware without any constant software overhead present with previous software-based approaches or without any extra within-processor core modification requirements present with previous hardware-based approaches. As will be described later in Chapter 3, SoCLC distributes the locking functionality between hardware and software in an efficient manner with low cost.

In this thesis, we also consider task preemption (context switch) events under a real-time operating system. As the CS length is increased, so does the waiting time for the tasks blocked on the lock variable guarding that CS. Therefore, the waiting tasks should be allowed to yield the PE for long CSes, in which case, the tasks are

<sup>&</sup>lt;sup>3</sup>Please see [16] for the definition of speedup that we used in our calculations.

not blocked on the lock variable. In the next section, we identify some blocking and non-blocking synchronization approaches that appear in the literature.

## 2.5 Blocking versus Non-blocking Synchronization

So far, we have discussed previous work in terms of reducing the overhead of the busy-wait problem, where the waiting processor spins on executing the synchronization primitive/algorithm. Busy-waiting (i.e., spinning) may be the preferred synchronization construct to implement if the waiting period is short. If the waiting period is long, however, it may be more advantageous to implement the blocking synchronization construct instead, where the waiting process/task suspends itself and yields the processor for other tasks to run and do useful work. However, blocking introduces an overhead associated with switching context, which involves a function call at the operating system level. Therefore, the busy-wait construct may be preferred over the blocking (i.e., preemptive) construct if the waiting time is less than the overhead introduced by suspending the waiting task and resuming the new ready task afterward.

Several blocking and non-blocking algorithms have been implemented and compared in the literature [31], [32], [33], [51], [20], where it has been shown that non-blocking (preemption-safe) locking outperforms blocking as parallelism (e.g., number of tasks per processor) is increased. This is because, especially in queue-based locking, the waiting tasks impose a strict FIFO order and this ordering may cause delays when, for example, a lock holder at the head of a queue is preempted. This may

degrade performance as all the other waiting tasks cannot be scheduled to do useful work until the lock holder is rescheduled and releases the lock.

On the other hand, in the case of long critical sections (CSes), non-preemption of waiting tasks may cause inefficient CPU utilization because disallowing preemption may incur stalls during the execution time of a long critical section holding a lock for which a task on another processor is waiting. In such a case, the lock will not be released for a long time, and the waiting task on the other processor will occupy the CPU resources, causing performance degradation. Therefore, it is desirable to enable the scheduler to preempt those tasks that are waiting for the lock and resume other tasks ready to run on the CPU, which makes the CPU resources available for other tasks in the system while the suspended tasks are waiting for the lock release.

# 2.6 Priority Inversion

Task scheduling involves additional concerns due to the fact that tasks share resources. In a parallel system with a preemptive RTOS, if a high priority task is blocked by lower priority tasks (due to a common CS), the priority inversion problem occurs. The consistency of shared data is maintained (by use of a lock variable) at a cost of serialized accesses to the shared resources, i.e., no more than one task can access a shared resource at the same time. This may lead to the following situation. A low priority task may have accessed some shared data before a high priority task attempts to access the same shared data, in which case the high priority task is forced to wait for the low priority task. Even worse, there might a middle priority task that preempts

the low priority task before releasing the lock, causing unpredictable and unacceptable delays for the high priority task. A detailed example of the priority inversion problem is given in Example 4.1.1 of Chapter 4.

The priority inversion problem is unavoidable when lock-based synchronization (i.e., mutual exclusion) is used to maintain consistency; however, it is possible to bound the waiting time and thereby avoiding unpredictable delays. Previous work has addressed the priority inversion problem and proposed the *priority inheritance* solution with priority inheritance protocols for uniprocessor systems [44] and multiprocessor systems [37], [10]. The proposed priority ceiling protocols in [37] and [10] avoid unbounded blocking and prevent deadlocks.

In this thesis, we present a solution to the priority inversion problem in the context of a multi-processor SoC by integrating a priority inheritance protocol, specifically, the immediate priority ceiling protocol (IPCP), implemented in *hardware*. Our approach provides higher performance and better predictability for a real-time system on an SoC. The IPCP is integrated with the SoCLC, which is a specialized custom hardware unit realizing effective lock-based synchronization for a multiprocessor shared-memory SoC.

## 2.7 Summary

In this chapter, we presented how a traditional locking algorithm, spin-lock, is implemented, and identified the busy-wait problem caused by spin-lock. We explained different software-based and hardware-based approaches presented in prior work as

solutions to the problems associated with the traditional spin-lock approach; we further introduced some drawbacks and/or limitations of each of the prior approaches. We also stated the difference between blocking and non-blocking synchronization constructs and why it is important to distinguish the two. Finally, we presented the priority inversion problem and what support we will add into SoCLC to remedy this problem.

In the next chapter, we present our methodology and the basic SoCLC architecture.

### **CHAPTER III**

# BASIC LOCK CACHE DESIGN AND

### **OPERATION**

# 3.1 Methodology

A locking scheme (typically using lock variables) provides atomic access to shared memory locations through which multiple execution units (processes/threads/tasks) in an application program can interact.

We have expressed in Chapter 2 that blocking synchronization renders an overhead associated with switching task context and that blocking was preferred over busy-wait if the CS length (equivalently, the waiting time for the lock to be released) were long. In this context, we match the busy-wait approach with short critical sections and the blocking approach with long critical sections as the more advantageous construct to implement. Our hardware architecture, SoC Lock Cache, is designed to support both types of lock synchronization (blocking and non-blocking) constructs effectively. Therefore, our solution addresses two different types of critical section interactions,

namely, (1) short CSes and (2) long CSes. Before going into detail about the lock synchronization mechanism, we first clarify the difference between a long CS and a short CS.

**Definition 3.1.1 Short CS.** In a short CS, the duration of execution on the shared data structure is fine grained, that is, the time between the lock acquisition and release is short (e.g., less than 1000 clock cycles). □

**Definition 3.1.2 Long CS.** In a long CS, the duration of execution on the shared data structure is coarse grained, that is, the time between the lock acquisition and release is long (e.g., more than 1000 clock cycles).  $\Box$