# Physical Design of Optoelectronic System-on-a-Chip/Package Using Electrical and Optical Interconnects: CAD Tools and Algorithms

A Dissertation Presented to The Academic Faculty

By

### **Chung-Seok Seo**

In Partial Fulfillment Of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

#### Georgia Institute of Technology

November 2004

Copyright © Chung-Seok Seo 2004

# Physical Design of Optoelectronic System-on-a-Chip/Package Using Electrical and Optical Interconnects: CAD Tools and Algorithms

Approved:

Dr. Abhijit Chatterjee, Advisor

Dr. Madhavan Swaminathan

Dr. David E. Schimmel

Dr. John A. Buck

Dr. C. P. Wong

Date Approved 11/08/2004

Dedicated to

my father, Sun-Kyu Seo, my mother, In-Hee Song,

my sister, Min-Jung Seo, my brother-in-law, Doo-Hyun Kim, my nephew, Yun-Geun Kim,

my brother, Chung-Hyeon Seo, my sister-in-law, Young Ra,

my wife, Jiwon Park

and

my son, Jonathan H. Seo

for their love, encouragement and belief.

### ACKNOWLEDGEMENT

First of all, I would like to express my sincere gratitude to Professor Abhijit Chatterjee for the guidance and support that he has provided during my graduate career. I would also like to thank all the Ph.D. committee: Professor Madhavan Swaminathan, Professor John A. Buck, Professor David E. Schimmel, and Professor C. P. Wong. I sincerely appreciate their time and effort in serving on my committee.

I would like to extend special thanks to my colleagues, Pramod Variyam, Pankaj Pant, Sudip Chakrabarti, Junwei Hou, Sasikumar Cherubal, Alfred Vincent Gomes, Xiangdong Xuan, Kyuwon Choi, Soumendu Bhattacharya, Achintya Halder, Yuvraj Singh Dhillon, Utku Diril, S. Sermet Akbay, Donghoon Han, Ganesh Srinivasan, Shalabh Goyal and Maryam Ashouei for the company and valuable discussions.

I am also thankful to my dear friends, Soojung Ryu, Ji-Weon Jeong, Jinsook Hong, Jungmo Yang, Yong-Seok Seo, Jeff Yoon, Hyungjoon Kim, Jiyoung We and Namsik Hong. I would like to give my special appreciation to Sung-Hwan Min and Hyo-Jeong Kim for their support and friendship.

I would like to thank my parents, Sun-Kyu Seo and In-Hee Song, my sister, Min-Jung Seo, her husband, Doo-Hyun Kim, her son, Yun-Geun Kim, my brother, Chung-Hyeon Seo, his wife, Young Ra, my parents-in-law, Young-Bae Park and Yang-Ja Um, my sister-in-law, So-Ra Park, her husband, Jung-Hoon Kim, her daughter, Ji-Soo Kim and other relatives.

Finally, I would like to express my deepest appreciation to my wife, Jiwon Park and my son, Jonathan H. Seo for their love, encouragement and belief.

# TABLE OF CONTENTS

| ACKNO                            | WLEDGEMENT iv                                                                           |

|----------------------------------|-----------------------------------------------------------------------------------------|

| TABLE (                          | OF CONTENTS vi                                                                          |

| LIST OF                          | TABLES                                                                                  |

| LIST OF                          | FIGURES                                                                                 |

| ABBREV                           | /IATIONS                                                                                |

| SUMMA                            | RYxx                                                                                    |

| CHAPTE                           | ER 1 INTRODUCTION                                                                       |

| 1.1 P                            | roblem Statement                                                                        |

| 1.1.1<br>1.1.2<br>1.1.3<br>1.1.4 | Module Placement2Interconnect Modeling3Interconnect Routing3Optimization Algorithm4     |

| 1.2 H                            | istory of the problem                                                                   |

| 1.2.1<br>1.2.2                   | Optical Interconnection                                                                 |

| 1.3 K                            | ey Contributions                                                                        |

| 1.3.1<br>1.3.2<br>1.3.3<br>1.3.4 | Interconnection Modeling11Place and Route12Optical Clock Routing12Hybrid Optimization13 |

| 1.4 S                            | ummary of Dissertation14                                                                |

| CHAI                                   | PTER 2 MODELING OF FREE-SPACE OPTICAL INTERCONNECT                                                      | 15             |

|----------------------------------------|---------------------------------------------------------------------------------------------------------|----------------|

| 2.1                                    | Introduction                                                                                            | 15             |

| 2.2                                    | Interconnect Models                                                                                     | 16             |

| 2.3                                    | Speed Performance Model                                                                                 | 20             |

| 2.4                                    | Energy Cost Model                                                                                       | 22             |

| 2.5                                    | Summary                                                                                                 | 24             |

|                                        | PTER 3 DESIGN OF SYSTEM-ON-A-CHIP USING FREE-SPACE OPTICA<br>RCONNECT                                   |                |

| 3.1                                    | Introduction                                                                                            | 25             |

| 3.2                                    | Assumption                                                                                              | 28             |

| 3.3                                    | Optimization Algorithms                                                                                 | 29             |

| 3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3 | <ul> <li>.2 Optical Routing Capacity</li> <li>.3 Module Compaction</li> <li>.4 Cost Function</li> </ul> | 33<br>35<br>36 |

| 3.4                                    | Results and Analysis                                                                                    | 38             |

| 3.4<br>3.4                             |                                                                                                         |                |

| 3.5                                    | Summary                                                                                                 | 47             |

| CHAI                                   | PTER 4 MODELING OF OPTICAL WAVEGUIDE INTERCONNECT                                                       | 48             |

| 4.1                                    | Introduction                                                                                            | 48             |

| 4.2                                    | Inherent Optical Waveguide Losses                                                                       | 49             |

| 4.3                                    | Optical Waveguide Bending Losses                                                                        | 50             |

| 4.4  | Clock Signal Timing Skew Calculation                                                        | 52  |

|------|---------------------------------------------------------------------------------------------|-----|

| 4.5  | Summary                                                                                     | 54  |

|      | PTER 5 DESIGN OF OPTICAL CLOCK DISTRIBUTION NETWORKS US                                     |     |

| OPTI | CAL WAVEGUIDE INTERCONNECT                                                                  | 55  |

| 5.1  | Introduction                                                                                | 55  |

| 5.2  | Problem Statement                                                                           | 58  |

| 5.3  | Optimization Algorithms                                                                     | 59  |

| 5.3  | .1 Design Assumptions                                                                       | 61  |

| 5.3  | .2 Layout Partitioning                                                                      | 61  |

| 5.3  | .3 Optical Clock Routing                                                                    | 62  |

| 5.3  | .4 Optical Data Input Location                                                              | 66  |

| 5.3  | .5 Local Routing Heuristic                                                                  | 67  |

| 5.4  | Results and Analysis                                                                        | 69  |

| 5.4  | .1 Preliminary Result                                                                       | 69  |

| 5.4  | .2 Symmetric Structure                                                                      | 70  |

| 5.4  | .3 Asymmetric Structure                                                                     | 73  |

| 5.4  | .4 Optical Power Loss and Signal Timing Skew                                                | 77  |

| 5.5  | Summary                                                                                     | 78  |

| СНА  | PTER 6 DESIGN OF OPTOELECTRONIC SYSTEM-ON-A-PACKAGE US                                      | ING |

|      | CAL WAVEGUIDE INTERCONNECT                                                                  |     |

| 6.1  | Introduction                                                                                | 80  |

| 6.2  | Problem Statement                                                                           | 84  |

| ()   | Diask Dissement Algorithm Deceder Consumer Dain                                             | 07  |

| 6.3  | Block Placement Algorithm Based on Sequence Pair                                            | 80  |

| 6.4  | Partition of Electrical and Optical Interconnects and Routing of Electrical<br>Interconnect | 89  |

| 6.5   | Optical Data Path Routing                    | 90  |

|-------|----------------------------------------------|-----|

| 6.6   | Results and Analysis                         | 97  |

| 6.7   | Summary                                      | 119 |

| CHAP  | TER 7 CONCLUSION AND FUTURE WORK             | 120 |

| 7.1   | Conclusion                                   | 120 |

| 7.2   | Future Work                                  | 122 |

| APPEN | NDIX A SIMULATION RESULTS FOR GSRC BENCHMARK | 124 |

| APPEN | NDIX B PUBLICATION GENERATED                 | 172 |

| REFEI | RENCES                                       | 174 |

| VITA. |                                              | 181 |

# LIST OF TABLES

| Table 1. Possible practical advantages of optical interconnects                                                     | 1   |

|---------------------------------------------------------------------------------------------------------------------|-----|

| Table 2. Coefficients for speed regression model                                                                    | 22  |

| Table 3. Coefficients for energy regression model                                                                   | 24  |

| Table 4. Comparison with different sensor distributions                                                             | 40  |

| Table 5. The percentage improvement of energy consumption and speed with the different number of optical directions | 46  |

| Table 6. Power loss along the longest path for each stage (dB)                                                      | 77  |

| Table 7. Signal timing skew along the longest path                                                                  | 78  |

| Table 8. Simulation results for optimized area by area and total interconnect length                                | 100 |

| Table 9. Simulation results after using optical interconnects                                                       | 102 |

# **LIST OF FIGURES**

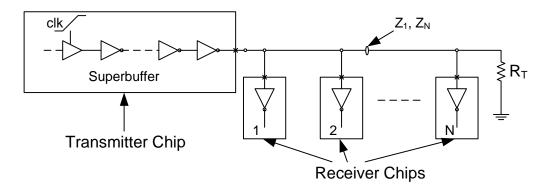

| Figure 1. Model of off-chip electrical interconnection with fan-out         | 16 |

|-----------------------------------------------------------------------------|----|

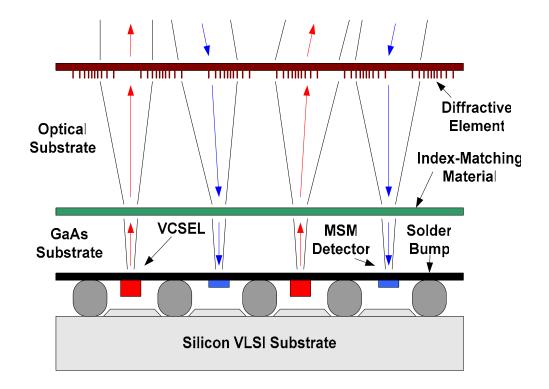

| Figure 2. Integration configuration for free-space optical substrate module | 17 |

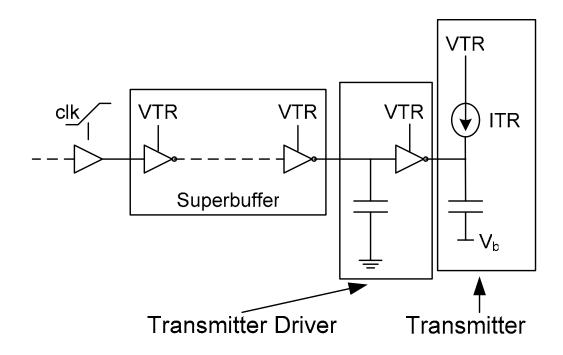

| Figure 3. Model of an optical signal transmitter                            | 18 |

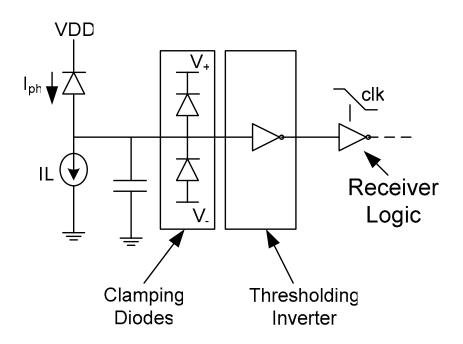

| Figure 4. Model of an optical signal receiver                               | 19 |

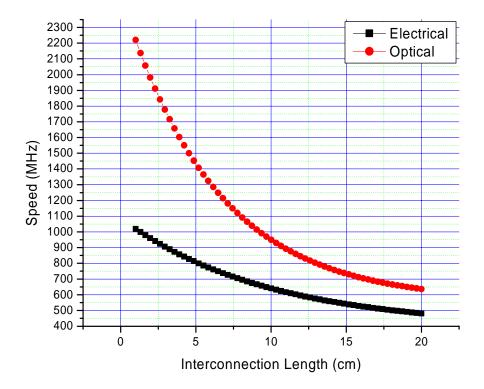

| Figure 5. Regression models for speed performance                           | 21 |

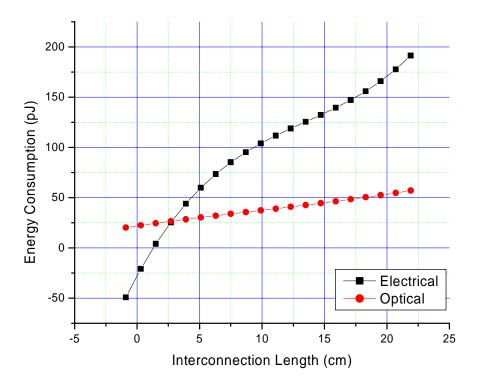

| Figure 6. Regression models for energy consumption                          | 23 |

| Figure 7. Optomechanical configuration in the neighborhood of the substrate | 28 |

| Figure 8. Three different sensor arrangements                               | 29 |

| Figure 9. An example that crossover operation does not work                 | 31 |

| Figure 10. Partially matched crossover                                      | 31 |

| Figure 11. GOETHE layout with optimization                                  | 33 |

| Figure 12. Optical vectors in Fourier plane                                 | 34 |

| Figure 13. Compression-Ridge Method                                         | 35 |

| Figure 14. The cost function                                                | 36 |

| Figure 15. Pseudo code for genetic optimizer                                | 37 |

| Figure 16. The cost graph                                                   | 39 |

| Figure 17. Placement and routing before optimization                        | 41 |

| Figure 18. Optical routing after optimization                               | 42 |

| Figure 19. | Electrical routing after optimization                                                                                                       | 43 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 20. | The graph for speed improvement vs. optical directions with various number of modules                                                       |    |

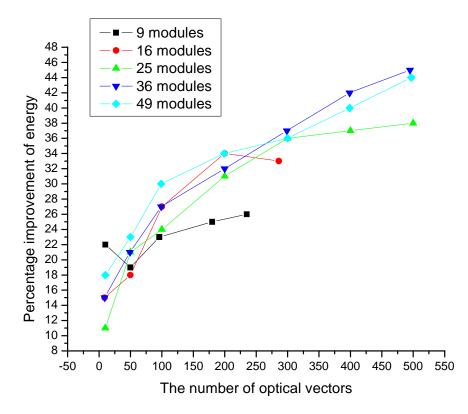

| Figure 21. | The graph for energy saving vs. optical directions with various numbers of modules                                                          | 45 |

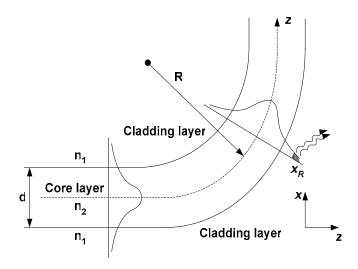

| Figure 22. | Bending loss derivation                                                                                                                     | 50 |

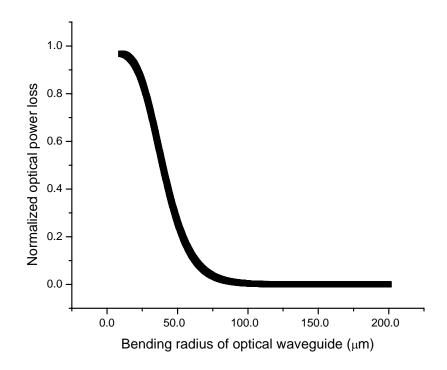

| Figure 23. | The normalized optical power loss                                                                                                           | 51 |

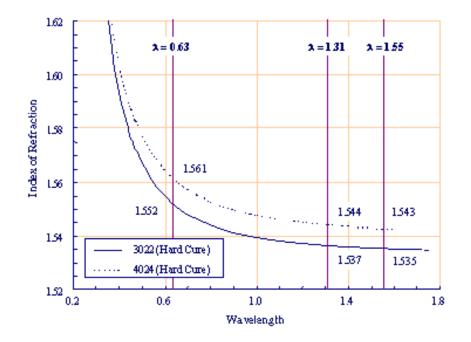

| •          | Index of refraction as a function of wavelength for photo BCB (4024-40) and<br>non-photo BCB (3022-46) after curing at 250°C for 60 minutes |    |

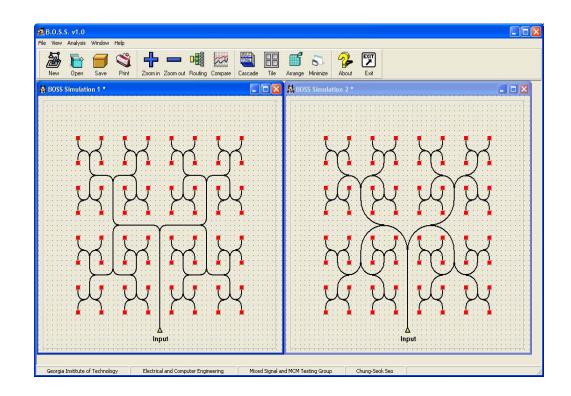

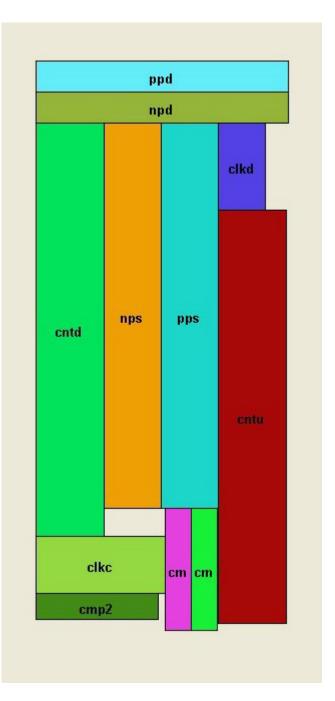

| Figure 25. | BOSS layout with a symmetric structure simulation                                                                                           | 57 |

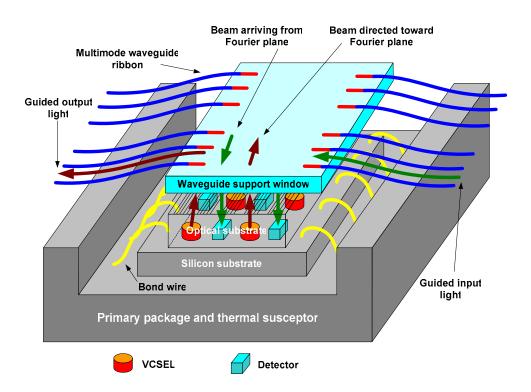

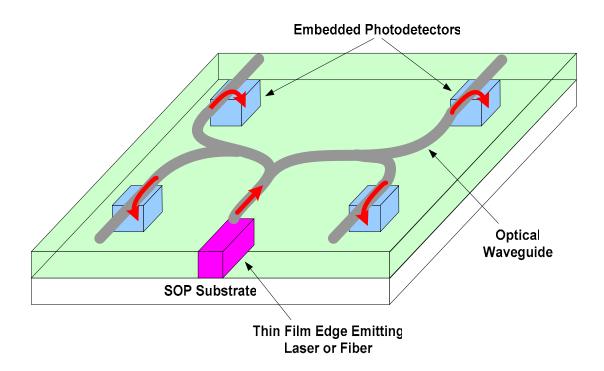

| Figure 26. | Integration configuration for high-speed optical clock distribution using embedded optoelectronics                                          | 58 |

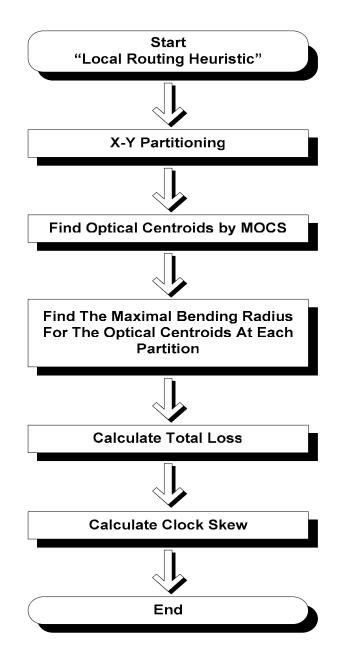

| Figure 27. | Overall flow of optical clock routing                                                                                                       | 60 |

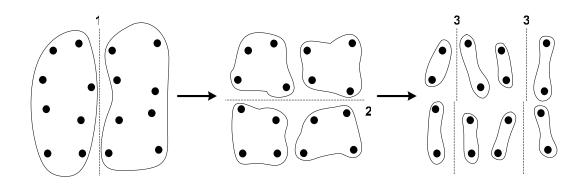

| Figure 28. | X-Y partition algorithm                                                                                                                     | 62 |

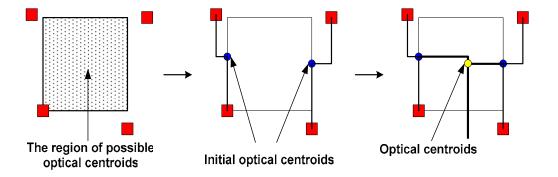

| Figure 29. | The method of optical centroid searching                                                                                                    | 63 |

| Figure 30. | Pseudo code for MOCS algorithm                                                                                                              | 64 |

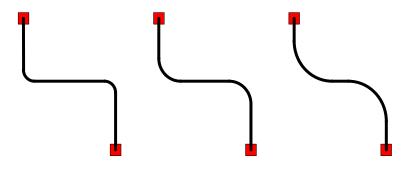

| Figure 31. | Example layout with different bending radii                                                                                                 | 67 |

| Figure 32. | Pseudo code for local routing heuristic                                                                                                     | 68 |

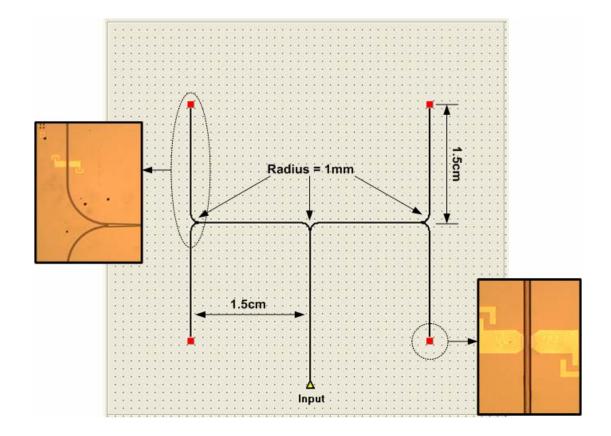

| Figure 33. | 1-to-4 H-tree structure layout with two enlarged microphotographs of fabrication                                                            |    |

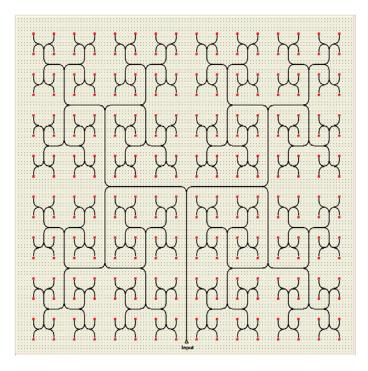

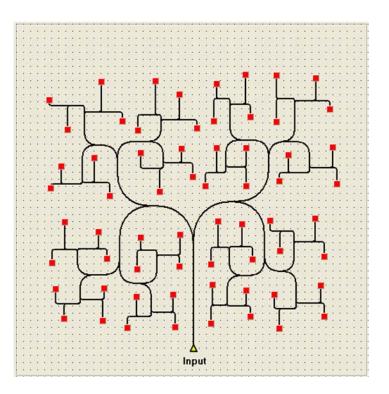

| Figure 34. | Symmetric clock routing of fanout 256 before optimization                                                                                   | 70 |

| Figure 35. | Symmetric clock routing of fanout 256 after optimization                                                                                    | 71 |

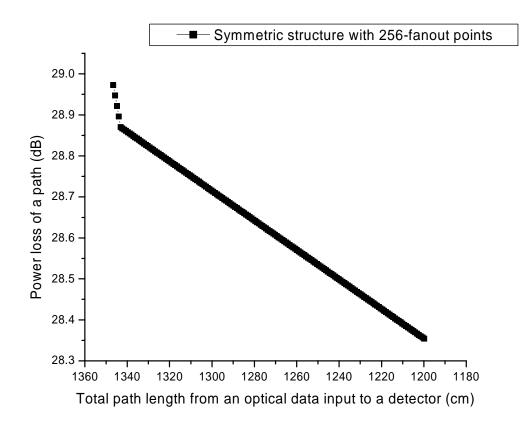

| Figure 36. | The reduction graph of total optical power loss of the longest path from an optical data input to a photodetector                           | 72 |

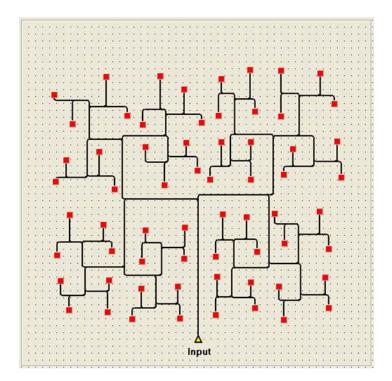

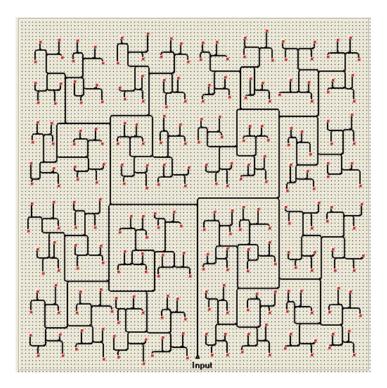

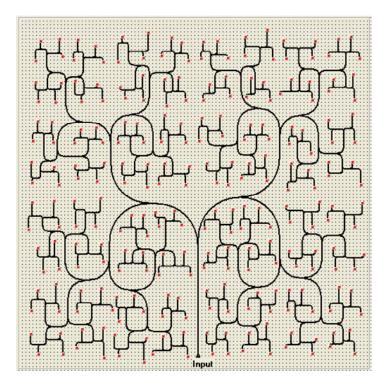

| Figure 37. Asymmetric clock routing of fanout 64 before optimization                                                                                                                               | . 73 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 38. Asymmetric clock routing of fanout 64 after optimization                                                                                                                                | . 74 |

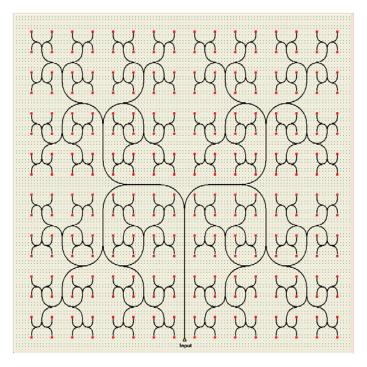

| Figure 39. Asymmetric clock routing of fanout 256 before optimization                                                                                                                              | . 75 |

| Figure 40. Asymmetric clock routing of fanout 256 after optimization                                                                                                                               | . 76 |

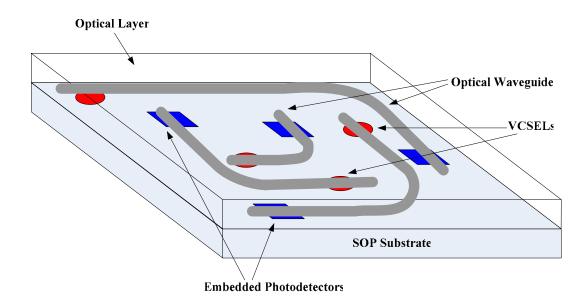

| Figure 41. Integration configuration for high-speed optical data path routingon a SOP substrate using enbedded optoelectronics                                                                     | . 82 |

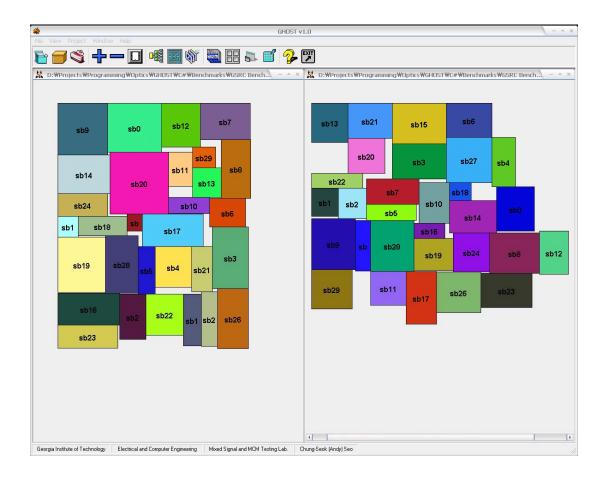

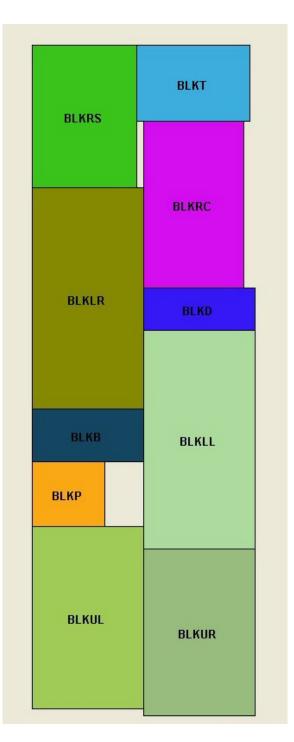

| Figure 42. GHOST layout                                                                                                                                                                            | . 83 |

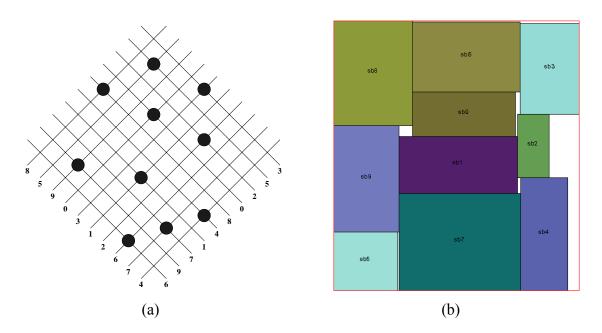

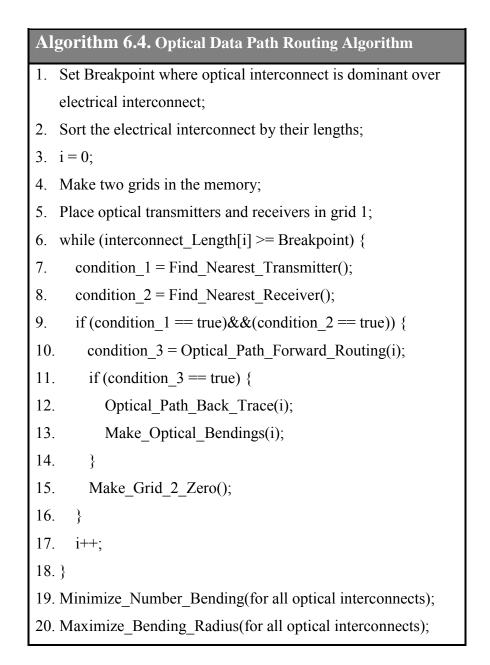

| Figure 43. The pseudo code for the simulated annealing                                                                                                                                             | . 84 |

| Figure 44. Hybrid genetic algorithm for optimization of module placement and routing electrical and optical interconnects                                                                          |      |

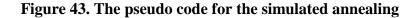

| Figure 45. An example of GSRC benchmark circuits: (a) 45 degree oblique grid of a sequence pair ((8 5 9 0 3 1 2 6 7 4), (6 9 7 1 4 8 0 2 5 3)), (b) Block representation by a sequence pair in (a) | . 87 |

| Figure 46. Block placement algorithm based on sequence pair representation by longes common subsequence computation                                                                                |      |

| Figure 47. Optical data path routing algorithm based on maze routing algorithm                                                                                                                     | . 91 |

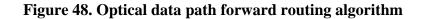

| Figure 48. Optical data path forward routing algorithm                                                                                                                                             | . 92 |

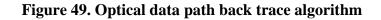

| Figure 49. Optical data path back trace algorithm                                                                                                                                                  | . 93 |

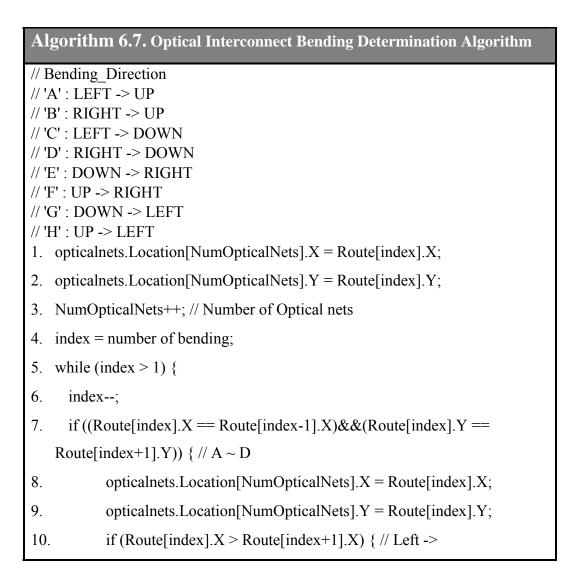

| Figure 50. Pseudo code for determining each bending radius of optical interconnects                                                                                                                | . 94 |

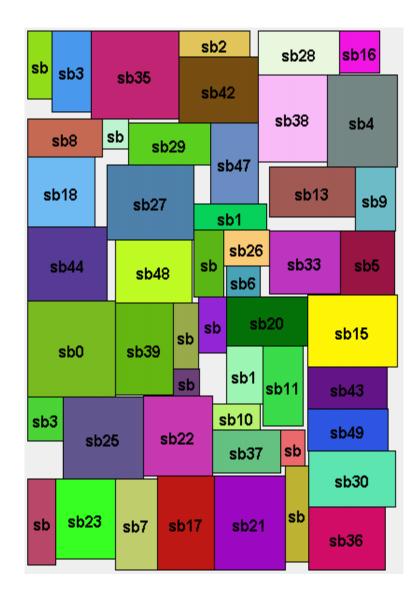

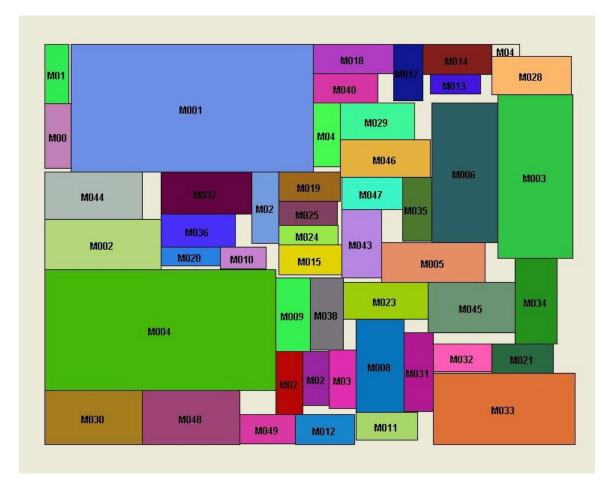

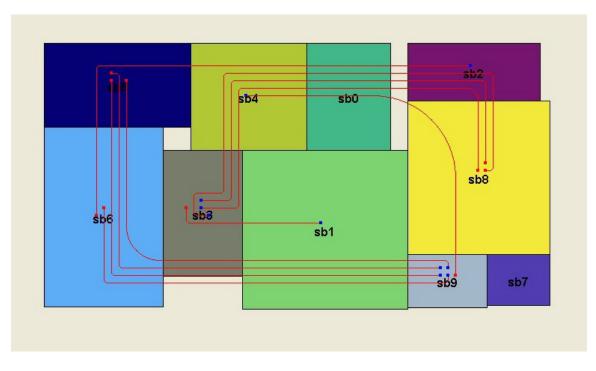

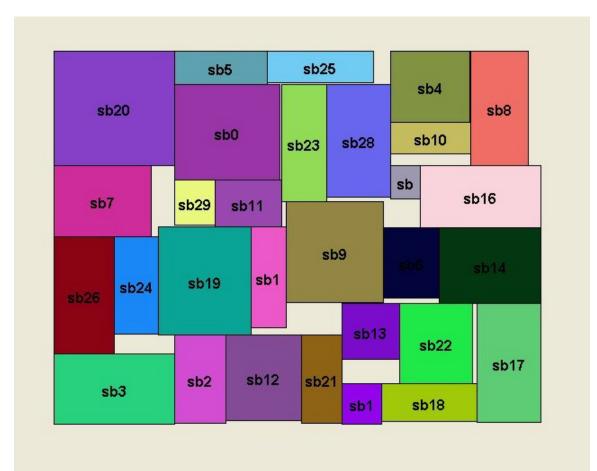

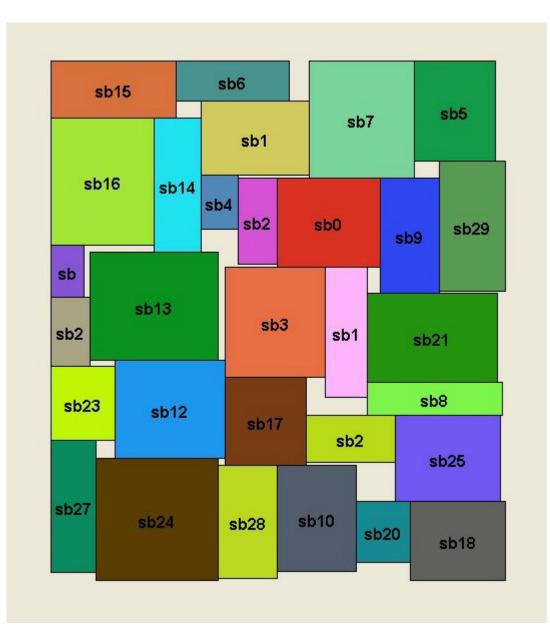

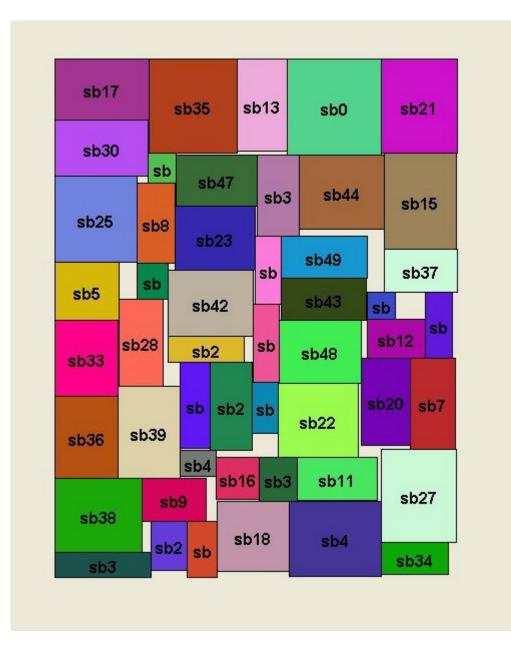

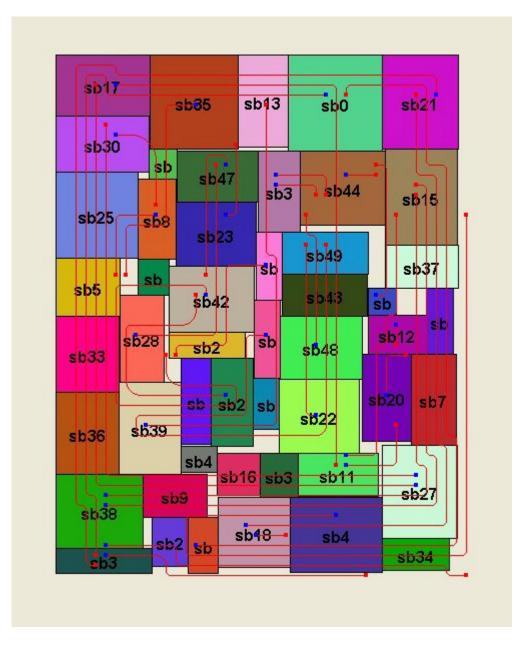

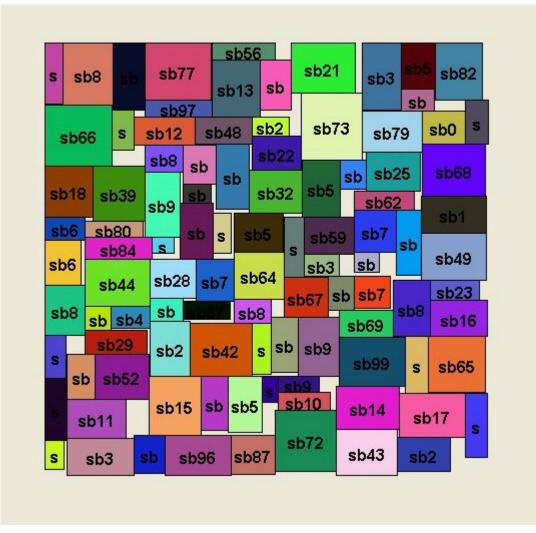

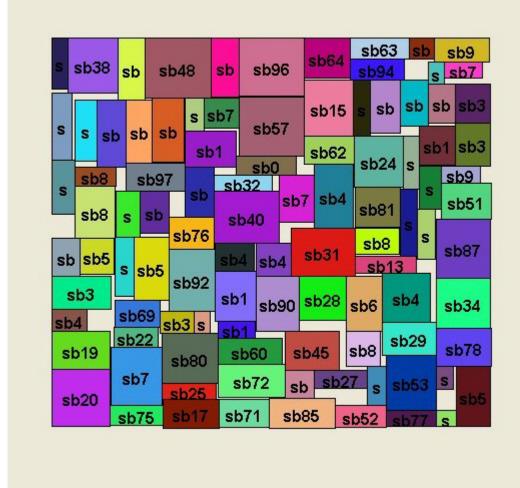

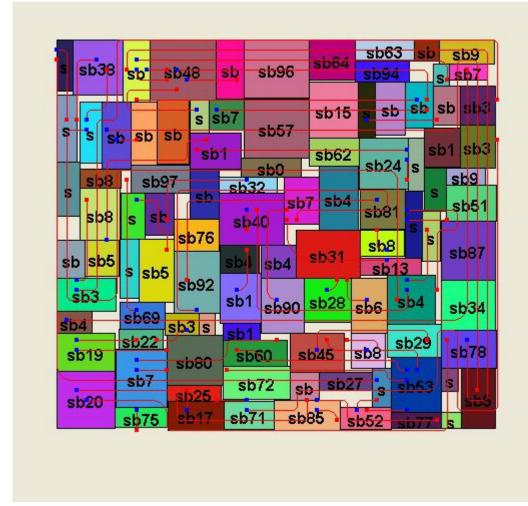

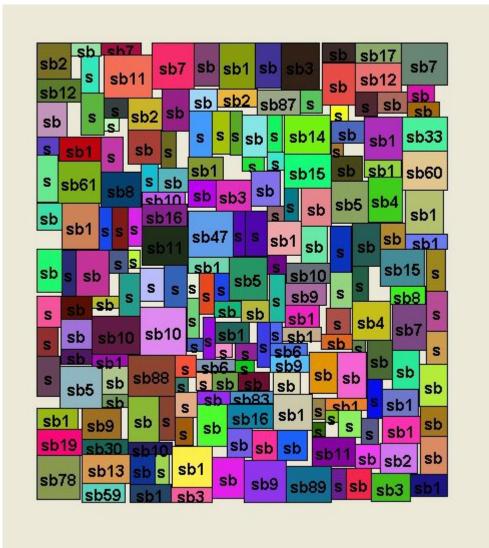

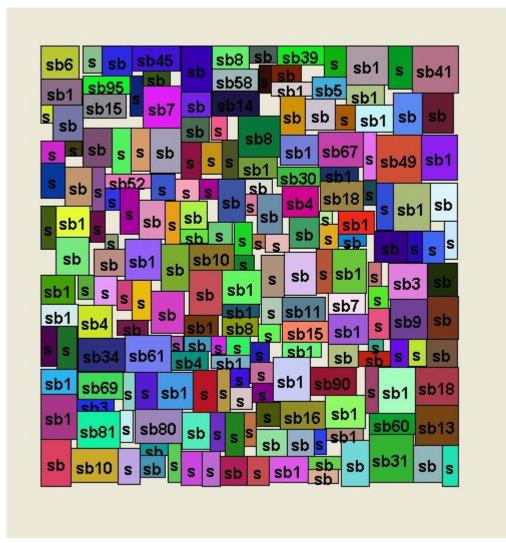

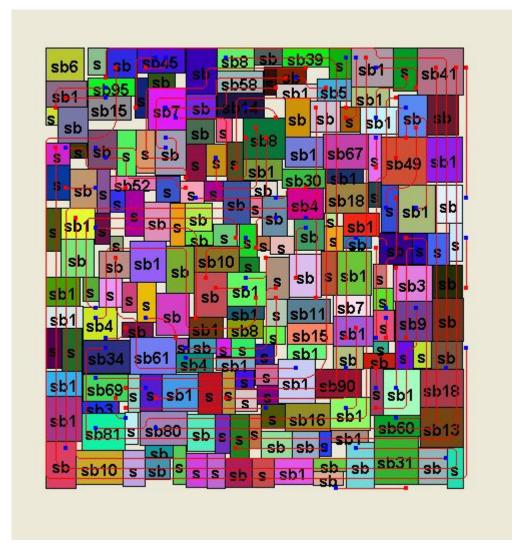

| Figure 51. GSRC benchmark circuit with 50 modules after area-driven optimization                                                                                                                   | . 98 |

| Figure 52. GSRC benchmark circuit with 50 modules after interconnect-driven optimization                                                                                                           | . 99 |

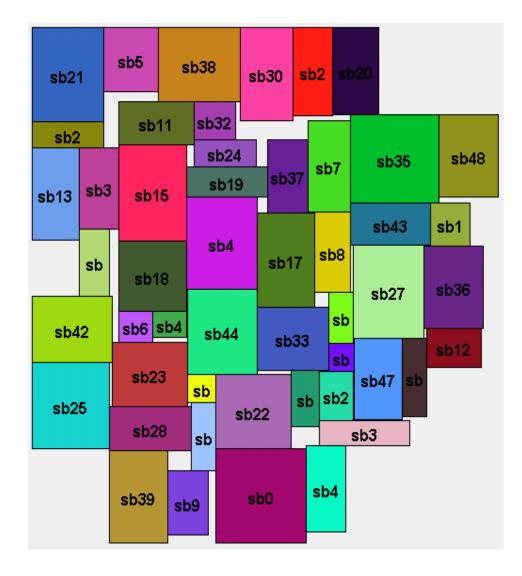

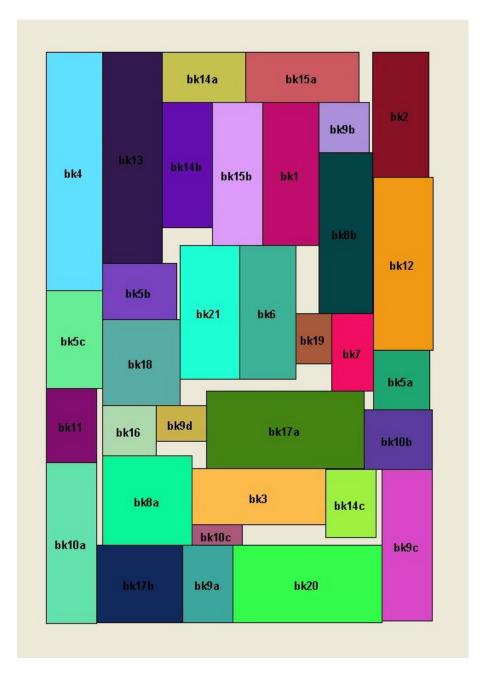

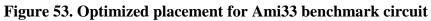

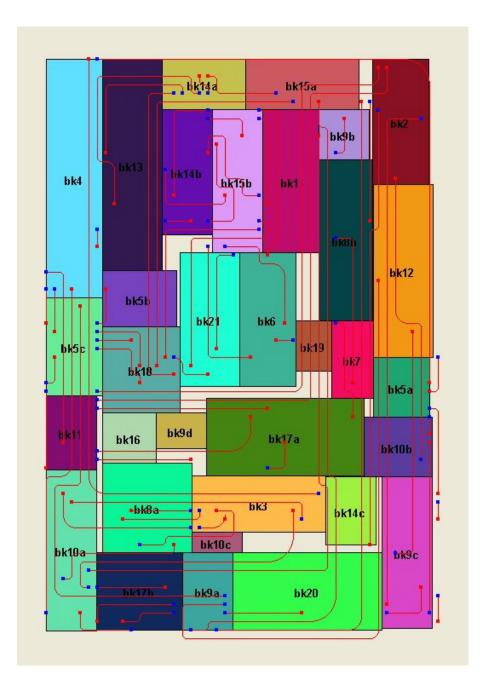

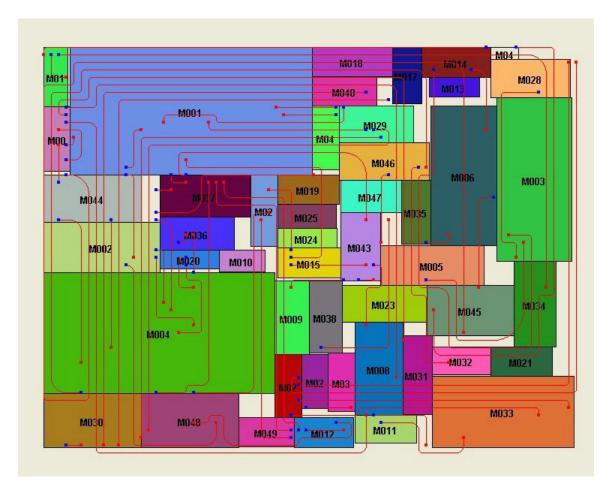

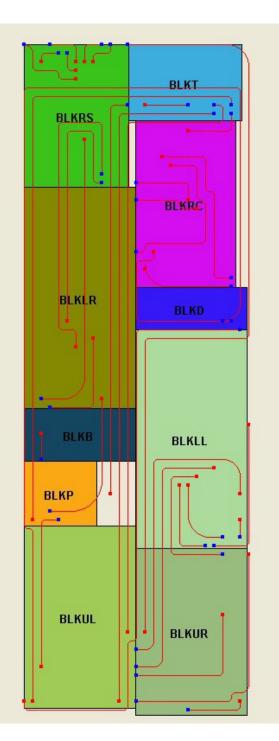

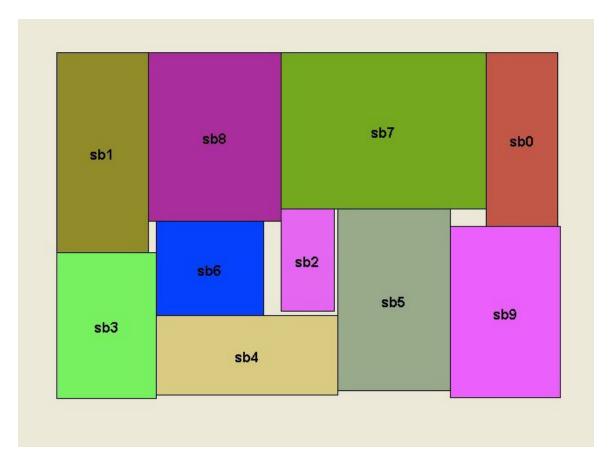

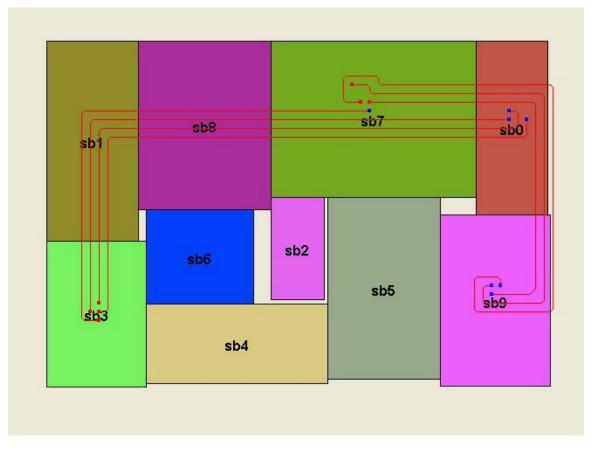

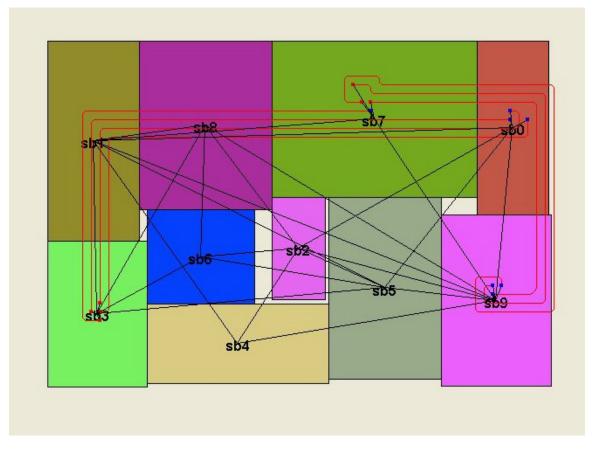

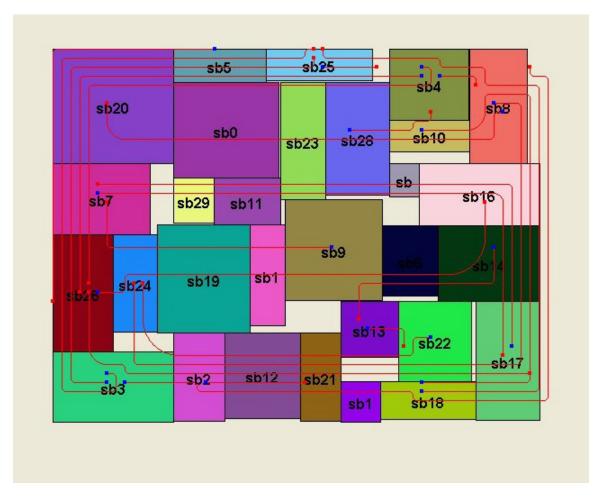

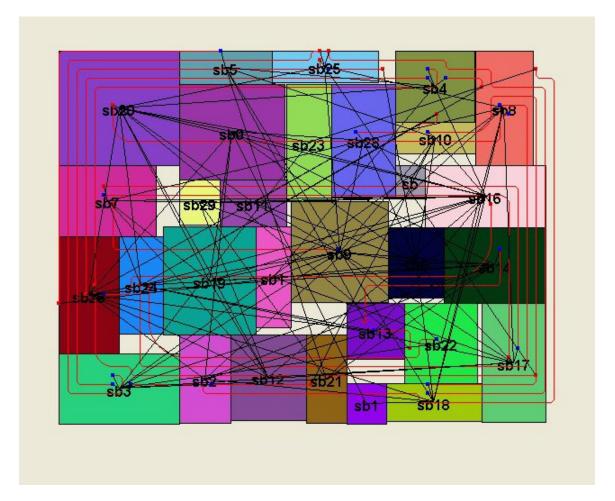

| Figure 53. Optimized placement for Ami33 benchmark circuit                                                                                                                                         | 104  |

| Figure 54. | Optimized placement and optical waveguide routing for Ami33 benchmark circuit                        |

|------------|------------------------------------------------------------------------------------------------------|

| Figure 55. | Optimized placement and both electrical and optical waveguide routing for<br>Ami33 benchmark circuit |

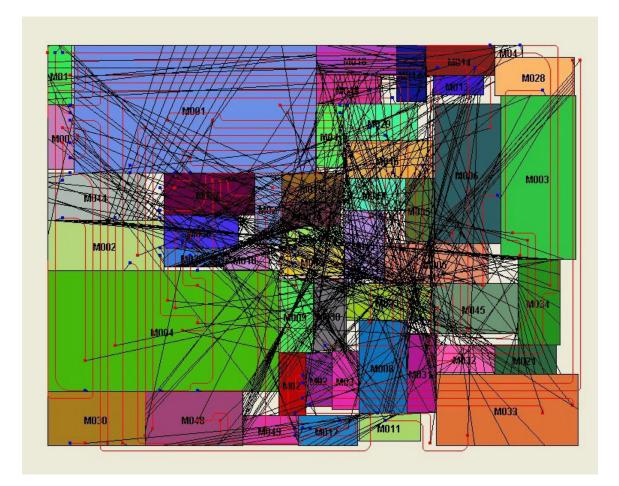

| Figure 56. | Optimized placement for Ami49 benchmark circuit 107                                                  |

| Figure 57. | Optimized placement and optical waveguide routing for Ami49 benchmark<br>circuit                     |

| Figure 58. | Optimized placement and both electrical and optical waveguide routing for<br>Ami49 benchmark circuit |

| Figure 59. | Optimized placement for Apte benchmark circuit 110                                                   |

| Figure 60. | Optimized placement and optical waveguide routing for Apte benchmark circuit                         |

| Figure 61. | Optimized placement and both electrical and optical waveguide routing for<br>Apte benchmark circuit  |

| Figure 62. | Optimized placement for Hp benchmark circuit 113                                                     |

| Figure 63. | Optimized placement and optical waveguide routing for Hp benchmark circuit                           |

| Figure 64. | Optimized placement and both electrical and optical waveguide routing for Hp benchmark circuit       |

| Figure 65. | Optimized placement for Xerox benchmark circuit 116                                                  |

| Figure 66. | Optimized placement and optical waveguide routing for Xerox benchmark circuit                        |

| Figure 67. | Optimized placement and both electrical and optical waveguide routing for<br>Xerox benchmark circuit |

| Figure 68. | Optimized placement for n10a benchmark circuit 124                                                   |

| Figure 69. | Optimized placement and optical waveguide routing for n10a benchmark circuit.                     | 125 |

|------------|---------------------------------------------------------------------------------------------------|-----|

| Figure 70. | Optimized placement and both electrical and optical waveguide routing for n10a benchmark circuit. | 126 |

| Figure 71. | Optimized placement for n10b benchmark circuit                                                    | 127 |

| Figure 72. | Optimized placement and optical waveguide routing for n10b benchmark circuit                      | 128 |

| Figure 73. | Optimized placement and both electrical and optical waveguide routing for n10b benchmark circuit  | 129 |

| Figure 74. | Optimized placement for n10c benchmark circuit                                                    | 130 |

| Figure 75. | Optimized placement and optical waveguide routing for n10c benchmark circuit                      | 131 |

| Figure 76. | Optimized placement and both electrical and optical waveguide routing for n10c benchmark circuit  | 132 |

| Figure 77. | Optimized placement for n30a benchmark circuit                                                    | 133 |

| Figure 78. | Optimized placement and optical waveguide routing for n30a benchmark circuit                      | 134 |

| Figure 79. | Optimized placement and both electrical and optical waveguide routing for n30a benchmark circuit  | 135 |

| Figure 80. | Optimized placement for n30b benchmark circuit                                                    | 136 |

| Figure 81. | Optimized placement and optical waveguide routing for n30b benchmark circuit                      |     |

| Figure 82. | Optimized placement and both electrical and optical waveguide routing for n30b benchmark circuit. | 138 |

| Figure 83. | Optimized placement for n30c benchmark circuit                                                    | 139 |

|            | Optimized placement and optical waveguide routing for n30c benchmark circuit                       | 140 |

|------------|----------------------------------------------------------------------------------------------------|-----|

|            | Optimized placement and both electrical and optical waveguide routing for n30c benchmark circuit.  | 141 |

| Figure 86. | Optimized placement for n50a benchmark circuit                                                     | 142 |

| -          | Optimized placement and optical waveguide routing for n50a benchmark circuit                       | 143 |

|            | Optimized placement and both electrical and optical waveguide routing for n50a benchmark circuit.  | 144 |

| Figure 89. | Optimized placement for n50b benchmark circuit                                                     | 145 |

|            | Optimized placement and optical waveguide routing for n50b benchmark circuit                       | 146 |

| -          | Optimized placement and both electrical and optical waveguide routing for n50b benchmark circuit.  | 147 |

| Figure 92. | Optimized placement for n50c benchmark circuit                                                     | 148 |

|            | Optimized placement and optical waveguide routing for n50c benchmark circuit                       | 149 |

| -          | Optimized placement and both electrical and optical waveguide routing for n50c benchmark circuit   | 150 |

| Figure 95. | Optimized placement for n100a benchmark circuit                                                    | 151 |

|            | Optimized placement and optical waveguide routing for n100a benchmark circuit                      |     |

|            | Optimized placement and both electrical and optical waveguide routing for n100a benchmark circuit. | 153 |

| Figure 98. | Optimized placement for n100b benchmark circuit                                                    | 154 |

|             | Optimized placement and optical waveguide routing for n100b benchmark<br>bircuit                  |

|-------------|---------------------------------------------------------------------------------------------------|

| Figure 100. | Optimized placement and both electrical and optical waveguide routing for n100b benchmark circuit |

| Figure 101. | Optimized placement for n100c benchmark circuit 157                                               |

| Figure 102. | Optimized placement and optical waveguide routing for n100c benchmark circuit                     |

| Figure 103. | Optimized placement and both electrical and optical waveguide routing for n100c benchmark circuit |

| Figure 104. | Optimized placement for n200a benchmark circuit 160                                               |

| Figure 105. | Optimized placement and optical waveguide routing for n200a benchmark circuit                     |

| Figure 106. | Optimized placement and both electrical and optical waveguide routing for n200a benchmark circuit |

| Figure 107. | Optimized placement for n200b benchmark circuit 163                                               |

| Figure 108. | Optimized placement and optical waveguide routing for n200b benchmark circuit                     |

| Figure 109. | Optimized placement and both electrical and optical waveguide routing for n200b benchmark circuit |

| Figure 110. | Optimized placement for n200c benchmark circuit 166                                               |

| Figure 111. | Optimized placement and optical waveguide routing for n200c benchmark circuit                     |

| Figure 112. | Optimized placement and both electrical and optical waveguide routing for n200c benchmark circuit |

| Figure 113. | Optimized placement for n300 benchmark circuit 169                                                |

| Figure 114. | Optimized placement and optical waveguide routing for n300 benchmark      |    |

|-------------|---------------------------------------------------------------------------|----|

|             | circuit                                                                   | 70 |

|             |                                                                           |    |

| Figure 115. | Optimized placement and both electrical and optical waveguide routing for |    |

|             | n300 benchmark circuit                                                    | 71 |

### **ABBREVIATIONS**

| CAD   | Computer-Aided Design, xii                              |  |

|-------|---------------------------------------------------------|--|

| MCNC  | Microelectronics Center of North Carolina, xvii         |  |

| GSRC  | Gigascale Systems Research Center, xvii                 |  |

| SoC   | System-on-a-Chip, 3                                     |  |

| SoP   | System-on-a-Package, 3                                  |  |

| NP    | Nondeterministic Polynomial, 4                          |  |

| VLSI  | Very Large Scale Integration, 6                         |  |

| VCSEL | Vertical Cavity Surface-Emitting Laser, 7               |  |

| MOSIS | Metal Oxide Semiconductor Implementation System, 7      |  |

| FSIM  | Free-Space Interconnected Module, 8                     |  |

| I/O   | Input and Output, 8                                     |  |

| MCM   | Multi-Chip Module, 8                                    |  |

| FSOI  | Free-Space Optical Interconnect, 8                      |  |

| SIA   | Semiconductor Industry Association, 9                   |  |

| BCB   | Benzocyclobutene, 11                                    |  |

| DSM   | Deep-Sub Micron, 15                                     |  |

| CMOS  | Complementary Metal Oxide Semiconductor, 20             |  |

| TE    | Transverse Electric, 61                                 |  |

| MOCS  | Method of Optical Centroid Searching, 62                |  |

| ITRS  | International Technology Roadmap for Semiconductors, 80 |  |

| EDA   | Electronic Design Automation, 81                        |  |

|       | Electronic metic Interference 01                        |  |

EMI Electromagnetic Interference, 81

### **SUMMARY**

Current electrical systems are faced with the limitation in performance by the electrical interconnect technology determining overall processing speed. In addition, the electrical interconnects containing many long distance interconnects require high power to drive. One of the best ways to overcome these bottlenecks is through the use of optical interconnect to limit interconnect latency and power.

This research explores new computer-aided design (CAD) algorithms for developing optoelectronic systems. These algorithms focus on place and route problems using optical interconnections covering system-on-a-chip design as well as system-on-apackage design. In order to design optoelectronic systems, optical interconnection models are developed at first. The CAD algorithms include optical interconnection models and solve place and route problems for optoelectronic systems. The microelectronics center of north Carolina (MCNC) and gigascale systems research center (GSRC) benchmark circuits are used to evaluate these algorithms.

### **CHAPTER 1**

### **INTRODUCTION**

Current electrical systems are faced with the limitation in performance by the electrical interconnect technology determining overall processing speed. In addition, the electrical interconnects containing many long distance interconnects require high power to drive. One of the best ways to overcome these bottlenecks is through the use of optical interconnect to limit interconnect latency and power.

In 2000, D. A. B. Miller codified the physical advantages of optical interconnect over electrical interconnect [1]. Some possible practical advantages of optical interconnects are described in below.

| Advantage                | Description                                    |

|--------------------------|------------------------------------------------|

| Design simplification    | No electromagnetic wave phenomena              |

|                          | • No distance and frequency dependence         |

| Architecture             | • Large numbers of long high-speed connections |

| Aremitecture             | • 2D interconnect architecture                 |

| Timing                   | • Predictable signal timing and no timing skew |

| Other physical advantage | Power savings                                  |

| other physical advantage | High interconnect density                      |

Table 1. Possible practical advantages of optical interconnects

Because of the above advantages, optical interconnects could increase overall performance of electrical packages, and reduce the crosstalk, power consumption and signal latency. Due to the lack of computer-aided design (CAD) algorithms/tools in optics, it necessitates the development of new CAD algorithms/tools for emerging technologies such as optical interconnect.

#### **1.1 Problem Statement**

This dissertation explores four issues, which are module placement, electrical and optical interconnect modeling, interconnection routing, and optimization algorithm.

#### **1.1.1 Module Placement**

Module placement is a crucial step in physical design cycle because it determines the performance of chips, boards or packages. A good placement provides less area and increases the performance [2].

Module placement problem is generally related to routing problem. However, a poor placement cannot be improved by high quality routing. Therefore, placement phase is a very critical step in physical design cycle.

The objective of module placement problem is to construct a layout which provides the locations of all blocks, routes all nets and minimizes the total layout area if given size of each fixed blocks and netlists. The detailed objective for designing high performance systems is to minimize the total delay of the system by minimizing the total lengths of the critical paths. It is usually performed by minimizing the length of the longest nets. This optimization is known as the *performance-driven placement optimization*.

#### 1.1.2 Interconnect Modeling

In this dissertation, routing phase has to be able to deal with both electrical and optical interconnects. It leads to a new problem which is when, where and how to use optical interconnects as a replacement of electrical interconnects. In order to identify the problem, a comparison model which satisfies the system requirement is required.

For the optoelectronic system-on-a-chip, free-space optical interconnect technology is adopted. To design and analyze the system-on-a-chip (SoC) performance, two comparison models are made in terms of speed performance and energy cost.

Optical waveguide interconnect technology is used to design the optoelectronic system-on-a-package (SoP). To design and analyze the system-on-a-package performance, a comparison model for signal delay time is made and a bending loss model is also made for minimizing the signal power loss in optical waveguide at bends.

#### 1.1.3 Interconnect Routing

After module placement phase, the exact location of module blocks and pins are determined. Using the region which is not occupied by the modules, nets are routed. This process is called *routing* [2].

The objective of the routing problem is to minimize the total interconnect length while using routing regions and completing all the interconnections. The interconnect routing should meet the timing budget of the systems.

Besides routing the interconnects among modules, special routing which is an optical clock routing is also explored in this dissertation.

#### 1.1.4 Optimization Algorithm

The place and route problems are optimization problems as known as a nondeterministicpolynomial (NP) problem. It translates that the problems cannot be solved with deterministic algorithms in polynomial time. Therefore, heuristic algorithm such as simulated annealing or genetic algorithm is used for solving the NP problems.

The problems of heuristic algorithm are the performance vs. the optimization time. Due to heuristic approach, the algorithms often converge to a local minimum which is far from the optimum solution. In order to avoid it, a modified algorithm is usually used.

The optimization time is also becoming a critical issue because the problem size is getting bigger and bigger nowadays. To meeting time-to-market, design time should be minimized. In physical design process, all the stages, partitioning, floorplanning, placement, global routing, detailed routing, compaction and verification, are iteratively performed until meeting the required specification of the system. Thus, the optimization time should be minimized while remaining the optimization performance.

#### **1.2 History of the problem**

In this section, the origin and history of both optical interconnect technology and place and route problem are presented.

#### **1.2.1 Optical Interconnection**

C. Chappe first invented the optical telegraph in 1791. This served as the starting point for optical communication systems. The fusion of optics and atomic physics began with J. Fraunhofer in 1818. N. Niepce invented photography in 1826 and C. Wheatstone invented stereoscopy in 1832 respectively and they are the first products of imaging systems. In 1870, J. Tyndall demonstrated that light could be guided in a water jet [3]. However, the idea of a communication system based on the propagation of light through circular dielectric waveguides was considered from the mid-1960s, albeit some theoretical studies were performed in the early years of the present century [3], [4].

The first optical data storage and retrieval system has been developed by J. L. Baird in 1925. In 1928, N. Bohr presented the development of quantum mechanics and the principle of wave-particle duality of light and matter. R. K. Luneburg identified the final mathematical identification of optics with electromagnetics in 1944. In 1948, D. Gabor invented holography [3].

During 1960s, the semiconductor diode laser had been developed. This was the starting point that tried to use optics in digital computation and led to the rapid

development of optical communication systems. As the conclusion of the first demonstration, optical devices could not substitute for transistors in general computing machines because they consumed too much power [5]. However, the ideas of optics for communication were conceived at that time. From the mid 1970s to the late 1980s, the optical switching was paid attention because optical switch could be much faster than any electrical transistor [6]. This is still valid because nonlinear optics can make logic devices much faster than any electrical devices. In the early 1980s, quantum well structures were enhanced and this led to further interest in semiconductor optical switching devices.

In 1984, J. W. Goodman proposed ideas of optical interconnection of very large scale integration (VLSI) electronics [7]: index-guided, unfocused free-space and focused free-space optical interconnect. In index-guided optical interconnect, two types of waveguides, optical fibers and optical waveguides integrated on a suitable substrate, can be used. The two optical interconnect technologies provide a compact and planar packaging of the global optical clock distribution without diffractive components. In unfocused free-space optical interconnect, the optical signals carrying the clock signals broadcast to the entire electronic chip. Because detectors are located in the same distance at the focal point of the lens, there is no clock skew. A focused free-space optical clock distribution uses a holographic optical element. The holographic optical element acts as a complex grating. They were the actual start of the field of optical interconnects.

The quantum-confined Stark effect was discovered in III-V semiconductor quantum wells in 1984 [8]. This effect was important for optical computing and optical

interconnects because of the allowance of low energy devices, the possibility of 2D interconnected modulator or switch and the capability of large arrays of devices. The very important devices, vertical cavity surface-emitting lasers (VCSELs), were developed [9] and demonstrated [10] in the late 1980s. The first demonstration which VCSEL was electrically pumped was successfully made at room temperature. VCSELs became very interested practical devices, especially for low-cost optical fiber connections. Moreover, they become candidate devices for optical interconnects to silicon chips.

In 1988, B. D. Clymer and J. W. Goodman presented the skew properties of an array of optical transimpedence receivers associated with a hologram-based focused free-space optical clock distribution [11]. The test circuit used 3µm Metal Oxide Semiconductor Implementation System (MOSIS) technology with 18 optical receivers.

P. J. Delfyett, et al, introduced the mode-locked operation of a semiconductor laser system as a jitterless timing source [12]. They demonstrated the optical clock distribution of 1024 separate ports utilizing optical fibers. The total accumulated timing jitter was less than 12ps.

An optomechanical configuration has been conceived [13] that is far less complex than any current approach in 1994. Implementing a Fourier-plane-based interconnect with an arbitrary degree of space variance, it comprises only two component aggregates requiring mutual alignment in free space. Connections among such free-space interconnected modules (FSIMs) are effected over waveguide ribbons in a natural fashion obeying the principles of hierarchical interconnections: all signals leave chips on the same physical transport medium, in this case through the optical array input and output (I/O) apertures to free-space modes. Use of a mechanically compliant medium (ribbons) decouples system scaling from free-space alignment requirements.

A prototype 3D optoelectronic neural network was implemented in 1994 [14]. It was composed of a 16-node input, 4-neuron hidden, and a single-neuron output layer. The prototype used high-speed optical interconnects for fan-out and mixed-signal VLSI circuits for fan-in. In 1997, S. P. Levitan, et al, developed "Chatoyant", a mixed-signal CAD tool for performing end-to-end system simulations of free space interconnection systems [15]. Chatoyant was able to analyze optical, electrical, and mechanical trade-offs. The prototype system for intra multi-chip module (MCM) interconnects was built in 1999 [16]. This system supported 48 independent free-space optical interconnect (FSOI) channels using 8 lasers and detectors. All chips were integrated on a ceramic substrate with three silicon chips.

A board-level free-space optical clock distribution system implemented with substrate mode hologram was presented by J. H. Yeh, et al in 1995 [17]. The system used an H-tree clock distribution to avoid clock skews. With 622MHz clock signal, 36ps of timing jitter and less than 10ps of clock skew were achieved.

In 1998, Y. Li, et al, reported board-level large bandwidth optical clock distributions with fanout of 128 on a printed circuit board using silica and polymer optical fibers [18]. The result showed the multi Gbps bandwidth capability.

A multi-GHz optical clock distribution on a Cray T-90 supercomputer multiprocessor board is presented in 1999 [19]. The optical clock signal is distributed to 48 fanout points on  $14.5 \times 27$  cm<sup>2</sup> printed wiring board through a polyimide optical waveguide organized as an H-tree structure.

M. Forbes, et al, presented three different types of approaches for optoelectronic interconnects between VLSI chips [20]: fibre-ribbons, planar waveguides and free-space optics. This paper pointed out the limitations of electrical interconnect and the advantages of optical interconnect.

The 2002 Semiconductor Industry Association (SIA) roadmap update [21] shows the substantial problems of electrical interconnects on silicon chips. Off-chip long distance interconnections suffer in performance. It is proposed to replace such interconnections with optical interconnect to mitigate specific interconnect performance issues.

Optical connections between individual computer systems are now available. N. Savage anticipated that optical interconnection would be introduced in the computer to connect circuit boards within 2-5 years [22] and connect chips within 5-10 years. Optical interconnects will be feasible in 15 years for on-chip interconnects.

#### **1.2.2 Place and Route**

In this dissertation, the place and route problem is considered as a combined problem. This approach has been researched and has produced some useful results. In 1983, M. Burstein and S. J. Hong presented a placement algorithm to interleave routing in a gate array system [23]. W. Dai and E. S. Kuh presented an algorithm for simultaneous floor planning and global routing for hierarchical building-block layout in 1987 [24]. P. R. Suaris and G. Kedem presented an algorithm for a quadrisection based combined place and route scheme for standard cell in 1989 [25]. In the same year, J. Cong presented an algorithm for pin assignment associated with global routing [26]. J. Rose developed a parallel global routing algorithm for standard cells which route multiple nets in parallel by relaxing data dependencies in 1990 [27].

In 1990, J. Garbers, *et al*, developed a hierarchical placement procedure based on routing and timing information [28]. This algorithm is based on min-cut method. After every cut which guides the subsequent cell partitioning, global routing and timing analysis is performed. In 1993, S. Sutanthavibul, E. Shargowitz and R. Lin presented an adaptive timing-driven placement for high performance VLSI chips [29]. J. Xu, P. Guo and C. Cheng presented an algorithm for cluster refinement for block placement in 1997 [30]. The algorithm is to minimize the chip size and interconnection wire length for mixed macro-cell and standard-cell. In 1997, C. J. Alpert, *et al*, revisited quadratic placement [31].

#### **1.3 Key Contributions**

The goal of this dissertation is to develop computer-aided design algorithms for optoelectronic systems utilizing optical interconnect technology. In order to achieve the

goal, the works are divided into four main parts, which are interconnection modeling, place and route, optical clock routing and adaptive optimization algorithm.

#### **1.3.1 Interconnection Modeling**

We have modeled two types of optical interconnects. Firstly, we modeled electrical interconnect and free-space optical interconnect in terms of speed performance and energy cost. Free-space optical interconnect uses VCSEL as an optical signal transmitter and shows the superiority to electrical interconnect. However, electrical interconnect is dominant if the interconnect length is less than 3cm from the energy cost point of view.

Secondly, we modeled optical waveguide interconnect in terms of power losses in optical waveguide at bends. The result of bending loss with specific fabrication parameters is curve-fitted with Boltzmann function to specify to our CAD tool. The parameters which are used in this dissertation are taken from a real fabrication parameter [32]. They are 1µm Benzocyclobutene (BCB) as a core layer, SiO<sub>2</sub> as a cladding layer, 1µm waveguide thickness and a wavelength of 1.3µm. The BCB index of refraction is 1.537 at a wavelength of 1.3µm and the SiO<sub>2</sub> index of refraction is 1.45 at a wavelength of 1.3µm [32]. The result is only for a single-mode operation. The analytical regression model for the bending loss of optical waveguide. It translates that the bending loss is negligible over 240µm bending radius. For the simulations, the minimum bending radius of optical waveguide is assumed to be 100µm.

The signal propagation speed in optical waveguide interconnect is dominant over one in electrical interconnect once the interconnect length is over 2.4cm.

#### **1.3.2 Place and Route**

A new approach to designing high performance optoelectronic SoC utilizing free-space optical interconnect and SoP utilizing optical waveguide interconnect is developed.

The results for optoelectronic SoC show that more than 55% improvement in overall SoC speed and more than 11% saving in total energy consumption are obtained through the optimization process with the use of free-space optical interconnects. This translates to improve the overall SoC performance by a factor of over 1.5.

The result for optoelectronic SoP shows that more than 21% improvement in SoP performance is obtained through the use of optical waveguide interconnects.

#### **1.3.3 Optical Clock Routing**

Optical clock distribution network eliminates the disadvantages of electrical clock distribution such as clock skew, timing jitter, etc. Moreover, it allows no limitations on the maximum frequency of modulation of an optical signal.

We presented a new approach to optimized clock routing using optical waveguide. The results are very encouraging and show that less than 26.1psec in signal timing skew is obtained for a signal flight time of 614.38psec. This translates that the signal timing skew can be neglected (< 4%). For optical power consumption, about 15% reduction is also obtained over clock nets routed with existing (optical) methods.

#### **1.3.4 Hybrid Optimization**

In this dissertation, two types of optimization algorithms were used for simultaneous place and route, which are a genetic algorithm and a simulated annealing to compare the performance of optimization due to the parameter size of optimization problem. As a result, a genetic algorithm is faster than simulated annealing even though the optimization performance of simulated annealing is slightly better than that of a genetic algorithm.

Therefore, in order to increase the optimization performance of a genetic algorithm, we applied two more different variations to a genetic algorithm. The first one is called "Steady-state genetic algorithm." It is basically producing better children in the next generation. Therefore, if the children are not better than their parents, the children should be then discarded in the next population.

The second one is called "Hybrid genetic algorithm." It adopted "Force-directed algorithm" to crossover function in a genetic algorithm. Force-directed algorithm models the input graph as a system of forces and tries to find a minimum energy configuration of this system. Even though this hybrid genetic algorithm is much faster than a generational genetic algorithm, however, it converges to a local minimum in some cases.

#### **1.4 Summary of Dissertation**

The next six chapters of this dissertation discuss the models for comparison of electrical and optical interconnects and the CAD algorithms to optimizing both module placement and routing of electrical and optical interconnects using the optical interconnect models. Chapter 2 presents comparison models between electrical and optical interconnects in terms of speed performance and energy cost. Using the comparison models, chapter 3 presents CAD algorithms to design optoelectronic system-on-a-chip utilizing free-space optical interconnects. Chapter 4 presents a power loss model for optical waveguide interconnects. Chapter 5 presents new CAD algorithms to design optical clock distribution network using optical waveguide interconnect technology. Chapter 6 presents CAD algorithms to design optoelectronic system-on-a-package using optical waveguide interconnect technology. The final chapter, Chapter 7, summarizes the results of this dissertation and discusses future work. The appendix provides the results of Chapter 6 with GSRC benchmark circuits.

### **CHAPTER 2**

# MODELING OF FREE-SPACE OPTICAL INTERCONNECT

#### **2.1 Introduction**

VLSI feature size scaling is now up to deep-sub micron (DSM). As the scaling technology has been developed, it has brought unexpected phenomena, such as intolerable wire resistance and capacitance, skin effect, ground bounce, etc. As a result, long electrical interconnects become the key issues for determining the performance of VLSI systems. In order to overcome these bottlenecks, a new technology has been sought for several decades and optical interconnect technology has been suggested as a substitution technology for long electrical interconnection.

However, optical interconnect technology has its own limitations, such as requirement of additional components, which are optical signal transmitter and receiver, signal transformation cost from electrical to optical and voltage incompatibility. Therefore, it is required that identifies the superiority between electrical and optical interconnects and determines which technology should use where. There are lots of efforts that try to identify the superiority of optical interconnection as a substitution of electrical interconnection. In 1988, M. R. Feldman, *et al*, presented the comparison between optical and electrical interconnects based on power and speed consideration. G. I. Yayla, *et al*, reported a similar analysis, but expanded analysis in many ways about ten years later [34]. This chapter presents a comparison model between electrical and optical interconnects in terms of speed performance and energy cost using G. I. Yayla's circuit models.

#### 2.2 Interconnect Models

Basically, both an electrical and an optical interconnects are composed of three main parts which are a transmitter, a signal transmission medium and a receiver. Figure 1 shows the off-chip electrical interconnection scheme with a fan-out of N. The model consists of a transmitter chip which is followed by a superbuffer, the off-chip conductor, the receiver chips along the conductor and a parallel termination resistor  $R_T$ .

Figure 1. Model of off-chip electrical interconnection with fan-out

In this chapter, free-space optical interconnect technology is only considered. The optical signal is traveling through the air. It translates that only the optical signal transmitter and the optical signal receiver should be modeled because the refractive index in the air is almost 1.

The integration configuration for free-space optical substrate module is shown in Figure 2. On the silicon substrate, VCSEL and photodetector array is bonded based upon flip-chip technology. On the optical substrate, there is a microoptical substrate which carries focal-plane diffractive elements.

Figure 2. Integration configuration for free-space optical substrate module

In this research, VCSEL is considered as an optical signal transmitter. The optical signal transmitter model includes a transmitter, a transmitter driver and a superbuffer and is shown in Figure 3.

Figure 3. Model of an optical signal transmitter

Figure 4 shows the optical signal receiver model. The model consists of a photodiode, a thresholding current source, clamping diodes and an inverter. The clamping diodes limit the voltage swing and an inverter amplifies the photodiode output signal and restores the logic.

Figure 4. Model of an optical signal receiver

However, there are several assumptions to allow to use the above interconnect models.

• Interconnect length and fan-out are considered as independent variables.

- Large-scale digital computing systems using dense interconnections are only considered.

- Analog fan-in is not considered.

- Synchronous communication is assumed as the communication protocol.

- Static complementary metal oxide semiconductor (CMOS) logic design with rail-to-rail voltage swings is assumed.

- The scaling analysis of VLSI technology is not included, but 0.5 micron CMOS technology is used.

- Non-return to zero type of communication is assumed.

- A photodiode output voltage swing of 330mV is assumed, which is approximately equal to the transition width of a CMOS inverter transfer characteristic for 3.3V power supply voltage in 0.5µm CMOS.

- The interconnection conductor is assumed to be lossless.

## 2.3 Speed Performance Model

Using the above interconnect models, G. I. Yayla, *et al*, reported comparison results between electrical interconnect and free-space optical interconnect in 1998 from the speed performance and energy cost point of view. From the comparison results, the speed performance of both off-chip electrical interconnections and free-space optical interconnections are extracted and compared. Figure 5 shows interconnect length versus speed performance for electrical and optical interconnect obtained through regression

modeling using the exponential decay function, which produces exponential curve. The comparison models were obtained from G. I. Yayla's paper.

Figure 5. Regression models for speed performance

According to the above graph, optical interconnect is always dominant over electrical interconnect from the speed performance point of view.

The speed regression model is expressed by,

$$Speed = a + b \cdot e^{-x/c} \tag{1}$$

The coefficients of the models are shown in Table 2.

| Coefficient | а      | Ь       | С    |

|-------------|--------|---------|------|

| Optical     | 557.56 | 1952.58 | 6.23 |

| Electrical  | 393.19 | 693.82  | 9.70 |

Table 2. Coefficients for speed regression model

The CAD tool, which will be introduced in chapter 3, can accommodate any prescribed model for speed performance of electrical versus optical interconnect. Cases where optical sensor delays dominate the performance of optical interconnect can easily be accommodated into the proposed CAD framework.

# 2.4 Energy Cost Model

The original comparison data of the energy cost for both electrical and optical interconnects is obtained from G. I. Yayla's paper. The comparison data were curve-fitted by polynomial function, which produces cubic curve.

The results are shown in Figure 6.

Figure 6. Regression models for energy consumption

Figure 6 reveals that optical interconnect is superior to electrical interconnect if interconnect length is longer than 3cm. Thus, the CAD algorithm does not replace electrical interconnect with optical interconnect if the interconnect length is shorter than 3cm.

The energy cost model can be written as,

$$Energy = a + bx + cx^2 + dx^3$$

(2)

The coefficients of the models are shown in Table 3.

| Coefficient | а      | Ь     | С     | d     |

|-------------|--------|-------|-------|-------|

| Optical     | 21.93  | 1.77  | -0.03 | 0.001 |

| Electrical  | -27.56 | 22.84 | -1.28 | 0.032 |

Table 3. Coefficients for energy regression model

# 2.5 Summary

In this chapter, we have modeled electrical interconnect and free-space optical interconnect in terms of speed performance and energy cost. Free-space optical interconnect uses VCSEL as an optical signal transmitter and shows the superiority to electrical interconnect. However, electrical interconnect is dominant if the interconnect length is less than 3cm from the energy cost point of view.

Even though G. I. Yayla's models rather have several limitations and out-of date, but the models presents very broad comparison models between electrical and free-space optical interconnects.

In the next chapter, a new approach to designing optoelectronic system-on-a-chip using the speed performance and energy cost models will be presented.

# **CHAPTER 3**

# DESIGN OF SYSTEM-ON-A-CHIP USING FREE-SPACE OPTICAL INTERCONNECT

Flexible free-space optical interconnect architectures are currently being developed for low latency, low power, interconnection among on-chip, off-chip processor and memory elements to facilitate implementation of multi GHz clock multiprocessor. This requires replacing interconnects longer than a few *mm* with optical links based on Vertical Cavity Surface-Emitting Laser (VCSEL), resulting in minimized latency and reduced power and volume [13].

In this chapter, we propose a new gigascale optoelectronic system-on-a-chip architecture utilizing free-space optical interconnect technology and develop computeraided design (CAD) algorithms to achieve maximal use of on-chip electrical and optical interconnect resources by optimal assignment of a subset of nets to free-space optical interconnections.

### **3.1 Introduction**

At high speeds, electrical interconnections suffer from the problems of capacitive loading, mutual crosstalk, reflection, switching noise, clock skew, power consumption,

timing jitter, etc. In contrast, optical interconnections offer advantages such as high bandwidth, negligible mutual crosstalk, high speed, low power consumption, low timing jitter, etc. The use of optical interconnects is expected to increase packaging densities, interconnection bandwidth and chip speeds, and reduce crosstalk, power and chip latency.

In 1984, J. W. Goodman proposed optical interconnection of very large scale integration (VLSI) electronics [7]: intra-chip data communications and inter-chip data communications. They were the actual start of the field of optical interconnects. A prototype 3D optoelectronic neural network was implemented in 1994 [14]. It was composed of a 16-node input, 4-neuron hidden, and a single-neuron output layer. The prototype used high-speed optical interconnects for fan-out and mixed-signal VLSI circuits for fan-in. In 1997, S. P. Levitan, et al, developed "Chatoyant", a mixed-signal CAD tool for performing end-to-end system simulations of free space interconnection systems [15]. Chatoyant was able to analyze optical, electrical, and mechanical trade-offs. The prototype system for intra MCM interconnects (FSOI) channels using 8 lasers and detectors. All chips were integrated on a ceramic substrate with three silicon chips.

M. Forbes, et al, presented three different types of approaches for optoelectronic interconnects between VLSI chips [20]: fibre-ribbons, planar waveguides and free-space optics. This paper points out the limitations of electrical interconnect and the advantages of optical interconnect.

The 2002 Semiconductor Industry Association (SIA) roadmap update [21] shows the substantial problems associated with electrical interconnects on silicon chips. Offchip long distance interconnections suffer in performance. It is proposed to replace such interconnections with optical interconnect to mitigate specific interconnect performance issues.

Optical connections between individual computer systems are now available. N. Savage anticipated that optical interconnection would be introduced in computers to connect circuit boards within 2-5 years [22] and connect chips within 5-10 years. Optical interconnects will be feasible in 15 years for on-chip interconnects.

In this chapter, we introduce GOETHE (Generic Opto-Electronic system design THEurgist), a CAD tool for physical placement and routing of interconnections in System-on-a-Chip (SoC) utilizing free-space optical interconnect technology.

GOETHE determines which of the interconnects are routed electrically and which are routed optically without exceeding the routing capacity of the optical interconnect while minimizing total electrical interconnect length. Free-space optical interconnect technology is suitable for routing on-chip interconnects using an optical interconnect layer [7]. Data throughput between modules could be enhanced through the use of freespace optical interconnect by a factor of a thousand [22]. This research discusses the design of the circuit on silicon substrate and its interaction with the optical substrate and the architecture of SoC interconnection with free-space optical substrate that is discussed in this chapter is shown in Figure 7.

Figure 7. Optomechanical configuration in the neighborhood of the substrate.

# 3.2 Assumption

All module shapes are assumed to be rectangular-shaped. Pins are assigned into module periphery. A set of netlists are generated randomly for a specified number of modules. It is also assumed that the SoC operations are pipelined and that all module data transfers are buffered.

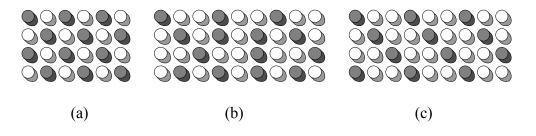

In this chapter, three arrangements of optical sensors are considered (see Figure 8). The gray circles represent transmitters and the white circles represent receivers.

**Figure 8. Three different sensor arrangements**

In the horizontal and vertical directions, the patterns of Figure 8 are repeated up to the size of a SoC. However, any regular sensor arrangements of transmitter-receiver configurations can be specified as an input to GOETHE. Therefore, it is possible to experiment with different sensor arrangements of transmitter-receiver configurations so that determines which gives the best performance.

# **3.3 Optimization Algorithms**

The optimization goals are as follows:

- *Given*: The preliminary locations of all modules and netlists and the arrangements of optical sensors in the VCSEL array.

- Determine: The optimal placement of all modules.

• *Such that (optimization criteria)*: (a) total electrical interconnect length is minimized and (b) the utilization of the optical routing capacity is maximized.

The optimization algorithm consists of a *placement and routing* and a *module compaction* step. These are described in Section 3.3.1 and 3.3.3.

#### 3.3.1 Placement and Routing

*Genetic Algorithm* is employed in order to optimize placement of modules and routing of electrical and optical interconnects simultaneously. There are three steps to find the best placement of modules which gives minimum routing cost.

First of all, *population* is generated as a group of many random orders of modules. The number of populations is one of the inputs to GOETHE. These orders are stored as a sequence of numbers. Second, two better groups which are called parents in the population and combine them to create two new solutions which are called children using *Crossover*. During crossover, a random point is picked in the parents' sequences and switched every number in the sequence after that point. When the placement of modules is changed, the sequence of the longest interconnects is also changed. However, the crossover sometimes may not work because the population is represented by a sequence of numbers. An example is shown below [35].

| Parent 1 | 1 2 3 4 5 <u>6 7 8 9</u> |

|----------|--------------------------|

| Parent 2 | 87632 <u>5491</u>        |

| Child 1  | 1 2 3 4 5 <u>5 4 9 1</u> |

| Child 2  | 87632 <u>6789</u>        |

Figure 9. An example that crossover operation does not work

To resolve this phenomenon, *partially matched crossover* is employed which is shown in Figure 10.

| Parent 1 | 1 <u>2 3 4 5</u> 6 7 8 9 |

|----------|--------------------------|

| Parent 2 | 876 <u>3254</u> 91       |

| Child 1  | 1 <u>3 2 5 4</u> 6 9 8 7 |

| Child 2  | 876 <u>2345</u> 91       |

Figure 10. Partially matched crossover

Finally, modules are rotated to random orientation during *Mutation*.

The above operations may not reproduce good parents to better children. Therefore, if the children are not better than their parents, the children should be then discarded in the population. This decision is made by total routing cost (see Figure 14).

The algorithm attempts to replace long electrical interconnects with optical interconnects in the sequence of interconnect length. However, the breakpoint which electrical interconnect can be replaced with optical interconnect should be determined because electrical interconnects is still dominant over optical interconnects for very short distance interconnect (< 3cm). It is described in Chapter 2.

The following operations are the overall goals of the optimization.

- Maximization of the utilization of the optical routing capacity.

- Minimization of the length of the critical (longest) electrical interconnects.

- Minimization of the total electrical interconnect length.

If an input port of one module is to be routed to an output port of another module optically, then the input port and the output port must first be routed electrically to the nearest receiver and transmitter respectively. The cost of routings electrically from I/O ports to the sensors is included in the total cost of the electrical interconnect routing.

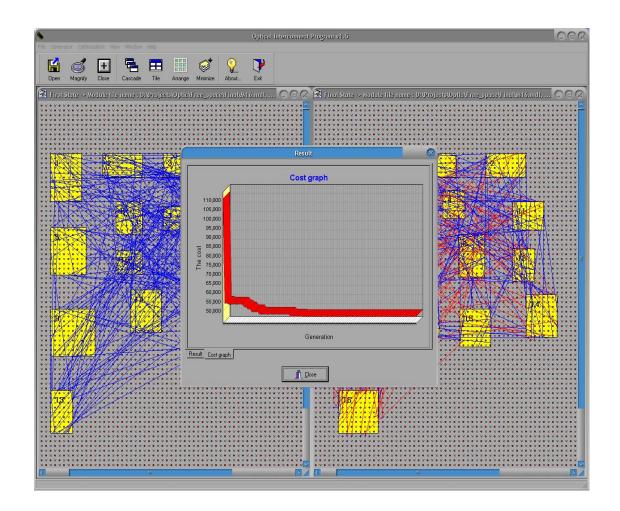

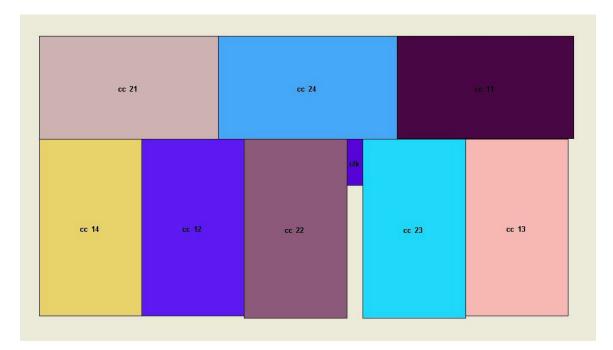

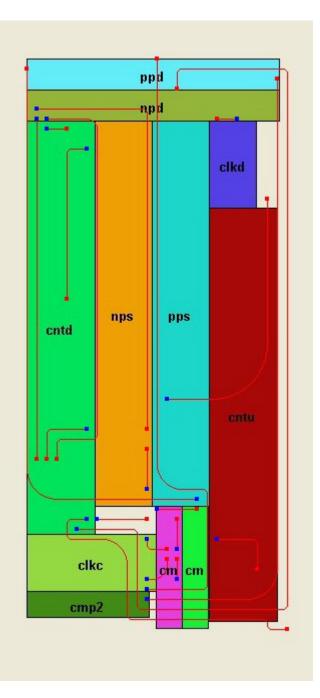

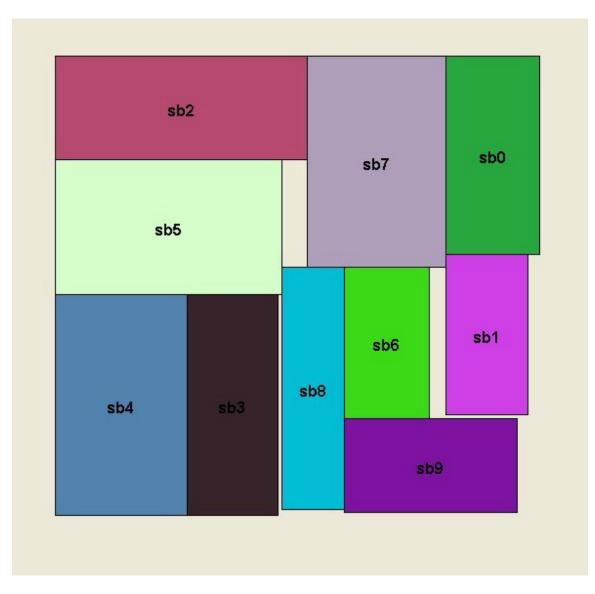

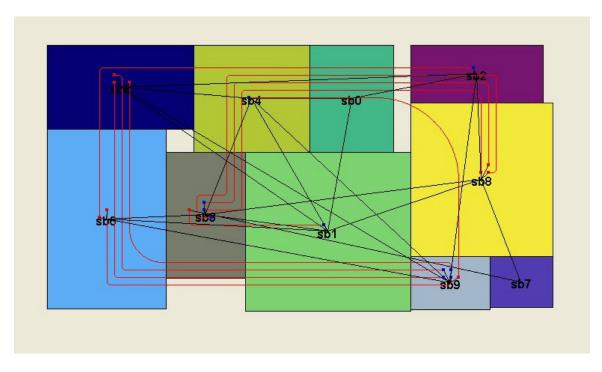

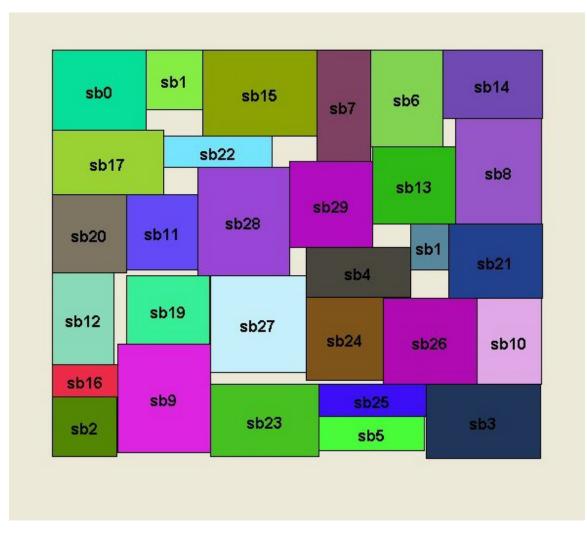

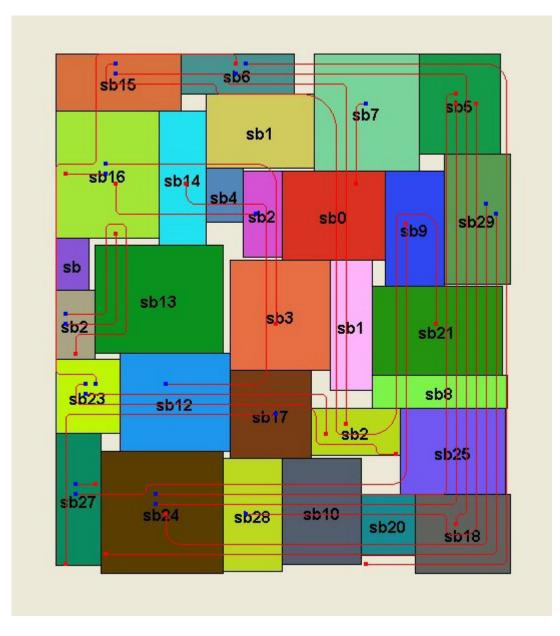

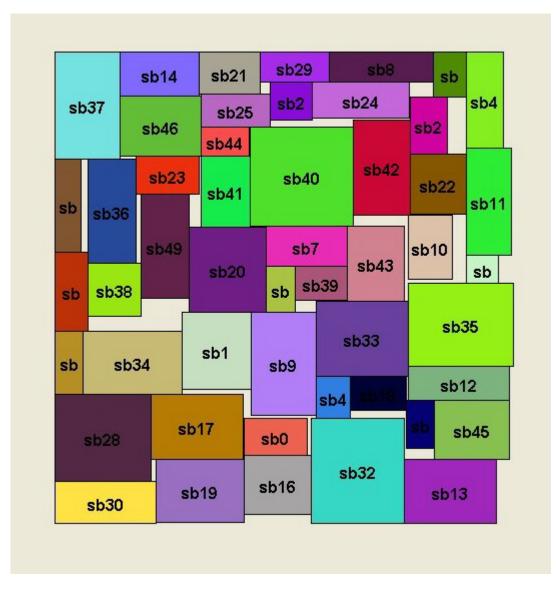

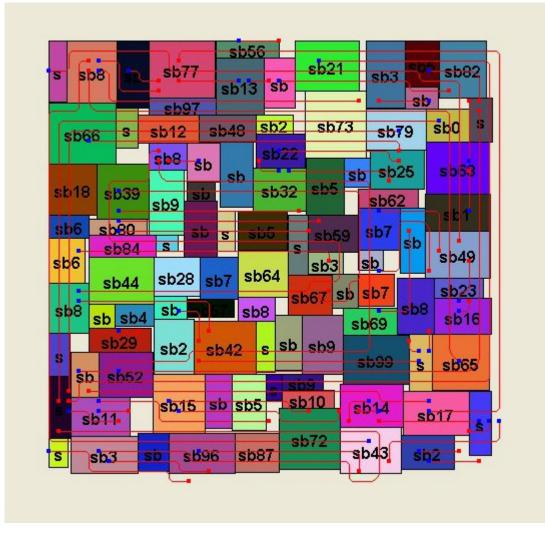

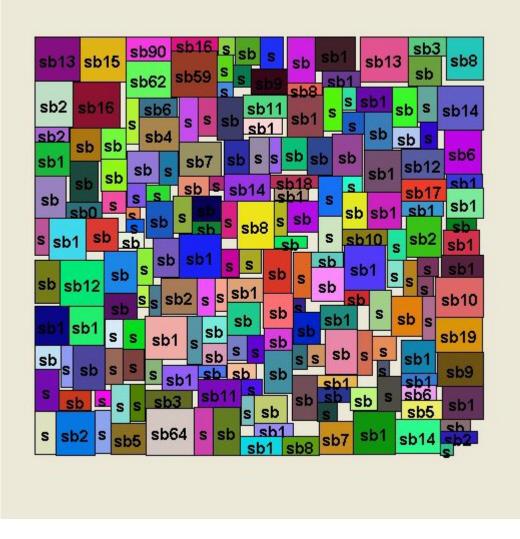

Figure 11 shows GOETHE layout after the optimization with 16 modules. The right window layout is an optimized layout of the one shown in the left window.

Figure 11. GOETHE layout with optimization

# 3.3.2 Optical Routing Capacity

The physical length of optical interconnect does not matter. This is different from electrical interconnects. The optical routing capacity is determined by the number of

optical directions in which signals have to be routed [13]. It turns out that due to the manner in which the diffraction grating of Figure 2 is fabricated, the optical routing capacity depends upon the number of optical directions rather than upon the number of physical routings of optical interconnects. Thereby, the number of optical directions that the optical substrate can support is one of the inputs to the optimization tool, GOETHE.

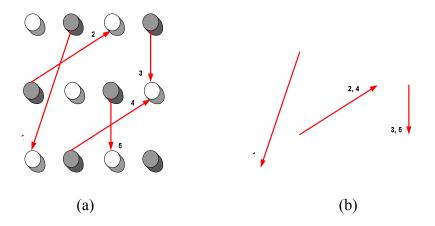

Figure 12(a) shows the physical routing of signals in the optical substrate. The gray circles represent transmitters and the white circles represent receivers. Figure 12(b) shows optical vectors that the routing configuration of Figure 12(a) reduces to. All parallel optical directions in Figure 12(a) trim down to a single optical vector in Figure 12(b).

**Figure 12. Optical vectors in Fourier plane**

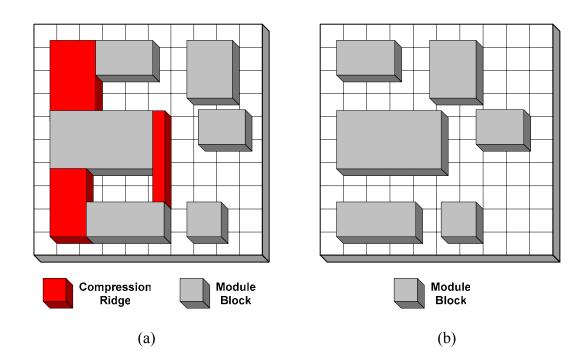

### **3.3.3 Module Compaction**

The regions between modules are called *channels*. At the beginning of the optimization process, GOETHE places modules with distance of wiring capacity. Then, virtual vertical direction lines are placed in the channels. The number of horizontal electrical interconnects crossing the vertical direction line for each channel is calculated. From this calculation, a difference between the wiring capacity and the wiring density which we call *Ridge*, is formed. The *Compression-Ridge method* is applied to delete the Ridge region [2]. This method is consecutively introduced in the horizontal direction.

Figure 13. Compression-Ridge Method

#### 3.3.4 Cost Function

The cost function for the optimization is described in Figure 14. It is composed of the electrical interconnect cost and the optical interconnect cost. The first term includes the electrical interconnect length due to all the electrical interconnect plus the interconnect length contributions due to the electrical interconnects to all transmitters and receivers which are occupied by optical interconnects. *Manhattan distance* is employed to calculate the electrical interconnect length.

$$Cost = \sum \left( Electrical \ interconnect \ length \right) + w \left( 1 - \frac{v}{D} \right)$$

where

$$\begin{cases} w = \text{Weight factor for optical cost} \\ v = \text{The number of optical vectors in current layout} \\ D = \text{The maximum number of optical directions} \\ \text{that the optical substrate can accommodate} \end{cases}$$

#### **Figure 14. The cost function**

The second term represents the optical interconnect cost. It attempts to minimize the unutilization of the optical routing capacity – note that at each step of the algorithm the longest interconnects are replaced with optical interconnect. w is the weight factor for the optical cost and is set to be 100 in this research. It turns out that the optical cost is the percentage of the unutilization of the optical routing capacity.

# 3.3.5 Pseudo Code for Optimizer

The pseudo code for a genetic algorithm [37] with the objective of minimizing the total routing cost in a SoC is as follows:

| Algorithm 3.1. Genetic Algorithm                                           |  |  |  |  |

|----------------------------------------------------------------------------|--|--|--|--|

| 1. Generate modules and netlists;                                          |  |  |  |  |

| 2. Generate population; // Section 3.3.1                                   |  |  |  |  |

| 3. Set the generation number;                                              |  |  |  |  |

| 4. for (each generation) {                                                 |  |  |  |  |

| 5. Partially matched crossover; // Section 3.3.1 – Swap modules            |  |  |  |  |

| 6. Module compaction; // Section 3.3.3 - Find the optimal module placement |  |  |  |  |

| 7. Mutation; // Section 3.3.1 - Rotate modules                             |  |  |  |  |

| 8. Module compaction; // Section 3.3.3 - Find the optimal module placement |  |  |  |  |

| 9. Evolution; // Section 3.3.4 - Optimize the total routing cost           |  |  |  |  |

| 10. }                                                                      |  |  |  |  |

| 11. Calculate speed improvement; // Section 2.3                            |  |  |  |  |

| 12. Calculate energy saving; // Section 2.4                                |  |  |  |  |

| 13. Save result files;                                                     |  |  |  |  |

### Figure 15. Pseudo code for genetic optimizer

During evolution, the algorithm makes total cost minimal.

# 3.4 Results and Analysis

In this section, we present experimental results of the optimization achieved by using GOETHE. All algorithms are implemented in C++.

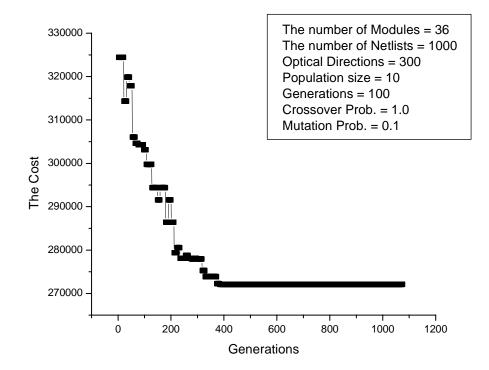

# 3.4.1 A Simulation Result

As mentioned in Section 3.2, a set of netlists was generated randomly for a specified number of modules. For comparison of overall SoC performance, cases with 9, 16, 25, 36 and 49 modules were simulated and a case of 36 modules is shown in this section. For the all simulations, the dimension of SoCs is set to be  $10 \times 10$ cm<sup>2</sup>.

Figure 16 shows the graph for the cost reduction versus the number of generations of the genetic optimizer with 36 modules and 1000 netlists. In this simulation, the optical routing capacity was 300.

Figure 16. The cost graph

The result shows about 20% saving in the electrical cost which is given in Figure 14. About 99.7% of optical routing capacity is occupied.

Table 4 shows reductions in interconnect length for the different sensor distributions of Figure 8 with 36 modules and 1000 netlists. For the simulations, optical routing capacity was 500.

| Arrangement | % of wires converted | % reduction in      | % reduction   | No. of optical |

|-------------|----------------------|---------------------|---------------|----------------|

|             | to optical links     | longest wire length | of total cost | directions     |

| (a)         | 50                   | 60                  | 69            | 495            |

| (b)         | 48                   | 52                  | 65            | 475            |

| (c)         | 43                   | 47                  | 62            | 428            |

Table 4. Comparison with different sensor distributions

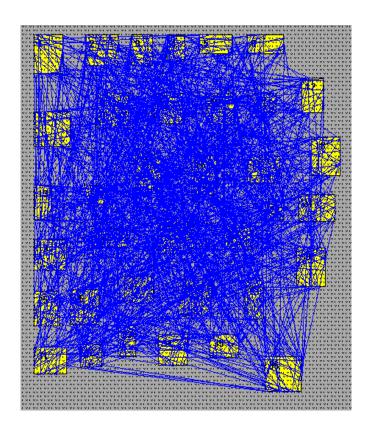

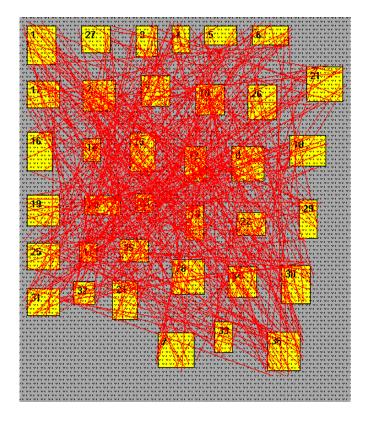

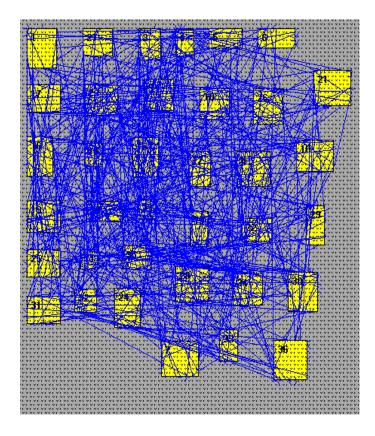

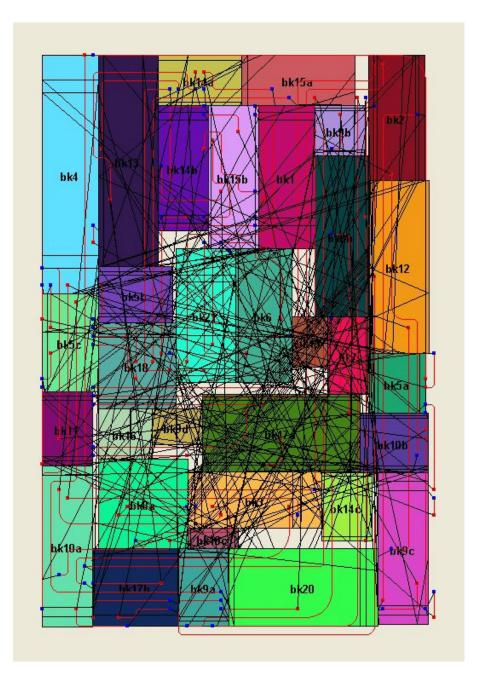

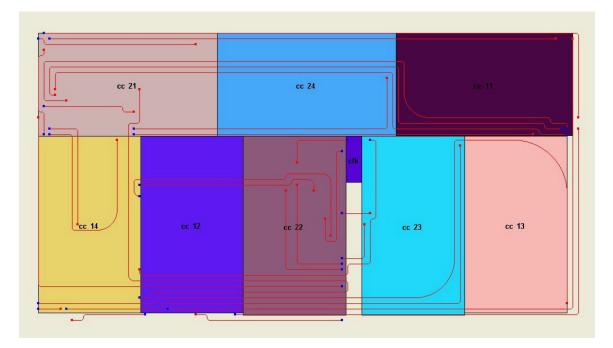

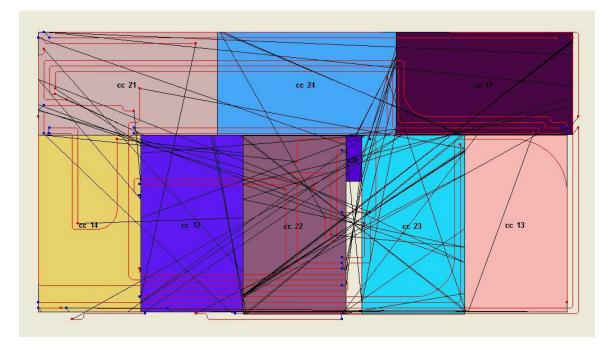

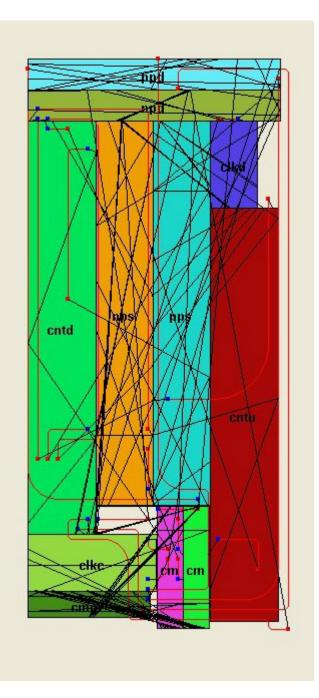

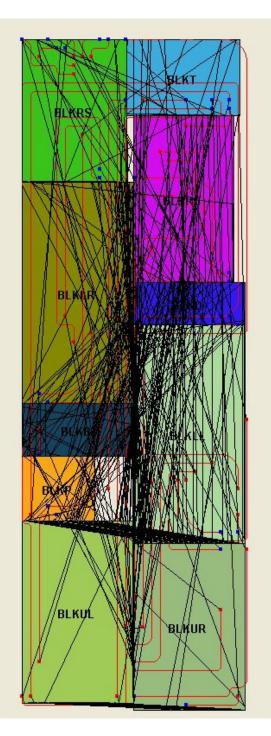

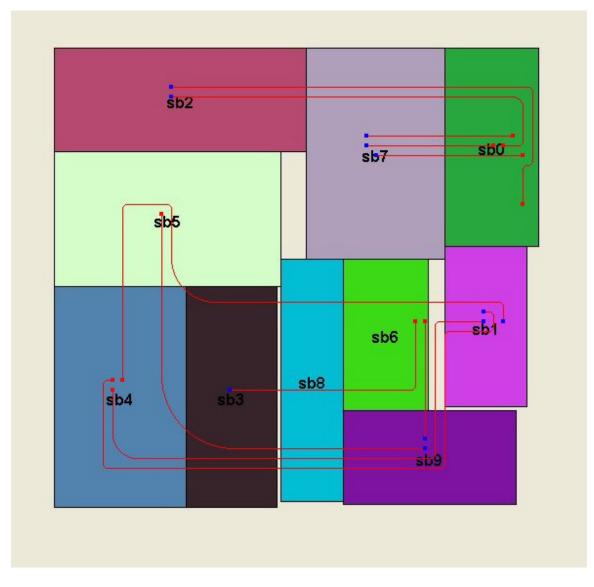

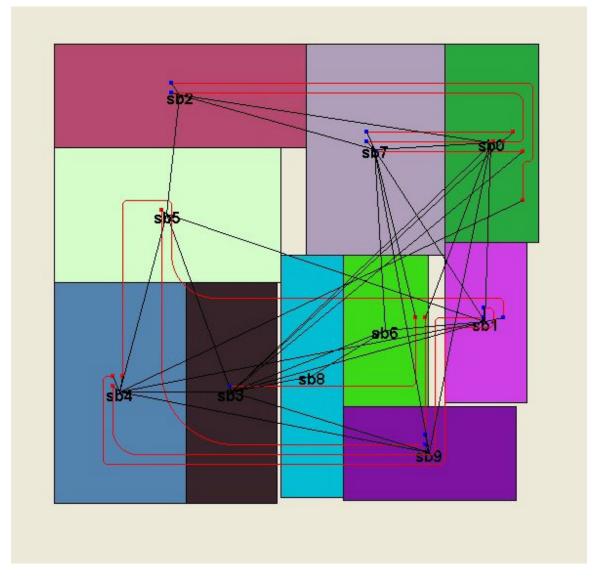

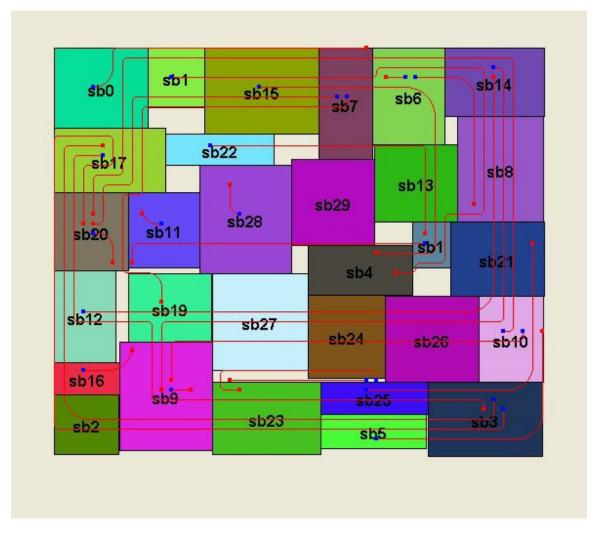

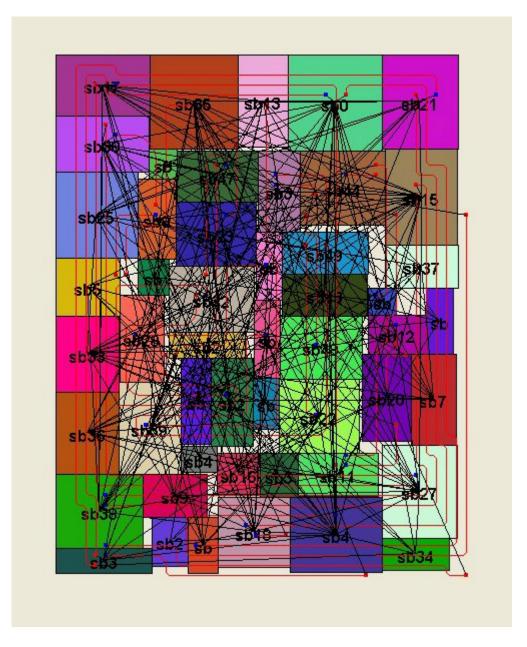

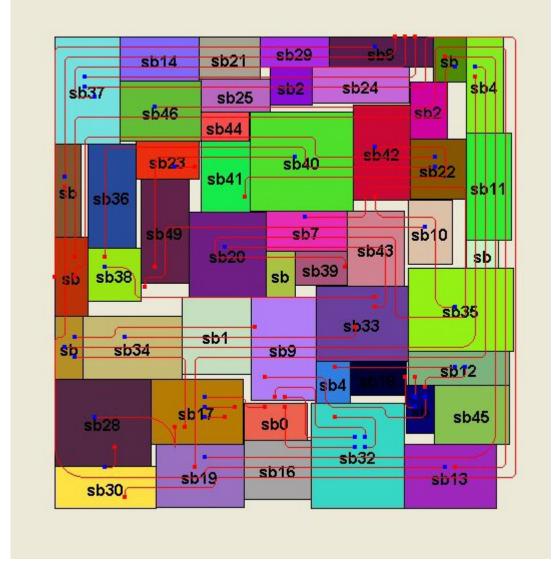

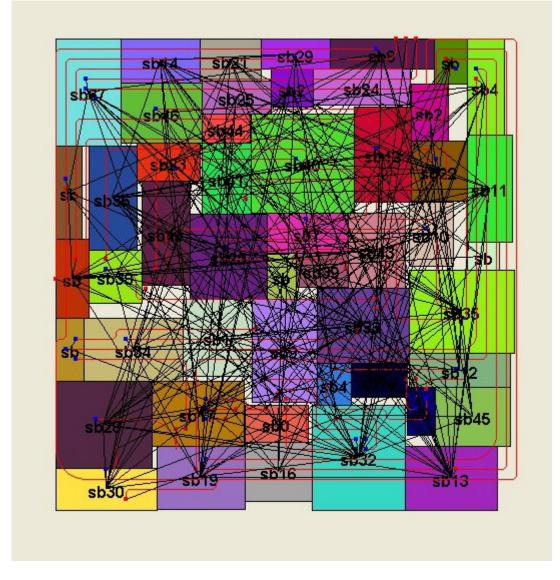

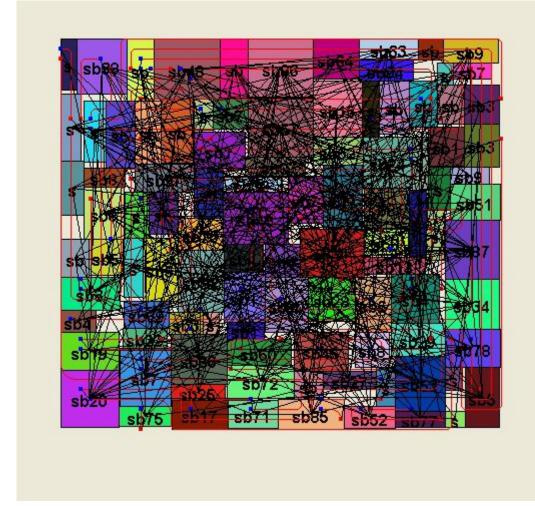

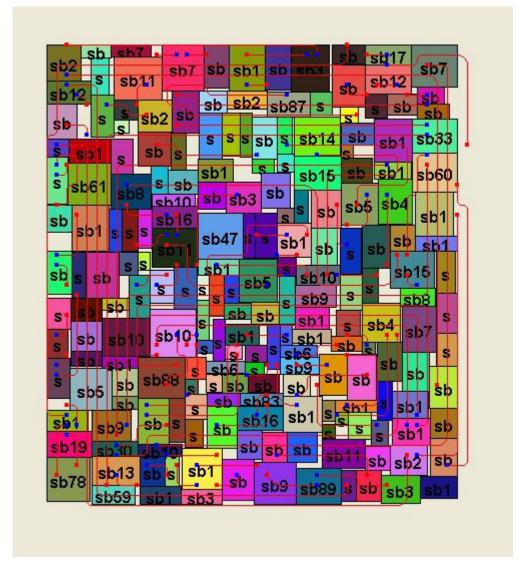

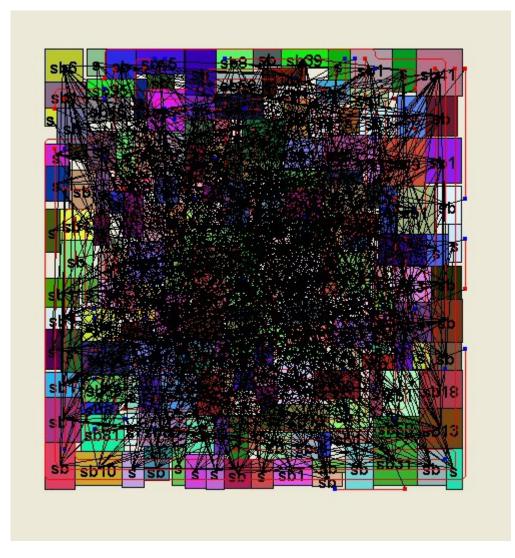

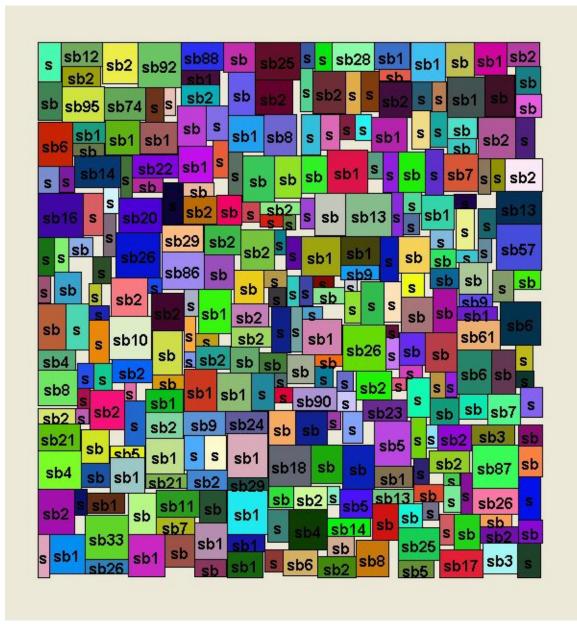

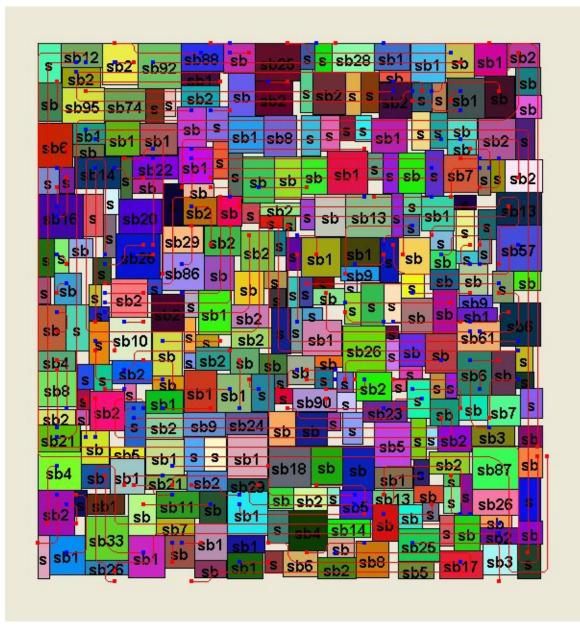

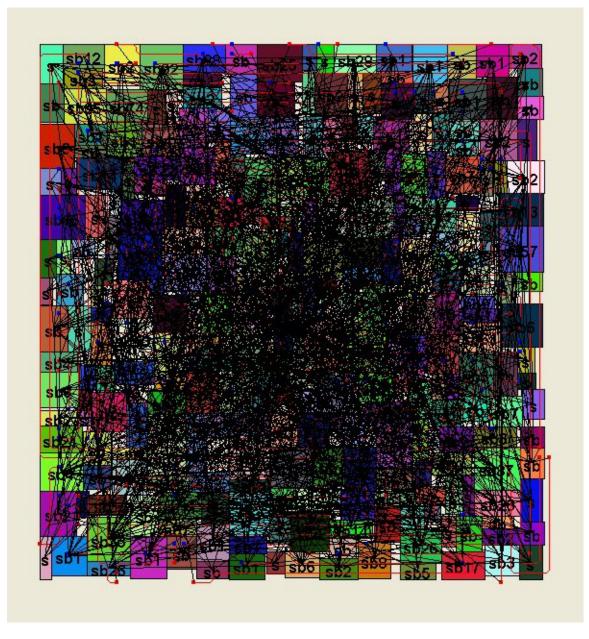

Figure 17, Figure 18 and Figure 19 show an example of the optimization performed by GOETHE. The blue lines represent electrical interconnects and the red lines represent optical interconnects. Figure 17 shows a layout and description of all the interconnects at the beginning of the optimization process.

Figure 17. Placement and routing before optimization

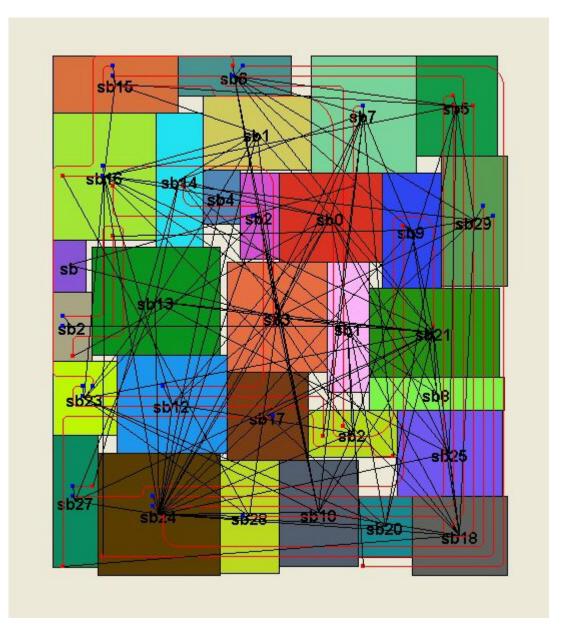

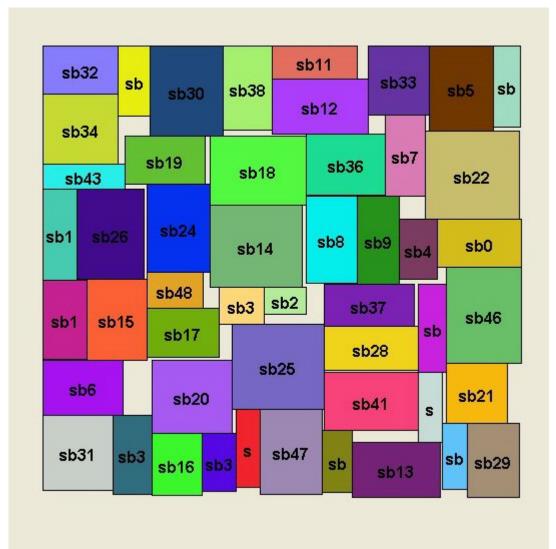

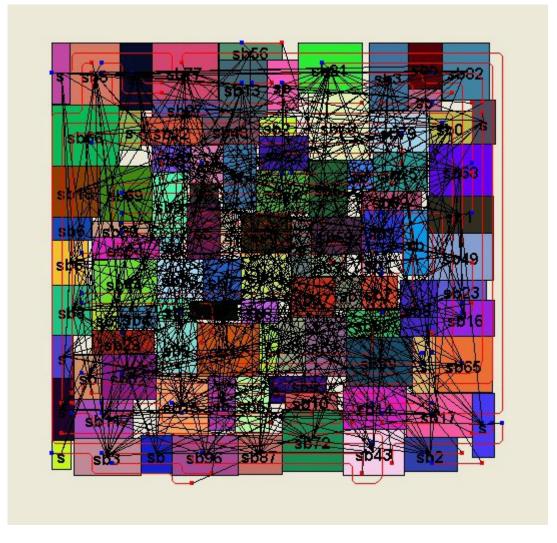

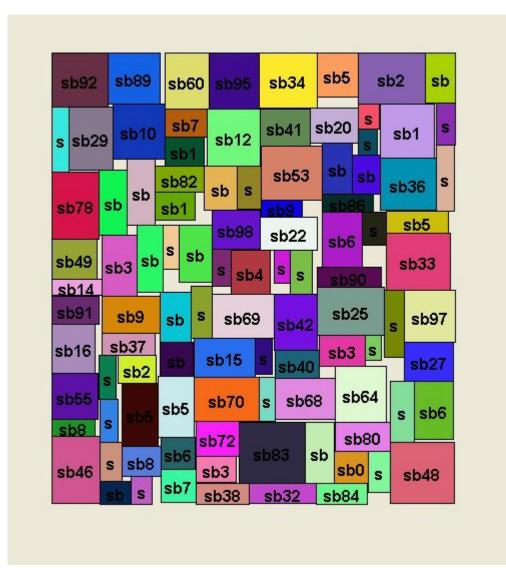

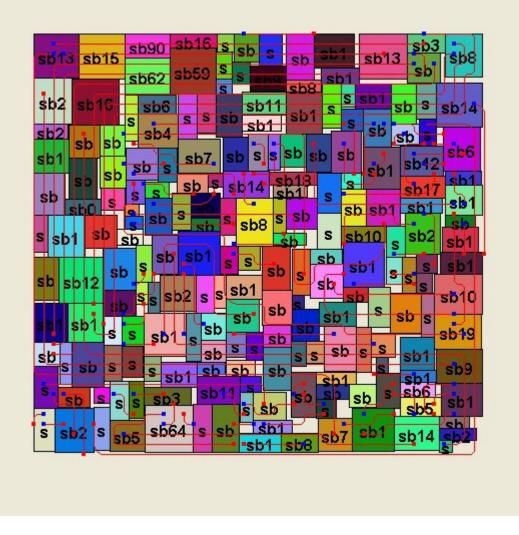

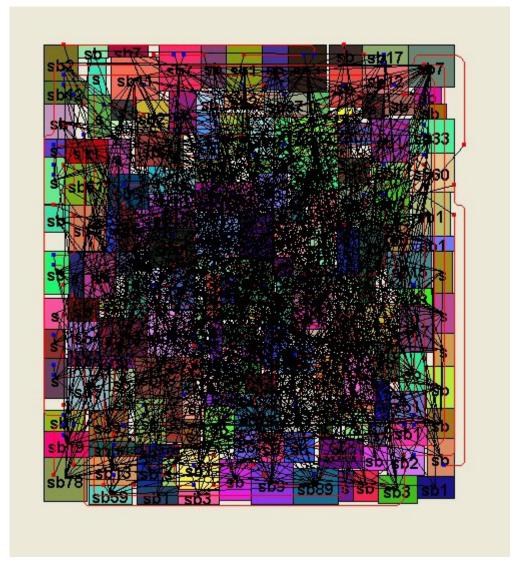

Figure 18 shows only the optical interconnects at the end of the optimization.

Figure 18. Optical routing after optimization

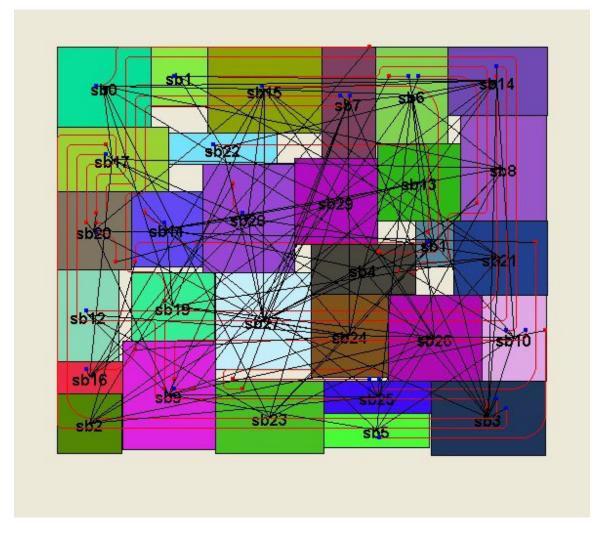

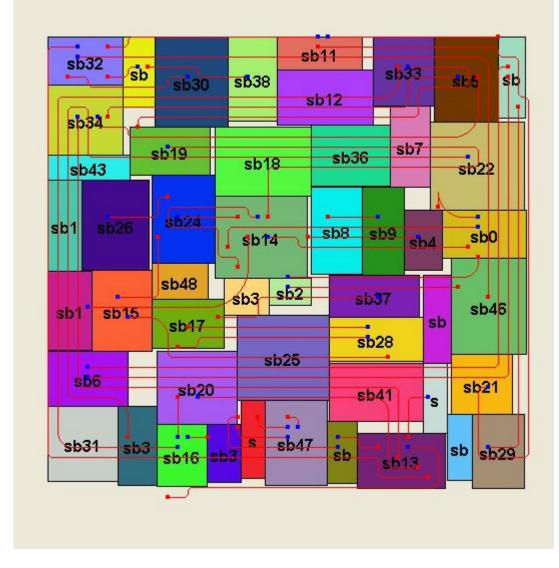

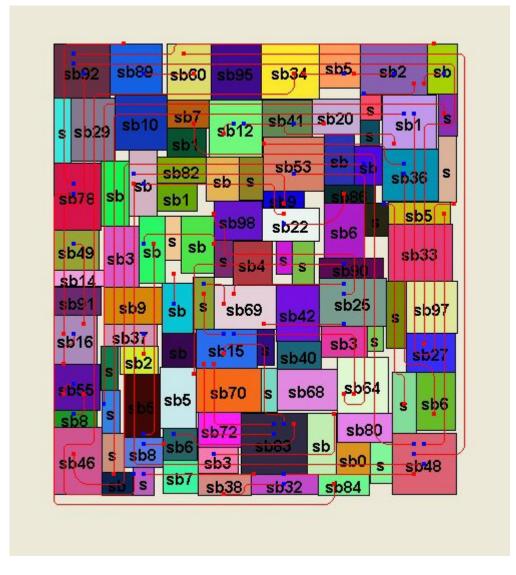

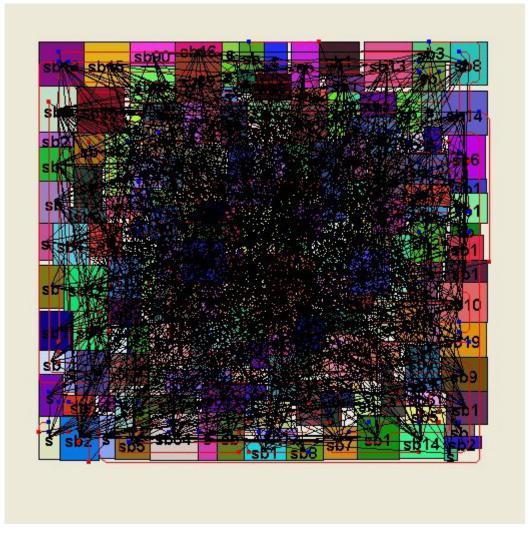

The electrical interconnects at the end of the optimization are shown in Figure 19.

Figure 19. Electrical routing after optimization

# 3.4.2 Speed and Energy Issues

In this section, we evaluate the SoC speed improvement and energy saving with 9, 16, 25, 36 and 49 modules.

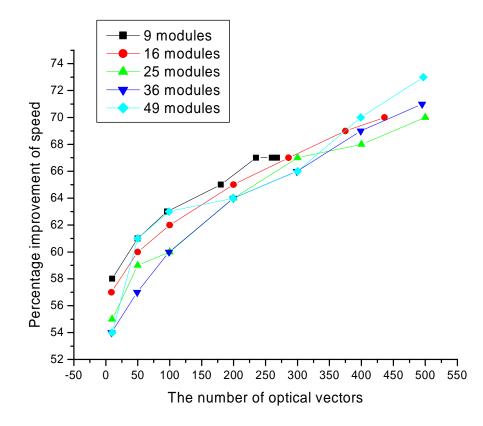

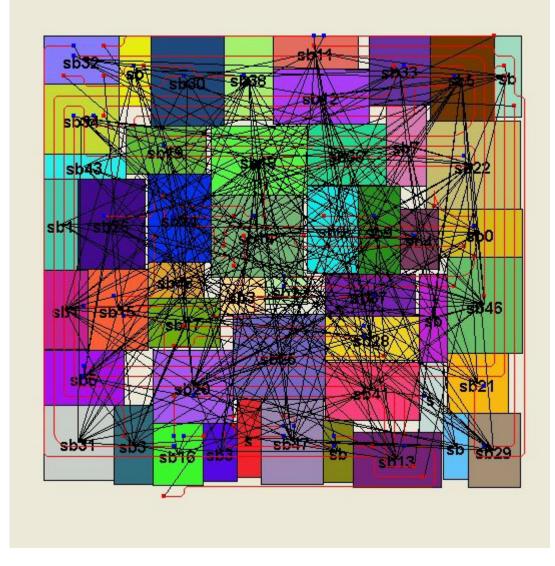

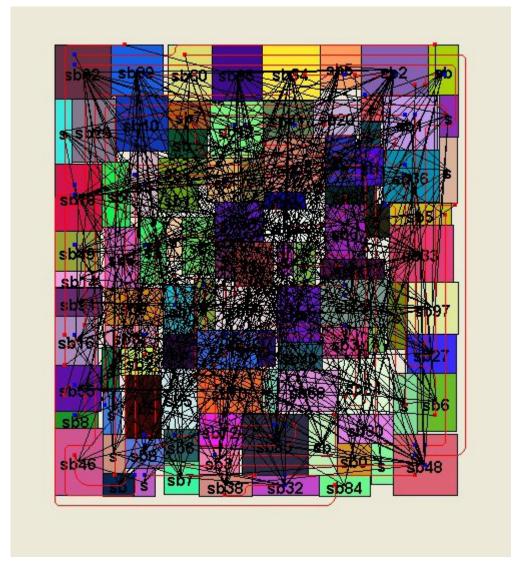

The graph for the percentage improvement of overall SoC speed vs. the number of optical vectors with various numbers of modules is shown in Figure 20.

Figure 20. The graph for speed improvement vs. optical directions with various numbers of modules

The results are very encouraging and show that more than 54% improvement in chip speed can be obtained through the use of optical interconnects.

Figure 21 shows the graph for the percentage saving of energy consumption vs. the number of optical vectors with 9, 16, 25, 36 and 49 modules.

Figure 21. The graph for energy saving vs. optical directions with various numbers of modules

In cases of 9 and 16 modules, the best results are with 235 and 200 optical interconnects respectively.

Table 5 shows results for optimization performed with 9, 16, 25, 36 and 49 modules against different number of optical directions supported by optical substrate. The table