# Universitat Politècnica de Catalunya

# Design of a 16-bit 50-kHz Low-Power SC Delta-Sigma Modulator for ADC in 0.18um CMOS Technology

MASTER THESIS

*Author:* Jose Cisneros Fernàndez IMB-CNM Supervisors: Michele Dei Francisco Serra Graells UPC co-advisor: Xavier Aragonès Cervera

A thesis submitted in fulfillment of the requirements for the degree of Master of Electronic Engineering

in the

ETSETB Escola Tècnica Superior d'Enginyeria de Telecomunicació de Barcelona

July 10, 2016

# UNIVERSITAT POLITÈCNICA DE CATALUNYA ETSETB

#### Master of Electronic Engineering

#### Design of a 16-bit 50-kHz Low-Power SC Delta-Sigma Modulator for ADC in 0.18um CMOS Technology

#### Jose Cisneros Fernàndez

# Abstract

A general purpose 16 Bits  $\Sigma$ - $\Delta$  modulator ADC for double precision audio 50 kHz bandwidth, targeted for Low-power operation, involving no additional digital circuit compensation, no bootstrapping techniques and resistor-less topologies, and relaying on Switched Capacitor  $\Sigma$ - $\Delta$  modulator topologies for robust operation and insensitivity to process and temperature variations, is presented in this work.

Designed in a commercial 180 nm technology, the whole circuit static current is calculated in 620  $\mu$ A with a nominal voltage supply of 1.8 V, performing a Schreier FOM of 174.16 dB. This outstanding state-of-the-art forseen FOM is achieved by the use of architectural and circuital Low-power techniques. At the architectural level a single loop Low-distortion topology with the optimum order and coefficients have been chosen, while at circuit level very novel OTA based on Variable Mirror Amplifiers allows an efficient Class-AB operation.

Specially optimized switched variable mirror amplifiers with a novel design methodology based on Bottom-up approach, allows faster design stages ensuring feasable circuit performance at architectural level without the need of large iterative simulations of the complete SC  $\Sigma$ - $\Delta$  modulator. Simulation results confirms the complete optimization process and the metioned advantages with respect to the tradicional approach.

**KEY WORDS-** 16 Bits, 50 kHz, Low-Power, Low-Distortion, No boostrapping, Switched Capacitor  $\Sigma$ - $\Delta$  modulator.

# Acknowledgements

I owe my gratitude to all those who contributed in some way in the realization of this master thesis.

Firstly, I would like to thank Dr. Francisco Serra Graells and Dr. Lluis Teres for the oportunity to develop my master thesis in the ICAS group at IMB-CNM.

This Thesis would not have been possible without the guidance and the help of Dr.Michele Dei and Dr. Francisco Serra, from which I'm thankful for their patience, motivation, and knowhow. Their guidance helped me in all the time of development and writing of this thesis.

I would like to express my sincere gratitude to my advisor Dr. Xavier Aragones, which gives me the opportunity and the time I need to learn from this world of electronics, without expecting anything in return.

I would like to express my deepest thanks to Joan Aymerich, for being part of this journey through the micro-electronics world and provide support and advice when needed. With no doubt its a pleasure to find people like you.

Last but not the least I would like to thank my parents and brother for their unending support and encouragement. Without their support this work would not have been possible.

# Contents

| Al | ostra      | ct                                                                           | ii              |

|----|------------|------------------------------------------------------------------------------|-----------------|

| A  | cknow      | wledgements                                                                  | iii             |

| 1  | Intr       | oduction                                                                     | 1               |

|    | 1.1        | ADC Fundamentals                                                             | 1               |

|    | 1.2        | ADC architectures                                                            | 3               |

|    | 1.3        | State-of-the-art ADCs                                                        | 4               |

|    | 1.4        | $\Sigma$ - $\Delta$ ADC                                                      | 7               |

|    |            | 1.4.1 $\Sigma$ - $\Delta$ Modulation Basics                                  | 7               |

|    |            | 1.4.2 CT and DT $\Sigma$ - $\Delta$ Modulation                               | 9               |

|    |            | 1.4.3 Classification of $\Sigma$ - $\Delta$ Modulators                       | 10              |

|    | 1.5        | Objectives                                                                   | 11              |

|    | 1.6        | Design methodologies                                                         | 12              |

|    | 1.7        | Structure of the Work                                                        | 16              |

| 2  | Mea        | asurements                                                                   | 17              |

|    | 2.1        | $\Sigma$ - $\Delta$ performance metrics                                      | 17              |

|    | 2.2        | $\Sigma - \Delta$ Modulator expected Performance                             | 19              |

|    | 2.3        | $\Sigma$ - $\Delta$ Test Vehicle                                             | 20              |

|    |            | 2.3.1 Test Vehicle Equipment                                                 | 20              |

|    |            | 2.3.2 Test Vehicle Board                                                     | 21              |

|    |            | 2.3.3 Test Vehicle Software                                                  | 22              |

|    | 2.4        | $\Sigma$ - $\Delta$ Modulator Measurements                                   | 23              |

|    |            | 2.4.1 Measurement Procedure                                                  | 23              |

|    | 2.5        | Measurement Results                                                          | 23              |

|    | 2.6        | Discussion                                                                   | 24              |

| 3  | Hia        | h level $\Sigma$ - $\Delta$ modelling                                        | 26              |

| 0  | 3.1        | $\Sigma$ - $\Delta$ modulator topologies                                     | 27              |

|    | 0.1        | 3.1.1 Distributed feedback $\Sigma$ - $\Delta$ modulator                     | 27              |

|    |            | 3.1.2 Feedforward $\Sigma$ - $\Delta$ modulator                              | 30              |

|    | 3.2        | $\Sigma$ - $\Delta$ Modulator Topology Election                              | 32              |

|    | 3.3        | Coefficient Optimization                                                     | 34              |

|    | 3.4        | Mismatch robustness test                                                     | 37              |

|    | 3.5        | Settling robustness test                                                     | 39              |

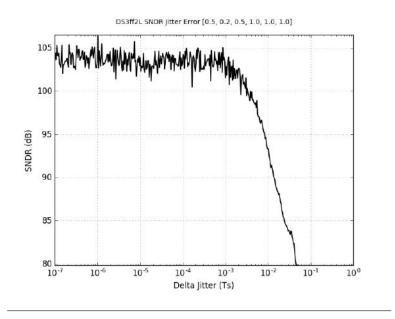

|    | 3.6        | Clock jitter robustness test                                                 | 40              |

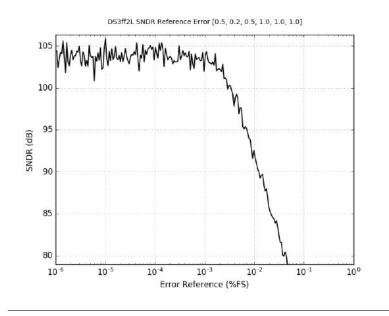

|    | 3.7        | Reference noise robustness test                                              | 41              |

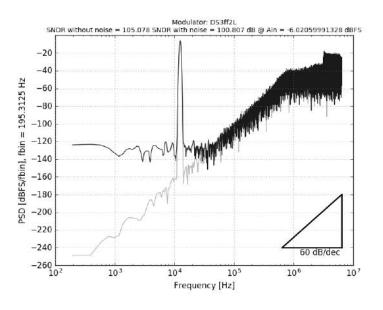

|    | 3.8        | Thermal noise                                                                | 42              |

| 4  | Circ       | wit loval design                                                             | 44              |

| ** | 4.1        | <b>cuit level design</b><br>Switched Capacitor $\Sigma$ - $\Delta$ Modulator | <b>44</b><br>44 |

|    | 4.1<br>4.2 | Modulator building blocks                                                    | 44<br>50        |

|    | 4.4        |                                                                              | 50<br>50        |

|    |            | 4.2.1 Phase Splitter                                                         | 50              |

|    |        | 4.2.2         | Single-b     | it Quantizer                                | 51 |

|----|--------|---------------|--------------|---------------------------------------------|----|

|    |        | 4.2.3         | Switche      | d Variable-Mirror Amplifiers                | 52 |

|    |        |               | 4.2.3.1      | Switched Variable-Mirror Amplifiers princi- |    |

|    |        |               |              | ple of operation                            | 53 |

|    |        |               | 4.2.3.2      | Switched Variable-Mirror Types              | 54 |

|    |        |               | 4.2.3.3      | Switched Variable-Mirror SC implementation  | 56 |

| 5  | Circ   | cuit opt      | imizatior    | n and simulation results                    | 58 |

|    | 5.1    | Simul         | ation Test   | bench                                       | 58 |

|    | 5.2    | Switc         | hes          |                                             | 61 |

|    |        | 5.2.1         | Switche      | s optimization process                      | 62 |

|    | 5.3    | Switc         | hed Varia    | ble Mirror Amplifier                        | 63 |

|    |        | 5.3.1         | Design s     | space and alternatives                      | 63 |

|    |        | 5.3.2         | Slew rat     | e and linear relaxation                     | 65 |

|    |        | 5.3.3         | SVMA 7       | Type 1 Optimization                         | 66 |

|    |        | 5.3.4         | SVMA 7       | Type 2 Optimization                         | 68 |

|    |        | 5.3.5         | $2^{nd}$ and | $3^{rd}$ SVMA stages                        | 71 |

|    | 5.4    | SC $\Sigma$ - |              | rical simulations                           | 71 |

| 6  | Con    | clusio        | ns           |                                             | 74 |

|    | 6.1    | Concl         | usions .     |                                             | 74 |

|    | 6.2    | Futur         | e work .     |                                             | 75 |

| Re | eferei | nces          |              |                                             | 76 |

# List of Figures

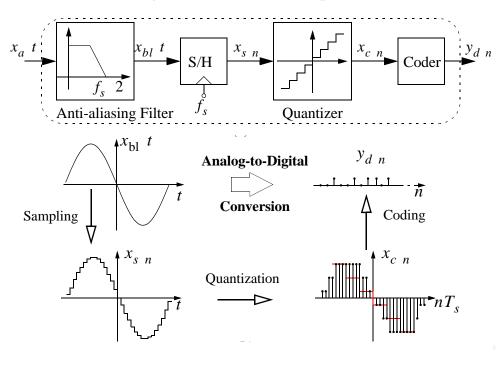

| 1.1  | ADC basic block diagram and Analog-to-Digital conversion process.                                                                                                                         | 2        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

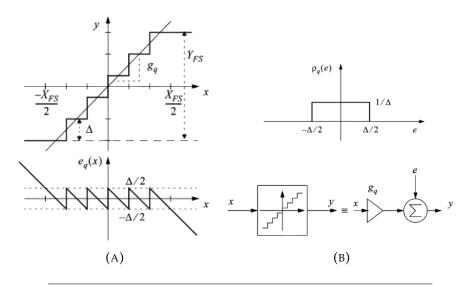

| 1.2  | (A) 6-level quantizer characteristic and its quantization error, $(B)$ equivalence of the quantizer block diagram with its simplified linear model accounting for the injection of a uni- | -        |

|      | formly distributed white noise.                                                                                                                                                           | 3        |

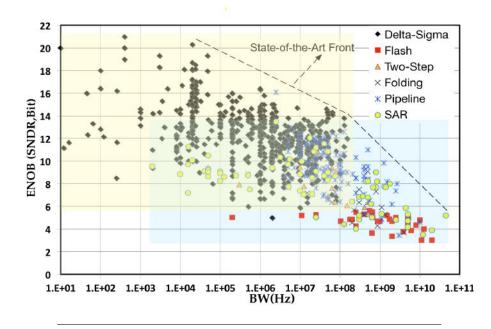

| 1.3  | Murmann survey of ADC performance: representation on                                                                                                                                      | U        |

|      | the ENOB versus signal bandwidth plane.                                                                                                                                                   | 5        |

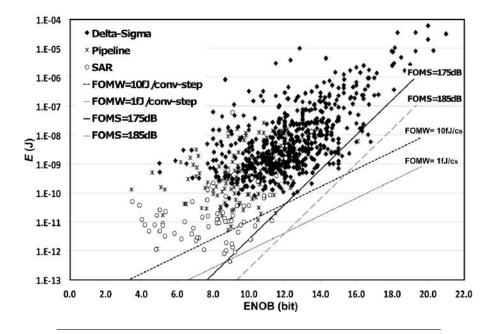

| 1.4  | Murmann survey of ADC performance: representation on                                                                                                                                      |          |

|      | the energy-per-conversion versus the ENOB.                                                                                                                                                | 6        |

| 1.5  | In-band noise power representations in three different cases:                                                                                                                             |          |

|      | Nyquist-rate ADC, oversampled ADC and oversampled with                                                                                                                                    | 0        |

| 1.0  | noise shaping ADC.                                                                                                                                                                        | 8        |

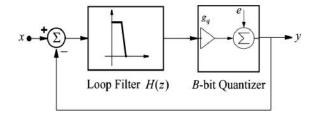

| 1.6  | Basic single loop $\Sigma$ - $\Delta$ Modulator block diagram.                                                                                                                            | 8        |

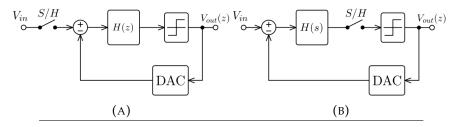

| 1.7  | Discrete time (A) and Continuous time (B) $\Sigma$ - $\Delta$ modulators                                                                                                                  | 9        |

| 1.8  | block diagram                                                                                                                                                                             | 9        |

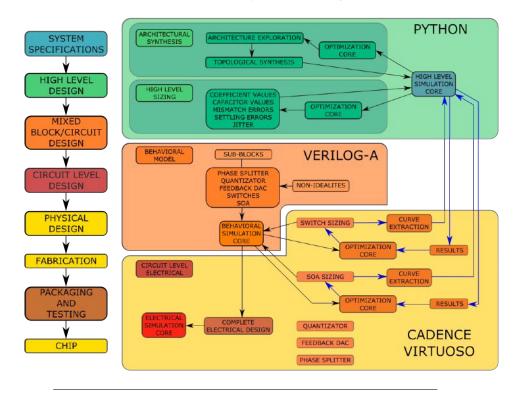

| 1.0  | have been mapped to their respective design environment.                                                                                                                                  | 13       |

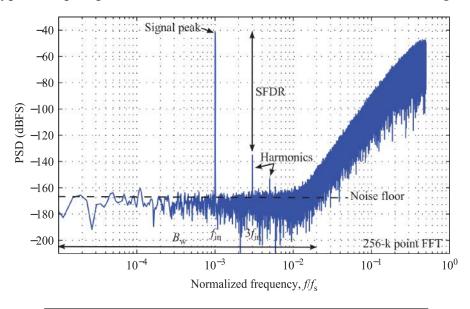

| 2.1  | Typical $\Sigma$ - $\Delta$ Modulator power spectral density with perfor-                                                                                                                 |          |

|      | mance metrics.                                                                                                                                                                            | 17       |

| 2.2  | Graphical representation of the most important performance metrics of $\Sigma$ - $\Delta$ ADC.                                                                                            | 19       |

| 2.3  | Test vehicle board of the $\Sigma$ - $\Delta$ ADC of [32].                                                                                                                                | 19<br>21 |

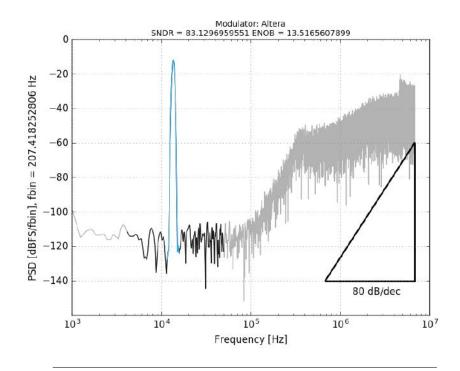

| 2.3  | $\Sigma$ - $\Delta$ Modulator PSD measurement of the $\Sigma$ - $\Delta$ ADC of [32].                                                                                                     | 21       |

| 2.1  | 2 A modulator 150 measurement of the 2 A ribe of [52].                                                                                                                                    | 22       |

| 3.1  | Design flow of High level modulator implementation                                                                                                                                        | 27       |

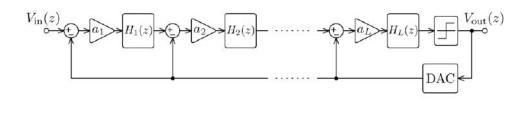

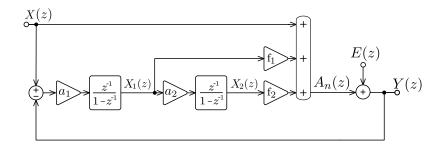

| 3.2  | <i>L-th</i> order distributed feedback $\Sigma$ - $\Delta$ Modulator                                                                                                                      | 28       |

| 3.3  | $2^{nd}$ order distributed feedback $\Sigma$ - $\Delta$ Modulator                                                                                                                         | 28       |

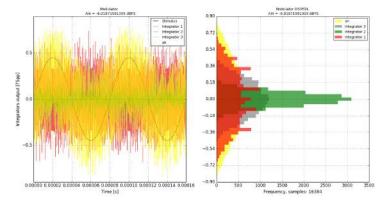

| 3.4  | Transient simulation and signal distortion at integrator out-                                                                                                                             |          |

|      | puts for a $2^{nd}$ order distributed feedback $\Sigma$ - $\Delta$ modulator                                                                                                              | 30       |

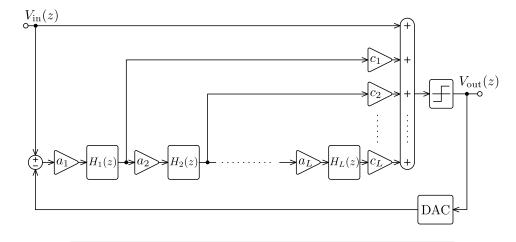

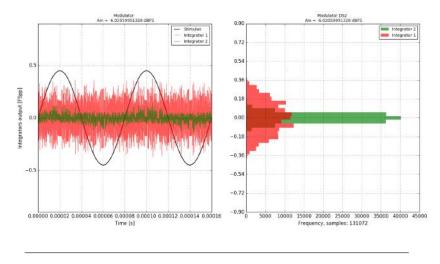

| 3.5  | <i>L-th</i> order Feedforward $\Sigma$ - $\Delta$ Modulator.                                                                                                                              | 30       |

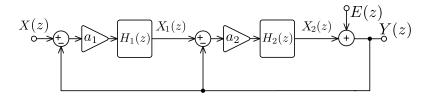

| 3.6  | $2^{nd}$ order Feedforward $\Sigma$ - $\Delta$ Modulator.                                                                                                                                 | 31       |

| 3.7  | Transient simulation and signal distortion at integrator out-                                                                                                                             | 22       |

| 3.8  | puts for a $2^{nd}$ order feedforward $\Sigma$ - $\Delta$ modulator.<br>Block diagram of the $3^{rd}$ order feedforward $\Sigma$ - $\Delta$ modulator                                     | 32       |

| 5.0  | developed in this work. $\dots$                                                                                                                                                           | 34       |

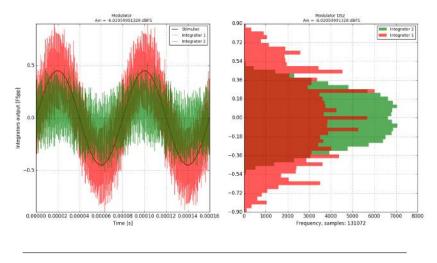

| 3.9  | Transient simulations and state variables distribution for two                                                                                                                            | 54       |

| 0.7  | different candidates of the grid search algorithm.                                                                                                                                        | 36       |

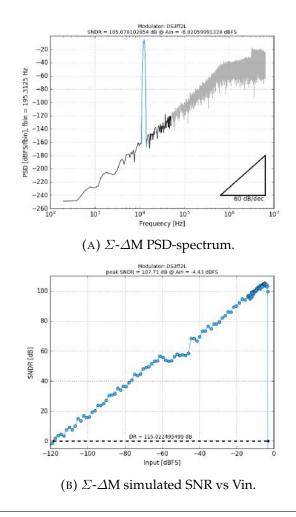

| 3.10 |                                                                                                                                                                                           | 00       |

|      | model of this work.                                                                                                                                                                       | 37       |

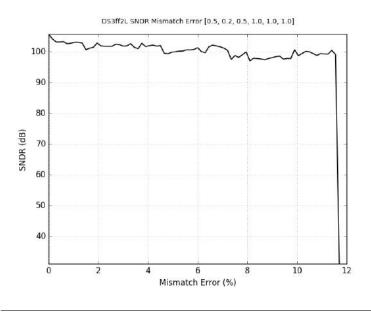

| 3.11 | Mismatch coefficient test results.                                                                                                                                                        | 38       |

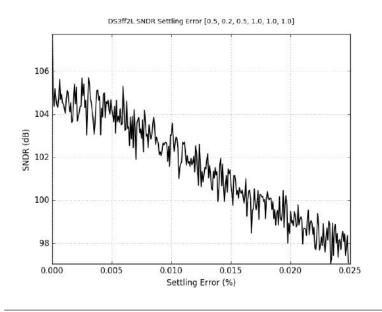

| 3.12 | SNDR degradation as function of the integrator settling error.                                                                                                                            | 39       |

| 3.13         | Graphical representation of a non-uniform sampling of a si-                                                                                                                                                                                                          |          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|              | nusoidal signal due to clock jitter                                                                                                                                                                                                                                  | 40       |

| 3.14         | SNDR degradation as function of Jitter.                                                                                                                                                                                                                              | 41       |

| 3.15         | Reference noise test results.                                                                                                                                                                                                                                        | 42       |

| 3.16         | High level PSD-spectrum with (Grey) and without (Black)                                                                                                                                                                                                              |          |

|              | thermal noise.                                                                                                                                                                                                                                                       | 43       |

|              |                                                                                                                                                                                                                                                                      |          |

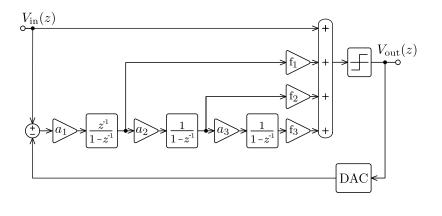

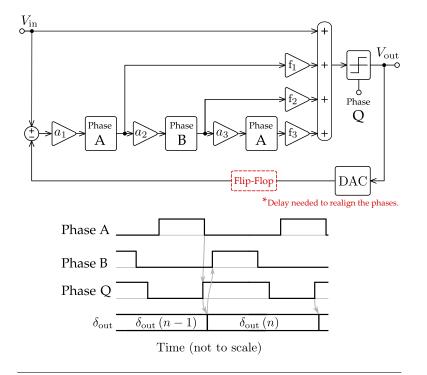

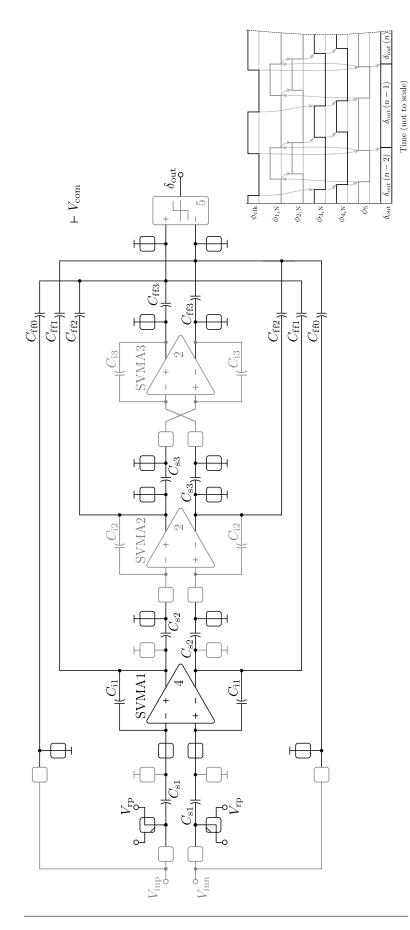

| 4.1          | Interleaved operation of switched OpAmps in a $3^{rd}$ order $\Sigma$ -                                                                                                                                                                                              |          |

|              | $\Delta$ Modulator. This implementation modifies the loop trans-                                                                                                                                                                                                     |          |

|              | fer function in a way that make the modulator dysfunctional.                                                                                                                                                                                                         |          |

|              | It is shown here for illustration purposes.                                                                                                                                                                                                                          | 45       |

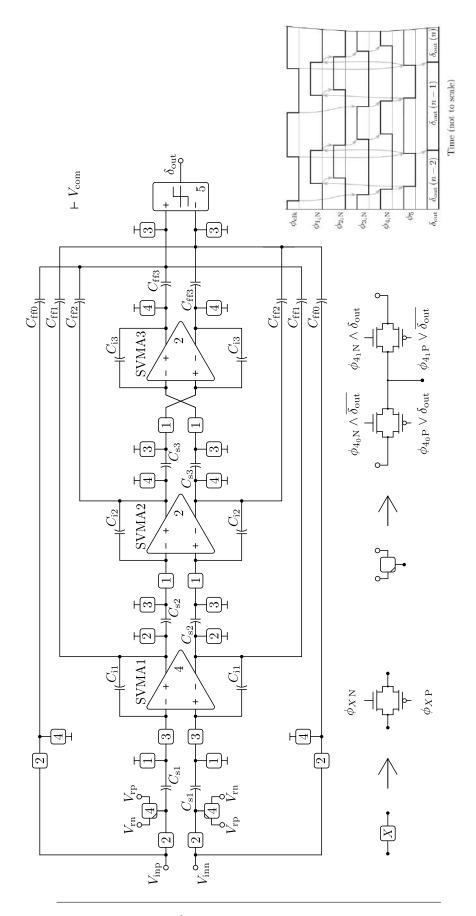

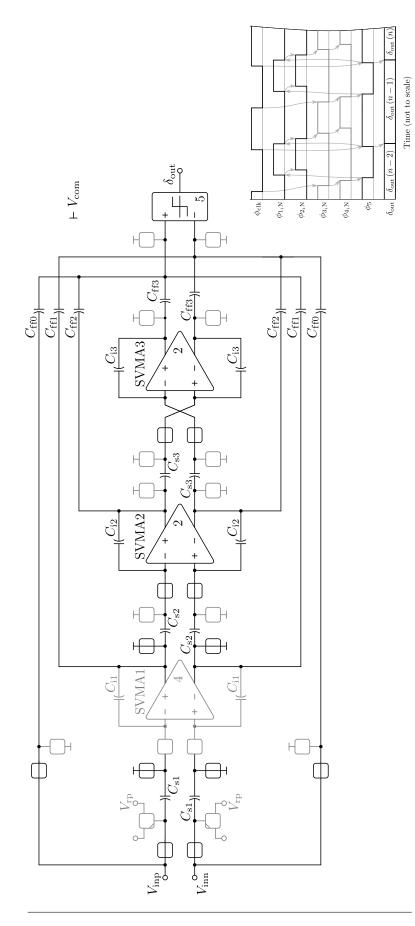

| 4.2          | $3^{rd}$ order $\Sigma$ - $\Delta$ M SC based on switched OpAmps. Here the                                                                                                                                                                                           |          |

|              | switched OpAmps blocks are labelled as SVMA accounting                                                                                                                                                                                                               |          |

|              | for the switched variable mirror amplifiers.                                                                                                                                                                                                                         | 46       |

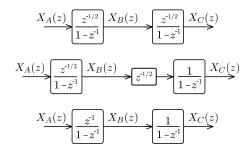

| 4.3          | Rearrangement of half delays in a cascade of two half delay                                                                                                                                                                                                          |          |

|              | integrators.                                                                                                                                                                                                                                                         | 47       |

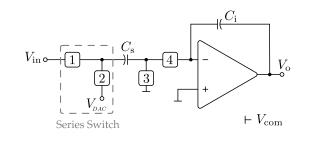

| 4.4          | $\Sigma$ - $\Delta M$ SC-switched OpAmp schematic during $\phi_{1-2}$                                                                                                                                                                                                | 48       |

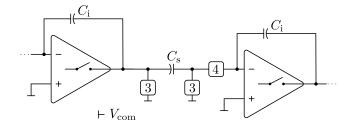

| 4.5          | $\Sigma$ - $\Delta$ M SC-switched OpAmp schematic during $\phi_{3-4}$                                                                                                                                                                                                | 49       |

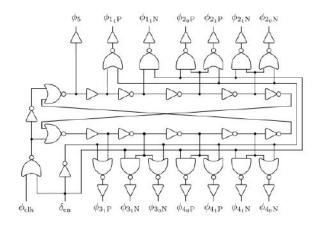

| 4.6          | $\Sigma$ - $\Delta$ M phase generator.                                                                                                                                                                                                                               | 50       |

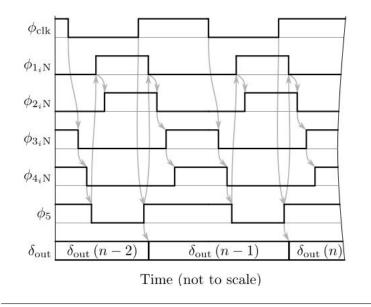

| 4.7          | $\Sigma$ - $\Delta M$ operation chronogram                                                                                                                                                                                                                           | 51       |

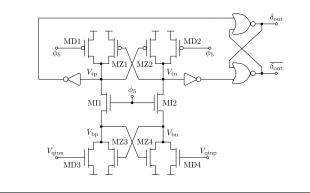

| 4.8          | $\Sigma$ - $\Delta$ modulator single bit quantizer.                                                                                                                                                                                                                  | 52       |

| 4.9          | $\Sigma$ - $\Delta$ modulator single bit quantizer waveform representation.                                                                                                                                                                                          | 52       |

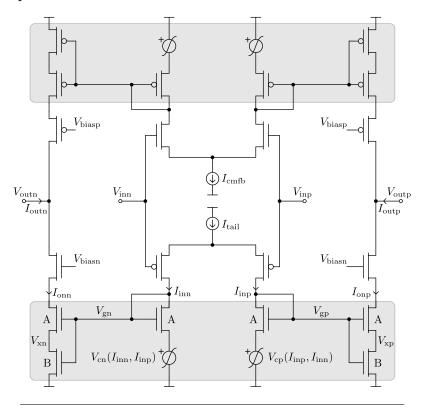

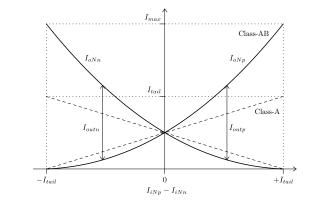

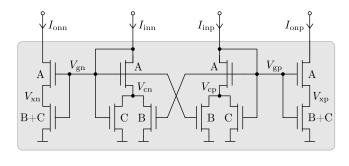

|              | General architecture of the proposed VMA[33].                                                                                                                                                                                                                        | 53       |

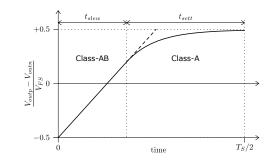

| 4.11         | Qualitative large-signal Class-AB operation[33].                                                                                                                                                                                                                     | 54       |

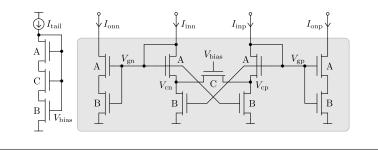

|              | Type 1 Class-AB current amplifier[33].                                                                                                                                                                                                                               | 55       |

|              | Type 2 Class-AB current amplifier[33].                                                                                                                                                                                                                               | 55       |

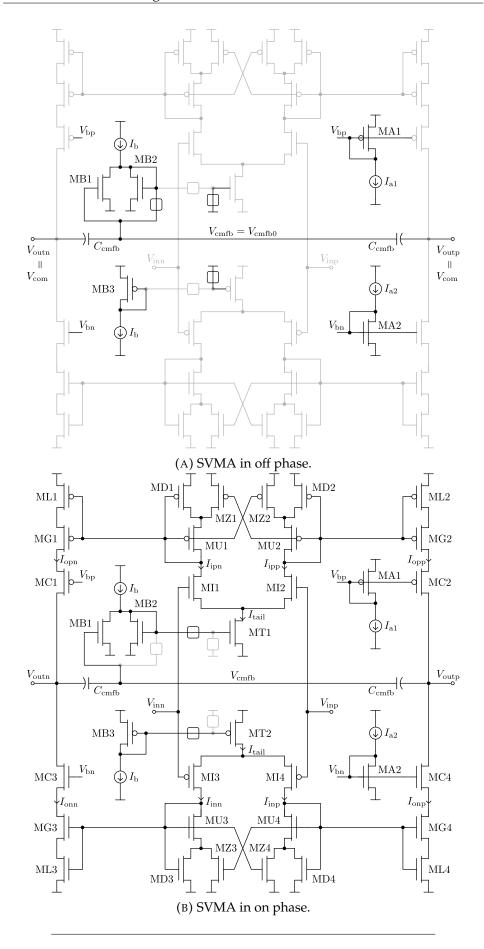

|              | SVMA schematic during off phase (A) and on phase (B).                                                                                                                                                                                                                | 57       |

|              |                                                                                                                                                                                                                                                                      | 0.       |

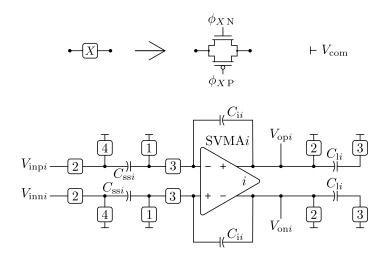

| 5.1          | Reduced Testbench schematic used in the optimization pro-                                                                                                                                                                                                            |          |

|              | Cesses.                                                                                                                                                                                                                                                              | 58       |

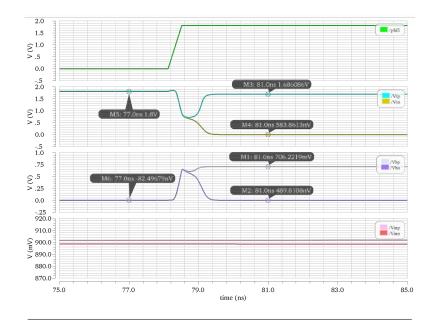

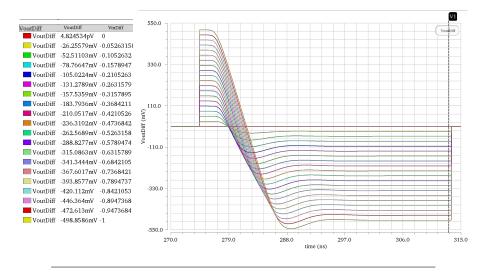

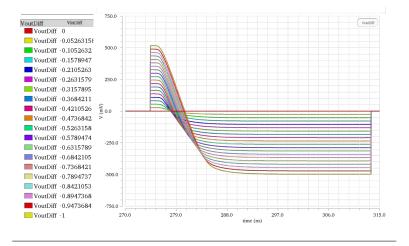

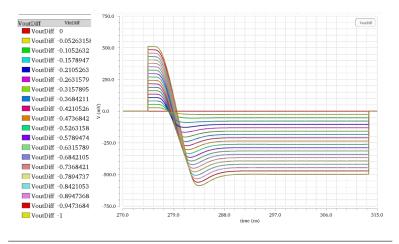

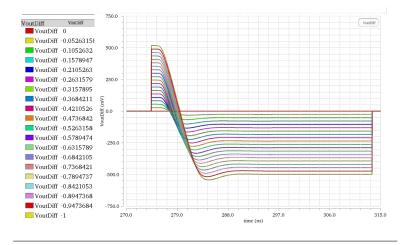

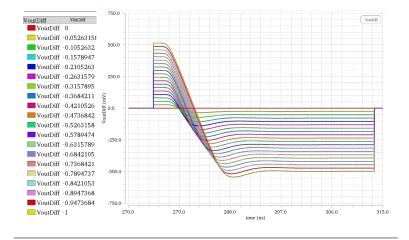

| 5.2          | Differential output voltage waveforms during the integra-                                                                                                                                                                                                            |          |

|              | tion phase for input differential voltage ranging from 0 to                                                                                                                                                                                                          |          |

|              | -1 V                                                                                                                                                                                                                                                                 | 59       |

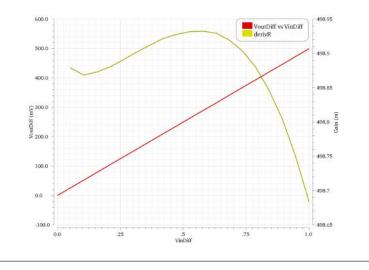

| 5.3          | Differential output voltage (Red) and its derivative (Yellow)                                                                                                                                                                                                        |          |

|              | representation obtained from Fig.5.2.                                                                                                                                                                                                                                | 60       |

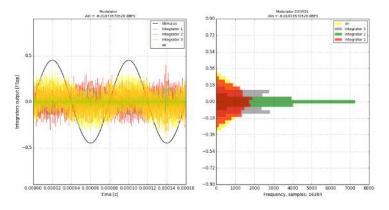

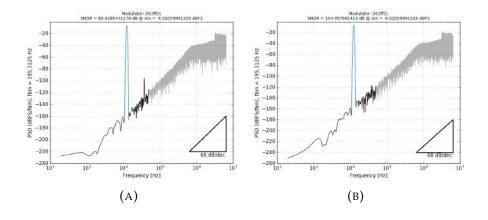

| 5.4          | High level simulation results for two design cases of Fig.5.1.                                                                                                                                                                                                       | 61       |

| 5.5          | SC $\Sigma$ - $\Delta$ modulator first stage schematic showing relevant is-                                                                                                                                                                                          |          |

|              | sues regarding the sampler switches.                                                                                                                                                                                                                                 | 62       |

| 5.6          | SC $\Sigma$ - $\Delta$ modulator second and third stage schematic illus-                                                                                                                                                                                             |          |

|              | trating the switched OpAmp action on the switching scheme.                                                                                                                                                                                                           | 63       |

| 5.7          | Qualitative transient response of the VMA differential out-                                                                                                                                                                                                          |          |

|              | put voltage.                                                                                                                                                                                                                                                         | 65       |

| 5.8          |                                                                                                                                                                                                                                                                      |          |

|              | Type 1 differential output voltage waveform with $K_{AB} = 4$                                                                                                                                                                                                        |          |

| 5.9          | Type 1 differential output voltage waveform with $K_{AB} = 4$<br>and $I_{tail} = 150 \mu A$ .                                                                                                                                                                        | 67       |

|              | and $I_{tail} = 150 \mu A$ .                                                                                                                                                                                                                                         | 67       |

|              | and $I_{tail} = 150 \mu A$                                                                                                                                                                                                                                           |          |

| 5.10         | and $I_{tail} = 150\mu A$                                                                                                                                                                                                                                            | 67       |

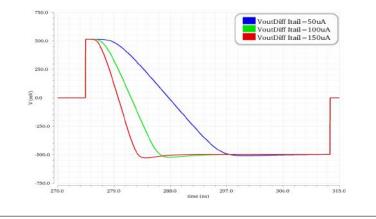

| 5.10         | and $I_{tail} = 150\mu A$                                                                                                                                                                                                                                            | 67<br>'F |

|              | and $I_{tail} = 150\mu A$ .<br>Type 1 differential output voltage waveform with $K_{AB} = 8$<br>and $I_{tail} = 150\mu A$ .<br>Type 1 differential output voltage waveforms for a fixed $Vin_{DIF}$<br>step of 1 V and $I_{tail}$ equal to 150, 100 and 50 $\mu A$ . | 67       |

| 5.10<br>5.11 | and $I_{tail} = 150\mu A$                                                                                                                                                                                                                                            | 67<br>'F |

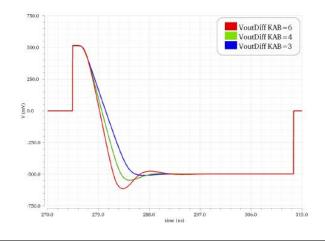

| 5.12 Ty | ype 2 differential output voltage waveforms for a fixed $Vin_{DIF}$           | F  |

|---------|-------------------------------------------------------------------------------|----|

| st      | ep of 1 V with $I_{tail}$ of 150 $\mu$ A and $K_{AB}$ equal to 3, 4 and 6.    | 69 |

| 5.13 Ty | ype 2 differential output voltage waveform with $K_{AB} = 4$                  |    |

| ar      | nd $I_{tail} = 100 \mu A.$                                                    | 70 |

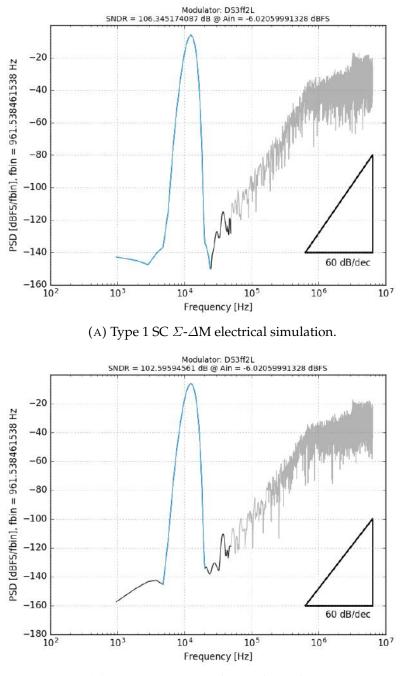

| 5.14 SC | $\Sigma \Sigma - \Delta M$ electrical simulations (Cadence), which represents |    |

| 7       | days of computing for 16 cycles with the ideal versions of                    |    |

| th      | e quantizer and the switching network, versus the maxi-                       |    |

| m       | um of 20 minutes spent in the bottom-up approach (sim-                        |    |

| pl      | lified Cadence testbench and Python code simulation)                          | 73 |

|         |                                                                               |    |

# List of Tables

| 1.1 | Initial specifications and characteristics of the $\Sigma$ - $\Delta$ Modulator of this thesis.    | 12 |

|-----|----------------------------------------------------------------------------------------------------|----|

| 2.1 | $\Sigma$ - $\Delta$ Modulator SNDR simulated under process and temper-<br>ature variations.        | 19 |

| 2.2 | $\Sigma$ - $\Delta$ Modulator SNDR measurements across temperature.                                | 24 |

| 3.1 | $\Sigma$ - $\Delta$ Modulator simulation time comparison on 12 GHz/24 CPUs x86_64 machine.         | 26 |

| 3.2 | SNDR peak value for various $\Sigma$ - $\Delta$ Modulator configurations, considered in this work. | 33 |

| 3.3 | Extracted output samples of the Grid search algorithm.                                             | 35 |

| 3.4 | Selected set of coefficients for the $3^{rd}$ order $\Sigma$ - $\Delta$ Modulator of this work.    | 36 |

| 3.5 | Gain coefficients generated for the mismatch sensitivity test.                                     | 38 |

| 3.6 | Capacitor sizing for the SC $\Sigma$ - $\Delta$ M                                                  | 43 |

| 5.1 | Capacitor values used in Fig.5.1.                                                                  | 59 |

| 5.2 | SVMA candidates performance for $K_{AB} = 6$ and $I_{tail} = 200 \mu A$ .                          | 65 |

| 5.3 | Type 1 explored design space.                                                                      | 68 |

| 5.4 | Type 2 explored design space.                                                                      | 70 |

| 5.5 | $2^{nd}$ and $3^{rd}$ SVMA stages scale down.                                                      | 71 |

| 5.6 | Simulated dynamic current consumption of each SC $\Sigma$ - $\Delta$ M                             |    |

|     | implemented for both SVMA types.                                                                   | 71 |

| 5.7 | SC $\Sigma$ - $\Delta$ M Type 2 simulation across corners                                          | 72 |

# **Chapter 1**

# Introduction

Technological advancement and growing demands for electronic devices with advanced features is currently driving the smart sensing portable devices. In current times smart sensors are an integral part of most of the handled electronics devices, automotive and biomedical equipment, between others, that offers advanced features.

Data converters play a crucial role inside this aspect by covering the essential need of connecting the physical or analog world, with the digital world of electronics. A direct consequence of it, is a raising interest in pushing the ADCs performance, increasing the resolution and speed of conversion while reducing the power consumption and the manufacturing cost.

Smart sensor applications usually requires for low bandwidth input signals with medium to high resolution data conversions and low power consumptions.  $\Sigma$ - $\Delta$  modulators are a common choice in smart sensors, providing an efficient way to implement high-performance ADCs without stringent matching requirements or calibration, at expenses of increasing the oversampling ratios. Besides,  $\Sigma$ - $\Delta$  modulators robustness and resolution allows the integration in a wide variety of applications.

# 1.1 ADC Fundamentals

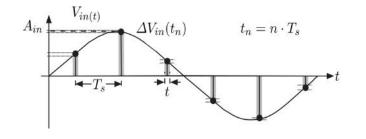

ADCs perform two basic fundamental operations: discretization in time and discretization in amplitude. These two functions are illustrated in Fig.1.1. The first operation of the ADCs is to discretize in time, or sample the input signal. Normally, the input signal is sampled at uniformly spaced times, at a given sampling frequency  $f_s$ , resulting in samples separated by one sampling period  $T_s$ . The result from this sampling process are impulses at each sampling time  $kT_s$ . Moreover, the sampling process limits the input signal frequency and imposes the speed requirement of the ADC.

The second operation described is the discretization in amplitude of the sampled signal, which limits the input signal accuracy and therefore the resolution of the ADC. In the operation, the ADC approximates the input signal amplitude of each sample with one of a finite number of possible values. Because the output of the ADC can only take a finite number of output values, the sampled amplitude can be represented by a digital code.

The number of discrete values M which the ADC can produce at the output determines the resolution usually expressed in number of bits N:

$$N = \log_2(M) \tag{1.1}$$

Another parameter related to the amplitude discretization is the quantization step  $\Delta$  which is determined by Eq. 1.2 and represents the distance between adjacent levels. The size of the quantization step  $\Delta$  depends on the full scale of the input signal ( $V_{min} < V < V_{max}$ ) and the number of bits.

$$\Delta = \frac{V_{max} - V_{min}}{2^N} \tag{1.2}$$

As consequence of the finite number of output values in a converter, errors into the digital representation of the analog input are introduced.

These errors are called quantization errors  $Q_{\epsilon}$  and are illustrated in Fig.1.2. The range of the quantization error in normal operation is  $-\Delta/2 < Q_{\epsilon} < \Delta/2$ , and usually is considered to have a uniform probability density function within its range. Because of that, the quantization error can be modelled as an additive white noise source, as shown in Fig.1.2a, while the power spectral density (PSD) in the range  $[-f_s/2 \text{ to } f_s/2]$  is given by

$$S_E(f) = \frac{1}{f_s} \left[ \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} e^2 \cdot de \right] = \frac{\Delta}{12f_s}$$

(1.3)

Two main groups of ADCs can be classified depending on the relationship between the sampling frequency  $f_s$  and the bandwidth (BW) of the input signal to be considered. The first group are named Nyquist ADCs and their sampling frequencies follows the Nyquist theorem, where  $f_s$  is chosen to be equal to twice the signal bandwidth. While the second group are the Oversampling ADCs in which the sampling frequency is higher than the previous case. The idea behind is to crease the sampling frequency in order to trade it off with a significant reduction of the quantization noise.

FIGURE 1.1: ADC basic block diagram and Analog-to-Digital conversion process.

Fig.1.2b represents the equivalent Quantizer block diagram, including the quantizator intrinsic gain  $g_q$  and quantization error as an input. This block is latter used in the extraction of the modulator transfer functions.

FIGURE 1.2: (*A*) 6-level quantizer characteristic and its quantization error, (*B*) equivalence of the quantizer block diagram with its simplified linear model accounting for the injection of a uniformly distributed white noise.

# **1.2 ADC architectures**

The vast majority of ADC architectures used nowadays have been discovered and published between the 40s and 60s [12]. Improvements in technology and in the optimization processes have made possible to increase the performance.

The ADC could be classified in terms of resolution, speed of conversion, mode of operation, internal structure, input/output type of signal, power consumption and others. The list provided below reflects what is traditionally known for each type of ADC, however must not be taken "as is" since research on this field is still very active, making the following distinctions more and more blurry. In the following list the converters are classified in terms of speed of conversion (form low to high speed of conversion versus the achievable resolution):

Integrating ADC ⇒ Integration ADCs are characterized for having a low speed of conversion and a high resolution. The idea behind this topology as the name suggest is the integration of the signal during a period of time by means of a capacitor and discharging the mentioned capacitor at a constant rate until is completely discharged. At that point knowing the two times and the value of the voltage reference, is possible to know the value of the input signal. The simplicity of this architecture makes them attractive for instrumental applications and digital acquisition systems in which the speed of conversion is not a must.

- Σ-Δ ADC ⇒ These ADCs are suited for low-mid conversion speeds and high resolution applications. These converters are based on two concepts, one is the oversampling and the other is the in-band noise shaping. The oversampling imposes a drawback in the frequency of the input signal and therefore in the speed of conversion. Resolutions of 14 to 20 bits are possible to be achieved with this architecture.

- SAR ADC ⇒ The Successive Approximation Register (SAR) ADC is suited for medium to high resolutions, with speed in the range of few mega-samples per second. The typical resolution achieved ranges between 8 to 16 bits maintaining a low power consumption and a great noise figure. It is typical to use SAR ADC in portable electronics and data acquisition systems.

- **Pipeline ADC** ⇒ Pipeline ADCs are used in applications with medium to high speed of conversion and resolutions between 6 to 16 bits. It also has a good relation between speed-resolution-consumption which is well suited for communication systems, image sensors and digital video systems between others.

- Flash ADC ⇒ Is the fastest ADC topology and it is used in high bandwidth applications. Its main drawback is power consumption, resolution and manufacturing cost. In fact, this type of ADC relies solely on the matching of electrical parameters that need to be trimmed (one device at time) to accomodate for acceptable resolution. For this reason they are normally used in oscilloscopes, radars, satellites and other applications in which the speed of conversion is a must. There is a topology in between the pipeline and the flash, called Half-Flash which obtains a good relation between cost, speed and resolution which makes them more competitive in signal processing applications.

### **1.3 State-of-the-art ADCs**

Monolithic ADCs integration has evolved following a Moore-like law over nearly four decades [12], thanks to the continuously increasing effort of the research community. ADC performance has shown a remarkable improvement in many key parameters with respect to the early days implementations. Low-power and small chip area are often pursued to allow the ADC to be part of a larger system-on-chip (SoC). This trend has evolved from the early days in which the major achievement was to implement a full converter in a single die with a modest speed and resolution and a high power consumption.

From a designer point of view it is crucial to understand the rate of performance and the roadmap of the different ADCs in other to be able to make the best topology election for each application. Several authors have presented works that blend the evolution surveys and derivations of theoretical physical limits to various degrees. Historically, one of the most widely cited surveys is the Walden survey[35], which is one of the pioneers and includes scientific and commercial ADC references from 1978 to 2008. Nowadays, the Murmann survey is usually referenced [16]. This survew is continuously updated and analyses ADC performance trends with a focus on energy per sample and signal to noise and distortion ratio (SNDR). There are also other surveys based on different analysis of the ADC performance [11] [15] [3] and different points of view [7].

Figure 1.3 compares the conversion region achieved by the state-of-theart oversampling ADCs with the one achieved by Nyquist ADCs. The figure was collected from [24] and the data used in this graph is obtained from the Murmann survey [16].

FIGURE 1.3: Murmann survey of ADC performance: representation on the ENOB versus signal bandwidth plane.

The figure 1.3 shows a space map of the different basic ADCs topologies pointed in terms of resolution in bits and speed in Hertz. From the state-ofthe-art, oversampling ADCs as  $\Sigma$ - $\Delta$  ADCs, have been proved to be used in high resolution and wide frequency (from hundreds of Hertz to hundreds of megahertz) applications. While Nyquist ADCs are more competitive in high frequency applications and medium resolutions.

It is necessary to introduce a third variable not reflected in Fig.1.3, which is the power consumption. In general it is possible to increase the data conversion speed at expenses of higher current consumption, i.e. two different points in Fig.1.3 can be equal in term of state-of-the-art. For this reason, the energy per conversion is normally used and expressed as  $E_j = Power/f_s$ . A way to include these three parameter is by means of figures of merit (FOM). Figure of merit are expressions which uses a combination of the most important parameters to obtain a value that could be used in a comparation.

In the case of ADCs there are two main FOMs which are the Walden FOM [35] and the Schreier FOM [26]. The Walden FOM is given by

$$FOM_{Walden} \equiv \frac{P}{2 \cdot BW \cdot 2^{ENOB}} \tag{1.4}$$

where P is the static power consumption and the ENOB is the effective number of bits, which is derived from the SNDR expressed in dB, and defined as

$$ENOB \equiv \frac{SNDR(dB) - 1.76}{6.02} \tag{1.5}$$

The main drawback with respect this FOMs is a bias towards low-power medium resolution designs rather than high resolution, and thus benefits from CMOS technology scaling. In other words, more FOM is gained by decreasing the power P rather than increasing the resolution ENOB, because Eq.1.4 does not correctly describe the trade-off between power and resolution in the ADCs.

The second FOM is the Schreier FOM which is described as

$$FOM_{Schreier} \equiv SNDR + 10\log(\frac{BW}{P})$$

(1.6)

This FOM is preferred for comparing high resolution ADCs limited by thermal noise. Finally Fig.1.4 represents the space map of the different ADCs with the lines representing the Schreier and Walden FOMs.

FIGURE 1.4: Murmann survey of ADC performance: representation on the energy-per-conversion versus the ENOB.

### **1.4** $\Sigma$ - $\Delta$ ADC

The next subsections are focused to explain the basics of the Sigma-Delta operation and a brief description of the main topologies used.

#### **1.4.1** $\Sigma$ - $\Delta$ Modulation Basics

$\Sigma$ - $\Delta$  ADCs are based on two concepts, one is the oversampling and the other one is the noise shaping [26][24][12]. All the architectures explained above except for  $\Sigma$ - $\Delta$  are also known as Nyquist ADCs, because the conversion rate follows the Nyquist theorem in which the sampling frequency  $f_s$  is two times the input signal bandwidth. Increasing the  $f_s$  above the Nyquist frequency  $f_{NY}$ , allows for the quantization noise to be reduced, since the same amount of quantization noise is spread over a wider frequency range, i.e. wider than the signal bandwidth. Ideally, the out-of-band noise power can be removed by filtering, leaving the in-band noise level signicantly lower. The ratio between both frequencies ( $f_s$  and  $f_{NY}$ ) is called the oversampling ratio (OSR).

$$OSR = f_s / f_{NY} = f_s / (2 \cdot BW) \tag{1.7}$$

The in-band noise power calculated for low-pass signals as function of the OSR is shown in Eq.1.8.

$$P_E = \int_{-BW}^{BW} S_E(f) \cdot df = \frac{\Delta^2}{12 \cdot OSR}$$

(1.8)

Therefore based in Eq.1.8 the in-band noise is reduced as the OSR increases. The effect is illustrated in Fig.1.5b, as the OSR is increased the inband noise spreads along higher frequencies reducing the amount of noise inside the band of interest. With this phenomena the  $P_E$  is reduced by 3 dB each time the OSR is doubled which implies a gain of 0.5 Bits.

The other concept behind  $\Sigma$ - $\Delta$  ADCs is the noise shaping, which is used to further increase the accuracy by filtering the quantization noise in such a way that most of its power lies outside the signal band.

A graphical example is shown in Fig.1.5c, in which it is possible to appreciate how the in-band noise is rejected to higher frequencies, differently to the mere oversampling that does not modify the shape of the noise power spectral density.

To implement this shift of noise power from low-to-high frequencies the signal undergoes a modulation which can be understood by looking at the basic  $\Sigma$ - $\Delta$  block diagram presented in Fig.1.6. This figure shows the main components used in a single loop feedback topology, which in this case are a low pass filter and a linear model of the quantizer.

FIGURE 1.5: In-band noise power representations in three different cases: Nyquist-rate ADC, oversampled ADC and oversampled with noise shaping ADC.

Since the circuit processes samples of the input signal, in can be analyzed in the discrete time transformed domain as X(z) and the output Y(z). The quantization error in the linear model of the quantizer is represented by E(z) and  $g_q$  is the quantizer gain.

FIGURE 1.6: Basic single loop  $\Sigma$ - $\Delta$  Modulator block diagram.

From the block diagram of Fig.1.6 the signal and noise transfer function is calculated in Eq.1.9.

$$Y(z) = STF(z) \cdot X(z) + NTF(z) \cdot E(z)$$

(1.9)

where signal transfer function (STF(z)) and noise transfer function is (NTF(z)). They are given by

$$STF(z) = \frac{g_q H(z)}{1 + g_q H(z)}; NTF(z) = \frac{1}{1 + g_q H(z)};$$

(1.10)

If the loop filter is designed in such a way that  $|H(z)| \to \infty$  inside the band of interest, the STF(z) = 1 and the NTF(z) = 0. This means that the signal can pass through the system without attenuation or distortion while the noise is rejected inside the band. However in practice it is not possible to completely reduce the quantization error due to gain limitations in the loop filter. Assuming an ideal  $NTF(z) = (1 - z^{-1})^L$ , where *L* is the loop order, the in-band shaped power noise is calculated by

$$P_Q = \int_{-BW}^{BW} \frac{\Delta^2}{12f_s} |NTF(f)|^2 \cdot df = \frac{\Delta^2}{12} \frac{\pi^{2L}}{(2L+1)OSR^{2L+1}}$$

(1.11)

assuming the following subtitution of the NTF(f)

$$NTF(f) = NTF(z)|_{z=e^{j2\pi f/f_s}}$$

(1.12)

In Eq.1.11, both effects oversampling and noise shaping are combined, showing a higher in-band noise reduction with the OSR than the previous Eq.1.8, which did not include the noise shaping effect. Therefore,  $\Sigma$ - $\Delta$  ADCs are able to take advantage of this combined effect that shows a higher reduction of the in-band noise and also enables a higher resolution.

From Fig.1.6, y is a modulated signal in the digital domain representing the analog discrete time (DT) of x. To complete the ADC conversion process, its high frequency spectral component must be eliminated and its rate must be shifted down to the Nyquist rate, corresponding to the Nyquist frequency of the input signal. This operation is performed in the digital domain by the so called decimator filter, which together with the modulator, composes the complete ADC Block. The analysis and the implementation of the decimator filter is out the scope of this work, the interested reader may reference [26].

#### **1.4.2** CT and DT $\Sigma$ - $\Delta$ Modulation

From the operation point of view  $\Sigma$ - $\Delta$  ADCs are classified in continuous time (CT) and discrete time (DT). The difference between them is the location of the sample and hold system (S/H). If the sampling operation is performed outside the  $\Sigma$ - $\Delta$  loop then the modulator is classified as DT  $\Sigma$ - $\Delta$ , and if its performed inside the loop the  $\Sigma$ - $\Delta$  is classified as CT. Fig.1.7 illustrates both topologies showing the position of the S/H system.

FIGURE 1.7: Discrete time (A) and Continuous time (B)  $\Sigma$ - $\Delta$  modulators block diagram.

DT realizations relying on switched-capacitor SC, present low sensitivity to clock jitter and higher robustness against process, supply-voltage and temperature (PVT) variations, mainly due to the linearity of integrated capacitors and matching-based design methodologies. Otherwise, the main drawbacks present in DT implementations are related to bandwidth limitations and the use of sampling switches which introduces non-linearites. SC implementation rely on almost complete settling of the OpAmps which happens to be at several time-constants. As the clock frequency increases this could be unfeasable from the OpAmp bandwidth point of view. CT implementations relax this aspect.

CT modulators based on active-RC and gm-C implementations have been introduced as an alternative for implementing loop filters for high bandwidth applications. Another positive aspect that makes this topology attractive is the built-in anti-aliasing filter and the absence of sampling errors. Besides these advantages, CT modulators are very sensitive to clock jitter, and also to PVT variations. Special attention must be paid to excessive loop delays in the feedback DAC to avoid instability problems.

For all these reasons DT  $\Sigma$ - $\Delta$  ADCs are preferred when a robust solution is needed.

#### **1.4.3** Classification of $\Sigma$ - $\Delta$ Modulators

Multiple efforts have been made in continuously increasing  $\Sigma$ - $\Delta$  modulators performance during the past decades, resulting in a number of different techniques:

- Low order Σ-Δ vs High order Σ-Δ ⇒ One simple way to obtain higher resolutions is to increase the order of the loop filter by adding more stages in series. In practice there are limitations in the order due to stability problems because of the path delays created in each new stage added [24][26]. Practically the order of the loop filter is less than a fifth-order.

- **Single-Loop**  $\Sigma$ - $\Delta$  **vs MASH**  $\Sigma$ - $\Delta$   $\Rightarrow$  As explained above stability problems arise when using high order simple-loop  $\Sigma$ - $\Delta$ . The problem in part can be solved by selecting the adequate scaling coefficients, but assuming a significant reduction of DR compared with an ideal  $\Sigma$ - $\Delta$  modulator. An alternative approach to obtain high order  $\Sigma$ - $\Delta$ avoiding instability problems is found in the number of quantizers.  $\Sigma$ - $\Delta$  modulators employing only one quantizer are called single-loop, whereas those employing several quantizers are often named MASH (multiple-stage noise shaping) or cascade  $\Sigma$ - $\Delta$  modulators. MASH modulators consist of N stages of  $\Sigma$ - $\Delta$  modulators, in which each stage remodulates a scaled version of the quantization error generated in the preceding one. All the outputs of the cascaded stages are processed conveniently in the digital domain by subtraction. MASH architectures gives the chance to increase the order and therefore the resolution, but at the cost of increasing the complexity of the design. Mismatch errors between different system blocks must be avoided in order to maintain the benefits explained.

In practice, for high resolution the effective order of the shaping is not achieved due to noise imperfect cancellation, causing lower shaped noise to leak in the final output.

Single-bit Σ-Δ vs Multi-bit Σ-Δ ⇒ Another approach is the use of multi-bit topologies[9][17][18] instead of the classical single bit DAC [31][28][36]. Increasing the number of bits in the quantizer not only increases the SNR but also the loop stability allowing the use of higher loop coefficients. However, since multi-bit DAC from the feedback loop is directly connected to the input of the Σ-Δ modulator, any non-linearity in the DAC can not be distinguished from the input signal and will be present at the output. Therefore, special attention to non-linearity and accuracy during the DAC design must be taken. Dynamic element matching (DEM) techniques are commonly used to tackle this problem, but they require extra circuitry representing an increase in area, power consumption and complexity. Single bit classical architectures in its counterpart don't require this extra circuitry which makes them more suitable for high linearity applications.

# 1.5 Objectives

The purpose of this thesis is focused on the realization of a Low-power 16 Bits  $\Sigma$ - $\Delta$  Modulator with a bandwidth of 50 kHz. The resulting modulator from the design process is intended to be part of an IP that could be reused in different designs, for this reason the bandwidth and the resolution requirements are high enough to cover a wide variety of applications.

The frame work of this master thesis tries to continue exploring new different ways of designing  $\Sigma$ - $\Delta$  modulators, taking as a start point a previous work done in the same research group by Stepan Sutula et. al.[32]. Many aspects of the design flow, from the architectural up to the circuital level will be revised, corrected and optimized in this work, giving degrees of freedom to explore the design space as well as to take decisions following a different path.

The previous work done by Sutula et. al. [32] [30] consist on a 4 order non-bootstraped feedforward single-bit  $\Sigma$ - $\Delta$  Modulator with Class-AB single stage switched VMAs [33], which consumes 7.9 mW and obtains 96.6 dB of SNDR from real measurements without using any calibration or analog tuning, and a Schreier FOM of 164.6 dB.

The objectives this thesis aims to achieve are declared in the next lines.

- Contribute to the development of a platform for high-level modelling based on open source software.

- Using the High level models implemented in an open source software, to explore the possibility of using a lower loop order, oversampling ratio and a different number of the quantizer bits (from 1 to 1.5), while maintaining the same performance and stability behaviour.

- Search for optimization methods focused in Bottom-up design flows instead of the Top-down classical approach [34], trying to reduce simulation times and increasing the design efficiency.

- Mapping the physical implementation to a 180 nm 1P6M technology from Xfab, including triple MiM<sup>1</sup> capacitors which allows a significant area reduction, with respect to the previously used technology (UMC 180 nm single MiM).

- Continuing exploring the benefits of using the different types of Class-AB switched Variable Mirror Amplifier (SVMA) introduced in [32]. Increasing the Class-AB coefficient while reducing as much as possible the power consumption.

The performance requirements of the  $\Sigma$ - $\Delta$  Modulator are summarized in table 1.1.

| Modulator architecture               | Single-loop Feed-forward |

|--------------------------------------|--------------------------|

| Bandwidth                            | 50 kHz                   |

| <b>Over Sampling Ratio</b>           | 128                      |

| Input signal fullscale               | >2 V p-to-p differential |

| Target SNDR peak                     | 16 Bits                  |

| <b>Circuit level characteristics</b> | Switched Capacitors,     |

|                                      | Switched OpAmp,          |

|                                      | Non-bootstrapping,       |

|                                      | No analog calibration,   |

|                                      | Resistor-less            |

TABLE 1.1: Initial specifications and characteristics of the $\Sigma$ - $\Delta$  Modulator of this thesis.

# **1.6 Design methodologies**

In order to handle the increasing complexity of analog and mixed-signal IC design, a clear definition of a hierarchical design flow is essential. Despite the advances made during the last decades, the design automation tools in analog domain cannot support the complete design process[10].

Since then and specially in the case of  $\Sigma$ - $\Delta$  Modulator, the intervention of a designer with a complete systematic design method and a series of customized tools are required.

Traditionally, analog circuit design has been done following two systematic design flows, Top-down and Bottom-up. Top-down methodologies can be defined as the natural way to approach a complex design. Defining the requirements needed and spending time in developing system-level models and verification environments before planing the sub-blocks division and starting the simulations.

Bottom-up flow methodologies decompose the design in different subblocks, which constitute a simple and independent design units. Setting the requirements of each individual block, the transistor level design can be done in parallel by several design teams. Each block is verified as a standalone unit against the specifications and integrated with the rest of

<sup>&</sup>lt;sup>1</sup>Metal Insulator Metal (MiM) capacitors are implemented using the parasitic capacitance between two conductors on a metal layer. Several metal layers are connected in parallel by vias, forming a vertical metal wall or mesh which increases the capacitance density (capacitance per unit area of silicon chip)

individuals as a system. Verification of the overall system is performed to ensure the correct behaviour of the final design.

$\Sigma$ - $\Delta$  Modulator design procedures traditionally use Top-down methodologies[34]. But in the case of this work both techniques are used in combination to improve the design procedures and also to reduce the simulation times. The synthesis procedure together with the software environments, followed in this work are schematically shown in Fig.1.8.

FIGURE 1.8: Design flow diagram adopted in this work. Design tasks have been mapped to their respective design environment.

Different functions are performed in each individual block shown in the synthesis procedure. The description of each stage is presented in the next list.

- System specifications ⇒ Is the first phase of the design and includes all the requirements imposed in the design. At this stage topological or architectural solutions to be used in the next stage are discussed.

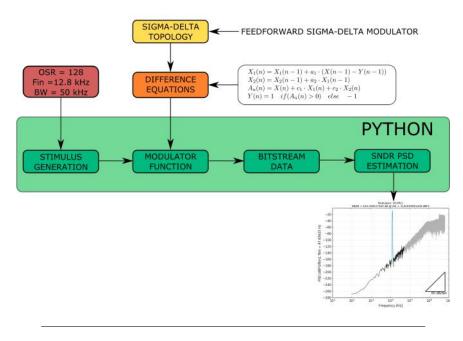

- High level design ⇒ It has the main task to calculate the different equations in discrete time domain for a quite large number of clock cycles, since, as described in the previous sections, the Σ-Δ Modulation operates an oversampling over the original signal bandwidth.

Includes the different theoretical models used in the architectural synthesis and also the performance and verification tests. Behavioural simulation programs such as Matlab Simulink [25] are normally used. But in this work following an open source solution Python proves to be a good candidate. Therefore, the high level simulation core is coded using a friendly distribution of Python which includes all the necessary to compile on the fly the written code. In the case of this work, the optimization core block represents the analytical function done by a designer taking the proper design decisions based on simulation results. While the High level simulation core contains the different functions used to simulate the different  $\Sigma$ - $\Delta$  Modulator topologies.

The design flow in first place explores the different topologies selected during the system specification and confirms the expected behaviour. After the candidates are synthesised and simulated using the simulation core the next step is to test the robustness against coefficient mismatch, jitter, settling errors and feedback DAC reference errors. A re-evaluation of the different coefficients selected is possible if the requirements are not satisfied.

Mixed Block/Circuit Design ⇒ Cadence Verilog-A represents the intermediate step point between the high level simulations and the circuit level design [8]. Is the link between the numerical simulations done in Python and the electrical simulations in Cadence. Verilog-A is a behavioural kind of language used in electrical simulations to describe the behaviour of any analog or digital block. Verilog-A is simulated in the same environment as the circuit level design using Cadence virtuoso.

Classically, the  $\Sigma$ - $\Delta$  Modulator is divided in different blocks following the indications of Top-down methodologies. Each independent block is described using Verilog-A to form the complete system. When the hole system is described, the next step is to start simulating.

The main optimization and tests during the design are done in the mixed/signal stage by substituting each block by its circuit level counterpart and maintaining the rest of blocks in Verilog-A. Therefore, the block of interest is optimized while the rest remains ideal i.e. with a negligible contribution to the non-idealities and linearity of the circuit.

The simulations performed in this part are less time consuming than substituting all the blocks with the transistor level designs. But are high enough to represent a drawback in the optimization process. For this reason in the next point an alternative to the classical approach is presented.

Circuit level design ⇒ The transistor level design of each individual block selected in the previous stage is simulated and optimized in this stage. As explained above, the classical approach begins by substituting the previous ideal block by its real counterpart maintaining ideal views in the rest of blocks.

The new approach represented in Fig.1.8 using blue lines, is mainly based on the electrical extraction of the main characteristics in form of curves, based on a reduced schematic and on short full-electrical transient simulations. The curves can be passed to the high level models and used to evaluate the block performance by doing lengthy simulations in terms of numer of clock cycles.

The simulation time is drastically reduced allowing the evaluation of different solutions in a short period of time. Therefore the optimization process is fessable using the proposed method. This Bottom-up method is also compatible with the traditional design flow of using Verilog-A as an intermediate point.

Physical Design ⇒ The circuit level design represents the characteristics and disposition of each component. In order to be able to manufacture the design the components are converted to its geometrical representations separating each material or process in a different layer.

The first step inside the layout is the floorplaning which consist in the division of the chip into small blocks. The process of identifying each structure and the connection requirements is essential to meet the available space without losing performance.

The following step consist in the placement of each component inside the blocks defined in the floorplaning. The position of the different components is a key point to avoid future problems of performance and routing conflicts.

After the routing a design verification is performed to ensure the correct behaviour of the final design. Different verification test are used to ensure the layout compliance with all the technological requirements (Design Rule Checking DRC), the consistency with the original netlist (Layout vs Schematic LVS) and with all the electrical requirements (Electrical Rule Checking ERC).

- **Fabrication** ⇒ The final design is send to the factory to start the manufacturing process. Normally the foundry uses its own verification tools to ensure the design is able to be processed. After confirming the viability of the design the order start the process.

- Packaging and testing ⇒ Represents the last step in the fabrication process and consist in the encapsulation of the silicon wafer to a supportive case which prevents physical damage and corrosion. The encapsulation or package not only supports the silicon but also allows to stablish the electrical contacts between the IC and a circuit board.

The testing compromises all the steps and elements used as a test vehicle to prove the expected performance.

Chip ⇒ Finally after the achievement of all the different stages the design is completed in the shape of a chip.

The present work covers almost all the stages of the design but others are sorted due to time constrains. The sorted stages are the captions shown in Fig.1.8 filled in yellow.

### **1.7** Structure of the Work

This thesis is organized in 6 chapters.

• Chapter 2: Measurements

Real measurements across temperature with  $\Sigma$ - $\Delta$  modulator designed presented in [32] [30]. Robusness comprovation and extraction of conclusion used during the former design process.

• Chapter 3: High level  $\Sigma$ - $\Delta$  modelling

High level  $\Sigma$ - $\Delta$  modulator modelling of the different topologies selecting the best candidate after performing robustness and optimization tests.

Chapter 4: Circuit level design

Transistor level description of each individual block that comforms the complete  $\Sigma$ - $\Delta$  modulator.

• Chapter 5: Simulation results

Description of the novel optimization process followed during the design. Explanation and optimization of the different SVMA candidates used in the complete  $\Sigma$ - $\Delta$  modulator system. Simulation results presentation including corners.

• Chapter 6: Conclusions

Review of the different design steps, conclusions and future work.

# Chapter 2

# Measurements

As already stated in the first chapter of this work, the starting point was the design presented in [32] [30] developed within the ICAS group at IMB-CNM. Since only few proof of concept measurements were previously performed, a good starting point for this work can be the measurement against temperature variations of the previous design chip. Avoiding the large fabrication cycle required for microelectronics manufacturing and allowing to gain a valuable experience for the new design, as well as on the experimental characterization of sigma-delta ADCs such as the one designed in this work. Therefore, the current section is intended to show how  $\Sigma$ - $\Delta$  Modulator performance is measured demonstrating the robustness against variations in temperature.

### **2.1** $\Sigma$ - $\Delta$ performance metrics

In  $\Sigma$ - $\Delta$  modulators different performance metrics based on dynamic measurements are used, rather than static measurements used low-frequency Nyquist ADCs. The metrics are obtained from the frequency domain representation of the time-domain digital output sequence. An example of a typical output spectrum and its main characteristics is illustrated in Fig.2.1.

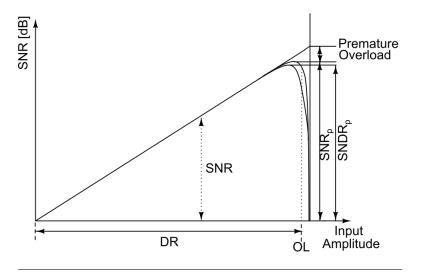

FIGURE 2.1: Typical  $\Sigma$ - $\Delta$  Modulator power spectral density with performance metrics.

The most important measures extracted from the output spectrum are collected in the following list and illustrated in Fig.2.2:

Signal-to-noise-ratio (SNR) ⇒ The SNR is the ratio of the input signal power to the noise power measured inside the band (IBN), accounting only for the modulator linear performance without the in-band power associated to harmonics of the input signal. The maximum SNR a converter can achieve is called the peak signal-to-noise-ratio (SNR<sub>p</sub>).

$$SNR(dB) = 10 \cdot \log_{10}(\frac{P_{signal}}{IBN})$$

(2.1)

- Signal-to-noise-and-distortion-ratio (SNDR) ⇒ The SNR is the ratio of the input signal power to the total noise power measured inside the band (IBN). Accounting for all the possible harmonics present at the Σ-Δ modulator output. The maximum SNDR a converter can achieve is called the peak signal-to-noise-and-distortion-ratio (SNDR<sub>p</sub>).

- Dynamic Range (DR) ⇒ The DR is the ratio between the maximum input signal power which can be applied without a significant performance degradation and the minimum detectable input signal power. Assuming a 3 dB of drop from the SNR peak as a significant performance degradation. From Eq.1.11 and Eq.2.1 the DR expression in dB as function of the loop order *L*, the number of bits *B* and the oversampling ratio *OSR* is obtained as follows

$$DR(dB) = 10 \cdot \log_{10}(\frac{3(2^B - 1)^2(2L + 1)OSR^{2L + 1}}{2\pi^{2L}})$$

(2.2)

In Practice when the  $\Sigma$ - $\Delta$  modulator performance is assessed, the DR is obtained from the evaluation of the SNDR plot as function of the input signal amplitude, represented in Fig.2.2.

Effective number of Bits (ENOB) ⇒ Similar to the given expression for an ideal Nyquist ADC (Eq.1.5), there is an expression established for Σ-Δ modulators, where the ENOB can be defined as the number of bits needed for an ideal Nyquist ADC to achieve the same DR as the Σ-Δ ADC

$$ENOB = \frac{DR(dB) - 1.76}{6.02}$$

(2.3)

• **Overload Level (OL)** ⇒ The overload level is the relative input where the SNR decreases by 3 dB from the SNR peak

FIGURE 2.2: Graphical representation of the most important performance metrics of  $\Sigma$ - $\Delta$  ADC.

As observed in Fig.2.2, the SNDR plot versus the input signal amplitude offers a wide variety of relevant information about the final performance of the designed  $\Sigma$ - $\Delta$  modulator. Among all these different metrics the most important parameter is the peak SNDR which gives the instantanious resolution for the maximum amplitude allow by the modulator. Generally the DR which is the horizontal measurement of the converter resolution takes very similar values to the peak SNDR since the SNDR versus input amplitude is typically a linear function with unitary slope.

### **2.2** $\Sigma$ - $\Delta$ Modulator expected Performance

The previous work done by Sutula et.al.[32] [30] consists in a 4th order 50 kHz bandwidth non-bootstrapped single-bit  $\Sigma$ - $\Delta$  Modulator, which obtains experimental 96.6 dB of SNDR operating at 1.8 V and consuming 7.9 mW. Simulation results (Table.2.1) for the full set of technology and temperature corners of the fabricated  $\Sigma$ - $\Delta$  Modulator exhibit a very low sensitivity.

|        | Slow     | Typical  | Fast     |

|--------|----------|----------|----------|

| -40 °C | 110.2 dB | 109.2 dB | 109.2 dB |

| 27 °C  | 110.6 dB | 111.3 dB | 110.7 dB |

| 80 °C  | 110.7 dB | 109.3 dB | 109.6 dB |

TABLE 2.1:  $\Sigma$ - $\Delta$  Modulator SNDR simulated under process and temperature variations.

However, the post-layout simulations for the typical process show a substantial drop of the SNDR down to 103 dB. Therefore, lower SNDR value and tendency with the temperature is expected in the real measurements. Furthermore, the design of [32] lacks of on-chip decoupling capacitors which contributes to degrade even mode the SNDR.

### **2.3** $\Sigma$ - $\Delta$ Test Vehicle

The Test Vehicle is used as interface between the chip and the external equipment needed to measure the design performance. This platform includes the circuitry that generates all the voltage and current references and also the interface used to capture the bit-stream from the  $\Sigma$ - $\Delta$  Modulator.

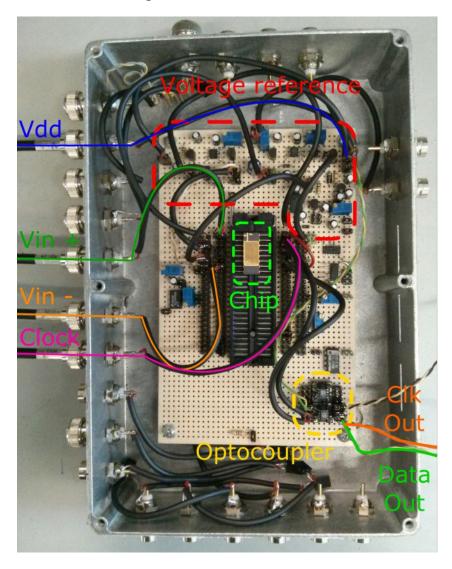

The same prototype board of [32] was used here, however all the cable connections have been revised and enhanced to avoid as much as possible distortion and noise coupling deriving from the cables themselves.

Clear limitations are evident at this point, however a fast prototyping was preferred over a dedicated PCB design in order to accomplish with time limitations.

#### 2.3.1 Test Vehicle Equipment

Different equipments have been used during the measurements, this subsection tries to summarize their main characteristics including a brief description of their use in the measurements.