University of Warwick institutional repository: http://go.warwick.ac.uk/wrap

### A Thesis Submitted for the Degree of PhD at the University of Warwick

http://go.warwick.ac.uk/wrap/3773

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

### Predictive Analysis and Optimisation of Pipelined Wavefront Applications Using Reusable Analytic Models

by

### Gihan Ravideva Mudalige

A thesis submitted to the University of Warwick in partial fulfilment of the requirements for admission to the degree of

**Doctor of Philosophy**

### **Department of Computer Science**

University of Warwick

July 2009

### **Abstract**

Pipelined wavefront computations are an ubiquitous class of high performance parallel algorithms used for the solution of many scientific and engineering applications. In order to aid the design and optimisation of these applications, and to ensure that during procurement platforms are chosen best suited to these codes, there has been considerable research in analysing and evaluating their operational performance.

Wavefront codes exhibit complex computation, communication, synchronisation patterns, and as a result there exist a large variety of such codes and possible optimisations. The problem is compounded by each new generation of high performance computing system, which has often introduced a previously unexplored architectural trait, requiring previous performance models to be rewritten and reevaluated.

In this thesis, we address the performance modelling and optimisation of this class of application, as a whole. This differs from previous studies in which bespoke models are applied to specific applications. The analytic performance models are generalised and reusable, and we demonstrate their application to the predictive analysis and optimisation of pipelined wavefront computations running on modern high performance computing systems.

The performance model is based on the LogGP parameterisation, and uses a small number of input parameters to specify the particular behaviour of most wavefront codes. The new parameters and model equations capture the key structural and behavioural differences among different wavefront application codes, providing a succinct summary of the operations for each application and insights into alternative wavefront application design.

The models are applied to three industry-strength wavefront codes and are validated on several systems including a Cray XT3/XT4 and an InfiniBand commodity cluster. Model predictions show high quantitative accuracy (less than 20% error) for all high performance configurations and excellent qualitative accuracy.

The thesis presents applications, projections and insights for optimisations using the model, which show the utility of reusable analytic models for performance engineering of high performance computing codes. In particular, we demonstrate the use of the model for: (1) evaluating application configuration and resulting performance; (2) evaluating hardware platform issues including platform sizing, configuration; (3) exploring hardware platform design alternatives and system procurement and, (4) considering possible code and algorithmic optimisations.

## to my parents and grandmother with love and gratitude

### Acknowledgements

I am indebted to many people for the help, advice, guidance, support and friendship they have provided me during the course of this work. Several have made special contributions, influencing not only my thesis work but also my technical and professional development in research and computer science. It is a privilege to acknowledge them here.

My supervisor, Dr. Stephen Jarvis, first guided me to conduct research in this area, giving me the opportunity to work in the High Performance Systems Group at Warwick and provided a never-ending source of optimism, good-will and guidance. I am truly grateful for his support, advice and encouragement.

Prof. Mary Vernon, my advisor, during the research fellowship year at the University of Wisconsin-Madison has been an inspiration for developing analytic models. I am sincerely indebted to her for giving me the opportunity to work at Madison and for the many long hours of discussions, advice and motivation.

I am grateful to Dr. Daniel Spooner for acting as my second supervisor, particularly for his advice during the early years of my degree.

A special vote of thanks should go to my colleague and fellow labmate, Simon Hammond for his relentless hard work, support and the many hours of discussions during our research collaborations.

I would like to acknowledge and thank Jon Holt, Andy Herdman, Ash Vadgama and Ben Ralston of the Parallel Technology Support team at AWE for providing us with access to the Chimaera benchmark code as well as supporting our research with valuable comments. Additionally I am thankful to Patrick H. Worley for giving us access to the ORNL Cray XT3/XT4 under the PEAC project, Howard Pritchard for his comments on the Cray XT3/XT4 and David Sundram-Stukel for his comments during the development of the reusable analytic model.

It is a pleasure to acknowledge the many members and colleagues of the High Performance Systems Group both past and present including, Dr. Ligang He, Dr. Guang Tan, Dr. David Bacigalupo, Dr. Graham Nudd, Dr Nathan Griffiths, Dr Arshad Jhumka, Dr. Elizabeth Ogston, Dr. Tongcheng Guo, Jonathan Smith, Justin Dyson, Xenu Chen, Peter Wong, Jonathan Byrd, Brian Foley, Paul Isitt, Lei Zhao, James Wen Jun Xue, Adam Chester, Matthew Leeke, Alistair Mills and Mohammed Al Ghamdi.

I would also like to acknowledge the support of my many friends, particularly Dr. Dhammika Widanage and Matthew Higgins for the supportive discussions and guidance during my PhD years.

Finally, my profound appreciation goes to my parents and my grandmother. My father whose perfectionism in his work will be a continuing source of inspiration to me, my mother whose love, support and limitless optimism shatters the daunting perception of even the most impossible undertaking and my grandmother who brought me up during my school days with love and unending compassion. I dedicate this thesis to them, with love and gratitude.

### **Declarations**

This thesis is presented in accordance with the regulations for the degree of Doctor of Philosophy. It has been composed by myself and has not been submitted in any previous application for any degree. The work described in this thesis has been undertaken by myself except where otherwise stated.

Portions of this work have been published in the following publications:

#### Parts of Chapter 2 in [1]:

S.A. Jarvis, D.P. Spooner, G.R. Mudalige, B.P. Foley, J. Cao, and G.R. Nudd. Performance Evaluation of Parallel and Distributed Systems, chapter *Performance Prediction Techniques for Large-scale Distributed Environments*. Mohamed Ould-Khaoua and Geyong Min Eds. Nova Science, 2005.

#### Chapters 3, 4 and 5 in [2]:

G.R. Mudalige, M.K. Vernon, and S.A. Jarvis. A Plug-and-Play Model for Evaluating Wave-front Computations on Parallel Architectures. In *IEEE International Parallel and Distributed Processing Symposium (IPDPS 2008)*. April, 2008. IEEE Computer Society.

#### Chapter 6 in [3]:

G.R. Mudalige, S.A. Jarvis, D.P. Spooner, and G.R. Nudd. Predictive Performance Analysis of a Parallel Pipelined Synchronous Wavefront Application for Commodity Processor Cluster Systems. In *Proc. IEEE International Conference on Cluster Computing - Cluster*2006, Barcelona, September 2006. IEEE Computer Society.

#### Parts of Chapter 7 in [4]:

S.D. Hammond, G.R. Mudalige, J.A. Smith, and S.A. Jarvis. Performance prediction and procurement in practise: Assessing the suitability of commodity cluster components for wavefront codes. In *Proc. Performance Engineering Workshop 08 (UKPEW)*, Imperial College, London, July 2008. Also accepted for publication in *IET Software* 2009.

#### and in [5]:

G.R. Mudalige, S.D. Hammond, J.A. Smith, and S.A. Jarvis. Predictive Analysis and Optimisation of Pipelined Wavefront Computations. In *Proc. 11th Workshop on Advances in Parallel and Distributed Computational Models (APDCM 2009)*, held as part of the 23rd IEEE International Parallel and Distributed Processing Symposium (IPDPS 2009), Rome, Italy, May 2009. IEEE Computer Society. Also invited for publication in the International Journal of Parallel, Emergent and Distributed Systems (IJPEDS), 2010. Taylor and Francis Publications.

Other work that has been conducted as part of this research has been published in:

[6] S.D. Hammond, G.R. Mudalige, J.A. Smith, and S.A. Jarvis. WARPP - A Tool Kit for Simulating High-Performance Parallel Scientific Codes. *In Proc. 2nd International Conference on Simulation Tools and Techniques (SIMUTools 2009)*, Rome, Italy, March 2009. ACM Press.

[7] S.D. Hammond, J.A. Smith, G.R. Mudalige, and S.A. Jarvis. Predictive Simulation of HPC Applications. In *The IEEE 23rd International Conference on Advanced Information Networking and Applications (AINA 2009)*, Bradford, U.K., 26-29 May 2009. IEEE Computer Society.

### Sponsorship and Grants

The research in this thesis was part-sponsored by research grants from:

The University of Warwick Department of Computer Science Fellowship (2004-2005), The Warwick Postgraduate Research Fellowship (WPRF) (2005-2006 and 2007-2008), The Overseas Research Student Fellowship (ORS) by the Government of the U.K. (2004-2006 and 2007-2008), The Warwick, Wisconsin-Madison Research Fellowship (2006-2007) and The National Science Foundation (NSF), U.S. under grant CNS-0435437.

Access to the Chimaera benchmark was provided by the Atomic Weapons Establishment (AWE) U.K. under grants CDK0660 (*The Production of Predictive Models for Future Computing Requirements*) and CDK0724 (*AWE Technical Outreach Program*).

This research work used resources at the National Centre for Computational Sciences (NCCS) at the Oak Ridge National Laboratory (ORNL), which is supported by the Office of Science of the U.S. Department of Energy (DOE) contract DE-ASC05-00OR22725 under the Performance Evaluation and Analysis Consortium (PEAC).

This research also made use of resources at the Centre for Scientific Computing (CSC) at the University of Warwick under the Science Research Investment Fund and Joint Research Equipment Initiative under grant JR00WASTEQ.

### **Abbreviations**

API - Application Programming Interface

ASC - Advanced Simulation and Computing Program

AWE - Atomic Weapons Establishment (U.K)

BLAS - Basic Linear Algebra Subprograms

BSP - Bulk Synchronous Parallel (model)

CFDs - Computational Fluid Dynamics

CHIP<sup>3</sup>S - Characterisation Instrumentation for Performance Prediction of Parallel Systems

CMP - Chip Multi-Processor

CNL - Compute Node Linux

CRCW - Concurrent Read Concurrent Write

CREW - Concurrent Read Exclusive Write

DMA - Direct Memory Access

EPCC - Edinburgh Parallel Computing Centre

EREW - Exclusive Read Exclusive Write

FFT - Fast Fourier Transforms

FLOPS - Floatingpoint Operations per Second

HMCL - Hardware Model Characterisation Language

HPC - High Performance Computing

HPF - High Performance FORTRAN

IMB - Intel MPI Benchmark

ILP - Instruction level parallelism

LAN - Local Area Network

LANL - Los Alamos National Laboratory (U.S)

LAPACK - Linear Algebra Package

LU - Lower and Upper triangular system solution application benchmark in NPB

MFLOPS - Millions of Floating-Point Operations per Second

MIMD - Multiple Instruction (stream) Multiple Data (stream)

MIPS - Millions of Instructions per Second

MISD - Multiple Instruction (stream) Single Data (stream)

MTU - Maximum Transmission Unit

MPI - Message Passing Interface

MPMD - Multiple Program Single Data

MPP - Massively Parallel Processor

MTU - Maximum Transmission Unit

MVA - Mean Value Analysis

NPB - NASA's Aerodynamic Simulation Parallel Benchmarks

NIC - Network Interface Card

NoW - Network of Workstations

NUMA - Non Uniform Memory Access

ORNL - Oak Ridge National Laboratory (U.S)

PACE - Performance Analysis and Characterisation Environment

PAPI - Performance Application Programming Interface

PBB - Purpose Bases Benchmarks

PGAS - Partitioned Global Address Space

PRAM - Parallel Random Access Machine

PSL - Performance Specification Language

PVM - Parallel Virtual Machine

QoS - Quality of Service

SDR - Single Data Rate

SIMD - Single Instruction (stream) Multiple Data (stream)

SISD - Single Instruction (stream) Single Data (stream)

SMP - Symmetric Multi Processor

SPEC - Standard Performance Evaluation Corporation

SPMD - Single Program Multiple Data

SSOR - Successive Over-Relaxation

UMA - Uniform Memory Access

WAN - Wide Area Network

WarPP - Warwick Performance Prediction toolkit

### **Notations**

| C                  | Number of cores on a CMP(section 4.3.3)                                                                                                                      |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

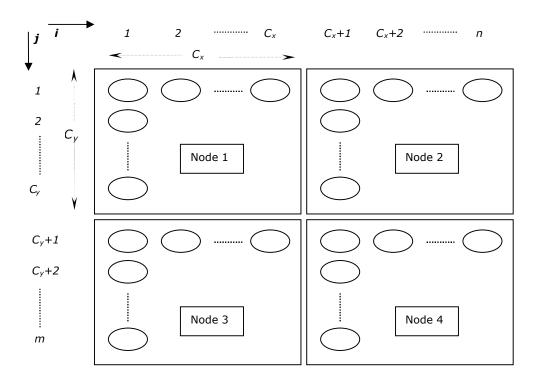

| Cx                 | Number of cores in the $x$ dimension on a CMP (section 4.6)                                                                                                  |

| Cy                 | Number of cores in the $y$ dimension on a CMP (section 4.6)                                                                                                  |

| G                  | LogGP parameter: <i>Gap per byte</i> defined as the time taken to transmit a byte on to the network (section 2.3.4)                                          |

| $G_{copy}$         | Gap per byte for a memory copy on-chip (section 4.3.2)                                                                                                       |

| $G_{dma}$          | Gap per byte for a DMA transfer on-chip(section 4.3.2)                                                                                                       |

| $H_{tile}(cells)$  | Height of the tile in the $z$ dimension (section 4.2)                                                                                                        |

| it,jt,kt           | Number of grid cells in $x,y$ and $z$ dimension for Sweep3D (section 3.1.2)                                                                                  |

| I                  | NIC contention (interference) time (section 4.6)                                                                                                             |

| L                  | LogGP parameter: the upper bound on the <i>latency</i> of the network the flight time for a message from one point of the network to another (section 2.3.4) |

| m                  | Number of processors along the $y$ dimension of the 2D processor array (section 3.1.2)                                                                       |

| mmi                | Number of angles solved per sweep step in Sweep3D (section 3.2.2)                                                                                            |

| mk                 | Height of the tile in the $z$ dimension for Sweep3D (section 3.2.2)                                                                                          |

| $MessageSize_{EW}$ | Message size (East-West or West-East) (section 4.2)                                                                                                          |

| $MessageSize_{NS}$ | Message size (North-South or South-North) (section 4.2)                                                                                                      |

| n                  | Number of processors along the $\boldsymbol{x}$ dimension of the 2D processor array (section 3.1.2)                                                          |

| $n_{diag}$         | Number of sweeps that completes from corner up to and including the main diagonal (section $4.2$ )                                                           |

| $n_{full}$         | Number of sweeps that completes fully (from corner to opposite corner) (section $4.2$ )                                                                      |

| $no\_of\_Kblocks$  | Number of tiles on a processor stack in the Sweep3D analytic model in $\[8\]$ (section 4.2)                                                                  |

| $n_{sweeps}$       | Total number of sweeps (section 4.2)                                                                                                                    |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| $N_x, N_y, N_z$    | Number of grid cells in $x$ , $y$ and $z$ dimension (section 3.1.2)                                                                                     |

| O                  | LogGP parameter: the <i>overhead</i> time taken by a processor to transmit/receive a message. (section 2.3.4)                                           |

| $o_{c2NIC}$        | Time to setup a, DMA or other, copy of the message data between kernel memory and the NIC and to prepare or process the message header (section 4.3.1)  |

| $o_{copy}$         | Processing time before and after the message copies on the sender and the receiver on-chip (section 4.3.2)                                              |

| $o_{dma}$          | Overhead of setting up a DMA or other, copy of the message data between kernel memory and the NIC on-chip (section 4.3.2)                               |

| $O_h$              | The processing time for a handshake request or reply, including the time to prepare a new message header (section 4.3.1)                                |

| $o_{init}$         | Overhead for a message copy between application and kernel (section $4.3.1$ )                                                                           |

| P                  | LogGP parameter: number of processors (section 2.3.4)                                                                                                   |

| $P_r$              | Probability that a processor takes $W_r$ time to complete a block of cells of height $H_{tile}$ (section 7.4.1)                                         |

| R                  | Execution time for a single simulation (section 5.2)                                                                                                    |

| Receive            | Time to obtain a message from the network (section 4.2)                                                                                                 |

| Send               | Time to release a message to the network (section 4.2)                                                                                                  |

| $StartP_{i,j}$     | Time to begin the main computation on processor $(i, j)$ (section 4.2)                                                                                  |

| $T_{allreduce}$    | Time to complete an MPI allreduce operation (section 4.3.3)                                                                                             |

| $T_{diagfill}$     | Time gap between starting a sweep at a corner processor and the first wavefront of that sweep reaching up to the main diagonal processors (section 4.2) |

| $T_{fill}$         | Time for a wavefront operating on a 1D processor array to arrive from one end processor to the opposite side processor (section 4.5)                    |

| $T_{fullfill}$     | time gap between starting a sweep at a corner processor and the first wavefront of that sweep reaching the opposite corner processor (section 4.2)      |

| $T_{nonwavefront}$ | Time to complete non-wavefront portions (section 4.2)                                                                                                   |

| $Total\_Comm$      | End to end communication time (section 4.2)                                                                                                             |

| $T_{stack}$ | Time taken by a processor to solve its stack of tiles (section 4.2)                |

|-------------|------------------------------------------------------------------------------------|

| $W_g$       | A grid cell computation time (main computation block) (section 4.2)                |

| $W_{g,pre}$ | A grid cell computation time (pre-computation block) (section 4.2)                 |

| $W_{g,rhs}$ | A grid cell computation time (LU RHS computation block) (section $4.7.1$ )         |

| X           | Total number of simulations that complete per unit time (throughput) (section 5.2) |

| $\eta$      | Number of overlapping simultaneous sweeps (section 7.3.2)                          |

### **Contents**

| Abstract                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowled                                                           | lgements iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Declaration                                                         | ns v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Sponsorsh                                                           | p and Grants vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Abbreviati                                                          | ons vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Notations                                                           | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Contents                                                            | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| List of Figu                                                        | ures xv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| List of List                                                        | ings xvii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| List of Tab                                                         | es xix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.1 Mo<br>1.1<br>1.2 Th<br>1.3 Th<br>1.4 Th<br>Chapter 2<br>2.1 Int | .2 Reusable Performance Models esis Contributions .2 Sesis Limitations .3 Sesis Limitations .4 Sesis Overview .5 Performance Analysis and Prediction .7 roduction .7 roduction .7 rallel Computing and Parallel Programs .7 Parallel Computing Architectures .7 Parallel Programming Models and Languages .8 Parallel Programming Models and Languages |

| 2.3 Pe<br>2.3<br>2.3<br>2.3<br>2.3                                  | rformance Engineering Methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.4<br>2.4<br>2.4<br>2.4                                            | 2.4.1.3 Profiling       26         .2 Statistical Analysis       28         .3 Simulation       28         .4 Analytic Modelling       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5               | Discussion                                                       | 32                                                   |

|-------------------|------------------------------------------------------------------|------------------------------------------------------|

| Chapter           | 23 Pipelined Wavefront Computations                              | 35                                                   |

| 3.1               | Pipelined Wavefront Sweeps                                       | 35                                                   |

|                   | 3.1.1 Wavefront Sweeps on 2D Data Grids                          | 35                                                   |

|                   | 3.1.2 Wavefront Sweeps on 3D Data Grids                          | 37                                                   |

| 3.2               | Pipelined Wavefront Applications                                 | 41                                                   |

| 5.2               |                                                                  |                                                      |

|                   | 3.2.1 NPB - LU                                                   | 41                                                   |

|                   | 3.2.2 Sweep3D and Chimaera                                       | 44                                                   |

| 3.3               | Related Work                                                     | 47                                                   |

| Chanter           | 4 A Plug-and-Play Reusable Analytic Model                        | 51                                                   |

| _                 | Application Parameters                                           | 51                                                   |

| 4.1               |                                                                  |                                                      |

| 4.2               | Reusable Model: Single Core                                      | 54                                                   |

| 4.3               | The Cray XT3/XT4 and MPI Communications Performance              | 59                                                   |

|                   | 4.3.1 MPI Send/Receive: Off-node                                 | 62                                                   |

|                   | 4.3.2 MPI Send/Receive: On-chip                                  | 64                                                   |

|                   | 4.3.3 MPI Allreduce                                              | 65                                                   |

| 4.4               | Measuring Computation Performance                                | 68                                                   |

|                   |                                                                  |                                                      |

| 4.5               | Deriving a Model for 2D Regular Orthogonal Grids                 | 70                                                   |

| 4.6               | Extending the Reusable Model to CMP Nodes on the XT4             | 71                                                   |

| 4.7               | Model Validations                                                | 74                                                   |

|                   | 4.7.1 NPB - LU                                                   | 74                                                   |

|                   | 4.7.2 Sweep3D                                                    | 75                                                   |

|                   | 4.7.3 Chimaera                                                   | 76                                                   |

|                   |                                                                  |                                                      |

|                   | 4.7.4 Discussion on Validation Results                           | 78                                                   |

| 4.8               | Summary                                                          | 79                                                   |

| Chapter           | 5 Wavefront Application and Platform Design                      | 80                                                   |

| 5.1               |                                                                  | 80                                                   |

|                   | Application Design: Htile                                        |                                                      |

| 5.2               | Platform Sizing and Configuration                                | 83                                                   |

| 5.3               | Platform Design: Multi-core Nodes                                | 87                                                   |

| 5.4               | Application Bottlenecks                                          | 88                                                   |

| 5.5               | Sweep Structure Re-design                                        | 91                                                   |

| 5.6               | Summary                                                          | 93                                                   |

| 0.0               | Summary                                                          | ,,,                                                  |

| Chapter           | 6 Wavefront Simulation Models                                    | 94                                                   |

| 6.1               | The PACE Discrete Event Simulation System                        | 94                                                   |

| 6.2               | A PACE Model for Sweep3D                                         | 97                                                   |

| 6.3               | Enhancing the Predictive Accuracy of PACE for Modern HPC Systems | 103                                                  |

| 6.4               | The WarPP Simulation Toolkit                                     | 107                                                  |

|                   |                                                                  |                                                      |

| 6.5               |                                                                  | 109                                                  |

| Chapter           | Summary                                                          |                                                      |

|                   | ·                                                                |                                                      |

|                   | 7 Optimisations and System Procurement                           | 111                                                  |

| 7.1               | 7 Optimisations and System Procurement Introduction              | <b>111</b><br>111                                    |

| 7.1<br>7.2        | 7 Optimisations and System Procurement Introduction              | <b>111</b><br>111<br>111                             |

| 7.1               | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>111<br>113                             |

| 7.1<br>7.2        | 7 Optimisations and System Procurement Introduction              | <b>111</b><br>111<br>111                             |

| 7.1<br>7.2        | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>111<br>113                             |

| 7.1<br>7.2        | 7 Optimisations and System Procurement Introduction              | <b>111</b> 111 111 113 114                           |

| 7.1<br>7.2<br>7.3 | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>113<br>114<br>115                      |

| 7.1<br>7.2<br>7.3 | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>113<br>114<br>115                      |

| 7.1<br>7.2<br>7.3 | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>113<br>114<br>115<br>118<br>119        |

| 7.1<br>7.2<br>7.3 | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>113<br>114<br>115<br>118<br>119<br>121 |

| 7.1<br>7.2<br>7.3 | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>113<br>114<br>115<br>118<br>119        |

| 7.1<br>7.2<br>7.3 | 7 Optimisations and System Procurement Introduction              | 111<br>111<br>113<br>114<br>115<br>118<br>119<br>121 |

| 7.6                                              | 7.5.2 Computation, Latency and Bandwidth                                                                                                                                                     | 123<br>125                                           |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 8.1<br>8.2                                       | r 8 Conclusions and Future Work Contributions and Conclusions Future Work 8.2.1 Further Validations and Model Extensions 8.2.2 Future Work on Wavefront Computations                         | 126<br>128<br>128<br>128<br>129                      |

| Bibliog                                          | raphy                                                                                                                                                                                        | 141                                                  |

| A.1<br>A.2<br>A.3<br>A.4<br>Append<br>B.1<br>B.2 | dix A Modelling Contention on CMPs  Dual Core CMP  Quad Core CMP  8 Core CMP  16 Core CMP  tix B Model Validations  Chimaera Validations  Sweep3D Validations  dix C cflow work from sweep.x | 142<br>143<br>144<br>144<br>147<br>147<br>148<br>150 |

| D.1<br>D.2<br>D.3<br>D.4<br>D.5<br>D.6           | Single Core Model  2D Model                                                                                                                                                                  | 153<br>153<br>153<br>153<br>154<br>154<br>155<br>155 |

| E.1                                              |                                                                                                                                                                                              | 156<br>156<br>156                                    |

### **List of Figures**

| 1.1        | Operation of a Wavefront computation                                                                   | 3        |

|------------|--------------------------------------------------------------------------------------------------------|----------|

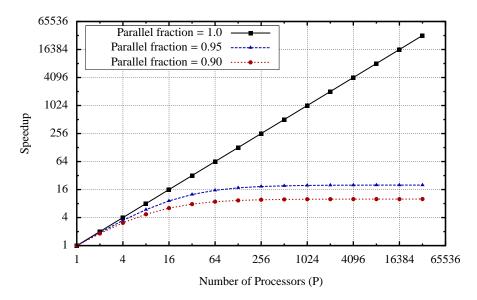

| 2.1<br>2.2 | Speedups projected by Amdahl's law                                                                     | 16<br>20 |

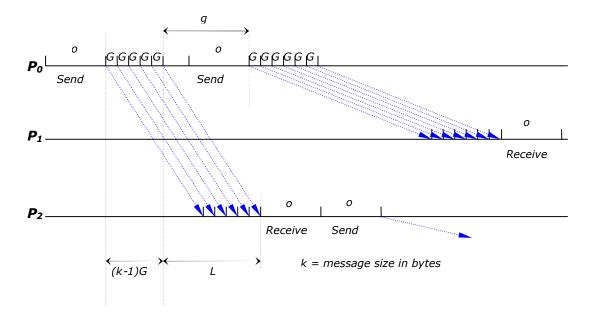

| 2.3        | LogGP parameters                                                                                       | 22       |

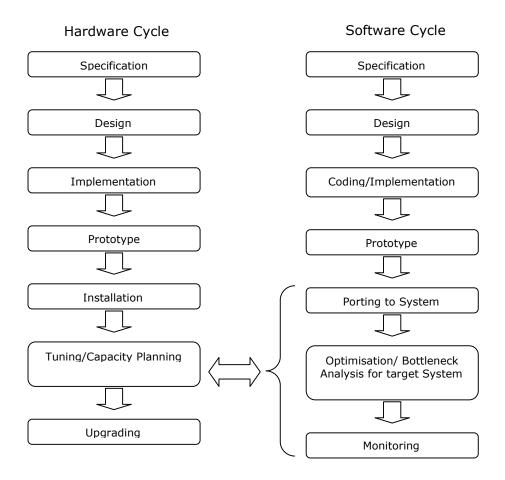

| 2.4        | Stages in the HPC lifecycle                                                                            | 23       |

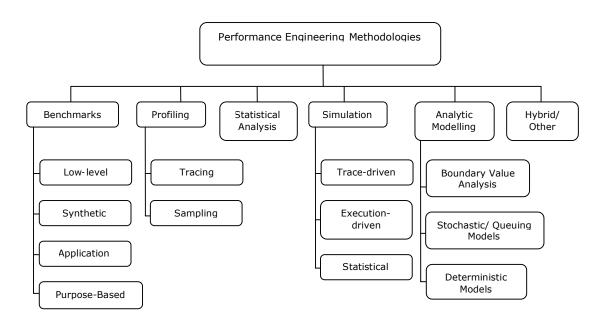

| 2.5        | Performance Engineering Methodologies                                                                  | 33       |

| 3.1        | A 2D pipelined wavefront operation on a 1D processor array                                             | 36       |

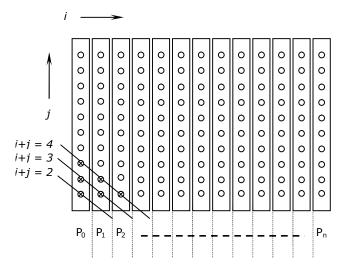

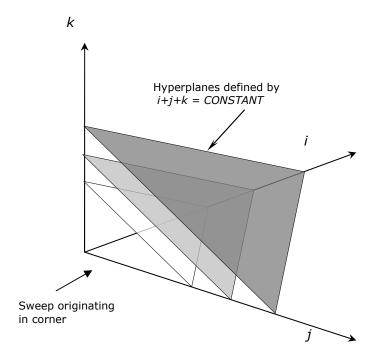

| 3.2        | Hyperplanes on a 3D grid of data                                                                       | 37       |

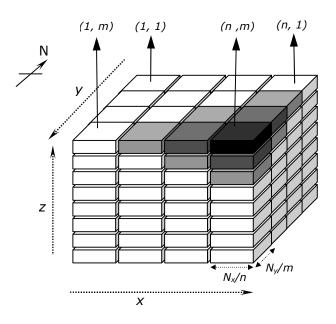

| 3.3        | 3D data grid mapping on to a 2D processor array                                                        | 38       |

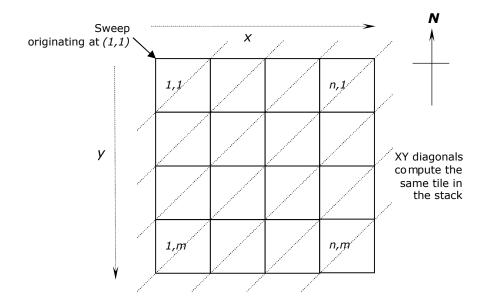

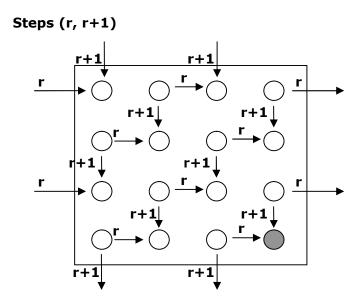

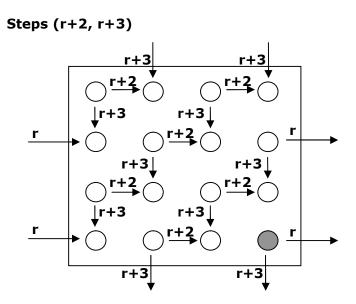

| 3.4        | Pipelined wavefronts on the 2D processor array                                                         | 39       |

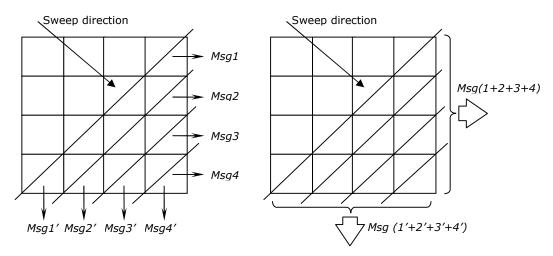

| 3.5        | Fine-grained messaging and agglomerated messaging                                                      | 40       |

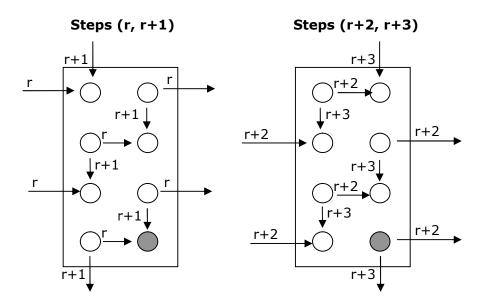

| 3.6        | LU pipelined wavefront operation on the 2D processor array                                             | 43<br>45 |

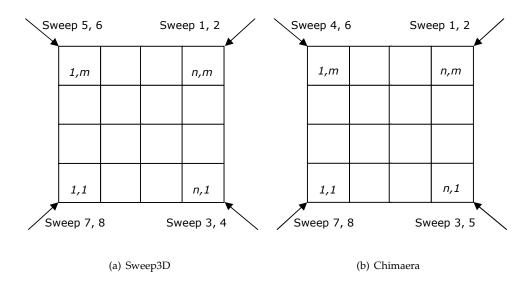

| 3.7        | Sweep3D and Chimaera pipelined wavefront operation on the 2D processor array                           | 43       |

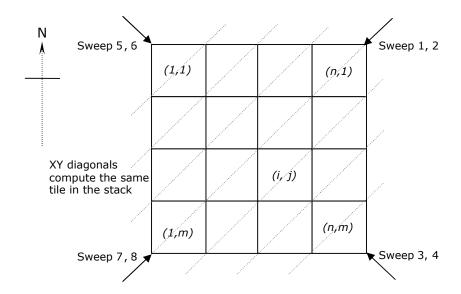

| 4.1        | Pipelined wavefront operation on a 2D processor array                                                  | 56       |

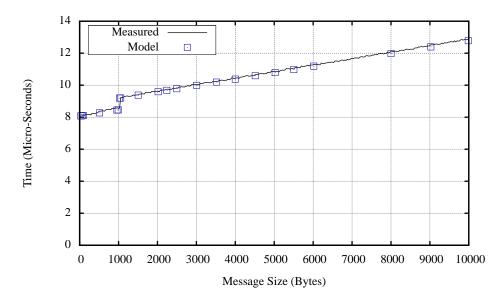

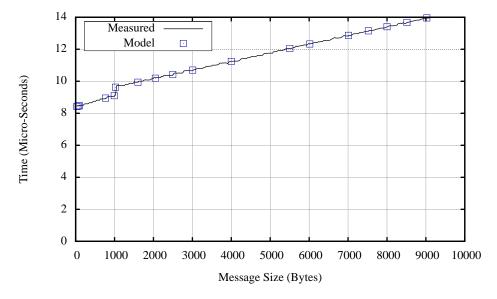

| 4.2        | Measured and modelled Cray XT4 off-node MPI end-to-end communication times                             |          |

| 4.3        |                                                                                                        | 61       |

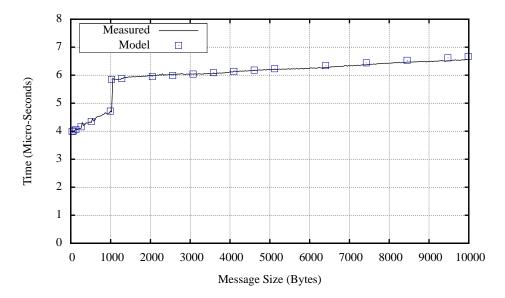

| 4.4        | Measured and modelled Cray XT4 on-chip MPI end-to-end communication times                              |          |

| 4.5        | MPI allreduce operation on dual-core nodes                                                             | 67       |

| 4.6        | MPI allreduce operation on quad-core nodes                                                             | 67       |

| 4.7        | Wavefront operation on a 2D data grid                                                                  | 70       |

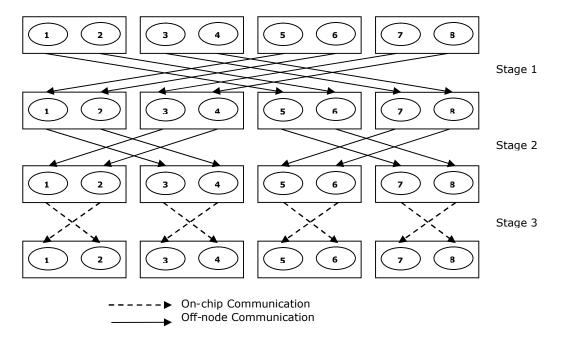

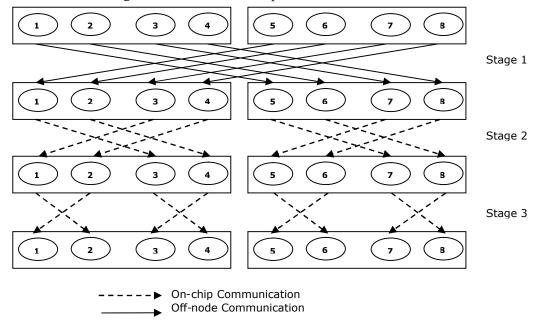

| 4.8<br>4.9 | Wavefront application mapped to multi-core nodes                                                       | 72<br>72 |

| 4.10       | Wavefront operation and collisions on quad core nodes                                                  | 73       |

| 4.10       | •                                                                                                      | 75       |

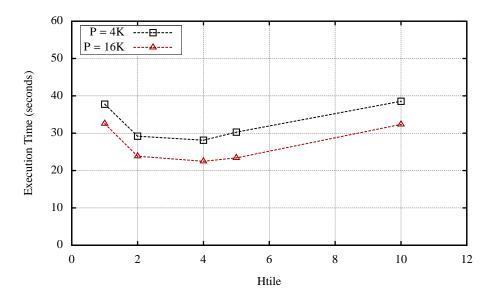

| 5.1        | Execution time vs. $H_{tile}$ : Sweep3D 20 Million cell problem                                        | 81       |

| 5.2        | Execution time vs. $H_{tile}$ : Chimaera $240 \times 240 \times 240$ cell problem                      | 81       |

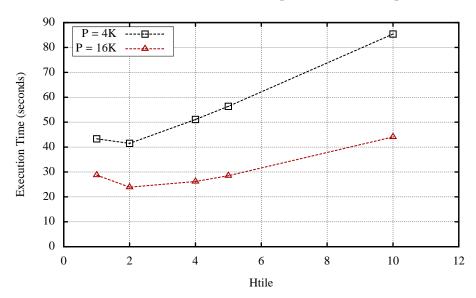

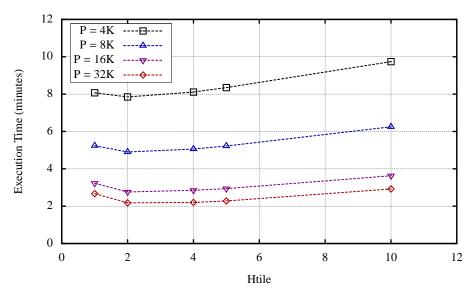

| 5.3        | Execution time vs. $H_{tile}$ : Sweep3D 1 Billion cell problem                                         | 82       |

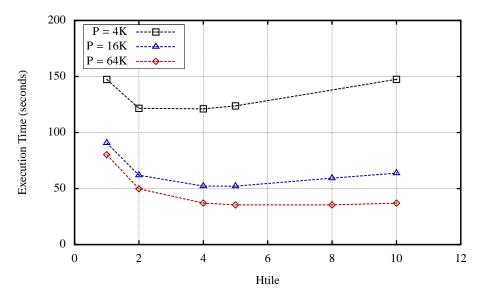

| 5.4        | Execution time vs. $H_{tile}$ : Chimaera $240 \times 240 \times 960$ cell problem                      | 82       |

| 5.5        | Execution time vs. System size: Sweep3D Billion cell problem, $10^4$ time steps,                       |          |

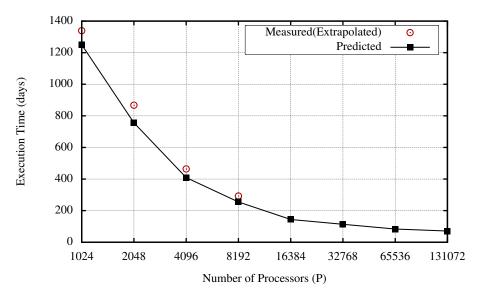

|            | 30 energy groups, 120 iterations, $H_{tile} = 2 \dots \dots \dots \dots \dots \dots \dots \dots$       | 83       |

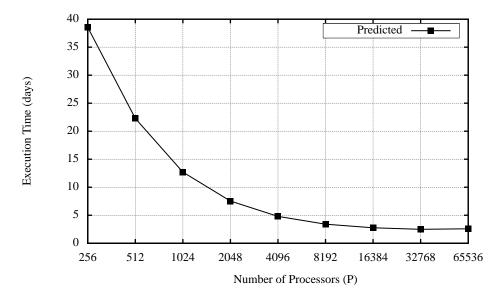

| 5.6        | Execution time vs. System size: Chimaera 240 <sup>3</sup> cell problem, 10 <sup>4</sup> time steps, 16 | 0.4      |

|            | energy groups, 419 iterations, $H_{tile} = 2$                                                          | 84       |

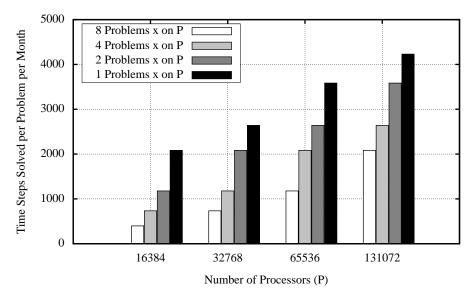

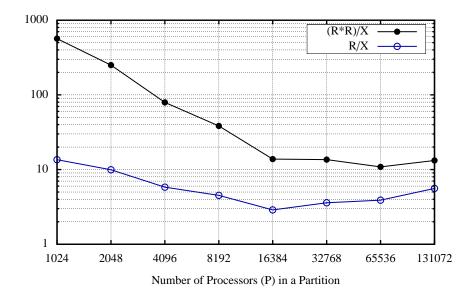

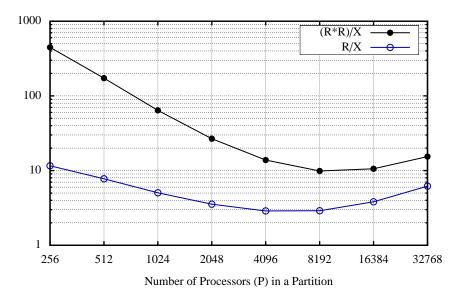

| 5.7        | Throughput vs. Partition Size (Sweep3D 10 <sup>9</sup> Cells, 10 <sup>4</sup> time steps, 30 energy    | 0.4      |

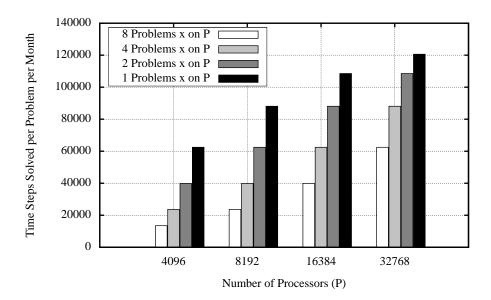

| 5.8        | groups 120 iterations, $H_{tile} = 2$ )                                                                | 84       |

| 3.6        | groups 419 iterations, $H_{tile} = 2$ )                                                                | 85       |

| 5.9        | Optimising Partition Size (Sweep3D 1 Billion Cells, Total number of available                          | 65       |

| 3.9        | processors = 128K)                                                                                     | 86       |

| 5 10       | Optimising Partition Size (Chimaera 240 <sup>3</sup> Cells, Total number of available pro-             | 00       |

| 0.10       | cessors = 32K)                                                                                         | 86       |

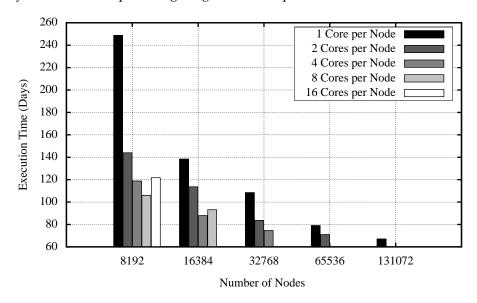

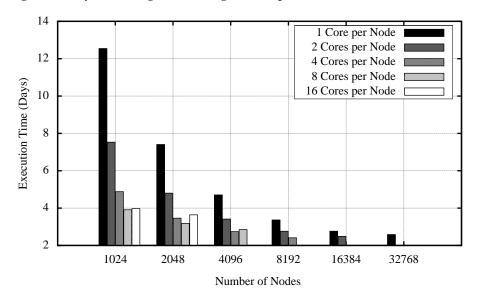

| 5.11       | Execution time on multi-core nodes (Sweep3D 1 Billion Cells, 10 <sup>4</sup> time steps, 30            |          |

|            | energy groups, 120 iterations, $H_{tile} = 2$ )                                                        | 87       |

| 5.12       | Execution time on multi-core nodes (Chimaera 240 <sup>3</sup> Cells,10 <sup>4</sup> time steps, 16 en- |          |

|            | ergy groups 419 iterations, $H_{tile} = 2$ )                                                           | 88       |

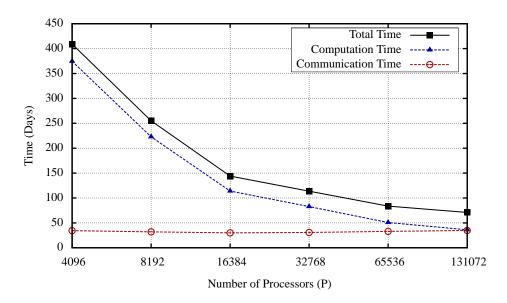

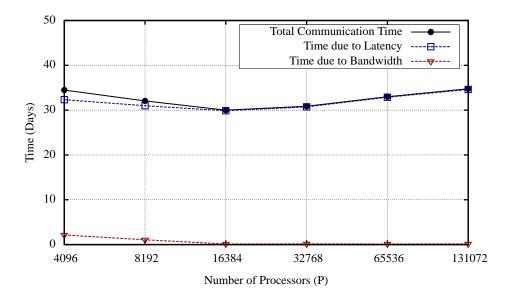

| 5.13       | Computation and communications cost breakdown (Sweep3D 1 Billion Cells, $10^4$ time steps, 30 energy groups, 120 iterations, $H_{tile} = 2$ )                                         | 88                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 5.14       | Computation and communications cost breakdown (Chimaera $240^3$ Cells, $10^4$                                                                                                         | 00                                |

|            | time steps, 16 energy groups 419 iterations, $H_{tile} = 2$ )                                                                                                                         | 89                                |

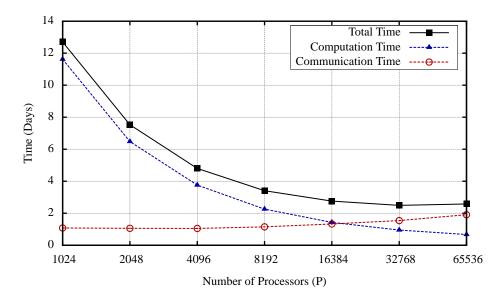

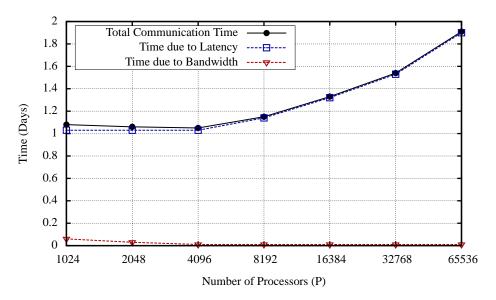

|            | Communications cost breakdown (Sweep3D 1 Billion Cells, $10^4$ time steps, 30 energy groups, 120 iterations, $H_{tile} = 2)$                                                          | 90                                |

|            | Communications cost breakdown (Chimaera $240^3$ Cells, $10^4$ time steps, 16 energy groups 419 iterations, $H_{tile} = 2)$                                                            | 90                                |

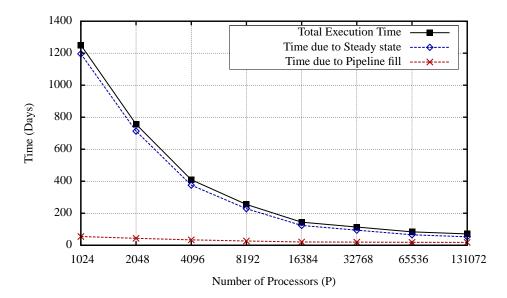

|            | Pipeline fill and steady state cost breakdown (Sweep3D 1 Billion Cells, $10^4$ time steps, 30 energy groups, 120 iterations, $H_{tile} = 2$ )                                         | 91                                |

|            | Pipeline fill and steady state cost breakdown (Chimaera $240^3$ Cells, $10^4$ time steps, 16 energy groups 419 iterations, $H_{tile} = 2$ )                                           | 91                                |

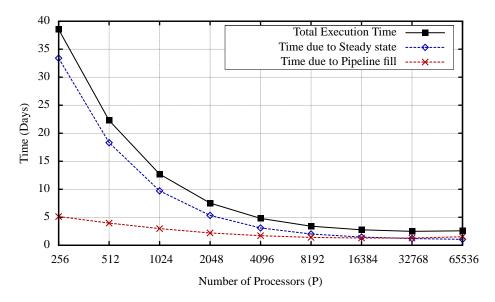

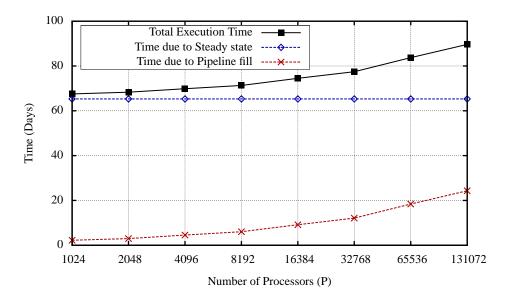

|            | Pipeline fill and steady state cost breakdown (Sweep3D $4 \times 4 \times 1000$ Cells per processor, $10^4$ time steps, 30 energy groups, 120 iterations, $H_{tile} = 2$ )            | 92                                |

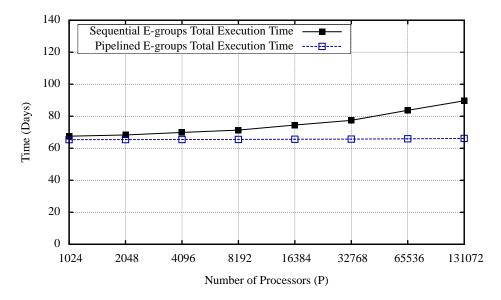

| 5.20       | Sweep structure redesign - pipelining 30 energy groups (Sweep3D $4 \times 4 \times 1000$ Cells per processor, $10^4$ time steps, 30 energy groups, 120 iterations, $H_{tile} = 2$ ) . | 92                                |

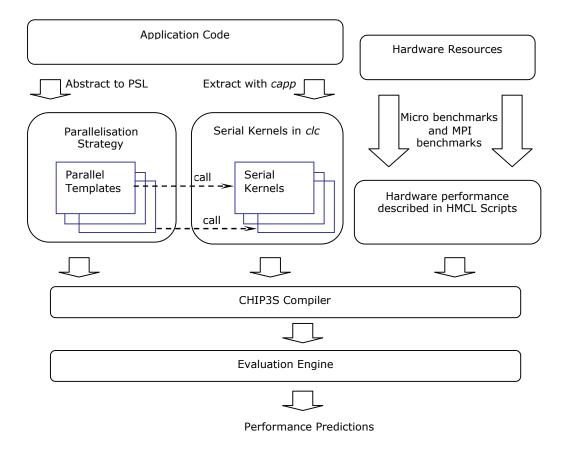

| 6.1        | Overview of the PACE simulator and toolset                                                                                                                                            | 95                                |

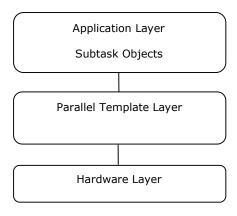

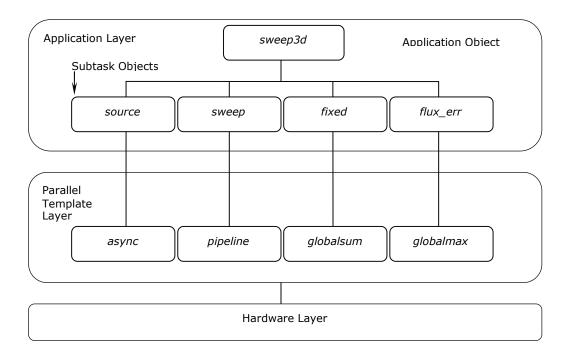

| 6.2        | Layers in a PACE model                                                                                                                                                                | 96                                |

| 6.3        | Layered objects for PACE Sweep3D model                                                                                                                                                | 101                               |

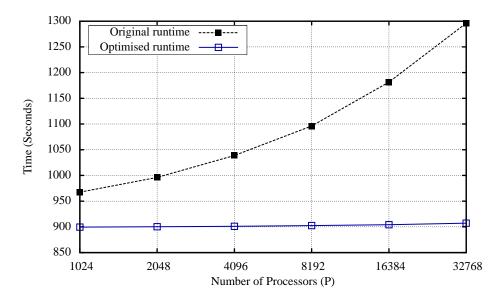

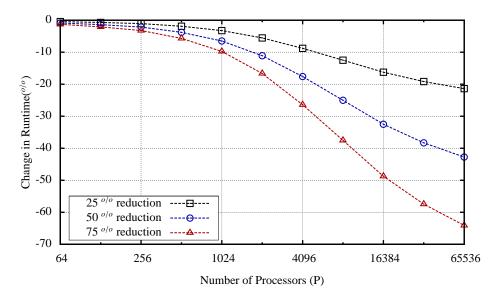

| 7.1        | Optimisation by shifting computation costs to pre-computation - strong scaling (Speculative Chimaera type application, 240x240x240 Cells, 1 time step, 16                             |                                   |

| 7.2        | energy groups 419 iterations, $H_{tile}=1$ )                                                                                                                                          | 112                               |

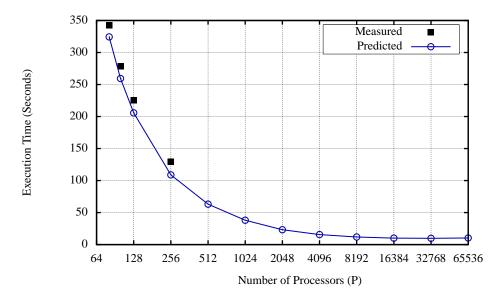

| 7.3        | 16 energy groups 419 iterations, $H_{tile}=1)$                                                                                                                                        | 113                               |

| 7.4        | lem size, $H_{tile} = 1$ )                                                                                                                                                            | 114                               |

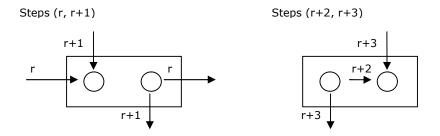

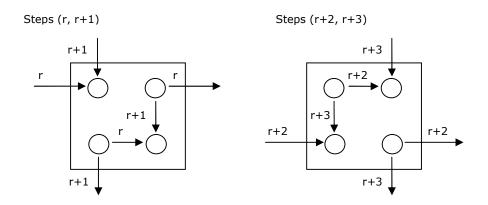

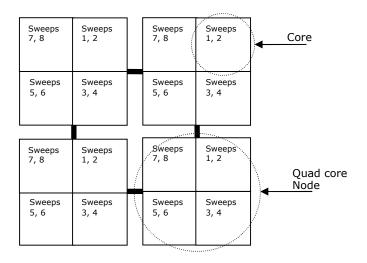

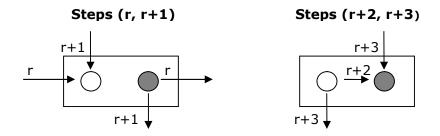

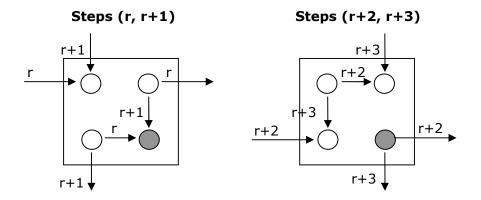

| 7.4<br>7.5 | Multiple simultaneous sweeps on separate cores                                                                                                                                        | 115                               |

| 7.0        |                                                                                                                                                                                       | 115                               |

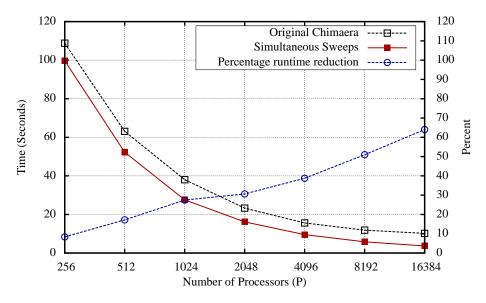

| 7.6<br>7.7 | Simultaneous multiple wavefronts overlapping steps                                                                                                                                    | <ul><li>116</li><li>118</li></ul> |

| 7.8        | Parallel efficiency of larger problem sizes (Chimaera, 1 time step, 16 energy groups 419 iterations)                                                                                  | 123                               |

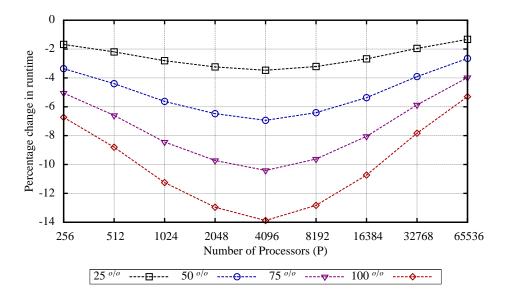

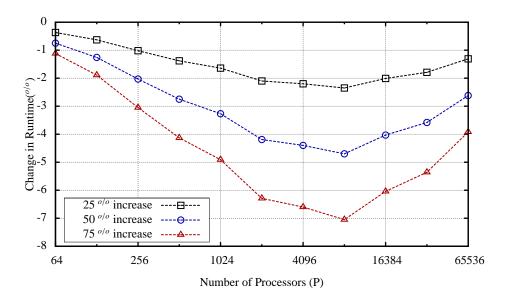

| 7.9        | Change in runtime due to improved computation performance (Chimaera 240x240x240, 1 time step, 16 energy groups 419 iterations)                                                        | 123                               |

| 7.10       | Change in runtime due to reduced network latency (Chimaera 240x240x240, 1                                                                                                             |                                   |

| 7.11       | time step, 16 energy groups 419 iterations)                                                                                                                                           | <ul><li>124</li><li>125</li></ul> |

| A.1        | Wavefront operation and collisions on dual core nodes                                                                                                                                 | 142                               |

| A.2        | Wavefront operation and collisions on quad core nodes                                                                                                                                 | 143                               |

|            | Wavefront operation and collisions on 8 core nodes                                                                                                                                    | 144                               |

|            | Wavefront operation and collisions on 16 core nodes                                                                                                                                   | 145                               |

| A.5        | Wavefront operation and collisions on quad core nodes                                                                                                                                 | 146                               |

### **List of Listings**

| 3.1  | A simple sequential loop operating on a 2D data array                      | 35  |

|------|----------------------------------------------------------------------------|-----|

| 3.2  | Parallelised loop for a 2D data array using pipelined wavefronts           | 36  |

| 3.3  | A simple sequential loop operating on a 3D data array                      | 37  |

| 3.4  | Parallelised loop for a 3D data array using pipelined wavefronts           | 38  |

| 3.5  | General pipelined wavefront algorithm                                      | 40  |

| 3.6  | LU sequential algorithm                                                    | 43  |

| 3.7  | LU parallel algorithm                                                      | 43  |

| 3.8  | The pipelined wavefront algorithm in LU                                    | 44  |

| 3.9  | The pipelined wavefront algorithm in Sweep3D                               | 46  |

| 3.10 | The pipelined wavefront algorithm in Chimaera                              | 46  |

| 4.1  | Timer instrumentation of a wavefront code                                  | 68  |

| 6.1  | Application object:sweep3d                                                 | 97  |

| 6.2  | Subtask object:sweep                                                       | 99  |

| 6.3  | Parallel template object:pipeline                                          | 99  |

| 6.4  | Hardware model for a Pentium 3 2-way SMP Myrinet2000 cluster               | 102 |

| 6.5  | Modified clc for the serial computation $work$ from subtask object $sweep$ | 104 |

| C.1  | sweep.x                                                                    | 150 |

### **List of Tables**

| 2.1  | Pros and cons of performance prediction methodologies                                       | 33    |

|------|---------------------------------------------------------------------------------------------|-------|

| 4.1  | Plug-and-Play Reusable Model Application Parameters                                         | 52    |

| 4.2  | Plug-and-play LogGP Model: One Core Per Node, on 3D Data Grids                              | 59    |

| 4.3  | The ORNL Jaguar: System Details                                                             | 60    |

| 4.4  | XT4 Communication Parameters                                                                | 65    |

| 4.5  | LogGP Model of XT4 MPI Communication                                                        | 65    |

| 4.6  | Validations for the LogGP MPI allreduce model on a Cray XT4                                 | 66    |

| 4.7  | Plug-and-play LogGP Model for Wavefront Codes on 2D Data Grids                              | 70    |

| 4.8  | Re-usable Model Extensions for CMP Nodes                                                    | 73    |

| 4.9  | LU Model Validation on Jaguar (Cray XT3) - $64^3$ cells per processor                       | 75    |

| 4.10 | LU Model Validation on Jaguar (Cray XT3) - 102 <sup>3</sup> cells per processor             | 75    |

|      | Sweep3D Model Validation on Jaguar (Cray XT4) - 1000 <sup>3</sup> total problem size,       |       |

|      | $H_{tile}=2, mmi=6$                                                                         | 76    |

| 4.12 | Sweep3D Model Validation on Jaguar (Cray XT4) - $20 \times 10^6$ total problem size,        |       |

|      | $H_{tile}=2, mmi=6$                                                                         | 76    |

| 4.13 | Chimaera Model Validation on Jaguar (Cray XT4) - 240 <sup>3</sup> total problem size        | 77    |

| 1.10 | community 210 total problem once :                                                          | ,,    |

| 6.1  | Model Validation Systems                                                                    | 105   |

| 6.2  | Sweep3D simulation model validations on an Intel Pentium-3 2-way SMP clus-                  |       |

|      | ter with a Myrinet 2000 interconnect                                                        | 105   |

| 6.3  | Sweep3D simulation model validations on an AMD Opteron 2-way SMP cluster                    |       |

|      | interconnected by a Gigabit Ethernet                                                        | 106   |

| 6.4  | Sweep3D simulation model validations on an SGI Altix Intel Itanium-2 56-way                 |       |

|      | SMP                                                                                         | 106   |

| 6.5  | Intel InfiniBand (CSC-Francesca) Cluster - Key Specifications                               | 108   |

| 6.6  | Chimaera Model Validation on a Intel Xeon-InfiniBand cluster - 120 <sup>3</sup> total prob- |       |

|      | lem size                                                                                    | 108   |

| 6.7  | Chimaera Model Validation on a Intel Xeon-InfiniBand luster - 240 <sup>3</sup> total prob-  |       |

|      | lem size                                                                                    | 108   |

| 6.8  | InfiniBand network model parameters                                                         | 109   |

|      |                                                                                             |       |

| 7.1  | Predictions for a system with heterogeneous processors (Chimaera 240x240x240                |       |

|      | Cells, 1 time step, 16 energy groups 419 iterations, $H_{tile} = 1$ )                       | 120   |

| D 1  |                                                                                             | 1 45  |

| B.1  | Chimaera Model Validation on Jaguar (Cray XT4) - $60^3$ problem size, $H_{tile} = 1$        | 147   |

| B.2  | Chimaera Model Validation on Jaguar (Cray XT4) - $120^3$ problem size, $H_{tile} = 1$       | 147   |

| B.3  | Chimaera Model Validation on Jaguar (Cray XT4) - $240^3$ problem size, $H_{tile} = 1$       | 147   |

| B.4  | Chimaera Model Validation on a Intel Xeon-InfiniBand cluster - 120 <sup>3</sup> problem siz |       |

| B.5  | Chimaera Model Validation on a Intel Xeon-InfiniBand luster - 240 <sup>3</sup> problem siz  | e 147 |

| B.6  | Sweep3D Model Validation on Jaguar (Cray XT4) - 1000 <sup>3</sup> total problem size,       |       |

|      | $H_{tile} = 2, mmi = 6$                                                                     | 148   |

| B.7  | Sweep3D Model Validation on Jaguar (Cray XT4) - $20 \times 10^6$ total problem size,        |       |

|      | $H_{tile} = 2, mmi = 6$                                                                     | 148   |

| B.8  | Sweep3D Model Validation on Jaguar (Cray XT4) - $5 \times 5 \times 400$ per processor       |       |

|      | problem size, $H_{tile} = 5$ , $mmi = 6$                                                    | 148   |

| B.9  | Sweep3D Model Validation on Jaguar (Cray XT4) - $14 \times 14 \times 255$ per processor     |       |

|      | problem size, $H_{tile} = 2.5$ , $mmi = 6$                                                  | 149   |

| B.10 | Sweep3D Model Validation on Jaguar (Cray XT4) - $20 \times 20 \times 1000$ per processor |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | problem size, $H_{tile} = 5$ , $mmi = 6$                                                 | 149 |

| B.11 | Sweep3D Model Validation on Jaguar (Cray XT4) - $45 \times 45 \times 1000$ per processor |     |

|      | problem size, $H_{tile} = 5$ , $mmi = 6$                                                 | 149 |

# Introduction

The use of computational methods is now an essential research methodology that propels modern science, medicine and engineering. The scientific methods of computational modelling and simulation are now as ubiquitous as the traditional theoretical and experimentation approaches to scientific research. Particularly through computational modelling and simulation, domain scientists and researchers in these fields have been able to conceptualise, discover, design and produce more innovative solutions and solve highly complex problems than was ever possible with traditional *paper and pencil* methods. Thus, such computational methods have established themselves as a third pillar of scientific investigation, comparable to experimental and theoretical approaches. In the last decade, the use of these techniques has grown rapidly, due to the increasing availability of efficient and large-scale computational resources.

High Performance Computing (HPC) or its more popularly known designation - *super-computing* - is concerned with the research, design, development, manufacturing, deployment and usage of such high-end computer systems. It is more specifically characterised by the use of parallel processing for running advanced application programs quickly, efficiently and reliably. HPC systems can be of the form of a high-end server, or a massively parallel *super-computer* with thousands of processors interconnected by high speed networks or a large distributed system that is spread across a building, city, country or even continents.

As the name implies, performance is key to HPC and the goal is to achieve the best performance in a cost-effective and resource efficient manner. Analysis and evaluation of performance as well as its prediction and speculating about future behaviour have therefore been key aspects of HPC. These activities - collectively referred to as performance engineering - are particularly invaluable, as these systems and software often require a large investment not only from the end user and owners but also from the designers, developers and vendors. The advantages of performance engineering also extend beyond this, allowing efficient scheduling by anticipating a workload's behaviour prior to execution [9, 10], which in turn allows efficient utilisation of resources and sustainable levels of Quality of Service (QoS) [11]. It has been recognised that performance engineering techniques can be used throughout the lifecycle of a system [9, 12]. For example, at the design stage they can serve to quantify the advantages and disadvantages of different architectural options. When procuring systems, users can utilise performance predictions to compare alternative systems and at the implementation stage predictions based on an implemented prototype can serve as a forecast for the final system [13]. After installation, predicted results can be used to validate whether the installation was successful, and whether the system is configured accurately to obtain optimum system efficiency. Additionally, during maintenance such performance analysis data can indicate faults that affect the system behaviour and also quantify the possible benefits that can be gained by upgrading. On the application side, for example, performance engineering enables application scientists to design near optimal application code by exposing software bottlenecks [14] and hardware facilities that should be exploited to obtain maximum efficiency and resource utility [15].

Due to these significant benefits, performance engineering has been and continues to be an important research area in the field of HPC. But understanding the performance aspect of an HPC application when running on various parallel high performance systems and architectures still remains to be a significantly difficult task. The complexity of the HPC applications and systems, the rapid pace of technology development and the lack of expertise in performance engineering make it highly non-trivial and labour intensive.

The underlying objective of this work is to assist the complex and demanding task of performance engineering for HPC. To this end, the dissertation investigates the performance of a significantly important, non-trivial and ubiquitous class of HPC computations - Pipelined Wavefront Computations - on modern HPC systems. We conduct a performance engineering study of these codes by developing a reusable analytic model, attesting it as a technique that simplifies the task of performance engineering, and then utilise the model for comprehensively assessing the quantitative and qualitative performance of pipelined wavefront computations on modern HPC systems.

### 1.1 Motivation and Problem Statement

Pipelined Wavefront Computations, originally described as hyperplane methods [16] by Lamport form a major portion (up to 80 % [17]) of the high performance scientific computing workload at institutes such as the Los Alamos National Laboratories (LANL) in the U.S [18] and the Atomic Weapons Establishment (AWE) [19] in the U.K. The communication primitives used in these parallel benchmark codes are the blocking send, receive, and group communication primitives in the Message Passing Interface (MPI) [20]. To aid the design, procurement and optimization decisions of these applications on high-end computers, there has been and continues to be considerable research interest in performance engineering of these codes.

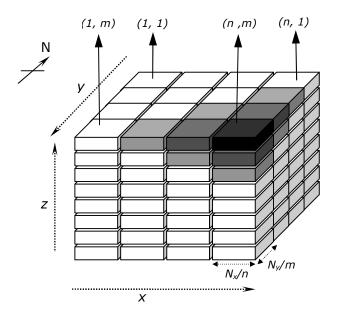

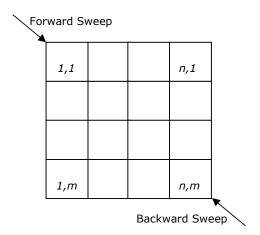

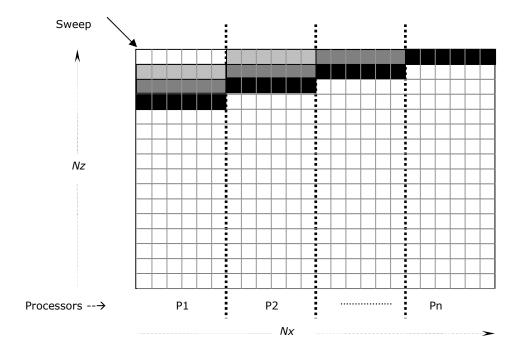

Pipelined Wavefront Computations, generally operates on a 3D grid of data cells (although the algorithm extends equally well on to 1D and 2D grids), where the parallel processing of the computation can be viewed as a wavefront originating from a corner of the data grid propagating to the oppisite corner of the data grid. Figure 1.1 illustrates this operation. Here, a 3D data grid of size  $N_x \times N_y \times N_z$  is decomposed onto a 2D array of  $m \times n$  processors. Each partition of data cells assigned to a processor can be viewed as a stack of tiles, each of 1 cell high. The data dependency of the cells held in processors results in a sequence of wavefronts (or a sweep) that starts at one of the corner processors, computing over the cells of its topmost or bottommost tile and propagating to the opposite processor's bottommost or topmost tile. The shaded tiles in Figure 1.1 depict three basic steps of the general wavefront operation. It illustrates the tiles that are processed during the nal three wavefronts (or final three sweep steps) - light Gray, then medium Gray, then dark Gray - belonging to a sweep that originated at the bottommost tile on processor (1,1), ending at the topmost tile on (n,m).

There have been several previous performance engineering studies on pipelined wavefront computations. In [14], Yarrow *et al.* develop analytic models of two different versions of the NAS parallel benchmark [21], LU. LU employs pipelined wavefront computations to

Figure 1.1: Operation of a Wavefront computation

solve a compressible Navier-Stokes equation used in computational fluid dynamics (CFDs). The model elucidates the differences in communications structure and predicts performance with a maximum of 30% error compared with measured LU execution time on an IBM SP system. Sundaram-Stukel and Vernon [8] develop an analytic model based on LogGP [22] for the pipelined wavefront application Sweep3D [23] on an IBM SP/2 system. This model has high accuracy with less than 10% error for up to 128 processors. Mathis *et al.* [24] develop a general analytic performance model for Sweep3D and apply the model to explore two possible alternative domain decompositions. Hoisie *et al.* [17] develop analytic models for a single *sweep* of the wavefront code based on Sweep3D, while Kerbyson *et al.* [25] use the single sweep equation to model the total Sweep3D runtime. In [26], Hoisie *et al.* detail the contention arising in wavefront computations when executed on clusters of SMPs where processors in a node share router links to communicate with processors in other nodes.

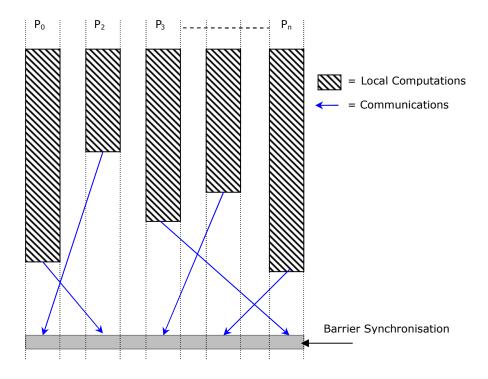

Non-analytic performance engineering work on wavefront codes include the Sweep3D simulation model developed and evaluated using PACE [27, 28] and MPI-SIM [29, 30] which was part of the POEMS [31] system. PACE uses a layered performance characterisation method and provides tools that model and evaluate (using discrete-event simulation) the computation and communication activities in an application by linking serial code graphs with a template that models the message passing and concurrency behaviour. MPI-SIM simulates an application by direct execution of computation and parallel discrete even simulation for communication and I/O operations. Other tools of note that have been used to evaluate Sweep3D include Kojak [32] and PTI [33].

Other related work on wavefront codes includes a study on the best methods to present them to the compiler for effective generation of parallel codes [34]. In this work the wavefront algorithm is parallelised using three approaches: message passing, compiler driven automatic parallelisation and programmer defined explicit parallel language features. The work assesses the efficiency of these approaches for parallelising wavefront algorithms.

In spite of all the above work, we believe that three key issues continue to make performance engineering of wavefront applications important:

Firstly, the complex synchronisation pattern of computation and communications in wavefront codes brings with it a considerable amount of structural variations and optimisation possibilities. Each of the previous performance engineering studies are specific to LU or Sweep3D and require significant and unspecified restructuring to apply them to other wavefront codes of interest. As will be seen in the applications that are analysed in this dissertation, each have considerable differences in domain decompositions, operational characteristics, parallel overlappings and optimisations. Therefore one of the key difficulties has been that each new wavefront application has had to be performance engineered from scratch.

Secondly, the above problem was confounded by each generation of HPC systems, introducing a previously unexplored aspect that made previous studies of wavefront computations require a considerable (sometimes almost entire) re-evaluation. For instance, the typical approach to performance engineering of new wavefront applications or evaluating a new HPC system was to modify existing performance studies to reflect the behaviour of the new code or the new systems. However, the modification process is error-prone and thus each new model must be extensively validated. One of the underlying goals of this dissertation is to develop methods that reduce this effort, alleviating the above problems and assisting in future performance engineering work of wavefront applications.

Finally and more importantly, all the previous performance studies on wavefront applications have only addressed (in most cases through customised models) the performance and thus the optimisation of a specific application has not explored or investigated the class of applications as a whole. A considerable motivation for us, therefore, is the open question of what optimisations are possible given this important class of parallel applications. Particularly, one of the interesting questions, is that if the underlying scientific or numerical solution permits, what the optimal software design for this class of application is and how best it can be run on a particular HPC system. Moreover, we want to develop tools that address performance questions posed by application domain scientists who are required to develop their own wavefront codes and need to understand the optimal design possibilities, given their scientific and numerical boundaries. The aim is to develop techniques that not only answer the above questions, but also motivate and expose new questions and at the same time enable us to obtain solutions in a speedy, efficient and low cost manner.

Thus, motivated by the above key open issues, this dissertation develops analytic performance models that are generalised or *reusable* and demonstrate, their use for predictive analysis and optimisation of pipelined wavefront computations running on modern HPC systems. In the remainder of this section, we discuss the incentives for using analytic methods and motivate the idea of reusable performance model development.

### 1.1.1 Analytic Modelling

An analytic performance model is a mathematical construct that represents key aspects of a computer system and/or program. The analytic model is made up of parameters that abstractly represent the inputs, outputs, and the system. Given the required input parameters, performance predictions are extracted as solutions of this mathematical expression. It is one

of the four broad performance engineering methodologies. The others being Benchmarking (or direct measuring/monitoring), Statistical Analysis, and Simulation.

Performance measurement or monitoring is the most direct and straightforward form of performance analysis. In the simplest case, a program of interest (a collection of programs or a workload) is executed on the system of interest and quantitative values such as execution time and floating point operation rates are monitored. The workload plays an important part here. In order to compare systems the workloads executed on them should be compatible for comparison. A benchmark is such a workload that is developed to assess systems. Also related to benchmarking is the use of profiling tools that enables one to instrument a code and extract measures and behaviours of the code as it runs dynamically.

Based on measurements taken on a working system, statistical methods can be used to understand expected behaviour of systems. Statistical methods such as regression and curve fitting are used to make speculations for possible future systems. For example data from a relatively small cluster running an HPC application may provide an initial idea of how the application will scale to a larger cluster made up of similar nodes and communication channels.

In contrast, simulation techniques seek to capture application behaviour by executing a representation of the application's control flow, communication structure and synchronisation behaviour. In effect they model the application running on a real-world system as a computer program, also called a simulator. The events that occur during execution, such as computation, memory access and communications, are represented as events in the simulator. Simulation allows one to model the events of the system at any level of detail from low-level instruction simulations to high-level transactions.

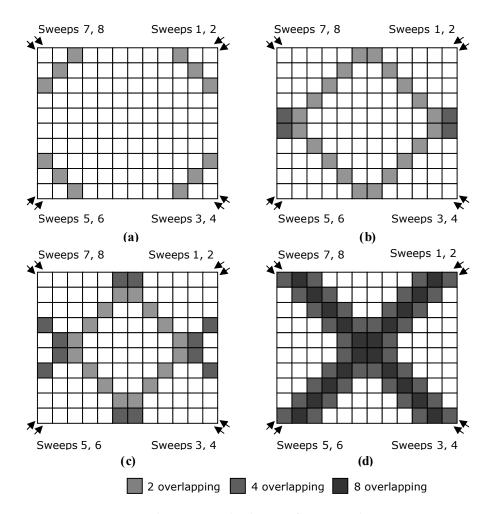

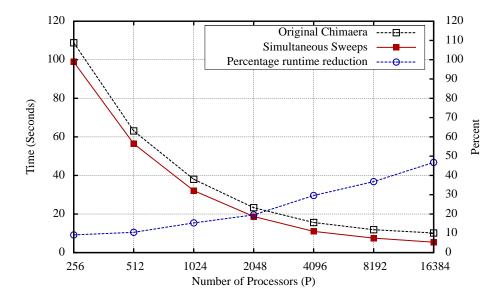

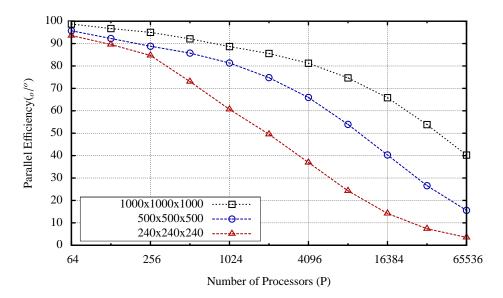

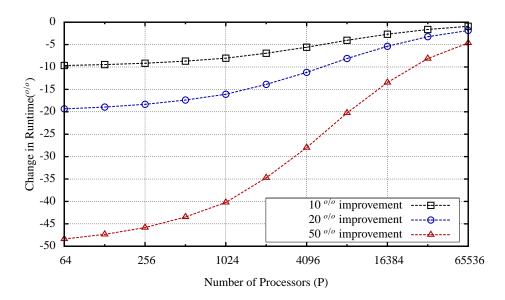

The previous performance engineering work for wavefront applications consists of research, based on all of the above methodologies, where in most cases they employ multiple or a hybrid of these techniques. Especially for analytic and simulation based methods, there is a need to benchmark a system to obtain initial performance behaviour, system parameter values etc. Additionally, the initial insights gained from some basic statistical technique can be an integral part of model/simulator development, testing and validation.