#### Εθνικό Μετσοβίο Πολυτέχνειο

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# A client-server synchronization model for concurrent data structures implemented in SCC

$\Delta$ ΙΠΛΩΜΑΤΙΚΉ ΕΡΓΑΣΙΑ

του

ΤΑΣΟΥΛΑ ΖΩΗ - ΓΕΡΑΣΙΜΟΥ

Επιβλέπων: Δημήτριος Σούντρης

Αναπληρωτής Καθηγητής Ε.Μ.Π.

Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων

# A client-server synchronization model for concurrent data structures implemented in SCC

#### $\Delta$ III $\Lambda$ $\Omega$ MATIKH EPFA $\Sigma$ IA

του

#### ΤΑΣΟΥΛΑ ΖΩΗ - ΓΕΡΑΣΙΜΟΥ

Επιβλέπων: Δημήτριος Σούντρης

Αναπληρωτής Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 23η Μαρτίου 2016.

Δημήτριος Σούντρης Νεκτάριος Κοζύρης Κιαμάλ Πεκμεστζή Αναπληρωτής Καθηγητής Ε.Μ.Π. Καθηγητής Ε.Μ.Π.

Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων

ΤΑΣΟΥΛΑΣ ΖΩΗΣ - ΓΕΡΑΣΙΜΟΣ

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

Copyright © Τασούλας Ζώης - Γεράσιμος, 2016. Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

# Περίληψη

Αντιχείμενο της διπλωματιχής εργασίας είναι η αξιολόγηση κάποιον ταυτόχρονων δομών δεδομένων στο πολυπύρηνο σύστημα Single-chip Cloud Computer της εταιρίας Intel. Συγχεχριμένα κατά τη διάρχεια της διπλωματιχής εργασίας μελετήθηκαν και αξιολογήθηκαν για διάφορες παραμέτρους οι δομές δεδομένων της στοίβας, της FIFO ουράς προτεραιότητας και του διονυμιχού σωρού μεγίστου.

Το σύστημα Single-chip Cloud Computer είναι ένας υπολογιστής γενικού σκοπού με 48 πυρήνες, η δημιουργία του οποίου προορίζεται για ερευνητικούς σκοπούς και μελέτη των πολυπύρηνων συστημάτων. Ο μεγάλος αριθμός πυρήνων και το μοναδικό αυτό σύστημα μας παρότρυνε να το επιλέξουμε για να μελετήσουμε τις επιδώσεις και την συμπεριφορά πολυπύρηνων συστημάτων. Ένα επίσης ενδιαφέρον στοιχείο που μας οδήγησε να επιλέξουμε την έρευνα πάνω σε αυτόν τον υπολογιστή είναι η ιδιαιτερότητα του μοντέλου μνήμης, γεγονός που μας δημιούργησε το ενδιαφέρον να δοκιμάσουμε το μοντέλο πελάτη εξυπηρετητή για την οργάνωση και των συγχρονισμό ταυτόχρονων δομών δεδομένων.

Στη διάρχεια της διπλωματιχής συγχρίναμε την συμπεριφορά και την επίδοση των δομών δεδομένων που αναφέραμε. Χρησιμοποιήσαμε ένα πλήθος διαφορετιχών σεναρίων αιτημάτων και διεργασιών από τους πυρήνες και λάβαμε μετρήσεις τόσο για την χρονιχή επίδοση, όσο και για την κατανάλωση ενέργειας από κάθε δομή. Αχόμη δοχιμάσαμε κατά πόσο επηρεάζει την επίδοση η κατανομή των πυρήνων κατά τη δέσμευσή τους, αν θα είναι συνεχείς ή διασχορπισμένοι. Επίσης είδαμε κατά πόσο η θέση του πυρήνα εξυπηρετητή επηρεάζει την επίδοση, και πώς θα συμπεριφέρονταν οι δομές και το σύστημα στην περίπτωση που μεσολαβούσε κάποια καθυστέρηση ή η ενασχόληση με κάποια άλλη δουλειά από τους πυρήνες, μεταξύ δύο διαδοχικών αιτημάτων για αλλαγές στη δομή δεδομένων.

#### Λέξεις Κλειδιά

Ταυτόχρονες δομές δεδομένων, πολυπύρηνα συστήματα, συγχρονισμός, μοντέλο πελάτη εξυπηρετητή, SCC

#### Abstract

The purpose of this diploma thesis is to evaluate concurrent data structures with the multicore system by Intel, the Single-chip Cloud Computer. Specifically during the work for this thesis we examined and evaluated through different parameters the data structures of stack, FIFO queue and binary max heap.

The Single-chip Cloud Computer system is a general purpose computer of 48 cores. Its creation was meant for research purposes and further study of multicore systems. The big number of cores and this unique system made us choose it to examine the performance and the behaviour of multicore systems. Another interesting fact that led us choose to do our research with this computer is the special memory model that the Single-chip Cloud Computer has, which created the curiosity to test and evaluate the performance of a client-server model for the synchronization and the organizing of the concurrent data structures.

During this thesis we compared the behaviour and the performance of the data structures we mentioned above. We used a set of different scenarios consisting of a different set of requests and transactions from the cores. We gathered measurements both for the time performance and also for the power consumption by every data structure. In addition to this, we tested how the position of the allocated cores, if they are continuously allocated or distributed, affects performance. Also we wanted to see how and if the position of the server core in the client-server model affects performance and how the data structures and the system will behave and perform in case there would be a delay or some time spent by cores to handle another task, between two consecutive requests for transactions with the data structure.

#### Keywords

Concurrent data structures, multicore systems, synchronization, client server model, SCC

# Ευχαριστίες

Θα ήθελα να ευχαριστήσω στο σημείο αυτό τον επιβλέποντα καθηγητή κ. Δημήτριο Σούντρη που με εμπιστεύτηκε και μου έδωσε την ευκαιρία να ασχοληθώ με το θέμα αυτό. Τον ευχαριστώ επίσης για την πολύ καλή μας συνεργασία και επικοινωνία και για την προθυμία του να με βοηθήσει και να με καθοδηγήσει στις ακαδημαϊκές μου επιλογές.

Επίσης ευχαριστώ ιδιαίτερα τον υποψήφιο διδάκτορα κ. Λάζαρο Παπαδόπουλο για την καθοδήγηση και την άριστη συνεργασία μας κατά την διάρκεια εκπόνησης της διπλωματικής αυτής εργασίας. Η επικοινωνία μας ήταν άριστη και ήταν πάντα διαθέσιμος ώστε να λύνουμε τα θέματα που ανέκυπταν και να προχωράμε στην περάτωση της εργασίας αυτής. Να ευχαριστήσω επίσης τον κ. Γιώργο Χατζηκωνσταντή γιατί ήταν πρόθυμος και διαθέσιμος να συμβάλει με την βοήθειά του και την εμπειρία στο κομμάτι των μετρήσεων της κατανάλωσης ενέργειας.

Τέλος θα ήθελα να ευχαριστήσω την οιχογένειά μου, την μητέρα μου και τις αδερφές μου, για την υποστήριξή τους, την αγάπη τους και την υπομονή τους όλα αυτά τα χρόνια. Ήταν ένα σημαντικό κομμάτι της προσπάθειάς μου και χωρίς αυτές πολλά πράγματα θα ήταν δύσκολα. Να ευχαριστήσω επίσης την Αλεξάνδρα αλλά και όλους τους φίλους με τους οποίους ήρθαμε σε επαφή λόγω του Εθνικού Μετσόβιου Πολυτεχνείου ή γενικότερα των σπουδών. Έκαναν την διαδρομή μέχρι την απόκτηση του πτυχίου πιο ευχάριστη και πολλές φορές ήταν η αφορμή να διδαχθώ και να μάθω πολλά πράγματα.

# Περίληψη διπλωματικής

Όπως φαίνεται από τον τίτλο, το θέμα της διπλωματικής αυτής εργασίας είναι η μελέτη, σχεδίαση και αξιολόγηση ενός μοντέλου συγχρονισμού πελάτη-εξυπηρετητή, για ταυτόχρονες δομές δεδομένων, υλοποιώντας το για τον υπολογιστή Single-chip Cloud Computer της εταιρίας Intel.

Η επιλογή του ειδικού αυτού υπολογιστή έγινε γιατί είναι ένα σύστημα που διαθέτει 48 επεξεργαστικούς πυρήνες. Σχεδιάστηκε από την Intel για ερευνητικούς σκοπούς και διατίθεται για έρευνα πάνω σε διάφορους τομείς των πολυπύρηνων συστημάτων, όπως λειτουργικά συστήματα για πολυπύρηνα συστήματα, τρόποι επικοινωνίας των πυρήνων, βέλτιστες πρακτικές για αποδοτική επικοινωνία, χρήση μνήμης και εξοικονόμηση ενέργειας σε πολυπύρηνους υπολογιστές γενικού σκοπού. Ο λόγος που δημιουργήθηκε το ενδιαφέρον για τη μελέτη του μοντέλου πελάτη-εξυπηρετητή είναι η ύπαρξη μιας ιδιαιτερότητας στο σύστημα μνημών του Single-chip Cloud Computer. Αργότερα θα σχολιάσουμε εκτενέστερα την οργάνωση και την ιεραρχία των μνημών, αλλά αυτό που προξενεί ενδιαφέρον και είναι αφορμή για έρευνα και μελέτη είναι η ύπαρξη μιας πολύ γρήγορης, μικρής μεν στο μέγεθος, μνήμης εντός κάθε ψηφίδας του συστήματος.

Η ιδιαίτερη αυτή μνήμη ήταν η αφορμή για να δοχιμάσουμε πώς μπορεί ένα μοντέλο συγχρονισμού που θα βασίζεται στην ανταλλαγή μηνυμάτων και δεδομένων μικρού μεγέθους να αποδώσει, σε σύγκριση με άλλα μοντέλα. Συγκεκριμένα δοχιμάσαμε κάποια μοντέλα με κλειδώματα και τα συγκρίναμε με αυτό του πελάτη-εξυπηρετητή. Το χύριο αντικείμενο της διπλωματικής αυτής εργασίας είναι η σύγκριση των μοντέλων αυτών σε διάφορους τομείς, όπως χρονική επίδοση, κατανάλωση ενέργειας, δικαιοσύνη στην ολοκλήρωση αιτημάτων και κάποιες άλλες κατηγορίες συγκρίσεων που θα δούμε παρακάτω.

Για τις διεργασίες και την ολοκλήρωση της διπλωματικής αυτή εργασίας χρησιμοποιήθηκαν κυρίως εργαλεία ελεύθερου λογισμικού όπου αυτό ήταν δυνατό. Επίσης για τη συγγραφή χρησιμοποιήθηκε η τυπογραφική σουίτα ΙΔΤΕΧ.

Στο κείμενο που ακολουθεί θα δούμε με σειρά κάποια θεωρητικά στοιχεία για αρχές συγχρονισμού, τόσο παραδοσιακές όσο και κάποιες προχωρημένες αρχές που εμφανίστηκαν πρόσφατα. Στη συνέχεια θα παρουσιάσουμε με περισσότερες λεπτομέρειες το σύστημα Single-chip Cloud Computer καθώς και τις υλοποιήσεις που χρησιμοποιήσαμε για τις μετρήσεις μας. Έπειτα την βάση και τη δομή των σεναρίων που χρησιμοποιήσαμε για να αξιολογήσουμε τις διάφορες δομές δεδομένων καθώς και θα σχολιάσουμε ποια μεγέθη και ιδιότητες μετρήσαμε. Τέλος θα σχολιάσουμε τα αποτελέσματα που εξάγαμε και θα προτείνουμε κάποιες μελλοντικές

προεκτάσεις της δουλειάς μας για αυτή τη διπλωματική εργασία.

#### 1.1 Μέθοδοι συγχρονισμού

Μιλώντας για τις αρχές συγχρονισμού των ταυτόχρονων δομών δεδομένων, αυτές είναι απαραίτητες στα πολυπύρηνα συστήματα και όταν μιλάμε για ταυτόχρονες ή παράλληλες διεργασίες. Αυτό προκύπτει από το γεγονός ότι είτε υπάρχει δυνατότητα πολλαπλών προσβάσεων ταυτόχρονα στη μνήμη, είτε το υλικό δεν επιτρέπει κάτι τέτοιο και τα αιτήματα πρόσβασης στη μνήμη σειριοποιούνται, πρέπει να υπάρχει ένας μηχανισμός που να εγγυάται την ακεραιότητα των αιτημάτων, δηλαδή την ακεραιότητα των δεδομένων. Πρέπει επίσης να είμαστε σίγουροι ότι η κατάσταση της μνήμης θα είναι συνεπής έπειτα από κάποια διεργασία με τα δεδομένα της, ότι τα δεδομένα που θα διαβάζονται ή θα γράφονται θα είναι τα επιθυμητά και τέλος ότι δεν θα προκύπτουν απροσδιόριστες καταστάσεις.

Όπως έχουμε δει από την αρχιτεκτονική των υπολογιστών ή από τον τρόπο λειτουργίας των μεταγλωττιστών, πολλές εντολές μπορεί να αναδιαταχθούν, μπορεί για εξοικονόμηση χρόνου και βελτίωση της επίδοσης μια πρόσβαση στη μνήμη να μην γίνει ακριβώς όταν ζητείται αλλά αργότερα όταν το σύστημα κρίνει ότι είναι η καταλληλότερη στιγμή. Επίσης όταν υπάρχουν ταυτόχρονα αιτήματα πρέπει να προκύπτει με σαφήνεια πιο αίτημα θα πραγματοποιηθεί πότε και προφανώς να μην έχουμε αλληλοκαλύψεις αιτημάτων και εντολών που μπορούν να οδηγήσουν σε ασυνέπεια δεδομένων ή λανθασμένες αναγνώσεις και εγγραφές στοιχείων.

Για την αποφυγή όλων των παραπάνω κινδύνων και την προστασία των δεδομένων, της κατάστασης της μνήμης και της λειτουργίας των εφαρμογών και των προγραμμάτων μας, είναι απαραίτητοι οι μηχανισμοί συγχρονισμού. Ο συγχρονισμός μπορεί να γίνεται είτε από το υλικό είτε με λογισμικό. Υπάρχουν δε αλγόριθμοι και μηχανισμοί συγχρονισμού που παρότι υλοποιούνται με λογισμικό χρειάζονται υποστήριξη από ειδικό ή συγκεκριμένο υλικό, αυτοί οι μηχανισμοί ονομάζονται υβριδική. Με λίγα λόγια ο συγχρονισμός είναι ένας μηχανισμός που αναλαμβάνει να εγγυειθή την σωστή και συνεπή λειτουργία προγραμμάτων που εκτελούνται παράλληλα και αλληλεπιδρούν με την μνήμη. Με διάφορους τρόπους, υλικού, λογισμικού ή υβριδικούς, αναλαμβάνει να διαθέτει την πρόσβαση στη μνήμη σε κάθε πυρήνα ή νήμα προγράμματος με τρόπο ασφαλή για τα δεδομένα.

Κάποιες από τις παραδοσιαχές μεθόδους συγχρονισμού είναι τα χλειδώματα, οι ατομιχές λειτουργίες, μνήμη συναλλαγών (transactional memory) και οι παρακολουθητές και οι μεταβλητές συνθηκών (monitors and conditional variables). Ξεκινώντας από τα κλειδώματα, είναι ίσως ο πιο απλός σε ιδέα μηχανισμός και πολλές φορές αρκετά απλός στην υλοποίηση. Η ιδέα του μοντέλου αυτού για συγχρονισμό είναι η ύπαρξη ενός ή περισσοτέρων κλειδωμάτων τα οποία θα προστατεύουν τμήματα της δομής ή ολόκληρη τη δομή. Για να αλληλεπιδράσει ένας πυρήνας ή νήμα με την δομή θα πρέπει να αποκτήσει τον έλεγχο του κλειδώματος. Το κλείδωμα μπορεί να είναι μια δομή λογισμικού η οποία να υποστηρίζεται από ατομικές πράξεις στο υλικό ή άλλες λειτουργίες υλικού. Κάθε φορά που κάποιος θέλει να αποκτήσει πρόσβαση στη μνήμη, διεκδικεί το κλείδωμα και υπάρχει συναγωνισμός ανάμεσα στους πυρήνες ή τα νήματα. Όποιος αποκτήσει το κλείδωμα μπορεί να προχωρήσει και να έχει πρόσβαση στη

δομή ενώ οι υπόλοιποι που δεν το έλαβαν κάνουν μια άλλη εργασία, ανάλογα με το τι θέλει ο προγραμματιστής ή με το ποιος είναι ο σκοπός του προγράμματος. Παραδείγματος χάρη, οι πυρήνες που δεν θα καταφέρουν να λάβουν το κλείδωμα στην κατοχή τους μπορούν να επιστρέψουν κάνοντας κάποια άλλη εργασία και να το διεκδικήσουν αργότερα, μπορούν να συνεχίσουν να το ζητάνε μέχρι να το λάβουν ή ακόμα και να μπουν σε κατάσταση αναμονής για κάποιον χρόνο και να το διεκδικήσουν αργότερα. Κάθε μία στρατηγική έχει θετικά και αρνητικά σημεία οπότε επιλέγεται ανάλογα την εφαρμογή.

Πλέον υπάρχουν πολλές ιδέες και τρόποι υλοποίησης κλειδωμάτων που δεν μπορούν να εξαντληθούν σε αυτό το κείμενο. Όταν πρέπει να διαλέξουμε ανάμεσα στις διάφορες υλοποιήσεις κλειδωμάτων, χρειάζεται να κάνουμε μια επιλογή και να ζυγίσουμε παράγοντες όπως, επίδοση του μηχανισμού και της στρατηγικής του κλειδώματος, ευκολία στη χρήση και ευκολία στην υλοποίηση. Αν και παρακάτω θα μιλήσουμε περισσότερο για τις υλοποιήσεις που χρησιμοποιήθηκαν για τα πειράματά μας, ας αναφέρουμε εδώ ότι χρησιμοποιήσαμε απλές προσεγγίσεις με coarse grain κλειδώματα και busy waiting.

Η επόμενη τεχνική συγχρονισμού που χρησιμοποιείται ευρέως και αξίζει την αναφορά μας είναι οι ατομικές λειτουργίες. Η ατομικότητα εγγυάται την απομόνωση από διεργασίες που τρέχουν ταυτόχρονα και η ατομική αρχή εγγυάται ότι οι αλληλεπιδράσεις με την μνήμη φαίνονται σαν να έγιναν άμεσα και σαν να μην υπήρχε χρονική επικάλυψη ανάμεσα σε διαφορετικά αιτήματα.

Οι ατομικές λειτουργίες μπορούν να υλοποιηθούν με δύο τρόπους, μέσω υλικού ή λογισμικού. Η υλοποίηση μέσω υλικού περιλαμβάνει είτε πρωτόκολλα συνέπειας μεταξύ κρυφών μνημών ή μέσω καταχωρητών test&set. Και στις δύο αυτές περιπτώσεις πρέπει το διαθέσιμο υλικό να έχει ήδη μια από αυτές τις δομές, δηλαδή να έχει σχεδιαστεί ώστε να παρέχει στους χρήστες και προγραμματιστές αυτή τη δυνατότητα. Η άλλη περίπτωση είναι υλοποίηση ατομικών λειτουργιών μέσω δομών λογισμικού. Για αυτές τις περιπτώσεις χρησιμοποιούμε είτε έλεγχο σε μεταβλητές είτε ελέγχο στην χρονική σφραγίδα μιας λειτουργίας, δηλαδή την χρονική στιγμή που κάποια λειτουργία σημειώθηκε ως εκτελεσμένη. Αν μετά τον έλεγχο των χρόνων προκύψει επικάλυψη ή σύγκρουση λειτουργιών που μπορεί να οδηγήσει σε λανθασμένα ή αβέβαια δεδομένα, οι εντολές αυτές ακυρώνονται και πρέπει να επαναληφθούν ή ξεχνιούνται, ανάλογα με τις προγραμματιστικές επιλογές που έχουμε κάνει.

Στην συνέχεια έχουμε την μνήμη συναλλαγών, μια πιο προχωρημένη μέθοδο συγχρονισμού. Η μνήμη συναλλαγών είναι εμπνευσμένη από τους μηχανισμούς συναλλαγών βάσεων δεδομένων (database transactions mechanisms). Είναι μια μέθοδος συγχρονισμού υψηλότερου επιπέδου και αφαιρεί βάρος από τον προγραμματιστή αφού αυτός απλά σημειώνει σε ποια σημεία θέλει συγχρονισμό και το σύστημα αναλαμβάνει και εγγυάται ότι εκεί που ζητήθηκε θα υπάρξει ατομικότητα και συνέπεια δεδομένων. Με τον τρόπο αυτό μειώνονται οι πιθανότητες λαθών, μη αποδοτικών υλοποιήσεων και χρήσεων του συγχρονισμού αφού ο προγραμματιστής δεν επιβαρύνεται με αυτά, έχουν ασχοληθεί πριν από αυτόν άλλοι ώστε να υλοποιήσουν και να παρέχουν συγχρονισμό με μνήμη συναλλαγών, είτε μέσω υλικού είτε μέσω λογισμικού.

Η τελευταία από τις απλές μεθόδους συγχρονισμού που θα σχολιάσουμε είναι οι παρακολουθητές και οι μεταβλητές συνθηκών. Οι παρακολουθητές είναι δομές που συνδυάζουν

δεδομένα, μεθόδους και συγχρονισμό σε ένα πακέτο, όπως οι κλάσεις στις γλώσσες προγραμματισμού συνδυάζουν δεδομένα και μεθόδους. Η ύπαρξη παρακολουθητών πρέπει να συνοδεύεται από υποστήριξη υλικού, είτε μέσω παροχής ατομικών λειτουργιών είτε μέσω της δυνατότητας να απενεργοποιούνται οι διακοπές (interruprts). Η ιδέα για τους παρακολουθητές προέκυψε ώστε να αντιμετωπίσει προβλήματα που εμφάνιζαν τα κλειδώματα.

Τελειώνοντας την αναφορά μας στις μεθόδους και τις αρχές του συγχρονισμού θα αναφέρουμε δυο προχωρημένες τεχνικές συγχρονισμού, οι οποίες δεν χρησιμοποιούνται ευρέως στην πράξη αλλά μελετούνται ερευνητικά και παρουσιάζουν ενδιαφέρον. Οι μέθοδοι αυτοί είναι η ενσωματωμένη μνήμη συναλλαγών και τα C-κλειδώματα. Η ενσωματωμένη μνήμη συναλλαγών σαν ιδέα προήλθε από την απλή μνήμη συναλλαγών που αναφέραμε πιο πάνω. Αρχικά προορίζονταν για χρήση σε ενσωματωμένα συστήματα αλλά πλέον δοκιμάζεται η χρήση της και σε υπολογιστές γενιχού σχοπού. Η διαφορά της ενσωματωμένης μνήμης είναι ότι με προγραμματιστικές επιλογές και με πρωτόκολλα που χρησιμοποιούνται, προσπαθεί να καταναλώσει λιγότερη ενέργεια μειώνοντας το πλήθος των υποθετικών εκτελέσεων ώστε να μην χάνεται ενέργεια από τις αποτυχημένες υποθέσεις. Επίσης με βάση έρευνες μπορεί αχόμα να πετύχει και βελτίωση στην απόδοση. Το C-κλείδωμα τώρα, είναι μια μέθοδος συγχρονισμού που βασίζεται στο υλικό και απευθύνεται σε ενσωματωμένα συστήματα. Συνδυάζει τα κλειδώματα με την μνήμη συναλλαγών ώστε να προσφέρει έναν μηχανισμό συγχρονισμού που θα προσφέρει καλύτερη επίδοση. Με την υποστήριξη επιπλέον υλικού, οι πυρήνες αλληλεπιδρούν με την μνήμη με βάση τις αρχές της μνήμης συναλλαγών, αλλά αν διαπιστωθεί κάποια σύγκρουση στα δεδομένα τότε ο τρόπος συγχρονισμού αλλάζει και οι πυρήνες διεκδικούν κλειδώματα για να έχουν πρόσβαση στα δεδομένα αυτά. Με τον τρόπο αυτό προσπαθούμε να πετύχουμε μικρότερη κατανάλωση ενέργειας και να συνδυάσουμε τα πλεονεκτήματα των κλειδωμάτων με αυτά της μνήμης συναλλαγών.

#### 1.2 SCC και υλοποιήσεις

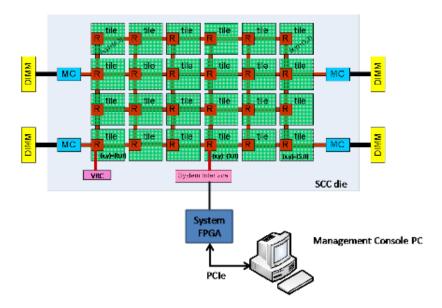

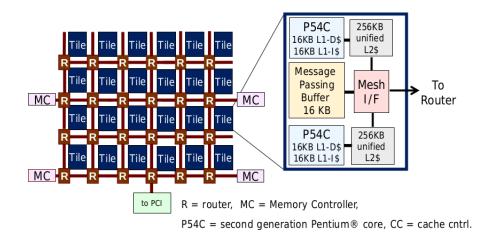

Ας δούμε τώρα την δομή του υπολογιστικού συστήματος SCC με περισσότερες λεπτομέρειες. Όπως έχουμε αναφέρει νωρίτερα το SCC αποτελείται από 48 πυρήνες. Οι πυρήνες αυτοί είναι οργανωμένοι ανά ζευγάρια σε ψηφίδες, δηλαδή συνολικά έχουμε 24 ψηφίδες με δύο πυρήνες στην κάθε μία. Οι ψηφίδες αυτές είναι διαταγμένες σε ένα πλέγμα  $6 \times 4$  και κάθε ψηφίδα έχει έναν διακομιστή (router) εντός της, ο οποίος αναλαμβάνει όλη την επικοινωνία με δομές εκτός της ψηφίδας, δηλαδή με τις υπόλοιπες ψηφίδες, με την κεντρική μνήμη ή με τον υπολογιστή που διαχειρίζεται όλο το σύστημα του SCC.

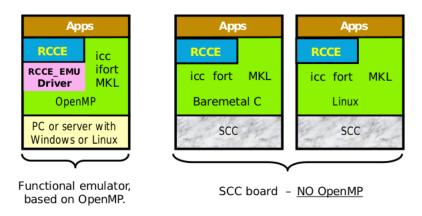

Για να λειτουργήσει το σύστημα SCC πρέπει να είναι συνδεδεμένο σε έναν υπολογιστή γενικού σκοπού, 64-bit ο οποίος μπορεί να τρέχει λειτουργικό GNU\Linux ή Windows και μέσω αυτού γίνεται η διαχείριση του SCC. Οι πυρήνες μπορούν επίσης να τρέξουν μια προσαρμοσμένη διανομή GNU\Linux αλλά αυτό δεν είναι απαραίτητο και εξαρτάται από τις επιλογές και τον στόχο του προγραμματιστή. Δηλαδή οι πυρήνες μπορούν να χρησιμοποιηθούν και χωρίς έτοιμο λειτουργικό, αν ο προγραμματιστής θέλει να έχει πρόσβαση σε χαμηλό επίπεδο προγραμματισμού των πυρήνων.

Η αρχιτεχτονιχή των επεξεργαστών είναι IA P54C και είναι κατασκευασμένοι σε τεχνολογία 45nm high K metal gate CMOS και σε όλο το chip υπάρχουν 1,3 δισεκατομμύρια τρανζίστορ. Το chip επίσης διαθέτει τέσσερις ελεγκτές μνήμης (memory controllers) οι οποίοι χρησιμοποιούνται από τους πυρήνες για να επικοινωνήσουν με την κεντρική μνήμη. Τον ποιο ελεγκτή θα χρησιμοποιήσει κάθε πυρήνας εξαρτάται από τη θέση του πυρήνα και το τμήμα της μνήμης που θέλει να προσπελάσει. Η διαδρομή δηλαδή που θα ακολουθήσει το αίτημα κάποιου πυρήνα εξαρτάται από το σύστημα και δεν το καθορίζει άμεσα ο προγραμματιστής. Επίσης από το σύστημα επιλέγεται η διαδρομή που θα ακολουθήσει κάποιο αίτημα ή μήνυμα από κάποιον πυρήνα προς κάποιον άλλο. Ο προγραμματιστής δεν επιλέγει και δεν καθορίζει με ποιον τρόπο θα κινηθεί το μήνυμα μέσα στον δίαυλο του chip για να φθάσει στον προορισμό του.

Το SCC επίσης έχει την υλική υποδομή και μας προσφέρει προγραμματιστικά εργαλεία έτσι ώστε να μπορούμε να ελέγξουμε και να μεταβάλλουμε την συχνότητα με την οποία δουλεύουν οι πυρήνες ακόμα και την τάση τροφοδοσίας τους. Για την συχνότητα έχουμε 24 διαιρέτες, δηλαδή κάθε ψηφίδα μπορεί να έχει την δική της συχνότητα, ενώ για την τάση έχουμε 7 πεδία τιμών που μπορούμε να επιλέξουμε και οι πυρήνες μπορούν να ρυθμιστούν σε ομάδες των 4. Οπότε έχουμε 6 σύνολα πυρήνων που μπορούν να έχουν διαφορετική τάση.

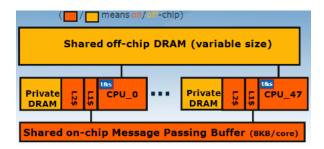

Ας περάσουμε τώρα να δούμε λίγο την οργάνωση της μνήμης στο σύστημα μας. Γενικά η μνήμη του συστήματος χωρίζεται σε κρυφή μνήμη εντός των ψηφίδων, καταχωρητές ανταλλαγής μηνυμάτων (message passing buffers) και αυτοί εντός των ψηφίδων και στην κύρια μνήμη η οποία βρίσκεται εκτός του chip.

Σχετικά με την κρυφή μνήμη, υπάρχει κρυφή μνήμη δύο επιπέδων. Κάθε πυρήνας έχει συνολικά 32 KB κρυφή μνήμη πρώτου επιπέδου, L1, από αυτή, τα 16 KB είναι κρυφή μνήμη εντολών και τα άλλα 16 KB κρυφή μνήμη δεδομένων. Επίσης κάθε πυρήνας έχεις τη δικιά του κρυφή μνήμη δευτέρου επιπέδου, L2, η οποία είναι εννοποιημένη και έχει συνολική χωρητικότητα 256 KB.

Σε κάθε ψηφίδα επίσης υπάρχουν 16 KB μνήμης καταχωρητών ανταλλαγής μηνυμάτων. Αυτό σημαίνει ότι συνολικά στο chip έχουμε 382 KB τέτοιας μνήμης, αφού υπάρχουν 24 ψηφίδες. Η μνήμη αυτή είναι τύπου SRAM οπότε είναι αρκετά γρήγορη. Κάθε πυρήνας έχει δικαίωμα να γράψει και να διαβάσει σε οποιονδήποτε καταχωρητή, ανεξάρτητα σε ποια ψηφίδα βρίσκεται. Επομένως είναι μια μοιραζόμενη, κατανεμημένη μνήμη εντός του chip.

Η χύρια μνήμη εχτός του chip μπορεί να χυμανθεί μεταξύ 16 GB και 64 GB. Κάθε ελεγχτής μνήμης, από τους 4 που υπάρχουν, μπορεί να διευθυνσιοδοτήσει από 4 έως 16 GB και κάθε πυρήνας μπορεί να δει έως 4 GB χύριας μνήμης. Η χύρια αυτή μνήμη είναι τύπου DRAM και μπορεί να λειτουργήσει τόσο ως ιδιωτιχή όσο και ως μοιραζόμενη. Τα δεδομένα από την μνήμη αυτή αντιγράφονται στις χρυφές μνήμες των δύο επιπέδων χάτι όμως που δεν συμβαίνει με τα δεδομένα που προέρχονται από χαταχωρητές ανταλλαγής μηνυμάτων. Τα δεδομένα που προέρχονται από αυτούς τους χαταχωρητές είναι χατάλληλα σημειωμένα και δεν παραμένουν στην χρυφή μνήμη.

Ένα τελευταίο χαρακτηριστικό των μνημών που θα φανεί σημαντικό στην επεξήγηση των αποτελεσμάτων αργότερα είναι το ότι δεν υπάρχει πρωτόκολλο συνάφειας μεταξύ των κρυφών

μνημών των διαφόρων πυρήνων. Αυτό έχει ως συνέπεια, όταν χρησιμοποιούμε την κύρια μνήμη ως μοιραζόμενη, να είμαστε αναγκασμένη κάθε φορά που μεταβάλλουμε κάποιο μοιραζόμενο δεδομένο, για να είναι αυτό εμφανές σε όλους τους πυρήνες να πρέπει να γραφτεί αμέσως στην κύρια μνήμη. Ακόμα, αν θέλουμε να διαβάσουμε ένα μοιραζόμενο δεδομένο, το οποίο το έχουμε διαβάσει και νωρίτερα, δεν πρέπει να κοιτάμε στην κρυφή μνήμη αλλά πρέπει να το φέρνουμε εκ νέου από την κύρια μνήμη, γιατί μπορεί κάποιος άλλος πυρήνας στο μεταξύ, να το έχει μεταβάλει. Για να λύσουμε όλο αυτό το πρόβλημα, το προγραμματιστικό μοντέλο του SCC μας παρέχει μια εντολή καθαρισμού της κρυφής μνήμης από τα μοιραζόμενα δεδομένα. Αυτό σημαίνει ότι πριν διαβάσουμε ένα δεδομένο της μοιραζόμενης μνήμης ή αφού γράψαμε σε αυτό, πρέπει να εκτελέσουμε την εντολή εκκένωσης της κρυφής μνήμης από τα μοιραζόμενα δεδομένα.

Τελειώνοντας την αναφορά και την παρουσίαση του συστήματος, πρέπει να αναφερθούμε στο προγραμματιστικά μοντέλα που είναι διαθέσιμα και σε αυτό που χρησιμοποιήσαμε για την ανάπτυξη των εφαρμογών που χρειάστηκαν για τις εργασίες της διπλωματικής αυτής.

Αρχικά να πούμε ότι αν κάποιος δεν έχει πρόσβαση σε κάποιο φυσικό μηχάνημα SCC, τότε υπάρχει και ένας προσομοιωτής του περιβάλλοντος. Αυτός λειτουργεί σε υπολογιστές με λειτουργικά συστήματα GNU\Linux ή Windows και βασίζεται στην γλώσσα OpenMp για να υλοποιήσει τις παραλληλίες. Ωστόσο, όσοι χρησιμοποιούν τον προσομοιωτή αυτόν θα πρέπει να είναι ενήμεροι ότι δεν είναι ασφαλές να εξάγονται συμπεράσματα ως προς μετρήσεις γιατί οι χρόνοι και άλλα στοιχεία, όπως η κατανάλωση είναι πολύ πιθανόν να διαφέρουν από το πραγματικό σύστημα.

Στο πραγματικό σύστημα τώρα, όπως είπαμε και πριν υπάρχει η επιλογή να φορτώσουμε κάποια ειδική διανομή GNU\Linux για τους πυρήνες ή να τους χρησιμοποιήσουμε χωρίς λειτουργικό σύστημα, στην Baremetal εκδοχή, όπως λέγεται. Προφανώς αν επιλέξουμε να φορτώσουμε λειτουργικό σύστημα στους πυρήνες θα έχουμε την δυνατότητα να χρησιμοποιήσουμε και να επωφεληθούμε από πολλά έτοιμα εργαλεία λογισμικού που είναι συμβατά με το λειτουργικό. Οι εφαρμογές που γράφουμε για τους πυρήνες του SCC μπορούν να είναι είτε σε γλώσσα C είτε σε γλώσσα Fortran, γιατί για αυτές τις δύο γλώσσες παρέχονται μεταγλωττιστές από την Intel.

Για την περαιτέρω βοήθεια και στήριξη της προγραμματιστικής κοινότητας του SCC, παρέχεται μια επιπλέον προγραμματιστική διεπαφή, με την μορφή μιας βιβλιοθήκης που εμπλουτίζει τη γλώσσα C. Η προγραμματιστική αυτή διεπαφή λέγεται RCCE και παρέχει έναν αριθμό έτοιμων συναρτήσεων που βοηθάνε σημαντικά και απλοποιούν το προγραμματιστικό έργο. Για την ανάπτυξη των εφαρμογών για τις μετρήσεις αυτής της διπλωματικής, χρησιμοποιήσαμε την βιβλιοθήκη RCCE και τις συναρτήσεις που προσφέρει για επικοινωνία των πυρήνων, για υλοποίηση σημαιών που είναι χρήσιμες προγραμματιστικές δομές για συγχρονισμό και επικοινωνία αλλά και άλλες συναρτήσεις που βοήθησαν σημαντικά.

Ας δούμε τώρα με περισσότερες λεπτομέρειες τις υλοποιήσεις που χρησιμοποιήσαμε για τα διάφορα μοντέλα κάθε δομής δεδομένων του αξιολογήσαμε. Για την στοίβα υλοποιήσαμε τρία μοντέλα, ένα πελάτη-εξυπηρετητή, ένα μοντέλο πελάτη-εξυπηρετητή με εξάλειψη, θα εξηγήσουμε παρακάτω τι σημαίνει αυτό, και ένα μοντέλο με ένα κλείδωμα για όλη τη δομή.

Για την FIFO ουρά υλοποιήσαμε επίσης τρία μοντέλα, ένα πελάτη-εξυπηρετητή, ένα μοντέλο με ένα κλείδωμα και ένα μοντέλο με δύο κλειδώματα. Τέλος για τον σωρό υλοποιήσαμε δύο μοντέλα, ένα πελάτη εξυπηρετητή και ένα με ένα κλείδωμα.

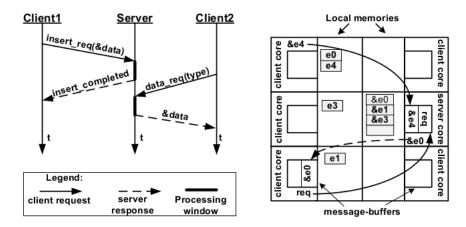

Ξεχινώντας ας μιλήσουμε πρώτα για την δομή των υλοποιήσεων της στοίβας. Όπως αναφέραμε και πιο πάνω, για την ανάπτυξη των εφαρμογών μας χρησιμοποιήσαμε την διεπαφή RCCE και προγραμματίσαμε σε γλώσσα C. Στην πρώτη υλοποίηση, στο μοντέλο πελάτηεξυπηρετητή, από τους N πυρήνες που δεσμεύουμε, οι N-1 είναι πελάτες και ένας πυρήνας είναι ο εξυπηρετητής. Ο ρόλος του εξυπηρετητή είναι να λαμβάνει αιτήματα από τους πελάτες και να τα υλοποιεί. Η δομή δεδομένων βρίσκεται στην ιδιωτική μνήμη του εξυπηρετητή και μόνο αυτός έχει πρόσβαση σε αυτήν. Οι πελάτες στέλνουν τα αιτήματά τους στον εξυπηρετητή και περιμένουν μέχρι να υλοποιηθούν για να προχωρήσουν στο επόμενο. Η ανταλλαγή αυτή γίνεται μέσω της μνήμης των καταχωρητών ανταλλαγής μηνυμάτων. Συγκεκριμένα οι δομή δεδομένων δέχεται αχεραίους των 32 bit ως στοιχεία. Επομένως οι πελάτες γράφουν στον τοπικό τους καταχωρητή των αριθμό που θέλουν να προσθέσουν στη δομή, ειδοποιούν μέσω σημαιών τον εξυπηρετητή για το αίτημά τους, ο εξυπηρετητής όταν κληθεί να υλοποιήσει αυτό το αίτημα διαβάζει από τον καταχωρητή του πελάτη τον ακέραιο και τον προσθέτει στην δομή. Έπειτα ενημερώνει κατάλληλα τον πελάτη ότι το αίτημα έχει ολοκληρωθεί. Αντίστοιχα όταν κάποιος πελάτης ζητάει να αφαιρεθεί κάποιο στοιχείο από τη δομή περιμένει μέχρι ο εξυπηρετητής να γράψει τον ακέραιο στον καταχωρητή τού πελάτη, από όπου ο δεύτερος τον διαβάζει και συνεχίζει την λειτουργία του.

Η δομή των προγραμμάτων είναι η εξής, αρχικά κάνουμε τις κατάλληλες δεσμεύσεις μνήμης για την δομή, για τις σημαίες που θα χρησιμοποιήσουμε και για τους καταχωρητές ανταλλαγής μηνυμάτων. Στη συνέχεια αρχικοποιούμε την δομή μας ώστε να υπάρχουν κάποια δεδομένα μέσα από την αρχή. Έπειτα οι πυρήνες χωρίζονται σε δύο μέρη και το καθένα εκτελεί διαφορετικό κομμάτι κώδικα. Οι πελάτες εισέρχονται σε έναν βρόχο, ο οποίος τρέχει καθορισμένες από εμάς φορές, ανάλογα με το πόσα αιτήματα θέλουμε να υποβάλλουμε. Αφού εκτελέσουν όλα τα αιτήματά τους, βγαίνουν από το βρόχο και μπορούν να τερματίσουν.

Από την άλλη ο εξυπηρετητής εισέρχεται σε έναν βρόχο ο οποίος επαναλαμβάνεται συνεχώς ελέγχοντας μόνο μια συνθήκη. Η συνθήκη αυτή ικανοποιείται όταν όλοι οι πελάτες έχουν ολοκληρώσει τα αιτήματά τους, τότε ο εξυπηρετητής σταματάει να επαναλαμβάνει τον βρόχο, προχωράει σε επόμενο κομμάτι όπου τυπώνει τα αποτελέσματα, τον χρόνο δηλαδή που έτρεξε το πρόγραμμα και μετά τερματίζει.

Μέσα στον βρόχο τώρα, υπάρχουν δύο εμφωλευμένοι βρόχοι. Στον πρώτο ο εξυπηρετητής ελέγχει με τη σειρά δύο πίναχες που περιέχουν σημαίες. Οι σημαίες είναι μια προγραμματιστιχή δομή που μας παρέχει η διεπαφή RCCE. Θα μπορούσαμε να πούμε ότι μοιάζει με μία μεταβλητή τύπου boolean αφού μπορεί να πάρει μόνο δύο τιμές. Η δομή αυτή υλοποιείται σε μνήμη καταχωρητών ανταλλαγής μνήμης, οπότε με τις συναρτήσεις που επίσης παρέχονται από την διεπαφή RCCE ένας πυρήνας μπορεί να διαβάσει οποιαδήποτε σημαία άλλου πυρήνα. Έτσι έχουμε για τις εφαρμογές μας έναν εύχολο τρόπο συγχρονισμού και ανταλλαγής μηνυμάτων. Συγχεχριμένα κάθε πελάτης έχει δύο σημαίες, μια για κάθε είδος αιτήματος που μπορεί να κάνει, εισαγωγή ή εξαγωγή στοιχείου. Ανάλογα με το τι θέλει να κάνει ο πελάτης θέτει την

κατάλληλη σημαία και στην συνέχεια ο εξυπηρετητής ελέγχοντας συνεχώς όλες τις σημαίες μπορεί να δει αυτή τη θέση της σημαίας και έτσι να ενημερωθεί για το αίτημα και να προχωρήσει στην εξυπηρέτησή του. Αφού σε κάθε επανάληψη του εξωτερικού βρόχου ελέγξει όλες τις σημαίες, όλων των πελατών και για τους δύο τύπους αιτημάτων, προχωράει στον επόμενο βρόχο, στον οποίο ελέγχει τις σημαίες τερματισμού. Με τις σημαίες αυτές κάθε πελάτης ενημερώνει πότε έχει ολοκληρώσει τα αιτήματα του. Έτσι μπορεί και ο εξυπηρετητής να ξέρει πότε δεν υπάρχουν άλλα αιτήματα προς εξυπηρέτηση και μπορεί να σταματήσει να ελέγχει τις σημαίες αιτημάτων. Ο εξυπηρετητής λοιπόν ελέγχει κάθε φορά με τη σειρά τις σημαίες τερματισμού ώσπου να βρει κάποια που δεν είναι σε θέση. Αυτό σημαίνει ότι τουλάχιστον ένας πελάτης έχει αιτήματα που περιμένουν, άρα επαναλαμβάνει τον εξωτερικό βρόχο. Αν όμως όλες οι σημαίες τερματισμού είναι σε θέση, τότε μπορεί και ο εξυπηρετητής να τερματίσει.

Με λίγα λόγια αυτή είναι η λειτουργία του μοντέλου πελάτη εξυπηρετητή. Αυτό που κάναμε στην υλοποίηση με την εξάλειψη είναι ότι κρατήσαμε όλο το προηγούμενο πρόγραμμα ίδιο αλλά προσθέσαμε έναν επιπλέον έλεγχο. Αυτό που γίνεται με την εξάλειψη είναι ότι όταν ο εξυπηρετητής χειρίζεται ένα αίτημα προσθήκης στοιχείου στη δομή, ελέγχει το αμέσως επόμενο αίτημα αν είναι για αφαίρεση στοιχείου από τη δομή. Αν αυτό συμβεί τότε δεν υπάρχει λόγος να πειράξει την στοίβα, αντιγράφει απλά το στοιχείο που θα προσέθετε στον καταχωρητή του πελάτη που έκανε αίτημα αφαίρεσης στοιχείου. Έτσι γλιτώνουμε προσβάσεις στην κύρια μνήμη, με το κόστος όμως ενός επιπλέον ελέγχου. Αργότερα στα αποτελέσματα θα δούμε πώς απέδωσε αυτή η τεχνική. Δηλαδή η αλλαγή σε σχέση με το προηγούμενο μοντέλο είναι ο επιπλέον έλεγχος του επόμενου αιτήματος στην περίπτωση προσθήκης στοιχείου και η κατάλληλη μετακίνηση του στοιχείου αυτού.

Ας μιλήσουμε τώρα για το μοντέλο με το κλείδωμα. Το μοντέλο αυτό διαφέρει σημαντικά με το προηγούμενο, η δομή δεδομένων βρίσκεται σε μοιραζόμενη μνήμη εκτός του chip και έχουν πρόσβαση σε αυτή όλοι οι πυρήνες. Σε αυτό το μοντέλο δεν υπάρχει κάποιος διαμεσολαβητής ή κάποιος που αναλαμβάνει να χειριστεί αιτήματα. Κάθε πυρήνας διεκδικεί πρόσβαση στη δομή και εκτελεί την εργασία του. Η πρόσβαση στην δομή γίνεται μέσω ενός κεντρικού κλειδώματος. Για να υλοποιήσουμε αυτό το κλείδωμα χρησιμοποιήσαμε τον καταχωρητή τεst&set που υπάρχει στο υλικό κάθε πυρήνα. Συγκεκριμένα χρησιμοποιήσαμε πάντα τον καταχωρητή του πυρήνα με το νούμερο #0. Οπότε κάθε πυρήνας που θέλει να αλληλεπιδράσει με την στοίβα, διεκδικεί το κλειδί που υλοποιείται από τον καταχωρητή που αναφέραμε. Το κλειδί αυτό είναι busy waiting και θα δούμε αργότερα πώς αυτό επηρεάζει την επίδοση των προγραμμάτων.

Στις εφαρμογές αυτού του μοντέλου αρχικά γίνονται οι δεσμεύσεις μνήμης από τους πυρήνες και στη συνέχεια αρχικοποιείται η μνήμη, όπως κάναμε και στο μοντέλο πελάτη-εξυπηρετητή. Έπειτα οι πυρήνες μπαίνουν σε ένα βρόχο του οποίου οι επαναλήψεις εξαρτώνται από το πόσα αιτήματα θέλουμε να υλοποιήσει κάθε πυρήνας. Μέσα σε αυτό τον βρόχο, ανάλογα με το σενάριο που θέλουμε να εκτελέσουν οι πυρήνες, κάνουν είτε προσθήκες είτε αφαιρέσεις στοιχείων από την στοίβα. Αφού κάποιος πυρήνας τελειώσει με τα αιτήματά του τότε βγαίνει από το βρόχο και μπλοκάρει σε ένα φράγμα (barrier) ώσπου όλοι οι πυρήνες να τελειώσουν. Τότε, αφού δηλαδή όλοι οι πυρήνες φθάσουν στο φράγμα, ένας πυρήνας

αναλαμβάνει να τυπώσει τα δεδομένα που μετρήσαμε και έπειτα όλοι τερματίζουν.

Όπως έχουμε αναφέρει και πιο πάνω, με την χρήση της μοιραζόμενης μνήμης πρέπει να φροντίζουμε για την σωστή εκδοχή των δεδομένων στις κρυφές μνήμες των πυρήνων. Οπότε σε αυτό το μοντέλο, με κάθε προσθήκη ή αφαίρεση στοιχείου από κάποιον πυρήνα αναγκαζόμαστε να κάνουμε συχνά εκκαθάριση της κρυφής μνήμης από τα μοιραζόμενα δεδομένα ώστε να είναι η τελευταία εκδοχή τους εμφανής σε όλους τους πυρήνες.

Προχωρώντας τώρα στις υλοποιήσεις της FIFO ουράς, τα μοντέλα πελάτη-εξυπηρετητή και ενός κλειδώματος δεν διαφέρουν ιδιαίτερα από τις υλοποιήσεις της στοίβας. Το μοντέλο πελάτη-εξυπηρετητή δεν αλλάζει σημαντικά αν εξαιρέσει κανείς ότι οι συναρτήσεις για τις πράξεις με την δομή δεδομένων είναι προφανώς διαφορετικές από αυτές για την στοίβα. Το μοντέλο με το κλείδωμα έχει και εδώ ένα κλειδί που υλοποιείται με τον καταχωρητή test&set του πυρήνα #0 και κλειδώνει όλη τη δομή, και τα δύο άκρα.

Από την άλλη μεριά το μοντέλο με τα δύο κλειδώματα εμφανίζεται σαν υλοποίηση μόνο στην δομή της ουράς. Εδώ χρησιμοποιήσαμε δύο κλειδιά, ένα στον πυρήνα #0 και ένα στον πυρήνα #1. Το ένα χρησιμοποιείται για την πρόσβαση στο άκρο που προσθέτονται στοιχεία και το άλλο για το άκρο που αφαιρούνται στοιχεία. Στα προγράμματά μας φυσικά κάνουμε τους κατάλληλους ελέγχους ώστε αν αδειάσει κάποια στιγμή η δομή να μην μπορεί ο δείκτης του ενός άκρου να ξεπεράσει τον άλλο. Οι πυρήνες διεκδικούν το αντίστοιχο κλειδί ανάλογα με την δουλειά που θέλουν να κάνουν.

Τέλος για την δομή του σωρού, είχαμε δύο υλοποιήσεις οι οποίες επίσης δεν διαφέρουν ιδιαίτερα από αυτές ας πούμε της στοίβας. Η διαφορά στις υλοποιήσεις του σωρού, εκτός από τις διαφορετικές συναρτήσεις για την αφαίρεση μεγίστου και προσθήκη στοιχείου στην δομή, είναι ότι κατά την αρχικοποίηση της δομής, και στα δύο μοντέλα, εισάγουμε τα μισά στοιχεία από αυτά που θέλουμε για την αρχικοποίηση, μετά καλούμε την συνάρτηση που δημιουργεί τον σωρό και τα υπόλοιπα εισάγονται τηρώντας τις ιδιότητες του σωρού. Αυτό γίνεται για να εξοικονομήσουμε λίγο χρόνο στην αρχικοποίηση.

#### 1.3 Αξιολόγηση δομών δεδομένων

Σε αυτό το σημείο ας αναφερθούμε με περισσότερες λεπτομέρειες στην δομή των σεναρίων που εκτελούσαν τα προγράμματα και στα μεγέθη τα οποία μετρήσαμε και αξιολογήσαμε. Συνολικά χρησιμοποιήσαμε τέσσερα διαφορετικά σενάρια για να αξιολογήσουμε τις δομές μας. Τρία από αυτά είχαν ίσο αριθμό αφαιρέσεων και προσθηκών στοιχείων στη δομή ενώ χρησιμοποιήσαμε και ένα σενάριο με τυχαίο αριθμό από τα είδη των αιτημάτων, ο τυχαίος αυτός αριθμός δημιουργήθηκε με την συνάρτηση rand της γλώσσας C.

Το πρώτο από τα σενάρια με ίσο αριθμό προσθηκών και αφαιρέσεων είχε τυχαία κατανεμημένο τον τύπο των διεργασιών με την δομή. Δηλαδή κατασκευάσαμε έναν πίνακα 200 θέσεων, που περιείχε τους αριθμούς 0 και 1. Κάθε πυρήνας ξεκίναγε να διαβάζει τον πίνακα από την θέση που αντιστοιχούσε στο ID του. Κάθε φορά κινούνταν κατά μια θέση μέσα στον πίνακα, αν τα αιτήματα ήταν πάνω από 200 ή έφτανε στο τέλος του πίνακα απλά ξεκίναγε πάλι από τη θέση 0. Ανάλογα με τον αριθμό που θα διάβαζε εκτελούσε την αντίστοιχη εργασία, είτε

προσθήχη είτε αφαίρεση.

Το δεύτερο σενάριο που είχε συνολικά ίσο αριθμό προσθηκών και αφαιρέσεων στοιχείων βασίζονταν στην παραδοχή ότι το πρώτο μισό των πυρήνων θα έκαναν μόνο προσθήκες και το δεύτερο μισό μόνο αφαιρέσεις στοιχείων. Για παράδειγμα σε ένα μοντέλο οποιασδήποτε δομής με ένα κλείδωμα, αν τρέχαμε την εφαρμογή μας με 12 πυρήνες, οι 6 με τα μικρότερα αναγνωριστικά (0, 1, 2, 3, 4, 5) θα έκανα συνέχεια προσθήκες, ενώ οι υπόλοιποι 6 πυρήνες μόνο αφαιρέσεις στοιχείων από τη δομή. Συνολικά όμως θα γίνονταν ίσο πλήθος αφαιρέσεων και προσθηκών.

Το τρίτο και τελευταίο σενάριο που είχε μοιρασμένα αιτήματα προσθηκών και αφαιρέσεων στοιχείων βασίζονταν σε διαφορετική κατανομή των αιτημάτων σε σχέση με τα δύο προηγούμενα. Και εδώ οι μισοί πυρήνες έκαναν μόνο προσθήκες και οι υπόλοιποι μόνο αφαιρέσεις αλλά αυτή τη φορά άλλαζε η κατανομή τους στο chip. Οι πυρήνες με περιττό αναγνωριστικό (ID) θα κάνουν μόνο προσθήκες, ενώ οι πυρήνες με άρτιο αναγνωριστικό θα αφαιρούν στοιχεία. Δηλαδή αν τρέχουμε ένα πρόγραμμα με 10 πυρήνες και υλοποίηση με ένα κλείδωμα, οι πυρήνες με αναγνωριστικά 1, 3, 5, 7, 9 θα έκαναν μόνο προσθήκες στοιχείων στην δομή, ενώ οι υπόλοιπη θα αφαιρούσαν στοιχεία. Έτσι σε κάθε ψηφίδα θα είχαμε έναν πυρήνα να προσθέτει στοιχεία και έναν πυρήνα μόνο να αφαιρεί.

Τέλος πήραμε μετρήσεις και με ένα σενάριο που είχε τυχαίο πλήθος αφαιρέσεων στοιχείων και προσθηκών. Αποτελούνταν και αυτό από έναν πίνακα 200 θέσεων με 0 και 1 τον οποίο επαναλάμβανε κάθε πυρήνας μέχρι να ολοκληρώσει όλα του τα αιτήματα. Ξεκίναγε την ανάγνωση του πίνακα και εδώ ανάλογα με το αναγνωριστικό του (ID) και κάθε φορά προχώραγε μια θέση.

Ένα άλλο χαρακτηριστικό της πλειοψηφίας των πειραμάτων που πραγματοποιήσαμε είναι ότι δεσμεύαμε τους πυρήνες με τη σειρά και όχι διασκορπισμένους. Δηλαδή αν θέλαμε να τρέξουμε ένα πρόγραμμα χρησιμοποιώντας 20 πυρήνες τότε δεσμεύαμε τους πυρήνες από #0 έως #19. Στα περισσότερα πειράματα ακολουθήσαμε αυτή την τακτική, αλλά πραγματοποιήσαμε και μερικά πειράματα για να δούμε πόσο επηρεάζει η θέση των πυρήνων την επίδοση.

Ας μιλήσουμε τώρα για τα μεγέθη που μετρήσαμε και αξιολογήσαμε, οι μετρήσεις φαίνονται στο κύριο μέρος της εργασίας. Αρχικά μετρήσαμε τις χρονικές επιδόσεις των δομών. Συγκρίναμε για κάθε δομή δεδομένων πώς συμπεριφέρονται χρονικά οι διαφορετικές υλοποιήσεις και τα διαφορετικά μοντέλα συγχρονισμού. Επίσης φτιάξαμε και διαγράμματα για την απόδοση (throughput) των δομών δεδομένων. Για τις μετρήσεις αυτές χρησιμοποιήσαμε τα σενάρια που παρουσιάσαμε παραπάνω.

Έπειτα μετρήσαμε την κατανάλωση ενέργειας των προγραμμάτων. Το σύστημα SCC παρέχει την δυνατότητα να παίρνουμε μετρήσεις της τάσης και του ρεύματος ανά τακτά χρονικά διαστήματα. Έτσι με την επεξεργασία αυτών των μετρήσεων μπορούμε να υπολογίσουμε την ενέργεια που καταναλώνεται από το σύστημα όταν εκτελείται μια εφαρμογή. Και εδώ πήραμε μετρήσεις για τα σενάρια που αναφέραμε νωρίτερα.

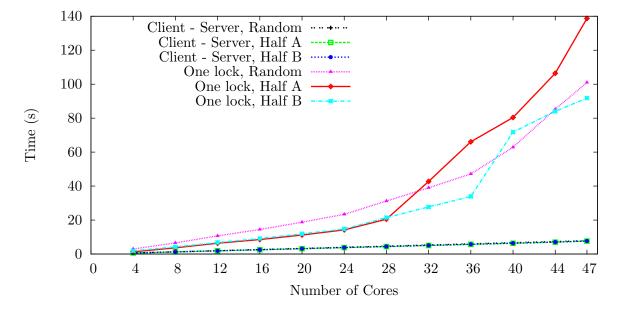

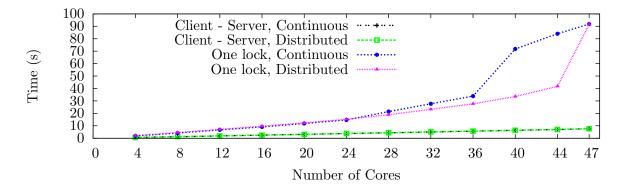

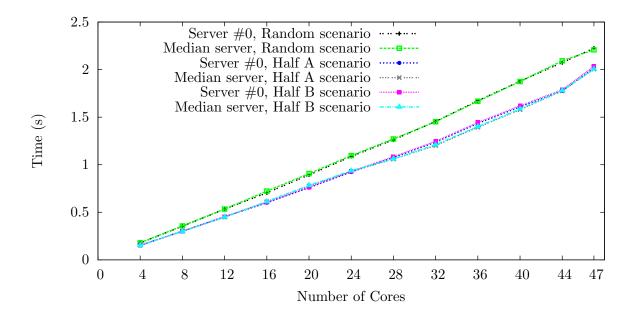

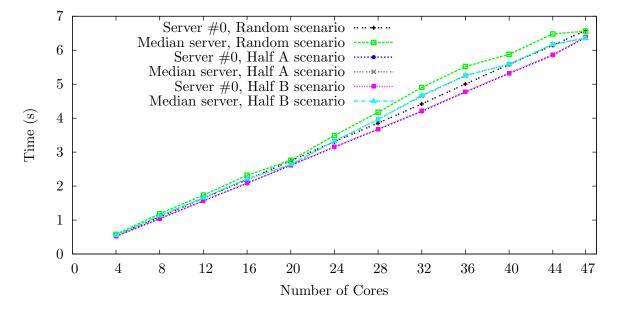

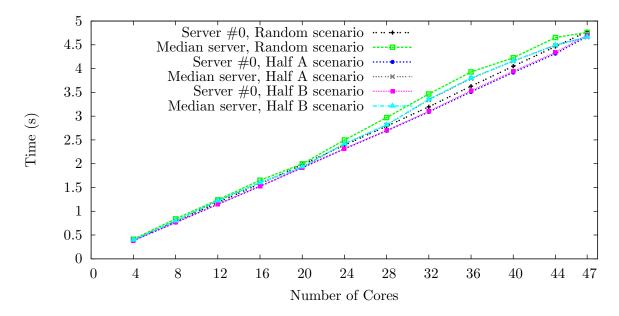

Ακόμη αξιολογήσαμε κατά πόσο παίζει ρόλο η κατανομή των πυρήνων στο chip και συγκρίναμε τις χρονικές επιδόσεις μιας διασκορπισμένης κατανομής σε σχέση με την συνεχή δέσμευση των πυρήνων. Είδαμε επίσης αν παίζε ρόλο η θέση του πυρήνα εξυπηρετητή στα

μοντέλα πελάτη-εξυπηρετητή κάθε δομής δεδομένων. Συγκρίναμε δύο τακτικές, μία ο εξυπηρετητής να είναι πάντα ο πρώτος πυρήνας, δηλαδή αυτός με αναγνωριστικό #0, και μια ο εξυπηρετητής να είναι κάθε φορά ο μεσαίος σε σχέση με αυτούς που έχουμε δεσμεύσει.

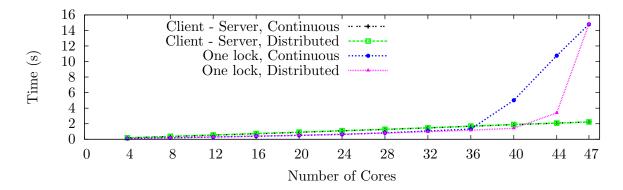

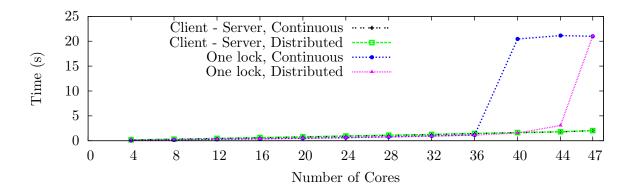

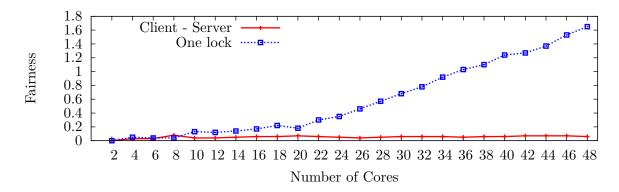

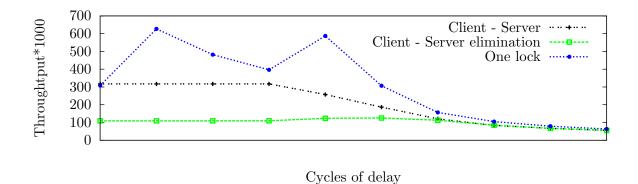

Κλείνοντας, μετρήσαμε κατά πόσο είναι δίκαιες οι μέθοδοι συγχρονισμού. Δηλαδή πόσο δίκαιο είναι το μοντέλο πελάτη-εξυπηρετητή και πόσο δίκαια είναι τα κλειδώματα. Και είδαμε ακόμη πώς θα συμπεριφέρονταν το σύστημα και οι δομές δεδομένων αν μεσολαβούσα κάποια καθυστέρηση μεταξύ των αιτημάτων κάθε πυρήνα. Δοκιμάσαμε με διάφορα μεγέθη καθυστέρησης και ξεκινήσαμε από μικρή καθυστέρηση αυξάνοντάς την σταδιακά. Η καθυστέρηση αυτή θα μπορούσε να προσομοιώσει ένα πραγματικό σύστημα στο οποίο μεταξύ των αιτημάτων θα μεσολαβούσαν κάποιοι υπολογισμοί από κάθε πυρήνα ή θα ασχολούνταν οι πυρήνες και με άλλες εργασίες.

#### 1.4 Συμπεράσματα και προεκτάσεις

Καταλήγοντας στα συμπεράσματα αυτής της εργασίας, τα οποία προέχυψαν από τις μετρήσεις που πήραμε παραθέτουμε τα παραχάτω σχόλια.

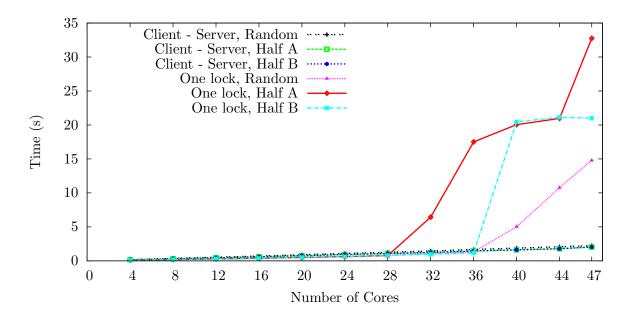

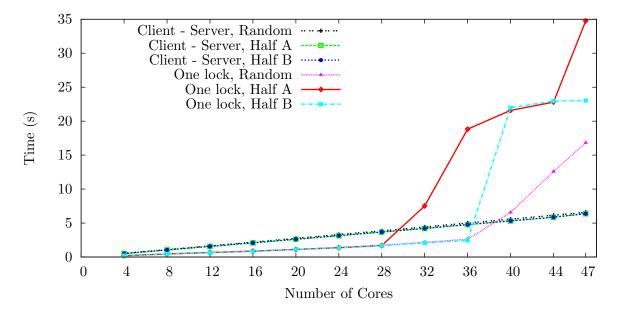

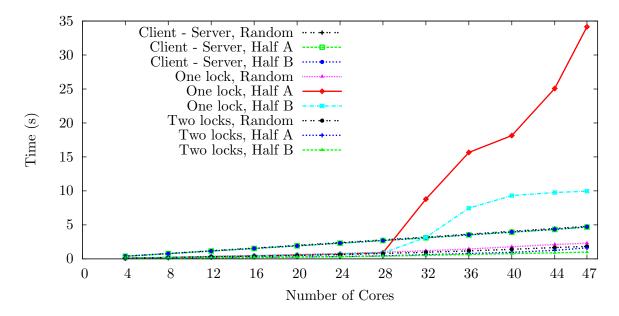

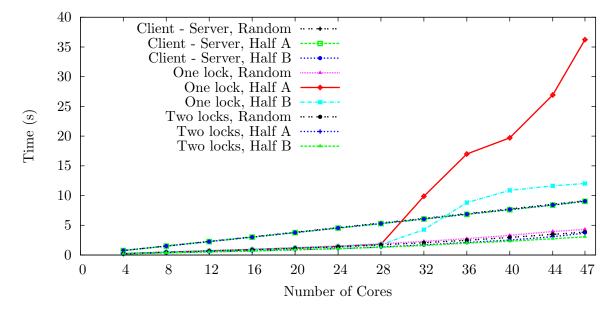

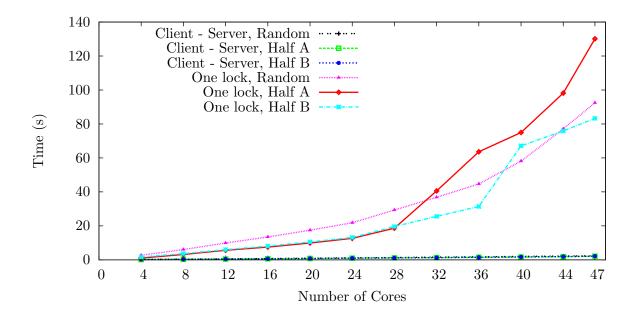

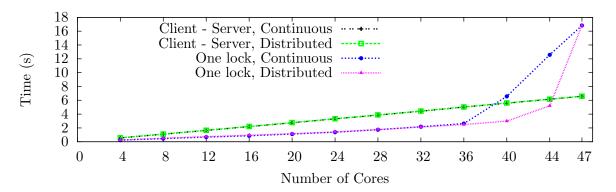

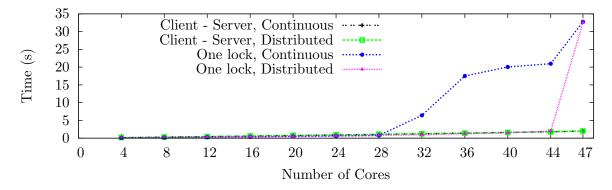

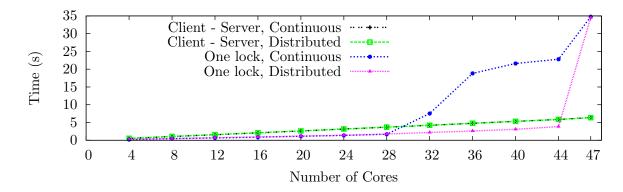

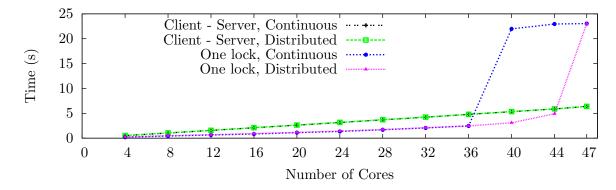

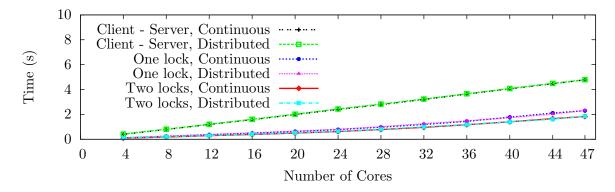

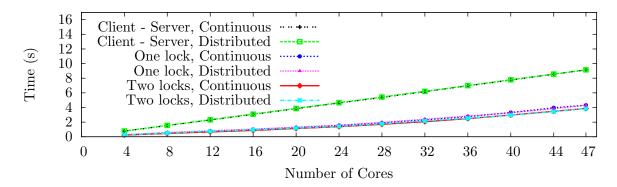

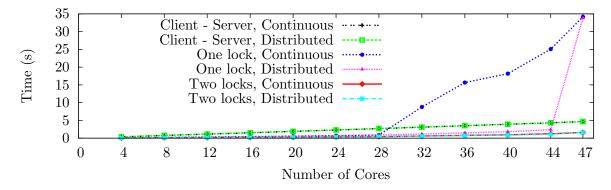

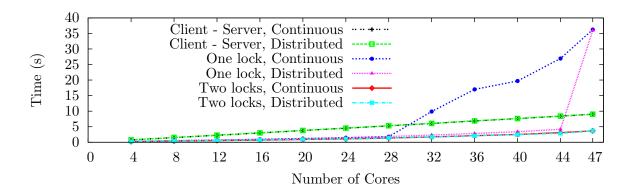

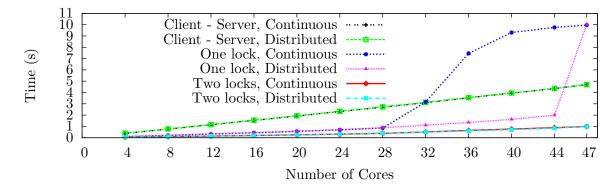

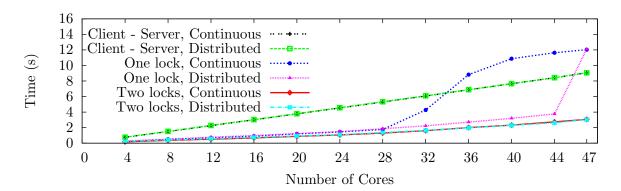

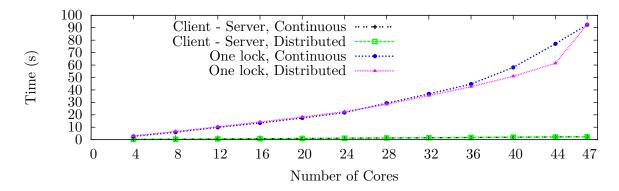

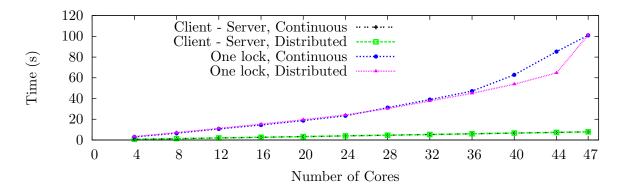

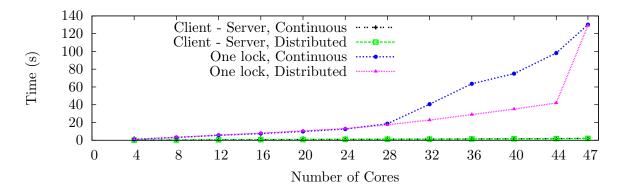

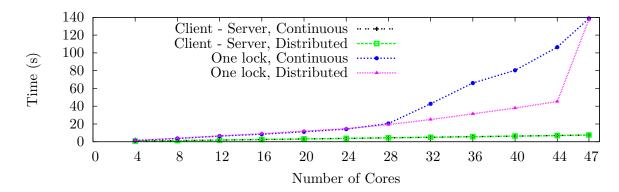

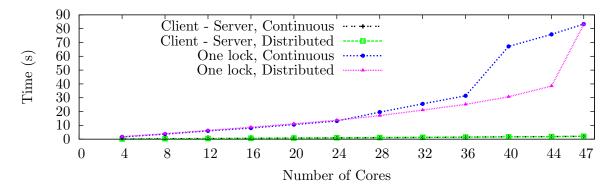

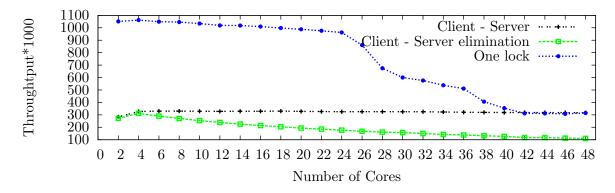

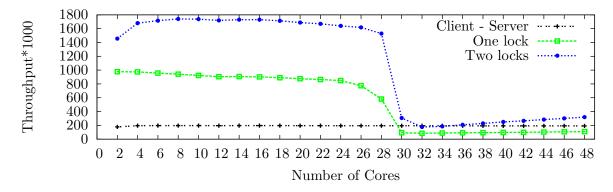

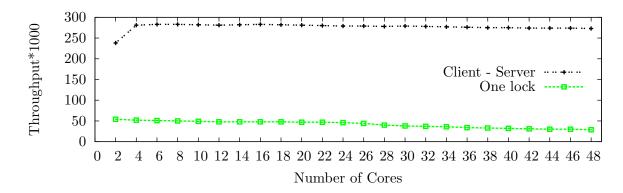

Όσον αφορά την χρονική επίδοση, για τις δομές της στοίβας και της ουράς, βλέπουμε ότι μετά από έναν αριθμό πυρήνων, το μοντέλο πελάτη-εξυπηρετητή έχει καλύτερη επίδοση από αυτό με το ένα κλείδωμα. Ωστόσο για λίγους πυρήνες έχουν ίδια ή μερικές φορές το μοντέλο ενός κλειδώματος έχει καλύτερη επίδοση. Η υλοποίηση με δύο κλειδώματα για την ουρά βλέπουμε ότι παρουσιάζει την καλύτερη επίδοση και είναι πάντα καλύτερη από το μοντέλο πελάτη-εξυπηρετητή. Από την άλλη η υλοποίηση της στοίβας με εξάλειψη παρατηρούμε ότι δεν πέτυχε καλύτερες επιδόσεις από τις άλλες δύο υλοποιήσεις. Για τον σωρό βέβαια βλέπουμε την σημαντικά καλύτερη επίδοση του μοντέλου πελάτη-εξυπηρετητή από αυτό με το κλείδωμα και αυτό κυρίως οφείλεται στην κακή αξιοποίηση της κρυφής μνήμης στο μοντέλο με το κλείδωμα, λόγω μοιραζόμενης μνήμης.

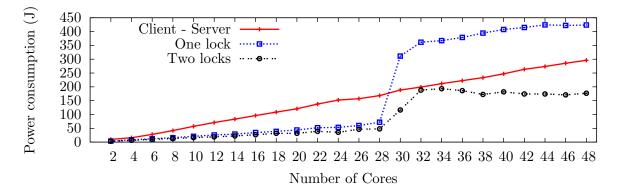

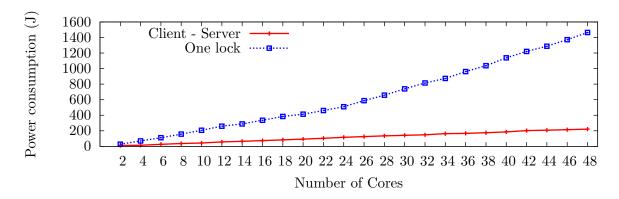

Όσον αφορά την κατανάλωση ενέργειας, βλέπουμε ότι εξαρτάται αρκετά από τον χρόνο που χρειάζεται κάθε πρόγραμμα, οπότε προκύπτουν ανάλογα αποτελέσματα με αυτά που είδαμε για τον χρόνο.

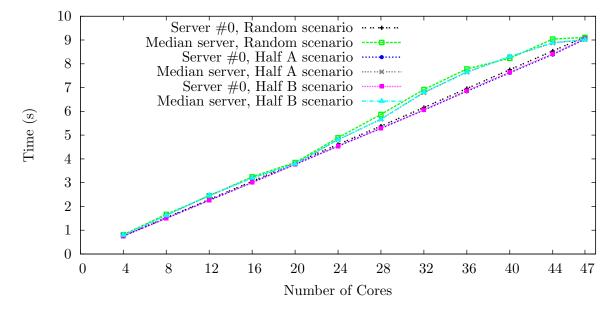

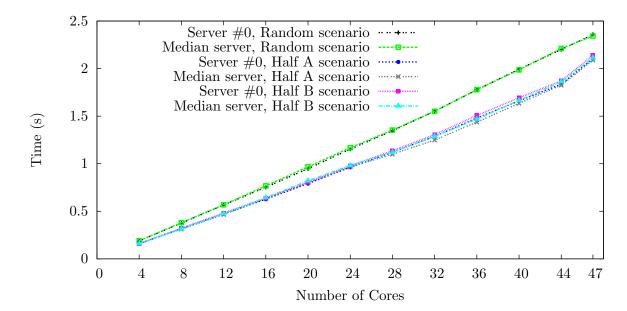

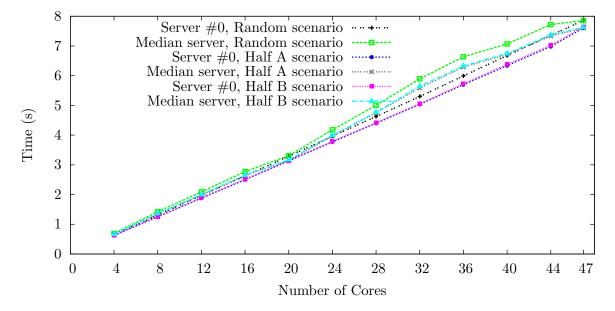

Η θέση των πυρήνων και η διασπορά τους βλέπουμε ότι επηρεάζει την χρονική επίδοση σε κάποια περιοχή των πυρήνων, μεταξύ 28 και 47 πυρήνων. Από την άλλη δεν βλέπουμε σημαντική διαφορά αλλάζοντας την θέση του πυρήνα εξυπηρετητή, πολλές φορές έχουμε ελάχιστα καλύτερη επίδοση με τον εξυπηρετητή στην θέση \*0.

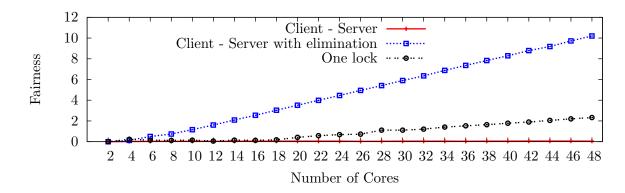

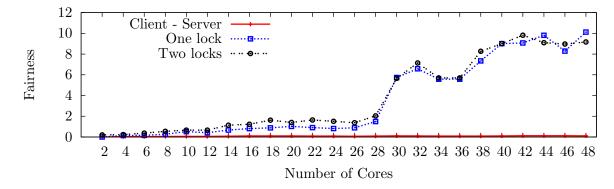

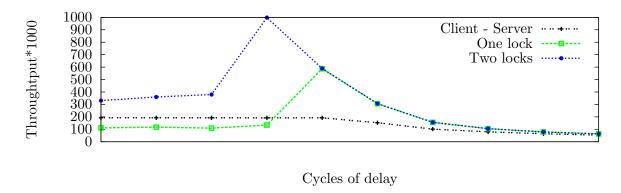

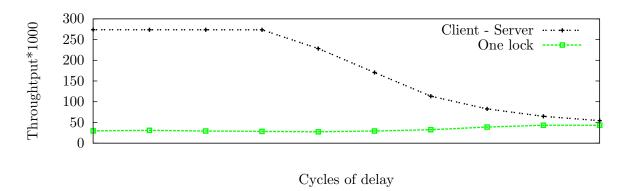

Τέλος το μοντέλο πελάτη-εξυπηρετητή είναι ένα σαφώς πιο δίκαιο μοντέλο από τα κλειδώματα τα οποία έχουν αρκετές διακυμάνσεις στο πόσο δίκαια δίνουν πρόσβαση στη δομή στους διάφορους πυρήνες. Ακόμη, με την εισαγωγή καθυστέρησης έχουμε ενδιαφέροντα αποτελέσματα που δείχνουν ότι θα μπορούσαμε να έχουμε βελτίωση στην απόδοση των προγραμμάτων αν εισάγαμε καθυστέρηση μεταξύ των αιτημάτων κάθε πυρήνα.

Ως προεχτάσεις αυτής της εργασίας η μελλοντιχή έρευνα θα μπορούσαμε να προτείνουμε την εξέταση και άλλων δομών δεδομένων. Ένα στοιχείο επίσης που δεν εξετάσαμε είναι αν οι πυρήνες όσο περίμεναν θα μπορούσαν να μπαίνουν σε μία χατάσταση αναμονής αντί να

διεκδικούν ενεργητικά τα κλειδώματα συνεχώς, μέχρι να τα λάβουνε.

Μια άλλη δυνατότητα που μας δίνει το σύστημα SCC αλλά δεν χρησιμοποιήσαμε είναι η ρύθμιση της συχνότητας και της τάσης κάθε πυρήνα. Ρυθμίζοντας τις παραμέτρους αυτές όταν οι πυρήνες είναι σε αναμονή θα μπορούσαμε να πετύχουμε εξοικονόμηση ενέργειας και πιθανώς να μεταβάλλονταν και άλλα χαρακτηριστικά της επίδοσης.

Κλείνοντας, ένα μοντέλο που θα μπορούσαμε να δοχιμάσουμε για να δούμε πώς αποδίδει θα ήταν ένα υβριδικό ανάμεσα στο μοντέλο με κλειδώματα και στο μοντέλο πελάτη-εξυπηρετητή. Δηλαδή θα μπορούσαν ανά ομάδες οι πυρήνες να έχουν ένα εξυπηρετητή, δηλαδή να υπάρχουν περισσότερη του ενός εξυπηρετητές οι οποίοι όμως θα εξυπηρετούσαν λιγότερους πυρήνες από ότι δοχιμάσαμε στην εργασία μας. Αυτοί οι εξυπηρετητές θα έχουν μιχρές δομές σε ιδιωτιχή τους μνήμη. Όταν αυτές οι δομές γεμίσουν τότε θα μπορούσε να υπάρχει η χύρια δομή σε μοιραζόμενη μνήμη και οι εξυπηρετητές να συγχρονίζονται μεταξύ τους μέσω χλειδωμάτων για να αντιγράφουν τις τοπιχές τους δομές στην χύρια δομή και μετά να ελευθερώνουν την ιδιωτιχή τους μνήμη και να συνεχίζουν να δέχονται αιτήματα από τους πελάτες τους.

# Contents

| 1 | Intr | roduction 3                              | 31 |

|---|------|------------------------------------------|----|

|   | 1.1  | Objective                                | 31 |

|   | 1.2  | Tools and programs                       | 32 |

|   | 1.3  | Thesis structure                         | 33 |

| 2 | Cor  | acurrent data structures                 | 35 |

|   | 2.1  | Introduction                             | 35 |

|   | 2.2  | Synchronization primitives               | 36 |

|   |      | 2.2.1 Locks                              | 36 |

|   |      | 2.2.2 Atomic operations                  | 39 |

|   |      | 2.2.3 Transactional memory               | 40 |

|   |      | 2.2.4 Monitors and conditional variables | 42 |

|   | 2.3  | More complex mechanisms                  | 43 |

|   |      | 2.3.1 Embedded Transactional Memory      | 43 |

|   |      | 2.3.2 C-Lock                             | 44 |

| 3 | Sing | gle-chip Cloud Computer 4                | 17 |

|   | 3.1  | SCC description                          | 47 |

|   |      | 3.1.1 Tile overview                      | 48 |

|   |      | 3.1.2 Memory overview                    | 49 |

|   |      | 3.1.3 Programming interfaces             | 51 |

|   | 3.2  | SCC implementations                      | 52 |

|   |      | 3.2.1 Stack                              | 53 |

|   |      | 3.2.2 FIFO queue                         | 58 |

|   |      | 3 2 3 Binary max heap                    | 60 |

26 CONTENTS

| 4  | Eva   | luation of concurrent data structures in SCC | 63 |

|----|-------|----------------------------------------------|----|

|    | 4.1   | Analysis of method and scenarios             | 63 |

|    | 4.2   | Properties measured                          | 66 |

| 5  | Exp   | perimental Results                           | 69 |

|    | 5.1   | Throughput measurements                      | 69 |

|    | 5.2   | Power measurements                           | 77 |

|    | 5.3   | Fairness measurements                        | 80 |

|    | 5.4   | Server position evaluation                   | 84 |

|    | 5.5   | Evaluation with delay inserted               | 85 |

| 6  | Con   | aclusion                                     | 91 |

|    | 6.1   | General Remarks                              | 91 |

|    | 6.2   | Future Work                                  | 94 |

| A  | Cod   | <b>le</b>                                    | 95 |

| Bi | bliog | craphy 1                                     | 13 |

# List of Figures

| 3.1  | SCC Top-Level Architecture (Source: [14])                                                                  | 48 |

|------|------------------------------------------------------------------------------------------------------------|----|

| 3.2  | SCC die and tile overview (Source: [7])                                                                    | 49 |

| 3.3  | Programmer's view of the SCC memory (Source: [13])                                                         | 51 |

| 3.4  | The SCC platform overview (Source: [6])                                                                    | 53 |

| 3.5  | Client-server model visualization                                                                          | 56 |

| 5.1  | Communication time measurements for the stack, comparing three scenarios                                   | 70 |

| 5.2  | Total time measurements for the stack, comparing three sce-                                                |    |

| 5.3  | narios                                                                                                     | 70 |

| 5.4  | paring three scenarios                                                                                     | 71 |

|      | scenarios                                                                                                  | 71 |

| 5.5  | Communication time measurements for the binary max heap, comparing three scenarios                         | 72 |

| 5.6  | Total time measurements for the binary max heap, comparing three scenarios                                 | 72 |

| 5.7  | Communication time measurements for the stack, random scenario, comparing continuous and distributed cores | 73 |

| 5.8  | Total time measurements for the stack, random scenario, comparing continuous and distributed cores         | 73 |

| 5.9  | Communication time measurements for the stack, half A sce-                                                 | 10 |

| U.J  | nario, comparing continuous and distributed cores                                                          | 73 |

| 5.10 | Total time measurements for the stack, half A scenario, comparing continuous and distributed cores         | 74 |

| 5.11 | nario, comparing continuous and distributed cores                                                                      | 74 |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 5.12 | Total time measurements for the stack, half B scenario, comparing continuous and distributed cores                     | 74 |

| 5.13 | Communication time measurements for the fifo queue, random scenario, comparing continuous and distributed cores        | 75 |

| 5.14 | Total time measurements for the fifo queue, random scenario, comparing continuous and distributed cores                | 75 |

| 5.15 | Communication time measurements for the fifo queue, half A scenario, comparing continuous and distributed cores        | 75 |

| 5.16 | Total time measurements for the fifo queue, half A scenario, comparing continuous and distributed cores                | 76 |

| 5.17 | Communication time measurements for the fifo queue, half B scenario, comparing continuous and distributed cores        | 76 |

| 5.18 | Total time measurements for the fifo queue, half B scenario, comparing continuous and distributed cores                | 76 |

| 5.19 | Communication time measurements for the binary max heap, random scenario, comparing continuous and distributed cores   | 77 |

| 5.20 | Total time measurements for the binary max heap, random scenario, comparing continuous and distributed cores           | 77 |

| 5.21 | Communication time measurements for the binary max heap, half A scenario, comparing continuous and distributed cores . | 78 |

| 5.22 | Total time measurements for the binary max heap, half A scenario, comparing continuous and distributed cores           | 78 |

| 5.23 | Communication time measurements for the binary max heap, half B scenario, comparing continuous and distributed cores . | 78 |

| 5.24 | Total time measurements for the binary max heap, half B scenario, comparing continuous and distributed cores           | 79 |

| 5.25 | Throughput measurements for the stack, random scenario with unequal insertions and removals                            | 79 |

| 5.26 | Throughput measurements for the fifo queue, random scenario with unequal insertions and removals                       | 79 |

| 5.27 | Throughput measurements for the binary max heap, random scenario with unequal insertions and removals                  | 80 |

29

### Chapter 1

# Introduction

#### 1.1 Objective

The objective of this thesis is to evaluate concurrent data structures on the Intel Single-chip Cloud Computer and compare different mechanisms of synchronization methods for those data structures. As multicore systems occupy more and more space in the computing machines domain and the software must adapt and utilize multicore systems and parallelism as effectively as possible, there is an open space to research and examine the power and the abilities that these systems can offer. Also there is need to evaluate the existing programming techniques for multicore architectures and if possible design new techniques or primitives that could make a breakthrough in the the multicore and parallel computing society.

The Single-chip Cloud Computer is an experimental platform by Intel to help and encourage the computer science society to research further many-core systems. As a 48 core system it poses a new challenge for researchers to evaluate and understand how easy and effective it is to program for a platform like this. Also how one can effectively utilize this computer. The demand for concurrent data structures and the further understanding of their efficiency in manycore systems like the SCC was a major objective for us to experiment with the SCC and try to offer and add some more knowledge on the usage and the aspects of this computer system.

Based on the already existing research and material on the Single-chip Cloud Computer ([10], [11] and [15]), our goal was to further investigate the concurrent data structures on this machine and add some knowledge on

the SCC and multicore community. The interesting part about the Singlechip Cloud Computer is the special memory architecture that exists and this gave us an incentive to research how using different kinds of this memory can affect performance, power consumption and other aspects of the concurrent data structures. In our experiments we tried to make clear if a trade-off between faster memory but not so popular synchronization methods and slower memory with easier and at times more effective methods is worth.

To add to the mentioned above, another objective was to have some data about the performance and the consumption of concurrent data structures on a manycore general purpose computer, like the Single-chip Cloud Computer, that someone can use to compare with multicore or manycore embedded systems.

#### 1.2 Tools and programs

In this section we are going to mention the tools and programming suites that helped during the work for this thesis, the development of programs and the editing of this text. We tried to base our work on free software when that was possible but of course to complete this thesis proprietary software was also used.

To begin with, the editors used for the development of the data structures libraries, the programs simulating and running the concurrent data structures on the Single-chip Cloud Computer and the scripts that helped automate the running of the programmes, the gathering of the results and the manipulation and usage of these results were *Vim* and *gedit*. *Vim* is a cross-platform editor which is free and open source software. It was originally written by Bram Moolenaar and released publicly in 1991. It supports both a command-line interface and a graphical user interface application. On the other hand, *gedit* was released in 1999 and was the work of 7 developers. It is also a cross-platform editor, based on a simple graphical user interface and released as free and open-source software.

For the designing of all the graphs present in this thesis, the *gnuplot* application was used. *Gnuplot* was released in 1986 and is a cross-platform command-line program that is used to plot functions and draw diagrams. It is a piece of free software and nowadays there are third-party programs available that use *gnuplot* as an engine but offer a graphical user interface.

Another piece of software that proved really useful for the work needed to be done during this thesis was *GNU Octave*. It is designed by John Eaton and others and released in 1988 but not in the nowadays form. *GNU Octave* is a free software high-level programming language originally developed to support and ease numerical computations. It provides a command-line interface but also a graphical user interface and it shows compatibility with MATLAB, an non-free equivalent software, maybe the most popular for this kind of use. *GNU Octave* can be used to solve equations, plot figures and also programming algorithms.

Finally, for the developing of the text of this thesis and the typesetting, IATEXwas used. IATEXwas released initially in 1985 from Leslie Lamport and it is based on Donald Knuth's TeX. It is a word processor and a document mark-up language that differs from famous word processors as the result is not displayed immediately but the user writes in plain text and the input has to be compiled to see the output. IATEX a free software and is considered a good option for high quality typing products.

#### 1.3 Thesis structure

At this point we are going to present the structure of the thesis and talk about the chapters that are going to follow. This thesis consists of 6 chapters and we are going to describe the content of each one, except of the first.

To begin with, the next chapter, chapter number 2, has the title "Concurrent data structures". In that chapter we are going to present synchronization primitives, both basic ones and some more advanced. We are going to have an idea of the widely used primitives for synchronization on concurrent data structures but also present new ideas that exist in research in the last years.

Next in chapter number 3, with the title "Single-chip Cloud Computer", we are going to present the main computer that we worked on and tested our concurrent data structures, Intel's SCC. We are going to talk about hardware aspects of this system, as well as programming interface. In addition we are also going to present with details our implementations for the data structures.

In chapter number 4 we are going to explain the method that we followed when conducting our measures and the properties we evaluated and measured. The title of this chapter is "Evaluation of concurrent data structures in SCC".

The 5th chapter, "Experimental Results", is where all our measurements and outcomes are presented. We provide the graphs from all the different scenarios we examined and simulated. In this chapter someone can find all the material that is the result of our experiments.

Finally, in chapter number 6, "Conclusion", we summarize the remarks we made throughout this work and these experiments. We give some conclusions that resulted from the simulations and the evaluation of the concurrent data structures on the Single-chip Cloud Computer. Also we propose some future work and other aspects that can be researched.

# Chapter 2

### Concurrent data structures

#### 2.1 Introduction

With multi-core systems being present more and more in the domain of computer systems and parallelism being the solution to overcome practical computer science problems and the path that will lead beyond present efficiency thresholds, concurrent data structures is one of the key factors that need to be examined and researched to establish good performance and reliability of parallel systems.

As concurrent data structures, we define the data structures that give us the ability to store and handle data by multiple threads or processing cores. In many occasions a concurrent data structure is nothing more than a usual data structure, e.g. a stack, a queue, a heap, enriched with protocols of usage or mechanisms to ensure that important properties of the structure and its function are secured and guaranteed. Nevertheless there is a lot of research interest and work done towards more complex and advanced structures, to optimize transactions with the data structures with many threads or cores taking part. Those advanced structures are not useful for single core – one thread systems.

A concurrent data structure faces many risks and dangers if certain steps and measures are not taken. One must ensure that memory transactions are made with the same order that the requests are placed, memory state and the data saved need to be in a consistent state and the values of the variables and generally the memory locations need to be the expected ones. Problems for example could occur if access is given to more than one thread, to the same

memory address simultaneously, the compiler rearranges instructions so the executed code is not what we were expecting or the compiler or memory drivers rearrange the sequence of two or more memory accesses of different cores, so the data read or written are not the expected one. These situations could lead in problems such as unexpected behaviour, if data other than the expected is read or written, program, thread or core crush, or even security holes. These situations are more than common and as an example we have the first versions of Intel processors Haswell and Broadwell that had a buggy implementation of their transactional memory implementation, TSX, that could lead to unpredictable system behaviour. We are going to present the transactional memory technique in the following paragraphs.

Having said that, one of the key principals that secure the correct and accurate function of concurrent data structures is synchronization. Synchronization guarantees that memory accesses will be secure, they will happen in the same order that it was requested, if that is needed, and the cores or threads will interact with the data structure in a way that ensures consistency and expected results. There are many ways and ideas to implement synchronization, from naive ones to much more complex. Before implementing or choosing to use a synchronization method, one should weight the implementation difficulty, the efficiency that the method provides, the software and the hardware available and the functions that both support.

Following, we are going to analyse synchronization primitives, starting from simple concepts and moving on to more complex ones.

#### 2.2 Synchronization primitives

#### 2.2.1 Locks

Locks are maybe the simplest way to achieve synchronization and many times, the first that comes to mind as a concept. The principle is that a thread or a core has to acquire the lock to access the memory. Only the holder of the lock can access the memory at that moment and no one else. The lock is an abstract entity, it could be a variable declared by the programmer, a structure provided by the language implementation or provided by a library.

A lock refers to a memory location, thus a naive approach is to lock with one lock the whole data structure. Later we will see that this is called a coarse-grain lock. This approach is simple to implement but as we can imagine limits concurrency, as at any given time, only one thread can interact with the memory. Of course there is a lot of research around locks so there are many more lock patterns and even, as we will see later, lock-less concurrent data structures. The thread or core that has acquired the lock can do any transaction with the memory, whereas, any other thread or core that wanted to access memory should wait, either postpone its job if possible, or continue asking for the lock until it is released and available.

Before someone uses locks there are some aspects that we need to have clear. An important issue with locks is efficiency. Efficiency depends on many factors, such as the implementation of the lock, the hardware available on a system, the number of locks that we use for our data structure and the synchronization tactic of the lock. Depending on the problem we want to solve or what we implement with our program a use of a lock could give acceptable efficiency or could be totally inefficient. We also need to keep in mind, that many lock implementations that are based on reading and writing to a memory location, to update or check the condition of the lock, e.g. if it is available, are bus based implementation. Which has serious impact on bus usage and contention, thus consuming more power and creating delay. Also we need to consider what tactic we follow when a thread or core finds a lock unavailable. There are techniques such as polling or sleeping and again weight decisions such as implementation simplicity and energy consumption or delay.

The naive implementation of locks lead to a blocking synchronization method. This is also a parameter we need to consider when we decide about the synchronization method we are going to use. Although research has provided non-blocking techniques. Locks are also a mechanism that enters competition among the threads or cores. So depending on many factors, such as the place of the lock and the kind of the memory, e.g. if it is NUMA memory, some threads can have easier or faster access to the locks thus creating inequalities in the lock possession, a situation that is measured by fairness of the lock.

If this competition is not well thought and during the implementation we do not design well our lock protocol, problems such as deadlocks or starvation can arise. Deadlock is a situation that more than one thread claim the lock, the lock is available but due to erroneous design, there is no progress as no one can acquire the lock. On the other hand, starvation is happening when a lock is not fair and we encounter the situation where some threads or cores progress excessively whereas other threads or core have little or no job done.

Following we are going to mention some synchronization techniques for locks.

#### Coarse-grain synchronization

Coarse-grain synchronization for concurrent data structures means that there will be one lock for the whole data structure. To interact with the structure one must acquire access and during his transactions with the memory, no one else (core or thread) is allowed to have access to the memory. It is a simple concept that has the advantage of a really simple implementation for most data structures but many times, limits parallelism. Simply because only one core or thread at a time can have access to the data structure, so others that may want to access memory must stall or generally wait, thus losing potential computing time.

#### Fine-grain synchronization

On the other hand, a fine-grain synchronization tactic means that there will be more than one locks for our structure. Depending on the memory area that a core or thread wants to access, it tries to acquire the appropriate lock. With fine-grain synchronization we achieve better parallelism, as more than one threads or cores can interact with the data structure simultaneously, if they want to access different parts of the structure. The drawbacks of this approach are that it is generally more difficult to implement and we need caution to avoid problems such as deadlocks while threads are competing for the locks.

#### **Optimistic Synchronization**

With this technique, we make a basic assumption that the majority of the times, nothing bad or unwanted will happen. As a consequence, when we want to insert or delete an element in our data structure, we first search if it exists, without acquiring a lock. After the search if we need to proceed with

the insertion or the removal, we acquire a lock, we look again if the element is present or not, and do the function we want. This technique also has a bigger implementation difficulty and depending on the situation we use it, it does not guarantee more efficiency.

#### Lazy synchronization

The lazy synchronization tactic is a tactic divided into two parts, a light one and a heavy one. The light one is done with synchronization and immediately, for example removing logically a node by updating a tag value. Later follows the heavy part during which there is no need for synchronization and for example the logically removed node is removed permanently by freeing the memory it occupied. Again, when using this tactic we need to consider the implementation cost and the the efficiency depending on the exact data structure that we will use.

#### 2.2.2 Atomic operations

Moving beyond locks, we have to discuss the primitive of atomic operations or atomic transactions. Atomicity guarantees isolation from other processes that run concurrently and the atomic primitive makes transactions appear as they were made instantaneously, with small pauses between each other and there was no overlapping. Atomic operations have an other characteristic, they either succeed in changing the machine's state or make no change in the state or the memory if they fail.

Atomic operations show a lot of interest because they can offer waitingfree and block-free implementations of concurrent data structures. That is because when using atomic primitives, either hardware or software implemented, we can omit mutual exclusion primitives such as locks. A property that may not come to mind but is present when using atomic operations, is retrying. With that, we want to say that if an atomic operation fails, which is not uncommon, we have to retry, maybe more than once until this operation succeeds.

Atomic operations are based on two implementations, hardware ones, with cache coherency protocols provided by the hardware designers or with special *test&set* registers. But also atomicity can be achieved with software implementations such as checking the state of variables or checking time

stamps of operations by cores or threads. The main principle of atomicity in many-core - multi-thread systems is that every operation is made independently without thinking about the other cores or threads, but before the results are accepted-saved, the thread or core checks a value. If that value has changed, which means somebody else has already changed the data before this core - thread, then it cannot save the changes, the operation fails and it has to retry or move on, depending on our program's functionality and design. If during the check the value does not appear changed then all is good and the operation is successful.

The main mechanisms of atomicity are *cache coherency* protocols, *test&set* registers and *compare&swap* registers.

Atomic operations, as we mentioned before, can help construct blockless and wait-free concurrent data structures but one should be careful and examine well their usage as atomic primitives do not always guarantee a more efficient program or data structure.

#### 2.2.3 Transactional memory

Moving beyond locks and atomic operations, we need to examine transactional memory. The primitives mentioned above have certain limits and when using them we face certain problems.

To be more precise, coarse-grain locks, although they are easy to implement and use, have poor efficiency as they take little advantage of parallelism and concurrency. On the other hand, fine-grain locks have much better efficiency but are difficult to implement, need a lot of attention when using them to avoid dead locks and are hard to manage if the number of the locks is big. In addition to these, locks can reveal a convoying effect. In a preemptive processor or operating system, a thread that has acquired the lock but takes a lot of time, may be forced to leave the execution unit, while holding the lock, thus leading to great time loses as other threads that want the lock have to keep waiting although no one is working in a critical part. Also locks have the problem of uncertain behaviour and very possible crash, if a core holding the lock crashes.

Atomic primitives, the other choice for synchronization, face the problem that work on only a single word which leads to complex algorithms, hard to implement and with high overhead sometimes.

With these limitations, concurrent programs being more and more used and the solution of hiring high skilled programmers every time someone needed to overcome a concurrency developing obstacle being expensive and not practical, research has offered a solution. That is transactional memory, inspired by database transactions mechanisms. The motivation for transactional memory is giving the ease to the programmer, without interfering with locks or atomic operations and facing the danger of erroneous implementations, with a declarative style, to let him define the transactional parts. So transactional memory is a higher level implementation of synchronization, where the weight of synchronization is moved from the developer of the application to the hardware designer or the developer of the run time system or language system.

Within this transactional parts, the transactional memory system must guarantee atomicity, consistency and isolation. Atomicity means that either all the commands in the transactional part will be successful and committed or none. Consistency means that all data changes should be made by allowed ways and isolation means that no other than the transactional part can see the changes made until they are committed.

There are two approaches for transactional memory, the hardware implemented and the software one. Although there are also some hybrid approaches that combine elements of the previous two implementation methods. The hardware implementations are based on cache coherency protocols. In many-core systems it is common that every core has his own cache but data is shared among cores. To achieve transactional memory a bit can be added to every cache line. So if a line is marked as transactional it cannot be evicted or shared until the transactional operation is finished. This limits transactional operations to the size of a cache. Although this is a limitation, it is a progress when we compare with atomic operations that are generally limited to a word. The software approach is based on data versioning and spotting conflicts and solving them. Usually a data conflict will lead to a transaction abort and retry for some core or cores. When comparing software implementations with the hardware ones, it is common that software implementations come with a performance penalty.

Although transactional memory is a very promising and convenient synchronization primitive, we need to keep in mind that there must be more research in that direction and overcome certain problems. The example of the

problematic IBM Blue Gene/Q processor that TSX transactional mechanism led to unexpected behaviour should remind us that transactional memory must be well designed before used excessively.

#### 2.2.4 Monitors and conditional variables

Finally, to conclude our reference to some of the simple synchronization primitives we will present monitors. Of course the list of synchronization primitives and mechanisms is not exhausted by our references and readers that want to have a complete view of the subject are urged to study the relevant bibliography.

For concurrent data structures, a monitor is a synchronization construct that combines data, methods and synchronization in a single modular package like classes combine data and methods. Monitors offer mutual exclusion together with the ability to block until a certain condition is met. The existence of monitors is based on the support from hardware, for example the existence of hardware that offers atomic operations or disabling interrupts during critical paths.

Monitors are a construction that was aimed to address several problems that locks had. With the monitor construction, threads and cores are guaranteed safe execution of critical parts and the problem of deadlocks or the problem with threads holding the lock when they are not progressing is surpassed. The problem that is addressed, is that a thread could acquire the lock but a certain needed condition is not met, for example a thread wants to read from an empty queue. This thread is going to keep the lock forever, if the synchronization design says that it should block, thus depriving other threads, of the lock, that may want to write to the queue. As a result this program will not progress, although there are threads that want to write to the empty queue.

This problem is solved with monitors as they come with conditional variables. This means that we could implement synchronization without spinning, so when a condition is met, the threads that are interested in getting the lock are signalled and start to compete for the lock. With this protocol no thread holds the lock without progressing. This signalling can be implemented with semaphores and the threads that have pending conditions could sleep or generally not being busy waiting.

Nevertheless there are also potential problems when using monitors, such as the lost wakeup problem. In this situation a thread may miss the signal that a condition has changed which may lead to this thread never waking up. Fortunately there are ways to overcome this problem that may arise, either by setting a waiting time-out or always signalling all threads on a condition, not just one. Other potential drawback of monitors and semaphores is the fairness again, among the threads that compete when there is only one lock available. So we need to evaluate again the implementation of the monitors on the system and the language we are using and estimate the performance we can get and if it is acceptable.

### 2.3 More complex mechanisms

Moving on, we are going to see some more complex synchronization mechanisms that are recent to the computer science society and present some research and practical interest.

#### 2.3.1 Embedded Transactional Memory

Having presented the transactional memory primitive, we want to mention here the embedded transactional memory, a hardware implementation of transactional memory that was firstly designed for embedded systems but now with works like Sutirtha Sanyal et al [12] we try to introduce it to large scale multi-processor systems.

Embedded transactional memory is oriented to consume less energy and, by the resent research, even to provide a speed-up. The idea is to spare energy from speculative executions that would be aborted. As we have seen from the classic transactional memory, there are transactions that due to conflicts are going to be aborted and retried. Thus researchers try with a protocol and hardware support, to minimize the loss of energy by improving speculation and stopping paths that are going to be aborted, as soon as possible.

The idea is to introduce gated clocks to the processing cores. When the system finds out that a conflict has arisen and thus a roll back in a check point is needed by one or more cores, then those cores should be cut off by the gated clock. This will lead to eliminate dynamic power consumption.

With the gated clocks we will save power from operations that would be dumped due to conflicts but also we could get a speed-up, as by cutting off cores until they begin again from the last check point, we can minimize competition for the commit. Minimizing competition means minimizing contention on the bus and fewer memory accesses. This leads to a better contention management thus an overall speed-up

Although this mechanism is new and not used extensively in practise, it is a promising technique not only for embedded systems but also for large-scale systems that could lead to more efficient execution.

#### 2.3.2 C-Lock

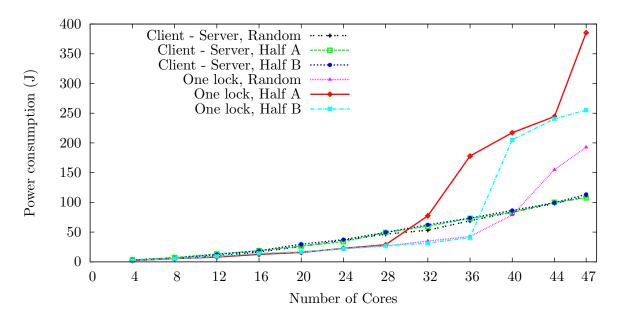

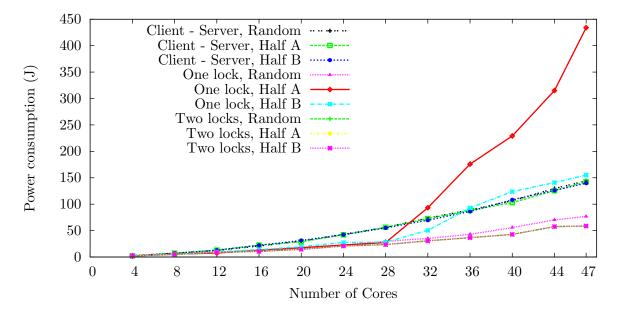

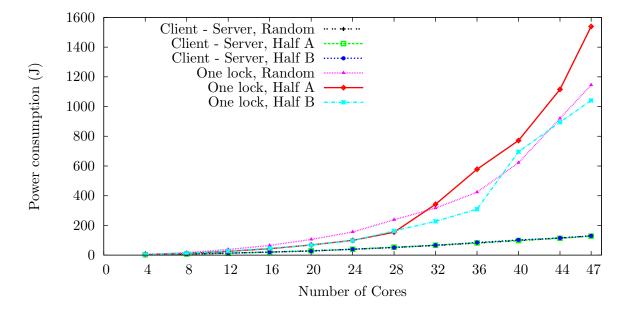

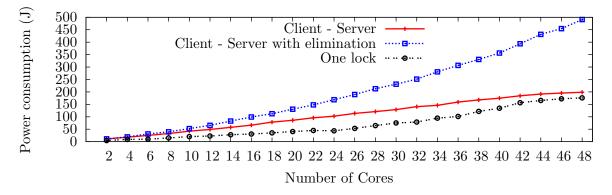

The C-Lock mechanism is a hardware based synchronization mechanism, designed for embedded multicore systems by Seung Hun Kim et al [5]. Embedded systems have specific constrains and demand different attention than large scale computing systems. This constrains are many times conflicting, for example we demand very good energy efficiency by embedded systems but sometimes throughput and responsiveness are also as important as energy consumption, thus having conflicting demands.