## **RICE UNIVERSITY**

# Exploiting Address Space Contiguity to Accelerate TLB Miss Handling

by

**Thomas W. Barr**

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

## **Master of Science**

APPROVED, THESIS COMMITTEE:

alan L Cox

Alan L. Cox, Chair Associate Professor of Computer Science and Electrical and Computer Engineering

ent

Scott Rixner Associate Professor of Computer Science and Electrical and Computer Engineering

Peter Varman Professor of Electrical and Computer Engineering and Computer Science

Houston, Texas

April, 2010

UMI Number: 1486028

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 1486028 Copyright 2010 by ProQuest LLC. All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

### ABSTRACT

### Exploiting Address Space Contiguity to Accelerate TLB Miss Handling

by

### Thomas W. Barr

The traditional CPU-bound applications of the past have been replaced by multiple concurrent data-driven applications that use lots of memory. These applications, including databases and virtualization, put high stress on the virtual memory system which can have up to a 50% performance overhead for some applications. Virtualization compounds this problem, where the overhead can be upwards of 90%. While much research has been done on reducing the number of TLB misses, they can not be eliminated entirely. This thesis examines three techniques for reducing the cost of TLB miss handling. We test each against real-world workloads and find that the techniques that exploit course-grained locality in virtual address use and contiguity found in page tables show the best performance.

The first technique reduces the overhead of multi-level page tables, such as those used in x86-64, with a dedicated *MMU cache*. We show that the most effective MMU caches are *translation caches*, which store partial translations and allow the page walk hardware to skip one or more levels of the page table. In recent years, both AMD and Intel processors have implemented MMU caches. However, their implementations are quite different and represent distinct points in the design space. This thesis introduces three new MMU cache structures that round out the design space and directly compares the effectiveness of all five organizations. This comparison shows that two of the newly introduced structures, both of which are translation cache variants, are better than existing structures in many situations. Secondly, this thesis examines the relative effectiveness of different page table organizations. Generally speaking, earlier studies concluded that organizations based on hashing, such as the inverted page table, outperformed organizations based upon radix trees for supporting large virtual address spaces. However, these studies did not take into account the possibility of caching page table entries from the higher levels of the radix tree. This work shows that any of the five MMU cache structures will reduce radix tree page table DRAM accesses far below an inverted page table.

Finally, we present a novel device, the SpecTLB, that is able to exploit alignment in the mapping from virtual address to physical address to interpolate translations without any memory accesses at all. Operating system support for automatic page size selection leaves many small pages aligned within large page "reservations". While large pages improve TLB coverage, they limit the control the operating system has over memory allocation and protection. Our device allows the latency penalty of small pages to be avoided while maintaining fine-grained allocation and protection.

#### Acknowledgments

There is a long list of people that deserve great thanks for enabling the work in this thesis to even be possible. It would be impossible to list them all here, but I would be remiss if I didn't try. First, I thank my committee members for their constant and detailed feedback and their unwavering motivation. The diversity of viewpoints granted to me from working with Dr. Alan L. Cox, Dr. Scott Rixner and Dr. Peter Varman have been entirely invaluable. The ability to compile a single work from so many areas of computing is a rare honor, one that would never have been possible without their help.

Secondly, I must thank all the people who indirectly helped me complete this work. While a project such is this is never easy, they have made the past year of my life a delight. The constant, unquestioning support of my closest family and friends allowed me to bounce back from the many failures along the way. I dedicate my successes to you.

# Contents

|   | Abst | tract                              | ii |

|---|------|------------------------------------|----|

|   | List | of Illustrations vi                | ii |

|   | List | of Tables                          | x  |

| 1 | Int  | roduction                          | 1  |

|   | 1.1  | Introduction                       | 1  |

|   | 1.2  | Contributions                      | 4  |

|   | 1.3  | Organization                       | 6  |

| 2 | x86  | Address Translation                | 7  |

|   | 2.1  | Page Walk Details                  | 7  |

| 3 | Rel  | ated Work 1                        | 2  |

|   | 3.1  | Caching                            | 2  |

|   | 3.2  | Alternate page table formats       | 3  |

|   | 3.3  | Reducing TLB miss frequency        | 4  |

| 4 | MN   | AU Caching 1                       | 6  |

|   | 4.1  | Introduction                       | 6  |

|   | 4.2  | Caching page walks                 | 8  |

|   |      | 4.2.1 Page table caches            | 9  |

|   |      | 4.2.2 Translation caches           | 1  |

|   |      | 4.2.3 Translation-Path Cache (TPC) | 4  |

|   |      | 4.2.4 Design space summary         | 5  |

|   | 4.3  | Design comparison                  | 5  |

|   |      | 4.3.1 Indexing                     | 6  |

|   |                                         | 4.3.2                                                                                | Partitioning                                                                                                                                                                                                                                       | 27                                                                     |

|---|-----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|   |                                         | 4.3.3                                                                                | Coverage                                                                                                                                                                                                                                           | 29                                                                     |

|   | 4.4                                     | Impler                                                                               | nentation                                                                                                                                                                                                                                          | 30                                                                     |

|   |                                         | 4.4.1                                                                                | CAM Bypass                                                                                                                                                                                                                                         | 31                                                                     |

|   |                                         | 4.4.2                                                                                | VI-LRU shift register implementation                                                                                                                                                                                                               | 34                                                                     |

|   | 4.5                                     | Metho                                                                                | dology                                                                                                                                                                                                                                             | 36                                                                     |

|   |                                         | 4.5.1                                                                                | Application Memory Traces                                                                                                                                                                                                                          | 36                                                                     |

|   |                                         | 4.5.2                                                                                | Memory System Simulation                                                                                                                                                                                                                           | 37                                                                     |

|   |                                         | 4.5.3                                                                                | Synthetic Application Memory Traces                                                                                                                                                                                                                | 38                                                                     |

|   | 4.6                                     | Cache                                                                                | design simulations                                                                                                                                                                                                                                 | 38                                                                     |

|   |                                         | 4.6.1                                                                                | TLB miss penalty                                                                                                                                                                                                                                   | 39                                                                     |

|   |                                         | 4.6.2                                                                                | Sizing considerations                                                                                                                                                                                                                              | 43                                                                     |

|   |                                         | 4.6.3                                                                                | Replacement policy                                                                                                                                                                                                                                 | 46                                                                     |

|   | 4.7                                     | Virtual                                                                              | ization                                                                                                                                                                                                                                            | 47                                                                     |

|   |                                         |                                                                                      |                                                                                                                                                                                                                                                    |                                                                        |

|   | 4.8                                     | Conclu                                                                               | isions                                                                                                                                                                                                                                             | 49                                                                     |

| 5 |                                         |                                                                                      |                                                                                                                                                                                                                                                    | 49<br>53                                                               |

| 5 |                                         | ernate                                                                               |                                                                                                                                                                                                                                                    | 53                                                                     |

| 5 | Alte                                    | e <b>rnate</b><br>Hasheo                                                             | page table formats                                                                                                                                                                                                                                 | <b>53</b><br>53                                                        |

| 5 | <b>Alte</b><br>5.1                      | e <b>rnate</b><br>Hashed<br>Transla                                                  | page table formats                                                                                                                                                                                                                                 | <b>53</b><br>53<br>57                                                  |

|   | <b>Alte</b><br>5.1<br>5.2<br>5.3        | e <b>rnate</b><br>Hashed<br>Transla<br>Conclu                                        | page table formats       5         d page tables       5         ation Storage Buffers       5         usion       5                                                                                                                               | <b>53</b><br>53<br>57                                                  |

|   | <b>Alte</b><br>5.1<br>5.2<br>5.3        | Hashee<br>Hashee<br>Transla<br>Conclu<br><b>cTLB</b>                                 | page table formats 5   d page tables 5   ation Storage Buffers 5   usion 5   Parallelizing TLB Miss Handling 5                                                                                                                                     | <b>53</b><br>53<br>57<br>58                                            |

|   | Alte<br>5.1<br>5.2<br>5.3<br>Spe        | Hashee<br>Hashee<br>Transla<br>Conclu<br><b>cTLB</b>                                 | page table formats   d page tables   ation Storage Buffers   usion   • Parallelizing TLB Miss Handling   round                                                                                                                                     | <b>53</b><br>53<br>57<br>58<br><b>59</b>                               |

|   | Alte<br>5.1<br>5.2<br>5.3<br>Spe        | ernate<br>Hashed<br>Transla<br>Conclu<br>cTLB<br>Backgu<br>6.1.1                     | page table formats   d page tables   ation Storage Buffers   usion   • Parallelizing TLB Miss Handling   round                                                                                                                                     | <b>53</b><br>53<br>57<br>58<br><b>59</b><br>61<br>61                   |

|   | Alte<br>5.1<br>5.2<br>5.3<br>Spe<br>6.1 | ernate<br>Hashed<br>Transla<br>Conclu<br>cTLB<br>Backgu<br>6.1.1                     | page table formats   d page tables   ation Storage Buffers   usion <b>: Parallelizing TLB Miss Handling</b> round   FreeBSD Reservation System                                                                                                     | <b>53</b><br>53<br>57<br>58<br><b>59</b><br>61<br>61<br>61             |

|   | Alte<br>5.1<br>5.2<br>5.3<br>Spe<br>6.1 | ernate<br>Hashed<br>Transla<br>Conclu<br>cTLB<br>Backga<br>6.1.1<br>Page ta          | page table formats   d page tables   ation Storage Buffers   usion <b>: Parallelizing TLB Miss Handling</b> round   FreeBSD Reservation System   able speculation                                                                                  | <b>53</b><br>53<br>57<br>58<br><b>59</b><br>61<br>61<br>61<br>62<br>63 |

|   | Alte<br>5.1<br>5.2<br>5.3<br>Spe<br>6.1 | ernate<br>Hashed<br>Transla<br>Conclu<br>cTLB<br>Backga<br>6.1.1<br>Page ta<br>6.2.1 | page table formats 5   d page tables 5   ation Storage Buffers 5   usion 6   e Parallelizing TLB Miss Handling 6   round 7   FreeBSD Reservation System 6   able speculation 6   Explicit page table marking 6   Heuristic reservation detection 6 | <b>53</b><br>53<br>57<br>58<br><b>59</b><br>61<br>61<br>61<br>62<br>63 |

vi

|   |     | 6.3.1   | Platform simulator                           |  |

|---|-----|---------|----------------------------------------------|--|

|   |     | 6.3.2   | Benchmarks                                   |  |

|   |     | 6.3.3   | SpecTLB Simulation                           |  |

|   | 6.4 | Simula  | tion results                                 |  |

|   |     | 6.4.1   | TLB miss parallelization                     |  |

|   |     | 6.4.2   | Overlap opportunity                          |  |

|   |     | 6.4.3   | Power overhead                               |  |

|   |     | 6.4.4   | Sizing considerations                        |  |

|   |     | 6.4.5   | Replacement policy                           |  |

|   | 6.5 | Discus  | sion                                         |  |

|   |     | 6.5.1   | More aggressive reservation creation         |  |

|   |     | 6.5.2   | Very large page support for virtual machines |  |

|   |     | 6.5.3   | Explicit marking                             |  |

|   | 6.6 | Conclu  | usions                                       |  |

|   |     |         |                                              |  |

| 7 | Cor | nclusio | ns 81                                        |  |

|   | 7.1 | Future  | work                                         |  |

| A | MN  | IU Co   | verage Proofs 86                             |  |

|   | A.1 |         | rison of TPC and Unified Coverage            |  |

|   |     | •       | -                                            |  |

|   | A.2 | Compa   | arison of TPC and SPTC Coverage              |  |

|   |     |         |                                              |  |

# Bibliography

# Illustrations

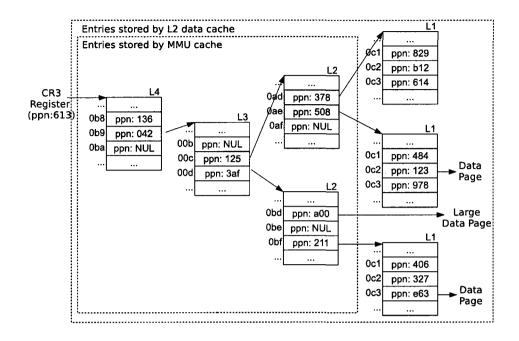

| 2.1  | Decomposition of the x86-64 virtual address.                                | 8  |

|------|-----------------------------------------------------------------------------|----|

| 2.2  | An example page walk for virtual address (0b9, 00c, 0ae, 0c2,               |    |

|      | 016). Each page table entry stores the physical page number for either the  |    |

|      | next lower level page table page (for L4, L3, and L2) or the data page (for |    |

|      | L1). Only 12 bits of the 40-bit physical page number are shown in these     |    |

|      | figures for simplicity.                                                     | 9  |

|      |                                                                             |    |

| 4.1  | An example of the contents of a UPTC.                                       | 19 |

| 4.2  | An example of the contents of a SPTC                                        | 20 |

| 4.3  | An example of the contents of a STC                                         | 22 |

| 4.4  | An example of the contents of a UTC.                                        | 22 |

| 4.5  | An example of the contents of the TPC                                       | 24 |

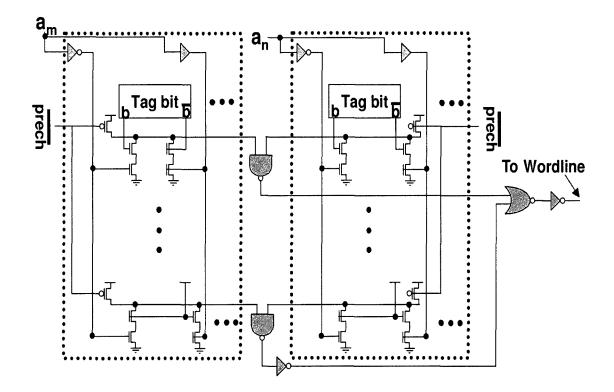

| 4.6  | Fully associative cache design.                                             | 32 |

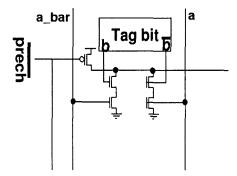

| 4.7  | Dynamic bit logic circuit.                                                  | 33 |

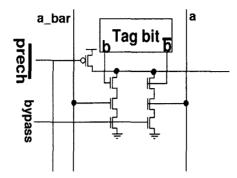

| 4.8  | Dynamic bit logic circuit with bypass.                                      | 34 |

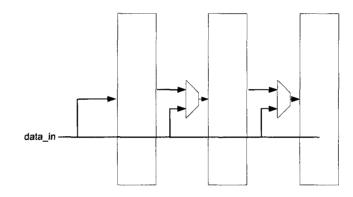

| 4.9  | A shift register.                                                           | 35 |

| 4.10 | A VI-LRU shift register.                                                    | 35 |

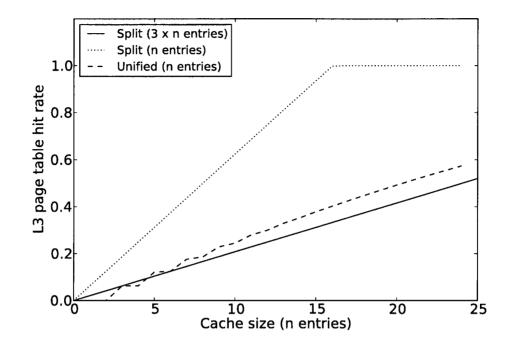

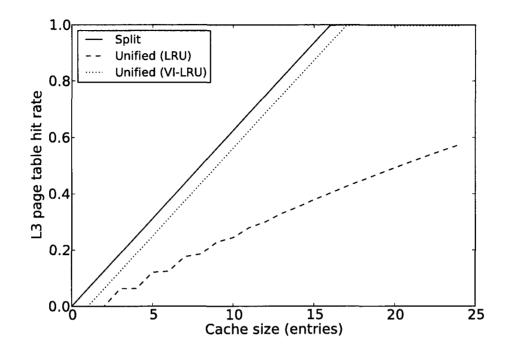

| 4.11 | L3 page table hit rate for the 16GB database join                           | 44 |

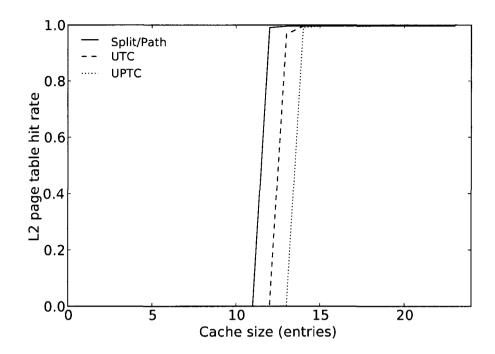

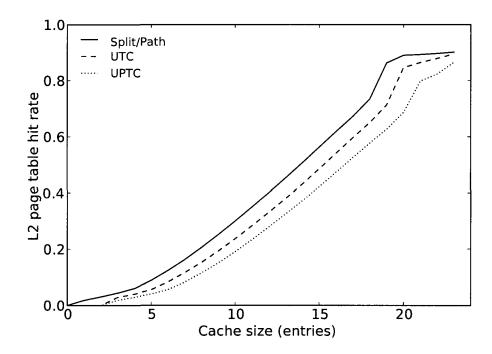

| 4.12 | L2 page table hit rate for Sweep3d                                          | 45 |

| 4.13 | L2 page table hit rate for CactusADM                                        | 46 |

| 4.14 | L3 page table hit rate for the 16GB database using VI-LRU replacement       | 48 |

|      |                                                                             |    |

| 6.1  | A page table containing a marked reservation.                               | 64 |

| 6.2  | An example of the contents of a SpecTLB                                     | 64 |

|      |                                                                             |    |

\_\_\_\_\_

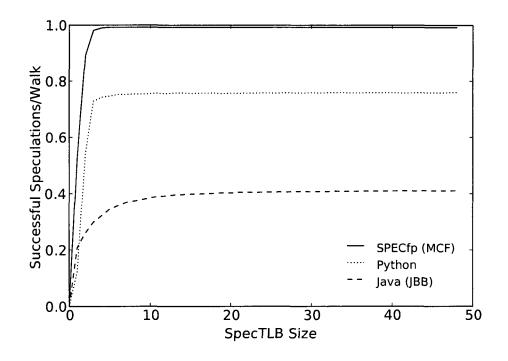

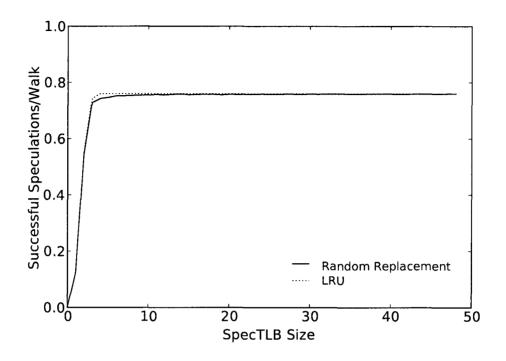

| 6.3 | Speculation rates for different sizes of SpecTLB     | 72 |

|-----|------------------------------------------------------|----|

| 6.4 | Speculation rates for different replacement policies | 73 |

# Tables

| 4.1 | General parameters for different cache designs                             | 30 |

|-----|----------------------------------------------------------------------------|----|

| 4.2 | Specific parameters for different cache designs on AMD64                   | 31 |

| 4.3 | The frequency of TLB misses for each workload, shown as the number of      |    |

|     | instructions, memory accesses and DRAM accesses between TLB misses.        |    |

|     | These results are shown for three different L2 data cache sizes and the    |    |

|     | TLB configuration described in Section 4.5.                                | 40 |

| 4.4 | TLB memory access patterns for various benchmarks                          | 51 |

| 4.5 | Effect of replacement policy on MMU cache miss rate                        | 52 |

|     |                                                                            |    |

| 5.1 | L2 hits and DRAM accesses to the page table per walk for a radix tree      |    |

|     | page table for the 16GB database join benchmark. Results are shown for     |    |

|     | an uncached radix tree, a cached radix tree, and a half-full inverted page |    |

|     | table with various numbers of clustered translations per tag               | 55 |

|     |                                                                            |    |

| 6.1 | SpecTLB simulation results for SPEC CPU2006                                | 79 |

| 6.2 | SpecTLB simulation results for other benchmarks                            | 80 |

# CHAPTER 1

# Introduction

## 1.1 Introduction

Virtual memory is not a solved problem. While it is conceptually simple, mapping multiple large virtual address spaces to a single physical address space is a massive organizational challenge. There can be millions of pages resident in memory at any given time. Additionally, virtual address spaces are large and sparsely used. Even though a particular process may only use a few gigabytes of memory, this data may be spread over a many terabyte region of the virtual address space. To support this, page tables on x86-64 use a multi-level radix tree. This format saves space, but requires multiple accesses to the page table to translate a single address.

On modern systems, this *address translation* becomes the dominant performance overhead of virtual memory. The limited size of translation lookaside buffers (TLBs) means that misses are inevitable and the page table must be consulted to translate addresses. Recent work has shown that the impact of address translation on overall system performance ranges from 5-14% even for nominally sized applications in a non-virtualized environment [1].

As the application's memory footprint increases, it has a significantly larger impact on virtual memory performance, approaching 50% in some cases [2]. In this thesis, we show that databases can be particularly taxing on address translation hardware. A common oper-

ation in databases is the join, which can use hash tables of many gigabytes for in-memory databases. Such joins are common, and the performance of large joins is representative of overall database performance [3]. Modern scientific supercomputing workloads are working with fewer dense matrices and more with sparse and graph structures [4]. These workloads are have less spatial locality in their access pattern and therefore will see a far higher TLB miss rate than traditional scientific applications. In the future, all of these applications are likely to use more memory as available physical memory increases.

Compounding address translation overhead is virtualization. Nested paging, the current technique for hardware supported memory virtualization, increases virtual memory overhead geometrically. Each address in a guest virtual address space must first be translated into a guest physical address. That guest physical address must then be translated into a host physical address. Since guest page tables on x86-64 store pointers in guest physical address form, a so-called *nested translation* can take as much as twenty-four memory accesses. Under nested paging, the overhead of virtual memory increases to up to 89% for real world workloads [1].

The primary focus of recent research to reduce this overhead has been to directly reduce the number of TLB misses by increasing the coverage of the TLB. Since TLBs are on the critical path of a memory access, their size is technology limited. Therefore, an increase in TLB coverage must come from an increase in the coverage of each particular entry, in other words, an increase in page size. Large pages have been shown to improve system performance for some workloads up to 30% as compared to using only small pages [5]. However, using large pages limits the ability of the operating system to control the allocation and protection of data. This can lead to wasted physical memory and I/O overheads. Additionally, fine-grained protection is required to emulate I/O devices in virtualization.

While this work has been successful at reducing the number of TLB misses, they can

never eliminate the problem entirely for two reasons. First, many environments like virtualization require fine grained allocation and protection, precluding the use of large pages. Additionally, while large pages increase TLB coverage, they only delay the problem. As physical memory sizes increase, the fraction of memory that can be covered by the TLB continues to shrink.

Comparatively less attention has been paid to reducing the cost of TLB misses once they happen. On x86-64, the high overhead of virtual memory is often traced to the large number of memory accesses required for a radix tree page table. In the common case, to translate a small page, it requires four accesses to the memory hierarchy per translation. However, since there is locality in virtual address use on a granularity larger than a page, there is reuse of these higher level page table entries. To exploit this, Intel and AMD have both introduced *MMU caches*, dedicated caches to serve upper levels of the page table. These devices can reduce the number of memory hierarchy accesses required to translate an address from four to nearly one.

AMD's MMU cache, the *page walk cache*, is essentially a very small L1 cache for page table entries. It holds 24 entries, uses an LRU replacement scheme and each entry is tagged by the page table entry's address in physical memory space. Intel's *paging structure caches* are a set of three caches, each responsible for caching a particular level of the table. This cache is tagged using portions of the virtual address translated by the page table entry. This allows the page walk hardware to "skip" cached levels of the tree. The differences in behavior between these very different designs has not been previously investigated.

Alternatively, other work has proposed replacing the radix table entirely. Some processors utilize a page table based on hashing, a decision supported by a significant body of research [6, 7]. In the ideal case, a hash table can reduce the number of required memory accesses to one. However, a hash table comes with significant overhead in terms of

tagging which can reduce the efficiency of page table entry caching. Literature comparing these designs is relatively old and has not investigated the impact of MMU caching on this tradeoff.

These systems all try to reduce the number of memory hierarchy accesses required per translation to one. However, this final memory access is the one most likely to miss in the data cache, so it can be extremely expensive. Nonetheless, no work has been done on reducing the impact of this final access. There is significant opportunity for performance increase if a system can be developed that predicts translations without any memory accesses at all. The use of a reservation based physical memory allocator can make such predictions possible. Such a system leaves significant alignment and contiguity in the mapping between virtual pages and physical pages. There is currently no system which exploits the predictability inherent in these underfilled reservations.

### **1.2 Contributions**

This thesis begins by examining two current approaches to accelerating address translation: caching and alternative page table formats. We show that exploiting inter-page spatial locality is critical to performance. We performed the first comprehensive design space exploration and developed the first descriptive nomenclature of MMU caches. We divide five different designs into a two dimensional space. We show that caches tagged by virtual address parts (dubbed *translation caches*) outperform caches tagged by page table entry (PTE) physical address (*page table caches*). While their coverage is similar, translation caches are able to skip levels of the page table, reducing the number of memory hierarchy accesses required per walk.

We also analyze the tradeoffs between split and unified caches. This choice is a tradeoff between isolating data of differing importance and adaptability to differing workloads. Split caches preserve upper level entries at the expense of flexibility and die area. This hampers performance on large-memory applications. We present a novel replacement policy, Variable-Insertion Point LRU, that dynamically partitions the cache for a given workload. This replacement policy adapts to preserve entries that have high reuse. It allows a unified MMU cache of n + 1 entries to perform as well as a split cache holding a total of  $3 \times n$ entries, even under pathological workloads.

Secondly, we compare the current x86-64 radix tree page table with competing formats. We examine an inverted page table, a clustered page table and a translation storage buffer. Our work is the first to compare a radix tree page table with a dedicated MMU cache against these alternate formats. We find that the overhead of tagging dramatically reduces the cachability of page table entries. Additionally, in a radix table, translations for pages adjacent in the virtual address space are adjacent in the page table. In a hash-based page table, however, adjacent translations are from random virtual addresses. This decreases the spatial access locality to the page table. The alternate page table formats require up to 4x as many DRAM accesses than the standard radix table. We conclude that the most important factors in page table design are the number of adjacent translations that can fit in a cache line and the total number of translations that can fit in the processor cache.

Finally, we present a novel device that exploits alignment and contiguity in the physical address space created by reservation based memory allocators. Our device can predict the physical address of a request that causes a TLB miss by using interpolation. This predicted address can be used for speculative execution while the page walk occurs in parallel, eliminating the latency of the TLB miss for these cases. In our simulations, it is able to remove a per-benchmark average of 56% of MMU-related DRAM accesses from the critical path of execution.

## 1.3 Organization

This thesis is organized as follows. Chapter 2 introduces the x86-64 page table. It discusses the evolution of the table and its support for multiple page sizes. Chapter 3 discusses related work. Chapter 4 discusses and evaluates the different MMU cache designs. Each cache design is compared using a variety of different workloads. Chapter 5 evaluates competing page table formats using traces developed in Chapter 4. Chapter 6 introduces our novel speculative TLB design. Finally, we Conclude in chapter 7.

# CHAPTER 2

# **x86 Address Translation**

Much of the overhead of the x86 address translation system is due to its multilevel nature. The 48-bit virtual address space supported on current x86-64 processors is far too large to be supported by a simple flat page table. Therefore, it uses a four-level radix tree to efficiently store a sparsely utilized large address space. While this design is space efficient, it requires four sequential accesses to the page table per translation, causing a large latency penalty. This chapter examines the history and use of this page table design in detail while Chapter 4 examines hardware techniques to accelerate it.

### 2.1 Page Walk Details

All x86 processors since the Intel 80386 have used a radix tree to record the mapping from virtual to physical addresses. Although the depth of this tree has increased, to accommodate larger physical and virtual address spaces, the procedure for translating virtual addresses to physical addresses using this tree is essentially unchanged. A virtual address is split into a page number and a page offset. The page number is further split into a sequence of indices. The first index is used to select an entry from the root of the tree, which may contain a pointer to a node at the next lower level of the tree. If the entry does contain a pointer, the next index is used to select an entry from this node, which may again contain a pointer to a node at the next lower level of the tree. These steps repeat until the selected entry is either

| 63:48 | 47:39  | 38:30  | 29:21  | 20:12  | 11:0        |

|-------|--------|--------|--------|--------|-------------|

| se    | L4 idx | L3 idx | L2 idx | L1 idx | page offset |

Figure 2.1 : Decomposition of the x86-64 virtual address.

invalid (in essence, a NULL pointer indicating there is no valid translation for that portion of the address space) or the entry instead points to a data page using its physical address. In the latter case, the page offset from the virtual address is added to the physical address of this data page to obtain the full physical address. In a simple memory management unit (MMU) design, this procedure requires one memory access per level in the tree.

Figure 2.1 shows the precise decomposition of a virtual address by x86-64 processors [8]. Standard x86-64 pages are 4KB, so there is a single 12-bit page offset. The remainder of the 48-bit virtual address is divided into four 9-bit indices, which are used to select entries from the four levels of the page table. The four levels of the x86-64 page table are named PML4 (Page Map Level 4), PDP (Page Directory Pointer), PD (Page Directory) and PT (Page Table). In this thesis, however, for clarity, we will refer to these levels as L4 (PML4), L3 (PDP), L2 (PD) and L1 (PT). Finally, the 48-bit virtual address is sign extended to 64 bits. As the virtual address space grows, additional index fields (*e.g.*, L5) may be added, reducing the size of the *se* field.

An entry in the page table is 8 bytes in size regardless of its level within the tree. Since a 9-bit index is used to select an entry at every level of the tree, the overall size of a node is always 4KB, the same as the page size. Hence, nodes are commonly called page table pages. The tree can be sparsely populated with nodes—if at any level, there are no valid virtual addresses with a particular 9-bit index, the sub-tree beneath that index is not instantiated. For example, if there are no valid virtual addresses with L4 index 0x03a, that entry in the top level of the page table will indicate so, and the 262,657 page table pages

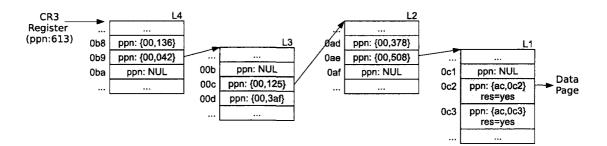

Figure 2.2: An example page walk for virtual address (0b9, 00c, 0ae, 0c2, 016). Each page table entry stores the physical page number for either the next lower level page table page (for L4, L3, and L2) or the data page (for L1). Only 12 bits of the 40-bit physical page number are shown in these figures for simplicity.

(1 L3 page, 512 L2 pages, and 262,144 L1 pages) beneath that entry in the radix tree page table will not exist. This yields significant memory savings, as large portions of the 256 TB virtual address space are never allocated for typical applications.

Figure 2.2 illustrates the radix tree page table walk for the virtual address 0x0000 5c83 15cc 2016. For the remainder of the thesis, such 64-bit virtual addresses will be denoted as (*L4 index, L3 index, L2 index, L1 index, page offset*) for clarity. In this case, the virtual address being translated is (0b9, 00c, 0ae, 0c2, 016). Furthermore, for simplicity of the examples, only 3 hexadecimal digits (12 bits) will be used to indicate the physical page number, which is actually 40 bits in x86-64 processors.

As shown in the figure, the translation process for this address proceeds as follows.

First, the page walk hardware must locate the top-level page table page, which stores L4 entries. The physical address of this page is stored in the processor's CR3 register. In order to translate the address, the L4 index field (9 bits) is extracted from the virtual address and appended to the physical page number (40 bits) from the CR3 register. This yields a 49-bit physical address that is used to address the appropriate 8-byte L4 entry (offset 0b9 in the L4 page table page in the figure). The L4 entry may contain the physical page number of an L3 page table page (in this case 042). The process is repeated by extracting the L3 index field from the virtual address and appending it to this physical page number to address the appropriate L3 entry. This process repeats until the selected entry is invalid or specifies the physical page number of the actual data in memory, as shown in the figure. Each page table entry along this path is highlighted in grey in the figure. The page offset from the virtual address. Note that since page table pages are always aligned on page boundaries, the low order bits of the physical address of the page table pages are not stored in the entries of the page table.

Given this structure, the current 48-bit x86-64 virtual address space requires four memory references to "walk" the page table from top to bottom to translate a virtual address (one for each level of the radix tree page table). As the address space continues to grow, more levels will be added to the page table, further increasing the cost of address translation. A full 64-bit virtual address space will require six levels, leading to six memory accesses per translation.

Alternatively, an L2 entry can directly point to a contiguous and aligned 2MB data page instead of pointing to an L1 page table page. In Figure 2.2, virtual address (0b9, 00d, 0bd, 123f5d7) is within a large page. This large-page support greatly increases maximum TLB coverage. In addition, it lowers the number of memory accesses to locate one of these pages from four to three. Finally, it greatly reduces the number of total page

table entries required since each entry maps a much larger region of memory.

# CHAPTER 3

# **Related Work**

Work on reducing the performance penalty of virtual memory can be divided into techniques that reduce the impact of TLB misses and those that reduce their frequency. Previous work on reducing the impact of TLB misses have primarily investigated alternative page table formats and caching, as examined in this thesis. Systems that reduce TLB miss frequency have been primarily related to large page use and TLB prefetching. Our work is generally complementary to these techniques.

## 3.1 Caching

Some early work on caching page table entries was done before the introduction of AMD and Intel's MMU caches. This work was targeted at accelerating software TLB miss handling. Bala *et al.* introduced a software cache for page table entries [9]. This cache is read by the software page fault handler and manages entries in physical memory to avoid cascading TLB misses that come from reading page table entries in virtual memory space. Wu and Zwanepoel expanded this to a hardware/software design [10]. They propose a dedicated cache to handle L2 page table entries. If a translation hits in their structure, the MMU loads the L1 entry directly, as in the caches presented in this thesis. If the translation misses, a software fault is triggered. We extend this proposal into a device that caches all upper levels in Chapter 4.

McCurdy *et al.* investigated the TLB performance of a wide variety of highperformance computing applications over different page sizes [2]. They show that this class of application can have significant overhead from memory management. Changing page sizes can change application performance by up to 50% in many cases. They also show that the HPCC and SPEC benchmarks do not necessarily represent these applications, and are poor analogues for choosing page sizes with.

The authors point out the importance of the L2 data cache in storing page table entries. Applications were profiled with performance counters on actual hardware. This reveals that applications that use large pages can show improved performance even in the face of *decreased* TLB hit rates. This is due to the shallower, and therefore smaller, page table when using large pages.

Bhargava *et al.* first described the AMD page walk cache and their extensions to it to support virtualization. This cache is described in detail in Chapter 4.

### **3.2** Alternate page table formats

Jacob and Mudge [11] compare five production and proposed systems with different memory management systems. They conclude that the x86-32 MMU has the highest performance because it works entirely in hardware, without any software handling. The precise interrupts required by software MMUs, such as those on MIPS, present an overhead that is not hidden by caching. We examine these interrupts in the context of SPARC's Translation Storage Buffer in Chapter 5. They also show that MMU related memory accesses can cause higher than expected cost due to user program and data being evicted by page table entries. This effect further emphasizes the importance of efficient storage of page table entries.

In terms of space, a radix tree-based page table can be an inefficient representation for a large, sparsely-populated virtual address space. Liedtke introduced *Guarded Page Tables* to

address this problem [12]. In particular, Guarded Page Tables allow for path compression. If there is only one valid path through multiple levels of the tree, then the entry prior to this path can be configured such that the page walk will skip these levels.

Talluri and Hill presented alternate forms of inverted page tables called clustered and subblocked page tables [6, 7]. These designs associate a power of two number of adjacent translations with a single virtual tag. The high bits of a virtual address are compared against the tag while the low bits select a particular subblock. We simulate a similar system in Section 5.1 and compare it to both traditional inverted page tables and cached radix tree tables. They also present support for a subblock TLB which uses the same tag stored in the page table. Each entry in their TLB stores multiple translations with a common virtual tag. This provides some of the benefits of large pages without requiring operating system modifications beyond support for the new page table format.

This technique reduces the space overhead of the page table by reducing the number of tags that are required per translation. However, it also increases the number of translations in the page table that can fit in a processor data cache (or a single line of the cache), which we show in Chapter 5. We conclude that such a system is not as efficient as the radix tree page table.

## **3.3 Reducing TLB miss frequency**

Talluri and Hill ([6]) first proposed a reservation based system for using clustered page tables. Navarro *et al.* ([5]) extended this idea into a practical memory allocator for superpages and implemented it under FreeBSD. Most critically, this extension developed the reclamation of underfilled superpage reservations. While these works are trying to create full reservations, as a by-product, they also create contiguity in the page table that is exploited in this thesis. Additionally, their work extended the system to support multiple page

sizes.

Early work on implementing superpage support in general-purpose operating systems used a static page size determination. IRIX ([13]), Solaris ([14]) and HP-UX ([15]) allocate superpages at page fault time. An process tells the operating system that a region of its address space should be allocated using large pages. These operating systems then allocate and map the entire page at once, unlike the reservation and promotion process used by FreeBSD. Since these systems do not place small pages in a reservation, they will not benefit from the techniques described in this work.

Romer *et al.*, ([16]) propose the creation of superpages by moving existing pages, previously scattered throughout physical memory, into contiguous blocks. While this process may be prohibitively expensive for very large superpages, it may have more success with the architecture described here that does not require a full reservation.

Saulsbury *et. al.* propose a prefetching scheme for TLBs that preload pages based recently accessed pages [17]. Unlike the techniques presented in this thesis, their techniques require page table modification. More recent work [18, 19] has proposed architecturally independent prefectching techniques based on access patterns and inter-core cooperation.

These techniques all focus on reducing the frequency of TLB misses while our work focuses on reducing the cost of servicing a TLB miss. Both types of techniques are complementary and could easily be combined.

# **CHAPTER 4**

# **MMU** Caching

## 4.1 Introduction

This chapter explores the design space of memory-management unit (MMU) caches for accelerating virtual-to-physical address translation in processor architectures, like x86-64, that implement paged virtual memory using a radix tree for their page table. In particular, these caches accelerate the page table walk that occurs after a miss in the Translation Lookaside Buffer (TLB). In fact, a hit in some of these caches enables the processor to *skip* over one or more levels of the tree and, in the best case, access only the tree's lowest level.

For several generations of x86 processors, from the Intel 80386 to the Pentium, the page table had at most two levels. Consequently, whenever a TLB miss occurred, at most two memory accesses were needed to complete the translation. However, as the physical and virtual address spaces supported by x86 processors have grown in size, the maximum depth of the tree has increased, first to three levels in the Pentium Pro to accommodate a 36-bit physical address within a page table entry, and more recently to four levels in the AMD Opteron to support a 48-bit virtual address space. In fact, with each passing decade since the introduction of the 80386, the depth of the tree has grown by one level.

Recent work has shown the impact of TLB misses on overall system performance ranges from 5-14% for nominally sized applications, even in a non-virtualized environ-

ment [1]. As the application's memory footprint increases, TLB misses have a significantly larger impact on performance, approaching 50% in some cases [2]. Although the use of large pages can lessen this impact, with further increases in the memory footprint their effectiveness declines. Therefore, both AMD and Intel have implemented MMU caches for page table entries from the higher levels of the tree [20, 1]. However, their caches have quite different structure. AMD's Page Walk Cache stores page table entries from any level of the tree, whereas Intel implements distinct caches for each level of the tree. Also, AMD's Page Walk Cache is indexed by the physical address of the cached page table entry, whereas Intel's Paging-Structure Caches are indexed by portions of the virtual address being translated. Thus, in this respect, the Page Walk Cache resembles the processor's data cache, whereas the Paging-Structure Caches resemble its TLB.

This chapter's primary contribution is that it provides the first comprehensive exploration of the design space occupied by these caches. In total, it discusses five distinct points in this space, including three new designs. Specifically, it presents the first head-to-head comparison of the effectiveness of these designs. In general, the results of this comparison show that the *translation caches*, which store partial translations and allow the page walk hardware to skip one or more levels of the page table, are the best. In addition, the new translation caches that are introduced by this chapter are better than the existing caches in many situations and workloads.

This chapter is organized as follows. Section 4.2 describes the design space, identifying the essential differences between AMD's Page Walk Cache, Intel's Paging-Structure caches, and the new structures developed in this chapter. Section 4.3 qualitatively compares these structures, and Section 4.5 describes this chapter's methodology for quantitatively comparing them. Section 4.6 presents quantitative simulation results of their effectiveness as compared to one another. Finally, Section 4.8 summarizes this chapter's conclusions.

## 4.2 Caching page walks

While radix-tree page tables require many accesses to translate a single address, the accesses to the upper level page table entries have significant temporal locality. Walks for two consecutive pages in the virtual address space will usually use the same three upper level entries, since the indices selecting these entries come from high-order bits of the virtual address, which change less frequently.

While the MMU does access the page table through the memory hierarchy, it only has access to the L2 data cache in at least one major commercial x86 design [1]. Since the L2 data cache is relatively slow on modern CPUs, accessing three upper-level page table entries on every page walk will incur a penalty of several tens of cycles per TLB miss, even if all entries are present in the L2 data cache.

Therefore, the x86 processor vendors have developed private, low-latency caches for the MMU that store upper level page table entries [1, 20]. In this section, we describe the design space and provide a nomenclature for the different tagging and partitioning schemes used by these MMU caches.

MMU caches may store elements from the page table tagged by their physical address in memory, as a conventional data cache might. We call such MMU caches *page table caches*. Examples include AMD's *Page Walk Cache* and the L2 data cache, although it is not private to the MMU. Alternatively, MMU caches can be indexed by parts of the virtual address, like a TLB. We call such MMU caches *translation caches*. Intel's *Paging-Structure Caches* are translation caches.

For either of these tagging schemes, elements from different levels of the page table can be mixed in a single cache (a *unified* cache), or placed into separate caches (a *split* cache). Finally, each cache entry can store an entry from one level along the page walk, or it can store an entire path (a *path* cache).

#### 4.2.1 Page table caches

The simplest example of a page table cache is the processor's L2 data cache. The page walker generates a physical address based upon the page table page to be accessed and an index from the virtual address. This physical address is then fetched from the processor's memory hierarchy starting with the L2 data cache.

Page table caches use this same indexing scheme. Elements are tagged with their physical address in the page table. These tags are the size of the physical page number plus the size of one page table index. L1 entries are not cached in any of the designs presented here (since the TLB itself caches those entries).

| Base Location | Index | Next Page |

|---------------|-------|-----------|

| 125           | 0ae   | 508       |

| 042           | 00c   | 125       |

| 613           | 0b9   | 042       |

|               |       |           |

Figure 4.1 : An example of the contents of a UPTC. Each entry is tagged with the address of a page table entry, consisting of the 40-bit physical page number of the page table page and a 9-bit index into it. The entry then provides a 40-bit physical page number for the next lower level page table page. (Only 12 bits of the physical page numbers are shown, for simplicity.)

### **Unified Page Table Cache (UPTC)**

The simplest design for a dedicated page table cache is a single, high-speed, read-only cache for page table entries, tagged by their physical address in memory. Entries from different levels of the page table are mixed in the same cache, all indexed by their physical address. Such a cache is analogous to a private, read-only L1 data cache for page table

|            | Base Location | Index | Next Page |

|------------|---------------|-------|-----------|

| L2 entries | 125           | 0ae   | 508       |

| L2 chuics  |               |       |           |

|            |               |       |           |

| L3 entries | 042           | 00c   | 125       |

| LJ enuies  |               | •••   |           |

|            |               |       |           |

| L4 entries | 613           | 0b9   | 042       |

|            |               |       |           |

Figure 4.2 : An example of the contents of a SPTC. Each entry holds the same tag and data as in the UPTC.

entries. However, like a TLB, coherence between this cache and the page table can be maintained by software with little overhead. AMD's Page Walk Cache has this design [1].

Figure 4.1 shows an example of the Unified Page Table Cache (UPTC) after the MMU walks the page table to translate the virtual address (0b9, 00c, 0ae, 0c2, 016). If the MMU subsequently tries to translate the virtual address (0b9, 00c, 0ae, 0c3, 103), the page walk will begin by looking for the page table entry 0b9 in the L4 page table page (located at 613 and referenced by the CR3 register). Since this page table entry is present in the UPTC, it does not need to be loaded from the memory hierarchy.

This entry indicates that the L3 page table page has physical page number 042. The same process is then repeated to locate the L2 and L1 page table pages. Once the address of the L1 page table page is found, the appropriate entry is loaded from memory to determine the physical page address of the desired data.

Without a page table cache, all four of these accesses to page table entries would have required a memory access, each of which may or may not hit in the L2 data cache. In contrast, with the page table cache, the three top entries hit in the private page table cache, and only one entry (the L1 entry) requires a memory access, which may or may not hit in

the L2 data cache.

#### Split Page Table Cache (SPTC)

An alternate design for the page table cache separates the page table entries from different levels into separate caches. Figure 4.2 illustrates a Split Page Table Cache (SPTC). In this design, each individual entry contains the same tag and data as it would in the unified page table cache. The primary difference is that each page table level gets a private cache, and entries from different levels do not compete for common slots.

### 4.2.2 Translation caches

As an alternative to tagging cache entries by their physical address, they can be tagged by their indices in the virtual address. An L4 entry will be tagged by the 9 bit L4 index, an L3 entry with the L4 and L3 indices, and an L2 entry with the L4, L3, and L2 indices. We call this device a *translation cache*, because it is storing a partial translation of a virtual address.

With this tagging scheme, data from one entry is not needed to lookup the entry at the next lower level of the page table. All of the lookups can be performed independently of each other. In the end, the MMU will select the entry that matches the longest prefix of the virtual address because it allows the page walk to skip the most levels.

### Split Translation Cache (STC)

Like an SPTC, the Split Translation Cache (STC) stores entries from different levels of the page table in separate caches. However, as shown in Figure 4.3, the STC uses a different way of tagging the entries. The Intel *Paging-Structure Caches* [20] exemplify the STC organization.

|            | L4 index | L3 index | L2 index | Next Page |  |  |

|------------|----------|----------|----------|-----------|--|--|

| L2 entries | 0b9      | 00c      | 0ae      | 508       |  |  |

| L2 enuies  |          |          | • • •    |           |  |  |

|            |          |          |          |           |  |  |

| L3 entries | 0b9      | 00c      |          | 125       |  |  |

| L5 entites | •••      | •••      |          | • • •     |  |  |

|            |          |          |          |           |  |  |

| L4 entries | 0b9      |          |          | 042       |  |  |

|            |          |          |          |           |  |  |

Figure 4.3 : An example of the contents of a STC. Each index is 9-bits, and the data holds a 40-bit physical page number of the next page table level. An entry in the L2 cache must match on all three indices, an entry in the L3 must match on two and the L4 on one.

| L4 index | L3 index | L2 index | Next Page |

|----------|----------|----------|-----------|

| 0b9      | 00c      | 0ae      | 508       |

| 0b9      | 00c      | xx       | 125       |

| 0b9      | xx       | xx       | 042       |

|          |          |          |           |

Figure 4.4 : An example of the contents of a UTC. An "xx" means "don't care".

The example in Figure 4.3 shows the split translation cache after the MMU walks the page table to translate the virtual address (0b9, 00c, 0ae, 0c2, 016). If the MMU subsequently starts to translate the virtual address (0b9, 00c, 0dd, 0c3, 929), it will attempt to locate the L1, L2 and L3 page table pages in their corresponding caches using portions of the virtual address. The location of the L3 page table page would be stored in the L4 entry cache and tagged by the L4 index, (0b9). Similarly, the location of the L2 page table page would be stored in the L3 entry cache and tagged by the L4 and L3 indices, (0b9, 00c). Finally, the location of the L1 page table page would be stored in the L2 entry cache and tagged by the L4, L3 and L2 indices, (0b9, 00c, 0dd).

These searches can be performed in any order, and even in parallel. In the above example, the cache can provide the location of the appropriate L3 and L2 page table pages, but not the L1 page table page, as (0b9, 00c, 0dd) is not present in the L2 entry cache. Ultimately, the MMU would use the (0b9, 00c) entry from the L3 entry cache because it allows the page walk to begin further down the tree, at the L2 page table page.

### **Unified Translation Cache (UTC)**

Just as the page table caches can be built with either a split or a unified organization, a Unified Translation Cache (UTC) can also be built. Moreover, just like the UPTC, the UTC mixes elements from all levels of the page table in the same cache.

Figure 4.4 shows the UTC after the MMU walks the page table to translate the virtual address (0b9, 00c, 0ae, 0c2, 016). If the MMU subsequently starts to translate the virtual address (0b9, 00c, 0dd, 0c3, 929), it will first look in the UTC for the physical page numbers of the L1, L2 and L3 page table pages. As with the previous example that used the STC, the MMU finds two matching entries in the UTC. Ultimately, the MMU decides to use the UTC's second entry, which is an L3 entry that has the L4 and

L3 indices (0b9, 00c) as its tag, because this tag matches the longest prefix of the virtual address. Thus, the MMU can skip the L4 and L3 page table pages and start walking from the L2 page table page.

### 4.2.3 Translation-Path Cache (TPC)

Note that in the UTC example in Figure 4.4, the tags for the three entries representing a single path down the page table all have the same content. The L4 and L3 entries use less of the virtual address than the L2 entry does, but the fragments that they do use are the same. Consequently, it is possible to store all three physical page numbers from this example in a single entry. In such a *Translation-Path Cache* (TPC), a single entry represents an entire path, including all of the intermediate entries, for a given walk instead of a single entry along that walk.

| L4 index | L3 index | L2 index | L3  | L2  | L1  |

|----------|----------|----------|-----|-----|-----|

| 0b9      | 00c      | 0ae      | 042 | 125 | 508 |

|          |          |          |     | ••• |     |

Figure 4.5: An example of the contents of the TPC after the virtual address (0b9, 00c, 0ae, 0c2, 016) is walked. The TPC holds three 9 bit indices, as the translation caches do, but all three 40-bit physical page numbers are stored for all three page table levels.

The example in Figure 4.5 shows the TPC after the MMU walks the page table to translate the virtual address (0b9, 00c, 0ae, 0c2, 016). All data from that walk is stored in one entry. If the MMU subsequently starts to translate the virtual address (0b9, 00c, 0ae, 0c3, 929), the entry referencing the L1 page table page is discovered just as it would have been in the unified translation cache. Specifically, the MMU finds the entry in the cache with the tag (0b9, 00c, 0ae) and reads the physical page number 508 of the L1 page table page from this entry.

If the MMU later starts to translate the virtual address (0b9, 00c, 0de, 0fe, 829), this address shares a partial path (0b9, 00c) with the previously inserted entry. Therefore, the translation-path cache will provide the physical address of the appropriate L2 page table page.

#### 4.2.4 Design space summary

In summary, the caches described in this section fit into the following two-dimensional design space (annotated with the section number in which each design is described):

|                   | Unified | Split | Path  |

|-------------------|---------|-------|-------|

| Page Table Cache  | 4.2.1   | 4.2.1 | N/A   |

| Translation Cache | 4.2.2   | 4.2.2 | 4.2.3 |

The unified page table cache (UPTC) is the design that appears in modern AMD x86-64 processors. The split translation cache (STC) is the design that appears in modern Intel x86-64 processors. The remaining three designs have been introduced in this chapter.

Note that there is no useful page table counterpart to the translation-path cache. This is a direct result of the indexing scheme. While a "path" of physical addresses could be stored as an MMU cache index, it would have to be searched sequentially because the MMU cannot create a path of physical page numbers directly from the virtual address. It must look up each physical page in turn. Therefore, storing complete paths would yield no benefit over the other page table cache designs.

## 4.3 Design comparison

All of the designs presented in the previous section are able to accelerate page walks by caching information from the upper levels of the page table. However, these designs have

differences in their indexing, partitioning, coverage, and complexity. This section discusses the effects of these differences.

#### 4.3.1 Indexing

The indexing scheme determines how the cache is searched. Cache indices can be derived from the physical addresses of components of the page table or they can be derived from the virtual address and correspond to the levels of the page table.

Page table caches use the physical addresses of the page table entries as indices. In fact, they operate identically to any physically indexed cache—a UPTC is essentially another data cache in the memory hierarchy dedicated to the page table. The MMU will generate a physical address for the page table entry at each stage of the page walk, and that address will be used as an index into the appropriate page table cache. While this leads to a simple design, it requires the cache lookups to occur in a top-down order. The result of the L4 entry gives the physical page number of the L3 entry search can begin, because the L4 entry gives the physical page number of the L3 page table page, which is needed to generate the physical address of the L3 page table entry. Similarly, the L2 search is dependent on the result of the L3 search. In the case where the cache holds all three entries (L4, L3, and L2), the cache must be accessed three times to generate the physical address of the L1 page table entry.

In contrast, translation caches use components of the virtual address as indices. For example, the TLB is an L1 translation cache that uses the virtual page number as its index. In general, for translation caches, the MMU uses a prefix of the virtual page number as the index. This allows the translation caches to be searched in any order (L4 first, L2 first, or in parallel). Thus, on a TLB miss, the L2 translation cache can immediately be searched. Upon a hit which yields the L2 translation, the address of the L1 page table entry can be computed immediately. If no L2 translation is available, the L3, then L4, translation caches

can be searched. Upon a hit, the page walk would begin at that point in the tree.

#### 4.3.2 Partitioning

MMU caches can either be unified or partitioned, or they can store complete path information. The partitioning of the cache determines how the entries of the cache are allocated to different levels of the page table. This effectively determines how well the entries from different levels are isolated from each other.

The impact of the partitioning scheme largely depends on whether the application densely or sparsely utilizes its virtual address space. For applications that densely use their virtual memory, a few L4 and L3 entries are heavily utilized and there is significant reuse of the L2 entries. In contrast, for applications that sparsely use their virtual memory, there will be little reuse for L2 entries, but a larger number of L4 and L3 entries will exhibit reuse. The partitioning strategy and replacement policy determine how these entries will compete for slots, which can have a significant impact on the effectiveness of the MMU cache.

For applications that densely use their virtual memory, there will be many more L2 entries than upper level entries in use. However, for a page table cache design, these upper level entries are critical for translation performance. If a random replacement scheme is used in conjunction with a unified cache, these important entries can be frequently replaced, resulting in memory accesses to entries at or near the top of the table. However, if entries from different levels are kept in separate caches, a random replacement policy is less detrimental.

For applications that sparsely use many gigabytes of virtual memory, L2 entries will have very little reuse, and effective caching of L3 entries is critical. In a split entry cache, a static allocation of entries to each level must be made. If this allocation is optimized for small applications, it will have many more L2 entries than L3 entries, harming performance in this situation. Moreover, if an application makes heavy use of large pages and limited use of small pages, the dedicated L2 entries will be of little or no use. In contrast, in a unified cache, the allocation happens dynamically, but recently accessed L2 entries that will not be reused might evict L3 entries that might otherwise be reused. A level-aware replacement policy can help to avoid this.

The Greedy Dual algorithm is a popular content-aware replacement scheme [21]. This algorithm will replace recently used entries early if they are easier to reload into the cache. This scheme can be adapted for MMU caches by preferentially replacing lower-level entries with upper-level entries, thus reducing conflict between entries of high and low reuse. While Greedy Dual is not an algorithm that can easily be implemented in hardware, it is possible to implement a similar algorithm with minimal modification to an LRU cache.

In our modified LRU algorithm, entries from lower levels of the page table are inserted into the LRU queue at a recency position behind the most-recently-used position. If these lower level entries are reused, they are promoted to the most recently used position. However, if they are not reused, the portion of the cache in which lower level entries compete with upper level entries is small. These positions can be fixed, for simplicity, or they can change to adapt to different workloads. We propose a *variable insertion-point LRU replacement policy* whereby entries from lower levels of the cache are inserted into a recency position below the most recently used position that is proportional to the current number of upper level entries stored. For example, if there are two L4 entries and six L3 entries currently in the cache, a new L2 entry is inserted in the ninth most recently used position in the cache.

The path translation cache avoids these partitioning problems, as each slot holds an entry from all levels. This prevents the competition for slots while not requiring a static allocation of slots to levels. However, since this cache may hold many paths with the same upper level entries, its effective capacity for holding upper level entries is less than three equally sized split entry caches.

#### 4.3.3 Coverage

Characterizing the coverage of an MMU cache is not straightforward. In particular, the exact meaning of coverage for an MMU cache must first be considered. For example, suppose an address translation hits on an L3 entry in a page table or translation cache but does not hit on an L2 entry. In this case, the translation was accelerated by the MMU cache, but nonetheless required a memory access to fetch the page table's L2 entry. Thus, it is arguable whether or not the MMU cache provided coverage. We take the strict position that coverage means that no memory accesses were required to fetch L4, L3, or L2 page table entries.

In general, with the same number of entries, translation caches are able to cover a larger portion of the address space than page table caches. The reason is that a translation cache can make more efficient use of its entries than a page table cache. For a page table cache to provide coverage it must simultaneously hold an L4, L3, and L2 entry, whereas a translation cache can provide coverage with only an L2 entry. In other words, the translation cache may be able store additional L2 entries in place of the L4 and L3 entries that are required to provide coverage in the page table cache.

It can be shown that regardless of access pattern, a TPC storing n paths can provide any entry stored in a n entry unified cache. Additionally, a split page table cache of  $3 \times n$ entries can provide any entry stored in an n path TPC. These proofs are given in Appendix A.

When the application is simply too large for the MMU cache to provide full coverage,

|             |   | Unified         | Split                 | Path            |

|-------------|---|-----------------|-----------------------|-----------------|

|             | C | 1               | l-1                   |                 |

| Page Table  | Т | p-3             | $\{p-3,, p-3\}$       | N/A             |

|             | D | p - 12          | $\{p-12,, p-12\}$     |                 |

|             | C | 1               | l-1                   | 1               |

| Translation | T | $(l-1) \cdot n$ | $\{n,,(l-1)\cdot n\}$ | $(l-1) \cdot n$ |

|             | D | p - 12          | $\{p-12,, p-12\}$     | 3(p-12)         |

Table 4.1 : The number of caches (C), the number of tag bits per entry (T), and the number of data bits per entry (D) for each design.

the unified caches with our proposed VI-LRU replacement policies, the split caches, and the TPC are able to accelerate translations for more of the address space than the unified caches with conventional replacement policies. This is due to the fact that upper level entries are maintained longer in these caches. Since these effects are highly dependent on workload, the relative hit rates of the cache designs are studied experimentally in Section 4.6.

### 4.4 Implementation

In this section, we examine the relative costs of implementing the caches discussed in Section 4.2. While the design of caches in general is a well-studied field, each design has differing requirements. We begin by comparing these requirements on a high level, then we conclude by examining some specific circuit details unique to MMU caches.

All of the organizations examined are effectively fully associative caches, which can be implemented by a CAM array to match the tags and a RAM array to store the data entries. However, the different cache organizations have different tag and data widths, and will potentially require differing numbers of entries to achieve similar hit rates. These factors will lead to different implementation complexities for the different organizations.

Table 4.1 shows the number of caches, tag bits per entry, and data bits per entry that

|             |   | Unified | Split            | Path |

|-------------|---|---------|------------------|------|

|             | C | 1       | 3                |      |

| Page Table  | Т | 49      | $\{49, 49, 49\}$ | N/A  |

|             | D | 40      | {40, 40, 40}     |      |

|             | C | 1       | 3                | 1    |

| Translation | T | 27      | $\{9, 18, 27\}$  | 27   |

|             | D | 40      | $\{40, 40, 40\}$ | 120  |

Table 4.2 : MMU cache parameters for x86-64 processors. We have used the architectural definition of physical address width, 52 bits [8]. Actual implementations may use fewer bits.

are needed for each organization. These characteristics are parameterized by the number of levels of address translation, l, the number of bits in a physical address, p, and the number of offset bits in a page table index for a particular level, n. In x86-64 processors, l = 4, p = 52, and n = 9, which leads to the values shown in Table 4.2.

It should be noted that for current architectural parameters, translation caches require significantly smaller tags. This will make a translation cache smaller and more power efficient than an equivalent page table cache, as the CAM array is likely to dominate the power and area required by the structure.

#### 4.4.1 CAM Bypass

Fully-associative caches are not a new invention. However, the TPC and UTC add some additional complexity to the design because portions of the virtual address must be selectively ignored during a search. In this section we present some conjectural modifications to a standard fully-associative cache to support this constraint. We use the cache model from the CACTI tool from HP Labs [22] as our baseline in Figure 4.6.