# Locality Data Properties of 3D Data Orderings with Application to Parallel Molecular Dynamics Simulations

A thesis submitted in partial fulfillment of the requirement for the degree of Doctor of Philosophy

**Ibrahim Al Kharusi**

2019

Cardiff University School of Computer Science & Informatics

#### Declaration

This work has not previously been accepted in substance for any degree and is not concurrently submitted in candidature for any degree.

Signed ..... (candidate)

Date .....

#### Statement 1

This thesis is being submitted in partial fulfilment of the requirements for the degree of PhD.

Signed ..... (candidate)

Date .....

#### Statement 2

This work has not been submitted in substance for any other degree or award at this or any other university or place of learning, nor is it being submitted concurrently for any other degree or award outside of any formal collaboration agreement between the University and a partner organisation).

Signed ..... (candidate)

Date .....

#### Statement 3

I hereby give consent for my thesis, if accepted, to be available in the University's Open Access repository (or, where approved, to be available in the University library and for inter-library loan), and for the title and summary to be made available to outside organisations, subject to the expiry of a Universityapproved bar on access if applicable.

Signed ..... (candidate)

Date

### Word Count

(Excluding summary, acknowledgements, declarations, contents pages, appendices, tables, diagrams and figures, references, bibliography, footnotes and endnotes)

To my family for their patience and support.

### Abstract

General-purpose computing on GPUs is widely adopted for scientific applications, providing inexpensive platforms for massively parallel computation. This has motivated us to investigate GPU performance in terms of speed and memory usage, specifically in relation to data locality in molecular dynamics simulations. The assumption is that enhancing data locality of these applications will lower the cost of data movement across the GPU memory hierarchy. In this research, we analyse spatial data locality and data reuse (temporal data locality) characteristics for row-major, Hilbert, and Morton data orderings, and hybrid variants of these, and assess their impact on the performance of molecular dynamics simulations (MDS). Data locality in MDS applications, based on the relationship between a bin and its neighbouring bins, that are generated using an approximately spherical stencil, previously has not been widely studied. In this research, a simple cache model is presented, and this is found to yield results that are consistent with timing results for the particle force computation obtained on NVIDIA Geforce GTX960 and Tesla P100 graphical processing units (GPUs). The NVIDIA profiling tool is used to investigate the execution time results and to observe the memory usage in terms of cache hits and the number of memory transactions. The analysis also provides a more detailed explanation of execution behaviour for the different orderings. To the best of our knowledge, this is the first study to investigate memory analysis and data locality issues for molecular dynamics simulations of Lennard-Jones fluids on NVIDIA's Maxwell and Tesla architectures.

### Acknowledgements

This thesis would not have been possible without the inspiration and support of a number of wonderful individuals — my thanks and appreciation to all of them for being part of this journey and making this thesis possible. I owe my deepest gratitude to my supervisor, Professor David Walker. Without his enthusiasm, encouragement, support and continuous optimism, this thesis would have been difficult to complete. Also, I express my warmest gratitude to Dr George Theodorakopoulos, Dr Christine Mumford, Dr Xianfang Sun for all their input and support.

Thanks to my parents and my wife for their support, encouragement and patience, and also to my lovely children, AlKhalil, Issra, Alaa and Ahmed, for being strong and patient when I was away from them. Thanks to my brothers and sisters, and all my family members and friends, who coped with my absence during my PhD journey. Hopefully, they will all be proud of me.

To me, there is nothing better than having good brothers and friends, so I feel a great sense of pride while offering them my deepest gratitude: Yahya, Saif, Hamed, Shathan, Abdullah, Ahmed, Adil, Yousef, Abdualrahman, Khalid, Mohammed, Sulieman, Salim Al-Mutani, Mazin Al-Shidhani, Dr Taimur Al Said, Dr Sahar, Dr Aseela Al-Harthi, Shahd Alahdal.

I must also thank my fellow research students in the School, and there are truly too many of you to name, without risking missing someone out.

Thanks to Oman, for educating us and imbuing within us the sense that ambition has

no limit, and that through hard work we will achieve our dreams. We will continue to work tirelessly for you.

Thanks to the Information Technology Authority (Oman), for their trust and confidence whilst completing my studies. Thanks to Dr Salim Al Ruzaiqi (CEO of ITA), Omar Al Shanfari (Deputy CEO of ITA for Operations), the NDCC team, and the HR team for their continuous cooperation, support and motivation.

I would like also to thank the anonymous reviewers, whose comments helped us to improve our research work and enhance it before publication.

Most of all, foremost praise is to Allah, the Almighty, the greatest of all, on whom ultimately we depend for sustenance and guidance. I would like to thank Almighty Allah for guiding me through this journey and the continuous grace, mercy, and blessings have been with me throughout my life and even more so during my studies.

# Contents

| Ał | ostrac        | et                 | vii |  |  |

|----|---------------|--------------------|-----|--|--|

| Ac | cknow         | vledgements        | ix  |  |  |

| Co | ontent        | ts                 | xi  |  |  |

| Li | st of I       | Publications x     | ix  |  |  |

| Li | st of Figures |                    |     |  |  |

| Li | ist of Tables |                    |     |  |  |

| Li | st of A       | Algorithms xx      | ix  |  |  |

| Li | st of A       | Acronyms xxx       | iii |  |  |

| 1  | Intr          | oduction           | 1   |  |  |

|    | 1.1           | Overview           | 1   |  |  |

|    | 1.2           | Problem Definition | 3   |  |  |

|    | 1.3           | Hypothesis         | 5   |  |  |

|   | 1.4  | Aims a  | nd Objectives             | 6  |

|---|------|---------|---------------------------|----|

|   | 1.5  | Thesis  | Contributions             | 7  |

|   | 1.6  | Thesis  | Structure                 | 8  |

|   | 1.7  | Summa   | ary                       | 10 |

| 2 | Bacl | kground | l                         | 11 |

|   | 2.1  | Data L  | ocality                   | 12 |

|   |      | 2.1.1   | Cache Architecture        | 12 |

|   |      | 2.1.2   | Types of Cache Miss       | 15 |

|   |      | 2.1.3   | Cache Use Optimizations   | 16 |

|   | 2.2  | Space-  | Filling Curves            | 18 |

|   |      | 2.2.1   | SFC Definition            | 19 |

|   |      | 2.2.2   | Geometric Representation  | 20 |

|   |      | 2.2.3   | Arithmetic Representation | 22 |

|   | 2.3  | Data O  | rderings                  | 25 |

|   |      | 2.3.1   | Linear Ordering           | 26 |

|   |      | 2.3.2   | Hilbert Ordering          | 28 |

|   |      | 2.3.3   | Morton Ordering           | 32 |

|   |      | 2.3.4   | Hybrid Orderings          | 34 |

|   | 2.4  | Molecu  | alar Dynamics Simulations | 36 |

|   |      | 2.4.1   | Main Principles           | 37 |

|   |      | 2.4.2   | Molecular Interaction     | 37 |

|   |      | 2.4.3    | Periodic Boundary Conditions              | 41 |

|---|------|----------|-------------------------------------------|----|

|   |      | 2.4.4    | Neighbour Lists                           | 41 |

|   |      | 2.4.5    | Thermodynamics                            | 42 |

|   |      | 2.4.6    | Time Integration                          | 43 |

|   | 2.5  | Paralle  | el Programming                            | 44 |

|   |      | 2.5.1    | Memory Access and Process Synchronization | 45 |

|   |      | 2.5.2    | GPGPU Architecture and Programming        | 46 |

|   |      | 2.5.3    | GPU General Architecture                  | 47 |

|   |      | 2.5.4    | CUDA Programming                          | 49 |

|   | 2.6  | Optim    | ization and Performance Analysis          | 52 |

|   |      | 2.6.1    | GPUs Optimizations                        | 52 |

|   |      | 2.6.2    | Performance Analysis                      | 54 |

|   | 2.7  | Summ     | ary                                       | 55 |

| 3 | Lite | rature l | Review                                    | 57 |

|   | 3.1  | Data L   | ocality                                   | 57 |

|   |      | 3.1.1    | Loop Transformation                       | 58 |

|   |      | 3.1.2    | Drawbacks of Loop Transformation          | 63 |

|   |      | 3.1.3    | Data Order                                | 63 |

|   | 3.2  | Space    | Filling Curve Algorithms                  | 66 |

|   |      | 3.2.1    | Hilbert Order                             | 67 |

|   |      | 3.2.2    | Morton Order                              | 69 |

|   | 3.3  | Molec   | ular Dynamic Simulations Optimizations                     | 71  |

|---|------|---------|------------------------------------------------------------|-----|

|   |      | 3.3.1   | MDS Optimization Based on Reducing the Neighbour List Size |     |

|   |      |         | and Update Frequency                                       | 73  |

|   |      | 3.3.2   | MDS Optimization Based on Re-ordering                      | 74  |

|   | 3.4  | Summ    | ary                                                        | 80  |

| 4 | Sten | cil and | Data Locality Properties                                   | 83  |

|   | 4.1  | Spher   | ical Stencil                                               | 84  |

|   | 4.2  | Data L  | ocality Metrics                                            | 85  |

|   |      | 4.2.1   | Memory Access Patterns                                     | 86  |

|   |      | 4.2.2   | Cache Miss Rate                                            | 91  |

|   |      | 4.2.3   | Shared Stencil Bins                                        | 97  |

|   | 4.3  | Summ    | ary                                                        | 97  |

| 5 | GPU  | J Imple | mentation                                                  | 99  |

|   | 5.1  | Object  | ives and Scope                                             | 100 |

|   | 5.2  | MiniM   | ID Modules                                                 | 100 |

|   |      | 5.2.1   | Input Module                                               | 101 |

|   |      | 5.2.2   | Atom Module                                                | 103 |

|   |      | 5.2.3   | Neighbour Module                                           | 104 |

|   |      | 5.2.4   | Force Module                                               | 106 |

|   |      | 5.2.5   | Communication Module                                       | 107 |

|   |      | 5.2.6   | Thermodynamics Module                                      | 109 |

|   |       | 5.2.7   | Integration Module                              | 109 |

|---|-------|---------|-------------------------------------------------|-----|

|   |       | 5.2.8   | Timer Module                                    | 111 |

|   |       | 5.2.9   | Output Module                                   | 112 |

|   | 5.3   | Implen  | nented Modifications                            | 112 |

|   |       | 5.3.1   | Ordering Module                                 | 112 |

|   |       | 5.3.2   | Force Computation on the GPU                    | 119 |

|   |       | 5.3.3   | Implementation Analysis                         | 124 |

|   | 5.4   | Summa   | ary                                             | 125 |

| 6 | Donf  | anmana  | e Experiments, Results and Analysis             | 127 |

| U | 1 011 |         |                                                 |     |

|   | 6.1   | Experi  | mental Objectives                               | 127 |

|   | 6.2   | Hardw   | are for the Experiments                         | 128 |

|   | 6.3   | Profili | ng Tools                                        | 129 |

|   | 6.4   | Experi  | mental Setup                                    | 129 |

|   | 6.5   | CPU E   | experiments                                     | 131 |

|   |       | 6.5.1   | Force Module Execution Time                     | 131 |

|   |       | 6.5.2   | CPU Execution Time for Different Data Orderings | 132 |

|   | 6.6   | GPU E   | Experiments                                     | 134 |

|   |       | 6.6.1   | Theoretical Occupancy                           | 134 |

|   |       | 6.6.2   | GPU Force Computation Ratio                     | 135 |

|   | 6.7   | Localit | ty Analysis                                     | 138 |

|   |       | 6.7.1   | Execution Efficiency Analysis                   | 143 |

|   |             | 6.7.2 GPU Memory Analysis   | 152 |

|---|-------------|-----------------------------|-----|

|   | 6.8         | Summary                     | 156 |

| 7 | Con         | clusions and Future Work    | 157 |

|   | 7.1         | Conclusion                  | 157 |

|   | 7.2         | Research Questions Answered | 160 |

|   | 7.3         | Limitations                 | 162 |

|   | 7.4         | Future Work                 | 162 |

|   | 7.5         | Summary                     | 164 |

| A | Devi        | ce Query Output             | 165 |

|   | A.1         | Ruthenium (GeForce GTX 960) | 166 |

|   | A.2         | Hawk (Tesla P100)           | 167 |

| B | Gen         | erated Experiments          | 169 |

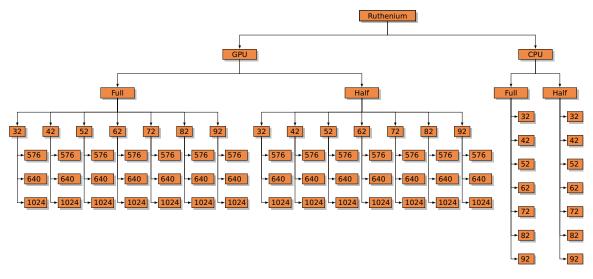

|   | B.1         | Ruthenium Experiments       | 169 |

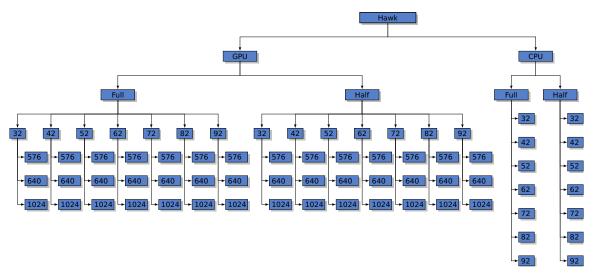

|   | B.2         | Hawk Experiments            | 170 |

| С | Haw         | k System Scripts            | 171 |

|   | <b>C</b> .1 | Main Execution Script       | 171 |

|   | C.2         | Create Configuration File   | 176 |

|   | C.3         | Create Batch Job            | 176 |

| D  | Hawk Execution Time |                 |     |  |  |  |

|----|---------------------|-----------------|-----|--|--|--|

|    | D.1                 | Block Size: 576 | 180 |  |  |  |

|    | D.2                 | Block Size: 640 | 181 |  |  |  |

| Bi | Bibliography        |                 |     |  |  |  |

## **List of Publications**

The work described in this thesis is partially based on the following publication [6].

I. Al-Kharusi and D. W. Walker (2019). Locality properties of 3D data orderings with application to parallel molecular dynamics simulations. *The International Journal of High Performance Computing Applications*. https://doi.org/ 10.1177/1094342019846282.

# **List of Figures**

| 1.1 | Simple example of 3-dimensional array with approximately spherical                                                                                                                                                                                         |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | stencil, and its representation in memory                                                                                                                                                                                                                  | 4  |

| 2.1 | High level logical presentation of memory hierarchy                                                                                                                                                                                                        | 14 |

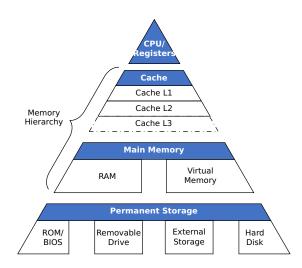

| 2.2 | Each of of the Hilbert orders $(h_1, h_2, \text{ and } h_3)$ is constructed based on<br>the predecessor pattern $(h_{n-1})$ that is manipulated based on the defined<br>operations in Table 2.1. The curve continuity feature connects all the             |    |

|     | points within the defined Hilbert size                                                                                                                                                                                                                     | 22 |

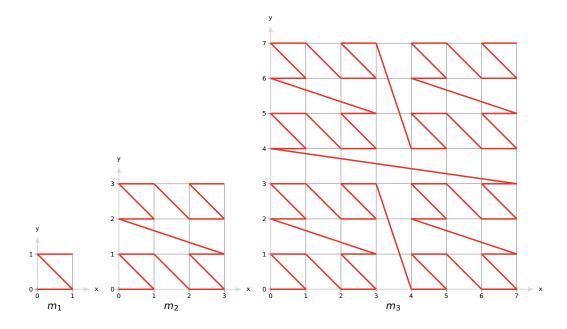

| 2.3 | Each of the Morton orderings $(m_1, m_2, \text{ and } m_3)$ is constructed based on<br>the predecessor pattern $(m_{n-1})$ that is manipulated based on the defined<br>operations in Table 2.2                                                             | 23 |

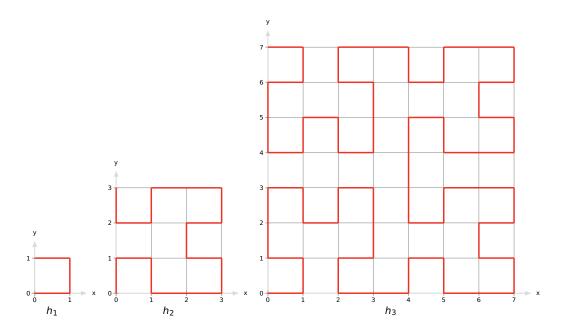

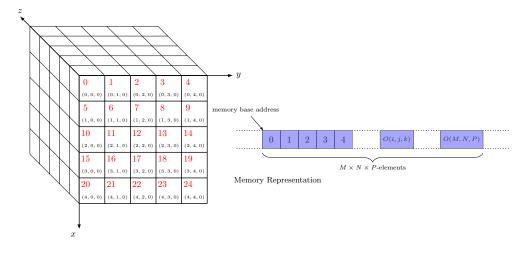

| 2.4 | Example of 3-dimensional array labelling and memory representation.<br>In this case, $M = N = P = 5$ , and $0 \le i, j, k < 5$                                                                                                                             | 27 |

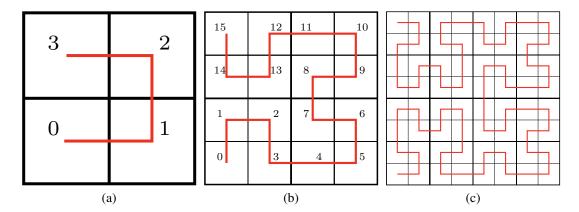

| 2.5 | (a), (b), and (c) are examples for Hilbert curves generated for orders $n = 1, n =$ , and $n = 3$ , respectively, and the number of labels is $4^n$ .                                                                                                      | 28 |

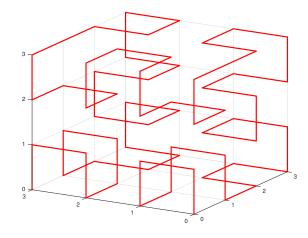

| 2.6 | Three-dimensional Hilbert ordering for a $4 \times 4 \times 4$ array. The index,<br><i>b</i> , increases by 1 each time the red path passes from one location to<br>another, starting with index 0 at $(0, 0, 0)$ and ending with index 63 at<br>(3, 0, 0) | 31 |

|     | (3, 0, 0)                                                                                                                                                                                                                                                  | 51 |

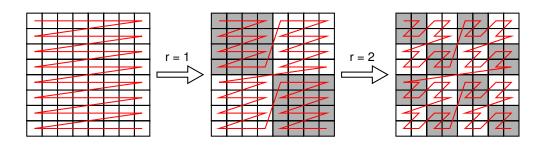

| 2.7  | The left-hand part of the figures is the original $M \times M$ array. The middle   |    |

|------|------------------------------------------------------------------------------------|----|

|      | part shows the result of Morton ordering to level $r = 1$ . The right-hand         |    |

|      | part of the figure shows the Morton ordering to level $r = 2$ . In each            |    |

|      | recursion, the size of sub-array is $M/2^r \times M/2^r$ as shown by the shading   |    |

|      | which highlights the division into sub-arrays. Each square is labelled             |    |

|      | starting from the top left corner until the end of the bottom right corner         | 33 |

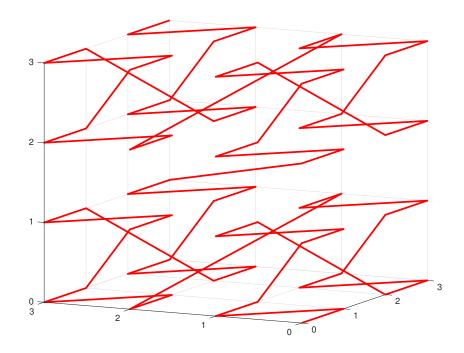

| 2.8  | Three-dimensional Morton ordering for a $4 \times 4 \times 4$ array. The index,    |    |

|      | b, increases by 1 each time the red path passes from one location to               |    |

|      | another, starting with index 0 at $(0, 0, 0)$ and ending with index 63 at          |    |

|      | (3,3,3)                                                                            | 33 |

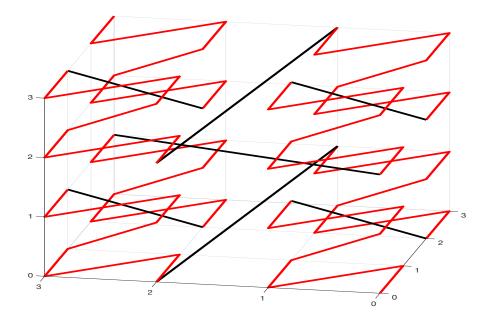

| 2.9  | Three-dimensional hybrid ordering by row-major and Morton for a                    |    |

|      | $4 \times 4 \times 4$ array. In this example, $t = 1$ and $m = 2$ . Each sub-array |    |

|      | consists of $2^{3t}$ items ordered by row-major, presented by the red line.        |    |

|      | The sub-arrays are ordered by Morton ordering and sorted according                 |    |

|      | to the black line path                                                             | 35 |

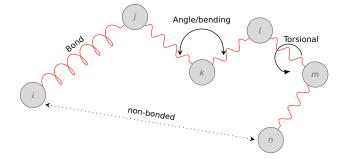

| 2.10 | Graphical illustration of interaction forces.                                      | 38 |

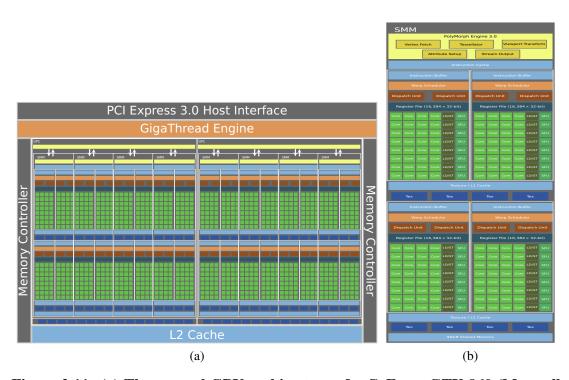

| 2.11 | (a) The general GPU architecture of a GeForce GTX 960 (Maxwell                     |    |

|      | GM206). It shows two GPCs, 8 SMMs where there are two in each                      |    |

|      | sub-unit. L2 Cache is shared by all SMMs, and one gigathread engine                |    |

|      | controls and manages the distribution of computations between SMMs.                |    |

|      | (b) Shows the components of each of the streaming processors [35,                  |    |

|      | 152]                                                                               | 48 |

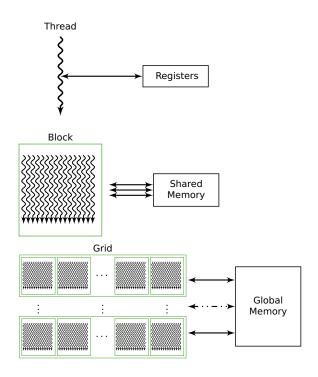

| 2.12 | Memory hierarchy sharing level with threads, blocks and grid, from                 |    |

|      | top left to right                                                                  | 51 |

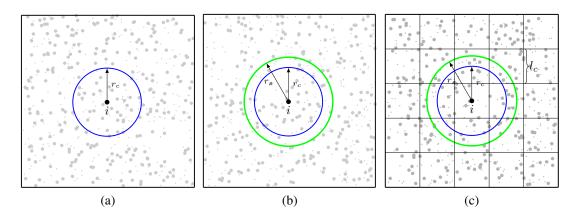

| 3.1 | (a) shows the neighbouring particles that are within the cut-off distance                                                                        |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | $r_c$ . The neighbour list must be modified every time step as a particle                                                                        |    |

|     | might move across the perimeter of the circle; (b) shows the search                                                                              |    |

|     | radius (skin radius) as introduced by Verlet; and (c) shows the linked-                                                                          |    |

|     | cells obtained by dividing the simulation box cells with edges of length                                                                         |    |

|     | $l_c = r_c \ldots \ldots$ | 71 |

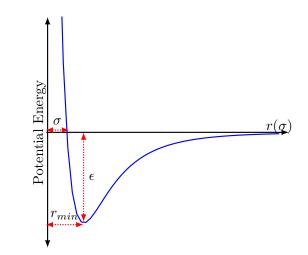

| 3.2 | Example of LJ curve generated with $\epsilon = 157$ , $\sigma = 3.9$ and incremental                                                             |    |

|     | time 0.124. $r_{min}$ is the distance where the potential reaches the equilib-                                                                   |    |

|     | rium position of the two particles                                                                                                               | 73 |

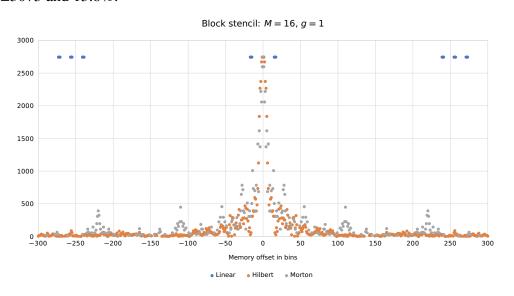

| 4.1 | Memory offsets for a block stencil with $g = 1$                                                                                                  | 87 |

| 4.2 | Accumulated memory offsets in bins for a block stencil with $M = 16$                                                                             |    |

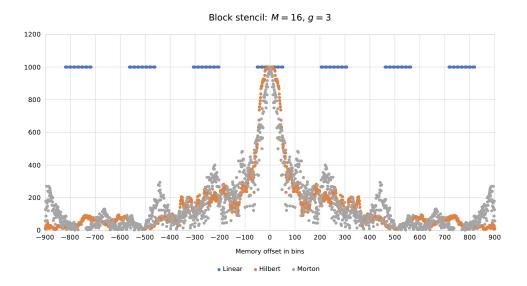

|     | and $g = 1$                                                                                                                                      | 88 |

| 4.3 | Accumulated memory offsets in bins for a block stencil with $M = 16$                                                                             |    |

|     | and $g = 3$                                                                                                                                      | 88 |

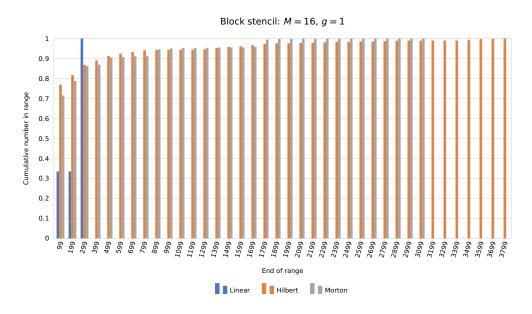

| 4.4 | Cumulative fraction of bins within a given memory offset for a block                                                                             |    |

|     | stencil with $g = 1$ and an array with $M = 16$ . For each set of bars the                                                                       |    |

|     | range is from 0 up to the x-axis label                                                                                                           | 90 |

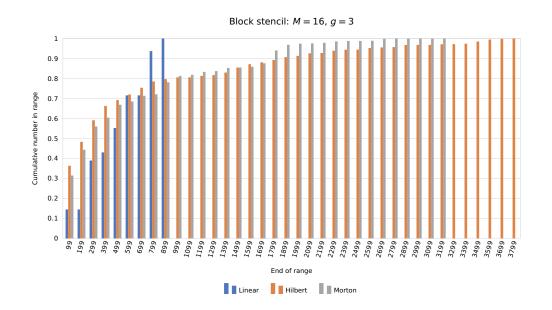

| 4.5 | Cumulative fraction of bins within a given memory offset for a block                                                                             |    |

|     | stencil with $g = 3$ and an array with $M = 16$ . For each set of bars the                                                                       |    |

|     | range is from 0 up to the x-axis label                                                                                                           | 90 |

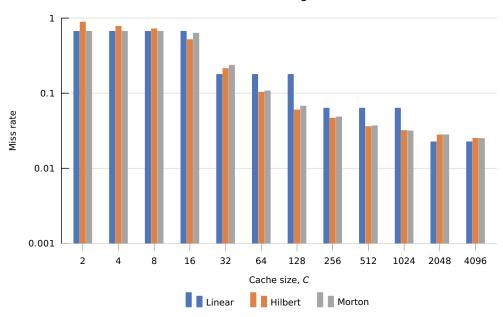

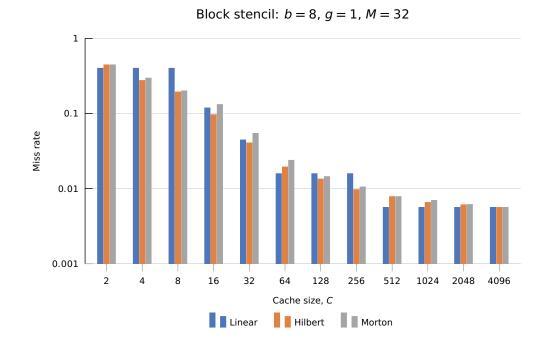

| 4.6 | Miss rate as a function of cache size, $c$ , for a block stencil with $g = 1$ ,                                                                  |    |

|     | an $M = 32$ array, and a cache block size of $b = 2$ bins $\ldots \ldots$                                                                        | 94 |

| 4.7 | Miss rate as a function of cache size, $c$ , for a block stencil with $g = 1$ ,                                                                  |    |

|     | an $M = 32$ array, and a cache block size of $b = 8$ bins                                                                                        | 95 |

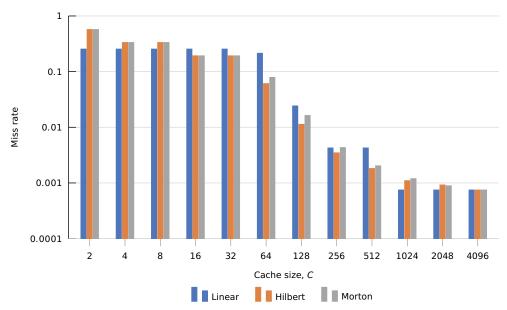

| 4.8 | Miss rate as a function of cache size, $c$ , for an approximately spherical                                                                      |    |

|     | stencil with $g = 3$ , an $M = 32$ array, and a cache block size of $b = 8$ bins                                                                 | 96 |

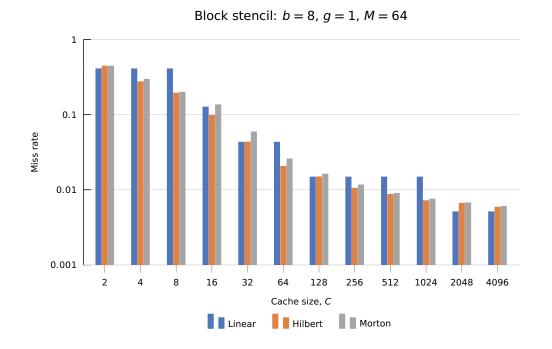

| 4.9 | Miss rate as a function of cache size, $c$ , for a block stencil with $g = 1$ , |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | an $M = 64$ array, and a cache block size of $b = 8$ bins $\ldots$ $\ldots$     | 96  |

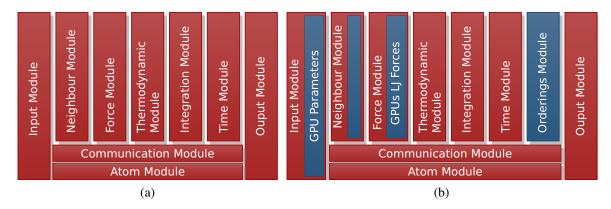

| 5.1 | MiniMD before the modifications (a) and after the modifications (b)             | 112 |

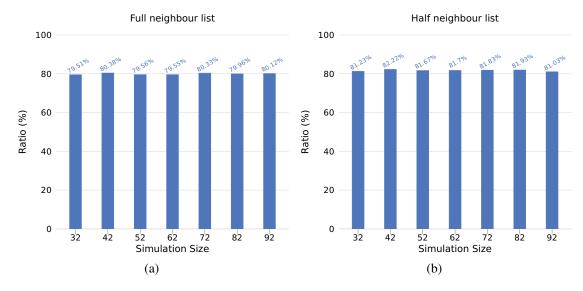

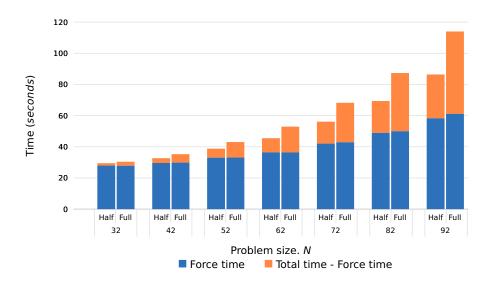

| 6.1 | (a) and (b) shows that the force computation for both the full and half         |     |

|     | neighbour list cases is about 80% of the overall simulation time, re-           |     |

|     | gardless of the simulation size                                                 | 132 |

| 6.2 | Ruthenium,full neighbour list case: time to execute one time step of            |     |

|     | the force computation on the CPU                                                | 133 |

| 6.3 | Ruthenium, half neighbour list case: time to execute one time step of           |     |

|     | the force computation on the CPU                                                | 133 |

| 6.4 | Ruthenium: dependency of total execution time and theoretical occu-             |     |

|     | pancy for different thread block configurations for the full (a) and half       |     |

|     | (b) neighbour list cases. The problem size is N=92 $\ldots \ldots \ldots$       | 135 |

| 6.5 | Hawk: dependency of total execution time and theoretical occupancy              |     |

|     | for different thread block configurations for the full (a) and half (b)         |     |

|     | neighbour list cases. The problem size is N=92                                  | 136 |

| 6.6 | Total simulation time and force computation time for the CPU imple-             |     |

|     | mentation on Ruthenium, accumulated over the first 100 time steps,              |     |

|     | for different problem sizes, $N$ . Times are shown for the half and full        |     |

|     | neighbour list algorithms. Note the total height of each column is the          |     |

|     | total time for the simulation                                                   | 137 |

| 6.7 | Total simulation time and force computation time for the GPU imple-             |     |

|     | mentation on Ruthenium with 1024 threads per block, accumulated                 |     |

|     | over the first 100 time steps, for different problem sizes, $N$ . Times are     |     |

|     | shown for the half and full neighbour list algorithms. Note the total           |     |

|     | height of each column is the total time for the simulation                      | 137 |

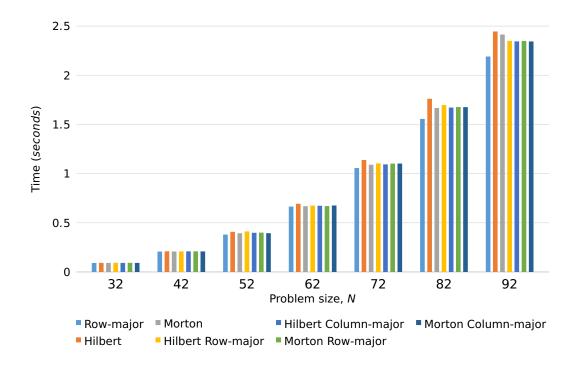

| 6.8  | Ruthenium, full neighbour list case. Time for execution of force com-         |     |

|------|-------------------------------------------------------------------------------|-----|

|      | putation kernel on the GPU for one time step                                  | 140 |

| 6.9  | Ruthenium, half neighbour list algorithm. Time for execution of force         |     |

|      | computation kernel on the GPU for one time step                               | 141 |

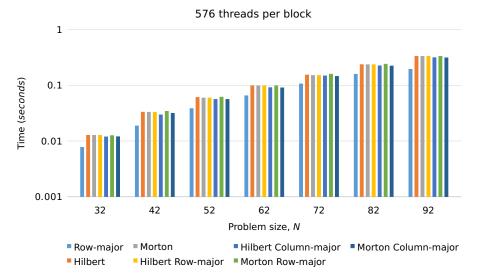

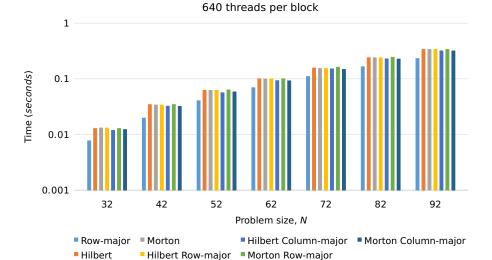

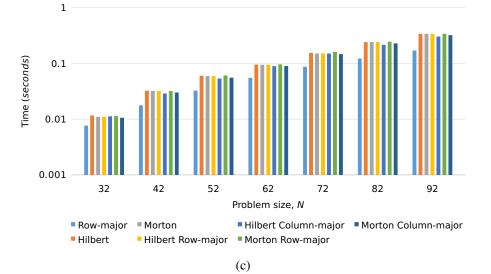

| 6.10 | Hawk: time for execution of force computation kernel on the GPU for           |     |

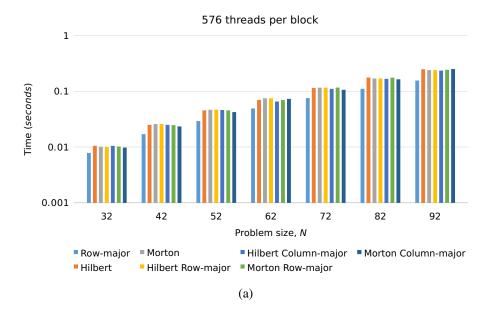

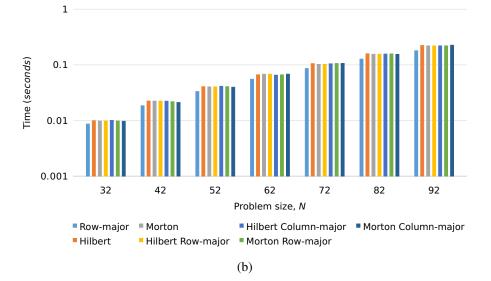

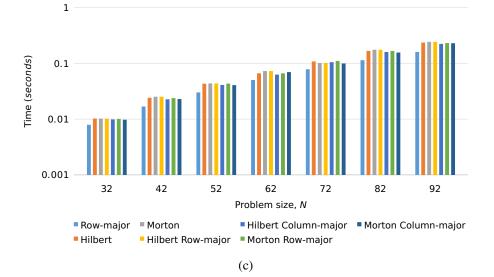

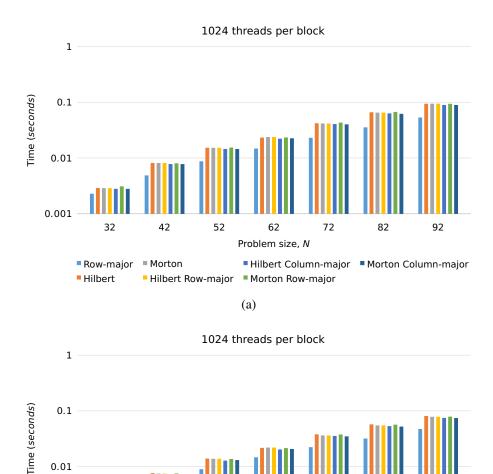

|      | one time step in the full (upper) and half (lower) neighbour list cases .     | 143 |

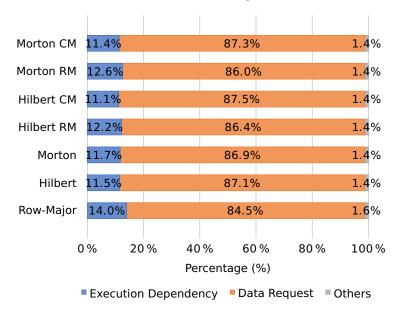

| 6.11 | Ruthenium, full neighbour list case. Output from <i>nvprof</i> giving the     |     |

|      | cause of warp stalling in the force computation kernel using the differ-      |     |

|      | ent orderings                                                                 | 146 |

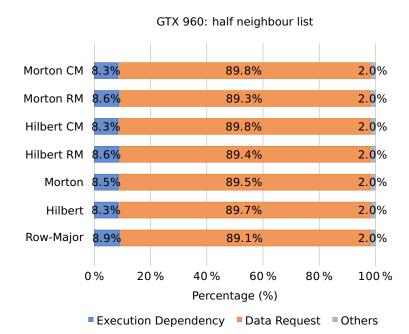

| 6.12 | Ruthenium, half neighbour list case. Output from <i>nvprof</i> giving the     |     |

|      | cause of warp stalling in the force computation kernel using the differ-      |     |

|      | ent orderings                                                                 | 146 |

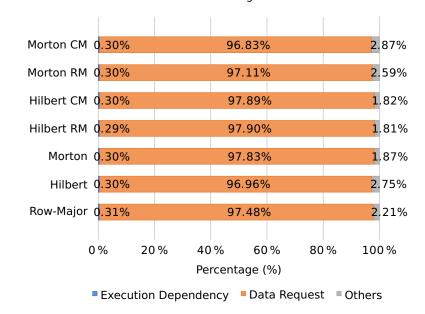

| 6.13 | Hawk: full neighbour list case. Output from <i>nvprof</i> giving the cause of |     |

| 0.12 | warp stalling in the force computation kernel using the different orderings   | 147 |

|      | warp starting in the force computation kerner using the different orderings   | 117 |

| 6.14 | Hawk, half neighbour list case. Output from <i>nvprof</i> giving the cause of |     |

|      | warp stalling in the force computation kernel using the different orderings   | 148 |

| 6.15 | Ruthenium: warp execution and branch efficiency for the full (a) and          |     |

|      | half (b) neighbour list algorithms                                            | 149 |

| 6.16 | Hawk: warp execution and branch efficiency for the full (a) and half          |     |

| 0110 | -                                                                             | 150 |

|      |                                                                               | 150 |

| 6.17 | Ruthenium: the percentages of divergent branches and control flow             |     |

|      | divergence warp execution and branch efficiency for the full (a) and          |     |

|      | half (b) neighbour list algorithms. Note, low percentage is more efficient    | 151 |

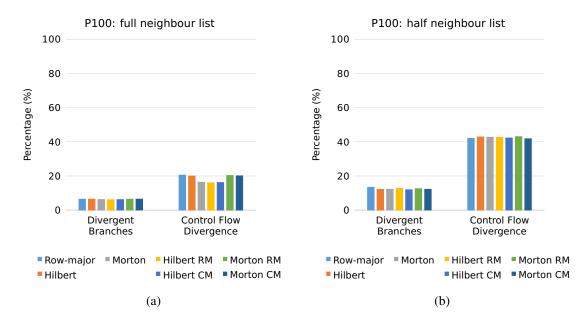

| 6.18 | Hawk: the percentages of divergent branches and control flow diver-           |     |

|      | gence warp execution and branch efficiency for the full (a) and half (b)      |     |

|      | neighbour list algorithms.Note, low percentage is more efficient              | 151 |

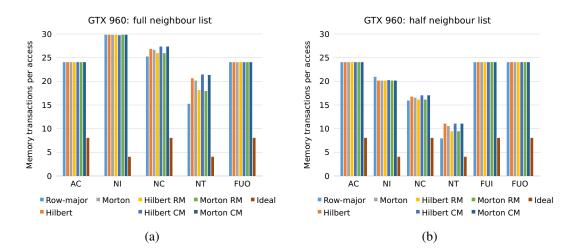

| 6.19 | Ruthenium: number of memory transactions per access for the full (a)         |      |

|------|------------------------------------------------------------------------------|------|

|      | and half (b) neighbour list algorithms                                       | 153  |

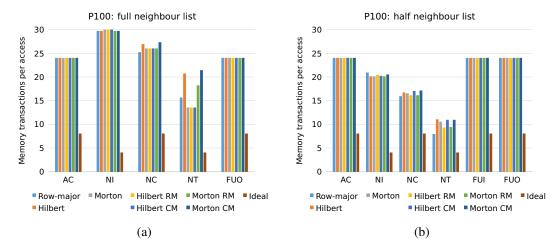

| 6.20 | Hawk: number of memory transactions per access for the full (a) and          |      |

|      | half (b) neighbour list algorithms                                           | 154  |

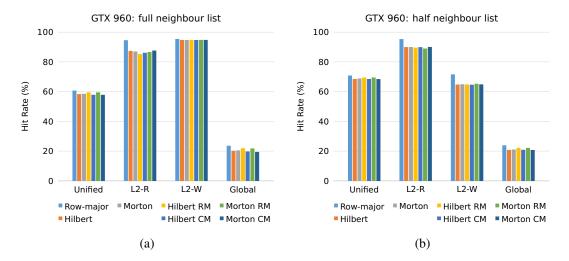

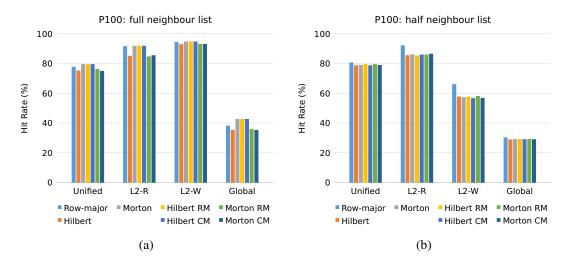

| 6.21 | Ruthenium: cache hit rate for the full (a) and half (b) neighbour list       |      |

|      | algorithms                                                                   | 155  |

| 6.22 | Hawk: cache hit rate for the full (a) and half (b) neighbour list algorithms | s156 |

| B.1  | The generated experiments for each data ordering, and with 100 and           |      |

|      | 1100 time steps                                                              | 169  |

| B.2  | The generated experiments for each data ordering, and with 100 and           |      |

|      | 1100 time steps                                                              | 170  |

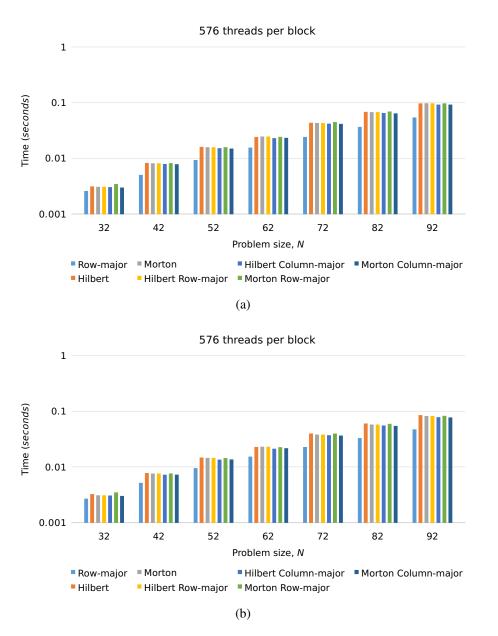

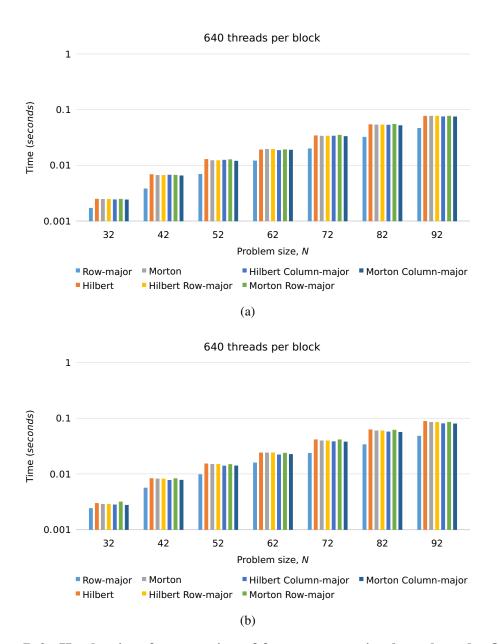

| D.1  | Hawk: time for execution of force computation kernel on the GPU for          |      |

|      | one time step in the full (upper) and half (lower) neighbour list cases      | 180  |

| D.2  | Hawk: time for execution of force computation kernel on the GPU for          |      |

|      | one time step in the full (upper) and half (lower) neighbour list cases      | 181  |

# **List of Tables**

| 2.1 | Construction of Hilbert curve $h_n$ based on previous $h_{n-1}$ curve where   |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | the edge length is maintained constant (without scaling down the next         |     |

|     | level to fit the area of previous level). The last point in each of the first |     |

|     | 3 component parts is then connected to the first point of the next part .     | 20  |

| 2.2 | Morton geometrical operations for constructing $m_n$ based on the previ-      |     |

|     | ous $m_{n-1}$ pattern                                                         | 22  |

| 2.3 | Meaning of the symbols in the rewrite rule for a 3D Hilbert curve             | 30  |

| 2.4 | Examples of the relation between the number of elements within each           |     |

|     | sub-block, that are ordered using row-major, and the number of sub-           |     |

|     | blocks that are ordered using Morton-ordering. Note, if $m - t = 0$ ,         |     |

|     | there will be only one block for which the elements are ordered using         |     |

|     | row-major ordering                                                            | 35  |

| 4.1 | Number of bins and the percentage deviation from sphericity                   | 85  |

| 5.1 | Key run settings that can be used to set the program execution                | 101 |

| 5.2 | Sample of definition of various simulation parameters in LJ units             | 102 |

| 5.3 | Different orderings that are supported by the ordering module                 | 113 |

| 6.1 | Ruthenium and Hawk specifications.                                                                                                                 | 128 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2 | GPU specification for Ruthenium and Hawk                                                                                                           | 129 |

| 6.3 | Various variables of our experiments                                                                                                               | 130 |

| 6.4 | Ruthenium: ratio of CPU to GPU execution time for the force compu-<br>tation. In the GPU computation there are 1024 threads per block              | 138 |

| 6.5 | Number of active cycles and percentage of active warps that are eli-<br>gible per active cycle, for $N = 92$ and 1024 threads per block. Ruthenium |     |

|     | (upper) and Hawk (lower)                                                                                                                           | 145 |

# **List of Algorithms**

| 3.1 | Before Loop Fusion                                                                                                                                                                                            | 59 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | After Loop Fusion                                                                                                                                                                                             | 59 |

| 3.3 | Before Loop Interchange                                                                                                                                                                                       | 60 |

| 3.4 | After Loop Interchange                                                                                                                                                                                        | 60 |

| 3.5 | Before Loop Skewing                                                                                                                                                                                           | 60 |

| 3.6 | After Loop Skewing                                                                                                                                                                                            | 60 |

| 3.7 | After Strip Mining                                                                                                                                                                                            | 61 |

| 4.1 | distHistogram: high level of the histogram distances computation. The functions path2RMO and RMO2path convert between a location in the ordering and the row-major index.                                     | 87 |

| 4.2 | cacheModel: high level view of the cache model. The functions path2RMO<br>and RMO2path convert between a location in the ordering and the row-<br>major index.                                                | 92 |

| 4.3 | inBlock: check if the bin exists witin the block or not                                                                                                                                                       | 92 |

| 4.4 | inCache: check if the bin exists in any of the blocks within the cache by calling inBlock method. If the bin exist, modify the recent used bin to the last accessed bin and increment number of cache misses. | 93 |

|     |                                                                                                                                                                                                               | 15 |

| 4.5 | addToCache: insert the <i>jbin</i> in the block with the <i>jspace</i> index and then |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | modify the corresponding indices (firstBin, lastUsed and nblocks) to                  |     |

|     | track the insertion and removal of the bins.                                          | 93  |

| 5.1 | pbc: forces all the particles to be within the simulation box                         | 104 |

| 5.2 | buildStencil: the algorithm used to build and generate the stencil                    |     |

|     | array. It takes into consideration the full or half neighbour-list configur-          |     |

|     | ation as the number of elements can be reduced by half compared to the                |     |

|     | full neighbour-list. binDistance returns the distance from the central                |     |

|     | bin to the bin $(i, j, k)$ .                                                          | 105 |

| 5.3 | compFullNeigh: shows the computation for full neighbour list of the                   |     |

|     | interaction forces and the potential energy. In a multithreading imple-               |     |

|     | mentation an Atomic region is defined to ensure there is no race condi-               |     |

|     | tion among the threads. This algorithm is optimized for MPI and Open-                 |     |

|     | MPI (threading)                                                                       | 108 |

| 5.4 | run: the main function to run the MD simulation by calling appropriate                |     |

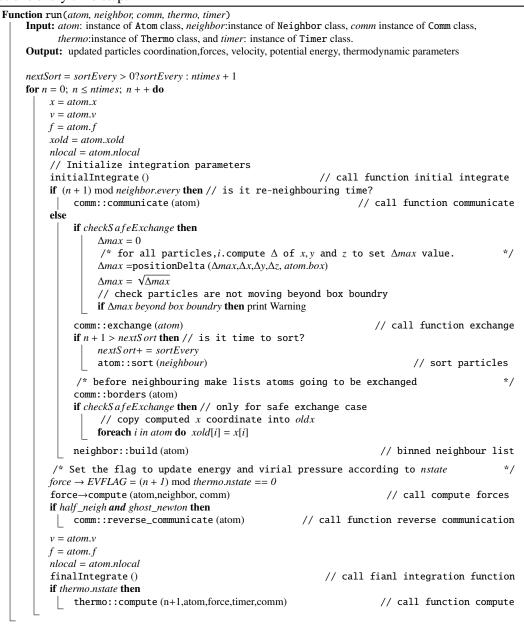

|     | functions every time step.                                                            | 110 |

| 5.5 | setRowMajor: generates ostore and invstore arrays for a row-major or-                 |     |

|     | dering. $nbins = N \times N \times N$ is the total number of bins                     | 114 |

| 5.6 | hilbert3D: generates Hilbert number $h$ and curve points $(px, py, pz)$ which         |     |

|     | are advanced according to Algorithm 5.7                                               | 115 |

| 5.7 | hilbert3D: updates points to move to the next location according to the               |     |

|     | orientation matrix.                                                                   | 115 |

| 5.8 | morton3D: Translates the row major index into the Morton label                        | 116 |

| 5.9 | morton3D: Using bit manipulation to dilate the input value in 3D                      | 116 |

| 5.10 | setHybridHilbertRM: generates hybrid Hilbert and row-major order-           |       |

|------|-----------------------------------------------------------------------------|-------|

|      | ing and the array inverse values                                            | 117   |

| 5.11 | setHybridMortonRM: generates hybrid Morton and row-major order-             |       |

|      | ing by using the dilate3D function that is used for Morton ordering         | 118   |

| 5.12 | cudaLJForceCompute: prepares the required parameters and copies             |       |

|      | the data between host and device and vice versa. The function records       |       |

|      | the time taken by devHalfNeigh or devFullNeigh                              | 120   |

| 5.13 | devFullNeigh: shows the computation for the full neighbour list case        |       |

|      | of the interaction forces and the potential energy. A potential race condi- |       |

|      | tion for potential energy and virial pressure is avoided using the cudaAtom | icAdd |

|      | function.                                                                   | 122   |

| 5.14 | devHalfNeigh: computing the inter-particle forces in the half neigh-        |       |

|      | bour list case.                                                             | 124   |

## **List of Acronyms**

- ASIC Application-Specific Integrated Circuit

- AVL Georgy Adelson-Velsky and Evgenii Landis

- **BLAS** Basic Linear Algebra Subprograms

- CUDA Compute Unified Device Architecture

- **DEM** Discrete Element Method

- **DMA** Direct Memory Access

- DNA Deoxyribonucleic Acid

- **DRAM** Dynamic Random Access Memory

- EAM Embedded-Atom Method

- FAST Fast Architecture Sensitive Tree

- FFT Fast Fourier Transform

- FMM Fast Multipole Method

- GPU Graphical Processing Unit

- HCP Hierarchical Charge Partitioning

- **HPC** High Performance Computing

| LJ Lennard Jones                         |

|------------------------------------------|

| LRU Least Recent Used                    |

| MDS Molecular Dynamics Simulation        |

| MKSA Metre, Kilogram Second, Ampere      |

| MPI Message Passing Interface            |

| MSM Multilevel Summation Method          |

| OpenCL Open Computing Language           |

| <b>OpenMP</b> Open Multi-Processing      |

| PBC Periodicity Boundary Condition       |

| PME Particle Mesh Ewald                  |

| SIMD Single Instruction Multiple Data    |

| SIMT Single Instruction Multiple Threads |

| SFC Space Filling Curve                  |

TLB Translation Lookaside Buffer

### **Chapter 1**

### Introduction

The exploitation of data locality and performance engineering are important issues in compiler and algorithm design where the aim is to fully exploit device architectures, especially in multicore/manycore systems, within the context of complex memory hierarchies governed by various rules and policies. This thesis investigates the data locality properties of our graphical processing unit (GPU) implementation of a molecular dynamics simulation. Different orderings of the particle data are investigated and compared in terms of observed performance and profiling data, and these results are interpreted in terms of the software and hardware features of the GPUs studied. To the best of our knowledge, this study has not been conducted before. In this study we approach the problem of data locality of molecular dynamics simulations on GPUs using execution time and a number of profiling measurements, especially those related to GPU execution efficiency and memory access.

### **1.1** Overview

Alongside the advances in computer architectures, processor speeds, and main memory, the efficient use of various levels of cache and other specialized memories remains essential to achieving high computation efficiency. Therefore, for scientific applications where execution time is critical, understanding the data locality properties of the application, and the execution platform, can enhance application performance through the optimal use of the execution platform. This is particularly true in GPUs where latency tolerance techniques based on the scheduling of threads are used to mask the disparity between the bandwidth to global memory and the GPU's peak execution speed. For example, for an NVidia P100 system, the global memory bandwidth is a maximum of 732 GB/s and the peak single-precision [4] performance is 9.3 Tflop/s. Thus, in the absence of latency tolerance, the expected execution speed is 732G/4 Gflop/s, where *G* is the number of floating-point operations per global memory access and floats are assumed to be 4 bytes. For G = 1, this is a factor of 50 less than the peak performance.

Data locality[112, p. 374] is a significant factor in the efficient use of hierarchical memory. When one item is moved from a lower level of memory to a higher level, other items that are nearby in memory are also moved along with it as the data are copied in blocks of fixed size, known as cache lines, rather than as individual elements. Most applications and computations are local in nature, so if items are stored in memory based on their location, when one item is moved from low-level memory into a higher level of memory, the other items upon which its processing depends will also be moved, and consecutively loaded instructions will process the consecutive data, thereby exploiting *spatial data locality* and improving performance. Likewise, data that is already in the higher level memory can be processed by the same or different instructions. This situation illustrates *temporal data locality*, where better performance is achieved by repeatedly accessing data while it is held in the higher levels of the memory hierarchy.

Space filling curves [17, 123], have recently been adopted in various applications to enhance computation through data ordering. A number of orderings based on space filling curves have been identified whose properties lead to variations in computation performance. Their property of grouping related data into virtual blocks means that the elements of a block can be held together in high level memory, if the block size is aligned with the size of the high level cache. In addition, processing data along the path of a space filling curve has a high potential for spatial and temporal data locality as the data elements are stored in consecutively in memory and elements are located within the virtual block close to other data elements upon which their processing depends.

Molecular dynamics simulation (MDS) is a useful tool that uses a deterministic approach to simulate a molecular system by following the movement of particles and their status at each time step of the simulation. The interaction forces and potential energy of a molecular system depend on the adopted numerical model. In this research the Lennard-Jones model [47, 72] is used to compute particle interactions, and deciding which particles interact is a compute-intensive task that depends on the distance between particles. In the Lennard-Jones model, particles that are sufficiently far apart do not interact. However, particles that are closer may interact, and each particle has a set of neighbouring particles with which it potentially interacts. Only computing the interactions with these neighbouring particles reduces the computational complexity for the inter-particle force computation.

GPUs have a complex memory architecture and a high level of dependency between the hardware components. In addition, the application programmer has little direct control over the scheduling of threads or the movement of data between levels in the memory hierarchy. Therefore, application programmers are encouraged to follow best practices in programming style that coerce the compiler and the runtime system into running code efficiently, resulting in optimal utilization of the system architecture. NVIDIA graphics cards and the CUDA programming language are used in this study. CUDA is highly compatible with NVIDIA GPUs, as they are provided by the same vendor, which can result in high computation performance. In addition, NVIDIA profiling tools enable us to investigate the relation between the data locality properties of MDS applications and the ordering of particles in the GPU implementation.

## **1.2 Problem Definition**

The allocation of data in memory, the degree of dependency between different memory locations, and the movement of data across the memory hierarchy, significantly af-

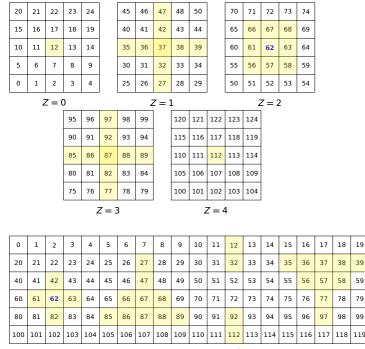

fects application performance. In MDS applications, the generation of the neighbour lists (discussed in 2) engenders a high degree of data dependency. The ordering of the particles is based on which spatial bin they are located in, and in turn these bins usually have a row-major ordering. For example, Fig. 1.1 represents a simple 3-dimensional array of size  $5 \times 5 \times 5 \times 5$  and an approximately spherical stencil of width 5 (for simplicity). The yellow shading shows the bins that the bin with index 62 interacts with for this stencil. The lower part of the figure shows how these bins are scattered in the memory, and this scattering can degrade application performance because data are fetched from the memory hierarchy in blocks. Consequently irrelevant data will also be fetched and a larger number of memory accesses will be required to fetch the data, compared with the case of consecutive data. Consecutive data have a high likelihood of being loaded by one memory access, subject to other factors, as explained in Chapter 2, such as cache size, cache line size, and the caching policies.

# Figure 1.1: Simple example of 3-dimensional array with approximately spherical stencil, and its representation in memory.

A limited number of research works have addressed the data locality properties of MDS

and most previous studies have focused primarily on reducing the number of neighbour list particles to make it, as close as possible, the same as the actual interaction list, as will be seen in Chapter 3. Exploring the data locality properties of MDS enables deeper understanding of the MDS computations and optimises their performance. In addition, different data ordering have different characteristics that distinguish them. Thus, their adoption lead, to differences in performance indicators in terms of execution time and memory hierarchy utilization. This type of research can then be applied to different types of application that might have different types of data dependency relationships. Data locality properties also have a high dependency on the memory hierarchy architecture, and therefore conducting this study on GPU architectures will examine the approach to analysing various data orderings and their utilization of the memory hierarchy.

Therefore, in this research, we will answer the following research questions:

- What is the impact of different computation stencils on the data locality properties of MDS applications?

- What is the impact of data locality on MDS applications implemented on GPUs?

- Do space filling curves (SFC) have better data locality properties compared with conventional row-major orderings?

- How should data locality and performance analysis be conducted for GPUs?

## 1.3 Hypothesis

Increases in processor speed have not been accompanied by a commensurate increase in memory speed. Therefore, to exploit a processor's capabilities, the various levels in the memory hierarchy must be efficiently utilized. Therefore, it is hypothesised that data locality enhancements in an application lower the cost of data movement across the memory hierarchy of a GPU by optimising data reuse in the higher levels of memory. This increases the likelihood of finding data in the first or the second level of cache, which, in turn, reduces the latency of global memory accesses. Molecular dynamics simulations have strong data dependencies as the force computation for a particle depends on its neighbouring particles. Therefore, we study the properties of various data orderings in the context of a molecular dynamics simulation on GPUs to investigate the optimal data ordering for this type of application.

## 1.4 Aims and Objectives

The main aim of this thesis is to present the relationship between different data orderings and computation stencils, and their performance in molecular dynamics simulations. It aims to provide a detailed analysis of the spatial and temporal data locality properties for each of the adopted orderings. The efficiency of an ordering is not only measured by the runtime of the application, but also by the properties of the stencil used, and a detailed analysis of the memory profile. In doing this, the aim is to increase knowledge of the data locality properties of molecular dynamics simulations on GPU platforms.

In order to achieve our aims we conducted the followings:

- The implementation of the space filling curves data orderings.

- The implementation of the cache model to explore the data locality of the implemented data orderings. This includes the analysis of the cubic and approximate spherical relationship with implemented different orderings.

- GPU version of the Lennared Jones implementation and conducting the required modification to the MiniMD version integrated with space filling curves data orderings.

- Executing the applications in two different GPUs and with various configurations and simulation's sizes.

- NVIDIA profiler is adopted for memory profiling and caompred with cache model results.

## **1.5** Thesis Contributions

The main contributions presented by this thesis are:

- The data locality properties for different orderings have been studied from three perspectives: the relation between a data ordering and an adopted stencil; the execution time of the force kernel on GPUs; and, memory profiling using the NVIDIA *nvprof* profiler. Most of the previous literature (as will be seen in Chapter 3) does not considered all these prespectives and they are limited to the execution time analysis. In regards to the GPU implementation and analysis they did not utilize NVIDIA profiler. The relation between the stencil and data orderings is not only valid for MDS applications but can be adopted for other applications. Different stencils have a different relationship with each of the adopted data orderings which requires to modify slightly our cache model.

- A GPU implementation of the Lennard-Jones force computation using CUDA, without introducing complex data structures to ensure the alignment with the original CPU version of the miniMD application. This principle enables a fair comparison between the CPU and GPU implementations. A number of literature adopted tree-based data structures which introduces additional overhead cost. In our implementation the modifications to any of the adopted data orderings are of  $cost O(\infty)$ .

- To the best of our knowledge, this is the first research which has been conducted into the data locality properties of molecular dynamics simulations, especially

for Lennard-Jones force computations on GPUs. The implemented cache model and NVIDIA profiler with the adopted orderings have not been covered by any previous literature. Thus, this will provide good understanding of MDS data locality in GPU by using different data orderings.

- To the best of our knowledge, this is the first GPU profiling study for the Lennard-Jones case to analyse the use of various levels in the GPU memory hierarchy. The adoption of NVIDA profiler is not only shows how to utilize such tool as part of MDS tool or any other applications but also to confirm the cache model analysis and the experiments results how they are aligned.

- This work also acts as a framework for investigating the data localities of other applications that cannot be readily tiled/blocked as independent data. The approach adopted in this research can be adopted as guideline to conduct performance analysis not only for MDS applications but with any other similiar applications that are implemented within GPU.

## **1.6 Thesis Structure**

In this multi-disciplinary research, our thesis is structured as follows:

Chapter 2 introduces background knowledge with regard to the concepts that are used in the rest of this thesis. A general background to the concept of data locality is given, and issues and limitations are discussed in the context of a GPU implementation. Space-filling curves are explained in terms of their geometric and arithmetic representations. It also explains the different types of data orderings that are used in this research. The various orderings are: row-major, Hilbert, Morton, hybrid Hilbert, and hybrid Morton. Molecular dynamics simulations are introduced, and the main principles explained. The justification for using the Lennard-Jones force model in our computations is explained. This chapter also

provides details of the essential concepts and techniques surrounding the main principles of molecular dynamics simulations. Parallel implementation models, especially for general-purpose GPU architectures and programming models, are introduced. The GPU architecture and CUDA implementation are described in detail in order to understand the algorithm and the implementation chapter of this research. Finally, key factors in terms of optimization and performance analysis that need to be considered, and are adopted in this work, are identified.

- Chapter 3 presents a literature review conducted on all aspects of our study. It shows the research that has been carried out to optimize the data locality from the perspective of optimizing the computation and data order. The use of space filling curves for data ordering enhancements in various applications is explored. Data locality and optimization in molecular dynamics simulation studies conducted in this field are provided, especially in terms of their implementation on GPU platforms.

- Chapter 4 clarifies the relationship between data orderings and an approximately spherical stencil, which is widely adopted in various applications, especially in molecular dynamics simulations. In addition, a simple cache model is used to explore in detail the relation between our data orderings and the approximately spherical stencil.

- Chapter 5 provides an overview of the miniMD implementation that is used in our performance evaluations. Its various key modules and components are explained in detail, especially the Lennard-Jones force computation module, which is used as part of our research to evaluate the impact of various data orderings. Then we explain the implementation of our work and the modifications that have been incorporated into the original miniMD implementation. The force computation module for full and half neighbour list force computations on the GPU, and the ordering module, are the main modules that are described in this chapter.

- Chapter 6 describes all the various experiments, results and analysis that have

been conducted in our research. In this chapter, the hardware used for conducting this research is described in detail. In addition, all the setup of the various experiments, the simulation size, the data orderings, and the platforms used in each experiment are identified prior to the discussion of the experimental results.

• Chapter 7 concludes the thesis, linking the thesis contributions to the relevant chapters, and discussing this work's limitations and making recommendations for future work.

### 1.7 Summary

To sum up, our thesis is as follows: to study and analyse the data locality properties of various data orderings for a molecular dynamics application implemented on NVIDIA GPUs. In this chapter, an overview of our research and its hypothesis were briefly introduced, and the aims and objectives of this work were described. In addition, the research contributions and thesis structure were provided. The next chapter provides more detailed information on the problem addressed.

## Chapter 2

## Background

This chapter introduces essential background information about the concepts that are used in the rest of this work. First, the concept of data locality is introduced, together with its importance as one of the factors that impact computation efficiency. A general overview of data locality obstacles, issues, and limitations will be presented. Specifically, GPU data locality problems will be defined. Then, some of the solutions that have been introduced in this field will be considered, before further details are provided in the literature review (Chapter 3). After that, data orderings and their contribution to data locality will be briefly introduced. MDS will be outlined, and the reasons for performing a data locality study for an MDS application will be explored. A number of simulation tools that have been investigated will be introduced, and the reason for selecting miniMD in this dissertation will be explained. Introductory MDS works have been performed on GPU platforms to investigate the key factors in maximizing GPU utilization. Parallel computing is then broadly discussed, especially computation on GPUs, which is a central aspect of this work. NVIDIA GPUs have been selected in this work, and the reasons for this will be explained, together with their architecture and features.

## 2.1 Data Locality

Data locality, also known as the principle of locality, is the propensity for existing data in high-level memory to be accessed repetitively before being expelled to a lower level in the memory hierarchy. Two types of data locality are distinguished: spatial data locality and temporal data locality. Spatial data locality represents how the data are consecutively ordered in the memory such that consecutive instructions access a contiguous data set, or in a thread-based implementation, the same instruction is applied to consecutive blocks of data. This feature is based on the fact that the data are fetched from low level memory into a high level memory in contiguous blocks known as cache lines. This reduces the number of data fetches needed for each instruction. On the other hand, temporal data locality, also known as reuse data locality, refers to the repeated use of a specific data and/or resource by the same instructions that depend on the same single data item in a loop, or by other consecutive instructions that depend on the same data. As with spatial locality, a high degree of temporal data locality reduces the number of high latency requests for the same data from low-level memory, and as a result improves the overall application performance.

A brief background on the general cache architecture will be presented in order to identify the various memory components that affect computation performance. In addition, the next section will explore cache issues and identify various solutions, as well as how these could be enabled. Then, ways of enhancing data locality will be introduced, and related features and terminology will be discussed.

#### 2.1.1 Cache Architecture

Rapid advances in processors (CPUs) and media has accelerated the movement of data between different device components, and as a result has left hierarchical cache and memory components as a bottleneck for achieving high computational performance. The memory hierarchy varies from one architecture to another according to a number of

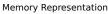

factors, such as the number of memory hierarchy levels, their size, the bandwidth and latency between levels, and the configuration policy that is applied. The top level of the memory hierarchy has the smallest, fastest, and most expensive memory per bit, while the largest, slowest, and cheapest memory per bit is at the bottom level [112, p. 12]. A memory hierarchy, as shown in Figure 2.1, is the simplest and most widely used way to evade the "memory wall" problem, defined by Wulf and McKee in [153]. For example, the recent Intel Coffee Lake architecture (for core i5/i7 8000 series processors) has six cores, each with an L1 instruction and data cache size of 32 KB, an L2 cache of 256 KB, and an L3 cache size of up to 2 MB per core (where the L3 cache is shared between the cores by a ring based connectivity [5, 8, 23]). Intel has announced that the size of all the caches will be doubled in the new Ice Lake microprocessor architecture, which is scheduled to be on the market in 2020 [9]. Another factor affecting cache performance is the cache replacement algorithm, also referred to as the cache policy. The most common policies are the Random, Least Recently Used (LRU), Partial LRU (PLRU), and Least Frequently Used (LFU) policies. Random replacement removes an arbitrary block to insert a new candidate block. It does not record any information about the request history, which is one of its advantages. LRU replaces the leastrecently accessed data in the cache with the new candidate, if the cache is full. This process is maintained by using an age-bit to ensure the discarded block is the leastrecently inserted or modified data. PLRU is an approximation for the LRU algorithm in which the access information is recorded by using a binary tree [73]. LFU records the number of accesses to each block in the cache and the block with the minimum number of accesses is discarded and replaced by the new block. Belady's algorithm is based on future data use, rather than on historical information, wherein the evicted data are those which are not going to be used in the next instructions [136]. These algorithms have trade-offs between miss rate and latency time as they have a high dependency on the associativity degree.

Associativity organizes the cache blocks into *S* sets, such that S = B/N where *B* and *N* are the total number of blocks and the degree of associativity, respectively. If the

Figure 2.1: High level logical presentation of memory hierarchy

number of sets equals the number of cache blocks (i.e., S = B), then this case is known as direct mapping. On the other hand, if the associativity is equal to the number of blocks, then it is called a fully-associative cache. Otherwise, it is known as an *N*-way associative cache [62, p. 482]. The advantage of this is to reduce the need to search the full cache and optimize the cache utilization. In the fully-associative cache case, a search for an address requires the full cache to be scanned. Thus, if the requested data is situated at the end of the cache, all the preceding cache lines must be checked to fetch the requested data, which results in a high latency. Thus, a higher degree of associativity comes with the cost of increasing access time [112, p. 77].

The Translation Lookaside Buffer (TLB) is another type of cache that is located in the memory management unit. The TLB records recent virtual or physical translated addresses and, therefore, it resides between the processor and cache, or between different caches levels, or between the CPU and main memory. Thus, an architecture may have multiple TLBs. For example, in the Coffee Lake microarchitecture [5] the L1 data and instruction caches each have a dedicated TLB, and another is provided for the L2 cache. In general, TLBs are fully associative as they are small, and TLB misses are costly. In addition, various types of register are part of the CPU, varying from architecture to architecture. Normally they are very limited in size, and have specific functionality.

#### 2.1.2 Types of Cache Miss

Having defined the memory hierarchy in a simple way, the different scenarios in which a cache does not fulfil a request will be described:

- A *compulsory miss* occurs the first time data in a block is requested starting with an empty cache. Therefore, the data is not yet loaded into the cache, and is not in the TLB either; nor is its value stored in any register. This is also known as a cold start miss. There is nothing that can be done to reduce the impact of this type of miss as the cache line and cache capacity are finite in size.

- A *capacity miss* occurs if the requested data or instruction is not available in the corresponding cache and the cache is full. Thus, this necessitates removing one of the cache lines currently in the cache according to the replacement policy and inserting the new cache line.

- A *conflict miss* occurs when many memory accesses are mapped to the same index set in a cache. The likelihood of a conflict miss increases with cache line size, since the number of blocks within the cache is large. A fully associative approach with a LRU replacement algorithm would eliminate conflict misses [76].

- A *coherence miss* results from being unable to maintain the consistency between various caches, especially in multiprocessing architectures and distributed systems [130]. For example, L3 caches are shared between the processors in the Coffee Lake architecture, as mentioned earlier. Thus, data coherency is essential to enable processors to load the recently updated data by any other processor. L3 data coherency, consequently introduces other issues, such as identifying the type of instruction accesses and preventing modification by different processors at the same time. Serialization and scheduling of processor modifications to mutually exclusive data requires a hardware and software implementation.

#### 2.1.3 Cache Use Optimizations

The memory hierarchy facilitates large data bandwidths by accessing multiple data items in blocks and reducing the memory latency by enabling independent parallel tasks between processors and various cache levels. However, there are still opportunities for optimising the use of cache in order to achieve high performance. Such optimisation could require specific hardware and/or software features to overcome the performance impact of cache misses. These can be categorized as: reducing the penalty incurred by a cache miss; minimizing the number of misses; and reducing the number of memory accesses [125].

The penalty of a cache miss refers to the cost in time during which a processor is stalled waiting for the completion of a memory access [73]. In this scenario, the solution is focused on hiding the latency of loading the data from main memory into cache. This can be done using a non-blocking (or lockup-free) cache that allows the processor to run the next instruction assuming that next execution cycle does not involve the current missed data. In fact, it can allow one miss or multiple misses known as "hit-under-miss" and "miss-under-miss", respectively. Therefore, this approach requires hardware and compiler-optimizations to handle all the missed addresses, their destinations and data dependencies, and to manage the data consistency due to various load and store misses, especially within the same cache line. Prefetching is another approach, where the data are loaded before they are needed. The prefetching might be triggered by hardware, or by an instruction, or by a combination of both. In general, software prefetching methods are based on the compiler's ability to analyse a program's behaviour and predict the required prefetching instruction as part of the program executable. On the other hand, hardware methods utilize spatial locality or the access pattern of the executed program dynamically (see [157] for a list of relevant hardware and software algorithms). One of the challenges for prefetching methods is to fill the pipeline with prefetched instructions rather than instructions ready for execution. In addition, prefetching methods may introduce too much overhead time.

The second factor is reducing the number of misses, which could be accomplished by increasing the cache size, or by increasing the number of levels in the memory hierarchy, or by using additional buffers between various levels. For example, Jouppi in [75] proposed introducing three types of cache between the L1 and L2 caches: the miss, victim, and stream caches. As discussed earlier, the replacement algorithm and degree of associativity, if supported by the hardware architecture, can be adapted according to the program benefits. In addition, compiler optimization is an essential component in reducing cache misses, and this will be discussed in more detail in the next chapter. A common compiler optimisation is to order the instructions to minimize cache misses and to reduce data swapping between cache memory and registers. In multithreading implementations, a competitive miss cache is one of the key concerns, especially within shared caches [117].

Finally, access patterns, which are a focus of this work, are one of the important aspects that are in the hands of application developers and compiler designers. As compiler optimization contributes to reducing the number of cache misses, restructuring of the instructions with the required data plays a part in achieving high performance. In fact, improving the access pattern reduces the cache misses for various buffers and the memory hierarchy. The access pattern exploits the locality of reference principle, which has two aspects: *spatial* and *temporal* locality. Spatial locality refers to the degree to which data that are close in the cache space are used by successive instructions in a consecutive approach. Temporal locality (also called *reuse* or *intrinsic reuse*), refers to when data loaded into a cache are used repeatedly before being evicted. In this situation, the number of dispatches and loads will be reduced and excessive accesses to the lower cache levels are minimized. In addition, enhancing the access pattern can expose parallelism by vectorizing loop iterations.

In order to ensure the access pattern has good locality of reference, the data layout can be reordered so that the data are organized appropriately for an optimizing compiler. For example, if a compiler orders matrices in row-major order then the corresponding data should be in row-major order. Similarly, if a compiler orders matrices in columnmajor order, such as with Fortran compilers, then the data should be in column-major order. Prefetching methods order the required instructions and data based on the principle of locality of reference, and an algorithm's efficiency is based on the instructions and data orderings aligning for execution at the right time. Similarly, loop transformation methods are intended to change the order of execution of loops so that data are accessed with greater temporal locality.

There are a number of methods to enhance data locality, such as using sorting and search algorithms and adopting various conventional data structures: queues, lists and different types of tree (some of these methods will to be discussed in the literature review in Chapter 3). Padding has been found to reduce cross interference of array references [84]. However, if the padding is within an array it is normal to replace an array of structures by a structure of arrays, and this results in filling the cache line with data that is not going to be used. In addition, data merging from various data structures into one structure is another approach to enhance spatial locality. Array transposition can be applied for two-dimensional arrays, and has a similar result to loop interchanges, and enhances data locality. Reordering the data into blocks or tiles has significant spatial and temporal locality benefits, especially for parallel implementations.

In this work, the row-major, Hilbert (a space-filling curve), Morton and hybrid orderings are used to study the data locality properties of different orderings for molecular dynamics simulations. Background information on space-filling curves and molecular dynamics simulations is given in the following subsections.

## 2.2 Space-Filling Curves

The space-filling curve (SFC) was introduced by Peano as a continuous mapping of the line segment [0, 1] onto the unit square, and this concept was then further developed by Hilbert and Sierpinski. It is a significant tool used in various types of application, such

as big data analysis [105], computer graphics, networking algorithms, and volume slicing. It has been used to ensure a high level of data access coherency, wherein data can be stored in memory in the traversal sequence furnished by the SFC traversal pattern. This dissertation focuses mainly on the Hilbert and Morton orderings, thus in this section the definition of a space-filling curve, its generation and related algorithms and applications will be introduced.

#### 2.2.1 SFC Definition

In general, a space-filling curve maps the multi-dimensional space (or multi-dimensional data or key values) into a one-dimensional space (a single key value). Bader in [17, p. 17] has defined it as follows:

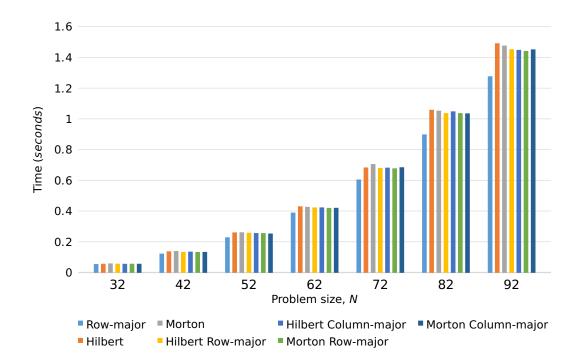

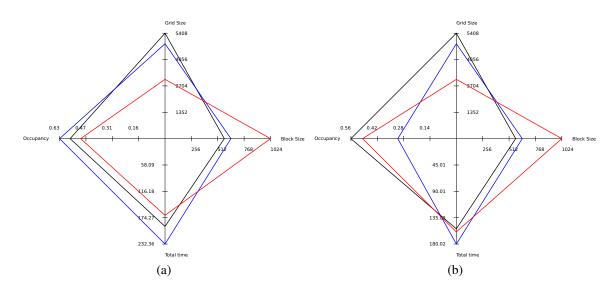

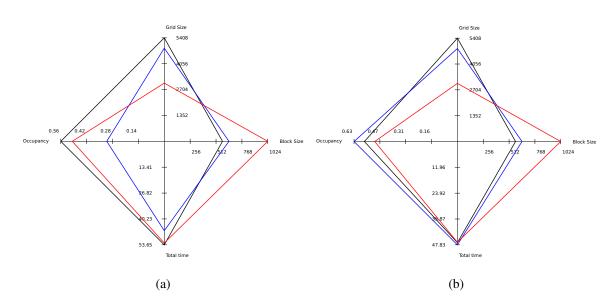

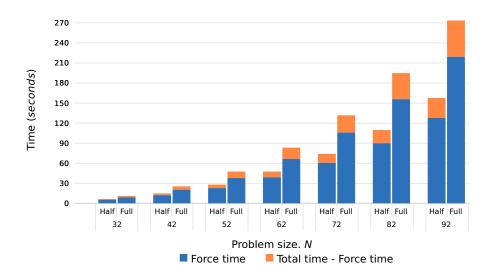

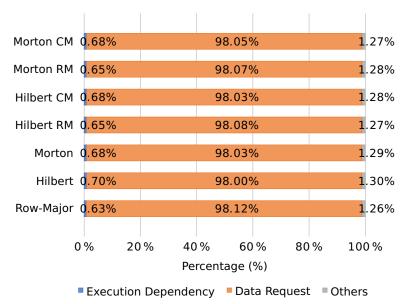

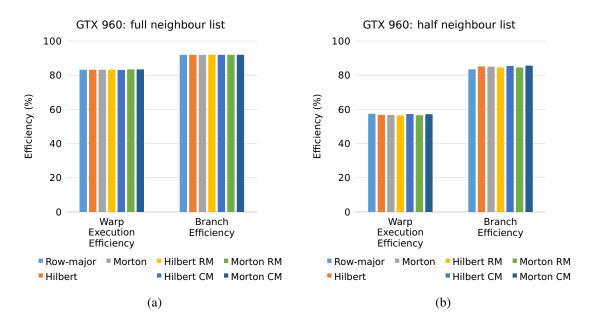

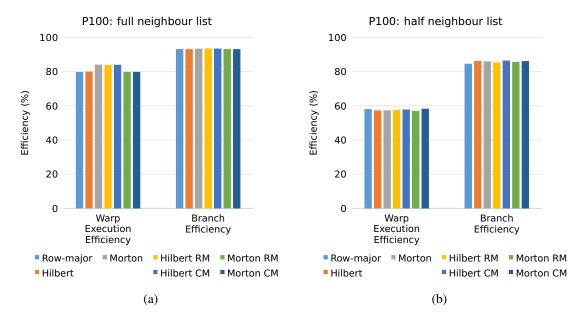

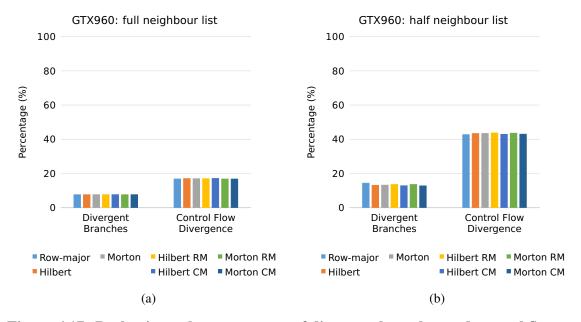

**Definition 2.1** (Space-filling Curve). Given a curve  $f_{\star}(I)$  and the corresponding mapping function:  $f : I \to \mathbb{R}^n$ , then  $f_{\star}(I)$  is called a space-filling curve, if  $f_{\star}(I)$  has a Jordan content (area for n=2 or volume for n=3,...) larger than 0.