# HIGH-EFFICIENCY AND BROADBAND PA DESIGN CONSIDERING THE IMPACT OF DEVICE KNEE VOLTAGE

A thesis submitted to Cardiff University in candidature for the degree of

#### **Doctor of Philosophy**

By

Syed Muhammad Hilmi Syed Anera, M.Eng.

Centre for High Frequency Engineering

School of Engineering

Cardiff University

United Kingdom

June 2019

## **Declarations**

| This work has not previously been accepted in substance for any degree and is not                                                                                                                                |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| concurrently submitted in candidature for any degree.                                                                                                                                                            |  |  |  |

|                                                                                                                                                                                                                  |  |  |  |

| Signed                                                                                                                                                                                                           |  |  |  |

| STATEMENT 1                                                                                                                                                                                                      |  |  |  |

| This thesis is being submitted in partial fulfilment of the requirements for the degree of                                                                                                                       |  |  |  |

| PhD                                                                                                                                                                                                              |  |  |  |

|                                                                                                                                                                                                                  |  |  |  |

| Signed                                                                                                                                                                                                           |  |  |  |

| STATEMENT 2                                                                                                                                                                                                      |  |  |  |

|                                                                                                                                                                                                                  |  |  |  |

| This thesis is the result of my own work/investigation, except where otherwise stated.                                                                                                                           |  |  |  |

| Other sources are acknowledged by explicit references.                                                                                                                                                           |  |  |  |

|                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                                                                                                                  |  |  |  |

| Signed                                                                                                                                                                                                           |  |  |  |

| Signed                                                                                                                                                                                                           |  |  |  |

|                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                                                                                                                  |  |  |  |

| STATEMENT 3                                                                                                                                                                                                      |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside                        |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for                                                                                                          |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside                        |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.  Signed |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.         |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.  Signed |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.  Signed |  |  |  |

| I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.  Signed              |  |  |  |

| STATEMENT 3  I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.  Signed |  |  |  |

## Acknowledgements

I would like to express my gratitude to my main supervisor, Prof. Johannes Benedikt for believing in me to work with, and providing supports through the whole journey of completing this PhD. I would not be here, writing this thesis, if he had not offered me with this research right after I had just finished my M.Eng. studies back in 2015. I would also like to thank Mr. Munawar Kermalli and Futurewei Technologies for the funding of this research and providing guidance for the direction of this research, including the specifications requirements for this research. I would also like to thank all my colleagues from Centre for High Frequency Engineering, for sharing the knowledges, especially helping me with the measurement system in the laboratories. A special dedication to Dr. Nyle Parker (RIP), for being my housemates for most the most of time for our PhD studies. I will always remember our good times together.

I would also like to thank my family for providing financial support to complete this research and finishing up this thesis. To all my friends here in Cardiff, I am grateful that we got to share our good times together. A special shout out to my best friend, Matt Evans for being aside me for the most of my PhD time. Thank you for driving me around, having a good time together, and listening to the complains of my work, despite you didn't understand the most of it.

### **Abstract**

The new 5G communications system requires the power amplifier (PA) circuits to be operated with high efficiency at both peak and back-off power within a broad RF and video bandwidth. The new 5G signal has an increased complexity for the modulation scheme, resulting into a high signal peak-to-average ratio (PAPR). In consequence, the performances of the PA are limited. This thesis addresses the design analysis for high efficiency and broadband PAs based on harmonic tuned continuous class-F (CCF) mode by including the I-V knee interaction. Most PA modes and waveform engineering techniques to elevate PA performances are ignoring the practical knee voltage. This thesis addresses the new performances of the CCF mode when the I-V knee interaction from the waveforms in considered. The current waveforms are a function of voltage waveforms, that clipped and generates harmonics when voltage waveform is expanded into knee region, as the device is operated with compression. The new performances of the CCF mode does not follow the ideal theoretical performances, instead, changes along the phase of 2<sup>nd</sup> harmonic impedance termination.

The interaction of the current and voltage (I-V) knee on the waveforms of CCF mode allowing load-pull emulation to be calculated, where the  $\alpha$  in CCF mode is the function of  $2^{nd}$  harmonic impedances termination in the actual device's load-pull technique. In this research, the load-pull emulation is performed only through mathematical calculation in MATLAB by manipulating the equation of drain current and voltage waveforms. Output power and efficiency contours are generated from load-pull emulation for CCF mode, that have almost identical behaviour with the actual device model and measurement, when the non-linear I-V knee interaction is considered. This emulation also investigates the efficiency of the device at the output power back-off (OPBO) range, with the sweep of the  $\alpha$  parameter. The investigation of the new CCF mode with I-V knee interaction is used as guide for a PA design with restriction of the phase of  $2^{nd}$  harmonic impedances termination to keep the efficiency high across wide bandwidth.

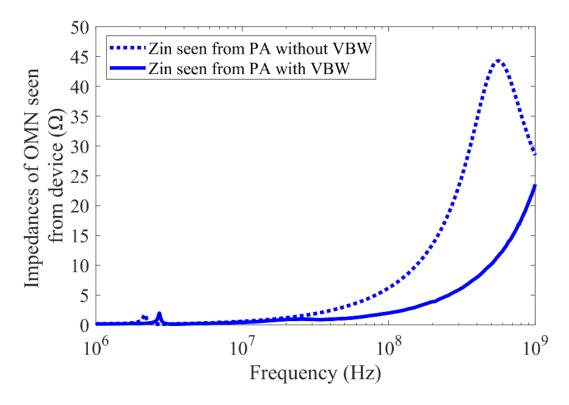

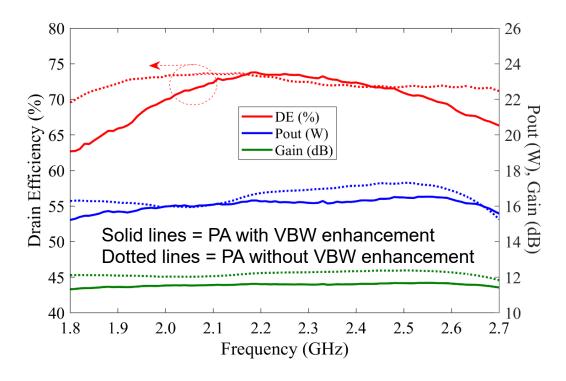

The video-bandwidth (VBW) performances for the PA can be extended using a baseband termination circuit at the device's output to shift the resonance frequency coming from the bias network and the device's output parasitic capacitance. The VBW enhancement is crucial in the 5G communication system where it is expected to operate up to 800 MHz, or even beyond this frequency, for the instantaneous bandwidth. Analyses are made on the components used in the baseband termination circuit in this thesis, where the VBW can be further extended by having the highest value of the shunt capacitor that is placed close to the device, with the lowest equivalent series inductance. This configuration shifted the resonance frequency and reduced the impedances seen by the device output on the matching and bias network. All the methods described in this thesis are adapted to design and investigate the performances of compact PA with integrated matching and baseband termination network. This PA is aimed to operate with high efficiency at the 50  $\Omega$  load impedances and at load modulated output power back-off across a wide-bandwidth. A CW simulation tests are used to evaluate the performances of the PA at peak power, while 2 tones signal with sweep frequency spacing is used to evaluate the VBW performances.

## **List of Publications**

#### First author:

S. M. H. Syed Anera, T. Husseini, S. Alsahali, J. J. Bell, R. Quaglia, M. Kermalli, P. J. Tasker and J. Benedikt, "High-efficiency broadband PA design based on continuous class-F mode with compression," in *IEEE International Microwave Symposium*, Boston, USA, June 2-7, 2019.

#### Co-author:

T. Husseini, A. Al-Rawachy, S. Syed Anera, J. Bell, P. Tasker and J. Benedikt, "On the effective modeling of the test-set non-linearity," in 91st ARFTG Microwave Measurement Conference (ARFTG), Philadelphia, USA, 2018.

S. Alsahali, D. Gecan, A. Alt, G. Wang, S. M. H. Syed Anera, P. Chen, S. Woodington, A. Sheikh, P. Tasker, and J. Lees, "A novel modulated rapid load pull system with digital pre-distortion capabilities," in *93<sup>rd</sup> ARFTG Microwave Measurement Conference (ARFTG)*, Boston, USA, July 7, 2019.

### List of Abbreviations

1G – First Generation

2G – Second Generation

**3G** – Third Generation

4G – Fourth Generation

**5G** – Fifth Generation

ACLR – Adjacent Channel Leakage Ratio

ADS – Advanced Design System

**AM/AM** – Amplitude to Amplitude Modulation

**AM/PM** – Amplitude to Phase Modulation

**CCF** – Continuous Class-F

**CGP** – Current Generator Plane

**CW** – Continuous Waves

**DC** – Direct Current

**DE** – Drain Efficiency

**DUT** – Device Under Test

eMBB - Enhanced Mobile Broadband

**ESL** – Equivalent Series Inductance

**ESR** – Equivalent Series Resistance

**FET** – Field Effect Transistor

**FFT** – Fast Fourier Transform

GaAs – Gallium Arsenide

GaN – Gallium Nitride

**HEMT** – High Electron Mobility Transistor

**IoT** – Internet-of-Things

**IMD** – Intermodulation Distortion

IMD3 – Third Order Intermodulation Distortion

**IMN** – Input Matching Network

**JFET** – Junction-Field Effect Transistor

**LDMOS** – Laterally Diffused Metal-Oxide-Semiconductor

**LNA** – Low Noise Amplifier

LTE – Long Tern Evolution

**MIMO** – Multiple-Input Multiple-Output

**MMIC** – Monolithic Microwave Integrated Circuit

**MOSFET** – Metal-Oxide-Semiconductor Field Effect Transistor

**OMN** – Output Matching Network

**OPBO** – Output Power Back-Off

**PA** – Power Amplifier

**PAE** – Power-Added Efficiency

**PAPR** – Peak to Average Power Ratio

**PEP** – Peak Envelope Power

**Pout** – Output Power

**RF** – Radio Frequency

SiC – Silicon Carbide

**SMD** – Surface-Mount Device

**VBW** – Video-Bandwidth

WiMAX – Worldwide Interoperability for Microwave Access

## **Table of Contents**

| Declarationsii                                       |

|------------------------------------------------------|

| Acknowledgementsiii                                  |

| Abstractiv                                           |

| List of Publicationsv                                |

| List of Abbreviationsvi                              |

| Table of Contentsvii                                 |

| Chapter 1 - Introduction1                            |

| 1.1 Research Motivations                             |

| 1.2 RF Power Amplifier Devices                       |

| 1.3 Classical Power Amplifier Modes                  |

| 1.3.1 Class-A4                                       |

| 1.3.2 Class-B                                        |

| 1.3.3 Class-AB                                       |

| 1.3.4 Class-C6                                       |

| 1.4 Research Objectives                              |

| 1.5 Research Flows                                   |

| 1.6 Thesis Organisation 9                            |

| Chapter 2 – High-Efficiency RF Power Amplifiers      |

| 2.1 Introduction                                     |

| 2.2 High Efficiency PA Modes through Harmonic Tuning |

| 2.2.1 Class-F and Inverse Class F                                      | 13  |

|------------------------------------------------------------------------|-----|

| 2.2.2 Continuous Class-F                                               | 18  |

| 2.3 Efficiency Enhancement Techniques Over Dynamic Range               | 21  |

| 2.3.1 Doherty Power Amplifier                                          | 22  |

| 2.3.2 Chireix Outphasing Power Amplifier                               | 25  |

| 2.3.3 Envelope Tracking                                                | 27  |

| 2.4 Chapter Summary                                                    | 28  |

| Chapter 3 – CCF Mode with I-V Knee Interaction                         | 30  |

| 3.1 Introduction                                                       | 30  |

| 3.2 Reformulation of CCF Mode with I-V Knee                            | 32  |

| 3.3 Simulation of CCF Mode with Compression on 10 W GaN Device         | 37  |

| 3.4 Measurement of CCF Mode with Compression on 10 W GaN Device        | 40  |

| 3.5 Chapter Summary                                                    | 43  |

| Chapter 4 – Broadband 10 W GaN PA Design Based on CCF Mode with        |     |

| Compression                                                            | 44  |

| 4.1 Introduction                                                       | 44  |

| 4.2 Load-pull Simulation                                               | 45  |

| 4.3 Broadband Matching Network                                         | 48  |

| 4.4 CW Measurement                                                     | 54  |

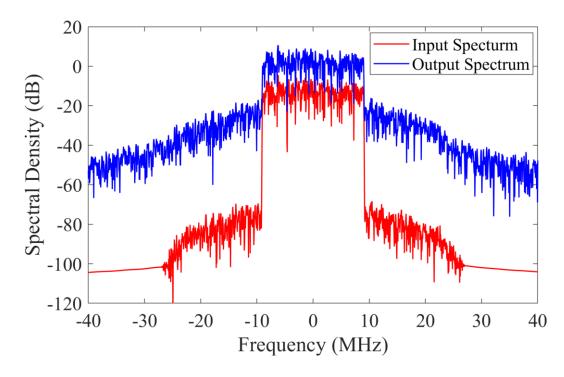

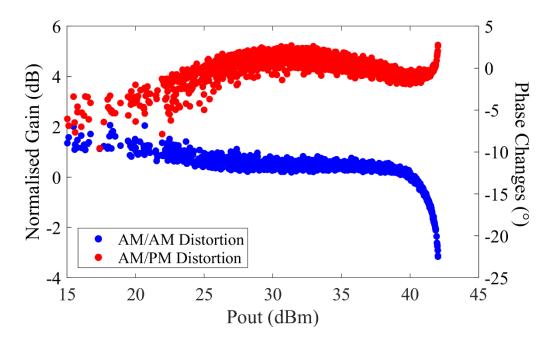

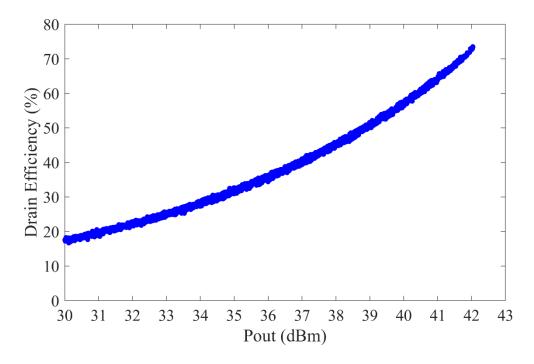

| 4.5 Modulated Signal Test                                              | 59  |

| 4.6 Chapter Summary                                                    | 62  |

| Chapter 5 – Generating Power and Efficiency Contours for CCF Mode with | I-V |

| Knoo                                                                   | 61  |

| 5.1 Introduction                                                                         |

|------------------------------------------------------------------------------------------|

| 5.2 Linear Load-line Model on CCF Mode                                                   |

| 5.3 Non-linear Load-line Knee Model on CCF Mode                                          |

| 5.4 Verification from Fundamental Load-pull with Sweep Phase of 2 <sup>nd</sup> Harmonic |

| Impedance79                                                                              |

| 5.4.1 Load-pull Simulation79                                                             |

| 5.4.2 Active Load-pull Measurement                                                       |

| 5.5 Load-pull measurement                                                                |

| 5.6 Chapter Summary91                                                                    |

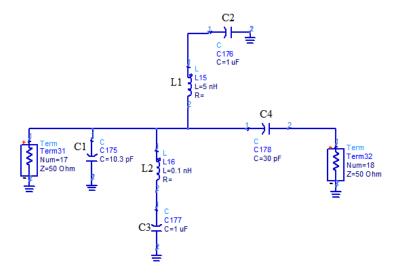

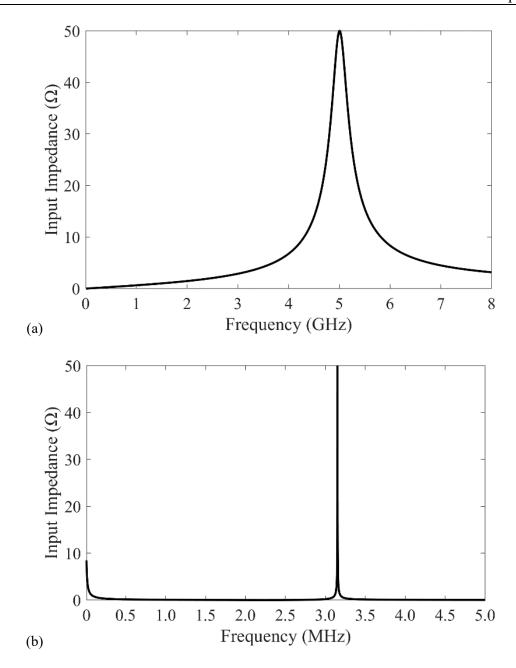

| Chapter 6 – Theoretical Video-Bandwidth Extension93                                      |

| 6.1 Introduction93                                                                       |

| 6.2 Extending VBW with Series Low Inductance and High Capacitance Circuit 95             |

| 6.3 High Value Capacitor with Low ESL for Further Extending VBW Performances             |

|                                                                                          |

| 6.4 Chapter Summary                                                                      |

| Chapter 7 – Compact Broadband PA with Integrated Matching and VBW                        |

| Extension114                                                                             |

| 7.1 Introduction                                                                         |

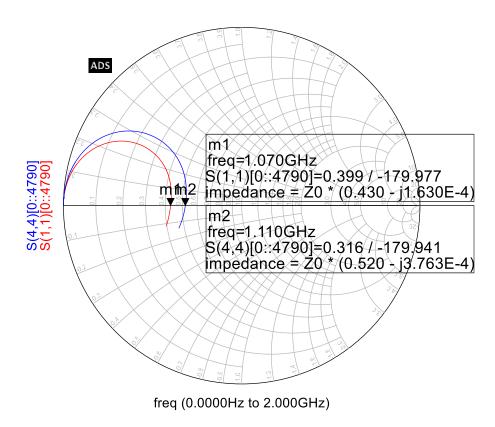

| 7.2 15 W GaN Bare Die Device Characterisation in CCF Mode                                |

| 7.2.1 Cds Parasitic Drain Capacitance Extraction                                         |

| 7.2.2 CCF Mode - Finding Optimum Impedances                                              |

| 7.3 Matching Network Design using Ideal Components                                       |

| 7.3.1 Ideal Input Matching Network                                                       |

| 7.3.2 Ideal Output Matching Network                              | 127          |

|------------------------------------------------------------------|--------------|

| 7.4 3D PA Model Implementation in EMPro                          | 129          |

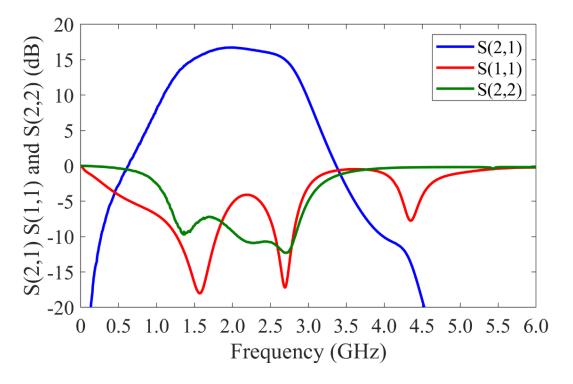

| 7.4.1 S-Parameters Comparison between Ideal and 3D PA Simulation | on132        |

| 7.4.2 PA without VBW Enhancement                                 | 134          |

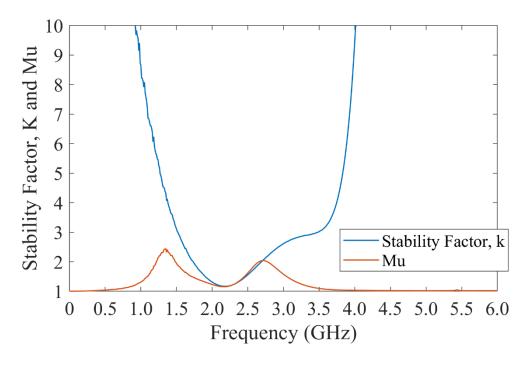

| 7.5 PA Simulations                                               | 135          |

| 7.5.1 S21 Output Resonant                                        | 135          |

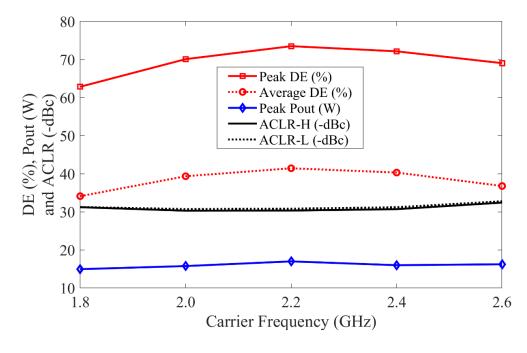

| 7.5.3 CW Signal Test                                             | 138          |

| 7.5.4 PA Linearity under Modulated Signal Test                   | 144          |

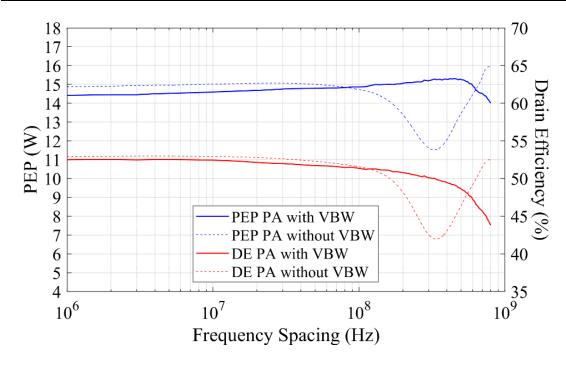

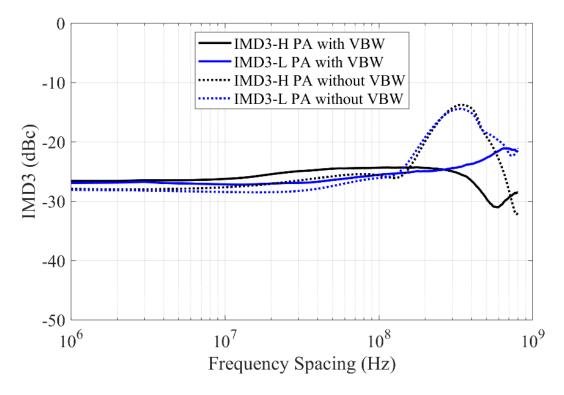

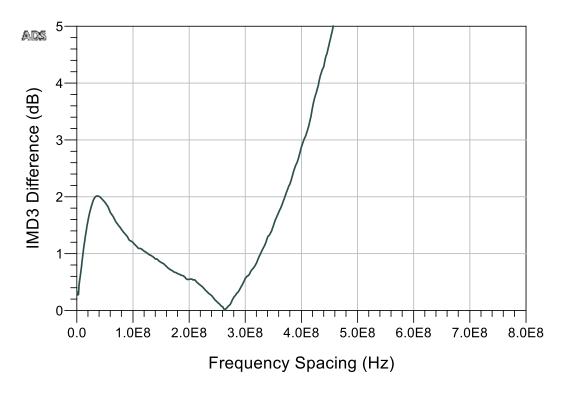

| 7.5.5 VBW Performances                                           | 147          |

| 7.6 Narrowband Outphasing PA Application                         | 151          |

| 7.7 Chapter Summary                                              | 156          |

| Chapter 8 – Conclusions and Future Work                          | 158          |

| 8.1 Conclusions                                                  | 158          |

| 8.2 Future Work                                                  | 160          |

| References                                                       | 163          |

| Appendix 1 – MATLAB Code for Ideal CCF Mode                      | 174          |

| Appendix 2 – MATLAB Code for Emulating CCF Mode with Compre      | ession using |

| I-V Knee Interaction                                             | 177          |

| Appendix 3 – MATLAB Code for Generating Contour Plots of CCF M   | Mode with    |

| Non-linear I-V Knee Interactions                                 | 184          |

| Appendix 4 –Publication 1                                        | 188          |

## Chapter 1

## Introduction

#### 1.1 Research Motivations

Wireless communications have been growing and evolving ever since the first successful transmission in 1896 by Guglielmo Marconi [1]. Wireless telecommunications standards have been introduced, initially from 1G, and now, at the time this thesis is being written, 5G has just been launched in several major cities in the world [2]. The difference between these wireless communication standards is the technologies that are introduced in their systems. 1G standard is an analogue based signal, while 2G is based on digital signal [3]. The complexity of the wireless standards increases over time as the demand for the data transfer increases. The 3G standards was introduced to support mobile broadband, where the users can have internet access through their mobile phones [4]. The easy access for the mobile internet has open a new way of communications where users can access the internet to watch TV, streaming videos and video call wirelessly. While the 3G system can support mobile broadband network, this system is not good enough to support higher demand of data over multiple users at higher speed. 4G system is introduced in 2006, where the data transfer rates are aiming up to 1 Gb/s [5]. Several technologies within 4G were introduced such as Worldwide Interoperability for

Microwave Access (WiMAX) and Long-Term Evolution (LTE) to meet the 4G requirements. Within this network, users can access much faster internet speed wirelessly, allowing for example, the streaming of high definition contents without the need for buffering.

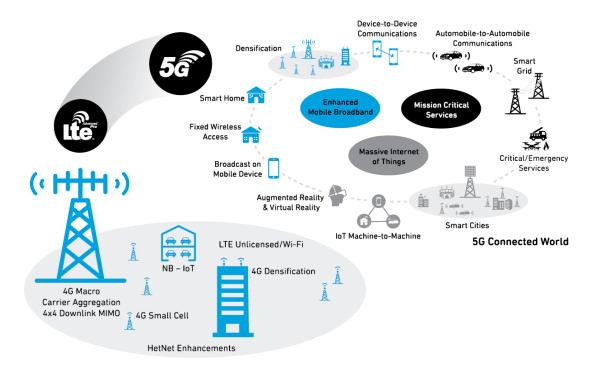

The 5G communication which is now under development and partly being introduced since 2<sup>nd</sup> quarter of 2019, is the most anticipated technology in the next decade, and is expected to fully roll out from 2020. The 5G will replace 4G standards such that it will improve significantly on the data rates, with higher connectivity and lower latency [2]. 5G is expected to connect to a much larger network, with increased number of Internet-of-Things (IoT). The major technologies expected in 5G communications are the massive multiple-input and multiple-output (MIMO), and millimetre waves. These technologies allow the 5G communication expected to deliver up to 10 Gb/s to the users [6]. Figure 1.1 illustrates the comparison between 4G and 5G communication demands [6], indicating an increased demands for the new network.

Figure 1.1. Comparison of communication demands between 5G and 4G LTE [6].

#### 1.2 RF Power Amplifier Devices

The power amplifier (PA) is the main energy-consumer in the RF communications systems. The digital signal which is carrying the information for transmission has to be amplified, in the RF analogue forms, using PAs. A very basic explanation for PA operation is, the RF input signal is amplified using one or more transistors, by converting the DC power feeding into the device to amplify the small input signal into a large output signal. Transistors are used in PA circuits, with the first transistor was invented in the Bell's Laboratories in 1947. Prior to this invention, vacuum tubes were largely used, however they were bulky and experience heating issues.

Different types of transistors are available in the market, such as BJT, FET, JFET, MOSFET and etc. RF transistor technologies have evolved from the widely used GaAs and LDMOS devices to currently most advanced GaN devices [7]. LDMOS transistor are the most rugged, that can achieve more than 1000 W for a single transistor and operates with high efficiencies. They have been used for the PAs in the base-stations, military applications as well as RF heating for cooking. Despite having an outstanding performance, the LDMOS device can only operates up to a few GHz, recently reported up to 12 GHz [8], where the performances drop and becoming obsolete at millimetre wave frequencies.

On the other hand, GaAs devices have been used in most RF applications, ranging from PA, LNA, switches and attenuators. In the PA application, the GaAs devices emerged primarily for the development of MMIC. It has been used mostly in low power PA and LNA especially in mobile phones applications. GaAs devices can operate at higher frequencies than LDMOS, at millimetre waves frequencies.

More recently, GaN technologies emerged in the market, and have been widely involved in PA research. There are many advantages of this new device technology, such as excellent efficiency and the device operates at very high frequencies beyond 100 GHz towards THz [9]. GaN devices can operate with high breakdown voltage and can also withstand high temperature in comparison to other device technologies [10]. GaN devices have high power density, allowing them to deliver higher power due to high bandgap of 3 eV. Several processes of GaN are available, mostly on SiC, but it also available on diamond [11]. The major drawbacks of GaN technologies are due to its production cost and the market prices.

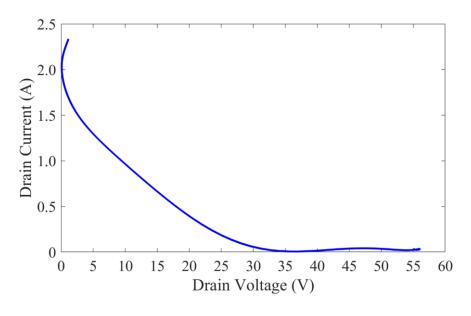

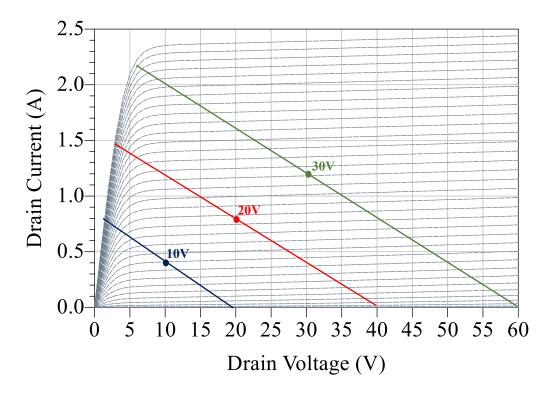

#### 1.3 Classical Power Amplifier Modes

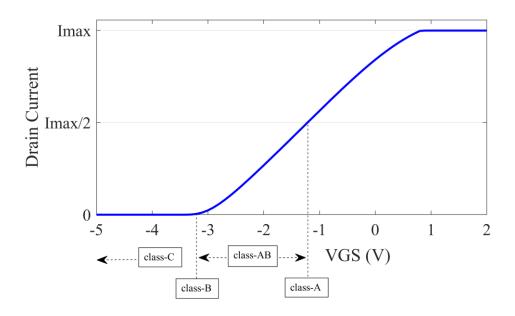

The typical power amplifier operation is classified based on their biasing points [12, 13, 14, 15]. The biasing indicates the PA modes, dividing it into different classes of operation. Considering the transistor as a current source, the biasing points determine the output current drawn into the device, where such behaviour is illustrated in Figure 1.2. This figure shows the transfer characteristic of the device, in this case, using an example of 10 W GaN HEMT device (CGH40010F) [16] is simulated, with a constant drain bias of 28 V.

#### **1.3.1** Class-A

Class-A amplifier is the most linear among the other PA modes, where the device is biased at half of the maximum current, *Imax*, that the transistor can generate. The good linearity performances from this PA mode comes from the full 360 ° conduction angle of the output current and resulting harmonic-free voltage waveform, although non-linearities can still be generated, especially if the device is operated with compression. Despite being

the most linear PA among other classes and producing a high gain, this PA can theoretically operate only at a maximum of 50 % efficiency at the peak power. The class-A amplifier is typically used in a linear PA application such as driver amplifiers for highly input-sensitive RF equipment.

Figure 1.2. PA modes based on the device's gate biasing.

#### **1.3.2** Class-B

Class-B mode PA is achieved when biasing the transistor device right at the pinch -off voltage, where the quiescent current drawn by the transistor drain reduced to zero, as shown in Figure 1.2. The conduction angle is 180 °, producing half-rectified sinusoidal current waveform, as the device is operated with compression. The harmonics contents in the current waveforms is greater in this mode, due to its truncated shape, while, the harmonics in the voltage waveform have to be short-circuited to maintain a sinusoidal waveform. The harmonics generated by the device output in this mode result into some non-linearity issues, despite efficiency boost of up to 78.5 % theoretically. The operation of the PA in this mode is based on self-biasing, which means that at the low RF input

signal, the device is turns off, drawing very little or no current, which can affect the small signal gain.

#### 1.3.3 Class-AB

Class-AB amplifier can be achieved by biasing the device between class-B and class-A, drawing very small amount of current and up to half of the *Imax*. Thus, the conduction angle varied between 180 ° to 360 °. The PA is less linear than the class-A amplifier, however, it can provide better linearity than the class-B mode. The theoretical efficiency obtained from this mode ranges between 50 % to 78.5 %, depending on the biasing point. Typically, in RF PA application, a deep class-AB mode is chosen, drawing a very small quiescent current from the biasing just above the pinch-off voltage, allowing the PA to operate at high efficiencies, while also provides high gain and good linearity. Class-AB has been in favour in many RF PA design because it provides the trade-off between power, efficiency and linearity.

#### **1.3.4 Class-C**

Class-C mode amplifier is similar to the class-B amplifier, where it is biased to draw zero quiescent current at the device output. However, the gate bias voltage is lower than the pinch-off voltage, as indicated in Figure 1.2, thus the conduction angle for this amplifier mode is less than 180 °. Class-C amplifier is theoretically more efficient than the class-B amplifier, ranging between 78.5 % to 100 %. However, the output of the amplifier generates higher order harmonics, giving it worst linearity performances as compared to the previous mentioned PA modes.

#### 1.4 Research Objectives

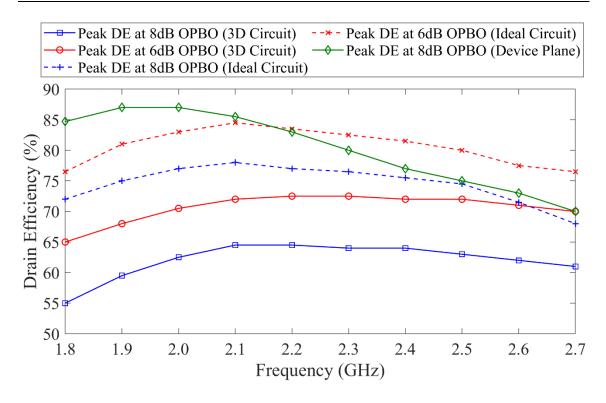

The overall aim for this research is to improve the efficiency performances of the power amplifier, which is operating over a wide frequency band, mainly focusing between 1.8 GHz to 2.7 GHz. This research aiming to improve the efficiency at 8dB output power back-off (OPBO), targeting for outphasing PA application, as per Huawei's requirement. The specific aims for this research are as follows:

- To develop understanding through mathematical waveform theory, for the efficiency performances of CCF mode, when considering the device's knee voltage.

- To emulate the waveforms and performances of CCF mode when the device is operating under compression.

- To verify the mathematical reformulation of CCF mode with the knee interaction using load-pull simulation and measurement of a GaN device.

- To design, fabricate and measure a hybrid and broadband GaN PA with high efficiency, gain and output power in S-band frequencies based on the reformulated CCF mode operated with compression.

- To develop understanding through mathematical waveform theory, the separation between power and efficiency impedance optima for the CCF mode by considering the device's knee voltage. Understanding the separation between the two optima is crucial to improve the peak DE at output power back-off.

- To develop mathematical analysis for extending video-bandwidth (VBW) in power amplifier design using a practical baseband termination circuit.

- To design a single-stage broadband and compact PA using the integrated matching elements with high efficiency across S-band frequencies and enhanced video-bandwidth.

#### 1.5 Research Flows

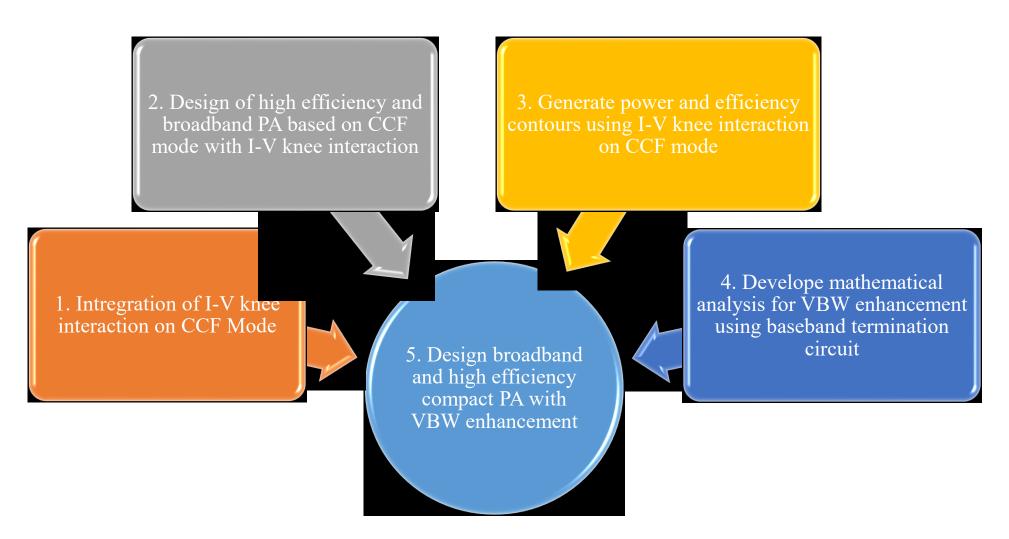

Figure 1.3. Summary of the research flows.

#### 1.6 Thesis Organisation

This thesis consists of 8 chapters in total. The first chapter here, consists of the research motivations, aims, and the basic power amplifier classes of operation. The remaining chapters are summarised as follows:

Chapter 2: This chapter mainly describes the efficiency enhancement techniques for the power amplifier designs that are mostly adapted by PA designers. Different classes of PA modes are described, that are based on harmonic tuning. From class-F mode to the more recent continuous class-F mode, these PA modes have been the main aspiration for this work. The ideal CCF mode is described, showing its classical performance, where the knee voltage is ignored. Following this, other efficiency enhancement PA architectures, that focus on improving efficiency at power back-off are described. These architectures include Doherty, outphasing and envelope tracking PAs. These PAs represent the hottest topics being discussed as they are likely to be the most suitable PA candidates to be used in the 5G communication systems.

Chapter 3: This chapter describes the behaviour of CCF mode when the device is operated with compression. Ideal CCF mode is used as a starting point, whereby the definition of waveforms are reformulated to include the effect of I-V knee interaction. This I-V knee interaction emulates the waveforms behaviour within the knee boundary region, which is observed through mathematical calculation in MATLAB. The new performance of the CCF mode, by including the non-linearities coming from knee interaction are analysed. The mathematical emulation is verified using 10 W GaN device through load-pull simulation and active load-pull measurement.

**Chapter 4:** The main objective for the work in this chapter is to utilise the new mathematical reformulation of CCF mode from Chapter 3, to design a broadband RF PA

with high performances, especially for the drain efficiency, targeted at least 65 % across the wide S-band frequencies (1.7 GHz to 2.8 GHz). A 10 W GaN packaged transistor device is used for the RF PA design, that was designed and simulated using ADS software. The fabricated RF PA is measured, using small signal, large CW signal and modulated signal, to verify its performances.

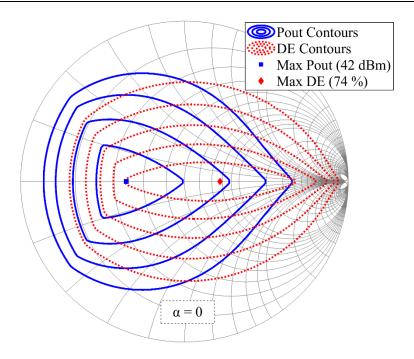

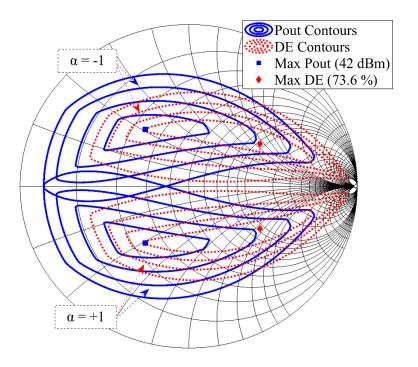

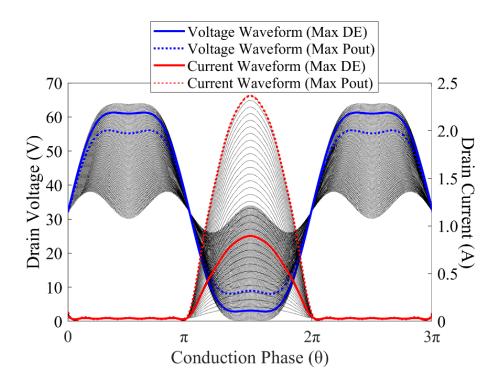

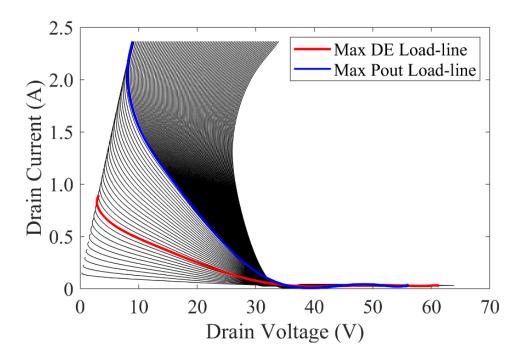

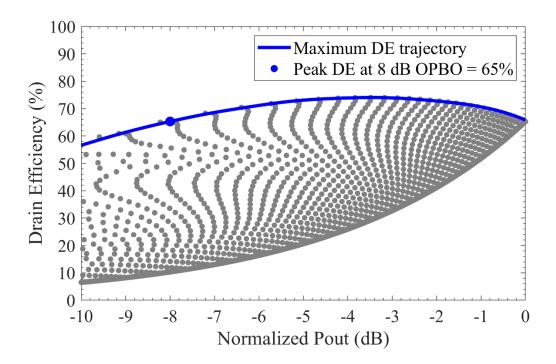

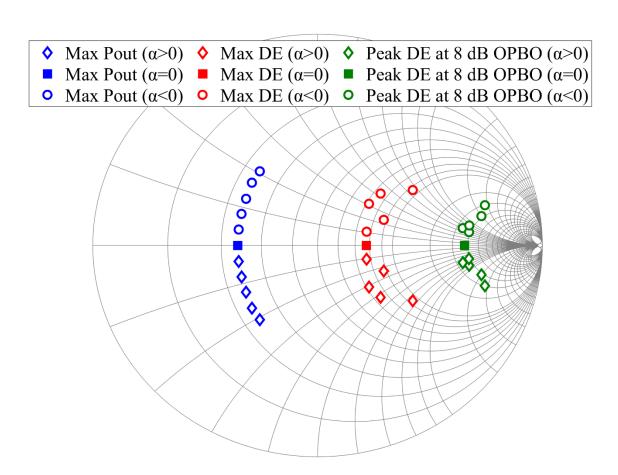

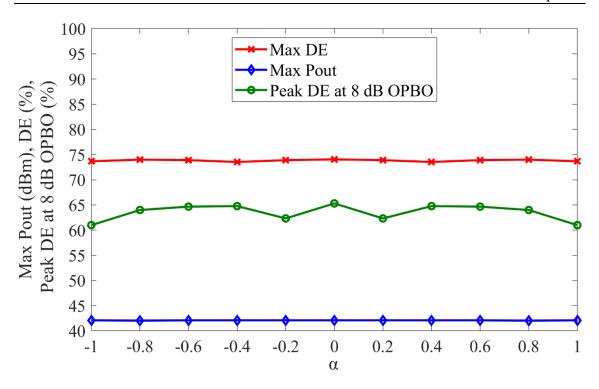

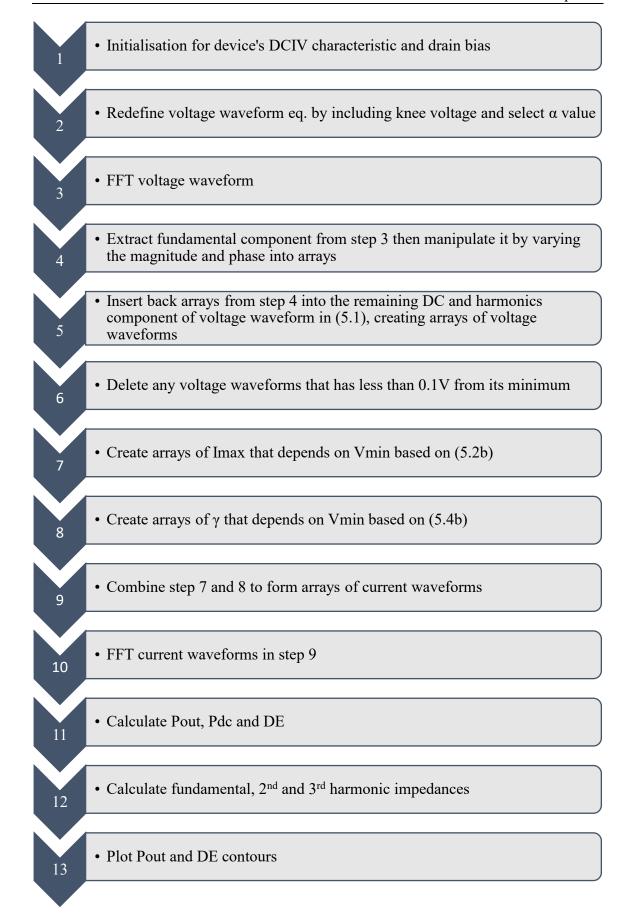

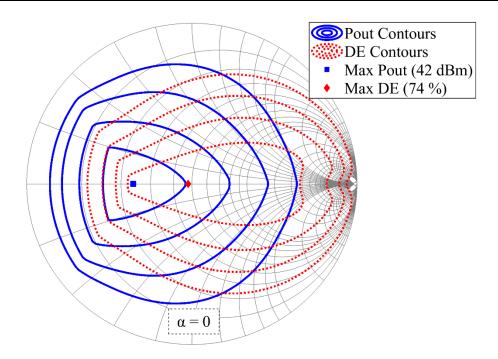

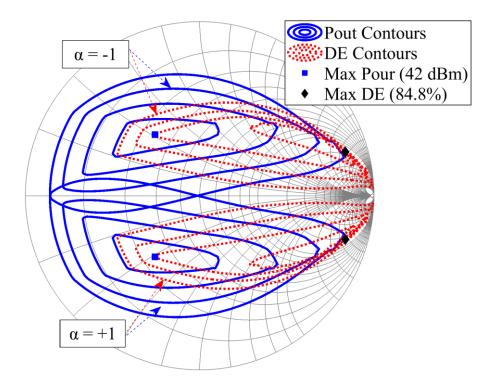

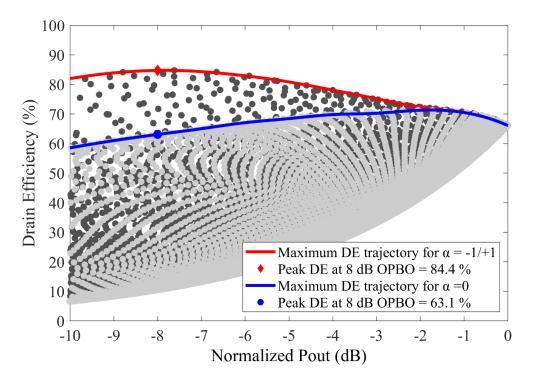

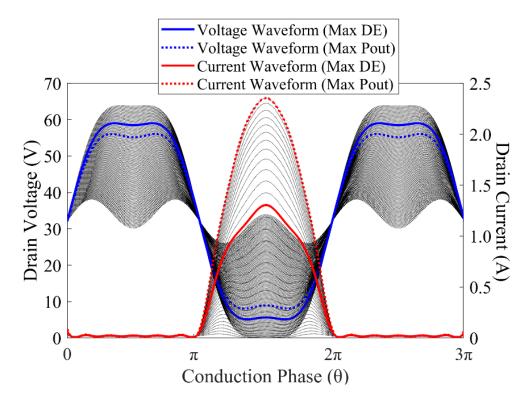

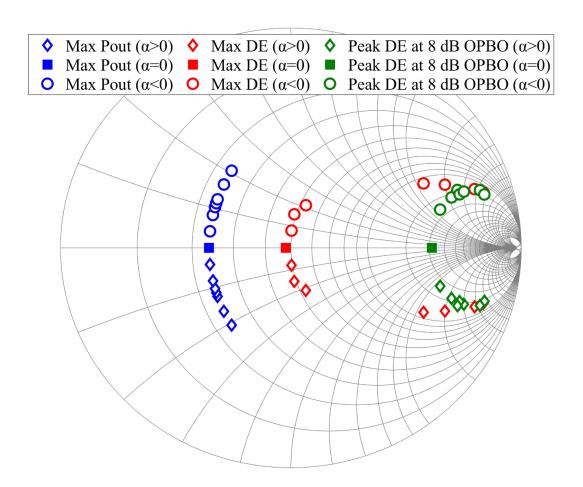

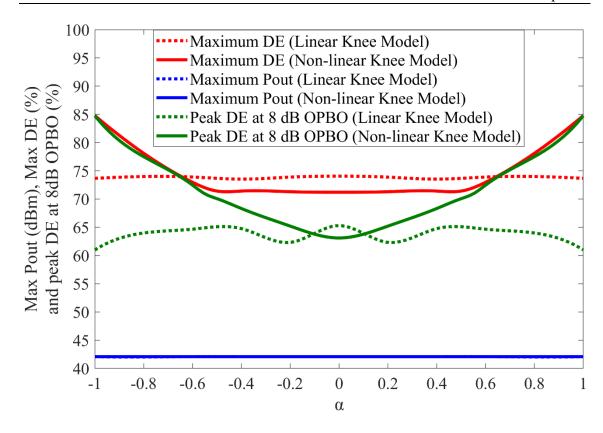

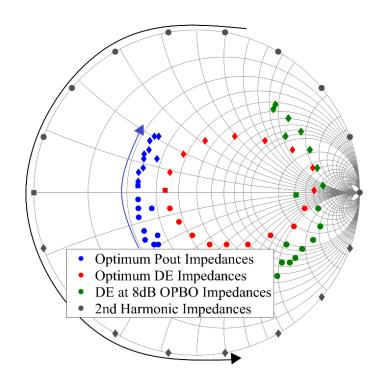

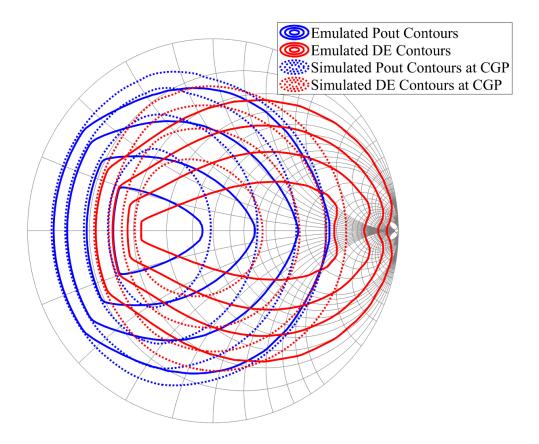

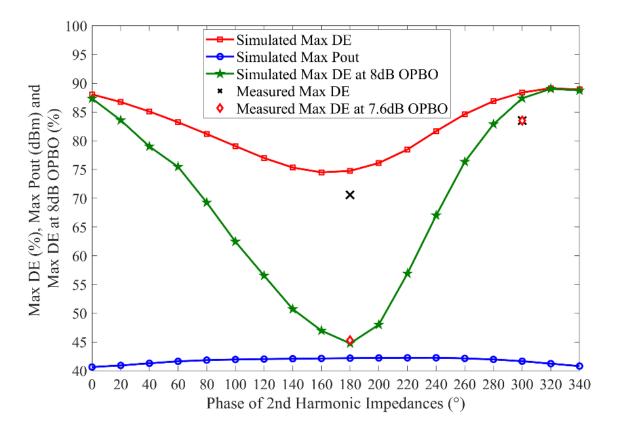

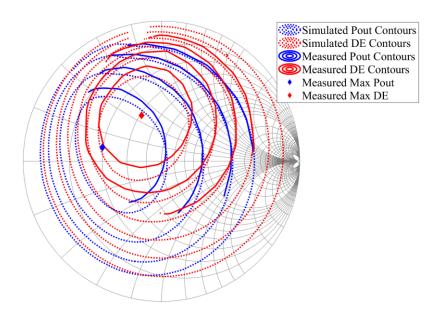

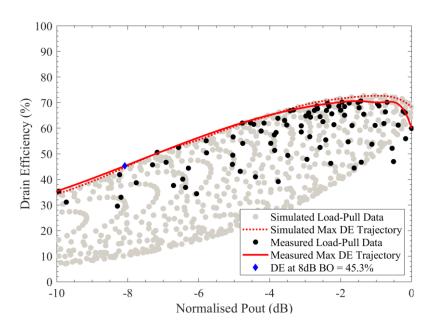

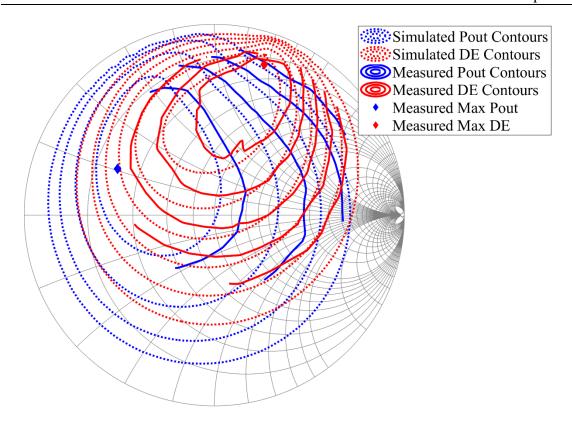

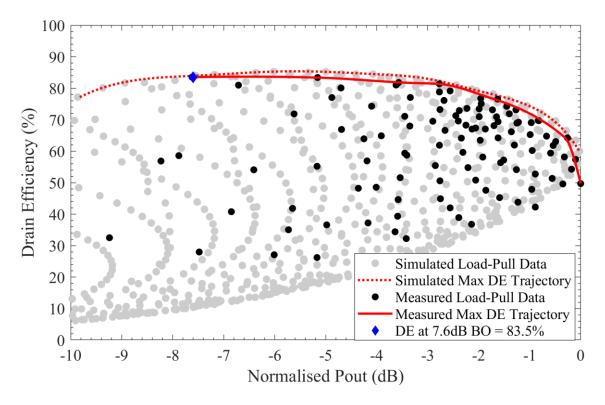

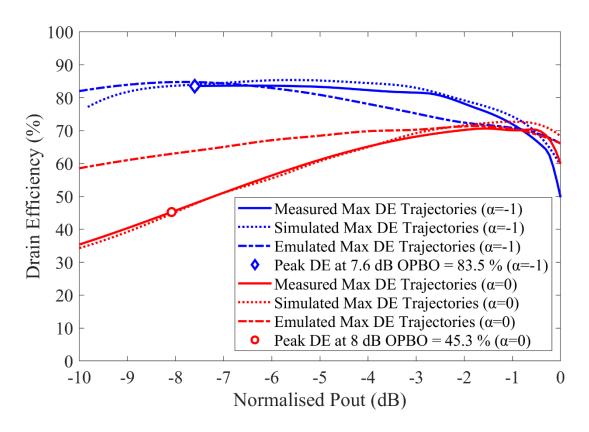

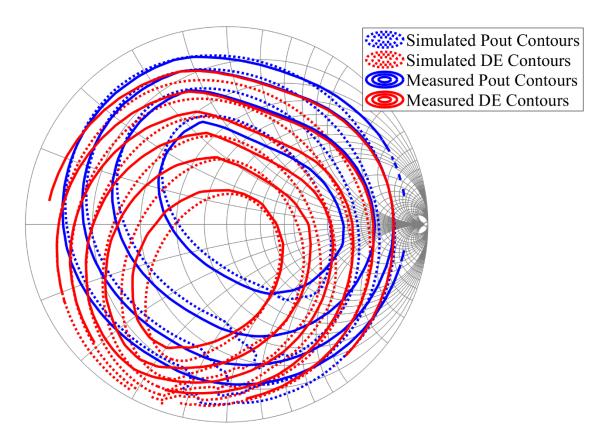

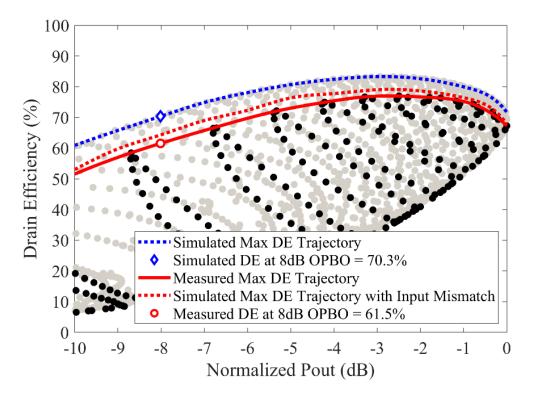

Chapter 5: The work in this chapter extends the mathematical reformulation of CCF mode from Chapter 3, to emulate load-pull based on the waveform's theory, by including the I-V knee interaction on the CCF mode waveforms. The main objective for this work is to generate power and drain efficiency contours of CCF mode, through the mathematical emulation, to investigate the separation between optimum output power and drain efficiency impedances. The first investigation is performed using Pedro's linear load-line analysis [17]. This analysis is extended by including the non-linear I-V knee interaction into the mathematical emulations to give a much more accurate prediction of the actual device behaviour. This theory is supported by the load-pull simulation and measurement of the GaN device, where fundamental load-pull is performed, with a sweep of the 2<sup>nd</sup> harmonic impedances along the edge of the Smith chart. The maximum Pout, DE and peak DE at 8 dB OPBO are compared between the mathematical emulations, device's simulations and measurements.

Chapter 6: This chapter provides mathematical calculation and analyses for extending the video-bandwidth of a broadband PA using a baseband termination circuit. First, the analysis is based on the widely used baseband termination circuit by placing a shorted high value capacitor close to the device through a series of a low value inductor. The analysis is based on an ideal circuit, which is then extended for a more realistic approach, by including the equivalent circuit from the ideal components. The novelty in this chapter, is discussed through the analysis of each components within the circuit that is varied, to

improve the VBW performance.

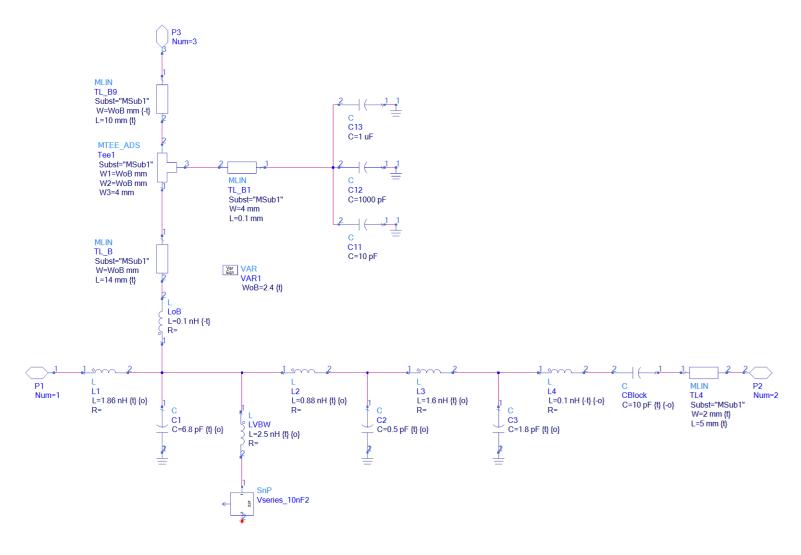

Chapter 7: The final work in this thesis is presented in this chapter. The main objective for this work is to combine all the theories and analyses from the previous chapters, into a single PA design. The PA is also required to have a wide video-bandwidth. All these performance objectives are achieved through a compact PA design using an integrated matching network.

**Chapter 8:** This chapter provides the final conclusions for this thesis, by relating the aims and objectives initially set to the research with the overall work achievement. Here, the future works are underlined to describe any improvements that can be carried out from this research, as well as potential further work that can be investigated.

## Chapter 2

## High-Efficiency RF Power Amplifiers Designs

#### 2.1 Introduction

The demand for power amplifiers operating with high efficiency has increased over the years, especially with the introduction of the new 5G standards. Mobile equipment that depends on a limited power availability, such as satellites and mobile phones, require high efficiency PAs to be able to operate much longer. In order to deliver bigger and faster data rates, the new communications standards require complex modulated signals, resulting into a high peak-to-average power ratio (PAPR) signals. For example, the LTE signal has 7.6 dB PAPR, which further reduce the overall efficiency performance of PAs when operated under this signal. Several design techniques have been presented, to improve the efficiency of the PA at the peak and back-off power, compared to classical PA modes and architectures.

#### 2.2 High Efficiency PA Modes through Harmonic Tuning

The most common efficiency enhancement techniques for a single stage PA is achieved through harmonic tuning. The harmonic impedances presented to the device are tuned to shape the output waveforms for better efficiency performance [13, 14, 18, 19, 20]. Using the waveform engineering techniques, the desired waveforms that yield high performances are stipulated, making it possible to estimate optimum impedances at fundamental and harmonic frequencies. Several publications have optimised their PA performance by selectively tuning the harmonic impedances to enhance efficiency as well as increasing the frequency bandwidth. Here, the termination for the 2<sup>nd</sup> harmonics impedances is considered in [21, 22, 23, 24].

#### 2.2.1 Class-F and Inverse Class F

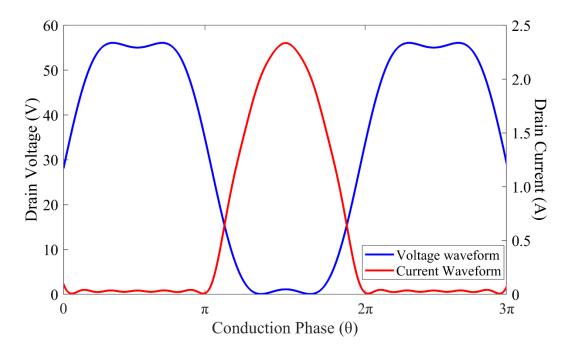

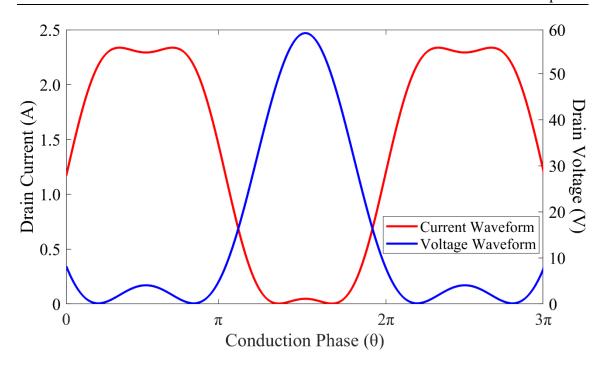

The class-F mode PA can be achieved by shaping the output waveforms of the transistor, such that the drain voltage waveform is a square wave-shape, while the drain current waveform is a half-rectified sinusoidal wave-shape [13, 18, 19, 25]. The conduction angle between the 2 waveforms where the current and voltage alternately turn on is 180°, as shown in Figure 2.1. Theoretically, these output waveforms are achieved by terminating the even and odd harmonics to short and open circuits respectively, giving a 100 % efficiency. However, infinite numbers of harmonics are needed to achieve this theoretical value, which is not possible for a practical RF PA design. The drain voltage and current waveforms in class-F mode equation is defined in (2.1) and (2.2) [25].

$$V_{ds}(\theta) = V_{dc} * \left(1 + \frac{231}{200}\sin(\theta) + \frac{77}{400}\cos(3\theta)\right)$$

(2.1)

$$I_{ds}(\theta) = \frac{Imax}{2} * \left(\frac{2}{\pi} + \sin(\theta) - \frac{4}{\pi} * \sum_{r=1}^{n} \frac{\cos(2r\theta)}{(2r)^2 - 1}\right)$$

(2.2)

Figure 2.1. Ideal class-F mode waveforms considering up to three harmonics for voltage waveform and up to ten harmonics for current waveforms.

The square voltage waveforms can be expressed in different ways for different wave-shapes. The definition in (2.1) is for a square waveform expressed up to  $3^{rd}$  harmonic only, with a minimum 'bounce' or ripple on the wave-shape. Vdc is the DC bias voltage on the device's output drain terminal. Other square waveform definitions as in [26] have more pronounce 'bounce' in the minimum and maximum of the wave-shape, while [13, 25] introduced maximally flat square waveform. The different definition of the square waveform shapes has only a minor effect on the shape of the load-lines. However, the current waveform defined in (2.2) consist of the general Fourier expansion for the half-rectified sinusoidal wave-shape, where Imax is the maximum output current the transistor can generate, and n is the number of even-order harmonics to define the waveform. Figure 2.1 shows the class-F mode waveforms, where the drain current is

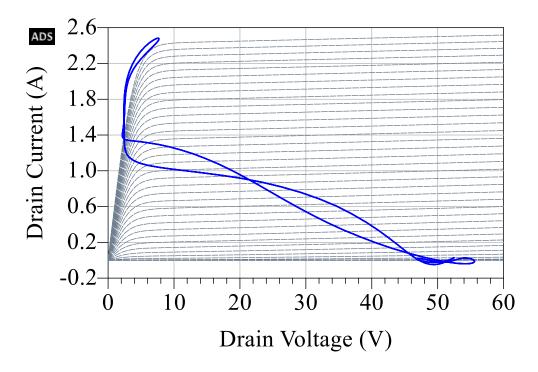

defined up to the 10<sup>th</sup> harmonic. A value of 28 V and 2.5 A is used for the *Vdc* and *Imax* respectively which is taken from the DCIV characteristic of a typical packaged 10 W GaN device [16]. These waveforms are considered as ideal because the knee voltage of the transistor is ignored. Figure 2.2 shows the ideal load-line for this mode, indicating that the device is turn-on, producing high output current, even though the voltage is at 0 V.

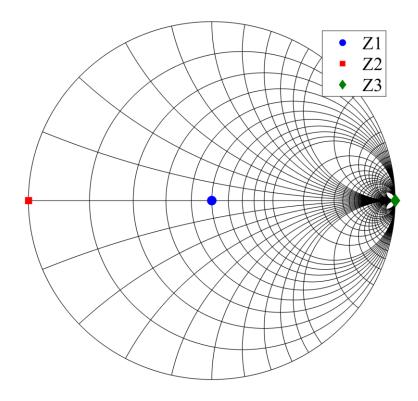

The ideal analysis is used to analyse the performances for the PA under this mode. The output power obtained from the waveform is 18.6 W or 42 dBm. The efficiency is 86.9 %, which is reduced from the maximum theoretical value, due to only small number of harmonics considered. However, this value is higher than the maximum theoretical efficiency in class-B and class-AB. The optimum fundamental impedance for the waveforms in Figure 2.1 is  $28 + j \ 0 \ \Omega$ . Figure 2.3 shows the optimum fundamental,  $2^{nd}$  and  $3^{rd}$  harmonic impedances, normalised to the optimum fundamental impedance, plotted on the Smith chart. The single solution for the optimum impedances for this mode indicates that it can only be useful to design a narrowband PA [27]. A higher efficiency performance for class-F PA can be obtained by considering higher harmonic terminations of the harmonic impedances, as investigated in [28, 29].

Figure 2.2. Ideal class-F mode load-line.

Figure 2.3. Optimum fundamental, 2<sup>nd</sup> and 3<sup>rd</sup> harmonic impedances for ideal class-F mode.

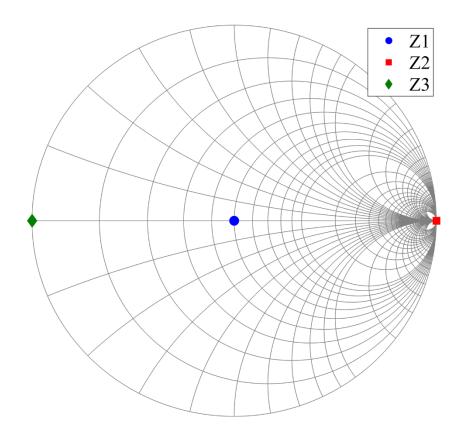

In inverse class-F mode, the definition for the voltage and current waveforms are the dual to the original class-F mode. The current waveform for inverse class-F mode is a square wave-shape while the voltage waveform is a half-rectified sinusoidal wave-shape. This mode can be achieved by terminating the even harmonics to the open circuit and the odd harmonics to a short circuit. Similar to the class-F mode, the ideal inverse class-F mode with an infinite number of harmonics terminated to the device will theoretically give 100 % efficiency. Figure 2.4 illustrates the output waveforms for this mode, by considering up to three harmonics to define both waveforms, which gives 79.5 % efficiency. Figure 2.5 shows the optimum fundamental, 2<sup>nd</sup> and 3<sup>rd</sup> harmonics impedances normalised to the optimum fundamental impedance, for ideal inverse class-F mode.

Figure 2.4. Ideal inverse class-F mode waveforms considering up to three harmonics.

Figure 2.5. Optimum fundamental,  $2^{nd}$  and  $3^{rd}$  harmonic impedances for ideal inverse class-F mode.

#### 2.2.2 Continuous Class-F

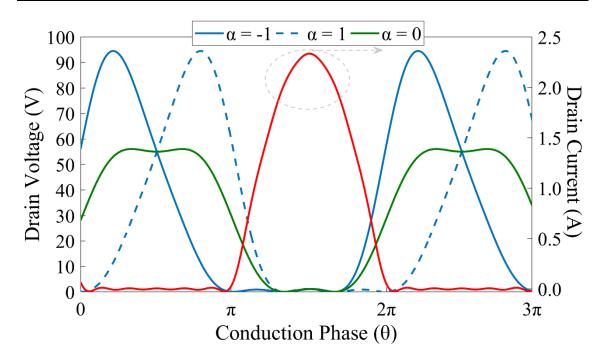

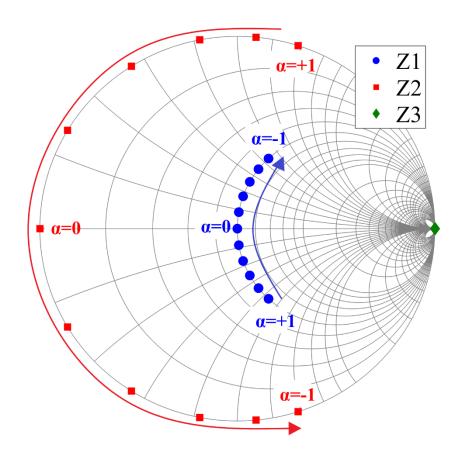

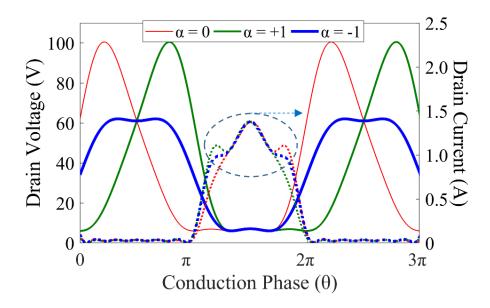

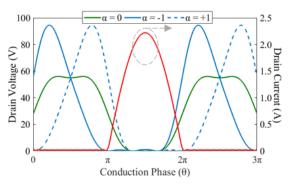

The continuous class-F (CCF) mode has been introduced through waveform engineering, based on the class-F mode, by extending the voltage waveforms definition when multiply with continuous operator, 1-  $\alpha \cos(x)$  [30, 31, 32, 33, 34, 26]. The derivation of the voltage waveform equation for CCF mode is shown in (2.3) where the definition of the Fourier expansion is up to the 4th harmonics. The current waveform for this mode remains as the half-rectified sinusoidal wave-shape with 180 ° conduction angle. The  $\alpha$  parameter changes the voltage waveform shape, as shown in Figure 2.6, peaking at more than 3 times the drain DC bias. The value of  $\alpha$  can only exist between -1 to +1 to abide with the device's physics, otherwise, beyond this value, the voltage waveforms starts to expand below 0 V. In this analysis, the definition of Vdc is 28 V and the current waveform is similar to the current waveform of the class-F mode shown from Figure 2.1. When the  $\alpha$  parameter increases or decreases to  $\pm 1$  value, even harmonics components appear in the voltage waveform, resulting in inductive and capacitive fundamental and 2<sup>nd</sup> harmonic impedances, as shown in Figure 2.7. The 3<sup>rd</sup> harmonic impedance remains at open circuit because the current waveforms defined from (2.2) do not contain any odd harmonics, which give infinite 3<sup>rd</sup> harmonic impedance when dividing the voltage by current waveform.

$$V_{ds}(\theta) = \left[ V_{dc} * \left( 1 + \frac{231}{200} \sin(\theta) + \frac{77}{400} \cos(3\theta) \right) \right] * (1 - \alpha \cos(\theta))$$

(2.3a)

$$V_{ds}(\theta) = V_{dc} * \left(1 - \alpha \cos(\theta) + \frac{231}{200} \sin(\theta) - \frac{539}{800} \alpha \sin(2\theta) + \frac{77}{400} \cos(3\theta) - \frac{77}{800} \alpha \sin(4\theta)\right)$$

(2.3b)

Figure 2.6. Ideal CCF mode waveforms.

Figure 2.7. Ideal CCF mode optimum fundamental, 2<sup>nd</sup> and 3<sup>rd</sup> harmonics impedances.

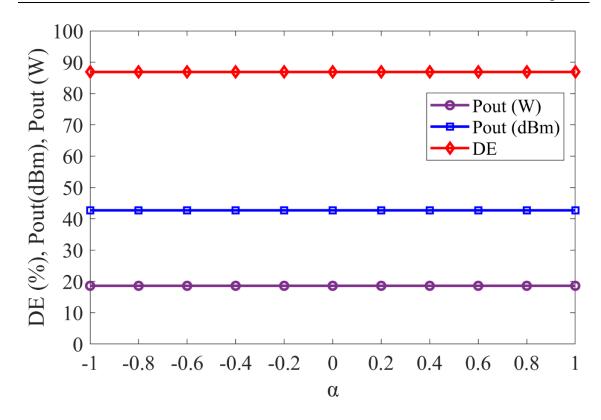

Figure 2.8. Ideal CCF mode performances.

The  $\alpha$  parameters rotates the optimum fundamental and  $2^{nd}$  harmonic impedances as shown in Figure 2.7. The  $\alpha$  rotations can be translated into the frequency dependences of PA operation, which can be used as the design space for a broadband PA. The ideal CCF mode provides a constant high efficiency and output power, equal to the performances of class-F mode, but is extended for the whole range of  $\alpha$ . Figure 2.8 shows the DE and Pout values that are constant at 86.9 % and 42 dBm across entire range of  $\alpha$  values. The DE value depends on the number of harmonics contained in the definition of voltage and current waveforms, whilst the Pout value depends on the value of Vdc and Imax from the current and voltage waveform initialisation. The full calculations to obtain the performances for the ideal CCF mode using MATLAB is shown in the Appendix 1.

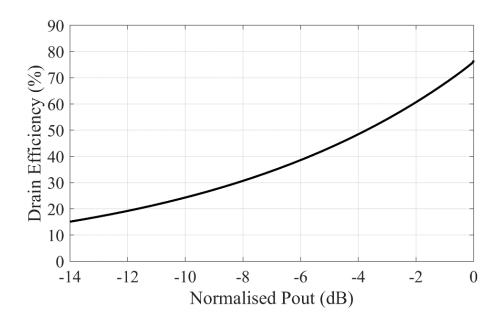

#### 2.3 Efficiency Enhancement Techniques Over Dynamic Range

Although the harmonic tuned PA modes such as the class-F and CCF can improve the efficiency performance, referring back to the waveform theory, high efficiency can only be achieved at the peak power level, where these waveforms are initially defined. The efficiency drops when the input and output power to the PA is backed-off, because the load-line is contracted. Figure 2.9 shows the typical class-AB PA performances over normalised output power level, reaching as low as 30 % at 8 dB power back-off. This value is relatively small when compared to the peak performances. Considering when the actual LTE signal is applied to the PA, the average output power will be at -7.6 dB from the peak, reaching down to -12 dB, resulting into a very low efficiency PA. Moreover, the PAPR for a 5G signal can be expected to be up to -15 dB. Several efficiency enhancement techniques have been introduced to enhance the PA efficiency, not only at the peak, but also at the back-off power level.

Figure 2.9. Typical DE vs normalised Pout for class-AB PA.

#### 2.3.1 Doherty Power Amplifier

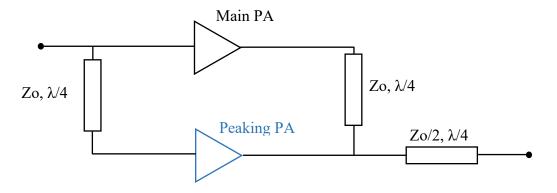

The Doherty power amplifier was introduced by W. H. Doherty at the Bell Telephone Laboratories, dating back to 1936 [35], to improve the efficiency of very highpower broadcasting transmitters using vacuum tubes. The classical Doherty PA architecture consist of 2 parallel and identical PAs, that are the main/carrier PA and the peaking/auxiliary PA [12, 18, 35], as illustrated in Figure 2.10. The operations for this symmetrical Doherty PA are as follows. The input signal is split into each PA, where a  $\lambda/4$  line shifts the phase of the input signal to the peaking PA by 90 °. Power divider such as Wilkinson or hybrid type is usually used for the signal splitter. The main PA is biased typically at class-AB mode, meaning it is always turned on, producing a small signal gain. The peaking PA is biased in class-C mode, that is depends on a large RF signal for it to turn on. At low input power level, the peaking PA is turned off, producing zero current, while the main PA remains active. During this low input signal operation, the peaking PA has high impedance (presenting open circuit), while the main PA has impedances of 2\*Ropt due to the added  $\lambda/4$  line. The total output power is -6 dB from the maximum. At large input signal, the self-biasing on the peaking PA turns it on, reducing the optimal impedance seen by the main PA to Ropt. This operation creates a load-modulation seen by the main PA, in which at both states, the main amplifier is saturated. The maximum voltage of the main amplifier is constant at its peak between 0 dB to -6 dB total output power. The operation of the peaking PA actively load-pulling the main PA, through the  $\lambda/4$  line. Practically, delay lines are added at both the devices' input and output in order to balance the phase delay between the  $\lambda/4$  inverter line. Another  $\lambda/4$  line with Zo/2 characteristic impedance is added to restore the impedance back to 50  $\Omega$  load impedances.

Figure 2.10. Classical Doherty PA circuit diagram.

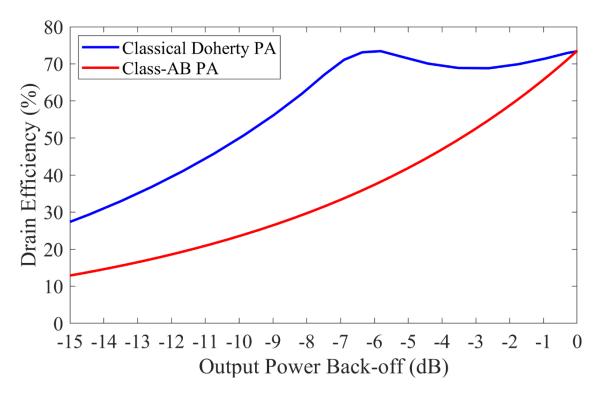

Figure 2.11 shows the efficiency enhancement of the classical symmetrical Doherty PA compared to class-AB PA over output power back-off range. The total power for both PAs is normalised to its peak power level. It can be seen that, for the class-AB PA, the efficiency reaches it maximum at peak power, however, it drops continuously as the output power is backed-off. In contrast, the Doherty PA has a minor efficiency degradation between 0 dB and -6 dB output power back-off, before it reaches the

Figure 2.11. Example of output power back-off on drain efficiency performances between classical symmetrical Doherty PA and class-AB PA.

maximum value of DE again at -6 dB back-off. The DE gradually decreases after this point. To compare, the DE can be greatly improved at the output power back-off from Doherty PA compared to the classical class-AB mode.

Over the years, the Doherty PAs have been a popular choices of the PA designer due to its good efficiency performance over output back-off ranges. The single-input and single-output configuration for this PA makes it preferable for use in RF front-end system. The efficiency performances of the Doherty PA over output back-off range can be extended with multiple stage configuration [18, 36, 37]. In the three stages Doherty PA, 2 peaking PAs are used, with 1 main PA, which reduces the dip of efficiency between maximum power and -6 dB output back-off as seen from classical symmetrical Doherty configuration. An asymmetrical Doherty PA is designed such that the output power of the peaking PA is much higher than the main PA [18, 38, 39]. The benefit of using asymmetrical Doherty PA is that the efficiency performances can be extended beyond the -6 dB output power back-off range, depending on the ratio of the main-to-peak PA power level.

More recently, the Doherty PA has been reconfigured such that the single input signal is not split to the main and peaking PA, instead each PA is driven separately and individually using a digital control [40, 41]. The advantage of using digitally control Doherty PA is that it removes the usual 3 dB losses of the power splitter, hence the gain of the overall Doherty PA can be increased. The phase shift between the input signal to the main and peaking PA can be controlled digitally, which is also beneficial to improve the overall bandwidth performances of the Doherty PA [40]. However, the complexity for this PA configuration could be a drawback for the cost of operation [41]. Additional controlled signal has to be in placed which also added another power consumption and increases the size of the overall circuit.

#### 2.3.2 Chireix Outphasing Power Amplifier

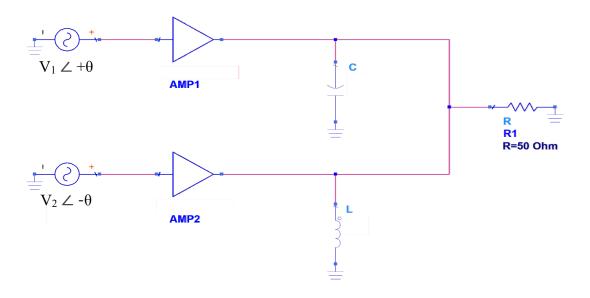

Another efficiency enhancement technique was proposed by Chireix in 1935 using an outphasing PA configuration [42]. The term outphasing in this PA meaning 2 non-isolating RF input that are feeding into equally non-linear operating PAs with equal amplitudes but opposite phases [43].

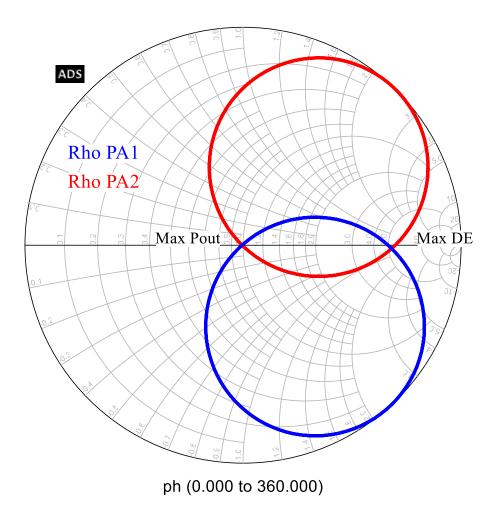

At a specific outphasing angle introduced to the PA's inputs, the reactive element of the load impedances can be cancelled using the shunt reactive elements as shown in Figure 2.12. The operation of sweeping the outphasing angle from the input signal introduces load modulation seen by both PAs, as illustrated in Figure 2.13. The modulated load impedances varies between the optimum Pout impedance to the optimum DE impedance. Strategically, the compensation and the combiner network are designed such that, they will present load modulated impedances to each device, in track with the optimum output power and efficiency of each PA, when the outphasing angle of the RF input is swept [44, 45]. Due to the separation between the optimum power and efficiency of the transistor device, the peak efficiency is obtained at the load impedances where the output power is backed-off (OPBO points).

Figure 2.12. Chireix outphasing PA configuration with compensation network.

A packaged integrated Chireix outphasing PA is designed in [46, 47], with reduced size of the overall PA, where the combiner network is designed using transformers that is implemented using bondwires. A compensation network using offset transmission lines, such as in used Doherty PA, is included in the outphasing PA designs in [48, 49] to replace the ideal compensation network using a shunt capacitor and inductor. A combination of Doherty and Outphasing in a single PA, or also called DOPA, extended the operational bandwidth of a typical narrowband Doherty PA and outphasing PA [40, 50]. The PA works in outphasing mode at back-off power, while switching to Doherty mode at the peak power. A self outphasing Chireix PA is designed in [51], where only single input is required for the outphasing PA, that reduces the complexity for the PA operations.

Figure 2.13. Impedances seen by each outphasing PA with compensation network as a function of outphasing angle.

#### 2.3.3 Envelope Tracking

Typically PAs are operated with a fixed supply voltage. The envelope tracking power amplifier operates on the basis of shifting the load-line when the drain bias of the transistor device is reduced, with the same slope [12, 18, 52]. The output power is reduced, however, when the device is operated with compression, the efficiency is maintained high. Figure 2.14 shows the movement of the load-line when the drain bias voltage is reduced. The envelope tracking PA can be used to improve the efficiency at the back-off power by modulating the DC supply voltage to track the envelope of the input modulated signal. A DC modulator is used to detect the envelope of input or output modulated signal, which is then used to vary the drain DC voltage supply. In return, the DC bias is reduced for low output power, while keeping the device operated at saturation, which increases the overall efficiency.

Figure 2.14. Load-line when changing the drain bias voltage.

#### 2.4 Chapter Summary

This chapter has described the efficiency enhancement technique for PA design which is the crucial aspect that has driven the overall research within the PA community in recent years. The PA efficiency at the peak power can be improved through harmonic tuning such as in the class-F, inverse class-F and continuous class-F mode. In fact, the fundamental and harmonic impedances have to be carefully chosen to obtain the optimum efficiency performances at the peak power. Other continuous modes that are worth mentioning is the continuous class-B/J and the duality of CCF mode; the continuous inverse class-F mode [53, 54, 55]. PA designs using these modes improves the overall performances across wide bandwidth. Moreover, the input harmonics can also be tuned to improve the drain efficiency and improve the linearity of the PA [56]. The most common techniques used by PA designers for harmonic tuning PAs is to evaluate the transistor performances using load-pull, where the load impedances presented to the device are varied systematically. Active load-pull measurement have been introduced [57, 58, 59] to control fundamental and harmonic impedances presented to the device for the device measurement. More recently, a fast active load-pull measurement [60, 61, 62] improved the time taken for the necessary measurement to only few seconds, giving the PA designer the advantage of being able to evaluate transistor performances more accurately and more quickly.

Over the years, the complexity of the modulated signal used in communication systems has increased, which affects the overall efficiency performance of the PAs used. Several efficiency enhancement techniques have been introduced, dating back to the 1930s, where the Doherty PA and the outphasing PA are introduced. Recently, these PAs together with and the envelope tracking PA, have been widely investigated, because they are considering to be deployed in the 5G communications system. These PAs improve

efficiency at the output power back-off ranges, compared to for example, a typical single stage class-AB PA. More recently, a load-modulated balanced amplifier, or LMBA has been introduced, that is based on a balanced amplifier concept, with an additional controlled injection signal combined at the output through a hybrid couple, to actively load-modulate the PA for higher efficiency at back-off power [63, 64] and which operates over wide bandwidth.

## Chapter 3

# CCF Mode with I-V Knee Interaction

#### 3.1 Introduction

To model a realistic transistor operation using the output waveforms, the knee clipping region should not be ignored. The knee region affects the device's load-line from the interaction between current and voltage waveform [12, 65]. Several recent publications have addressed the impact of integrating the operational knee voltage on PA design [66, 67]. The optimum impedance for the main PA in Doherty amplifier at the back-off changes due to non-zero knee voltage, affecting the Doherty performances if it not taken into account [68]. The soft turn-on knee characteristic of the transistor device is used to obtain separated power and efficiency contours of transistor device, to give a better understanding of its load-modulation characteristic [69, 17, 70]. In waveform theory, the realistic approach of modelling the transistor drain waveforms is to include the knee voltage [12], whereby the drain current waveform is now a function of the drain voltage waveform and the knee voltage, simplified in (3.1). In equation (3.1),  $Vds(\theta)$  and  $Ids(\theta)$  refers to the drain voltage and current waveform respectively. This I-V knee

relationship is used to model a realistic operation of transistor within the gain compression region, when the load-line is expanded into the non-linear knee region.

$$I_{ds,knee}(\theta) = \left(1 - e^{-\left(\frac{V_{ds}(\theta)}{Vknee}\right)}\right) * I_{ds}(\theta)$$

(3.1)

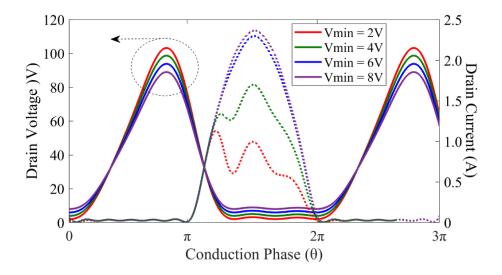

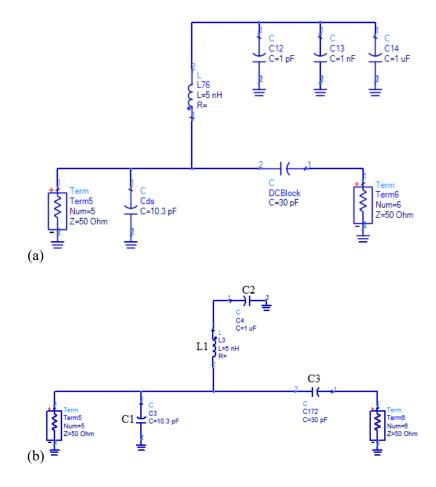

Figure 3.1. CCF mode waveforms with original I-V knee interaction.

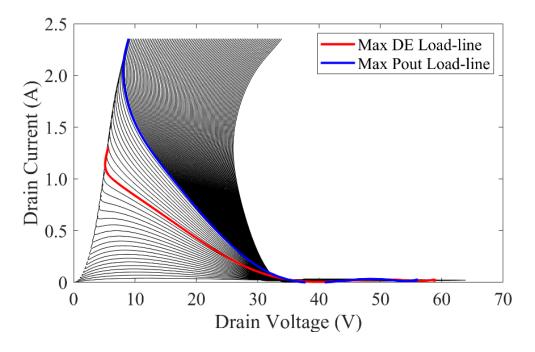

Figure 3.2. CCF mode load-lines with original I-V knee interaction.

An example for class-F waveforms operated with I-V knee scaling are as follows. First, the drain voltage waveforms are scaled to be within the knee boundary by adding

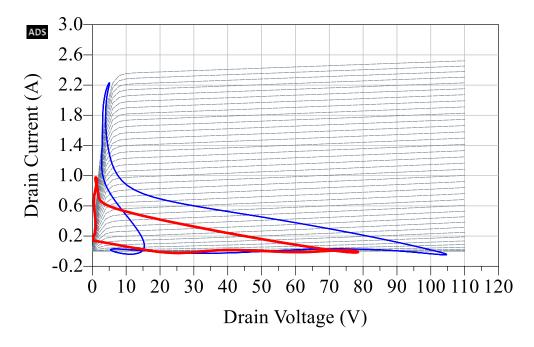

voltage offset so that the minimum voltage is above zero but less than the knee voltage. The knee voltage is 8 V, taken from 10 W GaN HEMT Wolfspeed device. Using eq. (3.1) above and the resulting waveforms are shown in Figure 3.1, where the current waveforms are now clipped and truncated by the drain voltage waveform and the knee voltage. Figure 3.2 shows the load-lines plotted relatives to the DCIV curve for the device, which are not in-line with the knee-boundary and have limited maximum current, *Imax*.

This chapter addresses this issue by reformulating the I-V knee scaling in (3.1) for compressed CCF mode waveforms. The new performances for the CCF mode by including the knee interaction are obtained through this new emulation and supported by the device verification in simulation and measurement. Passive load-pull simulation is performed in Keysight's ADS by presenting a load tuner at the device's output that defines the fundamental and harmonics impedances. Load-pull measurements are performed on the device using an active load-pull system. In the active load-pull system, fundamental and harmonic signals are injected into the device at the load, to control the impedances presented to the device respectively [57, 58, 59]. This chapter expands upon the first half of the published conference paper accepted in the International Microwave Symposium 2019 [71].

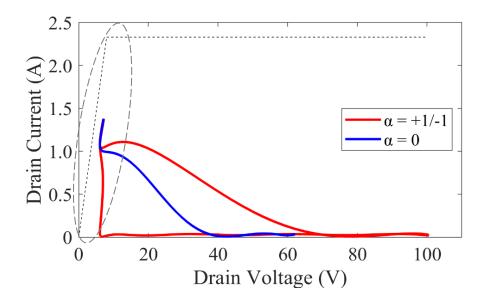

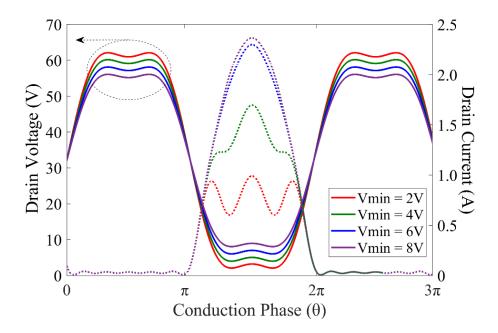

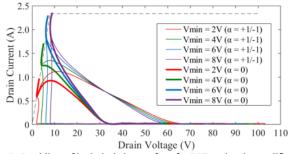

#### 3.2 Reformulation of CCF Mode with I-V Knee

Modifications are introduced to both voltage and current waveforms to accurately represent these waveforms in a compressed CCF mode through the load-line analysis. In (3.2),  $\kappa$  is introduced to scale the magnitude of fundamental and harmonic components of the voltage waveform to emulate the compression of the device outputs. The default value of  $\kappa$  is 1 and it is valid only for  $1 \le \kappa \le 4/3$  to keep the voltage waveform above zero to

abide the device's physic as limitation. At the default value  $\kappa = 1$ , the device is in the linear region, and the minimum of the voltage waveform is equal to the knee voltage of the device, defined here at the drain voltage value (8 V) at the maximum drain current, *Imax*. As  $\kappa$  increases, the device is further compressed, and it enters the non-linear knee region.

$$V_{ds,new}(\theta) = \left(Vdc - \frac{Vknee}{2}\right) * \left(1 + \kappa * \left(-\alpha cos\theta + \frac{231}{200}sin\theta\right) - \frac{539}{800}\alpha sin2\theta + \frac{77}{400}sin3\theta - \frac{77}{800}\alpha sin4\theta\right)\right) + Vknee$$

(3.2)

$$I_{ds,new}(\theta) = \left(1 - e^{-\left(\frac{V_{ds,new}(\theta)}{\gamma}\right)}\right) * I_{ds}(\theta)$$

(3.3a)

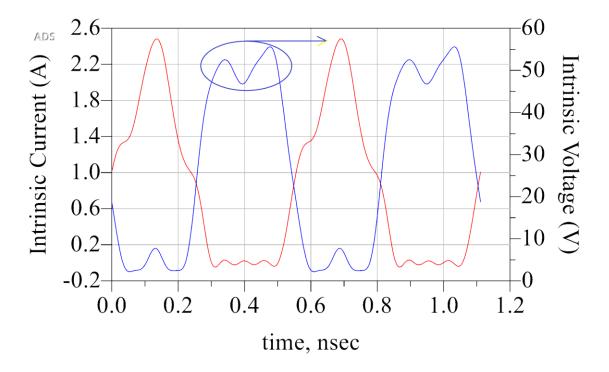

In [12], *Vknee* has a constant value, whereas [69, 17, 70] suggested a varying *Vknee* that leads to separation of power and efficiency optimum impedances. The current waveform equation is modified, shown in (3.3). In (3.3a), the knee voltage scaling is a function of the minimum from the voltage waveform ( $V_{ds,new}$ ), *Vmin*, that can be represented by a Piecewise function, detailed in (3.3b). This Piecewise function is introduced, as a simple solution to keep the load-lines in track within the knee boundary. Figure 3.3 and Figure 3.4 show the waveforms of the modified CCF mode for  $\alpha = 0$  and  $\alpha = 1$ , respectively. These waveforms are based on the minimum of the voltage waveforms that are set to 2 V, 4 V, 6 V and 8 V respectively, by varying the  $\kappa$  parameter. The voltage waveforms expanded, reaching a minimum value towards 0, as  $\kappa$  is increases. Consequently, the current waveforms interact with the voltage waveforms movement within the knee boundary, resulting into current waveforms clipping. The movement of

these load-lines is now tracking with the knee boundary region of the device (shown on the grey dotted lines), as shown in Figure 3.5.

Figure 3.3. Emulated CCF waveforms ( $\alpha$  = 0) using modification of I-V knee scaling with compression, by varying the  $\kappa$  parameter to change the minimum of the voltage waveform, Vmin, to be within the knee boundary.

Figure 3.4. Emulated CCF waveforms ( $\alpha = 1$ ) using modification of I-V knee scaling with compression.

Figure 3.5. Emulated CCF load-lines using modification of I-V knee scaling with compression.

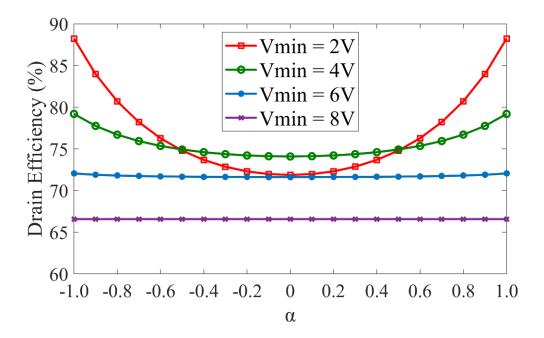

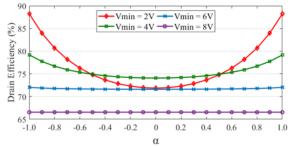

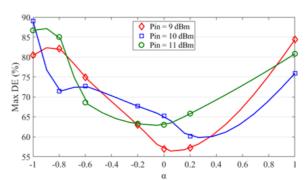

Figure 3.6. Emulated CCF mode drain efficiency at different level of compression within  $\alpha$  spaces.

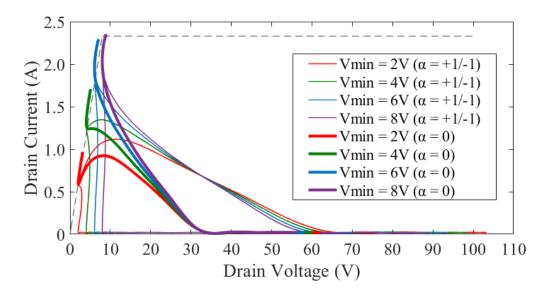

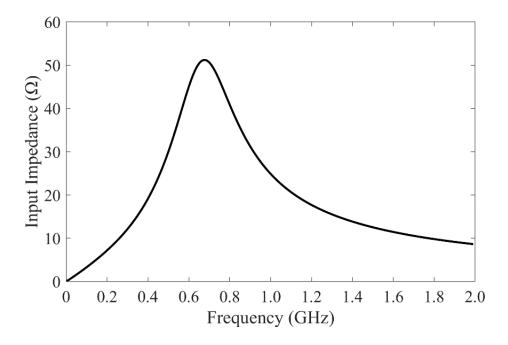

Figure 3.6 shows the new emulated drain efficiency of the CCF mode with compression from the generated waveforms in Figure 3.3 and Figure 3.4. This efficiency calculation was also extended to cover the entire range of the  $\alpha$  space. The drain efficiency is constant across  $\alpha$  space when the minimum of the voltage waveform is just at the knee

voltage, 8 V, similar to the ideal CCF behaviour in [31, 33, 26]. However, the value of the DE is relatively low, due to a big difference between voltage and current waveforms. The DE increases as the load-lines moves further into knee region, reaching its peak when  $\alpha = -1/+1$ . The drain efficiency is at minimum when  $\alpha = 0$ , as in Class-F mode. Essentially, the new peak drain efficiency changes when the knee voltage is accounted and the device is compressed, showing a symmetrical behaviour around  $\alpha = 0$ . The full calculations for the CCF mode operated with I-V knee interaction through MATLAB is shown in the Appendix 2.

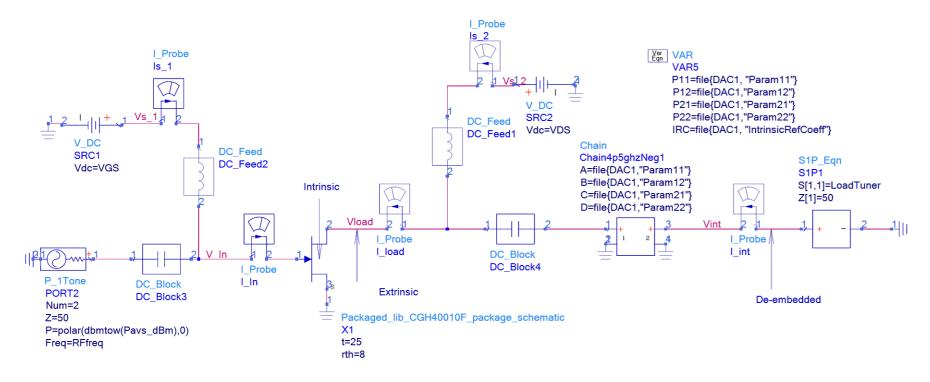

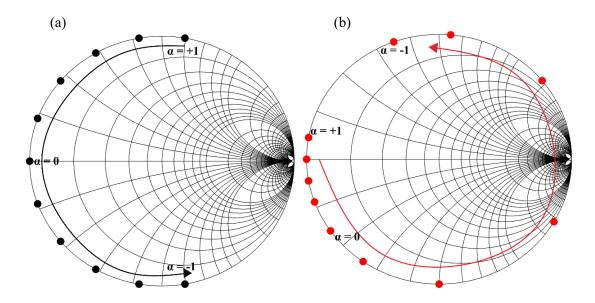

## 3.3 Simulation of CCF Mode with Compression on 10 W GaN Device

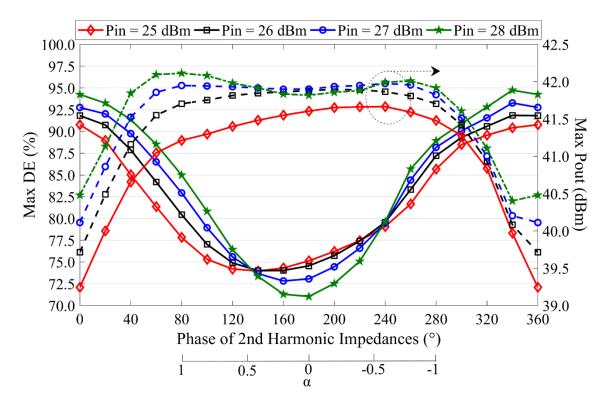

A 10 W GaN HEMT packaged device from Wolfspeed (CGH40010F) is used to test the new CCF theory in the previous section. ADS load-pull simulation is performed on the device's non-linear model and the device is de-embedded at the output plane so that the fundamental and harmonics load impedances are presented at the device's intrinsic drain plane. The device is de-embedded using a static de-embedding file which is used in the ADS simulation. To simulate CCF mode on the 10W device, the fundamental load impedances are swept across the entire region of the Smith chart while the 2<sup>nd</sup> harmonic load impedances are swept from 80° to 280° around the edge of Smith chart. The variation of 2<sup>nd</sup> harmonic impedances equals the α space of CCF mode, which for this device,  $80^{\circ}$ ,  $180^{\circ}$  and  $280^{\circ}$  is equal to  $\alpha = +1$ ,  $\alpha = 0$  and  $\alpha = -1$  respectively. The 3<sup>rd</sup> harmonic impedances are kept constant at an open circuit for all simulation points. The device is biased at 28 V and -3.2 V at drain and gate respectively (Idq=13 mA) through ideal DC feed and ideal DC blocks are used at both device's input and output to contain the DC in the PA circuit only. The transistor is driven into compression by an RF input of 2.0 GHz with 50  $\Omega$  source impedances and Pin = 25, 26, 27 and 28 dBm. Figure 3.7 depicts the schematic of the passive load-pull simulation performed in ADS. The load tuner shown on the right-side in this figure consists of several sets of equations, that set the matrices of fundamental impedances across the entire Smith chart, 2<sup>nd</sup> harmonic impedances swept across the edge of the Smith chart and 3<sup>rd</sup> harmonic impedance set to open circuit.

Figure 3.8 shows the maximum output power exceeds 10 W (40 dBm) for all swept input powers and phases of  $2^{nd}$  harmonic impedances within the  $\alpha$  space (approximately between  $80^{\circ}$  to  $280^{\circ}$ ). The device achieved its saturated output power (>15 W) at about 4

Figure 3.7. Schematic of ADS passive load-pull simulation.

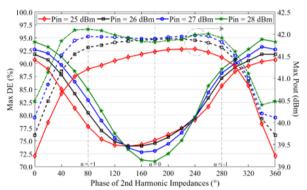

dB gain compression for a source input power of 28 dBm. The changes of maximum output power with phase of  $2^{nd}$  harmonic impedances are minimum when the device is compressed and has reached its saturation point. The maximum DE shows symmetrical changes with the phase of the  $2^{nd}$  harmonic impedances around  $180^{\circ}$ . Within the  $\alpha$  space, DE is highest at the boundaries and lowest for in the middle ( $\alpha = 0$ ) of the  $\alpha$  space. The overall variation of DE approaches 20 % and is in good agreement with the emulated data in Figure 3.6. Although maximum DE continue to increase outside the restricted  $\alpha$  spaces, the maximum Pout shows a steep drop indicating a restriction for 2nd harmonics impedances that can be utilised for the CCF mode.

Figure 3.8. Peak DE and Pout from load-pull simulation on 10 W GaN device at CGP by varying phase of 2<sup>nd</sup> harmonic impedance along the edge of Smith chart.

### 3.4 Measurement of CCF Mode with Compression on 10 W GaN Device

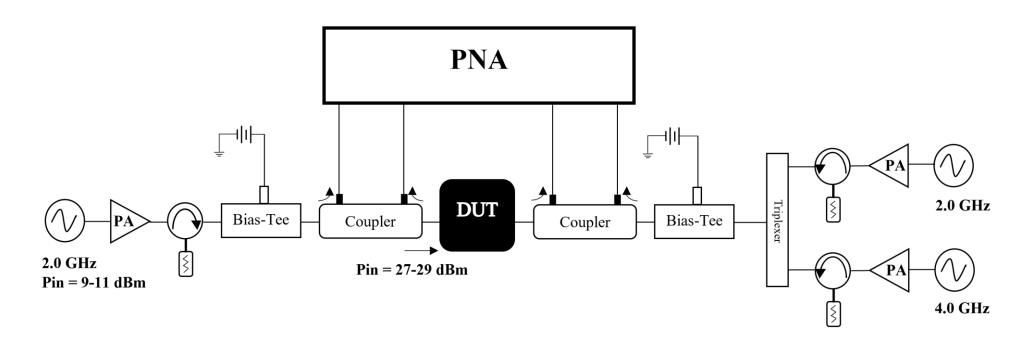

The device is measured in a test fixture with an active load-pull system to confirm with the previous ADS simulation. The device is biased with 28 V and -2.85 V at the drain and gate respectively (Idq = 13 mA) through bias tees. CW signal from a signal generator with 50  $\Omega$  characteristic impedance at 2.0 GHz is connected to the device's input through a driver amplifier. The magnitude of the signal generator is varied from 9 dBm to 11 dBm. Two signal generators are connected to the device output through two separate driver amplifiers, to control the fundamental and  $2^{nd}$  harmonic impedances presented to the device package plane. Fundamental impedances are swept throughout the Smith chart while the  $2^{nd}$  harmonic impedances are controlled at the edge of Smith chart with different phases. Meanwhile the  $3^{rd}$  harmonic impedances are not controlled due to their small impact on the device performances [72]. All these impedances are presented and measured at the device's package plane within the test fixture using short, open, line and thru (SOLT) calibration [73]. Figure 3.9 shows the set-up for this active load-pull measurement.

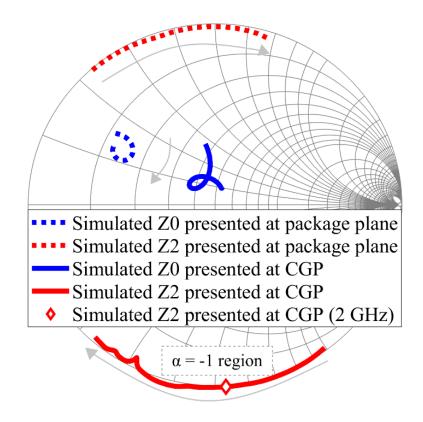

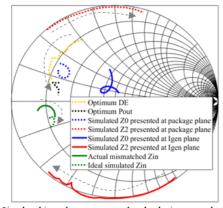

Due to the package's parasitic effect on the transistor, the phases of  $2^{nd}$  harmonic impedances from the edge of the Smith chart that have to be presented at the package plane are shifted from the phases presented at the device's current generator plane, which were used in the previous simulation. These phases rotation representing  $\alpha$  space (-1, 0 and +1) at the device's current generator plane from the package plane are: 100°, 200° and 165° respectively at 2.0 GHz, as depicted in Figure 3.10.

Figure 3.9. Schematic for active load-pull measurement set-up.

Figure 3.10. Simulated 2<sup>nd</sup> harmonic impedances presented at (a) the CGP and shifted to (b) package plane due to packaged parasitic effects.

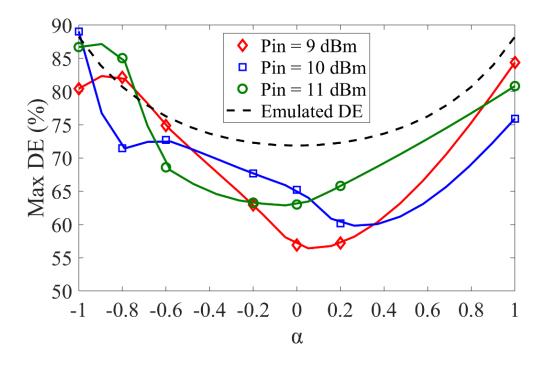

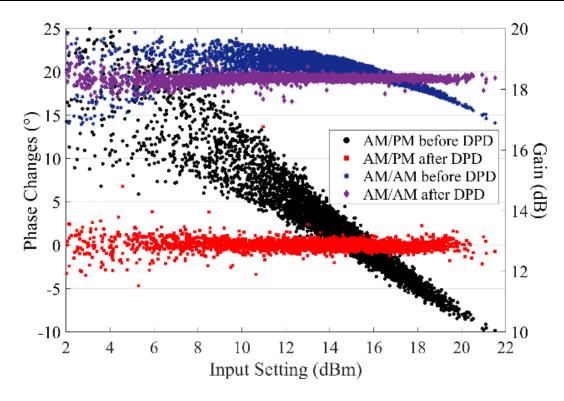

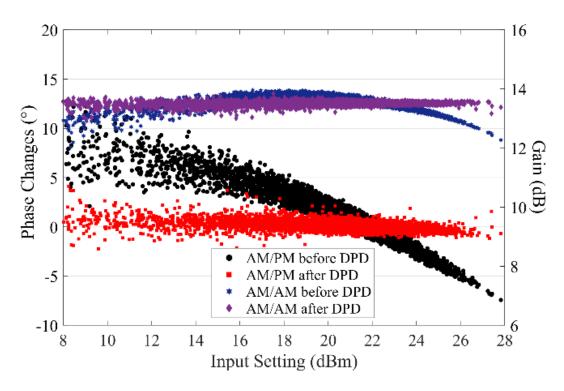

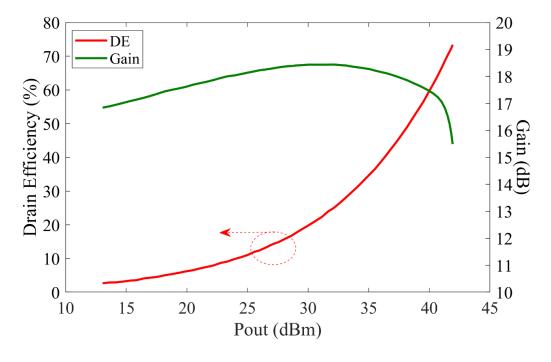

Figure 3.11 shows the maximum DE obtained from each fundamental load-pull with 7 different phases of  $2^{nd}$  harmonic impedances chosen that are normalised to the  $\alpha$  space at 3 input drive levels. Maximum Pin = 11 dBm from signal generator provides up to 29 dBm to the device input after been amplified by the driver amplifier. Minimum DE are measured at  $\alpha$  close to 0 for all 3 input drives which varies from 57 % to 63.7 % with different input setting. The peak DE are measured at both ends of the  $\alpha$  range. The difference between max DE obtained at  $\alpha$  = -1 and  $\alpha$  = 0 for Pin=11 dBm is 23 %, which is slightly larger than the emulated and simulated data. Especially for  $\alpha$  = 0 case, this difference between the measured peak DE and the simulated DE could be due to the lack of  $3^{rd}$  harmonic impedance control. Nevertheless, the variation of peak DE across  $\alpha$  is well match with the emulated results.

Figure 3.11. Measured and emulated peak DE from fundamental load-pull of 10 W packaged device with respect to α space and Pin from signal generator.

#### 3.5 Chapter Summary

This chapter has concluded, for the first time, the new performances of the CCF mode by including the I-V knee interaction on its waveforms. This new theoretical analysis has reformulated the ideal CCF mode waveforms to include the non-linearities from the knee boundary region, that result in drain current waveforms clipped by both voltage waveform and the knee voltage. When the device is operated with gain compression, the drain efficiencies are no longer constant across the  $\alpha$  space, instead, the peak efficiencies are reached at  $\alpha$  = -1/+1. This new CCF behaviour has been successfully simulated and measured through fundamental load-pull while varying the phase of 2<sup>nd</sup> harmonic impedance across the edge of Smith chart, showing a good agreement with the theoretical prediction. The difference of the peak DE measured at  $\alpha$  close to 0 from Figure 3.11 can be improved by additional 3<sup>rd</sup> harmonic control on the active load-pull measurement by presenting open circuit to the CGP.

## Chapter 4

# Broadband 10 W GaN PA Design Based on CCF Mode with Compression

#### 4.1 Introduction

Chapter 3 introduced a reformulation of the CCF mode by introducing additional non-linear I-V knee interaction into the waveform theory. As the device is operated with compression, the knee interaction between the waveforms is unavoidable and must be taken into consideration. The drain efficiency is at the peak, only at the  $\alpha = \pm 1$ , and drops to the lowest value when  $\alpha = 0$ . Several publications have demonstrated the practicality of designing broadband PA using CCF mode by utilising the entire  $\alpha$  space for their broadband PA design [34, 74, 75, 76, 77, 78, 79, 80]. These broadband PAs, including other continuous PA modes in [81, 82, 83, 84, 85] are all measured at compression level, when the device is tested under CW excitation, meaning that the drain waveforms are operating within the knee boundary. The ideal performances of the CCF mode are no longer useful to evaluate the PA performances, when the realistic operation of the device is considered.

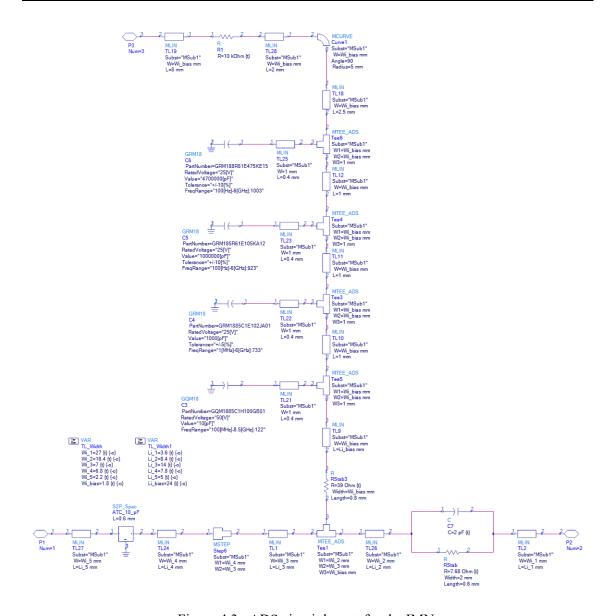

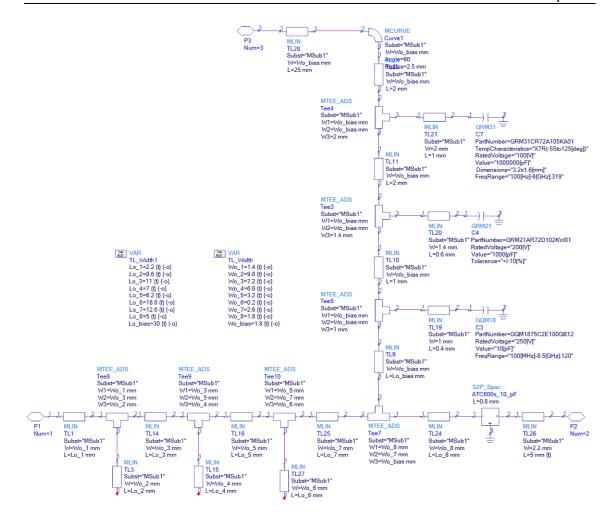

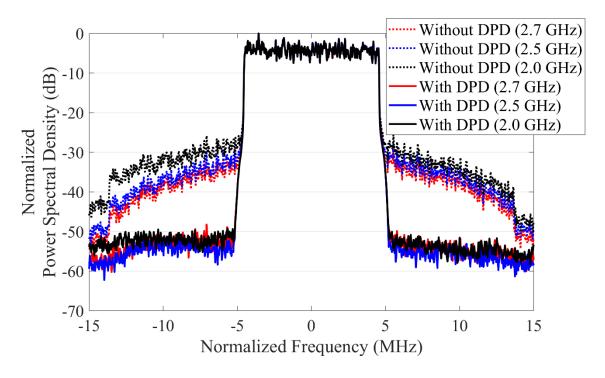

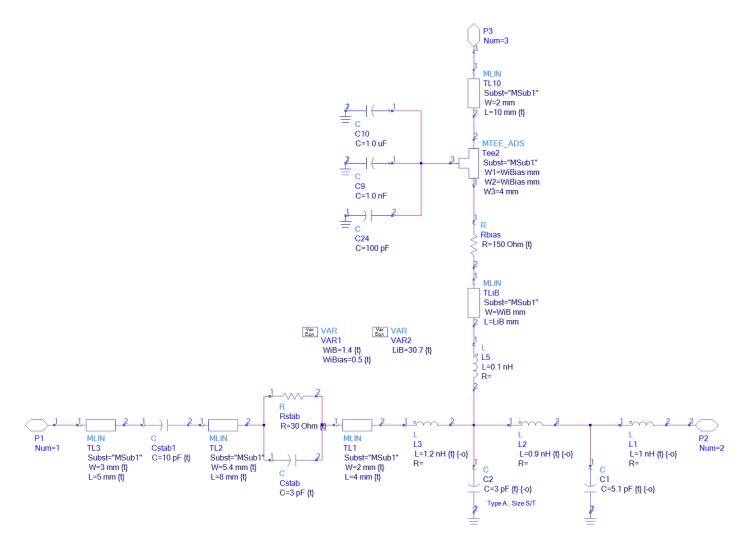

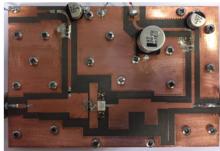

In this chapter, a broadband 10 W GaN PA is designed based on the CCF mode for broadband and high efficiency performance, by considering the symmetrical DE performances across the  $\alpha$  space described in the previous Chapter 3. Here, the phase rotation of  $2^{nd}$  harmonic impedances is restricted to lie along the edge of Smith chart within close range to  $\alpha = -1$  in order to keep the drain efficiency at the maximum. This chapter summarises as follows. Load-pull simulations with sweep  $2^{nd}$  harmonic impedances are performed on the 10 W GaN device model in ADS to obtain the  $\alpha$  design space, across the bandwidth. The PA is designed and fabricated with an optimised matching network that tracks with the fundamental and  $2^{nd}$  harmonics impedances optima across the targeted bandwidth (1.8 GHz to 2.7 GHz). The fabricated PA is tested with CW excitation and modulated signal to verify its performances. This chapter describes the final half of the published conference paper in International Microwave Symposium 2019 [71].

#### 4.2 Load-pull Simulation

Fundamental load-pull simulation with swept phase of the 2<sup>nd</sup> harmonic impedances is performed at the package plane of 2<sup>nd</sup> generation 10 W device from Wolfspeed (CG2H40010) [86] using the available non-linear behaviour device model, to determine the optimum impedance throughout the design bandwidth for the PA. In this simulation, the 2<sup>nd</sup> harmonic impedance is fixed at a point at the edge of Smith chart, while fundamental impedances is swept across the entire Smith chart. This simulation is repeated by changing the phase of the 2<sup>nd</sup> harmonic impedance to cover along all the region of the edge of the Smith chart. The impedance matching network is always rotating in a clockwise direction with increasing frequency, as the Smith chart. This rotation has

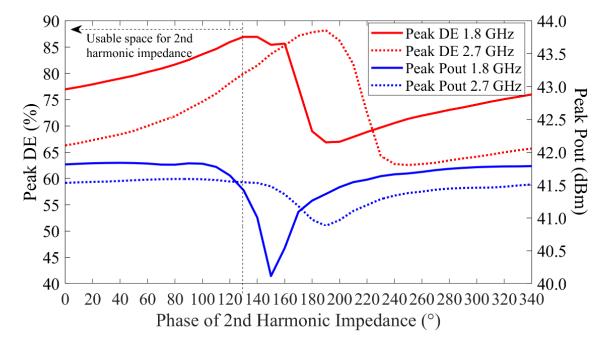

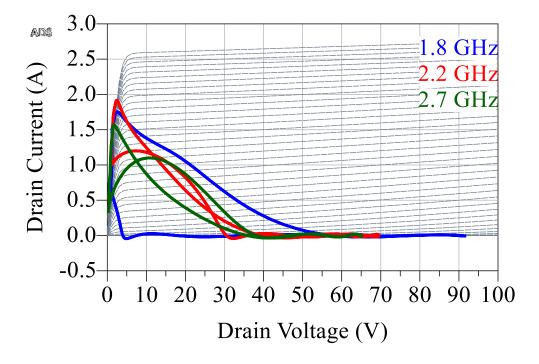

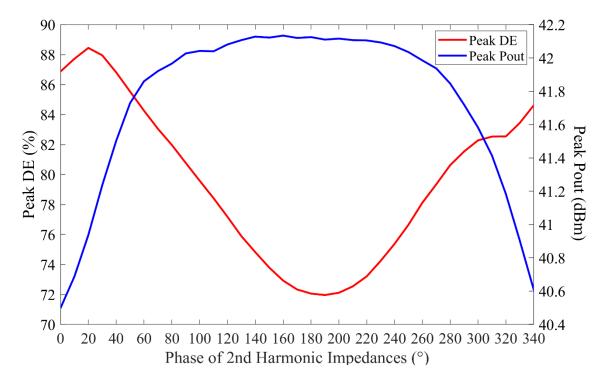

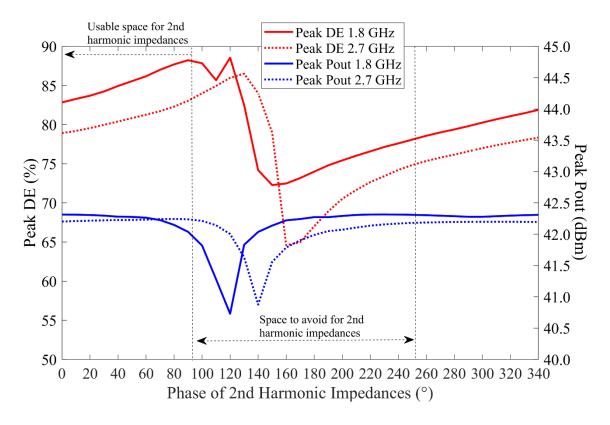

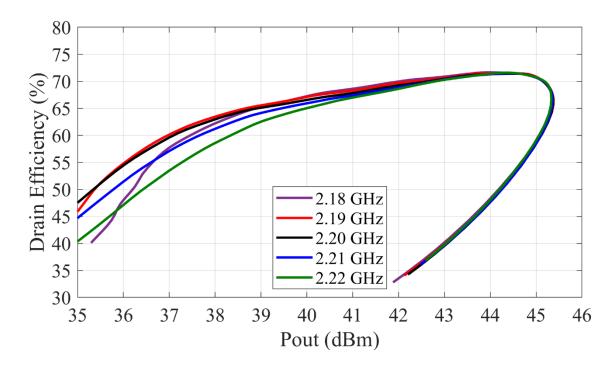

to be taken into consideration when designing the broadband output matching network to keep the  $\alpha$  rotation close to -1 only across the bandwidth, between 1.8 GHz to 2.7 GHz. Figure 4.1 shows the peak DE and Pout obtained from fundamental load-pull while varying phase ofthe  $2^{nd}$  harmonic impedance across the edge of Smith chart at lower and upper design frequency, 1.8 GHz and 2.7 GHz. The variation of peak Pout and DE with phase of the  $2^{nd}$  harmonic impedance indicates the  $\alpha$  space at the device's package plane. The  $\alpha$  space (-1, 0 and 1) for 1.8 GHz and 2.7 GHz is approximately 120°, 200° and 165°, and 170°, 240° and 210° respectively at the package plane.

Figure 4.1. Peak Pout and DE from load-pull simulation of 10 W GaN device with sweep phase of 2nd harmonic impedance.

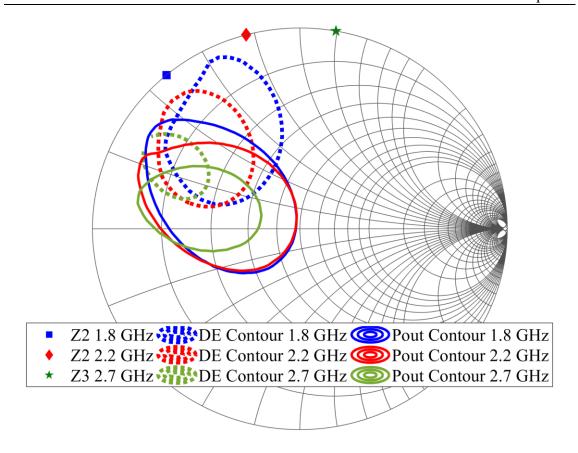

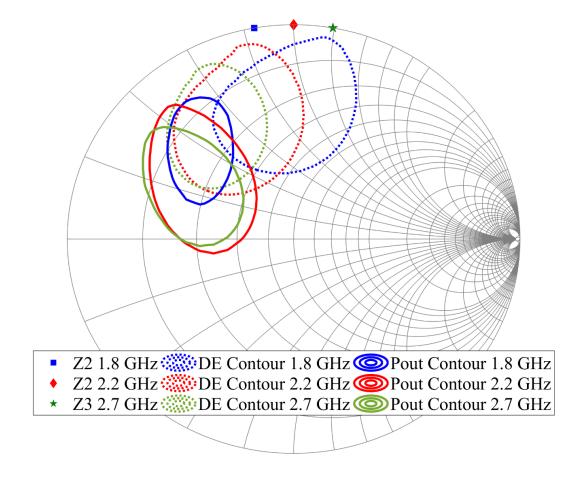

The results shown in Figure 4.1 indicates that the phase of  $2^{nd}$  harmonic for  $\alpha = -1$ rotates counter-clockwise on the Smith chart when the frequency increases from 1.8 GHz to 2.7 GHz (from 130 ° to 170 °). Therefore, the design space for the optimum phase of  $2^{nd}$  harmonic impedance for  $\alpha = -1$  has to start at 120 °, at 1.8GHz and it will rotate clockwise for higher frequency. Next, fundamental load-pull simulation is performed with fixed termination of 2<sup>nd</sup> harmonic impedance at selected frequency within the bandwidth: 1.8 GHz =  $1 \perp 130$ °, 2.2 GHz =  $1 \perp 105$ ° and 2.7 GHz =  $1 \perp 80$ °. The  $3^{rd}$ harmonic impedances are kept constant at open circuit across all frequencies. All these impedances are presented to the device's package plane during the load-pull simulation. Figure 4.2 shows the movements of Pout and DE contours (Pout = 40 dBm and DE = 70 dBm) %) across the 3 different frequencies. The Pout and DE contour show a larger area at 1.8 GHz because the setting for the  $2^{nd}$  harmonic impedance is at the optimum of  $\alpha = -1$ . On the other hand, the DE contours area becoming much smaller at higher frequencies because the  $2^{nd}$  harmonic impedance is not located at the optimum  $\alpha = -1$  region, as shown in Figure 4.1. This indicates the compromise that has to be considered when designing a broadband PA circuit. The area of Pout contour is reduced at 2.7 GHz because the peak Pout at this frequency dropped at the same gain compression shown in Figure 4.1. This is a well-known behaviour of a power transistor that has unstable performance over frequency [13, 18].

Figure 4.2. Simulated Pout contours (> 40 dBm) and DE contours (> 70 %) for different 2<sup>nd</sup> harmonic load impedances at 1.8 GHz, 2.2 GHz and 2.7 GHz.

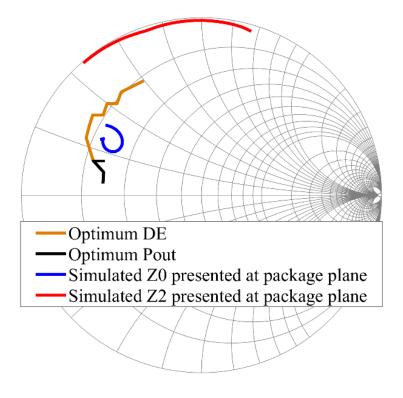

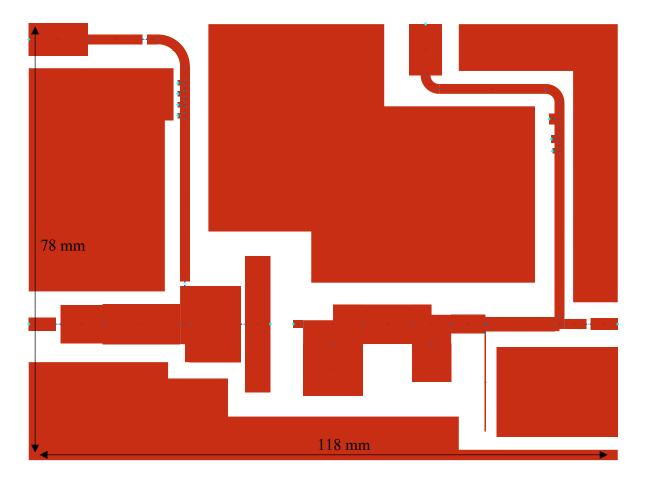

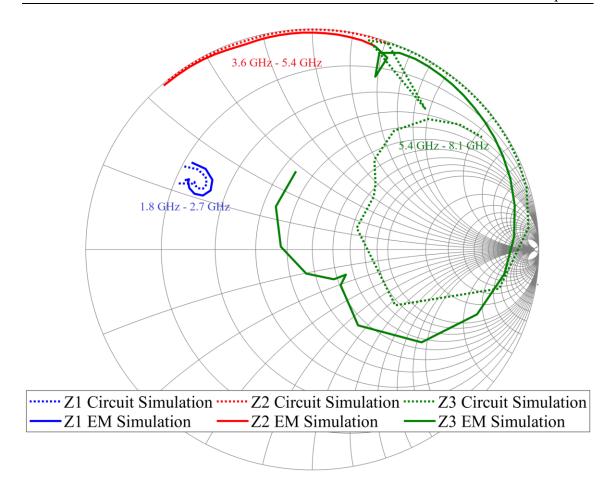

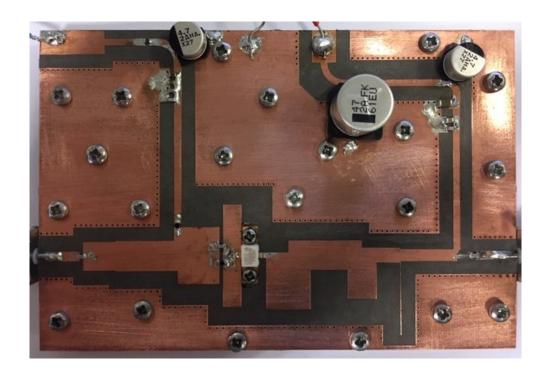

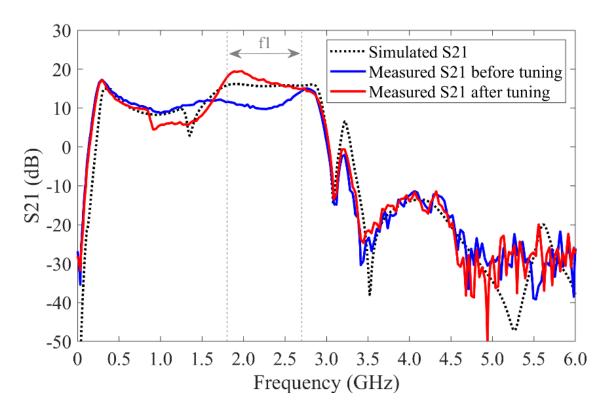

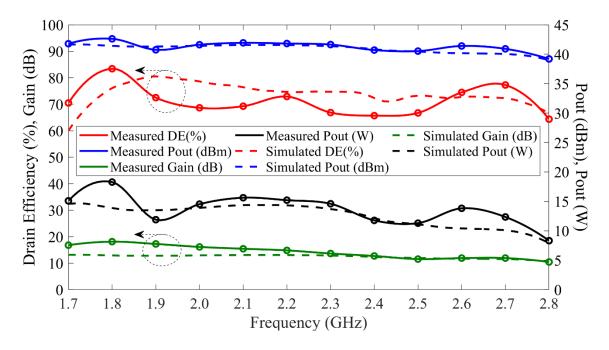

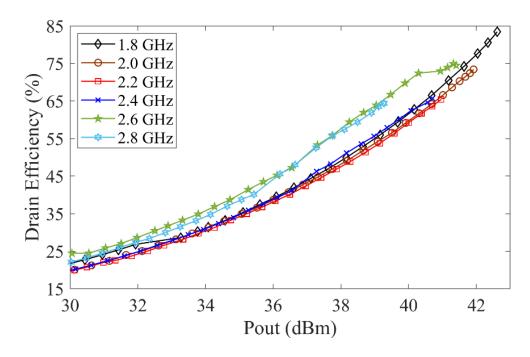

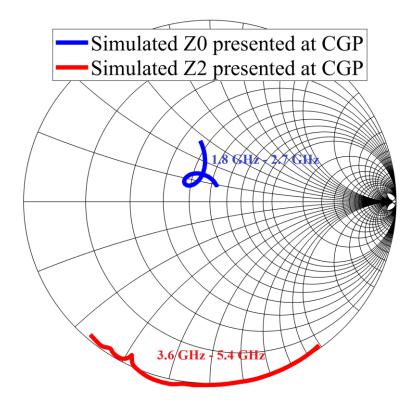

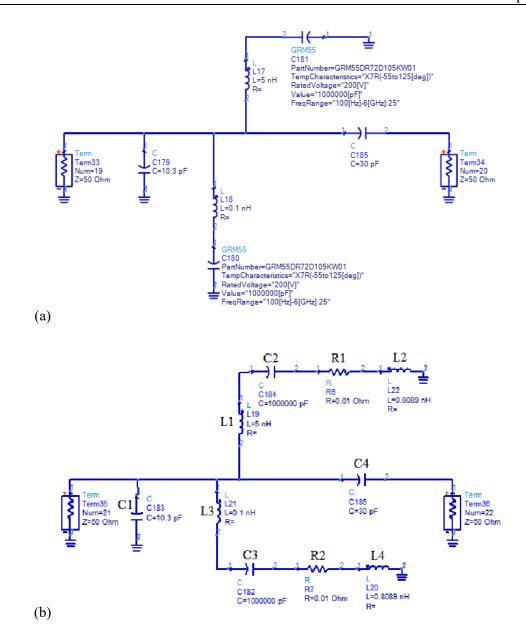

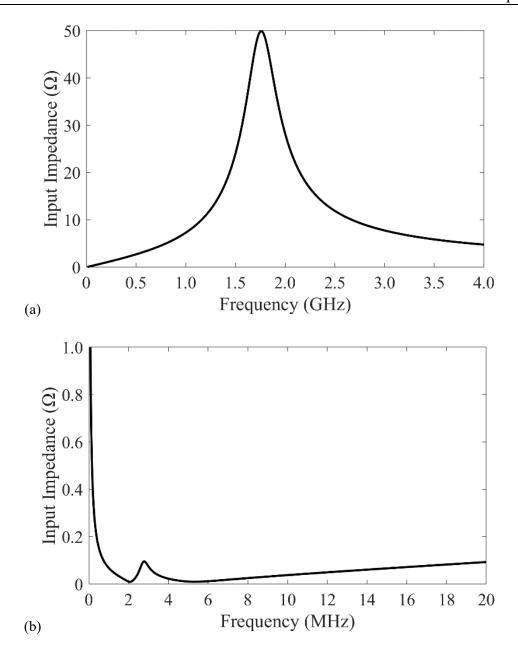

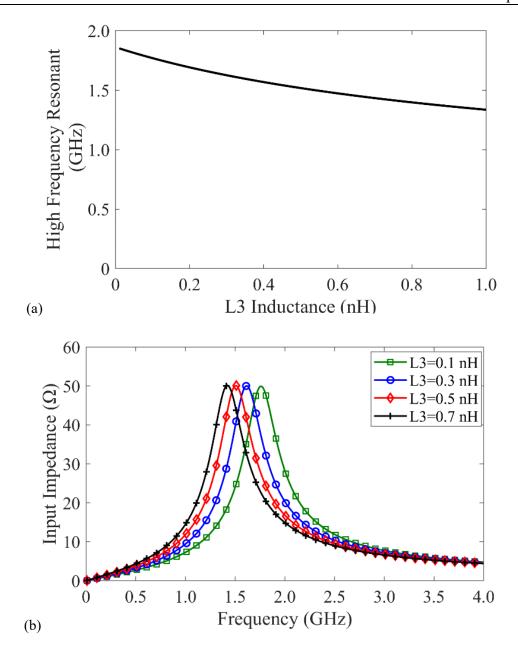

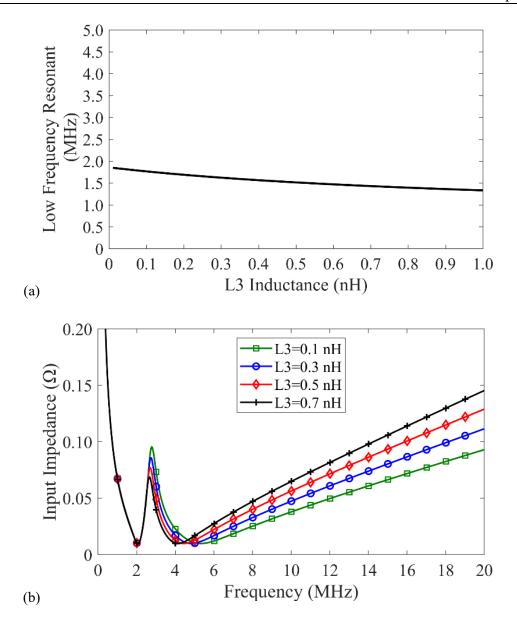

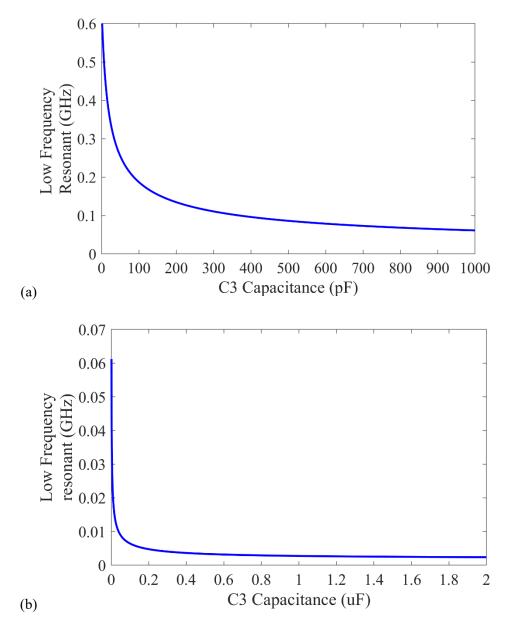

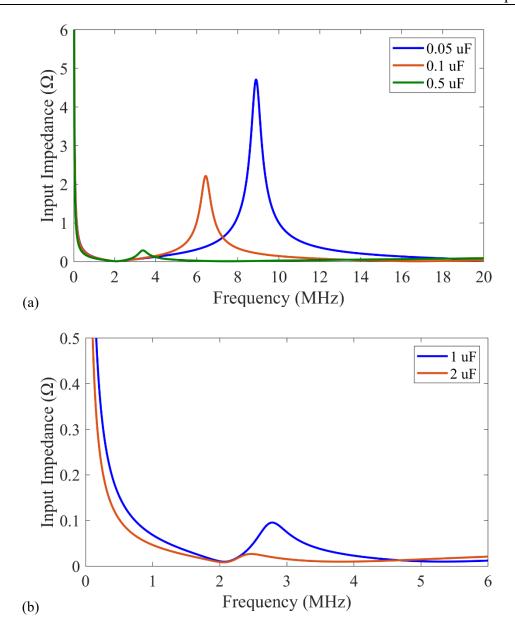

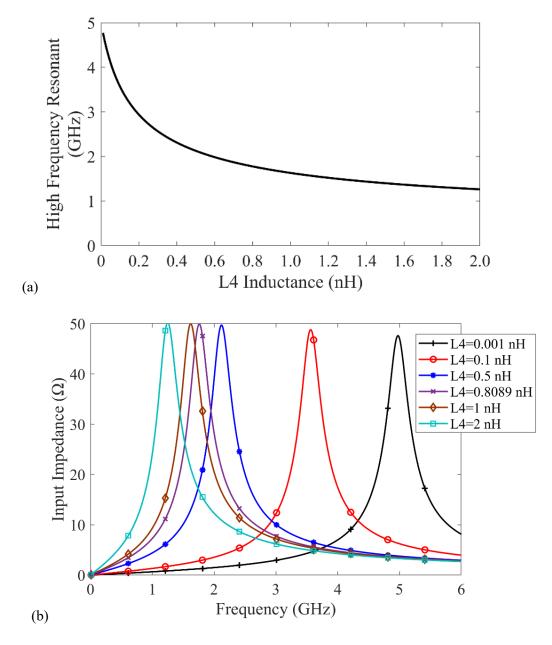

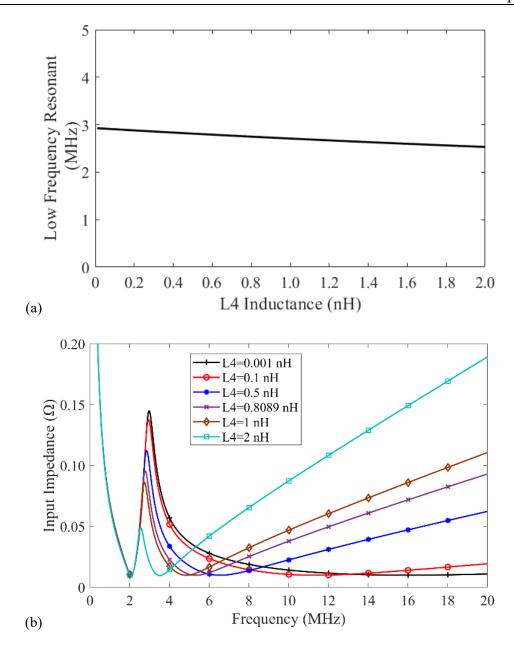

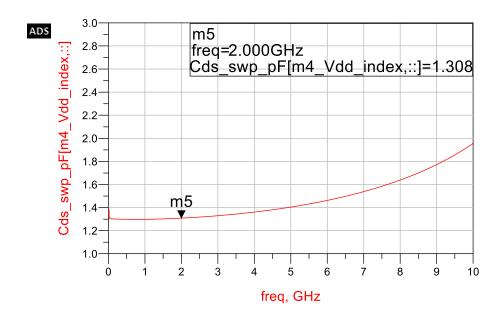

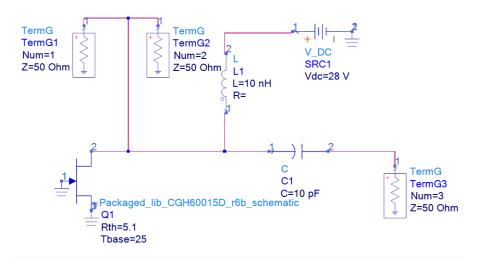

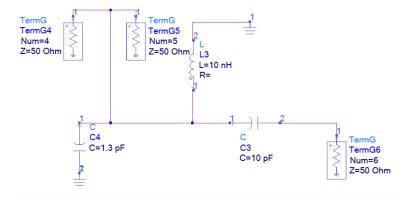

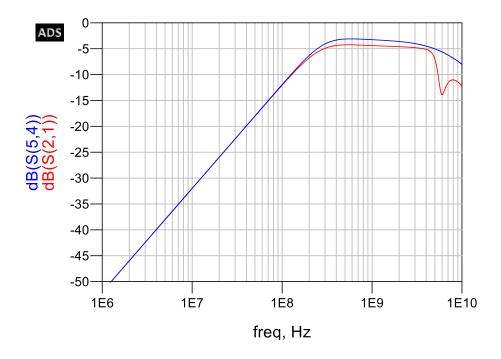

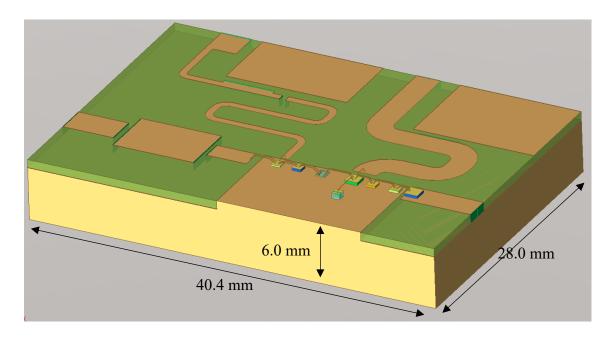

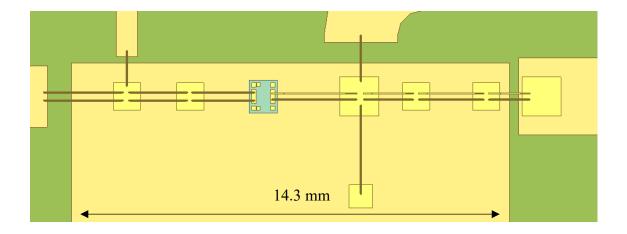

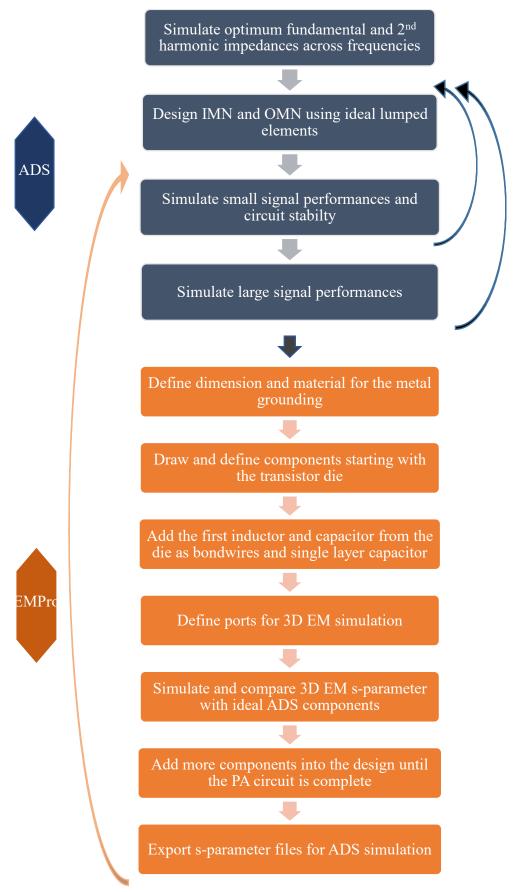

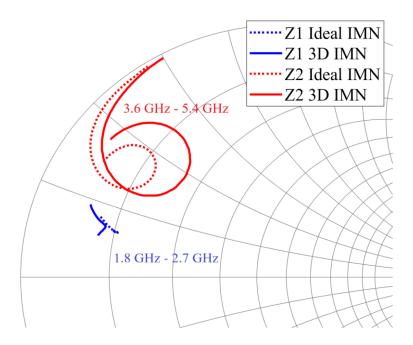

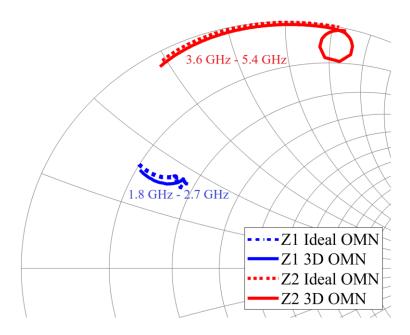

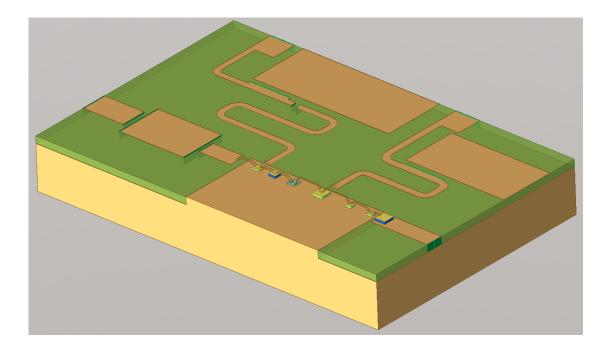

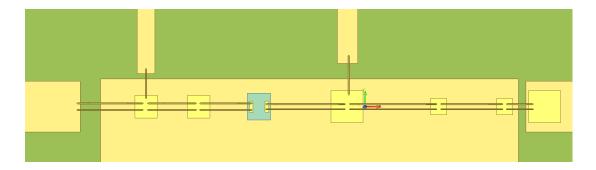

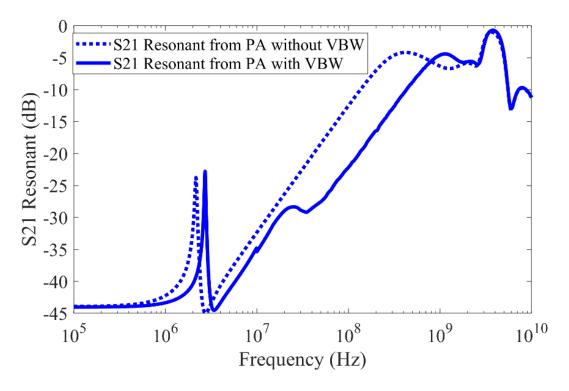

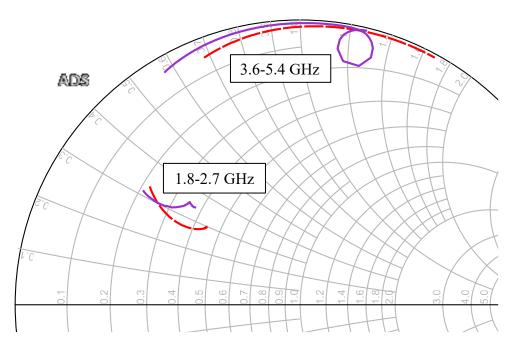

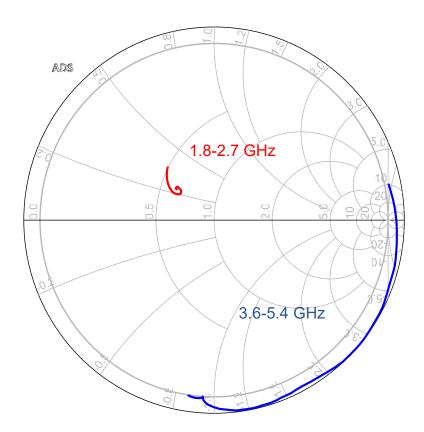

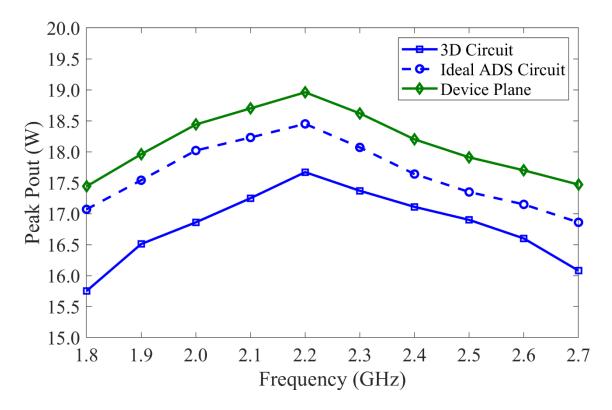

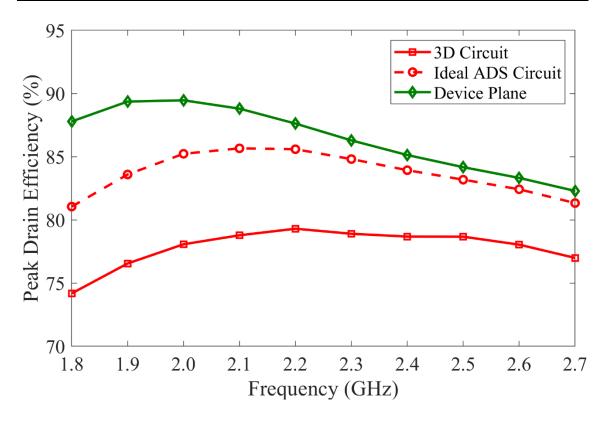

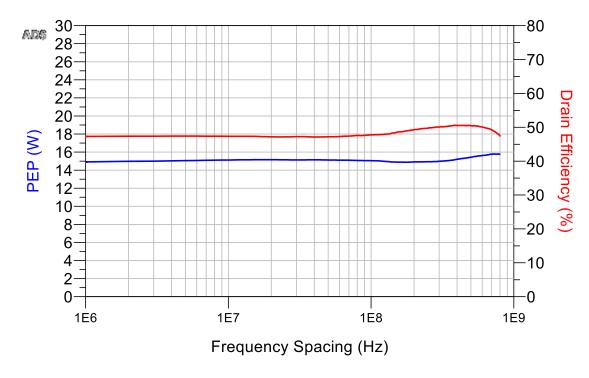

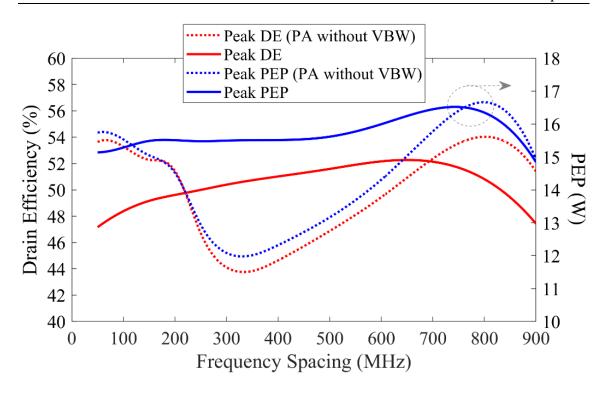

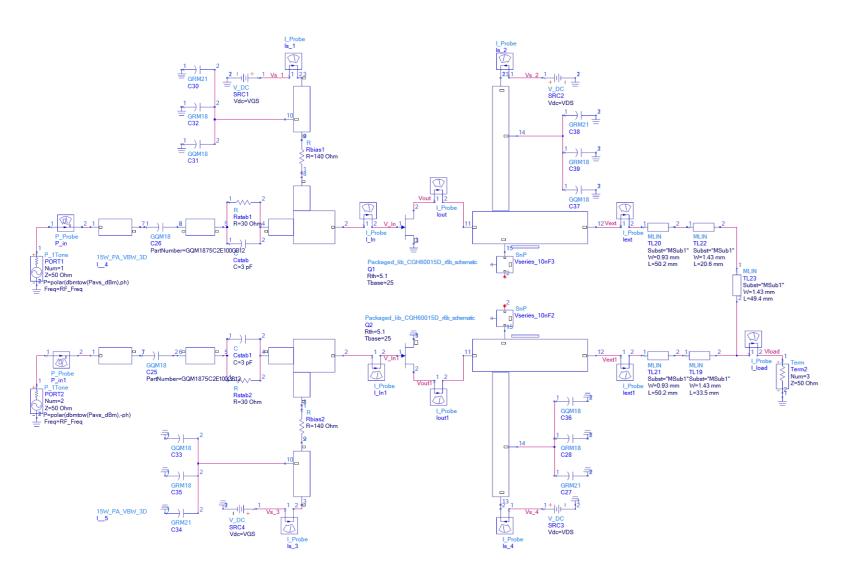

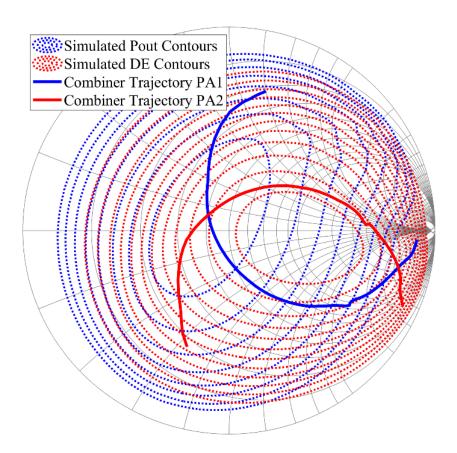

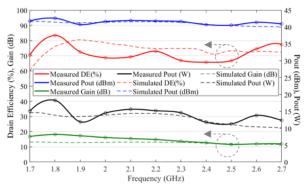

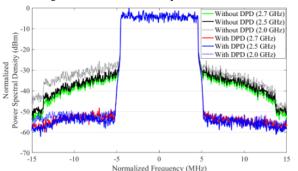

#### 4.3 Broadband Matching Network