### **RICE UNIVERSITY**

# Exploiting Instruction-Level Parallelism for Memory System Performance

by

Vijay S. Pai

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

### **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Sarita Adve, Chair Associate Professor in Electrical and Computer Engineering

Keith D. Cooper Professor of Computer Science

Kenneth W. Kennedy, Jr. Ann and John Doerr Professor in Computational Engineering

Willy E. Zwaenepoel Noah Harding Professor of Computer Science and Electrical and Computer Engineering

Houston, Texas August, 2000

# Exploiting Instruction-Level Parallelism for Memory System Performance

Vijay S. Pai

#### Abstract

Current microprocessors improve performance by exploiting instruction-level parallelism (ILP). ILP hardware techniques such as multiple instruction issue, out-of-order (dynamic) issue, and non-blocking reads can accelerate both computation and data memory references. Since computation speeds have been improving faster than data memory access times, memory system performance is quickly becoming the primary obstacle to achieving high performance. This dissertation focuses on exploiting ILP techniques to improve memory system performance. This dissertation includes both an analysis of ILP memory system performance and optimizations developed using the insights of this analysis.

First, this dissertation shows that ILP hardware techniques, used in isolation, are often unsuccessful at improving memory system performance because they fail to extract parallelism among data reads that miss in the processor's caches. The previously-studied latency-tolerance technique of software prefetching provides some improvement by initiating data read misses earlier, but also suffers from limitations caused by exposed startup latencies, excessive fetch-ahead distances, and references that are hard to prefetch.

This dissertation then uses the above insights to develop compile-time software transformations that improve memory system parallelism and performance. These transformations improve the effectiveness of ILP hardware, reducing exposed latency by over 80% for a latency-detection microbenchmark and reducing execution time an average of 25% across 14 multiprocessor and uniprocessor cases studied in simulation and an average of 21% across 12 cases on a real system. These transformations also combine with software prefetching to address key limitations in either latency-tolerance technique alone, providing the best performance when both techniques are combined for most of the uniprocessor and multiprocessor codes that we study.

Finally, this dissertation also explores appropriate evaluation methodologies for ILP shared-memory multiprocessors. Memory system parallelism is a key feature determining ILP performance, but is neglected in previous-generation fast simulators. This dissertation highlights the errors possible in such simulators and presents new evaluation methodologies to improve the tradeoff between accuracy and evaluation speed.

## Acknowledgments

I would like to thank my advisor, Sarita Adve, for research direction, challenges, and a real commitment to my professional growth. I also thank my officemate, co-author, and friend, Parthasarathy Ranganathan, for many interesting discussions and adventures (technical and otherwise) since we started working together. It has been a great pleasure to work with these two people for the past six years.

My Ph.D. thesis committee of Keith Cooper, Ken Kennedy, and Willy Zwaenepoel have given me excellent feedback on this work since the time of my proposal, and this feedback has been instrumental in shaping both the technical content of this work and my presentation of it. Some of this work draws from my M.S. thesis, for which I also profited from the suggestions of my committee of Alan Cox and Bob Jump.

I would also like to thank all the others with whom I have had a chance to interact over the years, with whom I have been a co-author, and who have given me feedback on the research leading to this dissertation and on my presentations of this research. In particular, this dissertation draws heavily from joint work that I pursued with Murthy Durbhakula, Dan Sorin, Mary Vernon, and David Wood. I thank all those who read my paper drafts and attended my practice talks over the years, and I feel that their comments have greatly helped refine both the content and presentation of this work. Vikram Adve, Chen Ding, John Mellor-Crummey, and Shubu Mukherjee particularly went far beyond the call of duty here. Credit also goes to all the RSIM team members over the years, including Hazim Abdel-Shafi, Dennis Geels, Jon Hall, Tracy Harton, Chris Hughes, and Praful Kaul. Doug Moore's Hilbert-curve library helped make Mp3d an interesting and tractable application for the course of this study. Donald Yeung provided the source code for the Em3d application used in this study. I cannot thank my family enough for everything they have given me over the years. I owe a tremendous debt to my parents, Sadananda and Sharda Pai, for very practical contributions of guidance, support, and encouragement over the past twenty-six years. I also thank my grandmother, Janabai Kamath, for support and many nutritious meals. My brother Vinay and my sister-in-law Aarti have also given their support, and his kids have provided a great source of amusement and amazement on their visits. Finally, my brother Vivek and I shared most of the years of our graduate school experience. I have profited tremendously from his suggestions, discussions, and feedback on technical and nontechnical matters, and I am very glad that we now have an opportunity to be colleagues as well.

My graduate career was supported by a Fannie and John Hertz Foundation Fellowship from September 1994 through May 1999. The research presented in this dissertation was also supported by IBM Corporation, Intel Corporation, the National Science Foundation under Grant No.CCR-9410457, CCR-9502500, CDA-9502791, CDA-9617383, CCR-0096126, the Texas Advanced Technology Program under Grants No. 003604-016 and 003604-025, and the Alfred Sloan Research Foundation. This dissertation was initiated to *Early Underground* by Moby and concluded to *Fight Club* by the Dust Brothers.

# Contents

|   | Abst | tract     |                                                              | ii  |

|---|------|-----------|--------------------------------------------------------------|-----|

|   | Ack  | nowledg   | gments                                                       | iv  |

|   | List | of Illust | rations                                                      | xi  |

|   | List | of Table  | es                                                           | xiv |

| 1 | Inti | roduct    | ion                                                          | 1   |

|   | 1.1  | Motiva    | ation                                                        | 1   |

|   | 1.2  | Contri    | butions                                                      | 2   |

|   |      | 1.2.1     | Analyzing the Impact of ILP Techniques on Memory System      |     |

|   |      |           | Performance                                                  | 2   |

|   |      | 1.2.2     | ILP-Specific Code Transformations to Improve Multiprocessor  |     |

|   |      |           | Performance                                                  | 3   |

|   |      | 1.2.3     | Analyzing and Addressing the Impact of ILP on Multiprocessor |     |

|   |      |           | Evaluation Methodology                                       | 5   |

|   | 1.3  | Organi    | ization                                                      | 7   |

| 2 | The  | e Imna    | act of ILP on Memory System Performance                      | 8   |

| - | 2.1  | -         | dology                                                       | 8   |

|   |      | 2.1.1     | Simulated Architectures                                      | 9   |

|   |      | 2.1.2     | Performance Metrics                                          | 12  |

|   |      | 2.1.3     | Evaluation Workload                                          | 12  |

|   | 2.2  |           | mental results on multiprocessor system                      | 14  |

|   |      | 2.2.1     | Overall Results                                              |     |

|   |      | 2.2.2     | Factors Contributing to ILP Speedup                          |     |

|   |      |           |                                                              |     |

| 2.3 | Experimental results on uniprocessor system | 22 |

|-----|---------------------------------------------|----|

| 2.4 | Sensitivity to system latencies             | 23 |

| 2.5 | Summary and Implications                    | 24 |

# **3** Interaction of Software Data Prefetching with Instruction-Level

|   | Par | allelis | m                                                                   | 25 |

|---|-----|---------|---------------------------------------------------------------------|----|

|   | 3.1 | Softwa  | are prefetching algorithm                                           | 26 |

|   |     | 3.1.1   | Algorithm for Adding and Scheduling Software Prefetches             | 26 |

|   |     | 3.1.2   | Prefetching Algorithms for Irregular Memory References              | 27 |

|   | 3.2 | Measu   | ring prefetching effectiveness                                      | 28 |

|   |     | 3.2.1   | Simulated systems                                                   | 29 |

|   |     | 3.2.2   | Performance Metrics                                                 | 29 |

|   |     | 3.2.3   | Applications and Prefetching                                        | 29 |

|   | 3.3 | Experi  | mental results                                                      | 30 |

|   |     | 3.3.1   | Overall Results                                                     | 30 |

|   |     | 3.3.2   | Factors Contributing to the Effectiveness of Software Prefetching . | 32 |

|   |     | 3.3.3   | Application-Specific Details                                        | 34 |

|   |     | 3.3.4   | Impact of Software Prefetching on Execution Time                    | 36 |

|   | 3.4 | Sensiti | vity to System Latencies                                            | 37 |

|   | 3.5 | Summ    | ary and Implications                                                | 37 |

| _ |     |         |                                                                     |    |

| 4 | Cod | le Tra  | nsformations to Improve Memory Parallelism                          | 39 |

|   | 4.1 | Improv  | ving Read Miss Clustering in ILP Processors                         | 40 |

|   | 4.2 | Analys  | sis and Transformation Framework                                    | 42 |

|   |     | 4.2.1   | Dependences that Limit Memory Parallelism                           | 42 |

|   |     | 4.2.2   | Background on Floating-point Pipelining                             | 46 |

|   |     | 4.2.3   | Resolving Memory Parallelism Recurrences                            | 47 |

|   |     | 4.2.4   | Resolving Window Constraints                                        | 51 |

| 4.3 | Measu  | ring the Impact of Optimizations                   | 52 |

|-----|--------|----------------------------------------------------|----|

|     | 4.3.1  | Evaluation environments                            | 52 |

|     | 4.3.2  | Evaluation Workload                                | 53 |

|     | 4.3.3  | Evaluation metrics                                 | 56 |

| 4.4 | Perfor | mance of Latbench Microbenchmark                   | 57 |

| 4.5 | Simula | ated Application Performance                       | 58 |

|     | 4.5.1  | Impact of clustering on execution time             | 58 |

|     | 4.5.2  | Memory Parallelism and Contention                  | 60 |

|     | 4.5.3  | Sensitivity to system parameters                   | 61 |

| 4.6 | Exemp  | blar Application Performance                       | 62 |

| 4.7 | Summ   | ary and Discussion                                 | 63 |

|     |        |                                                    |    |

| Coi | npariı | ng and Combining Read Miss Clustering and Software | •  |

| Pre | fetchi | ng                                                 | 65 |

5

| 110 |         | 18                                                         | 05 |

|-----|---------|------------------------------------------------------------|----|

| 5.1 | Limita  | tions of Read Miss Clustering and Software Prefetching     | 66 |

|     | 5.1.1   | Limitations of Read Miss Clustering                        | 66 |

|     | 5.1.2   | Limitations of Software Prefetching                        | 67 |

|     | 5.1.3   | Limitations Shared by Clustering and Prefetching           | 67 |

| 5.2 | Combi   | ning Clustering and Prefetching                            | 67 |

|     | 5.2.1   | Potential Benefits of Combining Clustering and Prefetching | 68 |

|     | 5.2.2   | Addressing a Limitation of Clustered Prefetching           | 70 |

| 5.3 | Experi  | mental Methodology                                         | 72 |

| 5.4 | Simula  | tion Results                                               | 74 |

|     | 5.4.1   | Comparing Clustering and Prefetching                       | 75 |

|     | 5.4.2   | Combination of Clustering and Prefetching                  | 76 |

| 5.5 | Results | s on Real Machine                                          | 81 |

| 5.6 | Summa   | ary and Discussion                                         | 83 |

| 6 | Ana  | alyzing | g and Improving the Accuracy vs. Speed Tradeoff for | ſ   |

|---|------|---------|-----------------------------------------------------|-----|

|   | Sim  | ulatin  | g Shared-Memory Multiprocessors with ILP Proces     | -   |

|   | sors | 5       |                                                     | 85  |

|   | 6.1  | Backg   | round                                               | 86  |

|   |      | 6.1.1   | Direct execution with simple processors             | 87  |

|   |      | 6.1.2   | Simulators for ILP shared-memory systems            | 88  |

|   | 6.2  | Direct  | execution with ILP shared-memory multiprocessors    | 88  |

|   |      | 6.2.1   | Values for non-blocking reads                       | 89  |

|   |      | 6.2.2   | Timing simulation of ILP features                   | 90  |

|   | 6.3  | Impler  | nentation of DirectRSIM                             | 91  |

|   |      | 6.3.1   | Application code instrumentation                    | 91  |

|   |      | 6.3.2   | Timing simulator                                    | 92  |

|   | 6.4  | Evalua  | tion Methodology                                    | 95  |

|   |      | 6.4.1   | Simulated architectures                             | 95  |

|   |      | 6.4.2   | Applications                                        | 95  |

|   |      | 6.4.3   | Simulators                                          | 97  |

|   |      | 6.4.4   | Metrics                                             | 98  |

|   | 6.5  | Result  | s on simulator accuracy                             | 99  |

|   |      | 6.5.1   | Base system configuration                           | 99  |

|   |      | 6.5.2   | Other system configurations                         | 100 |

|   | 6.6  | Result  | s on simulator speed                                | 103 |

|   |      | 6.6.1   | Comparing Simple with Wisconsin Wind Tunnel-II      | 103 |

|   |      | 6.6.2   | Comparing RSIM, DirectRSIM, and Simple              | 104 |

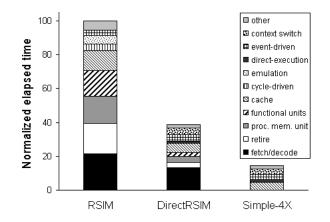

|   |      | 6.6.3   | Detailed analysis of DirectRSIM speed               | 105 |

|   | 6.7  | Summ    | ary and Implications                                | 107 |

| 7 | Fas  | t Char  | racterization of ILP Memory System Parameters       | 113 |

|   | 7.1  | Funda   | mental ILP Memory System Parameters                 | 113 |

|   | 7.2 | Fast High-Level Simulation                    | 114 |

|---|-----|-----------------------------------------------|-----|

|   | 7.3 | Validation of FastILP Parameters              | 116 |

|   | 7.4 | Summary                                       | 118 |

| 8 | Rel | ated Work                                     | 119 |

|   | 8.1 | Work related to ILP memory system performance | 119 |

|   | 8.2 | Work related to software prefetching          | 122 |

|   | 8.3 | Work related to ILP multiprocessor simulation | 123 |

| 9 | Cor | nclusions and Future Directions               | 126 |

|   | 9.1 | Conclusions                                   | 126 |

|   | 9.2 | Future directions                             | 127 |

|   | Bib | liography                                     | 130 |

# Illustrations

| 2.1 | Layout of CC-NUMA multiprocessor used in simulatioon studies, along         |    |

|-----|-----------------------------------------------------------------------------|----|

|     | with detailed diagram of individual processing node                         | 11 |

| 2.2 | Impact of ILP on multiprocessor execution time and its components           | 14 |

| 2.3 | ILP speedup of total execution time and components as seen in               |    |

|     | multiprocessor system.                                                      | 15 |

| 2.4 | The instruction window (reorder buffer) of an out-of-order issue processor. |    |

|     | Older instructions are shown at the right, and cache misses are shaded      | 16 |

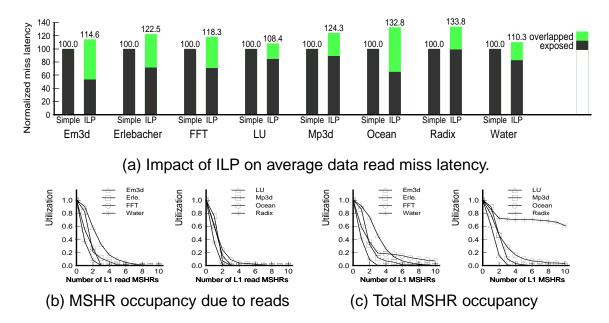

| 2.5 | Factors shaping data read miss ILP speedup. The latency figures indicate    |    |

|     | overall overlap and contention, while the MSHR graphs show specific         |    |

|     | sources of overlap (read MSHRs) and contention (total MSHRs)                | 19 |

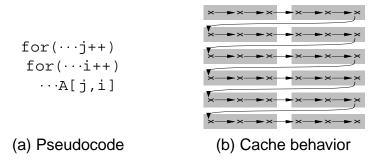

| 2.6 | Pseudocode and representation of cache-behavior for a matrix traversal      |    |

|     | optimized for cache locality. The pseudocode is shown with row-major        |    |

|     | notation, and the graphic shows the matrix in row-major order. Crosses in   |    |

|     | the graphic represent matrix elements, and shaded blocks represent cache    |    |

|     | lines                                                                       | 21 |

| 2.7 | Impact of ILP on uniprocessor execution time and its components             | 22 |

| 2.8 | ILP speedup of total execution time and components as seen in               |    |

|     | uniprocessor system.                                                        | 22 |

| 2.9 | Impact of ILP on execution time for systems with faster processors          | 23 |

|     |                                                                             |    |

| 3.1 | Pseudocode of a 2-D matrix traversal, before and after applying software    |    |

|     | prefetching. All pseudocode uses row-major notation.                        | 27 |

| 3.2 | Interaction of ILP with software prefetching in Simple and ILP systems     |    |

|-----|----------------------------------------------------------------------------|----|

|     | with base configuration.                                                   | 31 |

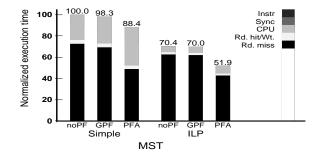

| 3.3 | Comparing greedy prefetching and prefetch arrays for MST on simulated      |    |

|     | Simple and ILP uniprocessors. Execution times are normalized to the        |    |

|     | Simple system without prefetching.                                         | 36 |

| 3.4 | Interaction of ILP with software prefetching in Simple and ILP systems     |    |

|     | with faster processors.                                                    | 37 |

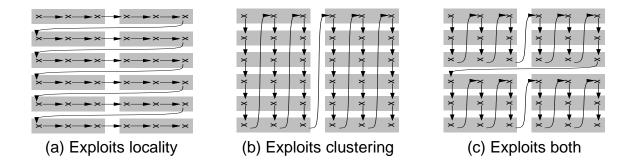

| 4.1 | Impact of matrix traversal order on miss clustering. Crosses represent     |    |

|     | matrix elements, and shaded blocks represent cache lines. The matrix is    |    |

|     | shown in row-major order.                                                  | 40 |

| 4.2 | Pseudocode for Figure 4.1 matrix traversals (row-major notation)           | 41 |

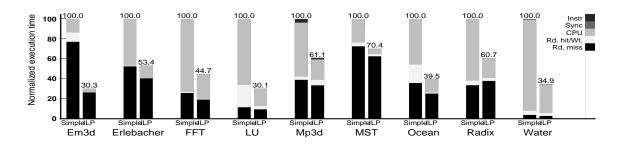

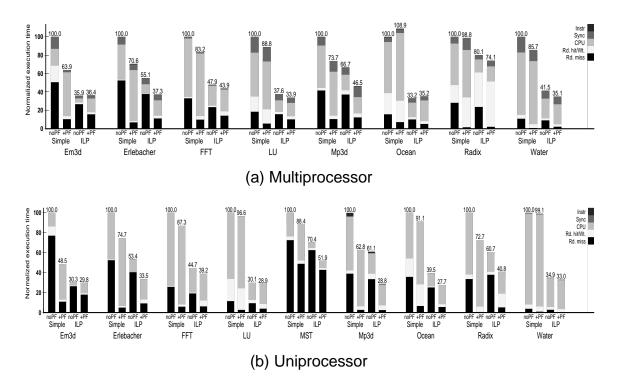

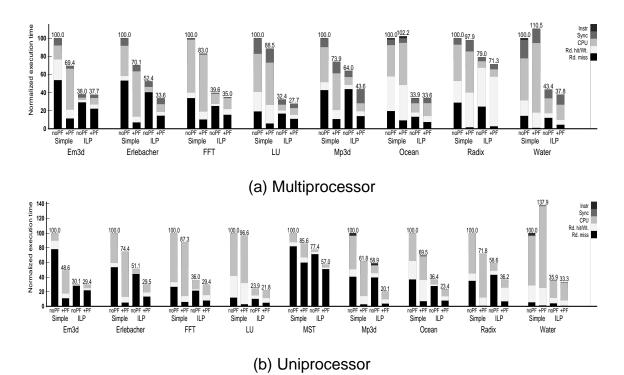

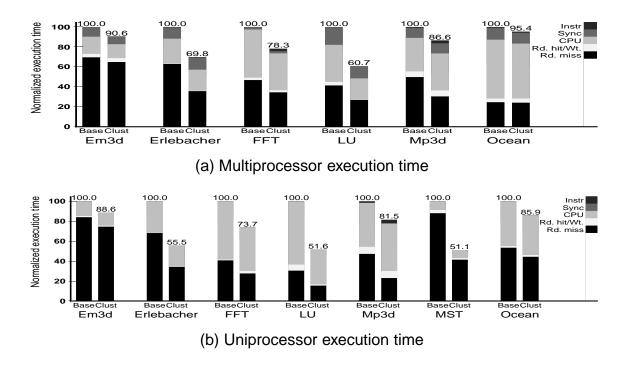

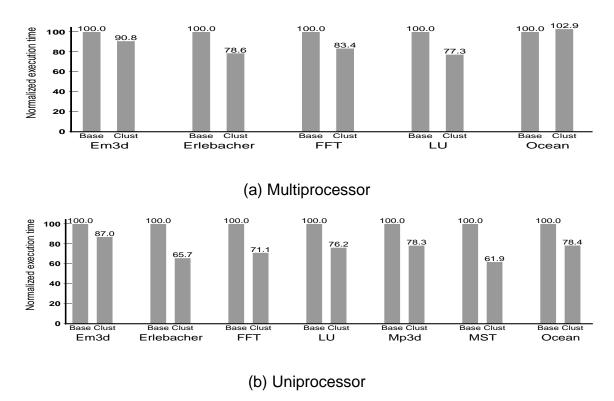

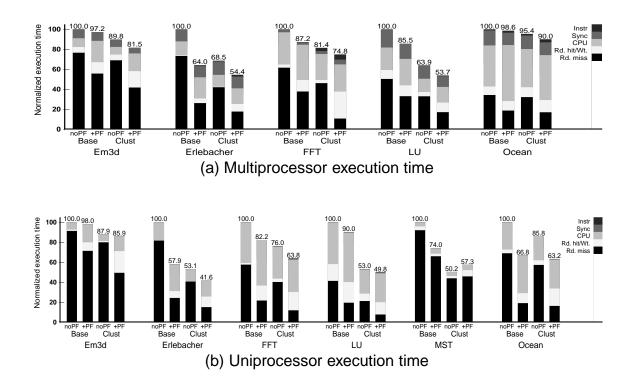

| 4.3 | Impact of clustering transformations on application execution time         | 58 |

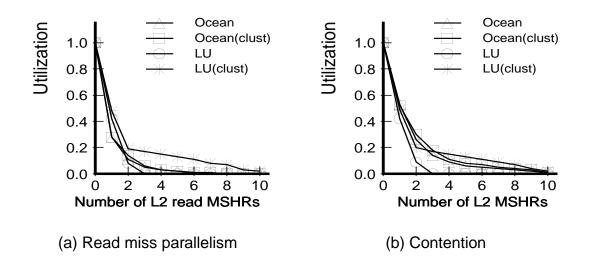

| 4.4 | Factors shaping memory parallelism (read L2 MSHR utilization) and          |    |

|     | contention (total L2 MSHR utilization).                                    | 60 |

| 4.5 | Execution times on simulated system with faster processors                 | 61 |

| 4.6 | Impact of read miss clustering on Convex Exemplar execution time           | 63 |

| 5.1 | Pseudocode of a 2-D matrix traversal, (a) as originally generated, and (b) |    |

|     | after read miss clustering with unroll-and-jam (postlude not shown). All   |    |

|     | pseudocode uses row-major notation. Figure 5.2 shows the corresponding     |    |

|     | codes after the addition of prefetching.                                   | 68 |

| 5.2 | Pseudocode of the 2-D matrix traversals of Figure 5.1 after adding         |    |

|     | software prefetching. Figure 5.1(a) tolerates latencies with software      |    |

|     | prefetching alone, while Figure 5.1(b) uses the combination of clustering  |    |

|     | and prefetching.                                                           | 69 |

| 5.3 | Applying both software prefetching and loop interchange to provide         |    |

|     | clustered prefetching in the postlude left by unroll-and-jam               | 73 |

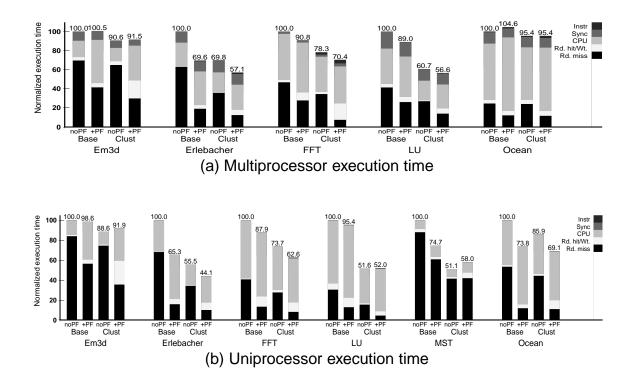

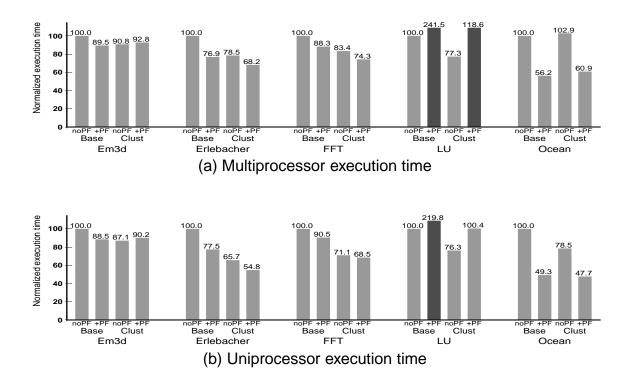

| 5.4 | Execution times on base simulated system with software prefetching,         |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | clustering, and their combination. All times are shown normalized to the    |     |

|     | execution time with neither prefetching nor clustering.                     | 74  |

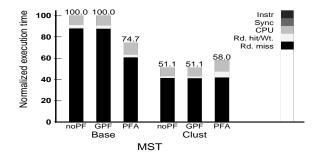

| 5.5 | Comparing greedy prefetching and prefetch arrays for MST on base            |     |

|     | simulated uniprocessor system. Execution times are normalized to the        |     |

|     | unclustered code without prefetching.                                       | 75  |

| 5.6 | Number of late prefetch stalls after clustered prefetching represented as a |     |

|     | percentage of the late prefetch stalls seen with prefetching alone          | 76  |

| 5.7 | Execution times of Em3d on base system when less clustering is used in      |     |

|     | combination with prefetching.                                               | 78  |

| 5.8 | Execution times on simulated system with faster processors                  | 80  |

| 5.9 | Execution times on Convex Exemplar with software prefetching,               |     |

|     | clustering, and their combination. All times are shown normalized to the    |     |

|     | execution time with the same number of processors and neither               |     |

|     | prefetching nor clustering. (Darker bars represent degradations beyond the  |     |

|     | size of the charts.)                                                        | 82  |

|     |                                                                             |     |

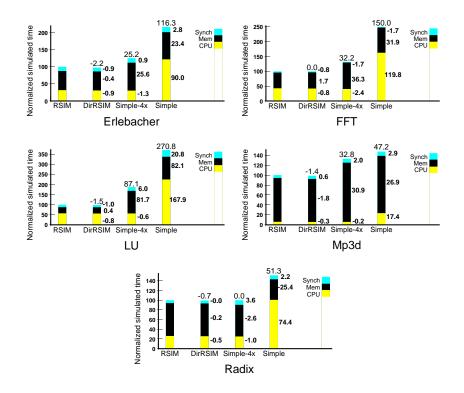

| 6.1 | Simulator accuracy for the base system.                                     | 99  |

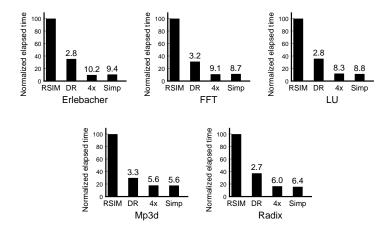

| 6.2 | Simulator speed for the base system. DR=DirectRSIM, 4x=Simple-4x,           |     |

|     | Simp=Simple                                                                 | 105 |

| 6.3 | Components of elapsed time for various simulators                           | 106 |

|     |                                                                             |     |

# Tables

| 2.1 | Base system configuration used in evaluating impact of ILP techniques on    |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | multiprocessor performance.                                                 | 10  |

| 2.2 | Evaluation workload for simulated system                                    | 13  |

|     |                                                                             |     |

| 3.1 | Classification of prefetches                                                | 30  |

| 3.2 | Detailed data on effectiveness of software prefetching in multiprocessor    |     |

|     | system                                                                      | 32  |

|     |                                                                             |     |

| 4.1 | Functional unit latencies for the base system configuration used in         |     |

|     | simulating impact of memory clustering transformations. All other system    |     |

|     | parameters are identical to the ILP system of Chapters 2 and 3, as given in |     |

|     | Table 2.1.                                                                  | 53  |

| 4.2 | Data set sizes and number of processors for experiments on simulated and    |     |

|     | real systems                                                                | 55  |

|     |                                                                             |     |

| 5.1 | Key features of read miss clustering and software prefetching               | 66  |

|     |                                                                             |     |

| 6.1 | Base system parameters. The number of processors varies by application,     |     |

|     | as described in Section 6.4.2 and Table 6.2.                                | 96  |

| 6.2 | Application input sizes and number of simulated processors                  | 97  |

| 6.3 | Variations on base configuration.                                           | 101 |

| 6.4 | Simulator accuracy for all configurations. (Averages are over absolute  |

|-----|-------------------------------------------------------------------------|

|     | values of the errors.)                                                  |

| 6.5 | Simulator errors due to the memory component. (Averages are over        |

|     | absolute values of the errors.)                                         |

| 6.6 | Simulator errors due to the CPU component. (Averages are over absolute  |

|     | values of the errors.)                                                  |

| 6.7 | Simulation time for Simple and WWT-2                                    |

| 6.8 | Simulator speed for all configurations                                  |

| 6.9 | Absolute speed of the simulators in thousands of instructions simulated |

|     | per second                                                              |

|     |                                                                         |

| 7.1 | ILP workload parameters as measured by RSIM                             |

| 7.2 | ILP workload parameters as generated by FastILP | 17 |

|-----|-------------------------------------------------|----|

|     |                                                 |    |

## Chapter 1

## Introduction

#### **1.1 Motivation**

Current commodity microprocessors improve performance by using aggressive techniques to exploit high levels of instruction-level parallelism (ILP). These techniques include multiple instruction issue, out-of-order (dynamic) scheduling, non-blocking reads, and speculative execution. We refer to these techniques collectively as *ILP techniques* and to processors that exploit these techniques as *ILP processors*. ILP processors are being used not only for uniprocessor systems, but also for high-performance shared-memory multiprocessors that focus on data-intensive scientific and commercial applications.

Most previous studies of shared-memory multiprocessors, however, have assumed a *simple processor* with single-issue, in-order scheduling, blocking reads, and no speculation. This assumption allows the use of direct-execution simulation, which is significantly faster than the detailed simulation currently required to model an ILP processor pipeline. A few multiprocessor architecture studies model state-of-the-art ILP processors [Gor95, NHO96, ONH<sup>+</sup>96, PRAH96], but do not analyze the impact of ILP techniques. Further, many uniprocessor studies focus on instruction-level parallelism without specifically targeting optimizations toward memory system performance. Memory system performance is quickly becoming the primary factor determining overall system performance, so optimization approaches that target this subsystem are becoming more important.

To fully exploit recent advances in ILP technology for memory system performance, a detailed analysis is required to indicate how ILP techniques affect memory system performance in high-performance uniprocessor and multiprocessor systems and how they interact

with memory system optimizations that are not specific to ILP. Such an analysis is also required to assess the validity of the continued use of direct-execution simulation with simple processor models to study next-generation shared-memory architectures. This dissertation performs such an analysis and uses the insights of this analysis to address the limitations of aggressive ILP-based systems, both in memory system performance and in evaluation methodology.

### **1.2** Contributions

This dissertation makes three key contributions to the state-of-the-art. First, we analyze the impact of ILP hardware techniques on data memory system performance. Second, we use the insights of that analysis to propose and evaluate new ILP-specific optimizations to improve data memory system performance. Third, we also analyze and improve the tradeoff between accuracy and speed in evaluating ILP-based systems. This work was enabled by the development of RSIM (the Rice Simulator for ILP Multiprocessors) as a part of this thesis. RSIM was the first publicly-available shared-memory multiprocessor simulator to model processors that aggressively exploit instruction-level parallelism.

The following discusses each of these topics more thoroughly.

#### 1.2.1 Analyzing the Impact of ILP Techniques on Memory System Performance

This work characterizes the effectiveness of state-of-the-art ILP processors in sharedmemory multiprocessor and uniprocessor systems, using a detailed ILP multiprocessor and uniprocessor simulator (RSIM) driven by full scientific applications [PRA97b, PRA96, PRAA99]. We show that all of our applications see performance improvements from the use of current ILP techniques in multiprocessors. However, the improvements achieved vary widely. In particular, ILP techniques successfully and consistently reduce the CPU component of execution time, but their impact on the memory (read) stall component is lower than their impact on CPU time and is also more application-dependent. As a result, data read stall time becomes a larger bottleneck than in previous-generation systems. These deficiencies in the impact of ILP techniques on memory stall time arise primarily because of insufficient potential in our applications to overlap multiple read misses, as well as system contention from more frequent memory accesses. This portion of the dissertation (Chapter 2) draws from joint work with Parthasarathy Ranganathan.

This work also analyzes the interaction between software prefetching and ILP techniques in shared-memory multiprocessors [RPAA97, PRAA99]. Software-controlled nonbinding prefetching has been shown to be an effective technique for hiding memory latency in simple processor-based shared memory systems [Mow94]. We show several important factors that can limit the effectiveness of prefetching and relate these to the ILP techniques in general and our applications in particular. On the whole, we find prefetching to be less effective in reducing memory stall time in ILP-based systems than in systems with simple processors. This portion of the dissertation (Chapter 3) draws from joint work with Parthasarathy Ranganathan and Hazim Abdel-Shafi.

Overall, our results suggest that, despite the inherent latency-tolerating mechanisms in ILP processors, multiprocessors built from ILP processors actually exhibit a greater potential need for additional latency reducing or hiding techniques than previous-generation multiprocessors. We identify clustering of read misses together within the ILP processor's instruction window as a potentially effective optimization for better exploiting the ILP features of current processors.

#### **1.2.2 ILP-Specific Code Transformations to Improve Multiprocessor Performance**

The second contribution of this dissertation is to propose software code transformations to improve read miss clustering for systems with out-of-order processors, while preserving cache locality [PA99, PA00]. We exploit code transformations already known and implemented in compilers for other purposes, providing the analysis needed to relate them to read miss clustering. The key transformation we use is unroll-and-jam, which was originally proposed for improving floating-point pipelining and for scalar replacement [AC72, CCK88, CK94, Nic87]. We develop an analysis and transformation frame-

work that maps the read miss clustering problem to floating-point pipelining.

We evaluate the clustering transformations applied by hand to a latency-detection microbenchmark and seven scientific applications running on simulated and real uniprocessor and multiprocessor systems. These transformations reduce data memory latency stall time by over 80% for the latency-detection microbenchmark. For the scientific applications, the transformations reduce execution time by 5–39% (averaging 20%) in the simulated multiprocessor and 11–49% (averaging 30%) in the simulated uniprocessor. A substantial part of these execution-time reductions arise from improving memory parallelism, particularly as memory stall time becomes more significant. We confirm the benefits of our transformations on a real system (Convex Exemplar), where they reduce application execution time by 9–38% for 6 out of 7 applications.

We then show that the techniques of read miss clustering and software prefetching are actually mutually beneficial, each helping to overcome the performance limitations of the other. Thus, the combination can expose opportunities for latency tolerance missed by either technique alone. We evaluate read miss clustering, software prefetching, and their combination both with a detailed simulator (RSIM) and on a real system (Convex Exemplar). We apply miss clustering by hand in both cases and apply prefetching by hand for the simulation. We consider prefetching for both regular and irregular applications [KDS00, LM96, Mow94, RS99]. Experimental results show that clustering alone outperforms prefetching alone for most of the applications and systems that we study, and that the combination of read miss clustering and prefetching yields better execution time benefits than either technique alone in most cases. The combination of clustering and prefetching yields a significant improvement in latency tolerance over prefetching alone (the state-of-the-art implemented in systems today), with an average of 21% reduction in execution time across all cases studied in simulation and an average of 16% reduction in execution time for 5 out of 10 cases on the Exemplar. The experimental results also show reductions in execution time relative to clustering alone averaging 15% for 6 out of 11 cases in simulation and 20% for 6 out of 10 cases on the Exemplar.

## 1.2.3 Analyzing and Addressing the Impact of ILP on Multiprocessor Evaluation Methodology

The third contribution of this thesis focuses on evaluation methodologies for sharedmemory multiprocessors built from ILP processors. We first study the validity of current simple-processor direct-execution simulation based models to model ILP multiprocessors [PRA97b]. For applications where our ILP multiprocessor fails to significantly overlap read miss latency, a simulation using a simple previous-generation processor model with a higher clock speed for the processor and the L1 cache provides a reasonable approximation to the results achieved with a more detailed simulation system. However, when ILP techniques effectively overlap read miss latency, all of our simple-processor-based simulation models can show significant errors for important metrics. Overall, for total simulated execution time, the most commonly used simulation technique gave an average error of 137% (ranging 9%-438%), while even the best approximate model saw an average execution time discrepancy of 46% (ranging 0%-128%). These errors depend on both the application and the ILP characteristics of the system; thus, models that do not properly capture these effects may not be able to effectively characterize an ILP-based multiprocessor system. Nevertheless, direct-execution simulations appear attractive since they are as much as an order of magnitude faster than the detailed simulator RSIM [DPA99]. This portion of the study draws from joint works with Murthy Durbhakula and Parthasarathy Ranganathan.

This dissertation then presents two evaluation methodologies to speed up the characterization of ILP multiprocessors. The first is a novel adaptation of direct-execution simulation that substantially speeds up simulation of shared-memory multiprocessors with ILP processors, without much loss of accuracy [DPA99, DPA98]. We have developed a new simulator, DirectRSIM, based on this new technique. This thesis evaluates the accuracy and speed of DirectRSIM by comparing it with RSIM and with two representative simpleprocessor based direct-execution simulators. For a variety of system configurations and applications, we find that DirectRSIM, on average, is 3.6X faster than RSIM with an error in reported execution time relative to RSIM of only 1.3% (range of -3.9% to 2.2%). Simpleprocessor based simulators remain an average of 2.7X faster than DirectRSIM. However, this additional speed comes at the cost of their much larger and more unpredictable errors. This result suggests a reconsideration of the appropriate simulation methodology for shared-memory systems. Earlier, the order-of-magnitude performance advantage of the simple-processor based simulators over detailed simulators like RSIM made a compelling argument for their use in spite of their potential for large errors. It is not clear that those errors are still justifiable given only a 2.7X performance advantage relative to DirectRSIM. This portion of the dissertation draws from joint work with Murthy Durbhakula.

The second new evaluation methodology presented in this dissertation is a high-level simulation methodology called FastILP [SPA+98]. FastILP interacts with a new analytical model of ILP-based multiprocessors. Analytical modeling is an attractive alternative to simulation because of its high speed. However, most analytical models are driven by synthetic parameters that may not represent any real workload. FastILP generates the parameters needed to allow this new analytical model to capture relevant information about the workload. Specifically, FastILP characterizes an application in terms of fundamental ILP parameters, rather than attempting to measure the time required for the application. The parameters measured are the distribution of read misses outstanding at the time that processor action stalls (an indicator of overlap) and the rate and variance by which external memory requests are sent from the active processor (indicators of contention). Since FastILP does not need to measure the exact cycle count for an execution, it can achieve very high performance by abstracting both the ILP processor and the memory system, and modeling only enough state to generate the required ILP parameters. The combination of FastILP and the new analytical model can be used to compute performance estimates very quickly while still accounting for important workload characteristics. FastILP and the analytical model for ILP multiprocessors were developed jointly with Daniel Sorin, Mary Vernon, and David Wood.

### 1.3 Organization

The rest of this dissertation is organized as follows. Chapter 2 analyzes the impact of current techniques that exploit instruction-level parallelism and their effectiveness in targeting memory system performance. Chapter 3 shows the interaction between software prefetching and ILP. Chapter 4 proposes software code transformations that aim to improve the interaction of ILP with memory system performance by increasing memory parallelism. We also evaluate these transformations on both a simulator and a real machine. Chapter 5 compares and combines the software latency tolerance techniques discussed in the previous chapters (software prefetching and read miss clustering), and explains how each of these techniques can address limitations in the other. Chapter 6 analyzes the accuracy and performance of simulators for ILP multiprocessor systems and presents a new simulation methodology to improve the tradeoff between accuracy and simulation speed. Chapter 7 discusses our fast high-level evaluation methodology that characterizes applications in terms of fundamental ILP parameters instead of specific timings. Chapter 8 discusses related work, and Chapter 9 describes the conclusions of this study and planned future work.

## **Chapter 2**

## The Impact of ILP on Memory System Performance

Most multiprocessor architectural studies have used simple-processor-based models for the evaluation of their benefits. Some studies have modeled the effects of ILP, but have not detailed the benefits of techniques to exploit ILP in multiprocessors [NHO96, ONH<sup>+</sup>96, GGH92, PRAH96, ZB92]. Many other works study the impact of ILP on uniprocessor systems without specifically analyzing its interaction with memory system performance. Our work seeks to provide a detailed analysis of the impact of ILP on data memory system performance, both to assess the efficacy of techniques to exploit ILP and to identify limitations to high performance.

This chapter evaluates the impact of instruction-level parallelism on memory system performance. Section 2.1 describes the architectural models and applications studied, as well as the quantitative metrics used. Section 2.2 focuses on multiprocessor systems, comparing the performance of systems based on simple and ILP processors and characterizing the effectiveness of current techniques to exploit ILP. Section 2.3 shows the impact of ILP on uniprocessor systems. Section 2.4 describes the sensitivity of our experimental results to system latencies as the processor-memory speed gap continues to grow. Finally, Section 2.5 summarizes the key findings of these studies and describes additional issues in the impact of ILP on shared-memory multiprocessor performance.

### 2.1 Methodology

This section describes the ILP and simple processor based systems that we investigate in our study, our simulation infrastructure, and the evaluation workload we use to characterize our systems.

#### 2.1.1 Simulated Architectures

To determine the impact of ILP techniques on multiprocessor performance, we compare two CC-NUMA multiprocessor systems – *ILP* and *Simple* – equivalent in every respect except the processor used. The ILP system uses state-of-the-art ILP processors while the Simple system uses simple processors, as described below. We compare the ILP and Simple systems not to suggest any architectural tradeoffs, but rather, to understand how aggressive ILP techniques impact multiprocessor performance. Therefore, the two systems have identical clock rates, and include identical aggressive memory and network configurations suitable for the ILP system. Table 2.1 summarizes all the system parameters.

**Processor models.** The ILP system uses state-of-the-art processors that include multiple issue, out-of-order (dynamic) scheduling, non-blocking reads, and speculative execution. The Simple system uses previous-generation simple processors with single issue, in-order (static) scheduling, and blocking reads, and represents commonly studied sharedmemory systems. Since we did not have access to a compiler that schedules instructions for our in-order Simple processor, we assume single-cycle functional unit latencies (as also assumed by most previous simple-processor based shared-memory studies). Both processor models include support for software-controlled non-binding prefetching to the L1 cache (discussed in Chapter 3).

**Memory Hierarchy and Multiprocessor Configuration.** We simulate a hardware cache-coherent, non-uniform memory access (CC-NUMA) shared-memory multiprocessor using an invalidation-based, three-state MSI directory coherence protocol. We extend our MSI protocol to issue reads in exclusive-mode when a write instruction to the same cache line appears later in the processor's instruction window. We model the release consistency memory model because previous studies have shown that it achieves the best performance [PRAH96].

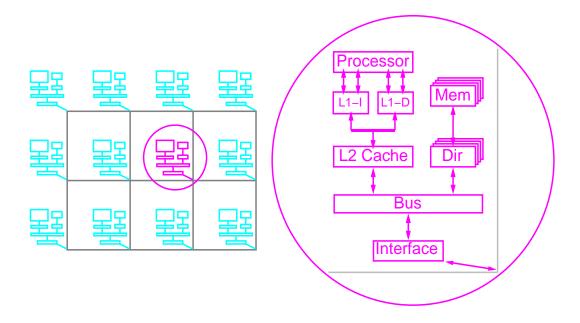

Figure 2.1 shows the topology and features of our CC-NUMA system. The processing nodes are connected using a two-dimensional mesh network. Each node includes a processor, a primary instruction cache, a primary data cache, a unified secondary cache, a portion

| Processor parameters                      |                                                    |  |  |  |  |  |

|-------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Clock rate                                | 500 MHz                                            |  |  |  |  |  |

| Fetch/decode/retire rate                  | 4 per cycle                                        |  |  |  |  |  |

| Instruction window                        | 64 instructions in-flight                          |  |  |  |  |  |

| Memory queue size                         | 32                                                 |  |  |  |  |  |

| Outstanding branches                      | 16                                                 |  |  |  |  |  |

| Number of functional units                | 2 ALUs, 2 FPUs, 2 address generation units         |  |  |  |  |  |

| Functional unit latencies                 | 1 cycle                                            |  |  |  |  |  |

| Memory hierarchy and network parameters   |                                                    |  |  |  |  |  |

| L1 D-cache                                | 16 KB, direct-mapped, 2 ports, 10 MSHRs,           |  |  |  |  |  |

|                                           | 64-byte line                                       |  |  |  |  |  |

| L1 I-cache                                | 16 KB, direct-mapped, 64-byte line                 |  |  |  |  |  |

| L2 cache                                  | 64 KB (for Erlebacher, FFT, LU, and Mp3d)          |  |  |  |  |  |

|                                           | or 1 MB (for Em3d, MST, and Ocean),                |  |  |  |  |  |

|                                           | 4-way associative, 1 port, 10 MSHRs, 64-byte line, |  |  |  |  |  |

|                                           | pipelined                                          |  |  |  |  |  |

| Memory banks                              | 4-way, permutation-based interleaving              |  |  |  |  |  |

| Bus                                       | 167 MHz, 256 bits, split transaction               |  |  |  |  |  |

| Network                                   | 2D mesh, 250MHz, 64 bits, flit delay of 2 network  |  |  |  |  |  |

|                                           | cycles per hop                                     |  |  |  |  |  |

| System latencies in absence of contention |                                                    |  |  |  |  |  |

| L1 hit                                    | 1 processor cycle                                  |  |  |  |  |  |

| L2 hit                                    | 10 processor cycles                                |  |  |  |  |  |

| Local memory                              | 85 processor cycles                                |  |  |  |  |  |

| Remote memory                             | 180-260 processor cycles                           |  |  |  |  |  |

| Cache-to-cache transfer                   | 210-310 processor cycles                           |  |  |  |  |  |

Table 2.1 : Base system configuration used in evaluating impact of ILP techniques on multiprocessor performance.

of the global shared-memory and directory, and a network interface. A split-transaction bus connects the network interface, directory controller, and the rest of the system node. Both data caches are non-blocking, cache with a write-allocate write-back policy, and use miss status holding registers (MSHRs) [Kro81] to store information on outstanding misses and to coalesce multiple requests to the same cache line. The cache sizes are scaled based on application input sizes according to the methodology of Woo et al. [WOT<sup>+</sup>95]. Realistic application inputs would typically require an impractical amount of simulation time. How-

Figure 2.1 : Layout of CC-NUMA multiprocessor used in simulatioon studies, along with detailed diagram of individual processing node.

ever, smaller input sizes may lead to overly optimistic views of cache performance. Thus, this methodology suggests scaling the cache sizes down according to the simulated working sets, and is widely used in multiprocessor architectural studies. The primary working sets for our applications typically fit in the L1 cache, while the secondary working sets do not fit in the L2 cache. The memory banks use permutation-based interleaving on a cache-line granularity to support a variety of strides [Soh93].

**Simulation environment.** We use RSIM, the Rice Simulator for ILP Multiprocessors, to model the systems studied [PRA97a]. RSIM is an execution-driven simulator that models the out-of-order processor, memory system, and interconnection network in detail, including contention at all resources. It takes SPARC application executables as input.

#### 2.1.2 Performance Metrics

Our primary metric for determining the impact of ILP is the total execution time. To characterize the performance bottlenecks in our system, we also categorize simulated execution time as follows: data read miss stall (for stalls caused by data references to main memory), data read hit or write stall (usually exposed only in the event of high resource contention), CPU (busy time and functional-unit stalls), synchronization, and instruction memory stall times. We account for stall cycles in the ILP processor as follows, similar to previous work (e.g., [LM96]). For each cycle, we calculate the ratio of the instructions retired from the instruction window to the maximum retire rate and attribute this fraction of that cycle to busy time. The rest of the cycle is attributed as stall time to the first instruction that could not retire that cycle, or as instruction memory stall if no instruction is available in the window because of an I-cache stall.

We also define a derivative metric to characterize the impact of ILP, which we call the *ILP speedup*. This is the ratio of the execution time with the Simple system relative to that achieved by the ILP system. For detailed analysis, we analogously define an ILP speedup for each component of execution time.

#### 2.1.3 Evaluation Workload

Table 2.2 summarizes the evaluation workload for the simulated system. The number of processors used for the multiprocessor experiments is based on application scalability, with a limit of 16. The input sizes were chosen to ensure reasonable simulation times. Since a SPARC compiler for our ILP system does not exist, we compiled our applications with the commercial Sun SC 4.2 or the gcc 2.7.2 compiler (whichever gave better simulated ILP system performance) with full optimization turned on. The compilers' deficiencies in addressing the specific instruction grouping rules of our ILP system are partly hidden by the out-of-order scheduling in the ILP processor.

FFT, LU, Ocean, and Radix are array-based codes from the SPLASH-2 suite consisting primarily of loops and loop nests [WOT<sup>+</sup>95]. FFT, LU, and Ocean are *regular* codes:

| Application | Input Size                      | Processors |

|-------------|---------------------------------|------------|

| Em3d        | 32K nodes, deg. 20, 20% rem.    | 1,16       |

| Erlebacher  | 64x64x64 cube, block 8          | 1,16       |

| FFT         | 65536 points                    | 1,16       |

| LU          | 256x256 matrix, block 16        | 1,8        |

| Mp3d        | 100000 particles                | 1,8        |

| MST         | 1024 nodes                      | 1          |

| Ocean       | 258x258 grid                    | 1,8        |

| Radix       | 1024 radix, 512K keys, max 512K | 1,8        |

| Water       | 512 molecules                   | 1,16       |

Table 2.2 : Evaluation workload for simulated system.

the array indices used in these codes are affine functions of the controlling loop variables. Radix has one important phase with irregular references formed by indirection. For better load balance, LU is modified slightly to use flags instead of barriers.

Mp3d and Water are from the SPLASH suite [SWG92]. To eliminate false-sharing in the irregular, asynchronous, and communication-intensive Mp3d application, key data structures were padded to a multiple of the cache line size. To reduce true-sharing and improve locality in Mp3d, the data elements were sorted by position in the modeled physical world [MWK99].

Erlebacher is a shared-memory port of a code by Thomas Eidson at the Institute for Computer Applications in Science and Engineering (ICASE). Like FFT, LU, and Ocean, Erlebacher is also a regular array-based code dominated by loop nests.

Em3d is a shared-memory adaptation of a Split-C application [CDG<sup>+</sup>93]. This code spends most of its time in loop nests and includes both regular and indirect references.

MST is the minimal-spanning tree algorithm from the Olden benchmarks [RCRH95]. MST is dominated by linked-list traversals for lookups in a hash-table. This is an example of a *linked data structure* application, as opposed to the other codes which are based on arrays. MST has an irregular access pattern. We do not run a multiprocessor version of MST because of excessive synchronization overhead.

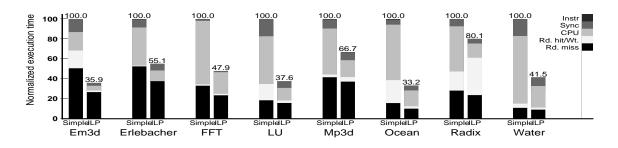

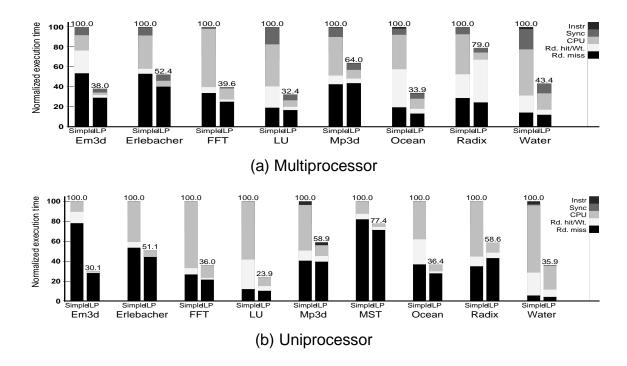

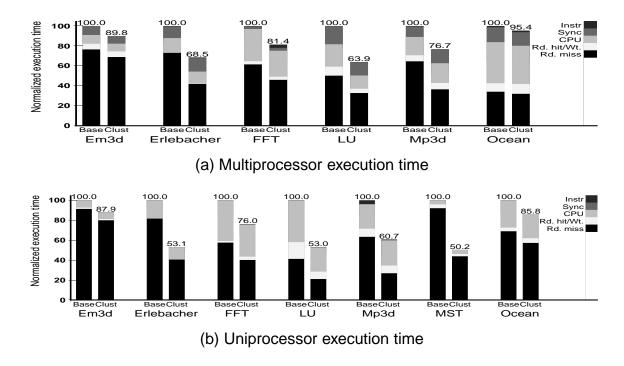

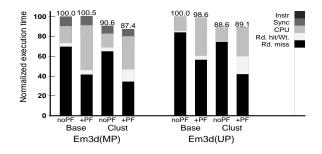

Figure 2.2 : Impact of ILP on multiprocessor execution time and its components.

### 2.2 Experimental results on multiprocessor system

This section analyzes the impact of ILP techniques on multiprocessor performance by comparing the Simple and ILP multiprocessor systems.

#### 2.2.1 Overall Results

Figure 2.2 illustrates our key overall results for multiprocessor systems. For each application, Figure 2.2 shows the total execution time and its three components for the Simple and ILP systems (normalized to the total time on the Simple system).

This figure show two key trends:

- ILP techniques improve the execution time of all our applications. However, the impact of ILP is variable, ranging from 20% to 67% reduction in execution time. The average reduction in execution time is only 50%.

- The data memory stall component is generally a larger part of the overall execution time in the ILP system than in the Simple system.

We next investigate the reasons for the above trends.

#### 2.2.2 Factors Contributing to ILP Speedup

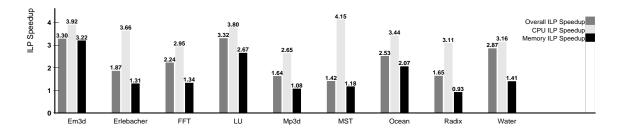

Figure 2.2 shows that the most important components of execution time are CPU time and data memory stalls. Thus, ILP speedup will be shaped primarily by CPU ILP speedup and

Figure 2.3 : ILP speedup of total execution time and components as seen in multiprocessor system.

data memory ILP speedup. Figure 2.3 summarizes these speedups (along with the total ILP speedup). The figure shows that the low and variable ILP speedup for our applications can be attributed largely to insufficient and variable data memory ILP speedup; the CPU ILP speedup is similar and significant across all applications (ranging from 2.73 to 3.92). Figure 2.2 particularly shows that for most of our applications, data memory stall time is dominated by stalls due to reads that miss in the L2 cache. We therefore focus on the impact of ILP on L2 read misses below.

The data read miss ILP speedup is the ratio of the stall time due to data read misses in the Simple and ILP systems, and is determined by three factors, described below. The first factor tends to increase the speedup, the second tends to decrease it, and the third may either increase or decrease it.

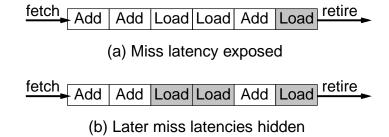

**Memory parallelism.** Since the Simple system has blocking reads, the entire read miss latency is exposed as stall time. In the ILP system, read misses can be overlapped with other useful work, reducing stall time and increasing the ILP read miss speedup. Figures 2.4(a) and 2.4(b) show instructions being processed in the instruction window (reorder buffer) of an out-of-order issue processor. Instructions in the window can issue and complete out-of-order. However, to maintain precise interrupts, instructions must commit their results and retire from the window in program order after completion [SP88]. (Stores may retire before completing at the memory hierarchy in systems that support write-buffering.)

As described in Section 2.1, an external cache miss may require hundreds of proces-

Figure 2.4 : The instruction window (reorder buffer) of an out-of-order issue processor. Older instructions are shown at the right, and cache misses are shaded.

sor cycles. However, current out-of-order processors typically have only 32–80 element instruction windows [Hun95, Kel96, MIP96]. Figure 2.4(a) shows an instruction window in which an outstanding read miss has reached the head of the window and the other instructions in the window are all low latency (such as typical computation and read hits). Then, the other instructions in the window will not be sufficient to completely overlap the oldest read's miss latency. Since the instructions retire in program order, the instruction window fills up and blocks the processor. Thus, ILP features such as out-of-order issue and non-blocking reads are insufficient to hide the read's miss latency.

Figure 2.4(b) shows an otherwise identical instruction window where other independent read misses are scheduled into the window behind the oldest outstanding miss. Here, the later misses issue in parallel with the first miss, and their latencies are overlapped with the stall time of the first miss. Thus, read miss latencies are typically only effectively overlapped in parallel with other read misses. Achieving such *memory parallelism* requires read misses to multiple cache lines to cluster together within the same instruction window. We call this phenomenon *read miss clustering*, or simply *clustering*.

**Contention.** Compared to the Simple system, the ILP system typically sees longer latencies from increased contention due to the higher frequency of misses, thereby negatively affecting data read miss ILP speedup.

Change in the number of misses. The ILP system may see fewer or more misses

than the Simple system because of reordering of memory accesses or speculation, thereby positively or negatively affecting read miss ILP speedup.

We define the following equations to mathematically express the relations of these factors to read miss ILP speedup.

$$Read Miss Speedup = \frac{M_{Simple} \times l_{Simple}}{M_{ILP} \times l_{ILP,exposed}}$$

(2.1)

Equation 2.1 expresses the read miss speedup of these applications in terms of the miss counts and average exposed miss latencies seen in the system.  $M_{Simple}$  and  $M_{ILP}$  represent the count of L2 data read misses in the Simple and ILP systems, respectively. The term  $l_{Simple}$  represents the average data read miss latency in Simple system, which is entirely exposed because of the single-issue, static scheduling and blocking reads of the system. The term  $l_{ILP,exposed}$  represents the average exposed data read miss latency in ILP system.

$$Read Miss Speedup = \frac{M_{Simple}}{M_{ILP}} \times \frac{l_{Simple}}{l_{ILP,exposed}}$$

(2.2)

$$Miss \ Factor = \frac{M_{Simple}}{M_{ILP}} \tag{2.3}$$

Equations 2.2 and 2.3 split off the portion of read miss speedup caused by a change in miss count from the portion caused by a change in the exposed latencies. Equation 2.3 defines the *miss factor*, which represents the ratio of the miss count in the Simple and ILP systems. A miss factor greater than 1 contributes positively to read miss speedup, while a lower miss factor hinders read miss speedup.

All of our applications except Radix see a similar number of cache misses in both the Simple and ILP systems. Radix sees 15% fewer misses in ILP because of a reordering of accesses that otherwise conflict in the L2 cache. When the number of misses does not change, the ILP system sees (> 1) read miss ILP speedup if the exposed ILP latency is less than the Simple latency. This occurs when the benefits of memory parallelism in the ILP system outweigh any additional latency from contention.

$$Exposed \ Factor = \frac{l_{ILP,exposed}}{l_{Simple}}$$

(2.4)

Equation 2.4 defines the *exposed factor*, which represents the ratio of the average exposed latency in the ILP system to the average Simple system latency. Since the read miss speedup varies inversely with this factor, an exposed factor less than 1 contributes to higher read miss speedup, while a greater exposed factor leads to lower read miss speedup.

$$Exposed \ Factor = \frac{l_{ILP} - l_{ILP, overlapped}}{l_{Simple}}$$

(2.5)

$$Exposed \ Factor = \frac{l_{Simple} + l_{ILP,extra} - l_{ILP,overlapped}}{l_{Simple}}$$

(2.6)

$$Exposed \ Factor = 1 - \left(\frac{l_{ILP,overlapped}}{l_{Simple}} - \frac{l_{ILP,extra}}{l_{Simple}}\right)$$

(2.7)

Equations 2.5–2.7 then expand the exposed factor to express it in terms of  $l_{Simple}$ ,  $l_{ILP}$  (the average data read miss latency in the ILP system),  $l_{ILP,overlapped}$  (the average data read miss latency overlapped by the ILP system; equivalent to  $l_{ILP} - l_{ILP,exposed}$ ), and  $l_{ILP,extra}$  (the average data read miss latency increase caused by the ILP system; equivalent to  $l_{ILP} - l_{Simple}$ ). Since a low exposed factor leads to higher read miss ILP speedup, Equation 2.7 indicates that the exposed factor will be beneficial whenever the latency overlapped by the ILP system exceeds any increase in latency.

$$Overlapped \ Factor = \frac{l_{ILP, overlapped}}{l_{Simple}}$$

(2.8)

$$Extra Factor = \frac{l_{ILP,extra}}{l_{Simple}}$$

(2.9)

Equations 2.8 and 2.9 extract two new terms from the Equation 2.7: the *overlapped factor* and the *extra factor*. These represent the ratio of the overlapped latency and extra latency in the ILP configuration, respectively, relative to the total Simple latency.

$$Read Miss Speedup = \frac{Miss Factor}{1 - (Overlapped Factor - Extra Factor)}$$

(2.10)

Equation 2.10 summarizes the above equations by expressing the L2 data read miss ILP speedup in terms of three key parameters that we can directly gauge from our simulation results: the miss factor (Equation 2.3), the overlapped factor (Equation 2.8), and the extra factor (Equation 2.9). The miss factor expresses the impact of ILP on L2 read miss count

Figure 2.5 : Factors shaping data read miss ILP speedup. The latency figures indicate overall overlap and contention, while the MSHR graphs show specific sources of overlap (read MSHRs) and contention (total MSHRs).

through speculation and reordering, the overlapped factor quantifies the benefits of memory parallelism, and the extra factor indicates contention.

Figure 2.5(a) provides the average L2 read miss latencies for the applications in the Simple and ILP systems, normalized to the Simple system latency. The latency shown is the total miss latency, measured from address generation to data arrival, including the overlapped part (in ILP) and the exposed part that contributes to stall time. The difference in the bar lengths of Simple and ILP indicates the additional latency due to contention in ILP. When normalized to the length of the Simple bar, the exposed part of the ILP bar is the exposed factor of Equation 2.4, the overlapped part of the bar is the overlapped factor of Equation 2.8, and the difference in bar lengths is the extra factor of Equation 2.9.

All of the applications see some latency increase from resource contention in ILP. However, some of the applications (such as Em3d and Ocean) can overlap all of their additional latencies, as well as a large portion of their base (Simple) latencies. Such applications see a high memory ILP speedup. On the other hand, Radix cannot overlap its additional latency. Radix sees a slight ILP read miss speedup only because of its miss factor; overall, it sees a data memory slowdown because of its increase in contention (explained in more detail below).

We use the data in Figures 2.5(b) and 2.5(c) to further investigate the causes for the memory parallelism and contention-related latencies in these applications. (As described above, all applications studied except for Radix have a miss factor near 1; thus, memory parallelism and contention are the primary factors shaping data read miss ILP speedup.)

Sources of memory parallelism. Figure 2.5(b) shows the ILP system's L1 MSHR occupancy due to read misses for the applications. Each curve shows the fraction of total time for which at least N MSHRs are occupied by read misses, for each possible N (on the X axis). This figure shows that Em3d achieves significant overlap of read misses, with up to 7 read miss requests outstanding simultaneously at various times. In contrast, Radix almost never has more than 1 outstanding read miss at any time. This difference arises because read misses are clustered together in the instruction window in Em3d, but typically separated by too many instructions in Radix. Among the other applications, Erlebacher, FFT, Mp3d, and Ocean have moderate overlap, while LU and Water have poor overlap.

To understand the sources of poor read miss clustering in typical code, we consider a loop nest traversing a 2-D matrix. Figures 2.6(a) and 2.6(b) show a matrix traversal optimized for spatial locality, following much compiler research. The pseudocode is shown in row-major notation, while the graphic shows the matrix in row-major order, with crosses for data elements and shaded blocks for cache lines. In this row-wise traversal, L successive loop iterations access each cache line, where L is the number of data elements per cache line. While this traversal maximizes spatial locality, it minimizes clustering. For example, an instruction window that holds L or fewer iterations never holds read misses to multiple cache lines, preventing clustering. This problem is exacerbated by larger cache lines or larger loop bodies.

**Sources of contention**. Figure 2.5(c) extends the data of Figure 2.5(b) by displaying the total MSHR occupancy for both read and write misses. Write miss overlap in the system

Figure 2.6 : Pseudocode and representation of cache-behavior for a matrix traversal optimized for cache locality. The pseudocode is shown with row-major notation, and the graphic shows the matrix in row-major order. Crosses in the graphic represent matrix elements, and shaded blocks represent cache lines.

is illustrated by the difference between the read MSHR occupancy and the total MSHR occupancy in Figures 2.5(b) and (c). The figure indicates that Radix has high write miss overlap. This overlap does not contribute to an increase in memory ILP speedup since write latencies are already hidden in both the Simple and ILP systems due to release consistency. The write miss overlap, however, increases contention in the memory hierarchy, causing cache hits to see exposed stalls and resulting in a 29% ILP memory slowdown in Radix. Contention-related latencies in most of the other applications come primarily from read misses, but these effects are offset by the resulting benefits in memory stall time.

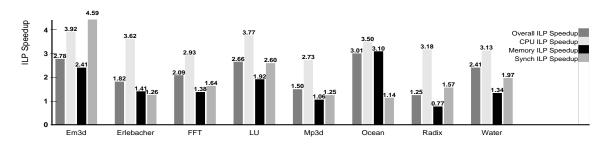

ILP features can also reduce or hide synchronization time by reducing computation time, overlapping data read misses, and overlapping synchronization with other operations. ILP features can increase synchronization stall time because of additional contention in the memory system. These factors lead to synchronization ILP speedups ranging from 1.07 to 4.59 for our applications; however, synchronization has a small impact on total execution time and thus also contributes little to overall ILP speedup.

Figure 2.7 : Impact of ILP on uniprocessor execution time and its components.

Figure 2.8 : ILP speedup of total execution time and components as seen in uniprocessor system.

## **2.3** Experimental results on uniprocessor system

Figure 2.7 shows the impact of ILP on uniprocessor execution time. As in the multiprocessor, this impact is highly variable, providing 30–70% reduction in execution time. However, the average execution time reduction is somewhat higher (56% for the codes which have both uniprocessor and multiprocessor versions, 53% across all codes), as are the individual execution time reductions in all applications with comparable multiprocessor versions except for Ocean.

Figure 2.8 provides the ILP speedups for the uniprocessor configuration for reference. The uniprocessor also generally sees lower memory ILP speedups than CPU ILP speedups. However, the impact of the lower memory ILP speedup is greater in the multiprocessor because the longer latencies of remote misses and increased contention result in a larger relative memory component in the execution time (relative to the uniprocessor). Second, the dichotomy between local and remote miss latencies in a multiprocessor causes some

Figure 2.9 : Impact of ILP on execution time for systems with faster processors.

applications (most notably, Em3d and LU) to see substantially lower memory ILP speedup in the multiprocessor than in the uniprocessor. For effective latency tolerance, read misses must be overlapped with other read misses *that have similar latencies*; this is trivial in the uniprocessor, but not always true in a CC-NUMA multiprocessor system<sup>\*</sup>.

# 2.4 Sensitivity to system latencies

Processor speeds and external memory latencies diverge further for processors in the gigahertz frequency range. To model this trend, we also performed experiments that modified our base configuration to include 1 GHz processors without changing any absolute memory hierarchy times (in ns or MHz). The results in Figure 2.9 show behavior qualitatively similar to Figures 2.2 and 2.7, with ILP having a greater impact on CPU time than data

<sup>\*</sup>This would also not necessarily be true in an SMP system, since cache-to-cache transfers have different characteristics from ordinary data transfers.

memory time and data memory time making up a much larger fraction of total execution time in the ILP system than the Simple system.

## 2.5 Summary and Implications

This study finds that for the applications and systems that we investigate, ILP techniques effectively address the CPU component of execution time, but are less effective in reducing the data memory component of execution time, which is dominated by read misses. This disparity arises in our applications primarily because of insufficient opportunities to overlap multiple read misses and to a lesser extent because of system contention from more frequent accesses in the ILP system. As a result, data read miss latency actually appears as a greater relative performance bottleneck in ILP systems than in previous-generation systems, despite the latency-tolerating techniques incorporated in ILP processors.

These observations suggest that ILP systems have a greater need for both conventional and novel additional techniques to tolerate or reduce memory latency. A commonly used technique for better latency tolerance is software-controlled non-binding prefetching [CKP91, MG91, MLG92, Mow94, TE95, LM96]. Chapter 3 evaluates the interaction of this technique with instruction-level parallelism. Our results also motivate a specific technique novel to ILP processors: application-level clustering of read misses. Chapter 4 proposes and evaluates code transformations that improve miss clustering and also shows that these techniques can facilitate improved software prefetching.

Hardware enhancements can also increase read miss overlap; for example, through a larger instruction window. However, such hardware may be increasingly insufficient or infeasible as the processor-memory speed-gap continues to grow. Targeting contention requires increased system hardware resources or other latency reduction techniques (e.g. [AHAA97]).

# Chapter 3

# Interaction of Software Data Prefetching with Instruction-Level Parallelism

Chapter 2 shows that the ILP system sees a greater bottleneck from memory latency than the Simple system. To reduce memory stall time, many current processors support software-controlled non-binding prefetching [ERB+95, Hun95, MIP96, Sun97]. With this technique, the compiler or programmer schedules an explicit prefetch instruction for a location that will be accessed by the processor at a later time, with the goal of bringing the location into the processor's cache before it issues a demand memory access for that location [CKP91]. Previous studies have shown that software-controlled non-binding prefetching can eliminate a large fraction of memory stall time in shared-memory multiprocessors and uniprocessors [MG91, MLG92, Mow94, TE95, LM96]. However, the multiprocessor studies used previous-generation processors with single-issue, static scheduling, and blocking reads. Some of the uniprocessor studies modeled ILP processors, but did not specifically relate their benefits or limitations to ILP features. Consequently, such studies do not account for the interactions between software prefetching and the other latency-tolerating techniques already incorporated in ILP-based systems. An analysis of these interactions is required to assess the effectiveness of current software prefetching strategies for state-ofthe-art systems.

This chapter seeks to understand how software prefetching interacts with ILP, and to identify its limitations. Section 3.1 gives detailed information on the prefetching algorithms used in this study. Section 3.2 describes the systems, applications, and metrics used in this study. Section 3.3 gives the experimental results of the study. Section 3.4 describes the sensitivity of the results in this study to our simulated system latencies. Section 3.5

summarizes the results of the study and discusses possible solutions to the limitations of prefetching.

# **3.1** Software prefetching algorithm

The following discusses the best known and implemented software prefetching algorithm for regular memory references, as well as prefetching algorithms that support irregular references.

#### 3.1.1 Algorithm for Adding and Scheduling Software Prefetches

The best known software prefetching algorithm implemented in a compiler is the loopbased algorithm of Mowry et al. [Mow94, MG91, MLG92]. The *analysis* phase of the algorithm identifies the static references which can miss (leading references). Then, the *scheduling* phase uses loop peeling, unrolling, and strip-mining to insert prefetches only for the dynamic instances of leading references that are expected to miss. The innermost loop for a miss reference is software pipelined to schedule a prefetch ahead of the demand access by a certain number of iterations, called the *prefetch distance*. The prefetch distance (*d*) is computed as:

$$d = \min(L \times \lceil \frac{D}{CL} \rceil, I_i)$$

(3.1)

The terms in Equation 3.1 are defined as follows:

- D expected miss latency in cycles

- *C* estimates the shortest possible path through an iteration (in cycles)

- L number of successive inner-loop iterations that share a cache line

- $I_i$  total number of inner-loop iterations (the upper limit on inner-loop software pipelining)

The term  $L \times \left\lceil \frac{D}{CL} \right\rceil$  represents the distance needed to completely overlap the prefetch latency.

The software pipelining applied produces a prologue, steady-state, and epilogue from the original inner loop. The prologue consists only of prefetches to cover the data of the first d iterations of the original loop. The steady-state includes both prefetches (scheduled

```

for (j=0; j<I_o; j++)

for (i=0; i<I_i; i++)

\cdots A[j,i]

(a) Original code

for (j=0; j<I_o; j++)

for (j=0; i<I_o; j++)

for (i=0; i<d; i++)

for (i=0; i<I_i - d; i++)

if (imod L \equiv 0) PF(\&A[j, i+d])

\cdots A[j, i]

(b) After prefetching

```

Figure 3.1 : Pseudocode of a 2-D matrix traversal, before and after applying software prefetching. All pseudocode uses row-major notation.

according to the prefetch distance) and computation for  $I_i - d$  iterations of the original loop. Either strip-mining, unrolling, or a conditional test is used to insure that a prefetch is issued for a reference only once for every L iterations of the original loop. The epilogue includes only computation for the last d iterations of the original inner loop; no prefetches are issued since all the inner-loop iterations have already been prefetched in the prologue and steady-state. Figures 3.1(a) and 3.1(b) illustrate a matrix traversal before and after applying software prefetching, respectively.

### 3.1.2 Prefetching Algorithms for Irregular Memory References