# RF-IV Waveform Engineering Inspired MMIC design

A thesis Submitted to Cardiff University in candidature for the degree of

Doctor of Philosophy

By

Mervin Haynes, BEng, MSc.

Division of Electronic Engineering School of Engineering Cardiff University United Kingdom

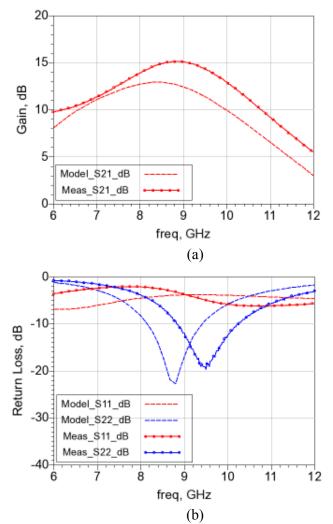

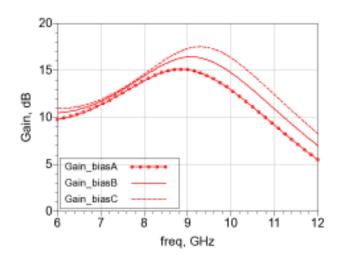

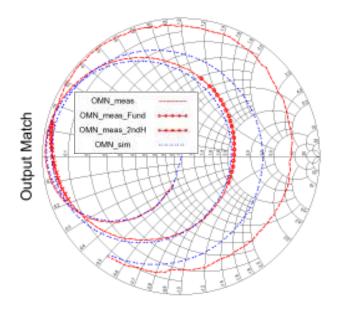

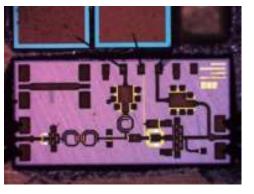

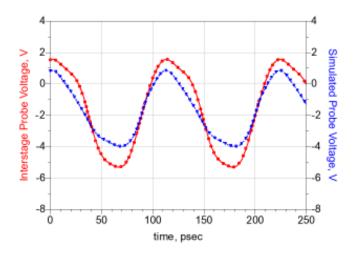

# DECLARATION

This work has not been submitted in substance for any degree or award at this or any other university or place of learning, nor is being submitted concurrently in candidature for any degree or other award.

# STATEMENT 1

This thesis is being submitted in partial fulfilment of the requirements for the degree of PhD.

# STATEMENT 2

This thesis is the result of my own independent work/investigation, except where otherwise stated, and the thesis has not been edited by a third party beyond what is permitted by Cardiff University's Policy on the use of Third Party Editors by Research Degree Students. Other sources are acknowledged by explicit references. The views expressed are my own.

| Signed | (Candidate) | Date |

|--------|-------------|------|

| 0      | ()          |      |

# STATEMENT 3

I hereby give consent for my thesis, if accepted, to be available online in the University's Open Access repository and for inter-library loan, and for the title and summary to be made available to outside organisations.

# ABSTRACT

The research work presented in this thesis sets out to investigate improvements to the power amplifier (PA) design cycle through the use of Waveform Engineering techniques. This is approached using alternative simulation methods with strong links to the data available from time domain based radio frequency waveform measurement and characterisation systems.

One key objective of this work is to improve the overall efficiency of the radiofrequency power amplifier stage by focusing on circuit design. More specifically, the direct utilisation of waveform-engineering techniques in the development of multi-stage amplifiers to improve power added efficiency was targeted.

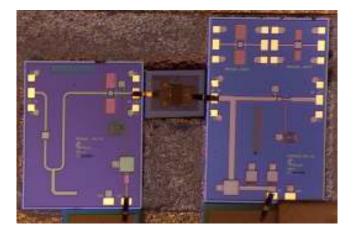

In developing these power amplifier design methodologies, the techniques are demonstrated and validated using monolithic microwave integrated circuit (MMIC) implementation. This work has also led to an increase in understanding of the operation of the device terminal waveforms which is used to drive an alternative simulation approach.

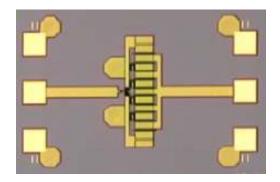

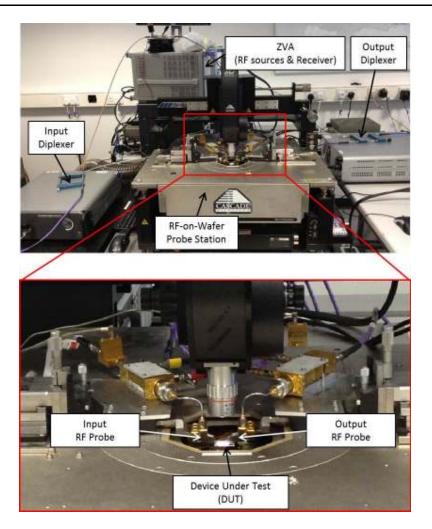

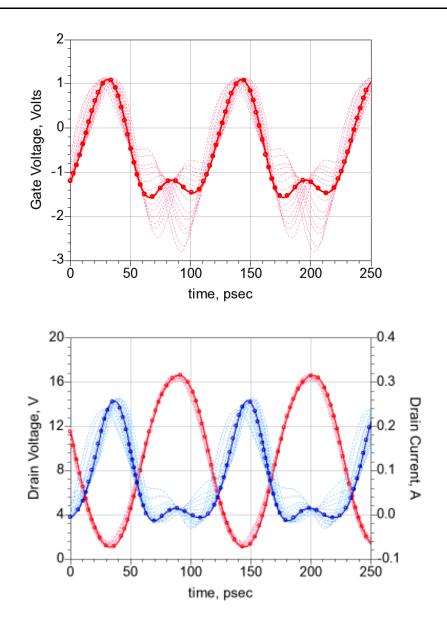

Through the use of standard computer-aided design (CAD) device models and measured waveform data, a 2-stage MMIC Gallium Nitride power amplifier has been detailed. This amplifier also uses internal node probe points in the interstage matching network, along with a new application of the waveform measurement system, to allow investigation of the terminal waveforms to validate the performance.

This direct implementation of these waveform measurements provides valuable information on the design of the interstage networks to reduce the number of design iterations resulting in a more efficient design process.

Waveform-engineering-based designs completed in this research have been demonstrated with test circuits and the time domain measurement system to demonstrate new modes of operation, as well as complete designs realised as prototype MMIC power amplifiers.

# SUMMARY OF ORIGINAL CONTRIBUTION

This work contains three main original contributions during the development of this thesis:

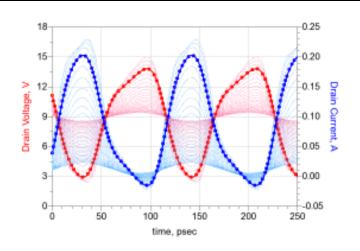

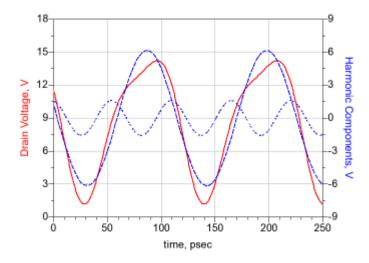

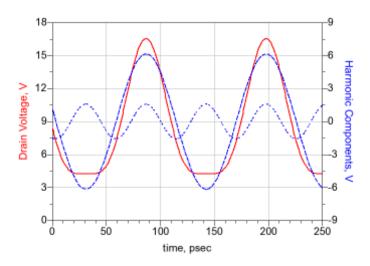

- 1. The use of voltage source simulation methods to define the correct and appropriate waveforms at the intrinsic nodes of the Device Under Test. The waveforms are defined by the theoretical expressions and used directly in the simulator to force the correct amplifier operating mode on the transistor.

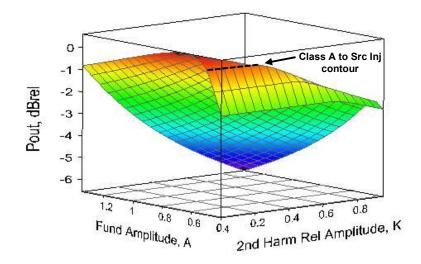

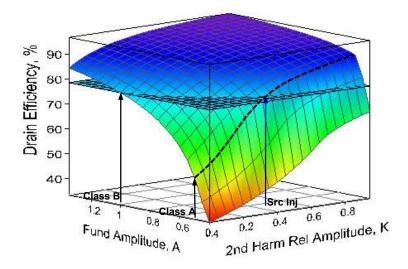

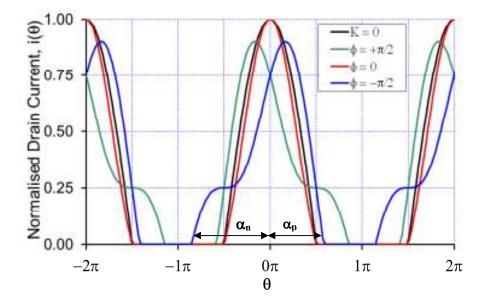

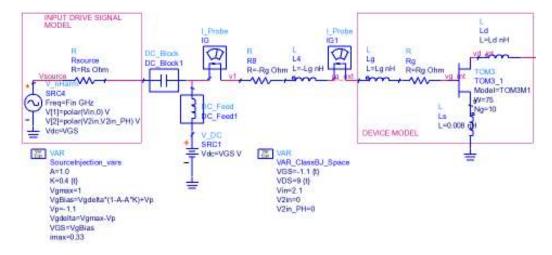

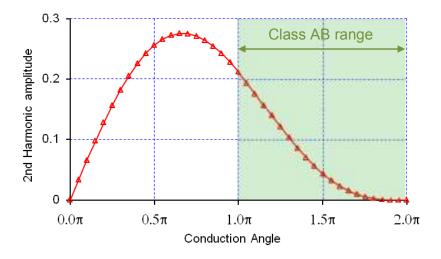

- 2. A Second harmonic source injection amplifier design strategy is presented. The theoretical waveform sets are presented to define the design space, and this is used in the design of a two stage amplifier. Practical device parameters are considered which detail the performance limits which are achievable.

- 3. An in-circuit waveform measurement and analysis technique is outlined. This approach uses a standard time domain load pull system in a novel manner. The use of the system creates a high impedance at the fundamental and harmonic frequencies, allowing direct contact measurement at internal circuit nodes, without loading the circuit.

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank Professor Paul Tasker for his help and guidance as supervisor during the journey of this PhD. His expertise and knowledge in the field of Microwave Engineering are outstanding and I am grateful for his patience and understanding during our discussions when he tried to explain the concepts to me. I would also like thank my second supervisor Professor Johannes Benedikt for his support and mentoring. It was as a result of some initial discussions with him that led to me pursuing this course of study.

I would also like to thank Professor Steve Cripps who has helped me enormously during my time at Cardiff. His insights into circuit design are unique and our discussions have been invaluable in the development of this work.

There are numerous others in the Cardiff University research group over the years who have helped and supported my endeavours. A special thanks to Simon Woodington, Tudor Williams, Randeep Saini, James Bell, Tim Canning, Minghao Koh and Michael Casbon all who helped educate me on the 'subtleties' of the measurement system in order to configure the equipment for my specific needs. There are too many others to name individually but I would like to thank you all.

My thanks also go to Mr Paul Robertson, former head of department at Selex ES Ltd, who encouraged me and supported my request to take this degree. He sadly passed away before the end of this journey but my gratitude will always be with him – Thank you Paul.

Finally, and most importantly, I would like to thank my family. My wife Victoria has been supportive during these long years of study. She has not complained throughout my endless nights in front of the computer screen and the days away at University. She has taken the additional burden of things I have neglected to do in her stride and has always been there for me. I am truly blessed to have her in my life.

I dedicate this thesis to my children Oliver and Daisy.

#### LIST OF PUBLICATIONS

Haynes, Merv; Cripps, Steve C.; Benedikt, Johannes; Tasker, Paul J.; , "PAE improvement using 2nd harmonic source injection at x-band," Integrated Nonlinear Microwave and Millimetre-Wave Circuits (INMMIC), 2012 Workshop on , vol., no., pp.1-3, 3-4 Sept. 2012.

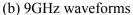

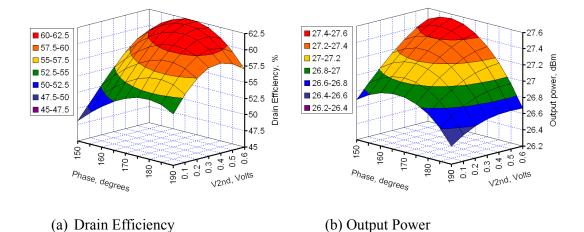

*Abstract* – Theory and measurements are presented comparing Class B amplifier performance of a 0.5 W GaAs pHEMT driven with (a) a sinusoidal signal or (b) using 2nd harmonic input injection. Engineering the input waveform in this way leads to a class B operating mode requiring 3.4 dB less input drive at 9 GHz. This increases power gain and maintains the output power above 26.4 dBm. The 2nd harmonic injection case shows a 5.9% Power Added Efficiency (PAE) improvement over the class B case.

Haynes, M.; Tasker, P.J.; Cripps, S.C., "High Efficiency PA Design Strategy at X-Band," Compound Semiconductor Integrated Circuit Symposium (CSICS), 2013 IEEE, vol., no., pp.1-4, 13-16 Oct. 2013. doi: 10.1109/CSICS.2013.6659232.

*Abstract* – There is an growing demand for high efficiency power amplifiers at high frequencies, X-band and above. It is well understood that design strategies targeting high efficiency requires output IV waveform engineering; switching the mode of device operation from the Class A or AB modes to the Class B or C modes. Unfortunately, this mode switch results in a significant reduction in gain, which since the maximum amount of gain at high frequencies is limited, can result in degraded rather than enhanced power added efficiency. An improved design strategy, incorporating input IV waveform engineering, can be used to minimize this gain reduction thus providing for improved power added efficiency.

Haynes, M.; Bullen, A; Hone, D; Singh,D; "Overview of GaN Technology applications within Finmeccanica" in Automated RF and Microwave Measurement Society Conference, April 2016. *Abstract* – The increased availability of GaN technology over recent years has enabled higher power amplifiers and components but has had a slower take up in military systems. The cost and access of the technology and the performance at the high microwave frequencies has kept this largely in the research domain. Solutions to these barriers are now coming to fruition and this technology is breaking through into products.

The early years used single transistors which provided simple hybrid circuits to demonstrate the practically achievable performance and the positive benefits of this technology. The follow on development, through various EDA programmes (Korrigan and Magnus) plus internal research initiatives, have moved the technology forward into MMIC implementation. This is contrasted against the improvement in availability and performance of COTS transistor components which has kept hybrid microwave solutions alive for military airborne systems.

# LIST OF SYMBOLS AND ABBREVIATIONS

| ADS       | Advanced Design System, CAD tool from Keysight Technologies                  |

|-----------|------------------------------------------------------------------------------|

| AESA      | Active Electronically Scanned Array                                          |

| ALPS      | Automatic Load Pull System                                                   |

| С         | Capacitance                                                                  |

| CAD       | Computer-Aided Design                                                        |

| CF        | Centre Frequency                                                             |

| $C_{j0}$  | Schottky junction zero bias capacitance                                      |

| CW        | Continuous Wave                                                              |

| DARPA     | Defense Advanced Research Projects Agency                                    |

| d         | Dielectric Thickness                                                         |

| dB        | Decibels                                                                     |

| dBc       | Decibels (reference to carrier power)                                        |

| dBm       | Decibels (reference to 1mW)                                                  |

| dc        | Direct Current                                                               |

| DRFM      | Digital Radio Frequency Memory                                               |

| DUT       | Device-Under-Test                                                            |

| Eg        | Energy Gap                                                                   |

| EIRP      | effective isotropically radiated power                                       |

| ESCAN     | Electronic Scan (Antenna)                                                    |

| EW        | Electronic Warfare                                                           |

| eV        | Electron Volts                                                               |

| F, pF,fF  | Farads, pico-Farads, Femto-Farads, unit of capacitance                       |

| FD30      | $0.3 \mu m$ gate length GaAs pHEMT MMIC process from Compound Photonics $^1$ |

| FET       | Field Effect Transistor                                                      |

| Freq., f  | Frequency                                                                    |

| GaAs      | Gallium Arsenide                                                             |

| GaN       | Gallium Nitride                                                              |

| $G_{P,A}$ | Class A device power gain                                                    |

| $G_{P,B}$ | Class B device power gain                                                    |

| GSG       | Ground-Signal-Ground, connection type used on MMICs and the probes           |

| H, nH     | Henrys, nano-Henrys unit of inductance                                       |

|           |                                                                              |

<sup>&</sup>lt;sup>1</sup> Compound Photonics was formerly RFMD(UK) Ltd foundry in Newton Aycliffe, Co Durham.

| HPA          | high power amplifier                                              |

|--------------|-------------------------------------------------------------------|

| HEMT         | High Electron Mobility Transistor                                 |

| HT           | Harmonic tuned                                                    |

| Hz, GHz      | Hertz, Giga-Hertz                                                 |

| I, i         | Current                                                           |

| Idq          | Quiescent Drain Current                                           |

| Idss         | Saturation Drain-Source Current                                   |

| Ids          | Drain-Source Current                                              |

| Igen         | Current-Generator Plane                                           |

| Igd          | Gate-Drain Current                                                |

| Igs          | Gate-Source Current                                               |

| ISS          | Impedance Standard Substrate, as used for measurement calibration |

| j            | Denotes the imaginary component of a complex impedance            |

| L            | Inductance                                                        |

| LP           | Load-Pull                                                         |

| μm           | micro-metres                                                      |

| MAG          | Maximum Available Gain                                            |

| MMIC         | Monolithic Microwave Integrated Circuit                           |

| Nd           | Semiconductor doping concentration                                |

| NL           | Nonlinear                                                         |

| Р            | Power                                                             |

| $P_{1dB}$    | Output power at 1dB gain compression                              |

| PA           | Power Amplifier                                                   |

| PAE          | Power-Added Efficiency                                            |

| PDK          | Process Design Kit                                                |

| PHD          | Poly Harmonic Distortion                                          |

| pHEMT        | Pseudomorphic High Electron Mobility Transistor                   |

| PUF          | Power Utilisation Factor                                          |

| q            | Electronic charge                                                 |

| R            | Resistance                                                        |

| RF           | Radio Frequency                                                   |

| RF-IV        | RF Current-Voltage                                                |

| RFOW         | RF-on-wafer                                                       |

| S-parameters | Scattering Parameters                                             |

|              |                                                                   |

| SiC                | Silicon Carbide                          |

|--------------------|------------------------------------------|

| SWaP-C             | Size, Weight, Power and Cost             |

| TRL                | Thru, Reflect, Line – Calibration method |

| TRM                | Transmit-Receive Module                  |

| UAV                | Unmanned Aerial Vehicle                  |

| UGW                | Unit Gate Width, of transistor device    |

| V, v               | Voltage/Volts                            |

| Va                 | Applied Schottky junction bias           |

| Vbi                | Schottky built in potential              |

| Vds                | Drain-Source Voltage                     |

| Vgd                | Gate-Drain Voltage                       |

| Vgs                | Gate-Source Voltage                      |

| Vk                 | Knee Voltage                             |

| Vp                 | Pinch-off Voltage                        |

| VNA                | Vector Network Analyser                  |

| W, mW              | Watts, milli-Watts                       |

| Х                  | Reactance                                |

| Ζ                  | Impedance                                |

| ε <sub>r</sub>     | Relative Dielectric Constant             |

| ε <sub>s</sub>     | Permittivity                             |

| K <sub>eff</sub>   | Effective Dielectric Constant            |

| λ                  | Wavelength                               |

| $\eta_{D,A,ideal}$ | Ideal Drain Efficiency, Class A          |

| $\eta_{D,A}$       | Drain Efficiency, Class A                |

| $\eta_{D,B}$       | Drain Efficiency, Class B                |

| $\eta_G$           | Gain efficiency factor                   |

| $\eta_K$           | Knee voltage efficiency factor           |

| $\eta_{\rm L}$     | Matching loss efficiency factor          |

| $\eta_D$           | Drain Efficiency                         |

| $\eta_{FB}$        | Feedback Efficiency factor               |

| Ø                  | Electrical Length                        |

| Γ                  | Reflection Coefficient                   |

| Ω                  | Ohms                                     |

# CONTENTS

| 1 | Int | roduction1                                            |

|---|-----|-------------------------------------------------------|

|   | 1.1 | Airborne Radar HPA requirements2                      |

|   | 1.2 | EW HPA requirements                                   |

|   | 1.3 | MMIC HPAs                                             |

|   | 1.4 | Future system trends                                  |

|   | 1.5 | High Power Microwave Amplifier Design Process5        |

|   | 1.6 | Waveform Engineering                                  |

|   | 1.7 | Research Objective & Thesis Structure                 |

| 2 | Am  | plifier Operating Modes21                             |

|   | 2.1 | Amplifier operating modes                             |

|   | 2.2 | Factors affecting Efficiency                          |

|   | 2.3 | Multistage amplifiers                                 |

|   | 2.4 | Conclusion                                            |

| 3 | Wa  | veform De-embedding                                   |

|   | 3.1 | Calibration and de-embedding40                        |

|   | 3.2 | De-embedding measurement data42                       |

|   | 3.3 | Determination of de-embedding networks44              |

|   | 3.4 | De-embedding to the intrinsic device plane            |

|   | 3.5 | Conclusion                                            |

| 4 | Sim | ulation Methods68                                     |

|   | 4.1 | Standard Large Signal simulation methods68            |

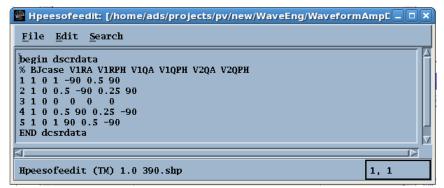

|   | 4.2 | Voltage source simulation methods73                   |

|   | 4.3 | Conclusion                                            |

| 5 | RF  | -IV Waveform engineering                              |

|   | 5.1 | Strategies for improving Efficiency92                 |

|   | 5.2 | Power gain under reduced conduction angle operation95 |

|   | 5.3 | Device Input Impedance Effects99                      |

|   | 5.4 | Input Waveform Engineering109                         |

|   | 5.5 | Design strategy using input waveforms138              |

|   | 5.6 | Conclusion                                            |

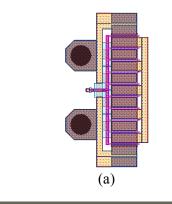

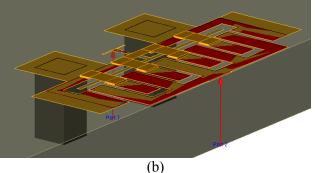

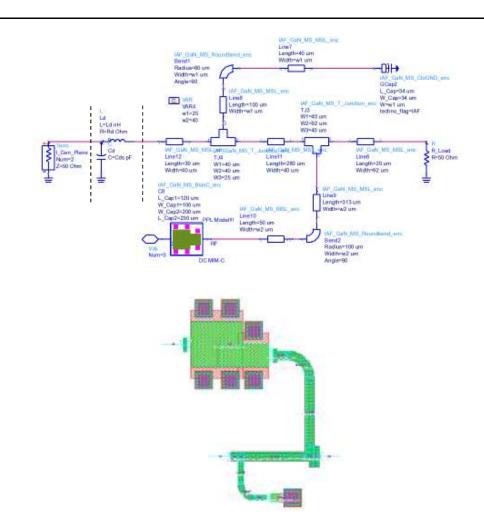

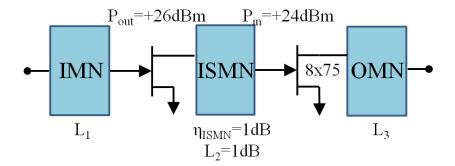

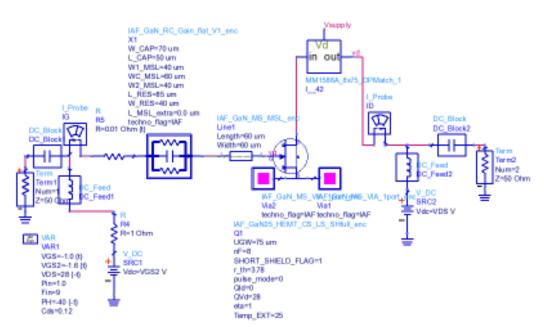

| 6 | Gal | N MMIC Amplifier Design142                            |

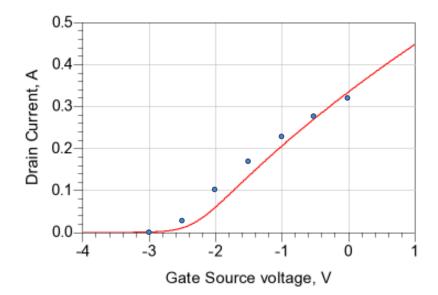

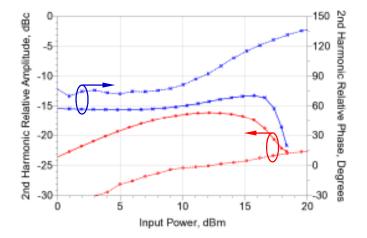

|   | 6.1 | IAF GaN25 process overview144                         |

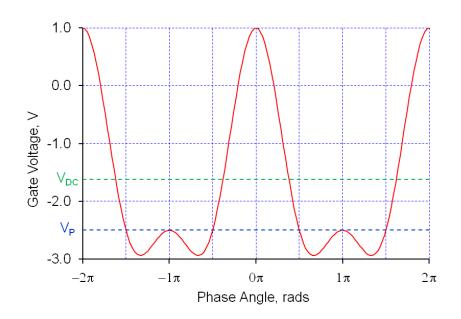

|   | 6.2 | Initial PA design analysis144                         |

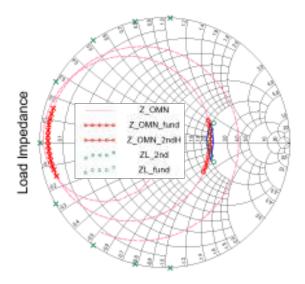

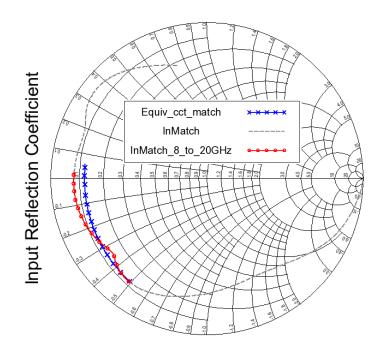

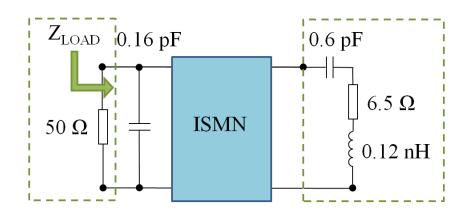

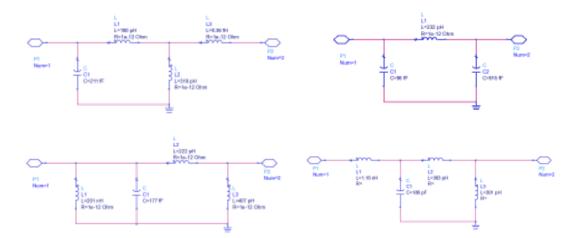

|   | 6.3 | MMIC Design                      | 150 |

|---|-----|----------------------------------|-----|

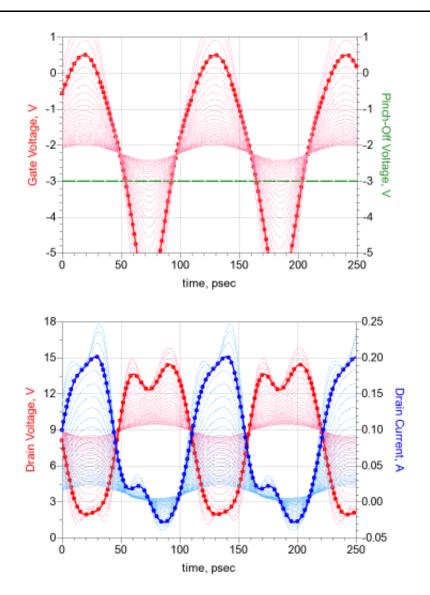

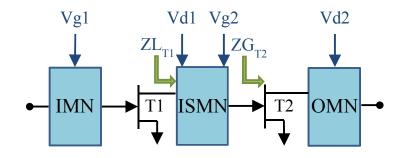

|   | 6.4 | Interstage Waveform Measurement  |     |

|   | 6.5 | MMIC Measurements                |     |

|   | 6.6 | MMIC Circuit Reverse Engineering |     |

| 7 | Cor | nclusions and further work       | 210 |

|   | 7.1 | Conclusions                      |     |

|   | 7.2 | Further Work                     | 211 |

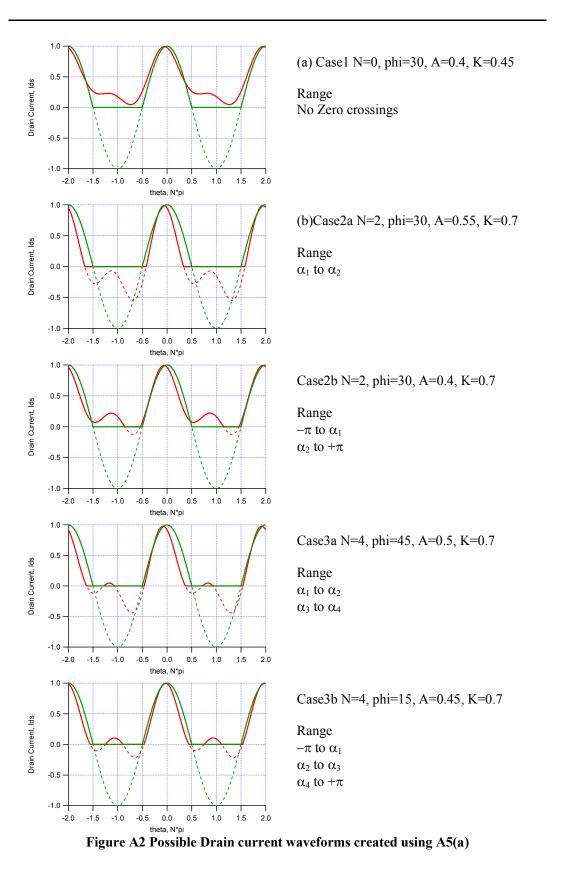

| 8 | AP  | PENDICES                         |     |

|   | 8.1 | Appendix A                       |     |

|   | 8.2 | Appendix B                       |     |

| 9 | Ref | ferences                         | 231 |

#### **1** INTRODUCTION

The high power amplifier (HPA) is a key building block in many military Radar and Electronic Warfare (EW) systems. Modern radars are realised with Active Electronically Scanned Array (AESA) Antennas [1],[2]. These systems deliver high effective isotropic radiated power (EIRP) by the virtue that the power from many radiating elements are combined. This power addition, together with the array factor (AF) focusses the power in a specific direction.

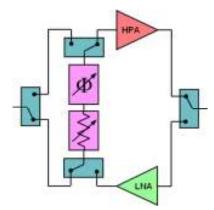

In these AESA systems the design focus centres on the transmit-receive module (TRM) as they are the crucial building blocks with a dominant impact on performance [3]. The basic block diagram of a typical TRM is shown in Figure 1.1, highlighting the major functions. The focus of this work will concentrate on the HPA.

Figure 1.1 Typical 'Common leg' Transmit Receive module architecture

In the transmit path of an 'n' element array, each TRM provides 1/n of the total antenna power, where n ranges from ~10 in lightweight unmanned air vehicle (UAV) systems to ~2000 in large fire-control radars, leading to the requirement of the high power amplifiers (HPAs) to deliver several watts output power to each antenna element.

Airborne electronic warfare (EW) power modules, in contrast, tend to be transmit only, with the receive function performed by the Electronic Support Measures (ESM) part of the equipment. Recent developments in off-board RF decoys however [4], [5] have shown the need for similar transmit-receive functionality in EW applications.

These EW HPAs have similar power output requirements to AESA radar applications but with increased bandwidth.

#### 1.1 Airborne Radar HPA requirements

Airborne ESCAN radars typically operate in X-band for airborne fire-control or surveillance systems, compared to S-band or C-band in the case of naval radars. The electrical requirements are diverse, but specifications for solid-state modules often include the following:-

- In the transmit path each module must provide a typical peak output power of several watts operating with pulse lengths ranging from 500ns to as much as several hundred microseconds.

- Prime generator power is at a premium, especially in fighter aircraft, all the

electrical characteristics must be achieved at minimum DC consumption. It

should be remembered that cooling, DC-DC conversion, and power

switch/circulators dominate the overall efficiency of these RF systems. All

these factors demand the availability of highly efficient HPAs.

- Mass is severely constrained in airborne platforms, especially in the case of transmit-receive modules. Because an E-scan antenna may contain 1000-2000 such modules, each gram added to the TRM will immediately increase the antenna mass by 1-2kg, but the problem is compounded by the need for a stronger structure to support a heavier array.

- Cost of the TRM is also a key parameter as the total cost is then scaled by the number of modules. Minimising cost of the key functions is translated into reduced chip area for MMIC components.

The basic system design of power modules is quite elementary, with only simple passive networks to create the desired beam steering and polarisation signals. However the electrical implementation is complex due to the small physical size, wide bandwidths and thermal problems which exist in such modules. In order to get the functionality in the required size, extensive use has been made of GaAs MMIC technology, which allows integration of circuit functions with the required performance across the operating band. Other technologies are emerging which could offer enhanced performance are being considered (e.g. GaN for HPA applications).

#### **1.2 EW HPA requirements**

The wide bandwidth and high frequency operation, typically 6-18GHz, of the EW power modules has meant the RF power amplifiers are in the domain of GaAs pHEMT technology and more recently GaN FETs. Operation is generally at CW (or very long pulse lengths) which results in increased power dissipation, as power added efficiencies (PAE) are lower than those for radar bands. Higher channel temperatures result which can adversely affect reliability.

The prime power is also of consideration, especially in the off-board RF decoys systems [4], [5] where this power is derived from battery technology. Less efficient amplifiers will lead to reduced jamming time. In addition these systems have small form factors and cooling is very limited so efficient operation is paramount.

The HPA components need also to be capable of working without some form of output isolation, such as a circulator. These components are difficult to achieve across the EW frequency range. However, without any output isolation it is possible for the amplifiers to see highly mismatched loads producing high voltages at the output of the devices resulting in destructive breakdown.

#### 1.3 MMIC HPAs

During the 1980s MMIC technology was being developed for AESA radar applications, with GaAs as the semiconductor of choice [1]. In spite of much interest in GaAs HBT amplifiers during the 1990s, GaAs pHEMT technology (0.5µm or 0.25µm) now offers good power-added efficiency (>40% at X-band) and is more widely deployed. Although a single MMIC will deliver up to 10W at 10GHz, a balanced pair of HPAs is likely to offer comparable efficiency and better match even when switched off. In radar modules operating at any significant duty cycle the HPA drain-source current dominates the power consumption, and the component is often biased to give Class AB operation rather than Class A. Following fabrication of the MMIC, the wafer is thinned in order to reduce the thermal resistance of the finished die, which will typically be soldered to a thermally conductive plinth.

More recently, the performance requirements for military systems has become more demanding requiring higher power and improved efficiency HPAs. The development of GaN technology is now being pursued for these components.

| Technology | Frequency<br>(GHz) | Power | Size<br>(mm) | PAE     | Source      | Ref  |

|------------|--------------------|-------|--------------|---------|-------------|------|

| GaAs pHEMT | 6-18               | >5 W  | 5.8 x 5.8    | ~ 22%   | BAE Systems | [8]  |

| GaAs pHEMT | 6 – 18             | 5.6 W | 5.7 x 4.3    | ~ 25%   | TriQuint    | [9]  |

| GaAs HBT   | 9 - 10             | 11 W  | 5 x 3.6      | ~ 40%   | UMS         | [10] |

| GaAs pHEMT | 9 - 10             | 11 W  | 4.4 x 3.6    | 43-45 % | MACOM       | [11] |

| GaAs pHEMT | 8.5-10.5           | ~ 8 W | 3.5 x 2.6    | 35-42%  | TriQuint    | [12] |

Table 1.1 summarises some currently available wideband and narrowband HPA GaAs MMICs and the relative performance figures.

Table 1.1 Sample of commercially available HPA MMICs

The data shows that the X-band power amplifiers have efficiencies around 40% and the wideband amplifiers around 30%.

It is clear from this simple top level view of the radar and EW systems that the power amplifier is the key driver in performance, packaging, cooling and cost. Developing highly efficient power amplifiers addresses several of these important aspects simultaneously. Reduced power dissipation helps more modules to be powered up improving transmit power<sup>2</sup>. This also reduces thermal load on the cooling equipment. It also allows the packaging to be simpler, without having to resort to exotic materials and assembly techniques, thus reducing cost.

#### 1.4 Future system trends

The efficiency of RF PAs is becoming more important for future systems where multi-functionality is to be exploited [6],[7]. In these systems a single antenna can be used for radar, EW and communications. Other systems are optimised to use multiple communication bands in a single unit. These systems can be reconfigurable and the use of bespoke amplifiers for each application is not feasible, however as shown from section 1.3, increasing the operational bandwidth generally leads to a lowering of efficiency.

<sup>&</sup>lt;sup>2</sup> Modules can be switched off to keep within dc power budgets in the AESA system. Allowing more modules to be active increases the total transmitted power.

The drive for future systems is therefore for reduced size, weight, power and cost (SWaP-C). In this respect there are several high profile research programmes aiming to improve technology and applications to increase efficiency in reduced form factors or to manage the associated thermal management problem.

Improving the efficiency at the circuit level relaxes the thermal consideration and will complement the improvements made under these programmes, and allow higher power operation on standard foundry processes where the exotic materials and processes may not exist.

#### 1.5 High Power Microwave Amplifier Design Process

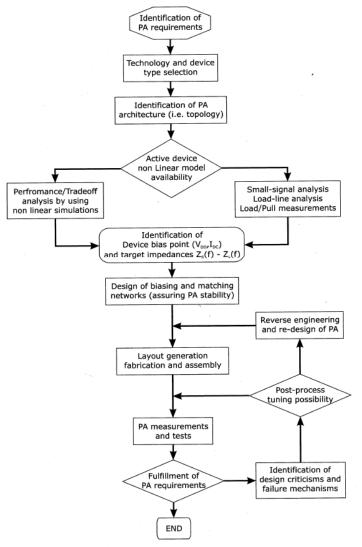

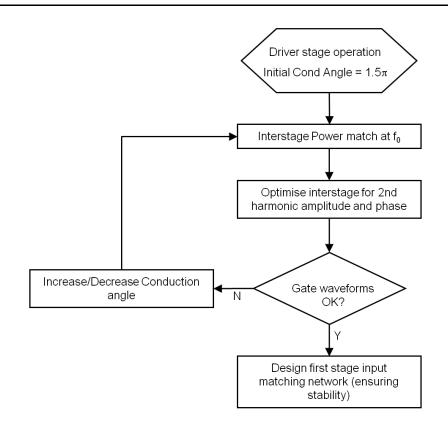

The typical power amplifier design flow, Figure 1.2 [13] starts with capturing the initial system performance and operational requirements. The active device technology choice and biasing Class follow. In low frequency microwave designs, the device choice is varied but as the frequency increases the technology choice reduces. At X-band frequencies and above, the implementation of power amplifiers in the 1 W to 10 W output power range is dominated by the use of Field Effect Transistor (FET) devices in Gallium Arsenide (GaAs) and, more recently, Gallium Nitride (GaN) semiconductor materials. The work in this thesis will concentrate on these FET devices (and in particular MMIC implementation) but the techniques and approach are technology independent.

The basic amplifier circuit then defines a load impedance space,  $Z_L(f)$ , for correct operation at the chosen bias point and operating class. These impedances can be identified by various means.

- 1. Cripps method approximation

- 2. Simulation using CAD software with device non-linear models

- 3. Load pull measurements

These processes increase in complexity down the list from the basic theoretical view point to the full measurement based load pull approach.

The output from this process is a defined load impedance space  $Z_L$  for the device to deliver the output power and efficiency in accordance with the specification. The design

then becomes a problem of synthesising the network response to deliver these impedances to the device reference plane.

It is interesting to note that during this design flow there is little attention to the device waveforms, even though the underlying theory of the amplifier classes comes from a RF I-V waveform viewpoint. The design task and resulting circuit optimisation are confined to the frequency domain [13]. Furthermore, in the design of multistage amplifier optimisation goals relating to the output power and efficiency are usually defined. Allowing the interstage matching to be varied with these goals is obviously non-optimum as the variables and the goals are uncoupled as the internal load line and operating waveforms are not considered.

Figure 1.2 Typical HPA design flow [13]

#### 1.5.1 Definition of the load impedances

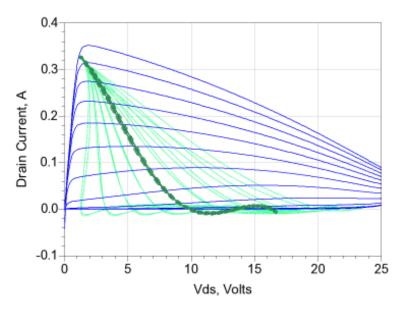

Power amplifier design and analysis requires knowledge of the large signal performance of the transistor and non-linear effects and design strategies have long been based on load-pull techniques. These allow determination of the optimum impedances which need to be applied to the device at the reference planes. These load impedances can be derived by analysis, using CAD simulation and via measured load pull data.

## 1.5.1.1 Analysis – The Cripps Load

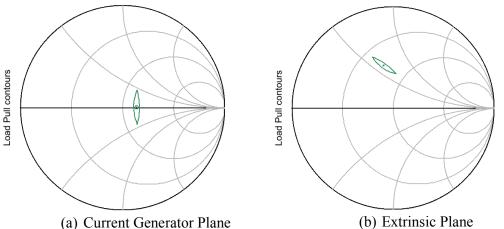

Cripps [14] demonstrated the shape of the load pull contours is defined by the device RF-IV characteristics. This method is a simple but powerful analytical approach and showed that the impedances to be created need to be referred to the correct reference plane, the current generator. These impedances are modified by the parasitic elements (e.g. packages, bond wires etc.). This allowed the initial amplifier designs to start on a theoretical footing to derive some basic parameters and matching networks.

It can also be used to define a region of the smith chart to reduce the need to fully characterise the impedance plane, resulting in a targeted sweep of the values and reduce the measurement space and hence improving the design time.

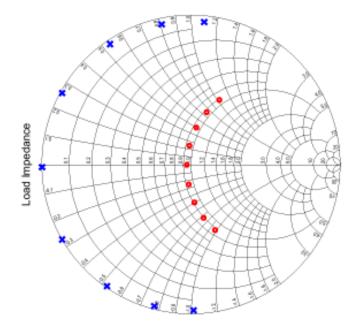

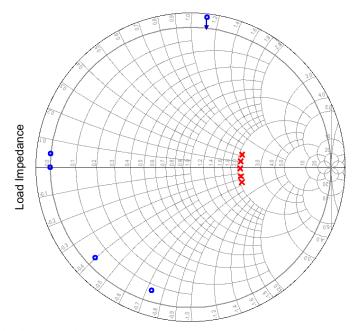

(a) Current Generator Plane

(b) Extrinsic Plane

Figure 1.3 Cripps load analysis for CP FD30 MMIC process 10x75μm pHEMT device (a) Current generator plane (b) Extrinsic Plane (Frequency=9GHz)

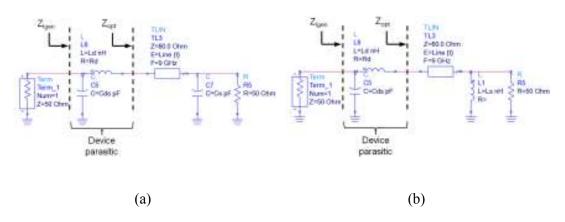

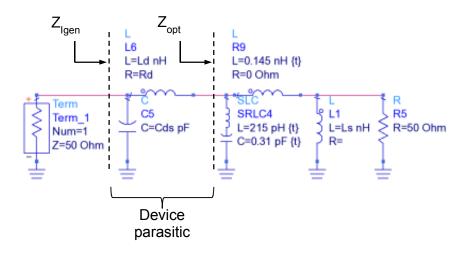

# 1.5.1.2 CAD Simulation methods

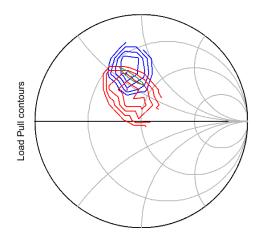

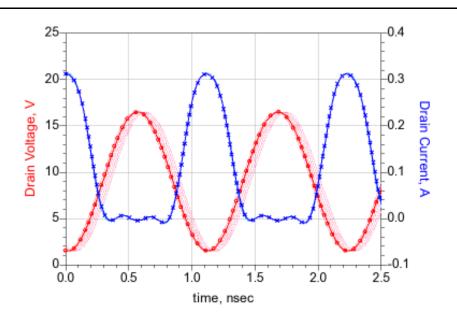

Use of the circuit simulator with non-linear device models can preclude the measurement of the load pull data and can speed up the design process by performing analysis in the CAD tool. A typical response is shown in Figure 1.4 showing close correlation to the Cripps load.

Figure 1.4 Simulated load pull data for CP FD30 MMIC process 10x75µm pHEMT device Power contours (red), PAE contours (blue), Cripps load (green)

This approach requires a non-linear model to be available for the device in question. These are generally compact models (especially through foundry access Process Design Kits) although new behavioural modelling approaches based on measured data are available. This in itself, however, still doesn't give an insight into the waveforms of the amplifier but the simulator allows voltage probes to be included at any node in the circuit for waveform monitoring.

The simulator can also be configured to provide an alternative design strategies which can overcome some of the shortfalls of existing design approaches or to investigate different scenarios.

#### 1.5.1.3 Load Pull measurements

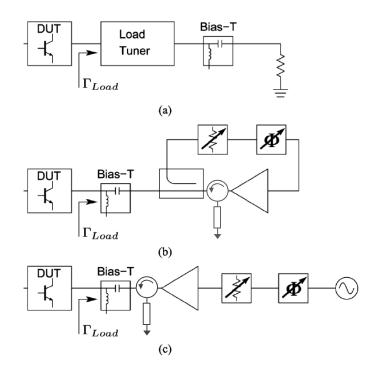

Load Pull is the act of presenting a set of controlled impedances to a device under test (DUT) and measuring a set of parameters at each point. Practical Load Pull measurement systems can be split into passive and active solutions [19] and are shown in block diagram form in Figure 1.5.

Figure 1.5 Load pull system block diagram (a) Passive load pull, (b) Closed loop Active Load pull and (c) open loop active load pull [19]

Passive load pull systems, Figure 1.5(a), use passive networks with tuneable elements (moveable stubs etc.) to alter the impedance presented to the device-under test (DUT) [20][21]. These passive systems have limitations with the impedance space that can be covered due to systems losses, that is impedances on the extremities of the Smith chart are unrealisable.

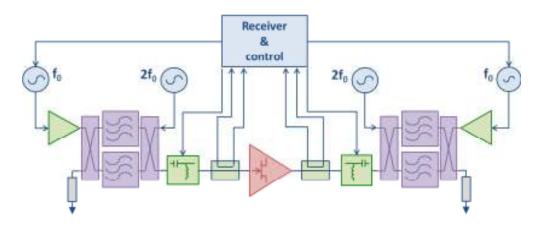

The impedance presented to the DUT is actually the ratio between the reflected and incident waves at the load. By terminating the signal from the DUT and using an injected signal at the output with varying amplitude and phase, an electronically adjustable impedance is created. Active Load Pull systems, Figure 1.5 (b) and (c), therefore measure and terminate the normal amplifier output signal, using an isolator or

circulator and load, then inject a system generated signal to the output of the DUT. This can be performed in open loop or closed loop configurations. The closed loop systems take a portion of the amplifier signal and feed it back to the DUT after varying the amplitude and phase. These systems can become unstable with the feedback network. Open loop systems do not suffer these instabilities as the amplifier signal is sampled and terminated, with an artificial reflection (injection) signal created at the correct amplitude and phase with a signal generator, usually under computer control. Phase shifters and digital attenuators control the injected signal to synthesise the load impedances [23] in both these configurations.

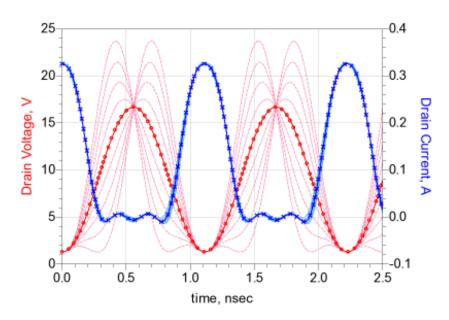

More recently, the active load pull techniques have been configured in time domain systems [24]. These systems allow the direct measurement and analysis of amplifier operating modes with reference to the time domain waveforms. The output data files from these systems can be used for the application for this is the behavioural modelling.

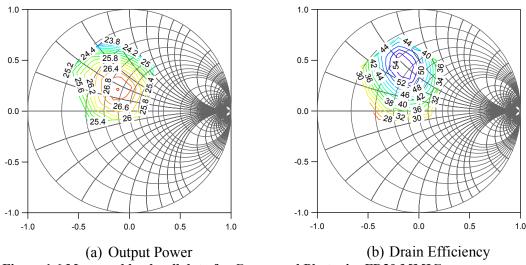

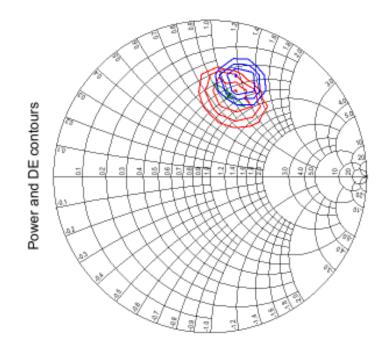

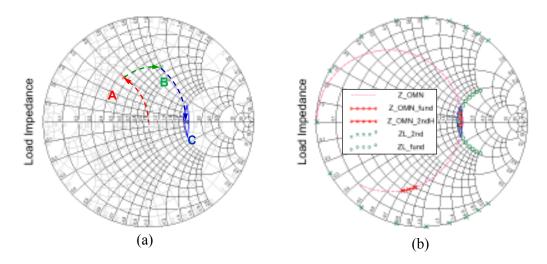

The typical response from these load pull systems is shown in Figure 1.6 mapping output power performance and drain efficiency against load impedance.

Figure 1.6 Measured load pull data for Compound Photonics FD30 MMIC process 10x75µm pHEMT device (a) Output power contours and (b) Drain Efficiency contour (Frequency=9GHz, Vds=+9V, Vgs=-1.1V)

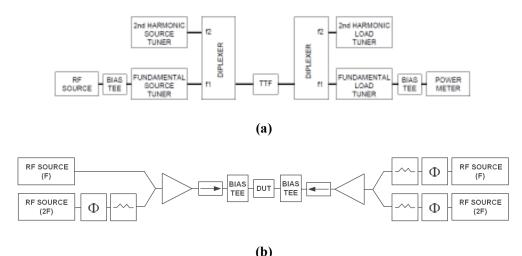

These systems can be configured to control harmonic impedances as well as the traditional fundamental only set-ups (Figure 1.7). In these systems the signals are split to include fundamental and harmonic frequency paths, with impedance control in each

arm. The signal splitting is either via a diplexer, as in the case of the passive tuner based systems (Figure 1.7(a)), or with a power combiner network feeding a driver amplifier (Figure 1.7(b)).

Figure 1.7 Typical Harmonic load pull configurations. (a) Passive system [22] and (b) Active system (after [13]). Control interfaces not shown

#### 1.5.2 Source pull

Source pull is the same as load pull except the input impedance seen by the active device is varied rather than the load impedance. Source impedance strategies are less well defined, with the approaches based solely on measured impedance sweeps [25] as there are no closed form solutions available.

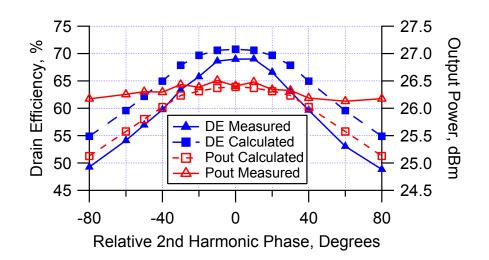

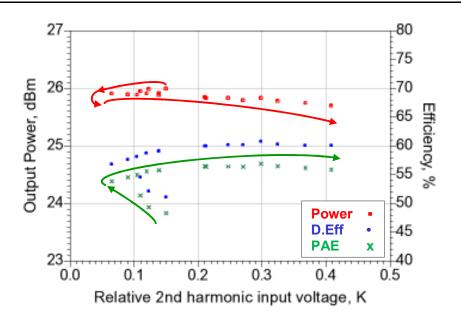

The input harmonic space has been investigated, using the system shown in Figure 1.7(a), providing evidence that there is a significant effect of the second harmonic input terminating impedances on the efficiency of the amplifier [22].

#### 1.5.3 Load Pull Summary

The design of power amplifiers has traditionally started from the impedance space and designing matching networks to deliver a specific set of impedances to the device for a specific operating mode. Cripps explained the shape of the load pull contours and this, coupled with the measurement methods outlined in this section have been used successfully in the design of power amplifiers for many years.

They are also useful to

i. Verify simulation results of a transistor model (model validation) and gather characterization data for model extraction (behavioural model extraction)

- ii. Ensure a microwave circuit's ability to perform after being exposed to high mismatch conditions (ruggedness test)

- iii. Confirm the stability or performance of a microwave circuit or consumer product under non-ideal VSWR conditions.

The more recent time domain based measurement systems have added an extra dimension to the traditional load pull where the exact operating mode can be determined with reference to the actual device terminal voltage and current waveforms.

#### 1.6 Waveform Engineering

The role of the terminal RF-IV time varying waveforms in improving efficiency and optimising PA performance has been known for many years. Tyler [26] demonstrated this approach in valve technology where flattening the voltage waveforms (class F) was found to be beneficial in efficiency improvement whilst providing higher output power than class C operation, which was the reference approach for high power generation at the time. Snider [28] provided a comprehensive mathematical analysis of this Class F operation, with the optimal loading condition of zero or infinite harmonic impedances, alongside a comparison to Class B. This approach to amplifier design and analysis, involving the ability to modify the time varying terminal waveforms has been described as 'Waveform Engineering' [27]. Waveform engineering is the process of using the device, dc bias operating points and circuit terminating impedance characteristics to generate the specified waveforms for a given class of amplifier.

#### 1.6.1 Output Waveforms

The 'high efficiency' modes of operation (Class F etc.) using this analysis technique have dominated and require properly defined fundamental and the harmonic frequency terminating impedances at the transistor output terminal. This has long been the focus and the mathematical analysis of waveforms has been further developed by Raab [29][30] where the harmonic content of the ideal voltage waveforms have been optimised and analysed. This work has also included an analysis of bandwidth limited operation, i.e. truncating the number of harmonics utilised in the waveforms [31][32]. Rhodes [33] has taken the idealised transistor characteristics and derived an elegant expression for the load impedance network element values in order to create the class F amplifier operating mode, demonstrating the results are dependent on the terminating network impedances and not transistor properties.

The development of these modes has expanded with the operating space by the use of the continuous mode theory [18]. Here the Class B and Class J operation are shown to be points on the same continuum of operation providing the same power and efficiency as class B.

In addition to these classical amplifier modes, there has been an expansion of research in this area involving the manipulation of the harmonic content to adjust the waveforms to optimise PA efficiency [13]. Colantonio et al have studied several options

with various numbers of harmonics being controlled. Initial research targeted amplifiers with second harmonic load terminations [33]. This approach adds a correctly aligned second harmonic component of drain voltage. The theoretical analysis of this design space defines a voltage gain function increasing the fundamental content of the waveform. Further work using higher harmonics [34][35] has been reported by the same research team and has been coined as the "Harmonic Manipulation Technique" [34]. These operating modes were demonstrated by appropriate selection of the harmonic content based on load pull sweeps [36]. Theoretical analysis of the technique has expanded a design space and has shown that the efficiency can be improved by optimising the ratio of the harmonic contents rather than rely on analysing the amplifier under the ideal zero and open circuit load impedances [37].

These methods so far have implemented waveform engineering using passive impedances. Harmonic injection at the output, resulting in active rather than passive load impedances have been investigated [42] and shown to improve the efficiency of the amplifier stages. This implementation requires complex circuitry to split the input signal and double to create the output harmonic injection. This is then manipulated in amplitude and phase before injection at the output port via a diplexer arrangement. It does, however, provide an efficiency improvement even when considering the added power of the auxiliary second harmonic generation circuit and amplifier.

| Туре              | F GHz    | DE %  | PAE % | Power dBm | G <sub>p</sub> dB | Ref       |

|-------------------|----------|-------|-------|-----------|-------------------|-----------|

| GaAs amp RF board | 2.0      | -     | 76    | +21       | 13                | [44] 2005 |

| Class F           |          |       |       |           |                   |           |

| GaAs pHEMT        | 9.6      | 50    | -     | +28       | 6                 | [38] 2010 |

| Class F           |          |       |       |           |                   |           |

| GaN board PA      | 1.5 -2.5 | 60-70 | -     | +39       | 18                | [41] 2009 |

| Class J continuum |          |       |       |           |                   |           |

| GaN Board PA      | 0.9      | 74    | -     | +40       | 20                | [37] 2010 |

| Class F, Harm Inj |          |       |       |           |                   |           |

| GaAs transistor   | 0.9      | 75-82 | -     | +20.2     | 20                | [39] 2011 |

| Class F continuum |          |       |       |           |                   |           |

| GaAs hybrid PA    | 5.0      | 73.7  | 60    | +25.6     | 6.5               | [34] 2000 |

| Harmonic tuned    |          |       |       |           |                   |           |

| GaAs MESFET       | 5        | -     | 55    | +25       | 7                 | [37] 2003 |

| Harmonic tuned    |          |       |       |           |                   |           |

| GaN MMIC PA       | 8        | -     | 34    | +36       | 10                | [40] 2003 |

| Class B           |          |       |       |           |                   |           |

Table 1.2 Summary of published single transistor amplifier performance.

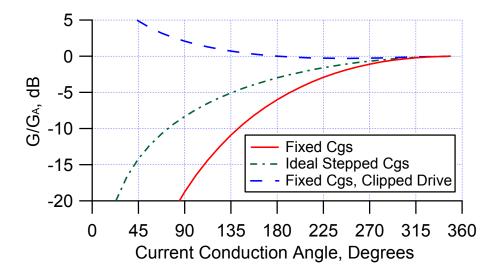

A further point on the review of the output waveform engineering results has shown a reliance on presenting drain efficiency results, ignoring any effects of the input drive levels. This is especially true of the low frequency applications (Table 1.2). The work at higher frequencies with full harmonic manipulation methods has made reference to the gain reduction of these modes and the data has been extended to include the PAE of the amplifier [34][37].

It is clear from this review that waveform engineering has been exploited practically (after initial postulation from a theoretical perspective) and that most of the focus is on the impedance environment for implementation. Furthermore, in the majority of these research themes it should be noted that this has been confined almost exclusively to the load impedances and the input side of the circuit has been largely neglected.

#### 1.6.2 Input Waveforms

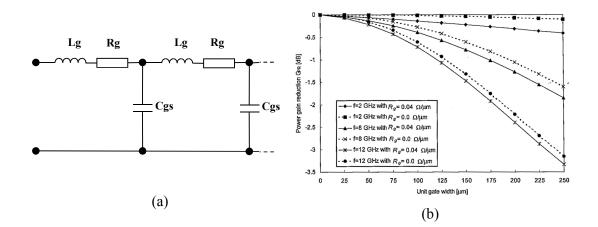

Investigation into the benefits of input harmonic impedance terminations have been reported in high efficiency amplifier operation [43][44][45][46]. These early works show circuit techniques to present passive input (source) impedances to the transistor device under test (DUT). These circuit modifications improve efficiency by reducing the effects of pHEMT Cgs varactor distortion on the output current conduction angle. White [43] uses capacitive and resonant elements to short circuit the input second harmonic currents arising from the varactor effects, which broaden the gate voltage shape, and hence the output current pulse. This leads to reduced efficiency as there is significant current flow during the output voltage swing. White also demonstrated second harmonic distortion of the gate signal of a pHEMT is more problematic than for a MESFET circuit due to the more severe capacitance-voltage characteristic of the Gate-Source capacitance (Cgs). The result was an impressive 49% - 81% improvement in simulated PAE. This work has recently been extended on by Canning et al [47] demonstrating this efficiency improvement practically and linking this to the intrinsic device waveforms for MMIC implementation. Here the resonant circuit places the harmonic short circuit impedance at the device input intrinsic Cgs plane.

Maeda [45][46] used second harmonic source impedances to create a 'quasi square wave' signal at the gate terminal of a FET to minimise the switching time of the transistor waveforms. The waveform is acknowledged to have an 'increased flat portion at the maximum of the waveform leading to improved output power. The realised power module showed an efficiency improvement of 6% at 900MHz when adding in the passive source harmonic termination.

Gao [44] again identifies the critical performance of the input circuit and describes a simulation procedure of defining the optimum fundamental and harmonic source impedances. The work demonstrates the strong relationship between efficiency and the second harmonic input termination at 2GHz. The optimum impedance condition is offset by an amount predicted by the author to be related to the simple circuit theory considering the parasitic elements of the package – a similar effect to the Cripps Load at the output.

The work on harmonic tuned amplifiers by Colantonio [34] developed a design methodology for the output load conditions and also included an assessment of the role of the input waveform on the clipping of the output current shape and the corresponding effect on the output terminating impedances and hence voltage waveforms. In this work the design space was mapped using a gain overshoot function (to demonstrate the level of harmonic voltage level required for improved performance and related these to the second and third relative harmonic levels. It is noted that using the 2nd HT PA design method requires additional design efforts related to the control of the input harmonic terminations to properly generate the output harmonic components with appropriate phase relationships. These source impedance strategies are less well defined, with the approaches based solely on measured impedances [25].

Commercial application of these techniques is also noted. The work by Mitsubishi Electric [48] shows a high efficiency internally matched amplifier approach at 5.8GHz, where the input side second harmonic tuning was noted to have a dominant effect on performance. Although the impedance space was swept using a harmonic load pull system, there was no explanation provided on the strategy or the improvement noted. Subsequently, a C-band 100W GaN HEMT power amplifier was released by Mitsubishi quoting the record PAE of 67% is "enabled by the world's first harmonic tuning circuit placed in front of each GaN HEMT cell on the substrate" [48].

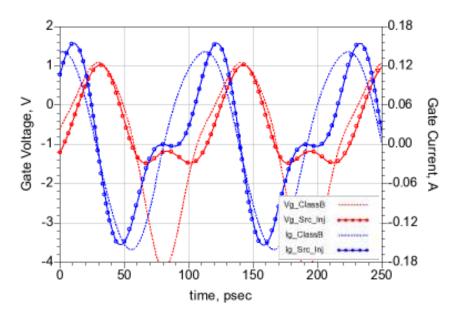

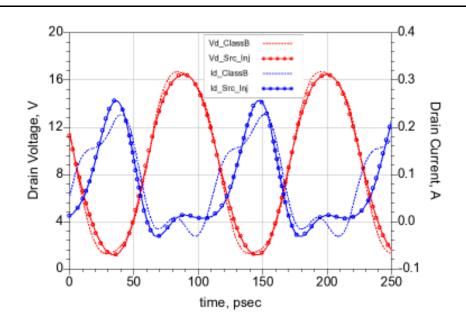

More recent work has expanded the operating space from the passive source impedances and demonstrated the concepts for active injection techniques Ingruber [50] Ramadan [51], Kusonoki [55] and Fan [56]. Here the input waveform can be shaped by adding a second harmonic contribution to the input signal from an external source.

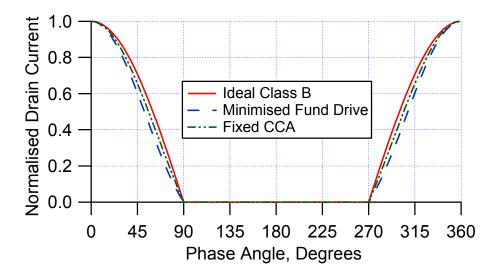

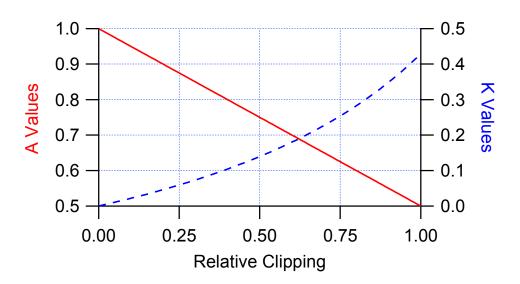

Ingruber [50] describes an amplifier concept using a second harmonic input injection method at 1.6GHz, named by the author as a "harmonic controlled amplifier". This paper acknowledges the low gain of reduced conduction angle operation and presents this as a method of improving the PAE and intermodulation distortion of the amplifier. The power stage injection signal is created from a driver amplifier stage which splits the signal through separate amplitude and phase shaping paths and injected to a class F power stage via a diplexer arrangement. The circuit has a method for tuning the amplitude and phase of the fundamental and second harmonic drive signal. The paper also mentions optimising the gate bias voltage as a consequence of the synthesised signal. There is no explanation of the interstage matching except there is a phase shifting network to create an optimum waveform shape. Similarly, Ramadan [51] has identified an experimental study demonstrating the injection technique on a discrete GaN transistor device in class F and F<sup>-1</sup> at 2GHz, creating a clipped sinewave drive signal using test set-up. This is compared with a passive short circuit load condition. The authors present an efficiency improvement and describe the performance being due to the reduced 'on-time' conduction angle of the drain current. Extension of this work by Ramadan [52]has shown the effect of the reduced conduction angle from a second harmonic injection signal has on the output current pulse leading to improve amplifier efficiency, with the Fourier analysis driving the optimum gate voltage. It was noted that this work does highlight the need for any driver stage to be able to create these harmonic components. This approach was developed further [53] in a two stage amplifier designed using the gate voltage waveform shaping at 1.8-2.2GHz. The design basis was to shape the gate waveform to reduce the 'on' time of the current pulse at the drain. No procedure is provided for the interstage matching network and it is clearly evident there is significant tuning of the hybrid circuit to achieve the waveform performance.

Source injection has also been used to improve amplifier linearity. Fan [56] analysed the intermodulation distortion components from a FET device using Volterra

series description of the non-linearities and demonstrated these can be cancelled by controlling the injection signal at the baseband and second harmonic frequencies. Kusonoki et al [55] expanded this work and demonstrated the approach and the additional load impedance dependence of the circuit to optimise the linearization technique. Both these works show a practical circuit implementation of an amplifier stage and a linked second harmonic generator circuit fed in via a diplexer arrangement.

#### 1.7 Research Objective & Thesis Structure

High Power Amplifier theory uses a simplified approach to derive the waveforms and hence performance characteristics of amplifier classes and operating modes. However, the design of power amplifiers has traditionally started from the impedance space and designing matching networks to deliver a specific set of impedances to a device.

This thesis seeks to address the design and development of high efficiency high frequency MMIC PAs using circuit techniques using RF-IV waveform information directly in the design process. Therefore, the first objective is to investigate high efficiency amplifier operating modes looking from a waveform engineering perspective and to understand the drivers affecting efficiency. The second objective is an investigation into methods to overcome these limiting mechanisms, leading to a design strategy suitable for MMIC implementation of high frequency PAs, with the focus of the work concentrated on transistor input driving networks and waveforms.

This thesis first presents the basic amplifier theory and operating modes. It develops this theory further by presenting an analysis on how the input circuit affects amplifier performance. This theory is practically demonstrated using large signal measurements on simple transistor cells leading to a novel concept for harmonic 'source injection'. The theoretical analysis of the source injection mode is presented, followed by validation measurements. The source injection mode is then applied to the design of a 2 stage PA demonstrator implemented in a GaN MMIC process.

Chapter 2 starts with a review on classic Amplifier operating modes looking in detail at PA behaviour from a device terminal current and voltage waveform perspective, along with the factors affecting efficiency.

Chapter 3 outlines the de-embedding processes required in future chapters to find the intrinsic waveforms either from measurements or for use in the circuit simulator to drive the design process. It details the extraction of the device element models and derives the parasitic elements required to effectively de-embed the waveforms.

Chapter 4 reviews the standard microwave amplifier simulation methods and presents a new waveform based approach which define the transistor terminal waveforms directly, where the impedances are then derived for amplifier implementation.

Chapter 5 analyses the role of the input circuit on amplifier performance and the second harmonic source injection mode is proposed. The theoretical operation is presented and backed up with validation measurements.

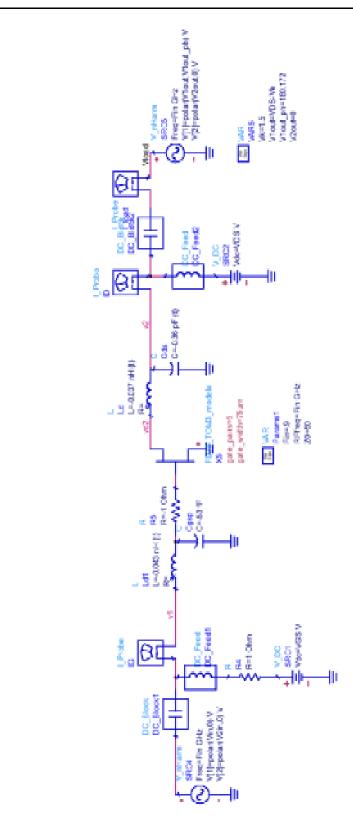

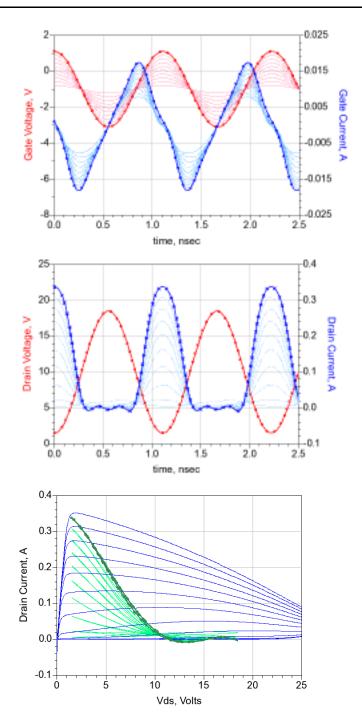

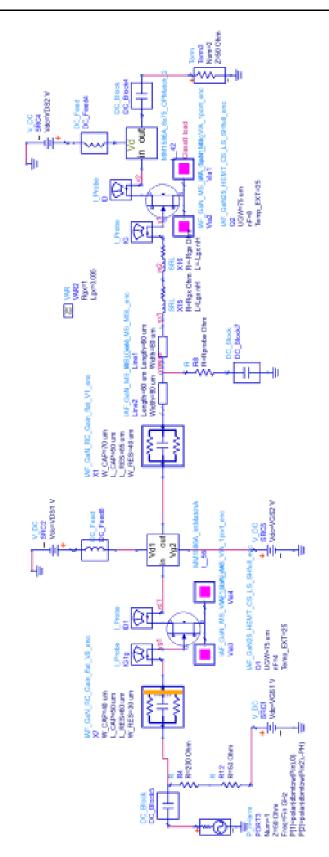

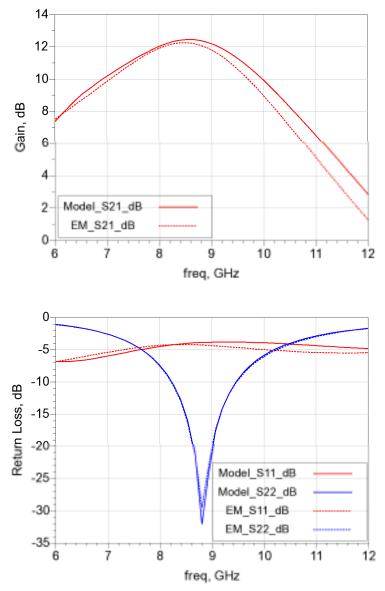

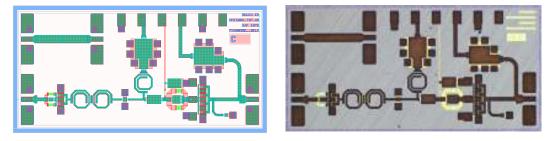

Chapter 6 describes the design and evaluation of a two stage GaN MMIC PA demonstrator using the second harmonic source injection technique. The design of the interstage network to generate the required driving voltage waveform is presented.

Finally, Chapter 7 draws conclusions and summarises the thesis. In addition, future work and suggested extensions to this research are also presented.

# 2 AMPLIFIER OPERATING MODES

#### 2.1 Amplifier operating modes

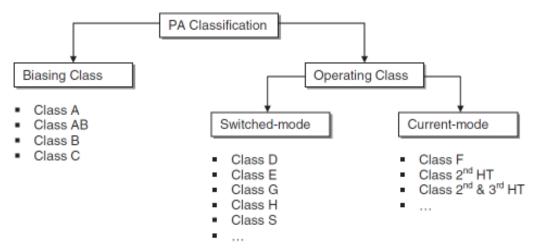

Amplifier modes are generally categorised by the bias voltage operating point, where the device is assumed to behave as a current source with a sinusoidal input drive e.g. classes A, AB, B and C. This bias point affects the output current conduction angle and differentiates the circuit operation. Further classification is possible by the device operating conditions indicating there are specific matching network conditions for operation e.g. class J and Class F [13] but use a Class B or AB bias point.

Figure 2.1 Typical PA classification as described by Colantonio et al. [13]

These operating modes can also be further expanded with the continuous mode theory, defining the class BJ continuum (covered later) and the continuous class F mode.

Inverse class amplifiers (e.g. class  $F^{-1}$ ) are also possible where the voltage and current waveform are swapped.

More specifically the operating modes are described by the RF-IV waveform shapes at the output terminal, which is in part due to the bias point and part operating impedance environment.

# 2.1.1 Class A Amplifier

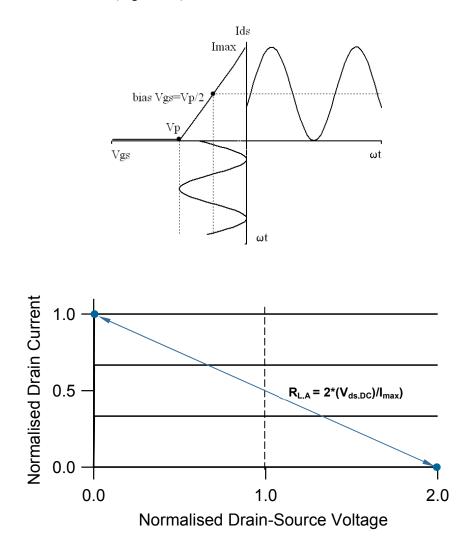

This is the simplest class of amplifier and is characterised by biasing a transistor at a quiescent bias point midway between the maximum current and pinch-off. The RF input signal is injected about this bias point. The resulting output current swings up to  $I_{max}$  and down to zero (Figure 2.2).

Figure 2.2 Class A operation (a) bias point and waveforms and (b) optimum load line

The ideal load for this configuration has been defined by Cripps [14] and is simply the ratio of the output voltage swing defined by the voltage supply,  $V_{ds,DC}$ , and the maximum device current,  $I_{max}$  (Figure 2.2)

$$R_{L,A,ideal} = \frac{2V_{ds,DC}}{I_{\max}}$$

2.1

Drain Efficiency,  $\eta_{D_i}$  is simply the ratio of fundamental RF output power to total DC power.

$$P_{out,RF} = \frac{I_{\max}}{2\sqrt{2}} \frac{V_{ds,DC}}{\sqrt{2}} = \frac{I_{\max}V_{ds,DC}}{4}$$

2.2

$$P_{DC,A} = \frac{I_{\max} \cdot V_{ds,DC}}{2}$$

2.3

$$\eta_{D,A,ideal} = \frac{P_{out,RF}}{P_{DC,A}} = \frac{1}{2}$$

2.4

The maximum drain efficiency for this class of amplifier is 50% at full drive. This is the drawback of Class A configuration as the dc power is independent of drive level and efficiency during back-off is poor.

Another important parameter, often neglected in the literature dealing with amplifier operating modes, is the power gain,  $G_P$ . The power gain is defined here as the "available power gain" [15] of the device. The output power is the optimum power available from the transistor, before the amplifier exhibits any compression or non-linear characteristic - which is the basic assumption for linear power amplifier theory. The input power is assumed to be the power available from the source.

The power gain,  $G_P$ , for the Class A amplifier is simply the ratio of the output power to the input power, where the input power is assumed to be proportional to the input voltage amplitude,  $V_{in}^2$ [15][16].

$$V_{in} \propto \left(\frac{\frac{1}{2}(V_{gs,max} - V_P)}{\sqrt{2}}\right)^2$$

2.5

$$G_{P,A} = \frac{I_{\max}(1-\beta)V_{ds,DC}}{4} \cdot \frac{1}{\left(\frac{\frac{1}{2}(V_{gs,\max}-V_P)}{\sqrt{2}}\right)^2} = \frac{2I_{\max}(1-\beta)V_{ds,DC}}{(V_{gs,\max}-V_P)^2}$$

2.6

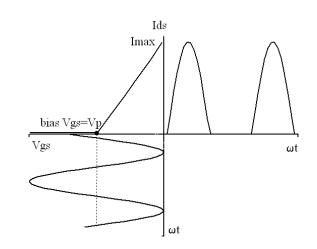

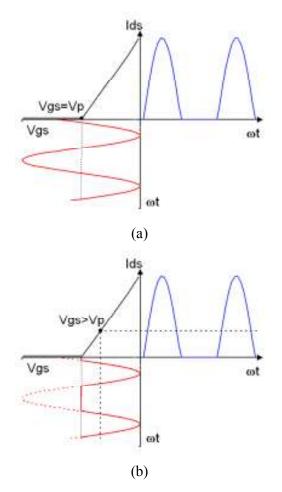

### 2.1.2 Class B Amplifier

It is well understood that correct high efficiency power amplifiers design strategy involves the engineering of the output RF current and voltage waveforms. The reference design, Class A, was shown to have sinusoidal current and voltage waveforms (section 2.1.1) providing a theoretical maximum drain efficiency of 50%. To improve efficiency either one or both of these waveforms must be modified by the introduction of harmonics terminated in non-dissipating loads.

The Class B case requires the transistor biased and driven in a manner that provides a half-rectified current waveform. The classical approach to realizing Class B amplifier (sometimes called tuned load) operation [13][17] is achieved by biasing transistors at pinch-off, such that there is no quiescent current flow at the active device output in the absence of any input signal. The input RF signal is then superimposed on this dc bias level causing the active device to conduct during the positive excursions of the input signal, and forcing the device further into pinch–off during the negative cycle of the sinusoidal input signal. The resulting output current waveform is a half wave rectified sinewave (Figure 2.3). Fourier analysis of the current waveform (2.7) provides the detail on the relative amplitudes of the harmonic components.

$$I_{ds}(\omega t) = \frac{I_{\max}}{\pi} + \frac{I_{\max}}{2}\cos(\omega t) + \frac{2I_{\max}}{3\pi}\cos(2\omega t) + \dots$$

2.7

The fundamental component of this current waveform is  $I_{max}/2$ , the same as for the Class A case, and, when terminating all the even harmonic components of this half-rectified output current waveform into short circuits, the output voltage waveform is sinusoidal, as for the Class A case, resulting in the same optimum load impedance and output power as given in (2.1) – (2.3).

Figure 2.3 Class B operating point and waveforms

The dc component of the current waveform under Class B operation is  $I_{max}/\pi$ , hence the dc power is given by:

$$P_{DC,B,ideal} = \frac{I_{\max}.Vds}{\pi}$$

2.8

This dc power is lower than under the Class A bias and thus this mode of operation has the benefit of improved drain efficiency, by a factor  $\pi/2$  (2.9), over the Class A case with no degradation in output power.

$$\eta_{D,B,ideal} = \frac{P_{out,RF}}{P_{DC,B}} = \frac{I_{\max} V ds}{I_{\max} V ds} = \frac{\pi}{4} = \frac{\pi}{2} \eta_{D,A,ideal}$$

2.9

Such a waveform has a fundamental current waveform component, and hence output power, identical to Class A but with a drain efficiency increased 78.5%.

This class of amplifier is part of the reduced conduction angle operating region. In between the Class A and Class B end points amplifiers are in Class AB.

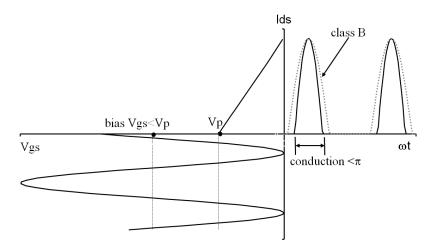

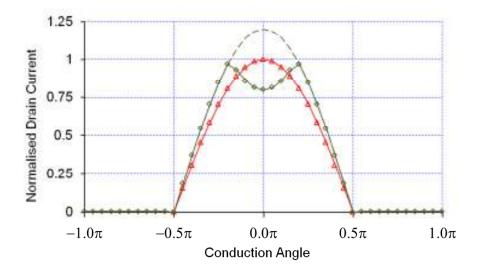

### 2.1.3 Class C amplifier

The class C amplifier follows from an extension of the class A and B cases with the gate bias point reduced further to below the pinch-off voltage. This results in a smaller conduction angle as the gate voltage is above pinch-off for a reduced part of the drive cycle, Figure 2.4

Figure 2.4 Class C operating point and waveforms

Here the current pulse is seen to be smaller than for the class B operating mode, with a conduction angle,  $\alpha$ , less than  $\pi$  radians.

The expressions for the fundamental component of the drain current pulse and the dc component can be found from Fourier analysis of this drain current waveform [13][17] and are given by (2.10) and (2.11)

$$I_{1} = \frac{I_{\max}}{2\pi} \left[ \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \right]$$

2.10

$$I_{dc} = \frac{I_{\max}}{2\pi} \left[ \frac{2\sin(\alpha/2) - \alpha\cos(\alpha/2)}{1 - \cos(\alpha/2)} \right]$$

2.11

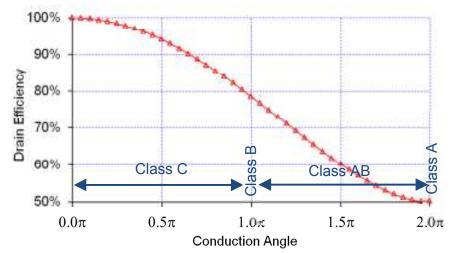

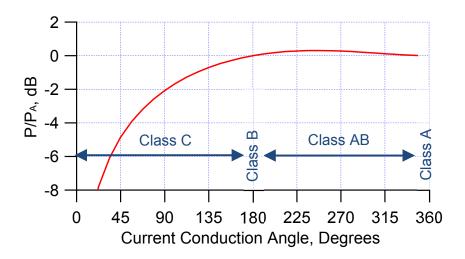

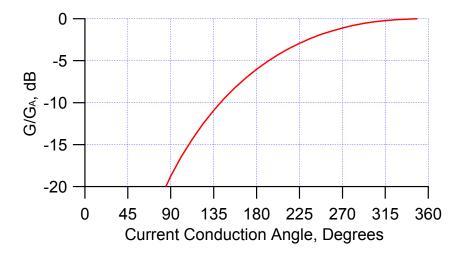

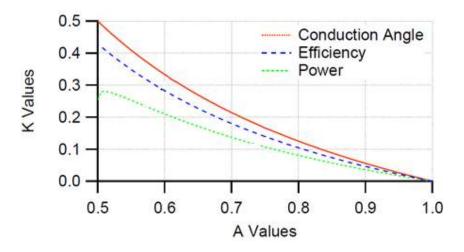

The efficiency is improved under this operating mode as shown in Figure 2.5, but a consequence of the reduced conduction angle operation is the lower output power achievable, which is discussed in section 2.1.7.

Figure 2.5 Efficiency versus conduction angle for reduced conduction angle operation.

# 2.1.4 Class J Amplifier and the BJ continuum

Relaxation of the output load harmonic impedances from the Class B short circuit case to include a 2<sup>nd</sup> harmonic reactive component (generally the device Cds) and a corresponding opposite reactive element to the fundamental load impedance is shown to deliver the same efficiency and power as the Class B operation. This mode of operation has been named Class J [17].

Recent work has expanded this theory leading to the Class BJ continuum [18] showing that the Class B and Class J modes are just the end points in a generalised theory relating the fundamental and second harmonic components at the output.

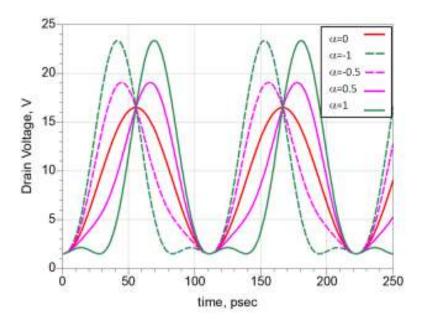

The waveforms can be simply described by the sum of two harmonics with a phase angle between them and results in the expression

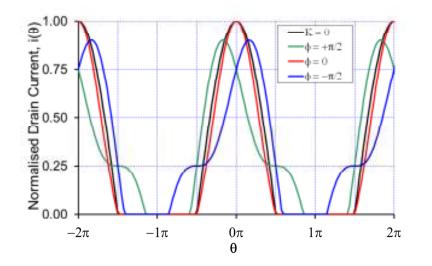

$V_{BJ}(\theta) = (1 - \beta \cos \theta)(1 - \alpha \sin \theta)$  2.12

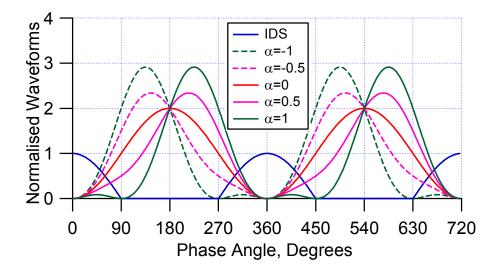

These waveforms are plotted in Figure 2.6 for varying  $\alpha$  from  $\alpha =-1$  (Class J<sup>-1</sup>) through  $\alpha =0$  (Class B) to  $\alpha =+1$  (Class J)

Figure 2.6 Class BJ ideal waveforms from (2.12) for varying  $\alpha$  ( $\beta$ =1 in all cases) [18]

All these voltage waveforms, combined with the half sinusoidal current waveform, have the same power and efficiency as the classic Class B sinusoidal derivation. These operating points require different impedances at the fundamental (by including a reactive term) and the addition of a non-zero 2<sup>nd</sup> harmonic impedance.

The impedances are now defined as the ratio V/I for each of the harmonic components from (2.7) and (2.12) resulting in

$$Z_{Lf0,BJ} = R_L + j\frac{\alpha}{\beta}R_L$$

2.13

$$Z_{L2f0,BJ} = 0 - j\alpha \frac{3\pi}{8} R_L$$

2.14

The fundamental real impedance component,  $R_L$ , is identical to the Class A and B case. The reactive terms are clearly identified in (2.13) and (2.14) and how they are related to  $R_L$  with the Class J parameters  $\alpha$  and  $\beta$ .

### 2.1.5 Class F Amplifier

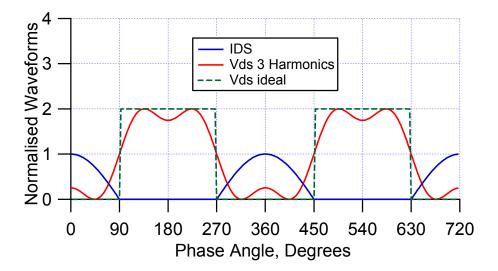

Reduced conduction angle operation has been shown to improve efficiencies by effectively reducing the time when the current and voltage waveforms overlap (hence minimising dissipation). Further efficiency improvements can be made by selecting the output drain voltage waveform to be a square wave whilst maintaining the half wave current waveform, see Figure 2.7. This mode of operation (Class F) was originally demonstrated by Tyler for valve devices [26] and expanded upon by Snider [28].

In this mode a 100% theoretical efficient amplification can be achieved – but this assumes control of infinite harmonics. Generally the design procedure is considered by controlling the first three harmonics only. Raab has presented several papers reviewing the control of the harmonics for optimum waveforms [29][30][31][32] using a numerical approach.

Figure 2.7 Class F ideal waveforms showing optimum square wave voltage and the 3rd harmonic approximation.

This class of operation uses the same basic bias point as Class B, although optimisation during the design procedure moves this point subtly by minimising the even harmonic current content.

The optimum fundamental impedance for the class F is defined by the peak fundamental voltage, which will be larger than the equivalent class B operating point. The value is  $R^*(4/\pi)$  for an ideal square wave. Practical values range from  $1.125^*R_{L,A}$

the maximally flat condition to  $1.273 * R_{L,A}$  by optimising the voltage waveform shape and the number of harmonics to be controlled.

The harmonic terminating impedances are  $Z_L=0$  for even harmonics and  $Z_L=\infty$  for odd harmonics.

Recent research developments on the continuous mode theory [39] have expanded this operating space to allow the use of a larger area of the impedance plane, to remove the need for the open and short circuit harmonic impedances.

# 2.1.6 Inverse Class F Amplifier

The inverse class F (Class  $F^{-1}$ ) mode of operation just requires interchanged output waveforms with respect to Class F, i.e. a squared current waveform, containing only odd harmonic components, and a half sinusoidal voltage waveform, having only the fundamental and even harmonic components [13][38], leading to the basic requirement for a short circuit impedance at the odd harmonics and an open circuit at the even harmonics. This mode of operation will maintain the same efficiency as the class F mode.

The drain current waveform shape needs some consideration. In order to achieve the square current waveform, the amplifier needs to be overdriven, such that it causes the saturation condition.

Figure 2.8 Class F<sup>-1</sup> current waveform from an overdriven transistor.

This overdrive signal causes bifurcation of the drain current pulse at the peak amplitude [38] and, coupled with the pinch-off performance flattening the bottom of the current pulse, a quasi-square current waveform shape is created (Figure 2.8).

# 2.1.7 Power Utilisation Factor

One of the main, and not widely publicised, effects of reduced conduction angle operation is the varying RF output power. Moving towards Class C operation does indeed improve the efficiency but the output power drops. This is a delicate balance between the requirements for power and the gain of efficiency. A figure of merit, the 'Power Utilisation Factor' (PUF), has been defined [17] to quantify this effect which shows the output power relative to the Class A case. This is shown in Figure 2.9.

Figure 2.9 Power Utilisation Factor (PUF) for reduced conduction angle operation

The power output is the same for the Class A and Class B bias points and shows the classical increase in power in the Class AB range. The power drops significantly as the Class C operating region is entered.

# 2.2 Factors affecting Efficiency

The ideal waveforms and operating points discussed in section 2.1 explain basic amplifier operation and provide a basis for comparing the waveform requirements and the resulting efficiency gains, however, real transistor performance deviates from the simple linear theory of sections 2.1.1-2.1.6, and these affect efficiency. This section discusses these factors and identifies methods to reduce or alleviate the effects of these non-idealities.

# 2.2.1 Knee Voltage

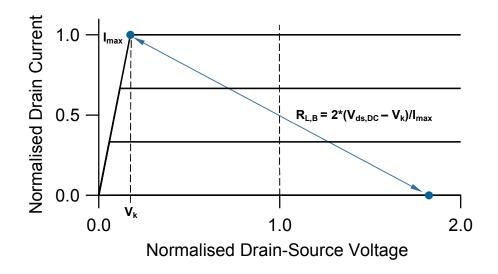

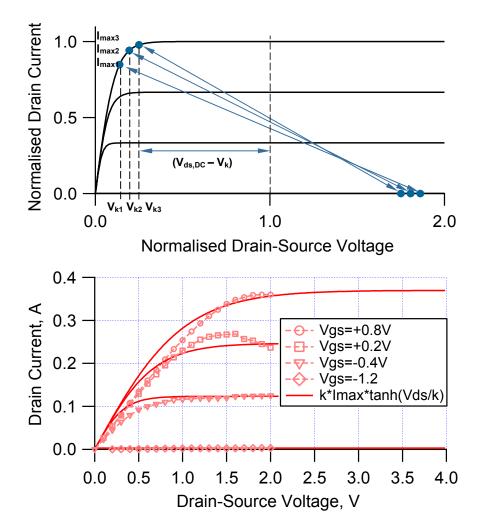

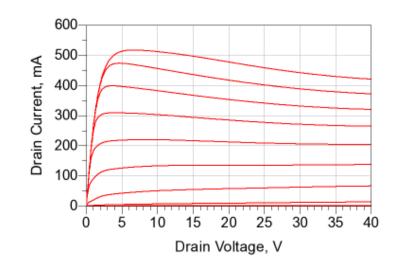

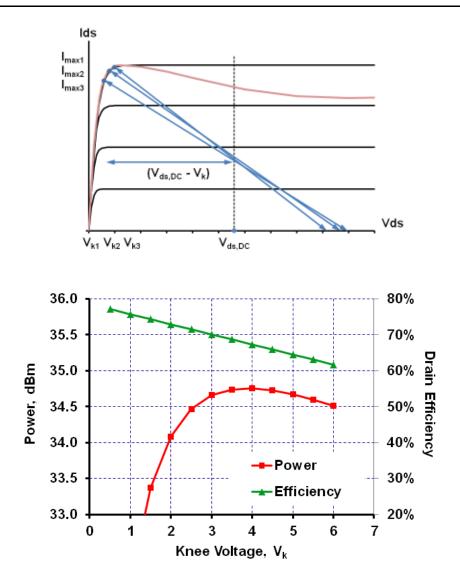

The most notable difference is the inclusion of the knee Voltage,  $V_k$ , which modifies the Ids–Vds transfer characteristics (shown in Figure 2.10) to account for the limit on minimum drain voltages in real devices.

Figure 2.10 Class A operation optimum load line with knee voltage

Rewriting expression (2.1) for Class A load resistance with the knee voltage component gives (2.15).

$$R_{L,A} = \frac{2(V_{ds,DC} - V_k)}{I_{\max}} = \frac{2(1 - \beta)V_{ds,DC}}{I_{\max}}$$

2.15

Where  $\beta = V_k/V_{ds,DC}$ , the ratio of knee voltage to DC supply voltage.

The RF fundamental voltage swing is correspondingly reduced by the knee voltage, so the fundamental output power is given by

$$P_{out,RF} = \frac{I_{\max}}{2\sqrt{2}} \frac{(1-\beta)V_{ds,DC}}{\sqrt{2}} = \frac{I_{\max}(1-\beta)V_{ds,DC}}{4}$$

2.16

The expressions for gain and Drain Efficiency,  $\eta_D$ , can be expanded to include this reduced fundamental RF output power. As the input power is unchanged, the knee voltage reduces gain and efficiency by the factor (1- $\beta$ ) as shown by (2.17) and (2.18).

$$G_{P,A} = \frac{I_{\max}(1-\beta)V_{ds,DC}}{4} \cdot \frac{1}{\left(\frac{\frac{1}{2}(V_{gs,\max}-V_P)}{\sqrt{2}}\right)^2} = \frac{2I_{\max}(1-\beta)V_{ds,DC}}{(V_{gs,\max}-V_P)^2}$$

2.17

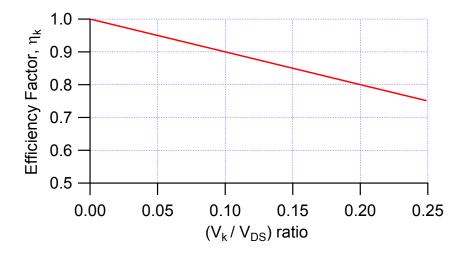

$$\eta_{D,A} = \frac{P_{out,RF}}{P_{DC,A}} = \frac{1}{2} (1 - \beta) = \eta_{D,A,ideal} \eta_k$$

2.18

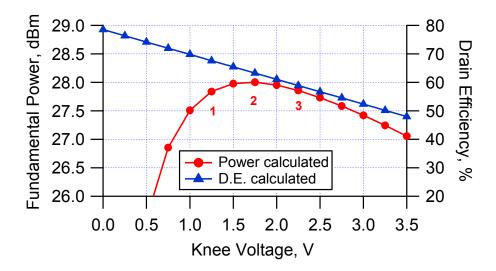

This factor is especially detrimental when low supply voltages are used, as the  $\beta$  term increases towards unity. The response is shown in Figure 2.11.

Figure 2.11 Knee voltage efficiency factor versus Knee to supply voltage ratio.

For the Class B case, the efficiency can also be modified to take account of the knee effect and this suffers the same degradation.

$$\eta_{D,B} = \frac{P_{out,RF}}{P_{DC,B}} = \frac{\pi}{4} (1 - \beta) = \frac{\pi}{2} \eta_{D,A}$$

2.19

Gallium Nitride (GaN) has a lower carrier mobility,  $\mu_n$ , than Gallium Arsenide (GaAs). This translates to the 'knee' voltage,  $V_k$  of the DC-IV curves in GaN transistors being higher than that of GaAs HEMTs, by the order of about 5 times. The critical factor in device operation however is ratio of Vmax to Vk allowing higher operating voltages which can compensate for the higher knee.

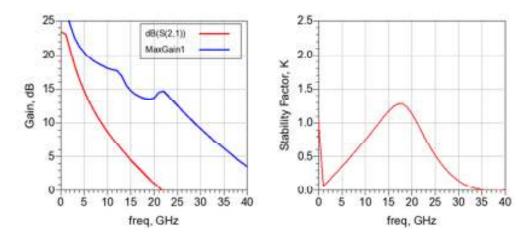

### 2.2.2 Device Gain

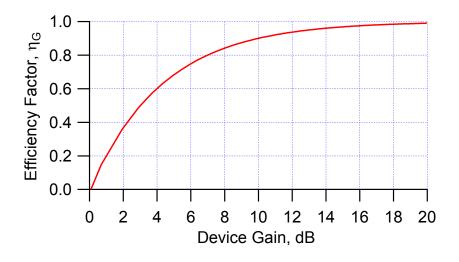

The discussion and analysis of the amplifier operating modes so far has involved the drain efficiency,  $\eta_D$ , as a measure of performance. An alternative and more relevant definition for efficiency, which also takes account of the device gain, is power added efficiency (PAE). This is the ratio of the total RF output power, less the RF input power, and divided by the total dc input power [7].

$$PAE = \frac{P_{out,RF} - P_{in,RF}}{P_{DC}} = \frac{P_{out,RF}}{P_{DC}} (1 - \frac{1}{G_P}) = \eta_D (1 - \frac{1}{G_P}) = \eta_D \eta_G$$

2.20

Here, the efficiency gain dependency can be clearly seen. For high power gain  $(G_P \gg 10)$ , the  $(1-1/G_P)$  factor,  $\eta_G$ , has little effect and the PAE is almost equal to the drain efficiency. However, when this power gain value drops to 10dB and below the PAE is affected significantly. For example a 10dB power gain results in a 90% factor of  $\eta_D$  (Figure 2.12).

Figure 2.12  $\eta_G$  (=PAE/Drain efficiency) factor versus device power gain

This factor is a considerable problem at high frequencies, where device gain is lower, and for power amplifier design, where the power gain is further reduced due to the effect of compression, which is more pronounced in the GaN technology.

## 2.2.3 Matching network loss

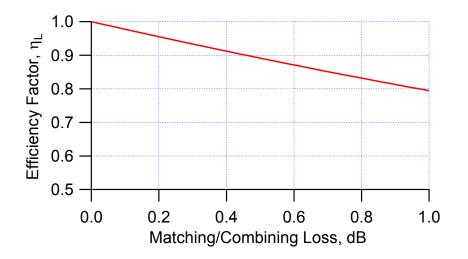

The design of any amplifier requires the termination of the fundamental and harmonic components into defined impedances using some form of circuit network. Practical realisation of these matching networks will add some losses, from the resistivity of the conductor metal layers and the dissipation factor (tan  $\delta$ ) of the substrate and capacitor dielectric layers. These losses are often forgotten (or neglected) during the initial design process, where the implementation is described using ideal circuit elements, but their impact on circuit design needs to be considered.

Losses in the output network are more detrimental to efficiency than if they were to appear at the input in PA design. Minimizing of these losses at the output of PAs is therefore key to maintaining high efficiency.

The effect of the losses on the drain efficiency versus output matching network loss is shown in Figure 2.13. As an example, a 0.2dB loss translates to a 96% efficiency factor.

Figure 2.13 Efficiency factor versus output combining losses

# 2.2.4 Overall impact of efficiency factors

The overall effect of these factors is multiplicative such that the overall realisable efficiency is dramatically reduced from the ideal value. In order to illustrate this some typical values are chosen, for a GaAs process:

Knee voltage 1V for a 9V operation  $\Rightarrow \eta_k = 0.89$

Gain = 10dB  $\Rightarrow \eta_G=0.9$

Output Matching circuit loss =  $0.2dB \Rightarrow \eta_L = 0.96$

$PAE = \eta_{ideal.} \eta_{k.} \eta_{G.} \eta_{L}$

Considering Class B operation with a theoretical efficiency of 78.5%, the actual achievable PAE is (78.5%).(0.89).(0.9).(0.96) = 60.4% which is a significant reduction from the starting point. This illustrates the need to manage these factors in any design approach.

#### 2.3 Multistage amplifiers

The factors described so far are mainly related to individual transistor amplifier stages. Generally high frequency amplifiers involve multiple stages, with the most common approach confined to two stages. Under these conditions the PAE must also account for the dc consumption of the driver stage(s).

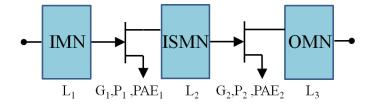

Figure 2.14 Two stage amplifier block diagram showing efficiency contributions.

The amplifier total PAE can be derived from the individual stage performance [58] as shown in (2.21)

$$PAE_{total} = \frac{PAE_1 \cdot PAE_2 (L_1 L_2 L_3 G_1 G_2 - 1)}{PAE_1 L_1 L_2 G_1 (G_2 - 1) + PAE_2 L_1 (G_1 - 1)}$$

2.21

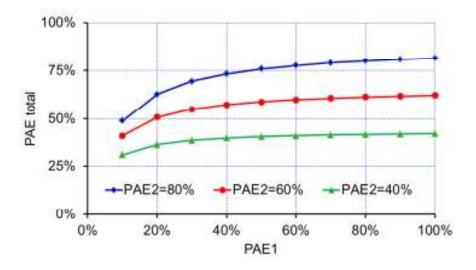

The response is plotted in Figure 2.15 for the simple case of lossless matching networks (L1,L2,L3=1), fixed and equal amplifier stage gain (G1=G2=10dB) and variable PAE1 and PAE2.

Figure 2.15 Effect of driver amplifier efficiency on overall amplifier PAE for G1=G2=10dB.

# 2.4 Conclusion

This chapter has described the operating modes of typical amplifiers and outlined the factors which need to be considered to maintain high efficiency, with a particular focus on high frequency operation. High efficiency modes are shown and the demands of the matching network impedances are identified, and it is clear that these modes are defined in terms of the output waveforms only.

The influence of gain on efficiency is obviously evident from the PAE reduction due the device gain and also any losses after the device. This is compounded in the two stage amplifier design, where the overall PAE is a function of both stage efficiencies and gains.

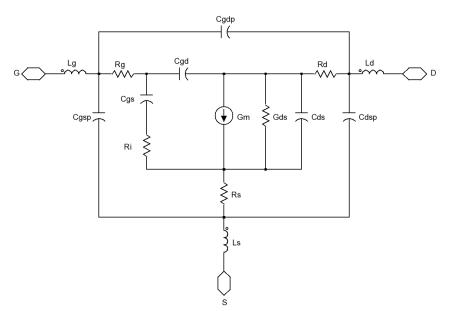

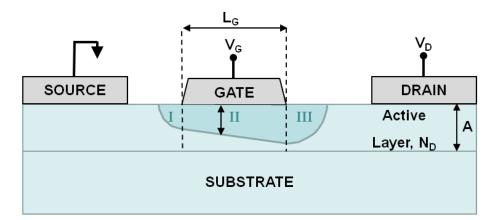

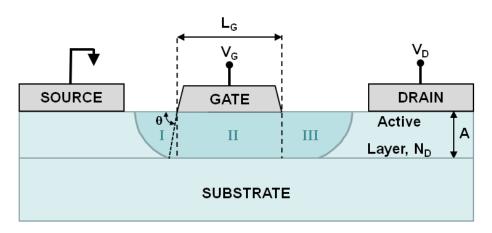

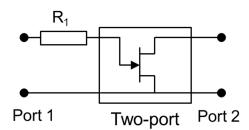

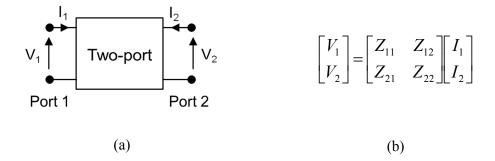

### **3** WAVEFORM DE-EMBEDDING

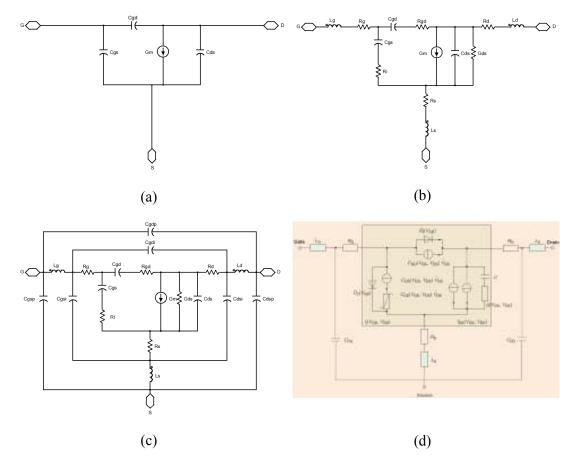

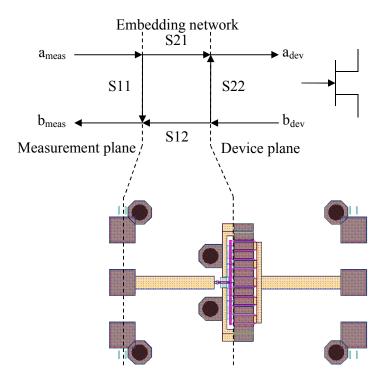

The design and analysis of PAs requires knowledge of the RF-IV waveforms as described in chapter 2. These waveforms are all referenced to the 'intrinsic' transistor device planes. That is, the device current generator plane at the output and the gate controlling node at the input (in the case of FET technology). A simple model to describe this situation is shown in Figure 3.1(a) where the main intrinsic device elements are identified. This model has limited usefulness in this form, for example low frequency operation and/or very small unpackaged devices. A better model is required to capture the full performance of the transistor.

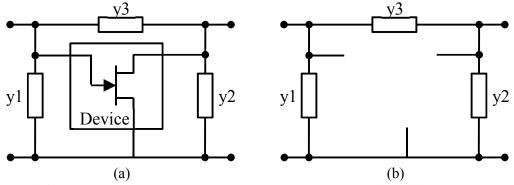

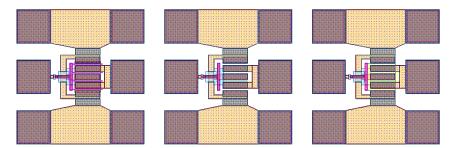

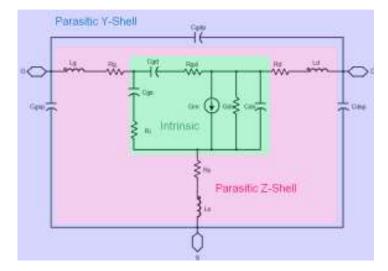

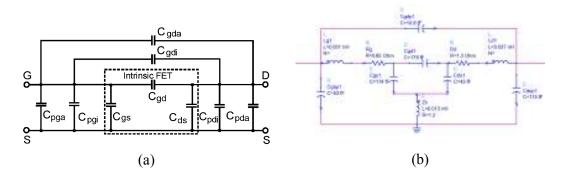

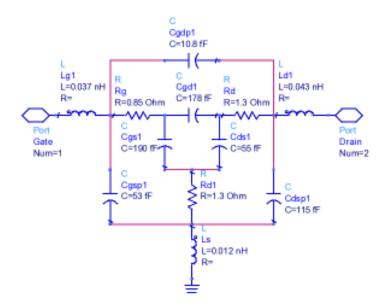

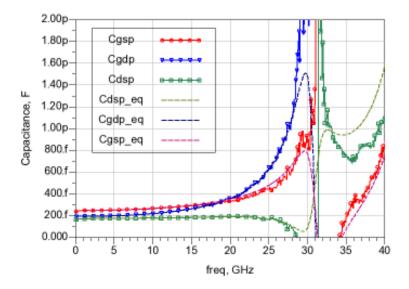

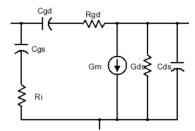

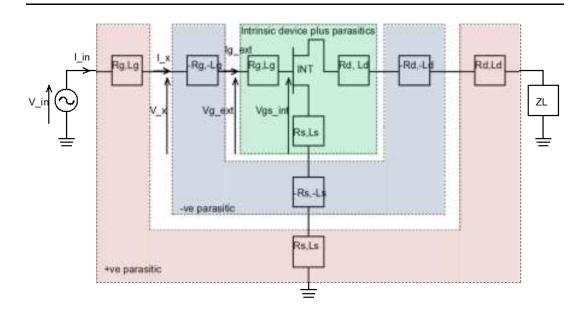

Figure 3.1 equivalent circuit models for FET technology (a) simple low frequency model, (b) basic Small signal model, (c) Improved small signal model to account for distributed effects and (d) non-linear model [59] version of model (c).

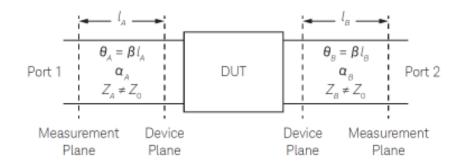

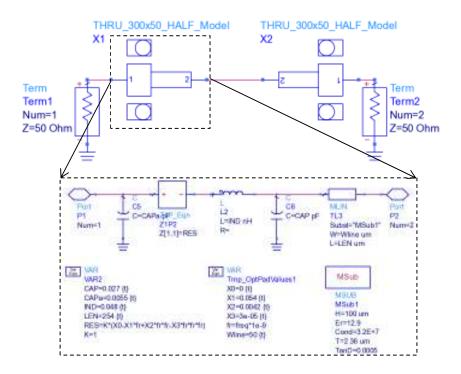

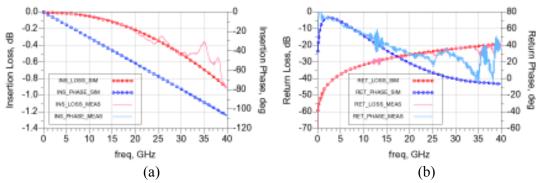

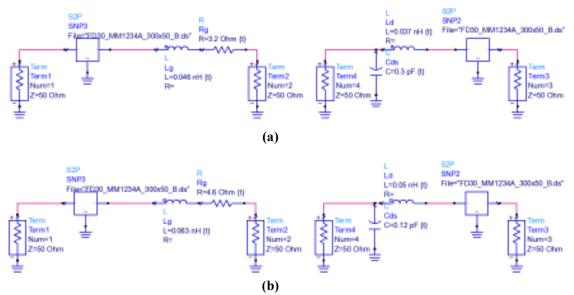

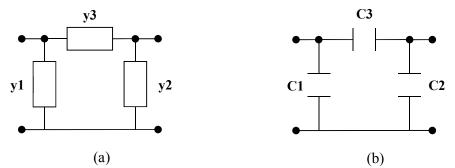

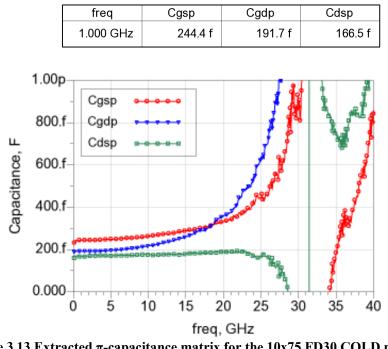

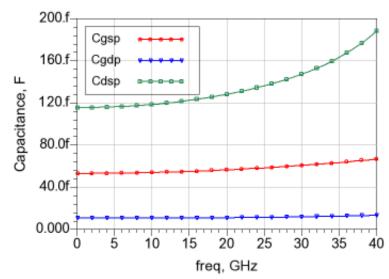

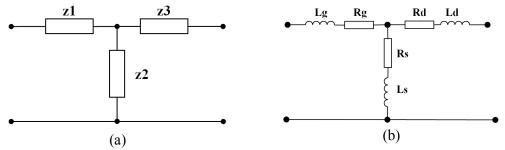

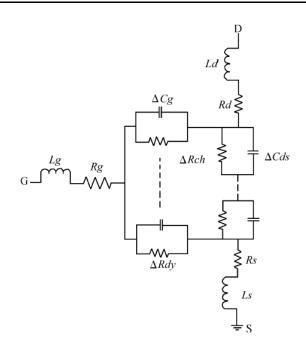

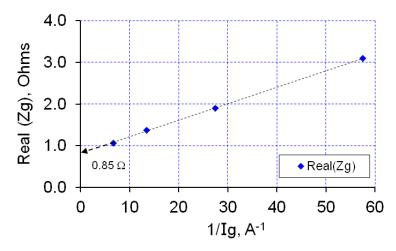

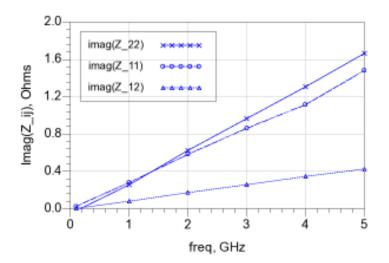

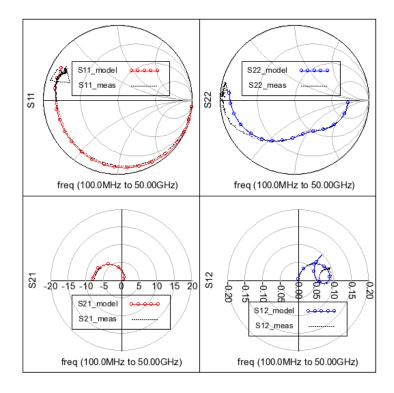

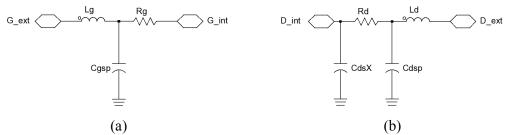

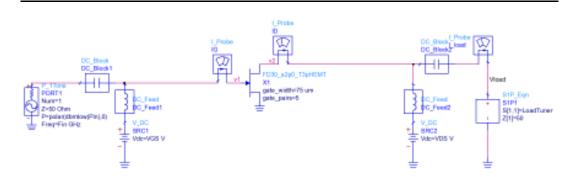

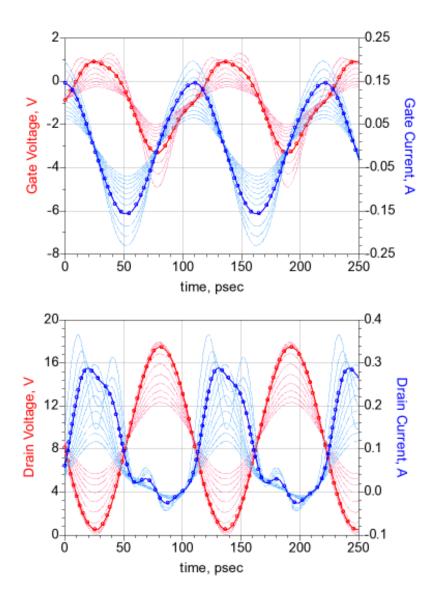

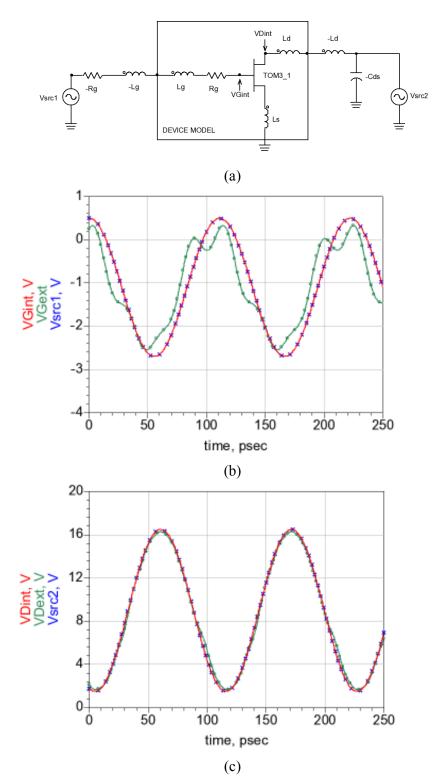

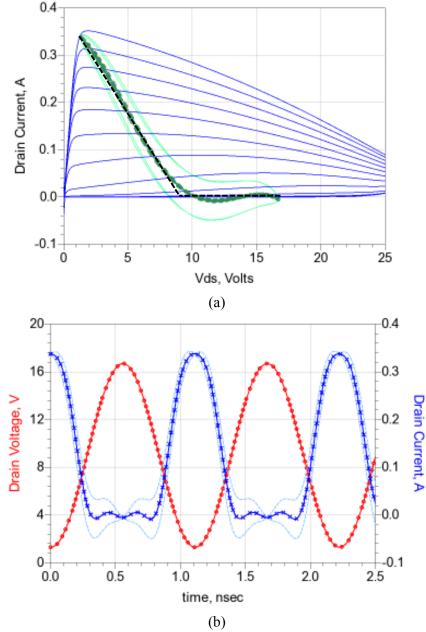

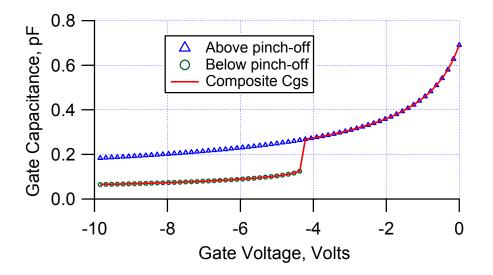

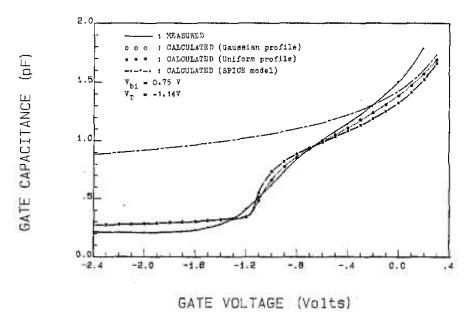

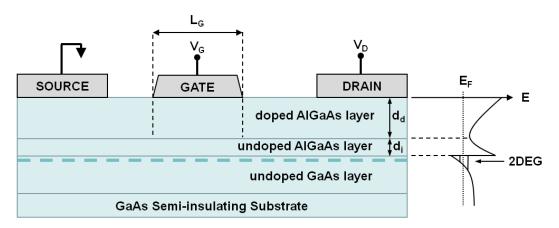

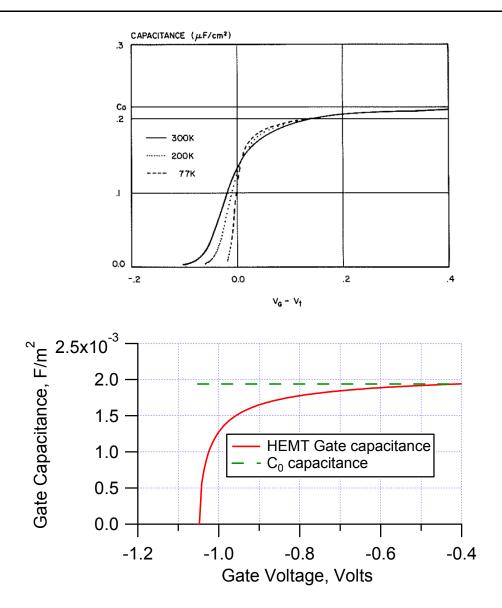

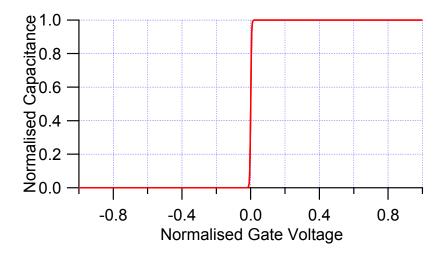

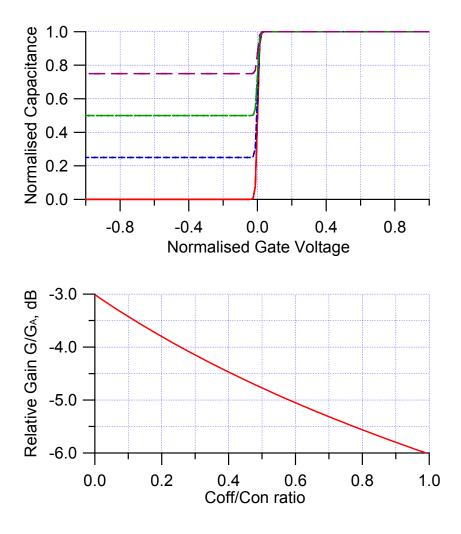

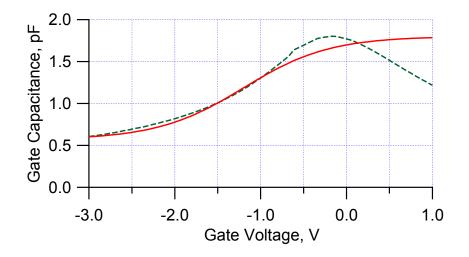

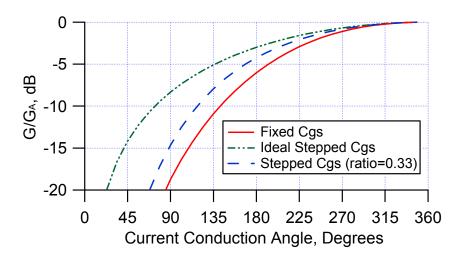

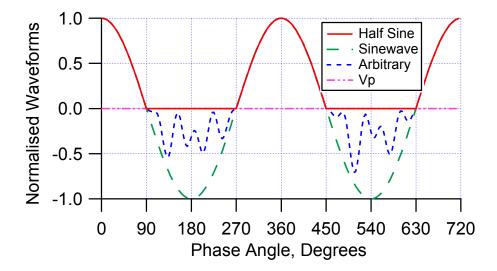

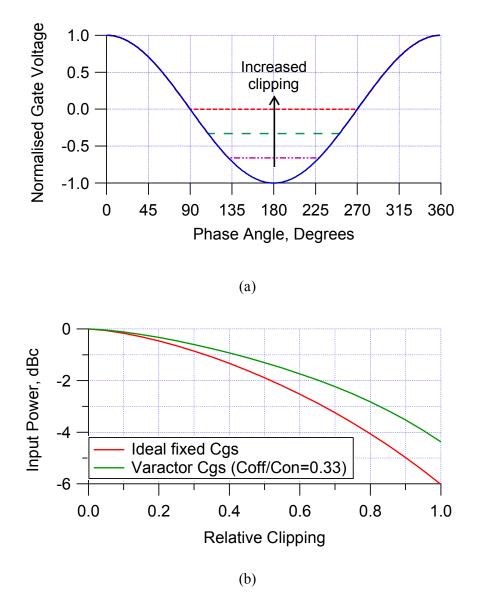

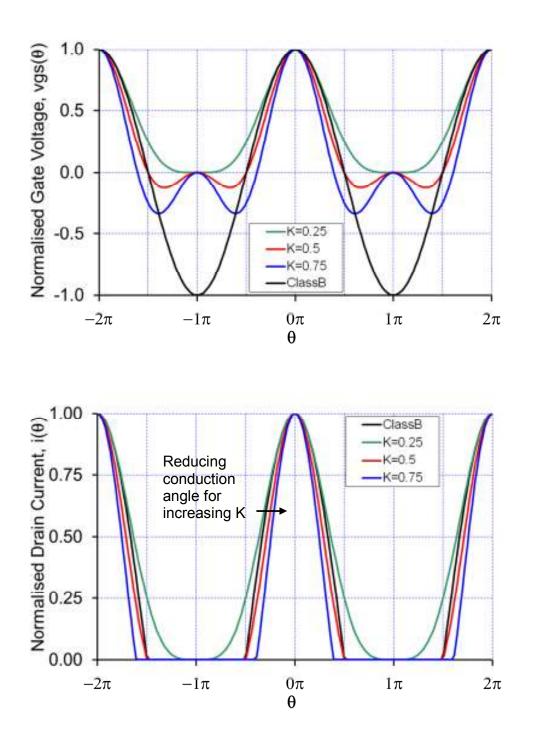

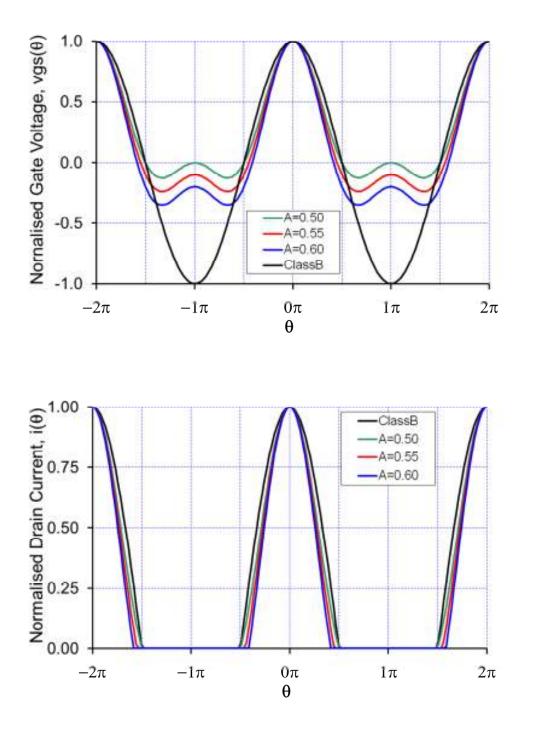

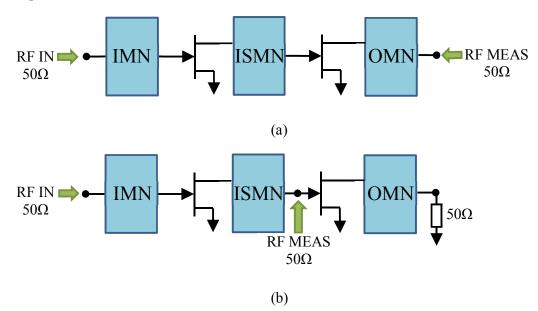

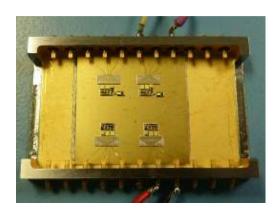

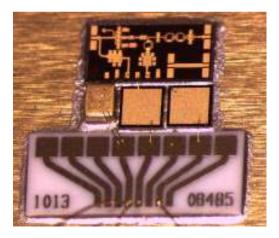

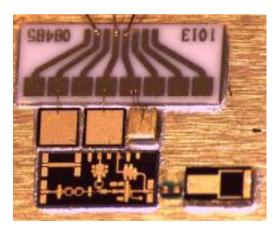

Practical devices have this intrinsic transistor structure embedded inside a parasitic 'shell' [59],[60],[61] which includes elements arising from the physical size of the device, and the connection to the outside world by bond pads, bond wire interconnects