# **CONTROL AND PROTECTION OF HVDC GRIDS**

THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

SHENG WANG

School of Engineering Cardiff University

Cardiff, 2016

# DECLARATION

This work has not been submitted in substance for any other degree or award at this or any other university or place of learning, nor is being submitted concurrently in candidature for any degree or other award.

Signed...... (candidate) Date.....

### **STATEMENT 1**

This thesis is being submitted in partial fulfilment of the requirements for the degree of ...... (insert Mch, MD, MPhil, PhD etc, as appropriate)

Signed...... (candidate) Date.....

#### **STATEMENT 2**

This thesis is the result of my own independent work/investigation, except where otherwise stated, and the thesis has not been edited by a third party beyond what is permitted by Cardiff University's Policy on the Use of Third Party Editors by Research Degree Students. Other sources are acknowledged by explicit references. The views expressed are my own.

Signed...... (candidate) Date.....

#### **STATEMENT 3**

I hereby give consent for my thesis, if accepted, to be available online in the University's Open Access repository and for inter-library load, and for the title and summary to be made available to outside organisations.

Signed...... (candidate) Date.....

# ABSTRACT

The decarbonisation of Europe's energy sector is a key driver for the development of integrated HVDC networks or DC grids. A multi-terminal HVDC grid will enable a more reliable power transfer from offshore wind farms and will facilitate the cross-border exchange of energy between different countries. However, the widespread deployment of DC grids is prevented by technical challenges, including the control and protection of DC grids. In order to close the gap, this thesis aims to contribute to three aspects (1): developing a control method for DC grids operation; (2): developing a method for optimising wind power delivery using DC grids; (3): developing a protection method for fast DC fault current interruption.

The control of a DC grid demands the regulation of DC voltage and hence keeps the power into and out from the DC grid balanced. It is also important to keep the accuracy of regulating the converter DC current. In this thesis, the Autonomous Converter Control (ACC) is developed to meet this requirement. With this method, alternative droop control characteristics can be used for individual converters to share the responsibility of regulation of DC voltage while precisely controlling the converter DC current. The control algorithms of alterative droop characteristics are developed and interactions of different control characteristics are analysed. Furthermore, the potential risk of having multiple cross-over in control characteristics is uncovered. The method for designing droop characteristics is provided to avoid the multiple cross-over. The ACC is demonstrated on different simulation platforms including the PSCAD/EMTDC and a real-time hardware 4-terminal HVDC test rig. It is found that the proper use of alternative droop characteristics can achieve better current control performance. The adverse impact of having multiple cross-over in control characteristics is also studied using both simulation platforms.

The effect of the control of both converters and DC power flow controllers (DC-PFCs) on DC power flow in steady state is also investigated. A method for re-dispatching control orders to optimise the wind power delivery is developed. Case studies are undertaken and it is found that both the DC line power loss and wind power curtailment can be reduced by re-dispatching the control orders of converters and DC-PFCs.

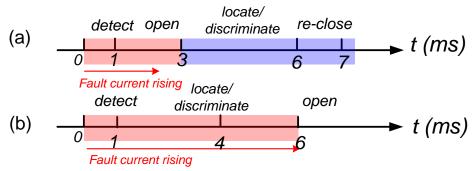

The protection of a DC grid demands a very fast speed for fault current interruption. Conventional methods proposed for HVDC grid protection take delays of several milliseconds to discriminate a faulted circuit to healthy circuits and then allow the DC circuit breakers (DC-CBs) to open at the faulted circuits. The fault current will keep rising during

the delayed time caused by fault discrimination. The Open Grid protection method is thus developed to interrupt fault current before fault discrimination. With this method, multiple DC-CBs open to interrupt the fault current based on local measurements of voltage (and current) and the DC-CBs on healthy circuits will reclose to achieve discrimination afterwards. This will reduce the delay for fault current interruption and hence the fault current can be interrupted with a much smaller magnitude. The developed Open Grid method is tested via simulation models developed in PSCAD/EMTDC. The results show that the Open Grid can detect very quickly and discriminate various faults under different fault conditions in a meshed HVDC grid.

# ACKNOWLEDGEMENTS

This dissertation would not have been possible without the invaluable and incessant support that I receive from many generous people.

I would like to convey my deepest and most sincere gratitude to my supervisor, Dr. Jun Liang, for delivering his extraordinary expertise, understanding and patience to shape my Ph.D. career. I am profoundly indebted to Professor Nick Jenkins and Dr. Janaka Ekanayake for their invaluable and ranging guidance on my research and inspiring support on improving my language skills. I would like to give very special thanks to Dr. Carlos Ugalde-Loo for his extremely kind encouragement and brilliant assistance throughout my study and every single football game. My thanks go to Prof. Jianzhong Wu who supported me in many ways during my studies in Cardiff. I also would like to thank Miss Catherine Roderick for sparing no effort in helping me improve my presentation skills.

My heartfelt gratitude goes to our industrial colleagues and friends, Dr. Andrzej Adamczyk, Mr. Robert Whitehouse and Prof. Carl Barker from Alstom Grid, for their kind assistance and inputs from an industrial point of view.

I wish to express my gratitude to all my colleagues and friends who help me navigate life as a Ph.D. student, especially those friends who shared the same office. I would like to thank Mr. Rui Dantas and Mr Senthooran Balasubramaniam for misunderstanding all my ideas, but nodding and smiling all the same. My thanks also go to colleagues at CIREGS, in particular friends within the MEDOW projects for creating such a friendly environment. My very special thanks go to Mr. Chuanyue Li who gave me much assistance in writing the thesis after my developing severe dry eye. I would like to thank Dr. Oluwole Adeuyi who help me proofread my thesis and provided kind comments.

I am particularly thankful to my family, especially my beloved parents for their intellectual contributions to my academic nature. More importantly, I appreciate for their unconditionally support, incessant encouragement and undoubted faith in my succeeding the Ph.D. career throughout all these years.

Last but not the least, this dissertation contains the outcome of projects with financial support from both Cardiff University and Alstom Grid. I would like to thank both.

# TABLE OF CONTENTS

| DEC   | CLARATION                             | II  |

|-------|---------------------------------------|-----|

| Abs   | STRACT                                | III |

| Аск   | NOWLEDGEMENTS                         | v   |

| Тав   | LE OF CONTENTS                        | vı  |

| List  | OF TABLES                             | x   |

| LIST  | OF FIGURES                            | XI  |

| List  | OF ABBREVIATIONS                      | xıv |

| Снд   | APTER 1                               | 1   |

| 1.    |                                       | 1   |

| 1.1   | UK Energy Policy                      | 1   |

| 1.2   | Motivations for Developing HVDC Grids | 2   |

| 1.2.1 | Offshore Power Transmission           | 2   |

| 1.2.2 | Point to Point HVDC Schemes           | 2   |

| 1.2.3 | Towards HVDC Grids                    |     |

| 1.3   | Technical Challenges                  | 6   |

| 1.4   | Research Objectives                   |     |

| 1.5   | Thesis Structure                      | 9   |

| 1.6   | List of Publications                  |     |

| 1.7   | Participation in Projects             |     |

| Сна   | APTER 2                               |     |

| 2.    | TECHNOLOGIES FOR HVDC GRIDS           | 13  |

| 2.1   | Introduction                          |     |

| 2.2   | AC/DC Converters                      |     |

#### CARDIFF E INSTITUTE OF ENERGY

|   | 2.2.1 | Line Commutated Converters                      |

|---|-------|-------------------------------------------------|

|   | 2.2.2 | Two-level Voltage Source Converters             |

|   | 2.2.3 | Multi-level Modular Converters15                |

|   | 2.2.4 | Basic Control of MMCs16                         |

|   | 2.3   | HVDC Transmission Lines                         |

|   | 2.4   | DC Circuit Breakers for HVDC Grid Protection    |

|   | 2.4.1 | HVDC Network Protection27                       |

|   | 2.4.2 | Proposed DC-CBs                                 |

|   | 2.5   | Summary                                         |

|   | Сна   | PTER <b>3</b>                                   |

|   | З.    | Control of an HVDC Grid                         |

|   | 3.1   | Introduction                                    |

|   | 3.2   | HVDC Grid Control Review                        |

|   | 3.2.1 | Requirement for Controlling an HVDC Grid        |

|   | 3.2.2 | Existing Control Methods                        |

|   | 3.3   | Autonomous Converter Control (ACC)              |

|   | 3.4   | Control Algorithm                               |

|   | 3.5   | Interaction of Control Characteristics          |

|   | 3.5.1 | Interactions between Droop Characteristics      |

|   | 3.5.2 | Interactions of Power and Droop Characteristics |

|   | 3.5.3 | Mathematical Analysis of control interactions   |

|   | 3.6   | Multiple Cross-Over of Control Characteristics  |

|   | 3.7   | Summary                                         |

|   | Сна   | PTER 4                                          |

| 4 | . (   | COMPUTER SIMULATION AND EXPERIMENTAL VALIDATION |

|   | of A  | ACC 57                                          |

|   | 4.1   | Introduction                                    |

| UNIVERSITY | INSTITUTE OF |

|------------|--------------|

| CAERDY     | ENERGY       |

|            |              |

| 4.2   | Configuration of 4-terminal HVDC Test Rig           |

|-------|-----------------------------------------------------|

| 4.3   | System Configuration for Testing ACC                |

| 4.4   | Control Units for Testing ACC                       |

| 4.5   | Implementation of Converter Control within ACC      |

| 4.6   | Case study                                          |

| 4.6.1 | Coordination of Converter Control                   |

| 4.6.2 | Multiple Cross-overs in the Static Characteristics  |

| 4.7   | Summary                                             |

| Сна   | PTER 5                                              |

| 5.    | <b>OPTIMISATION OF WIND POWER DELIVERY USING DC</b> |

| Pow   | ver Flow Controllers and AC/DC Converters75         |

| 5.1   | Introduction75                                      |

| 5.2   | DC Power Flow Controllers75                         |

| 5.3   | Control Strategy of an HVDC Grid with DC-PFCs       |

| 5.4   | Control of DC-PFCs                                  |

| 5.5   | DC Voltage versus Power Droop for Converters        |

| 5.6   | Impact of Changing Control Orders on DC Power Flow  |

| 5.7   | Optimisation of DC Power Flow                       |

| 5.8   | Case study                                          |

| 5.9   | Summary                                             |

| Сна   | PTER 6                                              |

| 6.    | HVDC GRID PROTECTION: OPEN GRID METHOD 94           |

| 6.1   | Introduction                                        |

| 6.2   | DC Grid Protection Review94                         |

| 6.3   | Basic Ideas of Open Grid Protection Approach        |

| 6.4   | Fault Detection Algorithm                           |

| 6.5   | Selection of Criteria for Fault Detection           |

| 6.6                                                                                              | Discrimination by Integration of Current in Transients 100                                                        |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 6.7                                                                                              | Discrimination by Residual Voltages101                                                                            |

| 6.8                                                                                              | Simulation Results                                                                                                |

| 6.8.1                                                                                            | Test System                                                                                                       |

| 6.8.2                                                                                            | Modelling of DC Components 106                                                                                    |

| 6.8.3                                                                                            | Case Studies                                                                                                      |

| 6.8.4                                                                                            | Summary                                                                                                           |

| Сна                                                                                              | PTER 7 118                                                                                                        |

| 7.                                                                                               | CONCLUSION AND FUTURE WORK                                                                                        |

| 1.                                                                                               |                                                                                                                   |

| <b>7</b> .1                                                                                      | Conclusion                                                                                                        |

| -                                                                                                |                                                                                                                   |

| 7.1                                                                                              | Conclusion118                                                                                                     |

| 7.1<br>7.1.1                                                                                     | Conclusion                                                                                                        |

| <ul><li>7.1</li><li>7.1.1</li><li>7.1.2</li></ul>                                                | Conclusion.118HVDC Grid Control.118HVDC Grid Protection.120                                                       |

| <ul><li>7.1</li><li>7.1.1</li><li>7.1.2</li><li>7.2</li></ul>                                    | Conclusion.118HVDC Grid Control.118HVDC Grid Protection.120Future Work.120                                        |

| <ul> <li>7.1</li> <li>7.1.1</li> <li>7.1.2</li> <li>7.2</li> <li>7.2.1</li> <li>7.2.2</li> </ul> | Conclusion.118HVDC Grid Control.118HVDC Grid Protection.120Future Work.120Protection of Non-permanent DC Fault120 |

# LIST OF TABLES

| Table 1-1 LIST OF MULTI-TERMINAL HVDC (MTDC) SYSTEM PROJECTS             |

|--------------------------------------------------------------------------|

| Table 2-1 SUMMARY OF THE OPERATION WITH CVB ALGORITHM                    |

| Table 3-1 COMPARISON OF AN AC GRID AND A DC GRID [57]                    |

| Table 3-2 TERMINOLOGIES FOR DIFFERENT DROOP TYPES    42                  |

| Table 3-3 SIGNAL FLOWING INTO/OUT OF THE SELECTION BLOCK44               |

| Table 3-4 CURRENT CONTROL PERFORMANCE OF DIFFERENT CONTROL METHODS       |

| Table 4-1 SUMMARY OF SIMULATION PARAMETERS    61                         |

| Table 4-2 BASIC DATA OF CONVERTER CONTROL FOR TEST ONE    69             |

| Table 4-3 BASIC DATA OF CONVERTER CONTROL FOR TEST TWO       71          |

| Table 5-1 PARAMETERS OF DC DEVICES                                       |

| Table 5-2 RESULTS OF CASE ONE    90                                      |

| Table 5-3 Change of control orders in case two                           |

| Table 5-4 COMPARISON OF WIND POWER DELIVERY IN CASE TWO                  |

| Table 5-5 Change of control orders in case three                         |

| Table 5-6 COMPARISON OF WIND POWER DELIVERY IN CASE THREE                |

| Table 6-1 COMPARISON OF VOLTAGE PROFILE    103                           |

| Table 6-2 PARAMETER FOR THE CONDUCTOR AND THE GROUND WIRE                |

| Table 6-3 CONDUCTOR DATA AND GROUND WIRE DATA OF OHL MODEL       107     |

| Table 6-4 Thresholds of protection and control setting of VSCs       109 |

# LIST OF FIGURES

|     | Fig 1.1 Generation and transmission capacity forecast [2]                    | 1  |

|-----|------------------------------------------------------------------------------|----|

|     | Fig 1.2 Dogger Bank connection overview [4]                                  | 2  |

|     | Fig 1.3 VSC based MTDC systems projects: (a) Nao'ao MTDC, (b): Zhoushan MT   | DC |

| Int | terconnection, (c): South-West Link [20], (d): Tres amigas superstation [21] | 5  |

|     | Fig 1.4 Challenges towards a large HVDC grid                                 | 7  |

|     | Fig 2.1 Typical layout of a LCC                                              | 13 |

|     | Fig 2.2 Architecture of a 2-level VSC                                        | 14 |

|     | Fig 2.3 Sinusoidal Pulse Width Modulation                                    | 15 |

|     | Fig 2.4 Architecture of a MMC and the output AC waveform                     | 16 |

|     | Fig 2.5 Hierarchical control structure of an MMC                             | 17 |

|     | Fig 2.6 Outer control loop for non-islanded control mode                     | 18 |

|     | Fig 2.7 Inner decoupled current control for non-islanded control mode        | 19 |

|     | Fig 2.8 Generation of AC voltage reference with islanded control mode        | 20 |

|     | Fig 2.9 Phase disposition modulation                                         | 21 |

|     | Fig 2.10 Phase shift modulation                                              | 21 |

|     | Fig 2.11 Nearest level control                                               | 21 |

|     | Fig 2.12 Control of CVB                                                      | 22 |

|     | Fig 2.13 Circulating current suppression control                             | 24 |

|     | Fig 2.14 Mass-impregnated cables [47]                                        | 26 |

|     | Fig 2.15 Extruded cables                                                     | 26 |

|     | Fig 2.16 Protection of a P2P HVDC link                                       | 27 |

|     | Fig 2.17 Protection of a HVDC grid                                           | 28 |

|     | Fig 2.18 A passive mechanical resonant breaker [50]                          | 30 |

|     | Fig 2.19 An active mechanical active resonant breaker [53]                   | 30 |

|     | Fig 2.20 Full solid-state breaker [54]                                       | 31 |

|     | Fig 2.21 Hybrid HVDC circuit breaker [56]                                    | 32 |

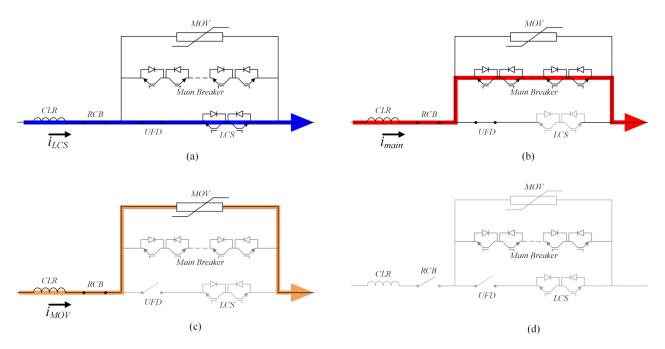

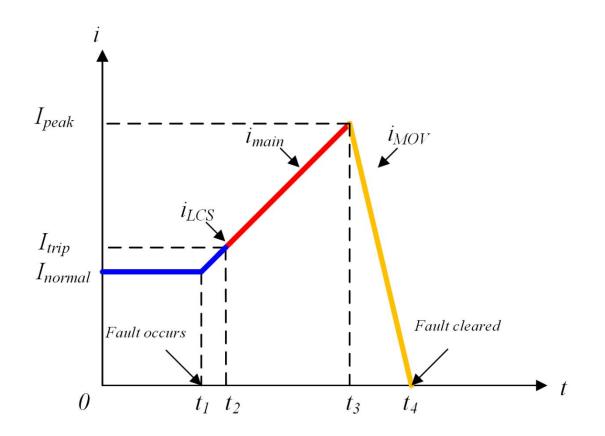

|     | Fig 2.22 Working principle of a hybrid HVDC breaker                          | 33 |

|     | Fig 2.23 Process of fault current interruption                               | 33 |

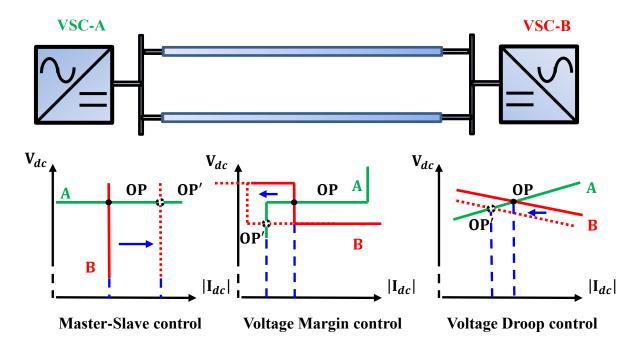

|     | Fig 3.1 Control methods for a HVDC network                                   | 37 |

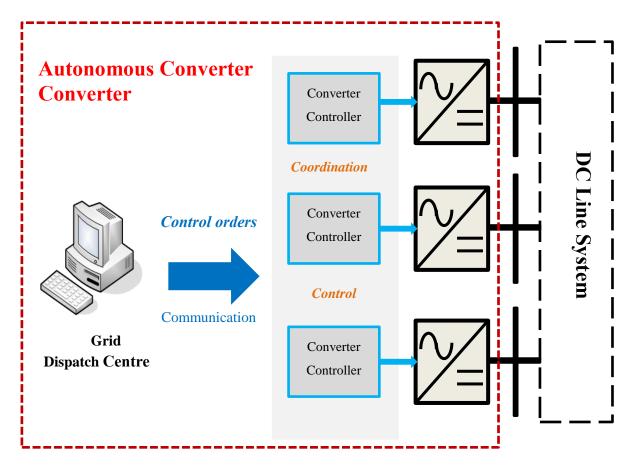

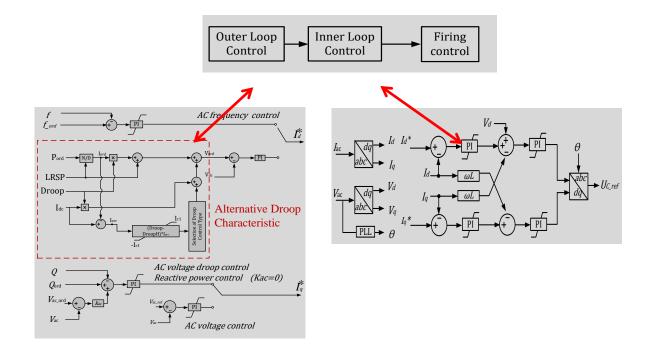

|     | Fig 3.2 Control structure of the Autonomous Converter Control                | 39 |

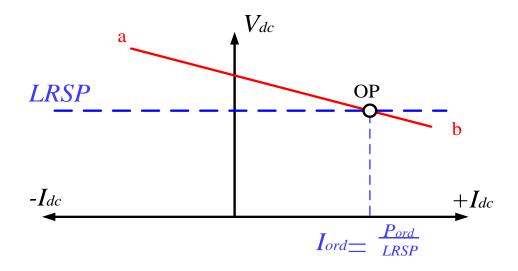

|     | Fig 3.3 DC converter droop characteristics                                   | 40 |

|     | Fig 3.4 Current error                                                        | 41 |

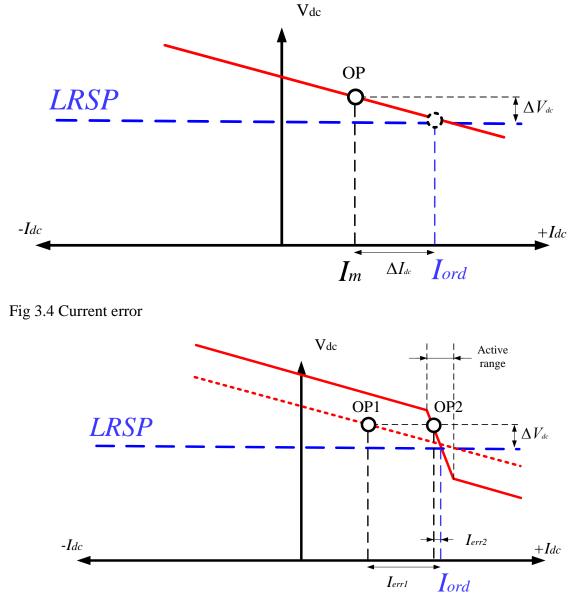

| Fig 3.5 Droop characteristics with current error function                              | 41      |

|----------------------------------------------------------------------------------------|---------|

| Fig 3.6 Further modification on current error function                                 | 42      |

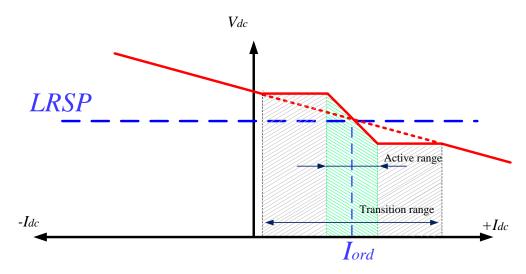

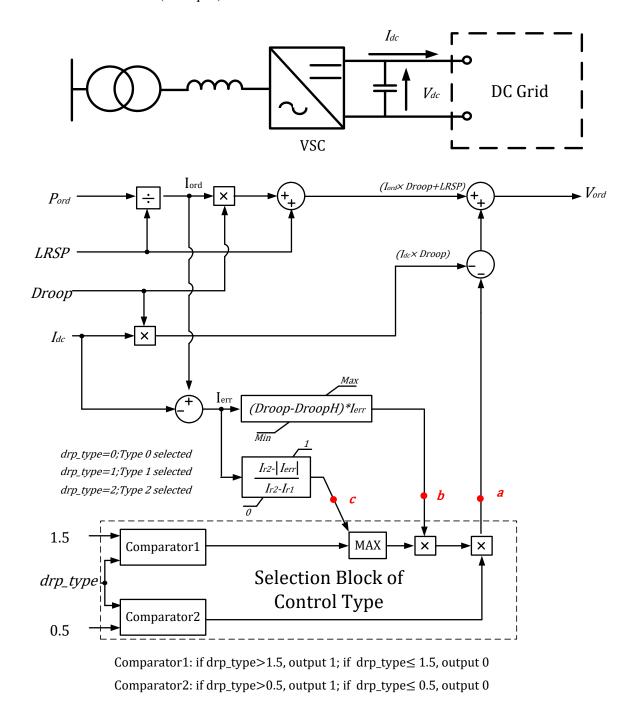

| Fig 3.7 Alternative droop control system                                               | 43      |

| Fig 3.8 Power control system                                                           | 46      |

| Fig 3.9 Interaction of different droop characteristics in (a): active range; (b): tran | sition  |

| range; and (c) outside the transition range                                            | 47      |

| Fig 3.10 Interaction of droop characteristics and power control characteristics        | 48      |

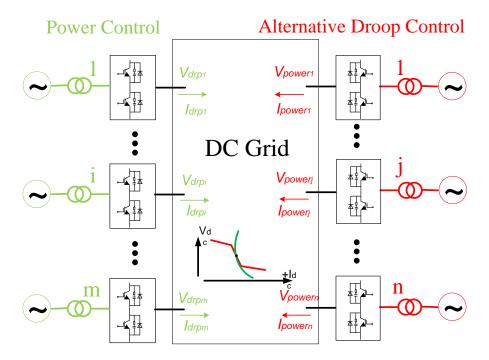

| Fig 3.11 A HVDC grid of controls in both power and alternative droop control           | 49      |

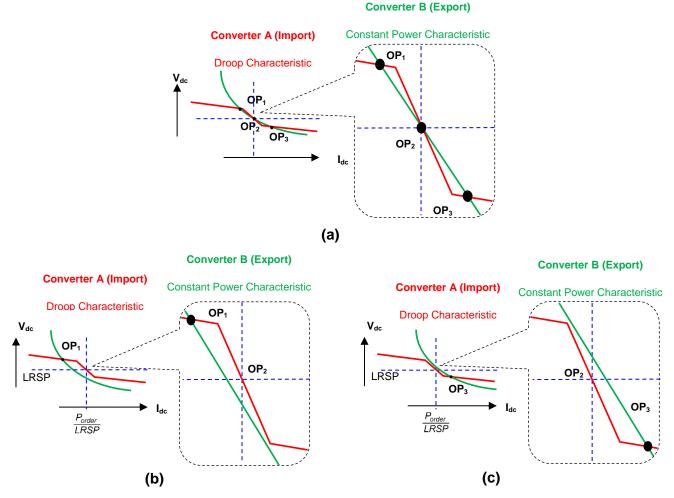

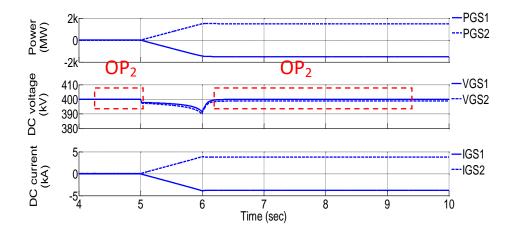

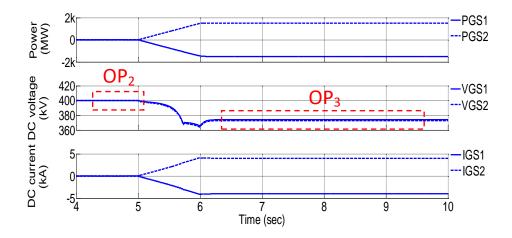

| Fig 3.12 a) Multiple Operating Points, b) Reduced Power, c) Increased Power            | 53      |

| Fig 3.13 Multiple operating points                                                     | 53      |

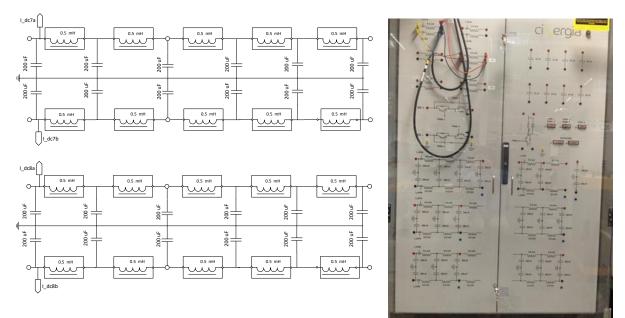

| Fig 4.1 Configuration of the 4-terminal HVDC test rig                                  | 57      |

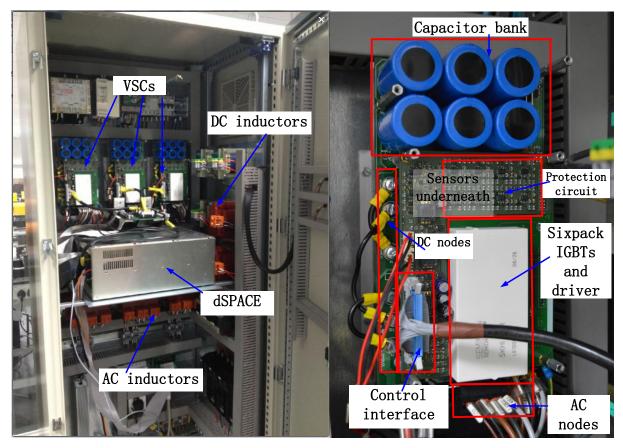

| Fig 4.2 Physical model of VSCs (a): inside view of cabinet of VSCs; (b) PCBs           | 58      |

| Fig 4.3 Inside view of cabinet containing Unidrives                                    | 59      |

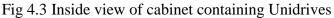

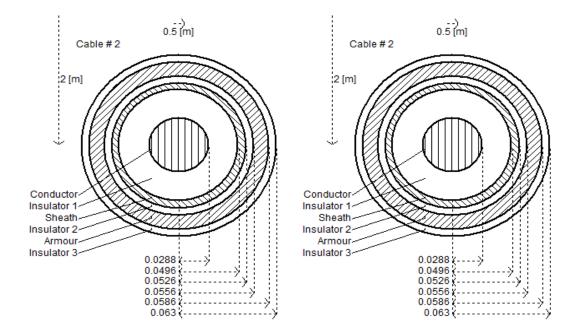

| Fig 4.4 Cable representations: (a) DC cable model (b) Physical representations         | 60      |

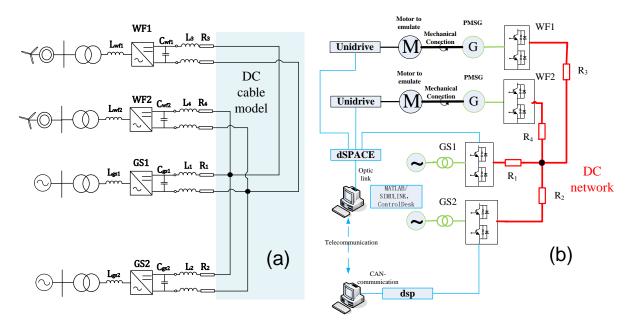

| Fig 4.5 Star-connected VSC simulator: (a) Circuit diagram; (b) Simulator set-up        | 60      |

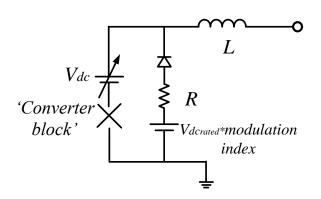

| Fig 4.6 Simplified VSC converter model [77]                                            | 62      |

| Fig 4.7 Control boards within the dSPACE control unit                                  | 62      |

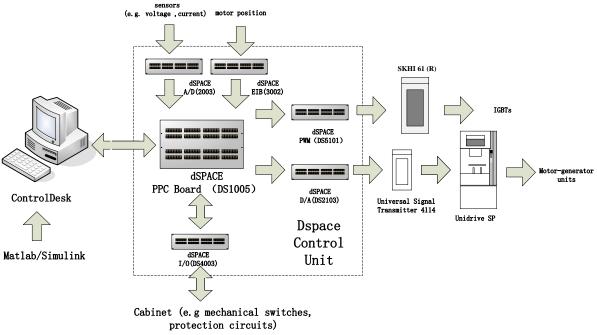

| Fig 4.8 Example of dSPACE – ControlDesk                                                | 63      |

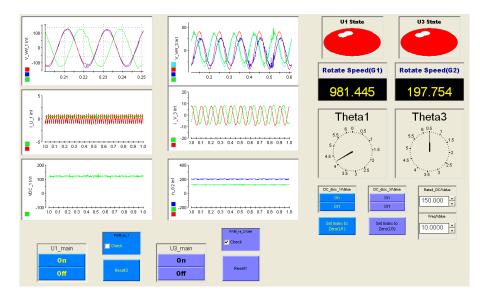

| Fig 4.9 Self-built Graphical User Interface                                            | 64      |

| Fig 4.10 Hierarchical structure of converter control implemented in the test rig       | 65      |

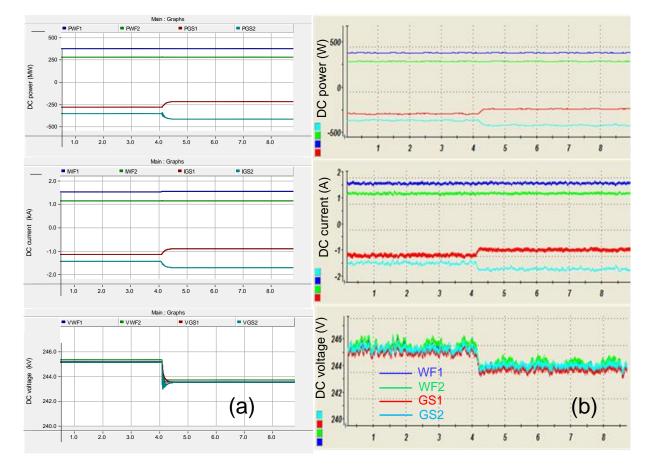

| Fig 4.11 Current error function simulation- (a): PSCAD result; (b): experimental resu  | ılt66   |

| Fig 4.12 Converter operation during change of power condition - (a): PSCAD resul       | t; (b): |

| experimental result                                                                    | 68      |

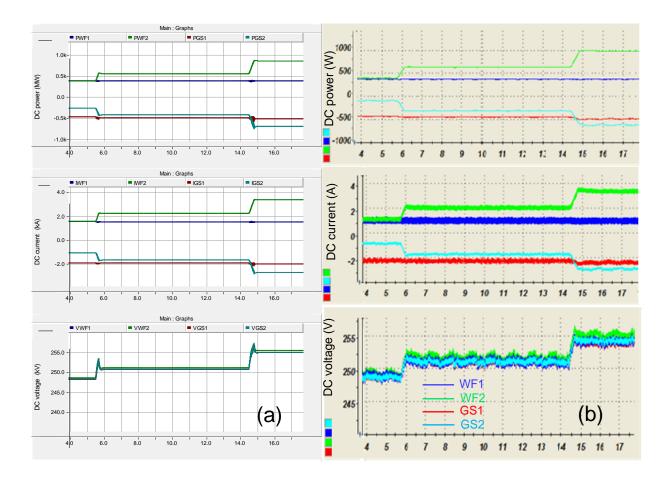

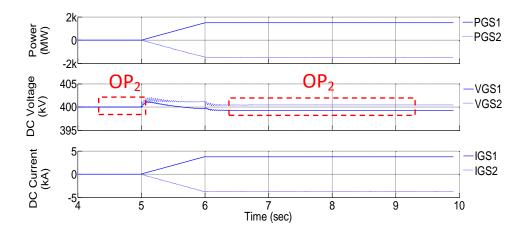

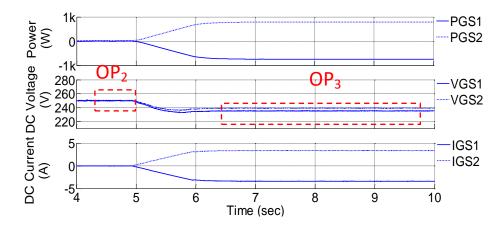

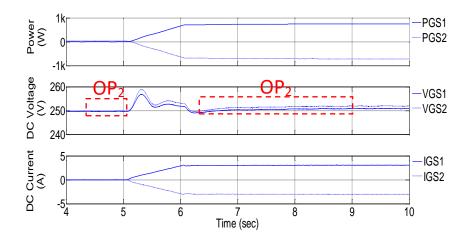

| Fig 4.13 (a) PSCAD: conventional droop characteristics (power ramp 0 MW to 1500        | MW)     |

|                                                                                        | 70      |

| Fig 4.14 (a) HVDC test rig: conventional droop characteristics (power ramp 0 to 75     | 50 W)   |

|                                                                                        | 72      |

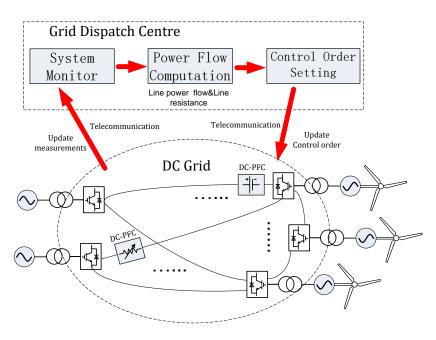

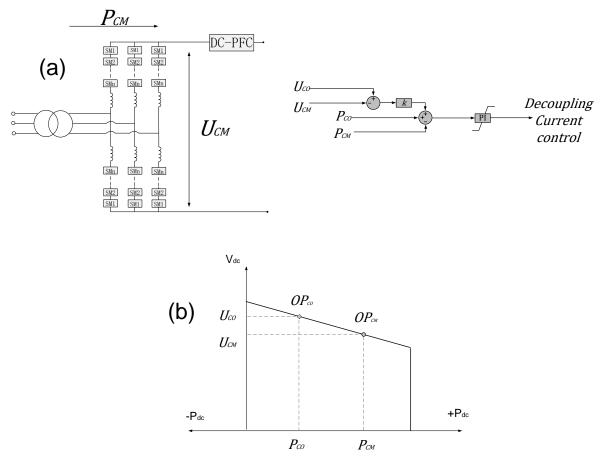

| Fig 5.1 Control strategy of a HVDC grid having DC-PFCs                                 | 76      |

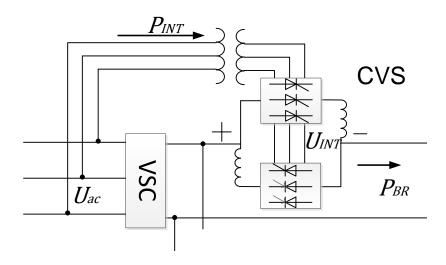

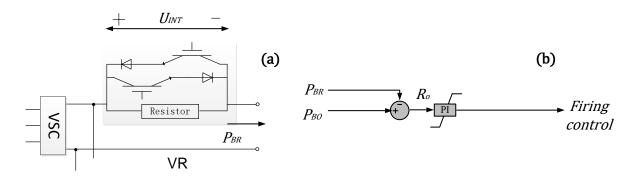

| Fig 5.2 Thyristor based Controllable Voltage Source (CVS)                              | 77      |

| Fig 5.3 IGBT based CVS                                                                 | 78      |

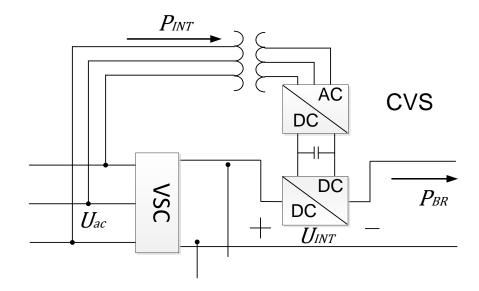

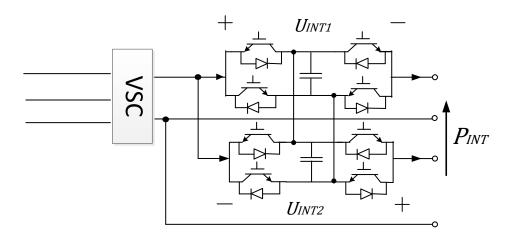

| Fig 5.4 An alternative power flow controller                                           | 78      |

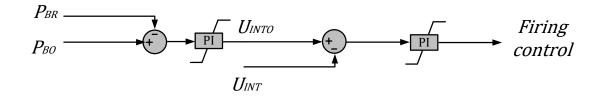

| Fig 5.5 Outer control loop for CVSs                                                    | 79      |

| Fig 5.6 An example of (a): Variable Resistor (VR) and (b): its control loop            | 79      |

| Fig 5.7 Converter with V/P droop: (a) control structure (b) V/P droop characteristics. | 80      |

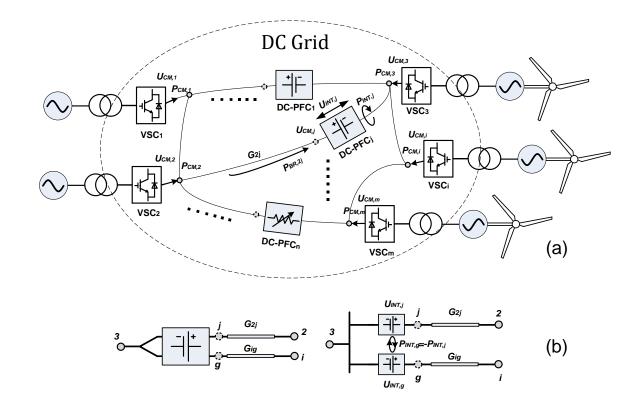

| Fig 5.8 An HVDC Grid integrated with <i>m</i> AC/DC converters and <i>n</i> DC-PFCs82       |

|---------------------------------------------------------------------------------------------|

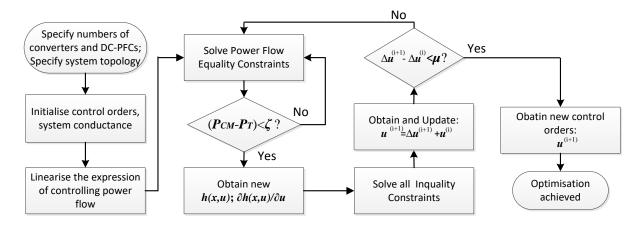

| Fig 5.9 Flow chart of solving optimal DC power flow                                         |

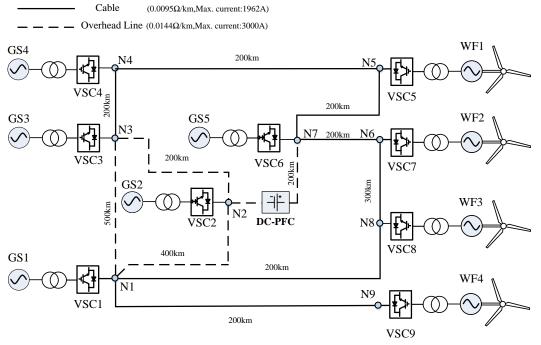

| Fig 5.10 A 9-terminal DC system with the integration of a DC-PFC                            |

| Fig 6.1 Action sequence of: (a) Open Grid protection method; (b) Conventional DC grid       |

| protection method96                                                                         |

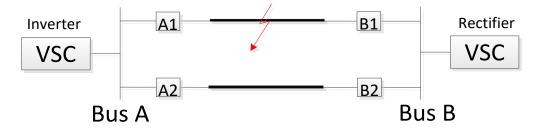

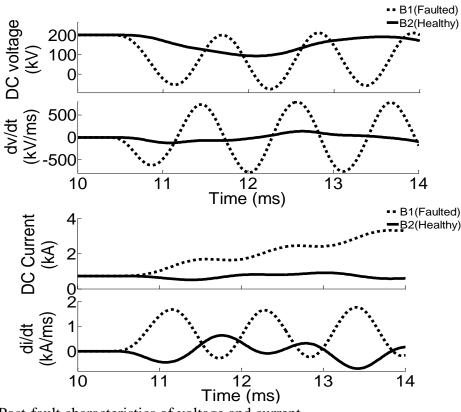

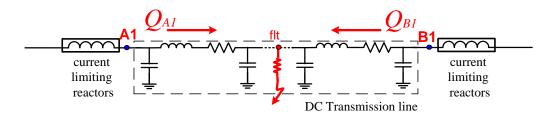

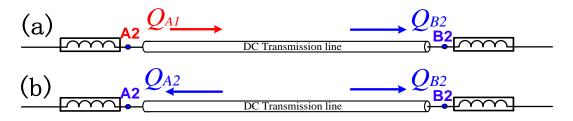

| Fig 6.2 One line diagram of the two-VSC, two-branch DC system97                             |

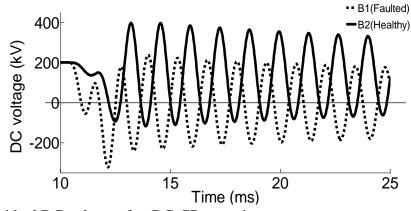

| Fig 6.3 Post-fault characteristics of voltage and current                                   |

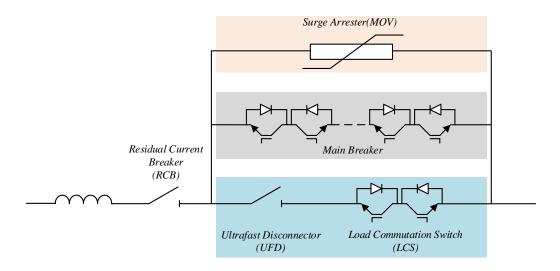

| Fig 6.4 A hybrid DC-CB99                                                                    |

| Fig 6.5 Integration of current in transient flowing through faulted circuit                 |

| Fig 6.6 Integration of current in transient flowing through healthy circuit100              |

| Fig 6.7 Residual DC voltage after DC-CBs opening                                            |

| Fig 6.8 Extracted DC component of residual DC voltage104                                    |

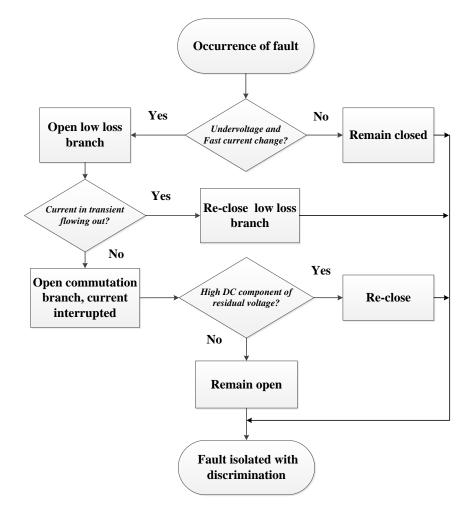

| Fig 6.9 Flow chart of DC-CB acting in a fault event105                                      |

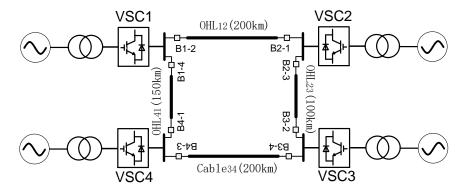

| Fig 6.10 One line diagram of meshed DC test system Power Component106                       |

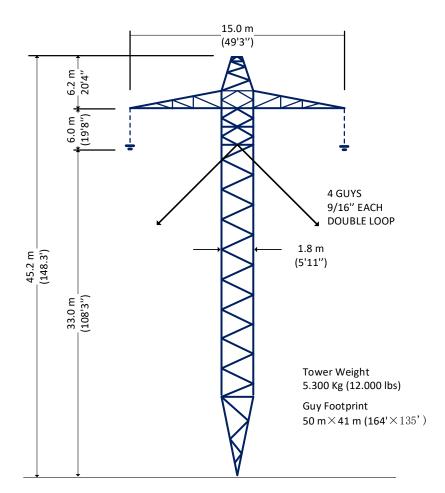

| Fig 6.11 Structure of the OHL tower108                                                      |

| Fig 6.12 Configuration of cable modelling in PSCAD/EMTDC108                                 |

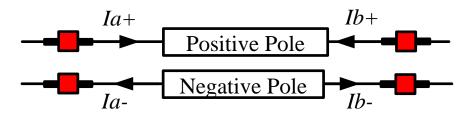

| Fig 6.13 Sign convention of current in both poles109                                        |

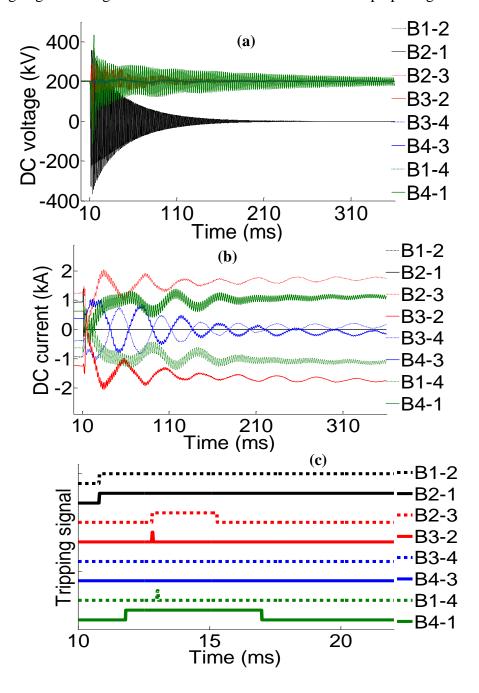

| Fig 6.14 Pole to pole fault on OHL12: (a) DC voltage; (b) DC current; (c) tripping          |

| timings of DC-CB110                                                                         |

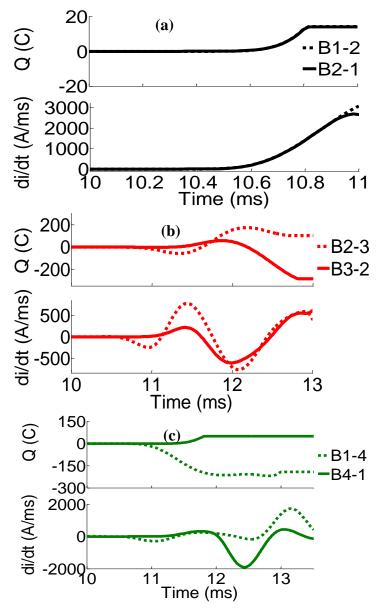

| Fig 6.15 Integration of current transient and current derivatives at: (a) OHL12; (b) OHL23; |

| (c) OHL14111                                                                                |

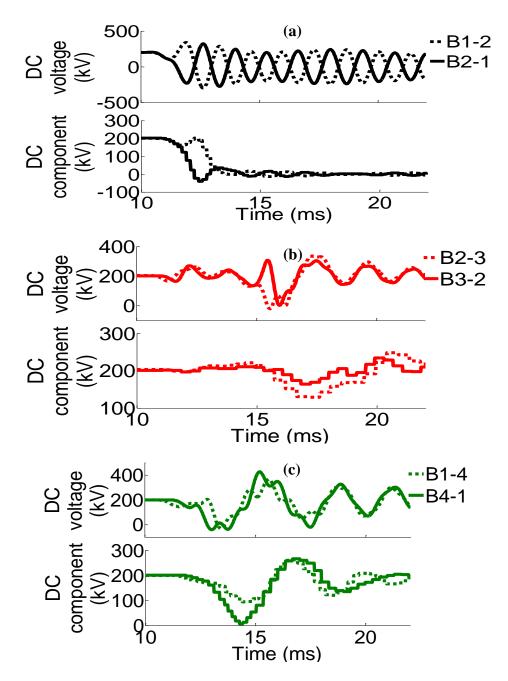

| Fig 6.16 DC voltages and their DC components at (a): OHL12; (b) OHL23; (c) OHL14112         |

| Fig 6.17 Pole to pole fault on Cable34: (a) DC voltage; (b) DC current; (c) tripping        |

| timings of DC-CBs113                                                                        |

| Fig 6.18 Pole to ground fault on OHL12: (a) DC voltage; (b) DC current; (c) tripping        |

| timings of DC-CBs114                                                                        |

| Fig 6.19 Integration of current transient and current derivatives at: (a) OHL12; (b) OHL23; |

| (c) OHL14115                                                                                |

| Fig 6.20 DC voltages and their DC components at (a): OHL12; (b) OHL23; (c) OHL14116         |

# LIST OF ABBREVIATIONS

| AC     | Alternate Current                 |

|--------|-----------------------------------|

| ACC    | Autonomous Converter Control      |

| AC-CB  | AC Circuit Breaker                |

| A/D    | Analogue/Digital                  |

| B2B    | Back To Back                      |

| CAN    | Controller Area Network           |

| CVB    | Capacitor Voltage Balancing       |

| CVS    | Controllable Voltage Source       |

| DC     | Direct Current                    |

| DC-CB  | DC Circuit Breaker                |

| DC-PFC | DC Power Flow Controller          |

| DSP    | Digital Signal Processor          |

| d- $q$ | Direct-Quadrature                 |

| EU     | European Union                    |

| FFT    | Fast Fourier Transfer             |

| GDC    | Grid Dispatch Centre              |

| GS     | Grid Side                         |

| GUI    | Graphical User Interface          |

| HB     | Half Bridge                       |

| HMI    | Human-Machine Interface           |

| HVAC   | High Voltage Alternate Current    |

| HVDC   | High Voltage Direct Current       |

| IGBT   | Insulated Gate Bipolar Transistor |

| I/O    | Input/Output                      |

| LCC    | Line Commutated Converter         |

| LCS    | Load Commutation Switch           |

| LRSP   | Load Reference Set Point          |

| MFC    | Microsoft Foundation Class        |

| MI     | Mass Impregnated                  |

| MMC    | Modular Multi-Level Converter     |

| MOV    | Metal Oxide Varistor              |

|        |                                   |

| MTDC    | Multi-terminal High Voltage Direct Current   |

|---------|----------------------------------------------|

| NLC     | Nearest Level Control                        |

| NSCOGI  | North Sea Countries Offshore Grid Initiative |

| ODIS    | Offshore Development Information Statement   |

| OFGEM   | Office for Gas and Electricity Markets       |

| OHL     | Overhead Line                                |

| OP      | Operating Point                              |

| OPF     | Optimal Power Flow                           |

| P2P     | Point To Point                               |

| PCB     | Printed Circuit Boards                       |

| PD-PWM  | Phase Disposition Modulation                 |

| PI      | Proportional Integral                        |

| PLL     | Phase Locked Loop                            |

| PS-PWM  | Phase Shift Modulation                       |

| PWM     | Pulse Width Modulation                       |

| RCB     | Residual Circuit Breaker                     |

| SM      | Submodules                                   |

| STATCOM | Static Synchronous Compensator               |

| STW     | Scottish Territorial Water                   |

| TSO     | Transmission System Operator                 |

| UFD     | Ultrafast Disconnector                       |

| UK      | United Kingdom                               |

| VR      | Variable Resistor                            |

| VSC     | Voltage Source Converter                     |

| WF      | Wind Farm                                    |

# **CHAPTER 1**

### INTRODUCTION

### **1.1 UK ENERGY POLICY**

The UK government anticipates that 15% of energy demand will be provided by renewable sources and Green House Gas emissions will be reduced by 34% by 2020 and eventually reduced by 80% by 2050. The National Grid Electricity Transmission has thus proposed four different scenarios [1] with only the 'Gone Green' scenario [2] representing a balanced approach to meeting this target in which electricity generation, heat and transport all contribute.

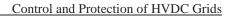

Under the 'Gone Green' scenario conventional coal plants will gradually be replaced by renewable energy generation. There will be 31% of electricity generated from renewable sources by 2020 (See Fig 1.1). The total transmission connected wind capacity will reach 26 GW by 2020 in which offshore wind will have a high proportion (17 GW). The Crown Estate has already issued three rounds of offshore wind farm licenses, which will potentially lead to a total capacity of over 40 GW. The first two rounds (including Round 2 extension) will contribute an offshore wind capacity of around 8 GW by 2020. The Round 3 and Scottish Territorial Water (STW) projects will contribute the remaining 9 GW by 2020. The UK government and OFGEM have estimated that the UK offshore transmission will spend over 15 billion pounds to connect the projects of the three rounds [3].

Fig 1.1 Generation and transmission capacity forecast [2]

## **1.2** MOTIVATIONS FOR DEVELOPING HVDC GRIDS

## **1.2.1 OFFSHORE POWER TRANSMISSION**

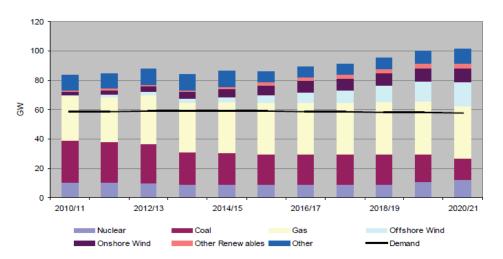

The average distance of the offshore WFs to shore will increase from 6 km in Round 1 projects to 65 km in Round 2 projects. For the Round 3 project on Dogger Bank, the average distance will be about 197.2 km (See Fig 1.2). Submarine HVAC is not an economic solution for transmitting power over such a long distance. HVAC transmission using cables is limited by the generation of reactive power (which requires compensation by shunt reactors) and by voltage. In contrast, HVDC transmission is free of reactive power and DC cables have higher power rating than that of AC. DC converters offer extra flexibility for power and voltage control, they can also support additional damping in case of power oscillations in AC grid. HVDC is expected to be the predominant option for long distance offshore transmission.

Fig 1.2 Dogger Bank connection overview [4]

## **1.2.2 POINT TO POINT HVDC SCHEMES**

Most of the existing HVDC transmission systems are point to point (P2P) schemes and which are based on two technologies namely Line Commutated Converter (LCC-HVDC) or Voltage Source Converter (VSC-HVDC). To date, LCC technology dominates the DC transmission market. However, there are several limitations of LCC-HVDC which makes it

inadequate for offshore transmission. The operation of a LCC requires voltage sources for commutation. Harmonics generated by LCC converters needs the deployment of large filters at converter stations. Commutation failure may occur in a LCC during system disturbance. The reverse of power flow direction in LCC-HVDC system can only be achieved by reversing voltage polarity.

Conversely, the operation of VSC converters does not consume reactive power while the size of filters can be reduced (or avoided if MMC technology used) which leads to small footprint of offshore platform. Both active and reactive power can be controlled in VSC-HVDC and there is no commutation failure problem. Furthermore, VSC-HVDC systems can reverse power flow direction by changing the direction of current which enables the wind farm black-start. These benefits of VSC have driven the market of VSC transmission in recent years; proposed VSC-HVDC schemes include Borwin, Dolwin, Helwin and Sylwin projects.

### **1.2.3 TOWARDS HVDC GRIDS**

It has been claimed that compared to several P2P systems, a HVDC grid has overall lower conversion losses and lower cost by reducing the number of converter stations and cable length. Interest in developing DC grids is reflected by the increased studies in which HVDC grids are proposed. Examples are given below:

The "*TradeWind*" project [5] of Intelligent Energy Europe is the first EU-level study to explore the benefits of building a European grid that can have on the integration of large amounts of wind power. This was followed by the "*OffshoreGrid*" project [6] which provides the first in-depth analysis of building a cost-efficient grid in the North and Baltic Seas. Both studies show that a HVDC mesh grid would be economically optimum means of the integration of offshore wind power. In 2009 to 2012, the countries around the North Sea discussed building the North Sea Super Grid (NSSG) under the *North Sea Countries Offshore Grid Initiative (NSCOGI)* [7]. Meanwhile, the UK National Grid proposed a coordinated strategy for offshore transmission based on DC grid in the *offshore development information statement (ODIS)* [8]. In 2013, the third demonstration project of "*TWENTIES*" [9] (funded by European Commission's Directorate-General for Energy) provided and demonstrated the secure operation of key building blocks for designing future DC grids including voltage source converter (VSC) and DC circuit breaker (DC-CB). The "*MEDOW*" project [10] (funded by the People programme of the Seventh Framework Programme of the European

Union) started in the same year and focuses on the research of using MTDC system to integrate offshore wind power. The Friends of the Super Grid proposed the *Roadmap to the Supergrid Technologies* [11] which anticipates a "DC supergrid" to be the backbone of Europe's future power system. This DC supergrid will deliver decarbonised electricity across the continent and enhance the existing AC networks. The ENTSO-E also considers a DC supergrid as one approach to meet the energy target for 2050 and it works in line with the Agency for the Cooperation of Energy Regulators to draft the network code on HVDC Connections [12]. Moreover, the working group B4 of CIGRE conducts a range of studies which focus on the feasibility of HVDC grids [13], Grid Codes for HVDC grids [14], HVDC grids modelling [15], load flow control device and system voltage control [16], control and protection of HVDC grids [17] and optimal reliability and availability of HVDC grids [18].

To date, there are a few multi-terminal HVDC system projects as listed in Table 1-1.

| Names/<br>Connection                    | No. of<br>Terminals                       | Converter<br>Type | Rating                           | Year          |

|-----------------------------------------|-------------------------------------------|-------------------|----------------------------------|---------------|

| HVDC Italy–<br>Corsica–Sardinia         | 3                                         | LCC               | 220kV/200MW                      | 1987          |

| Quebec – New<br>England<br>Transmission | 5 (3 in operation)                        | LCC               | ±450kV/2250MW                    | 1992          |

| Nelson River<br>HVDC System             | 2 (can be in<br>MTDC mode)                | LCC               | ±500kV/3800MW                    | 1985          |

| Pacific DC Intertie                     | 2 (can be in<br>MTDC mode)                | LCC               | ±500kV/3100MW                    | 1989          |

| North-East Agra                         | 4                                         | LCC               | ±800kV/6000MW                    | 2016 (Planed) |

| Shin Shinano3<br>terminal VSC-B2B       | 3                                         | VSC               | 10.6kV/53MW                      | 1999          |

| Nao'ao MTDC                             | 3 (4 <sup>th</sup> terminal being planed) | VSC               | ±160 kV,<br>200/100/50MW         | 2013          |

| Zhoushan MTDC<br>Interconnection        | 5                                         | VSC               | ±200kV,100/100<br>/100/300/400MW | 2014          |

| Tres amigas superstation                | 3                                         | VSC               | ±345kV/750MW                     | 2015          |

| South-West Link                         | 3                                         | VSC               | ±300kV/1440MW                    | 2018 (Planed) |

| Zhangjiakou DC<br>grid Demo Project     | 4                                         | VSC               | ±500kV/3000MW                    | 2018          |

Table 1-1

LIST OF MULTI-TERMINAL HVDC (MTDC) SYSTEM PROJECTS

4

The first two commissioned MTDC systems (*i.e.* the connection between Italy, Corsica and Sardinia and the connection from Hydro-Quebec to New England) are all LCC based and have three terminals in operation. There are also LCC based bipolar HVDC schemes (*i.e.* Nelson River HVDC System and Pacific DC Intertie) that are able to operate in a multi-terminal mode. Another LCC-HVDC grid will be built in India. This 1,728 km-long HVDC link will operate with an ultra-high DC voltage (*i.e.*  $\pm$ 800kV) and be able to deliver 6000MW of hydroelectric power from the country's northeast region to the city of Agra.

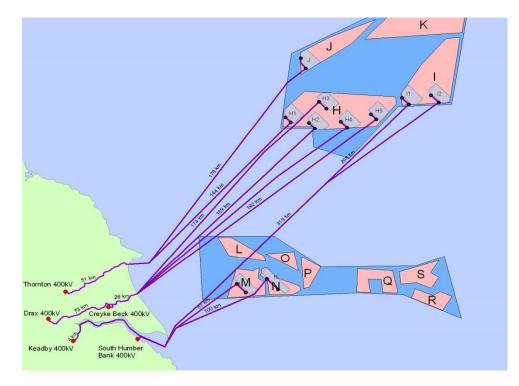

However, it appears that future DC grids for offshore transmission will be based on VSC due to its superiority over LCC. The first VSC based MTDC system is the Shin Shinano 3 terminal VSC Back-to-Back (B2B) system which was commissioned in Shin Shinano substation in Japan, 1999 [19]. This system interconnects the country's two main power grid sections which operate with different frequencies (*i.e.* east power grid: 50Hz, west power grid: 60Hz). However, this 3-terminal VSC-B2B system may not present a HVDC grid due to its small rating and absence of transmission lines. It then has been more than a decade until the commission of the first grid-level VSC-MTDC system (see Fig 1.3 (a)).

Fig 1.3 VSC based MTDC systems projects: (a) Nao'ao MTDC, (b): Zhoushan MTDC Interconnection, (c): South-West Link [20], (d): Tres amigas superstation [21]

ARDIFF NIVERSITY ARDYDE ENERGY

The Nao'ao 3-terminal VSC-MTDC system was built by China Southern Power Grid in 2013 for integrating the offshore wind power from the Nan'ao Islanded [22]. A total length of  $40.2\times2$  km DC cables has been used for connecting the 200 MW converter at the mainland to the 100 MW converter at Jingniu and the 50 MW converter at Qingao. A forth converter station rated at 50 MW will be built at Tayu in the near future. In 2014, the State Grid Corporation of China completed the first 5-terminal HVDC grid (*i.e.* Zhoushan MTDC Interconnection) project [23] to meet the increasing demand of power delivery to the Archipelago of Zhoushan. This HVDC grid is interconnected by a total length of  $129\times2$  km submarine cables and  $11.4\times2$  km underground cables. The 400 MW converter at Dinghai acts as rectifier delivering power to the other converters which operate as inverters. In the event of the outage of converter at Dinghai, the 300MW converter at Daishan will act as a rectifier and continue the power delivery to the three 100MW converters at Qushan, Yangshan and Sijiao.

In Europe, the first VSC based MTDC system is most likely to be the "South-West Link" project (see Fig 1.3 (c)) which is a key part of the development of the Swedish Transmission System Operator (TSO) Svenska Kraftnät. In Phase One of this project, two independent symmetric monopole HVDC connections (each of  $\pm 300$ kV/700MW) are being built in parallel to link the Barkeryd station with the Harva station. In Phase Two of this project, the HVDC system will be extended, connecting to the Tveiten in Norway to create a 3-terminal HVDC grid.

Moreover, in United States of America, a 3-terminal VSC based DC hub – "Tres Amigas superstation" (see Fig 1.3 (d)) will also be built to connect three U.S. asynchronous power grids: eastern (Southwest Power Pool), western (Western Electricity Coordinating Council) and Texas (Electric Reliability Council of Texas) networks.

#### **1.3 TECHNICAL CHALLENGES**

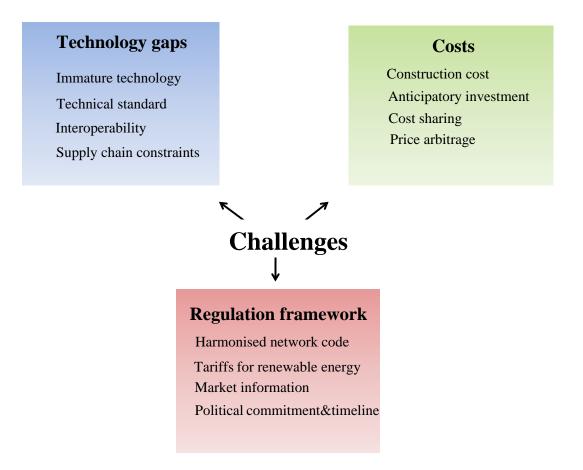

Small scaled HVDC grids have become realistic while much more efforts are needed for overcoming the challenges towards building large HVDC grids (*e.g.* DC supergrid). The Seventh Report [24] provided by the Energy and Climate Change Committee divided these challenges into three aspects: technology, cost and regulation (as summarised in Fig 1.4). This section will discuss the technology gaps.

Fig 1.4 Challenges towards a large HVDC grid

Both academia and industry should cooperate on closing the technology gaps. There are still immature technologies including DC circuit breakers, high rating HVDC cables, and HVDC grid control and protection algorithms which necessitate further development [24].

DC-CBs should be designed to block DC faults at very "low inertia" HVDC grids and in a few milliseconds. There has prototype hybrid DC-CBs been developed which can interrupt a fault current of 3 kA in 2.5 ms [25] whilst work is ongoing to make DC-CBs commercially available.

The development of HVDC cables for bulk power transmission at high voltages of 500 kV and above is ongoing. However, this is not seen as significantly problematic and recently a test extruded HVDC cable system has reached a voltage rating of 525 kV with its power rating up to 2.6 GW [26].

Research on HVDC grid control is also ongoing to overcome challenges including regulation of DC grid power flow and providing frequency support for AC system. Moreover, interests are also shown in developing new equipment for flexible controlling DC power flow in a future HVDC grid.

The design of HVDC grid protection could face many challenges in terms of fault detection and discrimination. Proposed algorithms of HVDC grid protection should be able to very fast detect any DC fault at any locations and make sure the DC-CBs operate correctly (*i.e.* only DC-CBs at the faulted section open by the end of a fault event).

Common technical standards should be established to (at some level) standardise the specification of HVDC equipment from different manufactures. This will ensure all equipment can operate together and be compatible with future DC supergrid initiatives. Moreover, this could potentially bring down the overall cost of forming a DC supergrid.

### **1.4 RESEARCH OBJECTIVES**

This thesis aims to contribute in two key research subjects: HVDC grid control and HVDC grid protection. The detailed of research objectives are outlined as:

- To design the **control algorithm of AC/DC converters** within a HVDC grid. The alternative DC voltage droop control was developed with which converters share the responsibility of control of DC voltages. The interaction between converters with differing operating modes was also studied via digital simulation.

- To develop a **4-terminal HVDC test rig** (physical analogue model) for further developing and validating the proposed alternative DC voltage droop control method. The experimental results were compared respectively to the results obtained by digital simulation which show good agreement.

- To investigate the impact of integrating DC Power Flow Control Devices (DC-PFC) into a HVDC grid. This was achieved by evaluating the influence of changing control orders of DC-PFCs to DC system power flow. Coordination of control between DC-PFCs and converters was also established for maximising the offshore wind power delivery.

- To develop the **protection strategy for HVDC grid** acknowledged as Open Grid. The DC grid protection has to be extremely fast for fault isolation. Therefore, fast tripping logic based on local measurements of each DC-CB was proposed to meet this requirement. Method for discriminating fault section from healthy circuits was also developed and validated.

#### **1.5 THESIS STRUCTURE**

This thesis consists six chapters.

<u>Chapter 2</u> gives a literature review of the major technologies toward a HVDC grid, including converters, transmission lines and DC-CBs. Introduction of different types of converters are presented while the Modular Multi-Level Converters (MMC) are highlighted. The generic control and modulation of individual MMCs are discussed in detail. The development of both OHLs and Cable are then presented. Moreover, the protection of HVDC is described. Different types of DC circuit breakers and their working principles are introduced.

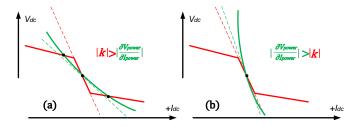

**Chapter 3** presents the development of alternative converter control (ACC) for HVDC grids. The chapter starts with the review of the control requirements of HVDC grid and the existing methods for HVDC grid control. The concept of ACC and its advantages are then introduced. The alternative droop characteristics are developed within the ACC. Proper use of the alternative droop characteristics allows precise converter current regulation during normal operation while stabilises DC voltage during power disturbance. As such, the guidance of how to select droop characteristics is provided based on mathematical analysis of interactions of different control characteristics. Studies in this chapter also uncover the potential risk of having multiple cross-over in control characteristics. The design of values of droop characteristics is thus discussed to avoid the multiple cross-over. The tests of ACC using different simulation tools will be presented in Chapter 4.

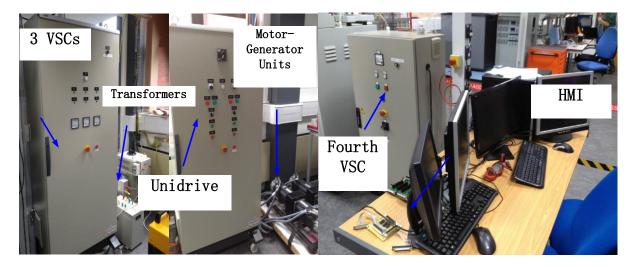

<u>Chapter 4</u> describes the implementation of ACC that has been proposed in Chapter 3 on a 4-terminal HVDC test rig. The set-up of this test rig is presented in detail. The effectiveness of using the alternatively droop (developed within ACC) to reduce the current error of converters is shown. The effects of multiple cross-overs in the static characteristics are also validated on the test rig. Comparisons were performed between the experimental results and the results obtained from digital simulation using PSCAD/EMTDC.

<u>Chapter 5</u> describes the optimisation of wind power delivery by adjusting the control parameters of both DC-PFCs and converters. The DC power flow expression for a HVDC grid with DC-PFCs is shown. The expression considers both the change of control orders for DC-PFCs and converters under the conventional droop control introduced in Chapter 3. Method for optimising power flow has been developed. The effectiveness of the proposed method is validated via case studies with different conditions of wind generation. The

curtailment of wind power and the DC line losses are can be reduced by the re-dispatching of optimised control orders.

<u>Chapter 6</u> describes the development and evaluation of Open Grid protection strategy in DC Grid. Alternative to the conventional protection method introduced in Chapter 2, the Open grid changes the protection sequence orders. With this strategy, each DC-CB trips rapidly based on local voltage and current without discrimination and then DC-CBs re-close to discriminate at healthy circuits. The analysis of the fault behaviours in events of a DC fault is given. Different DC fault characteristics have been described. Based on that, detailed protection algorithms are developed to meet DC protection requirement with different fault types, locations and fault impedances. Digital simulations are performed to validate the robustness of the Open Grid. The results show that the Open Grid can successfully detect and discriminate DC faults in different fault conditions in a meshed DC grid.

<u>Chapter 7</u> outlines the conclusions from the work presented in the thesis. Future work for the development of HVDC control and protection is discussed.

### **1.6 LIST OF PUBLICATIONS**

The following papers were written up based on work done within the Ph.D. study period:

#### JOURNAL PAPERS

- C. Barker, R. Whitehouse, J. Liang and S. Wang, "Risk of Multiple Cross-Over of Control Characteristics in Multi-terminal HVDC", *Generation, Transmission & Distribution. IET*, vol. 10, no. 6, pp. 1353–1360, 2016

- S. Wang, J. Guo, C. Li, S. Balasubramaniam, R. Zheng and J. Liang. "Coordination of DC Power Flow Controllers and AC/DC Converters on Optimising the Delivery of Wind Power", *Renewable Power Generation*, *IET*, vol. 10, no. 6, pp. 815 – 823, 2016

- S. Wang, J. Liang, A. Wen and C. Feng, "Cost and Benefits Analysis of VSC-HVDC Schemes for Offshore Wind Power Transmission", *Automation of Electric Power Systems*, vol. 37, no. 13, pp.36-43, 2013

- H. Li, T. An, S. Wang, J. Liang, "Analysis Algorithm for DC Grid with DC Power Flow Controllers", *Southern Power System Technology*, vol. 10, no. 5, pp. 80-86, 2016 (in Chinese)

5. S. Wang, R. Zheng, J. Liang, A. Adamczyk, C. Barker, R. Whitehouse "Evaluation of Open Grid protection strategy in DC Grid" [*full paper sent to GE Grid Solution for review, will be sent to Power Delivery, IEEE*].

#### **BOOK CHAPTERS**

C. Feng, S. Wang and Q. Mu, "DC Grid Power Flow Control Devices", Chapter in HVDC Grids for Transmission of Electrical Energy: Offshore Grids and a Future Supergrid, Wiley, 2016. ISBN: 978-1-118-85915-5.

#### **CONFERENCE PAPERS**

- C. Li, S. Wang, J. Liang, "Current control strategy of MMC-based DC-DC converter for commutation failure mitigation using current deviation detection method in LCC-HVDC systems", the 13<sup>th</sup> AC and DC Power Transmission International Conference, Manchester, UK, 2017 [full paper accepted by November, 2016]

- R. Zheng, S. Wang, J. Liang, G. Li, "Selection of TCSC parameters to mitigate SSR problems", the 13<sup>th</sup> AC and DC Power Transmission International Conference, Manchester, UK, 2017 [full paper accepted by November, 2016]

- C. Barker, R. Whitehouse, S. Wang and J. Liang, "Risk of Multiple Cross-Over of Control Characteristics in Multi-terminal HVDC", 11<sup>th</sup> AC and DC Power Transmission International Conference, Birmingham, UK, 2015.

- 10. S. Wang, C. Barker, R. Whitehouse and J. Liang, "Experimental Validation of Autonomous Converter Control in a HVDC Grid", 16<sup>th</sup> Power Electronics and Applications European Conference, Lappeenranta, Finland, 2014.

- 11. B. Shen, S. Wang, L. Fu and J. Liang, "Design and Comparison of Feasible Control Systems for VSC-HVDC Transmission System", 2<sup>nd</sup> Artificial Intelligence International Conference, Modelling and Simulation (AIMS), Madrid, Spain, 2014

- S. Wang, J. Liang and J. Ekanayake, "Optimised topology design and comparison for offshore transmission", 47<sup>th</sup> Universities Power Engineering International Conference, London, UK, 2012.

## **1.7 PARTICIPATION IN PROJECTS**

Within the framework of the doctorate degree, the author participated in the following projects:

- Alstom Grid UK Ltd project: Work package A1- DC Grid Control, Work package A2-DC Grid Protection

- 2. NGT project: Test of multi-terminal VSC HVDC control strategies by means of an analogue testing rig

- 3. Quzhou Hang Yong Transformer Corporation: Power Flow Control and Anti-Fault Strategies of DC grids

# **CHAPTER 2**

# **TECHNOLOGIES FOR HVDC GRIDS**

## 2.1 INTRODUCTION

The development of HVDC grids has taken huge steps forward since the first LCC-HVDC link was commissioned in 1954 [27]. Some important milestones in the development of the DC transmission technology are listed in [27].

In Europe, HVDC grids are required to facilitate the connection of offshore wind farms to land and interconnection of the power grids of different countries. This chapter reviews the major technologies for developing an HVDC grid, including the AC/DC converters, DC transmission lines and DC-CBs.

## 2.2 AC/DC CONVERTERS

### **2.2.1 LINE COMMUTATED CONVERTERS**

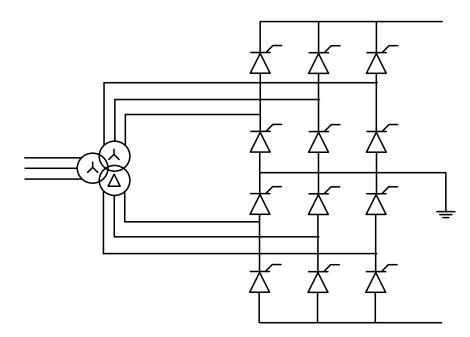

LCC-HVDC has become a mature and cost-effective technology for bulk DC power transmission. The most common layout of a LCC is given in Fig 2.1.

Fig 2.1 Typical layout of a LCC

The thyristor valves are arranged in two Graetz bridges [28] for AC to DC conversion in order to cancel the 6-pulse harmonics on both the AC and DC sides [29]. Only if there is a positive voltage applied between the anode and the cathode of a thyristor, the thyristor can conduct current from an AC system by having a firing pulse which is generated by synchronising the AC system. This firing pulse can be delayed from an instant when voltage starts to become positive. This is also known as the delay angle. The change of the delay angle will generate different average DC voltages (*i.e.* an increase of delay angle leads to a decrease of average DC voltage can be reversed (when delay angle > 90°) to change the direction of power delivery while the current flow is unidirectional due to the physical limit of a thyristor.

### 2.2.2 TWO-LEVEL VOLTAGE SOURCE CONVERTERS

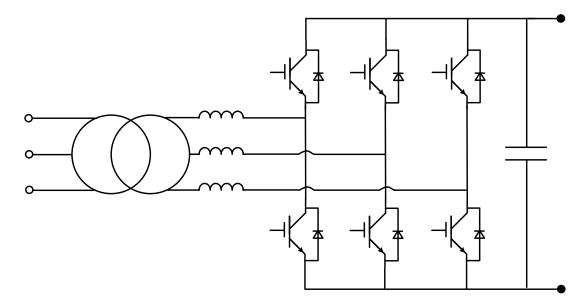

VSC technology is been actively developed for HVDC. Early VSC-HVDC links (*e.g.* Gotland HVDC Light [30]) were built based on Pulse Width Modulation (PWM) controlled two-level VSCs (see Fig 2.2).

#### Fig 2.2 Architecture of a 2-level VSC

Each two-level VSC has six valves that contain fully controllable switching devices (*e.g.* IGBTs in the most applications) connected in series to obtain a system-level DC voltage. These switching devices depend on a gate signal for their switching (turn on or off) operation. The gate signals can be generated using PWM technique (see Fig 2.3). Modulating the width of pulse is based on the comparison between a carrier waveform and a reference waveform. A

switching device turns on if the reference waveform ascends above a carrier waveform and vice versa. This will create an output sinusoidal waveform with high frequency harmonics. Therefore, phase reactors in combination with AC filters are needed for filtering the high frequency harmonics. Increasing the frequency of carrier waveform (*i.e.* switching frequency) will allow the use of filters with smaller sizes and thus bring down the cost of phase reactors and AC filters. However, this will simultaneously increase the switching losses. A typical switching frequency of 1 kHz to 2 kHz is used in most two-level VSC-HVDC practice [31] as a trade-off of harmonics and switching losses.

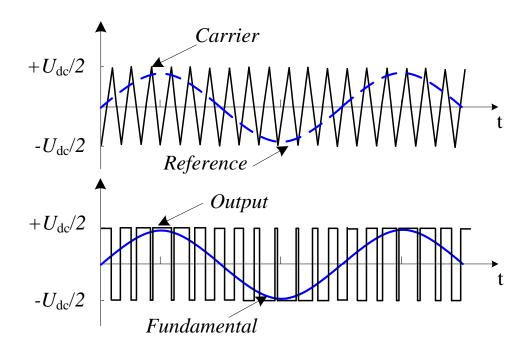

Fig 2.3 Sinusoidal Pulse Width Modulation

### 2.2.3 MULTI-LEVEL MODULAR CONVERTERS

The MMC was used as a utility STATCOM [32] and has soon become a viable solution for VSC-HVDC network since 2010 when the first MMC based HVDC link (*i.e.* Trans Bay Cable Project) was commissioned [33].

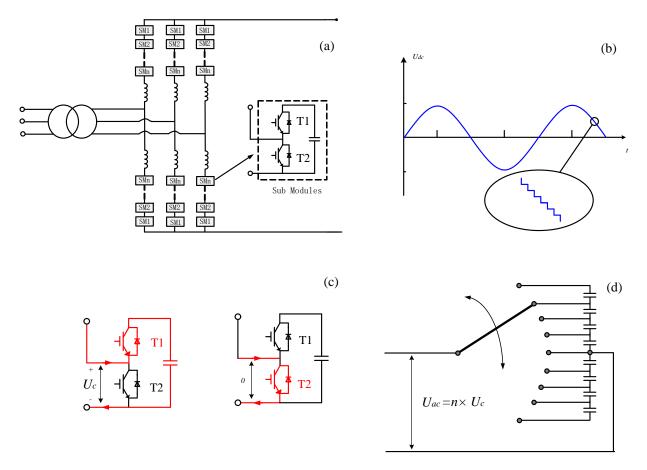

Within an MMC, each valve (see Fig 2.4 (a)) has hundreds of sub-modules (SMs) connected as "chain links" where the switching of each SM is individually controlled to produce a sinusoidal voltage (see Fig 2.4 (b)).

The Fig 2.4 (c) and Fig 2.4 (d) present the switching of IGBT and the establishment of AC voltage. A SM is composed of one half bridge (with two IGBTs) and a capacitor (see Fig 2.4 (c)). By closing the upper IGBT (T1) and opening the lower IGBT (T2), the capacitor

CARDING EINSTITUTE OF ENERGY

can be inserted into the circuit. The output voltage of the SM will be the voltage across the capacitor (*i.e.*  $U_c$ ).

To the contrary, bypassing the capacitor is achieved by opening T1 while closing T2. The output voltage of the SM then becomes zero.

Subsequently, the AC voltage is developed in small steps by inserting or bypassing different number of SMs (see Fig 2.4 (d)). This can significantly improve the power quality while reduce the switching power losses of AC/DC conversion.

Fig 2.4 Architecture of a MMC and the output AC waveform

### 2.2.4 BASIC CONTROL OF MMCS

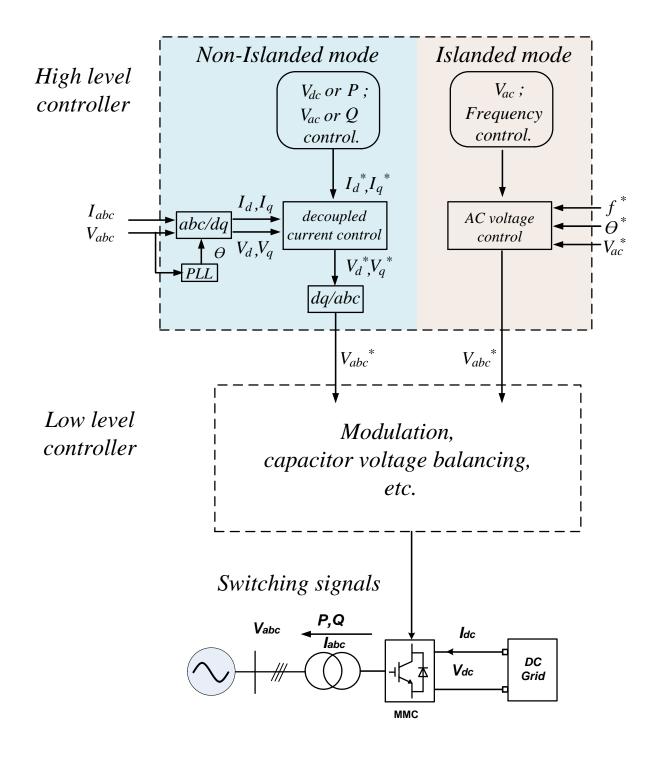

An MMC has a generic control structure (see Fig 2.5) [34] including a high level controller and a low level controller.

Fig 2.5 Hierarchical control structure of an MMC

#### A. High Level Controller

The high level controller of an MMC can either operate in a non-islanded mode or an islanded mode. The selection of operation modes is determined by the type of AC system that the MMC is connected to.

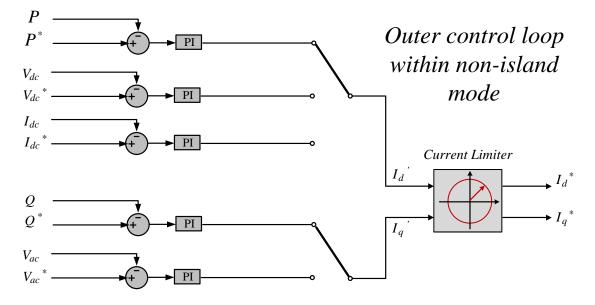

The **non-islanded mode** is used when an MMC converter is connected to an AC system with active synchronous generation (*e.g.* strong AC grid). The standard hierarchy of the non-islanded mode is shown in Fig 2.6 and Fig 2.7.

Fig 2.6 shows the outer control loop of the non-islanded mode where two variables can be regulated at a time. For example, it can control the active power (P) and reactive power (Q) simultaneously. A simple approach is to use PI control units to regulate both variables respective to the reference orders ( $P^*$  and  $Q^*$ ) given by a system operator. This will generate two current references (*i.e.*  $I_q^*$  and  $I_d^*$ ) which are further sent to the "decoupled current control" block as shown in Fig 2.5.

Fig 2.6 Outer control loop for non-islanded control mode

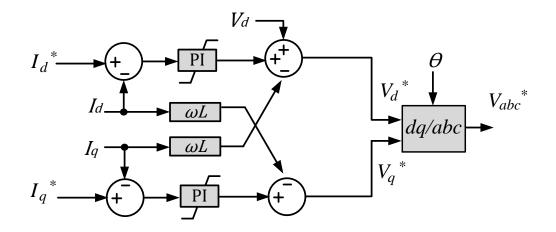

The "decoupled current control" block is designed for regulating the direct and quadrature components of the AC current (*i.e.*  $I_d$  and  $I_q$ ). The measurements of AC current are transformed into direct-quadrature frame using the *abc* to *dq* transformation (*i.e.* park transformation) as shown in Fig 2.5. A phase lock loop (PLL) is required for locking the voltage at the AC grid and generating the reference angle ( $\Theta$ ) for *abc* to *dq* transformation.

Currents  $I_d$  and  $I_q$  are then regulated regarding to the current reference given by the outer control loop (see Fig 2.7). This will create the AC voltage references in *d*-*q* frame (*i.e.*  $V_d^*$  and  $V_q^*$ ) which are then transferred back to *abc* frame.

Fig 2.7 Inner decoupled current control for non-islanded control mode

Alternatively, the **islanded mode** is used for converters connected to very weak AC systems. Two typical weak AC systems are wind parks and islanded loads. For example, an offshore wind parks consist of arrays of wind turbines connected to an AC grid with practically no local load. For these schemes the HVDC grid constitutes the only way of evacuating the generated power out of the system and as such the frequency of offshore AC voltage must be maintained within an acceptable range to keep the offshore power balanced (*i.e.* generated wind power matches the power flow through converter plus the power losses). Similarly, in cases the HVDC grid connected to islanded loads, an AC voltage must be established and the power in-feed into the islanded must match the load requirements to maintain the frequency of AC voltage. Therefore, in either case an AC voltage should be established with its frequency regulated at acceptable values. This is achieved by operating the MMCs in the islanded mode.

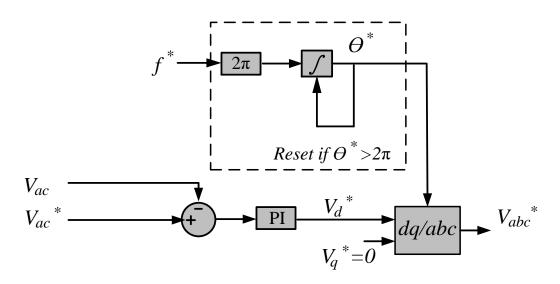

Fig 2.8 shows the control blocks with the islanded mode. Its inputs include an AC voltage amplitude reference  $(V_{ac}^*)$ , a measured AC voltage  $(V_{ac})$  and a frequency reference ( $f^*$ ). The PI controller eliminates the steady state error between  $V_{ac}^*$  and  $V_{ac}$  and generates a *d*-axis voltage reference  $(V_d^*)$  while the *q*-axis voltage reference  $(V_q^*)$  can be set to zero directly as no variable needs to be controlled via the *q*-axis in the islanded mode. The angle reference for *dq* to *abc* transformation is created by an independent oscillator. This is essentially different to that in the non-islanded mode where the angle reference is generated by a PLL locking the voltage at an active AC source. The final output of the islanded mode is a voltage reference in *abc* frame ( $V_{abc}$ ).

Fig 2.8 Generation of AC voltage reference with islanded control mode

#### B. Low level controller

Both the non-islanded and islanded control mode output an AC voltage reference for the lower level controller. The responsibility of low level controller is then to generate switching signals for IGBTs and hence establish a waveform of AC voltage following its reference.

The lower level controller generally includes two functions: 1) Modulation; 2) Capacitor Voltage Balancing (CVB).

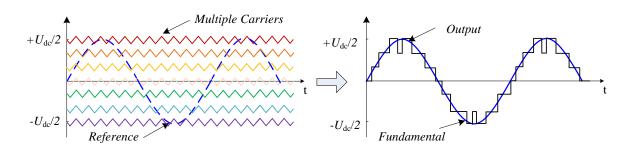

The objective of modulation is to determine the number of inserted SMs in both upper arms and low arms within a MMC. Proposed techniques for the modulation include the PMW based methods [35] and the Nearest Level Control (NLC) [36]. Fig 2.9 shows an example of Phase Disposition Modulation (PD-PWM). The AC voltage reference generated by high level controller is compared with multiple triangular carriers which are shifted in amplitude. One SM of MMC will be inserted if the reference value is larger than a carrier and vice versa. The final output of MMC will be a sinusoidal waveform with much lower frequency harmonics (compared to that with 2-level PWM). In fact, manufactured MMCs for HVDC applications have hundreds of levels and hence the output AC voltage has almost a pure sinusoidal waveform with little harmonics.

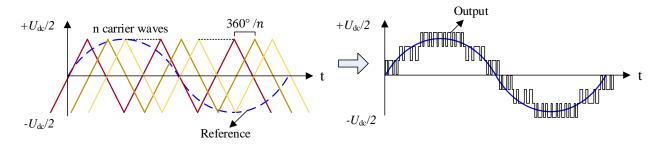

An example of using Phase Shift Modulation (PS-PWM) is also given in Fig 2.10. There are a number of *n* triangular carriers which are shifted in phase with a step of  $360^{\circ}/n$ . These triangular carriers are then compared with the AC voltage reference to determine the number of inserted SMs.

Fig 2.9 Phase disposition modulation

Fig 2.10 Phase shift modulation

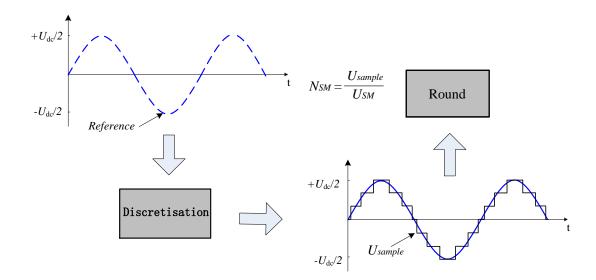

#### Fig 2.11 Nearest level control

Alternatively, the NLC can be used for the modulation (see Fig 2.11). With this method, the AC voltage reference will firstly be discretised and output a reference  $U_{sample}$ . The number of inserted SMs ( $N_a$ ) is then estimated by dividing  $U_{sample}$  with the average capacitor voltage of SMs ( $U_{SM}$ ). The calculated  $N_{SM}$  is usually not an integer number and hence rounding is needed to obtain an exact number for the inserted SMs.

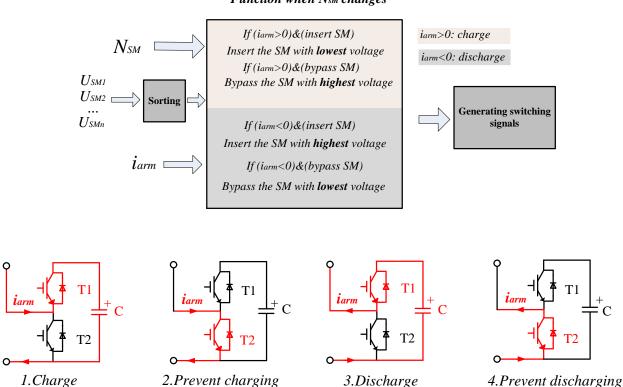

#### Function when Nsm changes

#### Fig 2.12 Control of CVB

The obtained number of inserted SMs will further be sent to another important block for CVB. The control of CVB aims to stabilise the capacitor voltage of each SM around the average value ( $U_{SM}$ ) and hence prevent the capacitor voltage from diverging. Different algorithms for CVB have been proposed in [37] to [41] while a conventional approach [41] is shown in Fig 2.12.

The input into the control block including the requested number of inserted SM ( $N_{SM}$ ), the direction of arm current ( $i_{arm}$ ) and the SM capacitor voltages which are sorted from the highest value to the lowest one. The CVB only functions at the instants of  $N_{SM}$  changing. For example, when  $N_{SM}$  increases by 1, the CVB decides which SM should be inserted and conversely, when  $N_{SM}$  decreases by 1, the CVB determines which SM should be bypassed.

The decision of which SM should be inserted or bypassed is made based on the four operating states of SMs. When the arm current feeds into a SM (*i.e.*  $i_{arm} > 0$ ), a SM can either be 1): inserted to charge its capacitor (*C*) or 2): bypassed to prevent its capacitor from charging. In order to balance the capacitor voltage, the SM with the lowest capacitor voltage will be inserted based on request and the capacitor voltage will be charged to higher values. Similarly, if bypass operation is requested (when  $i_{arm} > 0$ ), the SM with the highest capacitor

voltage will be bypassed to prevent its capacitor voltage to further increase. In contrast, when the arm current flows out of a SM (*i.e.*  $i_{arm} < 0$ ), a SM can either be 3): inserted to discharge its capacitor or 4): bypassed to prevent its capacitor from discharging. Then in cases that  $i_{arm}$ < 0, if the  $N_{SM}$  increases, the SM with highest capacitor voltage will be inserted while if the  $N_{SM}$  decreases, the SM with lowest capacitor voltage will be bypassed.

The operation with this CVB algorithm is summarised in Table 2-1.

| Action according to the change of $N_{SM}$          | <i>i<sub>arm</sub></i> > <b>0</b> (charge) | <i>i<sub>arm</sub></i> < 0 (discharge)   |

|-----------------------------------------------------|--------------------------------------------|------------------------------------------|

| N <sub>SM</sub> increases (insertion of SM needed ) | Insert SM with lowest capacitor voltage    | Insert SM with highest capacitor voltage |

| N <sub>SM</sub> decreases (bypass of SM needed)     | Bypass SM with highest capacitor voltage   | Bypass SM with lowest capacitor voltage  |

Table 2-1 Summary of the operation with CVB algorithm

In addition to the above control functions, a controller for circulating current suppression can be implemented to further improve the performance of MMCs. Within an MMC, three phase units are connected in parallel at its DC side. The charging (and discharging) of SM capacitor voltages in these phase units will cause asynchronous voltage ripples and hence create small inequality between the generated phase voltages [42]. This will further create a circulating current. The circulating current is in negative sequence and oscillates with the double fundamental frequency of the AC system. It only circulates within the phase units and does not affect either the DC or AC side of the MMC. However, the presence of circulating current:

- increases the power loss of converters

- distorts arm current

- increases the rated current of IGBTs

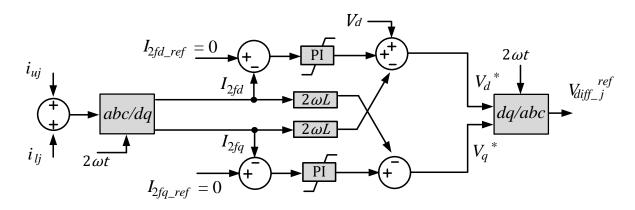

A controller can be developed to suppress the circulating current as shown in Fig 2.13 [43]. The inputs are the measured current of upper  $(i_{uj})$  and lower  $(i_{lj})$  arms. The generated current signal  $i_{zj}$  is composed of the circulating current and one third of the converter DC current. In order to suppress the circulating current, the  $i_{zj}$  needs to firstly be transferred into

the *d-q* frame (to generate the direct  $i_{2fd}$  and quadrature components  $i_{2fq}$ ) with an angle reference of the double fundamental frequency (2  $\omega t$ ) as the main frequency of circulating current is the second harmonic of the AC system. Then by setting the references (*i.e.*  $i_{2fd_ref}$  and  $i_{2fq_ref}$ ) of  $i_{2fd}$  and  $i_{2fq}$  to zero while using PI controllers to eliminate the errors between the references and measured currents, the circulating current can be suppressed. The final output is the demanded voltage reference  $V_{diff_j}^{ref}$  which can be added to the AC voltage reference  $V_{abc}^*$  before modulation.

Fig 2.13 Circulating current suppression control

## 2.3 HVDC TRANSMISSION LINES

HVDC transmission can make use of OHLs and cables.

#### A. Overhead line

OHLs are the most economical means for bulk power over long distance due to its low installation cost. The transmission capacity of an OHL is limited by the thermal rating of sag and the annealing temperature of the conductor. The conducting material of OHLs can be either copper or aluminium. The density and hence the weight of aluminium is lower than those of copper. Moreover, aluminium has lower cost per kilogram. These make the aluminium the preferred choice [44].

To date, the use of OHLs in HVDC projects has reached a voltage and power rating reach at 1100 kV and 10 GW respectively [45]. The applications of OHLs in HVDC practice are similar to those in AC systems. There is also no significant difference in the design of towers for OHLs in HVDC and AC systems. However, HVDC OHLs have higher

transmission capacity. It is studied that three-phase double circuit AC OHLs can have 40% to 80% more transmission capacity when they are converted and used as HVDC OHLs [44].

#### B. HVDC cable

HVDC cables can be used in submarine and underground applications. For example, they can be used for connecting offshore wind farms to inland load centre and also power transmission over long distance in the sea where the use of OHLs is no longer feasible. Moreover, small right-of-way of HVDC cables makes them ideal for being used in land power transmission including city areas.

HVDC cables consist of a conductor core, semiconductor screen, main insulation, sheath, armouring, and related accessories. The different characteristics of dielectric materials lead to different electrical, mechanical and thermal performance. HVDC cables are categorised into five types according to the dielectrics [46][47] as oil-filled DC cable, mass-impregnated cable (MI), extruded DC cable, gas insulated cable and superconducting cable. With the practical HVDC projects, the MI cables (see Fig 2.14) and extruded cables (see Fig 2.15) have been mainly used.

MI cables are acknowledged as "solid" insulation system since there is no free oil contained in the cable. The insulation of MI cables is made of mass-impregnated and non-draining paper. High-density papers ( $\approx 1000 \text{ kg/cm}^3$ ) can provide higher dielectric properties. The cable length in principle is unlimited due to no external pressure and oil feeding request.

As a proven reliable cable technology, MI cables have been used in HVDC applications for over 60 years. Recently, new insulation utilises laminated polymeric film and paper which increases the maximum conductor temperature of MI cables from 55 °C to 85 °C. The MI cable can hence be sized at higher rating. Such kind of MI cables has already been applied in practice like the Westernlink project where the MI cables are rated at 600 kV and 2200 MW [46].

Fig 2.14 Mass-impregnated cables [47]

Fig 2.15 Extruded cables

Extruded cables are relatively new developments. Its major insulation material is crosslinked polyethylene (XLPE). In 2002, the first extruded cables were developed in a laboratory in Japan. To date, this cable technology has been applied in practical projects with DC voltage rated up to 320 kV and active power rated up to 1000 MW. Moreover, ABB has claimed that the first 525 kV, 2600 MW extruded cable system has been developed [26].

The extruded cables have advantages over MI cables as listed below [49]:

• Have higher maximum conductor temperature, giving a more compact cable for the same power rating;

• Lighter moisture barriers can be used which makes the cable lighter;

• Joining of extruded cables is much simpler and requires less skill.

However, the extruded cables are vulnerable to voltage polarity reversal which will enhance the electric field and cause permanent failure in the insulation of extruded cables. Therefore, the extruded cables are used in VSC based HVDC networks which operations without the requirement of voltage polarity reversal. LCC-HVDC links still utilise MI cables since the change of power flow direction requires the voltage polarity reversal.

## 2.4 DC CIRCUIT BREAKERS FOR HVDC GRID PROTECTION

## 2.4.1 HVDC NETWORK PROTECTION

The protection of HVDC networks remains a main challenge for developing HVDC grids. A DC network has in general low inductance. Under the presence of a DC fault, a DC network will exhibit a higher fault current rise time and a faster fault propagation time when compared to an AC fault occurring in an AC network where the propagation of fault current is limited by the relatively large system inductance. Moreover, the DC fault current does not have a natural zero-crossing. These could bring difficulties in HVDC network protection, particularly HVDC grids.

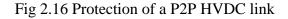

To date, the protection of P2P VSC-HVDC links has become relatively mature while new protection components, such as DC-CBs, will be needed for protecting HVDC grids. This is descripted in detail as below.

#### A. Point to point HVDC links

Fig 2.16 shows a typical protection circuit for a P2P HVDC link using VSCs, AC-CBs and DC disconnectors.

Following a DC fault, DC voltage will rapidly decrease, resulting in a fast increase of DC current. Current (and voltage) sensors located at each VSC station are employed to detect the first wave-front of fault current (and voltage). An overcurrent and undervoltage criterion is used to block the IGBTs within the VSCs. As a result the fault current will flow from the

#### CARDIFF E INSTITUTE OF ENERGY

AC sources to the fault location via the diodes of the IGBTs (assuming 2-level VSCs or half bridge MMCs are used). Fault clearance is achieved by the AC-CBs, which open their own mechanical breakers at the zero-crossing of AC currents to quench the arc between two contacts. The DC disconnectors will ultimately open once the fault current is drawn to zero so that the faulted line or cable is isolated.

The protection strategy described above relies on mature technologies and therefore has a low investment cost. However, the slow operation of AC-CBs and the inevitable shutdown of the entire system makes it unsuitable to protect HVDC grids.

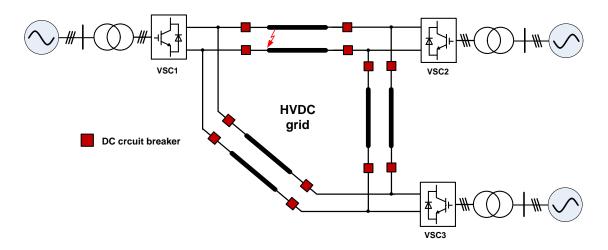

#### B. HVDC grids

More HVDC grids are likely to be built through the integration of existing P2P-HVDC links in the future. Fig 2.17 shows a simple MTDC grid consisting of three terminals and a meshed configuration to provide redundancy for system operation. DC power can flow through alternative paths in the events of failure or maintenance of a DC link.

#### Fig 2.17 Protection of a HVDC grid

As in a P2P HVDC link, DC faults will rapidly propagate across an entire HVDC grid, resulting in a DC voltage drop and a DC current increase. An effective protection system should be able to discriminate and isolate the fault and then disconnect the faulted section from the rest of the healthy system so that power can still be transmitted. Therefore, the inclusion of DC-CBs at both ends of the DC links is necessary to achieve fast fault discrimination and isolation (see Fig 2.17). In the event of a fault, the DC-CBs at the faulted link can detect and isolate the fault using local measurements of current and voltage.

Notice that the main protection system of an HVDC grid should avoid the use of communication as this may cause large time delays and would require an adequate synchronisation of DC-CBs. Moreover, a fault will not only affect a specific DC line but also other sections of the network. Therefore, the protection system must be designed to discriminate the healthy circuits from the faulted section. This can be done by comparing the currents and voltages measured at the faulted lines with those of the healthy circuits. The DC-CBs located at non-faulted lines should be kept closed throughout the fault.

## 2.4.2 PROPOSED DC-CBS

The demand of HVDC grid protection becomes a key driver of developing DC-CBs. A desirable DC-CB should be able to clear a DC fault within milliseconds and hence prevent the fault from affecting the healthy circuits significantly. Furthermore, it should be reliable and not affect the normal operation of a HVDC grid (*e.g.* cause large power loss). There is no high voltage DC-CBs commercially available at present. However, several potential solutions are provided as: the mechanical resonant breakers, the full solid-state breakers and the hybrid HVDC breakers.

#### A. Mechanical resonant breakers

There are passive mechanical resonance breakers and active mechanical resonance breakers.

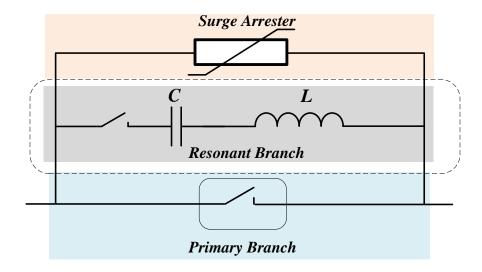

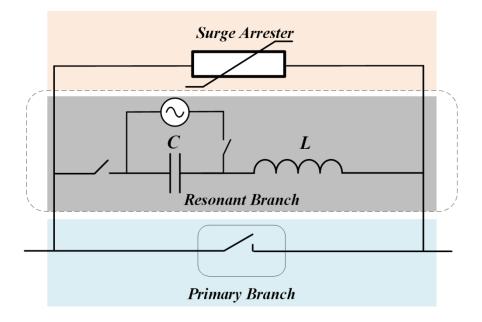

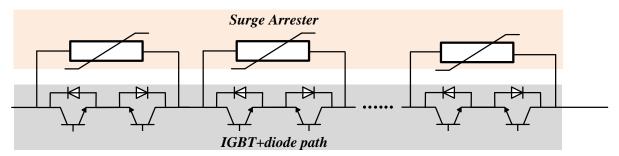

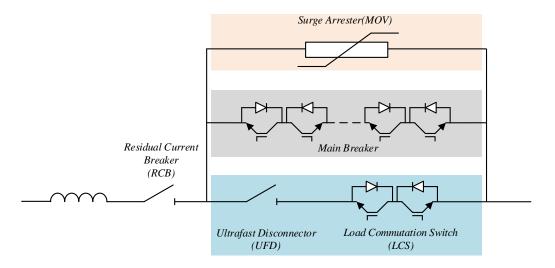

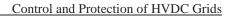

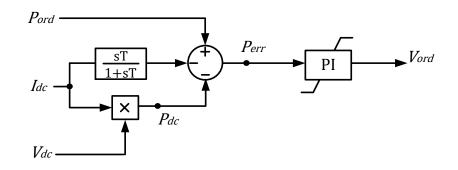

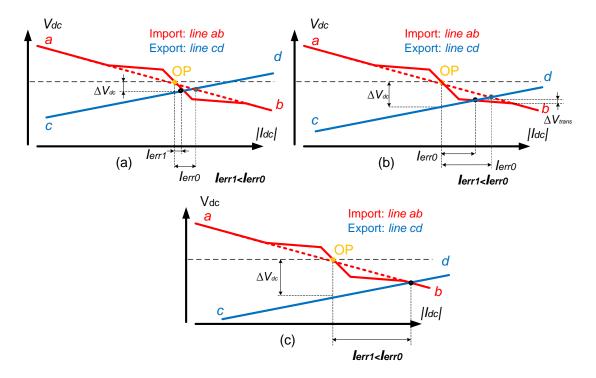

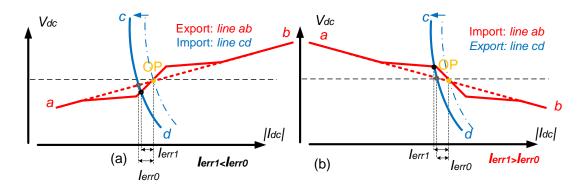

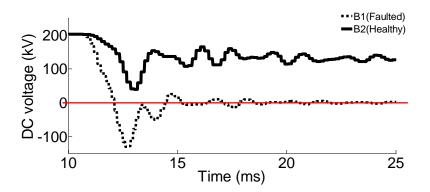

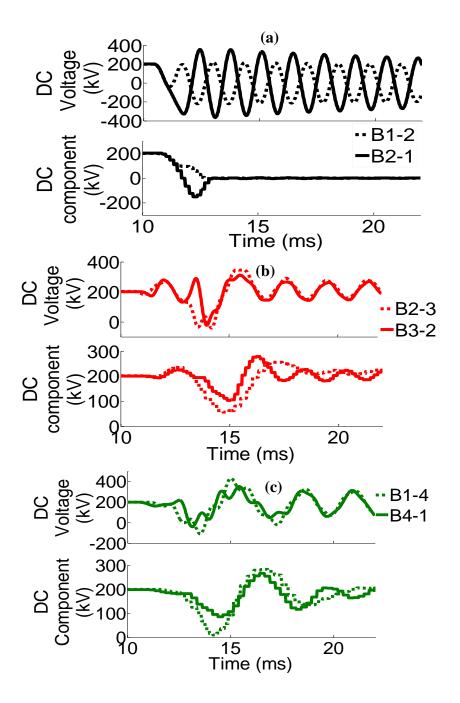

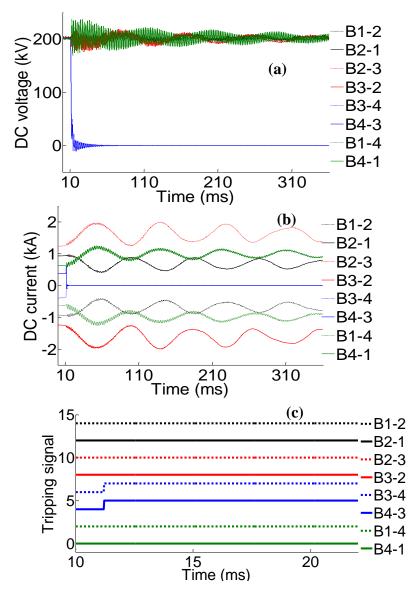

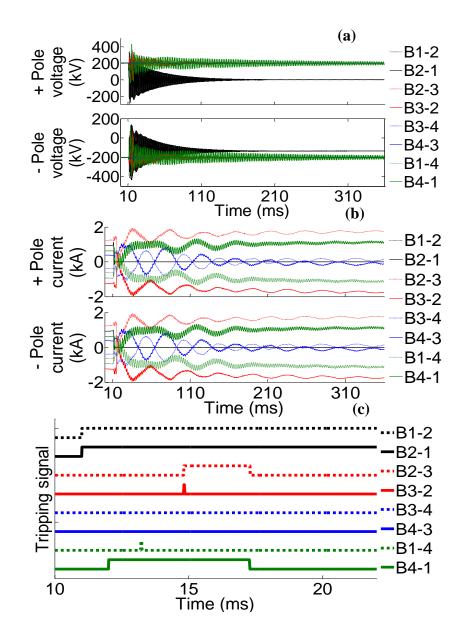

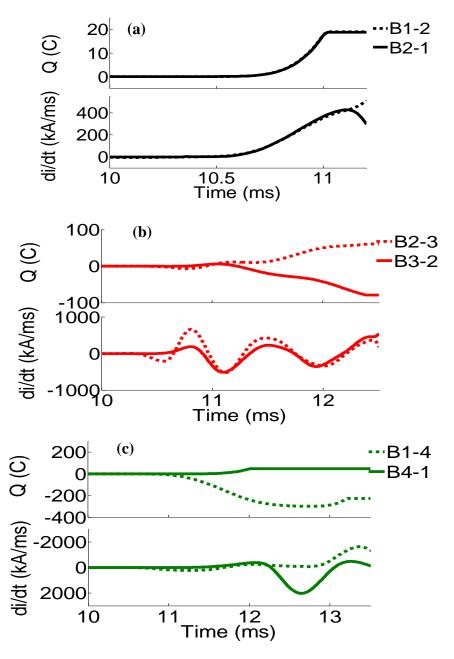

The passive mechanical resonance breakers are proposed in [50] and [51]. Fig 2.18 shows an example of a passive mechanical resonance breaker. It operates to create a current zero-crossing and hence interrupt the DC fault current using mechanical switches.