BINDING SERVICES Tel +44 (0)29 2087 4949 Fax +44 (0)29 20371921 e-mail bindery@cardiff.ac.uk

# Unified Field Multiplier For GF(p) and GF(2") with Novel Digit Encoding

Thesis by

Lai Sze Au

In Partial Fulfilment of the Requirements for the Degree of Doctor of Philosophy

Cardiff University

Cardiff School of Engineering PO Box 935, Cardiff, CF24 0YF Wales, UK

2004

(Submitted October 30, 2004)

UMI Number: U584710

### All rights reserved

### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI U584710

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

### **DECLARATION**

This work has not previously been accepted in substance for any degree and is not being concurrently submitted in candidature for any degree

Signed (Candidate)

Date

#### STATEMENT 1

This thesis is the result of my own investigations, except where otherwise stated.

Other sources are acknowledged by footnotes giving explicit references. A

Bibliography is appended.

Signed (Candidate)

Date

### **STATEMENT 2**

I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.

### **Acknowledgement**

I would like to take this opportunity, first of all, to say thank you to my supervisor, Prof. N. Burgess. Without his guidance and support, none of these would have been possible. He has always been so patient with me and I have truly learnt a lot from him.

Secondly, I would like to thank ARM Ltd. for sponsoring me. I would also like to express my appreciation to my parents, my brother and sisters for being so supportive.

Finally, big THANK YOU to my husband! Thank you for everything!

### **ABSTRACT**

In recent years, there has been an increase in demand for unified field multipliers for Elliptic Curve Cryptography in the electronics industry because they provide flexibility for customers to choose between Prime (GF(p)) and Binary  $(GF(2^n))$  Galois Fields. Also, having the ability to carry out arithmetic over both GF(p) and  $GF(2^n)$  in the same hardware provides the possibility of performing any cryptographic operation that requires the use of both fields. The unified field multiplier is relatively future proof compared with multipliers that only perform arithmetic over a single chosen field. The security provided by the architecture is also very important. It is known that the longer the key length, the more susceptible the system is to differential power attacks due to the increased amount of data leakage. Therefore, it is beneficial to design hardware that is scalable, so that more data can be processed per cycle. Another advantage of designing a multiplier that is capable of dealing with long word length is improvement in performance in terms of delay, because less cycles are needed. This is very important because typical elliptic curve cryptography involves key size of 160 bits.

A novel unified field radix-4 multiplier using Montgomery Multiplication for the use of GF(p) and  $GF(2^n)$  has been proposed. This design makes use of the unexploited state in number representation for operation in  $GF(2^n)$  where all carries are suppressed. The addition is carried out using a modified (4:2) redundant adder to accommodate the extra  $1^*$  state. The proposed adder and the partial product generator design are capable of radix-4 operation, which reduces the number of computation cycles required. Also, the proposed adder is more scalable than existing designs.

# **Contents**

| 1 | INTRO  | DUCTION                                                             | 1   |

|---|--------|---------------------------------------------------------------------|-----|

|   | 1.1    | Motivation                                                          | 1   |

|   | 1.2    | Thesis Outline                                                      | 2   |

| 2 | CRYPT  | OGRAPHY                                                             | 4   |

|   | 2.1    | Symmetric key cryptography                                          | 7   |

|   | 2.2    | DES and Triple DES                                                  | 9   |

|   | 2.3    | Other Symmetrical Block Cipher Algorithm – IDEA & AES               | 13  |

|   |        | 2.3.1 IDEA                                                          | 14  |

|   |        | 2.3.2 AES                                                           | 16  |

|   | 2.4    | Public Key Cryptography                                             | 16  |

|   |        | 2.4.1 Diffie-Hellman key agreement protocol                         | 17  |

|   |        | 2.4.2 RSA                                                           | 22  |

|   |        | 2.4.3 RSA Problem (RSAP)                                            | 25  |

|   |        | 2.4.4 Security of RSA                                               | 26  |

|   |        | 2.4.5 ElGamal                                                       | 29  |

|   | 2.5    | Comparisons: Symmetric Key Cryptography vs. Public key Cryptography | 35  |

|   | 2.6    | Elliptic Curve Cryptography (ECC)                                   | 41  |

| • |        | 2.6.1 Elliptic Curve Discrete Logarithm Problem (ECDLP)             | 42  |

|   |        | 2.6.2 Elliptic Curve Diffie-Hellman (ECDH)                          | 43  |

|   |        | 2.6.3 Elliptic Curve Digital Signature Algorithm (ECDSA)            | 44  |

|   |        | 2.6.4 ECC vs. RSA                                                   | 46  |

| 3 | FINITE | FIELD ARITHMETIC IN HARDWARE AND LITERATURE REVIEW                  | 49  |

|   | 3.1    | What is Elliptic Curve?                                             | 49  |

|   | 3.2    | Elliptic Curve Mathematical Background                              | 54  |

|   |        | 3.2.1 The order of an element                                       | 56  |

|   |        | 3.2.2 Generator                                                     | 56  |

|   |        | 3.2.3 Modular Arithmetic                                            | 57  |

|   |        | 3.2.4 Polynomial Basis                                              | 58  |

|   |        | 3.2.5 Optimal Normal Basis                                          | 59  |

|   | 3.3    | Elliptic Curve Operations                                           | 64  |

|   |        | 3.3.1 Point Addition over real number plane                         | 64  |

|   |        | 3.3.2 Point Doubling over real number plane                         | 65  |

|   |        | 3.3.3 Point Addition over GF(p)                                     | 67  |

|   |        | 3.3.4 Point Doubling over $GF(p)$                                   | 69  |

|   |        | 3.3.5 Point Addition over GF(2")                                    | 69  |

|   |        | 3.3.6 Point Doubling over GF(2 <sup>n</sup> )                       | 72  |

|   | 3.4    | ECC and Side Channel Attacks                                        | 72  |

|   |        | 3.4.1 Known ECDLP attacks                                           | 72  |

|   |        | 3.4.2 Side channel attacks                                          | 77  |

|   |        | 3.4.3 Simple Side Channel Analysis                                  | 78  |

|   |        | 3.4.4 Differential Power Analysis (DPA) attack                      | 79  |

|   |        | 3.4.5 Countermeasure Against Side Channel Attacks                   | 80  |

|   | 3.5    | Literature Review                                                   | 83  |

| 4 | UNIFIE | D FIELD REDUNDANT ADDER                                             | 89  |

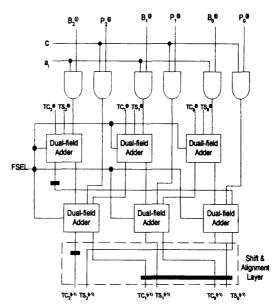

|   | 4.1    | Truly scalable unified field redundant adder                        | 89  |

|   |        | 4.1.1 Redundant Number Representation and redundant adder           | 90  |

|   | 4.2    | Unified field Redundant Adder                                       | 92  |

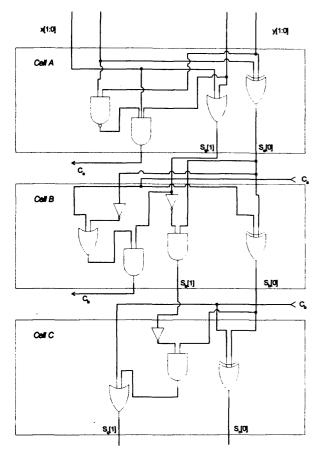

|   |        | 4.2.1 Cell A digit coding                                           | 95  |

|   |        | 4.2.2 Cell B digit coding                                           | 96  |

|   |        | 4.2.3 Cell C digit coding                                           | 97  |

|   | 4.3    | Unified field adders comparison                                     | 99  |

|   |        | 4.3.1 Area and Speed                                                | 99  |

|   |        | 4.3.2 Scalability                                                   | 104 |

| 5 |        | D FIELD MULTIPLIER                                                  | 108 |

|   | 5.1    | Modular Multiplication Algorithm                                    | 109 |

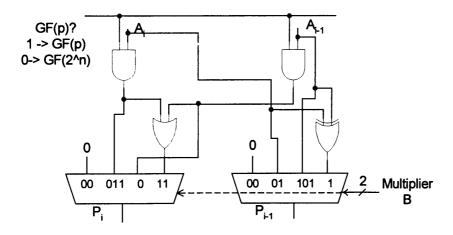

|   | 5.2    | Unified Field Montgomery Multiplication                             | 116 |

|   |        | 5.2.1 Montgomery Multiplication in GF(p)                            | 116 |

|   |        | 5.2.2 Montgomery Multiplication in GF(2n)                           | 117 |

|             |        | 5.2.3   | Unified Field Montgomery Multiplication                   | 118 |

|-------------|--------|---------|-----------------------------------------------------------|-----|

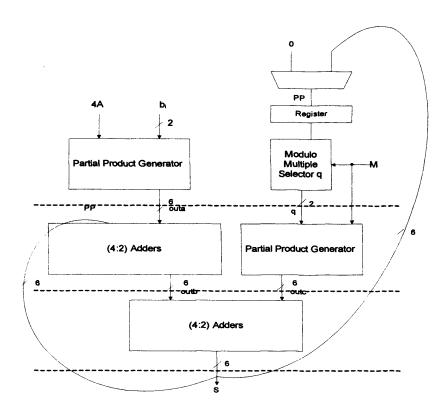

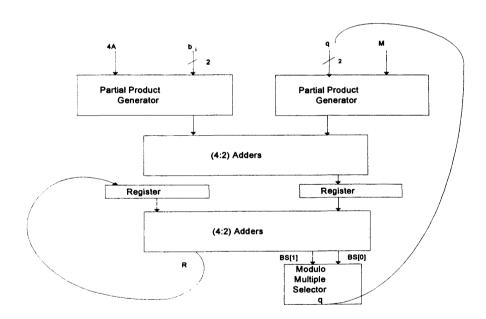

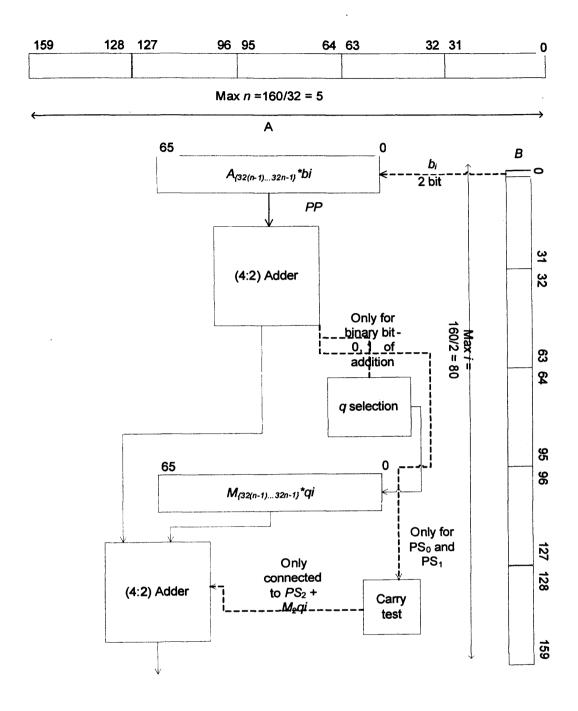

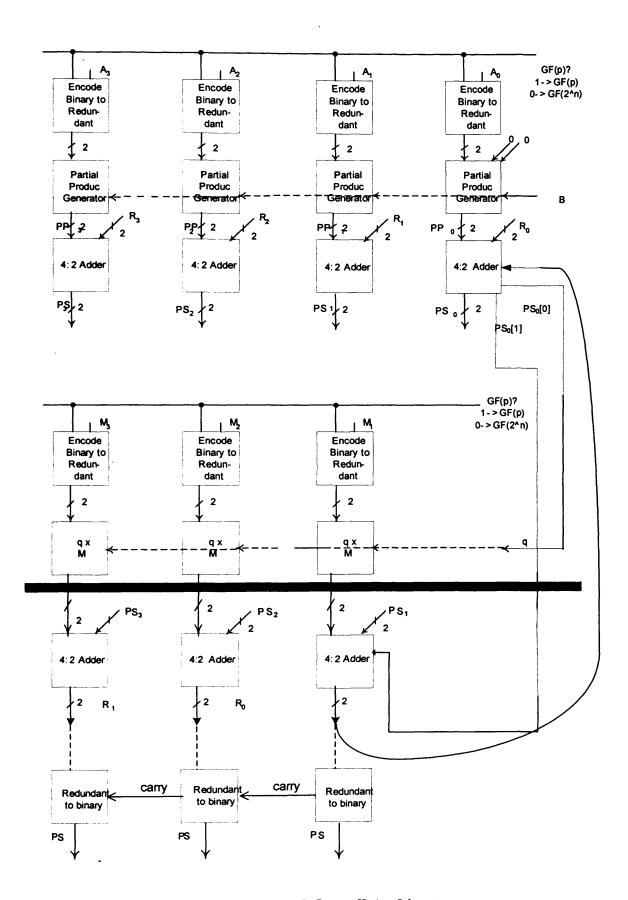

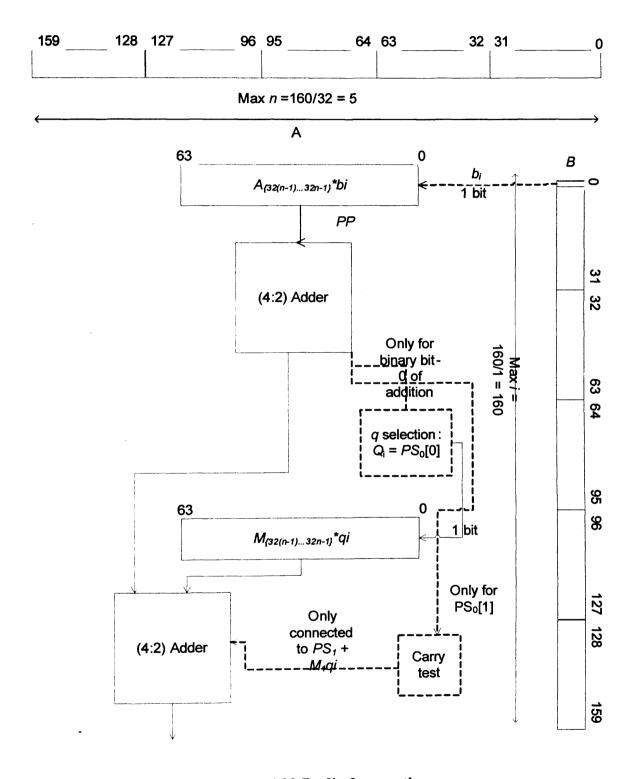

|             | 5.3    | Propos  | sed Word-Serial Montgomery Multiplier Architecture        | 119 |

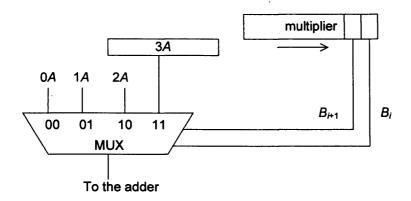

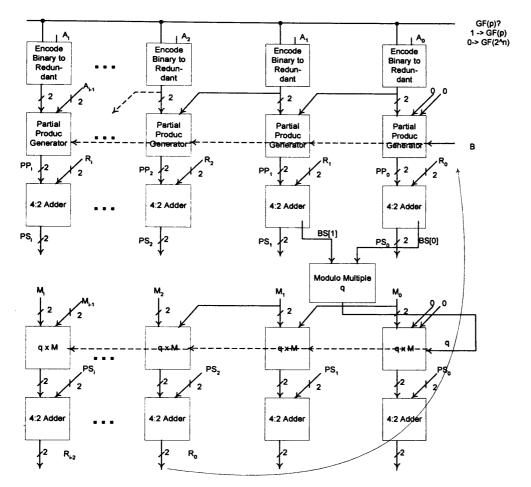

|             |        | 5.3.1   | Unified radix-4 Partial Product Generator                 | 121 |

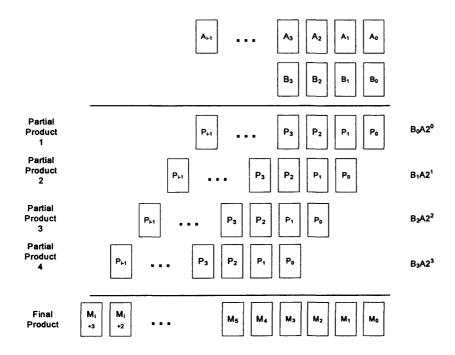

|             |        |         | 5.3.1.1 Radix-2 integer multiplication                    | 121 |

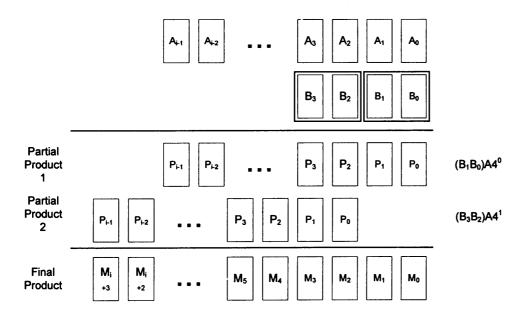

|             |        |         | 5.3.1.2 Radix-4 multiplication                            | 122 |

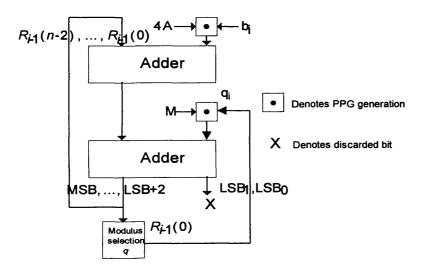

|             |        | 5.3.2   | Unified Modulo Reduction                                  | 127 |

|             |        | 5.3.3   | Carry absorption Unit                                     | 130 |

|             |        | 5.3.4   | Redundant to Binary Number Conversion                     | 136 |

| 6           | COM    | PARISON | NS, IMPROVEMENTS AND CONCLUSIONS                          | 143 |

|             | 6.1    | Overal  | Il unified field multiplier assessments                   | 143 |

|             |        | 6.1.1   | Area and Speed of Partial Product Generator               | 144 |

|             |        | 6.1.2   | Overall unified field multiplier assessment - Scalability | 149 |

|             |        | 6.1.3   | Area and Speed of Modulus Multiplier Digit Selection      | 155 |

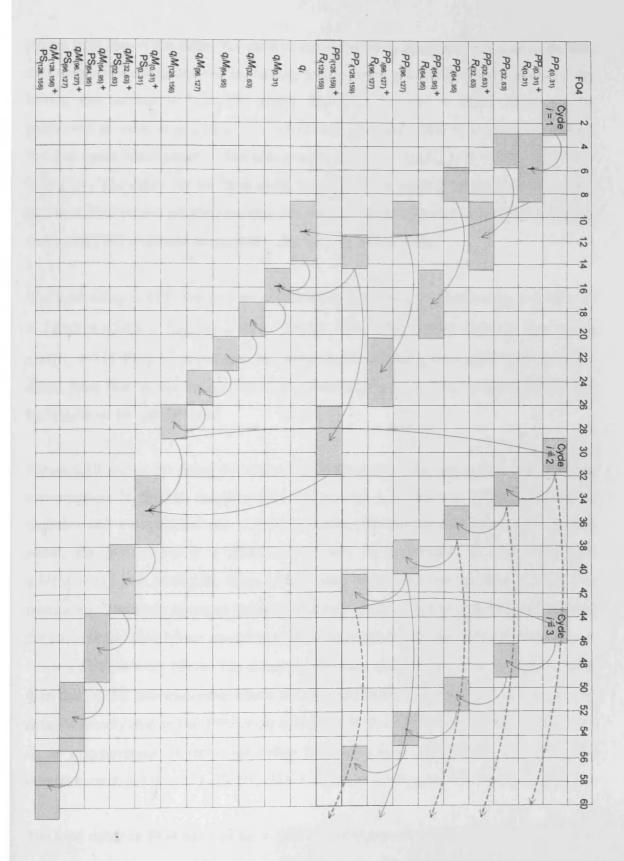

|             | 6.2    | Quotie  | ent pipelining                                            | 156 |

|             | 6.3    | M-bit   | ' M-bit multiplication                                    | 162 |

|             | 6.4    | Radix-  | 2 Multiplier design                                       | 170 |

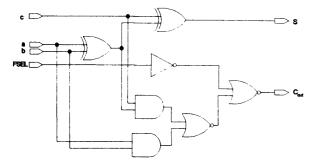

|             |        | 6.4.1   | Qi-selection                                              | 171 |

|             |        | 6.4.2   | Carry Test                                                | 172 |

|             |        | 6.4.3   | qiM + PS                                                  | 173 |

|             |        | 6.4.4   | M-bit 'M-bit multiplication using radix-2                 | 173 |

|             | 6.5    | Conclu  | usion                                                     | 179 |

| APPE        | NDIX 1 | – ALGOF | RITHMS                                                    | 181 |

| APPE        | NDIX 2 | - LOGIC | AL EFFORT                                                 | 184 |

| <b>APPE</b> | NDIX 3 | - SYNTH | ESIS RESULT REPORT                                        | 188 |

| APPE        | NDIX 4 | – PAPER | 1 [127]                                                   | 191 |

| APPE        | NDIX 5 | – PAPER | 2 [160]                                                   | 196 |

| REFE        | RENCES | 3       |                                                           | 207 |

|             |        |         | - []                                                      |     |

## **FIGURES**

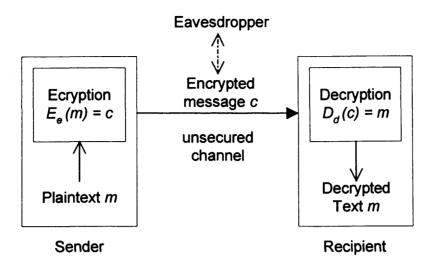

| Figure 2.1  | Schematic to show encryption and decryption                                            | 5   |

|-------------|----------------------------------------------------------------------------------------|-----|

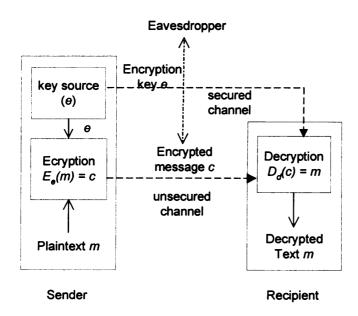

| Figure 2.2  | Schematic to show Symmetric key cryptography                                           | 7   |

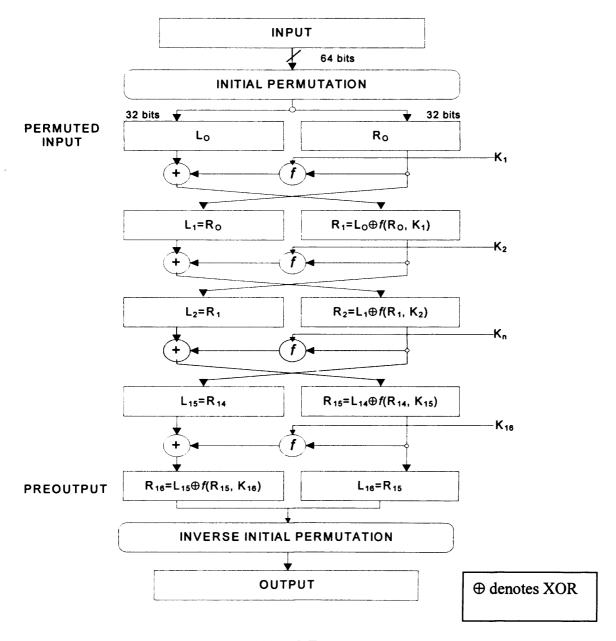

| Figure 2.3  | DES Encryption                                                                         | 10  |

| Figure 2.4  | DES inner function f                                                                   | 12  |

| Figure 2.5  | Block Diagram of the IDEA algorithm                                                    | 15  |

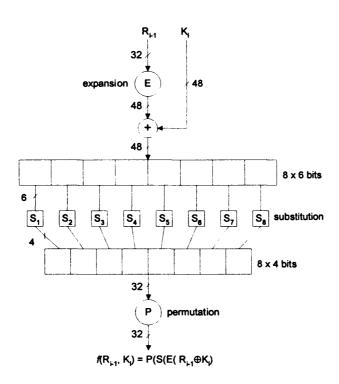

| Figure 2.6  | Schematic to show public key cryptography                                              | 17  |

| Figure 2.7  | DSA with SHA                                                                           | 20  |

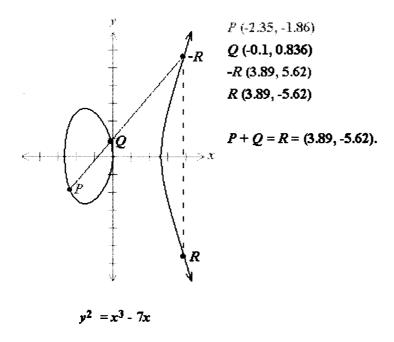

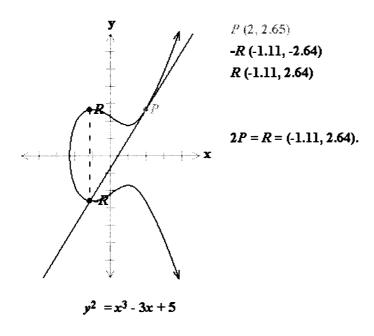

| Figure 3.1  | P+Q=R                                                                                  | 65  |

| Figure 3.2  | 2 <i>P=R</i>                                                                           | 66  |

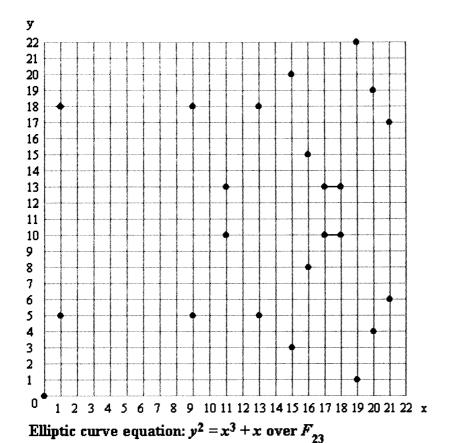

| Figure 3.3  | $y^2 = x^3 + x$ over GF(i) field $F_2^3$                                               | 68  |

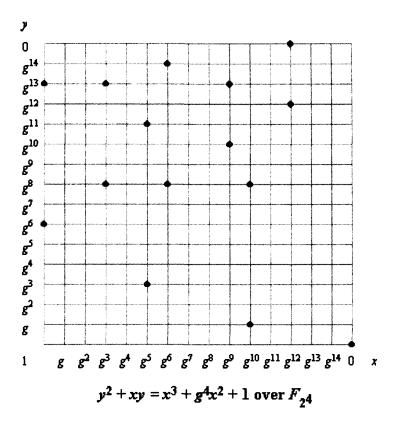

| Figure 3.4  | $x^3 + g^4x^2 + 1$ over $\hat{F_2}^4$                                                  | 71  |

| Figure 3.5  | Double-and-add method                                                                  | 79  |

| Figure 3.6  | The Montgomery Ladder                                                                  | 82  |

| Figure 3.7  | Double-and-add resistant against SPA                                                   | 82  |

| Figure 3.8  | Pen and paper multiplication                                                           | 85  |

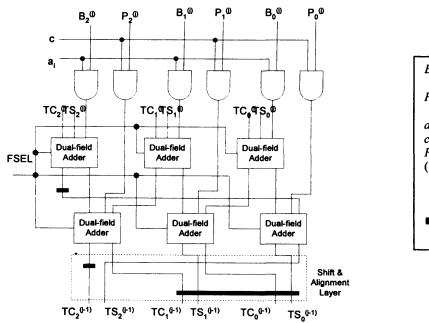

| Figure 3.9  | Savaş' et. al. Processing Unit: wordlength = 3                                         | 85  |

| Figure 3.10 | Savaş' dual-field adder synthesised by Mentor                                          | 86  |

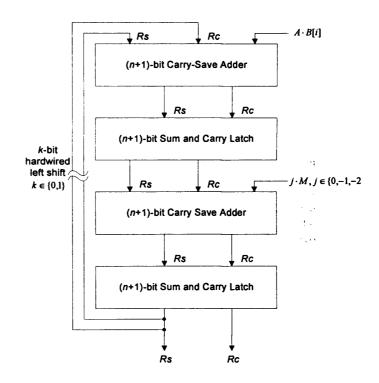

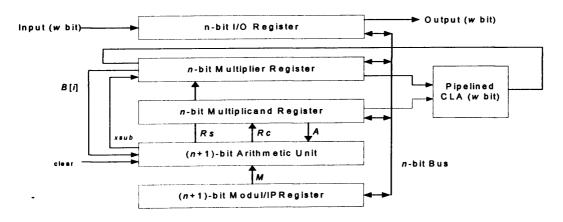

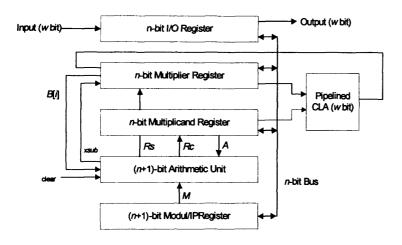

| Figure 3.11 | Arithmetic unit of Großshädl's n-bit unified multiplier                                | 87  |

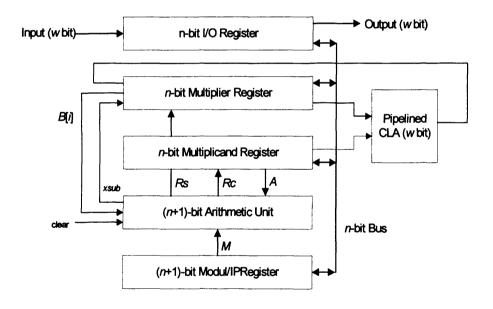

| Figure 3.12 | Block diagram of Großshädl's bit-serial multiplier architecture                        | 87  |

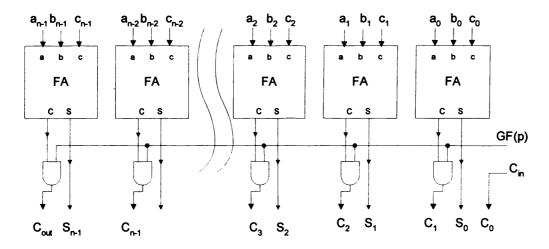

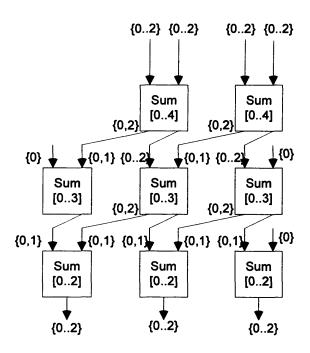

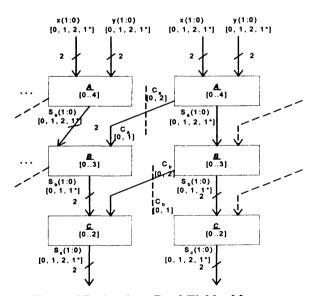

| Figure 3.13 | Carry Save Adder in Wolkerstorfer's design                                             | 88  |

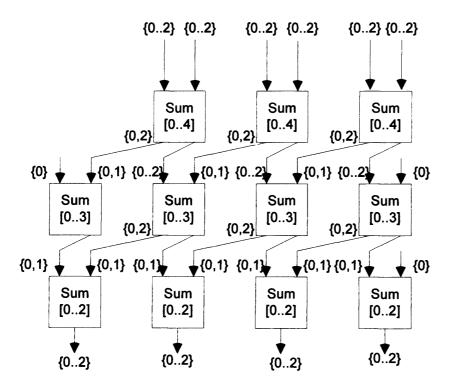

| Figure 4.1  | Conventional Redundant Adder w = 6                                                     | 91  |

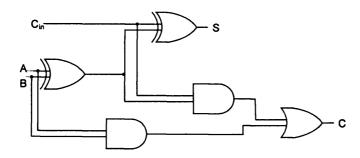

| Figure 4.2  | Binary Full Adder                                                                      | 91  |

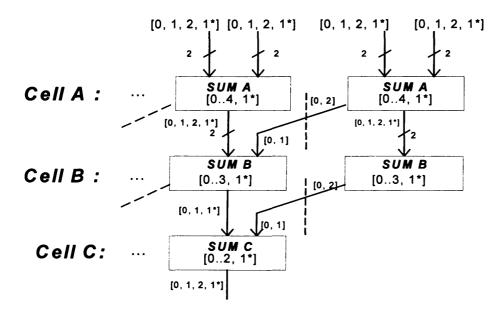

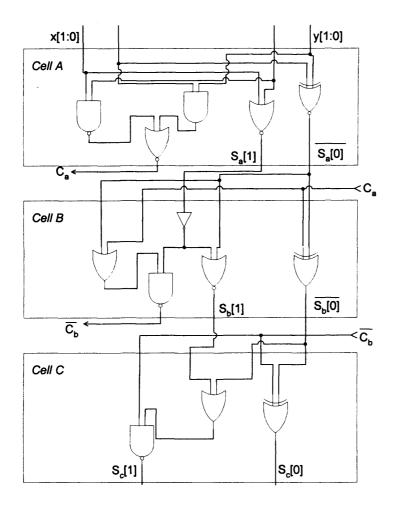

| Figure 4.3  | Redundant Dual Field adder                                                             | 93  |

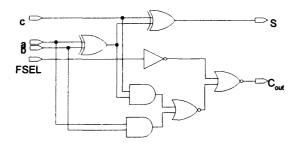

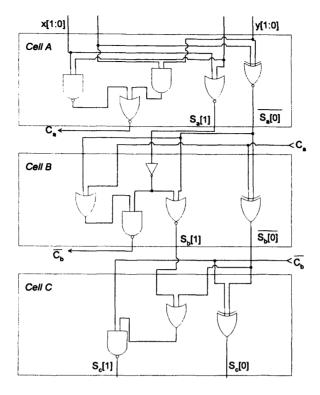

| Figure 4.4  | Overall gate implementation of new dual field (4:2) adder                              | 98  |

| Figure 4.5  | The ratio of delay due to transistor and wire to the delay due to                      | , , |

| 1 16410 1.5 | transistors alone                                                                      | 105 |

| Figure 5.1  | The classified pen-and-paper division method                                           | 110 |

| Figure 5.2  | Knuth Algorithm $(m_{n-1} \ge \lfloor b/2 \rfloor)$                                    | 111 |

| Figure 5.2  | Barrett's Algorithm $(m_n) \ge \lfloor 0/2 \rfloor$                                    | 113 |

| -           | Montgomery's Algorithm                                                                 | 114 |

| Figure 5.4  |                                                                                        | 117 |

| Figure 5.5  | Montgomery Multiplication in GF(p)                                                     | 117 |

| Figure 5.6  | Montgomery multiplication in GF(2")  Pit wise Montgomery Multiplication (step by step) | 120 |

| Figure 5.7  | Bit-wise Montgomery Multiplication (step-by-step)                                      | 120 |

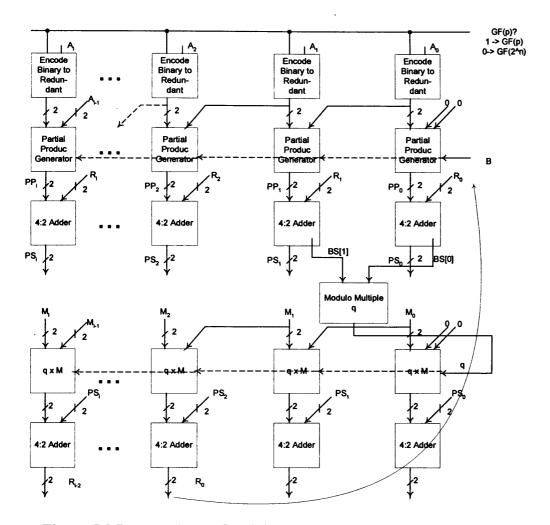

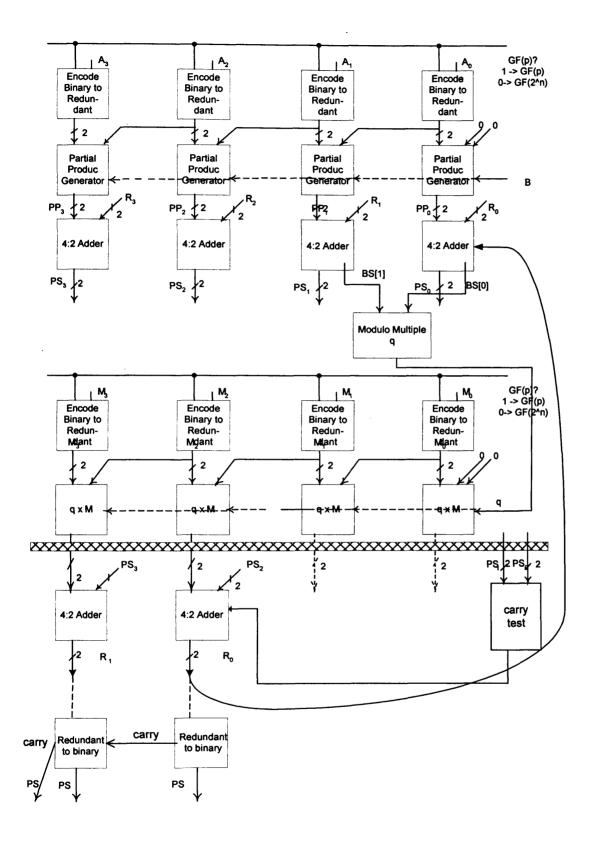

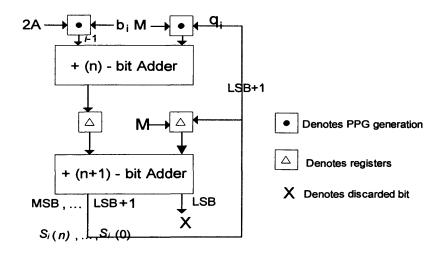

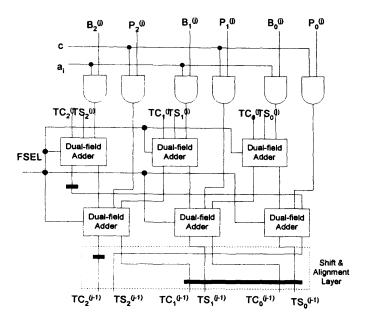

| Figure 5.8  | Proposed Word -Digit Dual-Field Multiplier Architecture                                | 121 |

| Figure 5.9  | unsigned Radix-2 AxB Multiplication                                                    |     |

| Figure 5.10 | Radix-4 multiplication                                                                 | 123 |

| Figure 5.11 | partial product generation in radix-4 with pre-computation of 3xA                      | 124 |

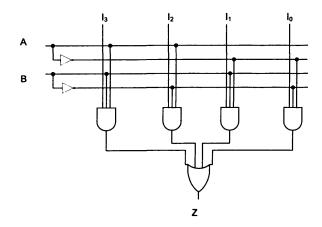

| Figure 5.12 | Grobschadl Booth encoder circuit                                                       | 124 |

| Figure 5.13 | Grobschadl unified radix-4 partial product generator                                   | 125 |

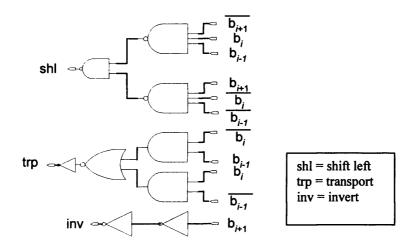

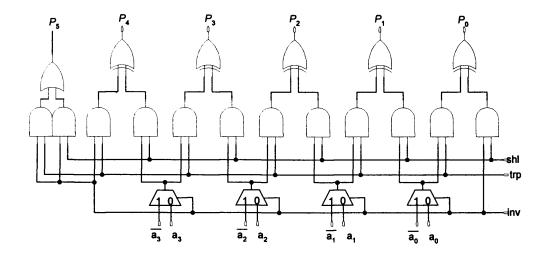

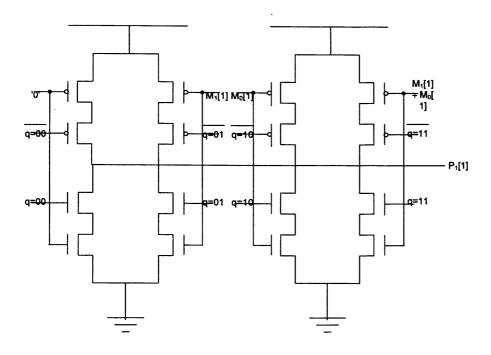

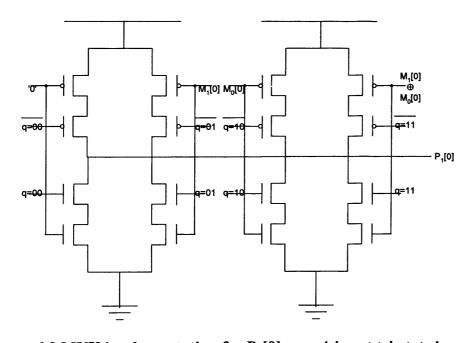

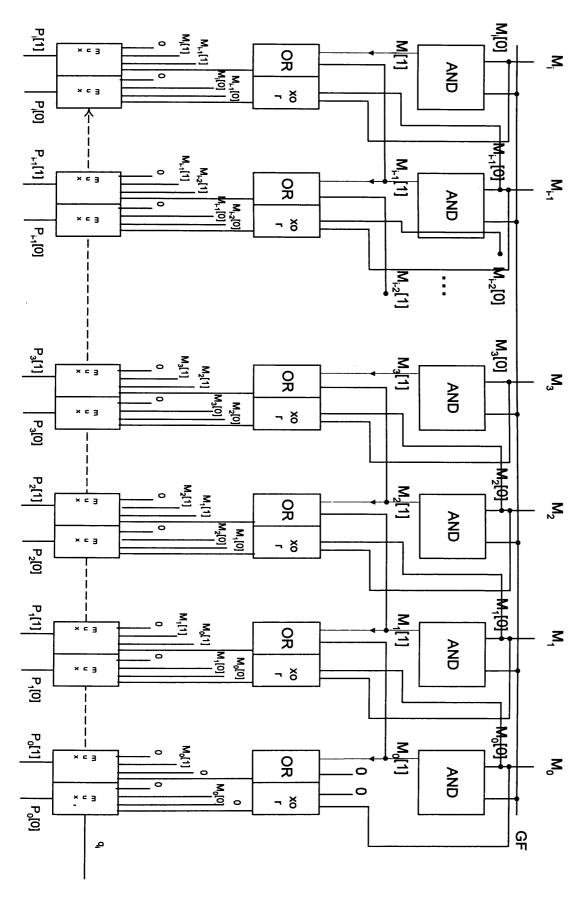

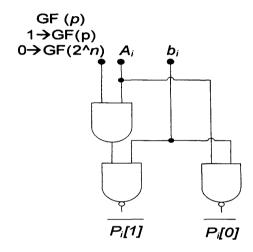

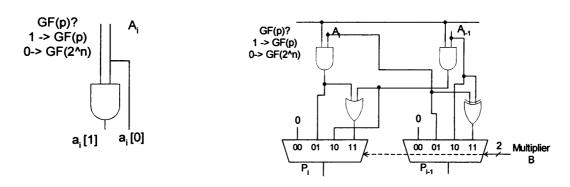

| Figure 5.14 | Field-Embedded Binary Number Encoder                                                   | 125 |

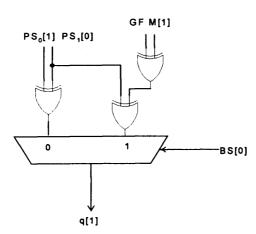

| Figure 5.15 | Radix-4 Partial Product Generator                                                      | 126 |

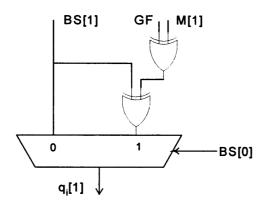

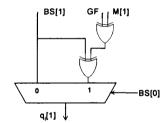

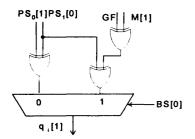

| Figure 5.16 | q[1] logic                                                                             | 128 |

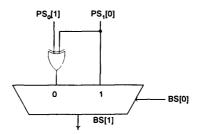

| Figure 5.17 | Logic for BS[1]                                                                        | 129 |

| Figure 5.18 | Simplified logic for $q_i$ [1] combined with BS[1] logic                               | 129 |

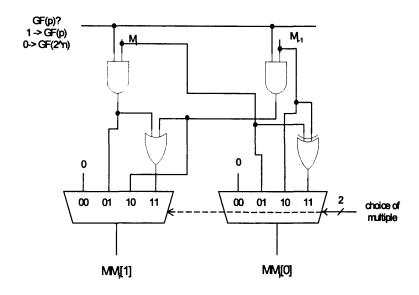

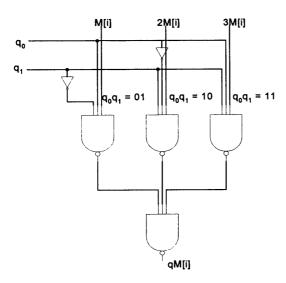

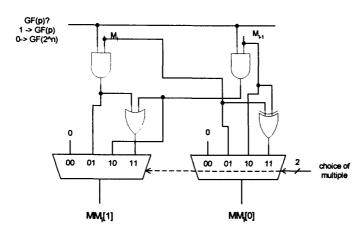

| Figure 5.19 | Modulo multiple generator                                                              | 130 |

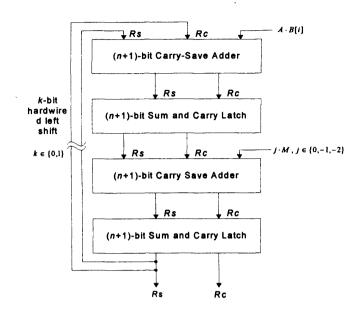

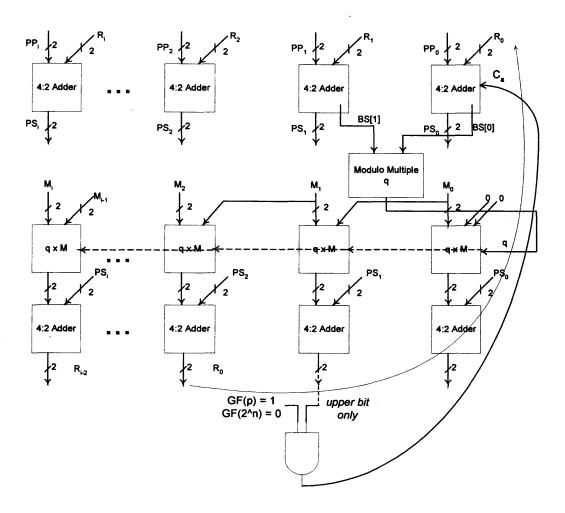

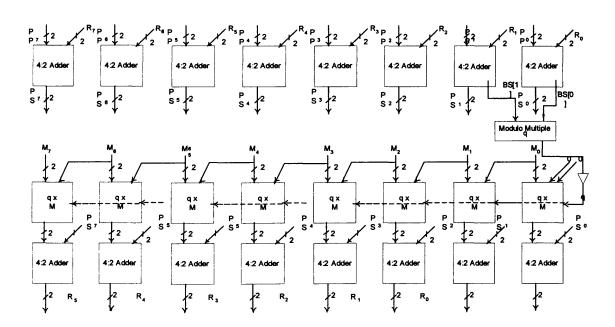

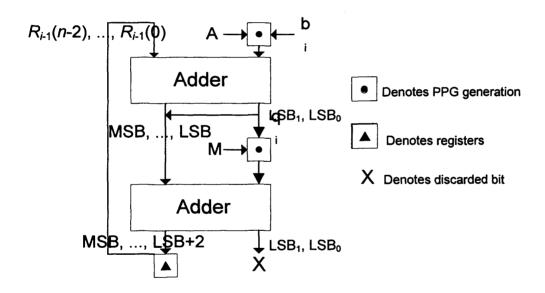

| Figure 5.20 | Modified architecture with carry absorption                                            | 131 |

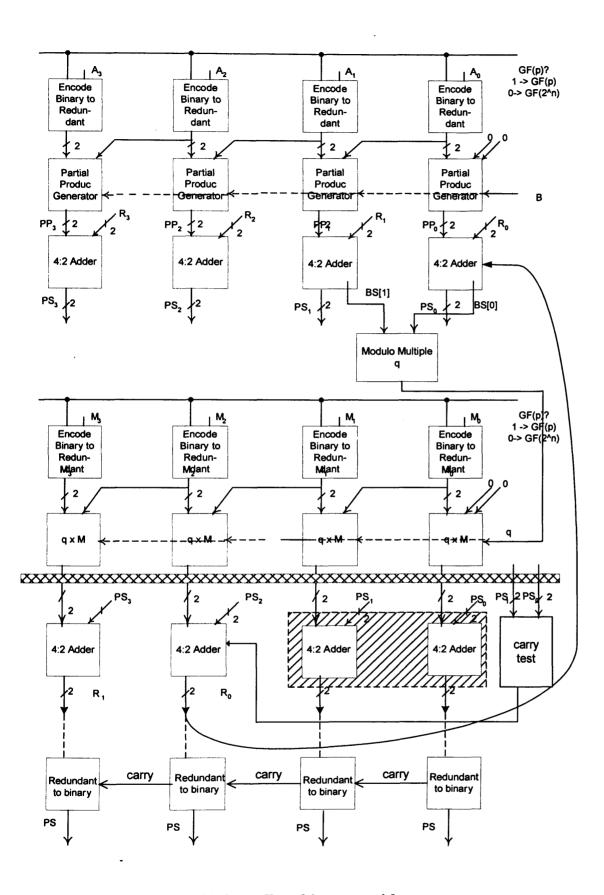

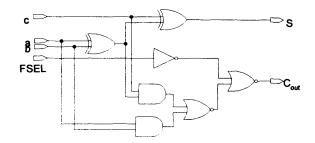

| Figure 5.21 | Overall architecture with carry test                                                   | 135 |

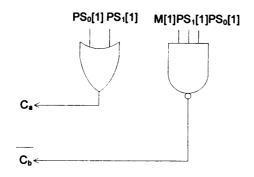

| Figure 5.22 | Carry Test                                                                             | 136 |

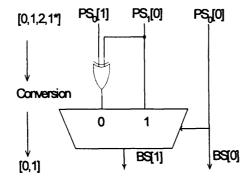

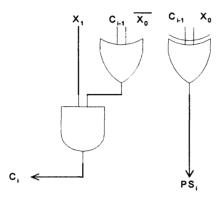

| Figure 5.23 | circuit for binary conversion                                                          | 140 |

| Figure 5.24 | Final overall architecture                                                             | 141 |

| Figure 6.1  | Traditional MUX implementation                                                         | 144 |

| Figure 6.2  | MUX implementation for P <sub>1</sub> [1] as a 4-inputtri-state inverter               | 145 |

| Figure 6.3  | MUX implementation for P <sub>1</sub> [0] as a 4-input tri-state inverter              | 145 |

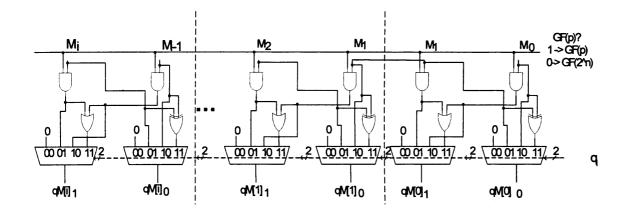

| Figure 6.4  | Multiplexer input connection for $q_iM$                                                | 147 |

| Figure 6.5  | 8-bit Multiplier simulation diagram                                                    | 148 |

| Figure 6.6  | PPG unit quotient qi propagation                                                       | 150 |

| Figure 6.7  | MUX implementation                                                                     | 150 |

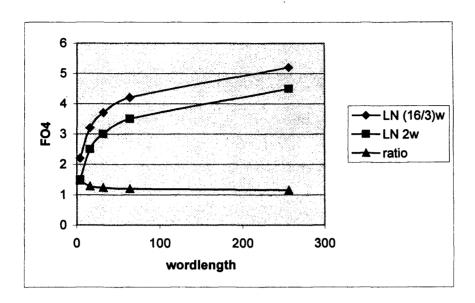

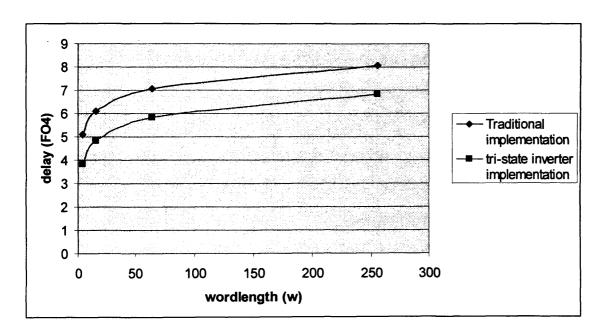

| Figure 6.8  | Wordlength w vs. Delay (FO4) for traditional and                                       |     |

|             | tri-state inverter multiplexer implementation                               | 154 |

|-------------|-----------------------------------------------------------------------------|-----|

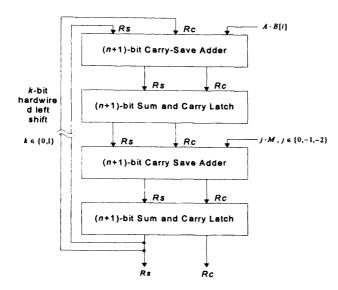

| Figure 6.9  | Algorithm 1 non-pipelined                                                   | 157 |

| Figure 6.10 | Architecture 1 non-pipelined                                                | 157 |

| Figure 6.11 | Algorithm 2 with quotient pipelining for radix 2 multiplication             | 158 |

| Figure 6.12 | Proposed architecture with quotient pipelining (for radix-4 multiplication) | 158 |

| Figure 6.13 | Quotient Pipelined multiplier architecture                                  | 159 |

| Figure 6.14 | Daly's modified architecture                                                | 160 |

| Figure 6.15 | Proposed architecture using Daly's quotient pipelined structure             | 161 |

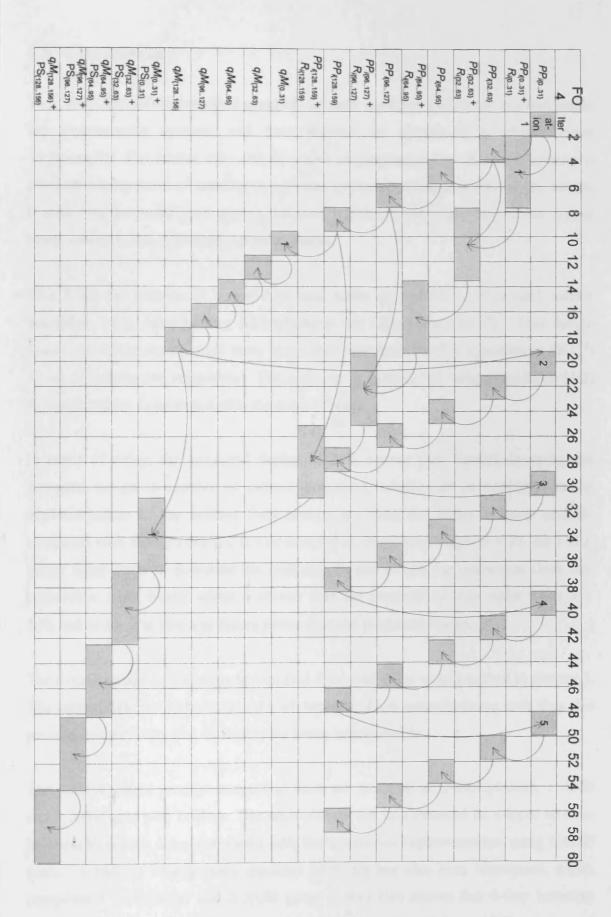

| Figure 6.16 | Radix-4 operation                                                           | 164 |

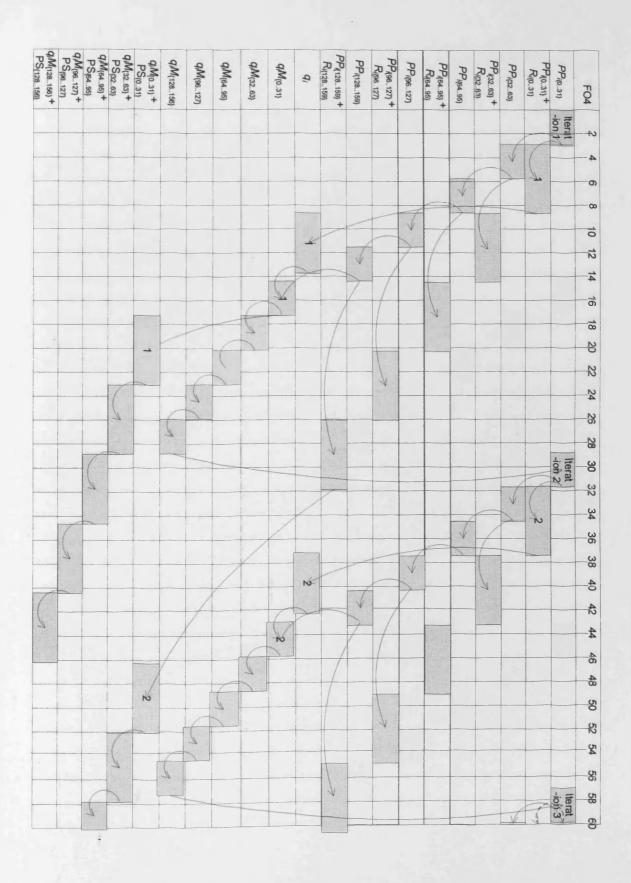

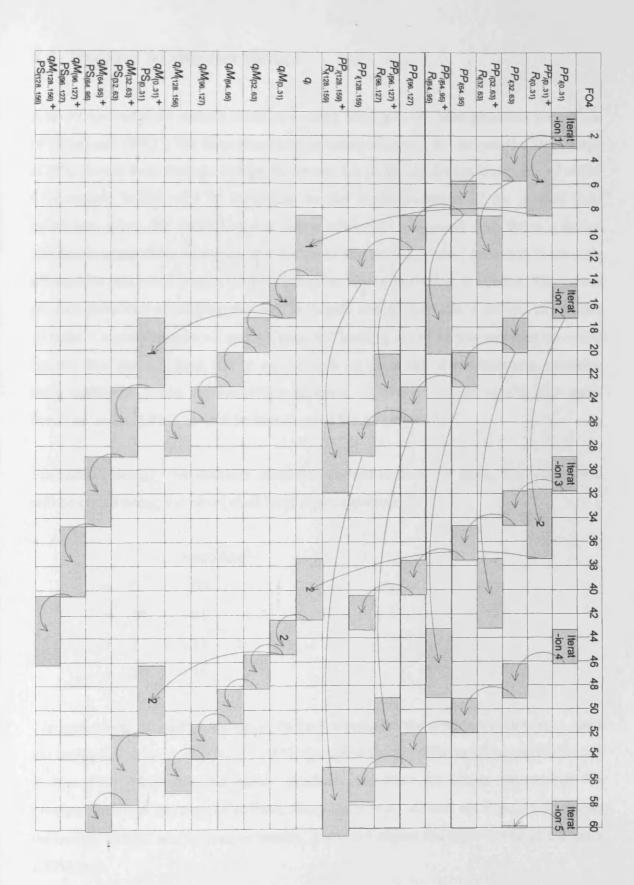

| Figure 6.17 | Timing diagram for radix-4 operation (reuse all modules)                    | 165 |

| Figure 6.18 | Radix-4 operation (duplicated adder modules)                                | 168 |

| Figure 6.19 | Radix-4 operation (duplicated adder and PPG modules)                        | 169 |

| Figure 6.20 | Radix 2 PPG unit                                                            | 171 |

| Figure 6.21 | Radix 2 Overall Architecture                                                | 174 |

| Figure 6.22 | Radix 2 operation                                                           | 177 |

| Figure 6.23 | Radix 2 (reuse all modules)                                                 | 178 |

|             |                                                                             |     |

# **TABLES**

| Table 2.1  | Advantages and disadvantages of Symmetric Key Algorithm                        | 35   |

|------------|--------------------------------------------------------------------------------|------|

| Table 2.2  | Advantages and disadvantages of Public Key Algorithm                           | 35   |

| Table 2.3  | Equivalent Strength                                                            | 37   |

| Table 2.4  | Recommended algorithms and minimum key sizes                                   | 39   |

| Table 2.5  | Recommended minimum symmetric security levels and RSA                          |      |

|            | key sizes based on protection lifetime                                         | 41   |

| Table 2.6  | System requirements for elliptic curve cryptosystems and RSA                   | 47   |

| Table 2.7  | The storage requirements in bits when making a naive comparison                | • •  |

| Table 2.7  | between an elliptic curve cryptosystem over $GF(q)$ where $q$ is 160           |      |

|            | bits in length and RSA with a 1024-bit modulus                                 | 47   |

| Table 3.1  | Number of field multiplications and inversions for affine and projective       | ٦,   |

| Table 3.1  | point addition and doubling                                                    | 52   |

| T-61- 2.2  |                                                                                | 53   |

| Table 3.2  | Timings (in ms) on a 1000 MHz Pentium III over Binary Field                    | 33   |

| Table 3.3  | Execution time for projective and affine coordinate                            | 50   |

| m 11 41    | implementations of elliptic curve multiplication                               | 53   |

| Table 4.1  | Conventional Redundant Representation                                          | 91   |

| Table 4.2  | Table of addition for $GF(p)$                                                  | 92   |

| Table 4.3  | Table of addition of for GF(2")                                                | 92   |

| Table 4.4  | Cell A addition                                                                | 94   |

| Table 4.5  | Cell B addition                                                                | 94   |

| Table 4.6  | Cell C Addition                                                                | 94   |

| Table 4.7  | Karnaugh Map for Cell A addition                                               | 95   |

| Table 4.8  | Table to show redundant representation of sums                                 | 96   |

| Table 4.9  | Karnaugh Map for Cell A addition                                               | 96   |

| Table 4.10 | Karnaugh Map for Cell B                                                        | 97   |

| Table 4.11 | Karnaugh Map for Cell C                                                        | 97   |

| Table 4.12 | Logical effort of (4:2) unified field adder                                    | 100  |

| Table 4.13 | Logical effort of path 1 of Savaş unified field adder                          | 102  |

| Table 4.14 | Logical effort of path 2 of Savas unified field adder                          | 103  |

| Table 4.15 | The ratio of delay due to transistor and wire to the delay due                 |      |

|            | to transistors alone                                                           | 104  |

| Table 4.16 | Logical effort of FSEL path in Savas unified field adder                       | 105  |

| Table 4.17 | Savas' Adder results                                                           | 107  |

| Table 5.1  | Complexity of the three reduction algorithm in reducing a 2k-digit             |      |

|            | number x modulo a k-digit modulus m                                            | 114  |

| Table 5.2  | Execution times for the reduction of a 2k-digit number modulo a                |      |

|            | k-digit modulus m for the three reduction algorithms compared to               |      |

|            | the execution time of a $k \times k$ - digit multiplication (r = 2 16, on a 33 |      |

|            | MHz 80386 based PC with WATCOM C/ 386 9.0)                                     | 115  |

| Table 5.3  | Radix-4 Partial Product Generation                                             | 126  |

| Table 5.4  | Multiple of M                                                                  | 127  |

| Table 5.5  | Selection of Modulo Multiple, $q_i \times M$                                   | 127  |

| Table 5.6  | Binary Conversion                                                              | 129  |

| Table 5.7  | Possible results $PP = A * b_i$                                                | 132  |

| Table 5.8  | All possible $PS = PP + R$ for $GF(p)$                                         | 132  |

| Table 5.9  | Combinations of $PS + q_iM$                                                    | 133  |

| Table 5.10 | Result M*qi for different cases of PS                                          | 133  |

| Table 5.11 | Results for R                                                                  | 133  |

| Table 5.12 | Redundant to binary representation                                             | 136  |

| Table 5.13 | Redundant to binary conversion with Carry                                      | 137  |

| Table 5.14 | Karnaugh map for binary bit conversion                                         | 137  |

| Table 5.15 | Karnaugh map for carry bit generation                                          | 138  |

| Table 5.15 | Redundant to binary conversion by checking carry from biti-1                   | 138  |

| Table 5.10 | Karnaugh map for binary conversion by checking carry from the bit i-1 1        | 139  |

| Table 5.17 | Karnaugh map for carry bit generation by checking carry from the biti-1        | 139  |

| Table 5.18 | 4 input MUX logical effort                                                     | 151  |

| Table 6.1  | Logical effort delay for the 4-input multiplexer                               | 131  |

| 1 4010 0.2 | (traditional implementation) of different wordlength                           | 152  |

|            | (additional implementation) of different wordlength                            | 1 32 |

| Table 6.3  | Logical effort for the 4-input multiplexer                  |     |

|------------|-------------------------------------------------------------|-----|

|            | (4-input tri-state inverter implementation)                 | 153 |

| Table 6.4  | Logical effort delay for the 4-input multiplexer            |     |

|            | (tri-state inverter implementation) of different wordlength | 154 |

| Table 6.5  | Modulus Multiplication Digit                                | 155 |

| Table 6.6  | Radix 2 multiplication                                      | 171 |

| Table 6.7  | Radix 2 $q$ - selection                                     | 172 |

| Table 6.8  | All possible PS                                             | 172 |

| Table 6.9  | PS and $q_i M$ combination                                  | 172 |

| Table 6.10 | Radix-2 Redundant Montgomery Multiplier Delay               | 175 |

## **List of Abbreviations**

| $GF(p)/F_p$       |       | Prime Galois Field           |

|-------------------|-------|------------------------------|

| $GF(2^n)/F_2^n$   |       | Binary Galois Field          |

| DES               | ••••• | Data Encryption Standard     |

| DEA               | ••••• | Data Encryption Algorithm    |

| IDEA              |       | International Data           |

|                   |       | Encryption Algorithm         |

| PES               | ••••• | Proposed Encryption Standard |

| IPES              |       | Improved Proposed            |

| 4 F/G             |       | Encryption Standard          |

| AES               |       | Advanced Encryption          |

|                   |       | Standard                     |

| mod               |       | Modular                      |

| SHA               | ••••• | Secure hash Algorithm        |

| DSA               | ••••• | Digital Signature            |

|                   |       | Algorithm                    |

| DSS               |       | Digital Signature Standard   |

| ECDSA             |       | Elliptic Curve Digital       |

|                   |       | Signature Standard           |

| ECDH              |       | Elliptic Curve Diffie-       |

|                   |       | Hellman                      |

| ECDLP             |       | Elliptic Curve Discrete      |

|                   |       | Logarithm Problem            |

| <b>⊕</b>          |       | XOR                          |

| DPA               |       | Differential Power           |

| DIA               | ••••• | Analysis                     |

| •                 |       | AND logic                    |

| ^                 |       | OR logic                     |

| V<br>FO4          | ••••• | Fan-out of 4                 |

| FO4               | ••••• |                              |

| Logical Effort: g | ••••• | Logical effort               |

| Logical Effort: b | ••••• | Branching effort             |

| Logical Effort: h |       | Electrical effort            |

| Logical Effort: p |       | Parasitic effort             |

| Logical Effort: N | ••••• | Number of Stages             |

| Logical Effort: F |       | Path Effort                  |

| Logical Effort: D |       | Delay                        |

| div               | ••••  | Divide (Arithmetic           |

|                   |       | function)                    |

| $\widehat{q}$     |       | Estimated q                  |

| gcd               |       | Greatest Common              |

| •                 |       | Denominator                  |

| PPG               |       | Partial Product Generator    |

|                   |       |                              |

| PP                |       | Partial Product              |

|                   |       | Partial Product Partial Sum  |

| PS                |       |                              |

|                   |       | Partial Sum                  |

| w     |                                         | Wordlength                   |

|-------|-----------------------------------------|------------------------------|

| $C_i$ |                                         | ith bit of the carry C       |

| FSEL  |                                         | Galois Field Selection       |

| MUX   | • • • • • • • • • • • • • • • • • • • • | Multiplexer                  |

| H     |                                         | Addition mod 2 <sup>16</sup> |

|       |                                         | register                     |

| X     |                                         | Discard bit                  |

|       |                                         | Pipeline latches             |

|       |                                         | PPG Generation               |

| •     |                                         |                              |

### 1 Introduction

### 1.1 Motivation

This thesis will describe the VLSI implementation of a modular multiplier that is capable of performing multiplication in both GF(p) and  $GF(2^n)$  Galois Fields for elliptic curve cryptography. Elliptic curve cryptography is becoming more popular compared with traditional cryptographic systems because it provides a similar level of security but much smaller key lengths are required.

One of the most used operations in cryptographic systems is modular exponentiation, which involves many long wordlength modular multiplications. For elliptic curve cryptography, modular multiplication is one of the most computationally demanding operations involved. For these reasons, elliptic curve cryptography was chosen to be the target system and hardware implementation for modular multiplication will be designed.

In recent years, there has been an increase in demand for unified field multipliers for Elliptic Curve Cryptography in the electronics industry, because they provide flexibility for the customer to choose between the Prime (GF(p)) and the Binary  $(GF(2^n))$  Field. Also, having the ability to carry out arithmetic over both GF(p) and  $GF(2^n)$  in the same hardware provides the possibility of performing any cryptographic operation that requires the use of both fields. The unified field multiplier is relatively future proof compared with multipliers that only perform arithmetic over a single chosen field.

The security provided by the architecture is also very important. It is known that the longer the key length, the more susceptible the system is to differential power attacks, due to the increase amount of data leakage. Therefore, it is beneficial to design a hardware that is scalable, so that more data can be processed per cycle. A scalable system is a system that can expand word length without affecting logic depth. An additional advantage of designing a multiplier that is capable of dealing with long wordlengths is improvement in performance in terms of delay, as less iterations are

needed. This is very important because typical elliptic curve cryptography involves key size of 160 bits.

Apart from being scalable and capable of dual field operation, the system must also be impartial, which means that it must not favour either of the fields. This unified field multiplier should avoid the need to compromise on speed and area in order to gain the dual field ability.

### 1.2 Thesis Outline

In this thesis, the hardware implementation of ECC in two different fields GF(p) and  $GF(2^n)$  will be explored. Even though GF(p) and  $GF(2^n)$  are structurally very different, they are very similar in nature, this can be exploited when designing this unified multiplier. This unified ECC multiplier for GF(p) and  $GF(2^n)$  provides a simple generic solution to the industry which could give flexibility to their customers to choose between GF(p) and  $GF(2^n)$  field with minimal penalty. Note that all the arithmetic operations in systems such as AES are carried out in finite field  $GF(2^n)$ , therefore the proposed multiplier could be used for this as well.

Unlike the existing designs, the proposed design does not require an external control signal that will be propagated to all the cell modules, which cause very high fan-out to the field selection signal that could affect the scalability of the design. Instead, the proposed design makes use of a unique 1\* implementation to embed field information into the number encoding itself.

The proposed multiplier will operate in radix-4; by increasing the radix of the system, the number of iterations will be reduced. However, there is a trade-off between the area consumption and the improvement in speed. Radix-4 system is considered to have the best trade-off between speed and area.

Furthermore, the design uses redundant addition to avoid long carry chains. The multiplier is in digit serial fashion and Montgomery multiplication is used.

The thesis is organised as follows:

Chapter 2 will provides the basic background theory on cryptography, particularly on common systems such as DES and RSA. Elliptic curve cryptography systems are also introduced.

In Chapter 3, the operational details of elliptic curves functions will be explored. This will first be explained in basic real number groups, then elliptic curve groups over GF(p) and  $GF(2^n)$  will be investigated. The second part of Chapter 3 will be dedicated to explaining side channel attacks, e.g. differential power attacks and timing attacks. The final section of Chapter 3 will explore what other unified field operators in particular multipliers have been implemented.

Chapter 4 describes the implementation of the proposed unified field redundant adder for multiplication in either GF(p) or  $GF(2^n)$ . This section will explain the unique encoding method that is employed in this design. The scalability of the adder will be assessed at the end of the chapter using a technique called Logical Effort.

Chapter 5 will present the overall implementation of the dual field multiplier. Montgomery multiplication will be compared with other modular multiplication methods such as Barrett modular multiplication, showing that Montgomery is more appropriate for the design. It will show the implementation of the partial product generator, modular reduction, carry test unit and the final redundant to binary conversion unit.

Chapter 6 will assess the results of the multiplier, suggest alternative methods to improve the operation of the multiplier, such as using a 4-input tri-state inverter to implement a multiplexer, rather than using a traditional design. This chapter will also examine radix-2 multiplier design and investigate the operation of the multiplier for  $M \times M$  multiplication. Finally, there is a conclusion.

## 2 Cryptography

Cryptography has become an integral part of modern day life as it provides secure communications. It provides a set of techniques to achieve the goal of different aspects of security, which are: confidentiality; data integrity; authentication and non-repudiation. Therefore, in order to achieve an adequate level of security for any communication, the following issues should be addressed:

- The data should only be readable by authorised recipients;

- the data itself should not be altered by any unauthorised person;

- parties involved in the communication and the data origination should be identified and authenticated;

- finally, no actions taken by any party involved are deniable.

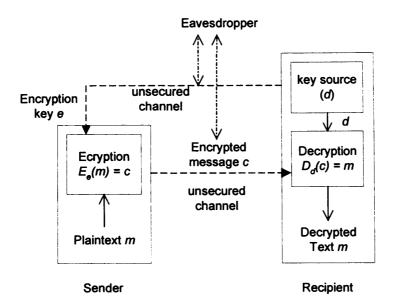

This is achieved by encrypting the original data, or the plaintext, with a mathematical function, in order to convert it to the ciphertext. The recipient will then decrypt the ciphertext with a mathematical function to obtain the plaintext. It is assumed that the transmission medium is unsecured and eavesdropper could interrupt, intercept, modify or fabricate the data. Figure 2.1 shows the basic concept of encryption and decryption. The plaintext m is encrypted by function E with key e. The ciphertext C is then transmitted to the recipient. The recipient decrypts C using function D with key e and the decrypted text can be retrieved. The keys should possess the following properties:  $D_d = E_e^{-1}$ , therefore,  $D_d(E_e(m)) = m$ . The two keys e and e could be the same.

Figure 2.1 Schematic to show encryption and decryption

The security of a cryptosystem depends upon the strength of the algorithm, and the length of the keys used for encryption and decryption. A cryptosystem should be secure enough to be able to avoid most attacks except "brute-force", which is a known-plaintext attack. The key length must be sufficiently great so that brute-force attack becomes computationally infeasible. However, it has been discovered that the longer the key is required by a system, the higher chance of the system being successfully attacked by differential power attacks [1]. Differential power attacks will be discussed in Section 3.4.4.

One-way function and trapdoor-one-way-function form the backbone of modern (public key) cryptography. One-way function is relatively easy to carry out in one direction, but computationally infeasible or impossible to carry out the reverse operation. Trapdoor-one-way-function is a one-way function such that, given the extra trapdoor information, the computation of the reverse function becomes computationally feasible or else it will be difficult or even impossible to reverse.

The main aim of cryptography is to keep the communication secure, which fundamentally means keeping the plaintext secret by keeping the decryption key secret. Cryptanalysis is the science of recovering the plaintext of the message without the knowledge of the key. Each attempt at Cryptanalysis is called an "attack". One should assume that the cryptanalyst has complete details of the cryptographic

algorithm and implementation. There are six commonly known attacks on encryption schemes rather than attacks on the implementation.

- 1. A *ciphertext-only attack* is one where the cryptanalyst only has knowledge of the ciphertext and tries to deduce the plaintext or the decryption key by observing the ciphertext.

- 2. A *known-plaintext attack* is one where the cryptanalyst obtains a quantity of plaintext and its corresponding ciphertext.

- 3. A *chosen-plaintext attack* is one where the cryptanalyst chooses the plaintext and is then able to obtain the corresponding ciphertext, by using this information the cryptanalyst can deduce the remaining plaintext of the ciphertext which was previously unseen.

- 4. An *adaptive chosen-plaintext attack* is fundamentally a chosen-plaintext attack, however, the choice of plaintext may depend on the ciphertext from the previous requests.

- 5. A chosen-ciphertext attack is one where the cryptanalyst chooses the ciphertext and is then able to obtain the corresponding plaintext. However, in order to carry out such operation the attacker needs to be able to gain access to the decryption equipment but not the decryption key. The cryptanalyst could now recover the corresponding plaintext of the different ciphertext from the information deduced before without access to such equipment.

- 6. An *adaptive chosen-ciphertext attack* is fundamentally a chosen-ciphertext attack, however, the choice of ciphertext may depend on the plaintext from the previous requests.

There are two different types of cryptography, Symmetric (Private Key) and Asymmetric (Public Key) cryptography.

### 2.1 Symmetric key cryptography

Symmetric key cryptography is a cryptographic system where the encryption key (e) is generated from the decryption key (d) or vice versa, as shown in the following equation:

$$d = e^{-1} \tag{2.1}$$

In most cases, the most practical choice of the key pair for symmetric key cryptography is when the encryption key (e) equals to the decryption key (d). Therefore, in order to keep the data secure, the key used must be kept secret. As a result, symmetric key cryptography is also called private key cryptography. However, there lies a so-called "key distribution problem", where an efficient protocol needs to be established for key agreement and key exchange in a secure manner (such protocols will not be discussed in this thesis). Figure 2.2 shows the schematic diagram of symmetric key cryptography.

Figure 2.2 Schematic to show Symmetric key cryptography

There are two different types of symmetric key cryptography, and they are block cipher and stream cipher. Block ciphers can be either symmetric key or public key; only symmetric key block ciphers are addressed in this section.

Block ciphers operate on plaintext and ciphertext in a group of bits, usually 64 bits but it could be longer. The blocklength of the plaintext blocks and the ciphertext blocks are the same. The most important classes of block ciphers are substitution ciphers and transposition ciphers. These ciphers substitute symbols or a group of symbols by other symbols or other group of symbols or the symbols in a block is permuted by a transposition function.

The encryption transformation  $E_e$  of a simple substitution cipher where  $e \in K$  can be shown as follows:

$$E_{e}(m) = (e(m_{1})e(m_{2})...e(m_{t})) = (c_{1}c_{2}...c_{t}) = c,$$

(2.2)

over A, defined to be an alphabet of q symbols, and M, the set of all strings of length t over A. In addition, K is the set of all permutations on the set A.  $m = (m_1 m_2 ... m_t) \in M$  For decryption, inverse permutation is carried out such that  $d = e^{-1}$ . The decryption transformation is:

$$D_d(c) = (d(c_1)d(c_2)...d(c_t)) = (m_1m_2...m_t) = m.$$

(2.3)

For an encryption scheme with block length t, the encryption function e which is a transposition function, where K is defined as the set of all permutation on the set  $\{1, 2...t\}$  can be shown as follows:

$$E_e(m) = (m_{e(1)}m_{e(2)}...m_{e(t)}) = (c_1c_2...c_t) = c.$$

(2.4)

For decryption, inverse permutation is carried out such that  $d = e^{-1}$ . The decryption function is:

$$D_d(c) = (c_{d(1)}c_{d(2)}...c_{d(t)}) = (m_1m_2...m_t) = m$$

(2.5)

Stream ciphers operate on streams of plaintext and ciphertext. They convert plaintext to ciphertext one bit at a time. Therefore, they can be considered as a very simple block cipher with block length equal to one. The encryption transformation  $E_e$  could be defined as follows, which makes use of a simple substitution cipher with block length equals to one:

$$c_i = E_{ei}(m_i), (2.6)$$

The keystream is defined as a sequence of symbols  $e_1e_2e_3...e_i \in K$ , where K is the key space for a set of encryption transformations. The keystream can be generated at random by an algorithm called keystream generator. The decryption transformation can be described as follows, where  $d_i$  denotes the inverse of  $e_i$ :

$$m_i = D_{di}(c_i). (2.7)$$

In general, block ciphers are more suitable for software implementations and stream ciphers are faster and require less complex implementation in hardware. Stream ciphers are more appropriate for situations where buffering is limited and error transmissions are high because they have little or no error propagation.

## 2.2 DES and Triple DES

The most popular symmetric key cryptographic algorithm is Data Encryption Standard (DES). DES is symmetric block cipher that uses 56-bit encryption key and has 64-bit block size. This is essentially an improvement of the algorithm "Lucifer" developed by IBM in the early 1970s [2]. In July 1977, the National Institute of Standards and Technology (NIST) adopted and issued DES as Federal Information Processing Standard Publication 46 (FIBS PUB 46) [3]. It provided standards and guidelines for this algorithm to be used by US Federal agencies. However, the standard could also be implemented and used by those outside the Federal

government, such as for commercial use. The American National Standards Institute (ANSI) approved DES as a voluntary standard in 1981 (ANSI X3.92) [4], calling it the Data Encryption Algorithm (DEA). Figure 2.3 shows the encryption process of DES.

Figure 2.3 DES Encryption

DES is a Feistel network, which means that a block of length n is divided into two halves: L and R. An iterated block cipher is defined where the outputs of the i<sup>th</sup> round is determined from the output of the previous round and are defined as follows:

$$L_i = R_{i-1} \tag{2.8}$$

$$R_{i} = L_{i-1} \oplus f(R_{i-1}, K_{i}) \tag{2.9}$$

where  $K_i$  is the sub-key for  $i^{th}$  iteration and f is an arbitrary function. Feistel function is invertible and so the same algorithm can be used for both encryption and decryption.

For DES encryption, the 64 bits input block will first undergo the initial permutation IP. The permutated input block becomes the input of a 16-stage complex key computation process. The output of the 16-stage computation plus a final stage of block interchange produce the preoutput block, which will then undergo the inverse of the initial permutation to provide the final encrypted output. The cipher function f operates on two blocks, the 32 bits  $R_n$  and the 48 bits  $K_n$  chosen from the 64-bit key and produces a block of 32 bits. This 32 bits block becomes the block R input for the next iteration. Figure 2.4 depicts the DES cipher function f and the function is described as follows:

$$f(R_{i-1}, K_i) = P(S(E(R_{i-1} \oplus K_i))), \tag{2.10}$$

The implementation of DES is relatively easy particularly on special purpose chip due to its repetitive nature.

Figure 2.4 DES inner function f

However, due to improvement in computational power, "single" 56-bit key DES has become less secure and so "single" DES has been phased out and is being replaced by Triple DES algorithm (TDEA) [5], which has an effective key length of 156 bits, even though the overall key length is 192 bits. This is because although the input key of DES is 64 bits, only 56 bits are actually used by the DES algorithm. The other 8 bits, which are not used by the algorithm, may be used for error detection and the least significant bit in each byte is a parity bit and is ignored. The procedure for encryption is the same as regular DES, but it is repeated three times and so TDEA is three times slower than single DES. The input block is first encrypted using DES algorithm with the first key (KEY1), the output will then become the input of the second stage where the block will be decrypted using the second key (KEY2). Finally, the output of the second stage will become the input of the third and last stage. The input block is encrypted using the third key (KEY3). The final result will then be used in the computation of the ciphertext. None of the intermediate results is revealed outside the cryptographic boundary.

DES is a hardware friendly algorithm due to its regular structure, which makes exploitation of parallelism by pipelining easy. DES and Triple-DES commercial

implementations are generally available in smart card IC design, such as mifare<sup>®</sup> pro X P8RF6008 by Philips [6]. This particular design makes use of a Triple-DES coprocessor to speed up the calculation time. According to the specifications, by using a co-processor, about three orders of magnitude of speed improvement could be achieved compared to software solutions and the total time for a triple-DES calculation to less than 35μs at 13.56MHz. Another example of Triple-DES IC smart card design is KS88C92008/4/2/1 by Samsung Electronics [7]. In this implementation, a specific Triple-DES module is included in the smart card design. The fastest DES execution time performed by this module is 77.9 μs at 4.52 MHz.

Even though DES was developed for implementation on hardware, many software implementations have been developed. However, DES implementation in software tends to be less efficient, an example of software implementation of DES can be found in [8]. In this report, the author shows the results of DES algorithm implementation using C code on the C6000 Digital Signal Processing platform and compiled on the Texas Instruments' Optimizing C Compiler where no assembly code is used. In this report, DES is implemented at data rates as high as 52.4 Mbits per second for DES and 22.3 Mbits per second for triple-DES on the C6201 McEVM (200 MHz). Using the C6211 DSK (150 MHz), data rates were measured as high as 38.8 Mbits per second for DES and 17.8 Mbits per second for triple-DES. The author found that using C code for DES implementation provides flexibility, and is a quick and inexpensive way to add encryption functionality to a design. Other DES software implementation examples can be found in [161] and [163].

## 2.3 Other Symmetrical Block Cipher Algorithm – IDEA & AES

In this section more symmetrical block cipher algorithm are introduced and they are IDEA and AES.

### 2.3.1 IDEA

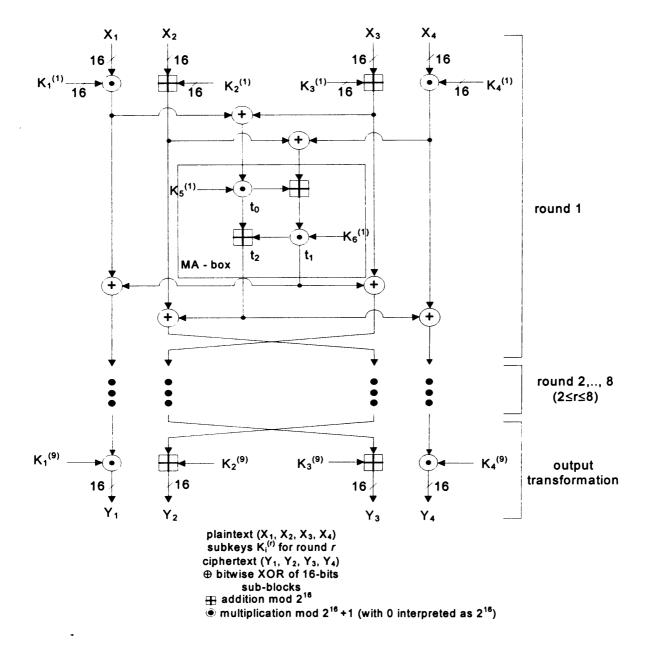

International Data Encryption Algorithm (IDEA) is a symmetrical block cipher algorithm with a 64-bit block length and a 128-bit input key. It was first proposed in 1990 by Xuejia Lai and James Massey and was called Proposed Encryption Standard (PES) [9]. It was then strengthened and renamed, from Improved Proposed Encryption Standard (IPES) to IDEA in 1992 [10]. Figure 2.5 shows the clock diagram of the IDEA algorithm. As in DES, IDEA is of the Feistel structure, it consists of eight iterations plus an output transformation only. The 64-bit input block is divided into four 16-bit sub-blocks and are denoted as  $X_1$ ,  $X_2$ ,  $X_3$ ,  $X_4$ . In the course of each iteration, the following events will take place:

- 1. Multiply plain text block  $X_1$  by the first sub-key  $K_1$

- 2. Add plain text block  $X_2$  with the second sub-key  $K_2$

- 3. Add plain text block  $X_3$  with the third sub-key  $K_3$

- 4. Multiply plain text block  $X_4$  by the fourth sub-key  $K_4$

- 5. XOR the results of step 1 and step 3

- 6. XOR the results of step 2 and step 4

- 7. Multiply the result of step 5 by the fifth sub-key  $K_5$

- 8. Add the results of step 6 and step 7

- 9. Multiply the result of step 8 by the sixth sub-key K<sub>6</sub>

- 10. Add the results of step 7 and step 9

- 11. XOR the results of step 1 and step 9

- 12. XOR the results of step 3 and step 9

- 13. XOR the results of step 2 and step 10

- 14. XOR the results of step 4 and step 10

Figure 2.5 Block Diagram of the IDEA algorithm

### 2.3.2 **AES**

In September 1997, NIST initiated the development of a new Encryption Standard – Advanced Encryption Standard (AES), they requested candidates develop a new algorithm strong enough to replace DES and Triple DES. On 26<sup>th</sup> November, 2001, NIST published a new federal standard known as FIPS PUB 197 [11], the chosen algorithm was called Rijndael [12].

The AES algorithm is a symmetric block cipher that is capable of using cryptographic keys of 128, 192, and 256 bits to encrypt and decrypt data in blocks of 128 bits. AES processes data in a group of eight (a byte), i.e., a sequence of eight bits is treated as one entity. Therefore, all the arithmetic operations required are carried out in finite field GF(2<sup>8</sup>). More details on arithmetic operations in GF(2<sup>8</sup>) are described in chapter 3.

## 2.4 Public Key Cryptography

As mentioned in section 2.1, secret key cryptography has a weakness of "key distribution problem" or "key management problem". This is caused by the fact that the same key is used for both encryption and decryption and therefore the key must be kept secret. Public key cryptography or asymmetric key cryptography overcomes this problem by using different encryption (e) and decryption (d) key pair so that confidentiality, data integrity, authentication and non-repudiation can be achieved. Figure 2.6 shows the schematic diagram of public key cryptography operations.

Figure 2.6 Schematic to show public key cryptography

### 2.4.1 Diffie-Hellman key agreement protocol

In 1976, Diffie and Hellman proposed a new cryptography system that makes use of public key with a key agreement protocol [13], which provided the ground for future development of public key cryptography. The key agreement protocol provides a means for two users to agree on a secret key over an insecure channel without prior arrangement. The security of the protocol depends on the discrete logarithm problem over a finite field GF(p) where p is a prime number. It has been proven that under certain assumptions breaking the Diffie-Hellman protocol is equivalent to computing discrete logarithms [14]. The Diffie-Hellman key agreement protocol involves a prime parameter p and a generator g, which is an integer smaller than p. Let:

$$n = g^k \bmod p \text{ for } 1 \le k \le p-1 \tag{2.11}$$

Therefore, k is:

$$k = \log_g n \mod p \text{ for } 1 \le n \le p-1$$

(2.12)

User A and user B can share a secret key by first of all generating a random private value a and b respectively, where both value a and b are from the set of integers  $\{1, ..., p-1\}$ . They then generate their respective public keys:

$$g^a \mod p$$

and  $g^b \mod p$  (2.13)

When the two users wish to communicate privately, they exchange their public keys.

A computes:

$$g^{ab} = (g^b)^a \bmod p \tag{2.14}$$

User B computes:

$$g^{ba} = (g^a)^b \bmod p \tag{2.15}$$

Since  $g^{ab} = g^{ba}$ , therefore they now have a shared key. It is assumed that the secret component  $g^{ab}$  is computationally infeasible to be worked out providing the random prime number p is large enough. In the same paper, Diffie and Hellman also suggested the idea of using digital signatures to ensure the authenticity of the data. Much research has been done to improve the authenticity of the data, Diffee *et al* proposed an authentication and authenticated key exchange protocol called station-to-station (STS) in 1992 [15].

Public key cryptography works on the assumption that it is computationally infeasible to work out decryption key d given the encryption key e. Encryption  $E_e$  is being viewed here as a trapdoor one-way function with the decryption key d being the trapdoor information necessary to compute the inverse function, hence allow decryption. Given that it is not necessary for the encryption key e to be kept secret, therefore it can be made public and hence it is called the public key. However, the corresponding decryption key must be kept secret and hence it is called the private key. The public key allows any entity to send encrypted messages to the same

recipient using the same public key, only the intended recipient can decrypt the message using their private key.

It is particularly important for public key cryptography to ensure the authenticity of the public keys to avoid protocol failure where the origin of the public keys are not known. Without appropriate measures, an adversary could impersonate the intended recipient B and issue false public key to sender A. The adversary will then be able to intercept and decrypt the message with the private key before sending the message to B, which is now encrypted with B's public key. One solution to such problem is by making use of Digital Signature Algorithm (DSA). The concept of digital signature algorithm is as follows:

Sender A "signs" the message set  $M = \{m_1, m_2, m_3, ...\}$  by using a signature transformation function  $S_A$ , which will be kept secret by the sender. The signature transformation function transforms the message set to give signature set  $S = \{s_1, s_2, s_3, ...\}$ . This transformation can be interpreted as follow:

$$s = S_{\mathcal{A}}(m) \tag{2.16}$$

Sender A transmits the signature pair (m; s) where s is the signature for message m. The recipient can verify the signature by obtaining the verification function  $V_A$  from A. Recipient B computes the following to verify the signature:

$$u = V_A(m; s) \tag{2.17}$$

The recipient accepts the signature when the signature pair (m; s) matches; otherwise, the signature is rejected.

In general, DSA enables digital signatures to be generated and verified. It is a pair of large numbers, which form the key pair, that are computed according to the specified algorithm, within parameters to verify the authenticity of the signature and hence the integrity of the data.

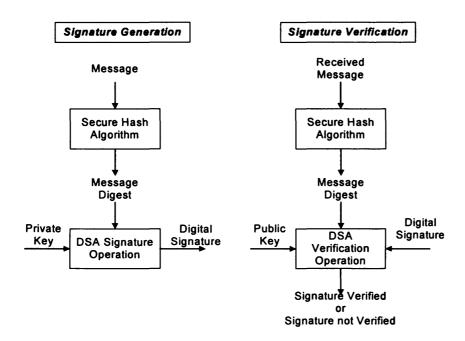

In practice, a hash function, sometimes called one-way hash function, is used in the signature generation process to obtain a condensed version of data called a message digest. Figure 2.7 shows digital signature generation and verification with a Secure Hash Algorithm. The Secure Hash Standard that is specified by NIST is known as FIPS PUB 180-1 [16] and the Secure Hash Algorithm is called SHA-1.

Figure 2.7 DSA with SHA

The hash function is a process that produces a condensed version of data of arbitrary length (signed or pre-signed message), called the hash value. In the case of FIPS 180-1 standard, the input message must be less than 2<sup>64</sup> bits in length, the output of the Secure Hash algorithm is called the message digest, and is 160 bits long. Hash function has the following properties:

- 1. It is relatively easy to compute for any given input.

- 2. It is one-way.

- 3. It is collision-free this means that the Hash function is computationally infeasible to find any two messages x and y such that H(x) = H(y).

For the digital signature generation process, the message digest becomes one of the two inputs to the digital signature operation, which generates the digital signature as the output. The digital signature and the signed message are sent to the verifier.

For digital signature verification process, the message digest is one of the three inputs to the digital signature verification operation, which verifies whether the signature matches or not. The Hash function used must be the same as the one used for signature generation.

Note that for digital signature operation with signature hash algorithm, only the hash value is signed. Compared with processes where the message is signed directly, signing just the message digest saves time and space. With the direct signing method, the message needs to be split into blocks of appropriate size and each block is signed individually.

Various other signature schemes exist, such as, the ElGamal signature scheme [17] and the Digital Signature Standard (DSS) FIPS 186 published by NIST in 1991 [18], which is a variant of ElGamal scheme. Another well-known digital signature scheme is RSA signature scheme, which was first introduced in 1977 [19] [20]. In July 2002, Alfred Menezes published Evaluation of Security Level of Cryptography: RSA Signature Schemes (PKCS#1 v1.5, ANSI X9.31, ISO 9796), which gave a good overview of the security of RSA signature schemes [21]. Digital Signature Standard (DSS) published by NIST on 27 January 2000 [22] described three algorithms for digital signature generation and verification. They are the following:

- 1. Digital Signature Algorithm (DSA)

- 2. RSA digital signature algorithm

- 3. Elliptic Curve Digital Signature Algorithm (ECDSA)

## 2.4.2 RSA

RSA cryptosystem was invented by R. Rivest, A. Shamir, and L. Adleman in 1978 [20], and is one of the most widely used public key cryptosystems. As mentioned previously, RSA not only encrypts and decrypts messages; it can also be used for digital signatures. Its strength is based on integer factorization problem, where a large number is to be factorized.

Prior to encryption, the RSA public key and the corresponding private key have to be generated before the entity A could encrypt the message with entity B's public key. The procedure for RSA key generation is as follows:

- 1. Generate two large random and distinct prime numbers p and q, for maximum security, p and q should be of equal length.

- 2. Compute the product:

$$n = pq \tag{2.18}$$

and

$$\emptyset = (p-1)(q-1) \tag{2.19}$$

- 3. Select a random integer encryption exponent e,  $1 < e < \emptyset$ , such that  $gcd(e, \emptyset) = 1$ , i.e. they are relatively prime.

- 4. Use the extended Euclidean algorithm (see Appendix 1) to compute the unique integer decryption exponent d,  $1 < d < \emptyset$ , such that  $ed = 1 \mod \emptyset$ , hence, d and n are also relatively prime.

$$d = e^{-1} \bmod ((p-1)(q-1)) \tag{2.20}$$

- 5. B's public key is (n, e); B's private key is d.

- 6. p and q could now be discarded and should never be revealed.

A can now encrypt a message for B, and B can decrypt using the private key. The RSA encryption and decryption procedures are as follows:

# 1. Encryption:

- a. Obtain B's authentic public key (n, e).

- b. Represent the message as an integer m in the interval [0; n-1].

- c. Compute  $c = m^e \mod n$

- d. Send the ciphertext c to B.

# 2. Decryption:

A decrypts plaintext m from c by carrying out the following:

$$m = c^d \mod n$$

.

The assumption is that the RSA function is a trapdoor one-way function and the private key is the trapdoor. In order to compute  $c = m^e \mod n$  efficiently, a "Repeated square-and-multiply algorithm for exponentiation in  $Z_n$ " could be used (see Appendix 1). This kind of modular exponentiation is performed each time a part of the message is encrypted/decrypted. Both e and n are very large integers and so this operation is very computationally intensive, however, the Chinese Remainder Theorem (CRT) (see Appendix 1) can be used as a method for computing the modular exponentiation. By using CRT, the large modulo exponentiation can be split into two smaller exponentiations, namely over p and over q, which are already known. Fermat's Little Theorem (see Appendix 1) can be used to further reduce the size of the problem.

Even with these improvements, RSA cryptography is slower than the commonly used symmetric-key encryption algorithms such as DES (typically, in software, DES is 100 times faster than RSA and in hardware can be between 1,000 to 10,000 times faster depending on the implementation). In practice, RSA encryption is most commonly

used for the transport of symmetric-key encryption algorithm keys and for the encryption of small data items.

RSA Laboratories' recommended standards can be found in [23]. RSA Laboratories recommended in 1999 that the current industry standards for the RSA algorithm, such as the ANSI X9.31 [24] banking standard for RSA signatures, require a minimum of 1024 bits for an additional level of security.

When entity B wants to send a signed message M to entity A, first B computes his signature for message M with his private decryption key  $(D_B)$ :

$$S = D_{R}(M) \tag{2.21}$$

B then encrypts the signed message using A's public key:

$$C = E_A(S) \tag{2.22}$$

A can decrypt the encrypted signed message with his private decryption key  $(D_A)$ :

$$S = D_A(C) \tag{2.23}$$

$$S = D_A(E_A(S)) \tag{2.24}$$

A can recover the message using B's public encryption key  $E_B$ :

$$M = E_B(S) \tag{2.25}$$

$$M = E_R(D_R(M)) \tag{2.26}$$

Hence, RSA signature scheme recovers the message from the signature, the sender does not need to send the encrypted message separately with the signature.

# 2.4.3 RSA Problem (RSAP)

The RSA Problem is defined as follows, given a positive integer n = pq, where p and q are two distinct odd primes; a positive integer e such that gcd(e; (p-1)(q-1)) = 1; Find the plaintext integer m such that  $m^e \equiv c \pmod{n}$ . Therefore, one has to find the  $e^{th}$  roots modulo a composite integer n. There is exactly one  $m \in (0, 1, ..., n-1)$  for each integer  $c \in (0, 1, ..., n-1)$ . Rivest and Kaliski [25] provides a good insight into the RSA Problem.

RSA assumption is that the security of RSA depends on large integer factorisation problem: RSA Problem becomes difficult to solve when the modulus n is sufficiently large and both p and q are two large random and distinct prime numbers, therefore both the plaintext m and ciphertext c is a random number between 0 to n-1. It is important for plaintext m to be random and be over a wide range of [0, n-1], otherwise an adversary can compute m by trying all possible values for m.

Factoring is believed to be a mathematically difficult problem, i.e. NP complete, it has not yet been mathematically proven and an efficient factoring algorithm remains to be discovered, however, this is widely believed to be unlikely.

It has been said that the RSA problem is closely related to factoring, Boneh and Venkatesan show the RSA problem may not be equivalent to integer factorisation when the public exponent is small [26], an example is given where public exponent e = 3. Another RSA problem consideration is that, it is not necessarily true that a large number is more difficult to factor than a small number. However, it is known that a number with large prime factors is more difficult to factor than a number with small prime factors; hence, large modulus should be used for an RSA cryptosystem. There are other rules in choosing the modulus in order to preserve security of RSA, as mentioned before, the two primes, p and q, which form the modulus should be of roughly equal length. In addition, one should be aware that if the two primes are too close together, it increases the ease of determining the values by the adversary, since:

If  $p \approx q$ , let mean of p and q = m = [(p+q)/2]; then p can be determined as:

$$p = m \pm \sqrt{(m^2 - n)} \; ; \tag{2.27}$$

Where n = pq.

However, the probability of this happening in reality is low. Another concern over increasing key size is that the overall RSA algorithm operations will also take longer. For example, doubling the length of the modulus will on average increase the time required for encryption and signature verification, (which made use of the public key) by a factor of four, and increase the time taken by the decryption and signature operation, (which make use of the private key) by a factor of eight. The reason why public key operations are affected less than private key operations is that the public exponent can remain fixed while the modulus is increased, whereas the length of the private exponent increases proportionally. One should choose a modulus (key) length with the following considerations:

- 1. The value of the protected data and the length of time it needs to be protected;

- 2. How powerful are the threats.

# 2.4.4 Security of RSA

In the previous section, the security of RSA cryptosystems relating to RSA problem and factoring was discussed. In this section, more security issues and attacks on RSA cryptography will be reviewed. Boneh provides a good general insight into security of RSA encryption [27].

# 1.- Attack relating to RSA factoring problem / Chosen Cipher Attack

As mentioned previously, public key cryptography is susceptible to chosen cipher attacks, RSA is also prone to this type of attack. Some characteristics of RSA can be exploited to perform chosen cipher attack,

such as multiplicative property of RSA. This is described in [28]. More chosen cipher attack on RSA are described in [29] and [30].

An effective method to defeat such an attack is known as Optimal Asymmetric Encryption Padding (OAEP) [31]. The objective of OAEP is to mask the plaintext message M with the hash G of a random number r and this string of masked data is concatenated with the XOR of hash H of the mask data  $(M \oplus G(r))$  with random string r as shown follows:

$$[M \oplus G(r)] [r \oplus H(M \oplus G(r))] \tag{2.28}$$

|| denotes concatenation. Different variations of OAEP can be found in [32] and [33].

### 2. Small Encryption Exponent e

The advantage of using small encryption exponent e, such as e=3 is that faster public key encryption and faster public key signature verification can be gained. However, it has been shown by Hastad [34] that having small encryption key could be insecure when the same plaintext is sent to many different recipients. Each recipient has their own public moduli, since these moduli are most likely pair-wise relatively prime, therefore an attacker could quite easily compute the plain text using Gauss's algorithm. In such cases, small encryption exponent should be avoided.

#### 3. Forward Search Attack

As mentioned previously, the range of message must be large and unpredictable, otherwise an adversary can decrypt a ciphertext by encrypting all possible plaintext. One method to avoid this attack is to append pseudorandom bit-string to the pre-encrypted plaintext message.

### 4. Small Decryption Exponent d

To speed up RSA signature generation or decryption time, one may choose to use small decryption exponent d, however, Boneh and Durfee [35] shows that when the private key used in the RSA public key cryptosystem is less than  $N^{0.25}$ , the system is insecure. Wiener [36] also proposed an attack on RSA when small decryption exponent d is used. To avoid this attack, the decryption exponent d should be roughly the same size as n.

## 5. Multiplicative Properties

Let  $m_1$  and  $m_2$  be two plaintext messages and let  $c_1$  and  $c_2$  be their respective RSA encryption:

$$(m_1 m_2)^e \equiv m_1^e m_2^e \equiv c_1 c_2 \pmod{n}$$

(2.29)

This means that the plaintext  $m = m_1 m_2 \mod n$  and the corresponding ciphertext is  $c = c_1 c_2 \mod n$ . Due to this property of RSA, adaptive chosen cipher attack can be performed, and the adversary can retrieve the plaintext. This can be avoided by applying pre-defined structure constraints on the plaintext. All ciphertext decrypted to a message which does not possess the same pre-defined structure will be rejected as fraudulent.

### 6. Common Modulus Attack

RSA system where the users within an organization would share the public modulus is susceptible to this type of attack. For example, the administration would choose the public modulus n, two users would then have their encryption and decryption key generated  $((e_1, n), d_1)$  and  $((e_2, n), d_2)$ ) from the same modulus. The eavesdropper can recover the plaintext by doing the following:

$$C_1 = M^{el} \bmod n \tag{2.30}$$

$$C_2 = M^{e^2} \bmod n \tag{2.31}$$

$$(e_1)a + (e_2)b = 1$$

if  $gcd(e_1, e_2) = 1$  (2.32)

$$M = C_1^{\ a} + C_2^{\ b} \bmod n \tag{2.33}$$

To avoid this attack each entity should choose its own RSA modulus n. Since any knowledge of encryption and decryption key pair allow for the factorisation of the modulus n.

# 7. Cycling Attack

Given  $c = m^e \mod n$ , there exists a k such that  $c^{e^k} \mod n = c$ , so  $c^{e^{k-1}} \mod n = m$ .  $c^{e^k} \mod n$  is then computed until c is obtained and the previous power is the message. However, this attack is considered non-threatening to the security of RSA since factoring n is assumed to be intractable.

### 8. Message Concealing

A message is unconcealed when it encrypts back to itself, i.e.  $m^e \equiv m \pmod{n}$ , however, this cannot be avoided since there will always be some messages which are unconcealed, such as, when m = 0, m = 1 and m = n-1. Even though this might be the case, it does in actuality pose a threat since the proportion of the unconcealed message is small as p and q are randomly chosen prime numbers, and e is also chose at random.

# 2.4.5 ElGamal

The ElGamal system [17] is a public-key cryptosystem, which unlike RSA algorithm is based on the discrete logarithm problem, where the security of RSA is based on integer factorisation. It is commonly used for both encryption and signature. The ElGamal encryption algorithm is similar in nature to the Diffie-Hellman key

agreement protocol, the system contains a prime integer p and an integer called generator g, whose power modulo p generates a large number of elements. Each entity creates a public key and a corresponding private key. Entity A creates the key pair and sends public key information to entity B. B will then encrypt the message with A's public key. A decrypts the message with his/her own private key. All entities can choose to use the same prime p and generator g. If common parameters are chosen, they do not need to be published as part of a public key. The advantage of having a common parameter is that the computation can be sped up by using precomputations. The disadvantage is that a larger moduli p may be needed in case of security being compromised.

The ElGamal system is based on discrete logarithm problems like the Diffie-Hellman system. For any cryptographic system that is based on discrete logarithm problems, the chosen large prime p must be chosen such that (p-1) has at least one large prime factor, otherwise the security of the system will be compromised. Discrete logarithm problems apply to mathematical structures called groups, where a group consists of a set G which could be finite or infinite, together with a binary operation called group multiplication. This group multiplication is defined as:

$$*G \times G \to G$$

(2.34)

This means that the product of a\*b is  $\in G$  for any two elements a and  $b \in G$ . A group consists of the following properties:

- 1. Associatively: The operation \* is associative, i.e.  $a^*(b^*c) = (a^*b)^*c$  for any  $a, b, c, \in G$ .

- 2. Identity element: For each element  $a \in G$ , there is an identity element where a\*e = e\*a = a.

- 3. Inverse element: For each element  $a \in G$ , there is an inverse element, such that a\*b = b\*a = e which is the identity element where  $b \in G$ .

The group G is said to be closed for all  $a, b \in G$ ,  $a^*b \in G$ , also the group G is said to be Abelian (or commutative) if  $a^*b = b^*a$  for all  $a, b \in G$ .

For  $g \in G$  and a number n,  $g^n$  means that g is multiplied itself n times, e.g.  $g^3 = g * g * g$  and the discrete logarithm problem is defined as follows:

Let  $g \in G$  and  $h \in G$ , find the value x such that:

$$g^x = h \tag{2.35}$$

The basic ElGamal Encryption scheme is defined as follows:

- 1. Key generation for ElGamal public key encryption: