A comparison of logarithmic and floating-point number systems implemented on Xilinx Virtex-II field-programmable gate arrays

UMI Number: U584674

### All rights reserved

### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

### UMI U584674

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

## DECLARATION

| being concurrently submitted in candidature for any degree. |                          |                                    |  |

|-------------------------------------------------------------|--------------------------|------------------------------------|--|

| Signed                                                      | l¥/c4                    | (candidate)                        |  |

| Date                                                        |                          |                                    |  |

| STATEMENT 1                                                 |                          |                                    |  |

| This thesis is the result of m                              | y own investigations, e  | xcept where otherwise stated.      |  |

| Other sources are acknowled                                 | lged by footnotes givin  | g explicit references. A           |  |

| bibliography is appended.                                   |                          |                                    |  |

|                                                             |                          |                                    |  |

| Signed Date                                                 | 14/04                    | (candidate)                        |  |

| Date                                                        | لرر                      |                                    |  |

|                                                             |                          |                                    |  |

| STATEMENT 2                                                 |                          |                                    |  |

| I hereby give my consent for                                | my thesis, if accepted   | , to be available for photocopying |  |

| and for inter-library loan, an                              | d for the title and sumr | nary to be made available to       |  |

| outside organisations.                                      |                          | •                                  |  |

| •                                                           | 1                        |                                    |  |

| Signed Date                                                 | 14/C4                    | (candidate)                        |  |

| Date                                                        | 4.                       |                                    |  |

|                                                             |                          |                                    |  |

This work has not previously been accepted in substance for any degree and is not

### Summary

The aim of this thesis is to compare the implementation of parameterisable LNS (logarithmic number system) and floating-point high dynamic range number systems on FPGA. The Virtex/Virtex-II range of FPGAs from Xilinx, which are the most popular FPGA technology, are used to implement the designs. The study focuses on using the low level primitives of the technology in an efficient way and so initially the design issues in implementing fixed-point operators are considered. The four basic operations of addition, multiplication, division and square root are considered. Carryfree adders, ripple-carry adders, parallel multipliers and digit recurrence division and square root are discussed. The floating-point operators use the word format and exceptions as described by the IEEE std-754. A dual-path adder implementation is described in detail, as are floating-point multiplier, divider and square root components. Results and comparisons with other works are given. The efficient implementation of function evaluation methods is considered next. An overview of current FPGA methods is given and a new piecewise polynomial implementation using the Taylor series is presented and compared with other designs in the literature. In the next section the LNS word format, accuracy and exceptions are described and two new LNS addition/subtraction function approximations are described. algorithms for performing multiplication, division and powering in the LNS domain are also described and are compared with other designs in the open literature. Parameterisable conversion algorithms to convert to/from the fixed-point domain from/to the LNS and floating-point domain are described and implementation results given. In the next chapter MATLAB bit-true software models are given that have the exact functionality as the hardware models. The interfaces of the models are given and a serial communication system to perform low speed system tests is described. A comparison of the LNS and floating-point number systems in terms of area and delay is given. Different functions implemented in LNS and floating-point arithmetic are also compared and conclusions are drawn. The results show that when the LNS is implemented with a 6-bit or less characteristic it is superior to floating-point. However, for larger characteristic lengths the floating-point system is more efficient due to the delay and exponential area increase of the LNS addition operator. The LNS is beneficial for larger characteristics than 6-bits only for specialist applications that require a high portion of division, multiplication, square root, powering operations and few additions.

### Thank you...

In memory of my father, who passed away on the 8th February 2003.

My girlfriend Asmah, for her love, support and sanity checking.

My mum, for not asking stupid questions, financial support and for being who she is so I can achieve my goals.

My brother, Councillor Rob Lee for more sanity checking and a cheap place to stay.

Neil Burgess (Icera Semiconductor and Cardiff University), for having faith in my ability when all seemed lost and for the support provided in every aspect of my PhD 'life'.

Richard Walke (QinetiQ Limited), I am very grateful for the many research area suggestions and for the many helpful discussions. I feel lucky to have had his support, as this thesis would *definitely not* have been possible without the level of motivation and dedication he promotes.

Sponsors QinetiQ (formerly, DERA Defence Research and Evaluation Agency), for the three years of financial support and for the excellent company work experience.

RTSL team and everyone else at QinetiQ, who made my periods of work at QinetiQ a very enjoyable experience.

Lai Sze Au (Fellow PhD student and friend).

Nikos Mallios (Fellow PhD student and friend), for many late night discussions, words of encouragement and excellent hospitality.

Wayne Luk (Imperial College, London), for being a friendly face, and offering much support at many PLD conferences. A true research ambassador.

David Defour (ENS, Lyon), for being a good friend on my visit to ENS, Lyon, France.

Ken Lever (Cardiff University), for many interesting and help mathematical and DSP discussions, and for the presentation contribution at Asilomar 2003 (a close one!).

Arnold Tisserand (ENS, Lyon), for allowing me to have a month stay at ENS Lyon (away from the rain), which inspired many a good idea.

Jean-Michel Muller (ENS, Lyon), the head of ENS Lyon.

Braden Philips (Cardiff University), a nice guy with many good suggestions.

Matthew Patterson, George Blackwell, Wing Yau and Ross Townend.

Tempus fugit

# **Contents**

| Cha | pt  | er 1                 | Introduction                                          | 1  |

|-----|-----|----------------------|-------------------------------------------------------|----|

| 1   | .1  | Progr                | ammable logic                                         | 1  |

| 1   | .2  | A bri                | ef FPGA technology history and overview               | 2  |

| 1   | .3  | FPG                  | A design flow                                         | 3  |

| 1   | .4  | Aim                  | of thesis: FPGA and high dynamic range number systems | 4  |

| 1   | .5  | Struc                | ture of the Xilinx Virtex and Virtex-II FPGAs         | 6  |

| 1   | .6  |                      | is organisation and chapter contribution summary      |    |

| Cha | nt  |                      | Fixed-point                                           |    |

|     | 2.1 |                      | ats                                                   |    |

|     | 2.2 |                      | ibution of fixed-point values                         |    |

|     | 2.3 |                      | l-point addition                                      |    |

|     |     |                      | A addition                                            |    |

| 2   |     | rrg.<br>2.4.1        | Add (addition)                                        |    |

|     |     | 2.4.2                | Sub (subtraction)                                     |    |

|     |     | 2.4.3                | Add/Sub (addition/subtraction)                        |    |

|     |     | 2.4.4                | Add/Sub/Zero (addition/subtraction/addition of zero)  |    |

|     | 2   | 2.4.5                | AddMux                                                |    |

|     | 2   | 2.4.6                | SubMux                                                | 14 |

|     | 2   | 2.4.7                | AddSubMuxConst                                        | 14 |

|     | 2   | 2.4.8                | Other configurations                                  | 15 |

|     | 2   | 2.4.9                | Compact serial adders                                 | 15 |

| 2   | 2.5 | FPG                  | A carry free addition                                 | 16 |

|     | 2   | 2.5.1                | [3:2] CSA (carry-save adder)                          | 16 |

|     | 2   | 2.5.2                | Carry-save adder/subtracter                           | 16 |

|     | 4   | 2.5.3                | High-radix carry-save adders                          |    |

|     | 2   | 2.5.4                | [4:2] CSA (carry-save adder)                          |    |

|     |     | 2.5.5                | New [4:2] CSA mapping                                 |    |

|     |     | 2.5.6                | Signed-digit addition                                 |    |

|     |     | 2.5.7                | Signed-digit to conventional digit addition           |    |

|     |     | 2.5.8                | Signed-digit and conventional digit adder/subtracter  |    |

|     |     | 2.5.9<br>2.5.10      | Signed-digit to signed-digit addition/subtraction     | 24 |

|     | 4   | 2. <i>3.</i> 10<br>T | epresentation                                         | 25 |

|     | ,   |                      | Conclusion                                            |    |

| 2   |     |                      | d-point multiplication                                |    |

| -   |     |                      | Unsigned multiplication                               |    |

|     |     |                      | <del>-</del>                                          |    |

| 2.6.2 Signed multiplication                                                         | 27 |

|-------------------------------------------------------------------------------------|----|

| 2.6.2.1 Signed-magnitude multiplication                                             |    |

| 2.6.2.2 Two's complement multiplication                                             | 27 |

| 2.6.3 High radix partial product generation                                         | 28 |

| 2.6.4 Multiplier structure                                                          | 28 |

| 2.7 FPGA multiplication                                                             | 29 |

| 2.7.1 Parallel multiplication                                                       |    |

| 2.7.2 Dedicated Virtex FPGA multiplier logic                                        |    |

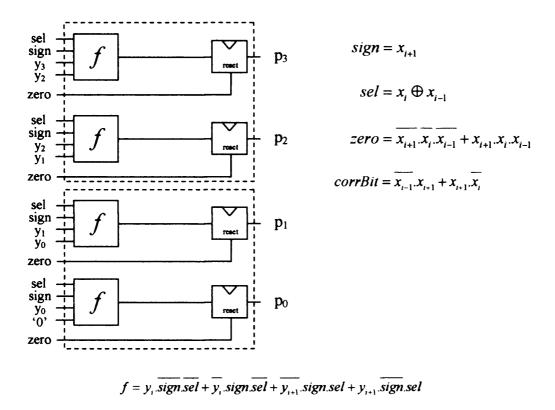

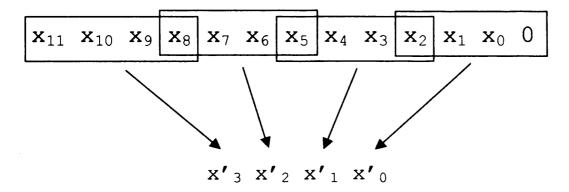

| 2.7.3 New radix-4 partial product generator mapping                                 |    |

| 2.7.4 Booth encoding                                                                |    |

| 2.7.4.1 Radix-4 algorithm (Booth-2)                                                 |    |

| 2.7.4.2 New Booth-2 partial product generator                                       |    |

| 2.7.4.3 Radix-8 algorithm (Booth-3)                                                 |    |

| 2.7.4.4 Higher radix algorithms                                                     |    |

| 2.7.5 Basic Virtex FPGA multiplication structure                                    |    |

|                                                                                     |    |

| 2.7.6 Summary                                                                       |    |

| 2.7.7 Virtex-II FPGA embedded multipliers                                           | 36 |

| 2.7.7.1 Splitting large multiplications across multiple multiplier                  | 26 |

| blocks                                                                              |    |

| 2.7.7.2 Signed multiplication                                                       | 38 |

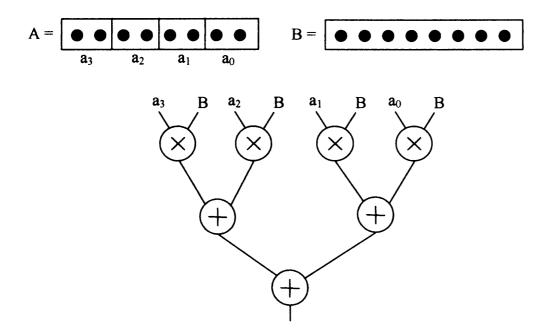

| 2.7.7.3 Improving the utilisation of embedded multipliers for large multiplications | 20 |

| 2.7.7.3.1 The two-way method                                                        |    |

| 2.7.7.3.2 Chapman method                                                            |    |

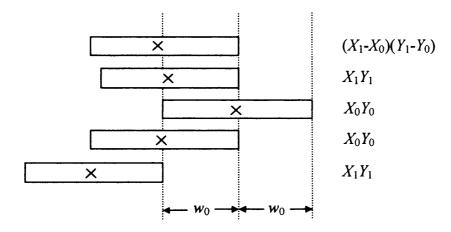

| 2.7.7.3.3 Beuchat method                                                            |    |

| 2.7.7.3.4 New method                                                                |    |

| 2.7.7.4 Implementation results                                                      |    |

| 2.7.7.5 Comparison                                                                  |    |

| 2.7.8 Squaring: a special case of multiplication                                    |    |

| 2.7.8 Squaring: a special case of multiplication                                    | 77 |

| multiplier                                                                          |    |

| 2.7.8.2 Implementation results                                                      | 50 |

| 2.7.8.3 Conclusion                                                                  |    |

|                                                                                     |    |

| 2.8 Fixed-point division                                                            |    |

| 2.8.1 Digit recurrence (sequential) division                                        | 52 |

| 2.8.1.1 Restoring                                                                   | 52 |

| 2.8.1.2 Non-restoring                                                               |    |

| 2.8.1.3 SRT digit recurrence division                                               | 33 |

| 2.9 FPGA digit recurrence division                                                  | 56 |

| 2.9.1 LCPQ (LUT columns per quotient bit) metric                                    | 56 |

| 2.9.1.1 Radix-2                                                                     | 56 |

| 2.9.1.2 Radix-4                                                                     |    |

| 2.9.1.3 Radix-8                                                                     |    |

| 2.9.1.4 Radix-16                                                                    |    |

| 2.9.1.5 Higher radices                                                              |    |

| 2.9.1.6 Summary                                                                     | 61 |

| 2.9.2 Pipelining issues                                          | 62 |

|------------------------------------------------------------------|----|

| 2.9.3 Quotient digit selection                                   | 62 |

| 2.9.4 Basic stage delay analysis                                 | 63 |

| 2.9.5 Summary                                                    | 64 |

| 2.9.6 Pre-scaling                                                |    |

| 2.9.6.1 A minimally redundant radix-8 divider with non-redundant |    |

| residual and pre-scaling                                         |    |

| 2.9.6.2 Divisor scaling region                                   |    |

| 2.9.6.3 Radix-8 divider scale region and scale values            |    |

| 2.9.6.4 Implementation results                                   |    |

| -                                                                |    |

| 2.10 Fixed-point square root.                                    |    |

| 2.10.1 Digit recurrence (sequential) square root                 |    |

| 2.10.1.1 Restoring         2.10.1.2 Non-restoring                |    |

| 2.10.1.2 Non-restoring                                           |    |

| 2.10.1.4 Summary                                                 |    |

| 2.11 FPGA non-restoring square root                              |    |

| 2.11.1 Other square root algorithms                              |    |

| 2.11.1 Other square root argorithms                              | ,  |

| Chapter 3 Floating-point                                         | 78 |

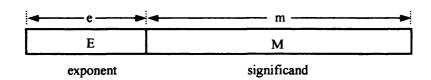

| 3.1 Format                                                       | 78 |

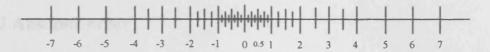

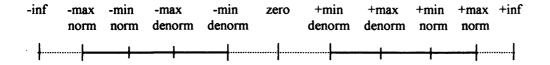

| 3.2 Distribution of floating-point values                        |    |

| 3.3 Absolute error                                               |    |

| 3.4 The IEEE floating-point standard                             |    |

| 3.4.1 IEEE std-754 word format                                   |    |

|                                                                  |    |

| 3.4.2 IEEE std-754 value types                                   |    |

| 3.4.3 IEEE std-754 rounding modes                                |    |

| 3.4.4 IEEE std-754 exceptions                                    |    |

| 3.4.5 Arithmetic operators                                       |    |

| 3.4.6 IEEE std-754 single and double formats                     |    |

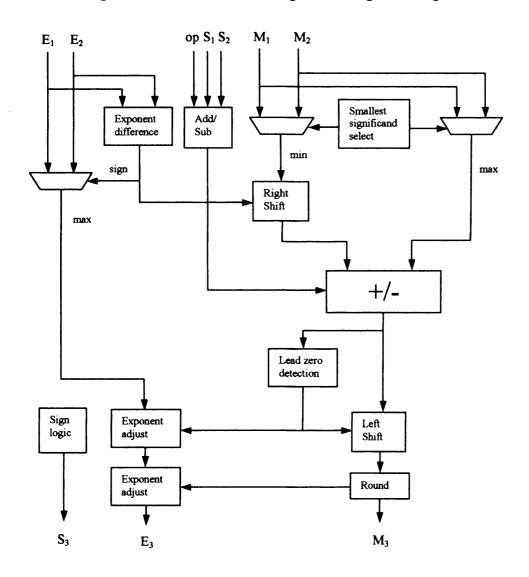

| 3.5 Floating-point addition/subtraction                          |    |

| 3.5.1 Vanilla algorithm                                          | 86 |

| 3.5.2 Dual-path (near and far path) algorithm                    | 88 |

| 3.5.2.1 Near path                                                | 88 |

| 3.5.2.2 Far path                                                 |    |

| 3.5.2.3 Far path right shifting                                  |    |

| 3.5.2.5 Dual-path summary                                        |    |

| 3.5.3 Detailed component and algorithm discussion                |    |

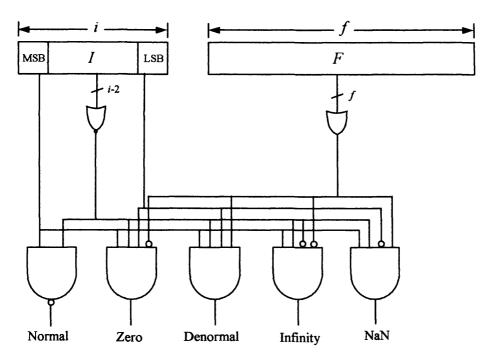

| 3.5.3.1 Special value detection                                  | 94 |

| 3.5.3.2 IEEE std-754 floating-point addition anomalies           | 96 |

| 3.5.3.3 Hidden bit insertion                                     | 97 |

| 3.5.3.4 Absolute exponent difference                             | 97 |

| 3.:      | 5.3.5 Addition/subtraction operation decision               | 97  |

|----------|-------------------------------------------------------------|-----|

|          | 5.3.6 Selection of the largest/smallest operand significand |     |

| 3.:      | 5.3.7 Right shifter                                         |     |

|          | 5.3.8 Left shifter                                          |     |

| 3.:      | 5.3.9 Lead zero detector                                    |     |

|          | 3.5.3.9.1 Comparison                                        |     |

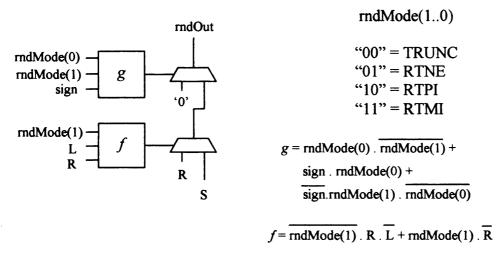

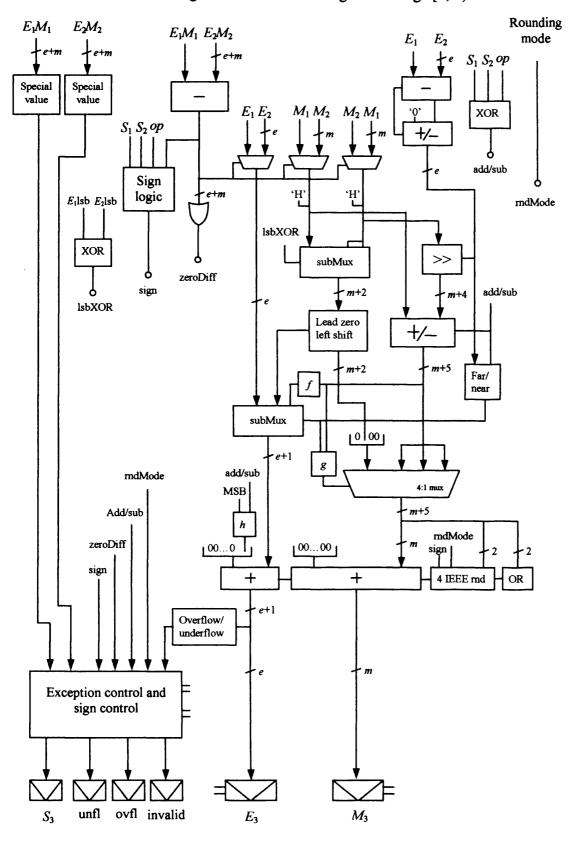

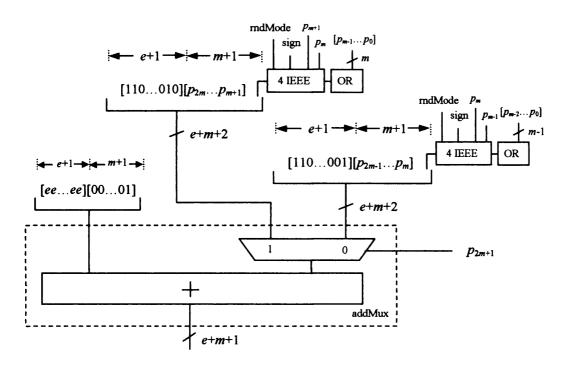

|          | 5.3.10 Rounding and exponent correction                     |     |

|          | 5.3.11 Sign logic                                           |     |

|          | 5.3.13 Overflow/underflow detection                         |     |

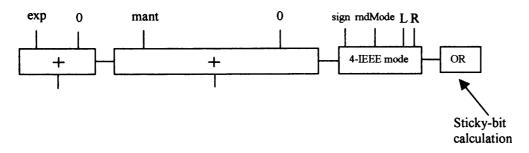

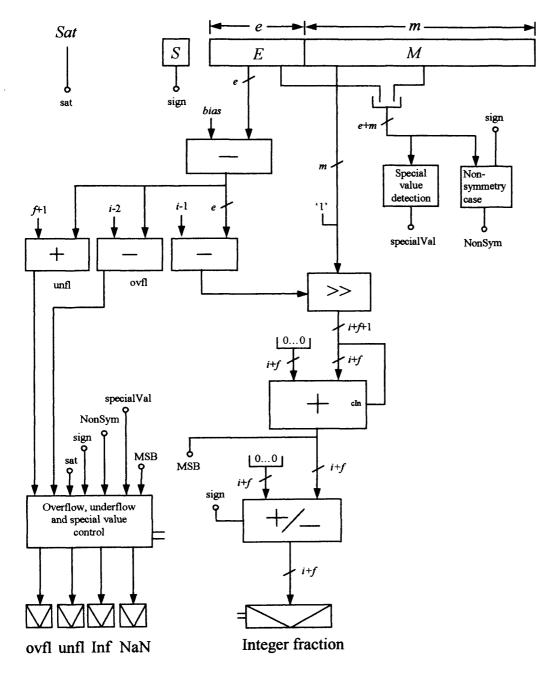

|          | 5.3.14 Complete floating-point adder diagram                |     |

|          | ting-point multiplication                                   |     |

| 3.6.1    | Special values                                              |     |

| 3.6.2    | Exponent bias                                               |     |

| 3.6.3    | Significand multiplication                                  |     |

| 3.6.4    | Normalising and rounding                                    |     |

| 3.6.5    | Overflow and underflow detection                            |     |

| 3.6.6    | Sign logic                                                  |     |

|          |                                                             |     |

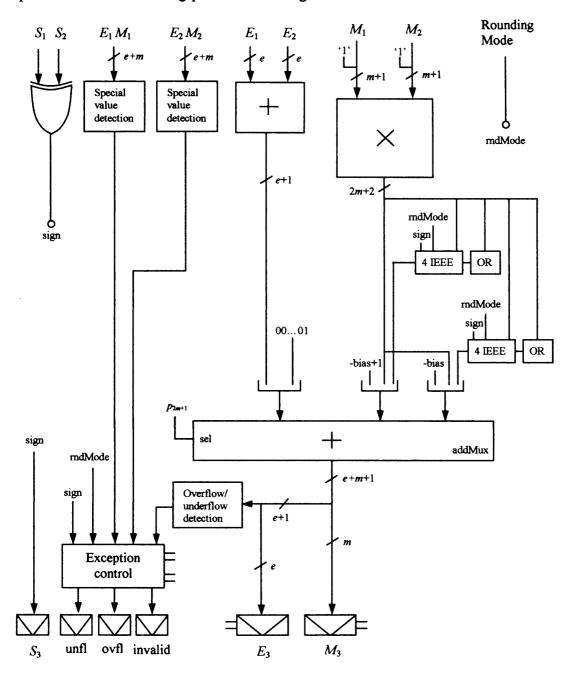

| 3.6.7    | Complete floating-point multiplier diagram                  |     |

|          | ting-point division                                         |     |

| 3.7.1    | Special values                                              |     |

| 3.7.2    | Exponent bias                                               |     |

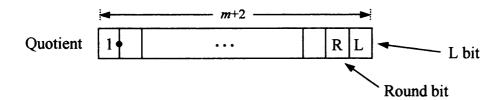

| 3.7.3    | Significand division                                        | 112 |

| 3.7.4    | Rounding and quotient correction                            | 113 |

| 3.7.5    | Overflow and underflow detection                            | 114 |

| 3.7.6    | Sign logic                                                  | 115 |

| 3.7.7    | Complete floating-point divider diagram                     | 115 |

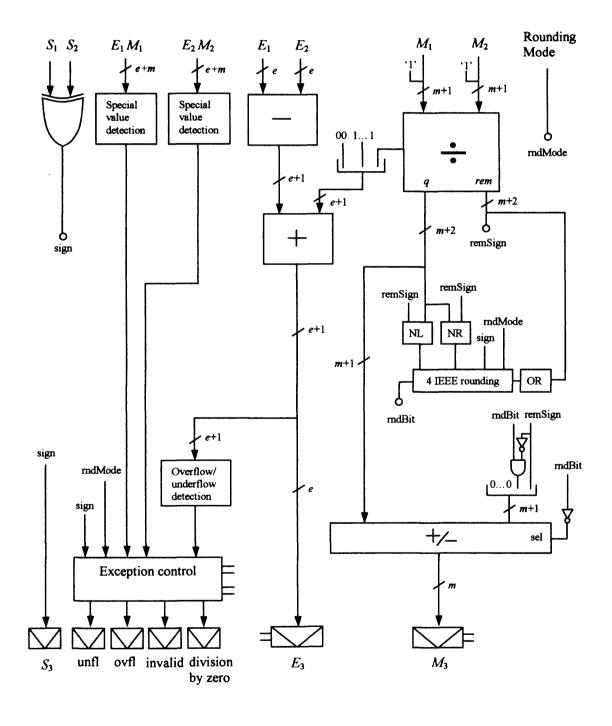

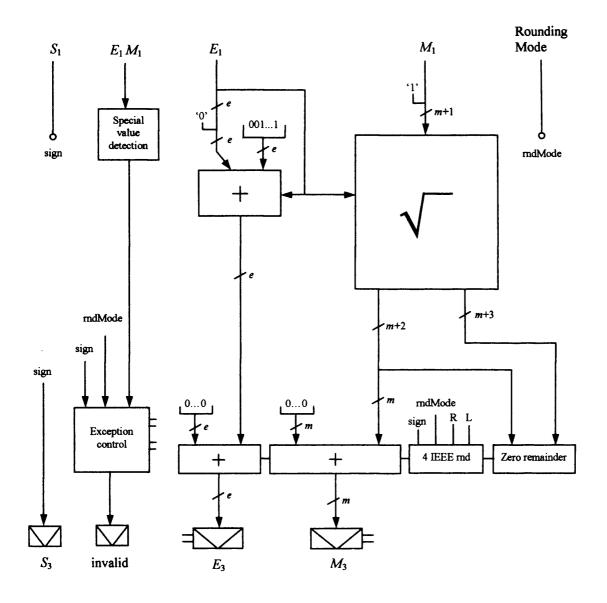

| 3.8 Floa | ting-point square root                                      | 116 |

| 3.8.1    | Special values                                              | 116 |

| 3.8.2    | Sign logic                                                  |     |

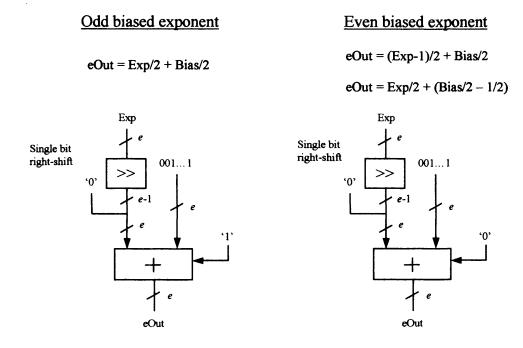

| 3.8.3    | Exponent handling                                           |     |

| 3.8.4    | Significand fixed-point square root                         |     |

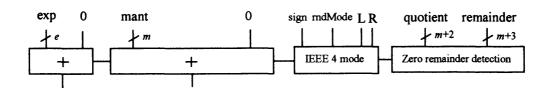

| 3.8.5    | Rounding, zero remainder detection and exponent adjusting   |     |

| 3.8.6    | Overflow and underflow                                      |     |

| 3.8.7    | Complete floating-point square root diagram                 |     |

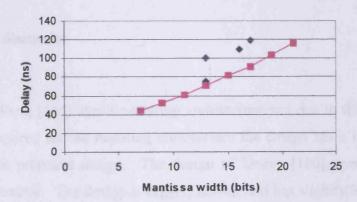

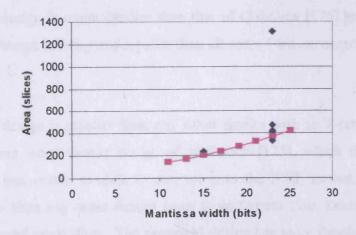

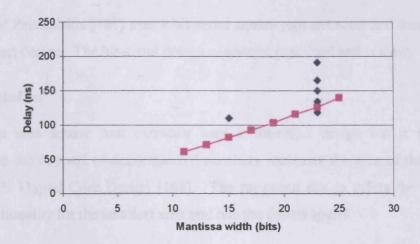

|          | ting-point implementation results                           |     |

| 3.9.1    | Fair comparison                                             |     |

| 3.9.1    |                                                             |     |

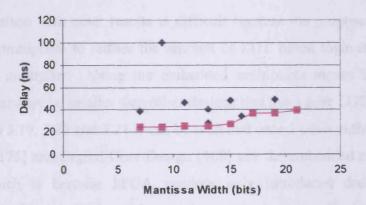

|          | 9.2.1 Comparison of floating-point addition results         | 126 |

|          | 9.2.2 Result discussion                                     |     |

|          | 9.2.3 Conclusion                                            | 129 |

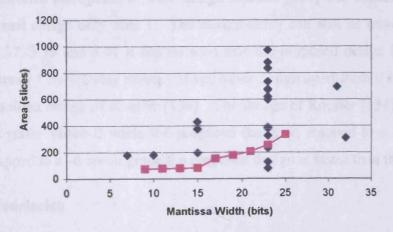

| 3.9.3    | Floating-point multiplication results                       | 130 |

|          | 9.3.1 Comparison of floating-point multiplication results   |     |

| 3.9.3.2 Result discussion                                                 |       |

|---------------------------------------------------------------------------|-------|

| J. J. J. J. CAUDIUSIANI                                                   | I J J |

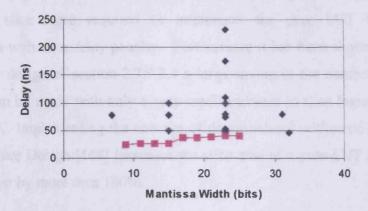

| 3.9.4 Floating-point division results                                     |       |

| 3.9.4.1 Comparison of floating-point division results                     |       |

| 3.9.4.2 Result discussion                                                 |       |

| 3.9.4.3 Conclusion                                                        |       |

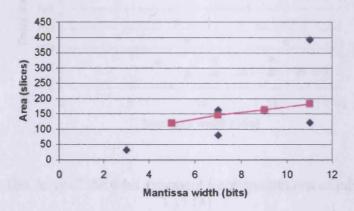

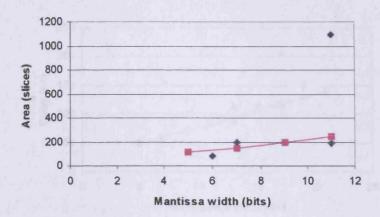

| 3.9.5 Floating-point square root results                                  | 142   |

| 3.9.5.1 Comparison of floating-point square root results                  |       |

| 3.9.5.2 Result discussion                                                 |       |

| 3.9.5.3 Conclusion                                                        | 148   |

| Chapter 4 Function evaluation                                             | 149   |

| 4.1 Common function approximation methods                                 | 149   |

| 4.1.1 Full table lookup                                                   | 149   |

| 4.1.2 Bipartite, SBTM, STAM and multipartite                              | 149   |

| 4.1.3 Polynomial approximation                                            |       |

| 4.1.3.1 Taylor and Maclaurin series                                       | 150   |

| 4.1.3.2 Approximation via a single polynomial                             |       |

| 4.1.3.3 Piecewise approximation                                           |       |

| 4.1.3.4 Rational approximation                                            |       |

| 4.1.4 CORDIC                                                              |       |

| 4.1.5 Other linear convergence algorithms                                 | 152   |

| 4.2 An overview of FPGA function approximation methods                    |       |

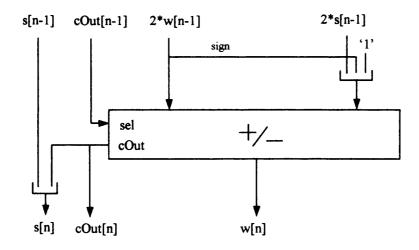

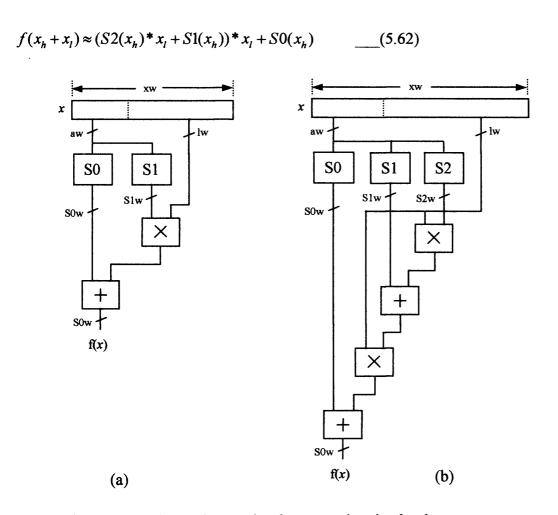

| 4.3 Piecewise Taylor series approximation                                 |       |

| 4.3.1 Taylor series                                                       |       |

| 4.3.2 Arithmetic and ROM component logic requirements                     |       |

| 4.3.3 1 <sup>st</sup> , 2 <sup>nd</sup> and 3 <sup>rd</sup> order details |       |

| 4.3.4 Approximation error and rounding                                    | 159   |

| 4.3.5 Hardware structure                                                  | 160   |

| 4.3.6 Model creation and testing                                          | 160   |

| 4.3.7 Results                                                             | 162   |

| 4.3.7.1 An implementation using only LUTs                                 | 162   |

| 4.3.7.2 Embedded multiplier and LUT implementation results                |       |

| 4.3.8 Conclusion.                                                         | 164   |

| Chapter 5 Logarithmic number system                                       | 165   |

| 5.1 Format                                                                | 165   |

| 5.2 An LNS literature overview                                            | 166   |

| 5.3 An FPGA LNS literature overview                                       | 169   |

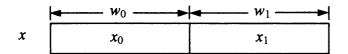

| 5.4 LNS word format                                                       | 170   |

| 5.5 Relative error                                                        | 171   |

| 5.6 Dynamic range                                                         | 173   |

| 5.7  | Spec   | al value  | encoding                                                                       | 174 |

|------|--------|-----------|--------------------------------------------------------------------------------|-----|

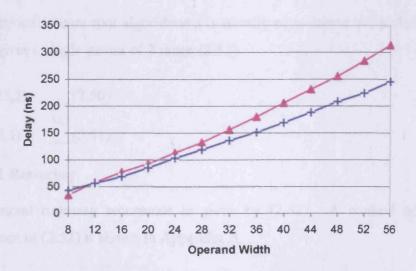

| 5.8  | Loga   | rithmic r | number system addition/subtraction                                             | 174 |

|      | 5.8.1  |           | ic algorithm                                                                   |     |

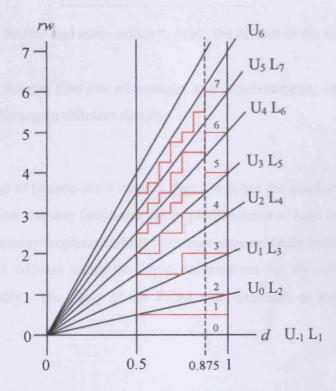

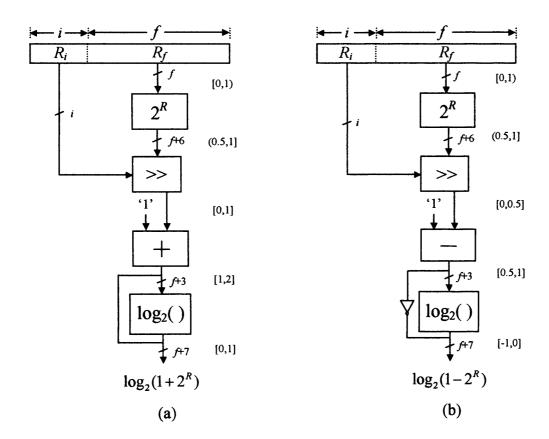

|      | 5.8.2  |           | lition/subtraction function                                                    |     |

|      | 5.8.3  |           | lition function                                                                |     |

|      | 5.8.4  |           | otraction function                                                             |     |

|      | 5.8.5  |           | nakers dilemma                                                                 |     |

|      | 5.8.6  |           | han floating-point accuracy (BTFP)                                             |     |

| 5.9  | Addi   |           | raction function approximation methods                                         |     |

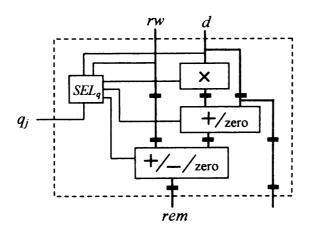

|      |        |           | th LNS addition/subtraction approximation                                      |     |

|      |        |           | ar path                                                                        |     |

|      | 5.9    |           | ear path                                                                       |     |

|      | 5.9    |           | unction approximation                                                          |     |

|      | 5.9    | .1.4 C    | hebyshev function approximation                                                | 189 |

|      | 5.9    | .1.5 L    | og <sub>2</sub> , 2 <sup>R</sup> and correction approximation ROM address, LSB |     |

|      |        | and       | ROM content widths                                                             | 193 |

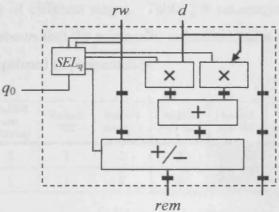

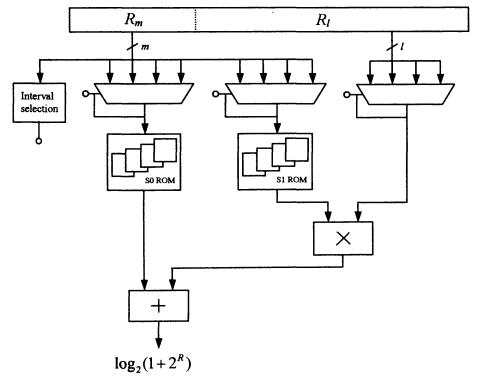

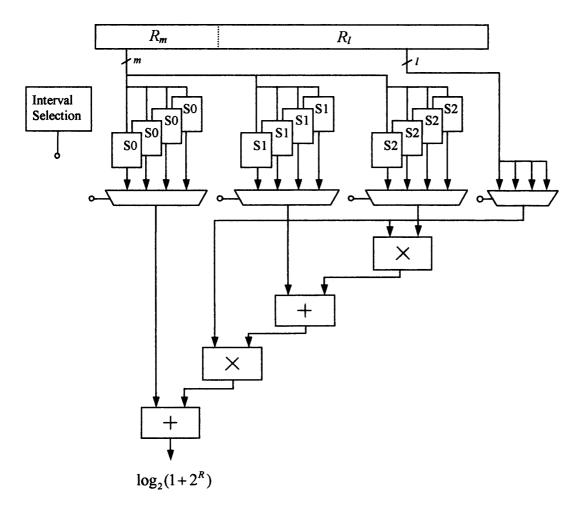

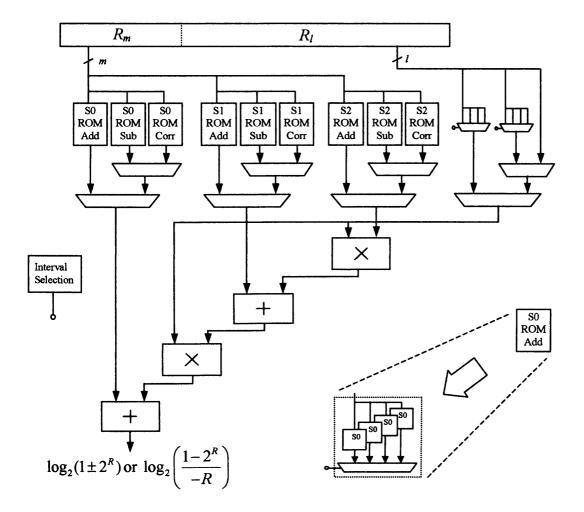

|      | 5.9.2  | Parallel  | -lookup function approximation                                                 | 194 |

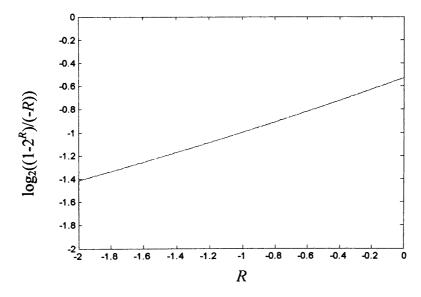

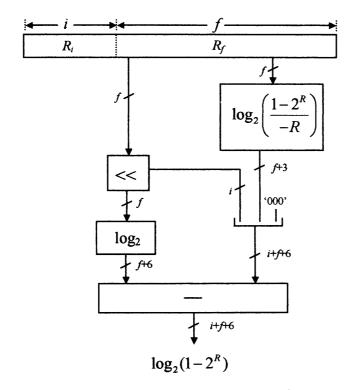

|      |        |           | unction decomposition                                                          |     |

|      | 5.9    |           | ddition function approximation                                                 |     |

|      | 5.9    | .2.3 St   | ubtraction function approximation                                              | 198 |

|      | 5.9    |           | new idea                                                                       |     |

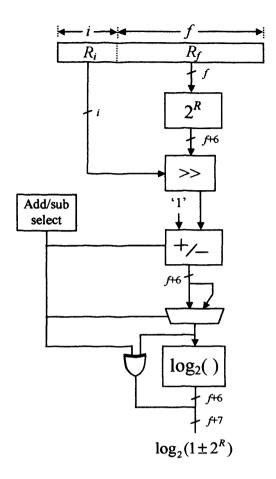

|      | 5.9    |           | ombining the addition/subtraction functions with hardward                      |     |

|      |        |           | ing                                                                            |     |

|      |        |           | tilising the Virtex-II FPGA on chip memory resource                            |     |

|      |        |           | he complete parallel-lookup addition/subtraction function.                     |     |

|      | 5.9    |           | ookup table content and address widths for the parallel-loc                    | _   |

|      |        |           | 10d                                                                            |     |

|      | 5.9.3  | An add    | ition or subtraction operation?                                                | 206 |

|      | 5.9.4  | Calcula   | ting the largest magnitude and the difference                                  | 206 |

|      | 5.9.5  | Sign log  | gic                                                                            | 206 |

|      | 5.9.6  | Special   | value detection                                                                | 206 |

|      | 5.9.7  | Special   | value input and output combinations                                            | 207 |

|      | 5.9.8  | Overflo   | w/underflow detection                                                          | 207 |

|      | 5.9    |           | verflow                                                                        |     |

|      | 5.9    | .8.2 U    | nderflow                                                                       | 207 |

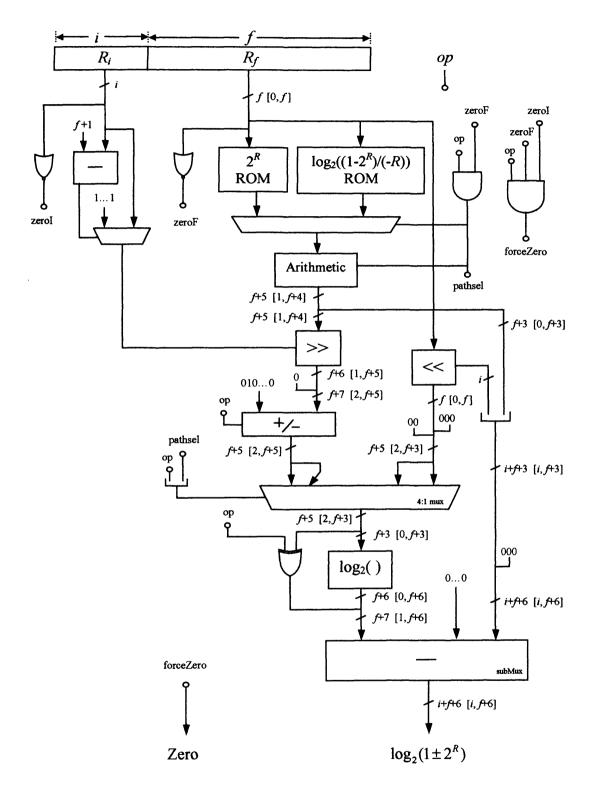

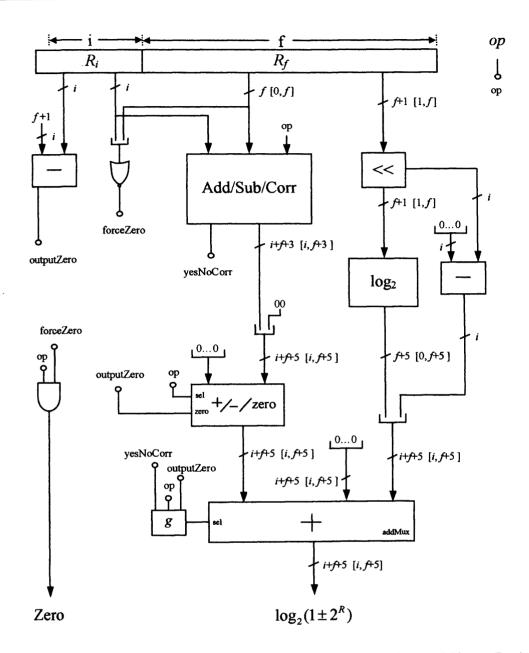

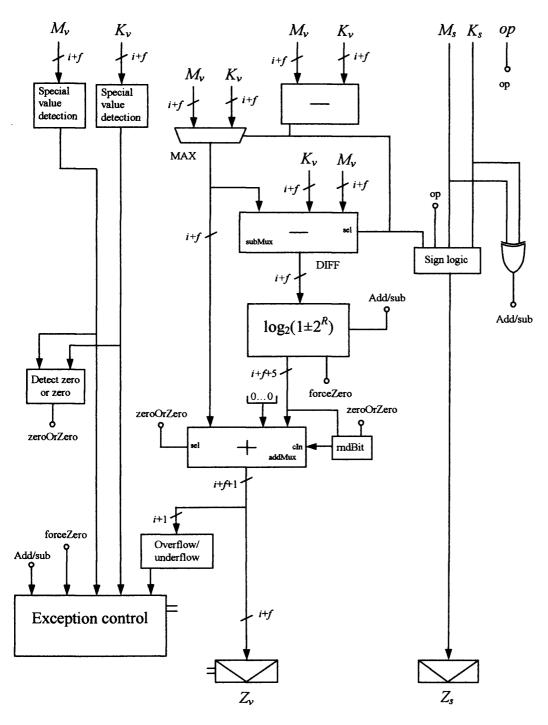

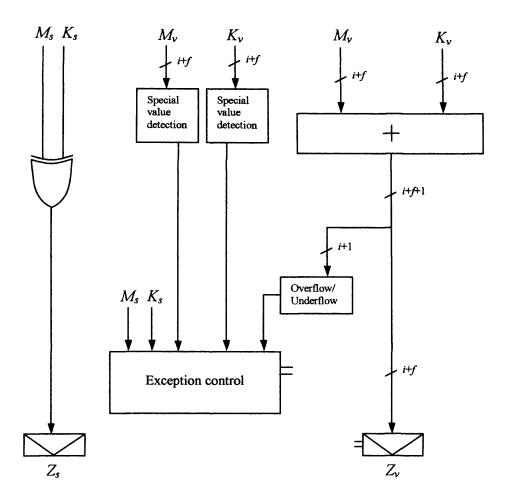

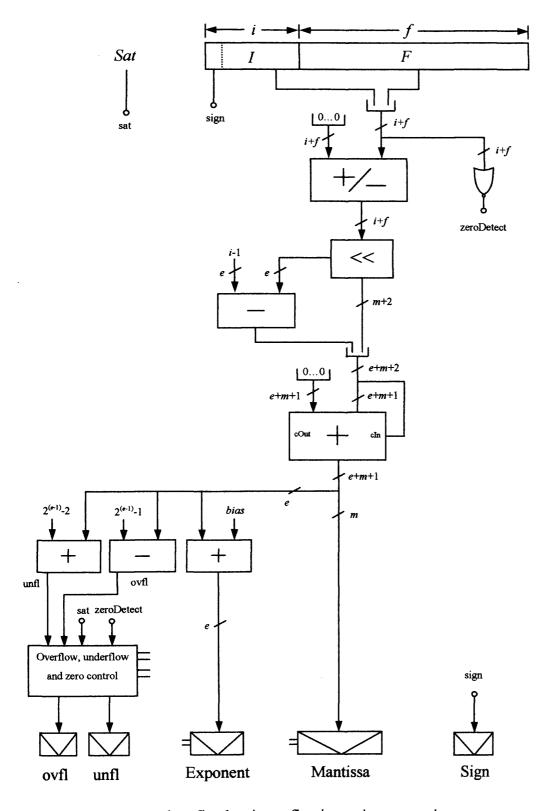

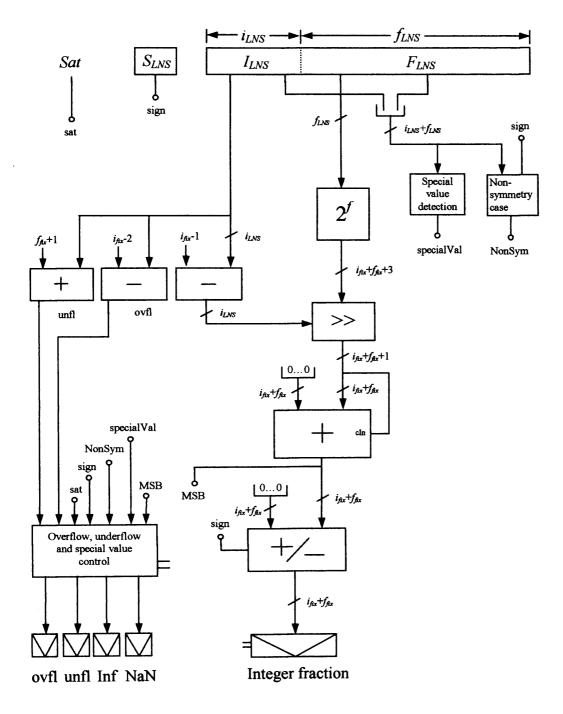

|      | 5.9.9  | Comple    | ete LNS addition diagram                                                       | 209 |

| 5.10 | 0 Loga | rithmic ı | number system multiplication                                                   | 209 |

|      |        |           | ultiplication error                                                            |     |

|      |        |           | value detection and handling                                                   |     |

|      |        | =         | w/underflow detection and handling                                             |     |

|      |        |           | verflow                                                                        |     |

|      |        |           | nderflow                                                                       |     |

|      |        |           | ete LNS multiplier diagram                                                     |     |

|      |        | _         | number system division                                                         | 211 |

| 5.11.1 LNS division error                                              | .212        |

|------------------------------------------------------------------------|-------------|

| 5.11.2 Special value detection and handling                            | .212        |

| 5.11.3 Overflow/underflow detection and handling                       | .212        |

| 5.11.3.1 Overflow                                                      |             |

| 5.11.3.2 Underflow                                                     | .212        |

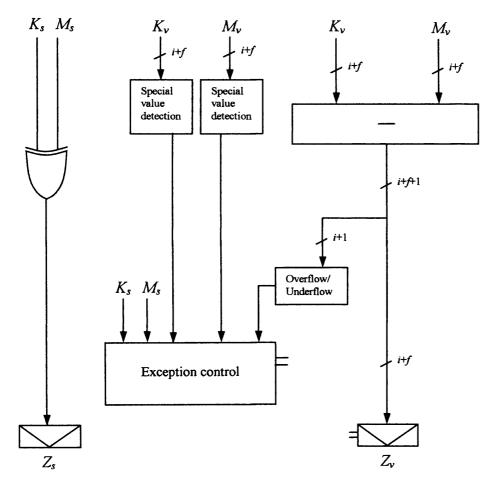

| 5.11.4 Complete LNS divider diagram                                    | .213        |

| 5.12 Logarithmic number system powering                                | .213        |

| 5.12.1 Powering error                                                  | .214        |

| 5.13 Logarithmic number system square root                             | .214        |

| 5.13.1 LNS square root rounding                                        | .214        |

| 5.13.2 Special value detection and handling                            |             |

| 5.13.3 Overflow/underflow                                              |             |

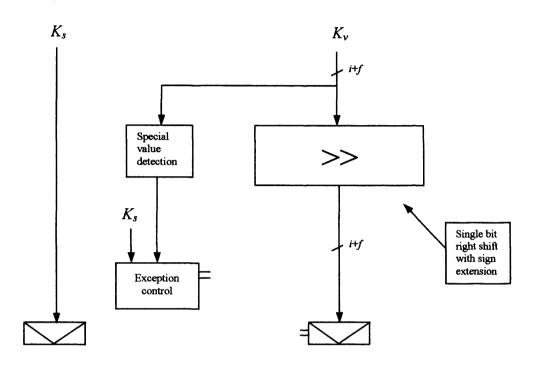

| 5.13.4 Complete LNS square root diagram                                |             |

| 5.14 LNS implementation results                                        |             |

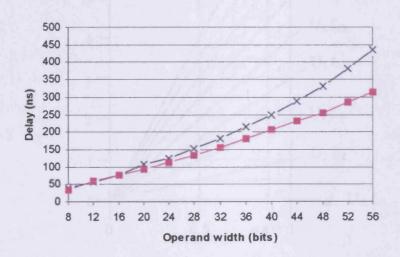

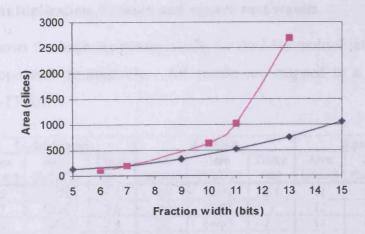

| 5.14.1 LNS addition results.                                           |             |

| 5.14.1.1 Comparison of the dual-path and parallel-lookup methods       |             |

| 5.14.1.2 A blockRAM-utilising 8-bit integer, 23-bit fraction parallel- |             |

| lookup design                                                          |             |

| 5.14.1.3 Comparison with other works                                   |             |

| 5.14.1.4 Comparison with another parameterisable design                |             |

| 5.14.1.5 Discussion                                                    |             |

| 5.14.1.6 Conclusion                                                    |             |

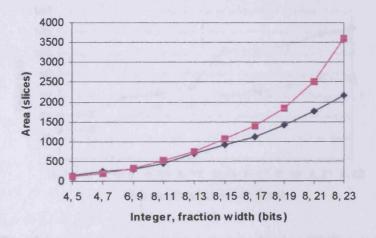

| 5.14.2 LNS multiplication, division and square root results            | .223        |

| 5.14.2.1 Comparison with other works                                   |             |

| 5.14.2.2 Discussion                                                    | .223        |

| Chapter 6 Conversion algorithms                                        | <b>22</b> 7 |

| 6.1 Fixed-point to floating-point conversion and vice-versa            | .227        |

| 6.1.1 Fixed-point to floating-point conversion                         |             |

| 6.1.1.1 Error                                                          |             |

| 6.1.1.2 Word lengths that determine the overflow possibility           |             |

| 6.1.1.3 Word lengths that determine the underflow possibility          | .228        |

| 6.1.2 Floating-point to fixed-point conversion                         |             |

| 6.1.2.1 Error                                                          |             |

| 6.1.2.2 Word lengths that determine the overflow possibility           |             |

| 6.1.2.3 Word lengths that determine the underflow possibility          |             |

| 6.1.3 Implementation results                                           | .232        |

| 6.1.3.1 Fixed-point to floating-point conversion                       |             |

| 6.1.3.2 Discussion                                                     |             |

| 6.1.3.3 Floating-point to fixed-point conversion                       |             |

| 6.1.3.4 Discussion                                                     |             |

| 6.2 Fixed-point to LNS conversion and vice-versa                       |             |

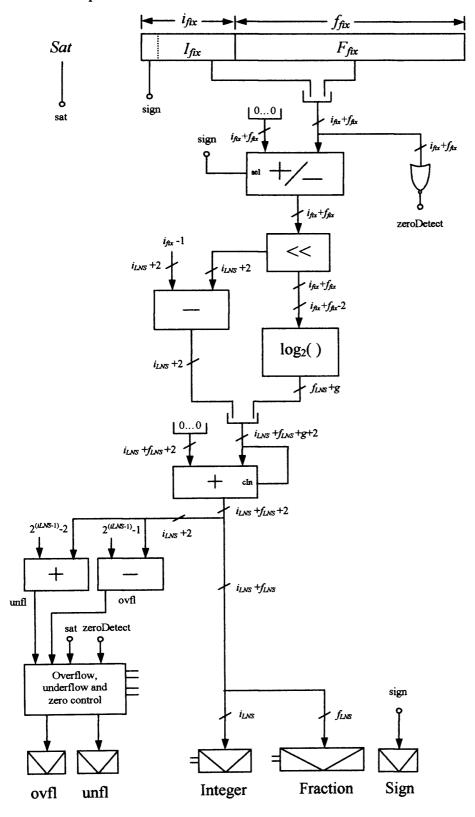

| 6.2.1 Fixed-point to LNS conversion                                    | .233        |

| 6.2.1.1 Error                                                          | 734         |

| 6.2.1.2 Word lengths that determine the overflow possibility           | 227         |

| 6.2            | 2.1.3 Word lengths that determine the underflow possibility | 235 |

|----------------|-------------------------------------------------------------|-----|

|                | LNS to fixed-point conversion                               |     |

|                | 2.2.1 Error                                                 |     |

| 6.2            | 2.2.2 Word lengths that determine the overflow possibility  |     |

| 6.2            | 2.2.3 Word lengths that determine the underflow possibility | 238 |

| 6.2.3          | Implementation results                                      | 238 |

| 6.2            | 2.3.1 Fixed-point to LNS conversion                         | 238 |

|                | 2.3.2 Discussion                                            |     |

|                | 2.3.3 LNS to fixed-point conversion                         |     |

| 6.2            | 2.3.4 Discussion                                            | 239 |

| Chapter 7      | MATLAB libraries                                            | 240 |

| 7.1 Float      | ting-point library                                          | 240 |

| 7.1.1          | Addition                                                    |     |

| 7.1.2          | Multiplication                                              |     |

| 7.1.3          | Division                                                    |     |

| 7.1.4          | Square root                                                 |     |

|                | •                                                           |     |

|                | library                                                     |     |

| 7.2.1          | Addition                                                    |     |

| 7.2.2          | Multiplication                                              |     |

| 7.2.3          | Division                                                    |     |

| 7.2.4          | Square root                                                 | 242 |

| 7.3 Conv       | version library                                             | 242 |

| 7.3.1          | Fixed-point to floating-point                               | 242 |

| 7.3.2          | Floating-point to fixed-point                               | 243 |

| 7.3.3          | Fixed-point to LNS                                          |     |

| 7.3.4          | LNS to fixed-point                                          |     |

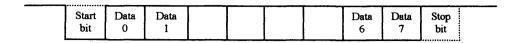

|                | al communication system                                     |     |

|                | ·                                                           |     |

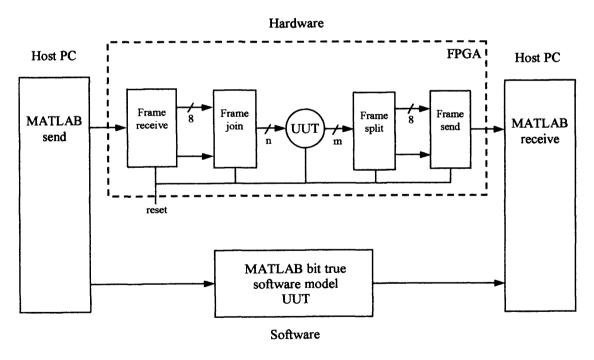

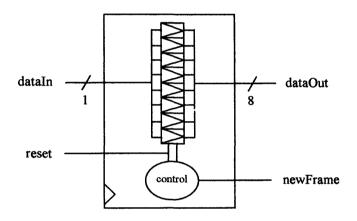

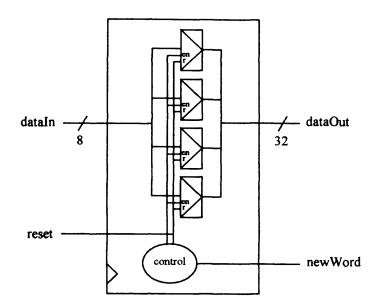

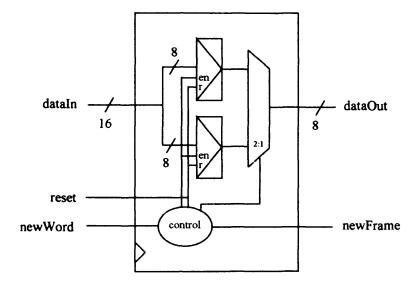

| 7.4.1          | Communication procedure                                     |     |

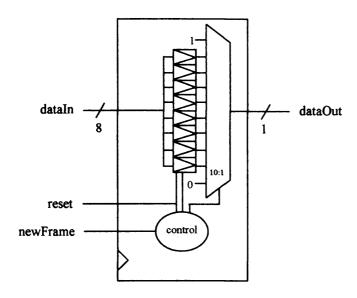

| 7.4.2          | FPGA communication system                                   | 244 |

| Chapter 8      | Comparison                                                  | 248 |

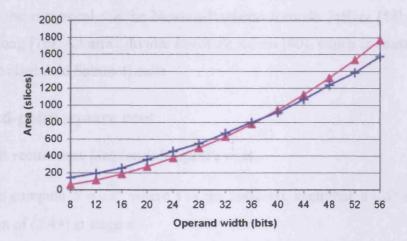

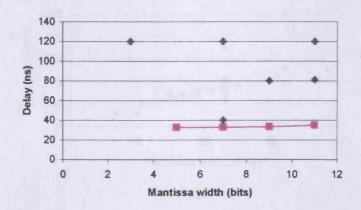

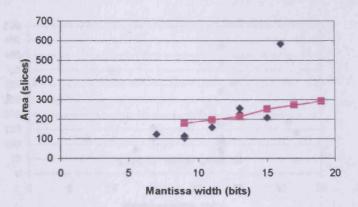

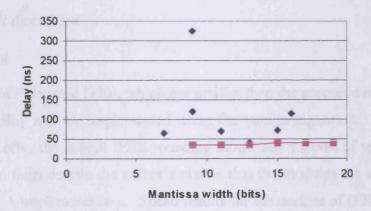

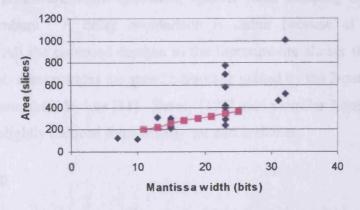

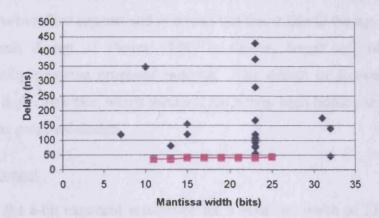

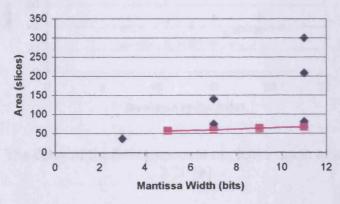

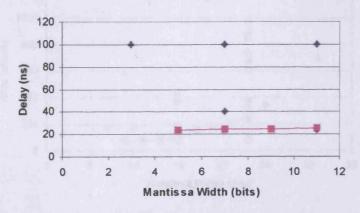

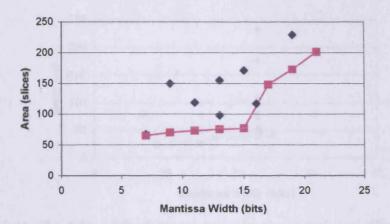

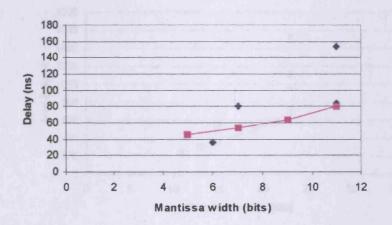

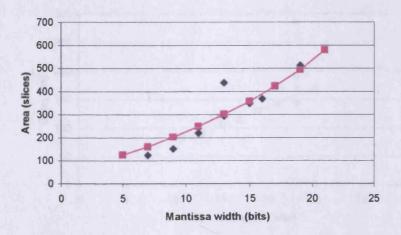

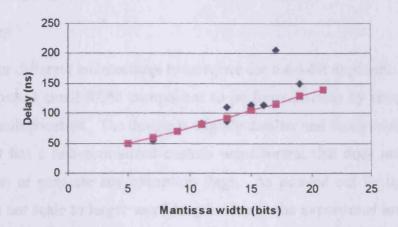

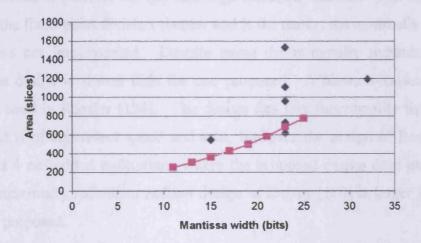

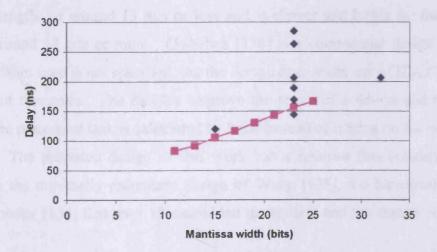

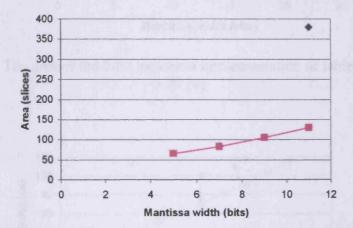

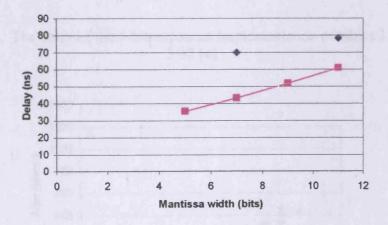

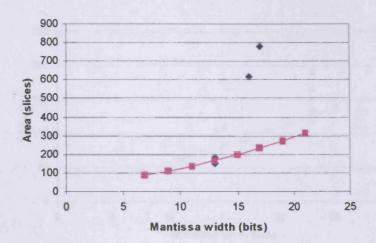

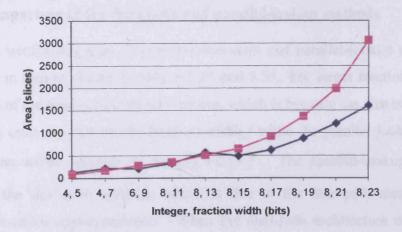

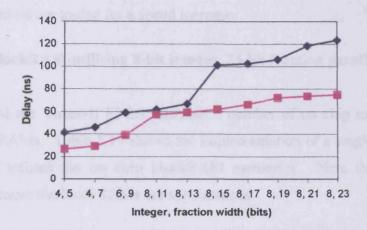

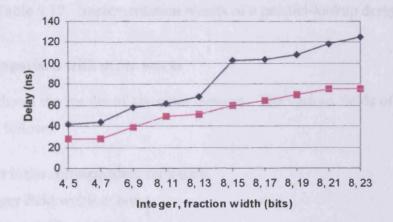

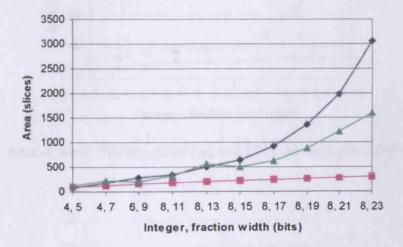

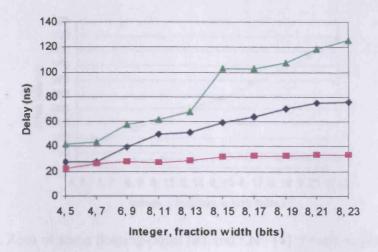

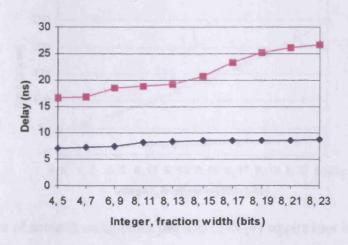

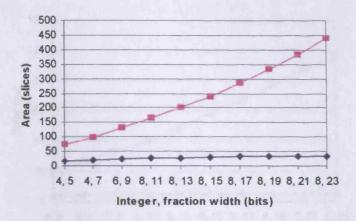

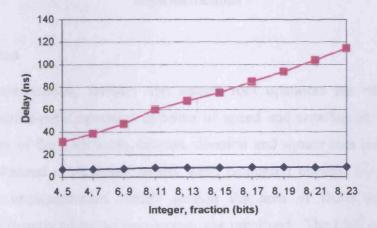

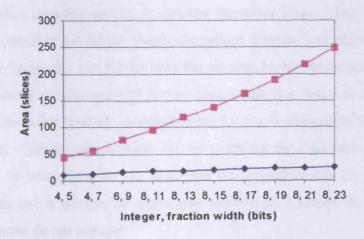

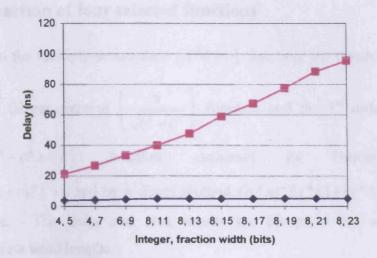

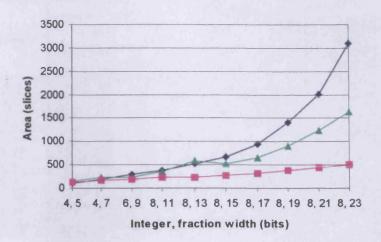

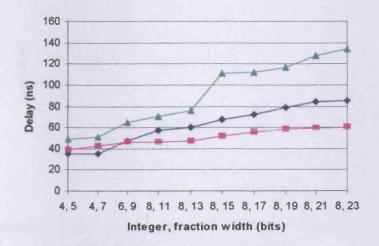

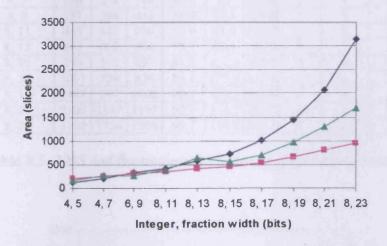

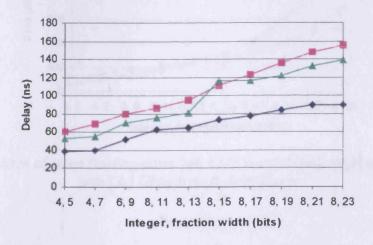

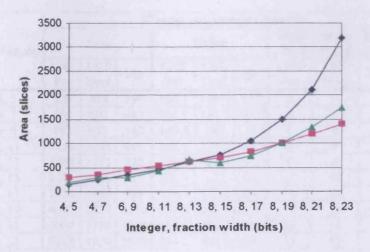

| 8.1 A co       | mparison of the four basic operators                        | 248 |

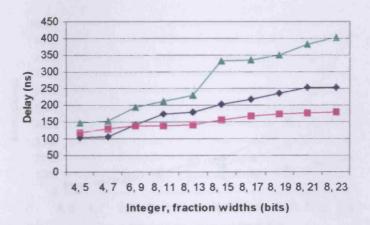

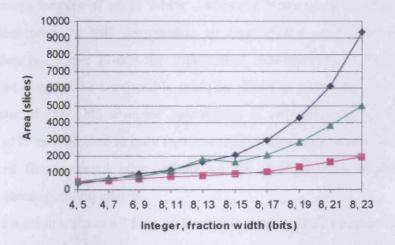

| 8.1.1          | Discussion                                                  | 252 |

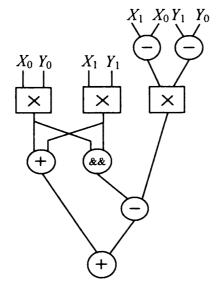

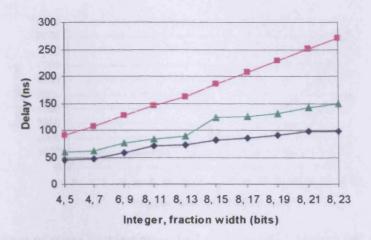

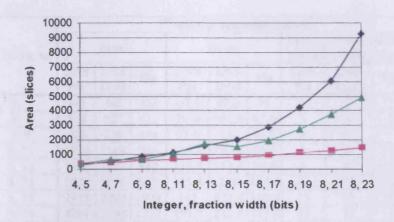

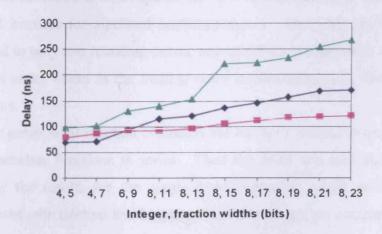

| 8.2 A co       | omparison of four selected functions                        | 253 |

| 8.2.1          | Multiply-accumulate                                         |     |

| 8.2.2          | Distance                                                    |     |

| 8.2.3          | Givens                                                      |     |

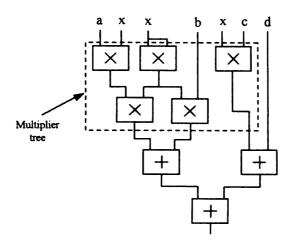

| 8.2.4          | 3 <sup>rd</sup> order polynomial (Horner)                   |     |

| 8.2.5          | 3 <sup>rd</sup> order polynomial (direct)                   |     |

| 8.2.5<br>8.2.6 | Discussion                                                  |     |

|                |                                                             |     |

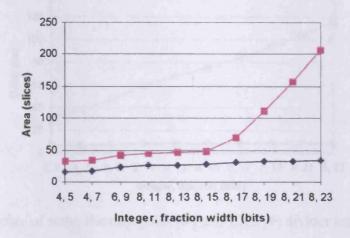

| 8.3 Conv       | version component comparison                                | 261 |

| 8      | 3.3.1 | Fixed-point to LNS/floating-point                                                  | 261 |

|--------|-------|------------------------------------------------------------------------------------|-----|

| 8      | 3.3.2 | LNS/floating-point to fixed-point                                                  |     |

| Chapte | er 9  | Conclusion                                                                         | 263 |

| 9.1    |       | l-point                                                                            |     |

| 9.2    |       | ing-point                                                                          |     |

| 9.3    |       | tion evaluation                                                                    |     |

| ,      |       | rithmic number system                                                              |     |

|        | _     | parison                                                                            |     |

|        | 9.5.1 | Operator comparison                                                                |     |

| 9      | 9.5.2 | Conversion comparison                                                              |     |

|        |       | or floating-point: which is the most suitable for FPGA mentation?                  | 268 |

| 9.7    | Futu  | re work                                                                            | 269 |

| Appen  | dix A | A SRT division                                                                     | 272 |

|        |       | x-2 SRT division with non-redundant residual                                       |     |

|        |       | x-4 SRT division with non-redundant residual and maximally dant quotient digit set | 274 |

| A.3    | Quot  | ient digit set redundancy                                                          | 276 |

| Appen  | dix l | Square root derivation                                                             | 277 |

| B.1    | Sequ  | ential square root                                                                 | 277 |

|        | •     | Restoring algorithm                                                                |     |

|        |       | non-restoring algorithm                                                            |     |

| Refere |       |                                                                                    | 281 |

### Acronyms

⊕ Logical XOR function.

+ Addition for numeric operations. OR for logical operations.

Logical AND function when used in logic expressions.

\* Arithmetic multiplication.

[a, b] A range including the limits a and b.

(a, b] A range not including the limit a.

[a, b) A range not including the limit b.

(a, b) A range not including the limits a and b.

∨ Logical OR function.

add/sub Component that performs addition and subtraction.

AND Logical AND function.

ALU Arithmetic Logic Unit.

ASIC Application Specific Integrated Circuit.

BlockRAM Memory components found on Xilinx Virtex FPGAs.

BTFP Better Than Floating-Point.

cc Carry-chain.

Ceil(.) Mathematical ceiling function.

CLB Configurable Logic Block.

CORDIC Coordinate Rotation Digital Computer.

CPA Carry Propagate Adder.

CPU Central Processing Unit.

CSA Carry Save Adder.

dbz Divide by zero.

DSP Digital Signal Processing/Processor.

EDIF Electronic Design Interchange Format.

Embed Mults 18x18-bit Embedded Multipliers found on Xilinx Virtex-II FPGAs.

exp Exponent of a floating-point number.

ff Flip-flop (D-type). flp Floating-point.

FPGA Field-Programmable Gate Array.

IEEE Institute of Electrical and Electronics Engineers.

inf Infinity.

kcm Constant coefficient multiplication.

LC Logic Cell.

LCPQ LUT Columns Per Quotient Digit.

LCPQP LUT Columns Per Quotient Digit Pipelined.

LE Logic Element.

LNS Logarithmic Number System.

LPQ Latency Per Quotient bit.

LSB Least Significant Bit.

LSDF Least Significant Digit First.

LUT Look Up Table.

LZA Lead Zero Anticipator.

LZD Lead Zero Detector.

MAC Multiply Accumulate.

mant Mantissa.

max(.) Function to calculate the maximum of a group of arguments. min(.) Function to calculate the minimum of a group of arguments.

MHz Megahertz.

MSB Most Significant Bit.

MSDF Most Significant Digit First.

mux Multiplexer. NaN Not-a-Number.

NOR Logical NOR function.

ns Nanoseconds.

OR Logical OR function.

ov Overflow.

P&R Place and Route.

PC Personal Computer.

PP Partial Product.

R4 Radix-4.

RAM Random Access Memory. RCA Ripple Carry Adder. RHS Right Hand Side.

RISC Reduced Instruction Set Computer.

RLOC Relative location.

ROM Read Only Memory.

RTN Round To Nearest.

RTNE Round To Nearest Even.

RTMI Round To Minus Infinity.

RTPI Round To Plus Infinity.

SBTM Symmetrical Bipartite Table Method.

SRT Sweeny, Robertson, Tocher.

SRAM Static Random Access Memory.

STAM Symmetrical Table Addition Method.

TRUNC Truncation.

UART Universal Asynchronous Receive Transmit.

ulp Unit in Last place (the weighting of the LSB).

un Underflow. UUT Unit Under Test.

VHDL Very high speed integrated circuit Hardware Description Language.

VLSI Very Large Scale Integration.

XOR Logical XOR function.

### Introduction

### 1.1 Programmable logic

The FPGA (Field-Programmable Gate Array) technology sector has grown immensely over the past decade as is evident from the number of conferences, companies and research centres dedicated to or involved with programmable logic. FPGAs are silicon programmable logic devices that can be reprogrammed numerous times (some companies claim an infinite number) to perform many different logic functions. Reprogrammability and flexibility are the key factors to the success of the FPGA as they allow simple design enhancements, such as bug fixes, or a total algorithm overhaul with no hardware cost and minimal time penalty. Furthermore, changes can be done remotely, very rapidly and with FPGA devices still in system. Prototyping and rapid implementation of algorithms and custom designs with hardware speeds is possible, and with high level programming languages the ease and speed of design implementation is increasing. However, the high level languages do come at a price and control over certain design aspects, such as placement and low level primitive use, are lost to the synthesis and place and route (P&R) tools. Although slower than major commercial processors the custom data-path configuration and reduced overhead means that FPGA hardware implementations can speed up many software algorithms implemented on general-purpose processors or DSPs (Digital Signal Processors). FPGAs cannot match the speed and low power consumption of full custom ASIC (Application Specific Integrated Circuit) design, but such procedures are very expensive to undertake and are generally only used for mass produced or specialist devices. However, low cost high volume FPGA devices such as the Spartan-3 from Xilinx [32] using the latest 90 nanometre technology are trying to break into this high volume market for certain applications.

### 1.2 A brief FPGA technology history and overview

The traditional FPGA architecture consisted of a rectangular array of identical logic elements constructed from small LUTs (Look Up Tables) or from a selection of combinatorial logic gates. Logic elements typically contained a flip-flop or could be configured as a flip-flop. Similarly to current FPGAs the traditional FPGAs were SRAM based, which allowed them to be reconfigured. SRAM cells, which reside throughout the FPGA, store the configuration bits that determine the function a LUT stores, the routing of a signal, the constant select signal value of a multiplexer, and so on. Logic elements, registers and the I/Os were routed together in the traditional FPGA architecture by using a programmable interconnect matrix in much the same way as current FPGAs, however current FPGA routing matrices are much more complex. The first FPGAs contained up to 600 logic elements with around 70 I/Os and operated at a maximum clock speed of 75 MHz. They were typically implemented with 1.0 µm VLSI technology and operated at 5V.

As the technology size has decreased in various steps from 1.0  $\mu$ m (0.6, 0.5, 0.45 ... 0.15, 0.13, 0.12  $\mu$ m) to the current 90 nm technology of today the density of devices has increased. Current devices Xilinx [36] and Altera [48] have up to 180K logic elements and up to 1100 I/Os compared to the 600 logic elements and 70 I/Os of the first FPGAs. The successive technology size decrease has also brought about a successive speed increase and a voltage decrease as current FPGAs can operate with internal clock speeds of over 450 MHz and a core voltage of just 1.2V.

The applications of FPGAs have demanded additional dedicated features be incorporated into the FPGA structure. The additional features reduce the burden and inefficiencies of their implementation with basic logic elements. The first additional feature on FPGAs was dedicated blocks of memory. The memory blocks started off small at 128 to 256-bits and with a limited dual-port functionality of 1 read and 1 write port. A single FPGA could implement a total of 3K to 18Kbits of memory. The size of the memory blocks quickly grew from 1K to 2K to 4K to 9K to 18Kbits and most recently Altera have included a 590K RAM block in their Stratix-II device [48]. Currently the largest FPGA can implement around 8.1Mbits of dedicated block memory. Configuration and functionality of the memory blocks has also grown and most memory blocks can implement true dual-port memory, where both ports can be configured to read and/or write. The second additional feature to appear on FPGAs

was dedicated carry logic. This logic enables very fast ripple-carry adders, comparators and wide logic gates to be created. The third feature to appear on FPGAs was dedicated multipliers [35] and DSP blocks [25] and [48]. FPGAs are increasingly being used in DSP applications where multiplication and multiply-accumulate (MAC) operations are required and so dedicated logic for these operations has been included. The dedicated multiplier blocks follow a de facto standard of being 18x18-bit signed two's complement. All the embedded DSP blocks contain a number of 9x9-bit multipliers and these can be configured to produce the de facto 18x18-bit and 36x36bit multipliers in a single block. The DSP blocks also provide support for multiply accumulate and complex multiplication functions at higher clock rates and with fewer pipeline stages than using logic elements to implement the same functions. fourth feature to appear on FPGAs was the high performance transceiver block [36], which allows very fast serial communication of up to 10Gb/s with a single I/O line. Data is serialised and de-serialised on chip in dedicated hardware. Finally the newest feature to appear on FPGAs is the dedicated RISC CPU. The Virtex-II PRO [36] contains up to 2 IBM PowerPC 405 RISC CPU cores.

### 1.3 FPGA design flow

Initially when creating a design a high level model of the system is created in a high level programming language such as C or Java or in a mathematical environment such as MATLAB. This allows the concept and validity of an algorithm to be tested in software before any hardware design is undertaken. The high-level software design is usually written to match the hardware design exactly and so is referred to as a 'bit-true' design. This provides the ultimate layer of testing, as the processed data that the hardware returns should match the data returned by the software model exactly. The hardware design is written in a hardware description language such as VHDL or Verilog. Certain vendors and research institutes also offer other high level languages and design environments such as handel-C (C based), the float environment (written in Perl), the PAM Blox-II environment, C++ integration via the ACS stream complier and Jbits design environment (Java), which are more familiar to software designers. The idea is to allow the designer to focus on the algorithm implementation and not to worry about the underlying hardware structure. The hardware description is run through a synthesis tool, which translates the design into gates and optimizes it for the

target FPGA architecture and outputs an industry standard EDIF (Electronic Design Interchange Format) netlist. After synthesis the design is placed and routed (P&R), which decides the layout of the logic components and the routing structure to connect them. Specifically the Xilinx P&R flow, which will be used in this work, contains three phases of 'translation', 'mapping' and 'place and route'. The translation phase combines multiple netlists and specific design constraint information. The mapping phase maps the logic to the components (logic cells, I/O cells, and other components) in the target FPGA. The place and route phase is as described above. After P&R a configuration bitstream is generated that can be downloaded onto a device to program it with the functionality of the created design. At different stages of the design different levels of testing can be carried out. After the design has been written in VHDL or Verilog a functional test can be undertaken. Post P&R a full backannotated test can be performed using the FPGA vendors' hardware libraries. This test provides the most accurate picture of how the final implemented design should perform. Finally there is a system test, where the final design running on hardware can be compared against the bit-true software model or any other successful test layer.

### 1.4 Aim of thesis: FPGA and high dynamic range number systems

Many algorithms use high dynamic range number systems to increase accuracy, increase the signal-to-noise ratio or to reduce the number of underflow and overflow exceptions. Application areas for high dynamic range number systems include digital signal processing applications such as FFT (Fast Fourier Transform) calculation, FHT (Fast Hartley Transform) calculation, digital sine-cosine generation, FIR (Finite Impulse Response) filtering and RLS (Recursive Least Squares) filtering; Image processing applications include video conferencing, compression and decompression in HDTV (High Definition Television), K-Means distance calculation, MPEG (Motion Pictures Expert Group) decoding, DCT (Discrete Cosine Transform) and IDCT (Inverse Discrete Cosine Transform) calculation; scientific applications include matrix operations, gravitational N-body interaction calculation, heat transfer in a 2D surface and seismic data processing; Telecommunication applications include network packet switching and cellular base station algorithms. Clearly there are many applications of high dynamic range computing, most of which are candidates for hardware acceleration using FPGA systems.

Chapter 1 Introduction

The I/O transfer rates, I/O pin counts and the density of current FPGAs have advanced sufficiently to accommodate these high dynamic range applications with ease. Furthermore the implications of Moore's law suggest that the density of FPGA technology will further increase in the next few years (until a technology wall is hit). This leads to the aim of this thesis, which is to investigate the trade offs in implementing two popular high dynamic range number systems on FPGAs, namely floating-point and logarithmic number system (LNS) arithmetic. LNS and floatingpoint are very different in their implementation but both have the capabilities of providing high dynamic range arithmetic. The question is, 'which one is most suitable for FPGA implementation?' Current FPGAs contain a restricted variety of logic elements compared to ASIC design and this poses quite a design challenge as the many efficient algorithms that have been developed for ASIC implementation do not necessarily map well to this design environment. An example of this is the compound adder that can calculate two different results of a+b and a+b+1 with a small delay and area overhead. Implementing such an adder on FPGA requires three times as much logic as a conventional adder (i.e. two adders and a multiplexer to select the output). A compound adder calculates two different results simultaneously while the decision whether to select a+b or a+b+1 is being performed, hence it is different to (faster than) calculating a+b then injecting '1' or '0' into the carry-in input as desired. The focus and challenge of this work is therefore to look at new ways to efficiently implement basic operations and components and then to use these components to implement floating-point and LNS operations. Furthermore a lowlevel design strategy will be adopted that will utilise the low-level primitives of the technology in an efficient way and will increase the design challenge. appreciated that this design strategy affects the portability of the design and goes against the high-speed rapid prototyping methodology of reconfigurable design, but it is felt that the knowledge gained of the underlying FPGA hardware and the smaller and faster designs that the proposed strategy leads to is worth the extra effort. The task of implementing efficient fixed-point, floating-point and LNS units is non-trivial due to the huge variety of techniques that need to be considered. In this work some of the more common ASIC techniques are considered and new techniques are developed in an attempt to provide the first steps in a fair comparison of LNS and floating-point arithmetic on FPGA. We say first steps, as the array of techniques is so vast that many substantial studies have been included in the future work section due to time

Chapter 1 Introduction

restrictions. Due to the influence of the sponsors, and of the technology available the study will focus primarily on using the Virtex-II range of FPGAs from Xilinx [35]. The Virtex-II FPGA is very representative of current technology because it contains features such as memory blocks, multipliers, fast carry-logic and an array of small lookup tables that are commonly found in all current FPGA architectures.

### 1.5 Structure of the Xilinx Virtex and Virtex-II FPGAs

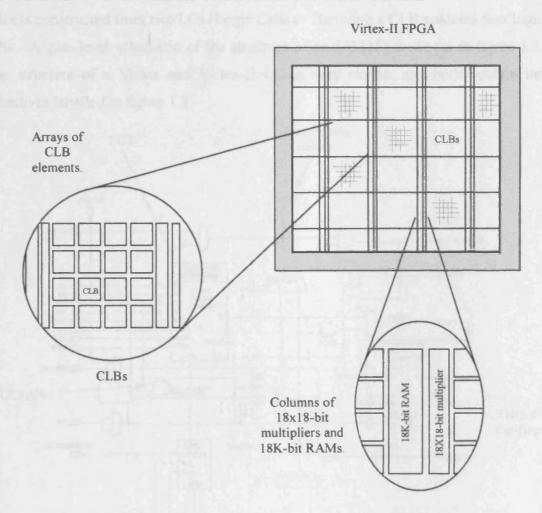

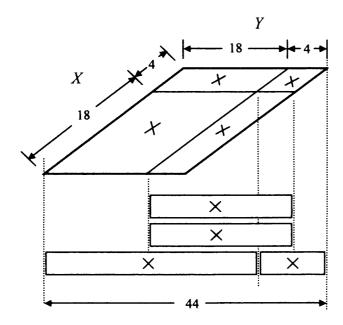

Figure 1.1. Logic structure of a Xilinx Virtex-II FPGA

Figure 1.1 shows the underlying structure of a Xilinx Virtex-II [35] FPGA. It can be seen that the chip consists of arrays of CLB (Configurable Logic Blocks) cells separated by columns of multiplier and RAM blocks. The structure of a Virtex [34] FPGA is very similar except that there are only two columns of RAM blocks on either side of the chip and there are no embedded multiplier blocks.

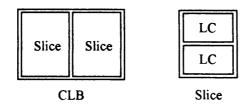

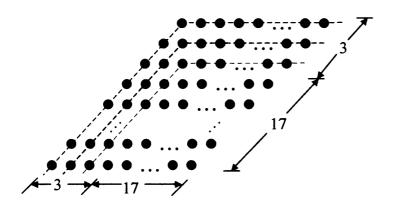

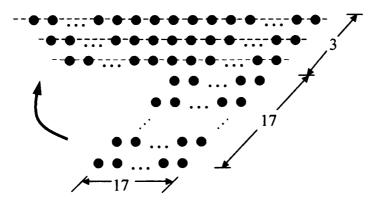

Figure 1.2. CLB and Slice structure of Xilinx Virtex and Virtex-II FPGAs

From figure 1.2 it can be seen that a CLB is constructed from two Slices and that a Slice is constructed from two LCs (Logic Cells). Therefore a CLB contains four logic cells. A gate-level schematic of the structure of an LC [35] is shown in figure 1.3. The structure of a Virtex and Virtex-II LC is very similar and both contain the primitives labelled in figure 1.3.

Figure 1.3. The structure of a Virtex-II logic cell (LC).

Chapter 1 Introduction

A brief description of each of the primitives labelled is given below:

• LUT. The LUT (Look-up Table) primitive is very versatile. It can be configured as a 4-bit input 1-bit output function generator, as a 16-bit memory (4-bit address, 1-bit data) or as a 16-bit shift register.

- Carry-chain. The carry-chain allows high-speed ripple-carry adders and wide logic gates to be produced. Each LC contains one 'MUXCY' carry-chain multiplexer. The bottom 'MUXCY' primitive shown in figure 1.3 is situated in the LC below.

- Output flip-flop. The output flip-flop allows the output of the LC to be registered

without using any extra LCs. The register can be bypassed and can also be

configured in numerous ways.

- MULTAND. The MULTAND primitive is a logical AND gate that facilitates the creation of efficient multipliers (the AND function is the same as a single bit multiplication).

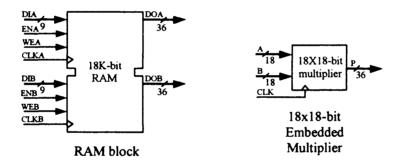

Figure 1.4. The interfaces of the Virtex-II RAM block and embedded multiplier

The Virtex-II RAM blocks are dual-port RAMs as shown in figure 1.4. Being dual-port means that there are two ports that access the same memory space. The embedded multipliers are 18X18-bit signed two's complement multipliers that produce a 36-bit signed two's complement output. The multipliers can be used synchronously or asynchronously. The interface of the 18X18-bit multiplier is shown in figure 1.4.

### 1.6 Thesis organisation and chapter contribution summary

In this section the outline of the thesis is given, as is the contribution made within each chapter. The publications where the contributions of the chapter were initially made are listed.

Chapter 2 looks at the implementation of fixed-point operators. Fixed-point is the basis of all arithmetic so in this chapter the focus is on efficient implementation of the four common fixed-point operators of addition, multiplication, division and square root. A new 4:2 adder mapping is shown in the addition section and the advantages and disadvantages of carry-free addition are discussed. A few ripple-carry adder configurations are then presented some of which are not discussed in the open literature. The multiplication section looks at the implementation of Booth encoding, which is not considered elsewhere in the open literature for implementation on the Virtex-II FPGA. Two new partial product generators are presented in the multiplier section. A new way of expanding the embedded multipliers is discussed in this section and is compared with other methods [50]. The new multiplier expanding technique is also applied to the special multiplication case of squaring [50]. The division section looks at the implementation of digit-recurrence style dividers, not previously considered in the way presented. New implementations of the nonrestoring, radix-4 SRT [51] and radix-8 SRT [50] dividers are given that are not previously given in the open literature. The prescaling technique, which has not before been considered for implementation on FPGA, is applied to the minimally redundant radix-8 design. A parameterisable non-restoring square root design is given in the final fixed-point section.

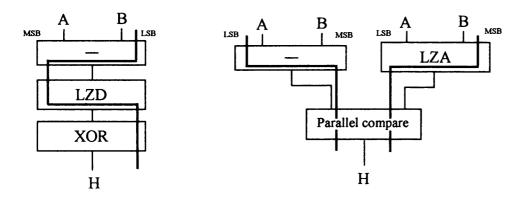

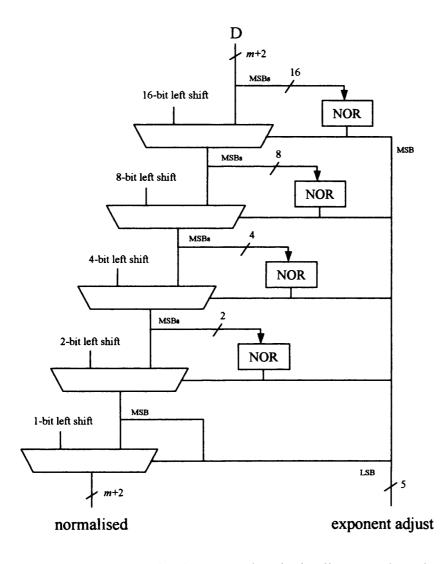

### Chapter 3

Floating-point operations of addition, multiplication, division and square root are considered in this chapter. The chapter begins with a brief overview of floating-point and the IEEE std-754 format. The first published FPGA implementation of the dual-path (far, near) floating-point addition algorithm is presented [51]. A new carry-chain unit for performing IEEE 4-mode rounding, a new shifter mapping, a new method for performing lead zero detection and new methods for performing rounding in FPGA floating-point units are described. The floating-point multiplier makes use of the new embedded multiplier expanding. The first floating-point divider using the radix-4 SRT division algorithm is presented [50].

Chapter 4 looks at ways of performing function approximation on FPGA. A new piecewise Taylor series approximation unit suitable for short to mid-length operands is described [52].

### Chapter 5

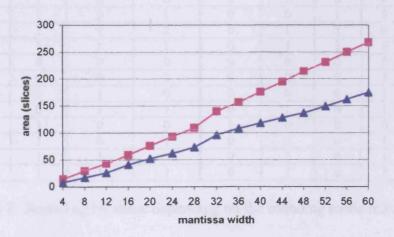

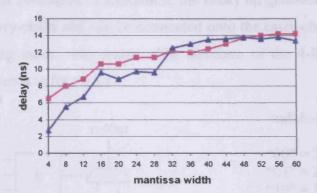

The implementation of the four LNS operators of addition, multiplication, division and square root are considered in this chapter. The word format, accuracy and operator structures are given. Two new methods for performing LNS addition are described and compared in this chapter [53], [54].

### Chapter 6

Chapter 6 deals with conversion from fixed-point to floating-point and vice-versa and from fixed-point to LNS and vice-versa. The structure of the conversion from fixed-point to LNS and vice-versa [55] is not discussed elsewhere in the open literature.

### Chapter 7

The MATLAB software libraries and function interfaces are briefly discussed in this chapter, as is the implementation of the UART serial interface to allow a low speed system test of the modules to be carried out.

### Chapter 8

In this chapter the logarithmic number system, floating-point operators and conversion components are compared in terms of area and delay. Some composite functions involving multiple operators are also compared to give a range of results.

### Chapter 9

Chapter 9 concludes the findings of the results and comparisons. The suitability of the logarithmic and floating-point systems for the processing of different algorithms is discussed and further studies are proposed.

# 2

### **Fixed-point**

In this chapter the focus will be on how to efficiently implement fixed-point operators on FPGA and more specifically on Xilinx Virtex FPGAs. Fixed-point arithmetic is the underlying type of arithmetic used in high dynamic range arithmetic schemes so we will begin by considering ways of implementing on FPGA the four basic operations of addition, multiplication, division and square root using fixed-point.

### 2.1 Formats

Fixed-point formats generally consist of an integer and a fractional field although sometimes the format is restricted to just an integer or fraction type. There are two main ways of implementing signed values: sign-magnitude and two's complement. Sign-magnitude is a symmetrical format, which contains a single sign bit, an *i*-bit integer part and an *f*-bit fraction part. The value of a *p*-bit (1+i+f) sign-magnitude value *X* is mathematically described in (2.1). For radix-2 (base-2) each bit *x*, of *X*, in equations (2.1) and (2.2) takes the value 0 or 1.

$$X = (-1)^{x_{p-f-1}} \left( \sum_{t=-f}^{p-f-2} x_t . 2^t \right)$$

(2.1)

The MSB (most significant bit) of a two's complement number is a magnitude bit that is negatively weighted. Two's complement is a non-symmetrical fixed-point format with an *i*-bit integer part and an *f*-bit fraction. The value of a *p*-bit (i+f) two's complement number X is given by (2.2).

$$X = -x_{p-f-1} \cdot 2^{p-f-1} + \sum_{t=-f}^{p-f-2} x_t \cdot 2^t$$

(2.2)

### 2.2 Distribution of fixed-point values

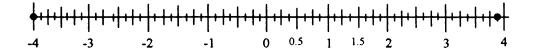

Consider a 6-bit fixed-point format with 3 integer bits and 3 fraction bits. Figure 2.1 illustrates the number line for the 6-bit two's complement format. From figure 2.1 it can be seen that the distribution of fixed-point values is even throughout the range of values.

Figure 2.1. Number line for a 3-bit integer and 3-bit fraction two's complement number

The dots in figure 2.1 illustrate the location of the maximum and minimum values.

### 2.3 Fixed-point addition

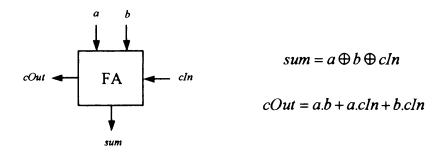

Fixed-point addition is the most basic arithmetic operation. The basic building block of the fixed-point adder is the full adder shown in figure 2.2. Full adder cells can be considered as 3-bit counters, where the inputs all have an equal weighting of '1', the sum has a weighting of '1' and the carry has a weighting of '2'. Full adder cells can be chained together to create RCAs (ripple-carry adders), which are a special type of CPA (carry propagate adder) where two non-redundant inputs are added (reduced) to a single non-redundant value.

Figure 2.2. A full adder cell

### 2.4 FPGA addition

The dedicated carry-chain embedded in the FPGA fabric allows very fast and efficient ripple-carry adders to be implemented. The carry-chain logic is so fast that alternative

adder designs Omondi [56], Parharmi [59] and Ercegovac [61], as used in ASIC devices, do not offer any implementation benefits. A survey of different FPGA CPA adder implementations is given in Xing [80] and Perri [81] and they show that the RCA is the most efficient adder design for FPGA. In this section we look at the basic RCA implementation and some very useful alternative configurations that are not available in the open literature. All the alternative structures use the same amount of logic as the basic adder design but the major difference is in the number of inputs a component requires and the logic function of the basic LUT elements.

### 2.4.1 Add (addition)

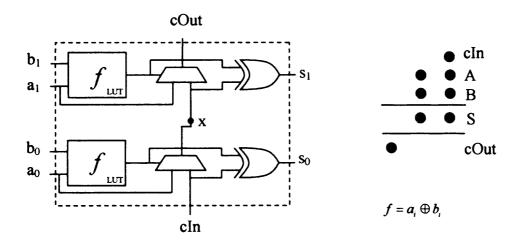

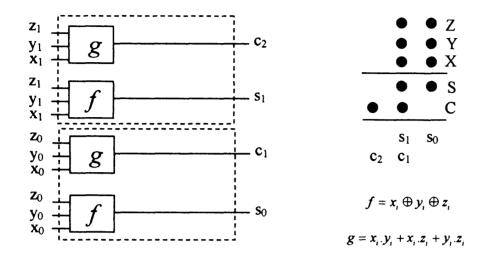

The full adder is the basic building block of the ripple-carry adder. The resources of a single LE (logic element) can be configured in such a way as to produce a full adder. Figure 2.3 illustrates a single slice, which contains two LEs configured as a two bit unsigned adder. The slice boundary is shown in figure 2.3 by the dashed box.

Figure 2.3. 2-bit adder implemented on a Virtex FPGA

A single full adder cell cannot be implemented on its own because there is no access to the carry-chain that joins the two LEs shown as point 'x' in figure 2.3. This has the repercussion that efficient [3:2] carry-save adders, a common carry free adder design, cannot be implemented efficiently on Virtex FPGAs.

### 2.4.2 Sub (subtraction)

True subtraction cannot be implemented efficiently on Virtex and Virtex-II FPGAs and so a two's complement system is used. The two's complement system involves

Chapter 2 Fixed-point

bit-inverting the operand to subtract, injecting a '1' into the carry-in (cIn) signal and then adding the two operands using a conventional ripple-carry adder. The LUT element needs to be configured with a logic function as shown in table 2.1.

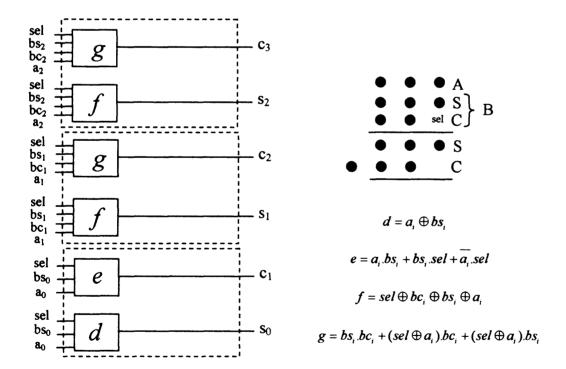

### 2.4.3 Add/sub (addition/subtraction)

The addition and subtraction components can be combined into one macro that can do both operations as determined by a single selection signal. A 'sel' (selection) signal forces subtraction when it is at the logical value '1', addition when it is '0' and feeds the carry-in input of the adder. The LUT element logic function is shown in table 2.1.

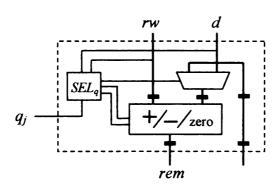

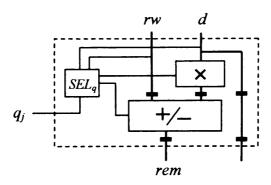

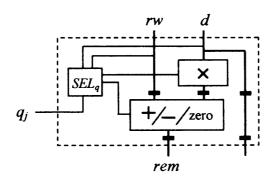

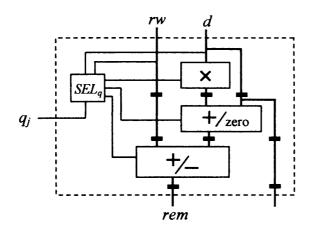

### 2.4.4 Add/sub/zero (addition/subtraction/addition of zero)

In the add/sub component there is a single input into the LUT element that is not used. This line can be used to force a 'no operation' or an 'addition of zero'. Therefore a useful component that allows the operations A+B, A-B or A+0 can be implemented. The LUT element logic function is shown in table 2.1.

#### 2.4.5 AddMux

Often when designing arithmetic components on FPGA the case where a choice of two values is to be added to another operand occurs. This can be pictured as an adder with a multiplexer on one of the inputs. A multiplexer consists of three inputs and an adder consists of two inputs. One of the adder inputs is fed by the multiplexer, thus four inputs are required for each bit, which fits into a LUT. The addMux component therefore calculates A+X or A+Y depending on the value of the 'sel' (selection) signal. Table 2.1 shows the LUT element logic function.

#### 2.4.6 SubMux

The subMux component is a variation on the addMux component. Instead of A+X or A+Y the component performs A-X or A-Y depending on the 'sel' signal. See table 2.1 for the LUT element logic function.

### 2.4.7 AddSubMuxConst

It is not possible to fit an AddSubMux component, which adds or subtracts a choice of two operands from a given operand, into one LUT column. This is because such a component requires a five input LUT function. However it is possible to create such a component if one of the operands to be subtracted or added is a constant and can be set at design time. The LUT function is then set at compile time and only a four input function is required to add/subtract a choice of a variable operand B or a constant operand K to/from a variable operand A. The component that performs this function is called an AddSubMuxConst component and the LUT element logic function for such a component is shown table 2.1.

### 2.4.8 Other configurations

There is scope to implement other types of adder that can blend logic functions that involve a particular input operand into the LUT used to implement the adder. This is a very useful way of reducing the delay and area of designs. Synthesis tools usually do not take advantage of this logic reduction technique and so it is advantageous to hand code macros to perform custom logic reduction functions.

| Component name | Number<br>of LUT<br>inputs | Input names             | Carry-<br>chain<br>input | Component function(s) | LUT function                                                                                                                                                                                                                                                                                                                     |

|----------------|----------------------------|-------------------------|--------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add            | 2                          | A, B,<br>cIn            | cIn                      | A+B                   | $a_i \oplus b_i$                                                                                                                                                                                                                                                                                                                 |

| Sub            | 2                          | A, B                    | '1'                      | A-B                   | $a_i \oplus \overline{b_i}$                                                                                                                                                                                                                                                                                                      |

| Add/sub        | 3                          | A, B,<br>sel            | sel                      | A+B, A-B              | $a_i \oplus b_i \oplus sel$                                                                                                                                                                                                                                                                                                      |

| Add/sub/zero   | 4                          | A, B,<br>sel,<br>zero   | sel                      | A+B, A-B,<br>A+0, A-0 | $a_{i}, \overline{b_{i}}, \overline{sel} + \overline{a_{i}}, \overline{b_{i}}, \overline{sel}, \overline{zero} + \overline{a_{i}}, \overline{b_{i}}, \overline{sel} + \overline{a_{i}}, \overline{sel}, \overline{zero} + \overline{a_{i}}, \overline{sel}, \overline{zero} + \overline{a_{i}}, \overline{sel}, \overline{zero}$ |

| AddMux         | 4                          | A, X,<br>Y, sel,<br>cIn | cIn                      | A+X, A+Y              | $a_i.x_i.\overline{sel} + \overline{a_i}.x_i.\overline{sel} + a_i.\overline{y_i}.sel + \overline{a_i}.y_i.sel$                                                                                                                                                                                                                   |

| SubMux         | 4                          | A, X,<br>Y, sel         | '1'                      | A-X, A-Y              | $\overline{a_i \cdot x_i \cdot sel} + a_i \cdot x_i \cdot \overline{sel} + a_i \cdot y_i \cdot sel + \overline{a_i \cdot y_i} \cdot sel$                                                                                                                                                                                         |

| AddSubMuxConst | 4                          | A, B,<br>sel,<br>const  | sel                      | A+B, A-B,<br>A+K, A-K | $(sel \oplus a_{i} \oplus b_{i}).\overline{const} + $ $(sel \oplus a_{i} \oplus k_{i}).const$                                                                                                                                                                                                                                    |

Table 2.1. The configuration details of various FPGA adder implementations

### 2.4.9 Compact serial adders

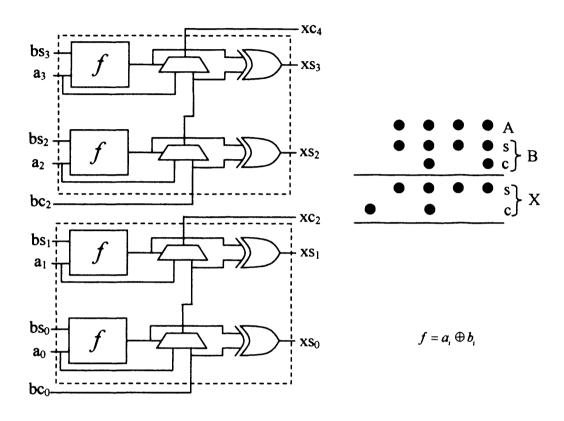

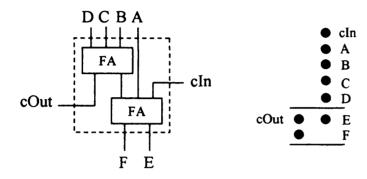

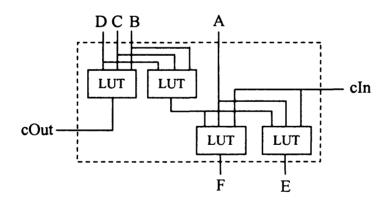

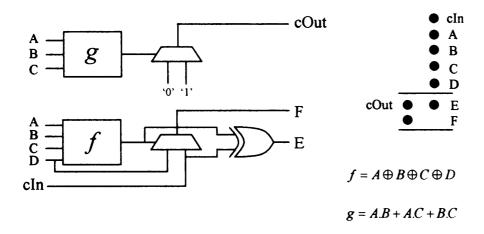

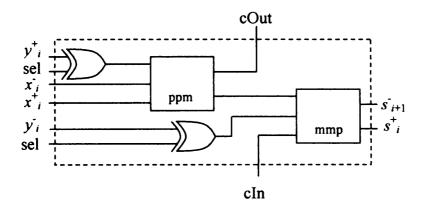

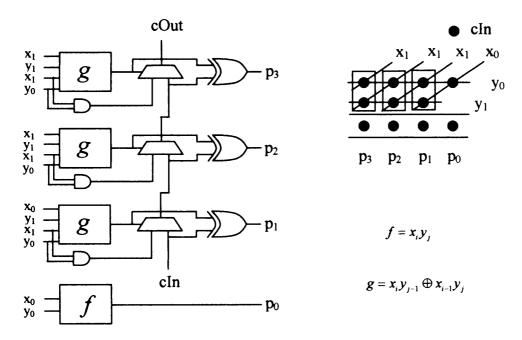

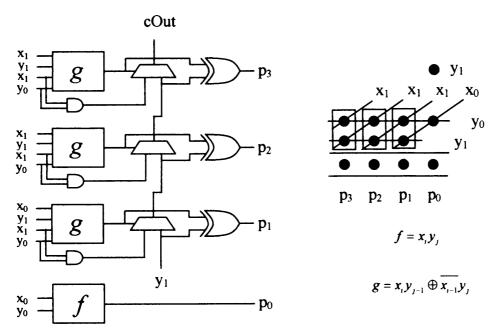

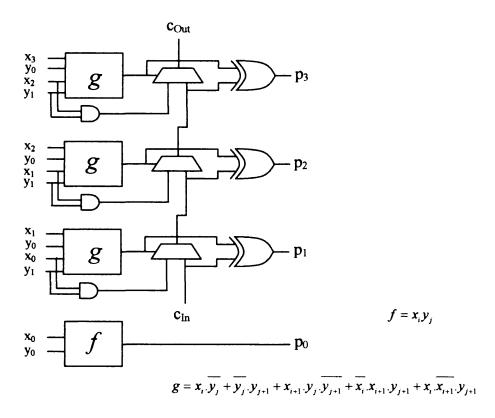

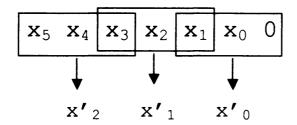

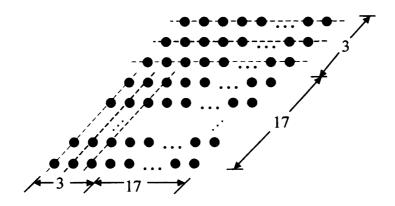

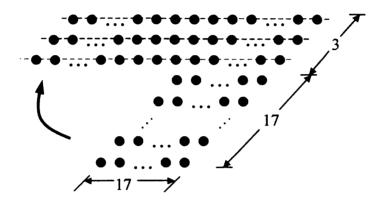

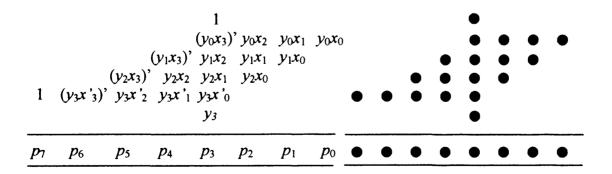

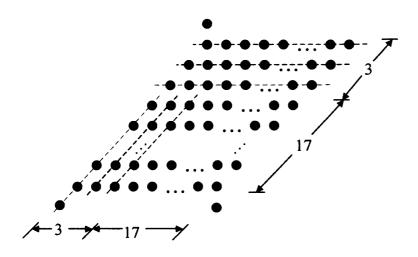

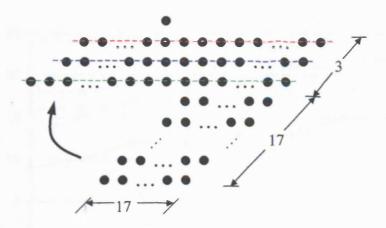

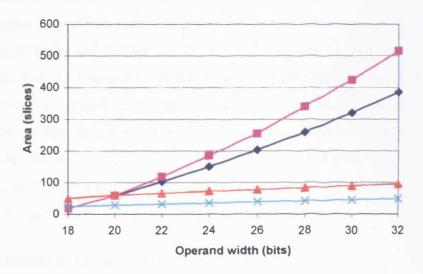

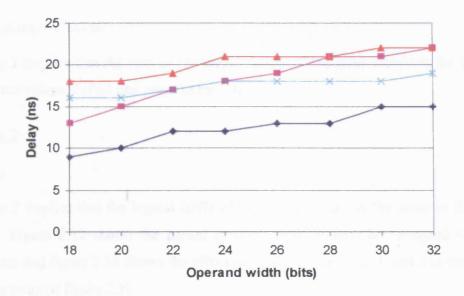

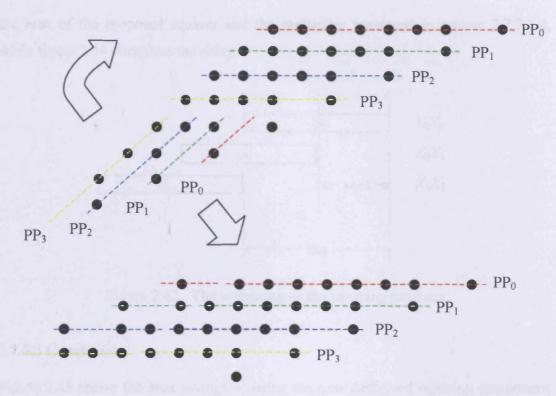

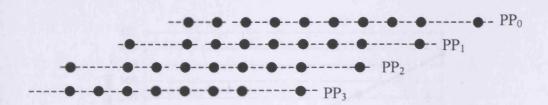

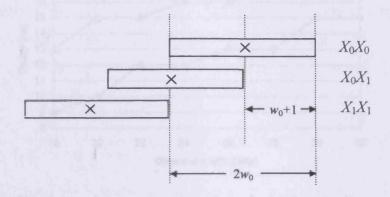

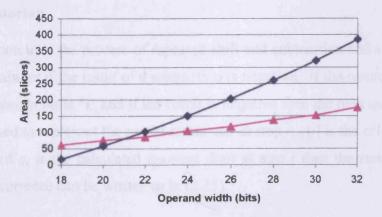

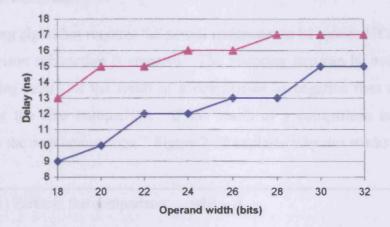

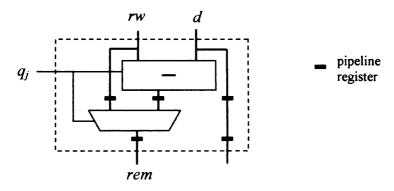

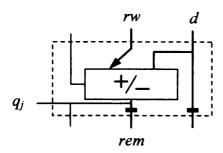

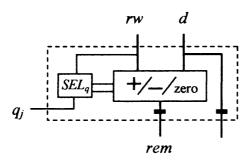

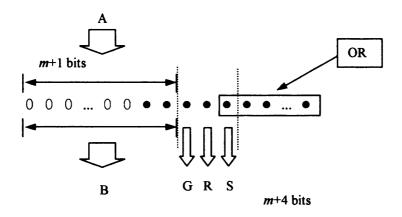

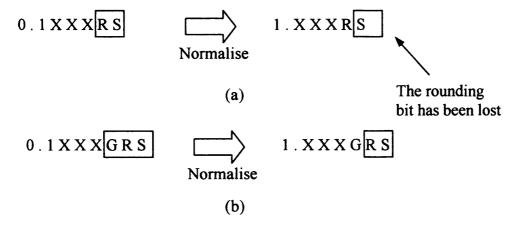

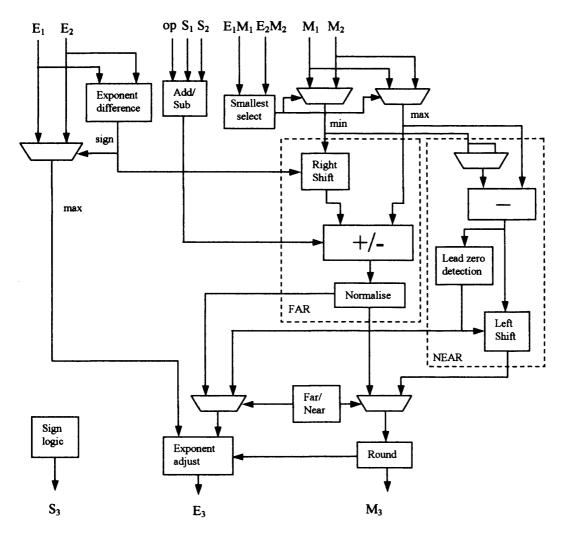

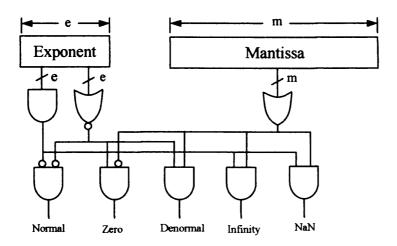

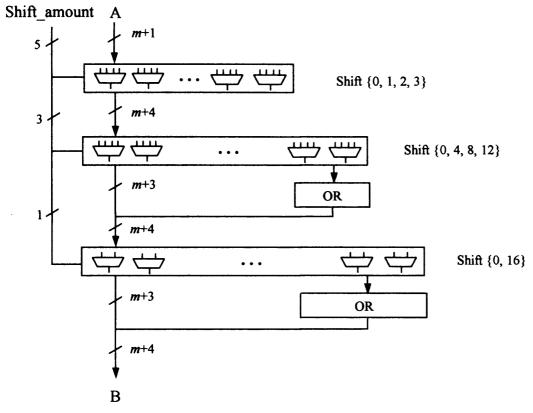

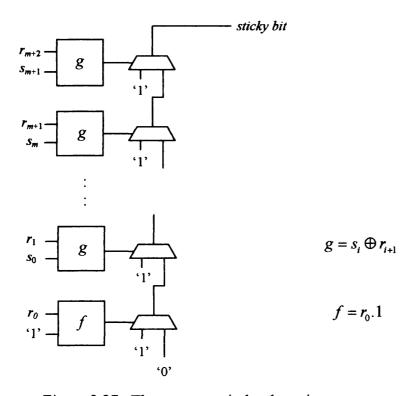

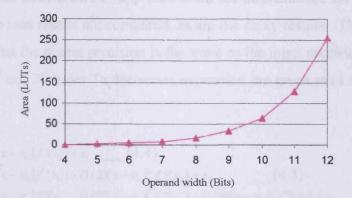

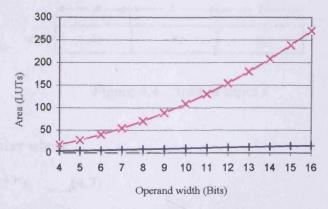

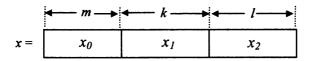

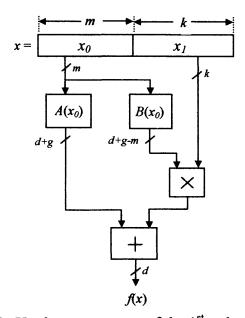

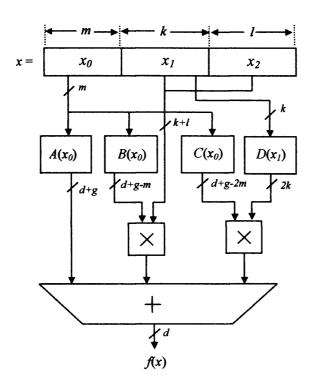

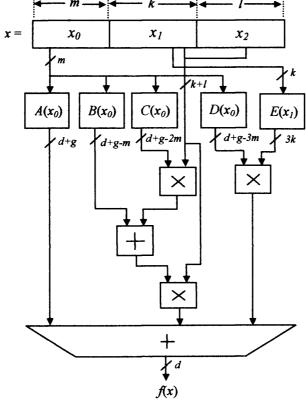

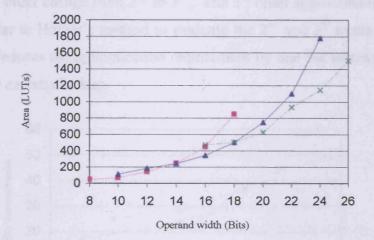

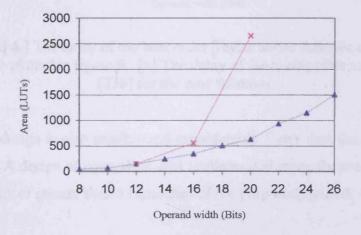

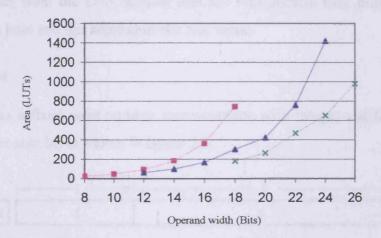

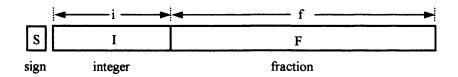

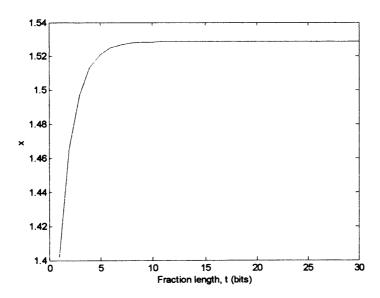

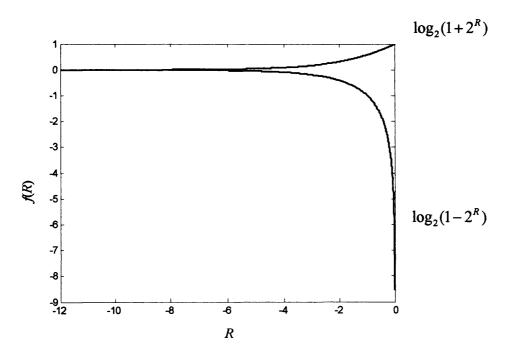

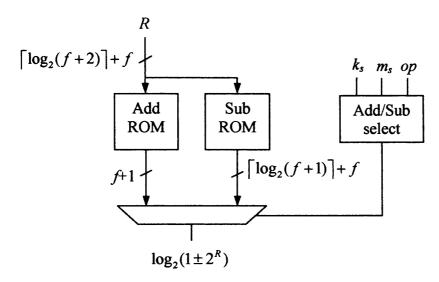

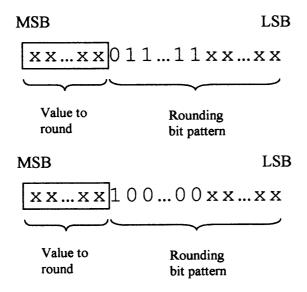

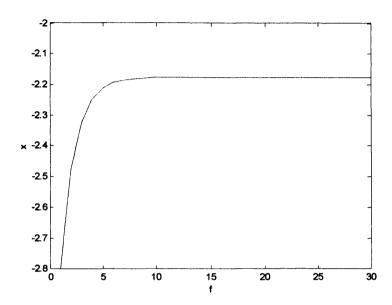

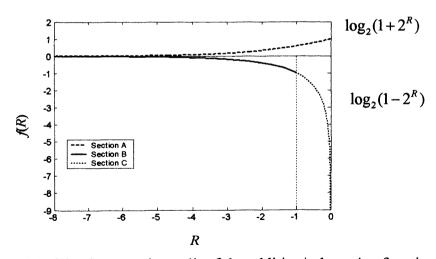

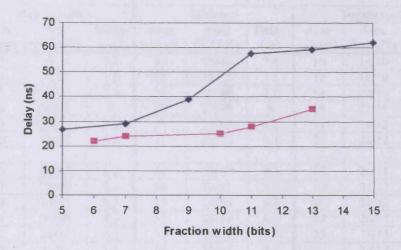

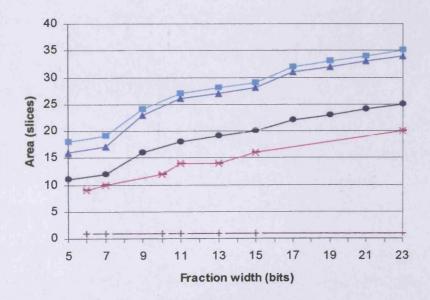

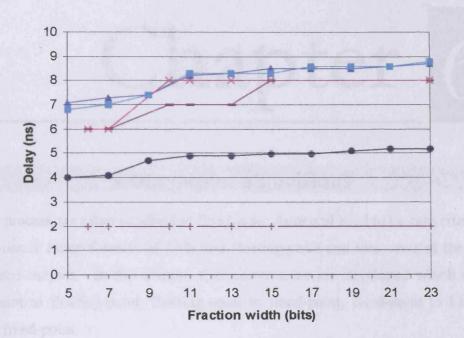

By performing an addition in a number of steps and reusing the same hardware in each step a compact adder can be produced. If we assume two operands A and B of length N that need to be added are supplied LSB first one bit at a time then a single full adder cell can be used to sum both operands, Smith [82] and Andraka [83] show FPGA implementations. N cycles are needed to sum both operands and such an